### Copyright © 1984, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## RATIO-INDEPENDENT ALGORITHMIC ANALOG TO DIGITAL CONVERSION TECHNIQUES

bу

P-W. Li

Memorandum No. UCB/ERL M84/66

20 August 1984

### RATIO-INDEPENDENT ALGORITHMIC ANALOG TO DIGITAL CONVERSION TECHNIQUES

by

P-W. Li

Memorandum No. UCB/ERL M84/66

20 August 1984

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720 Research sponsored by the National Science Foundation Grant ECS-8310442, and by the Intel Corporation.

# RATIO-INDEPENDENT ALGORITHMIC ANALOG TO DIGITAL CONVERSION TECHNIQUES

Ph. D.

Ping-Wai Li

Department of EECS

Chairman of Committee

#### **Abstract**

This thesis reports on an investigation on algorithmic analog to digital conversion techniques in achieving high resolution and linearity A/D converters, implemented using metal-oxide-semiconductor large scale integration. With this technique, high resolution converters can be realised within a small area.

A simple ratio-independent switching algorithm has been devised to overcome the gain error of MOS gain blocks that employs capacitor for the gain-setting. Using a delayed timing control scheme and a differential circuit implementation to cancel the charge injection from MOS transistors, high monotonicity and linearity can be achieved without the need for capacitor matching.

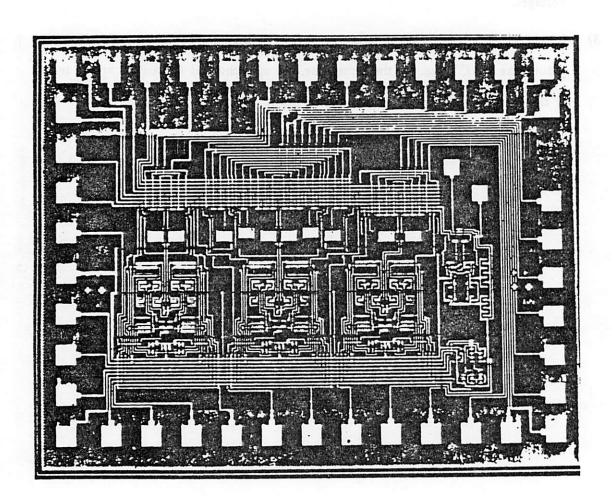

As a test vehicle an experimental integrated circuit has been fabricated using a 5-micron CMOS process. The converter showed monotonicity of 12 bits operating at a sampling frequency up to 8kHz. The integral linearity error was 3.2lsb. Total chip area for the analog circuit part of the converter was less than 2400mil<sup>2</sup>.

### TABLE OF CONTENTS

| Chapter 0 | Introduction                                          |

|-----------|-------------------------------------------------------|

| Chapter 1 | Algorithmic Analog to Digital Conversion Fundamentals |

| 1.1.      | Introduction                                          |

| 1.2.      | Successive Approximation Method for A/D Conversion    |

| 1.3.      | Algorithmic Analog to Digital Conversion Technique    |

| 1.3.1.    | Description of Conversion Technique                   |

| 1.4.      | An Implementation Example                             |

| 1.4.1.    | Mode of Operation                                     |

| 1.5.      | Sources of Error in Algorithmic A/D Converter         |

| 1.5.1.    | Quantizing the Analog Loop                            |

| 1.5.2.    | Sources of Errors in an MOS Implementation            |

| 1.5.2.1.  | Zeroth Order Error                                    |

| 1.5.2.2.  | First Order Error                                     |

| 1.5.2.3.  | Higher Order Error                                    |

| Chapter 2 | Ratio-Independent Circuit                             |

| 2.1.      | Introduction                                          |

| 2.2.      | Ratio-Independent Multiplication of a Signal          |

| 2.3.      | Problems                                              |

| 2.3.1.    | Finite Operational Amplifier Gain                     |

| 2.3.2.    | Operational Amplifier Input Voltage Offset            |

| 2.3.3.    | Charge Injection Effect                               |

| 2.3.3.1.  | Effect of Charge Injection                                    | 30 |

|-----------|---------------------------------------------------------------|----|

| 2.3.3.2.  | Cancellation of Signal Dependent Charge Injection             | 32 |

| 2.3.3.3.  | Cancellation of Charge Injection Offset                       | 32 |

| 2.3.3.4.  | Capacitance Voltage Coefficient Cancellation                  | 33 |

| 2.4.      | Ratio-Independent Multiply-by-Two Algorithm                   | 34 |

| 2.5.      | Ratio-Independent Sample/Hold                                 | 35 |

| Chapter 3 | Operational Amplifier Design                                  | 46 |

| 3.1.      | Introduction                                                  | 46 |

| 3.2.      | Motives                                                       | 46 |

| 3.3.      | Design Considerations                                         | 47 |

| 3.3.1.    | Gain Product of a Transistor                                  | 48 |

| 3.3.2.    | Cascoding of Transistors                                      | 49 |

| 3.3.3.    | Impact Ionization in MOS Transistors                          | 53 |

| 3.3.4.    | One Gain Stage Versus Two Gain Stage Design                   | 54 |

| 3.3.5.    | Slew Rate Considerations                                      | 57 |

| 3.3.6.    | Methods for Improving the Slew Rate                           | 58 |

| 3.4.      | Design of Operational Amplifier for the Converter             | 59 |

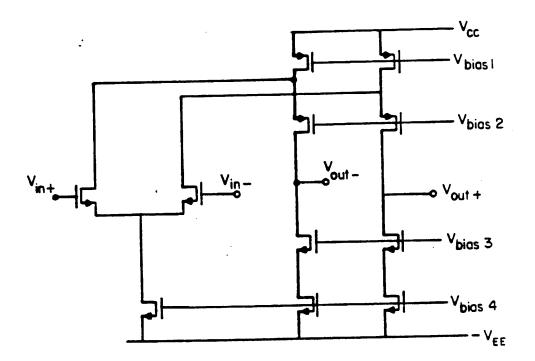

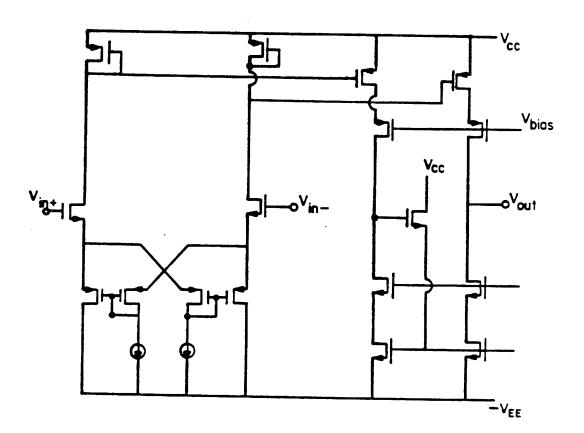

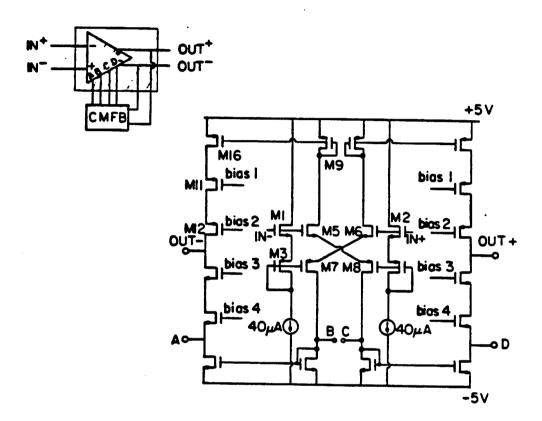

| 3.4.1.    | Circuit Description                                           | 60 |

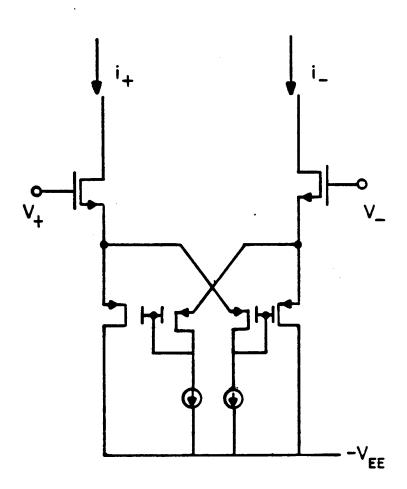

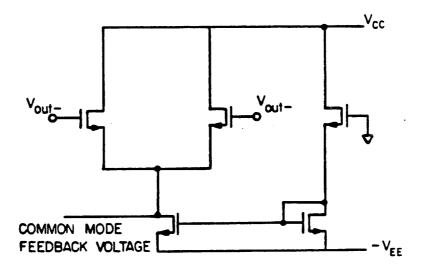

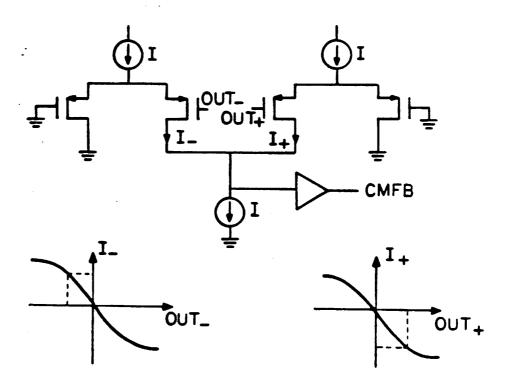

| 3.4.2.    | Common Mode Feedback Stage Design                             | 62 |

| 3.4.2.1.  | A Conventional Design                                         | 62 |

| 3.4.2.2.  | Balanced Common Mode Feedback Circuit Design                  | 63 |

| 3.4.3.    | Complete Operational Amplifier                                | 65 |

| Chapter 4 | Organization and Operational of the Algorithmic A/D Converter |    |

.

•

| ************ |                                                              |

|--------------|--------------------------------------------------------------|

| 4.1.         | Introduction                                                 |

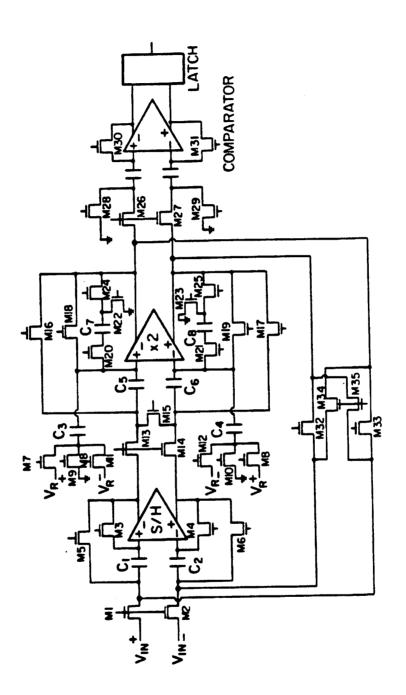

| 4.2.         | Description of the Converter Circuit                         |

| 4.3.         | Operation of the Converter                                   |

| 4.4.         | Control Logic for the Ratio-Independent Algorithmic A/D Con- |

| 4.4.1.       | Description                                                  |

| 4.4.2.       | Logic Implementation                                         |

| 4.5.         | Noise in the Ratio-Independent Algorithmic A/D Converter     |

| 4.5.1.       | Sources of Noise in Algorithmic A/D Converter                |

| 4.5.1.1.     | kT/C Noise in MOS Circuits                                   |

| 4.5.1.2.     | Operational Amplifier Noise                                  |

| 4.5.2.       | Noise Performance of the Multiply-by-Two and Sample/Hold     |

| Amplifi      | er                                                           |

| 4.5.3.       | Noise Cancellation Techniques                                |

| Chapter 5    | Experimental Results                                         |

| 5.1.         | Introduction                                                 |

| 5.2.         | Description of the CMOS Process                              |

| 5.3.         | Description of the Experimental Chip                         |

| 5.4.         | Control Circuit                                              |

| 5.5.         | Test Setups                                                  |

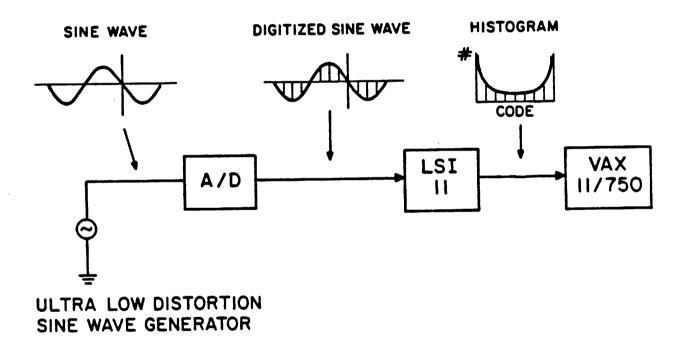

| 5.5.1.       | Code Density Test                                            |

| 5.6.         | Experimental Results and Discussions                         |

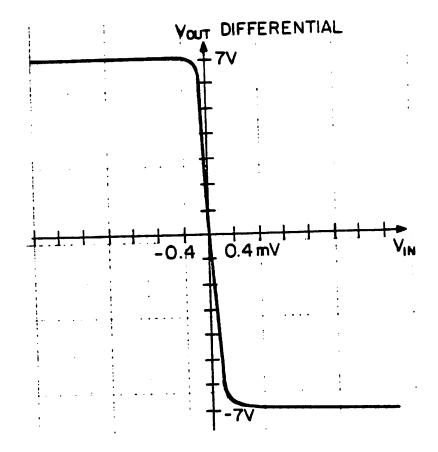

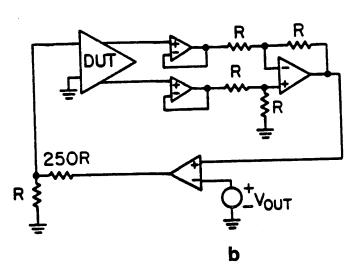

| 5.6.1.       | Operational Amplifier                                        |

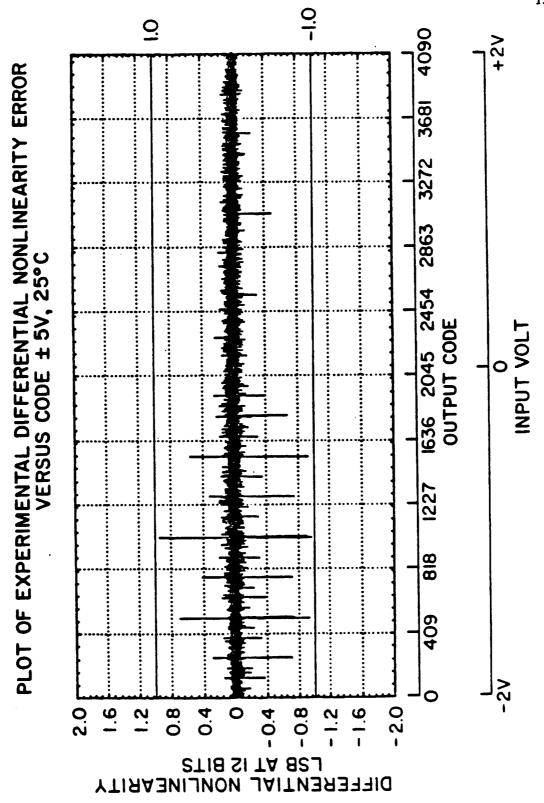

| 5.6.2.     | A/D Converter                | 126 |

|------------|------------------------------|-----|

| 5.7.       | Suggestions for Improvements | 128 |

| Chapter 6  | Conclusion                   | 138 |

| Appendix I | Berkeley CMOS Process        | 140 |

| References | ·                            | 152 |

# RATIO-INDEPENDENT ALGORITHMIC ANALOG TO DIGITAL CONVERSION TECHNIQUES

by

P-W. Li

Memorandum No. UCB/ERL M84/66

20 August 1984

**ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

Research sponsored by the National Science Foundation Grant ECS-8310442, and by the Intel Corporation.

# RATIO-INDEPENDENT ALGORITHMIC ANALOG TO DIGITAL CONVERSION TECHNIQUES

Ph. D.

Ping-Wai Li

Department of EECS

Abstract

This thesis reports on an investigation on algorithmic analog to digital conversion techniques in achieving high resolution and linearity A/D converters, implemented using metal-oxide-semiconductor large scale integration. With this technique, high resolution converters can be realised within a small area.

A simple ratio-independent switching algorithm has been devised to overcome the gain error of MOS gain blocks that employs capacitor for the gain-setting. Using a delayed timing control scheme and a differential circuit implementation to cancel the charge injection from MOS transistors, high monotonicity and linearity can be achieved without the need for capacitor matching.

As a test vehicle an experimental integrated circuit has been fabricated using a 5-micron CMOS process. The converter showed monotonicity of 12 bits operating at a sampling frequency up to 8kHz. The integral linearity error was 3.2lsb. Total chip area for the analog circuit part of the converter was less than 2400mil<sup>2</sup>.

### TABLE OF CONTENTS

| Chapter 0 | Introduction                                          |

|-----------|-------------------------------------------------------|

| Chapter 1 | Algorithmic Analog to Digital Conversion Fundamentals |

| 1.1.      | Introduction                                          |

| 1.2.      | Successive Approximation Method for A/D Conversion    |

| 1.3.      | Algorithmic Analog to Digital Conversion Technique    |

| 1.3.1.    | Description of Conversion Technique                   |

| 1.4.      | An Implementation Example                             |

| 1.4.1.    | Mode of Operation                                     |

| 1.5.      | Sources of Error in Algorithmic A/D Converter         |

| 1.5.1.    | Quantizing the Analog Loop                            |

| 1.5.2.    | Sources of Errors in an MOS Implementation            |

| 1.5.2.1.  | Zeroth Order Error                                    |

| 1.5.2.2.  | First Order Error                                     |

| 1.5.2.3.  | Higher Order Error                                    |

| Chapter 2 | Ratio-Independent Circuit                             |

| 2.1.      | Introduction                                          |

| 2.2.      | Ratio-Independent Multiplication of a Signal          |

| 2.3.      | Problems                                              |

| 2.3.1.    | Finite Operational Amplifier Gain                     |

| 2.3.2.    | Operational Amplifier Input Voltage Offset            |

| 2.3.3.    | Charge Injection Effect                               |

| 2.3.3.1.  | Effect of Charge Injection                                    |

|-----------|---------------------------------------------------------------|

| 2.3.3.2.  | Cancellation of Signal Dependent Charge Injection             |

| 2.3.3.3.  | Cancellation of Charge Injection Offset                       |

| 2.3.3.4.  | Capacitance Voltage Coefficient Cancellation                  |

| 2.4.      | Ratio-Independent Multiply-by-Two Algorithm                   |

| 2.5.      | Ratio-Independent Sample/Hold                                 |

| Chapter 3 | Operational Amplifier Design                                  |

| 3.1.      | Introduction                                                  |

| 3.2.      | Motives                                                       |

| 3.3.      | Design Considerations                                         |

| 3.3.1.    | Gain Product of a Transistor                                  |

| 3.3.2.    | Cascoding of Transistors                                      |

| 3.3.3.    | Impact Ionization in MOS Transistors                          |

| 3.3.4.    | One Gain Stage Versus Two Gain Stage Design                   |

| 3.3.5.    | Slew Rate Considerations                                      |

| 3.3.6.    | Methods for Improving the Slew Rate                           |

| 3.4.      | Design of Operational Amplifier for the Converter             |

| 3.4.1.    | Circuit Description                                           |

| 3.4.2.    | Common Mode Feedback Stage Design                             |

| 3.4.2.1.  | A Conventional Design                                         |

| 3.4.2.2.  | Balanced Common Mode Feedback Circuit Design                  |

| 3.4.3.    | Complete Operational Amplifier                                |

| Chapter 4 | Organization and Operational of the Algorithmic A/D Converter |

.

.

| ************* | ·                                                           |

|---------------|-------------------------------------------------------------|

| 4.1.          | Introduction                                                |

| <b>3.2.</b>   | Description of the Converter Circuit                        |

| .3.           | Operation of the Converter                                  |

| .4.           | Control Logic for the Ratio-Independent Algorithmic A/D Con |

| verter .      | ***************************************                     |

| 4.4.1.        | Description                                                 |

| 4.4.2.        | Logic Implementation                                        |

| 5.            | Noise in the Ratio-Independent Algorithmic A/D Converter    |

| 4.5.1.        | Sources of Noise in Algorithmic A/D Converter               |

| 4.5.1.1.      | kT/C Noise in MOS Circuits                                  |

| 4.5.1.2.      | Operational Amplifier Noise                                 |

| 4.5.2.        | Noise Performance of the Multiply-by-Two and Sample/Hold    |

| Amplifi       | ет                                                          |

| 4.5.3.        | Noise Cancellation Techniques                               |

| napter 5      | Experimental Results                                        |

| l <b>.</b>    | Introduction                                                |

| 2.            | Description of the CMOS Process                             |

| 3.            | Description of the Experimental Chip                        |

| 4.            | Control Circuit                                             |

| 5.            | Test Setups                                                 |

| 5.5.1.        | Code Density Test                                           |

| 5.            | Experimental Results and Discussions                        |

| 5.6.1.        | Operational Amplifier                                       |

.

| 5.6.2.     | A/D Converter                | 126 |

|------------|------------------------------|-----|

| 5.7.       | Suggestions for Improvements | 128 |

| Chapter 6  | Conclusion                   | 138 |

| Appendix I | Berkeley CMOS Process        | 140 |

| References | ·                            | 152 |

·

.

•

#### CHAPTER 0

#### Introduction

The rapid development of communication and data acquisition systems has demanded the integration of more analog signal processing circuitry on the same silicon chip. As a result, more area-efficient realization of given circuit functions have to be developed. Recent advances in analog MOS integrated circuits have fundamentally influenced the design approach for these circuits. Whereas resistor and transistor ratios are employed in the analog bipolar technology to define the accuracy of a circuit function, their functions are substituted by the MOS capacitor in analog MOS circuit. Not only does the MOS capacitor give better matching within the same area, it also possesses better stability and less voltage dependence than the monolithic resistor. This makes it very suitable for the integration of precision analog function on the silicon chip. One example of this new development is the switched capacitor filter. Instead of relying on accurate RC time constants, which is generally not available in the integrated circuit technology to define the frequency characteristics of the filter, it uses an accurately defined clock frequency and capacitors to realize precise time constants. The external clock frequency can be very accurate if it is derived from a crystal. With proper precaution, the capacitors can be matched to within 0.1%. The frequency response of switched capacitor filters are therefore relatively precise and they have found wide acceptance in voice band and even higher frequency communication systems. Another application of the ratioed capacitor in the data acquisition system is the charge redistribution technique which uses an array of ratioed capacitors to affect an analog to digital conversion. By

switching the binary ratioed capacitors between ground and the reference voltage, charges are subtracted or added to the signal charge and following a successive approximation procedure the digital representation of the signal can be found. This type of converter is capable of achieving 10 bit resolution and linearity with a conventional MOS technology.

Because of the matching requirement in the capacitors, they require comparably large geometrical areas. To this there are three disadvantages. Firstly the corresponding area of the circuit increases. Secondly the large capacitance slows down the circuit due to effects such as the RC discharge time constant or the settling time of MOS operational amplifiers. Finally and most importantly, the accuracy of the circuit is seriously limited by the matching accuracy of capacitors, which due to lithographical and etching error in a modern MOS process, often lies in the 8-9 bit region. This dissertation is aimed at the realization of precise analog functions using unratioed capacitors. Efforts have been concentrated in developing techniques which allow exact integral gain values to be obtained from MOS gain blocks without the used of matched capacitors. Other effects that have been investigated are related to circuit errors arising from charge injection from MOS transistors. As a verification of the techniques developed, a high resolution algorithmic analog to digital converter has been implemented and fabricated in CMOS technology. Here a ratio-independent switching algorithm is utilized to correct for the capacitor mismatch error in setting exact integral gain values with MOS gain blocks. Also it is shown how a combination of control signal timing and differential circuit can be used beneficially to cancel the charge injection from MOS transistor. A CMOS operational amplifier with a balanced common mode feedback stage ensures fast settling time and therefore moderately high speed conversion rate of the converter.

This dissertation is organized as follows. Chapter 1 describes in detail the principle and operation of the algorithmic A/D converter. The algorithmic conversion technique is analyzed in context to the successive approximation conversion technique. Following this, the various limitations or sensitivity problems of the converter are studied based on an earlier implementation.

In chapter 2, a practical implementation of the ratio-independent multiplication technique is given. This technique is essential to the operation of the algorithmic converter since it provides gain accuracy to the converter gain blocks previously unattainable by ratioed passive elements. However it is then shown that nonidealities still exist which perturbs the accuracy of the circuit. Amongst them the most critical is the charge injection effect of MOS transistor switches. To alleviate this effect, the differential circuit configuration and a delayed timing control scheme are developed. They allow a first order cancellation of the charge injection effect.

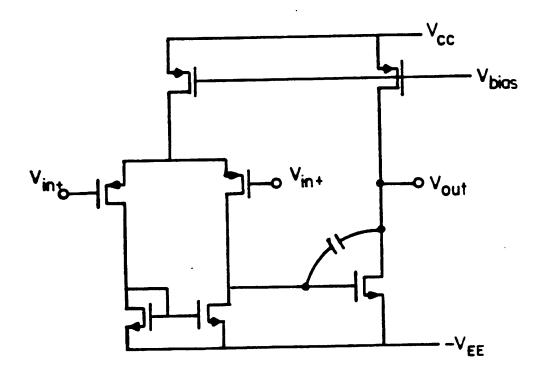

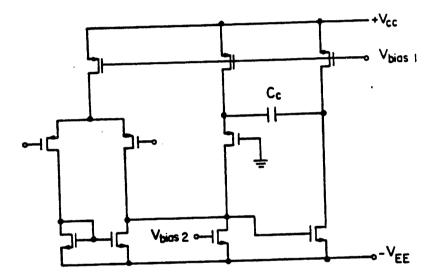

Chapter 3 depicts the design of the high speed high gain CMOS operational amplifier used for the converter. The advantages of using a single gain stage architecture are explained. An improved common mode feedback circuit featuring two balanced MOS differential pairs is used.

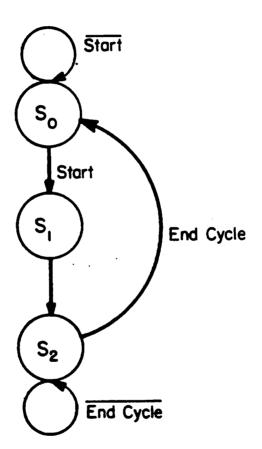

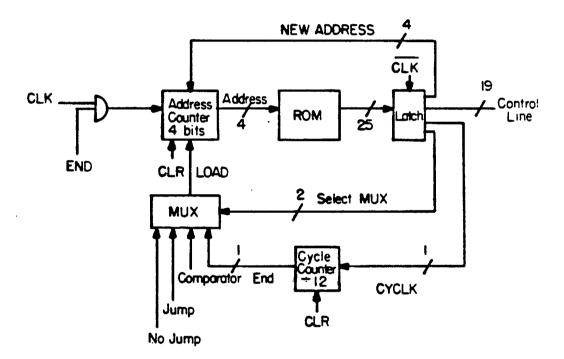

In chapter 4 the full implementation of the converter is given together with a detailed description of the individual stages involved. For experimental purpose, the analog circuit is controlled externally by a microprogrammable sequencer. But an on-chip ROM control scheme is proposed which uses minimum area. The noise property of the converter is also briefly discussed.

Chapter 5 gives some experimental results on a test circuit used to demonstrate the design concepts. It is an algorithmic A/D converter fabricated with a  $5\mu$ m CMOS technology. It achieves 12 bit resolution and 10 bit linearity at a conversion rate of 8 kHz.

#### CHAPTER 1

### Algorithmic Analog To Digital Conversion Fundamentals

#### 1.1. Introduction

In this chapter the concept of the algorithmic A/D converter is reviewed. The successive approximation technique for analog to digital conversion is introduced and compared to the algorithmic method. An example of an implementation of the algorithmic A/D converter in a metal gate CMOS technology will be given. With this implementation example, some of the pertinent variables in the converter are studied and effects of their nonidealities on the characteristics the converter investigated. Before we embark upon the task of describing the algorithmic A/D conversion method, we shall first explain the operation of the successive approximation method for A/D conversion. It will become apparent that the algorithmic A/D conversion method is nothing more than a successive approximation in disguise.

#### 1.2. Successive Approximation Method for A/D Conversion

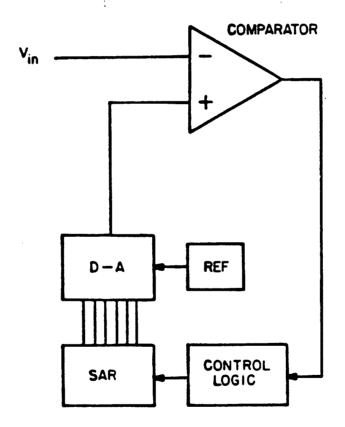

The successive approximation method of analog to digital conversion is widely used for high resolution and medium to high speed conversion[1]. The converter consists of a comparator, a digital to analog converter (DAC), a voltage reference, a successive approximation register (SAR) and control logic as shown in Fig 1.1. The conversion is achieved by comparing successively the input signal  $V_{in}$  with the sum of binary fractions of the reference generated by the DAC. The conversion usually starts by setting the most

significant bit (MSB) of the DAC and comparing the output with  $V_{in}$ . If this output is larger than  $V_{in}$  then the most significant bit of the input is 1, otherwise the MSB of the DAC is returned to 0 and the corresponding MSB of the input is 0 as well. This process is continued for each of the bits sequentially, keeping all the previously set or unset bits, until the desired accuracy has been reached. The bit pattern of the DAC then gives the digital representation of the input signal. Thus to decide n bits of digital data, n basic cycles are required. The basic cycle consists of a settling time for the DAC, the decision time for the comparator and the delay time through the logic. Mathematically, the procedure can be described as follows. Let the digital representation of an analog signal  $V_{in}$  be  $d_0 d_1, \dots, d_{n-1}$  where  $d_i \in \{0,1\}$ . The analog and digital representations are related by the equation:

$$V_{in} = \left(\frac{d_0}{2} + \frac{d_1}{2^2} + \dots + \frac{d_{n-1}}{2^n}\right) V_{ref} + \epsilon_n$$

(1.1)

where

Vin : input voltage

$d_0 d_1 \cdots d_{n-1}$ : digital representation of the signal; assumes the value 0 or 1

$V_{ref}$ : reference voltage

$\epsilon_n$ : quantization error

This equation expresses quantatively how the analog input signal can be represented with respect to the reference voltage by a string of binary digits. The last term  $\epsilon_n$ , commonly known as the quantization error, gives the error between the digital representation of the signal and the actual value of the signal. Its magnitude is

$$-\frac{V_{ref}}{2^{n+1}} < \epsilon_n < \frac{V_{ref}}{2^{n+1}}$$

so that the error of the digital approximation is always bounded.

To derive the MSB, we subtract the quantity  $\frac{V_{ref}}{2}$  from both sides of equation (1.1).

$$V_{in} - \frac{V_{ref}}{2} = \left(\frac{(d_0 - 1)}{2} + \frac{d_1}{2^2} + \dots + \frac{d_{n-1}}{2^n}\right) V_{ref} + \epsilon_n$$

(1.2)

Now it is true that

$$\frac{1}{2} > \frac{1}{2^2} + \frac{1}{2^3} + \dots + \frac{1}{2^n}$$

(1.3)

Therefore if  $d_0$  is 0, the right hand side of equation (1.2) would become negative. If we apply this argument to all the bits the digital representation can be easily obtained.

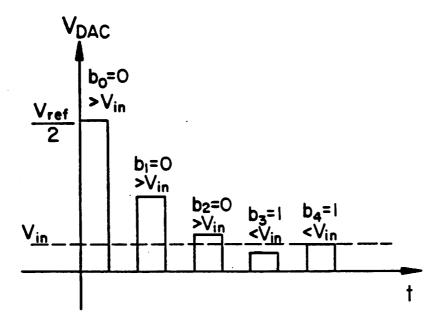

An example of an actual conversion is shown in the following figure. It depicts the output of the DAC as a function of time during a conversion. Take for example a signal of magnitude equal to 1/10 of the reference and it is required to convert to 5 bit accuracy. In the first cycle, the most significant bit of the DAC is set and the resultant output voltage  $V_{o,1} = \frac{V_{ref}}{2}$  is compared to the signal. Since it is larger than the input signal, this bit is not kept in the DAC. In the next cycle, the next MSB is set, changing the output voltage of the DAC to  $\frac{V_{ref}}{4}$ . This process is continued until the 4th bit is set and tested to be smaller than the input voltage. It is therefore kept and the 5th bit set and also kept in the last cycle. Thus all 5 bits have been obtained and the result is equal to 00011.

#### 1.3. Algorithmic Analog to Digital Conversion Technique

The algorithmic, also known as the cyclic or recirculating analog to digital conversion technique has been realized in various forms since the 1960's. It was first constructed

in a partially integrated form by Tom Hornak in 1975, using an external transformer to realize the multiplication of two[2]. Then McCharles et al integrated the analog portion of the converter using a metal gate CMOS technology[3] in 1978. Using matched capacitors, 8-9 bit of accuracy could be achieved. The first high precision converter using this technique was done by Harris Semiconductor where precise gain values were set using trimming technique on thin film resistors[4].

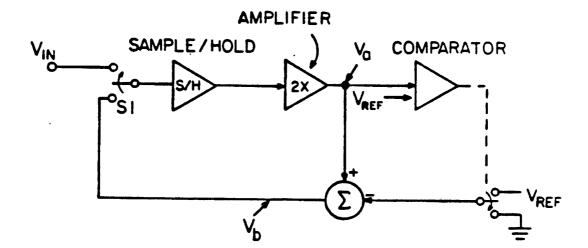

A block diagram of the implementation of the algorithmic analog-to-digital converter is shown in Fig. 1.3. It consists of an analog loop which contains:

- 1) sample/hold block

- 2) multiply-by-two block

- 3) reference subtraction circuit

- 4) comparator

There are also two switches  $S_1$  and  $S_2$ .  $S_1$  switches the input of the sample/hold block between the input path and the loop path.  $S_2$  controls (symbolically) the selection between reference and ground for the subtraction circuitry. The signal to be converted is first introduced into the loop by means of  $S_1$  and the sample/hold. From here, it would be cycled through the analog loop as often as the number of bits are required from the conversion.

From this implementation, the following characteristics of the algorithmic A/D converter can be identified:

the associated hardware is relatively simple. Instead of having to derive the n exactly ratioed references, only two precision elements are needed, i.e. both the sample/hold block and the multiply-by-two blocks must have exact gains of 1 and 2 respectively.

- 2) The converter possesses inherently the sample/hold function.

- 3) It possesses the so called floating point capability. The input signal can be amplified by a factor of 2<sup>m</sup> before the A/D conversion begins with m being an integer. This is done by cycling the signal in the analog loop, multiplying it repeatedly without doing an A/D conversion. This property makes the algorithmic A/D converter valuable e.g. in multiplexed operations where signal with different dynamic ranges must be converted into digital data.

#### 1.3.1. Description of the Conversion Technique

The conversion technique will be described using the restoring algorithm. At the start of the conversion, the input signal is sampled onto the sample/hold amplifier through the switch  $S_{in}$ . This signal is then passed onto the precision gain block where it is multiplied by the exact factor of 2. To extract the digital information from this analog signal, the loop signal, denoted by  $V_x$  in Fig. 1.3, is compared to the reference. If it is larger, then the first bit is set to an 1 and the reference is subtracted off from this signal. Otherwise the first bit is set to an 0 and the loop signal is passed on unchanged for the second bit conversion. Thus the A/D conversion process is continued in this manner until the desired number of bits is obtained. It can be seen that the digital information comes out in a serial pattern, starting with the most significant bit.

To see that this process indeed performs the analog-to-digital conversion that is wanted, consider the same equation:

$$V_{in} = (\frac{d_0}{2} + \frac{d_1}{2^2} + \cdots + \frac{d_{n-1}}{2^{n-1}})V_{rej} + \epsilon_n$$

In a successive approximation determination of the digital information, the signal is compared successively to different terms on the right hand side of equation (1.1) beginning with the first or numerically largest term, i.e.  $d_0 \frac{V_{ref}}{2}$ . If the result is positive, the difference is kept for the next comparison. Otherwise, the original signal is kept for the next comparison. By repeating this process, the bits are determined individually until the desired resolution is reached.

By rearranging equation (1.1) in another form, a description of the algorithmic A/D conversion technique can be derived. This is done by multiplying equation (1.1) on both side by 2 and moving the term  $d_0$  to the left side of the equation.

$$2(V_{in} - \frac{V_{ref}}{2}) = ((d_0 - 1) + \frac{d_1}{2} + \cdots + \frac{d_{n-1}}{2^{n-2}})V_{ref} + 2\epsilon_n$$

(1.4)

the first bit can be determined if the sign of left hand side of equation can be tested. If it is positive, then  $d_o$  is 1 and the equation is kept in the same form. Otherwise it is 0, in which case the subtraction will be annulled. In the same equation the quantization error or equivalently the comparator window error is also doubled. This has the effect that as the conversion proceeds, comparator error has less and less effect on the characteristics of the conversion. Similarly for the second bit,

$$2(2(V_{in} - d_0 \frac{V_{ref}}{2}) - \frac{V_{ref}}{2}) = ((d_1 - 1) + \frac{d_2}{2} + \cdots + \frac{d_{n-1}}{2^{n-3}})V_{ref} + 2^2 \epsilon_n (1.5)$$

The bits are extracted following this scheme of multiplication by two and compared until  $d_{n-1}$  is obtained through the equation:

$$2(2(...2(V_{in} - d_0 \frac{V_{ref}}{2}) - d_1 \frac{V_{ref}}{2})...) - d_{n-2} \frac{V_{ref}}{2}) - d_{n-1} V \frac{ref}{2}) = 2^n \epsilon (1.6)$$

Therefore the algorithmic A/D conversion technique requires 1 comparison per bit of

conversion, completely analogous to the successive approximation method. Also it is less sensitive to comparator error during the conversion. However there is an additional time delay involved in moving the signal through the analog loop.

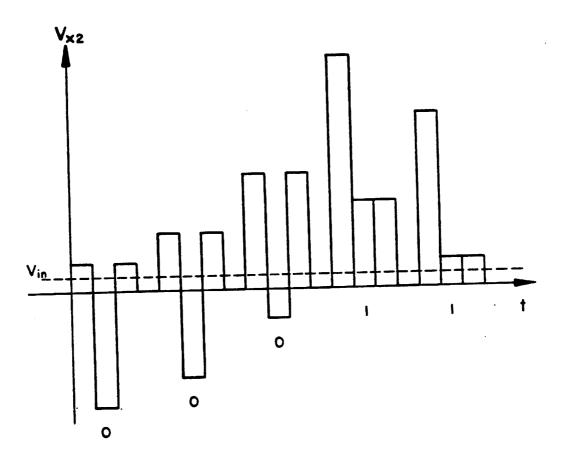

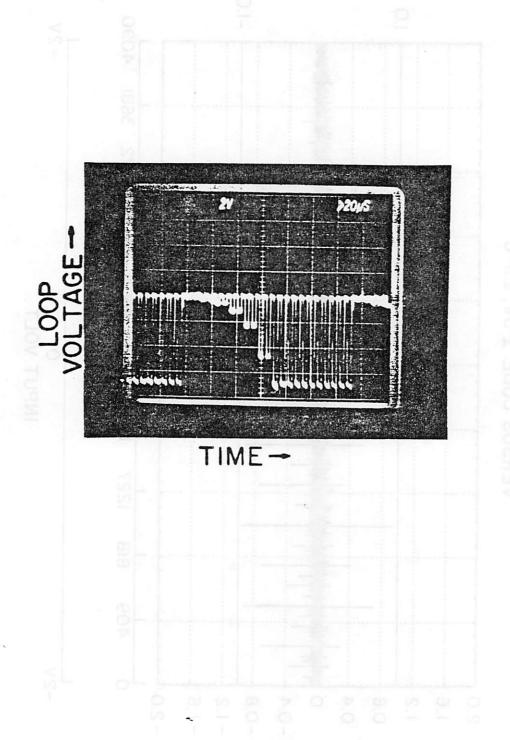

An example of the waveform of the multiply-by-two amplifier as a function of time is shown in Fig 1.4. In the first cycle, the input signal is multiplied by 2 and the reference voltage is subtracted off. If the result is positive, then this loop voltage is kept for the next conversion sequence. The conversion continues until the bit pattern is again obtained.

#### 1.4. An implementation example

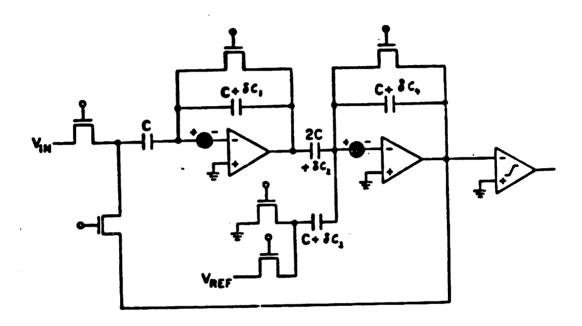

Fig. 1.5 illustrates an implementation of the algorithmic A/D converter with a metal gate CMOS technology[5]. The sample/hold and the multiply-by-two blocks are realized using MOS operational amplifiers and matched capacitors as precision feedback network. The reference subtraction circuit has been incorporated into the multiply-by-two amplifier by an extra capacitor  $C_5$  attached to the summing node of the operational amplifier. NMOS transistor switches  $T_1 - T_6$  form the interconnection paths closing the analog loop. They are be controlled by simple logic. With this circuit configuration, the signal is compared to the reference by first forming their difference and comparing to zero or ground. One of the advantages is that either the restoring or the non-restoring algorithms can be applied. Another is that it simplifies the design of the comparator because usually the reference is located very near to the voltage supply and if the signal is compared directly to the reference, the comparator must have a large input common mode voltage range. In this case, the large common mode voltage swing is avoided.

#### 1.4.1. Mode of operation

Assuming that the operational amplifiers are ideal, the input signal is introduced into the loop by turning on switch  $T_1$  and  $T_2$ ,  $T_2$  puts operational amplifier 1 into a unity feedback mode which establishes a quiescent voltage on the negative summing node equal to ground. At the same time, the input signal voltage is stored across  $C_1$ . Next, T<sub>1</sub>T<sub>2</sub> are turned off, isolating the summing node of operational amplifier 1. Simultaneously  $T_6 T_3$  are turned on. This nulls out operational amplifier 2. At the same time, one plate of capacitor  $C_1$  is being connected to ground. Thus the signal is transferred to the output of operational amplifier 1 which charges up capacitor C<sub>3</sub>. Now instead of first multiplying the signal by two and then compare it to the reference voltage, the reference voltage is subtracted simultaneously during the multiplication process. The comparator would then decide whether the original signal should be restored or the difference signal  $2V_{in} - V_{ref}$  be kept. This sequence of operations can be accomplished by turning on  $T_{5}$ , which displaces a charge through  $C_{4}$  representing the reference voltage. The comparator now makes the decision. If the signal is to be restored, the plate of  $C_5$  would be returned to ground from  $V_{ref}$ . Otherwise, the capacitor plate is kept at  $V_{ref}$ . In either case, the loop signal have been stored on  $C_1$  and by simply nulling operational amplifier 2 again, this signal can then be holded in operational amplifier 1 for the next conversion cycle. The rest of the conversion can be carried out in a similar fashion. Each bit conversion requires 2 or 3 operational amplifier settling times  $\tau$ . Let  $\tau$  determine the clock cycle, the worst case conversion time for n bits is  $3n \tau$ .

#### 1.5. Sources of Error in Algorithmic A/D converter

In the previous discussion and the implementation example, it has been assumed that the building blocks of the algorithmic converter were ideal. In practice, nonidealities occur which seriously affect the transfer characteristics of the converter. The nature of these nonidealities depends on the technique and the technology used to implement the converter. In the following section, a generalized method for quantifying the analog loop property shall be given which is similar to the analysis of the distortion in a nonlinear circuit by means of power series[6]. An understanding of this method gives some insight into the operation of the algorithmic converter and can provide some correlation between the error sources and experimental results obtained by the code density test[7].

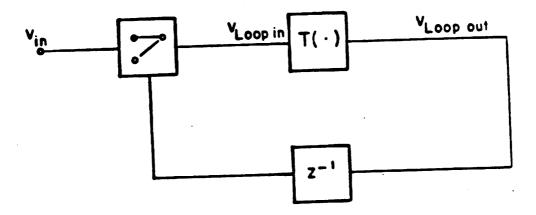

#### 1.5.1. Quantizing The Analog Loop

The quantization method consists in regrouping the building blocks into another set of building blocks as shown in Fig. 1.6. The block designated by  $z^{-1}$  is an analog delay block which has a unity gain and provides one clock cycle of delay to the analog signal. This is necessary because a direct connection between the input and output of an analog gain block in this case is not possible. The other block describes the analog loop transfer function  $T(V_I)$ . It describes the combined transfer characteristics of the multiply-by-two and the sample/hold amplifier. It is defined as

$$T\left(V_{t}\right) = \frac{V_{o}}{V_{t}} \tag{1.7}$$

and it can be expanded in a Taylor series

$$T(V_{i}) = \frac{e_{o}}{V_{i}} + (2 - e_{1}) + e_{2}V_{i} + e_{3}V_{i}^{2} + \cdots$$

(1.8)

where  $e_i$  is the ith order error in the loop transfer function. The effect of noise has not

been included in this loop transfer function. It can be described by the addition of a stochastic function to the series. By using this function together with a conversion algorithm, various error characteristics dependent on the coefficients  $e_0$ ,  $e_1$ ,  $\cdots$ ,  $e_n$  can be obtained.

#### 1.5.2. Sources of Error in an MOS Implementation

In an MOS technology, probably the easiest way to implement an algorithmic A/D converter is to use MOS operational amplifiers and capacitors. An example of an implementation was given earlier. With this example, the limitation towards achieving high accuracy A/D conversion can be studied. The loop transfer function equation gives a framework with which the various error terms can be identified.

#### 1.5.2.1. Zeroth Order Error

The zeroth order error in the loop transfer function is identical to the offset in a circuit. Offset voltage in the analog loop can be generated by various mechanisms. Referring to Fig. 1.5, it is assumed that the operational amplifiers have no input voltage offset. However MOS operational amplifiers usually have input offset voltages ranging from 2 to over 10 mV depending on the design and variations in process. These offset voltages are added to the loop signal as it passes around the loop, resulting in a zeroth order error in the loop transfer equation. It is therefore referred to as the loop offset error.

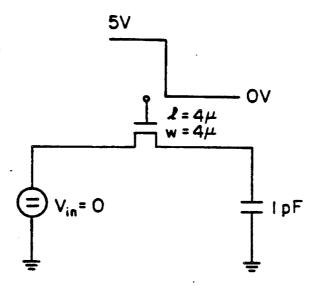

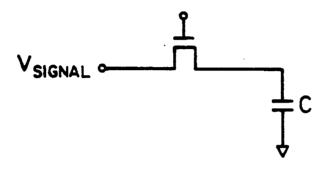

In addition to this contribution to the offset term, charge injection effect from MOS transistor switches also contribute to an offset voltage. To obtain a magnitude for this error, consider a minimum size transistor connected to a capacitor of 1pF as shown in Fig. 1.7. The transistor has dimensions of  $1=4\mu m$ ,  $w=4\mu m$  and the threshold voltage is  $V_r=0$ . The gate oxide has a thickness of 50nm. If the transistor is turned off then the channel

charge at a gate bias voltage of 5V is injected into a capacitor of 1pF, the voltage change on the capacitor is

$$\delta V = \frac{Q_{ch}}{C} = C_o, \frac{V_{\varepsilon}}{C} = 59mV \tag{1.9}$$

which is a significant error term for precision analog circuit operation. This injection voltage error appears as an offset term to the converter.

#### 1.5.2.2. First Order Error

The first order error contains three components:

- 1) capacitor mismatch

- 2) charge injection error

- 3) capacitor voltage coefficient

The capacitor matching in an MOS technology is limited by various process steps and typically attains an accuracy of 9-10 bits. Therefore if the gain of the sample/hold and multiply-by-two blocks are set by capacitor ratios, they cannot be more accurate than 0.1% which means that the worst case gain error for the analog loop is 0.2%. This introduces an first order error term into the loop transfer function.

Similarly, insufficient gain in the operational amplifier can cause a gain accuracy problem. A rough estimate of the open looped gain of the operational amplifier required to achieve a certain gain accuracy can be made with the equation

$$\delta \frac{A}{A} = \frac{\delta \frac{a}{a}}{1 + T} \tag{1.10}$$

where

$\delta A$ : change in closed loop gain

A: closed loop gain

$\delta a$ : change in open loop gain

a: open loop gain T: loop gain

For example, a closed loop gain accuracy to 13 bit requires a open loop gain of at least 20000 or 86dB.

In addition to the capacitor ratio problem, it can be shown in chapter 3 that charge injection from MOS switches can alter the gain of a MOS gain circuit. This is caused by charge injection effect which is proportional to the magnitude of the input signal.

Finally MOS capacitors are voltage dependent. When they are used in MOS gain stages, the voltage gain becomes a nonlinear function of the input. MOS capacitor are usually formed between two heavily doped polysilicon layers or between a heavily doped polysilicon layer and a diffusion layer in the substrate. The formation of accumulation or depletion layers in the silicon or polysilicon layers whose widths are dependent on the voltage introduces a voltage dependent capacitance effect. This effect contributes a significant amount to the first order error term.

#### 1.5.2.3. Higher Order Terms

Higher order terms in the analog loop equation are usually due to the nonlinear voltage dependence of the MOS capacitor and perhaps the nonlinear input-output transfer characteristics of the operational amplifier. Their effect is usually insignificant compared to the first two terms in the equation except e.g. when the operational amplifier has very low gain. The small loop gain would fail to suppress the highly nonlinear output characteristics of the operational amplifier.

Figure 1.1

Figure 1.2

Figure 1.3

Figure 1.4

• OP AMP OFFSET

~10 mV

• CHARGE INJECTION OFFSET

~10 mV

• CAPACITOR MISMATCH

~8-9 BIT ACCURACY

Figure 1.5

Figure 1.6

Figure 1.7

### CHAPTER 2

# Ratio-Independent Circuits

#### 2.1. Introduction

One of the prevalent method for obtaining well defined and stable gain is to apply negative feedback around an amplifier using a passive network. If the gain of the amplifier is very large, the overall gain of the circuit is equal to the reciprocal of the passive network transfer function. This gain setting technique makes the gain accuracy to depend on the accuracy of the feedback network transfer function which is much more readily achievable. In integrated circuit technology, the feedback network usually consists of resistors or for MOS technology, of capacitors. With a modern processing technology, these passive elements can be controlled typically within 10% of their designed value and the ratio between neighboring units can reach 0.1% when care is taken to avoid adverse processing effects. Thus 0.1% or correspondingly 10 bit accuracy represents the typical upper limit to the gain accuracy which can be obtained with a monolithic technology. To achieve higher gain accuracy in monolithic circuits, various techniques have been applied. Extra processing steps for obtaining precision elements for example have been developed. Thus laser trimming used on thin metallic film can achieve accuracy of 13 bit level or more. Also the fuse link trimming of resistor network has been used with relative success. But the disadvantage of these methods are the high manufacturing cost associated with the additional process steps.

In this chapter, we deal with circuit techniques that can deliver precise gain values with unmatched capacitors in a MOS integrated circuit technology. This has been seen by many other as a viable alternative to the use of more expensive technological tools in realizing precision circuits. Recently circuit techniques that can realized accurate analog-to-digital conversion without utilizing matching of passive elements have been introduced. One example is the dynamic element matching method developed by Van de Plaasche [9]. This method uses time-multiplexed current sources to achieved exact binary weighing of current sources for a DAC. The current glitches that are generated from the switching is smoothed out by attaching capacitors to the current sources. Linearity up to 15 bits can be achieved. Another method is the self-calibrating method [10] developed by H.S.Lee at U.C. Berkeley where known properties of the converter are used to calibrate the passive elements and later by correcting for these errors, an extremely linear analog to digital conversion can be made. The method that are developed in this thesis uses neither of these techniques but is rather a self-correcting technique in which the error in the gain setting capacitors are corrected in every cycle by means of a switching algorithm.

As it becomes apparent in the last chapter, among the factors that limit the linearity and resolution of the algorithmic analog-to-digital converter are the loop gain error and the loop offset error. Since the loop gain error represents the sum of the gain error in the multiply-by-two amplifier and the sample/hold amplifier, it may have a worst case minimum value of 0.2%. This means that if the algorithmic A/D converter is realized with the conventional gain-setting technique by using ratioed capacitors, linearity higher than 9-10 bit is very difficult to attain. Since this gain setting technique by using ratioed capacitors is inadequate for high resolution algorithmic A/D conversion, a technique for obtaining an exact integral multiplication of a voltage has been developed and is described in section 2.2. This technique involves a sequence of switching operations with a

switched capacitor integrator.

## 2.2. Ratio-independent Multiplication of a Signal

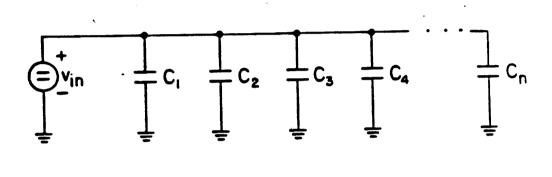

Conceptually, it is not difficult to obtain an integral multiplication of a signal by capacitors which have arbitrary values. In Fig. 2.1a, n of such capacitors with different capacitances  $C_1$ , ...,  $C_n$  are connected in parallel to the same voltage source  $V_{in}$ . To obtain  $nV_{in}$ , the capacitors are disconnected from the voltage source and stacked on top of each other as shown in Fig. 2.1b. The voltage at the top plate of  $C_n$  should be  $nV_{in}$ , independent of the capacitance values. In practice, however, the capacitors have small parasitic capacitances associated with their terminals. As a consequence, charge sharing would take place between the capacitors and the parasitic capacitances and the actual voltage at the top plate of  $C_n$  is smaller than  $nV_{in}$ .

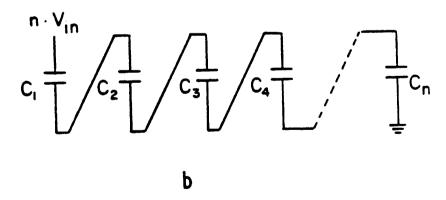

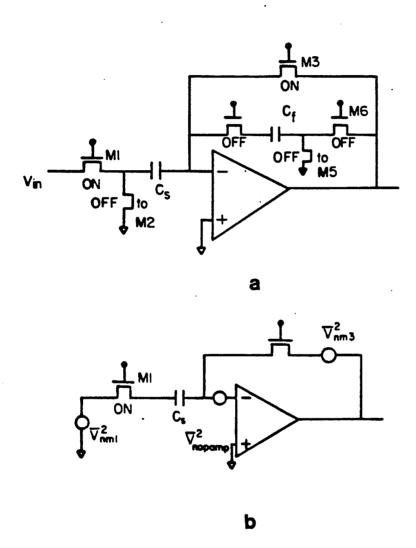

Instead of stacking capacitors on top of each other, the ratio-independent multiplication technique used in the present algorithmic A/D converter uses a switched capacitor integrator to sum the signal charge and then redeposit it onto the same sampling capacitor with which the signal charge is originally sampled. These operations are shown in Fig. 2.2a-f. An ideal operational amplifier is assumed in the discussion that follows. Fig. 2.2a shows the initialization phase of the integrator. The operational amplifier is nulled by the switch  $M_5$ , while the sampling capacitor  $C_5$  is connected to the voltage  $V_{in}$  by  $M_1$  and  $M_2$ . In Fig. 2.2b the signal charge  $Q_{in} = C_5 V_{in}$  is transferred to the integration capacitor  $C_f$ . While conserving the charge  $Q_{in}$  on  $C_f$ , another sample of  $Q_{in}$  is taken on  $C_5$  and integrated onto  $C_f$ . These operations are shown in Fig. 2.2c and d. After n such cycles, the total charge on  $C_f$  is  $nQ_{in}$  and the output voltage of the integrator is  $n \frac{C_5}{C_f} V_{in}$ . Obviously, the output voltage is still dependent on the ratio of the two capa-

citors. This is because the charge  $nQ_{in}$  is residing on  $C_f$  which bears no relationship to the sampled charge  $Q_{in}$ . Now if the position of the two capacitors are exchanged as shown in Fig. 2.2f by means of the transistor switches  $M_6$  and  $M_7$ , the charge residing on  $C_f$  is redistributed back onto  $C_s$  and the output of the integrator becomes  $nV_{in}$  which is the desired multiplication. Because the operational amplifier maintains a virtual ground point at one plate of  $C_f$  and drives the other plate with its active output stage, this multiplication scheme is insensitive to parasitics on  $C_s$  and  $C_f$ . This scheme has been independently proposed by C.C.Lee[11].

#### 2.3. Problems

It was tacitly assumed that all the components that build up the MOS integrator were perfect. In reality a number of effects exist that limit the performance of the ratio-independent-multiply circuit:

- 1) finite operational amplifier gain

- 2) finite operational amplifier offset

- 3) charge injection from MOS transistors

- 4) capacitance voltage coefficient

The effects of each of these non-ideal behavior on the circuit are analyzed in the following sections and ways to counteract or compensate them, if they are appropriate, are explained. The introduction of these compensation techniques leads to the development of a fully differential integrator with a modified timing control scheme adapted in a implementation of the algorithmic A/D converter.

# 2.3.1. Finite Operational Amplifier Gain

In order to have complete charge transfer between the capacitors in the ratio-independent-multiply circuit, the operational amplifier used must possess enough gain. The minimum required gain as a function of the gain accuracy for a feedback amplifier is given by

$$a_{\min} = \frac{A_{ideal} (A_{ideal} - \Delta)}{\Delta}$$

where  $A_{ideal}$  is the ideal feedback gain value and  $\Delta$  is the error between the actual and the ideal gain.

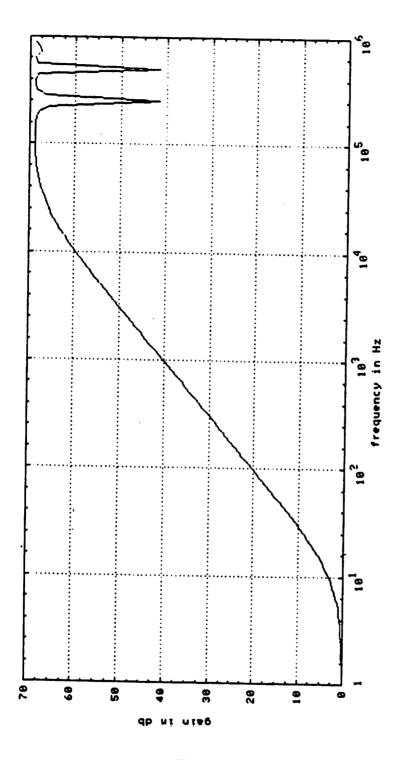

The actual gain that is needed is double the value because there is a cascade of two amplifiers in the loop. As explained in chapter 1, the loop gain accuracy must be comparable to the linearity of the conversion. Therefore to obtain 1/2 lsb of linearity for a 12 bit converter for example, the gain must be larger than 20000 or 86 dB for a ideal gain of 1.

Another consideration for using high gain in the operational amplifier is the suppression of operational amplifier output nonlinearity. Enough gain is required such that the *variation* in gain would not seriously disturb the gain accuracy.

In a NMOS technology, high operational amplifier gain cannot be achieved easily because of the lack of a satisfactory load device. In a CMOS technology it is easier to construct high gain operational amplifiers. With a conventional design, it would have called for a two stages architecture, which is not very desirable in terms of compensated bandwidth and slewing performance. These considerations lead to the design of an high gain single stage CMOS operational amplifier to be described in chapter 3. Therefore the problem of low dc gain in operational amplifier does not seem to be a fundamental

limitation to the ratio-independent multiplication scheme.

### 2.3.2. Operational Amplifier Input Voltage Offset

In spite of the inherent matching advantage of monolithic devices, small mismatches still exist between two adjacent, identical transistors of a differential stage. In addition to this device mismatch offset, which is mainly due to limitations in process technology such as photolithography and etching, certain circuit configurations may give rise to a natural imbalance in their output voltage or current, thus generating a systematic offset. Due to the low transconductance of the MOS transistor, such offset errors often take on offset voltages close to 2 10 mV expressed equivalently at the input of an MOS operational amplifier. In precision analog MOS circuits, care must be taken to prevent this offset from overriding the signal.

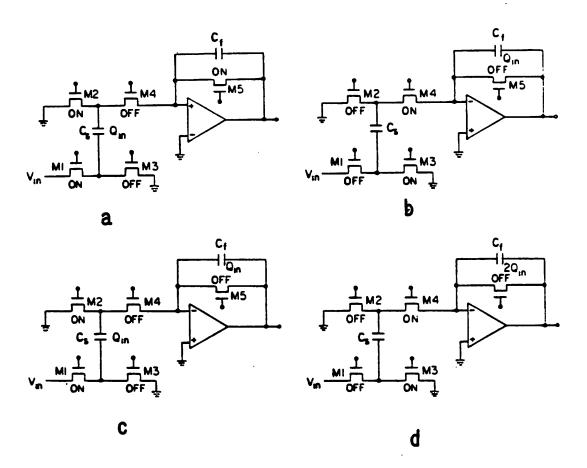

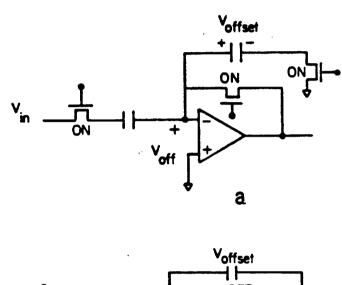

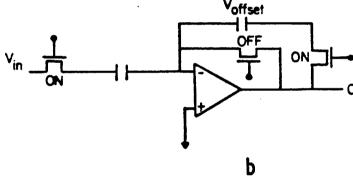

A very effective method of canceling this offset in switched capacitor circuit is to store the offset voltage on capacitors. This is shown with the MOS gain block in Fig. 2.3a. During the initialization phase, the operational amplifier is nulled and the capacitors connected to the signal source and ground as shown. The offset voltage  $V_{of\ f\ ser}$  is stored on capacitor  $C_f$ . This can be understood if  $C_f$  is disconnected from ground and connected to the output of the operational amplifier as in Fig. 2.3b. In this case the output of the operational amplifier is 0. Subsequently, as the input capacitor  $C_s$  is connected to ground, displacing the charge into  $C_f$ , the output voltage becomes  $C_s \frac{V_{in}}{C_f}$  independent of  $V_{of\ f\ ser}$ . One drawback of this approach is that charge injection from the nulling switch  $M_3$  contributes to another offset error. But since this charge injection offset error is not related to the operational amplifier input offset error, the latter can be considered as completely canceled.

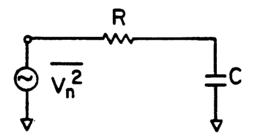

## 2.3.3. Charge Injection Effect

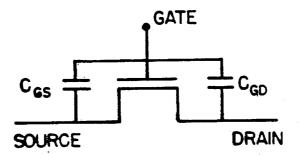

The MOS transistor functions as an analog switch in switched capacitor circuits, *i.e.* it acts as a short-circuit or an open circuit path for transmitting or blocking an analog signal between two circuit positions. A model of the transistor is illustrated in Fig. 2.4. The extrinsic MOS transistor is shown as the intrinsic MOS transistor together with the gate-source and gate-drain overlap capacitances. Such a partition is especially useful for considering the charge injection effect, because it separates the linear elements ( the overlap capacitances ) from the nonlinear elements ( the intrinsic MOS transistor ).

When an MOS transistor switch is turned on, a quantity of charge is stored in its channel. Subsequently, this charge is injected into the surrounding circuit nodes when the transistor is turned off. This phenomena is commonly known as the charge injection effect. The magnitude of this charge can be expressed in a first order equation as follows:

$$Q = C_{o_{\lambda}} (V_{\xi} - V_{t}) - C_{o_{\lambda}} V_{s} sp 1$$

$$= Q_{1} - Q_{2}$$

(2.1)

where

Q: charge stored in channel

$C_{ox}$ : gate capacitance of the transistor

V<sub>r</sub>: gate voltage

V, : threshold voltage of MOS transistor

$V_s = V_d$ : source or drain voltage

$$Q_1 = C_{ox} (V_p - V_r)$$

$$Q_2 = C_{ox} V_s$$

For simplicity, the back gate bias dependence of the threshold voltage has been neglected and the gate-source and gate-drain overlap capacitances are taken to be external elements. The difference between this injected charge and the charge injected form the overlap capacitances is that the transistor does not inject its channel charge continuously, but only until its gate voltage reaches the value  $V_t + V_s$ .

Notice that this charge has been split into two components,  $Q_1$  and  $Q_2$ . The first component  $Q_1$ , which shall henceforth be called the charge injection offset, is independent of the drain/source voltage and potentially gives rise to an offset error in a circuit. The second component  $Q_2$ , which is called the voltage dependent charge injection, is dependent on the source/drain voltage and can give rise to a gain error in a circuit if proper measures are not taken to eliminate it.

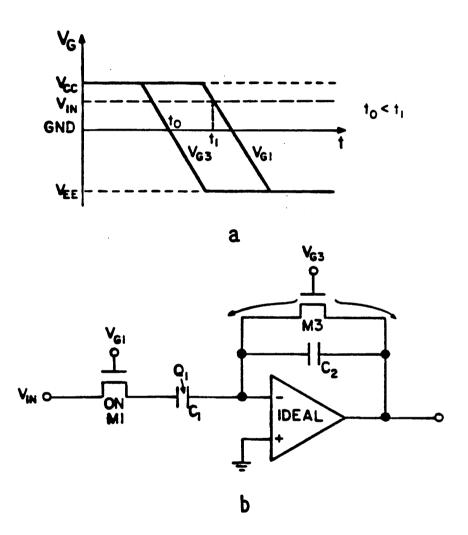

## 2.3.3.1. Effect of Charge Injection

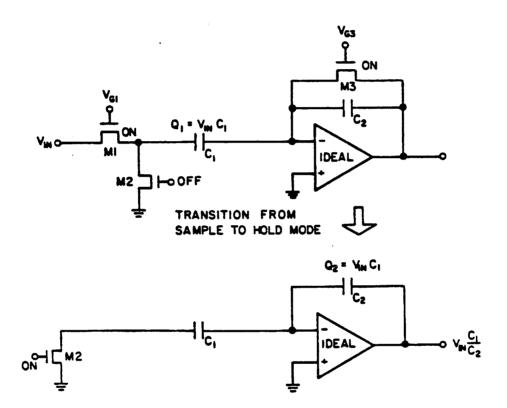

To illustrate the effect of charge injection on a circuit, consider a simple MOS gain block in the transition from the sample to the hold mode. Fig. 2.5 shows the gain block which consists of an MOS operational amplifier, a sampling capacitor  $C_1$ , a feedback capacitor  $C_2$  and three n-channel MOS transistor switches  $M_1$ - $M_3$ . During the transition, transistors  $M_1$  and  $M_3$  must be turned off and  $M_2$  turned on. For controlling the transistors, the gates of  $M_1$  and  $M_3$  are usually tied to the same control line or the same switching waveform. Now if the input voltage  $V_{in}$  is at a potential higher than the ground potential, transistor  $M_1$  will be turned off first, at time  $t_1$  as shown in Fig. 2.6a, causing the channel charge to be injected back into the voltage source node A and the operational amplifier summing node B. The state of the circuit between time  $t_1$  and  $t_0$  where  $M_3$  turns off is illustrated in Fig. 2.6b. The partition of the channel charge in  $M_1$  into source and drain is a complex function of the control voltage waveform and the

node impedances[12][13], but in this analysis, it is assumed that the charge is split into two equal halves. Since transistor  $M_3$  is still conducting when the charge injection takes place, the charge injection will displace from the sampling capacitor an amount of charge equal to

$$Q_{inj} = -\frac{1}{2}C_{ox}(V_g - V_I) + \frac{1}{2}C_{ox}V_{in}$$

(2.2)

so that the resultant sampling charge Qs becomes

$$Q_{s} = C_{1}V_{in} + \frac{C_{ox}}{2}V_{in} - \frac{C_{ox}}{2}(V_{g} - V_{t})$$

$$= (C_{1} + \frac{C_{ox}}{2})V_{in} - \frac{C_{ox}}{2}(V_{g} - V_{t})$$

(2.3)

Subsequently, when  $M_2$  is turned on,  $Q_s$  is transferred onto  $C_2$  and causes an output voltage equal to

$$V_{o} = \left(\frac{C_{1}}{C_{2}} + \frac{C_{ox}}{2C_{2}}\right)V_{in} - \frac{C_{ox}}{2C_{2}}(V_{g} - V_{t})$$

$$= AV_{in} + V_{of f sct}$$

(2.4)

Ideally, if there were no charge injection, the gain of the circuit A would be  $\frac{C_1}{C_2}$ . Thus through the charge injection effect, the gain becomes A' and there is an additional offset term  $V_{of\ f\ ser}$ . The alteration of the gain can be attributed to the signal dependent charge injection component  $Q_2$ .

In this analysis the charge injection from  $M_3$  has not been taken into account. It can be easily deduced that it would contribute another offset component to the gain block. When the operational amplifier is in the unity gain feedback mode as it is when  $M_3$  is on, the source/drain voltage of  $M_3$  is ideally zero thus independent of  $V_m$ . This means that under all circumstances the charge injected by  $M_3$  will be a constant.

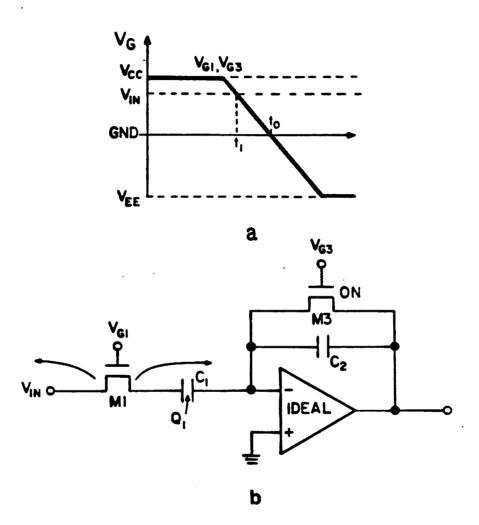

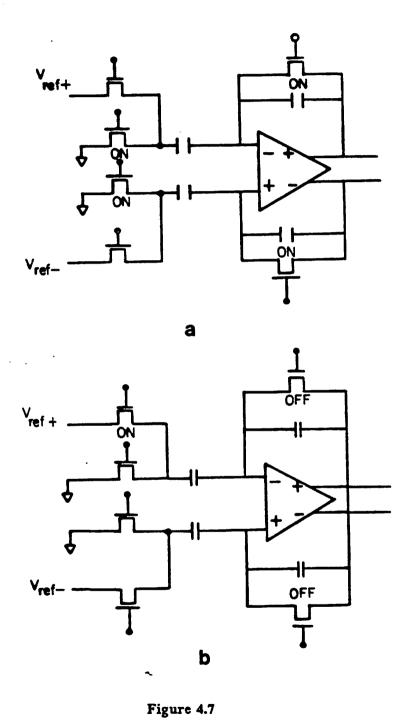

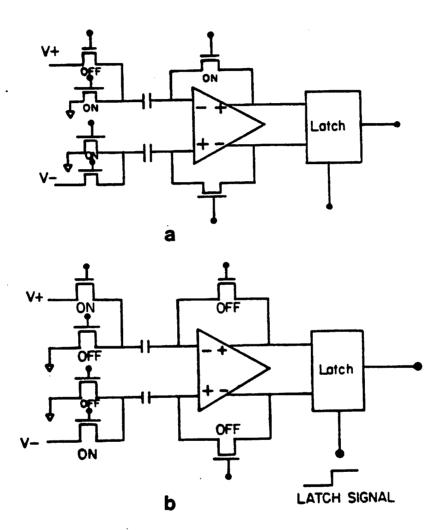

## 2.3.3.2. Cancellation of Signal Dependent Charge Injection

By proper scheduling of the timing control sequence, the signal dependent charge injection component and therefore the gain error can be eliminated. The timing diagram for achieving this is depicted in Fig. 2.7a. Notice that by delaying the switching off of  $M_1$ ,  $M_3$  can be controlled to switch off first at time  $t_0$ . The state of the circuit between  $t_0$  and  $t_1$  is shown in Fig. 2.7b. There is indeed still charge injection from  $M_3$ , but because the operational amplifier in negative feedback places  $M_3$  at a potential (0 for ideal operational amplifier) independent of the input signal, the displacement charge that flows into the operational amplifier summing node is

$$Q_{in j} = -\frac{C_{ni}}{2} (V_g - V_r). {(2.5)}$$

and depending on the speed of the operational amplifier and the node impedances of the circuit, this charge may distributes itself between the sampling capacitor  $C_1$  and the feedback capacitor  $C_2$  with varying proportions. But once  $M_2$  is turned on, the feedback action of the operational amplifier forces all charge to reside on  $C_2$ . As a result, the output voltage during the hold mode becomes

$$V_{o} = \frac{C_{1}}{C_{2}} V_{in} - \frac{C_{ox}}{2C_{2}} (V_{g} - V_{r})$$

(2.6)

and the gain is equal to the ideal gain.

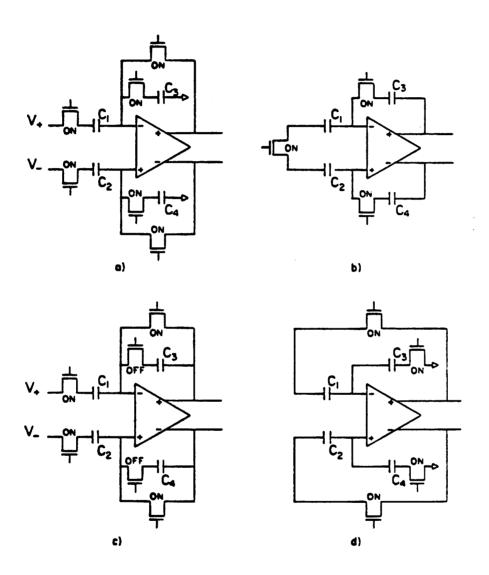

#### 2.3.3.3. Cancellation of Charge Injection Offset

The use of fully differential circuitry in switched capacitor filters [14] has contributed both to the increase of dynamic range and ease of design. In addition, it leads to a first order cancellation of the charge injection offset. This can be explained with Fig. 2.8, which shows the differential implementation of the MOS gain block that was described

earlier. It consists of two sets of capacitors  $C_1C_3$  and  $C_2C_4$  which constitute the two signal paths. The MOS transistor switches are duplicated in the two paths. In the transition from the sample to the hold mode, the transistor pairs  $M_1M_3$  and  $M_2M_4$  are turned off first. But instead of connecting the terminals of the capacitors to ground, they are connected together by means of the transistor  $M_5$ . In making use of the proper timing sequence explained in the last section, transistors  $M_2$  and  $M_4$  both inject charge into the operational amplifier summing nodes and displace charges in  $C_1$  and  $C_2$ . This charge injection is however common to both channels of the differential circuit and appears therefore as a common mode signal to the operational amplifier which is then suppressed by the common mode feedback circuit in the operational amplifier. The output is not affected if the transistors  $M_3$  and  $M_4$  have the same gate capacitance and overlap capacitances. In actuality, the transistors can be mismatched by as much as 10-20% in their capacitances and the cancellation is only approximate. The resultant offset error voltage in this case is

$$V_{of f set} = \delta C_{oa} \left( V_g - V_t \right) \tag{2.7}$$

where

$\delta C_{ox}$ : difference in the gate capacitances

This represents a significant reduction in the error due to the charge injection from MOS transistor.

## 2.3.4. Capacitance Voltage Coefficient Cancellation

The capacitor used in an MOS process is usually voltage dependent. This voltage dependence can be expressed as a Taylor series

$$C(V) = C_0 (1 + \alpha_0 V + \alpha_1 V^2 + \cdots)$$

(2.8)

where

Co: zero voltage capacitance

$\alpha_0$ ,  $\alpha_1$ ,  $\cdots$ : capacitance voltage coefficients

Normally, this capacitance voltage dependence introduces nonlinearities into the circuit which are intolerable for high precision circuit operations. However, the same differential circuit which is used to cancel charge injection effect also gives a cancellation of odd order capacitance voltage coefficients of the MOS capacitors. This is because an increase of voltage or capacitance in one channel is accompanied by an equal but opposite decrease of voltage or capacitance in the other channel of the circuit. These changes combine to give overall capacitance voltage coefficients equal to the difference of the odd order capacitance voltage coefficients of the capacitors in the two channels. The even order capacitance voltage coefficients are summed together. Since  $\alpha_1,\alpha_2$  ... are much smaller than  $\alpha_0$ , they can be neglected in a first order analysis and the net result is a voltage dependence of  $\delta\alpha_0$ .

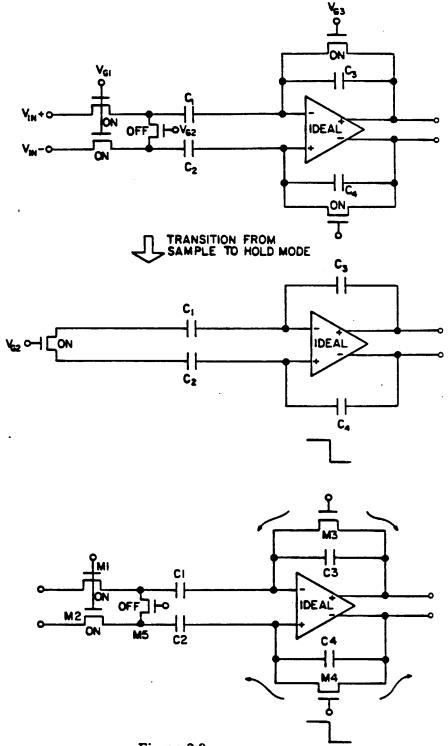

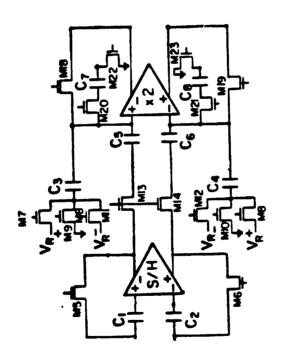

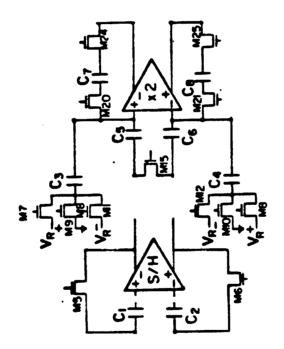

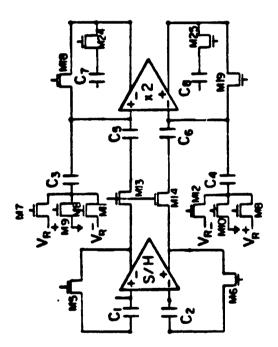

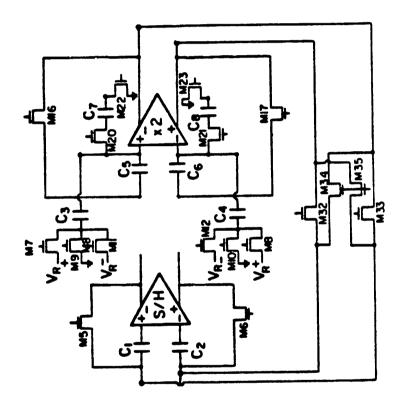

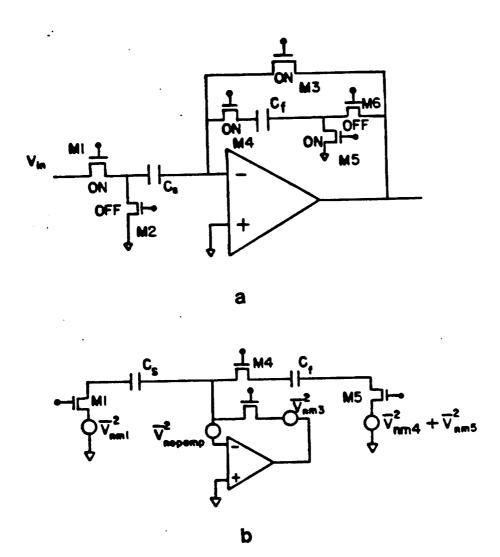

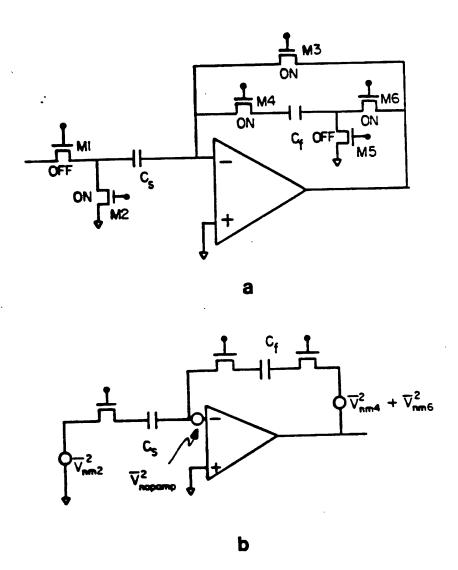

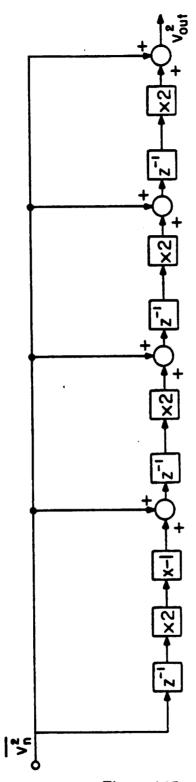

# 2.4. Ratio-independent Multiply-by-Two Switching Algorithm

Summarizing the foregoing discussions, the ratio-independent multiply-by-two function can be realized using a differential gain block or integrator with a switching sequence as shown in Fig. 9a-d. Assuming that the input differential voltage  $V_+-V_-$  is constant during the whole operation, it is first sampled onto the sampling capacitor  $C_1$  and  $C_2$  in the first clock cycle ( Fig. 2.9a ). This signal charge is then transferred onto the integrating capacitors  $C_3$  and  $C_4$  during the second clock cycle by turning on the switch M3 ( Fig. 2.9b ). Subsequently,  $C_3$  and  $C_4$  have to be separated from the operational amplifier feedback loop to prepare for the second signal sampling. To accomplish this task without introducing signal dependent charge injection, the capacitors are

separated from the operational amplifier input nodes. Another signal sample is then taken (Fig. 2.9c), and during the fourth or the last clock cycle, the first signal charge is redistributed back onto  $C_1$  and  $C_2$  from  $C_3$  and  $C_4$  (Fig. 2.9d). The operation takes four operational amplifier settling time periods which determine the length of the basic clock cycle.

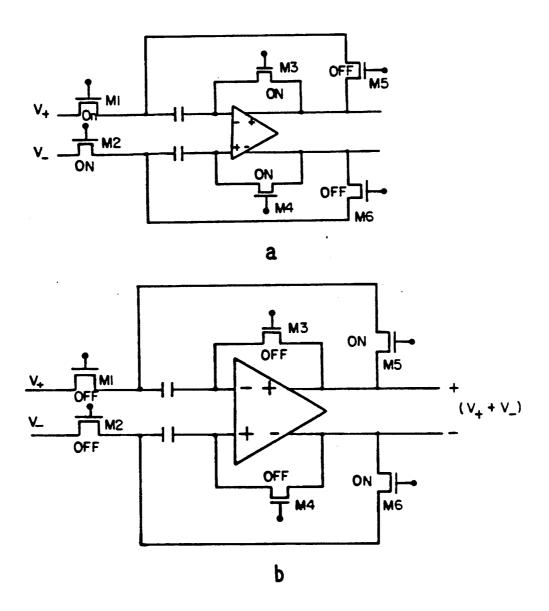

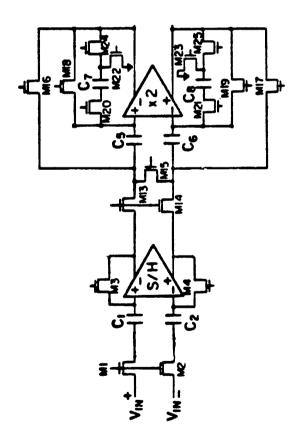

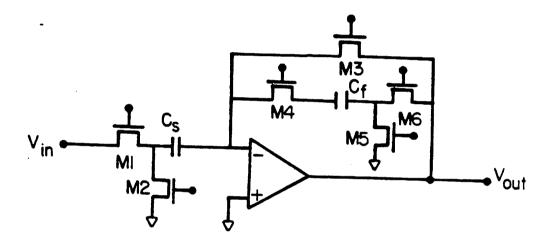

## 2.5. Ratio-independent Sample/Hold

A ratio-independent sample/hold function can be implemented very simply by an MOS operational amplifier and two capacitors. An intermediate storage capacitor is not needed. The operation is described in Fig. 2.10. Using a fully differential implementation again, the differential signal is sampled onto the capacitors as shown in fig. 2.10a. Any offset voltage on the operational amplifier would be stored onto the capacitors as well. Following this, the switches  $M_3$  and  $M_4$  are turned off and the capacitors connected to the output by means of switches  $M_5$  and  $M_6$ . The negative feedback then forces the operational amplifier outputs to assume the same potentials as the input voltages.

a

Figure 2.1

Figure 2.2

Figure 2.3

Figure 2.4

Figure 2.5

Figure 2.6

Figure 2.7

Figure 2.8

Figure 2.9

Figure 2.10

## CHAPTER 3

# Operational Amplifier Design

#### 3.1. Introduction

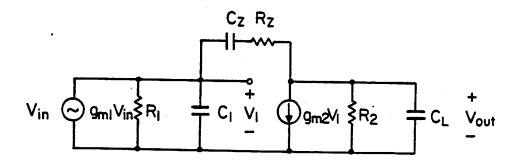

In the design of high accuracy sampled-data switched capacitor circuits, the operational amplifier constitutes the most important building block in the system. Without optimal performance from such an amplifier, accuracy and speed can not be achieved on the basis of an theoretical switching algorithm only. We have seen that accuracy is synonymous to high dc gain in the operational amplifier. Speed in this context is generally identical to how fast an operational amplifier in a particular feedback configuration can settle to a certain percentage of its final output value in the presence of a input signal. Thus the speed is not only a function of the small signal bandwidth of the operational amplifier but also one of its slew rate. For the algorithmic analog to digital converter there are special requirements that have to be fulfilled. Some sundry items concerning the design of operational amplifiers in CMOS technology will be discussed here.

#### 3.2. Motives

The designs of operational amplifiers for the application in a switched capacitor filter and in a algorithmic A/D converter have one fundamental difference. In a switched capacitor filter, the operational amplifier output only need to swings small voltage steps whereas in the algorithmic A/D converter, the output voltage can cover the

maximum signal dynamic range in the same amount of time. This particular application for the algorithmic converter necessitates an operational amplifier without slew rate limitation since a large part of the time needed for the output to converge to its final value is spent in the slewing period. For the MOS operational amplifier, two aspects of this slew rate limitation are apparent. First, for a single stage operational amplifier, the load capacitor acts as the compensation capacitor and determines the maximum slew rate and the small signal bandwidth of the operational amplifier. By a single stage operational amplifier it is meant an operational amplifier that has only one high impedance node. This is also true for the two stage amplifier. Second, for 2 stage operational amplifier designs, because of the finite driving capability of the second stage, the maximum slew rate at the output is the smaller of the two slew rates resulting from the internal compensation capacitor or the external loading capacitor. Additionally, it may contribute to another high frequency pole which affects the high frequency stability of the closed loop amplifier. Thus the configuration of the operational amplifier has an important bearing on various performance parameters.

In the present design, the sample, load and feedback capacitors need not be matched and are generally in the range of 2-4 pF. Therefore the operational amplifier must have a dc gain of up to 50000 and be capable of settling to 0.01% of the final accuracy within  $1\mu s$  for a differential voltage step of 4-6V while driving such capacitances. The specification for this speed translates approximately into a small signal bandwidth of larger than 5MHz and a slew rate of larger than  $25V/\mu s$  in both directions.

## 3.3. Design Considerations

Before we decide what configuration the operational amplifier should take, a thorough understanding of the  $g_m r_{old}$  or the gain product of a transistor is necessary.

The gain product is a measure of the maximum gain that can be obtained from a single device assuming it is biased by ideal current sources.

#### 3.3.1. Gain Product of A Transistor

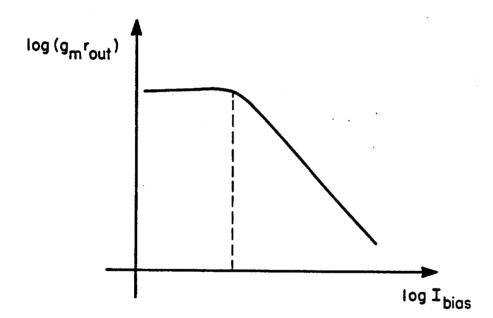

Fig. 3.1 shows a plot of the gain product of a MOS transistor as a function of the drain current operating with a fixed drain voltage. It can be seen that this product increases with decreasing current until it reaches the subthreshold operating region of the transistor where it flattens off. This occurs because the transconductance of the device  $g_m$  is proportional to the square root of the drain current  $I_d$

$$g_m = \sqrt{2I_d \, \mu C_{o_2} \left( W / L \right)} \tag{3.1}$$

and the output impedance is inversely proportional to the drain current

$$r_{out} = \left(\frac{1}{I_d} \chi \frac{1}{\lambda}\right) \tag{3.2}$$

so that their product becomes

$$g_m r_{out} = \left(\frac{1}{\sqrt{I_d}} \left(\frac{1}{\lambda}\right) \sqrt{2\mu C_{ox} \left(W/L\right)}\right)$$

(3.3)

As the device enters the subthreshold region, the transconductance becomes directly proportional to the drain current

$$g_m = \frac{I_d}{nV_T} \tag{3.4}$$

where  $V_T$  is the temperature voltage and n is the slope factor of the device and is equal to

$$n = 1 + \frac{C_d}{C_{ox}} \tag{3.5}$$

thus making the gain product independent of the drain current:

$$g_m r_{out} = \frac{1}{n \lambda V_T} \tag{3.6}$$

In a conventional MOS process, this maximum gain product is above 2000 for a long channel (e.g. >  $6\mu m$  electrical length) N-channel MOS device. Practically, because the transistor has to be biased so that it can achieve reasonable transconductance, the average value achievable is below 100. The implication of this result is that for the single transistor gain stage with active load, the maximum voltage gain that can be obtained with good frequency response is below 200 for long channel ( $>6\mu m$ ) transistors, given that the active load has about the same  $r_{out}$  as the driving device. This statement is of course fully arbitrary because we have not specified what a good frequency response is. Perhaps a good point to remember is that in the present state of the art MOS analog circuit design, the MOS transistor is biased to get at most 10-30% of the maximum available transconductance.

Therefore if higher gain is to be obtained, several single transistor stages each with a low gain product can be cascaded or some circuit of obtaining higher gain products from the basic transistor in a single stage can be used One way of doing this is by the cascoding of transistors.

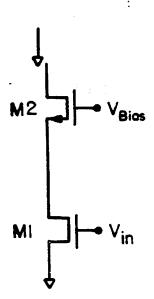

## 3.3.2. Cascoding of Transistors

With the cascode circuit, it is possible to achieve very high output impedance and therefore high voltage gain in a single amplifying stage. The two transistor circuit is shown in Fig. 3.2. It can be seen that since the drain to source capacitance in  $M_2$  and the

drain-gate overlap capacitance in  $M_1$  are extremely small, the high frequency feedback from the output back on the input is negligible. Also because the voltage gain from the input to the source of the upper transistor  $M_2$  is low:

$$\frac{V_1}{V_{in}} = -\frac{1}{1+\lambda} \frac{g_{m1}}{g_{m2}} \tag{3.7}$$

where  $\lambda$  is the backgate bias factor and is equal to

$$\lambda = \frac{\gamma}{2\sqrt{-V_{bs} + 2\phi_F}}$$

Thus for transistors of the same size, the gain is actually smaller than 1, which means that the Miller effect due to the drain gate overlap capacitance in  $M_1$  is reduced. This fact is important when the input transistor is driven with another diode connected transistor as in the current mirror. When looking into the drain of  $M_2$ , the output impedance is

$$r_{out} = g_{m,2} r_{out} \pm (1 + \lambda_2) r_{out,1}$$

(3.9)

As a result the voltage gain available from such a stage is

$$A = \frac{V_{out}}{V_{in}} = g_{m} \, {}_{1}r_{out} \, {}_{1}g_{m} \, {}_{2}r_{out} \, {}_{2}(1 + \lambda)$$

(3.10)

We see that this gain A is composed of the product of two  $g_m r_{out}$ 's together and is therefore proportional to the inverse of the drain current.

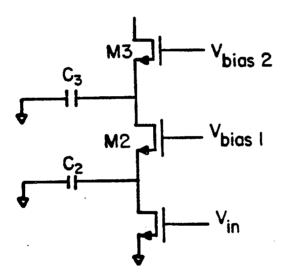

This idea of cascoding transistors can be extended to include three transistors from which a double cascode circuit is obtained. The circuit is shown in Fig. 3.3. The maximum gain product of this circuit can be calculated to be

$$A = g_{m,1} r_{out,1} g_{m,2} r_{out,2} g_{m,3} r_{out,3} (1 + \lambda_2) (1 + \lambda_3)$$

(3.11)

in which case is proportional to  $\frac{1}{I_d^{\frac{3}{2}}}$ . This circuit configuration gives rise to extremely

high gain even if the transistor bias current is large. However this is bought with an corresponding in the gain sensitivity with respect to the bias current and the transistor gate length. As was mentioned earlier, the gain product of the transistor decreases very rapidly as the gate length is shrunken from  $4-5\mu m$  to  $1-2\mu m$ . With the gain proportional to the cube power of this product, the reduction in gain could become substantial. Also since the "upper" transistors have to be biased so that the "next" transistor underneath it is in the saturation region of operation at all times, the output voltage range is limited to a narrow range. In fact, this is the major limitation to the application of the cascode circuit to low voltage supply circuits.

The frequency behavior of the double cascode circuit is quite simple. In addition to the dominant pole  $p_1$  formed by the nodal capacitance on the drain of  $M_3$  and the output impedance there are 2 nondominant poles. They are formed by the nodal capacitances on the sources of  $M_3$  and  $M_2$  and the impedances at those nodes.

$$p_{2} = \frac{g_{m2}}{(1 + \lambda_{2})C_{2}}$$

$$p_{3} = \frac{g_{m3}}{(1 + \lambda_{3})C_{3}}$$

(3.12)

The capacitances  $C_2$  and  $C_3$  are composed of the sum of the gate capacitances from the individual transistor and the parasitic capacitance connected with the nodes such as drain/source junction capacitance or interconnect capacitance.

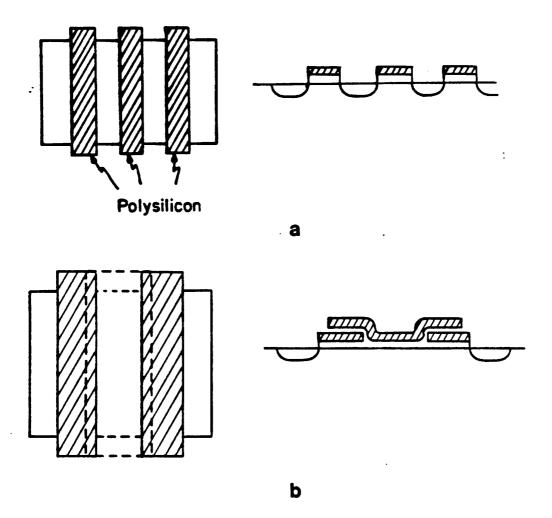

$$C_3 = \frac{2}{3}C_{ox\ 3} + C_{parasitics\ 3} \tag{3.13}$$

Thus  $M_2$  and  $M_3$  are operating very near to their intrinsic speed. To reduce  $C_2$  and  $C_3$  the gates of those transistors can be put very near to each other as shown in Fig. 3.4a for a single polysilicon MOS process. For a double polysilicon MOS process, the parasitic node capacitances can be eliminated by overlapping the two gates of the transistors which are formed by different layers of polysilicon[15]. This layout is shown in Fig. 3.4b.

In principle, the cascode transistor circuit can be extended to N transistors, with the corresponding composite gain product equal to

$$A = (g_m r_{out})^N (1 + \lambda)^N$$

C(3.14)

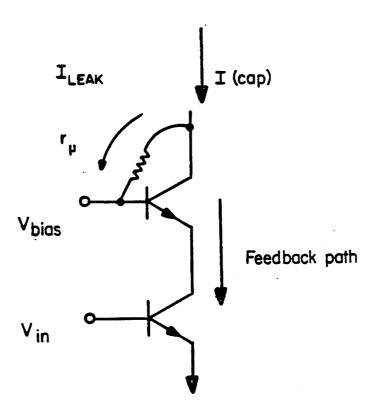

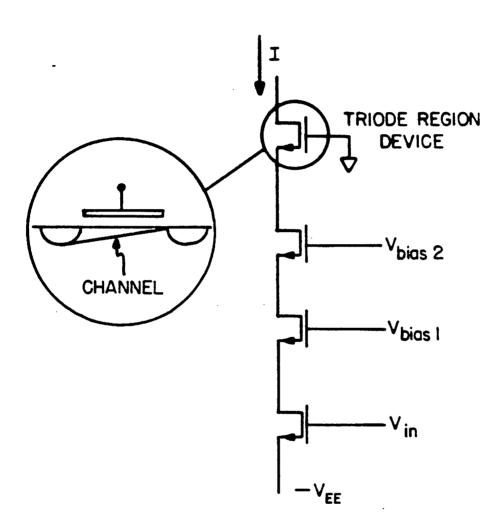

However, for reasons to become apparent later, repeated cascoding cannot be used, both in the bipolar as well as the MOS technologies. The double cascode configuration is not used in bipolar circuit design because the collector-base resistance  $r_{\mu}$  in the cascode transistor would limit the maximum obtainable impedance. This resistance would bleed current away from the negative feedback path formed by the cascode circuit into the biasing voltage source, in contrast to the output impedance of the cascode transistor which conducts a current only to the next lower transistor in the feedback path (Fig. 3.5). Thus it acts effectively as a shunt resistor from the high impedance node to ground.

IN MOS transistors such a resistance does not exist due to the insulating nature of the gate. The maximum obtainable impedance at a node is limited by other effects. One of them is the reverse biased leakage in the drain junction. This resistance of a  $10\mu mX$   $100\mu m$  junction can easily reach several G  $\Omega$  for a well controlled MOS process. Another one is the surface leakage currents between two conductors. This leakage depends on the surface cleanliness and is usually negligible if the wafer is passivated

with an additional passivation layer such as CVD oxide or nitride. Nevertheless the effect of impact ionization in the channel of an MOS transistor eventually this impedance level.

### 3.3.3. Impact ionization in MOS Transistors

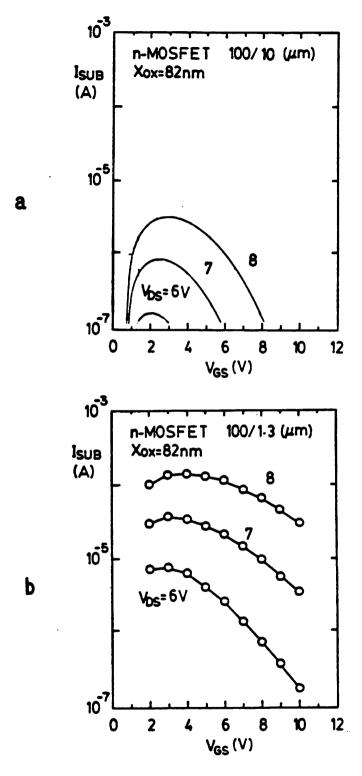

It has long been recognized that channel current in the high field region near the drain causes low-level avalanche multiplication effect thus resulting in a substantial substrate current. This problem is not limited to the short channel transistors alone but appears also in longer channel devices. Fig. 3.6a shows a plot of the substrate current for a  $100\mu m / 10\mu m$  device as a function of the gate voltage for several drain voltages. Fig. 3.6b is a plot for a  $100\mu m$  /  $2\mu m$  device. This substrate current can have several effects on the operations of analog integrated circuits. Firstly, a transistor can have different characteristics if they are located near to an adjacent transistor which injects substrate current. Usually, in the presence of a large substrate current, the drain current increases for the same bias voltages. As a result, the operating bias currents of some circuit paths may differ significantly from the designed values and cause parts of the circuit to enter into undesired operating states. Secondly, the strong dependence of the substrate current and therefore the drain current on the gate and the drain voltages represents a shunting resistance from the channel to the substrate. This would lower the impedances of high impedance circuit nodes and make them highly nonlinear with respect to the node potential.

From the circuit designer's viewpoint, the impact ionization current of the transistor should best be eliminated. But this is not always possible because of the tendency of modern MOS process in going to shorter channel lengths which further aggravates the problem. In seeking to understand and solve this problem, there is the problem of modeling which have to be overcome. It is now feasible to model the substrate current of a

MOS transistor by relating it to the maximum electrical field in the device by an exponential function which has the form

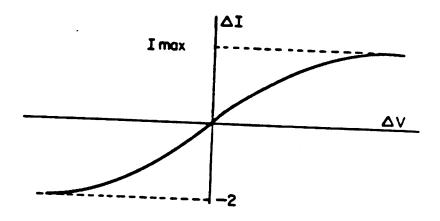

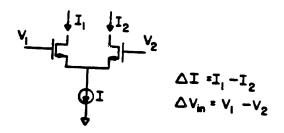

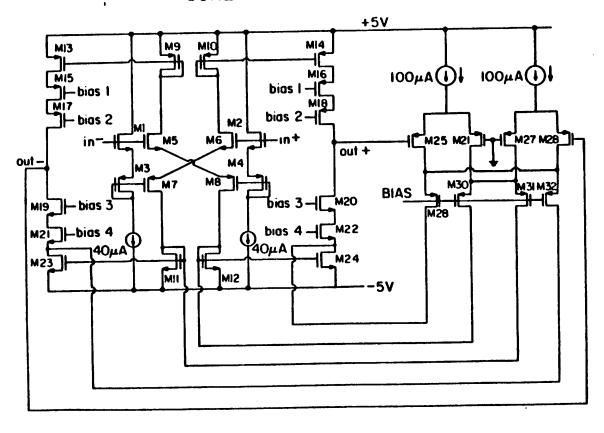

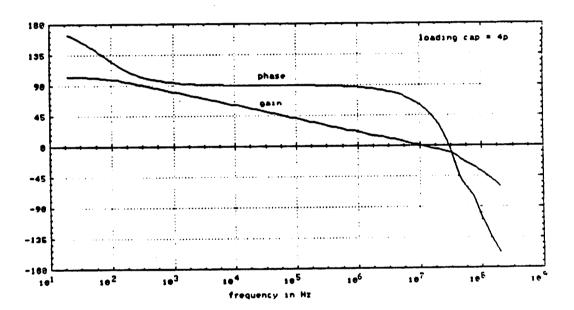

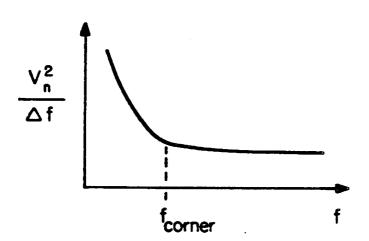

$$I_{sb} = I_{sbo} e^{\frac{a}{E_{\text{max}}}} \tag{3.15}$$