Copyright © 1984, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# ADVANCED MIXED-MODE SIMULATION TECHNIQUES

by

J. E. Kleckner

Memorandum No. UCB/ERL M84/48

6 June 1984

Covy

# ADVANCED MIXED-MODE SIMULATION TECHNIQUES

by

4

J. E. Kleckner

# Memorandum No. UCB/ERL M84/48

6 June 1984

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

# Advanced Mixed-Mode Simulation Techniques

By

#### James Ellis Kleckner

B.S. (California Institute of Technology) 1975 M.S. (University of California) 1977 M.S. (University of California) 1980

#### DISSERTATION

å

Submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

Engineering

in the

#### GRADUATE DIVISION

OF THE

## UNIVERSITY OF CALIFORNIA, BERKELEY

Approved: Date 4/18 4/17/84

# Advanced Mixed-Mode Simulation Techniques

-----

\_

B

0

D

Copyright <sup>©</sup> 1984

ЪУ

James Ellis Kleckner

All rights reserved.

## ADVANCED MIXED-MODE SIMULATION TECHNIQUES

James Ellis Kleckner

Ph.D.

Sponsor: Hewlett-Packard

| Department of | Electrical | Engineering   |

|---------------|------------|---------------|

|               | and Comp   | outer Science |

helied Signature \_

Committee Chairman

#### ABSTRACT

The increasing complexity of integrated circuits has resulted in higher costs for the simulation of those circuits. As a result, designers resort to abstract models to describe the circuit behavior that are less expensive to evaluate than detailed models. This leads to the problem of verifying that the abstract models are consistent with the detailed models they replace. Mixed-mode simulators have been developed which allow the use of abstract and detailed models in the same simulation program, providing faster simulation speeds and the ability to verify the consistency of the abstract and detailed models.

In this dissertation, advanced algorithms and techniques for mixed-mode simulation are presented. Mixed-mode simulation has been extended to allow simultaneous simulation of models at the detailed electrical, logic, and register-transfer levels i.e., those levels that can be represented by schematic diagrams. This investigation shows that mixed-mode simulation of widely differing models can be performed using a program architecture that facilitates the addition of new simulation levels without sacrificing either simulation speed or accuracy.

One result of the investigation is the development of a new simulation program, SPLICE2, which has been used to experiment with program architectures and simulation algorithms. New methods are presented for efficient scheduling of activity in an event-driven selective-trace simulator which are called *cached scheduling*. A new technique for accurate circuit level simulation called iterated timing analysis is also studied. Iterated timing analysis can provide up to two orders of magnitude speed improvement over more conventional forms of circuit simulation.

#### ACKNOWLEDGEMENTS

The author is deeply grateful to Prof. A. R. Newton, whose foresight and encouragement have made this research both possible and fun. He would also like to express his appreciation to Professors D. O. Pederson and A. L. Sangiovanni-Vincentelli who, along with Prof. Newton, have created a research environment that is very fertile for new ideas and projects.

R. Saleh, K. Keller, T. Quarles, S. Greenberg, J. White, and J. Deutsch, who have contributed substantially to this project with programming, assistance with examples, and numerous discussions, deserve many thanks. The author would also like to thank A. Vladimirescu, E. Cohen, G. Casinovi, E. Lelarasmee, K. Sakallah, and the inhabitants of 321 Cory Hall for many useful discussions. He is further indebted to J. Valdez, S. Greenberg, S. Potter, and B. Murphy for reading the manuscript and improving it with many comments, and to M. Bales for help producing it.

Support received from the Engineering Productivity Division of Hewlett Packard is gratefully acknowledged along with computers and equipment donated by the Digital Equipment Corporation and Tektronix Incorporated.

The author would especially like to thank his parents, Janet and James, for all the guidance, love, and encouragement they have given and his wife, Jennifer, whose love, understanding, and energy has made this experience both more meaningful and enjoyable than had been thought possible.

As usual on reaching the summit, it becomes clear that there are many higher peaks to climb that were not visible from below. So on to new peaks, with new and old friends alike. ٥

# TABLE OF CONTENTS

14

| Table of (  | Contents                                  | i      |

|-------------|-------------------------------------------|--------|

| List of Fig | gures                                     | ۰<br>v |

| Chapter     | 1. Introduction                           | 1      |

| 1.1         | Simulation                                | 2      |

| 1.2         | Mixed-Mode Simulation                     | 3      |

| 1.2.1       | Types of Simulation                       | 3      |

| 1.2.2       | Schematic Simulation                      | . 4    |

| 1.2.3       | Previous Work on Mixed-Mode Simulation    | 5      |

| Chapter     | 2. Architectures for Schematic Simulation | 7      |

| 2.1         | Goals                                     | 7      |

| 2.2         | Computing Environment                     | 9      |

| 2.3         | User Interface                            | 10     |

| 2.4         | Adding New Simulation Models              | 11     |

| 2.5         | Inter-Simulation Communication            | 12     |

| 2.6         | Choice of Simulation Levels               | 13     |

| 2.7         | Schematic Simulation                      | 15     |

| 2.8         | Signal Representations                    | 16     |

| 2.9         | Signal Mapping                            | 18     |

i

| 2.10    | Time Representation and Scheduling |

|---------|------------------------------------|

| 2.10.1  | Event Scheduling                   |

| 2.10.2  | Representation of Time             |

| 2.10.3  | Indexed List Method                |

| 2.10.4  | Cached Scheduling                  |

| Chapter | 3. Electrical Simulation           |

| 3.1     | The DCTRAN Problem                 |

| 3.2     | Resistor-Capacitor-Diode Example   |

| 3.2.1   | DC Solution                        |

| 3.2.2   | Transient Solution                 |

| 3.3     | Summary of Existing Techniques     |

| 3.4     | Error Measures                     |

| 3.4.1   | Specifying DC Error                |

| 3.4.2   | Specifying Waveform Error          |

| 3.4.3   | Optimal Choice of Time-step        |

| 3.5     | Speedup Factors                    |

| Chapter | 4. Iterated Timing Analysis        |

| 4.1     | Problem Formulation                |

| 4.2     | Relaxation of Systems of Equations |

| 4.2.1   | Linear Equations                   |

| 4.2.2   | Nonlinear Equations                |

| 4.2.3   | Under-Relaxation                   |

•

ii

,

| 4.3     | Transient Analysis                  | ••••••      |

|---------|-------------------------------------|-------------|

| 4.4     | ITA in SPLICE2                      |             |

| Chapter | 5. Discrete Simulation              |             |

| 5.1     | Logic Signals and Models            |             |

| 5.1.1   | How Many States Are Enough          |             |

| 5.1.2   | Logic-Electrical Interface          |             |

| 5.1.3   | Logic Delay Models                  |             |

| 5.2     | Logic Implementation in SPLICE2     |             |

| 5.3     | Register-Transfer Level             |             |

| Chapter | 6. Examples                         | ••••••••••• |

| 6.1     | Description of Example Circuits     |             |

| 6.2     | Measurements                        |             |

| Chapter | 7. Conclusions                      |             |

| Referen | Ces                                 |             |

| Appendi | ix A: Splice2 Listing               | ••••••••    |

| Appendi | ix B: Example Inputs and Outputs    |             |

| Appendi | ix C: Tables of Convergence Results |             |

| Appendi | ix D: Adding Models to SPLICE2      |             |

| Appendi | ix E: Static Program Statistics     | *******     |

.

.

# iii

# LIST OF FIGURES

| 1.1  | Simulation Levels                       |

|------|-----------------------------------------|

| 1.2  | Mixed-Mode Simulators                   |

| 2.1  | User Interface                          |

| 2.2  | Simulator Performance                   |

| 2.3  | Schematic View of Circuits              |

| 2.4  | Net as an Element                       |

| 2.5  | Signal Representations                  |

| 2.6  | Signal Mapping                          |

| 2.7  | Event Scheduling                        |

| 2.8  | Indexed List Method                     |

| 2.9  | Marker Event Overhead                   |

| 2.10 | ) List Insertion Time                   |

| 2.1  | Cache Performance Measurements          |

| 3.1  | DCTRAN waveforms                        |

| 3.2  | Simple Example                          |

| 3.3  | Example Circuit DCTRAN Waveforms        |

| 3.5  | Constant Source Approximation for Diode |

| 3.6  | Zero Order Load Line                    |

| 3.4  | DC Example                              |

| 3.7  | First Order Approximation for Diode     |

| 3.8  | First Order Load Line                   |

| 3.9 C  | onvergence Rate of Newton Raphson        |

|--------|------------------------------------------|

| 3.10   | Discretizing Time                        |

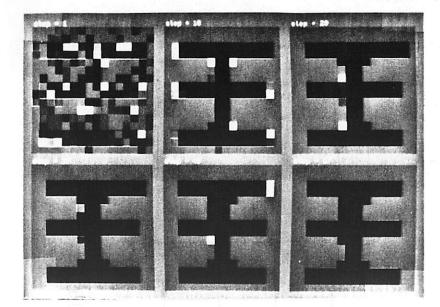

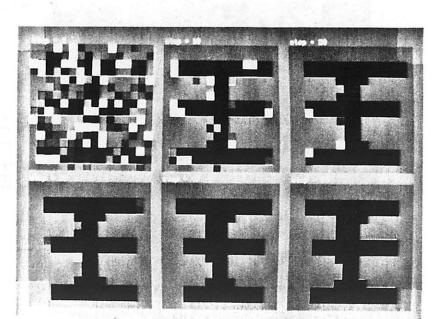

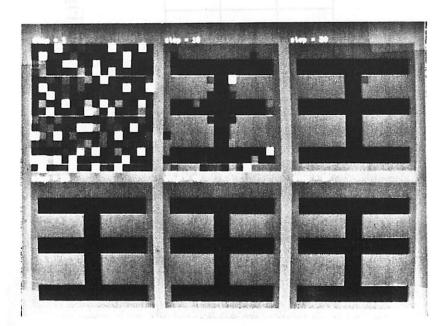

| 3.11   | Capacitor Companion Models               |

| 3.12   | Convergence Criterion                    |

| 3.13   | R-Diode Convergence Values               |

| 3.14   | Linearly Convergent Sequence             |

| 3.15   | Backward-Euler Predictor-Corrector       |

| 3.16   | Waveform Error                           |

| 3.17   | Waveform Local Truncation Error          |

| 3.18   | Example Using Time Tolerance             |

| 3.19   | Waveforms for Example                    |

| 3.20   | Waveform Distance Examples               |

| 3.21   | Optimum Time-Steps                       |

| 3.22   | Temporal Latency in Logic                |

| 3.23   | Distribution of Time-Steps               |

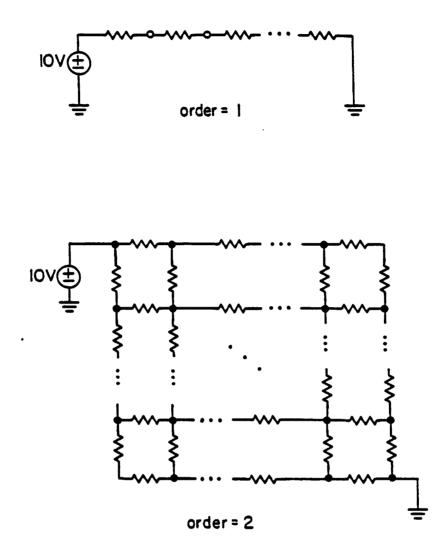

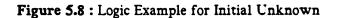

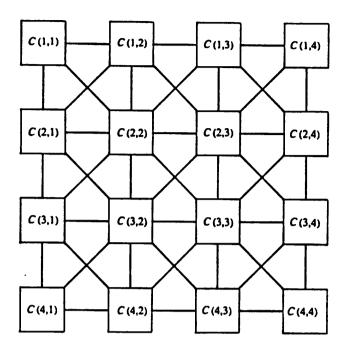

| 4.1 R  | esistor Artays                           |

| 4.2 E  | igenvalues and $\omega$ for Linear Array |

| 4.3 L  | inear Array Results                      |

| 4.4 C  | omparison of Acceleration Methods        |

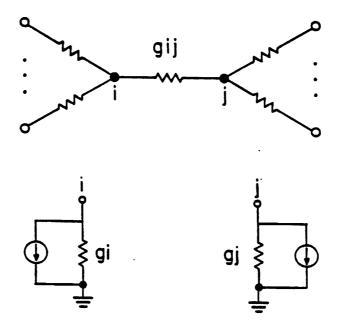

| 4.5 N  | orton Equivalents at Nodes               |

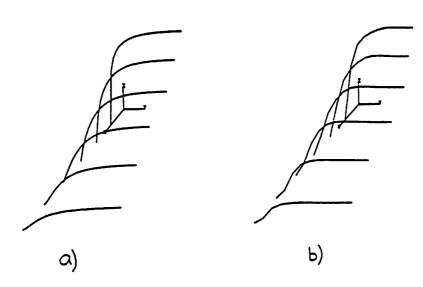

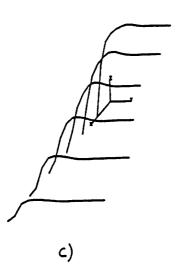

| 4.6 It | erate Plots for Resistors                |

| 4.7 E  | Difficult Resistor Example               |

| 4.8 E  | Data for Difficult Example               |

| 4.9 E  | biode Nonlinear Example                  |

vi

8

ø

0

. .

.

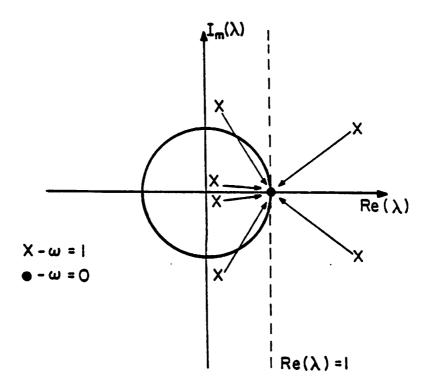

| 4.10 Convergence Data for Diode Example     |  |

|---------------------------------------------|--|

| 4.11 Convergence Plots for Diode Example    |  |

| 4.12 Convergence Plots for Opamp Example    |  |

| 4.13 Eigenvalues and Under-Relaxation       |  |

| 4.14 Stability of Fixed-Point Iteration     |  |

| 4.15 Fixed-Point Iteration of R/Diode       |  |

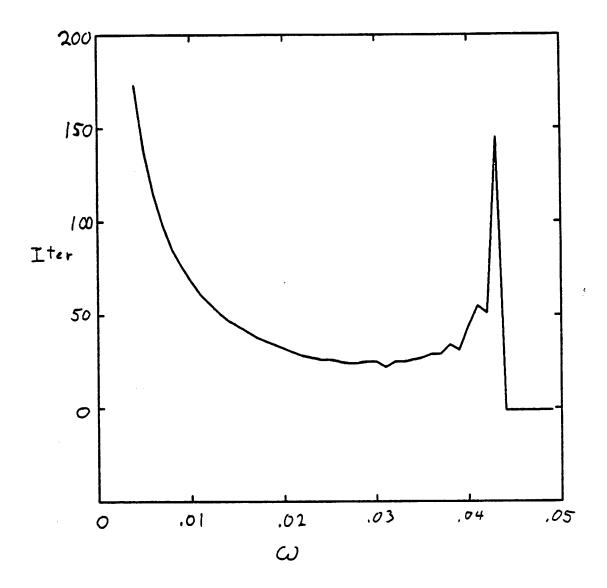

| 4.16 Iterations vs. SOR Factor              |  |

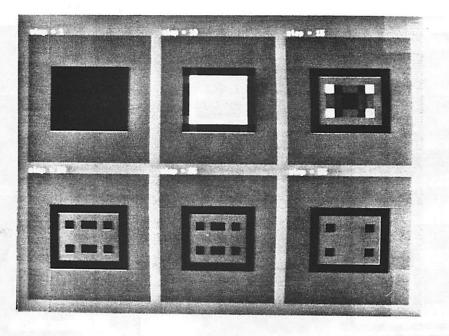

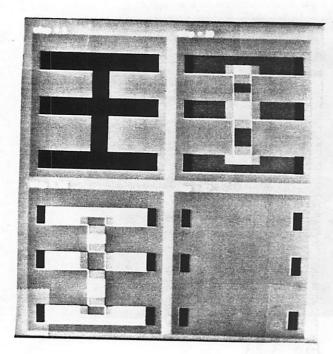

| 5.1 Nine-State Logic System                 |  |

| 5.2 Nine-State Counter-Examples             |  |

| 5.3 Logic to Electrical Mapping             |  |

| 5.4 Conversion Element Thevenin-Equivalents |  |

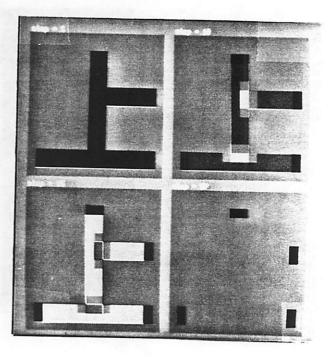

| 5.5 Thevenin DC Curves for Inverter         |  |

| 5.6 Thevenin Hysteresis for C=∞             |  |

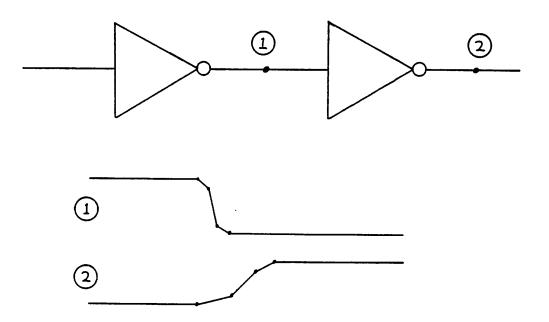

| 5.7 Inertial Delays and Multiple States     |  |

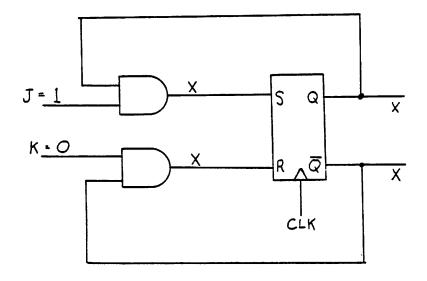

| 5.8 Logic Example for Initial Unknown       |  |

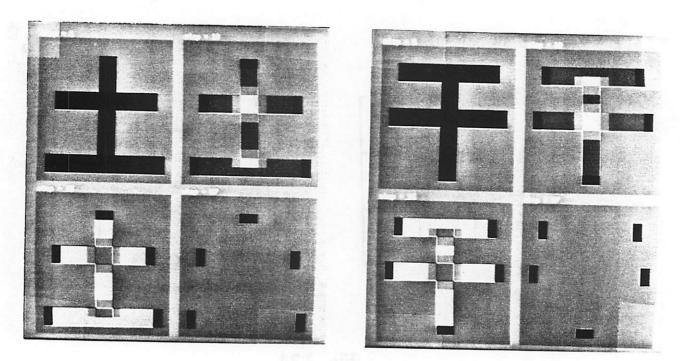

| 6.1 Example Circuit Descriptions            |  |

| 6.2 Measurement Descriptions                |  |

| 6.3 Raw Result File Names                   |  |

| 6.4 Example Circuit Characteristics         |  |

| 6.5 CPU Time Summary                        |  |

| 6.6 CPU Time Per Iteration                  |  |

| 6.7 Memory Usage Summary                    |  |

| 6.8 SPLICE1 Statistics Summary              |  |

| 69 SPICE2 Statistics Summary                |  |

# viii

9

ø

9

.

| 6.10 | Electrical Statistics for Solutions  | 138 |

|------|--------------------------------------|-----|

| 6.11 | Electrical Statistics for Time-Steps | 138 |

| 6.12 | Actual vs. Ideal Time-Step Histogram | 139 |

| 6.13 | Scheduler Operation Statistics       | 140 |

| 6.14 | Scheduler Performance Statistics     | 141 |

.

•

# **CHAPTER 1**

## Introduction

Simulation has long been used to verify the correctness of integrated circuit designs. However, increasing size and complexity of circuit design problems has forced designers to accept less and less detailed simulation. Large designs are too expensive to be simulated at the most detailed electrical level such as with SPICE2 [4]. An estimate [5] of the CPU time and memory that would be required by SPICE2 to simulate one 32-bit integer multiply instruction of a recent 450,000 device microprocessor [6] shows that the resources required exceed the capabilities of any computer that exists today. As a result, simulators have been developed to span a wide spectrum of levels of modeling, including behavioral, register-transfer, logic, timing, circuit, device and process simulation. Each simulation level can provide successively more detailed information for more computing cost. It is a desirable extension, therefore, for simulation programs to span more than one level so that models at different levels can be cross-checked. Mixed-mode simulation refers to simulation where more than one model level is used during simulation. The starting point for this work has been the SPLICE1 mixed-mode simulation program [1].

In this dissertation, advanced algorithms and techniques for mixed-mode simulation are presented. For reasons described later, only those types of simulation that can be represented by a schematic diagram i.e., are structural, are examined in detail. The thrust of this work is in two main areas. The first concerns techniques for combining effectively different kinds of simulation into one simulator. This includes issues such as simulator architecture, the representation of signals, and scheduling of activity. The second area is a new technique for circuit level simulation called Iterated Timing Analysis (ITA) [5, 7]. ITA is a relaxation based form of electrical simulation that is faster than standard techniques for simulation of large circuits. These ideas and techniques have been explored using a new simulation program called SPLICE2. To summarize a few key results here, a speedup of one to two orders of magnitude in large electrical simulations is achieved without performance penalty for mixed simulations. All levels of simulation from electrical through register-transfer level are included. Scheduling of activity is done with a floating point time variable using a novel and efficient scheduling technique.

The SPLICE2 program has been developed from a broad base of work [4, 8-14] most notably the SPLICE1 program (for more information on SPLICE1, see [1] and [3]). One goal of this effort has been to create a general-purpose program for the simulation of circuits that can be used to test new algorithms. The algorithms used must work independently of underlying circuit technology and must not be specific to just one technology, such as an n-channel depletion-load MOS process. The specific problem to be solved is that of dc operating point and nonlinear time domain transient simulation of the behavior of circuits at the electrical, logic, and register levels of description.

In the remainder of this chapter some background on simulation methods is presented and the mixed-level simulation problem is specified more fully. In Chapter 2 the issues for the design and architecture of a mixed-mode simulator and the choices made for the SPLICE2 program are presented. In Chapter 3 the electrical simulation problem is introduced and a tutorial example is used to illustrate the fundamental procedures. In Chapter 4 the Iterated Timing Analysis (ITA) method in particular is developed and compared with other techniques. In Chapter 5 discrete simulation at the Logic and Register-Transfer Level (RTL) is covered. In Chapter 6 examples of simulation spanning all the levels are given. Finally, in Chapter 7 conclusions and discussion of directions for further work are presented.

### 1.1. Simulation

If appropriate electrical circuit models are available for circuit components, the electrical behavior of a circuit can be predicted accurately using computer simulation. Usually, the

purpose of this prediction is to verify that a given network of devices will function correctly. The only way to avoid the need to verify circuit function is to use a design method that produces designs that are guaranteed to be correct by the techniques used to construct them (often referred to as *correctness-by-construction*). There is a large amount of active research on this topic but correctness-by-construction is, as yet, only feasible with specialized or constrained design styles. Other methods that are used for solving aspects of the verification problem include timing verification [15, 16] and fault analysis [17]. Timing verification is a technique that is used to verify that clocked logic designs satisfy the constraint that the delays of all paths from clocked elements, or registers, through combinational logic are less than the proper clock phase width. Fault simulation is used to determine how effective a particular input test pattern is at finding faults in the circuit. It is often based on an underlying logic simulator. Testability analysis [18] is a statistical technique used to determine the controllability and observability of the nodes of a network. It gives an estimate of the difficulty of finding a test pattern to detect faults at each node of a network. Simulation is also used as a predictor for optimization-based design of circuits [19].

#### 1.2. Mixed-Mode Simulation

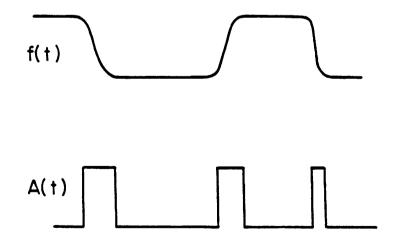

Mixed-mode simulators allow the simulation of devices by combining fundamentally different models and algorithms in the same simulation. The purpose of the following sections is to show where the SPLICE2 program fits in a taxonomy of simulation levels.

#### 1.2.1. Types of Simulation

In the course of design of electronic circuits, many types of simulation are used. Figure 1.1 lists seven kinds of simulation and indicates one typical use for each. Examples of process level simulators are the SUPREM [20] and SAMPLE [21] programs. This type of simulator is used by the process engineer to design or adjust the integrated circuit fabrication process. An example of a device level simulator is the GEMINI program [22]. Device level simulators are used by the process engineer to evaluate a process and develop models that predict the behavior of integrated circuit devices. An example of a circuit level simulator is SPICE2 [4]. Circuit level simulators are used by electrical engineers to check the detailed performance of a prospective circuit or possibly to experiment with new configurations. Timing simulation refers to the approximate electrical analysis such as found in the MOTIS [23] or initial SPLICE1 programs [1] and is used for the performance evaluation of large logic designs. An example of a logic level simulator is the TEGAS program [17]. Logic simulators are used to check the functional correctness of a logic circuit. Examples of RTL simulators are ISPS [24] and ADLIB [25]. Register-transfer level simulation differs from behavioral simulation primarily in that it is more structural with information between blocks communicated on busses. ISPS and ADLIB are RTL simulators as well as behavioral simulators. Examples of behavioral simulators include simulation languages such as GASP [26] and SIMULA [27]. These types of simulators are used by designers to check the functional correctness of algorithms or system components. Sometimes they are used to simulate microcode or perform operating system development.

#### 1.2.2. Schematic Simulation

As stated earlier, the present work deals only with schematic simulation. Schematic simulation is used here to mean simulation of electrical circuits at those model levels for which the circuits can be considered connections of lumped elements, or schematics, where

| Level             | Typical Use                     |

|-------------------|---------------------------------|

| Behavioral        | Algorithm Verification          |

| RTL<br>Logic      | Logic Verification              |

| Timing<br>Circuit | Performance Evaluation          |

| Device            | Device Model Development        |

| Process           | Fabrication Process Development |

Figure 1.1 : Simulation Levels

é

the communication between devices in the real circuit is implemented using wires. In particular this includes circuit, logic, and RTL model levels. The analysis of devices and processes is not easily represented strictly with lumped elements and wires and therefore is not schematic. The high-level models of behavioral simulation often communicate using abstract data types and via common variables and are also not schematic. The schematic levels of simulation were chosen for the SPLICE2 program since they have a common set of characteristics, as is shown in Chapter 2. Thus, SPLICE2 is intended for use in design from detailed electrical simulation up through simulation of building blocks at the register level.

#### 1.2.3. Previous Work on Mixed-Mode Simulation

A number of mixed-mode simulators have been developed in the past decade [1, 2, 13, 25, 28-33]. The term mixed-mode simulator is used here to mean one which allows the simulation of devices using fundamentally different models and algorithms in the same simulation. Some researchers use the term multi-level simulation to mean the same thing. The term multi-level is not used here to prevent confusion later since logic signal values have multiple levels and multiple strengths. A possibly better term than either of these terms is mixed-level simulation.

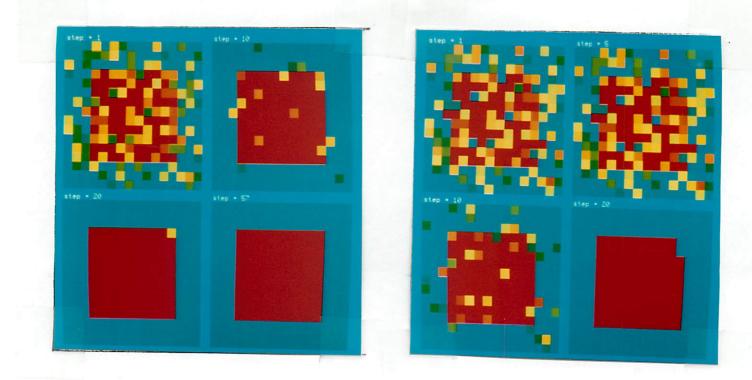

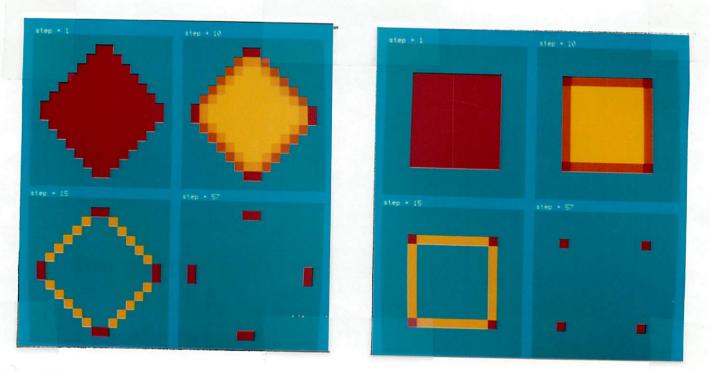

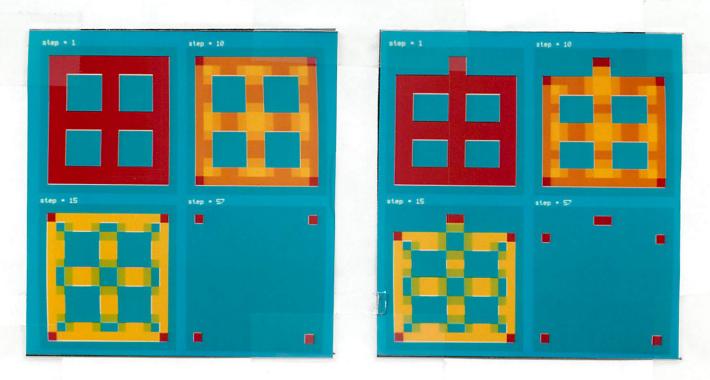

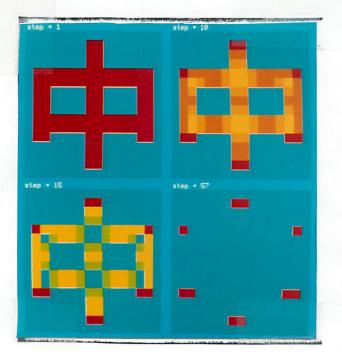

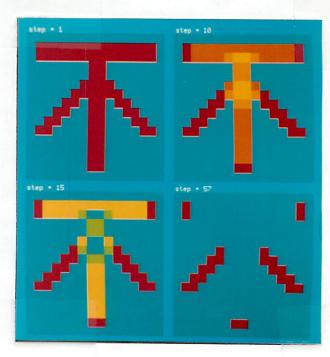

Figure 1.2 is a partial list of mixed-mode simulators that shows the choices of simulation levels implemented. The simulation levels from register-transfer through circuit simulation are grouped together as schematic levels of simulation. The last column indicates what method is used in the program to exploit latency (or inactivity) in the circuit being simulated. The bypass method refers to the technique of checking the input variables to a sub-block or element and if they have not changed since the last iteration, the sub-block is not simulated and the previous solution is used. The selective trace method refers to the technique of scheduling a sub-block to be processed only when the input signals change and not even checking it when they do not. Parentheses around the mark indicating that the simulation level is present in the program mean either that the simulation level is not fully implemented

| SIMULATOR            | SIMULATION LEVEL |      |            |          | LATENCY |     |        |

|----------------------|------------------|------|------------|----------|---------|-----|--------|

| SINCLATOR            | BHV              | RTL. | LOG        | TIM      | CIR     | DEV | METHOD |

| MEDUSA (Aachen)[31]  |                  |      |            |          | X       | X   | BY     |

| DIANA (Leuven)[2]*   |                  |      | Х          | Х        | X       |     | BY     |

| SAMSON (CMU)[13]     |                  |      | (X)        |          | X       |     | ST/BY  |

| SPLICE1 (UCB)[1]     |                  |      | Х          | Х        | Х       |     | ST     |

| SPLICE2 (UCB)        |                  | X    | Х          |          | Х       |     | ST     |

| M-M SIM. (Bell)[29]  |                  | X    | <u>X</u>   | <u> </u> |         |     | ST     |

| INTSIM (T.I.)[34]    | X                | X    | Х          |          |         |     | ST     |

| ADLIB (Stanford)[25] | X                | X    | (X)        |          |         |     | ST     |

| MIXS (NEC)[35]       | X                | X    | (X)        |          |         |     | ST     |

| Other Func.          | X                | (X)  | <u>(X)</u> |          |         |     | N/A    |

| SHIELD (Hughes)[30]  | X                | (X)  | (X)        | (X)      | (X)     |     | N/A    |

BHV Behavioral Simulation.

RTL Register-Transfer Simulation.

LOG Logic Simulation.

Timing Simulation. Circuit Simulation. TIM

CIR

DEV Device Simulation.

Bypass Method. BY

ST Selective Trace Method.

\* The DIANA program has recently been partitioned into two programs - DIANA-UP for bottom-up design and DIANA-DOWN for top-down design [33].

## Figure 1.2 : Mixed-Mode Simulators

or that the method of interfacing is such that the simulation level is not fully integrated into

one program.

9

# CHAPTER 2

# Architectures for Schematic Simulation

The architectural issues for mixed-mode simulation and the tradeoffs and choices made in the SPLICE2 simulator are presented in this chapter. The topics that follow include such issues as the goals used during the design of the SPLICE2 program, how the target computing environment affects the design choices, which simulation levels should be implemented, schematic simulation and signal representations, how different simulation levels communicate signal values, and finally how to represent time and perform event scheduling for algorithms of widely varying nature.

#### 2.1. Goals

The first step in the design of a mixed-mode simulator is defining the scope of the simulator and its goals. The scope of this work deals with the dc and transient simulation problem (DCTRAN). This type of simulation is applicable to a wide range of simulation levels that are *schematic* in nature. The characteristics that link these levels are explored more fully below in the section on schematic simulation. Briefly, the problem is to find the signal waveforms as a function of time. Other possible types of analysis include small-signal AC, noise, distortion, fault and timing verification. These other techniques are not applicable to as wide a range of simulation levels as the DCTRAN problem is. The goals for the SPLICE2 program are:

(1) Speed of simulation. Some of the major points of this thesis concern speed. It is important that each simulation level of the mixed-mode simulator when used for only that type of simulation not be significantly slower than a simulator of that type that is not mixed-mode. Otherwise, the user will resort to using the individual simulators. The overhead of translation between model levels should only be paid where necessary.

7

- (2) Technology independence. The algorithms chosen should not be limited to one technology. For example, logic simulation of TTL, ECL, NMOS or CMOS should all be possible. At the electrical level, more than just MOS devices should be available. Again, these should be available without speed tradeoff.

- (3) Permit varying simulation methods. The simulator should not decide for the user how he or she is to use it. It should provide primitive functions that are powerful enough to be used to build higher level functionality. An example of this is higher level model extraction and verification. A primitive function that takes a computed value from a simulation and stores it in a parameter of the input circuit description is sufficient to allow simulations that automatically extract relevant electrical information for higher level models in a manner that is similar to the actual test jig setup that might be used in the laboratory.

- (4) Ease of adding new models. This is an important goal at all levels of simulation but is especially important at the register-transfer level where the blocks are likely to have functionality that is quite different from standard libraries of devices and gates. This is accomplished in SPLICE2 by allowing models to be added at execution time and by using automatically generated tables to allow device models to be read and initialized.

- (5) User interface flexibility. The primitives available in the simulator should accommodate powerful and flexible user interfaces, and, as much as possible, the mechanisms by which the user interacts with the simulator should be regular and consistent.

- (6) Machine transportability. Within limits, the simulator should be transportable to a variety of computers and computer systems.

These sometimes competing goals are then weighed against one another.

#### 2.2. Computing Environment

In the design of a large program, it is important to take some note of the computing environment in which the program will be used. The stated goal of machine transportability raises the usual questions about generality versus performance. A special purpose simulation algorithm potentially can be made much faster than a general purpose algorithm. A text editor that works with only one type of video terminal can take advantage of more of the features than one that must work with many terminals. The question then arises about how much the computing environment should be allowed to affect the design decisions.

The nature of computing is changing away from the large centralized batch computing environment toward smaller, more distributed interactive computing environments. Computer and disk memory costs are dropping rapidly and good floating point performance is common. Most computing environments are becoming *virtually extended* so that programs have a much larger addressing range than that of physical memory. These trends ease the task of making a program more transportable since detailed knowledge of the underlying machine is not needed. However, the trend toward better human interfaces and work stations with high performance graphics pushes in the opposite direction.

The near-term future will continue to have lower prices for disk and main memory. The use of personal work stations with substantial amounts of main memory will provide more availability of computing but without increasing the peak performance of the computing engine over that of a shared computer. Thus, even more than today, the speed/space performance tradeoff will be biased in favor of speed at the expense of space. Applications will rely more heavily on high performance graphic interfaces for humans. The trend will be toward local-area networks that connect work stations to mainframes for simulations that are large, but the user will still want to interact with the mainframe via the work station. Thus, it is important for time consuming applications, such as simulation, to be kept portable to the large computer environment.

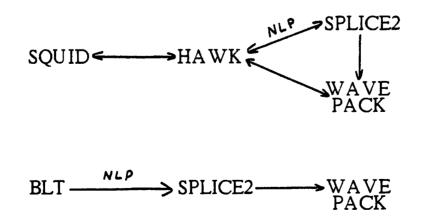

#### 2.3. User Interface

To take advantage of advanced graphic interface packages, while still maintaining large batch capability, the front and back ends of the simulator can be made separable so that they communicate via a set of functions. In the SPLICE2 program, the simulator is viewed as a net list processor (NLP) by the program that is the user front end interface. The set of functions are defined in the NLP [37] specification and are used to transfer the information about models, elements and their connectivity from the front end program to the simulator. Currently, there are two implementations of NLP driver programs for SPLICE2, a textual driver (the BLT program [38]) for compatibility with SPLICE1 and SPICE2, and a graphic editor program used at UC Berkeley for integrated circuit design and schematic diagram generation (the HAWK program [39]) Figure 2.1 shows how SPLICE2 communicates with the front end via NLP. The simulation results are written using a waveform storage package (WAP) [40] that can be monitored interactively.

Control and input for the SPLICE2 simulator are merged by using special simulation elements called control elements that cause specific control actions to occur when the element is processed by the scheduler. This is similar to using object-oriented or data-flow programming

Figure 2.1 : User Interface

3

methods where the functional or data-flow program is the circuit that is made of control elements. Control is accomplished by creating special elements and setting their parameters in exactly the same way that ordinary elements are created. This results in an extremely uniform interface between the front end program and the simulation engine. Thus, execution time options are passed as parameters to an option control element and the end of simulation occurs when the *end* control element is processed. In a similar fashion, interactive breakpoint elements are available to suspend the simulation at specified times or on simulation generated events. In this way, greater functionality can be added for the interactive environment without affecting the ability to run in a large batch environment.

#### 2.4. Adding New Simulation Models

New simulation models are added to the SPLICE2 program by allowing the user to program the new element behavior in the C programming language, compile the new model using the C compiler into machine executable object code, and then load (sometimes called link) the new machine code with the SPLICE2 program. This technique of extending and using an existing programming language for writing user generated model code is sometimes called an *embedded* approach. The details of creating a model for the SPLICE2 program are given in Appendix D. Briefly, the user must provide three types of information to the simulator for a new model: the topology (or net list information), the parameters, and the executable code. The topology and parameters are specified in a table that is built by a preprocessor which reads the C language data structure declaration for the element. The declaration has some added keywords for indicating the name, simulation level, and direction for each terminal for the element. The keyword PARAMETERS is used to indicate which members of the data structure are to be filled in as parameters by the user at run time. Thus, the member name and type given in the declaration of the data structure are automatically used as the name and type of the parameter for reading and initializing. In this way, there is very little chance of error in naming and using the parameters. Thus, adding a model requires only the

declaration of its C programming language data structures and the function which implements the model. An optional initialization function can be provided if any pre-calculation of values is needed for speed (such as the critical voltage for diodes [4]).

Dynamic loading is a technique for adding executable code to a running program and is found commonly in LISP programming environments [41]. SPLICE2 has a dynamic loading capability which, in combination with the table mechanism for model declaration presented above, allows new models to be added easily to a simulation even after execution of the simulation program has begun. Dynamic loading is not machine transportable and usually needs to be re-programmed for new computing environments and thus is at odds with the goal of machine transportability. However, conditional compilation makes it possible to load models statically and simulate when dynamic loading is not available. Libraries of models compiled into the simulator are adequate for electrical and low-level logic simulation, but at the register-transfer level (RTL), the user must be able to add new functions easily. RTL simulation is described in more detail in Chapter 5.

## 2.5. Inter-Simulation Communication

One basic decision about the simulation architecture that must be made at the outset is how the different levels of simulation communicate with each other and how much each level of simulation must know about the other levels of simulation. Various approaches exist, such as the SHIELD program [30] which runs each level of simulation separately with each simulation algorithm advancing in time only so far as its inputs allow. This allows each simulation program to be optimized for its type of simulation and keeps all the knowledge about how to translate from one level to another isolated in the control program. The primary difficulty with this approach is that the overhead is high when several levels are used and components of differing type are intermingled arbitrarily. A copy of every interface signal must be kept and transmitted through the supervisor program. Also the overhead of the scheduler is incurred more than once for each simulation event since each simulator performs time control locally as well as in the supervisor and must check to see when to return control to the supervisor.

The design choice for the SPLICE2 program has been to use one integrated scheduler mechanism for all simulation levels. Algorithms have been chosen and developed that use signals in a consistent way so that translation of a signal from a more detailed level to a less detailed level results in a reduction of detail that preserves the maximum amount of information. The design of the scheduler and the signal representations are described more fully later in this chapter.

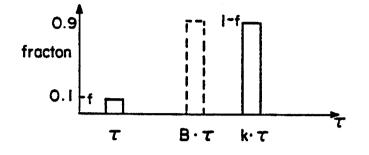

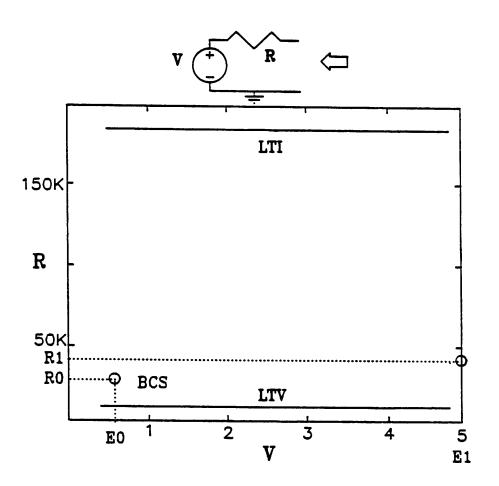

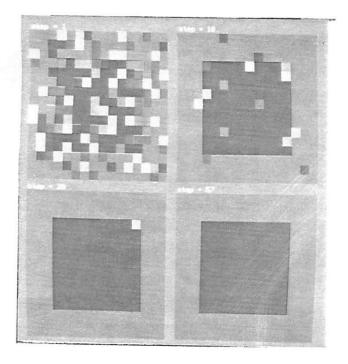

#### 2.6. Choice of Simulation Levels

Figure 2.2 gives an estimate of the CPU time and memory that would be required to simulate one 32-bit integer multiply instruction of a recent 450,000 device microprocessor [6] using four different levels of device models [5]. The multiply requires  $1.8\mu$ s in 33 clock cycles of 55ns each. These estimates are based on experience with the SPICE2 circuit analysis program [4, 42] and the SPLICE1 mixed-mode simulator [1, 3]. The CPU times shown are normalized to the performance of an IBM 370/168 and ignore virtual machine overhead i.e., assumes uniform addressing and memory access times. The term circuit means accurate analysis such as found in the SPICE2 program. Timing refers to the approximate electrical analysis such as found in the MOTIS [23] or SPLICE1 version 1.3 programs [1]. For the purpose of this work, *logic* means discrete valued simulation of unidirectional elements and *RTL* means *register-transfer level* where the elements may use complex internal models, such as an arithmetic logic unit. These model levels differ mainly in the way that signals are represented and combined, as is described later.

Figure 2.2 shows how reducing model complexity reduces the simulation cost. Two effects are responsible for this reduction. The first is that simpler models require less CPU time to evaluate. The second is that higher-level models represent the functionality of a number of lower level models and therefore require less data storage and fewer evaluations.

| LEVEL                | CPU TIME            | log <sub>10</sub> (CPU) | MEMORY         | log <sub>10</sub> (MEM) |

|----------------------|---------------------|-------------------------|----------------|-------------------------|

| CIRCUIT              | 6 Months            | 7.2                     | 250 MB         | 8.4                     |

| TIMING<br>ITA<br>NTA | 12 Hours<br>8 Hours | 4.6<br>4.5              | 60 MB<br>30 MB | 7.8<br>7.5              |

| LOGIC                | 10 Min.             | 2.8                     | 4 MB           | 6.6                     |

| RTL                  | <<1 Min.            | 1.8                     | <<.5 MB        | 5.7                     |

Figure 2.2 : Simulator Performance

The logarithmic values for time and memory indicate about one order of magnitude reduction in storage per level and about two orders of magnitude reduction in CPU time. The CPU time reduction reflects the effect of both reduced device count and simplified models.

The levels of simulation chosen for implementation in the SPLICE2 program are circuit, logic and RTL. The circuit simulation level uses a new method called iterated timing analysis (ITA) [3, 5] that is based on the non-iterated timing analysis (NTA) [1] from the SPLICE1.3 program with the relaxation iteration carried to convergence. ITA requires approximately 50% more CPU time than plain timing analysis but the actual requirements depend on the characteristics of the circuit being analyzed. It provides dc operating point and voltage waveforms with accuracy comparable to that of SPICE2. ITA is presented more fully in Chapter 4.

The choice of circuit, logic and RTL is only one choice for a set of simulation model levels. More detailed simulation such as device modeling and more abstract simulation such as behavioral simulation are not included in SPLICE2 because the algorithms are not similar enough to be compatible with the other three. Circuit, logic and RTL are similar in that circuits of those levels are represented by schematic diagrams. Figure 2.2 suggests that the choice of ITA, logic and RTL spans the range of schematic simulation fairly evenly. The difference in run time between ITA and logic analysis suggests that another form of approximate electrical simulation between ITA and logic might be appropriate. The inclusion of each additional model level adds more overhead in translating to other levels and makes the program bigger and more complicated. This overhead and complexity must be offset either with improved accuracy or faster overall simulation performance due to the hierarchy of model levels (higher level models require less time to evaluate than lower level models). The large fixed cost of adding a model level suggests that ITA, logic, and RTL are sufficient. In Chapter 5, it will be seen that a more general logic model can be used in the same way as a simple logic model and run with speed comparable to the simpler model. Some simulators allow the simultaneous simulation of logic elements that have models that use different numbers of logic states by allowing arbitrary numbers of translation routines. This approach can be expensive both in CPU time and complexity of the program.

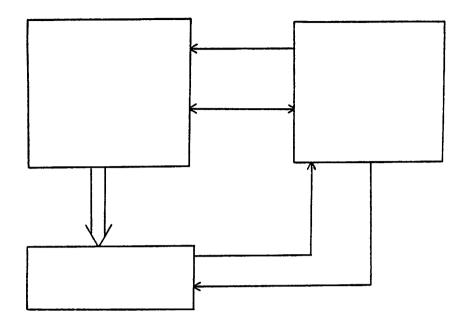

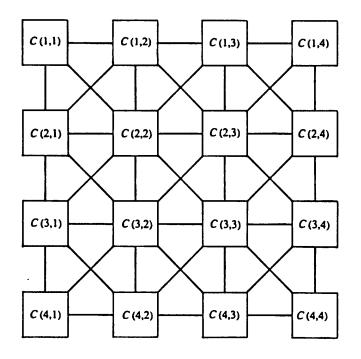

#### 2.7. Schematic Simulation

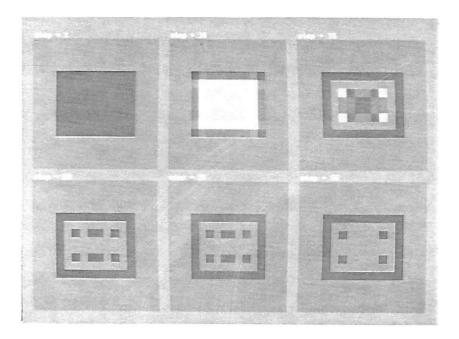

Schematic blocks are modules that communicate along wires. Figure 2.3 illustrates the structural relationship between blocks and wires. This partitioning suggests an architecture where blocks are represented by routines that model their behavior and wires (nets or nodes) are elements that understand how to transmit and translate the signals. This results in a simple architecture of one data structure for topology and state and one model routine for each element. The wires have model routines that implement each level of simulation. Thus there are electrical, logic, and RTL net models and their corresponding signal types. Adding a new level of simulation amounts to defining the new signal type, adding the new net model routine, and updating the other net models to coerce to and from the new signal type. It is this coercion overhead that limits the number of different simulation levels.

Figure 2.4 shows a situation where the net model translates from an electrical signal to logic and register levels. As integrated circuit switching devices become faster and faster, more of the total delay is due to the wires. Having an explicit net model allows these effects

Figure 2.3 : Schematic View of Circuits

to be treated accurately. The representations of signals and the method of combining them is critical for accurate simulation. The signal types in the SPLICE2 program are presented in the next section and the mapping from one to another is shown.

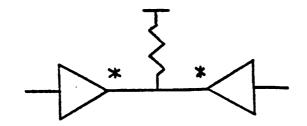

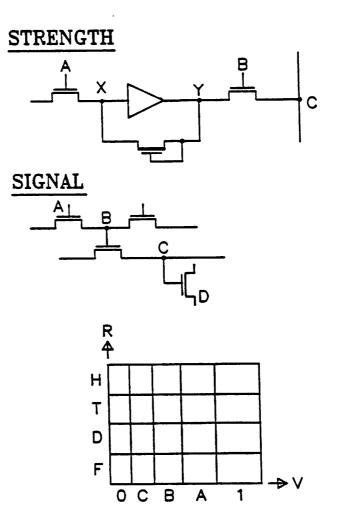

#### 2.8. Signal Representations

A consistent representation for signals over all model levels is critical for accurate mixed simulation. The main difference between model levels is the level of detail used in the models and signals. A high level model uses fewer bits of precision than a more detailed model. This is not to say that the higher level model is less accurate. The fact that the voltage on a wire is 4.285 Volts adds no useful information if the question being asked is simply whether the signal is true or false. Excess precision can easily get in the way when it is not appropriate and *data hiding* is important in hierarchical abstraction.

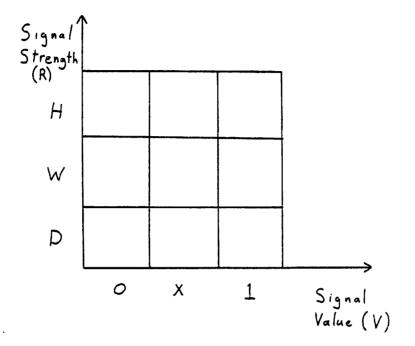

Since the function of nets is to combine signals, signals must have not only a *level*, but also a *strength*. For steady-state analysis, a Norton or Thevenin equivalent is needed for the

Figure 2.4 : Net as an Element

contribution of each element [43]. Figure 2.5 shows a pair of open-collector drivers that are connected to a bus. This wired-and function is a common example of how signals are combined. Since elements of all types can be connected together, information on how to combine them all must be available through the strength. The difference is that the number of bits used to represent the signal goes down as the detail decreases. The signal level represents the current state of the wire. At the electrical level it is a floating point number for the voltage while at the logic level the number becomes a small integer. Register signals are reduced to binary values that may be collected into arrays in order to represent busses as a single number. A strength bit-array is still necessary to indicate which bits are being driven.

Signal = Value + Strength Circuit: Floating Point Timing: Integer Logic: Integer Register: Bit Array

Figure 2.5 : Signal Representations

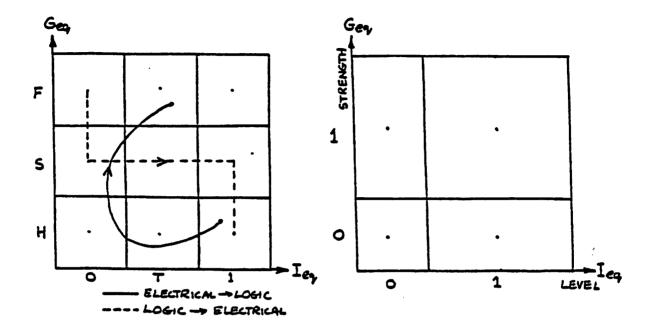

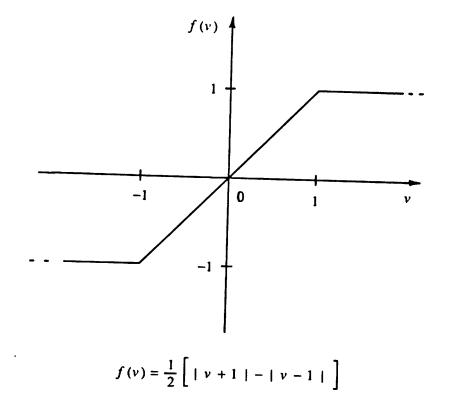

## 2.9. Signal Mapping

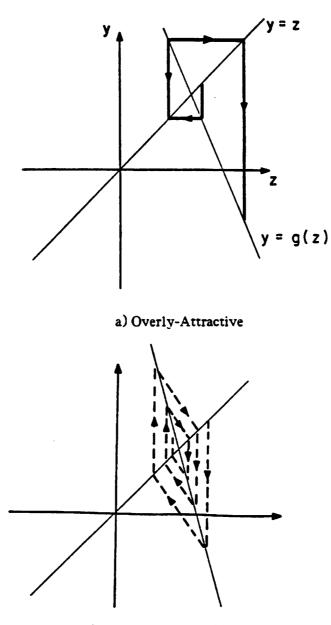

Communication between models in a mixed simulation requires translation of signals. At least one function to map signal types in each direction is needed with the addition of every model level. Figure 2.6 shows an example of possible mappings to and from the circuit level, or continuous domain, into the logic level, or discrete domain, and to and from logic into register. The choice of thresholds need not be uniform, but must cover all possible values. The same considerations apply to the discrete mappings. The number of states and the assignment of thresholds clearly depends on how much accuracy is desired and the technology being simulated. More detail on signal mapping is presented in Chapter 5 where discrete simulation is described.

#### 2.10. Time Representation and Scheduling

One of the most challenging tasks in designing a mixed-mode simulator is how to reconcile the divergent requirements of different algorithms for the representation and

Figure 2.6 : Signal Mapping

advancement of time. The purpose of this section is to define event scheduling, outline some existing event scheduling techniques, resolve the issue of how to represent time, and present some results on a novel approach implemented in the SPLICE2 program called *cached* scheduling.

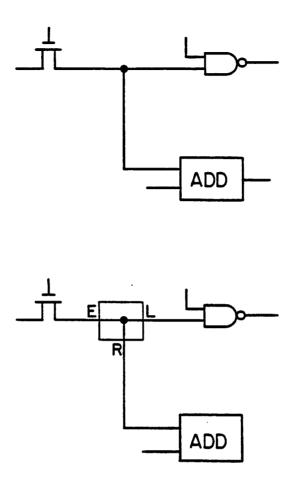

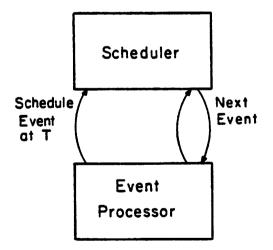

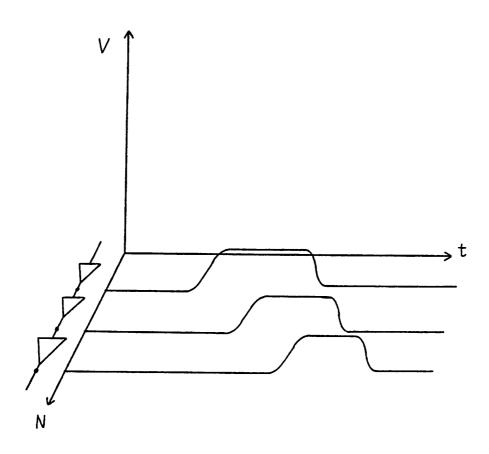

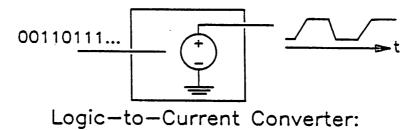

## 2.10.1. Event Scheduling

Discrete event simulation refers to computer simulations in which events occur at discrete, arbitrary points in time. The management of time-flow consists of sequencing the events and executing (or processing) the events and propagating their effects. Figure 2.7 illustrates the principal activities of event scheduling. The event processor carries out whatever action the event is intended to cause and the scheduler sequences the events and controls the evolution of time. The two main functions are schedule an event at time t in the future, sometimes called the *hold* function, and *next event* for finding the next action to perform. Depending on the simulator, there may also be an *unschedule* function to remove a pending event from the queue.

In circuit level simulators such as the SPICE2 program [4], the current value of time is represented by one floating point number that is the same for all of the equations. In logic simulation, such as in the VOTE program [44, 45], time is represented by an integer value and all delays must be specified as a multiple of the unit of time. Scheduling is done via the *time mapping* technique. A good description of the time wheel and the time mapping methods for time control is given in [46]. A technique similar to time mapping is used in the SPLICE1 program [1]. General purpose simulation languages such as SIMSCRIPT [47], GPSS [48], GASP [26], SIMULA [27], and others use a list of events ordered by a floating point time variable. A method for speeding the insertion of events onto the list called the indexed list method is presented in [49] which also gives a good comparison of scheduling techniques. Another variant of the indexed list method is described in [50]. The indexed list method with floating point time is used in the SAMSON program [13]. Floating point time is also used in the

Figure 2.7 : Event Scheduling

ð

#### ADLIB/SABLE program [25].

In an electrical level algorithm, there is a relatively large amount of computation done when a solution is obtained at a time-point and so the scheduling overhead is not very important. However in logic analysis, relatively little computation is done for each solution. Thus, the scheduling method must be fast and robust in the presence of large numbers of events if it is not going to limit the performance of the simulator.

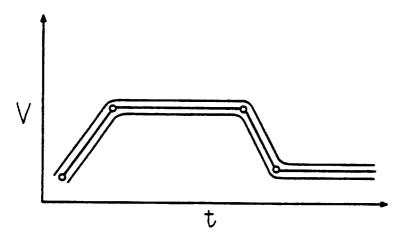

#### 2.10.2. Representation of Time

A mixed-mode simulation environment requires a large amount of range and precision from the time representation. The time-steps required during the solution of electrical equations may be considerably smaller than the smallest time-step of interest to the user. Therefore, the unit of time may be as small as  $10^{-12} - 10^{-15}$ . The total simulation time can be orders of magnitude larger than the rise and fall time of any particular logic gate. To be able to represent total simulation times on the order of 1 second yet still resolve electrical events requires a range of  $\approx 10^{15}$  or  $\approx 2^{50}$ . Thus the usual 32 bit integer with a range of  $\approx 10^9$  is not sufficient. A 64 bit integer has a range of  $\approx 10^{19}$  and would allow simulations of over one hour of simulated time with a resolution of  $10^{-15}$  seconds. Unfortunately, common programming languages do not have intrinsic 64 bit integer data types (even though some computers such as the VAX support it). Functions could be added to perform the extended arithmetic, but the overhead of calling those functions would be quite large. A single precision floating point number usually has a mantissa with a size less than 25 bits. Thus it has inadequate precision to resolve small time-steps when the time becomes large. A double precision floating point number usually has a mantissa of size greater than 50 bits and thus has the required precision. On computers with floating point units, the overhead of using a double precision number for time is likely to be less than the function call overhead of using an extended integer. An argument can be made that extended integers have a place as a scalar type in computer languages.

One disadvantage of the floating point representation for time is that the finite mantissa size causes arithmetic operations not to be commutative and associative. Thus, the exact result of a calculation depends on the order in which the operations are carried out. An advantage of the extended integer is that it can be used directly or bits extracted for use with the scheduler index. Tom Quarles has pointed out [51] that if care is taken to prevent overflow of the mantissa, then the floating point number can be used for exact calculations. This is similar to using the floating point number as an integer of size equal to that of the mantissa and is what is done in the SPLICE2 program. A double precision variable is used to represent time and two C language macros are defined: TO\_NORM\_TIME() to convert simulation time to normalized form and TO\_WALL\_TIME() to convert normalized time to simulation time. Addition and subtraction of normalized times can be performed safely but computations involving multiplications and divisions require re-normalization of the time variable. Because of the use of a C language type definition for time, if a 64 bit integer were to become available in the C language, only the type definition and the macros would need to be changed.

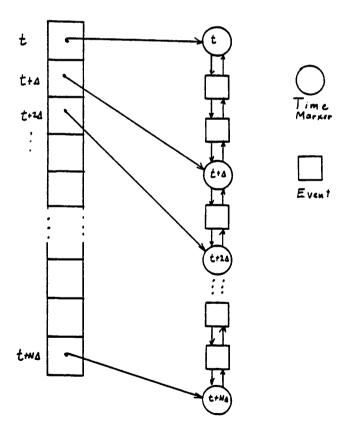

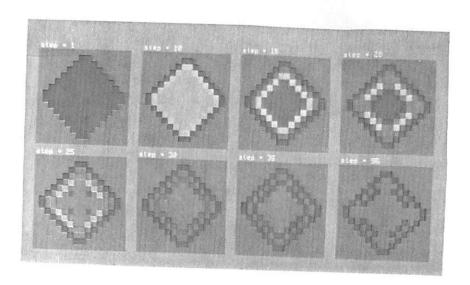

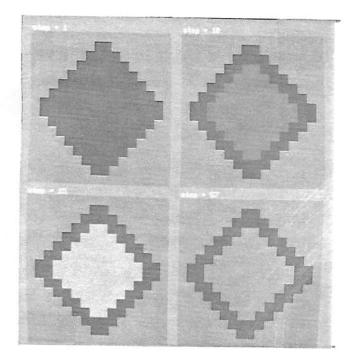

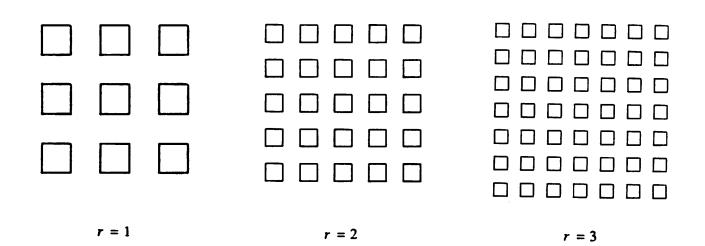

## 2.10.3. Indexed List Method

A simple organization for ordering all events by time is a linear linked list. If events are likely to be canceled, a back link is useful for quick removal from the list. For sequences of events with uniform distributions, the average number of scans for insertion on a linear list is  $\frac{N}{2}$  where N is the number of events already on the list. Thus, the total number of scans to insert N events is proportional to  $N^2$ . The indexed list method mentioned above reduces the number of scans by dividing the list into smaller sub-lists each of which spans a sub-interval of time. Figure 2.8 shows the data structure for the indexed list method. Dummy events are created as time markers to head each sub-list. The sub-intervals usually span equal sized time bins, although nonuniform spacing can be used. With uniform intervals, insertion of a new event is done by computing the index into an array of pointers to the marker events and then linear insertion of the event on that sub-list. The index interval size must be adjusted 3

periodically so that the number of events in each sub-list is neither too few, which means that excessive marker events are allocated and processed, nor too many, which means that insertion will degenerate to the linear case. For large N and uniform event distributions, the speedup of indexed list insertion over linear list insertion will be equal to the number of index bins.

The indexed list method has been implemented in the SPLICE2 program and measurements made to determine the overhead of the marker events and the insertion time for linear lists. These timings and all of the other performance figures quoted in this dissertation were made on a Digital Equipment Corporation VAX 11/780 with floating point accelerator. Figure 2.9 is a plot of execution time versus the number of dummy events in the list. The intercept

Figure 2.8 : Indexed List Method

at zero is labeled "b" on the graph and indicates an overhead of  $39 \ \mu S$  per marker event. This number is a lower bound and is made up mostly of the function call and return time plus the time to increment the current index of the array. If a normal event execution time were *m* times longer than the marker event execution time and the fraction of total events which are marker events were *f*, then the execution overhead events would be  $\frac{f}{f+(1-f)m}$ . For  $f = \frac{1}{2}$  and m = 4 the overhead would be 20%.

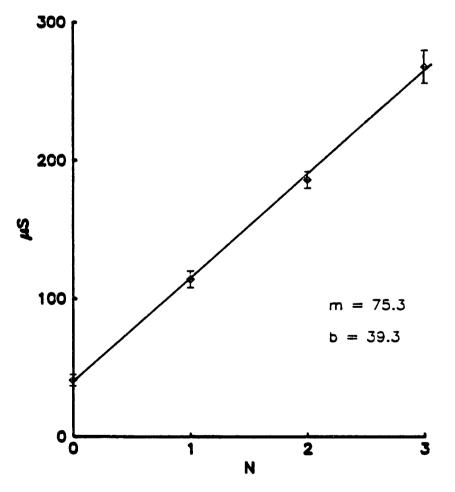

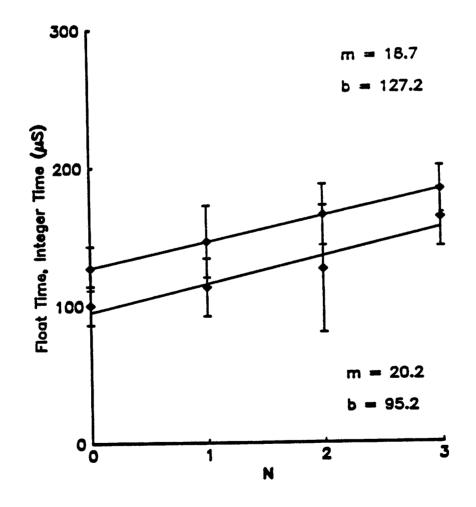

Figure 2.10 shows the time required to perform linear list insertion as a function of the number of events already on the list with the slopes and intercepts of the curves labeled "b"

Figure 2.9 : Marker Event Overhead

and "m", respectively. The upper curve is for the indexed list method using a single precision floating point number and the lower curve is using a 32 bit integer number. The intercepts at zero show\_that floating point scheduling requires about 30% more time than integer scheduling however the slopes are the same to within the accuracy of the measurements. Thus the increase in CPU time for using floating point numbers corresponds to slightly more than the amount of CPU time to scan one extra event. As the number of events increases, this difference becomes less important.

Figure 2.10 : List Insertion Time

The indexed list approach has several disadvantages. First, the dummy events require storage and, depending on details of the implementation, must be allocated and freed. Second, the dummy events lengthen the linear event list by their presence and require CPU time to be processed, thereby limiting the peak speed of the simulator. Third, schemes to re-compute the index interval for the array are required which can lag behind changes in the distributions of events and be fairly involved to carry out. Fourth, backing up simulation time is difficult. This situation occurs in electrical analysis when a time-step is rejected and the interval must be re-simulated with a smaller step size.

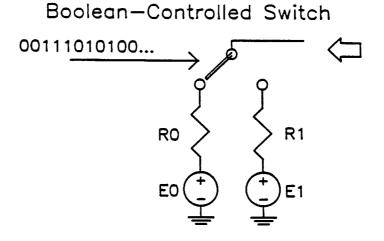

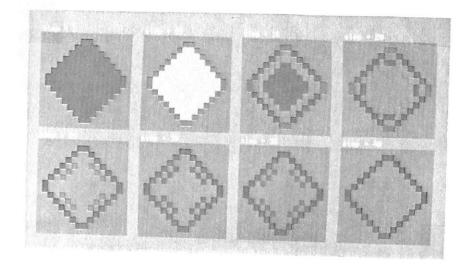

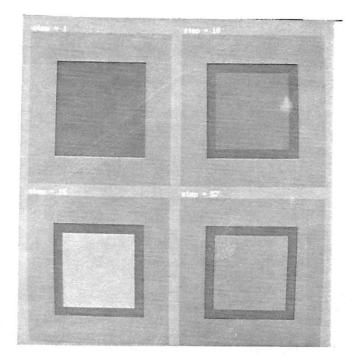

#### 2.10.4. Cached Scheduling

Cached scheduling is a new technique for indexing events which makes use of the statistical properties of the time distribution of event scheduling operations. Both the indexed list and the cached list methods use indices to find a *good* starting point in the linear list of events from which to insert the event to be scheduled. The cached list method makes use of the fact that the most recently scheduled event often is likely to be a good guess for the point at which to insert the next event. This is similar to the least recently used (LRU) policy for determining which memory buffer to invalidate in hardware cache memory management.

The method requires keeping one or more *cache pointers* to events. A cache pointer is *valid* if it points to a scheduled event whose scheduled time is less than or equal to the time at which the new event is to be scheduled. Before beginning insertion at the head of the list, the cache pointer is checked for validity and if it is valid, it is used as the starting point for the linear insertion. If the cache pointer is valid, then the event pointed to is at least as good a starting point as the head of the list. After inserting the new event on the list, the cache pointer is set to point to the new event.

Measurements have been made on a two element cache which has been implemented in the SPLICE2 program. One of the cache pointers is reserved for events which are scheduled at the current value of simulated time. When the current time cache pointer misses, then scheduling is performed using the other cache. The measurements are summarized in Figure 2.11. The peak performance is seen to be better than the peak performance of the indexed list technique as compared with Figure 2.10. Note that time is represented as a double precision floating point number for these measurements. The most important number for estimating cache effectiveness is the hit ratio which is the ratio of the number of times that the cache is found to be valid to the total number of schedules using that cache. This simple scheduling method is adequate for electrical analysis and some logic analysis. The overhead becomes fairly high in the Logic3 example indicating that the two element cache is overloaded.

A generalization of the cached list method is the *cached indexed list* method. The cached indexed list method uses an array of cache pointers very similar to the array of pointers to dummy events that is used in the indexed list method. The intention is to add more cache pointers and use the indexing mechanism to make the loading more uniform in order to increase the hit ratio. The algorithm proceeds as follows. When a new event is to be scheduled, the time is used to index into the array of cache pointers. If the index is larger than the array, then the *remote event* action, which is described later, is performed. If the cache pointer is valid, then it is used as the starting point for linear insertion and the cache pointer is updated to point to the new event just inserted. Otherwise, the cache point for linear insertion. If none of the cache pointers are valid, the head of the list is used. The original cache pointer indicated by the indexing operation is updated to point to the new event just inserted.

One observation is that the correct operation of the scheduling procedure does not depend on the validity or efficiency of the cache. In fact, all of the entries could be set to a null value (flushed) every scheduling operation and it would still work. Also, the efficiency of the cache is increased as the loading is made uniform. A cache pointer becomes invalid by one of two mechanisms: first, the event becomes processed and passes into the past, or second, the event is

| Example | NEN | NLN | NRN | %CPU | CHR   | CAIT (µs) |

|---------|-----|-----|-----|------|-------|-----------|

| Elect1  | 169 | 0   | 0   | 5.0  | 0.931 | 157       |

| Elect2  | 223 | 0   | 0   | 2.7  | 0.932 | 118       |

| Elect3  | 169 | 0   | 0   | 8.0  | 0.919 | 271       |

| Logic1  | 1   | 153 | 0   | 10.5 | 0.702 | 319       |

| Logic2  | 1   | 61  | 0   | 5.2  | 0.596 | 205       |

| Logic3  | 1   | 235 | 0   | 39.5 | 0.762 | 423       |

| Mixed 1 | 289 | 61  | 0   | 7.1  | 0.923 | 227       |

| Mixed2  | 1   | 118 | 4   | 28.3 | 0.691 | 292       |

| En en la | First Cache |       |          | Current Time Cache |                |                |  |

|----------|-------------|-------|----------|--------------------|----------------|----------------|--|

| Example  | TNS         | HR    | AIT (µs) | TNS                | HR             | AIT (μs)       |  |

| Elect1   | 107816      | 0.645 | 416      | 463524             | 0.998          | 96             |  |

| Elect2   | 58033       | 0.804 | 162      | 127533             | 0.99           | 96             |  |

| Elect3   | 801182      | 0.799 | 535      | 1253854            | 0.996          | 102            |  |

| Logic1   | 6209        | 0.603 | 411      | 2869               | 0.918          | 94             |  |

| Logic2   | 3801        | 0.487 | 234      | 1611               | 0.852          | 106            |  |

| Logic3   | 270396      | 0.668 | 582      | 135211             | 0.95           | 113            |  |

| Mixed1   | 123892      | 0.602 | 812      | 534643             | 0 <b>.99</b> 7 | <del>9</del> 0 |  |

| Mixed2   | 87077       | 0.585 | 363      | 41220              | 0.914          | 115            |  |

NEN = Number of Electrical Nets

NLN = Number of Logic Nets

NRN = Number of Register Nets

%CPU = Percent of total time spent scheduling

CHR = Composite Hit Ratio

TNS = Total Number of Schedules

HR = Hit Ratio

AIT = Average Insertion Time

CAIT = Composite Average Insertion Time

#### Figure 2.11 : Cache Performance Measurements

un-scheduled. The first mechanism is not important since new events are not scheduled in the past. Either there are other events at the current time and the first entry of the cache points to the last one of them, or the head of the list is the best starting point for insertion.

In steady-state operation with all of the cache pointers valid and a uniform distribution of events in time, the number of linear scans for insertion is comparable to that for the indexed list method. A uniform random distribution has no locality of reference and therefore is a difficult test example. With a uniform index interval and a uniform distribution, the average number of events per sub-list is equal, say N. The indexed list method will always start at the beginning of the interval and scan to the position of the new event which will be  $\frac{N}{2}$  positions down the list on the average. With the cached indexed list method each cache pointer will point to the middle of its interval on the average. The probability of a cache hit will be  $\frac{1}{2}$  and if it occurs the number of scans will be  $\frac{N}{4}$  on the average. If the cache hit does not occur, then the number scans from the preceding cache pointer will be  $\frac{N}{2}$ to get to the beginning of the current interval and  $\frac{N}{4}$  to get to the location in the list in the current interval. Thus the average number of scans will be  $\frac{N}{2}$  which is the same as the indexed list method for the uniform distribution.

The main advantage of the cached indexed list method is that there are no dummy events to maintain and re-index. This makes it very simple to back up time which is occasionally necessary for electrical algorithms as has been pointed out. To change the index interval, all that is necessary is to change the index interval variable to its new value. The array of cache pointers need not be altered although it might be advantageous to null them or copy some. The index will automatically achieve equilibrium as events are scheduled and the cache pointers are *faulted in*.

The remote list is managed using a cache with an index interval ten times larger than the main cache. Overflow from the remote index is handled with a final remote list pointer similar to that used in the indexed list approach. The index interval is computed by choosing a value that maintains the number of events in the near and remote sub-lists at some ratio. Other schemes for computing the index interval could be used.

Both the indexed list method and cached indexed list method can have long insertion times when the index is overloaded with events or for pathological event distributions. The technique described by Wyman [50] can be used to improve the worst case performance of the scheduler for both methods at the cost of adding more dummy events. Also, if the list is doubly linked, as is the case in the SPLICE2 program, then insertion scans can also be done in the reverse direction. This would avoid the need to scan events in the previous interval in order to arrive at a position in the beginning of the current interval.

Another way to distribute the loading on the cache is to use auxiliary information about the events such as whether they are electrical or discrete. A separate set of cache pointers could be used for the different types of events. A cache of size equal to the number of buffers used in the windowed iterated timing analysis algorithm works perfectly since electrical events are not scheduled at other times.

> i. R

Ì

30

÷.

# CHAPTER 3

# **Electrical Simulation**

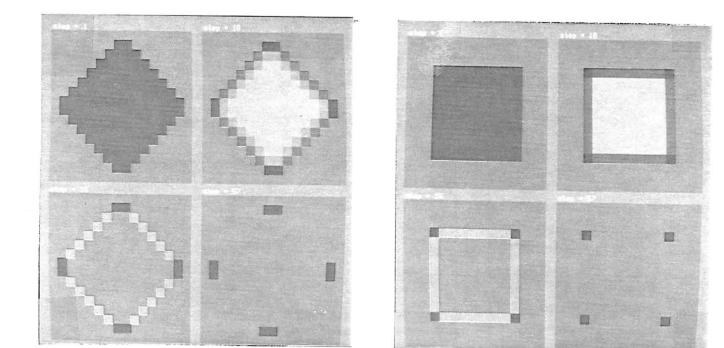

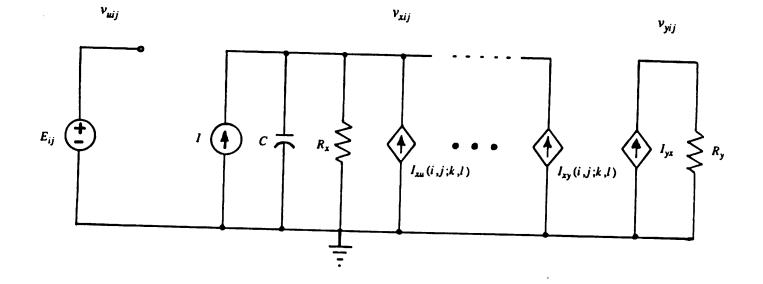

Electrical analysis of circuits is used to predict their accurate waveform behavior and is the most detailed level of simulation in a schematic simulator. The present chapter provides the background with which to compare the Iterated Timing Analysis (ITA) algorithm, described in detail in Chapter 4, with other existing techniques. In Section 3.1, the nonlinear dc and time-domain transient (DCTRAN) problem to be solved is defined. A specific circuit example is used in Section 3.2 to show how the nonlinear time-varying circuit equations are solved. In Section 3.3, a circuit interpretation for iterative processes is presented and some of the stability properties are examined. In Section 3.4, the differences between existing techniques for detailed electrical simulation are outlined. Finally, error measures and potential speedup factors are presented in Sections 3.5 and 3.6.

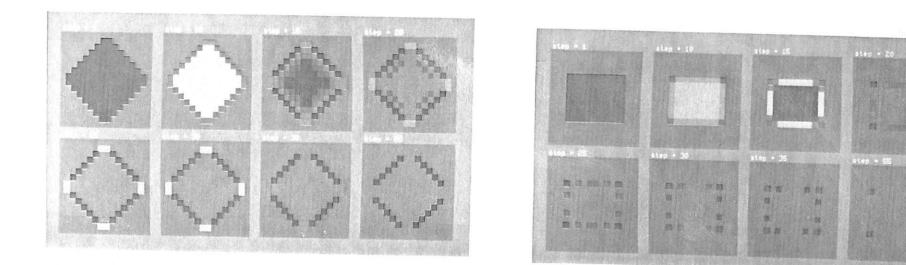

## 3.1. The DCTRAN Problem

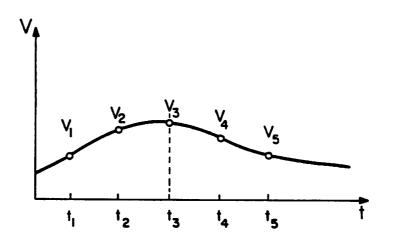

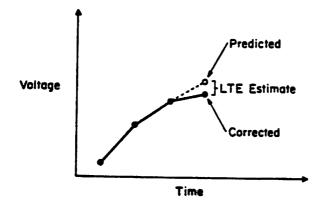

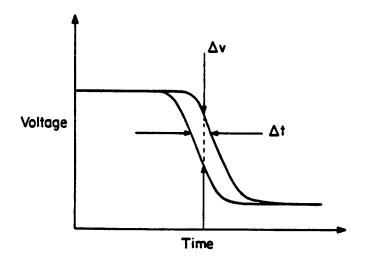

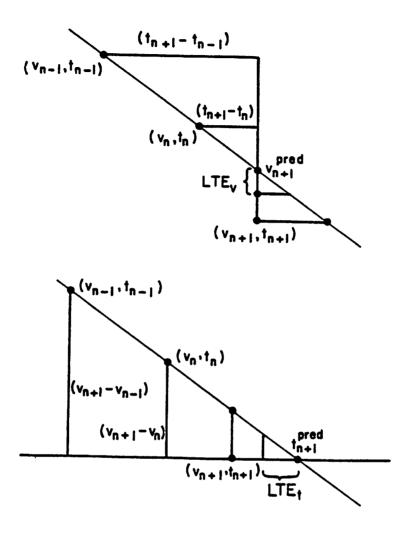

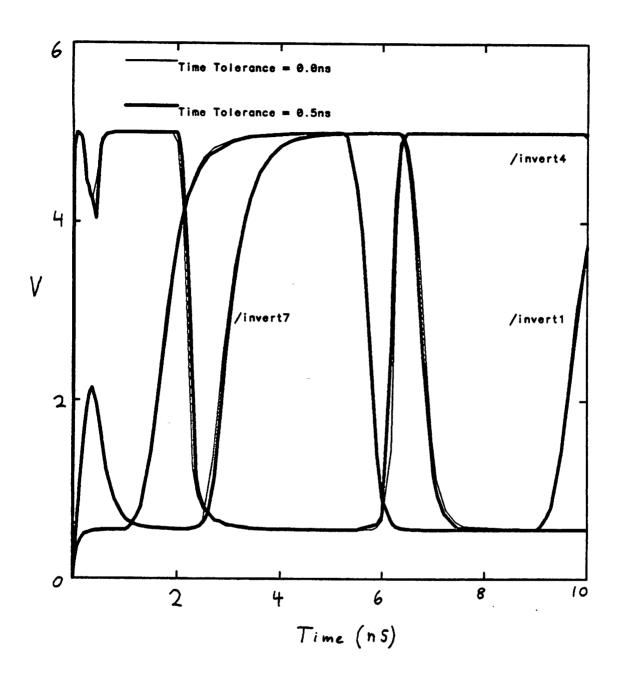

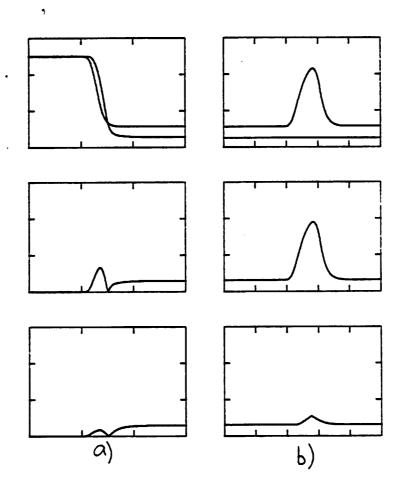

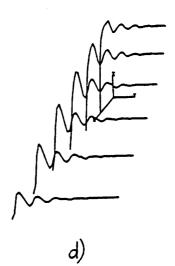

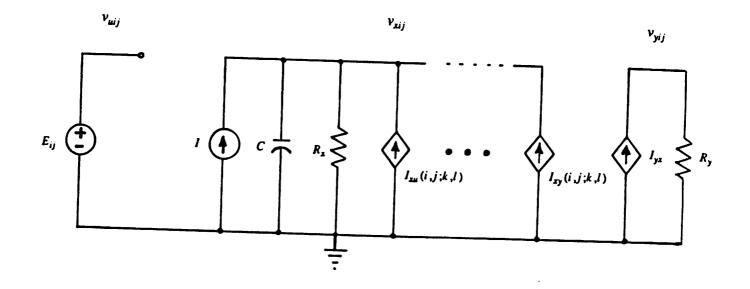

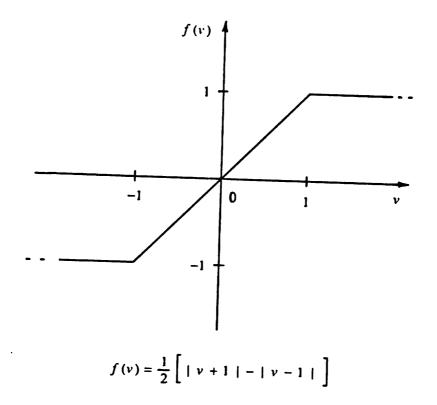

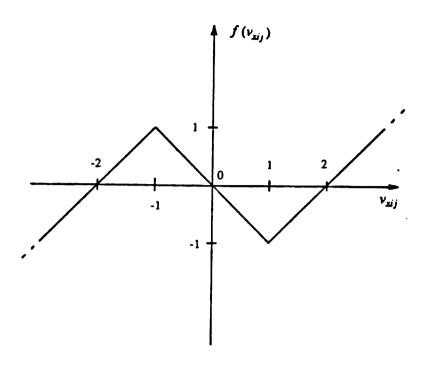

The DCTRAN problem is defined as finding the voltages as a function of time on all of the wires of a given network. Figure 3.1 illustrates this for an example of a chain of inverters. The problem then is to compute an approximate voltage waveform for all of the wires that is *close enough* to the exact solution. The meaning of *close enough* is examined more fully in section 3.5.

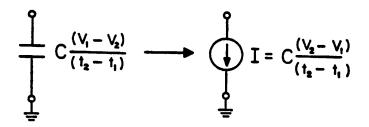

The elements of the network are modeled by mathematical equations called the Branch Constitutive Equations (BCE). Together with Kirchhoff's current and voltage laws, these models result in a system of first order nonlinear, time-varying, ordinary differential equations (ODE) which must be solved to predict the electrical behavior of the network. Most circuit simulation programs solve this system of equations by slicing the waveforms into discrete time intervals, or *time-steps*. Circuit elements, such as capacitors and inductors, whose branch

Figure 3.1 : DCTRAN waveforms

relations contain the time variable are said to have *memory*. Using a numerical integration scheme, these elements are then modeled with equivalent *companion* models which, at any given instant of time, are characterized by equations similar in form to the memoryless elements [4, 52]. This leads to a sequence of equivalent problems which, when solved, result in the desired waveforms. For practical numerical integration methods, these waveforms converge to the exact solutions of the ODE's as the time-steps are taken sufficiently small. Another class of methods, known as *waveform relaxation*, [53] has recently been studied which does not decompose the time behavior of the network into a sequence of dc-equivalent problems. Instead, the solution to each equation is approximated for all time and the resulting

waveforms are then iterated. In contrast to the waveform approach, the other way of iterating is sometimes referred to as *point at a time*.

In the point at a time approach, each system of nonlinear equations is solved using an iterative technique. In the next section these ideas are demonstrated using the specific example of a resistor, a capacitor and a diode.

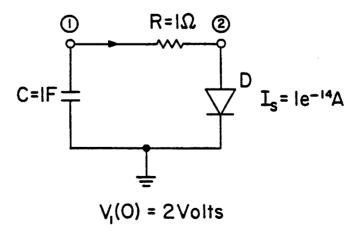

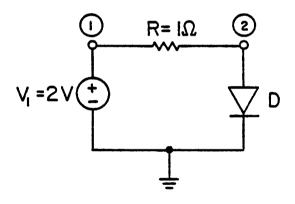

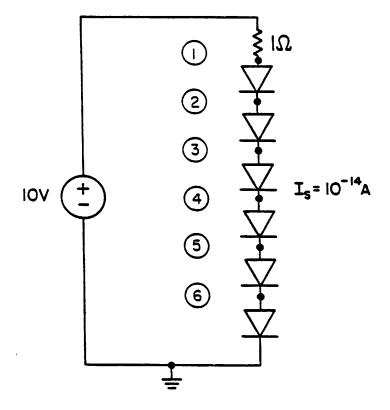

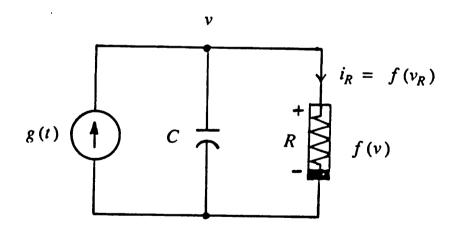

#### 3.2. Resistor-Capacitor-Diode Example

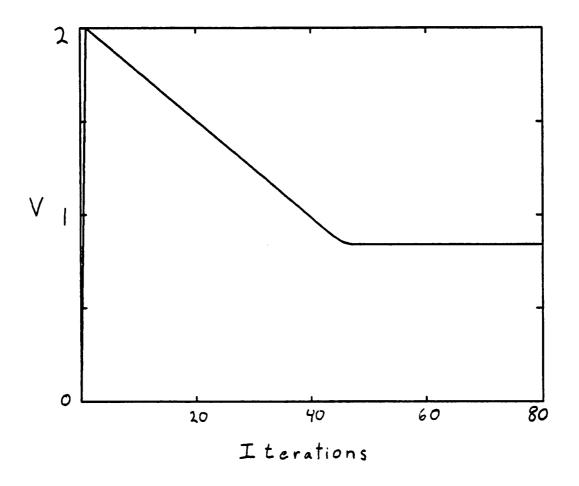

Figure 3.2 shows a nonlinear circuit which will serve as a simple example to illustrate the solution process. It consists of a capacitor, a resistor, and a diode with the initial condition on the capacitor that it is positively charged to a voltage of 2 Volts. The procedure here will be to simplify the example problem to the point where it can be solved and then show how the more general solution is built up out of the lower level techniques.

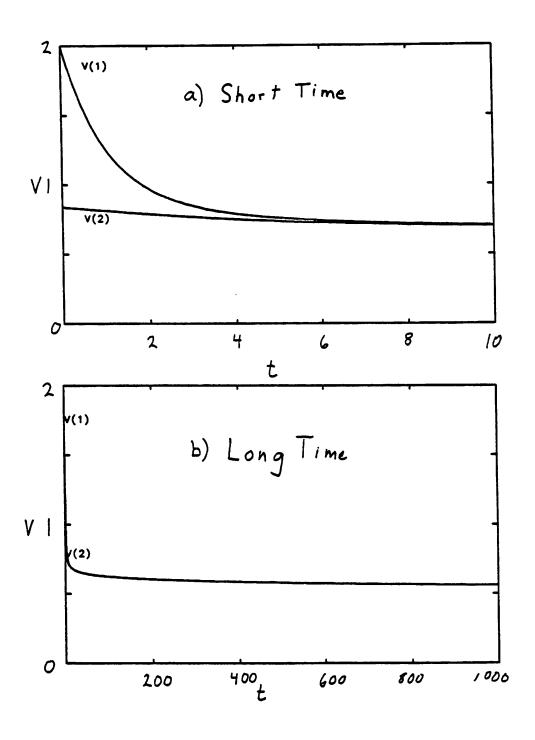

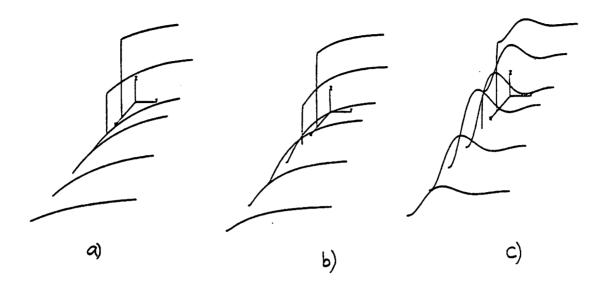

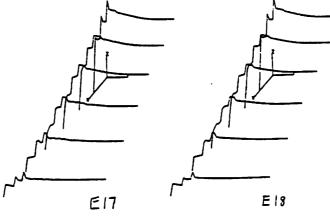

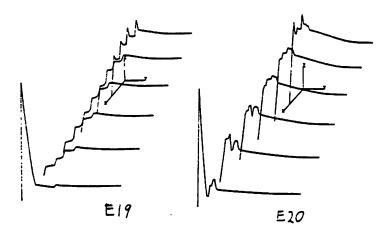

The solution of the DCTRAN problem for this network results in the voltage waveforms for nodes 1 and 2 which are shown in Figure 3.3. The waveforms have a fast and a slow component. Figure 3.3a shows the fast initial transient which occurs when the diode

Figure 3.2 : Simple Example

is fully on and has a very high conductance. As the voltage on the diode reaches its critical voltage, the conductance begins to drop quite rapidly, leading to the very slow tail shown in Figure 3.3b.

This example contains most of the characteristics of more complex examples. It has a strong nonlinear element (the diode), it has two nodes requiring a system of equations to be solved, and the capacitor introduces an element with memory. The following subsections will develop general DCTRAN analysis methods by first using this example to demonstrate nodal analysis of nonlinear dc circuits and then showing how integration techniques are used to obtain the time evolution.

## 3.2.1. DC Solution

The problem as defined here is to find the voltages on all of the nodes of the circuit for the simulated time interval. As mentioned above, this is usually accomplished by breaking time into intervals, or time-steps, and solving a series of dc-equivalent problems which result in the desired solution. In turn, the nonlinear dc problem is solved using an iterative technique (usually Newton Raphson) in which the circuit is approximated by a linear equivalent circuit. In this section, the problem is reduced to one equation in one unknown and techniques for solving it are explored. The generalization to systems of equations can be carried out in different ways and will be examined more fully in Section 3.4 when existing techniques are compared.

Nodal analysis is commonly used for the solution and makes use of the Branch Constitutive Equations (BCE or sometimes just branch equations), Kirchoff's Voltage Law (KVL) and Kirchoff's Current Law (KCL). This is often written in matrix form as

#### $\mathbf{Y}\mathbf{v} = \mathbf{i}$

where Y is the nodal admittance matrix, v is the vector of node voltages and i is a vector of the independent source currents [54].

Figure 3.3 : Example Circuit DCTRAN Waveforms

The branch relations for the three branches for this example are

$I_D = I_s \left( e^{V_2 / V_t} - 1 \right) \tag{3.1}$

$$I_{R} = \frac{V_{1} - V_{2}}{R}$$

(3.2)

$$I_C = C \frac{dV_1}{dt}$$

(3.3)

where  $V_t = \frac{kT}{q} \approx 26mV$  at 300K. Kirchoff's Current Laws for the two nodes are

$$I_C + I_R = 0 \tag{3.4}$$

$$I_R - I_D = 0 \tag{3.5}$$

Combining these equations gives

$$C \frac{dV_1}{dt} + \frac{V_1 - V_2}{R} = 0$$

(3.6)

$$\frac{V_1 - V_2}{R} - I_s \left( e^{V_2 / V_t} - 1 \right) = 0 \tag{3.7}$$

Equations 3.6 and 3.7 are a system of nonlinear ordinary differential equations. Before going on to solve this system of equations, the dc case where there is no time dependence is first examined.

A good treatment of the solution of systems of nonlinear equations using iterative methods is given in Chapter 7 of [55] and the application of these techniques to circuit analysis problems is given in [52]. At this point the system of equations will be reduced to one equation in order to contrast different solution methods.

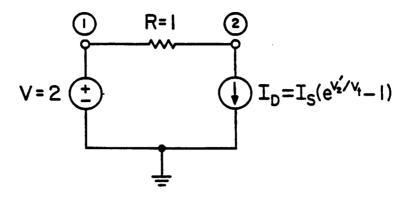

The dc equivalent of this example is shown in Figure 3.4. Here the capacitor is replaced with a voltage source in order to reduce the problem to the solution of only the voltage on node 2. Equation 3.6 can now be replaced with

$$V_1 = 2 \tag{3.8}$$

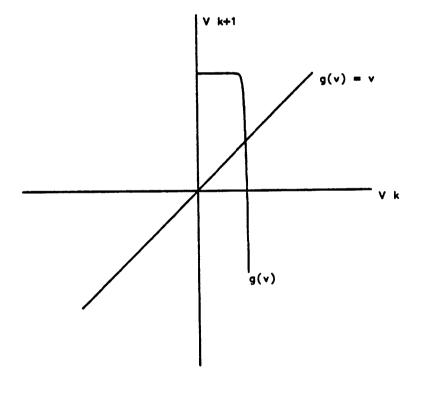

Equation 3.7 is now one nonlinear equation in one unknown. All iterative methods for solving nonlinear equations involve a scheme for finding an equation for the variable in terms of itself. In general, these are called *fixed-point* methods since at convergence the solution is stationary. Rearranging Equation 3.7 in the simplest way to solve for the single unknown,  $V_2$ :

$$V_2 = V_1 - R I_s (e^{V_2/V_t} - 1)$$

(3.9)

Using values of  $I_s = 10^{-14}$  and  $V_r = 26mV$ , if *m* is the iteration number index, then using a starting guess for  $V_2$  of 0 Volts results in the following sequence.

| m   | 0 | 1   | 2                   | 3   | 4                   | 5   |

|-----|---|-----|---------------------|-----|---------------------|-----|

| V 2 | 0 | 2.0 | $-2 \times 10^{19}$ | 2.0 | $-2 \times 10^{19}$ | 2.0 |

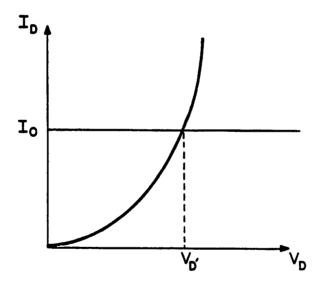

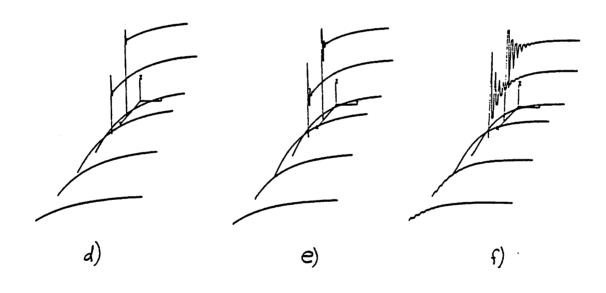

Obviously, the sequence oscillates quite quickly for this formulation. Figure 3.5 shows the linearized circuit equivalent for this equation where the diode is being modeled with a current source with a value given by Equation 3.1. This corresponds to a flat load line as shown in Figure 3.6.

Equation 3.9 could be rewritten by rearranging and taking the logarithm of both sides to give

$$V_{2} = V_{t} \ln(\frac{V_{1} - V_{2}}{R I_{s}} + 1)$$

(3.10)

This corresponds to solving for the branch voltage across the diode given the current through it. Equation 3.10 converges extremely rapidly as seen in the following table.

| m              | 0 | 1       | 2       | 3       | 4       |

|----------------|---|---------|---------|---------|---------|

| V <sub>2</sub> | 0 | 0.85616 | 0.84164 | 0.84196 | 0.84196 |

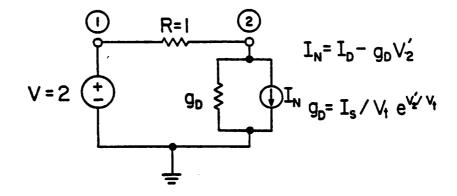

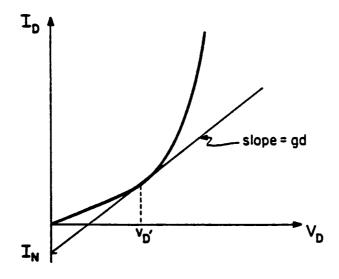

Nodal analysis is commonly used in the automatic generation of the circuit equations since it is easy to use element templates when loading the matrix. The nodal formulation of Equation 3.9 can be improved by using a first-order (Norton) model for the diode as shown in Figure 3.7 which corresponds to the load line in Figure 3.8. This results in a Newton-Raphson iteration. The nodal form of the equations can be written down directly from the circuit.

$$\frac{V_2 - V_1}{R} + V_2 G_d + G_N = 0 \tag{3.11}$$

where

$$G_d = \frac{dI_d}{dV_2} \tag{3.12}$$

and

$$G_N = I_d - G_d V_2 \tag{3.13}$$

Substituting Equations 3.12 and 3.13 into Equation 3.11 and rearranging Equation 3.11 to produce V  $_2$  in terms of itself gives

Figure 3.4 : DC Example

Figure 3.5 : Constant Source Approximation for Diode

Figure 3.6 : Zero Order Load Line

$$V_{2} = \frac{Is + \frac{V_{1}}{R} - Ise^{\frac{V'2}{V_{t}} V_{t}} (1 - \frac{V'_{2}}{V_{t}})}{\frac{1}{R} + \frac{Is}{V_{t}} e^{\frac{V'2}{V_{t}} V_{t}}}$$

(3.13)

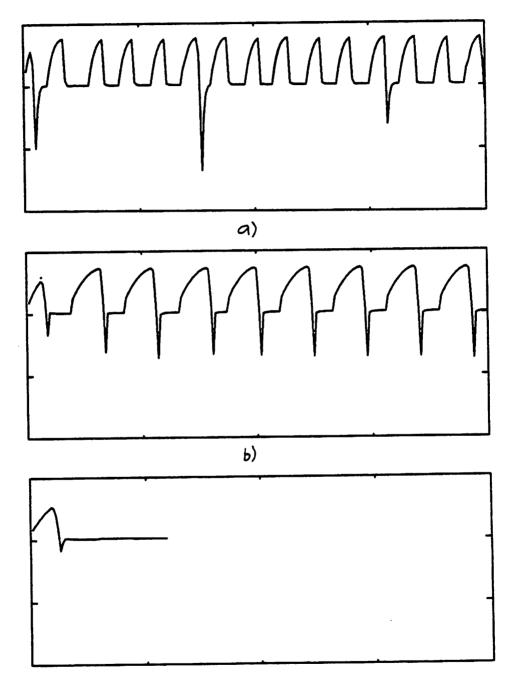

The iteration now converges as shown in the following table and in Figure 3.9.

| m   | 0 | 1   | 2     | 3     | 5     | 10    | 20    | 40    | 50      |

|-----|---|-----|-------|-------|-------|-------|-------|-------|---------|

| V 2 | 0 | 2.0 | 1.974 | 1.948 | 1.896 | 1.766 | 1.506 | 0.986 | 0.84196 |

To summarize the points about nonlinear equations, in general, a fixed-point iteration is not guaranteed to converge. "Zeroth-order" models for nonlinear devices may be made to converge but "first-order" models which result in a Newton-Raphson iteration converge more quickly. Higher order models in principle could be used, but this results in a system of polynomial equations which itself is not linear and must be solved. Even though it can be shown

Figure 3.7 : First Order Approximation for Diode

Figure 3.8 : First Order Load Line

Figure 3.9 : Convergence Rate of Newton Raphson

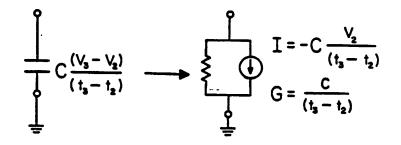

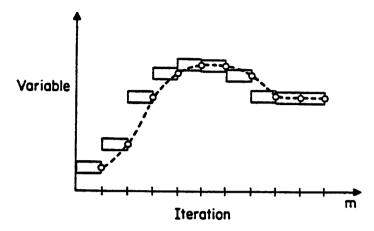

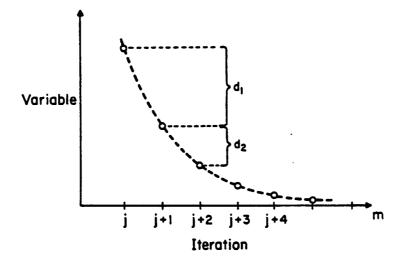

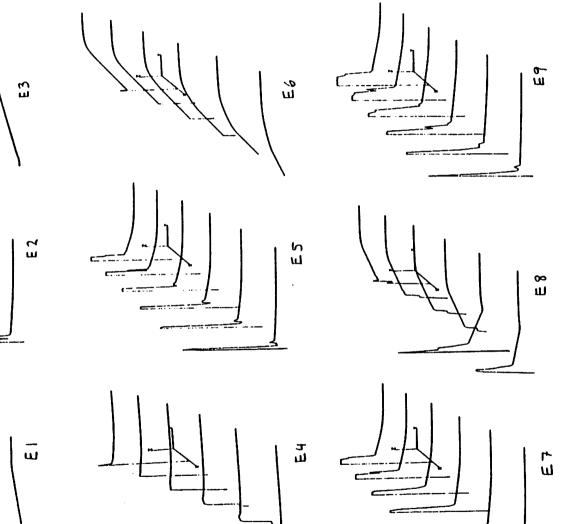

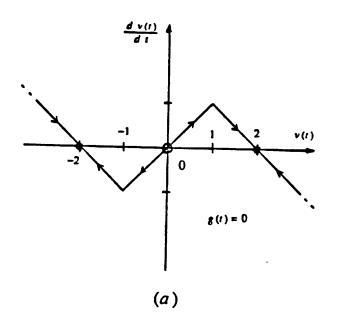

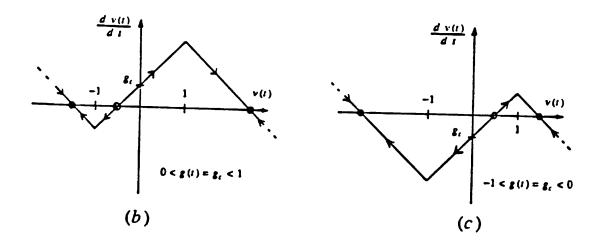

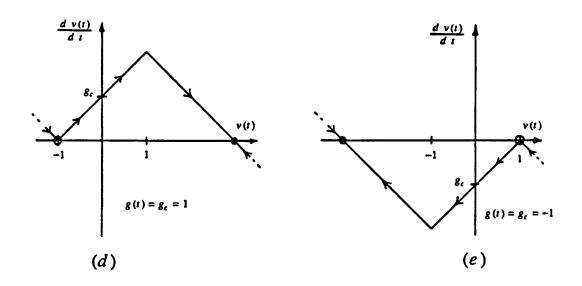

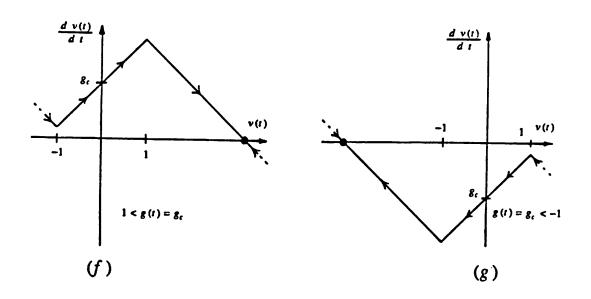

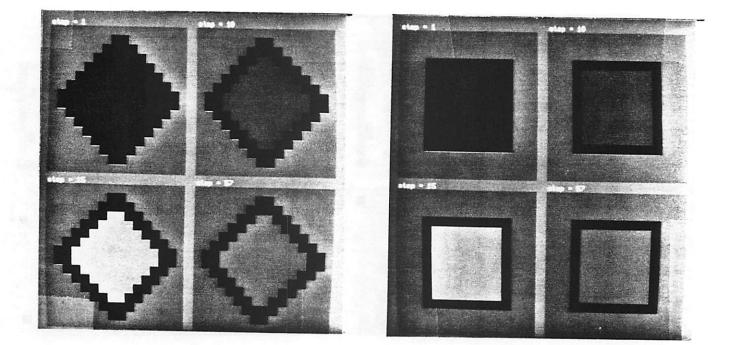

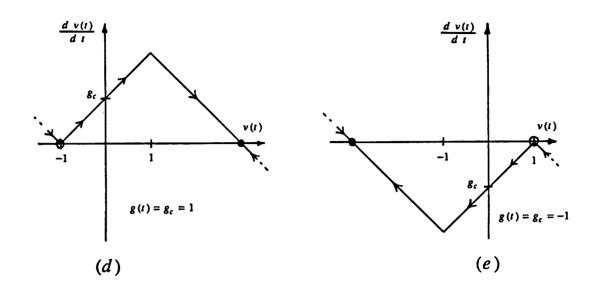

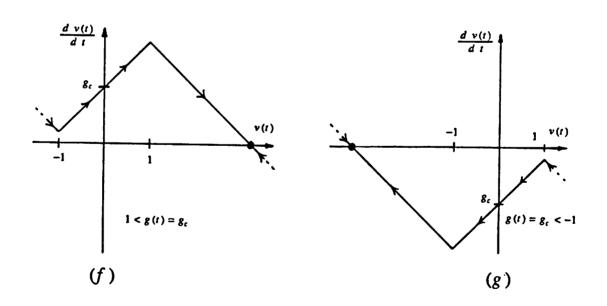

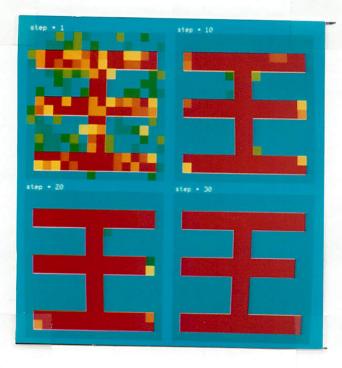

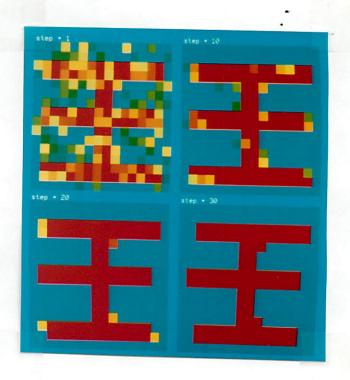

that a Newton-Raphson iteration converges quadratically near a point of contraction, Figure 3.9 demonstrates that the Newton-Raphson iteration may not converge quadratically in regions which are far from the solution.