Copyright © 1984, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## PLACEMENT ALGORITHMS AND APPLICATIONS

TO VLSI DESIGN

by

C-K. Cheng

Memorandum No. UCB/ERL M84/40

16 May 1984

(over)

## PLACEMENT ALGORITHMS AND APPLICATIONS TO VLSI DESIGN

by

C-K. Cheng

Memorandum No. UCB/ERL M84/40

16 May 1984

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720 By

## Chung-Kuan Cheng

B.S. (National Taiwan University) 1976 M.S. (National Taiwan University) 1978

## DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

Engineering

in the

## GRADUATE DIVISION

## OF THE

# UNIVERSITY OF CALIFORNIA, BERKELEY

Approved: 2:11-1-5-/14/54 ) Chairman Led (berlow 5/16/84 Quinin 5. Beda 5/16/24

# Placement Algorithms and Applications to VLSI Design

Ph.D.

Chung-Kuan Cheng

EECS Dept.

Signature:\_\_\_\_\_

Committee Chairman

## ABSTRACT

With the advent of VLSI technology, the number of components in a chip becomes very large. In view of the growing complexity of the chip and the need for fast turnaround time, the importance of automatic layout is quite obvious.

While there are many effective and efficient wiring algorithms currently available which have been used extensively, more work need to be done in partitioning and placement. This dissertation deals with theoretical study of partitioning and placement and the implementation of algorithms for chip design.

There currently exist three basic strategies for automatic chip layout, namely: the standard-cell, the gate-array, and the building-block custom chip.

We will demonstrate that the placement problem can be transformed to a network optimization problem. Based on the sparsity of the network, an efficient algorithm has been developed which is capable of solving the constructive placement problem.

The algorithm has been extended to assign components of different width into a row based on the row-type chip design such as the standard-cell and gate-array systems.

While the building-block custom chip system includes irregular sized and shaped components, a reduction process has been developed to tackle the overlapping problem. This process minimizes the chip area, but still maintains the original relative positions among the components. However, it allows rotation and flipping of modules.

Finally, an investigation of the placement problem in terms of different objective functions is explored. In linear placement, the sum of the wiring lengths, the sum of the squared lengths and the number of tracks required are used for comparison. Based on the max-flow min-cut method, an efficient algorithm for linear placement has been developed. It is shown that the method generates the best results in terms of the sum of the wire lengths, whereas the network optimization method achieves the best results in terms of the sum of squared lengths. ii

## Acknowledgement

I am deeply grateful to my thesis advisor, Prof. Ernest Kuh, for his patience, guidance and support. Working under him has been a most rewarding experience. In addition, I would like to thank Prof. T.C. Hu for his encouragement and advice on linear placement. Prof. A.R. Newton and Prof. W.G. Bade were also very helpful to me.

I am indebted to Dr. Jerry Lee for his encouragement and advice. Dr. B.S. Ting and Dr. B.N Tien of Hughes Aircraft strongly supported this project.

I would also like to thank C.C. Chen, and most particularly Dr. M. Marek-Sadowska, for many interesting and enlightening discussions. Also to be credited on this account are my colleagues T. Tarng, H. Chen, W.M. Dai, X.M Xiong and S.H. Lin. In providing an environment for implementation, J.T. Li and M. Turner worked diligently and with great skill on the BAGEL system. My friend C.L. DeMarco gave me much encouragement and advice throughout.

For their constant encouragement and faith, I am very grateful to my parents. Finally, I am most indebted to my wife, Chuan-Ying, for her continued faith and love.

# Table of Contents

| Abstract                                            | i          |

|-----------------------------------------------------|------------|

| Acknowledgement                                     | 1          |

| Table of Contents                                   | S          |

| 1 Introduction                                      | 5          |

| 2 Placement Based on Resistive Network Optimization | 13         |

| 2.1 Introduction                                    | 13         |

| 2.2 Formulation of the approach                     | 14         |

| 2.2.1 Objective function                            | 14         |

| 2.2.2 Network analogy                               | 16         |

| 2.2.3 Boundary constraints                          | 17         |

| 2.2.4 Slot constraints                              | 19         |

| 2.3 Proposed method                                 | 20         |

| 2.3.1 Optimization                                  | 21         |

| 2.3.2 Scaling                                       | 23         |

| 2.3.3 Relaxation                                    | <b>2</b> 5 |

| 2.3.4 Partitioning and assignment                   | 27         |

| 2.4 Discussion                                      | 28         |

| 2.4.1 Multi-module nets                             | 28         |

| 2.4.2 Computation complexity                        | 28         |

| 2.4.3 Experimental results                          | 29         |

| 2.5 Conclusion                                      | 37         |

| 3 Gate-Array and Standard-Cell placements | 39         |

|-------------------------------------------|------------|

| 3.1 Introduction                          | 39         |

| 3.2 Formulation of the approach           | 42         |

| 3.2.1 Objective function                  | 42         |

| 3.2.2 Network analogy                     | <b>4</b> 4 |

| 3.2.3 Slot constraints                    | 47         |

| 3.3 Proposed method                       | 47         |

| 3.3.1 Optimization                        | 47         |

| 3.3.2 Scaling                             | 49         |

| 3.3.3 Relaxation                          | 50         |

| 3.3.4 Partitioning and merging            | 52         |

| 3.3.5 Assignment                          | 53         |

| 3.4 Experimental results                  | 56         |

| 3.5 Conclusion                            | 60         |

| 4 Building Block Placement                | 61         |

| 4.1 Introduction                          | 61         |

| 4.2 Formulation                           | 62         |

| 4.3 Preliminary locations of the modules  | <b>6</b> 5 |

| 4.4 Basic operations                      | 65         |

| 4.4.1 Compaction                          | <b>6</b> 6 |

| 4.4.2 Decompaction                        | 67         |

| 4.4.3 Rotation                            | 73         |

| 4.4.4 Selection of preferable direction   | 74         |

| 4.5 Algorithms                            | 75         |

| 4.5.1 Spacing            | <b>7</b> 5 |

|--------------------------|------------|

| 4.5.2 Reduction          | 76         |

| 4.6 Assignment           | 78         |

| 4.7 Experiments          | 79         |

| 4.8 Conclusion           | 82         |

| 5 Linear Placement       | 84         |

| 5.1 Introduction         | 84         |

| 5.2 Formulation          | 85         |

| 5.3 Theory               | 87         |

| 5.4 Parallel graph       | 96         |

| 5.4.1 Algorithm          | 97         |

| 5.4.2 Example            | <b>9</b> 8 |

| 5.5 Arbitrary graph      | 101        |

| 5.5.1 Graph modification | 101        |

| 5.5.2 Algorithm          | 107        |

| 5.5.3 Example            | 107        |

| 5.5.4 Theorems           | 109        |

| 5.6 Application          | 112        |

| 5.6.1 Multi-pin nets     | 113        |

| 5.6.2 Algorithm          | 116        |

| 5.6.3 Discussion         | 117        |

| 5.6.4 Experiments        | 117        |

| 5.7 Conclusion           | 119        |

| References               | 121        |

•

•

•

•

•

----

# Chapter 1 Introduction

## 1.1. IC Layout

With the rapid evolution of VLSI technology, the number of components in a chip becomes large. In view of the growing density and complexity of the chip, physical layout becomes critical to turnaround time of the design and the performance of the circuit. Not only an extra long design period causes the cost of the product unreasonably high, but also an ill-designed layout might be fatal to the whole chip. Thus, an effective and efficient automatic layout is in need for the advancement of the integrated circuit technology.

Due to the tremendous complexity of the problem, layout system is usually decomposed into two phases, namely, placement and routing. The placement assigns the locations of the components on the chip. Based on the result of placement, the routing tries to complete the connections among the components under the constraint of specified design rules. Different placement results generate different connection patterns. Thus, the result of layout is much dependent on the phase of placement.

While there are now many effective and efficient routing algorithms available which have been used extensively, more work must be done in partitioning and placement. This thesis deals with theoretical study of placement and the implementation of algorithms for chip design.

#### 1.2. Placement problems

There are currently three basic structures for automatic chip layout.

namely: the standard-cell, the gate-array, and the building block custom chip.

Gate-array and standard-cell approaches have a regular structured chip. The 10 pads are placed on the boundary of the chip, while the modules are assigned to an array of rows inside the chip. Modules are assumed to have same height but varying width. The routing area is embedded between the rows and around the periphery of the array. This style significantly simplifies the design process. In gate-array approach, the chips are preprocessed to establish the transistor sites and, often, power and ground metallization as well. The chip size and routing areas are therefore fixed. Thus, achieving 100% routability is one objective for the layout. On the other hand, the standard-cell layout involves the customization of all mask layers. This additional freedom permits variable chip size and adjustable routing space between rows of active areas. Completing the routing with smallest chip area becomes important.

Building block design style is sometimes referred to as the general cell or macrocell approach. It is a popular approach for developing high density, high production-volume integrated circuit chips. Thus the sizes and shapes of the modules are irregular. No geometry or size limitation apart from yield considerations is put on the cell layout. The building block layout is to achieve 100% routability while keeping the chip size as small as possible.

#### 1.3. Review of placement

## 1.3.1. Objective function

The placement results are input to the routing phase where all the nets are routed. The size of routing areas are finally determined in the stage of routing. Because of the tremendous complexity of the combined problem, placement and routing are usually separated as independent procedures. In placement,

however, some of this complexity remains: the estimation of the exact sizes of routing areas can become very complicated. Therefore, the goal related to minimizing routing spaces has to be simplified so that the objective function is easy to enumerate on the computer. In the literature, the sum of wire lengths is commonly used as the objective function for placement.

One the other hand we prefer strongly-connected modules to be near each other to improve circuit performance. Otherwise, a long connection wire might cause signal to delay more than a tolerable range. We choose the sum of squared wire lengths as the objective function, since a small sum leads to both the chip size minimization and delay time reduction. With this objective function, the placement problem can be transformed into a network optimization problem.

#### 1.3.2. Placement algorithms

The algorithms for placement can be divided into two categories: constructive placement and iterative improvement of placement.

## A Constructive placement

One constructive algorithm is the clustering method. Initially, some modules are placed on the chip as seeds. The unplaced modules are then put on the chip sequentially. In each step, the module with the maximal connection to the placed modules is taken from unplaced modules. It is assigned to the position so that the lengths of connections is minimal. This process is repeated until all modules are placed.

Another algorithm is the top-down approach based on bipartitioning. The algorithm used is a minimal cut method such as the Kernighan and Lin's. Given

,

a cut-line which partitions the chip into two, the modules are iteratively exchanged between the two sides to minimize the number of crossing wires on the cut-line. Then each subregion is partitioned again into smaller subregions. The procedure continues until each subregion contains only one of the prescribed modules.

Both clustering and bipartitioning algorithms are greedy in the sense that they try to achieve the local optimal in each step, but does not view the problem globally. Quinn and Breuer introduced a force-directed method. In their formulation, point modules are assumed, and a force-model is used to determined the state of equilibrium. Hook's law gives the forces of attraction for modules connected by signal nets, and repulsive forces are used to keep modules apart for those which are not connected. This method leads to a good initial placement. However, the algorithm amounts to solving a large set of nonlinear equations , which is time consuming.

## **B.** Iterative improvement of placement

The purpose of this phase is to improve the placement by applying small local changes, such as the pair-wise exchange of modules. Goto, who used the concept of the medium of a module, suggested a multi-way exchange iterative improvement method. This method has better performance than the traditional pair-wise exchange method. But, it often leads to a local minimum solution.

Kirkpatrick introduced a thermal annealing concept to avoid the problem of trapping in the local minimum. The method simulates the physical thermal annealing process, which starts with an appropriately chosen high temperature. Pair of modules are randomly chosen to be exchanged. The difference of objective function is checked with respect to the exchange. According to the temperature, a probabilistic model is set to determine a threshold. The exchange of the pair is accepted if the difference of objective function is smaller than the threshold. The exchanges are repeated and the user gradually decreases the temperature until no more improvements can be obtained. During the process, a large number of different pairs of modules is tested for exchange. Therefore, it consumes a great amount of CPU time.

## 1.4. Resistive network optimization

As the number of modules becomes larger, a global view of the problem becomes more important. At the same time, the computational complexity of the algorithm should be kept as low as possible. Otherwise, a large amount of CPU running time would prohibit the implementation of the system.

In this thesis, we propose a constructive placement method. First, we simplify the problem by assuming that all modules are of same size and shape. Thus, the model of point module is assumed. Let slots be the fixed locations for modules to be assigned. The objective function is the sum of squared wire lengths. The placement problem is transformed into the problem of minimizing the power dissipation of a resistive network. The constraint of the slots is formulated in terms of a number of polynomial equations. In optimization, the first order constraint is chosen to simplify the problem. This amounts to keeping the center of gravity of modules at the center of the region. With network theory and optimization techniques, the optimal locations of modules are easily obtained.

Since only the linear constraint equation is used in optimization, the placement is more or less confined to the center of the region. Therefore, a scaling and relaxation scheme is proposed to spread the modules so obtained to the

entire region. Then, a partitioning process is used to put the modules into different subregions. The partitioning process continues until each subregion contains only one module.

From several experiments conducted, the method is shown to generate excellent placement results. Since the corresponding network inherits the sparsity of the placement problem, the method is very time efficient with the aid of sparse matrix techniques.

#### 1.5. Standard-cell and gate-array placements

The network optimization method is first implemented in standard-cell and gate-array placement. In the partitioning, the sums of the sizes of the modules are checked on the two sides of a dividing line to even out the distribution of the modules over the chip area. After modules are partitioned into rows, a decompaction process is used to separate the overlapping modules.

#### 1.6. Building block placement

The network optimization is extended to find the relative locations of modules in building block placement. Modules of rectangular circuit blocks are categorized into two types. The modules which have width or height greater than a certain threshold value are classified as **critical module**. After network optimization, critical modules are placed first. Then, other modules are relocated in the free spaces left by critical modules. A **spacing** algorithm is used to separate the overlapping modules by the operations of compaction, decompaction and rotation. In each iteration, the decompaction operation slides modules back toward the original locations to avoid overlap. Thus, the original relative locations are maintained during the process. The **reduction** algorithm is then applied to reduce the chip size. The algorithm reduces the breadth of chip in each iteration and calls for repeated use of the spacing algorithm until no more reductions can be made.

#### 1.7. Linear placement

In order to have a fully automatic layout system, the optimum placement ultimately means ease in routing. We need to compare different criteria used in placement. Thus, an investigation of the placement problem in terms of various objective functions is explored. In linear placement, the sum of wiring lengths, the sum of squared lengths and the number of tracks required are used for comparison.

Algorithms for linear placement are developed to minimize the sum of lengths. Two criteria, max-flow min-cut, and a cost ratio, are used to make partitions of the optimal order of the modules. The algorithm decomposes the modules into smaller subregions. This process is repeated until each subregion contains only one module.

It is shown that the linear placement method generates the best results in terms of the sum of the wire lengths, whereas the network optimization method achieves the best results in terms of the sum of squared lengths.

## 1.8. Thesis overview

The network optimization method is described in Chapter 2. Its extensions to standard-cell and gate-array are discussed in Chapter 3. Chapter 4 deals with the building block placement. The spacing and reduction algorithms which separate the modules and reduce the chip size are described. Finally, Chapter 5 describes the properties of linear placement and introduces two new algorithms. The proposed method and network optimization method are compared with

published results in terms of the sum of wiring lengths, the sum of squared lengths, and the number of tracks required.

All algorithms described have been implemented in C programming language and several examples obtained from industry have been used to test the algorithms. The results are far superior than the manual placements.

## Chapter 2

# Placement Based on Resistive Network Optimization

## 2.1. Introduction

The force-directed method introduced by Quinn and Breuer is a good constructive placement method which leads to initial placement[1]. In their formulation, point modules are assumed, and a force-model is used to determine the state of equilibrium. Hook's Law gives the forces of attraction for modules connected by signal nets, and repulsive forces are used to keep modules apart for those which are not connected. The algorithm amounts to solving a large set of nonlinear equations, which is time consuming. An improvement has been proposed by Antreich, Johnnes and Kirsch using the same force-directed method but with a more systematic formulation of equations[2].

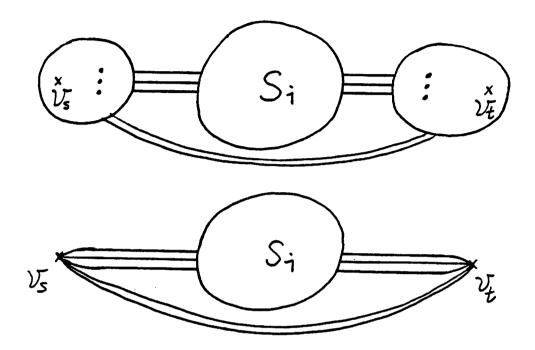

In this Chapter we propose a more efficient method based on resistive network analogy of the placement problem. The idea of using network analogy to attack layout problems was first introduced by Charney and Plato[3]. They proposed a method of module clustering according to the sensitivity of a network analogy for the purpose of partitioning. In the Chapter, we first solve the optimum placement problem in a systematic way by network analogy. The general formulation of the problem of placing modules on slots involves optimization with nonlinear constraints. However, if only the linear constraints are considered, the problem amounts to solving a linear sparse resistive network. Thus, sparse matrix techniques can be used. Because of its computational efficiency, the procedure is repeated in the overall algorithm of partitioning and module assignment. In the formulation, a key feature is that we allow some modules to be fixed in position. Fixed modules could represent 1-0 pads; but they also play an important role in solving each optimization problem in succession in the overall algorithm. In section 2 we give a detailed formulation of our approach to the problem. Section 3 is divided into subsections of optimization, scaling, relaxation, and partitioning and assignment. Section 4 briefly discusses the problem of multimodule nets, the computation complexity and experimental results.

## 2.2. Formulation of the approach

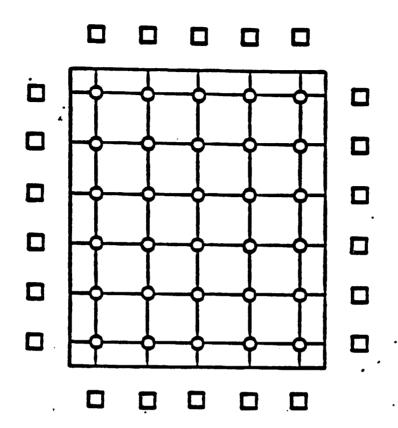

Consider the module placement problem in chip layout. With reference to Fig. 1 where movable modules together with fixed modules represent 1-0 pads are shown. The movable modules are to be placed on slots where horizontal and vertical lines intersect. The net interconnection specification is given by a net list relating nets and modules. We assume first that all nets are 2-module nets and multi-module nets have been preprocessed and replaced with 2-module nets[4]. Furthermore, all modules are assumed to have zero dimension, thus their shape, size and pin locations are initially ignored.

## 2.2.1. Objective function

Let the two dimensions on the chip be specified by the x and y coordinates. Let there be a total of n modules located at  $(x_i, y_i)$ , i=1,2,...,n. Let  $c_{ij}$  denote the connectivity between module i and module j, i.e., the number of wires between them. Thus  $c_{ii}=0$ . In the literature, the objective function used for placement is usually the sum of wire lengths. However, because of network analogy, we choose an objective function which is the sum of squared wire lengths. Let the objective function be given by:

Fig. 2.1. An example with movable modules to be placed on slots within the square and fixed modules on the boundary representing 1-0 pads.

$$\Phi[\mathbf{x},\mathbf{y}] = \frac{1}{2} \sum_{i,j=1}^{n} c_{ij} L_{ij}^{2} = \frac{1}{2} \sum_{i,j=1}^{n} c_{ij} \left[ \left[ x_{i} - x_{j} \right]^{2} + \left[ y_{i} - y_{j} \right]^{2} \right]$$

(1)

where  $l_{ij}$  is the Euclidean distance between module i and module j. Equation (1) can be written as follows[5]:

$$\begin{split} \hat{\Psi}[x,y] &= \frac{1}{2} \sum_{i,j=1}^{n} c_{ij} \left[ x_{i}^{2} + x_{j}^{2} - 2x_{i} x_{j} + y_{i}^{2} + y_{j}^{2} - 2y_{i} y_{j} \right] \\ &= \sum_{i=1}^{n} \sum_{j=1}^{n} c_{ij} x_{i}^{2} - \sum_{i=1,i'=j}^{n} \sum_{j=1}^{n} c_{ij} x_{i} x_{j} + \sum_{i=1,j=1}^{n} \sum_{j=1}^{n} c_{ij} y_{i}^{2} - \sum_{i=1,i'=j}^{n} \sum_{j=1}^{n} c_{ij} y_{i} y_{j} \\ &= x^{T} B x + y^{T} B y \end{split}$$

(2)

where

$$B = D - C \tag{3}$$

is an n×n symmetric matrix,  $C = [c_{ij}]$  is the connectivity matrix and D is a diagonal matrix whose i-th element  $d_{ii}$  is equal to  $\sum_{j=1}^{n} c_{ij}$ .

With the symmetry between x and y in Eq. (1), we need to consider only the one-dimension problem insofar as optimization is concerned. Thus we dispense with the y coordinate until the end of Sec. 3 where we discuss partitioning and assignment.

## 2.2.2. Network analogy

For those who are familiar with circuit theory, B in Eq. (3) is seen to be of the same form as the indefinite admittance matrix of an n-terminal linear passive resistive network. We will model the coordinate of module i,  $x_i$  with a node voltage  $v_i$  at node i. The reference coordinate x=0 is thus the datum voltage. The term  $-c_{ij}$  in Eq. (3) is then the mutual admittance between node i and node j, and  $d_{ii} = \sum_{i=1}^{n} c_{ij}$  is the self admittance at node i.

The power dissipation in the resistive network is

$$P = v^T Y_n v \tag{4}$$

where v is an n-vector representing the node voltage vector and  $Y_n$  is the indefinite admittance matrix which is symmetric. Thus the objective function of the placement problem becomes the power dissipation in the linear passive resistive network. It is well-known that in a passive resistive network the current distributes itself in such a way that the power is minimum[6]. That is, any other current distributions which are not the solution of the network would have a larger power dissipation. In other words, the problem of solving network equations is equivalent to that of minimizing a well-selected function which

represents power.

## 2.2.3. Boundary constraints

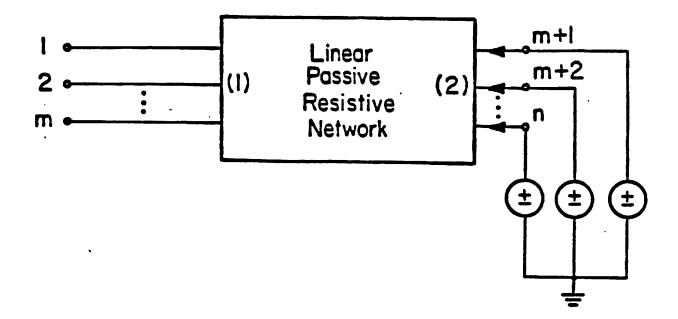

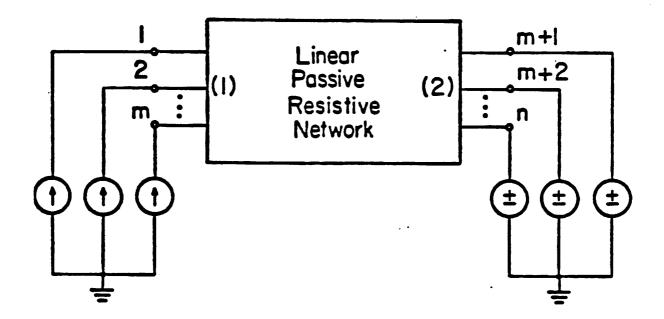

Consider the n-terminal resistive network shown in Fig. 2.2. The first m nodes are floating and their voltages are denoted by an m-vector  $v_1$ . The remaining n-m nodes are connected to voltage sources denoted by an (n-m)-vector  $v_2$ . Thus the coordinates of the n modules are represented by an n-vector  $v = \begin{bmatrix} v_1 \\ v_2 \end{bmatrix}$  where the coordinates of the fixed modules are specified by  $v_2$  and the coordinates of the movable modules which are to be determined are represented by  $v_1$ .

Fig. 2.2. An n-terminal linear, passive resistive network whose first m nodes are floating and the remaining n-m nodes are connected to voltage sources.

The network equations are:

$$0 = y_{11}v_1 + y_{12}v_2 \tag{5a}$$

$$i_2 = y_{21}v_1 + y_{22}v_2 \tag{5b}$$

where  $y_{11}$ ,  $y_{12}=y_{21}^T$  and  $y_{22}$  are the familiar short-circuit admittance submatrices of the indefinite admittance matrix,  $Y_n$ . From (4b), we obtain

$$v_1 = -y_{11}^{-1} y_{12} v_2 \tag{6}$$

which gives the solution of the movable modules in terms of the fixed modules and the admittance submatrices.

#### Remarks

- (1)  $y_{11}$  is the short circuit driving-point admittance submatrix of a passive resistive network and is positive definite; thus  $y_{11}^{-1}$  always exists.

- (2) The solution of Eq. (6) must fall inside the region defined by the smallest and largest voltages of the voltage sources. This is because in a passive resistive network, node voltage can not lie outside the range of voltage sources[6].

- (3) The dissipated power obtained from the solution in Eq. (6) is the minimum among all possible  $v_1$ . Any deviation from the solution will result in an increase in power.

### 2.2.4. Slot constraints

Up to now we have not imposed the constraint that the movable modules must be located on slots. This means that the voltage vector  $v_1$  when finally determined must represent a set of prescribed discrete voltages called the **legal values.** Let us designate the prescribed slots in terms of the permutation vector  $p=[p_1,p_2,...,p_m]^T$  where  $p_i$  is the i-th legal value and m is the total number of the movable modules. Thus the permutation of the m legal values must be assigned to the m modules of  $v_2$ . To express this in terms of our optimization problem, let  $v_1=[x_1,x_2,...,x_m]^T$ , i.e.,  $x_i$  denotes the coordinate of module i or the voltage at node i. We claim that the following set of equations represents the constraints on the modules which are required to be on slots:

$$\sum_{i=1}^{m} x_i = \sum_{i=1}^{m} p_i$$

$$\sum_{i=1}^{m} x_i^2 = \sum_{i=1}^{m} p_i^2$$

$$\sum_{i=1}^{m} x_i^m = \sum_{i=1}^{m} p_i^m$$

(7)

The first equation can be written as

$$\mathbf{1}^T \boldsymbol{v}_1 = \mathbf{1}^T \boldsymbol{p} \equiv \boldsymbol{d} \tag{8}$$

where 1 is a unit vector and d is a constant which is equal to the sum of the m legal values.

## **Proof**:

=> Let  $[x_1, x_2, ..., x_m]$  equal to any permutation of  $[p_1, p_2, ..., p_m]$ . Eq. (7) is automatically satisfied.

<= Let us define

$$f(x) = \prod_{i=1}^{m} \left\{ x + x_i \right\}$$

Then the coefficients of the variable x are multi-variable polynomials of  $[x_1, x_2, ..., x_m]$ . Through simple algebraic operations[7] and by using Eq. (7), we can show that

$$f(x) = \prod_{i=1}^{m} \left[ x + p_i \right]$$

which implies that all modules are on slots.

**Q.E.D.**

#### 2.3. Proposed method

The proposed method can be divided into subproblems of optimization, scaling, relaxation, and partitioning and assignment. The main idea is to solve a simple optimization problem using linear resistive network analogy repeatedly and, in the process, the movable modules are assigned to slots. We shall use node voltages and module coordinates interchangeably in the ensuing discussion, for sometimes it is more intuitive to make statements in terms of voltages; while in dealing with the actual placement problem it is more convenient to use the coordinates.

## 2.3.1. Optimization

From Eqs. (4) and (5), we wish to minimize the power dissipation

$$P = v^{T} Y_{n} v = \begin{bmatrix} v_{1}^{T} \cdot v_{2}^{T} \end{bmatrix} \begin{bmatrix} y_{11} & y_{12} \\ y_{21} & y_{22} \end{bmatrix} \begin{bmatrix} v_{1} \\ v_{2} \end{bmatrix} = v_{1}^{T} y_{11} v_{1} + 2v_{1}^{T} y_{12} v_{2} + v_{2}^{T} y_{22} v_{2}$$

(9)

subject to the complete set of constraint equations in Eq. (7). This is clearly not feasible. Therefore, we propose to use only the first equation in Eq. (7), which is a linear constraint expressed by Eq. (8).

The solution to the optimization problem of minimizing P in Eq. (9) subject to the linear constraint in Eq. (8) is derived from the well-known Kuhn-Tucker conditions. The first order necessary conditions, in addition to the constraints are

$$2y_{11}v_1 + 2y_{12}v_2 + \lambda 1 = 0 \tag{10a}$$

$$1^T \boldsymbol{v}_1 = \boldsymbol{d} \tag{10b}$$

where  $\lambda$  is the so called Lagrange multiplier. The solution of the above simultaneous equations is

$$\boldsymbol{v}_{1} = \boldsymbol{y}_{11}^{-1} \Big[ -\boldsymbol{y}_{22} \boldsymbol{v}_{2} + \boldsymbol{i}_{1} \Big]$$

(11a)

where

$$i_1 \equiv \frac{d+1^T y_{11}^{-1} y_{12} v_2}{1^T y_{11}^{-1} 1}$$

(11b)

With respect to the second order conditions, we find the Hessian matrix is equal to  $2y_{11}$  which is positive definite. Thus the solution is optimal.

It is seen that the first term in Eq. (11a) is precisely that given by Eq. (6) for which there is no constraint on slots. The second term of Eq. (11a) can be viewed as a correction term which attempts to put the solution on slots. In terms of electric network, we may use current sources to interpret the effect as shown in Fig. 2.3. Thus we have a linear resistive network with both voltage and current sources. In addition, we know that the network is sparse because of the

inherent nature of the placement problem. Using well-known sparse matrix algorithms, we can greatly reduce the computation time in comparison with those that use attraction and repulsion forces[1,2].

Fig. 2.3. Network interpretation of the optimization problem with linear constraints.

As mentioned previously, because only the linear constraint equation is used, the solution will not put modules on slots. As a matter of fact the result will lead to modules more or less confined to the center of the region. Therefore we must introduce ways to spread the modules so obtained apart and then to bring them to the legal positions. Thus the next step in our overall method is scaling which will distribute the solution more evenly over the entire region. However, let us first analyze the effect of module movements to changes in power dissipation. Let us assume that we deviate away from the solution  $v_1$  of

Eq. (11) by  $\delta v_1$  under the constraint of Eq. (8), i.e.

$$\mathbf{1}^T \delta \boldsymbol{v}_1 = 0 \tag{12}$$

We claim that the power dissipation is increased by

$$\delta v_1^T y_{11} \delta v_1.$$

**Proof**:

From equation (9), we have

$$\Delta P = P(v_1 + \delta v_1) - P(v_1) = 2\delta v_1^T y_{11} v_1 + \delta v_1^T y_{11} \delta v_1 + 2\delta v_1^T y_{12} v_2$$

From equation (11),

$$y_{12}v_2 = -y_{11}v_1 + i_1$$

and using Eq. (12), we obtain

$\Delta P = \delta v_1^T y_{11} \delta v_1$

Q.E.D.

Furthermore, it is possible to derive an upper bound on the increase in power dissipation in terms of  $y_M$ , the largest diagonal element in  $y_{11}$ . From the Theorem of Gerschgorin[8], we know that the eigenvalues of  $y_{11}$  are not larger than  $2y_M$ , then

$$\Delta P = \delta v_1^T y_{11} \delta v_1 \le |y_{11}| |\delta v_1|^2 \le 2 y_H \sum_{i=1}^m \delta v_i^2$$

(13)

Therefore the increase in power dissipation has an upper bound which is proportional to the norm of the deviation  $\delta v_1$ .

## 2.3.2. Scaling

The result of the optimization with linear constraint leads to solutions which have movable modules concentrated at the center of gravity of all modules. The linear constraint dictates the mean position of the modules. The only forces which attempt to scatter the modules are the fixed modules at the boundary. Therefore, in order to be able to partition the modules we will introduce scaling to redistribute the modules at the expense of increasing the power dissipation. The method used here is to minimize the increase of power  $\Delta P$  under the constraints which include both the first order and second order equations in Eq. (7). Fortunately, by using the norm of  $\delta v_1$  in Eq. (13), we again can resort to the well-known Kuhn-Tucker conditions.

Let us assume that in the region where there are k modules the legal values are given by the permutation vector  $[p_1, p_2, ..., p_k]$ . Let  $x_o = [x_{o1}, x_{o2}, ..., x_{ok}]$  denote the solution obtained from optimization and let  $x_n = [x_{n1}, x_{n2}, ..., x_{nk}]$  denote the new solution after scaling. Thus our problem is to minimize

$$\sum_{i=1}^{k} \left[ x_{ni} - x_{oi} \right]^2$$

(14)

under the constraints

$$\sum_{i=1}^{k} x_{ni} = \sum_{i=1}^{k} p_i$$

(15)

and

$$\sum_{i=1}^{k} x_{ni}^{2} = \sum_{i=1}^{k} p_{i}^{2}$$

(16)

The solution is derived from the Kuhn-Tucker conditions. The first order necessary condition is

$$2\left[\boldsymbol{x}_{n}-\boldsymbol{x}_{o}\right]+\lambda_{1}\boldsymbol{1}+2\lambda_{2}\boldsymbol{x}_{n}=0$$

(17)

In addition to the constraints of Eq. (15) and Eq. (16), the solution is

For i=1,2,...,k

$$x_{ni} = \frac{x_{oi} - c_o}{a_o} a_n + c_n \tag{18}$$

where

$$c_n = \frac{1}{k} \sum_{i=1}^k p_i \tag{19}$$

$$a_{n} = \left[\frac{1}{k}\sum_{i=1}^{k} \left[p_{i} - c_{n}\right]^{2}\right]^{\frac{1}{2}}$$

(20)

$$c_{o} = \frac{1}{k} \sum_{i=1}^{k} x_{oi}$$

(21)

and

$$\mathbf{a}_{o} = \left[\frac{1}{k}\sum_{i=1}^{k} \left[x_{io} - c_{o}\right]^{2}\right]^{\frac{1}{2}}$$

(22)

Thus  $c_0$  is the mean position of the computed module positions and  $a_0$  is the root mean square amplitude measured from  $c_0$ .

With respect to the Kuhn-Tucker second order conditions, we find the Hessian matrix is equal to  $2\frac{a_o}{a_n}$ , where I is an identity matrix. Where  $a_o > 0$ , the Hessian matrix is positive definite. The solution is optimal. If  $a_o$  turns out to be very small which approaches zero, so does  $x_{oi} - c_o$  in Eq. (18); then Eq. (18) must be replaced by

$$\mathbf{z}_{ni} = c_n \tag{23}$$

After scaling the norm of deviation becomes

$$\sum_{i=1}^{k} \left[ x_{ni} - x_{oi} \right]^{2} = k \left[ \left[ a_{n} - a_{o} \right]^{2} + \left[ c_{n} - c_{o} \right]^{2} \right].$$

(24)

The result of scaling represents an improvement from the result of optimization as far as module location is concerned, but it gives an increase in power dissipation.

#### 2.3.3. Relaxation

Before undertaking partitioning and assigning of modules to slots, we need to perform relaxation to be described below. This will greatly improve the preliminary results from optimization and scaling. The method calls for repeated use of scaling and optimization over subregions to be specified by designers. This tends to spread the modules out more evenly over the entire region. It is important to note that when a pertinent subregion is considered, modules outside are always kept fixed.

We propose to choose subregions in the following way: First we start from one end of the region, then the other end and, finally, the middle. After the initial optimization over the entire region, three such steps of scaling and optimization over subregions are carried out. The result tends to settle down and is ready for partitioning. Thus we have as

Input:

A one-dimensional region with coordinates of movable modules  $x_i$ , i=1,2,...,m obtained from initial optimization in the entire region with specified fixed modules  $x_i$ , i=m+1,m+2,...,n on the boundary. A parameter  $\beta$ is to be chosen by the designer with  $0<\beta<50\%$ .

## **Relaxation:**

- Order the modules from left to right according to coordinates with the smallest one first.

- (2) Choose  $[\beta m]$ † modules from the left, let other modules be fixed and do scaling in the left  $\beta$  region.

- (3) Fix the modules so determined in the left  $\beta$  region and release the modules in the right (1- $\beta$ ) region. Do optimization.

- (4) Choose  $[\beta m]$  modules from the right, let other modules be fixed and do scaling in the right  $\beta$  region.

- (5) Fix the modules in the right β region and release the modules in the left (1-β) region. Do optimization.

- (6) Choose [βm] modules from the left, let other modules be fixed and do scaling in the left β region.

- (7) Set modules in both the left  $\beta$  region and the right  $\beta$  region fixed and release the modules in the center subregion. Do optimization.

t k means the smallest integer which is larger than k.

Output:

A one-dimensional region with m modules and new coordinates  $x_i$ , i=1,2,...,m.

## 2.3.4. Partitioning and Assignment

We next partition the region into two. The ratio of the left subregion to the right subregion is [m/2]/[m/2] where [k] denotes the largest integer which is smaller than k. We do scaling once more for the left subregion and then for the right subregion. As before, in scaling for a subregion we always keep those modules outside fixed. The result of this gives two partitioned subregions together with their associated modules. We next repeat the process for each subregion, i.e., perform independently for each subregion, optimization, relaxation and partitioning.

In the following we will reinstate the y coordinate to summarize the 2dimensional partitioning and assignment problem.

Input:

A 2-dimensional region to be partitioned into rectangles each containing a module, a set of m movable modules together with their coordinates and a set of n-m fixed modules.

## Assignment:

- Do optimization on both the x coordinate and the y coordinate of the movable modules.

- (2) While each region contains more than one module

Do

Choose the direction of the cut-line.

Cut the longer side of region.

List all current regions.

For each region do partitioning.

(3) For each region, assign the module to the legal value.

## 2.4. Discussion

## 2.4.1. Multi-module nets

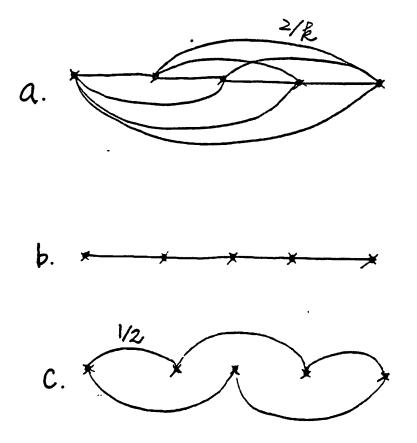

As mentioned in the introduction section, we assume that all nets are 2module nets in our treatment. Since multi-module nets are always present, we use the following two models to deal with them:

- At the beginning we use a clique to simulate a multi-module net. If there are r modules in a net, the weight of each edge on the clique is 2/r.

- (2) After the relative module position is determined, we use a chain to connect the modules. Consider the x direction, we order the modules according to their coordinates; we then link the modules by a chain in this order.

In the experiments to be discussed in 4.3, the lengths of wires are measured according to the model in (2) in x and y directions, respectively.

## 2.4.2. Computation complexity

The optimization algorithm amounts to a linear resistive network computation. Using sparse matrix technique, we have the computation complexity  $O(m^{1.4})$  where m is the number of movable modules. The scaling operation is linear with k where k is the number of modules in a subregion.

As to partitioning and assignment, in each iteration, all current regions are divided into two subregions. It takes  $\log_2 n$  iterations to make all the necessary divisions. Thus the total complexity is  $O(n^{1.4}\log_2 n)$ .

## 2.4.3. Experimental results

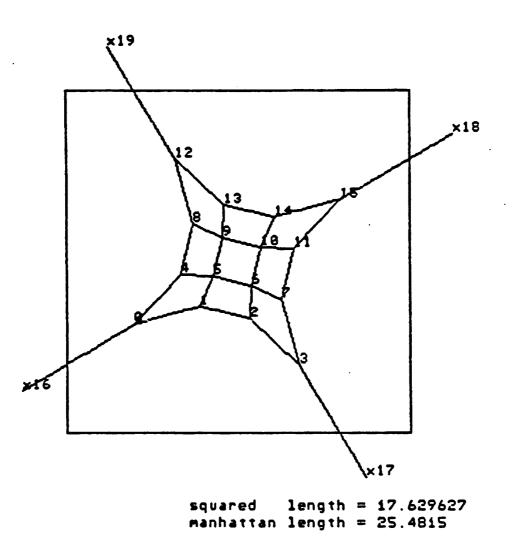

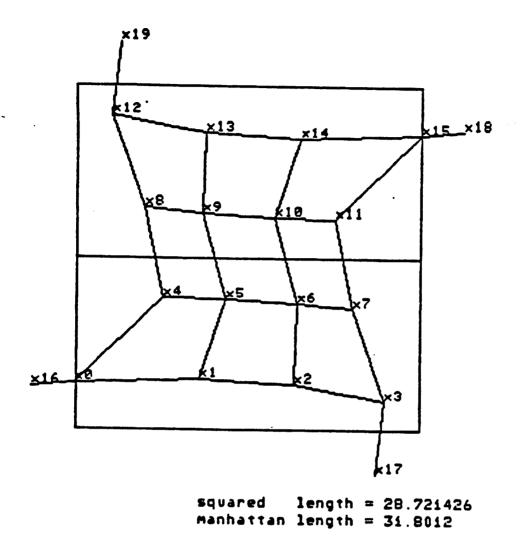

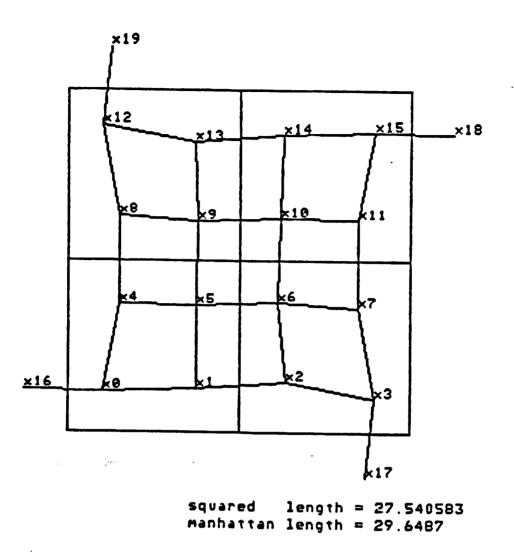

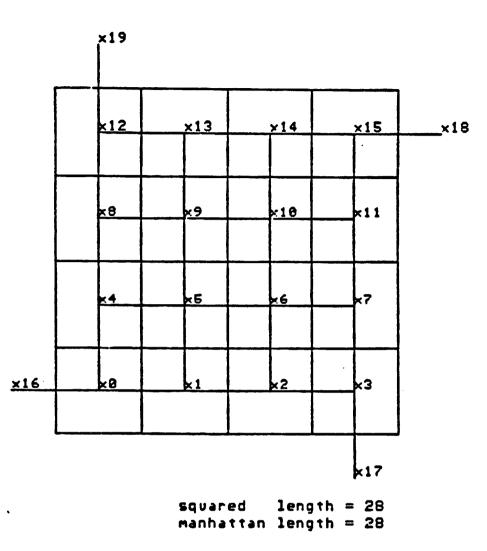

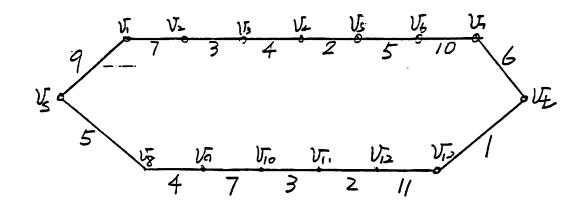

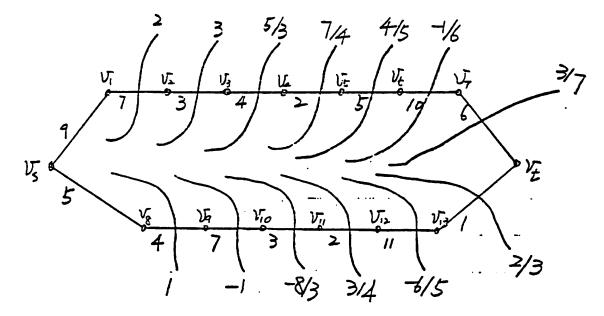

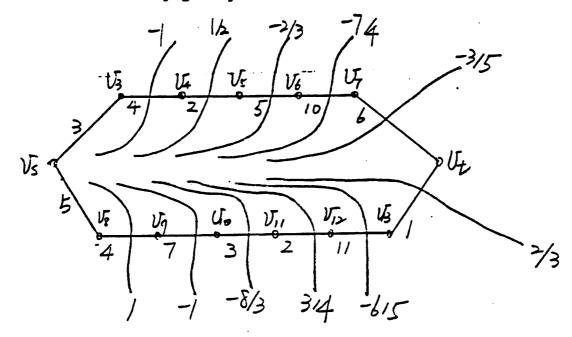

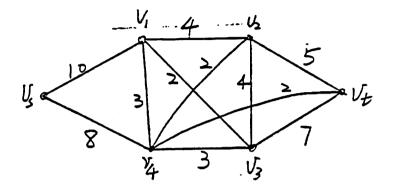

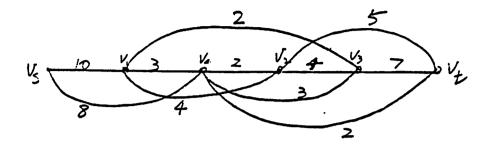

A 20 module example is designed to illustrate the procedure of our algorithm. As shown in Fig. 2.7, four modules are fixed on the four corners of the chip, and in the optimal placement every module is connected to the neighboring modules only. Figs.  $2.4\sim2.7$  illustrate how module locations evolve from the initial placement onto slots. In the figures, module positions are indicated by points with module numbers. The connectivity among modules is represented by linking lines.

Fig. 2.4. Result of assignment step (1) of the 20 module example. The module positions are optimal under the constraint that the center of

gravity of the modules is at the center of the chip.

Fig. 2.5. Result of first level partitioning and scaling after relaxation is carried out in the vertical direction.

Fig. 2.6. Result of second level partitioning and scaling.

Fig. 2.7. A 20-module placement problem with 4 fixed modules specified.

Fig. 2.4 is the result of initial optimization. The module positions are optimal under the constraint that the center of gravity of the modules is at the center of the chip. Relaxation is next carried out and the modules spread out over the entire region in the vertical direction. Next partitioning and scaling are used to relocate the modules into two subregions as shown in Fig. 2.5. Fig. 2.6 is the result of second level of optimization, relaxation and partitioning using a vertical cut-line; hence, module spread out in the horizontal direction. Fig. 2.7

is the solution of the final assignment. It is seen that all modules are located on slots.

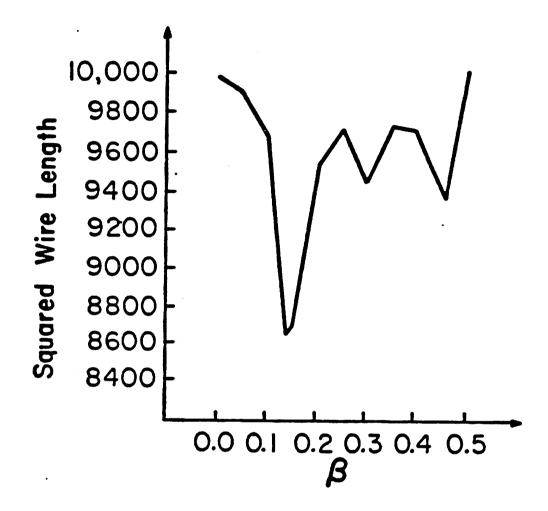

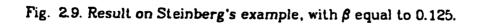

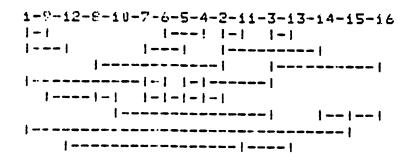

To evaluate the effectiveness of our method, we use the example given by Steinberg[5,9]. However, because we always assume that there exist fixed modules in our formulation, we modified Steinberg's example by fixing the position of the two modules (34 and 26 shown in Fig. 2.9) in the bottom row. In relaxation, we tried different values of  $\beta$  to compare the results. These are shown in Fig. 2.8 where we plot the sum of the squared length for different values of  $\beta$ . It is clear that  $\beta=0$  implies no relaxation. The placement for  $\beta=0.125$  which leads to the smallest squared wire length is shown in Fig. 2.9. This 34 modules, 172 nets example took 13.1 seconds of cpu time and 169K memory on VAX 11/780 machine. For comparison with Steinberg and Hall, we also calculated the sum of the Manhattan length and the sum of Euclidean length. The Table 2.1 summarizes the comparison.

Fig. 2.8. Result on Steinberg's example, with different values of  $\beta$  in relaxation.

| 1  | 9  | 2  |    |

|----|----|----|----|

| 16 | 8  | 3  | 17 |

| 10 | 4  | 18 | 5  |

| I  | 7  | 13 | 6  |

| 15 | 20 |    | 12 |

| 28 | 19 | 14 | 27 |

| 32 | 29 | 23 | 21 |

| 33 | 30 | 22 | 25 |

| 34 | 31 | 24 | 26 |

Squared length 8596 Manhattan length 5316 Euclidean length 4358.36

| Measure          | Steinberg | Hall    | Cheng-Kuh |

|------------------|-----------|---------|-----------|

| Squared length   | 11875     | 9699    | 8596      |

| Manhattan length | N.A.      | 5139    | 5316      |

| Euclidean length | 4894.54   | 4419.13 | 4358.36   |

Table2.1. Example 1: Steinberg's example

As a second example we use the ILLIAC IV PC Board problem given by Stevens[10]. Again we fix the IO Pads according to the placement result of Quinn and Breuer[1]. The result with  $\beta$ =0.25 is given in the Table 2.2 together with those of Stevens and, Quinn and Breuer. This 136 modules, 432 nets example took 104.2 seconds of cpu time and 480K memory on VAX 11/780 machine.

| Measure          | Stevens | Quinn and Breuer | Cheng-Kuh |

|------------------|---------|------------------|-----------|

| Squared length   | N.A.    | 8794             | 7521      |

| Manhattan length | 2733    | 2558             | 2495      |

Table2.2. Example 2: Placement of ILLIAC IV Board IC136.

In both examples it is seen that in terms of our chosen objective function, i.e., the sum of squared length, our method yielded the best results by far.

### 2.5. Conclusion

The module placement problem has been formulated in terms of linear resistive network optimization. The objective function used is the sum of

squared wire length which corresponds to power dissipation in the resistive network. Fixed modules become nodes with constant voltages. Movable modules then correspond to nodes whose voltages are to be determined. Since modules must be put on slots, a set of constraint equations are imposed on the modules. We consider only the first order linear constraint which, in essence, fixes the center of gravity of the movable modules. The optimization calculation can thus take advantage of the sparse matrix technique, and is repeated in the over-all algorithm. To assign modules to slots, we need to perform scaling, relaxation, partitioning and assignment. These comprise the over-all algorithm.

We have tried our method on well-known examples and compared our results with other methods. So far, we always obtain the least squared wire length as we expected. The extensions to gate-array, standard-cell, and building block designs will be discussed in the next two Chapters.

## Chapter 3

# Gate-Array and Standard-Cell Placements

### **S.1.** Introduction

Gate-array and standard-cell designs are now widely used for automatic layout of VLSI circuits. In these approaches, the designs of basic circuit configurations (modules) are stored in a library. A typical chip structure is shown in Fig. 3.1. The 10 pads are placed on the boundary of the chip, while the modules are assigned to rows inside the chip. Modules are assumed to have same height but varying width. The rectangular areas between rows are used for routing. This style significantly simplifies the design process. Often there are hundreds of modules on a chip. In such systems, automatic placement plays the important role of ensuring all modules are at their legal locations and furthermore achieving 100% routability.

In gate-array approach, rows of transistors are preprocessed. The chip size and routing areas are therefore fixed. In standard-cell, chip size and routing areas are adjustable. Thus, routing is different for these two systems. However, the formulation of placement problem is similar. Consequently, our placement algorithm is developed for both gate-array and standard-cell designs.

In this chapter, we extend the network optimization method to gate-array and standard-cell placement problems. The placement combined with a global routing system[11] and Yoshimura and Kuh's channel router[12] represents the major components of the Berkeley Automatic Gate-Array Layout System (Bagel)[13].

Since the modules have varying width, we have to consider the size of the modules in distributing them over the chip. Also, since pin locations can be far from the center of the module, we must modify our model of point modules pre-

viously used. Finally, in the assignment algorithm, we introduce a decompaction process to separate overlapping modules.

In section 2 we give a detailed formulation of our approach to the problem. Section 3 describes the extension of the network optimization method in gatearray and standard-cell approaches. Decompaction is also described in the assignment algorithm. Finally, we demonstrate the test results on 2K and 4K gate-array examples.

Fig. 3.1. An example with modules to be placed on rows within the chip and fixed IO pads on the boundary.

#### **3.2.** Formulation of the approach

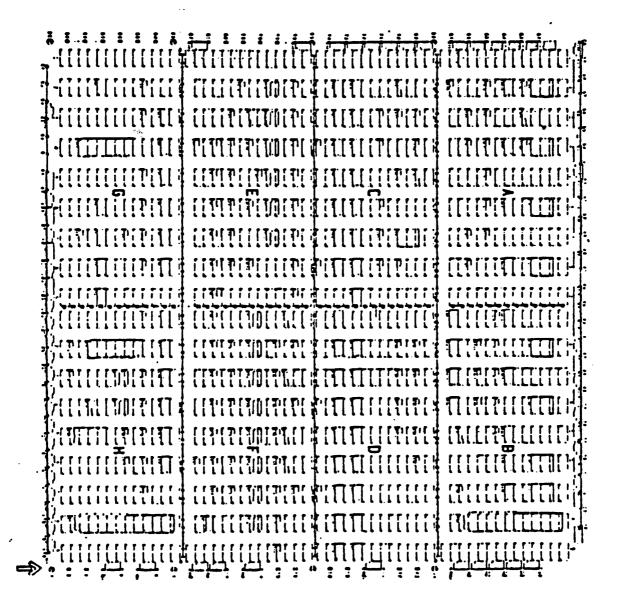

We formulate the placement problem in gate-array and standard-cell chips layout. Refer to Fig. 3.1 where array of rows together with slots on the boundary for external 1-O pads are shown. Given a set of modules, the modules have different width, but the height of modules is set equal to the height of rows of active areas. There are pins fixed on modules for the purpose of connection. Let N be a set of nets describing the connection of pins and 1-O pads. Placement assigns modules on rows of active areas with the constraint that no module can overlap each other. For each row, we denote the capacity to be the area available for modules as shown in Fig. 3.2. We denote the size of the module to be the area occupied by this module. As usual, we replace all multi-pin nets with twopin nets in the following formulation.

Fig. 3.2. Illustration of the capacity of each row and the size of the module.

#### **3.2.1.** Objective function

We choose the sum of squared wire lengths to be the objective function. Since the pin locations are considered, we formulate the function in terms of the pin coordinate  $(Pz_i, Py_i)$  where i is the index of pin. Let  $c_{ij}$  denote the connectivity between pin i and pin j. The objective function can be written as:

$$\frac{1}{2} \sum_{(i,j) \in N} c_{ij} L_{ij}^2 = \frac{1}{2} \sum_{(i,j) \in N} c_{ij} \left[ \left[ P x_i - P x_j \right]^2 + \left[ P y_i - P y_j \right]^2 \right]$$

(1)

43

where (i,j) is a pair of pin indices, and  $l_{i,j}$  is the Euclidean distance between pin i and pin j.

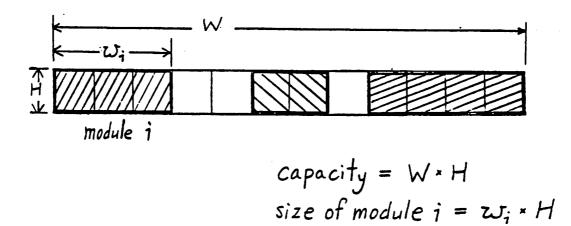

However, the locations of pins in Eq. (1) are constrainted with respect to the locations of modules to which the pins belong (Fig. 3.3). Let m(i) be the index of the module to which pin i belongs. In Fig. 3.3, the relative coordinate of pin i with respect to the center of the module is  $(dx_i, dy_i)$ . The pin location can then be formulated by the coordinates of module center,  $(x_{m(i)}, y_{m(i)})$ .

For each pin i.

$$Px_{i} = x_{m(i)} + Ox_{m(i)} * dx_{i}$$

$$Py_{i} = y_{m(i)} + Oy_{m(i)} * dy_{i}$$

(2)

In gate-array and standard-cell placements, the modules are not allowed to rotate by ninety degrees. They can only be reflected with respect to the x or y axis. In the above equation,  $(Ox_{m(i)}, Oy_{m(i)})$  denotes the reflection status of module m(i) in the x and y axes. The value of -1 indicating reflection and the value of +1 indicating no reflection.

The above equation indicates that the objective function in Eq. (1) can be formulated in terms of the coordinates of the module centers. Plugging Eq. (2)into Eq. (1), we see that the objective function is then formulated in terms of the coordinates of the module centers.

Fig. 3.3. Illustion of pin location with respect to module center.

#### 3.2.2. Network analogy

In Chapter 2, the model of point module is used for modules of same shape and size. Through network transformation, the point modules become the nodes of the corresponding linear resistive network. In this section, the model of modules is extended so that the distances between pin locations and module centers are taken into consideration.

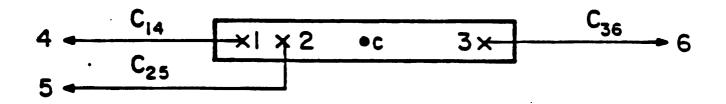

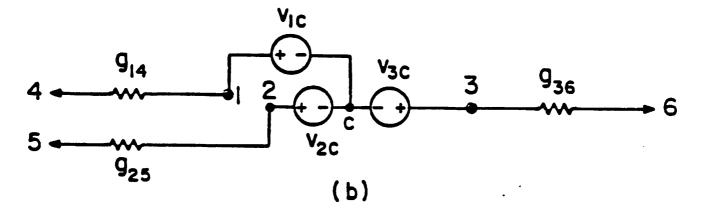

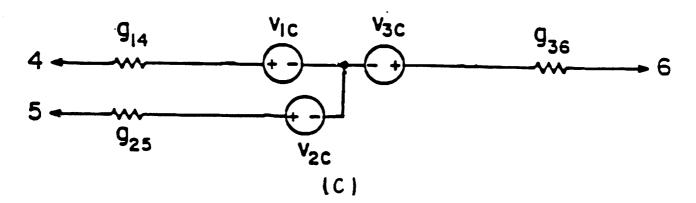

Suppose the orientations of modules are given. The distance between pin and the center of the module is a constant. In the network analogy, we transform coordinates to voltage values. Thus, the distance between pin and module center is transformed to a branch voltage source between the corresponding nodes. Fig. 3.4 illustrates this transformation. In Fig. 3.4a, we have a module with three pins 1, 2 and 3, connected to modules 4, 5 and 6, respectively. Point c is the center of the module. Fig. 3.4b is the corresponding network of Fig. 3.4a. Pins and modules together with point c are transformed to the nodes of the network. Connectivity is transformed to the conductance and constraint of pin locations is transformed to the branch voltage sources. Through voltage transformation, we can shrink nodes 1, 2 and 3 to node c and

transform the branch voltage sources to the voltage sources on branches (1,4), (2,5) and (3,6) as shown in Fig. 3.4c.

.

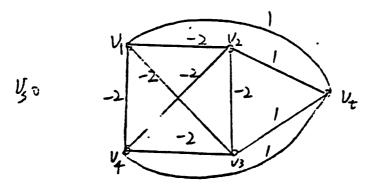

- Fig. 3.4. Network model of a large module with given orientation and pin location:

- (a) The module with three pins connected to other modules. c is the cneter of the module.

- (b) The network model of the module. Constraints on pin locations is modeled by branch voltage sources.

- (c) The network model after voltage transformation.

Thus, given n modules with pin locations on the modules, we have an analogy of an n-node linear resistive network with nodes representing the modules and branch voltage sources representing the constraint of pin locations.

Let G denote the branch conductance matrix, A the incidence matrix and  $E_b$  the branch voltage sources[6]. Let us set v to be the voltage vector of nodes. The power dissipation is now

$$P = \left(E_b + A^T \upsilon\right)^T G\left[E_b + A^T \upsilon\right]$$

(3)

#### 3.2.3. Slot constraints

For network optimization, we can formulate the slot constraint in terms of a number of polynomial equations. As in Chapter 2, we use the first order equation only. The first order equation expresses the constraint of keeping the center gravity of modules at the center of chip. Let  $w_i$  be the size of module i. This constraint is now written as:

$$\sum_{i=1}^{n} w_i x_i / \sum_{i=1}^{n} w_i = c_x \tag{4}$$

where  $c_x$  is the center of the region.

#### 3.3. Proposed method

The network optimization is modified to deal with modules of different size and the pin location constraints. A merging operation is introduced to improve the result after partitioning. We also describe the decompaction in subsection 3.3.5.

#### **3.3.1.** Optimization

Decomposing the voltage vector into floating voltage vector  $v_1$  and the fixed voltage sources  $v_2$ , we have the following formula for the power dissipation.

$$P = E_b^T G E_b + v_1^T y_{11} v_1 + 2v_1^T y_{12} v_2 + v_2^T y_{22} v_2 + E_b G A_1^T v_1 + E_b G A_2^T v_2$$

(5)

where  $y_{11}$ ,  $y_{12}$ ,  $y_{22}$  are the short-circuit submatrices of the indefinite admittance matrix  $Y = AGA^{T}$ .  $A_{1}$  and  $A_{2}$  are the submatrices of A corresponding to vector  $v_{1}$ and  $v_{2}$ .

We want to minimize the power dissipation subject to the constraints in Eq. (4). Similar to the result of Chapter 2, we obtain the following results from the well-known Kuhn-Tucker conditions:

$$v_1 = v_a + y_{11}^{-1} i_a$$

(6a)

$$\boldsymbol{v}_{a} = \boldsymbol{y}_{11}^{-1} \left[ -\boldsymbol{y}_{12} \boldsymbol{v}_{2} - \boldsymbol{A}_{1} \boldsymbol{G} \boldsymbol{E}_{b} \right]$$

(6b)

$$i_{a} = \frac{d - w^{T} v_{a}}{w^{T} y_{11}^{-1} w}$$

(6c)

where w is a vector of elements  $w_i$  and d is the constant to maintain the first order constraint.

It is seen that that first term in Eq. (6a) represents the solution for which there is no constraint on slots. The second term of Eq. (6a) can be viewed as a correction term which attempts to align the solution on slots. In terms of electric network, we may use current sources to interpret the effect. Thus we have a linear resistive network with both voltage and current sources.

Any deviation from this solution can cause the power dissipation to increase. Let us assume that we deviate away from the solution  $v_1$  of Eq. (6) by  $\delta v_1$  under the constraint of Eq. (4), i.e.

$$\boldsymbol{w}^{T}\delta\boldsymbol{v}_{1} = 0 \tag{7}$$

Then we claim that the power dissipation is increased by

$$\frac{1}{2}\delta v_1^T y_{11} \delta v_{1}. \tag{8}$$

Proof:

The proof is similar to the proof in subsection 2.2.1 except that the effect of the branch voltages and sizes of modules are considered here. From equation (5), we have

$$\Delta P = P[v_1 + \delta v_1] - P[v_1] = \delta v_1^T y_{11} \delta v_1 + 2v_1^T y_{11} \delta v_1 + 2\delta v_1^T y_{12} v_2 + E_{\delta} GA_1^T \delta v_1$$

From equation (6)

$$y_{11}\left(v_1-v_a\right)=i_a$$

and using equation (7). we obtain

$$\Delta P = \delta v_1^T y_{11} \delta v_1$$

**Q.E.**D.

Therefore the increase in power dissipation has an upper bound which is proportional to the norm of the deviation  $\delta v_1$ .

### 3.3.2. Scaling

The formulation of scaling in Chapter 2 is modified to take into account the sizes of modules. Without lose of generality, we assume there are certain number of legal locations for modules to be assigned in order to formulate the mean position and root mean square amplitude of the desired module distribution. Let us assume that in a region or a subregion, there are k modules with m legal locations given by  $[p_1, p_2, ..., p_m]$ . Let  $[x_{o1}, x_{o2}, ..., x_{ok}]$  denote the solution obtained from optimization and let  $[x_{n1}, x_{n2}, ..., x_{nk}]$  denote the new solution after scaling. For simplicity, we minimize the following objective function

$$\sum_{i=1}^{k} w_{i} \left( x_{ni} - x_{oi} \right)^{2}$$

(8)

under the first and second order slot constraints

$$\frac{\sum_{i=1}^{k} w_{i} x_{ni}}{\sum_{i=1}^{k} w_{i}} = \frac{\sum_{i=1}^{m} p_{i}}{m}$$

(9)

and

$$\frac{\sum_{i=1}^{k} w_{i} x_{m}^{2}}{\sum_{i=1}^{k} w_{i}} = \frac{\sum_{i=1}^{m} p_{i}^{2}}{m}$$

(10)

The solution is given by the Kuhn-Tucker conditions, i.e. For i=1,2,...,k

$$x_{ni} = \frac{x_{oi} - c_o}{a_o} a_n + c_n \tag{11}$$

where

$$c_n = \frac{1}{k} \sum_{i=1}^k p_i \tag{12}$$

$$a_{n} = \left[\frac{1}{k} \sum_{i=1}^{k} \left[p_{i} - c_{n}\right]^{2}\right]^{\frac{1}{2}}$$

(13)

$$c_{o} = \frac{1}{k} \frac{\sum_{i=1}^{k} w_{i} x_{oi}}{\sum_{i=1}^{k} w_{i}}$$

(14)

and

$$a_{o} = \left[\frac{\sum_{i=1}^{k} w_{i} \left[x_{io} - c_{o}\right]^{2}}{\sum_{i=1}^{k} w_{i}}\right]^{\frac{1}{2}}$$

(15)

where  $c_0$  is the mean position of the computed module positions and  $a_0$  is the root mean square amplitude from  $c_0$ . If  $a_0$  approaches zero, so does  $x_{oi}$ - $c_0$  in Eq. (11), and Eq. (11) can be replaced by

$$x_{ni} = c_n \tag{16}$$

It is easy to check that after scaling, the objective function in equation (8) . is equal to

$$\sum_{i=1}^{k} w_{i} \left[ \left[ a_{n} - a_{o} \right]^{2} + \left[ c_{n} - c_{o} \right]^{2} \right]$$

(17)

#### 3.3.3. Relaxation

The result of relaxation, as described in Chapter 2, leads to modules more or less confined to the center of the region. Therefore, relaxation scheme is used to spread the modules to the whole region. The method calls for repeated use of scaling and optimization over the subregions specified by designers. Modules are selected to the subregions according to the order of their

coordinates. We try to make the total size of the selected modules equal the capacity of the subregion. Since the sizes of modules are not uniform, total size of the selected modules and the capacity of the subregion may not match. In order to make the difference small, we develop a function to define the number of modules to be selected. Let P be the capacity of the subregion. Let module i be the critical module such that by adding this module the sum of selected module sizes would increase from a value T to  $T + w_i$  where  $T < P \leq T + w_i$ . If  $P-T > T + w_i - P$  then we select module i. Otherwise it is not selected. Thus, the difference is smaller than the size of the largest module. We define the number of the selected modules by function f(P).

Thus the relaxation is described as:

Input:

A one-dimensional region with coordinates of movable modules  $x_i$ , i=1,2,...,m obtained from initial optimization in the entire region with specified fixed modules  $x_i$ , i=m+1,m+2,...,n on the boundary. Sum of the m movable modules is S. A parameter  $\beta$  is to be chosen by the designer with  $0<\beta<50\%$ .

**Relaxation:**

- Order the modules left to right according to coordinates of the centers of modules

- (2) Choose  $f(S^*\beta)$  modules from the left, setting other modules fixed and do scaling in the left  $\beta$  region.

- (3) Fix the modules so determined in the left  $\beta$  region and release the modules in the right (1- $\beta$ ) region. Do optimization.

- (4) Choose  $f(S^*\beta)$  modules from the right, set other modules fixed and do scaling in the right  $\beta$  region.

- (5) Fix the modules in the right β region and release the modules in the left (1-β) region. Do optimization.

- (6) Choose f(S\*β) modules from the left, set other modules fixed and do scaling in the left β region.

- (7) Set modules in both the left  $\beta$  region and the right  $\beta$  region fixed and release the modules in the center subregion. Do optimization.

Output:

A one-dimensional region with m modules and their new coordinates  $x_i$ , i=1,2,...,m.

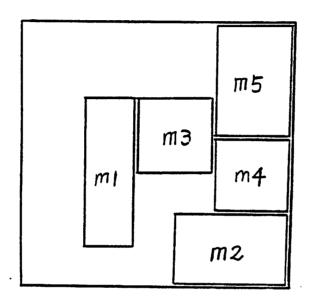

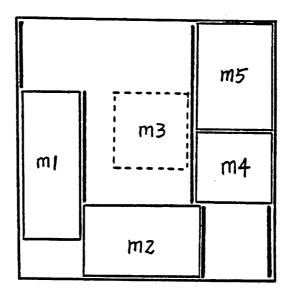

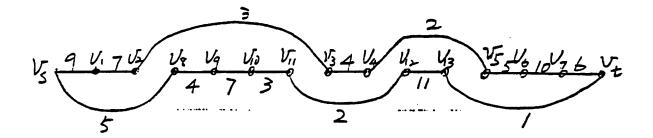

### 3.3.4. Partitioning and Merging

In partitioning, we divide a given region into two subregions. The modules in the region are redistributed to the two subregions. Also we try to make the ratio of module sizes in two subregions approaches the ratio of the capacities of the subregions. Let R be the ratio of the capacities of two subregions and S be the total size of the modules to be partitioned. The intended total sizes of modules in the two subregions would be  $S^* \frac{1}{1+R}$  and  $S^* \frac{R}{1+R}$ . Thus, f( $S^* \frac{1}{1+R}$ ) defines the number of modules to be seperated from other modules.

Each time we list all regions on the chip as current regions. The partitioning step divides the current regions into subregions. After all current regions are partitioned, we use a merging step to improve the result. We use a window to cover part of subregions, merge these subregions and do the partitioning again. We define two kinds of windows: horizontal and vertical. In the horizontal window, the number of columns of subregions is larger than the number of rows of subregions. In the vertical window we have a larger number of rows of subregions. In Fig. 3.5 we use a  $(1 \times 4)$  horizontal window. We scan rows from right to left with an increment of 2 and top to bottom with an increment of 1. The illustration of vertical window could be shown by rotating this picture 90 degrees and reflecting with respect to the x axis.

Fig. 3.5. Illustration of horizontal window.

### **3.3.5.** Assignment

We continue partitioning the chip until all modules are assigned to the predefined rows, while keeping the total size of modules in each row approximately the same. Because the size of modules is not uniform, two different rows of modules may not have the same size. When one row of the region is partitioned into two parallel rows of subregions, we check the difference of sums of module sizes between the two rows in the partitioning of each region. Thus, the difference of the total module sizes between the two rows is not larger than the size of the largest module.

Initially, because the orientation of modules is not determined yet, point model is assumed to represent all the modules. After optimization, the relative locations of modules are determined. Based on those locations, the reflection of each module is determined to minimize the wiring length. This process is repeated after the partitioning in each level.

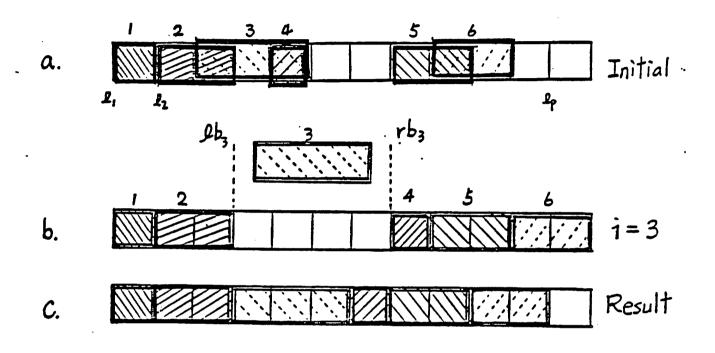

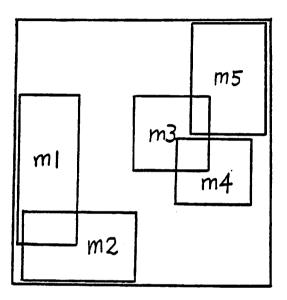

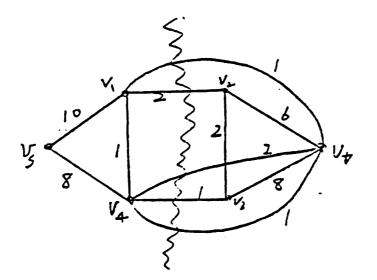

When modules have been assigned to rows, they might overlap, because the modules have different shapes. A decompaction step is done on each row to separate the overlapping modules. Scanning from right to left, we assign the feasible range of location for each module. For the current module, its left bound is set by the right edge of the previous module, and the right bound is set so that the capacity of the right region is equal to the sum of sizes of modules on the right hand side. Then the module is set between the boundary and located as close as possible to its original position obtained after partitioning. Fig. 3.6 illustrates this process. The modules are initially located in one row as shown in Fig. 3.6a. Fig. 3.6b demonstrates the process of decompaction. The vertical dotted lines indicate the left and right bounds of module 3. Module 3 is located within the boundary and set near to its initial location. Fig. 3.6c shows the result of decompaction.

Fig. 3.6. Decompaction on one row:

- (a) Initial locations of modules.

- (b) Decompaction process on module 3.

- (c) Result of decompaction.

The following shows the assignment algorithm.

Input:

A 2-dimensional region to be partitioned into rectangles each containing a

module, a set of m movable modules together with their coordinates, and a set of n-m fixed modules.

Assignment:

- Do optimization on both the x coordinate and the y coordinate of the movable modules.

- (2) While each region contains more than one module

Do

List all current regions.

For each region do partitioning.

Use horizontal window.

Do merging and repartitioning.

Use vertical window.

Do merging and repartitioning.

(3) For each row

Do decompaction.

#### **3.4. Experimental results**

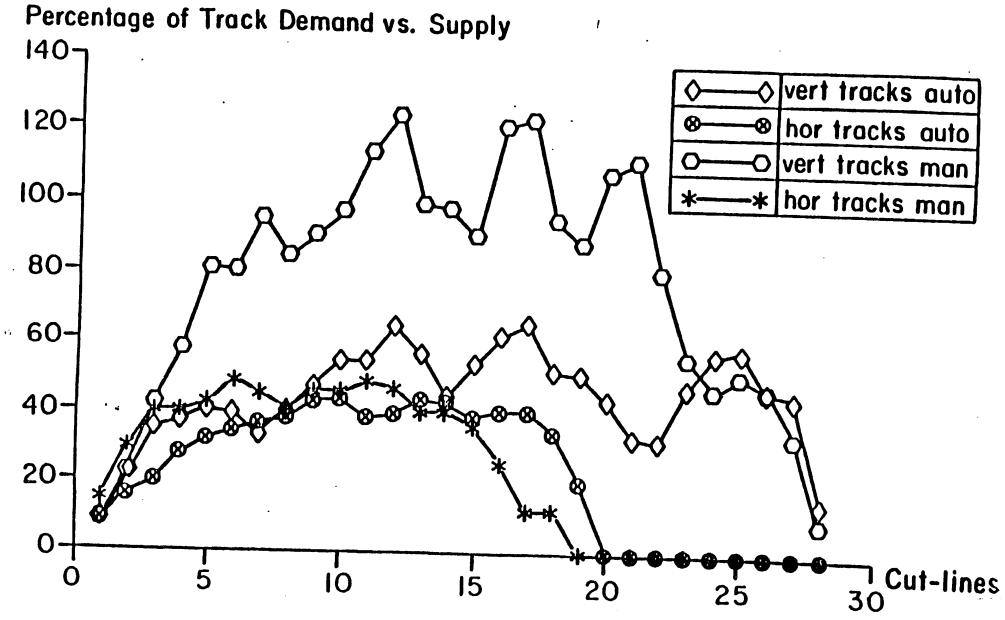

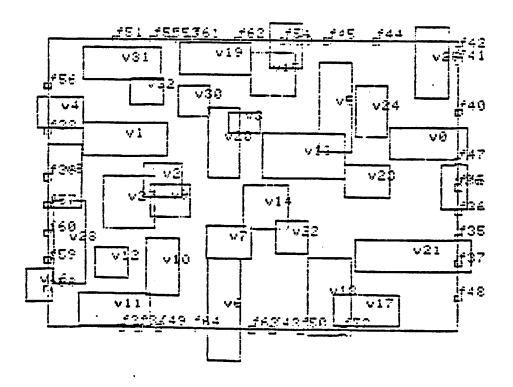

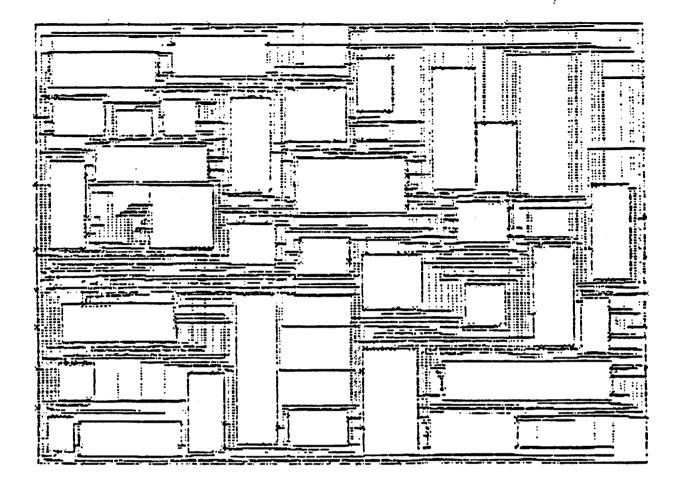

The above method has been implemented and tested with gate-array designs used at Hughes Aircraft Company and other industrial companies. Table 3.1 shows the comparison with manual designs on 4K gate-array chips. Four chips have been tested. It is shown that the sums of squared wiring lengths are reduced. Fig. 3.7 gives the solution of automatic placement of chip 1. Fig. 3.8 exhibits results in terms of wirability of chip 1 for both the automatic and manual designs. The abscissa represents cut-lines in the horizontal and vertical directions. The ordinate represents percentage of routing track demand oversupply. It is seen that in the horizontal direction both the manual and automatic placements yield results which are easily routable. However, in the vertical direction, the manual placement requires over a hundred percentage of track demand over supply, which is clearly unroutable, while the automatic placement requires a peak percentage of less than 70. In general, automatic placement tends to distribute the wires more uniformly and thus achieves better routability. The cpu time of the above placement is about one minute on an Amdahl V8.

| Chip # | manual placement     | network optimization |

|--------|----------------------|----------------------|

| 1      | 5.98×10 <sup>9</sup> | 1.31×10 <sup>9</sup> |

| 2      | 3.70×10 <sup>9</sup> | 3.37×10 <sup>9</sup> |

| 3      | 2.91×10 <sup>9</sup> | 1.83×10 <sup>9</sup> |

| 4      | 2.16×10 <sup>9</sup> | 0.94×10 <sup>9</sup> |

Table 3.1. Placement results of four 4K gate-array chips in terms of sum of the squared wire length.

Chip 1: 317 modules, 676 nets and 2284 pins.

Chip 2: 255 modules, 916 nets and 2049 pins.

Chip 3: 442 modules, 983 nets and 3012 pins.

Chip 4: 484 modules, 1030 nets and 1969 pins.

1. **WIN** 1 114 ä 74 ifi; 1 765.12 TLI-1 7*6* 14 ٠ŧ. Sector Sector ····· 1. 3. The States Ð tt. 11 ų. <u>」; 1 - 8 क</u> 1 21 ı: H -11 LIL 111 đ. 5 ij łł ń **H**H π T 71 1 1

Fig. 3.7. Picture of the chip placement.

We also compare with the traditional iterative improvement method[14] on a 2K gate array example. The specification of the example and the results are given in Table 3.2. It is shown that not only the sum of squared wire lengths decreases, but the sum of wire lengths is also reduced by 26%. This example takes 783.2 seconds of cpu time on VAX 11/780.

|                  | Iterative improvement | Network Optimization |

|------------------|-----------------------|----------------------|

| Manhattan length | 77326                 | 57191                |

| Squared length   | 9.99×10 <sup>6</sup>  | 3.01×10 <sup>6</sup> |

Table 3.2. Comparison with iterative improvement on 2K gate-array chip

445 modules, 464 nets and 1713 pins

#### **3.5.** Conclusion

We have implemented a resistive network optimization method for gatearray and standard-cell placement. Point modules are replaced by modules of different sizes on cell rows. A decompaction process is proposed to separate modules on each row. The results applied to 4K gate-array chips lead to far superior results than that of manual placements. Also, the comparison with the traditional iterative improvement method on a 2K gate-array example shows that our method produces better results.

### Chapter 4

# **Building Block Placement**

#### 4.1. Introduction

The building block layout is a popular approach for developing high-density, high production-volume integrated circuit chips. However, due to the wide variety of sizes and shapes of modules used in building block systems, the placement problem becomes very complicated.

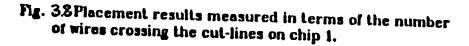

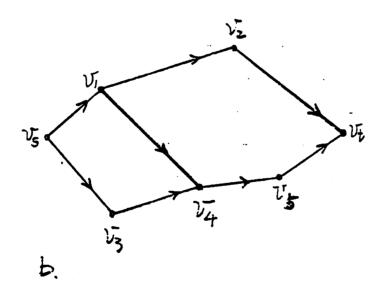

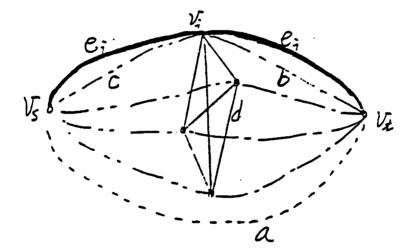

To dissect a rectangle into a finite number of non-overlapping squares, Tutte et al.[15] introduced a planar directed graph. This planar directed graph is later used as polar graph in building block placement. Based on the polar graph representation, many placement methods have been developed. Lauther[16] combined this graph representation with a min-cut placement algorithm to partition the modules into separated areas and improve the result by rotating and flipping of the modules. Hsuch and Pederson[17] also derived from the same graph a compaction algorithm to reduce the size of the chip. However, in the compaction, the connectivities among the modules are not taken into account. As a result, the wiring length might increase after a few interactions of compaction.

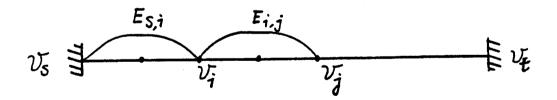

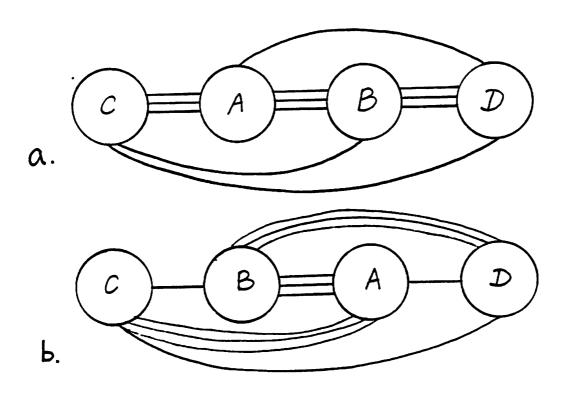

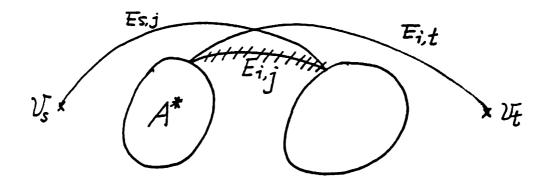

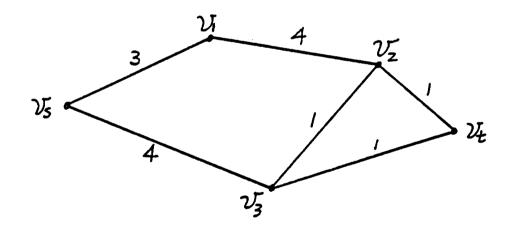

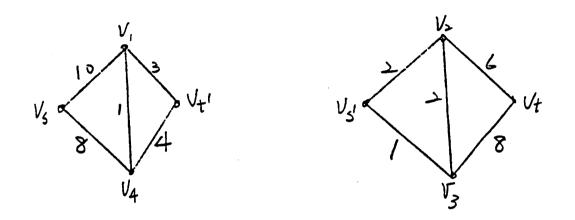

The structure of polar graphs represents the relative locations of the modules. There are different descriptions of the polar graph with respect to the implementations. This chapter uses a graph representation[17] which is extended from the traditional polar graph so that free spaces are allowed on the chip. Let us consider an example of such a graph illustrating placement of modules along the x-axis. In the graph, there are one source node and one sink node representing the left and right edges of the chip, respectively. Other vertices represent the modules. There is a branch (a,b) directed from a vertex a to vertex b if the vertices a and b in the graph correspond to "horizontal adjacent"

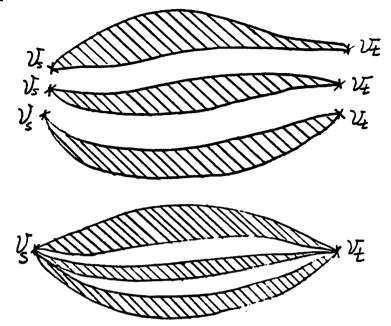

modules in the layout, and module a is on the left hand side of the module b. Two modules are horizontal adjacent if there exists a horizontal line which intersects with both modules, and no module placed between them is cut by this line. Each branch has a weight associated with it which equals the sum of half widths of the modules. This representation is shown in Fig. 4.1. The placement in Fig. 4.1a is represented by the graph shown in Fig. 4.1b. The free space is not included in the graph. Note that the topology of the graph might change when modules are moved from their current locations. It is important to note that the longest path in the graph determines the width of the chip.

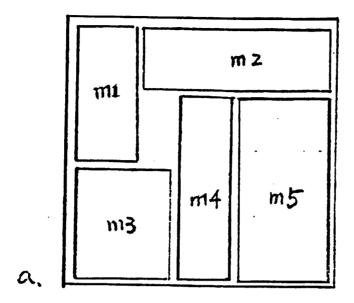

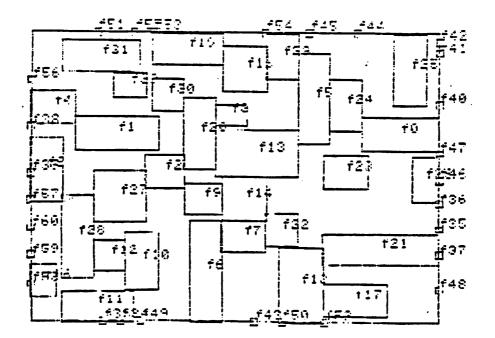

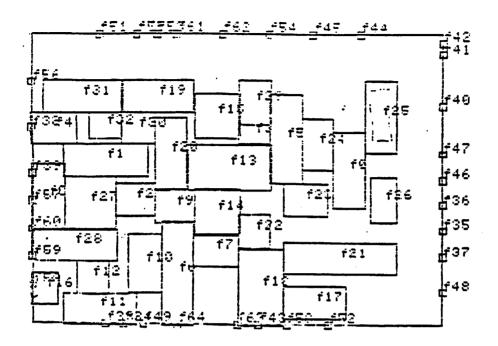

In the following sections, we describe a novel algorithm. This method applies the network optimization method[18] to locate the initial relative module locations. In order to spread the modules, the partitioning step of the network optimization in Chapter 2 is first used to divide the chip into 4x4 subregions. The modules whose dimension is comparable to the dimension of subregions are considered as critical modules and placed at this stage. After their position has been fixed, the capacity of each chip region is updated and network optimization method is used to relocated other modules. A reduction process is used to separate the overlapping modules and reduce the chip size, while still maintaining the original relative module locations. In preliminary experiments, this method generates results comparable with manual placement.

### 4.2. Formulation

Consider a set of rectangular modules of different shapes and sizes to be located within chip area. On the four sides of the modules are pins for connections. Given a netlist and external pads fixed on the boundary of the chip, the nets connect external pads and modules. The placement problem is to place the modules with the goal of minimizing the chip area and keeping modules with strong connectivities near each other.

Fig. 4.1. Illustration of polar graph.

The two objectives of minimizing the area and placing modules with strong connectivities close together are related to the cost of chip manufacturing and to its performance. The advantage of small chip size is obvious, while the objective of contiguous placement of modules with strong connectivity is needed to reduce the time delay of the signals. We choose the objective function of sum of squared wire lengths since a small sum leads to both the chip size minimization and delay-time reduction.

The results of placement are input to a routing system which wires the nets among the modules and pads to complete the layout. Therefore, the size of the routing areas also affect the results of layout. To concentrate on the placement itself, we assume the routing areas are given. The modules are expanded in both dimensions by an amount equal to half the channel width to cover the routing areas.

We also use grids to divide the chip area into basic square cells. The size of modules are then rounded off to the multiple of the basic square cells. Thus, the numbers of columns and rows of the grids define the size of the chip. The placement problem amounts to assigning modules on grids. This formulation simplifies the explanation and programming of the algorithms. However, the algorithms can be easily extended to gridless cases.

Donze and Sporzynski[19] have introduced the masterimage approach. This approach has a basic chip structure of gate array. The modules are allowed to have different widths and height, however. This method is considered to be intermediate between unconstrainted and constrainted approach. Thus, in the case that the channel widths are forced to be a constant and the module orientations are suitably constrained, the general building block placement problem reduces to the masterimage placement problem.

# 4.3. Preliminary locations of the modules

The network optimization method is used to determine the preliminary locations of the modules with the objective of minimizing the sum of squared wiring lengths.

Initially, each module is modeled by a single node of the network. After the optimal locations of modules are obtained, we choose the orientation of the module to minimize the wiring length. Then, in the corresponding network, the relative positions of pins are modeled by voltage sources connecting nodes pertaining to the module.

We assign modules into subregions in order to distribute the size of modules evenly over the chip. Because the size of modules is not uniform, the partitioning process checks the sum of sizes of modules in each partitioned row or column. For instance, when one row of regions is further partitioned into two parallel rows of subregions, we check the difference of sums of module sizes between the two rows in the partitioning of each region. Thus, the difference of the total module sizes between the two rows is not larger than the size of the largest module.

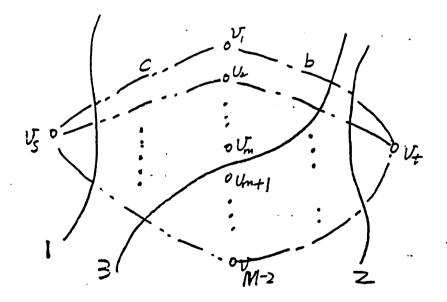

#### 4.4. Basic operations

With respect to the preliminary module locations, the modules might overlap due to their different sizes and shapes. This section introduces four basic operations, namely, compaction, decompaction, rotation and selection of preferable direction. The operations are processed in one dimension of the chip. Then the algorithms call for repeated use of the operations in each dimension to separate the modules and to minimize the chip size.