# Copyright © 1979, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# SOFTWARE MICROPROGRAMMING TOOLS FOR THE VAX-11/780

bу

Richard D. Tuck

Memorandum No. UCB/ERL M79/65

September 1979

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

Research supported in part by the U.S. Department of Energy Contract DE-AT03-76SF00034, Project Agreement DE-AS03-79ER10358, and the National Science Foundation Grant MCS-78-7291.

Partial fulfillment of Master of Science in Engineering.

# CHAPTER 1

## INTRODUCTION

Although the concept of microprogramming is nearly as old as electronic computing [Wilkes 51], it has only gained widespread popularity as an implementation technique since the introduction, in the early 1960's, of the IBM-360 family of computers. When a microprogram is used strictly as an implementation tool, the programmer is usually very familiar with the microarchitecture, if not its designer. Lately, however, microprogramming has been used for more than an instruction-set implementation tool: more and more operating systems routines are being microcoded [Stockenberg 78][Bondy 77], and several machines are user microprogrammable [Agrawala 76]. Also, as machine architectures become more complex, the supporting microprograms grow larger; the IBM-360, model 50 (1965) control store had a capacity of 2816, ninety-bit words [Husson 70]; the VAX-11/780 (1978) control store has a capacity of (at least) 5120, ninety-six-bit words. Larger microprogramming teams are required just to implement the instruction sets. Due to these factors, the people writing microprograms are less often the designers of the microarchitectures with which they are working, and are correspondingly less familiar with them.

The traditional microprogramming tools have been rather crude — either a flow-chart language, as used for the IBM-360s [Husson 70], or a more traditional assembly language [Davidson 78]. These sufficed for expert microprogrammers and compact microprograms, but are no longer any more appropriate than is assembly language for all systems and applications

macro-programming.

The desideratum, then, is a High Level Systems Program Language (HL-SPL) which could be translated into an efficient microprogram. As a first step towards this, we have designed and implemented a low-level language which hides from the programmer most of the baroque features of a particular microarchitecture. This language (Yet Another Low-Level Language, or YALLL) can be used as the machine-independent intermediate code output of a HL-SPL microcode compiler [Patterson 79]. The key observation concerning microarchitectures is not their differences, but their similarities: microinstructions invariably transform data between registers, and reference memory only in loading and storing their contents.

This paper describes the implementation of the YALLL microprogramming system running under Unix on Digital Equipment Corporation's VAX-11/780 [Strecker 78], hereafter known as YALLL/VAX. The VAX was chosen for this work because it is a new computer with 1024 words of user-programmable control store. Also, there are no other facilities for microprogramming this machine, as of this writing; those announced by the manufacturer will run under the VMX operating system, not Unix. Finally, it is anticipated that the VAX-11/780 will be extremely hard to microprogram even using DEC's announced macro-microassembler, because of the great microinstruction width.

The main constituent of this system is the VAX/YALLL compiler, called yc; this is a program consisting of 4456 lines of C [Ritchie 78], 495 of YACC [Johnson 76], and 283 of Lex [Lesk 75]. The YACC and Lex programs translate into 876 and 1404 lines of C, respectively. This translator contains an assembler mode embedded in the language. It is the only microassembler

**'**

وغ ۾

available for the machine at this time. The YALLL/VAX language, the assembly mode, and the use of yc are described in chapter three. The internals of the compiler are outlined in Appendix II, written mainly for the compiler maintainer.

The other software microprogramming tools are also described in chapter three: a linker, symbolic dump programs, floppy disk file transfer program, and DEC'S console program and console microdebugger. This description includes a tutorial example.

The approach described here, and supported by these programs, requires that the microprogram be written on the console floppy disk and loaded into writable control store (WCS) using a console LSI-11 command. The alternative to this is to load WCS directly from the VAX using the privileged WTPR instruction. The disadvantage of the latter approach is that failing to write a WCS image on the floppy disk does not permit the use of the console microdebugger to its fullest advantage. In particular, examining and changing WCS locations is impossible without the image file. These facilities may make little difference to the YALLL source programmer, but their absence would make microassembly-level debugging much more tedious than necessary.

A large part of this report is concerned with the VAX-11/780 architecture and microarchitecture. Chapter two presents a brief overview, and Appendix I is a fairly thorough description of the macro-architecture, the microarchitecture, and how they relate.

#### CHAPTER 2

# **VAX Architecture Summary**

This chapter presents a quick overview of the architecture of the VAX, and of the microarchitecture supporting it. Familiarity with this material will aid the understanding of that which follows, especially the examples of chapter four. The architectural features presented here are not necessarily the most interesting aspects of the machine, but those which most profoundly affect the microarchitecture, and thus the writing of microcode. For example, the variable length of the instructions affects how the microcode interacts with the instruction-fetch unit, and the size of data types supported determines how memory is accessed. All the material here is presented in much greater detail in Appendix A; in particular, the microarchitecture and microinstruction fields are presented there in great detail.

# 1. MACRO ARCHITECTURE

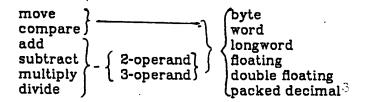

The architecture of the VAX-11 is based on that of the successful PDP-11 family of computers. The VAX does have a "compatibility mode", for running PDP-11 programs, but when running native-mode instructions, only "cultural compatibility" is maintained. That is, VAX data types are similar to corresponding PDP-11 data types. The VAX instruction format is also similar to that of the PDP-11; an opcode, followed by operand-specifying bits, using one of several address modes. VAX instructions may have zero to six operands, whose specifiers vary in length from one to nine bytes, as detailed in section 1.1.2.2 of Appendix A. Data types supported are: binary, two's complement integers (of length one, two, or four bytes), floating point numbers

(four or eight bytes), packed decimal strings (to thirty-one digits), and character strings. The architecture is basically register oriented, but some of the addressing modes facilitate the use of a stack, both for expression evaluation and local variables. There are sixteen, thirty-two-bit "general" registers, one of which (register r15) is the program counter, pc. Other registers are used by special instructions or convention including the stack pointer, sp (r14), frame pointer, fp (r13), and argument pointer, ap (r12). Furthermore, the decimal and character string instructions use some of registers r0-r5.

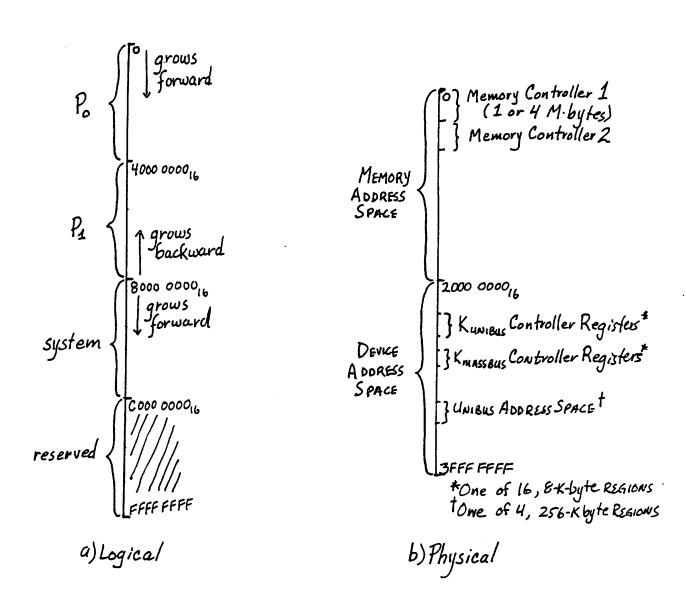

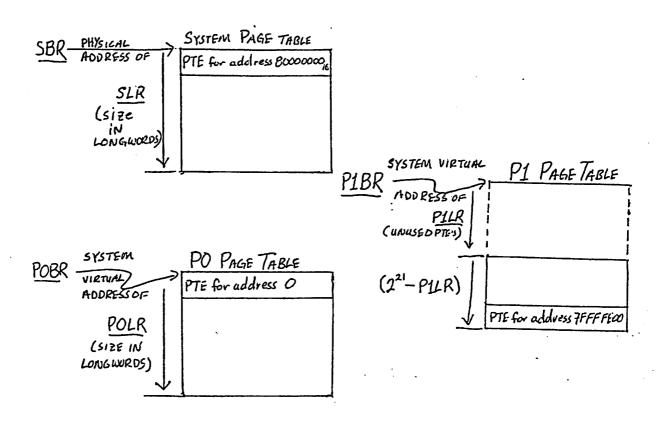

The VAX-11/780 has a 2<sup>32</sup> byte address space, of which the top fourth is "reserved" and unusable. The remaining addresses are divided into three regions: P0, P1, and system. Logical addresses are translated to physical addresses by way of paging. Each region has its own page table, containing one entry for each 512-byte logical page in that region.

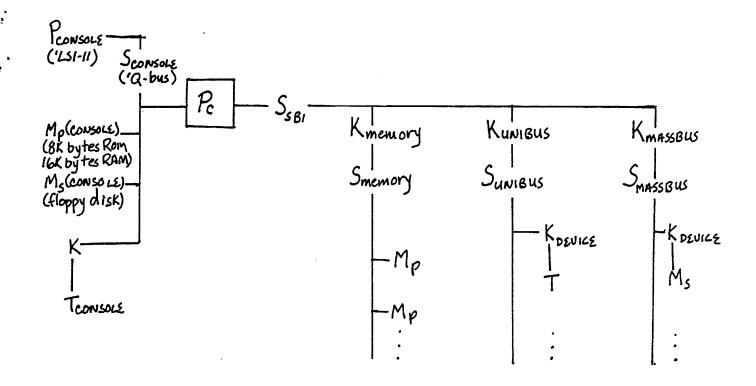

The physical memory, as well as peripheral devices, is connected to the CPU by way of a hierarchy of busses, the principle one of which is the Synchronous Backplane Interconnection (SBI). The SBI has a 2<sup>28</sup> longword address space, encompassing memory, secondary storage devices, and I/O devices.

# 2. MICROARCHITECTURE

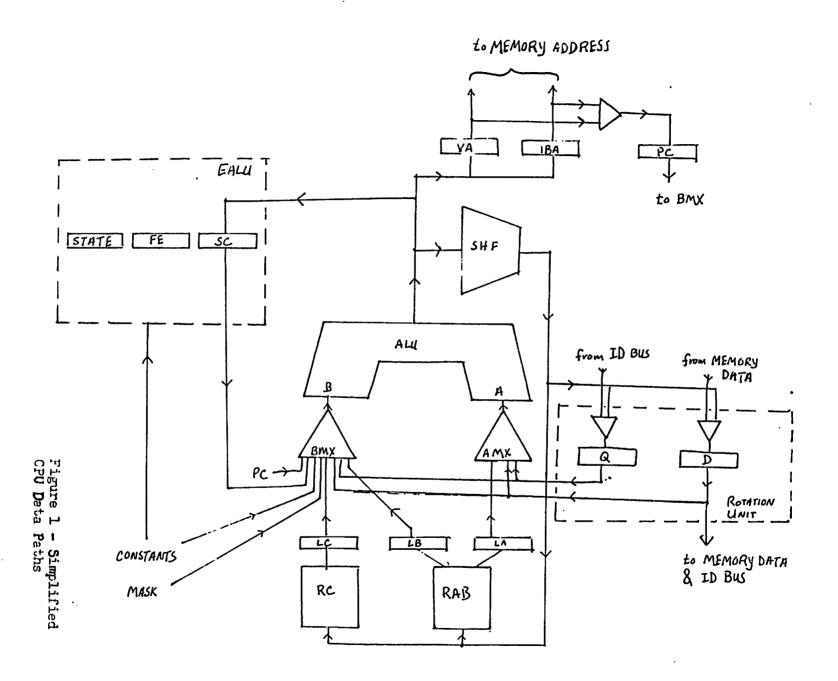

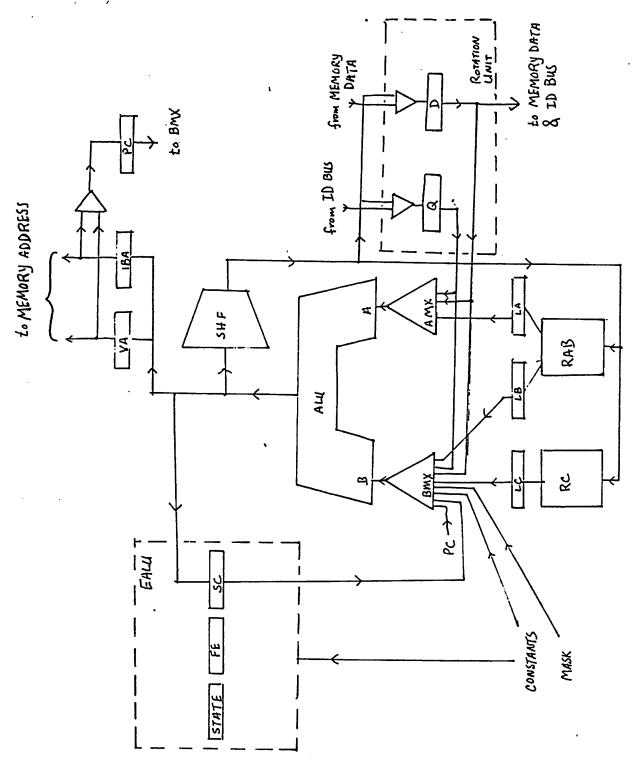

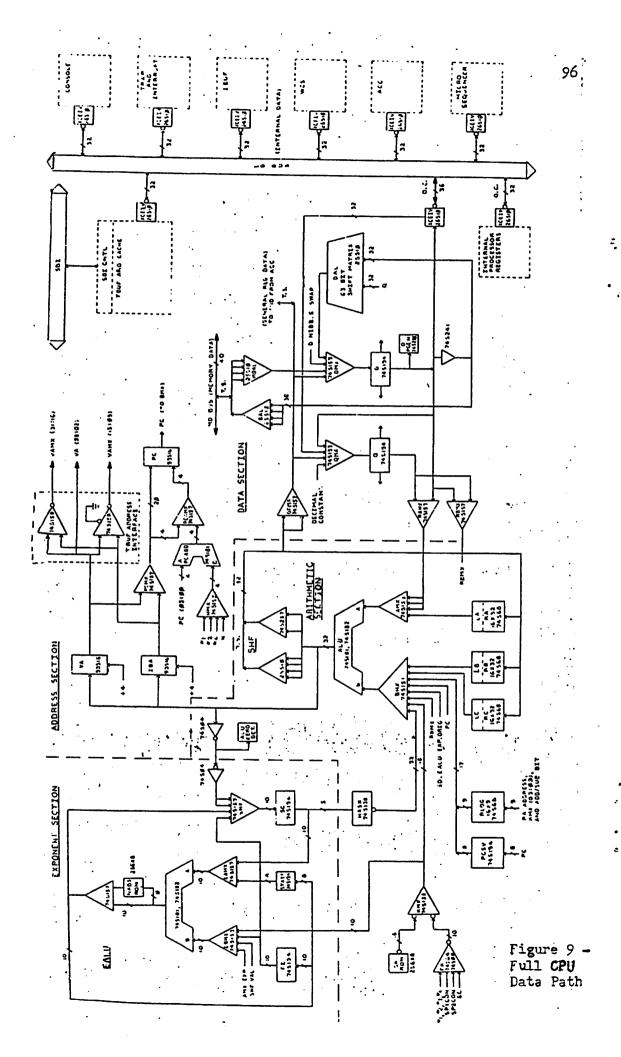

The heart of the VAX CPU is the 32-bit ALU and its associated registers. A simplified data path diagram is given in Figure 1. The general registers (r0-r14, but not pc) are kept in a register file (RAB). One set of registers' output passes through latch LA to the A (right) side of the ALU; the other passes through latch LB to its B (left) side. A file of temporaries (RC) is available on the ALU's left, passing through latch LC. A set of 64 16-bit constants

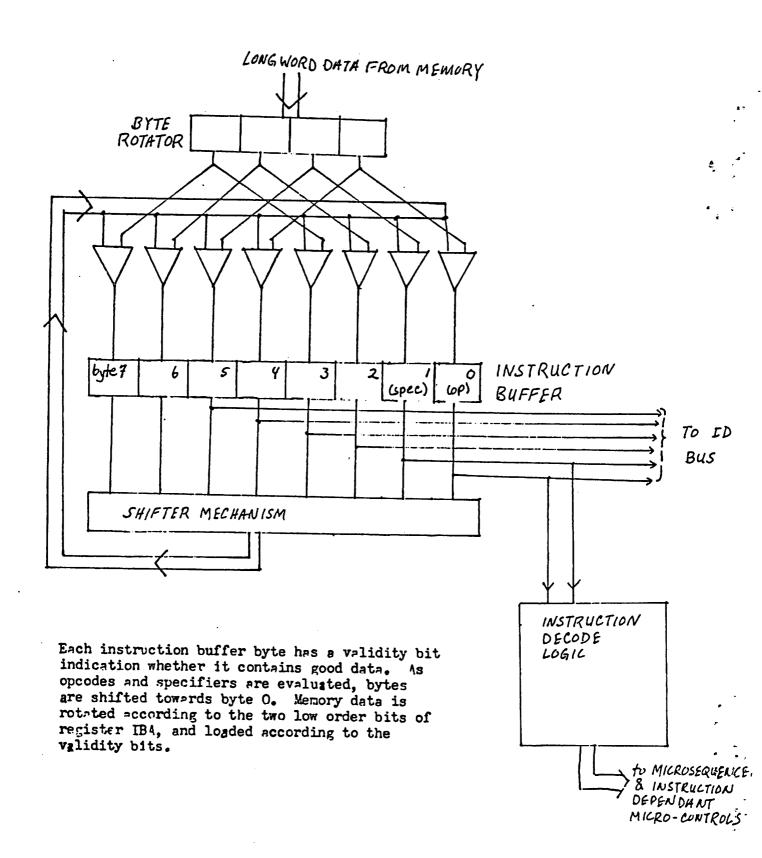

is also available on the ALU's left. Two very important registers, D and Q can be gated to either side of the ALU — they have several special properties, especially in regards to shifting. The 32-bit D register acts as the memory data register— all data routed to or from memory must pass through it. The "internal data" or ID bus takes its data from D and delivers to Q. This bus connects to several control registers (such as the alternate stack pointers, page table origin and length registers), as well as the instruction buffer (fetch-ahead unit). Instruction-stream data is received by this path, as are branch displacements.

The rotation unit takes the 64 bits from the Q and D registers (Q on the left), rotates by the amount specified by the contents of SC (or another source), and deposits 32 bits of the result back in D. A positive count denotes left rotation while a negative count denotes right rotation. SHF is also a limited shifter used for scaling index values.

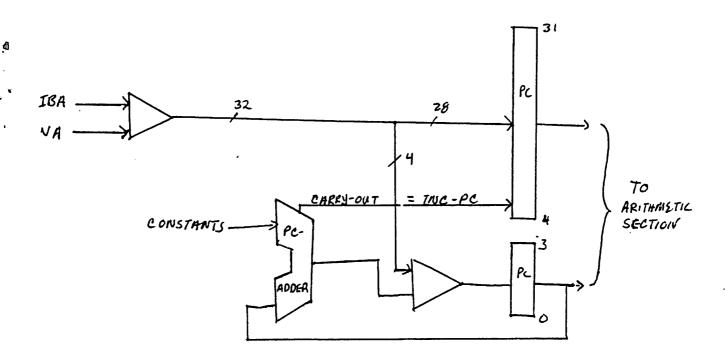

The memory address register VA, and instruction buffer address IBA, can be loaded from the ALU output; which of them is used as a memory reference address depends on the destination of the data—VA is used for data fetches (via register D) and IBA for program stream fetches (to the instruction buffer). Either of these registers may be loaded into the PC, which may be incremented using a dedicated adder, thereby avoiding use of the main ALU. In order to speed the handling of floating point quantities in machines without the optional floating point accelerator, an auxiliary, 10-bit ALU (called EALU) is provided. The major component in its data paths is the SC register, which is also used for shifting operations. Other registers associated with it are FE and STATE.

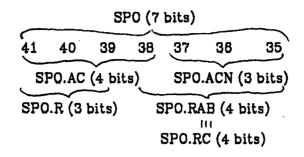

VAX microinstruction format. Control words are 96 bits wide, and divided into 30 fields (see Figure 2). Because of the great control word width, considerable parallelism is possible. Thirteen bits of each microinstruction are used to form the address of the successor instruction. When straight-line microcode is being executed, this address is used directly. But, when any conditional branches are taken (governed by the BEN microword field), other information is also used. BEN selects one of twenty-six groups of three, four, or five condition bits. For example, group "1A" is the PSL condition code bits: N, Z, V, & C. These conditions are ORed with the low-order bits of the microaddress field (JMP) to form the address of the successor microword. If the SUB field is one, a microsubroutine call is specified, and the address of the current microword is pushed onto a (sixteen deep) stack before the branch is taken. If the SUB field is a two, an address is popped off this stack, and is ORed with the instruction's JMP field, as well as any conditions specified, to form the next word address.

$\infty$

T, ~-

an - - -

with the state of

EALU | 13.12 V F S A E C IEK | MSC | K | K | CCK | EBMX | SMX | 31 30 29 26 25 24 23 22 20 19 18 17 16 A

D

| S | MCT/CID | FS | SPO | PCK |

47 46 43 42 41 35 34 32 63 | SI/ACM | QK | SGN | 58 57 55 54 51 50 48 DT |X | BEN |ACF | ALU |SUB | 79 78 77 76 72 71 70 69 66 65 64 95 92 91 88 87 85 84 82 81 80

Figure 2 - VAX microinstruction format

#### CHAPTER 3

# The YALLL Language

#### 1. YALLL Language Description

However widely computer macro-architectures vary, their supporting microarchitectures are remarkably similar. While macro-instructions may deal with control blocks, stacks, queues, and character strings, the microinstructions are concerned with registers, ALU functions, and transfers of data to and from memory. The YALLL microprogramming language deals with these same sorts of primatives: all arithmetic and logical operations are between registers, and the only accesses of main memory are via loads and stores. Statements are also provided for microprogram sequence control (conditional branch, subroutine call), and to control the binding of variables to registers. YALLL is thus very much like the assembly language for a machine such as the Data General Nova. One YALLL language statement is written on each line, with the exception of the jtab statement, which will be discussed later. The semicolon serves not as a statement separator, but as a comment escape; nothing written between the semicolon and the line's end affects the meaning of the program. A label and a colon may precede a statement, making it the possible destination of a jump. In the absence of branching statements, YALLL statements are executed in the order in which they appear in the source program (though they may not be loaded into control store in this order). Programs may not be self modifying, and there is no explicit means of accessing data in control store.

```

Syntax (diagram)

```

$$\left\{ egin{array}{l} {

m load} \\ {

m stor} \end{array}

ight\} \left[ {

m physical}

ight] \ reg. \left\{ egin{array}{l} {

m reg} \ [\pm \ cexp ] \\ {

m cexp} \end{array}

ight\}$$

$$\left\{ egin{array}{l} {f move} \\ {f cmpl} \end{array}

ight\} egin{array}{l} {m reg}, \left\{ egin{array}{l} {m reg} \\ {m cexp} \end{array}

ight\} \end{array}$$

$$\mathbf{jump} \left\{ \begin{array}{c} label \\ cexp \end{array} \right\} \left[ \mathbf{if} \left\{ \begin{array}{c} reg & relop \left\{ \begin{array}{c} reg \\ cexp \end{array} \right\} \\ reg & \left< cexp \right> relop & cexp \end{array} \right\} \right]$$

$$\mathbf{call} \left\{ \begin{matrix} label \\ cexp \end{matrix} \right\}$$

rtn

jtab reg [cexp:cexp] of

$$\begin{bmatrix} cexp \\ sel \end{bmatrix} \begin{bmatrix} \begin{bmatrix} cexp \\ sel \end{bmatrix} \end{bmatrix}^* : label \end{bmatrix}^+$$

[else label]

etab

pπa nigad dxao 310 dran amou reg name = reg algned  $\begin{bmatrix} \text{byte} \\ \text{word} \end{bmatrix} \begin{bmatrix} \text{byte} \\ \text{bongian} \end{bmatrix}$

$dxax \mp$ ( dxao ) | aurou | Laquinu =:: dxao

| %[0-7]<sup>+</sup> (octal number) (19-9) $^+$  (decimal number) =:: 13quinu

(redmun fsmicebsxad)  $X^{+}[\overline{4}-Ae-0][e-0]$

#[X10]<sup>+</sup> (X's in "don't care" positions)

=:: dojar (Tedmun vasnid) +[10]# |

1.2. Semantics

<> | = < | = > |

=:: 105

# 1.2.1. registers, types

mer the opportunity to specify types for his variables. The type indicates use the latter in a microprogram. This symbolic binding gives the programto designate transfer operands, or may bind symbolic names to them, and The YALLL programmer may use the machine's built-in register names

15

how many of a register's bits are to be considered significant and how conversions, if any, are to be done. The YALLL/VAX compiler does not support the type checking implied by strict typing, nor all the coercions implied by mixed type arithmetic. It is felt that, at this low a level, the former would be more of an encumbrance than an aid, and that the latter requires too much run-time overhead. In this implementation, the register type determines how much data is transferred on a memory access, and whether a quantity will be sign- or zero-extended or unchanged in the course of a move operation. A limited amount of type checking is done, so that one may add a short type into a longer operand, but not vice versa. Shift operations are also checked, to make sure the source of bits (not the shift count) is no larger than the destination. The only real typing problem occurs in the case of shifts; a byte circular shift, for example, is not what the term implies, but really a byte, extended into a longword, then rotated. The VAX rotation hardware actually only supports sixty-four-bit rotates, so that even a thirtytwo-bit arithmetic shift is not as efficient as one would hope. The section on VAX peculiarities gives more detailed information on registers, variable representation, and coercion action.

## 1.2.2. register transfer operations

Register transfer statements take three forms: memory access, register-register transfers, and three-register arithmetic. Memory accesses specify a source or destination register and a main memory address. This address is a constant, a register content, or the sum or difference of a register content and a constant. The amount of data transferred depends on the declared type of the target register. On the VAX, this defaults to a four-byte longword. A VAX memory reference is normally to virtual memory, since the

addresses passed from the macro-program are usually virtual addresses, and since the memory-mapping mechanism is quite easy for the microprogram to invoke. To avoid this address mapping the keyword **physical** should appear in the accessing statement.

A register-register transfer can be either a complement or a move. The source of data may be a register or a constant. Move is the only statement for which VAX microcode will be generated to do type conversion.

The three address register instructions provide most of the normal dyadic functions (addition, subtraction, logical and, or, exclusive-or), some shift operations (arithmetic left or right, logical left or right, circular longword left or right), as well as add1 and sub1. (The latter two compute  $dest \leftarrow src1 \pm src2 \pm 1$ , for implementing multiple-precision arithmetic.) On the VAX, a negative shift count does a shift of the same type (arithmetic, logical, circular) in the opposite direction to that specified.

By appending encc, for enable condition code, to one of these transfers, the machine's condition code bits may be set. On the VAX, only PSL bits N and Z are affected.

## 1.2.3. control operations

YALLL provides no code-structuring facilities such as compound statements or looping constructs; all of its control mechanisms are very simple: goto's, subroutine call, return, table jump, and exit. The unconditional goto is the jump statement, and takes a label or constant destination. A conditional jump is of the form "jump label if condition", where the condition is the comparison of a register's contents with those of another register, or

with a constant, or the test of a single bit. The subroutine call-return mechanism is simple and parameterless. The call statement causes the return address to be saved in a sixteen-deep stack, and the rtn causes the top address on this stack to be popped and used.

A more interesting construction is the jtab multi-way branch, where a field of a register is used to select one of several addresses as a jump destination. On the VAX, the width of the selecting field may be up to four bits. The mapping of integer field values to labels is given on the lines between the jtab and etab, the closing bracket. Each line is of the form of a comma separated list of values, a colon, then a label, which is the jump destination if the selected field takes on any of the corresponding values. Besides integers, the value list elements can be selectors, which have the form of binary numbers, but with X's in "don't care" positions. Thus "#XX1" is equivalent to the list "1, 3, 5, 7". The last line of the value-level map may be "else label", which specifies that for any values not specified on the preceding lines, control should transfer to the given label. If the else is not specified, and if the next executable statement.

The exit statement causes execution of the user's microcode to end, and macro-instruction fetching and interpretation to continue. If no argument is given, sequential instruction processing is assumed. If an address argument is given, it is used as a macro-program address, from which the next instruction is taken; the program counter, PC, is also loaded at this time. In VAX microcode, an exit without an argument causes the PC to be incremented by

<sup>&</sup>lt;sup>1</sup>On the VAX, arithmetic tests take into account the sign bit, so the result of comparisons of long unsigned quantities may be wrong. For example, unsigned FFFFFFFF (hex) > 0, but taking the sign into account gives the opposite result.

one, and the current op-code to be discarded.

#### 1.2.4. other pseudo-ops

In addition to the register name equating statements described earlier, YALLL provides a handfull of pseudo-ops to ease symbolic microprogramming. The equ statement serves to equate a name with a constant expression. The expression may include numbers and previously defined constant names; it should not include register names, nor labels (on the VAX, these are not given address values until after all code generation). The org statement allows one to assign an address to the beginning of the code generated by the following YALLL statement. This is often necessary for linking to a machine's native microcode, which generally jumps to a fixed location to enter the user's code.

The begin and end pseudos provide a means for controlling the scope of variable and constant names. These symbols obey the usual block-structure visibility rules under control of begin and end. Labels, however, are global. This means that the same register may be used with different names and types in separate (non-nested) parts of the program. (Recall, though, that a routine call and return from one area to another using the same registers does not cause the saving or restoring of them.) An end statement also denotes the end of the program text, and must be the last statement in it. End causes no code to be generated, and should not be confused with exit.

#### 1.3. VAX Peculiarities

Throughout this language description, I have tried to indicate which features are machine-dependent and, by implication, which are not. The most implementation-dependent features of YALLL/VAX are described in this

section. These peculiarities fall into four groups: representation of short types and conversions; register names; control store addresses; and an assembler escape.

#### 1.3.1. representation

In the VAX, all registers are thirty-two bit longwords. Words and bytes are sixteen and eight bits, respectively. In code produced by YALLL, all register quantities are represented as longwords, for the following reasons: The general, macro-program visible registers have the capability of storing partial register quantities, leaving the upper bits unchanged. However, none of the other registers in the CPU share this ability, so that, in order to avoid propagating garbage when doing operations between register types, one would have to mask or sign-extend quantities coming from the general registers. In order to avoid this overhead, YALLL/VAX always writes full-register results into them. No run-time bounds checking is ever done. So, for byte register x:

move x,255 add1 x,x,255

will cause x to contain 511, even though this quantity cannot be stored in a byte.

Sign "extension" is done, strangely enough, when moving a long quantity into a shorter quantity. Since all variables are represented in longwords, it is not necessary to change representation when moving from short to long. But going the other direction, long quantities are truncated, and sign or zero filled, to assure that the type of the receiving variable is not violated by the transfer. The type conversion for all combinations of source and destination types are shown in Figure 3. (These actions are coded into a table in the

translator, and may easily be changed by recompiling it.)

## 1.3.2. register names

The register names currently available to the YALLL/VAX programmer are shown in Figure 4, along with the location of their associated physical registers. These names are entered into the symbol table upon initialization of the translator. They all have default types of unsigned long, and are unreserved. ID bus registers are more expensive to access than are other registers, and some are read-only (see Appendix A).

The OPERAND register is the specifier byte of the instruction buffer; this is treated as a pseudo-register. Each time it is read, the byte is cleared, PC incremented, and the next instruction-stream byte shifted into place. The programmer should not, therefore, modify the PC to account for the macroinstruction argument(s).

| Source | Destination  |              |              |          |              |    |

|--------|--------------|--------------|--------------|----------|--------------|----|

| Source | ul           | sl           | นพ           | sw       | ub           | sb |

| ul     | <b>V</b>     |              | 0            | 0        | 0            | 0  |

| sl     | $\checkmark$ | $\checkmark$ | 0            | ±        | 0            | ±  |

| uw     | 1            | $\checkmark$ | <b>\</b>     | V        | 0            | 0  |

| SW     | V            | <b>V</b>     | <b>\</b>     | <b>V</b> | 0            | ±  |

| ub     | <b>V</b>     | <b>\</b>     |              |          | <b>√</b>     |    |

| sb     | <b>V</b>     | $\checkmark$ | $\checkmark$ | ✓        | $\checkmark$ |    |

#### where

ul - unsigned longword

√ - no change

sl - signed longword

0 - truncated and zero-filled

uw - unsigned word

± - truncated and sign-filled

sw - signed word

ub - unsigned byte

ab signed bads

sb - signed byte

Figure 3 - Coercion Actions

| Register    | Location | Regiser<br>name | Location     |

|-------------|----------|-----------------|--------------|

| rO          | RAB      | Dreg            | D            |

| ri          | RAB      | Qreg            | Q            |

| r2          | RAB      | VA              | ٧A           |

| r3          | RAB      | SC              | SC           |

| r4          | RAB      | PC              | PC           |

| r5          | RAB      | OPERAND         | $\mathbf{m}$ |

| r6          | RAB      | DAYTIME         | ${f I\!D}$   |

| <b>r</b> 7  | RAB      | RXCS            | ID           |

| r8          | RAB      | RXDB            | $\mathbf{m}$ |

| r9          | RAB      | TXCS            | ID           |

| r10         | RAB      | TXDB            | ID           |

| <b>r</b> 11 | RAB      | POBR            | 110          |

| r12         | RAB      | PIBR            | ID           |

| <b>r</b> 13 | RAB      | SBR             | ID           |

| r14         | RAB      | KSP             | ID           |

| r15         | RAB      | ESP             | ₽            |

| ŧ0          | RC       | SSP             | ID           |

| t1          | RC       | USP             | <u>1D</u>    |

| t2          | RC       | ISP             | ID           |

| t3          | RC       | PCBB            | ID           |

| t4          | RC       | SCBB            | 110          |

| t5          | RC       | POLR            | ID           |

| tB          | RC       | P1BR            | ID           |

| t7          | RC       | SLR             | ${f ID}$     |

Figure 4 - YALLL/VAX Registers

### 1.3.3. addresses

The areas of control store designated for user microprogramming are locations 10E0, and 1400-1800 hex. These are the only addresses the translator will attempt to bind to a microinstruction, and are the only addresses which should appear in org statements.

# 1.3.4. assembler escape

The YALLL language is not designed to allow one to use all the machine's resources, but only to make the writing of microprograms a reasonable task. Therefore, one might want to embed segments of microassembly language code in a YALLL program, either because the code emitted by the translator is unsatisfactory, or because there is no way of dealing with VAX-specific

mechanisms (such as interlock read/write, or the accelerator). To make this possible, one can write VAX microassembly statements between asm... msa brackets. The primary restriction on such statements is that one may not use DEC's macro definitions. (One may, however, write one's own macros and use the C compiler's pre-processor to expand them.) The form of an assembly-language statement is:

[label:]\* [const:] field-id/field-value [, field-id/field-value]\*

where the constant binds this word to a specific control store address, and field-value is either a compile-time constant, or a label (in the case of the J field). Assembly-language statements may be broken over several lines, so long as there is at least one field – value pair, with a trailing comma, on each line.

Finally, each address restricter, for constructing jump tables and subroutine linkages, takes the form =[01X]<sup>+</sup> and must be matched by a closing

bracket =end. For example, to jump to location "A" if the middle sixteen

bits of register r3 are zero, else location "B", code:

#### 2. VAX-11/780 MICRO-PROGRAMMING SYSTEM

Creating a microprogram for the VAX is a process of several steps, involving various software tools. The primary tools are an editor, the YALLL

ą '

compiler, and the console-resident microdebugger. In this section I shall describe the user's interaction with most of these, and detail the choices offered by them.

The excellent editors (ex and vi) available on CS VAX/UNIX are written by Bill Joy [Joy 77b], and should need no introduction to anyone familiar with the system. One of these editors should be used in preparing the YALLL source file. The next step is to have this file compiled.

#### 2.1. The YALLL Translator

The translator is a large 'C' program called yc. It will take an input file, and produce a binary output file. It will not produce a source code listing, but will dump the intermediate code at various points in the processing. Although the translator is actually a single program phase, it conceptually has three passes: the first reads the source, parses it, and generates intermediate code; the second does peephole code improvement; and the third assigns addresses to each microinstruction, and writes the binary file. The translator command line is:

yc inputfile [-d[1][2][3]][-2] [-o filename]

where the order of parameters is not significant, except that they are scanned from left to right. The inputfile is the source file, produced by an editing session. It is conventional to use filenames ending in ".m" (as in "source.m") for microprogram sources. If no filename is given, standard input is read until a fatal error or end-of-file (control-d).

The -d options specify that a dump of the intermediate code is to be produced after the specified pass(es) of the translator. This is a humanreadable representation of the binary being produced, and is written on the standard output file. The reading of dumps will be fully explained in a later section. The flag -2 specifies that the second compiler pass, code improvement, is to be suppressed. This should only be done if you feel that the microcode produced by the compiler is incorrect because of "improvements" made in the second pass. Note that microprogram segments entered in assembler-escape mode will not be touched by the code improver in any case.

Finally, the -o parameter governs the binary produced by yc. If this is -o -, no binary file is written. Otherwise, the following word of the command line is taken as a filename, and output is written in it. If no output disposition is specified, a binary file is written in file m.out.

#### 2.2. Macro Processing

The assembly escape provided in the YALLL translator permits the microprogrammer full access to the microarchitecture, including functions not employed by programs written in the YALLL language. However, assembly language programming using this facility is not as easy as programming with DEC's macro assembler. This task may be made easier by the use of the C pre-processor.

The C preprocessor allows one to define one-line macros, with or without parameters. A parameterless macro (such as a constant) is defined by:

#define name string

And a macro with parameters as:

#define name(parameter list) string

For example:

```

#define alu_q ALU/OF, AMX/1, RMX/1

#define R1 1

#define rab_alu(x) SHF/0, SP0/50X + x

asm

rab_alu(R1), alu_q

msa

```

To use the preprocessor to do macro expansions in a source file z, then translate the result using yc, the command is:

cc -E z 'ye options

One problem with this system is that it does not permit context-dependent constant names, as DEC's assembler does. Thus, defining "#define RAMX 1", so that one may write "AMX/RAMX" will only cause trouble when 1 is substituted for the field name in "RAMX/0", or the like. One should also avoid YALLL keywords and pre-defined registers names.

Rather than writing macro definitions in each microprogram source file, one may collect them in a file (or files), which the preprocessor will read as input upon encountering a line of the form

# #include "filename"

in its input. Note that the quotation marks are mandatory. The preprocessor does not pass the include directive to its standard output, but does insert several lines of its own. These are ignored by yc, but may throw off line numbers reported in error messages. The C preprocessor will read multiple files, providing an alternate method of including a macro collection. To read and macro process files x and y, then feed them to yc, the command line is:  $\frac{1}{2} (x + y) + \frac{1}{2} (x + y) + \frac{$

#### 2.3. Symbol Table and Code Dumps

At several points in the translation process, ye can be persuaded to dump some of its internal tables in human readable form. These are primarily intended for maintenance of the translator, but may also be useful to the programmer, as will be outlined.

A symbol table dump may be obtained at any point during the scan of the source program by the inclusion of a comment beginning; %. This dump may appear before any semantic action for that line has taken place. The dump has three parts: the histogram, local symbols, and global labels. The histogram gives an indication of hash table usage, and indicates, for each of the 256 table entries which is not empty, how many symbol names hashed to that entry. This statistic includes pre-defined symbols, such as register and field names, which do not appear elsewhere in this dump.

The local symbols are those visible at the point of the dump, according to the normal begin . . . end nesting rules. Global labels are program labels which were defined or first used within a block not including the point of the dump. The dump of each symbol entry gives: the number of characters in the symbol's name; the name; the line number where it was defined (if defined) or first used; the pseudo-line number on which it was first defined or used; its type (error or undefined; register; constant; label; and field name, which are for pre-defined symbols only, and should not appear in a dump); and its value, if defined. For labels, the value is a relative address in brackets. For registers, the value is an index into the compiler's register table. The pseudo-line number is the value kept in a variable set by the PS number pseudo-op. If a high-level language translator were to emit YALLL, a PS pseudo would mark the beginning of the code for each HLL statement, so

that the source of errors in the YALLL program would be traceable to a HLL statement.

At the end of the dump, one of the messages "open action pending" or "close action pending" may appear. The former indicates that the symbol begin has been scanned but not processed; the latter that end has been scanned but not processed. These should only appear when one writes, for example "end;", and may change the meaning of the dump. A symbol table dump may also occur spontaneously, as a result of certain kinds of internal translator errors. An error message will accompany such a dump.

A code dump may be obtained at the completion of any of the translator's three passes as indicated by the -d command line argument. The dump after the third pass gives the most information, as it shows the result of pass two code improvement, as well as address assignment. However, the relationship of YALLL source to assembly-like dump is hardest to see at this point. This relationship is much better shown by the pass one dump, which might be used as an aid to understanding the final code.

The dump exhibits several of the fields of each of the data structures representing a word of generated code. Each micro-node, as these are called, is represented by four attributes: address, field values, branch information, and uses-sets information. The address is given as a "relative" address, in brackets, optionally followed by an absolute address (in parentheses), or constrained address, preceded by an equals sign (=). In pass one and two dumps, absolute locations are the result of org statements, and constrained locations of conditional or table branches, or subroutine calls. By the end of pass three, all locations should be given absolute addresses. Relative addresses are decimal, absolute are hexadecimal, and

constraints binary. It is impossible for a location to have both constrained and absolute addresses.

The body of a microinstruction, its field values, is given in approximately the format accepted by the assembler: fieldname-slash-hex-value. Note, however, that the value given for the CID field is only that of the four bits not overlapping fields ADS nor FS. Fields not explicitly set during code generation, and thus taking their default values, are not shown. As an example, the pass one dump of the code generated by  $\mathbf{x}$ :  $\mathbf{jump} \mathbf{x}$  if  $\mathbf{r0} = \mathbf{t0}$  is shown in Figure 5.

#### CODE DUMP

SETS:

code size = 5 words

```

[0]:

SPO/20, QK/8, ALU/e, BMX/4,

J/[1]

USES: LatchC RegC

SETS: Qreg LatchC

[1]:

CCK/1, SPO/40, ALU/8, RMX/0, AMX/0, BMX/7,

J/[2]

USES: Qreg LatchAB RegAB

SETS: LatchAB CondCode

[2]:

BEN/1b,

J/[3], 2-way branch

USES: CondCode

SETS:

[3]:=1011:

J/[5]

USES:

SETS:

[4]:=1111:

J/[0]

USES:

```

Figure 5 - Code Dump

The jump address of each microinstruction is determined by the settings of the SUB, BEN, and J fields. The former two are shown with the other microword fields. The J field is given last, and indicates either a [relative] or (absolute) addresses. By the end of pass three, all jumps, like all addresses, should be absolute; if a relative jump appears in a third pass dump, a label reference did not get resolved, and a run-time error will occur. For a multiway branch (BEN not zero), an indication is given of the number of possible destination addresses for the jump.

For the purpose of pass two code improvement, the generation routines store in the micro-nodes not only the appropriate field values, but also the names of the resources (registers and latches) which are being manipulated by the microinstruction under construction. This appears on the two lines of uses-sets information of the dump of the micro-node. A resource is used if its value is used in a calculation, and set if a new value is clocked into it. The words EXCLUSIVE\_USE appear when a microinstruction should not be combined with those around it. This is the case when the assembly escape has been used, or when the generated code is sufficiently tricky that any attempt at code improvement might change its meaning. A micro-node represented by only the relative address and an "X" is one which has been deemed unnecessary by the code improver. These may be considered to have been deleted, as they are not assigned addresses, nor written on the outpu: file.

#### 2.4. Other VAX Microcoding Utilities

The binary file produced by ye is not ready to be loaded into WCS, but must first be linked with other routines to be loaded there. The output of ye contains no explicit address information; the first twelve bytes belong at control store location 10EO, and the following twelve-byte words are to be loaded

beginning at 1400 hex. The LSI-11-resident WCS loader can only load into sequential locations, and (because of the floppy disk file format), only in multiples of 512 bytes. Also, the console resident debugger requires a floppy disk resident image of WCS (see section 2.6). Thus it is desirable to make a single file containing the entire WCS image: both native and user-written microcode. The native microcode can be found in a floppy disk file, currently WCS118.PAT. This may be copied to a Unix file using arff, the floppy file utility. The program merger may be used to combine a Unix file copy of the native microcode (the "system file") with yc output ("user file") into a combined file ("target file"). The merger program will prompt the user for the appropriate file names.

To verify the performance of yc and merger, two versions of a dump utility are available, to interpret binary microcode files. The program undo will dump a named file (default m.out) in microassembler-like format. This file is assumed to be the output of yc. The dump format is the same as that of a translator code dump, except that: all fields are shown, as the filed use information has been lost; resource uses-sets information has, similarly, been lost; words are given in increasing order of address, which may have little to do with logical order. Similarly, interdump will verify a merger operation by dumping, in the same format as undo, requested addresses of the file named in the command line. Since the merged WCS image contains at least a thousand words, dumping the whole file would be impractical, thus it is done interactively.

Under the system described here, all WCS files are loaded by the console LOAD/WCS command. Thus, these files must be written on the floppy disk, in the format understood by the LSI-11 operation system. Two VAX programs

make this possible: The floppy disk device driver is part of the Unix kernel, and deals with transferring sectors (of 128 bytes) to and from the floppy. However, this program knows nothing of the disk format other than the sector size, and treats it as one long, sequential file. Thus it should not be used alone; a command such as "cat /dev/floppy" is almost certainly wrong.

The program arff, written by Keith Sklower, deals properly with the disk format and uses the Unix floppy driver to request the data transfers of the LSI-11 program (which actually deals with the device). Arff is meant to appear to the user like the program tar, and is invoked as

arff actioncode [filename...]

where actioncode is one of the following:

- t list which of the named files are listed in the floppy directory. If no filename arguments are given, the name of each file on the floppy is printed.

- tv like t, but more information is given with each listing, such as creation date, and size off the file, in blocks. Also, the number of directory entries remaining is printed, and, if listing the whole directory, the size of unused areas.

- x extract named file from floppy to Unix file. If the file name is a path name (with slashes), the last portion is taken to be the floppy file, and the entire qualified name is the Unix file.

- r replace (or add) floppy file from named Unix file. Qualified file names are interpreted as for x. If the named Unix file is larger than an existing floppy file of the same name, it may be necessary to first delete the floppy file, forcing an add action, rather than a replace. If the directory is full, or the whole floppy disk is full, an error message will be written.

**d** - delete named files from floppy directory.

For example, to repack the floppy, combining several small unused areas into a larger unused area, we could extract the entire contents, delete it all, then replace each file as follows:

% set fl='arff t' C- shell variable \$fl

% arff x \$fl

% arff d \$fl

% arff r \$fl

Floppy disk file names have up to six characters, optionally followed by an extension (qualifier) of up to three characters; e.g. WCS118.PAT, WCSMON.HLP. Furthermore, they must be composed only from the Radix-50 character set: A-Z, 0-9, \$, %, and period (.). The latter character should be avoided, since it is also the separator between name and extension. Arff does case translation, so that all letters appear to be in lower case. WCS image files should have names of the form WCSnnn.PAT, since there seems to be some restriction on the names of these files, and this formula seems to work.

#### 2.5. Dealing With UNIX

In order to load and debug microprograms on the VAX, it is necessary to stop timesharing, halt the machine, and either run stand-alone, or use Unix as a single user. Here we will outline some of the important Unix commands necessary for failure-free operation. It is assumed that you have arranged with the system manager to halt timesharing, and that you have a Unix account, though not necessarily root.

To increase disk through-put, Unix employs file read-ahead and writebehind. Because of this, if the system goes down unexpectedly, grave filesystem inconsistencies may result. The **sync** command causes all disk files to be brought up-to-date, by writing out buffers-full of data destined for writing. This command should be used whenever the system might stop, as when you are about to halt the machine, or test new or shaky microcode under Unix. See the Unix Programmer's Manual, sync (1 & 2), and update (8) for details. Unix is brought up from a halted machine using the console command B or QUNIX in response to the >>> prompt. This causes console commands to be executed from the floppy disk file UNIX. Finally, a VAX boot program is read from the hard disk, and will prompt file:, after which type unix, or whatever the appropriate name is for the system being run. This will be loaded, report on the available memory, and prompt with #. If a control-d is typed to this prompt, commands will be taken from the file /etc/rc, which will bring up timesharing. Therefore, don't type gratuitous control-d's!

Before bringing up timesharing, you should always check the integrity of the file system. This is done with the chk command (which in turn executes dcheck and icheck, see section one of the Unix Programmer's Manual): chk /dev/rrp0a /dev/rrp0g is the least you should do. This takes about fifteen minutes, and will report on any inconsistencies it finds. If dcheck reports a file having more entries than links, the system manager should be notified to fix this situation before you go any further. If you did sync's before taking the system down, there should be no problems.

If you don't wish to bring up the full system, but want to access files in your directory, it will be necessary to mount the /usr file structure with

# /etc/mount /dev/rp0g /usr

The easiest thing to do at this point is to use the **login** name command to give you your own home directory, shell, and identity. An alternate possibility, which retains the *root* user identity, is the following:

The problem with this is that any files you create in your directory belong not to you, but to root.

#### 2.6. At the Console

Loading and debugging microprograms from the VAX consol requires using DEC-supplied, LSI-11-resident console software. These programs are quite adequate for most of the simple tasks necessary for debugging a microprogram.

The console command interpreter takes the place of front panel lights and switches on the VAX. When the console is in "program I/O mode" (communicating with a VAX program, as when waiting for a login), it may be switched to console command mode by typing a control-p. The console prompt is >>>, character erase is del or rubout, line kill is control-u, program kill is control-c. The command SET TERMINAL PROGRAM is the inverse of the control-p command - it returns the console to program I/O mode. A HALT command stops VAX CPU instruction interpretation, and puts the microcode in a console-command servicing loop. The microcode's cooperation is necessary, for example, to manipulate main store locations from the console. The CONTINUE command restarts VAX instruction execution where it left off, and START address first sets PC to address, then starts instruction execution. Many other commands are available, and are outlined in the console floppy file CONSOL.HLP. This may be typed at the console by the command @CONSOL.HLP, or transferred to a Unix file with arff and listed; see also Figure 6a.

```

VIRTUAL EXAMINES AND DEPOSITS.

TO EFFECTIVE ADDRESS OF PHYSICAL AND

REGISTER, RELOCATION REGISTER IS ADDED

REGIZIER BETOCVION SEGIZIER IS ADDED

REL CHOCK NORMER, -SET CPU CLOCK FREQ TO NORMER

REL CHOCK FAST -SET CPU CLOCK FREQ TO FROM SET SOWN -SET SOWN -SET SOWN SET

GCTEAR STEP.

-DOES A QUAD WORD BOUNDARY(CLEARS ECC ERRORS)

-TO A QUAD CLEAR TO ADDRESS, WHICH IS FORCED

STEP DEPENDS ON LAST SET STEP. COMMAND

-TO A QUAD CLEAR TO ADDRESS, WHICH IS FORCED

TO A QUAD WORD

TO A QUAD WOR

CIEVE ZLES.

-ENVBIE ROUGH ON ZLES) WODE

-ENVBIE ZINGIE INZLENCLION WODE

-ENVBIE ZINGIE LIWE ZLALE CTOCK WODE

-TOVDE WICKO-DIVENOZLICZ'VANELZ COMWANDE

-ENDBE WICKO-DIVENOZLICZ'VANELZ COMWANDE

-ENDBE ZINGIE VAND CONZOITE

-ENDBE ZLALE CONZOITE VAND CENT ZLALE

-ENDBE ZINGIE

-ENDBE ZLALE

-ENDBE ZLALE CTOCK WODE

-ENDBE ZINGIE LIVEN ZLALE

-ENDBE ZLALE

-HALTS THE 1SP

TLAH.

CONTINUE

-IZZNEZ V CONTINUE TO THE ISP.

TO THE PC, ISSUES A CONTINUE TO THE ISP.

**EXAMINE IR**

-EXAMINE IR**

-EXAMINES IR**

-EXAMINES IR**

-INITIALIZES THE CPU, DEPOSITS < ADDRESS > -INITIALIZES THE CPU, DEPOSITS < ADDRESS > -INITIALIZES THE CPU, DEPOSITS TO THE T

UNIQUE COMMAND STRING IS: 'E/V 10245'(SEE ABBREV.HLP)

EXAMPLE: TO EXAMINE VIRTUAL ADDRESS 10245, THE SHORTEST

VAB. LOK ABOS KECISLEKS

V. LOK CENEKYT KECISLEKS

VI. LOK INLEKNYT(PROCESSOR) RECISLEKS

·EV/

'\varphi' FOR VIRTUAL MEMORY(THE DEFAULT)

ALL COMMANDS ARE TERMINATED BY CARRIAGE RETURN

THE PROPER ADDRESS SPACE TO USE:

THE PROPER AFTER THE COMMAND NAME TO SPECIFY

THE PROPER AFTER THE COMMAND NAME TO SPECIFY

THE PROPER AFTER THE COMMAND NAME TO SPECIFY

THE PROPER ADDRESS SPACE TO USE:

THE PROPER ADDRESS SPACE TO USE:

OVERRIDE. (%O FOR OCTAL, %X FOR HEX)

OR STRING OF DIGITS PREFIXED WITH A DEFAULT RADIX.

(IAST ADDRESS)

VAX-11/780 CONSOLE HELP FILE REV. 6 S6-JUL-1978

**ORMANDS**

**ORMAND

...

```

'SET DEFAULT <OPTIONS, ..., <OPTIONS' ARE: OR OCTAL, HEX, PHYSICAL, VIRTUAL, INTERNAL -SET CONSOLE DEFAULTS

TO THE TERMINAL AFTER <CR> OR <LF>. SET FILL COUNT FOR # OF BLANKS WRITTEN SET TERMINAL FILL: <NUMBER> GENERAL, VBUS, IDBUS, BYTE, WORD, LONG, QUAD

-PUT CONSOLE TITY INTO 'CONSOLE I/O' MODE ·~P·(CONTROLP) SET TERMINAL PROGRAM. -PUT CONSOLE TTY INTO 'PROGRAM I/O' MODE

(UNLESS MODE SWITCH IN 'DISABLE')

-PROCESS AN INDIRECT COMMAND FILE .**©**<LITENAME>. -PRINTS THIS FILE HELD

.FOVD\ACS <LITENVME>. -LOAD FILE TO MAIN MEMORY. .FOYD <FITENAME>

THE 'START: ADDRESS' QUALIFIER MAY ALSO BE USED TO MOLE -POVD LIFE SECRETED TO WCS

AIT BECILA LHE SLYKLING VDDKESS LOK V FOVD' OLHEKAISE FOVD

COMMANDS TYPED BY USER WHILE LINKING ARE STORED PRINTS REVERSED PROMPT TO INDICATE LINKING. ALL -CAUSES CONSOLE TO BEGIN COMMAND LINKING. CONSOLE TINK.

CONTROL-C TERMINATES LINKING. (SEE PERFORM) IN AN INDIRECT COMMAND FILE FOR LATER EXECUTION.

PERFORM

HEBERT SANT-CONSOLE-COMMANDS - CAUSES THE CONSOLE TO REPEATEDLY EXECUTE

CENERATED VIA A LINK COMMAND.

CENERATED VIA A LINK COMMAND.

THE COMMANDS FREVIOUSLY

THE COMMANDS PRÉVIOUSLY

THE COMMANDS

сутта міско-ревлесев. (гок ревлесев негь. ACZ. THE <CONSOLE-COMMAND>, UNTIL STOPPED BY A ~C

-ENABLES CONSOLE SOFTWARE TO ACCESS FLOPPY DRIVE ENABLE DXI: LLLE , @MCZWON'HIE,)

CAUSES A CONSOLE SOFTWARE RELOAD

1 ON THOSE SYSTEMS WITH DUAL FLOPPIES.

TCOGEAN!

-WHEN EXECUTED FROM AN INDIRECT COMMAND FILE, THIS WAIT DONE

COMMAND WILL CAUSE COMMAND FILE EXECUTION TO STOP

EXECUTION WILL CONTINUE), OR B) THE VAX-11/780 PROGRAM RUNNING IN THE VAX-11/780(COMMAND FILE UNTIL: A) A 'DONE' SIGNAL IS RECEIVED FROM THE

ECUTION WILL TERMINATE). HALTS, OR OPERATOR TYPES A ~C(COMMAND FILE EX-

# Figure 6a - Console Command Summary

load a WCS image file and invoke the microdebugger. Loading is accom-The commands directly relating to microprogramming are those that

## >>> LUAD/WCS/START: 1000 filename

plished by the command

disk-resident image of control store which it can inspect, if it is used to in, but not read from. Thus, the WCS microdebugger requires that there be a processor, writable control store is a write-only medium - it can be written file WCSMON.HLP is shown in Figure 6b. From the point of view of the console debugger is called by WCS, and prompts WCS>. Its command summary, from where the START option indicates the lowest address of the load. The

CURRENTLY LOADED IN THE WCS PORTION OF THE CONTROL STORE. NOLE: OBEN. 12 NRED 10 RECIEA V LITE CONTAINE THE MICRO-CODE DXI-(FILENAME). -OPEN RECIFIED FILE ON FLOPPY DRIVE 1 ODEN DXI:<br/>CHENAME>, -OPEN SPECIFIED FILE ON FLOPPY DRIVE O<br/>TOPEN SPECIFIED FILE ON FLOPPY DRIVE O

-RETURN TO THE CONSOLE PROGRAM

RETURN.

-DISVBITE SINCITE WICKO-INSLIGNCLION SLEE WODE:

CLEAR STEP

місво-зеблеисев:

DISTRUCTION TO EXECUTE, THEN HALT THE MICRO--ENVEIT SINCIE WICKO-INSTRUCTION STEP MODE.

REL SLES

-CIEVE THE STOP ON MICRO-MATCH! ENABLE -SET THE 'STOP ON MICRO-MATCH' ENABLE

CLEAR SOMM .ZEL ZOWM.

-HALT THE MICRO-SEQUENCER

TAAH'

-START MURO-SEQUENCER AT <ADDRESS>

.<ZYART <ADDRESS>

SPECIFIED BY CONTENTS OF MICRO-PC(UPC) -RESUME MICRO-INSTRUCTION EXECUTION AS

CONTINUE

NOIE: DEPOSITS TO THE RLOG STACK(RL) ARE NOT SUPPORTED.

'D <SYMBOLIC-NAME> <DATA> '-DEPOSIT <DATA> TO ONE OF THE SYMBOLICALLY

D BC <ADDRESS> <DATA>' -DEPOSIT <DATA> TO AN RC REGISTER

'D RC <ADDRESS> <DATA>' -DEPOSIT <DATA> TO AN RC REGISTER

LEIDS TO BE CLEARED.

NOTE: THE '/Z' QUALIFIER MAY BE USED TO CAUSE ALL UNSPECIFIED

ARE UNCHANGED.

INTO <FIELDNAME-1>, ETC. UNSPECIFIED FIELDS 'D <ADDRESS> <FIELDNAME-1> <DATA-1>,<FIELDNAME-2> <DATA-2>,.......-1>

'D <ADDRESS> <FIELDNAME-1> <DATA-1>,

-DEPOSIT TO WCS LOCATION, PUTTING <DATA-1>

NOTE: <SYMBOLIC-NAMES> = DR, FER, IBA, LA, LB, LC, Q, RL, SC, SR, UPC KECIZLEKS

-EXAMINE ONE OF THE SYMBOLICALLY NAMED

E < ZXMBOTIC-NAME>.

E RC <ADDRESS>

-EXAMINE AN RC REGISTER -EXAMINE AN RC REGISTER

E KY <ADDRESS>

RMX, SCK, SGN, SHF, SI, SMX, SPO, USU, VAK EBM, FEK, FS, IBC, IEK, UJM, KMX, MCT, MSC, PCK, QK

NOTE: <FIELDNAMES> = ACF.ACM.ADS.ALU.BEN.BMX,CCK,CID.DK,DT,EAL

THE FIELDS SPECIFIED.

E <PDDRESS> <FIELDNAME-1>,<FIELDNAME-N>

EXAMINE WCS LOCATION, DISPLAY ONLY FIELDS

-EXAMINE WCS LOCATION, DISPLAY ALL FIELDS

E <ADDRESS>

E/ID <PDDEESS: -EXPMINE ID BOS RECISLER

E\D <PDEESS: -EXPMINE BHASICPT MEMORA

DEBUGGER COMMANDS(ALL TERMINATED BY CARRIAGE RETURN)

TO STOP PRINTING, TYPE ~C MICKO-DEBUGGER HELP FILE

REV-0 MAY 1977

(ADDRESSES 1000(16) & UP IN THE CONTROL STORE) THIS FILE WILL BE USED FOR ALL EXAMINES OF THE WCS, SINCE THE WCS IS NOT DIRECTLY READABLE.

Figure 6b - WCS Debugger Command Summary

examine and patch microcode. (This is another reason for building a microcode image on the floppy, rather than going the shorter route of loading control store directly from the VAX.) The WCS command OPEN filename permits the debugger to use the named file, which it assumes has already been loaded, as shown previously. Modifying control store using the D command changes both the control store contents and the disk file. The format for examining and changing microstore locations is similar to the dump and assembly formats, except that field name is separated from value by a space for setting values and an equals sign for examining them (rather than a slash): CID overlaps FS and is only four bits, and MCT overlaps FS but not ADS.

A HALT to WCS will stop *microinstruction* execution, and is necessary before depositing in control store or registers.

A very useful feature for debugging is the ability to set a break point in the microprogram. The break point may be set either in console command mode or when running the microdebugger, by placing the break address in the micro-break ID register (21), then enabling the facility by the command SET SOMM. When the given location has been executed, the microprogram will halt, and a message will be printed. When you are done using this facility, it must be disabled by the command CLEAR SOMM. See the tutorial example for a use of the break point.

### 2.7. A Tutorial Example

This section gives a step-by-step example of the microprogram entry process, including use of the translator, loader, and console microdebugger. The example program will be a simple emulator, shown in Figure 7a. (This is very similar to the CS-152a and CS-292R SM-1 example for the HP 21-MXE computer.)

The simple computer emulated has an accumulator (AC), MAR, MBR, and PC, and 1024 words of (16-bit) memory. RAB register r0 will be used for AC, r1 for MAR, r2 for MBR, r3 for PC, and r4 will point to the area of memory to be used as the emulated memory. After these registers are loaded with the appropriate initial values, the microprogram is called by the XFC instruction; in assembler this is coded as ".byte Oxfc". When the program is done, it will return its values in the same registers and in memory. The emulation will use word addressing, and will interpret eight instructions. This source program should be typed into a file, call it sm1.m, using a Unix text editor.

2.7.1. translating the program Once the source is correctly entered, it should be translated using yc. To get an idea of the code produced, try

yc sm1.m -d13 | lpr

The pass one dump should be pretty easy to partition into the groups of instructions produced by each source statement. The pass three dump is much more convoluted. This, though, is the appropriate listing for debugging at the console.

Once the program has been translated, it must be combined with the native microcode to produce a new WCS image file, to be written on the floppy disk. If a copy of the native code is not available as a Unix file, one

#### Emulator for the SM1

**Ifetch**

jump

This program emulates a computer having eight instructions plus halt. It uses VAX general registers r0 - r3 as the emulated AC, MAR, MBR, and PC, and register r4 to point to the 1k word emulated memory in VAX memory. The XFC instruction takes no parameters except in registers; initial values for AC, PC, and the memory space pointer.

```

initial values for AC, PC, and the memory space pointer.

org

10E0

AC = r0 signed word

reg

reg

MAR = r1 unsigned word

reg

MBR = r2 signed word

PC = r3 unsigned word

reg

reg

base = r4 unsigned long

temp = Qreg

reg

Ifetch:

all

temp,PC,1; byte-to-word address factor

add

VA, temp, base

MBR, VA; MBR <- mem[base+PC]

load

:defer incrementing PC till end of execution cycle

MAR, MBR, 3FF ; extract address from instruction

; now do case jump on op-code

jtab MBR<15:12> of

0:Cmpl

1:Shr

2:Bneg

3:Jmp

4:Store

5:Load

6:And

7:Add

else Halt

etab

Halt:

add

PC,PC,1

exit

Cmpl:

AC,AC ; complement instruction

empl

jump

Inc_pc

Shr:

; shift right one bit instruction

AC,AC,1

ar l

jump

Inc_pc

Bneg:

; branch if (AC)<0

jump

Inc_pc if AC >=0

Jmp:

; unconditional branch

PC, MAR

move

```

Store:

all

; store instruction

temp, MAR, 1; word-to-byte address factor

add VA,temp,base stor AC,VA jump Inc\_pc

Load:

;Load instruction

call Fetch\_mem move AC, MBR jump Inc\_pc

And:

:Logical AND instruction

call Fetch\_mem and AC,AC, MBR jump Inc\_pc

Add:

; Addition instruction

call Fetch\_mem add AC,AC, MBR

Inc.pc:

add

PC.PC.1

jump Ifetch; its only safe to increment PC after all fetches; for this instruction are over, so a memory fault (page absent); won't cause us to restart in the wrong place.

Fetch\_mem:

:data fetch routine

sil temp, MAR, 1 add VA. temp, base load MBR, VA rtn

end

Figure 7a - SM-1 emulator example, YALLL source

should be obtained by running

% arff x wcs118.pat

Next, run the merger program:

% merger

System file name: wcs118.pat

User file name: m.out

Target File name: wcs101.pat

Check some locations of the resultant file with interdump wcs101.pat.

Compare them with the pass three dump. Those fields shown in the dump should also have the same values in the disassembly. Now, write the WCS file on the floppy disk with

## % arff r wcs101.pat

If more than one microprogram image is to reside on the floppy at a time, they obviously must have different names. So you may need to change the name in these examples, if more than one microprogram is being prepared.

## 2.7.2. running stand-alone

Now, we will bring the system down, and test the microcode stand-alone. Even in this mode of operation there are several things which have to be taken care of. The most pressing of these is the system control block (SCB). In the procedure that follows, this is set up to halt the processor on any error. The halt address will be the SCB vector address, which is determined by the source of error (see Figure 5 of Appendix I).

On the console, login to Unix. Make sure that everyone else has logged out (using the who command). Insure the integrity of the file system by issuing the sync command two or three times. Halt the VAX by typing control-p, to which the console will respond with the >>> prompt. Answer this with H return. The VAX should now be halted. Load your WCS file with the command LOAD/WCS/START:1000 WCS101.PAT. This should take a few seconds and respond that 6000 bytes were loaded.

In order to set up the VAX for stand-alone program operation, type the INIT console command. Among other things, this turns off memory mapping, so you do not have to worry about page tables. Now, type the following commands:

```

>>> SET DEF LONG

do longword deposits

>>> D/ID 3B 0

set SCBB to zero, where we'll set up SCB

>>> D/P 0 3

set up SCB to stop on any error

>>> D

+ 3

>>> D

+ 3

>>> D

+ 3

>>> D + 3 .

>>> D + 2

enable XFC microcode entry

>>> D

+ 3

>>> D + 3

>>> D/ID 2C 2000

set ISP and SP to 2000(hex)

>>> D/G SP 2000

```

Set up a small VAX program, and a small SM-1 program:

```

>>> D 100 FC

VAX program - XFC; halt

>>> SET DEF WORD

do word deposits

>>> D 200 5003

SM-1 program - load 3

>>> D + 0

complement

>>> D + A000

halt

>>> D + 00FF

location 3: data

>>> SET DEF LONG

>>> D/G R3 0

SM- 1 PC

>>> D/G R4 200

SM-1 memory base

>>> D/G RO BBBB

SM-1 AC - trash

```

Now run the interpreter program:

```

>>> START 100

```

This should quickly halt, with PC = 102. Examine some registers:

```

>>> E/G R0 AC, should show FFFFFF00

>>> E/G R4 base address, should still be 200

>>> E/G R3 PC, should show 3

```

Now that this worked (or even if it didn't), set a break point at the case instruction decoding the op-code, and watch it perform the complement operation.

```

>>> D/G R3 1 SM- 1 PC to complement

>>> D/ID 21 1421 micro- break at complement

>>> SET SOMM enable breakpoint

>>> START 100

```

The machine should halt with micro-PC = 1421. Enter the WCS debugger:

>>> WCS WCS> OPEN WCS101.PAT

Look at the D register, which should contain the complement opcode, zero. Also, r0, the pseudo-AC, which should still contain FFFFFF00.

WCS> E DR WCS> E RA O

Single step through the complement operation. Set single step mode, execute a microinstruction.

WCS> SET STEP single micro- step

WCS> START 1400 next microinstruction - beginning of complement

WCS> E LA

WCS> E Q

WCS> E RA 0

Notice that the register contents, latched into LA, were complemented on the way to register Q. Execute another microinstruction, then look at r0 again.

WCS> CONTINUE WCS> E RA 0

Now, look at the microinstruction which did the complement. Modify it so that, rather than a complement, it will exclusive-or register r0 with the constant 1, toggling the low-order bit.

WCS> E 1400 WCS> D 1400 ALU 8, BMX 6, KMX 1

Recall that this will change the disk file, as well as the control-store location. To single-step through this sequence of instructions again, use the command START 1400, then CONTINUE, examining the registers as before. Finally, change the program back to doing complements, then leave the debugger, clearing the machine.

WCS> D 1400 ALU A WCS> CLEAR STEP WCS> CLEAR SOMM WCS> RETURN >>> INIT

Invent a program to test all the opcodes.

## 2.7.3. running with Unix

If your microcode seems to work well, you are ready to try it out under Unix. When running microcode with the operating system, it is possible to write supporting routines in C and assembly language. This is generally easier (and less error-prone) than typing in hex machine codes by hand.

In console mode type:

>>> @UNIX file:unix

The system should come up, give you a message about available memory, and a # prompt. Type the sync command a couple of times, and halt the VAX as before. Recall that your WCS file, with your microcode, is still in control store. Enable the XFC instruction by changing longword 14 of the SCB (which Unix keeps at physical location zero). Then, bring Unix back up, and log in.

```

# sync

# sync

# control- p

>>> H

>>> D/P 14 2

>>> CONT followed by TWO returns

# /etc/mount /dev/rp0g /usr

# login yourname

```

After logging in, you should be able to run C programs with embedded XFC instructions. There are two ways to create such programs. If the microprogram can find its own parameters in the C program, or is parameterless, the XFC may be entered in the C source as

```

asm(" .byte Oxfc");

```

If, however, the microprogram requires parameters in registers, it is usually easier to produce VAX assembly language from the C program, using cc -S, and edit it. For example, compiling the routine of Figure 8a will produce the assembly program of Figure 8b, which can be edited as in Figure 8c, to pass parameters to and from the sm1 emulator program. Try running a more complex example.

After you have run some trials, you should halt the VAX, load the normal microcode, and bring up Unix multi-user. Restarting Unix loads the usual SCB on top of the one you changed so that the XFC instruction will no longer execute your microcode:

```

% sync

% sync

% control-p

>>> H

>>> LOAD/WCS/START:1000 WCS118.PAT

>>> @UNIX

file:unix

# chk /dev/rrp0a /dev/rrp0g

# control- d

```

```

sm1routine( accu , locc, codespace)

int *accu, *locc, *codespace;

{

register int ac = *accu,

pc = *locc,

*base = codespace;

*locc = pc;

return( ac);

}

```

Figure 8a - Microcode support C program

```

LLO:

.data

.text

.align 1

.globl _sm1rout

_sm1rout:

.word .R1

jbr

L13

L14:

movl *4(ap),r11

movl *8(ap),r10

movl 12(ap), r9

movl r10,*8(ap)

movl r11,r0

ret

ret

.set

.R1,0xe00

L13:

jbr

L14

.data

```

Figure 8b - Assembly language produced from Figure 8a

```

LLO:

.data

.text

.align 1

.globl _smirout

_sm1rout:

.word .R1

jbr

L13

L14:

*4(ap),r0

movl

*8(ap),r3

movl

movl

12(ap),r4

.byte

0xfc

movl r3,*8(ap)

ret

ret

.set

.R1,0xe00

L13:

jbr

L14

.data

```

Figure 8c - Figure 8b edited to pass parameters to emulator

### CHAPTER 4

## **EXAMPLES**

In order to illustrate the use of YALLL, some examples are presented here. Each is shown in several forms: YALLL source and object (as shown by a pass three dump) are given for each. In three cases, the latter is turned into DEC macro-code, for comparison with a hand-coded version of the program. Comparisons of various sorts are made with microcode for other machines. In two cases, comparisons are made with the code generated by the YALLL translator for the HP 300, a stack machine with a much simpler, vertical microinstruction. Comparisons are also made with microcode for the HP-21MXE, also a short microword, vertical machine.

## 1. String Translation

The first example is an instruction to transliterate a string according to a table. This is similar to the IBM-370's TR instruction. The character string is addressed by register 'str', and ends with a null (0) byte. A table is addresses by register 'tbl'. Each byte of the string is examined, and, if not zero, is replaced in memory by the byte in the table which it addresses; that is, memory( (tbl) + char). When a zero byte is encountered in the source string, the microprogram exits. To time this routine, the string "The quick brown fox jumps over the lazy dogs." was translated into upper case. The YALLL source is shown in Figure 9a, and the generated code in Figure 9b. This is expressed in macro-code in Figure 10a, and may be compared with Figure 10b, a hand-coded version. The VAX assembly code this replaces is shown in Figure 11a, and is (almost) equivalent to the C language fragment

```

org

10E0

str = r0

reg

tbl = r1

reg

reg

char = t0 unsigned byte

mar = VA

reg

loop:

; get addressed character

; test for zero, if zero, go quit

load

char, str

out if char = 0

jump

add

mar,char,tbl

; add to table base address

load

; fetch character from table

char, mar

stor

char,str

; replace character in string

str,str,1

add

; bump string address

jump

loop

; go do it again

out:

exit

end

```

Figure 9a - String translation YALLL source

| address<br>(10e0): | microinstrucion<br>VAK/1, SPO/40, ALU/f, AMX/0, J/(1400)                            |

|--------------------|-------------------------------------------------------------------------------------|

|                    |                                                                                     |

| (1400):            | FS/0. CID/8. ADS/0. DT/2. J/(1401)                                                  |

| (1401):            | SPO/30, KMX/12, ALU/d, RMX/0, AMX/1, BMX/6, J/(1402)                                |

| (1402):            | CCK/1, SPO/20, ALU/e, BMX/4, J/(1403)                                               |

| (1403):            | BEN/1b, J/(140b). 2-way branch                                                      |

| (140b):            | SPO/41, ALU/f. AMX/O, DK/8, J/(1404)                                                |

| (140f):            | PCK/4, IBC/c, J/(62)                                                                |

| (1404):            | SPO/20, ALU/5, RMX/0, AMX/1, BMX/4, J/(1405)                                        |

| (1405):            | VAK/1, ALU/5, RMX/0, AMX/1, BMX/4, J/(1408)                                         |

| (1406):            | FS/0, CID/8, ADS/0, DT/2, J/(1407)                                                  |

| (1407):            | SPO/31, KMX/12, ALU/d, RMX/0, AMX/1, BMX/6, J/(1408)                                |

| (1408):            | VAK/1, SPO/40, ALU/f, AMX/0, J/(1409)                                               |

| (1409):            | SPO/21, ALU/e, BMX/4, DK/8, J/(140a)                                                |

| (140a):            | SP0/40, FS/0, CID/6, ADS/0, SI/2, KMX/1, ALU/5, DT/2, AMX/0, BMX/6, SHF/0, J/(140c) |

| (140c):            | SP0/50, SI/2, KMX/1, ALU/5, DT/0, AMX/0, BMX/8, SHF/0, J/(10e0)                     |

Figure 9b - VAX microcode generated from Figure 9a

LOOP:

10E0:

VA\_R[R0]

D[BYTE]\_CACHE

RC[TO]\_D.AND.K[.FF]

ALU\_RC[TO], CLOCK.UBCC

ALU.CC?

=1011

D\_R[R1], J/CONTINUE

PC\_PC+1, CLR.IB.OPC, J/IRD

=END

CONTINUE:

ALU\_D+RC[T0]

VA\_D+RC[T0]

D[BYTE]\_CACHE

RC[T1]\_D.AND.K[.FF]

VA\_R[RO] D\_RC[T1]

CACHE[BYTE]\_D, ALU\_R[R0]+K[.1] R[R0]\_LA+K[.1], DT/LONG, J/LOOP

Figure 10a - Macro-Code of Figure 9b

LOOP:

10E0:

VA\_R[R0]

D[BYTE]\_CACHE

LAB\_R[R1], D.NE.0?

=101

PC\_PC+1, CLR.IB.O, J/IRD

VA\_ALU, ALU\_D.OXT[BYTE]+LB

=END

D[BYTE]\_CACHE

$VA_R[R0]$

CACHE[BYTE]\_D

R[R0]\_LA+K[.1], DT/LONG, J/LOOP

Figure 10b - Hand-Coded program for Figure 9a

register unsigned char \*tbl, \*str, c; while(c = \*str) \*str++ = tbl[c];

The VAX also has a string translation instruction which, although it won't translate a string in place, is otherwise very similar, as is shown in Figure 11b.

The size and speed comparisons for this example are shown in Figure 13.

All timings were made by executing the program segment 100,000 times.

loop:

movzbl (str),r0

beq

out

movb (tbl)[r0].(str)+

brb

loop

out:

Figure 11a - VAX assembler program to translate string

movtuc

\$s\_length,(src),\$0,(tbl),\$d\_length,(dest)

Figure 11b - VAX instruction to translate string

| Translate       | YA  | LLL | gene | nd-<br>rated<br>ocode | Assen | nbler           |

|-----------------|-----|-----|------|-----------------------|-------|-----------------|

|                 | HP  | VAX | HP   | VAX                   | HP    | VAX             |

| Speed<br>(usec) | 146 | 128 | 134  | 73                    | 1350  | 93.<br>174      |

| Size<br>(bytes) | 32  | 180 | 28   | 108                   | 20    | 11 <sub>*</sub> |

Figure 12 - Comparison of string translate routines

Then, the user-microcode overhead was subtracted from the time for each microcode example. This is the time it takes to enter user microcode upon the recognition of the appropriate macro-opcode, on the VAX-11/780 this is about 3.5 microseconds.

## 2. Pascal Assist Instructions

The second example (Figures 5 - 8) is a case-jump instruction for use by the Pascal interpreter, PX [Joy 77a]. This instruction grabs the next Pascal opcode byte from the location addressed by register 'lc' (which is incremented after use), and uses it to index into a table of offsets, whose zero-th

First figure for single instruction, second for four-instruction loop

element is addressed by register 'tbl'. The contents of this register are added to the two-byte offset fetched to form the target program address. This works very much like the VAX's CASE instruction, but the dispatch table need not follow the instruction, no range checking is done, and the case selector is implicitly the unsigned byte from the PX instruction stream. This instruction is executed at the end of the interpretation of each Pascal instruction, and thus begins the interpretation of the next.

A further PX-assist microprogram is shown in Figures 17 - 20. This combines the above dispatch function with computation of data addresses (L-values) using a lex-level and displacement from the PX instruction stream and a display in memory. Upon interpreter initialization, the display base address is passed to the microcode, which places it in SSP. Under Unix, this register (supervisor stack pointer) is an unused, per-process register. Thereafter, the microcode can be invoked to compute an address using this

```

10E0

org

reg

lc = r10

: PX location counter

reg

tbl = r8

; address of address table

opcode = t1 unsigned byte

:PX opcode

reg

reg

t_entry = Qreg signed word

;offset, from table

jaddress = t2

reg

lookup = Dreg

reg

MAR = VA

reg

dispatch:

load

opcode, lc

; fetch PX opcode

sll

lookup,opcode,1

; shift op to address words

add

MAR, lookup, tbl

; add table base - MAR now

; points to table entry

load

t_entry, MAR

; fetch displacement from table

add

jaddress, t_entry, tbl

; add to table base

add