# Copyright © 1978, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# A Machine Independent Algorithm for Code Generation and Its Use in Retargetable Compilers

by

Robert Steven Glanville

## Computer Science Division Department of Electrical Engineering and Computer Sciences

Technical Report No. UCB-CS-78-01 and Electronics Research Laboratory Memorandum No. ERL-M78/9

University of California, Berkeley 94720

# A Machine Independent Algorithm for Code Generation and Its Use in Retargetable Compilers<sup>†</sup>

#### Robert Steven Glanville

#### **Abstract**

This dissertation presents a method for the construction of efficient code generators for high-level procedural programming languages from a symbolic description of the instruction set of the target computer. A table driven algorithm is given that translates a relatively low-level intermediate representation of a program into assembly or machine code for the target computer. A construction algorithm is presented that produces the required tables from a functional description of the target machine. By supplying an appropriate machine description, new tables can easily be created, thus retargeting a compiler for the new computer. Techniques are developed to prove the correctness of the resulting code generator based on the instruction set description.

The output of the front end of the compiler is assumed to be a linearized intermediate representation (IR) of the source program consisting of a sequence of parenthesis-free prefix expressions. Implementation decisions concerning representation and storage allocation, as well as all but the low-level, machine dependent optimizations are already incorporated into the IR. Each machine instruction is described by a prefix expression and an assembly or machine language template. The code generation algorithm performs a pattern-matching similar to parsing. However, unlike the situation in syntax analysis, target machine descriptions are normally highly ambiguous. By defining a property called **uniformity**, which is satisfied by most instruction sets, it is possible to give a concise characterization of the sequence of prefix expressions computed by an instruction set, to check that all possible inputs to the code generator fall within this class, and to produce a left-to-right deterministic linear-time code generator.

Ambiguities in the machine description are resolved in favor of choosing longer instruction patterns over shorter ones, thus effectively attempting to produce the object program that is shortest in terms of the number of instructions generated while containing the same sequence of operations. In practice this heuristic works very well. In comparison with existing compilers, the code generated by this algorithm is of equal or better quality (in terms of the size of the code produced). The instances in which existing compilers produce superior code

<sup>†</sup>Research sponsored by National Science Foundation Grant MCS74-07644-A03.

2

stem from optimizations, i.e. changes in the sequence of operations, that were not employed in this work. Most of these optimizations could be combined with our method of code generation. The code generation routines for most existing compilers are written by hand and use sequences of instructions identified by the implementer. By choosing code sequences in a systematic algorithmic fashion, our code generators are more consistent and more successful in using the full range of machine instructions, including many special purpose instructions.

Professor Susan L. Graham Chairman of Committee

### Acknowledgements

i

I wish to express my gratitude to the many people who helped make this dissertation a reality. The members of the faculties at Berkeley and Southern Methodist Universities provided the excellent educational environment so necessary in such an endeavor. My special thanks goes to my advisor, Professor Susan L. Graham, who provided the encouragement and guidance I needed, and to the members of my committee, Professors Lawrence Rowe and Ilan Adler.

It is impossible to properly acknowledge the numerous persons upon whose work, ideas, and stimulating discussion this dissertation is based. Of particular note are Jeff Barth and Bill Joy, who were graduate students at Berkeley concurrent with myself. I cannot begin to express my thanks to my wife, Linda, who found the time and energy to provide the moral support I needed to complete this dissertation, despite the fact that she was suffering through the same ordeal with her own dissertation. I would also like to thank my parents for encouraging me in my academic pursuits. Finally, I would like to thank Polynomial who contributed countless hours of her undivided attention to each and every detail of my dissertation, even as I wrote it.

The financial support of the National Science Foundation under grant MCS74-07644-A03 is gratefully appreciated.

### Table of Contents

| Chapter 1: Introduction                                                | 1  |

|------------------------------------------------------------------------|----|

| 1.1 Goals of Automatic Code Research                                   | 2  |

| 1.2 Overview of Compilation                                            | 2  |

| 1.2.1 Analysis                                                         | 2  |

| 1.2.2 Synthesis                                                        | 4  |

| 1.3 Why Study Code Generation                                          | 5  |

| 1.4 Previous Work                                                      | 6  |

| 1.4.1 Procedural Code Generation                                       | 6  |

| 1.4.1.1 UNCOL                                                          | 6  |

| 1.4.1.2 Elson and Rake                                                 | 7  |

| 1.4.1.3 Wilcox                                                         | 9  |

| 1.4.1.4 Donegan                                                        | 11 |

| 1.4.1.5 Analysis of Code Generation Languages                          | 13 |

| 1.4.2 Code Generation by Semantic Machine Description                  | 13 |

| 1.4.2.1 Miller                                                         | 13 |

| 1.4.2.2 Weingart                                                       | 14 |

| 1.4.2.3 Analysis of Semantic Code Generation                           | 16 |

| 1.5 Summary of This Project                                            | 17 |

| 1.6 Comparison with Compiler-Compilers                                 | 17 |

| •                                                                      |    |

| Chapter 2: Design of a Machine Independent Compiler                    | 19 |

| 2.1 Machine Independent Aspects                                        | 20 |

| 2.2 Parameterizable Machine Dependent Implementation Decisions         | 22 |

| 2.3 Code Generation                                                    | 26 |

| 2.4 Optimization Phases                                                | 26 |

| 2.4.1 Constant Folding and Constant Propagation                        | 28 |

| 2.4.2 Peephole Optimization                                            | 29 |

| 2.4.3 Common Subexpression Elimination                                 | 30 |

| 2.4.4 Other Optimizations                                              | 31 |

|                                                                        |    |

| Chapter 3: The Target Machine Description                              | 32 |

| 3.1 The Internal Representation (IR)                                   | 32 |

| 3.2 Modeling Computer Instruction Sets                                 | 36 |

| 3.3 The Structure of TMDL                                              | 41 |

| 3.4 A Sample Machine Description                                       | 43 |

|                                                                        |    |

| Chapter 4: The Code Generation Algorithm                               | 45 |

| 4.1 Shift-Reduce Parsing Algorithm                                     | 46 |

| 4.2 Adding Semantic Information to the Parser to Make a Code Generator | 49 |

| 4.3 Register Allocation                                                | 51 |

| 4.4 A Simple Example                                                   | 52 |

| 4.5 Automatic Construction of a Code Generating Parser                 | 56 |

| 4.5.1 The Initial Table Construction                                   | 56 |

| 4.5.2 Correct Code is Always Generated                                 | 61 |

| 4.5.3 Looping                                                          | 66 |

| 4.5.4 Complexity of Loop Detection by Preprocessor                     | 68 |

| 4.5.5 Loop Elimination by Preprocessor                                 | 69 |

| 4.5.5 Blocking and Uniformity                                          | 71 |

| 4.5.7 Semantic Blocking                             | 82  |

|-----------------------------------------------------|-----|

| Chapter 5: Two Examples: The PDP-11 and The IBM 370 | 86  |

| 5.1 The Preprocessor and Coder Implementations      | 86  |

| 5.2 Generating PDP-11 Object Code                   | 87  |

| 5.3 Generating IBM 370 Object Code                  |     |

| Chapter 6: Results and Conclusions                  | 111 |

| 6.1 Postfix vs. Prefix                              | 112 |

| 6.2 Areas for Future research                       | 114 |

| References                                          | 116 |

| Appendix A: PDP-11 Machine Description              | 119 |

| Appendix B: IBM 370 Machine Description             | 122 |

## Figures

| 1.1 | Block Diagram of a Compiler                           | 3   |

|-----|-------------------------------------------------------|-----|

|     | GCL Floating Point Assignment Macro from [Elson70]    | 8   |

|     | Code Generation Template from [Wilcox71]              | 10  |

|     | CGPL Routines for ADD and SUB from [Donegan73]        | 12  |

|     |                                                       |     |

| 2.1 | Generation of a Machine Independent Compiler          | 20  |

| 2.2 | Bootstrapping to a New Computer                       | 22  |

| 2.3 | PASCAL-P Compiler Targeting Information               | 25  |

|     | Three Places for Modular Optimization                 | 27  |

|     | Some Peephole Optimizations                           | 30  |

| 3.1 | Sample Machine Description                            | 44  |

| 4.1 | Sample Instruction Set Description                    | 53  |

|     | Code Generation Table for Example                     | 54  |

| 4.3 | Initial State Computation for Example Instruction Set | 62  |

|     | Code Generation Table for Example                     | 63  |

| 4.5 | Graph Constructed to Eliminate Loop: d→→d             | 70  |

| 5.1 | A Machine Independent PASCAL Compiler                 | 87  |

|     | PDP-11 Preprocessor Execution Times                   | 89  |

|     | PDP-11 Code Generator Table Sizes                     | 90  |

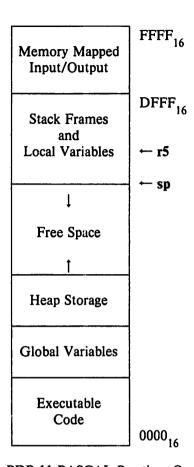

|     | PDP-11 PASCAL Runtime Organization                    | 92  |

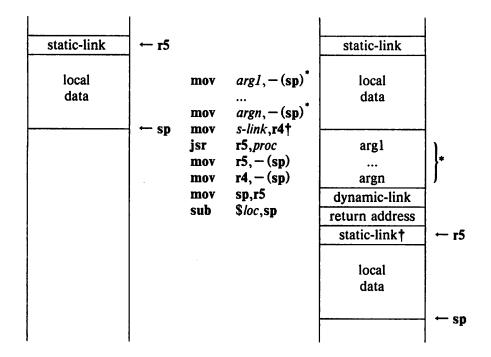

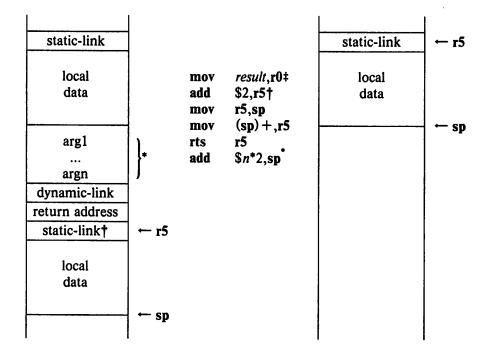

|     | PDP-11 PASCAL Procedure Entry and Exit Code           | 93  |

|     | Matrix Multiplication Routines                        | 94  |

|     | Integer Read Routines                                 | 95  |

|     | PDP-11 IR Translation of Test Pregrams                | 96  |

|     | Assembly Listings for matrixmult Routines             | 97  |

|     | O Assembly Output for readn Routines                  | 100 |

|     | 1 IBM 370 Preprocessor Execution Times                | 102 |

|     | 2 IBM 370 Code Generator Table Sizes                  | 102 |

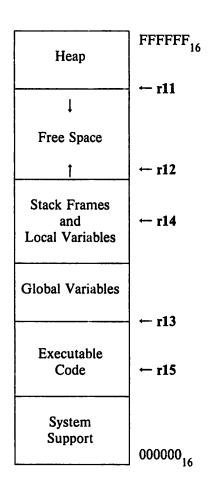

|     | 3 IBM 370 PASCAL Runtime Organization                 | 103 |

|     | 4 IBM 370 Translation of Test Programs                | 104 |

|     | 5 ALGOL-W Comparison Routines                         | 105 |

|     | 6 IBM 370 Assembly code for matrixmult                | 108 |

|     | 7 ALGOL-W Assembly code for matrixmult                | 109 |

|     | R IRM 370 Assembly code for ready Routines            | 110 |

## Algorithms

| 4.1 | The Code Generator                            | 50 |

|-----|-----------------------------------------------|----|

| 4.2 | The Initial LR(0) Code Generator Constructor  | 58 |

|     | The Initial SLR(1) Code Generator Constructor |    |

| 4.4 | Loop Detection                                | 69 |

| 4.5 | Loop Elimination                              | 72 |

| 4.6 | Uniformity Test for Algorithm 4.3             | 78 |

| 4.7 | Blocking—Uniformity Test for Algorithm 4.2    | 80 |

| 4 8 | Default List Construction                     | 84 |

### Chapter 1: Introduction

A compiler is a computer program which translates other programs, written in a particular programming language, into executable code for a specific target computer. This dissertation presents an approach to the problem of producing a retargetable (and transportable) compiler for a high level programming language. Such a compiler could be systematically reconfigured to generate object code for any one of a large class of commercially available computers. A major part of this research concerns the automatic creation of a suitable code generator for each target computer from a symbolic description of that computer's instruction set.

The overall design of a retargetable compiler that incorporates such a code generator is presented in Chapter 2. Particular emphasis is given to discussing the degree of machine dependence that is inherent in various portions of a compiler in a general implementation. Topics closely related to code generation, including register allocation and optimization, are also discussed. Finally, practical aspects are considered, such as the efficiency, modifiability, and maintainability of the resulting compiler.

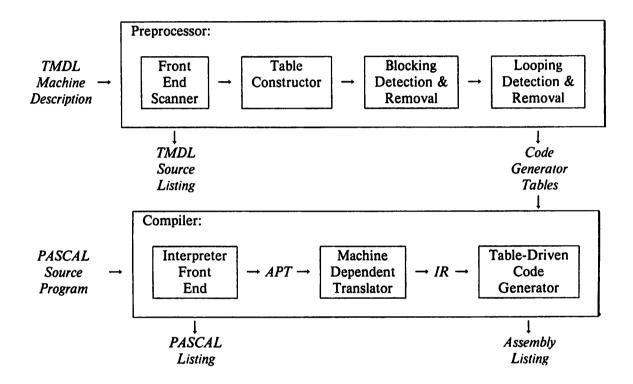

The target machine description language, TMDL, used by the machine independent compiler, is described in Chapter 3. Since the instruction set description, a major part of TMDL, is closely linked to the internal representation (IR) output of the analyzer, the internal representation is also discussed. Motivation is given for the design decisions, as they are very much affected by the code generation algorithm used.

Chapter 4 presents a table driven pattern matching algorithm that generates object code by 'parsing' the output of the recognition phase of the compiler using the target computer's instruction set as the grammar 'rules'. A finite state pushdown automaton is constructed from the patterns defining the computer's instruction set. At compile time, the output of the parser is taken as the input to the automaton. The longest leftmost instruction pattern is found and the corresponding object instruction is emitted. An algorithm is presented that computes the tables required by the code generator from a semantic description of the target computer's instruction set. The properties of the code generation algorithm are then investigated to determine the type of code produced, what it efficiently codes, and how one can insure that a machine's instruction set will cover all possible outputs of the compiler. The correctness of the code generator and coder construction algorithms is addressed next. Sufficient conditions that the code generator will not loop, block on valid input, or generate incorrect code are given. The machine independent code generation algorithm is thus proven to always generate correct code for any valid IR input.

Example code generators for a PASCAL implementation are presented in Chapter 5. The target computers used are the PDP-11 and the IBM 370. The code generated by the coder for several sample programs is compared with the output of existing compilers on the target computers.

Chapter 6 concludes with the overall results and comments on the feasibility of using this method of code generation both in code generation research and in production compiling. Areas for future research are also discussed.

#### 1.1. Goals of Automatic Coder Research

The major goal of this research is to design a compiler for a single, high-level language that can be systematically reconfigured to produce code for a variety of distinct target computers. The modularity necessary for this task is obtained primarily from the use of symbolic description of the target computer's instruction set. The compiler will be reconfigurable to 'favor' specific target computer architectures by allowing the implementer to choose between certain alternatives (such as how the run time stack is implemented) and to input specific facts about the computer (such as the number of registers). It is expected that machine independent local optimizations will be included in the compiler to allow it to produce good object code. Also, knowledge about the behavior of the particular code generation algorithm used should allow the compiler to arrange the intermediate text symbols, in a machine independent fashion, in a way that allows a simple-minded coder to do well. The work of [Loveman76] and [Carter75] suggests that such an approach is feasible. In Loveman's research source language transformations are used to improve the code generated; in Carter's work the intermediate code is transformed by various optimizations prior to code generation.

#### 1.2. Overview of Compilation

Code generation is one aspect of the complex process of compilation. Because the terminology used to describe some critical points in the compilation process is not standardized, a brief review of compilation is presented next. The model used is similar to that of [Wilcox71]. Figure 1.1 gives an overview of the structure of the compiler model used.

#### 1.2.1. Analysis

Analysis, the first portion of the compilation process, is the phase in which the compiler determines the structure and meaning of the source program being compiled. The original program, written for ease of human comprehension, is transformed into a form that is easy for the computer to manipulate. Analysis also provides the programmer with information about syntax

violations of the language present in the program. The analysis phase produces a set of tables describing the functional and representational aspects of the data manipulated by the program and an abstract program tree (APT) which represents the executable portion of the source program.

Analysis is divided into three subtasks: lexical analysis, syntactic analysis and semantic analysis. Lexical analysis, also referred to as scanning, is the process by which the compiler groups certain strings of characters into individual tokens. Identifiers, single and multiple character operators and numerical constants are examples of tokens. Comments and insignificant blanks are discarded. Each distinct token is given an integer number, allowing the compiler to work with fixed length integers instead of variable length character strings, thus simplifying the task. The output of the scanner is a list of tokens that represent the source program that is being compiled.

Syntactic analysis, or parsing, is the process by which the compiler determines the structure of the program. Normally, the tokens output by the lexical analyzer are treated as symbols in a context free language and parsed by one of the well known deterministic context free parsing algorithms. As the parse is performed, an APT is constructed that represents the program structure. An APT is similar to a parse tree. The interior nodes of a parse tree represent non-terminals in the context free grammar used to define the syntax of the program. All tokens appear as leaves of the tree. In an APT, tokens appear as interior nodes, and there are very few, if any, nodes that do not correspond to tokens in the source program.

Semantic analysis is the process of determining the meaning of a program. Attributes of variables, constants, functions and procedures are determined and put into the symbol table. In strongly typed languages, type checking is performed to determine the necessary coercions, and to insure that the use of a variable is consistent with its definition (an error message is issued if it is not). The meaning of ambiguous symbols such as +, which may be integer or real addition or perhaps set union, may also be determined.

#### 1.2.2. Synthesis

Synthesis is the process in which the compiler builds an equivalent object code representation of the program in the machine language of the target computer. Internal representations for the data objects described in the symbol table are chosen, and object code sequences are generated that manipulate the data as described by the APT. The environment required by the language being compiled must also be simulated on the target computer. Any implementation dependent restrictions violated by the program are reported. Wilcox calls the synthesis phase the code generation phase, but in this dissertation the term code generation will refer to the

restricted task of choosing actual object code instructions to implement the program.

Synthesis is divided into the subtasks of storage allocation, translation, code generation and, optionally, optimization. Storage allocation is the assigning of memory locations to variables. Translation converts the APT into a low level internal representation (IR). The IR can be thought of as the assembly language for some ideal, source language dependent computer. It is an efficient representation, and often contains operations that depend upon specifics of the particular language being compiled. Optimization is a translation of the IR into itself or another IR that will allow the code generator to produce better object code, according to some cost criteria. Code generation is the mapping of the final IR representation into instructions of the target computer.

The individual phases of real compilers are seldom as distinct as this model would indicate. In any particular implementation, distinct phases and tasks are often performed in parallel due to the strong interactions that must occur between phases or to allow a more efficient implementation. Translation is often performed by the parser as a consequence of each reduction. Storage allocation can be done as early as when the variable declarations are encountered, or as late as after the optimization phase to allow the additional information gained to better allocate available resources. And in a one pass compiler everything is done in parallel. In this dissertation, however, we will speak as though the phases occur sequentially, in the manner described, and note any difficulties that might be encountered in altering the model to correspond to real compilers.

#### 1.3. Why Study Code Generation

Research in code generation has lagged behind the rest of compiler research for several reasons. In order to analyze a problem mathematically one has to build a precise model of exactly what is happening. For scanning and parsing, there are clean models that allow very complete mathematical analysis. Optimization research also has provided models of the program improvement process. However, while there have been significant results in treating code generation mathematically ([Newcomer75] or [Aho76] for example), research has been with idealized models of computers. Real computers tend to be rather messy to describe as they simply do not have mathematically elegant instruction sets. There are always special instructions that implement certain computations quite efficiently. Furthermore, there are a variety of architecturally distinct commercial computers. A single model would have to be complex indeed to include them all, and would lead to a less efficient implementation of a code generator than a model that was tailored around a single computer design.

The fact remains that real compilers must generate object code for real computers. The result is that most code generators are designed from the ground level by the implementors. Retargeting a compiler for a new computer may require a substantial amount of work, especially if reasonably good object code is to be generated. This dissertation does not attempt to build a formal model of computer instruction sets, but instead presents a method of generating code by pattern matching with a simplified representation of a computer's instruction set. It is hoped that this research will help in the creation of retargetable and transportable compilers.

#### 1.4. Previous Work

We next turn to a summary of the efforts that have been made in the past to improve the code generation process. Previous research in code generation can be divided into two classes. The first class allows the user to provide information about the target machine in procedural form. The implementor describes the code generation process and makes all of the decisions as to what kind of code is to be generated. There are several special purpose code generation languages and interpreters that have been designed for this purpose. The second class uses information about the target machine supplied in a descriptive format, or data base. A code generator is automatically constructed from facts describing the resources of the target computer and the semantics of each instruction on that computer. The work carried out for this dissertation falls into the second class.

#### 1.4.1. Procedural Code Generation

#### 1.4.1.1. UNCOL

In the late 1950's, an attempt was made to define a UNiversal Computer Oriented Language, called UNCOL, to help make all languages easily available on all computers [Strong58] [Steel61]. UNCOL was an intermediate language which was to be used as a stepping stone in compiling any language. A program called a 'generator' would translate programs written in some source language into UNCOL, and a machine-dependent, language-independent program called a 'translator' would generate object code for a particular target computer from the UNCOL program. Thus, if a compiler was written for a new language it would become available immediately on all computers, either because the source language it was written in was already available on all computers, perhaps via UNCOL, or by translating the compiler into UNCOL and generating a version that would execute on the target computer through its already existing UNCOL to machine language translator. Likewise, for each new computer manufactured, once a single UNCOL to object code translator has been written, all existing languages would become available on that computer, as well as a wealth of existing application programs.

The UNCOL approach would substantially reduce the number of compilers required to have all languages available on all computers. For M languages to be available on each of N computers, there would only have to be M+N translators written, instead of the usual  $M\times N$ . There would also be a certain inherent compatibility among implementations of a language due to the fact that there would be virtually a single compiler for that language.

Unfortunately this project failed. The variety of languages, computer architectures, and instruction sets available at that time proved to be too difficult to adequately represent in a single intermediate language. There was also some concern that such a two translator scheme would be relatively inefficient when compared to a standard compiler. In any event, UNCOL never enjoyed wide-spread use despite its authors' dedication to practicality.

#### 1.4.1.2. Elson and Rake

Elson and Rake describe an implementation of a code generator which generates optimized code for an experimental PL/I compiler [Elson70]. The code generator interprets macro commands written in a special code generating language, GCL. Input to the coder is a syntax tree produced by the parser representing the program being compiled. General purpose tree referencing functions are provided to allow the coder to traverse the data structure easily.

The user provides a separate macro, coded in GCL, for each type of node that may appear in the tree. Each macro includes all required logic for optimization, code emission, and error detection and correction for that particular type of node. Flow of control is determined by conditional branches, parameterized subroutine invocations, and a multidimensional table look up facility that is used as a multidimensional computed GOTO. The language has an assembly language appearance and the examples given are difficult to comprehend, primarily because of the four dimensional computed GOTO's. For example, the floating point assignment macro is over 90 lines long and does not support double-double precision or complex data types. It is also optimized specifically for minimum execution time on the IBM 360 System/65. A portion of that macro appears in Fig. 1.2.

Elson and Rake's method has a number of advantages. The machine dependent code emitters provided by GCL ease the task of code emission. The quality of code produced by their implementation is quite good. The tree referencing primitives allow the implementor to test the context of a particular node to determine applicable optimizations. Powerful optimizations that would be difficult to detect in a linear representation may be readily implemented. For example, in the PL/I statement:

#### **@FLOATASSIGN OMD** START @FLOATASSIGN DCL (GOPT, LLEN, RLEN, WKCELL, RATR, LATR, LO, LB, LI, LL, LR, RO, RB, RI,RR,RL,WKCELL)CELL,GPR REG (FIXED) \*CHECK GLOBAL CELL WHICH HAS COMPILER OPTIONS IF (BIT(GOPT,OPTT) = 0 | BIT(GOPT,MG5) = 0),OKMSG'@FLOATASSIGN OPTIMIZED ONLY FOR MOD 65, TIME OPTION' \*FIND BYTE LENGTHS OF SOURCE AND TARGET \*@FLOATLENGTH UTILITY EXPECTS CURSOR AT PARENT OF ARITH NODE OK PUSH ARG(1) LINK @FLOATLENGTH(LLEN) POP. PUSH ARG(2) LINK @FLOATLENGTH(RLEN) IF (LLEN = 16 | RLEN = 16), NOT16 MSG'DOUBLE DOUBLE LENGTH NOT SUPPORTED BY @FLOATASSIGN' **RTN** NOT16 IF (ARG(1).ARG(1).COMPLEX | ARG(2).ARG(1).COMPLEX),NOTCPX MSG'COMPLEX NOT SUPPORTED BY @FLOATASSIGN' RTN NOTCPX SET LALN = 2 - ARG(1).UNALIGNED SET RALG = 2 - ARG(2).UNALIGNED\*NOW DO TABLE LOOKUP AND GO TO RESULT LABEL TO \*SET UP REQUIREMENTS FOR SOURCE RESULT, DEPENDING \*ON LENGTHS AND ALLIGNMENTS LOOK ERR1, WKCELL, TBL1 (LALN, LLEN/4, RALN, RLEN/4) GO TO WKCELL ERRI MSG'ERROR IN TBL1 LOOKUP IN @FLOATASSIGN' **RTN** \*FOLLOWING ARE THE RESULT LABELS OF LOOKUP \*TARGET 4 BYTES ALLIGNED, SOURCE ALLIGNED. ASK FOR \*RX REFERENCE OR FLOATING REGISTER RXFR1 SET RATR = M'F0001000'**GOTO LRX** \*8 - BYTE RESULT NEEDED IN FLOATING REGISTER, SO SOURCE \*WILL DO SDR, LE OR LD OR MVC(4), SDR, LE FRFW1 SET RATR = M'30000000'\*GET ADDRESSIBILITY OF TARGET AS RX OR RS REFERENCE LRX SET LATR = M'C0000000'**GOTO LINK** \*REOUEST BOTH SOURCE AND TARGET AS RS REFERENCES \*SINCE MVC WILL BE DONE RSI SET RATR = M'40000000'TBL1 TBL(2,2,2,2) REF ARRY RXFR1,RXFR1,FRFUL1,FRFUL1,FRFUL1,RS1,RS1,RS1,RS1, RS1,RS1,RS1,RS1,RS1,RS1

Fig. 1.2. GCL floating point assignment macro from [Elson70].

**END**

the code generated does not actually concatenate strings S1 and S2. Strength reduction is used to implement the concatenation operator as a much more efficient add instruction in the context of a length function. Code is generated that is equivalent to the statement:

$$I = LENGTH(S1) + LENGTH(S2);$$

This optimization results in substantially improved code. Finally, the code macros are easily altered to detect and exploit special cases that at first were thought unimportant.

Elson and Rake's method is not without its drawbacks. The fact that GCL is an interpreted language causes a certain amount of overhead. The macros tend to be large, complex and difficult to understand. They are, in fact, so large that they had to be paged in from disk in the authors' implementation. The size of the macros is due in part to the size and complexity of both the language being compiled and the instruction set of the IBM 360. The macros are machine dependent, relying heavily upon the target computer's architecture and instruction set not only with respect to optimization but also to type checking. The concatenation optimization mentioned previously, impressive as it is, is the result of a highly specific decision by the implementors to watch for this type of construct. The retargeting of this compiler for a new computer would require not only a complete rewriting of the code generation macros, but even a rewriting of part of the GCL itself, as there are specific procedures in GCL that depend upon the instruction formats of the target computer. This method relies heavily upon the implementor's ability to design and debug the code generation macros, quite a formidable task for a language/machine combination like PL/I on the IBM 360.

#### 1.4.1.3. Wilcox

Wilcox describes a model for code generation for modern high level programming languages that is based on the code generator he designed for the Cornell PL/C compiler [Wilcox71]. Code generation is divided into four phases: storage allocation, translation (of the APT into tuples), global optimization, and coding. The analysis phase of the compiler constructs an abstract representation of the program. The translator produces a code sequence for an artificial source language machine, called an SLM, that is based on the operators and data types of the source language. Each node of the APT results in a sequence of such instructions. The coder produces object code for the target computer from the SLM program after an optional optimization phase. An implementation map is used to generate a sequence of object machine code instructions for each SLM instruction.

In order to generate object code for a particular computer, the user provides a subroutine for each SLM instruction. These routines are written in a coding language, ICL, especially

designed for the object machine. Statements in ICL are precompiled into templates which are interpreted at compile time by the code generator. The code template for binary addition on the IBM 360 presented by Wilcox is reproduced in Fig. 1.3. ICL is low level and assembly like.

| ADDB                                                    | BR          | A,ADDB1 | ->ADDB1 If A is in a register         | 1  |

|---------------------------------------------------------|-------------|---------|---------------------------------------|----|

|                                                         | BR          | B,ADDB2 | ->ADDB2 If B is in a register         | 2  |

|                                                         | LGPR        | Α       | Generate code to load A into register | 3  |

| ADDB1                                                   | BR          | B,ADDB3 | -> ADDBB3 If B is in a register       | 4  |

|                                                         | GRX         | A,A,B   | Generate A+B                          | 5  |

|                                                         | В           | ADDB4   | ->Merge                               | 6  |

|                                                         |             |         |                                       |    |

| ADDB3                                                   | GRR         | AR,A,B  | Generate A+B                          | 7  |

| ADDB4                                                   | FREE        | В       | Release resources assigned to B       | 8  |

| ADDB5                                                   | POP         | 1       | Remove B descriptor from stack        | 9  |

|                                                         | EXIT        |         | •                                     |    |

| ADDB2                                                   | GRX         | A,B,A   | Generate A+B                          | 10 |

|                                                         | <b>FREE</b> | A       | Release resources assigned to A       | 11 |

|                                                         | SET         | A,B     | A now designates result location      | 12 |

|                                                         | В           | ADDB5   | ->Merge                               | 13 |

| •                                                       |             |         |                                       |    |

| Figure x.x Code Template for Binary Addition (one-pass) |             |         |                                       |    |

|                                                         |             |         |                                       |    |

|                                                         |             |         |                                       |    |

Fig. 1.3. Code Generation Template from [Wilcox71].

To retarget a compiler for a new computer, a new ICL compiler has to be designed for that target computer and an interpreter has to be written. This is not as difficult as it may sound, as ICL is like an assembly language and therefore relatively easy to compile. Then a new set of ICL templates has to be written to govern code generation. This is obviously not as simple a task as one might hope when retargeting a compiler. But Wilcox was primarily interested in code generation techniques, not portability. It seems possible to produce better object code using this method than other methods more concerned with portability. ICL templates also allow the implementor a separate vehicle for specifying the code generation part of the compiler, quite possibly reducing the implementation and debugging effort required. However, the addition of a new optimization may require minor additions to the ICL used in order to collect additional necessary information. The implementor still has to make all of the local optimizations and instruction choices, and, like GCL used by Elson and Rake, this method relies heavily on the implementor's ability to design and debug code generation routines.

#### 1.4.1.4. Donegan

In his dissertation, Donegan proposes an organization for a general code generation scheme, though it was not implemented [Donegan73]. The input to the code generator is a syntax tree and a symbol table. Code is generated directly from the tree without translation into a linearized form. To determine what code will be generated for each type of node in the syntax tree, a separate routine is written in a Code Generation Preprocessor Language, CGPL, designed by Donegan. Routines written in CGPL are translated by a preprocessor into PL/I source routines which can then be incorporated into a compiler.

The code generation algorithm accepts expressions of the language being compiled as a parameter and generates object code to compute that expression. Evaluation proceeds by a traversal of the syntax tree. As each operator is encountered, the coder is considered to be in a state that corresponds to the locations of its operands, such as in an accumulator or in memory. The operand state idea is based on earlier work done by [Miller71] which is summarized in a later section of this chapter. For each operator, the implementor specifies three sets of facts. The first is a list of special conditions that will apply to the operands upon entry to that CGPL procedure. An example would be that both operands cannot be in the accumulator of a single accumulator machine at the same time. The second is a set of state tuples from which code can be directly emitted for that operator, and the corresponding PL/I code to actually generate the correct code. The PL/I code is usually a single call to a particular code generation routine. The third set of inputs is a list of state transitions that transform operands from one state to another and PL/I code generation sequences to implement them. This information allows the code generator to automatically modify the state of the operands, bringing the coder into a terminal state from which code can be emitted. Example CGPL routines for integer addition and subtraction for a simple one accumulator computer with a stack appear in Fig. 1.4.

As stated earlier, the preprocessor generates PL/I routines as output from the CGPL input routines. It also generates a table for each operator that describes the state transition paths that will be used to generate code for all valid input state pairs. Thus the CGPL routine for a particular operator will not have to recompute transition paths each time it is invoked at code generation time. The preprocessor also checks to make sure that it is possible to generate code for all valid operand state pairs. Donegan discusses the problem of determining the shortest state transition path when several possible instruction sequences exist, based on supplied instruction costs.

CGPL is a higher level code generation language than those used in previous work. It allows a cleaner representation of the information than is possible in lower level languages, and consequently should require less implementation and debugging time. It has incorporated in it

```

$GENERATE ADD;

DECLARE CONDITIONS (VAR TREEPTR) MUTUALLY EXCLUSIVE,

(INACC, ONSTACK) INTERNAL;

TERMINAL

(VAR,INACC) -> GEN(ADD,OP1)',

(INACC, VAR) -> GEN(ADD, OP2)'

(ONSTACK,INACC) -> 'GEN(ADD,NIL)';

TRANSITION

(VAR,INACC) -> LOADUP,

(TREEPTR,INACC) -> TRANS,

(INACC,ONSTACK) -> 'GEN(PUSH,NIL)';

END

$GENERATE SUB;

DECLARE CONDITIONS

(VAR, TREEPTR) MUTUALLY EXCLUSIVE,

(INACC, ONSTACK) INTERNAL;

TERMINAL

(INACC,VAR) -> GEN(SUB,OP2)'

(INACC,ONSTACK) -> 'GEN(SUB,NIL)';

TRANSITION

(VAR,INACC) -> LOADUP,

(TREEPTR,INACC) -> TRANS,

(INACC,ONSTACK) -> 'GEN(PUSH,NIL)';

END;

```

Fig. 1.4. CGPL Routines for ADD and SUB from [Donegan73].

some ideas on automatically determining instruction sequences from a semantic description of what is needed to be done. In these two respects it is a distinct improvement over earlier work in code generation languages.

However, CGPL is not entirely portable due to its close tie to a single high level language and to the machine and implementation dependent state set and support routines. This author feels that the quality of the object code produced by the system is not much better than that produced by macro expansion. Operators are translated individually after all operands have been evaluated and without regard to the requirements of subsequent operators. There is no way to incorporate multiple operation instructions that might appear in a new computer's instruction set (such as memory to memory addition — equivalent to an add and a store, or a double indexed load — two adds and a load) without modifying the internal syntax tree to locate where they might be used.

An implementation of CGPL was done by Maltz as an extension to the PASCAL

programming language [Maltz77]. The language aspects were improved somewhat, especially the typing mechanism and syntax. Maltz's implementation also indicated that fair code could be generated, but that the drawbacks previously mentioned were present. CGPL is just another programming language that is specifically designed for writing code generators.

#### 1.4.1.5. Analysis of Code Generation Languages

Code generation languages are not as successful as might be hoped. While they are an improvement over the method of writing a code generator in a standard computer language, since some bookkeeping is done automatically, the implementor still has to make all of the low-level decisions, and consequently can make the same errors, whether they result in incorrect or merely inefficient object code. This problem is magnified when more than one programmer is involved in writing the code generator. It is more desirable to allow the programmer to input a concise description of the target computer and let the code generator make all of the decisions, assuming such a task could be efficiently done. If that description is concise, a single programmer could write and maintain the code generator for a large compiler. Even if several programmers were involved, the task would be simpler to understand. Many logical errors would be eliminated, and the bulk of the remaining errors would be clerical in nature, representing some misconception as to how the actual computer hardware behaves.

#### 1.4.2. Code Generation by Semantic Machine Description

#### 1.4.2.1. Miller

Miller describes an early attempt to automatically create a code generator from a semantic description of a target machine [Miller71]. In his system, DMACS, a code generator is created in two steps. In the first step the semantics of the language are defined by a set of machine independent macros. In the second step information describing the structure and semantics of the target computer is defined. All of the operators in the language macros must have instruction sequences that implement them in the target machine description.

The code generation process is modeled as a finite state machine whose state is determined by the runtime location of the operands to a particular macro. States are called **permitted** if object code can be directly generated to implement that macro from that state. If the coder is not in a permitted state, a series of automatic transitions is made to bring it into such a state. In order to do this, the user specifies a set of state transition paths and object code that implements them, such as load, store, and register to register move instructions.

Data referencing is treated as a separate task. The language implementor defines data reference macros and the machine specifier describes the resources available on the target machine and how the distinct data classes are to be represented. It is then possible to have automatic allocation and accessing of data items.

The problem with this work is that many simplifying assumptions are made concerning the architecture of the target computer. Compilers for real machines are more complex than Miller's model allows. Also, he only addresses the problem of generating code for two parts of a compiler, expression evaluation and data referencing. Nevertheless, Miller opened a new area of automatic code generation, the semantic machine description approach. A great deal of research has been and continues to be carried out in this area.

#### 1.4.2.2. Weingart

Weingart describes the code generator used in several implementations of the systems programming language IMP [Weingart73]. His method is based on matching the target computer's instruction set with the output of the parser to determine which instructions to generate. The instruction set is encoded into a tree structure to facilitate the pattern matching process. A tree traversing routine accepts patterns from the parser and searches the tree for equivalent patterns.

The user provides a description of the target computer's instructions in the form of a tree structured data base. Only those instructions that implement operators in the source language, are used. Instructions that move data between registers or load data from memory into a register do not implement any such operation and must be handled separately. Weingart describes a program that helps to construct the data base for the user. The user also describes the format in which the instructions will be output. Special conversion patterns are required in addition to the instruction set description to allow the coder to start generating code for certain instances for which the machine has no single instruction. For example, consider the statement:

$$A:=B+C;$$

The output of the recognizer is something like:

$$m m m + :=$$

where m stands for the address of a variable. On a machine without a multiple address add instruction the code generator would need some help in starting the code generation for this statement. Since instructions to load a single operand into a register are not automatically

utilized by the code generator, the user supplies a special pattern called a **conversion** pattern to match the 'm m +' portion of the input and arbitrarily generate code to load one specific operand into a register. When generating code for an operator it is the user's responsibility to specify conversion patterns for any case in which code cannot be directly generated. The input string is then altered to reflect the load instruction:

m m r + :=

and code generation continues. The 'm r +' portion of the input is then matched to an add instruction, code is issued, and the input is changed to:

m r :=

The major advantage of this method of code generation is that it relies on the instruction set of the target computer in deciding what code to emit. The clerical nature of describing an instruction set is less prone to error than the creative nature of writing code generation routines, macros, or templates. Every operational instruction is available to the coder, and with a careful ordering of the instruction tree, special cases for non-standard instructions are automatically discovered by the code generator. Weingart claims that good local code is generated. Finally, retargeting the compiler for a new computer is greatly simplified. One merely substitutes the new instruction set's description for the old as input to the tree builder and produces a data base for a code generator for the new machine.

The disadvantages of this method are the difficulty of creating and using an optimal tree structure for code generation and the lack of sufficient conditions to insure that a complete set of conversion patterns have been supplied. The efficiency of the code generation algorithm as well as the quality of the generated code are dependent upon an optimized version of the instruction tree. If the tree is not compressed as much as possible (by combining prefixes of similar instructions) then the coder will spend a lot of time searching the tree for patterns. If there is one instruction that is a more efficient but a special case of another instruction, then care must be taken to insure that the special case is matched first, or else it will never be used. For example, if there is an add immediate instruction that adds an integer constant to a register, and a more efficient increment instruction that adds 1 to a register, then it is desirable to use the increment instruction whenever possible. There is also a minor problem that would result from an incorrect description of an instruction. This would cause incorrect code to be generated, but would be relatively easy to detect as that instruction would always be issued incorrectly.

A more serious problem is the lack of a method to determine whether the necessary set of conversion patterns have been supplied. These patterns are not obtained directly from a description of the instruction set, though some progress in this area is surely possible. It is mandatory that the patterns be complete. Any omission would cause the coder to block at some point and it would not be able to generate code for some legal expression. Without a set of sufficient conditions that will insure that a complete set of conversion patterns have been supplied, there will be no guarantee that the coder will not block on valid input.

#### 1.4.2.3. Analysis of Semantic Code Generation

Semantic code generation is a promising area in compiler research. It strives to free the compiler writer from having to painstakingly analyze numerous special cases when choosing code sequences, and allows the entire code generation process to be viewed from a higher, more abstract level. More of the implementor's time can be devoted to studying the problem instead of juggling the solution, analogous to coding in a high level language as opposed to assembly language. The fact that a code generator can be automatically created provides both the possibility of writing a practical, easily retargetable compiler and developing a convenient tool for investigating instruction set designs. Both are becoming increasingly important due to the number of microprogrammable computers appearing today. Such development tools are absolutely necessary if the increased flexibility provided by these new computers is to be fully utilized.

A major problem with code generation by semantic machine description is to determine the proper level at which to define the semantic model. A description at too high a level would possibly make implicit assumptions about the target computer that are not always true, leading to either inefficient or incorrect implementations. A description at too low a level would either be too difficult to use or would result in an inefficient code generator. Furthermore, certain computer architectures are difficult to model by a semantic description. Particularly notable are the 'super computers' of both past and present and the one chip microcomputers. The difficulty is perhaps inherent in their design rather than a shortcoming of semantic modeling. Such computers are a product of pushing available technology to its limits in order to achieve a cost or performance breakthrough. They were designed either for high speed or for low cost, not for programming ease. Finally, there is some question as to whether any completely general code generation scheme can produce reasonably good code in an acceptable amount of computer time.

#### 1.5. Summary of This Project

The approach taken in this dissertation is to implement a machine independent compiler for a specific programming language that can systematically be tailored to generate code for any specific computer. The input to the compiler that gives it this flexibility consists of both a list of implementation decisions and a semantic description of the target computer. The implementation decisions govern the method by which certain language constructs are to be implemented, hopefully in a way that is most amenable to the target computer. The semantic machine description is at a relatively high level. To compensate for this fact the compiler is tailored to produce an internal representation that favors the target computer's architecture, according to the implementation decisions made. As many machine independent optimizations as are judged worth while may be included in the compiler (constant folding, etc.). Specific data concerning the target machine is used to guide other machine dependent optimizations. A preprocessing algorithm is presented that reads the target machine instruction set description, in the form of an ambiguous context free grammar, and outputs tables that a machine independent code generation algorithm can use to produce object code for the machine described. Prior work in the area of parsing table construction using ambiguous grammars proved useful [Aho75]. The IR input to the code generator is biased by the implementation decisions in a way that will allow a simple, machine independent code generation strategy to generate reasonably good code. Finally, algorithms are developed to eliminate the possibility of the coder looping or blocking on valid input, resulting in a proof of correctness for the resulting code generator. A more detailed description of this process is given in the next chapter.

#### 1.6. Comparison with Compiler-Compilers

One may rightfully ask how this work differs from the compiler-compiler approach to compiler construction and language portability. It may appear to be just a subset of compiler-compiler research. This observation is in fact partially correct. However, the main difference is that compiler-compilers strive to be as general as possible, especially at the front end, allowing many radically different languages to be compiled, while this work is primarily concerned with the code generation phase of compiling. What has been done is, in effect, to fix the front half of a compiler-compiler system for a specific language and to concentrate on the relatively non-understood back half, primarily code generation. Practically speaking, in our design, the front end can be written as efficiently as standard one language / one machine compilers, something not currently possible with compiler-compilers. Consequently such a compiler can be used in a production environment. In a research environment, this work provides a valuable tool for experimentation with code generation schemes and related areas, including register allocation algorithms, determining the effectiveness of certain optimizations, and, perhaps most

importantly, allows the impact of different instruction sets on object code size and efficiency to be studied.

the first conservation is sufficiently belong the contract and the contract of the contract of

raphore the following as a second of the second of the contraction of

garan ing tidak ang antawa an interaktika tengah ang akan aga nagaran kebaba

. Para la material de la companya d

era da la comparta de la comparta d

at the conservation of the state of the stat

and the control of the community of the control of

and the control of th

a destruita de la capación de la companya de la capación de la capación de la capación de la capación de la ca La filoración de la capación de la

the second of th

Notable Communication (Albertain)

and the entry executive and expension

State of the second of the second protection

### Chapter 2: Design of a Machine Independent Compiler

This chapter discusses the overall design of a machine independent compiler. A compiler is a program that translates programs written in a programming language into machine instructions that can be directly executed by the target computer. This is in contrast to an interpreter that translates source programs into pseudo code, which is in turn interpreted by another program when being run. A machine independent compiler can be reconfigured in a systematic and well-defined manner to generate object code that can be executed on any specific target computer.

In particular this chapter discusses a generalized retargetable compiler. A compiler is retargetable if there is a well-defined procedure by which it can be altered to generate object code for a variety of different target computers, even though the compiler itself might need to be executed on a particular computer. A portable compiler is a retargetable compiler that can be made to execute on the new target computer as well. The act of altering a compiler so that it will execute on and produce code for a new computer is called transporting the compiler to the new computer. The language compiled by a portable compiler is also said to be portable, as it can be made to run on any computer by the transporting of its compiler. There are several ways to actually transport a portable compiler [Welsh72] [Pasko73] [Nori74] [Poole74] [Glanville76], the most popular being variations of bootstrapping in which the compiler is written in the language which it compiles and then used to compile itself into code for the new target computer.

The organization of the compiler is described with respect to these areas:

- 1) language dependent machine independent aspects,

- machine dependent aspects that have a small number of reasonable implementations,

- 3) strongly machine dependent aspects (i.e. code generation), and

- 4) the use and effectiveness of specific optimizations.

Emphasis is placed on producing a compiler that can be retargeted for a new computer with minimum effort, yet allows fast compilation and the generation of reasonably good object code. It is argued that such a compiler can be written with almost the same effort required to implement a single compiler for a single computer, and that such a compiler is desirable from a language standard point of view as it would aid program portability. The final section discusses various machine independent and machine dependent but parameterizable optimizations that can optionally be included, with some observations as to their cost and effectiveness.

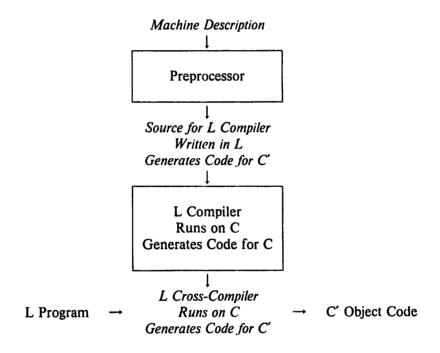

A compiler for a specific computer is generated by a preprocessor from a set of specifications that define the target computer and the implementation decisions to be used. The preprocessor can be thought of as a language dependent compiler-compiler. The input to the preprocessor is a list of implementation decisions, a list of machine instructions along with their semantics, and a set of parameters that describe the architecture of the target computer. The output consists of a program in some high level language which is the compiler. A general diagram of the compiler appears in Fig. 2.1. The implementor must also provide certain service routines that interface with the operating system under which the compiler will be run. These include routines for input and output, memory management, interprocess communication, and other local support.

Fig. 2.1. Generation of a Machine Dependent Compiler.

#### 2.1. Machine Independent Aspects

When compiling a program for a given language, there are certain tasks that must be done which are not dependent upon the target computer for which the code is to be generated. In fact, if a complete definition of the language is available, it is possible to write a parser and a semantic analyzer that would be adequate in a compiler for any target computer. The APT output of the recognition phase can also be in a machine independent language. Furthermore, a multitude of language dependent but computer independent optimizations can be performed,

either on the source language itself or on the intermediate text. These optimizations are discussed in Section 2.4.

In a machine independent compiler, machine independent aspects are programmed once and used in all implementations. When generating a new compiler for a new computer, the section of code for these aspects is simply copied. If the compiler is to be transported to new computers, instead of simply to be retargeted to produce code for them, the question arises of which language is to be used to write such a compiler. Assembly language is obviously not suitable, as it is both difficult to write in and, by nature, not readily transportable to new computers. High level programming languages, such as PL/I, FORTRAN or COBOL also have their problems. FORTRAN is available on most computers, but programs written in it are not necessarily portable. There are too many hardware and implementation dependent restrictions and 'enhancements', and it is not the ideal compiler implementation language. PL/I is better suited to compiler writing, but is available on only a few computers. Systems programming languages, such as PL/360, C, IMP, BLISS, and BCPL, are more suited to compiler writing but they are machine dependent and each is only available on a small number of computers.

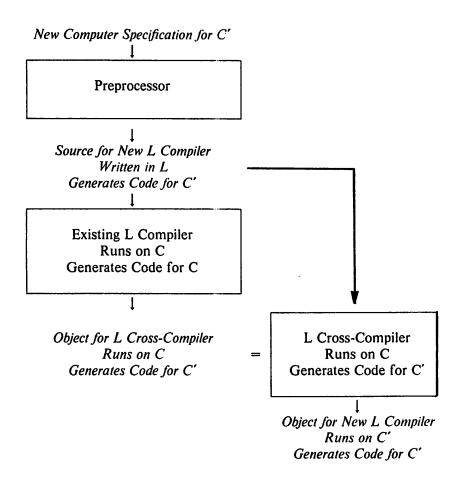

There are two immediate solutions to this dilemma. The first one applies only to those languages in which a compiler may easily be written. This method requires that the preprocessor and the machine independent compiler be written in the language to be compiled. Then it is a relatively simple task to bootstrap these programs onto another computer using the following steps: The specifications for the new implementation are input to the preprocessor and the source code for a compiler for the new computer is generated. That source is then compiled on the existing compiler and the resulting object code is a cross compiler that executes on the old computer and generates code for the new computer. Next, the source for the new compiler is compiled on the cross compiler, and the result is a compiler for the new computer. This process is illustrated in Fig. 2.2.

The second method would be used to implement machine independent compilers for languages which are not totally suited to compiler writing. The machine independent compiler is written in a language that either is already available on the new computer or is implemented via a similar machine independent compiler. The language used to implement the compiler for the new language is then transported to the new computer in the manner described above, if that language is not already available on the new computer. The machine semantics and implementation details for the primary language being transported are then input to the preprocessor, and source for the compiler that generates code for the new computer is output. This can then be compiled and run on the new computer via the existing secondary language compiler.

Fig. 2.2. Bootstrapping to a New Computer.

#### 2.2. Parameterizable Machine Dependent Implementation Decisions

There are certain implementation decisions that, though a single choice could be used for all target computers, can drastically affect the efficiency of the implementation. Such decisions should be made with an actual target computer in mind. An example is the run time display in ALGOL-like languages. On a computer with sufficient index or base registers, it may be best to keep the entire display in registers. On a computer with a few base or general purpose registers, it may be best to keep only the global and local displays in registers and access the others via the complete display stored in memory. Single register computers might do better allocating a fixed array in memory to the currently active display. The single register solution would work correctly on any computer, but certainly not as efficiently on most. The number of reasonable ways to implement the display, however, seems to be limited to these three. In fact, for a given language, there are many implementation decisions that appear to have only a few good choices on existing computers.

The idea of automatically tailoring the first part of a compiler to a specific target computer via a list of attributes of that computer is not new. The PASCAL-P compiler uses just such a scheme to automate variable allocation [Nori74]. The P compiler is actually the first half of a complete compiler. Source programs are translated into assembly language for a hypothetical stack computer, SC, with variable allocation and addressing governed by the machine dependent parameters supplied. Either the code can be interpreted (an interpreter written in PASCAL is supplied with the P-compiler), or various methods may be used to translate the assembly code for SC into object code for the target computer. Since the P-compiler is written in PASCAL, it is possible to bootstrap a compiler onto the new computer once this has been done. The P-compiler has been successfully bootstrapped onto a number of computers using this method, including the Univac 1108 and the IBM-360 [Richmond74], the PDP-11 [Bron76], and the PDP-10 [Grosse76], to mention a few.

When specifying a particular implementation of the machine independent compiler discussed in this dissertation, the implementor supplys a checklist of such implementation decisions. The preprocessor then emits the corresponding sections of code, in whatever language was used to implement the compiler, that correspond to the decisions. Since many such decisions are represented by a slight change to the IR produced in the translation phase, almost as macro expansions, this should not be a difficult task. Again, consider the ALGOL runtime display. The display is used to access variables. As discussed at length in Chapter 3, the IR is a low level representation of the program being compiled. Included in it are the implementation details of that particular compiler. So, any change in the implementation of the display will result in a corresponding change in the IR code to access variables that is input to the code generator. But this is a very local alteration to the IR, as if it were a macro substitution at each variable access. No other portion of the compiler need know about this decision (aside from the register allocator, which must not allocate any base registers, used to hold the display, for other tasks). The code generator blindly translates IR symbols into object code instructions, not knowing what ends they might accomplish.

Another example of an implementation decision that could be made via a checklist concerns the evaluation of Boolean expressions. It may be that the target computer has a set of efficient compare instructions that computes a Boolean result from two operands. In that case, it would be desirable to generate straightforward prefix code for the IR using relational operations. Otherwise, it might be best for the compiler to compute the value using conditional jumps [Bauer68] [Gries71] [Aho77b]. For example, the following Boolean expression:

could be represented in the two following pseudo target machine instruction sequences:

| load | r1,/         |                     | load | r1,/         |

|------|--------------|---------------------|------|--------------|

| lt   | r1, <i>J</i> |                     | comp | r1,J         |

| load | r2, <i>K</i> |                     | jge  | l.false      |

| ne   | r2,L         |                     | load | r1, <i>K</i> |

| and  | r1,r2        |                     | comp | r1, <i>L</i> |

|      |              |                     | jeq  | r1, l. false |

|      |              | l.true              | load | r1,=1        |

|      |              |                     | jump | next.ins     |

|      |              | l.false<br>next.ins | load | r1,=0        |

As the reader may have noticed, the two instruction sequences shown do not compute exactly the same expression. The first one evaluates the entire expression verbatim. It always compares K and L even though the result of the computation may have been determined by the comparison of I and J. (If one operand to a Boolean and operator is FALSE then the result will be FALSE regardless of the value of the other operand.) The second code sequence uses this fact to optimize the evaluation of the expression. If I is greater than or equal to J then a jump is made directly to the FALSE label.

There are several points to be considered concerning the evaluation of Boolean expressions. It is often a decision of the language designers to require full evaluation of Boolean expressions, to require the evaluation to stop as soon as the result can be determined (as in ALGOL-W [Bauer68] and BLISS-11 [Wulf75]), or to allow the implementor to make the decision (as in PASCAL [Jensen74]), either explicitly or accidentally. The last choice is undesirable since it may lead to problems when moving a program from one compiler to another. It is also important for the user to know which choice is being made. Consider the statement:

while

$$(i \leq MAXINDEX)$$

and  $(A[i] \neq x)$  do  $i := i + 1$ ;

where A is an array with dimension 1...MAXINDEX. The execution of this statement will sometimes result in a subscript referencing error when full evaluation is done, but never when minimal evaluation is used. Such expressions are also affected by the order of evaluation when the minimal computation method is used. In any event, the implementor of a compiler using the machine independent compiler described in this dissertation will not be making a choice of whether to use a partial or complete evaluation of Boolean expressions, as that is predetermined by the language being compiled. Instead the implementor decides whether Boolean compares are best implemented by arithmetic operations or conditional jumps on a particular target computer. It should also be noted that the compiler can often optimize jumps in a machine

independent manner, depending upon whether the Boolean value being computed is used in a flow of control test as in:

if

$$(i < j)$$

and  $(k \ne l)$  then ...

or an assignment statement:

Boolvar :=

$$(i < j)$$

and  $(k \neq l)$ ;

The difference stems from the fact that an **if** statement only needs to transfer control to one of two locations while the more general case of the use of a Boolean expression in the assignment statement requires some standard representation of TRUE or FALSE to be explicitly generated and stored into the variable *Boolvar*.

The PASCAL-P compiler requires 9 integer constants in order to specify a target computer. These constants are used to determine certain machine dependent limitations (such as maximum integer value accepted), how much storage to allocate for the basic types, and compiler limited constants (such as maximum string length). Figure 2.3 summarizes the required constants.

| Constant                                                               | Usage                                                                                                                                                                                                                          |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAXINT                                                                 | the largest integer which the compiler will process.                                                                                                                                                                           |

| CHARSIZE,<br>PTRSIZE,<br>INTSIZE,<br>BOOLSIZE,<br>REALSIZE,<br>SETSIZE | the number of basic, addressable storage units required to store the values of the indicated type. SETSIZE must be at least 59 as the P-compiler utilizes sets of that size. (Alignment boundaries are not handled).           |

| DIGMAX                                                                 | the maximum length string of characters which<br>may be used to represent unsigned numeric<br>constants. This allows the compiler to manipu-<br>late real values, which are not processed but<br>copied to the SC code output. |

| STRLGTH                                                                | the maximum length string that can be handled<br>by the computer. Must be greater than DIG-<br>MAX.                                                                                                                            |

Fig. 2.3. PASCAL-P Compiler Targeting Information.

#### 2.3. Code Generation

There are decisions that cannot be made without knowing certain facts about the target computer, most notably which object code instructions to issue and how much memory to allocate for variables and temporaries. The feasibility of a machine independent compiler depends upon the existence of a reasonably efficient generalized code generation algorithm. The efficiency of the code generator and of the code it generates will have a strong influence on the acceptance of the resulting compiler. The ease of specifying the instruction set semantics will largely determine the number of computers on which such compilers are implemented.

A major problem associated with a machine independent compiler is choosing which object code instructions to generate. This dissertation presents a model of computer instruction set semantics and a general code generation algorithm that facilitate the implementation of a code generator. The implementor supplies a list of the meanings of each instruction on the target computer to the preprocessor. The preprocessor outputs tables that are read by a machine independent code generator and are used to govern the object code generated at compile time. The task of determining which instruction or instructions to emit for a particular language construct is handled automatically by the algorithm.

#### 2.4. Optimization Phases

This section discusses modular code optimizations and how they could be included in the overall design of the machine independent compiler. Modular optimization passes can be conditionally selected by the user when desired, thus eliminating extra overhead when efficient execution is less critical (e.g. during program development). They would also provide researchers with a convenient tool with which to study various optimization techniques and instruction set designs. Empirical studies could be made to measure both the compile time cost and the efficiency improvements of the optimizations on actual programs.

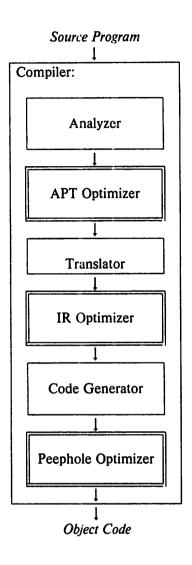

There are three places in the compiler that modular optimizations can conveniently be inserted. The first is as an APT to APT transformation that detects source language level optimizations. The second is an IR to IR translator that can utilize implementation dependent information, present in the IR, to perhaps produce better code than the first type of optimization. The last is peephole optimization that is used to improve the object code that has been generated by the code generator. Figure 2.4 shows the location of the optimizations in the compiler. Some of the optimizations presented are implementable in a totally language-dependent and machine-independent manner as a transformation of the APT. However, a much greater improvement in the code generated is possible if they are applied after the introduction of implementation dependent information. Some are only applicable in certain

implementations and not in others. In any event, it is usually desirable to introduce optimizations after a point at which the implementation dependent information is known.

Fig. 2.4. Three Places for Modular Optimization.