## Copyright © 1975, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Page 21

((n-1)a)

$$g_1(v) + g_2(v) + ... + g_{n-1}(v) \ge 0$$

whenever  $v_k \ge 0$

((n-1)b)

$$g_1(v) + g_2(v) + ... + g_{n-1}(v) \le 0$$

whenever  $v_k \le 0$

for all

$$k = 1, 2, ..., n-1$$

#### Page 34

(b) If the input terminal (a) and output terminal (c) are connected together, and it is assumed that there are no internal connections to either (a) or (c),  $^{17}$  then the bounding region of Fig. 8(b) shrinks to that shown in Fig. 8(c).

<sup>17</sup> This somewhat specialized condition will turn out to be relevant to the proof of Property 17. The connection shown is one that would seldom be encountered, in a network used for obtaining TC plots.

# QUALITATIVE PROPERTIES OF RESISTIVE NETWORKS CONTAINING MULTI-TERMINAL NONLINEAR ELEMENTS

Ъу

L. O. Chua, Y-F Lam and L. A. Stromsmoe

Memorandum No. ERL-M575

17 December 1975

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

## QUALITATIVE PROPERTIES OF RESISTIVE NETWORKS CONTAINING MULTI-TERMINAL NONLINEAR ELEMENTS

L.O. Chua, Y-F Lam, and K.A. Stromsmoe

#### ABSTRACT

This paper is concerned with the qualitative properties of nonlinear multiterminal resistors and nonlinear resistive networks--properties which give results that require neither computation nor equation formulation. The basic circuit theoretic concepts of passivity, local passivity, monotonicity, activity and local activity are defined and properties are developed that relate these fundamental concepts. The notion of "no-power gain" and that of "no-voltage gain" or "no current gain" are shown to be in general distinct from one another. The concept of no-gain elements is generalized to include multi-terminal elements. The main result obtained is that an n-terminal element possesses the no-gain property if, and only if, at each operating point, a connected network of n-1 positive linear two-terminal resistors exists which has the same operating point. This generalization serves as a basic tool for the derivation of bounds on the two most useful characterizations for nonlinear resistive networks; namely, the driving point (DP) and the transfer characteristic (TC) plots. The sharpest possible bounding regions are obtained for a large class of nonlinear networks--including networks which use operational amplifiers as one of the main elements.

The concepts of symmetric and complementary symmetric networks are introduced and used to show that various classes of networks have either <u>odd</u> or <u>even symmetric</u> DP and TC plots. Again when operational amplifiers are used as a basic circuit element, it is shown that many operational amplifier circuits exhibit odd symmetric DP and TC plots.

Finally, the concepts of locally no-gain n-ports and locally no-gain networks are introduced and it is shown that these concepts are related to the classical n-port resistor synthesis problem.

<sup>†</sup>Research Sponsored by the National Science Foundation Grant ENG72-03783 and the Naval Electronics System Command Contract N00039-75-C-0034/N00039-76-C-0022.

This.O. Chua and Y-F Lam are with the Department of EECS University of California, Berkeley, California and K.A. Stromsmoe is with the Department of Electrical Engineering, University of Alberta, Edmonton, Alberta, Canada.

## I. INTRODUCTION

Much research has been directed to the study of resistive nonlinear networks over the last decade. Most of these research activities can be grouped under the category of "existence and uniqueness results" [1], or under the category of "computational techniques" [2]. Very little research has been devoted to deriving results of a more qualitative nature — i.e. results which do not involve any computation or equation formulation—until the recent work by Willson on the nogain property for networks containing three-terminal elements [3]. Our objective in this paper is to derive qualitative properties for the two most useful and commonly specified characterizations of resistive nonlinear networks; namely, the associated driving—point and transfer characteristic plots 1— henceforth abbreviated simply as DP and TC plots [4]. In particular, we will show in Section IV that the DP and TC plots of various classes of resistive nonlinear networks must necessarily lie within some bounding regions. These bounding regions are the best possible that can be found and they can be determined by inspection of the network topology and the element constitutive relations.

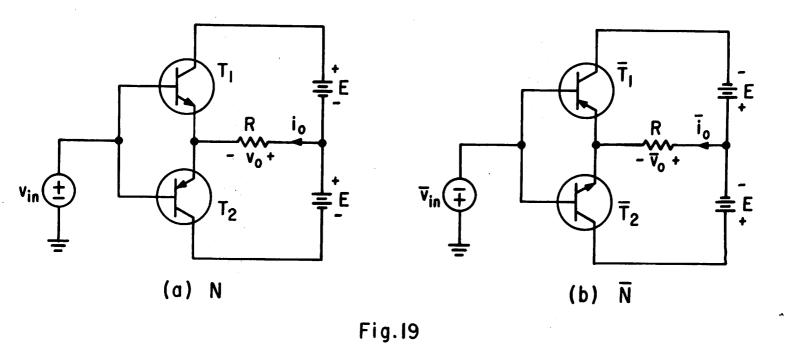

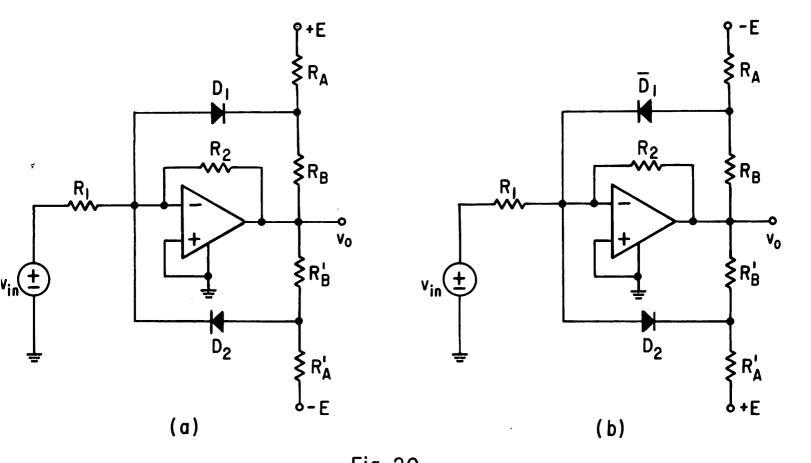

Another important qualitative property that will be derived in this paper is the conditions which guarantee that the DP plot or TC plot of various classes of networks will exhibit some form of symmetry. For example, it is generally known—though never explicitly pointed out—that the DP plot and TC plot of any circuit made up exclusively of operational amplifiers and bilateral two—terminal resistors (characterized by odd—symmetric v—i curves) are always odd symmetric regardless of the network topology [5]. It turns out that this is due to the fact that an operational amplifier satisfies a more subtle form of symmetry called "complementary symmetry" to be presented in Section V. This new concept does not require the network to display any topological symmetry and is therefore applicable to a very large class of practical networks.

For complete generality, we will allow our networks to contain not only two-terminal or three-terminal elements, but also multi-terminal elements such as <u>operational amplifiers</u> and <u>analog multipliers</u> [6], having more than three terminals. Since the key to our derivation of the bounding regions in Section IV is precisely the "no-gain property" of many solid state

We use the term "plot" and not "function" as normally found in linear network literatures because the driving-point and transfer characteristics for nonlinear networks could be multivalued and are therefore not functions.

devices, it is essential to generalize Willson's results in [3] to allow n-terminal elements. This turns out to be a non-trivial task because the formulation and methods of proof given in [3] are not suited for generalization to the multiterminal cases. Hence, a completely different approach has been developed and is presented in <u>Section III</u>. Even though the results in this section are used only as a tool for deriving the bounding regions in Section IV, they are of a rather basic nature and will no doubt find other applications in future works.

Willson has shown that passivity is only a necessary condition for 3-terminal no-gain elements. This observation is also true for n-terminal elements when n > 3. It is not surprising that this is the case since the concept of passivity is more germane to a study of power gain, and not voltage gain, or current gain. Indeed, it follows from Tellegen's theorem that to obtain power gain in a network N, it is necessary that at least one element of N be active. Hence passivity is synonymous to "no-power gain"; i.e., the power gain is not greater than unity. It has very little to do with voltage gain or current gain as aptly demonstrated by the ideal transformer which is passive but is capable of either a voltage gain, or a current gain greater than unity. Since all realistic models of real multiterminal devices must be passive, the more important notion is really that of local activity in so far as obtaining greater-than-unity local power gain is concerned. From a circuit-theoretic point of view, it is important that concepts which are relevant to power gain be clearly separated from those which are relevant to voltage gain or current gain. Hence it is appropriate that we first present a study of power-gain related concepts in Section II. In particular, we will present a careful study of the relationships between passivity and local passivity; as well as between monotonicity and local passivity for multi-terminal elements. The results in this section are relevant for a firm understanding of the results in section III.

Finally, since this paper is addressed exclusively to networks containing only dc independent voltage and current sources as well as <a href="mailto:multi-terminal">multi-terminal</a> resistors [4] defined by

$$f_1(v_1, v_2, ..., v_n, i_1, i_2, ..., i_n) = 0, i = 1, 2, ..., n$$

we will use the word "elements" and "resistors" interchangeably.

CONCEPTS AND PROPERTIES RELATED TO POWER GAIN

Our objective in this section is to study the relationship between a number

of circuit-theoretic concepts which are relevant to the study of <u>power gain</u> of multi-port nonlinear resistive networks.

<u>Definition 1</u> Passive and Locally Passive Resistors

An n-port resistor  ${\mathcal R}$  is said to be passive if, and only if, the scalar product

$$\langle \mathbf{v}, \mathbf{i} \rangle \stackrel{\Delta}{=} \sum_{j=1}^{n} \mathbf{v}_{j} \mathbf{i}_{j} \geq 0$$

(1)

7

1

for all admissible signal pairs (v,i). It is said to be locally passive if, and only if

$$\langle \delta y, \delta z \rangle \geq 0$$

(2)

for all admissible incremental signal pairs  $(\delta v, \delta i)$  about each operating point Q of R. It is said to be <u>strictly passive</u> if the <u>strict</u> inequality sign holds in (1) whenever  $v \neq 0$  and  $v \neq 0$ , and <u>strictly locally passive</u> if the <u>strict</u> inequality sign holds in (2) whenever  $\delta v \neq 0$  and  $\delta v \neq 0$ . The element R is said to be active if it is not passive and <u>locally active</u> if it is not locally passive.

#### <u>Definition 2</u> Monotone-Increasing Resistors

An n-port resistor  $\mathcal R$  is said to be monotone increasing if, and only if,

$$\langle \mathbf{y}^{\dagger} - \mathbf{y}^{\dagger}, \mathbf{i}^{\dagger} - \mathbf{i}^{\dagger} \rangle > 0 \tag{3}$$

for any two admissible signal pairs (v',i') and (v",i"). It is said to be <u>strictly</u> monotone increasing if the <u>strict</u> inequality holds in (3) for any two <u>distinct</u> admissible signal pairs.

For simplicity, we will assume throughout this section that our n-port resistor  $\Re$  is characterized by a C<sup>1</sup>-hybrid representation<sup>2</sup>

$$\dot{\underline{z}}_{a} = \dot{\underline{h}}_{a} (\dot{\underline{v}}_{a}, \dot{\underline{z}}_{b})$$

$$v_{b} = \dot{\underline{h}}_{b} (v_{a}, \dot{\underline{z}}_{b})$$

$$\wedge \quad t \quad t \quad t$$

(4)

where

$$\underline{\mathbf{y}} \stackrel{\Delta}{=} [\underline{\mathbf{y}}_a^t \underline{\mathbf{y}}_b^t]^t$$

and  $\underline{\mathbf{i}} = [\underline{\mathbf{i}}_a^t \underline{\mathbf{i}}_b^t].$

For a more general parametrizable case, see [7].

A simple characterization of monotone-increasing resistors was given in [8] and is reproduced here since it will be needed in the proof of Property 2.

## <u>Property 1</u> Monotone Increasing Criteria

An n-port resistor  ${\mathcal R}$  is monotone-increasing if, and only if, its incremental hybrid matrix

$$\underbrace{\mathbb{H}(\mathbf{y}_{\mathbf{a}}, \mathbf{i}_{\mathbf{b}})} \stackrel{\triangle}{=} \begin{bmatrix} \frac{\partial \mathbf{h}_{\mathbf{a}}}{\partial \mathbf{z}_{\mathbf{a}}} & \frac{\partial \mathbf{h}_{\mathbf{a}}}{\partial \mathbf{i}_{\mathbf{b}}} \\ \frac{\partial \mathbf{h}_{\mathbf{b}}}{\partial \mathbf{y}_{\mathbf{a}}} & \frac{\partial \mathbf{h}_{\mathbf{b}}}{\partial \mathbf{i}_{\mathbf{b}}} \end{bmatrix} = \begin{bmatrix} \mathbf{H}_{\mathbf{a}\mathbf{a}} & \mathbf{H}_{\mathbf{a}\mathbf{b}} \\ \mathbf{H}_{\mathbf{b}\mathbf{a}} & \mathbf{H}_{\mathbf{b}\mathbf{b}} \end{bmatrix} \tag{5}$$

is positive semi-definite<sup>3</sup> for all  $(v_a, i_b)$ . Moreover, if  $H(v_a, i_b)$  is positive definite<sup>3</sup> then R is strictly monotone-increasing.

The next property shows that the circuit theoretic concept of local passivity and the mathematical concept of monotonicity are equivalent to each other.

### Property 2. Equivalent Local Passivity Criteria

An n-port resistor  $\mathbb{Q}$  is <u>locally passive</u> {resp., <u>strictly locally passive</u>} if, and only if, it is <u>monotone increasing</u> {resp., strictly monotone increasing}.

#### Proof.

$$\langle \delta \tilde{\mathbf{y}}, \delta \tilde{\mathbf{i}} \rangle = \langle \delta \tilde{\mathbf{y}}_{\mathbf{a}}, \delta \tilde{\mathbf{i}}_{\mathbf{a}} \rangle + \langle \delta \tilde{\mathbf{y}}_{\mathbf{b}}, \delta \tilde{\mathbf{i}}_{\mathbf{b}} \rangle$$

$$= \langle \delta \tilde{\mathbf{y}}_{\mathbf{a}}, \tilde{\mathbf{H}}_{\mathbf{a}\mathbf{a}} \delta \tilde{\mathbf{y}}_{\mathbf{a}} + \tilde{\mathbf{H}}_{\mathbf{a}\mathbf{b}} \delta \tilde{\mathbf{i}}_{\mathbf{b}} \rangle + \langle \tilde{\mathbf{H}}_{\mathbf{b}\mathbf{a}} \delta \tilde{\mathbf{y}}_{\mathbf{a}} + \tilde{\mathbf{H}}_{\mathbf{b}\mathbf{b}} \delta \tilde{\mathbf{i}}_{\mathbf{b}}, \delta \tilde{\mathbf{i}}_{\mathbf{b}} \rangle$$

$$= [\delta \tilde{\mathbf{y}}_{\mathbf{a}}^{\mathsf{t}} \delta \tilde{\mathbf{i}}_{\mathbf{b}}^{\mathsf{t}}] \tilde{\mathbf{H}} (\tilde{\mathbf{y}}_{\mathbf{a}}, \tilde{\mathbf{i}}_{\mathbf{b}}) [\delta \tilde{\mathbf{y}}_{\mathbf{a}}^{\mathsf{t}} \delta \tilde{\mathbf{i}}_{\mathbf{b}}^{\mathsf{t}}]^{\mathsf{t}} \geq 0$$

Hence  $\langle \delta y, \delta i \rangle$  is non-negative {resp., positive} if, and only if,  $H(y_a, i_b)$  is positive semi-definite {resp., positive definite} and the conclusion follows from Property 1.

#### Property 3 Necessary Condition for Passivity

An n-terminal resistor  ${\mathcal R}$  characterized by a continuous hybrid representation

A not necessarily symmetric n×n matrix M is said to be positive semi-definite if, and only if,  $x^t \stackrel{M}{M} x > 0$  for any  $x \in \mathbb{R}^n$ . It is said to be positive definite if, and only if,  $x^t \stackrel{M}{M} x > 0$  for any  $x \neq 0$ . It is easy to prove that M is positive semi-definite or positive definite if, and only if, its symmetrical part  $M + M^t$  is positive semi-definite or positive definite, respectively.

of (4) is passive only if its constitutive relation passes through the origin.

<u>Proof.</u> Suppose  $(\underline{I}_a,\underline{E}_b) = (\underline{h}_a(\underline{0},\underline{0}),\underline{h}_b(\underline{0},\underline{0})) \neq (\underline{0},\underline{0})$ . Then at least one component of  $(\underline{I}_a,\underline{E}_b)$  is nonzero. Without loss of generality, let  $\underline{I}_1 \neq 0$ .

ž,

1

Assume first I > 0. Since  $h_a(0,0)$  is continuous, there exists an open ball  $B_{\epsilon}$  defined by

$$B_{\varepsilon} \stackrel{\Delta}{=} \{ (\underline{v}_{a}, \underline{i}_{b}) \in \mathbb{R}^{n} \colon \|\underline{v}_{a}\|^{2} + \|\underline{i}_{b}\|^{2} < 2\varepsilon > 0 \}$$

(6)

such that  $\mathbf{i}_1 = \mathbf{h}_1(\mathbf{v}_a, \mathbf{i}_b) > 0$  for all  $(\mathbf{v}_a, \mathbf{i}_b)$  in  $\mathbf{B}_{\varepsilon}$ . Consider a point  $(\mathbf{v}_a', \mathbf{i}_b') = (-\varepsilon, 0, 0, \dots, 0)$  in  $\mathbf{B}_{\varepsilon}$ . Let  $\mathbf{i}_a' = \mathbf{h}_a(\mathbf{v}_a', \mathbf{i}_b')$  and  $\mathbf{v}_b' = \mathbf{h}_b(\mathbf{v}_a', \mathbf{i}_b')$ . Then

$$\langle \mathbf{v}^{\dagger}, \mathbf{i}^{\dagger} \rangle = - \epsilon h_{1}(\mathbf{v}_{a}^{\dagger}, \mathbf{i}_{b}^{\dagger}) < 0$$

(7)

Similarly if  $I_1 < 0$ , then there exists an open ball  $B_{\hat{\epsilon}}$  as defined in (6) with  $\epsilon$  replaced by  $\hat{\epsilon}$ , such that  $i_1 = h_1 \ (v_a, i_b) < 0$  for all  $(v_a, i_b)$  in  $B_{\hat{\epsilon}}$ . In particular, let us consider the point  $(v_a, i_b) = (\hat{\epsilon}, 0, 0, \dots, 0)$  in  $B_{\hat{\epsilon}}$ . Let  $i_a = h_a \ (v_a, i_b)$  and  $v_b = h_b \ (v_a, i_b)$ . Then

$$\langle \mathbf{v}'', \mathbf{i}'' \rangle = \hat{\varepsilon} \ \mathbf{h}_{1}(\mathbf{v}_{a}, \mathbf{i}_{b}) < 0$$

(8)

Together (7) and (8) imply that if  $I_1 \neq 0$ , then  $\mathcal{R}$  is not passive. Since  $\mathcal{R}$  is passive by hypothesis,  $I_1 = 0$ . By repeating the above procedure for all components of  $(I_a, E_b)$ , we conclude that  $(I_a, E_b) = (0, 0)$ .

A <u>locally passive</u> n-terminal resistor need not be passive, and vice-versa. The precise relationship between the two is given by the next property.

## Corollary 3.1 Passivity and Local Passivity Relationship

A locally passive n-terminal resistor  $\mathcal{R}$  characterized by a  $C^1$ -hybrid representation of (4) is passive if, and only if, its constitutive relation passes through its origin.

<u>Proof.</u> A. Sufficiency: It follows from Property 2 that  $\mathcal{R}$  is <u>locally passive</u> if, and only if,  $\langle \underline{v}' - \underline{v}'', \underline{i}' - \underline{i}'' \rangle \geq 0$  for any two admissible pairs  $(\underline{v}', \underline{i}')$  and  $(\underline{v}'', \underline{i}'')$ . Now choose  $(\underline{v}''_a, \underline{i}''_b) = (0, 0)$ . Thus by hypothesis, this implies that  $(\underline{i}''_a, \underline{v}''_b) = (0, 0)$  and we have  $\langle \underline{v}' - \underline{v}'', \underline{i}' - \underline{i}'' \rangle = \langle \underline{v}', \underline{i}' \rangle \geq 0$  for any admissible pair  $(\underline{v}', \underline{i}')$ . Hence  $\mathcal{R}$  is passive.

B. Necessity: This follows directly from Property 3.

¤

Corollary 3.2 Strict Passivity and Strict-Local Passivity Relationship

A strictly locally passive n-terminal resistor R characterized by a C<sup>1</sup>-hybrid

representation of (4) is strictly passive if, and only if, its constitutive

relationship passes through the origin.

In the study of active networks, it is usually desirable to have some simple criteria for ascertaining whether an n-terminal resistor is active, or locally active. The following properties provide convenient sufficient conditions for this purpose.

## Property 4 Activity Criteria

Let  $\mathcal{R}$  be an n-terminal resistor having a terminal voltage  $v_k$  {resp.; terminal current  $i_k$ } which does not depend upon its associated terminal current  $i_k$  {resp.; terminal voltage  $v_k$ }, and is not identically zero; i.e.,

$$v_k = f_k(x_1, x_2, ..., x_{k-1}, x_{k+1}, ..., x_n) \stackrel{\triangle}{=} f_k(\bar{x})$$

(9)

{resp.;

$$i_k = g_k(x_1, x_2, ..., x_{k-1}, x_{k+1}, ..., x_n) \stackrel{\triangle}{=} g_k(x)$$

} (10)

where  $x_j$  denotes either  $v_j$  or  $i_j$  for each  $j \neq k = 1, 2, \ldots, n$ , and  $x = [x_1, x_2, \ldots, x_{k-1}, x_k, x_{k+1}, \ldots, x_n]^t$  with  $x_k = i_k$  {resp.;  $x_k = v_k$ }. Let  $y_j$  be the complementary variable, i.e.,  $y_j = v_j$  if  $x_j = i_j$  and  $y_j = i_j$  if  $x_j = v_j$ . If  $y_j$  does not depend upon  $i_k$  {resp.;  $v_k$ } for all  $j \neq k$ , then R is active.

<u>Proof</u>. We will prove the case corresponding to  $f_k(x)$  of (9) only.

Since  $f_k(\bar{x})$  is not identically zero by hypothesis, there exist  $\bar{x}$  such that  $f_k(\bar{x}) \neq 0$ . Choose

$$i_{k} = \overline{i}_{k} > 0 \text{ if } f_{k}(\overline{x}) \triangleq \overline{v}_{k} < 0$$

$$= \overline{i}_{k} < 0 \text{ if } f_{k}(\overline{x}) \triangleq \overline{v}_{k} > 0$$

(11)

Then

$$\langle \mathbf{v}, \mathbf{i} \rangle = \sum_{\substack{j=1 \ j \neq k}}^{n} \mathbf{v}_{j} \mathbf{i}_{j} + \mathbf{v}_{k} \mathbf{i}_{k}$$

(12)

Since  $\bar{x}_j$  is an independent variable and  $\bar{y}_j$  does not depend on  $\bar{i}_k$  by hypothesis, and

since  $\bar{v}_k$   $\bar{i}_k$  <0, we can always choose  $\bar{i}_k$  sufficiently large such that  $\langle v, v \rangle < 0$ . Hence  $\hat{R}$  is active.

## Property 5. Local Activity Criteria

An n-terminal resistor  $\mathcal R$  is locally active if there exists an operating-point Q having an incremental voltage  $\delta v_k$  {resp.; an incremental current  $\delta i_k$ } about Q, which does not depend upon its associated incremental current  $\delta i_k$  {resp.; incremental voltage  $\delta v_k$ }, and is not identically zero; i.e.,

$$\delta v_{k} = f_{k}(\delta x_{1}, \delta x_{2}, \dots, \delta x_{k-1}, \delta x_{k+1}, \dots, \delta x_{n}) \stackrel{\Delta}{=} f_{k}(\delta x)$$

(13)

{resp.;

$$\delta i_k = g_k(\delta x_1, \delta x_2, \dots, \delta x_{k-1}, \delta x_{k+1}, \dots, \delta x_n) \stackrel{\Delta}{=} g_k(\delta x)$$

} (14)

where  $\delta x_j$  denotes either  $\delta v_j$  or  $\delta i_j$   $\delta x_j = \left[\delta x_1, \delta x_2, \cdots, \delta x_{k-1}, \delta x_k, \delta x_{k+1}, \cdots, \delta x_n\right]^t$  with  $\delta x_k = \delta i_k$  {resp.;  $\delta x_k = \delta v_k$ }, and if the complementary variable  $\delta y_j$  of  $\delta x_j$  does not depend upon  $\delta i_k$  {resp.;  $\delta v_k$ } for all  $j \neq k = 1, 2, \cdots, n$ , then Q is locally active.

<u>Proof.</u> The proof of Property 5 is similar to that of Property 4 and is therefore omitted.

Observe that in order for these properties to hold, both  $f_k(\cdot)$  {resp.;  $g_k(\cdot)$ } and the remaining dependent variables  $y_j$  must not depend upon  $i_k$  or  $\delta i_k$  {resp.,  $v_k$  or  $\delta v_k$ }. For example, an ideal grounded two-port transformer characterized by  $v_2 = nv_1$  and  $i_1 = -ni_2$  satisfies the first condition ( $v_2$  is independent of  $v_2$ ) but not the second condition ( $v_2$  depends on  $v_2$ ). Indeed, this element is non-energic and is therfore passive. It follows immediately from Property 4 that the ideal linear operational amplifier (characterized by  $v_2 = 0$ , and  $v_3 = A(v_2-v_1)$ ) and the ideal analog multiplier (characterized by  $v_2 = 0$ , and  $v_3 = v_1v_2$ ) are both active 4-terminal elements. Similarly, all controlled sources are active. It also follows from Property 5 that any 3-terminal element having an incremental circuit model characterized by a transfer conductance function  $v_2 = f(v_1)$  and  $v_3 = v_1v_2$  are both active 4-terminal elements of  $v_3 = v_1v_2$  are both active 4-terminal elements. Similarly, all controlled sources are active. It also follows from Property 5 that any 3-terminal element having an incremental circuit model characterized by a transfer conductance function  $v_2 = f(v_1)$  and  $v_3 = v_1v_2$  and  $v_4 = v_1v_2$  and  $v_4 = v_1v_2$  and  $v_4 = v_1v_2$  and  $v_4 = v_1v_2$  are both active transfer resistance function  $v_2 = f(v_1)$  and  $v_3 = v_1v_2$  and  $v_4 = v_1v_2$  and  $v_4 = v_1v_2$  and  $v_4 = v_1v_2$  are both active transfer resistance function  $v_2 = f(v_1)$  and  $v_3 = v_1v_2$  and  $v_4 = v_$

#### III CONCEPTS AND PROPERTIES RELATED TO VOLTAGE AND CURRENT GAIN

In this section we consider various aspects of <u>no-gain circuits</u> [3,9,10]. Necessary and sufficient conditions are given to establish the relationship between a multi-terminal resistor and a no-gain element. The implications of these conditions on the representation of a multi-terminal resistor are examined. In particular, the constraints imposed upon "<u>locally no-gain elements</u>" are derived. These constraints turn out to be extremely strong, thereby implying the rather surprising observation that most multi-terminal elements  $(n \ge 3)$  should be capable of incremental voltage or current gain.

Finally to investigate the no-gain property of circuits containing elements such as ideal diodes whose constitutive relations fall right on the passivity boundary, we introduce the concept of "weakly no-gain elements" and derive their properties.

#### A. No-Gain Elements

## Definition 3 Q-loop and Q-cutset

An <u>S-loop</u> {resp.; <u>O-cutset</u>} is a loop {resp.; cutset} consisting of short {resp.; open} circuit elements only. An <u>aligned loop</u> {resp.; <u>cutset</u>} is a loop {resp.; cutset} for which the reference directions of all elements composing it have the same orientation.

To provide an important tool for the derivation of the main theorem in this section, "criteria for no-gain n-terminal resistors", we need to generalize the results of Wolaver in [10] to include both short circuit and open circuit elements. This generalization requires the use of the following two special cases of Minty's color arc Theorem [11]:

#### Lemma 1

(a) Let  $\mathcal B$  be the set of all branches in a network containing only two-terminal elements, and let b be an element of  $\mathcal B$ . Let  $\mathcal L$  and  $\mathcal C$  be any two subsets of  $\mathcal B$  such that  $\mathcal B$  = b  $\cup \mathcal L \cup \mathcal C$  and  $\mathcal L \cap \mathcal C$  is an empty set. Then b forms a loop exclusively with elements in  $\mathcal L$  or a cutset exclusively with elements in  $\mathcal C$ , but not both.

For brevity, a multi-terminal element is simply called an n-terminal element, where "n" is used in the generic sense, and  $n \ge 2$ .

- (b) In a network with the associated reference directions assigned to the elements each branch lies in either an aligned loop or an aligned cutset, but not both.

- Property 6 No Gain Property for Networks Containing Two-Terminal Elements

Given a network containing independent voltage and current sources, positive

linear two-terminal resistors, 6 short circuit elements which do not form 9-loops

and open circuit elements which do not form 9-cutsets, 7 then

- 1) the current magnitude through any element 8 is not greater than the sum of the current magnitudes through all independent voltage and current sources.

- 2) the voltage magnitude across any element <sup>8</sup> is not greater than the sum of the voltage magnitudes across all independent voltage and current sources.

<u>Proof.</u> We will prove the current magnitude case only. The voltage magnitude case can be proven in a dual manner.

The current magnitude through any independent source or open circuit element satisfies the conclusion trivially. Hence, we only have to consider the current magnitude through any short circuit element or any positive linear resistor.

To consider the current magnitude through any positive resistor R, we can coalesce any two nodes connected by a short circuit element, and delete all open circuit elements. The resulting circuit contains only independent sources and positive linear two-terminal resistors. Hence, the result of Wolaver's Theorem [10] applies—the current magnitude through any positive linear resistor is not greater than the sum of the current magnitudes through the sources.

It remains to consider the current magnitude through a short circuit element s. Without loss of generality, let us delete all open circuit elements. Since the network contains no S-loops, it follows from the color arc Lemma 1(a) that 5 The reference current of each branch enters the positive terminal of the referenced voltage of the same branch.

3

$<sup>^{6}\</sup>text{A}$  two-terminal positive linear resistor has a resistance R restricted by 0 < R <  $\infty.$

Clearly, if there is an S-loop in a circuit N, then a circulating current of arbitrary magnitude can be sustained by the short circuit elements forming this S-loop. In a dual manner, if there is an S-cutset, then the voltages across the open circuit elements forming this S-cutset can be raised by an arbitrary level, without affecting the branch voltages of other circuit elements inside N. Hence, any network containing an S-loop or S-cutset can not exhibit the no-gain property.

$<sup>^{8}</sup>$ This includes open and short circuit elements.

the short circuit element s must form a cutset exclusively with positive linear resistors and independent sources. (Choose b=s, ==set of all short circuit elements, and C=remaining elements.) Hence, as far as the current through s is concerned, there is no loss of information to coalesce any two nodes connected by a short circuit with the exception of s. The resulting circuit contains positive linear resistors, independent sources and the short circuit element s. We now use this simplified circuit to investigate the current is through the short circuit element s.

If s forms a cutset exclusively with independent sources, then i is given by an alegbraic sum of currents through the independent sources in the cutset. In this case, the conclusion follows trivially.

Suppose the short circuit element s does not form a cutset exclusively with independent sources. In this case, we let the associated reference directions of all positive linear resistors and independent sources be chosen such that all voltages across them are positive. It is clear that no matter which reference direction is assigned to s, there can be no aligned loop that contains s. (Otherwise there will be a loop containing positive-voltage branches and a zero-voltage branch thereby violating KVL.) It follows from Lemma 1(b) that there is a cutset  $C_s$  containing s such that the reference directions of all elements in  $C_s$ , except s, have the same orientation. The associated reference direction of s can be selected to coincide with those associated with the other elements in  $C_s$ . Hence,  $C_s$  is then an aligned cut set. Let A be the set of all positive linear resistors in  $C_s$  and let B be the set of all independent sources in  $C_s$ . It then follows from KCL that,

$$i_s + \sum_{k \in A} i_k + \sum_{j \in B} i_j = 0$$

(15)

Since all positive linear resistors have positive voltages,  $i_k \ge 0$  for all  $k \in A$ . Hence, (15) implies that

$$\left|\mathbf{i}_{\mathbf{s}}\right| \leq -\sum_{\mathbf{j} \in \mathbf{B}} \mathbf{i}_{\mathbf{j}} \leq \sum_{\mathbf{j} \in \mathbf{B}} \left|\mathbf{i}_{\mathbf{j}}\right| \tag{16}$$

The term on the right of (16) is no greater than the sum of the current magnitudes of all independent sources, the conclusion of Property 6 follows.

This completes the proof of Property 6.

#### Definition 4 No-Gain Networks

A resistive network is said to possess the <u>no-gain property</u> if each solution at any time is such that, (a) the magnitude of the voltage between any pair of nodes in the network is less than or equal to the sum of the magnitudes of the voltages appearing across the independent voltage and current sources, and (b) the magnitude of the current flowing into each terminal of every element is less than or equal to the sum of the magnitudes of the currents flowing through the independent voltage and current sources.

9

#### Definition 5 No-Gain Resistor

An n-terminal ( $n \ge 2$ ) resistor  $\mathbb R$  is said to be a <u>no-gain resistor</u> if each connected network containing  $\mathbb R$ , positive linear two-terminal resistors, short and open circuit elements which do not form  $\mathbb S$ -loops and  $\mathbb S$ -cutsets respectively, and nonzero independent voltage and current sources, <u>possesses the no-gain</u> property.

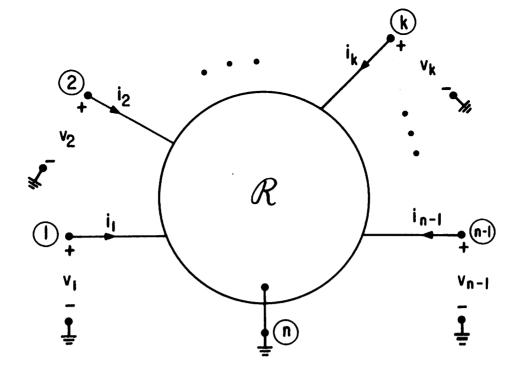

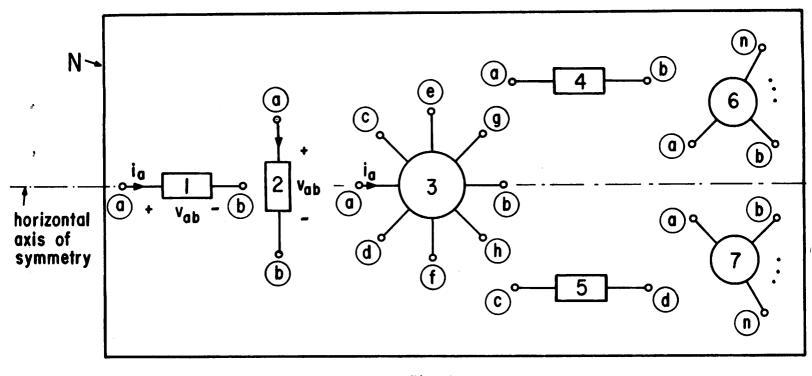

#### Reference Directions

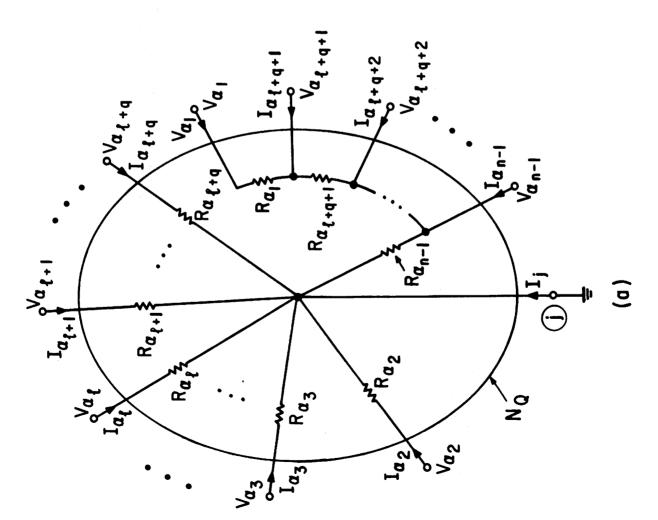

Unless specified otherwise, an n-terminal element has the reference directions shown in Fig. 1, where all voltages are assumed to be node-to-datum voltages and all terminal currents are assumed to enter the n-terminal element.

#### Theorem 1 The No-Gain Resistor Criteria

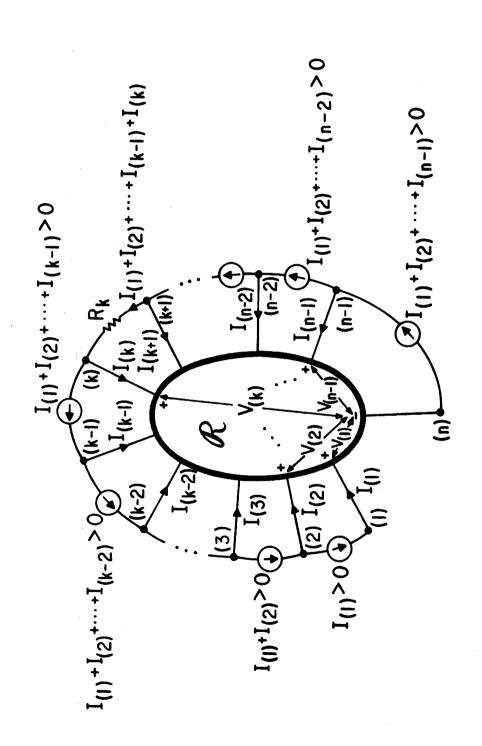

An n-terminal resistor  $\mathbb Q$  is a <u>no-gain resistor</u> if, and only if, at each dc operating point  $\mathbb Q$  of  $\mathbb Q$ , there exists a connected n-terminal network  $\mathbb N_{\mathbb Q}$  containing n-1 linear positive two-terminal resistors which has the same operating point.

#### Proof

A. Sufficiency: Let  $\widehat{\mathcal{R}}$  be imbedded in any connected network N containing only positive linear two-terminal resistors, short and open circuit elements which do not form S-loops and  $\widehat{\mathbb{C}}$ -cutsets respectively, and nonzero independent voltage and current sources. Let  $\widehat{\mathbb{Q}}$  be an operating point of the network and let  $\mathbb{Q}$  be the

Observe that the definition of a no-gain n-terminal resistor here differs from that given in [3]. One could argue that Willson had actually used the present definition in his proof of Theorem 2, when he connected terminals 2 and 3 together in Fig. 13(a) in [3] for the case where  $\mathbf{v}_2 = \mathbf{0}$ . This is because a short circuit element must be physically connected across terminals 2 and 3 in order to maintain the desired potential difference for  $\mathbf{v}_2$ . Moreover, the identity of  $\mathbf{v}_2$  would be lost if nodes 2 and 3 were coalesed into one node.

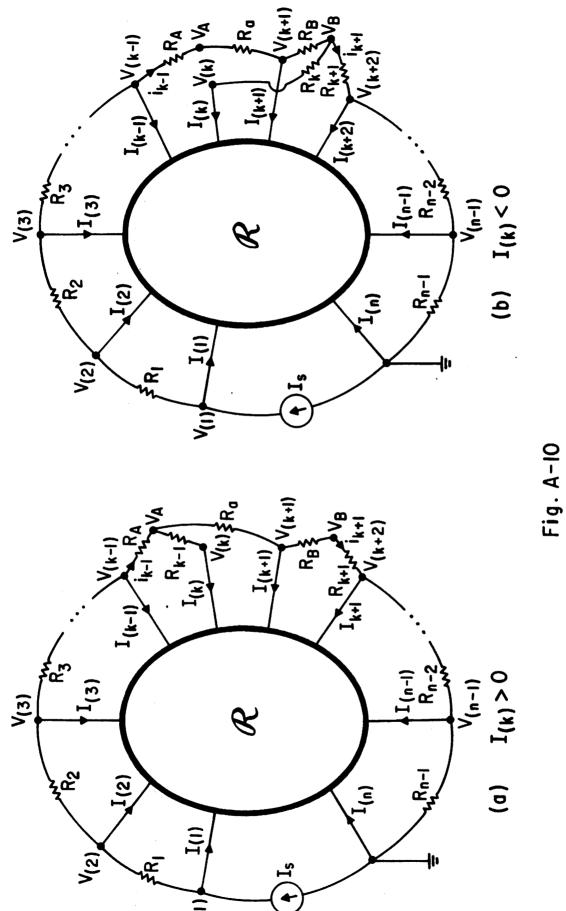

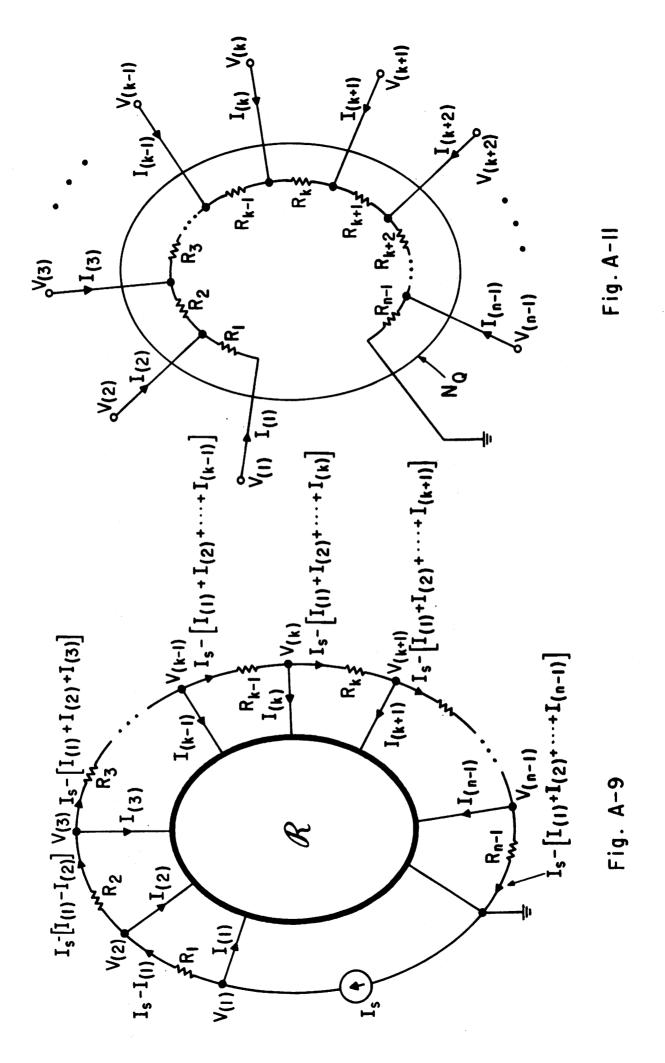

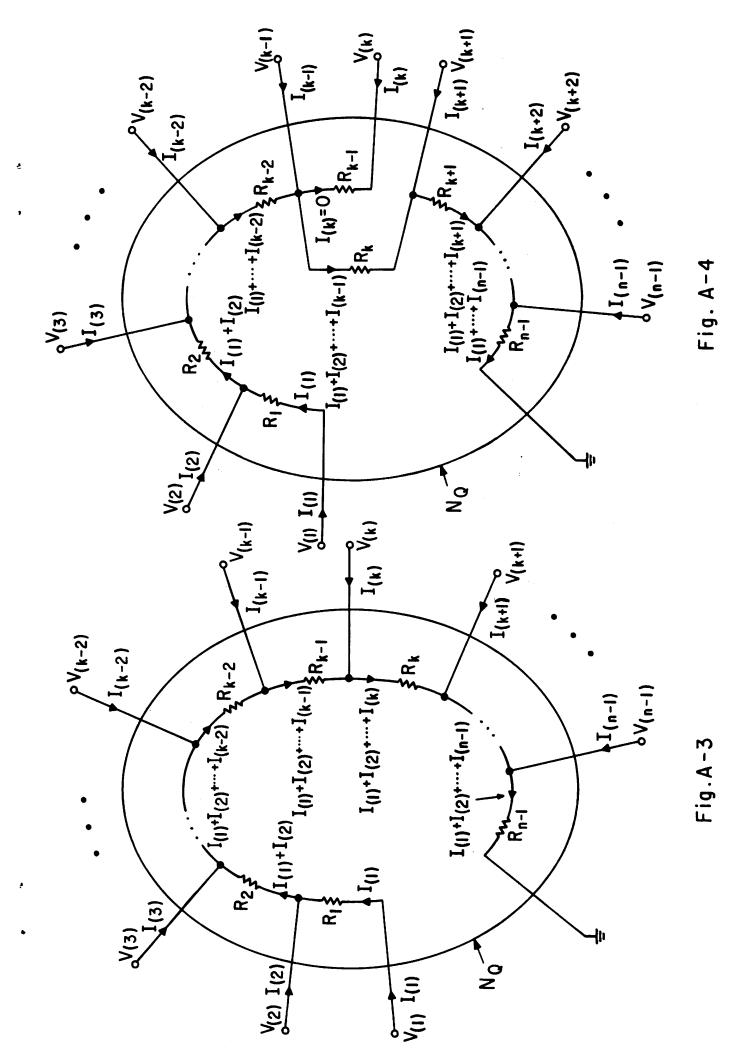

corresponding operating point of  $\mathcal{R}.$  By hypothesis, there exists an n-terminal network  $N_{\Omega}$  containing n-1 two-terminal positive linear resistors, which, when imbedded in N will result in the same operating point Q. Since the resulting network (i.e. with  $N_{\Omega}$  replacing  $\mathcal{R}$ ) satisfies all conditions of Property 6, it follows that the voltage between any two nodes and the current through any twoterminal element possesses the no-gain property. Hence, we only need to prove that the current through any terminal of  $N_0$  also possesses the no-gain property. Without loss of generality, let us choose any terminal @ of  $N_0$  and suppose that there are M  $\leq$  n-1 positive linear two-terminal resistors inside N $_0$  connected to node a . Partition these resistors into three sets  $S_1$ ,  $S_2$ , and  $S_3$ , where  $S_1 \stackrel{\triangle}{=} \{R_1, R_2, \dots, R_1\}$  denotes the set of resistors having actual current flowing away from node a, or  $\mathbf{i}_{R_1} < 0$  for k = 1, 2, ..., J;  $S_2 \stackrel{\triangle}{=} \{R_{J+1}, R_{J+2}, ..., R_L\}$ denotes the set of resistors having actual current flowing into node (a), or  $i_{R}$  > 0 for k = J+1, J+2, ..., L; and  $s_3 \triangleq \{R_{L+1}, R_{L+2}, \dots, R_M\}$  denotes the set of resistors having zero current. The partitioning scheme is shown in Fig. 2. terminal current  $i_{\alpha}$  is given by,

$$-i_{\alpha} = (i_{R_1} + i_{R_2} + \cdots + i_{R_J}) + (i_{R_{J+1}} + i_{R_{J+2}} + \cdots + i_{R_L})$$

(17)

where  $i_{R_k} < 0$  for k = 1, 2, ..., J and  $i_{R_k} > 0$  for k = J + 1, J + 2, ..., L.

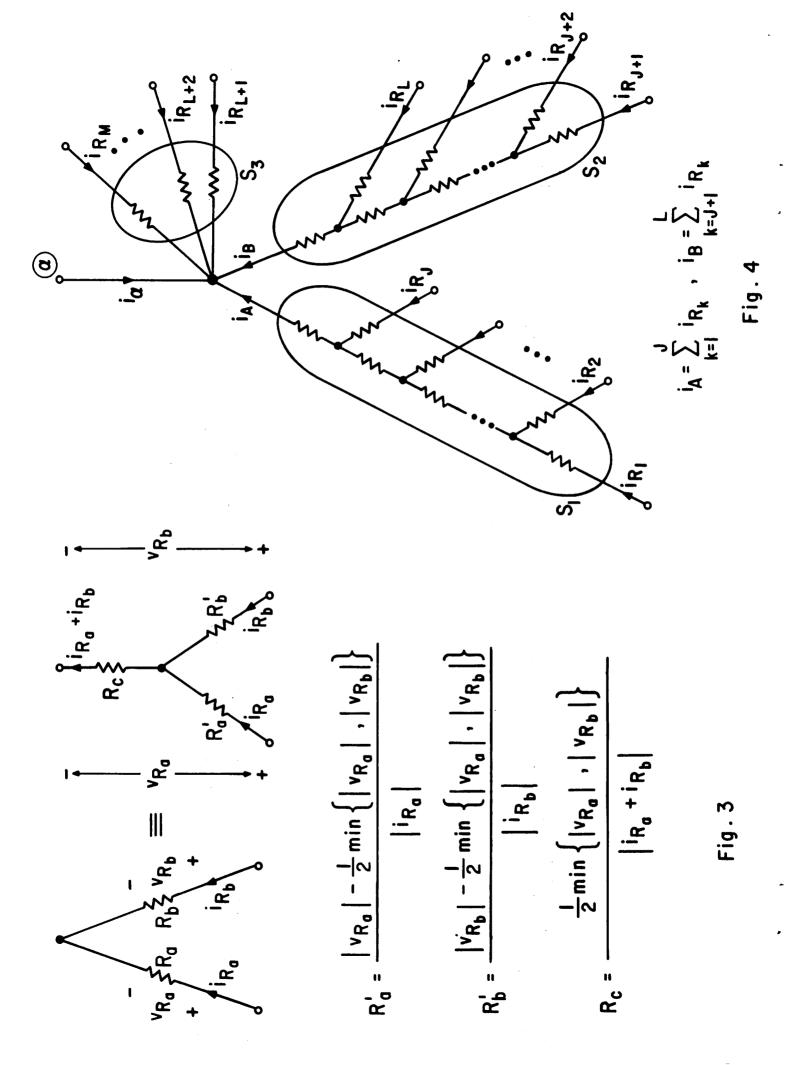

Using the method indicated by Willson [3], we can take any two resistors in  $S_1$  {resp.;  $S_2$ }, say  $R_a$  and  $R_b$ , and replace them by an equivalent subnetwork containing three positive linear resistors, as shown in Fig. 3, without effecting the operating point. Observe that the current flowing through the third linear resistor  $R_c$  is given by  $i_{R_c} = i_{R_a} + i_{R_b}$ . Clearly  $i_{R_c}$  possesses the no-gain property since the resulting network satisfies the conditions of Property 6. This procedure can obviously be repeated until all currents flowing through all resistors in  $S_1$  {resp.;  $S_2$ } is equal to a single current actually flowing away from {resp.; toward} node @ through a single two-terminal positive linear resistor, as shown in Fig. 4, where

$$i_A = \sum_{k=1}^{J} i_{R_k} < 0 \text{ and } i_B = \sum_{k=J+1}^{L} i_{R_k} > 0$$

(18)

If we replace the subnetwork of Fig. 2 by the equivalent subnetwork of Fig. 4 in

the overall imbedded network N, the resulting network still satisfies all hypotheses of Property 6. Hence  $i_A$  and  $i_B$  possess the no-gain property. Since  $i_A$  and  $i_B$  have opposite signs,

$$|\mathbf{i}_{\alpha}| = |\mathbf{i}_{A} + \mathbf{i}_{B}| \leq \max\{|\mathbf{i}_{A}|, |\mathbf{i}_{B}|\}$$

(19)

ç

Ĺ

Hence  $i_{\alpha}$  also possesses the no-gain property.

B. Necessity: Consider any imbedding network N as in the sufficiency proof, and let Q be an operating point of the no-gain resistor  $\mathcal R$  in the network. Without loss of generality, let us choose the terminal of  $\mathcal R$  having the lowest potential as the datum node, and relabel the remaining n-1 nodes of  $\mathcal R$  so that the operating point voltages of  $\mathcal R$  satisfy the inequality  $^{10}$

$$V_{(1)} \geq V_{(2)} \geq \cdots \geq V_{(k)} \geq \cdots \geq V_{(n-1)} \geq 0$$

$$(20)$$

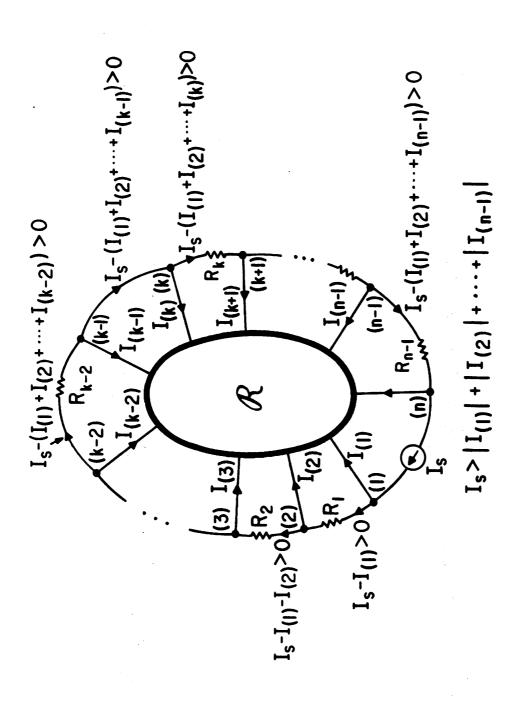

Let  $I_{(1)}$ ,  $I_{(2)}$ ,...,  $I_{(n-1)}$  be the corresponding operating point currents with the usual reference direction-current entering the no-gain n-terminal resistor  $\mathbb{Q}$ . Using this notation, let us now pause to consider two lemmas, whose proofs are given in the Appendix:

#### Lemma 2

(a) If

$$V_{(1)} > V_{(2)} > \cdots > V_{(k)} > \cdots > V_{(n-1)} > V_{(n)}$$

(21)

then the operating point currents of the no-gain resistor  ${\mathcal R}$  must satisfy the following system of strict inequalities

$$I_{(1)} > 0 \tag{22a}$$

$$I_{(1)} + I_{(2)} > 0$$

(22b)

:  $I_{(1)} + I_{(2)} + \cdots + I_{(k)} > 0$  (22c)

Note that  $V_{(1)}\{\text{resp.}; V_{(2)}, V_{(3)}...\}$  is the voltage between the highest {resp.; second highest, third highest,...} and the lowest operating-point potential nodes of the no-gain n-terminal resistor  $\mathbb{R}$ . Observe that the datum node may be different for different operating points.

$$\vdots \\ I_{(1)} + I_{(2)} + \cdots + I_{(k)} + \cdots + I_{(n-1)} > 0$$

(22d)

$$V_{(1)} > V_{(2)} > \cdots > V_{(k-1)} = V_{(k)} > V_{(k+1)} > \cdots > V_{(n-1)}$$

(23)

then the operating-point terminal currents of the no-gain resistor  ${\cal R}$  must satisfy the following system of inequalities

$$I_{(1)} > 0 \tag{24a}$$

$$I_{(1)} + I_{(2)} > 0$$

(24b)

:

$$I_{(1)} + I_{(2)} + \cdots + I_{(k-2)} > 0$$

(24c)

$$I_{(1)} + I_{(2)} + \cdots + I_{(k-2)} + I_{(k-1)} + I_{(k)} > 0$$

(24d)

$$I_{(1)} + I_{(2)} + \cdots + I_{(k-2)} + I_{(k-1)} \ge 0$$

(24e)

$$I_{(1)} + I_{(2)} + \cdots + I_{(k-2)} + I_{(k)} \ge 0$$

(24f)

$$I_{(1)} + I_{(2)} + \cdots + I_{(k-2)} + I_{(k-1)} + I_{(k)} + I_{(k+1)} > 0$$

(24g)

:

$$I_{(1)} + I_{(2)} + \cdots + I_{(k)} + \cdots + I_{(n-1)} > 0$$

(24h)

#### Lemma 3

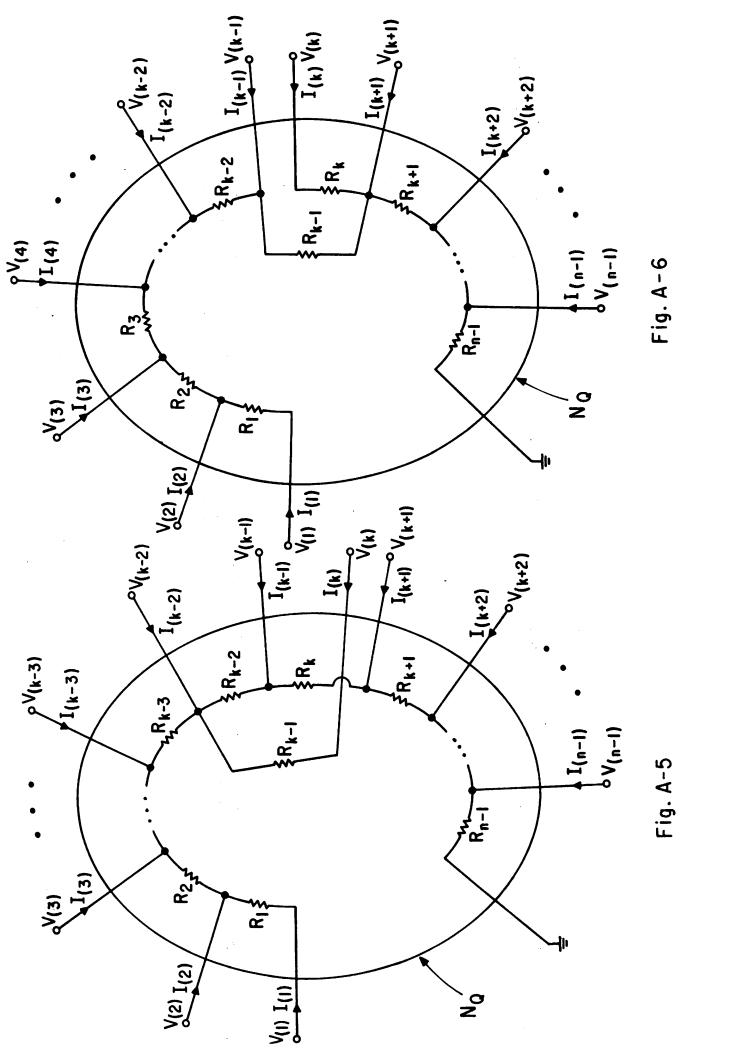

Given any set of n-1 node-to-datum voltages satisfying (21) {resp.; (23)}, and any set of terminal currents satisfying (22) {resp.; (24)}, there exists a connected n-terminal network containing n-1 linear positive two-terminal resistors having the same operating point voltages and currents.

With these two lemmas, we will now proceed to complete the necessity proof of Theorem 1 by first assuming that the operating-point voltages satisfy either the strict inequality of (21) or the mixed inequality of (23). By Lemma 2, the operating-point currents must satisfy the strict inequality of (22) in the former case and the mixed inequality of (24) in the latter case. It

follows from Lemma 3 that there exists a connected n-terminal network containing n-1 linear positive two-terminal resistors having the same operating-point voltages and currents as the no-gain resistor  $\mathcal{R}$ .

Using exactly the same procedures as in the proofs of Lemmas 2 and 3, it is easy to show that in the cases where there are more than two terminals of  $\mathbb{R}$  having identical potential at a particular operating-point such as

$$V_{(1)} > \cdots > V_{(\alpha)} = V_{(\alpha+1)} = \cdots = V_{(\beta)} > V_{(\beta+1)} > \cdots$$

$$> V_{(\gamma)} = V_{(\gamma+1)} = \cdots = V_{(\delta)} > \cdots V_{(n-1)}$$

(25)

The corresponding operating-point terminal currents of  ${\mathbb Q}$  must satisfy the following system of mixed inequalities

$$I_{(1)} > 0$$

$$\vdots$$

$$I_{(1)} + \cdots + I_{(\alpha-1)} > 0$$

$$I_{(1)} + \cdots + I_{(\alpha-1)} + I_{(\alpha)} + \cdots + I_{(\beta)} > 0$$

$$I_{(1)} + \cdots + I_{(\alpha-1)} + I_{(p)} \ge 0 \text{ for } p = \alpha, \alpha+1, \cdots, \beta$$

$$\vdots$$

$$I_{(1)} + \cdots + I_{(\alpha)} + \cdots + I_{(\gamma-1)} > 0$$

$$I_{(1)} + \cdots + I_{(\alpha)} + \cdots + I_{(\gamma-1)} + I_{(\gamma)} + \cdots + I_{(\delta)} > 0$$

$$\vdots$$

$$I_{(1)} + \cdots + I_{(\alpha)} + \cdots + I_{(\gamma-1)} + I_{(p)} \ge 0 \text{ for } p = \gamma, \gamma+1, \cdots, \delta$$

$$\vdots$$

$$I_{(1)} + \cdots + I_{(\alpha)} + \cdots + I_{(\delta)} + \cdots + I_{(n-1)} > 0$$

In turn the two systems of mixed inequalities in (25) and (26) guarantee that a connected n-terminal network, containing n-l positive linear two-terminal resistors having the same operating-point voltages and currents as the no-gain resistor  $\mathcal{R}$ , can be constructed. Hence the necessity part of the theorem is proved. This completes the proof of Theorem 1.

Corollary to Theorem 1 Interconnection of No-Gain Resistors (Closure Property)

Let  $\widehat{\mathcal{R}}$  be a connected n-terminal network obtained by a valid

interconnection  $^{11}$  of m multi-terminal resistors  $R_1, R_2, \ldots, R_m$ , where  $R_i$  is an  $n_i$ -terminal resistor and  $n_i \ge 2$  for  $i = 1, 2, \ldots, m$ . If  $R_1, R_2, \ldots, R_m$  are no-gain resistors, then  $R_i$  is a no-gain n-terminal element.

Proof: Let  $\mathbb R$  be imbedded in an arbitrary network N containing positive linear two-terminal resistors, independent voltage and current sources, short and open circuit elements which do not form  $\mathbb C$ -loops or  $\mathbb C$ -cutsets, respectively. Let  $\mathbb R$  be an operating point of the resulting circuit. This gives rise to an operating point  $\mathbb R_1$  for each resistor  $\mathbb R_1$  inside  $\mathbb R_2$ . Since each  $\mathbb R_1$  is a no-gain resistor, it can be replaced by  $\mathbb R_1$  - 1 positive linear two-terminal resistors, having the same operating point  $\mathbb R_1$ . If this procedure is repeated for all resistors  $\mathbb R_1$ ,  $\mathbb R_2$ , ...,  $\mathbb R_m$  inside  $\mathbb R_n$ , the resulting network inside  $\mathbb R_n$  contains only two-terminal positive linear resistors, which when imbedded in N will produce the operating point  $\mathbb R_n$ . This implies that the operating point  $\mathbb R_n$  possesses the no-gain property. In addition, one can use the technique employed in the proof of Theorem 1 to show that all terminal currents of  $\mathbb R_n$  also satisfy the no-gain property. Hence  $\mathbb R_n$  is a no-gain resistor.

Lemmas 2 and 3 have been formulated with the assumption that the terminals have been ordered and relabelled such that (21) and (23) are satisfied. In the following applications of these lemmas, it is convenient to reformulate them without any terminal relabelling. This can be achieved through the introduction of appropriate notations as given in the following properties.

Property 7 No-Gain Resistor Criteria in Terms of Terminal Currents

An n-terminal resistor  $\mathbb{Q}$ , shown in Fig. 1, is a no-gain element if, and only if, the following conditions are satisfied 12

A valid interconnection implies that each terminal of every multi-terminal resistor, say  $R_i$ , inside  $R_i$  is either a terminal of  $R_i$  or else it must satisfy the following constraints:

i) It is connected to at least one other multi-terminal resistor, say R with  $j \neq i$ , inside R

ii) It is connected to at most one terminal of each multi-terminal resistor inside  $\mathbb{R}$  lii) It is not connected to any other terminal of  $R_1$ . This is to insure that the interconnection of  $R_1$ ,  $R_2$ , ...,  $R_m$  does not produce short circuit and open circuit elements.

$<sup>^{12}</sup>$ Observe that conditions (1a), (1b), (2a) ... are written in a compact form. When expanded, each will give rise to several inequalities. A detailed expansion of these conditions is given in Corollary 7.2 for the case where n=3.

(1a)

$$i_k \ge 0$$

whenever  $v_k \ge v_1$

(1b)

$$i_k \le 0$$

whenever  $v_k \le v_j$  for all  $j = 1, 2, ..., n, j \ne k$ ; and  $k = 1, 2, ..., n$ .

(2a)

$$i_{k_1} + i_{k_2} \ge 0$$

whenever  $v_{k_1} \ge v_{k_j}$  and  $v_{k_2} \ge v_{j}$

(2b)

$$i_{k_1} + i_{k_2} \le 0$$

whenever  $v_{k_1} \le v_j$  and  $v_{k_2} \le v_j$

for all  $j = 1, 2, ..., n, j \ne k_1, k_2$  and  $k_1, k_2 = 1, 2, ..., n$  with  $k_1 \ne k_2$ .

(3a)

$$i_{k_1} + i_{k_2} + i_{k_3} \ge 0$$

whenever  $v_{k_1} \ge v_j$ ,  $v_{k_2} \ge v_j$  and  $v_{k_3} \ge v_j$

(3b)

$$i_{k_1} + i_{k_2} + i_{k_3} \le 0$$

whenever  $v_{k_1} \le v_j$ ,  $v_{k_2} \le v_j$  and  $v_{k_3} \le v_j$

for all  $j = 1, 2, ..., n, j \ne k_1, k_2, k_3$  and  $k_1, k_2, k_3 = 1, 2, ..., n$  with  $k_1 \ne k_2 \ne k_3$

.

$$((n-1)a) i_{k_1} + i_{k_2} + ... + i_{k_{n-1}} \ge 0 \text{ whenever } v_{k_p} \ge v_j$$

where the symbol ">" is used to denote that the equality sign on the left can hold only if at least one of the equality signs on the right holds.

<u>Proof:</u> In view of Lemmas 2 and 3,  $\mathbb{Q}$  is a no-gain element if, and only if, at every operating point where the terminal voltages satisfy (21) {resp.; (23)}, the terminal currents of  $\mathbb{Q}$  are constrained by (22) {resp.; (24)}. Conditions (1a), (2a),...((n-1)a) of Property 7 are merely a systematic method of representing the

conditions in Lemmas 2 and 3 for an n-terminal resistor with <u>fixed</u> labels.

Conditions (1b); (2b),...((n-1)b) follow from Lemmas 4 and 5 which are stated below.

#### Lemma 4

Using the notation of Lemma 2, we have:

(a) if the operating point node-to-datum voltages of  ${\mathcal R}$  satisfy

$$v_{(n)} < v_{(n-1)} < \cdots < v_{(2)} < \cdots < v_{(2)} < v_{(1)}$$

(27)

then the corresponding operating point terminal currents of  ${\mathcal R}$  must satisfy the following system of strict inequalities:

$$I_{(n)} < 0$$

$$I_{(n)} + I_{(n-1)} < 0$$

$$\vdots$$

$$I_{(n)} + I_{(n-1)} + \cdots + I_{(k)} < 0$$

$$\vdots$$

$$I_{(n)} + I_{(n-1)} + \cdots + I_{(k)} + \cdots + I_{(2)} < C$$

$$(28)$$

(b) if the operating point node-to-datum voltages of  ${\mathcal R}$  satisfy

$$v_{(n)} < v_{(n-1)} < \cdots < v_{(k+1)} = v_{(k)} < \cdots < v_{(2)} < v_{(1)}$$

(29)

then the corresponding operating-point terminal currents of  ${\mathbb R}$  must satisfy the following system of mixed inequalities:

$$I_{(n)} < 0$$

$$I_{(n)} + I_{(n-1)} < 0$$

$$\vdots$$

$$I_{(n)} + I_{(n-1)} + \cdots + I_{(k+2)} < 0$$

$$I_{(n)} + I_{(n-1)} + \cdots + I_{(k+2)} + I_{(k+1)} + I_{(k)} < 0$$

$$I_{(n)} + I_{(n-1)} + \cdots + I_{(k+2)} + I_{(k+1)} \leq 0$$

$$I_{(n)} + I_{(n-1)} + \cdots + I_{(k+2)} + I_{(k)} \leq 0$$

$$(30)$$

$$I_{(n)} + I_{(n-1)} + \cdots + I_{(k+2)} + I_{(k+1)} + I_{(k)} + I_{(k-1)} < 0$$

$$\vdots$$

$$I_{(n)} + I_{(n-1)} + \cdots + I_{(2)} < 0$$

Proof: The conclusions of Lemma 4 follow from Lemma 2 and the observation that

$$I_{(1)} + I_{(2)} + \cdots + I_{(k)} + \cdots + I_{(n)} = 0$$

(31)

•

Д

п

Lemma 5

Given any set of n-1 node-to-datum voltages satisfying (27) {resp.; (29)}, and any set of terminal currents satisfying (28) {resp.; (30)}, then there exists a connected n-terminal network containing n-1 linear positive two-terminal resistors having the same operating point voltages and currents.

Proof: The proof of Lemma 5 is similar to that of Lemma 3 and hence is omitted.

Corollary 7.1 No-Gain Criteria in Terms of Conductance Representation Let  $\mathcal R$  be an n-terminal resistor admitting an (n-1)-port conductance representation

$$i_k = g_k (v_1, v_2, ..., v_{n-1}) \triangleq g_k(y), \qquad k = 1, 2, ..., n-1$$

(32)

where  $y = [v_1, v_2, ..., v_{n-1}]^t$  is the node-to-ground port-voltage vector and node m is the common ground for all ports, as shown in Fig. 5. Then  $\mathbb{R}$  is a no-gain element if, and only if, the following conditions are satisfied,

(1a)

$$g_k(v) \ge 0$$

whenever  $v_k \ge 0$  and  $v_k \ge v_j$

(1b)  $g_k(y) \le 0$  whenever  $v_k \le 0$  and  $v_k \le v_j$  for all  $j = 1, 2, ..., n-1, j \ne k$ , and k = 1, 2, ..., n-1

(2a)

$$g_{k_1}(y) + g_{k_2}(y) \ge 0$$

whenever  $v_{k_1} \ge 0$ ,  $v_{k_1} \ge v_{j}$ ,  $v_{k_2} \ge 0$ ,  $v_{k_2} \ge v_{j}$

(2b)

$$g_{k_1}(v) + g_{k_2}(v) \le 0$$

whenever  $v_{k_1} \le 0$ ,  $v_{k_1} \le v_j$ ,  $v_{k_2} \le 0$ ,  $v_{k_2} \le v_j$

for all j = 1, 2, ..., n-1, j

$$\neq k_1$$

,  $k_2$

and  $k_1$ ,  $k_2$  = 1, 2, ..., n-1 with  $k_1 \neq k_2$ .

(3a)

$$g_{k_1}(v) + g_{k_2}(v) + g_{k_3}(v) \ge 0$$

whenever  $v_{k_1} \ge 0$ ,  $v_{k_1} \ge v_j$ ,  $v_{k_2} \ge 0$ ,  $v_{k_2} \ge v_j$ ,  $v_{k_3} \ge 0$ ,  $v_{k_3} \ge v_j$

(3b)

$$g_{k_1}(v) + g_{k_2}(v) + g_{k_3}(v) \le 0$$

whenever

$$v_{k_1} \le 0, v_{k_1} \le v_j, v_{k_2} \le 0, v_{k_2} \le v_j, v_{k_3} \le 0, v_{k_3} \le v_j$$

for all  $j = 1, 2, ..., n-1, j \ne k_1, k_2, k_3$  and  $k_1, k_2, k_3 = 1, 2, ..., n-1$  with  $k_1 \ne k_2 \ne k_3$ .

((n-1)a)

$$g_{k_1}(\underline{v}) + g_{k_2}(\underline{v}) + \dots + g_{n-1}(\underline{v}) \ge 0$$

whenever  $v_k \ge 0$

((n-1)b)  $g_{k_1}(\underline{v}) + g_{k_2}(\underline{v}) + \dots + g_{n-1}(\underline{v}) \le 0$  whenever  $v_k \ge 0$

for all  $k = 1, 2, \dots, n-1$

where the symbol  $"\ge"$  is used to denote that the equality sign on the left can hold only if at least <u>one</u> of the equality signs on the right holds.

Proof: Corollary 7.1 follows directly from Property 7 with

$$v_n = 0 \tag{33}$$

#### Corollary 7.2

Let  ${\mathcal R}$  be a 3-terminal resistor characterized by a two port conductance representation

$$i_1 = g_1(v_1, v_2)$$

$i_2 = g_2(v_1, v_2)$

then R is a no-gain element if, and only if,

(1a)

$$g_1(v_1, v_2) \ge 0$$

whenever  $v_1 \ge v_2$ ,  $v_1 \ge 0$

(1b)

$$g_1(v_1, v_2) \le 0$$

whenever  $v_1 \le v_2$ ,  $v_1 \le 0$

(2a)

$$g_2(v_1, v_2) \ge 0$$

whenever  $v_2 \ge v_1, v_2 \ge 0$

(2b)

$$g_2(v_1, v_2) \le 0$$

whenever  $v_2 \le v_1, v_2 \le 0$

(3a)

$$g_1(v_1, v_2) + g_2(v_1, v_2) \ge 0$$

whenever  $v_1 \ge 0$ ,  $v_2 \ge 0$

(3b)

$$g_1(v_1, v_2) + g_2(v_1, v_2) \le 0$$

whenever  $v_1 \le 0$ ,  $v_2 \le 0$

#### Remark

Corollary 7.2 serves as an example of the detailed expansion of Corollary 7.1 for a specific value of n=3. Without the symbol "\leq", as defined in Property 7, the equations would have to be expanded further to convey the proper meaning. For example condition (1a) of Corollary 7.2 could be written as the following 4 statements

$$g_1(v_1, v_2) > 0$$

whenever  $v_1 > 0$  and  $v_1 > v_2$  (34a)

$$g_1(v_1, v_2) \ge 0$$

whenever  $v_1 = 0$  and  $v_1 > v_2$  (34b)

$$g_1(v_1, v_2) \ge 0$$

whenever  $v_1 > 0$  and  $v_1 = v_2$  (34c)

$$g_1(v_1, v_2) \ge 0$$

whenever  $v_1 = 0$  and  $v_1 = v_2$  (34d)

where (34d) and its counterpart in condition (1b) of Corollary 7.2 together imply that

$$g_1(v_1, v_2) = 0$$

whenever  $v_1 = 0$  and  $v_2 = 0$  (35)

This Corollary corresponds to Theorem 5 of [3], where Willson has listed only three equations, in effect combining (1a) and (1b), (2a) and (2b), and (3a) and (3b). In doing this the boundary value information is lost, and he either requires that  $\mathbf{g}_1(\cdot)$  and  $\mathbf{g}_2(\cdot)$  be continuous or an additional 4 equations are required to specify the nature of  $\mathbf{g}_1(\cdot)$  and  $\mathbf{g}_2(\cdot)$  on the boundaries.

Property 8 No-Gain Resister Criteria in Terms of Terminal Voltages

Let  $\widehat{\mathbb{R}}$  be an n-terminal resistor with terminal currents and voltages defined as in Fig. 1. Then  $\widehat{\mathbb{R}}$  is a no-gain element if, and only if, the following conditions are satisfied:

- (1) At every operating point where not all the terminal currents of  $\mathbb{Q}$  are zero, and for every pair of terminals j, k = 1, 2, ..., n where  $j \neq k$ , we have

- (a)  $v_k v_j > 0$  {resp.;  $\geq 0$ } if either  $i_k > 0$  {resp.; = 0},  $i_j < 0$  and  $i_m \geq 0$ ; or  $i_k > 0$ ,  $i_j < 0$  {resp.; = 0}, and  $i_m \leq 0$  for all m = 1, 2, ..., n where  $m \neq j$  and  $m \neq k$ .

- (b)  $v_k v_j < 0 \text{ {resp.; } } \leq 0 \text{ } \text{ if either } i_k < 0 \text{ {resp.; } = 0 }, i_j > 0 \text{ and } i_m \leq 0; \text{ or } i_k < 0, i_j > 0 \text{ {resp.; } = 0 }, \text{ and } i_m \geq 0 \text{ for all } m = 1, 2, \dots, n \text{ where } m \neq j \text{ and } m \neq k.$

- (c) the terminal current of the highest {resp.; lowest} potential terminal of  $\mathbb R$  is positive {resp.; negative}. In the case where two or more terminals of  $\mathbb R$  are at the same highest {resp.; lowest} potential, at least one of them must have a positive {resp.; negative} terminal current.

- (2) At the operating point where all terminal currents  ${\mathcal R}$  are zero, we have

$$v_k = 0$$

for all  $k = 1, 2, ..., n$ .

#### Remark

Although it is not obvious, the conditions of Properties 7 and 8 are duals to each other. The proof of Property 8 is based on the dual versions of Lemmas 2 to 5. The details of the proof are given in the Appendix.

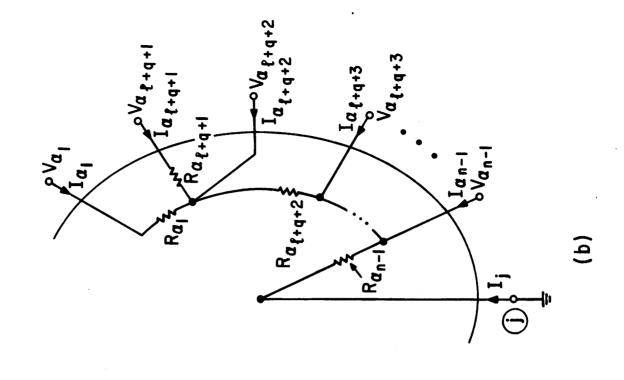

Corollary 8.1 No-Gain Criteria in terms of Resistance Representation

Let R be an n-terminal resistor admitting an (n-1)-port resistance representation

$$v_k = r_k(i_1, i_2, ..., i_{n-1}) = r_k(i)$$

$k = 1, 2, ..., n-1$  (36)

where  $\underline{\mathbf{i}} = [\mathbf{i}_1, \mathbf{i}_2, \dots, \mathbf{i}_{n-1}]^t$  are the port-currents, and  $\underline{\mathbf{v}} = [\mathbf{v}_1, \mathbf{v}_2, \dots, \mathbf{v}_{n-1}]^t$

are the node-to-datum port-voltages as shown in Fig. 5. Then  $\mathbb R$  is a no-grain element if, and only if,  $r_k(0) = 0$  for k = 1, 2, ..., n-1 and the following conditions are satisfied:

- (1) For any pair of terminals j, k = 1, 2, ..., n-1 where  $j \neq k$

- (1a)  $r_k(i) r_j(i) > 0$  {resp.;  $\geq 0$ } if either  $i_k > 0$  {resp.; = 0},  $i_j < 0$ ,  $i_m \geq 0$ , and  $i_1 + i_2 + \cdots + i_{n-1} \leq 0$ ; or  $i_k > 0$ ,  $i_j < 0$  {resp.; = 0},  $i_m \leq 0$ , and  $i_1 + i_2 + \cdots + i_{n-1} \geq 0$  for all  $m = 1, 2, \ldots, n-1$  where  $m \neq j$  and  $m \neq k$ .

- (1b)  $r_k(\underline{i}) r_j(\underline{i}) < 0$  {resp.;  $\leq 0$ } if either  $i_k < 0$  {resp.; = 0},  $i_j > 0$ ,  $i_m \leq 0$ , and  $i_1 + i_2 + \ldots + i_{n-1} \geq 0$ ; or  $i_k < 0$ ,  $i_j > 0$  {resp.; = 0},  $i_m \geq 0$ , and  $i_1 + i_2 + \ldots + i_{n-1} \leq 0$  for all  $m = 1, 2, \ldots, n-1$  where  $m \neq j$  and  $m \neq k$ .

- (2) For any terminal k = 1, 2, ..., n

- (2a)  $r_k(\underline{i}) > 0$  {resp.;  $\geq 0$ } if either  $i_k > 0$  {resp.; = 0},  $i_1 + i_2 + \cdots + i_{n-1} > 0$ , and  $i_m \geq 0$ ; or  $i_k > 0$ ,  $i_1 + i_2 + \cdots + i_{n-1} > 0$  {resp.; = 0}, and  $i_m \leq 0$  for all  $m = 1, 2, \ldots, n-1$  where  $m \neq k$ .

- (2b)  $r_k(i) < 0$  {resp.,  $\le 0$ } if either  $i_k < 0$  {resp.; = 0},  $i_1 + i_2 + \cdots + i_{n-1} < 0$ , and  $i_m \le 0$ ; or  $i_k > 0$ ,  $i_1 + i_2 + \cdots + i_{n-1} < 0$  {resp.; = 0} for all  $m = 1, 2, \ldots, n-1$  where  $m \ne k$ .

- (3) For each  $m = 1, 2, \ldots, n-1$  where  $i_m = 0$ , we have

$$\min_{\substack{j=1,2,\ldots,n-1\\i\neq m}} r_j(\underline{i}) \leq r_m(\underline{i}) \leq \max_{\substack{j=1,2,\ldots,n-1\\i\neq m}} r_j(\underline{i})$$

<u>Proof:</u> Corollary 8.1 follows directly from Property 8 by noting that  $v_n = 0$  and  $i_1 + i_2 + \cdots + i_{n-1} + i_n = 0$ . Hence the proof of Corollary 8.1 is omitted.

### B. Locally No-Gain Elements

#### Definition 6 Locally No-Gain Elements

An n-terminal resistor  $\mathbb{Q}$ , with terminal currents and voltages as defined in Fig. 1, is said to be <u>locally no-gain</u> at an operating point Q if, and only if, for every pair of incremental terminal voltage and current vector  $(\delta \mathbf{v}, \delta \mathbf{i})$  consistent with the characteristics of  $\mathbb{Q}$  at the point Q, where

$$\delta \underline{\mathbf{v}} = [\delta \mathbf{v}_1, \delta \mathbf{v}_2, \dots, \delta \mathbf{v}_{n-1}]^{\mathsf{t}}$$

and  $\delta \underline{\mathbf{i}} = [\delta \mathbf{i}_1, \delta \mathbf{i}_2, \dots, \delta \mathbf{i}_{n-1}]^{\mathsf{t}}$ ,

there exists a connected network with n-l positive linear two-terminal resistors having the operating point  $(\delta v, \delta i)$ . R is said to be a <u>locally no-gain element</u> if R is locally no-gain at every point in the characteristics of R.

## Property 9 Locally No-Gain Conductance Matrix

Let  $\mathbb{Q}$  be an n-terminal resistor admitting an (n-1)-port  $C^1$ -conductance representation

$$i = g(v) \tag{37}$$

where  $v = [v_1, v_2, \dots, v_{n-1}]^t$  and  $i = [i_1, i_2, \dots, i_{n-1}]^t$  are the port-voltage and port-current vectors, as shown in Fig. 5, and  $g(\cdot) = [g_1(\cdot), g_2(\cdot), \dots g_{n-1}(\cdot)]^t$ . Terminal m is the common terminal for all ports and  $v_k$  is the voltage across terminals m and m and m and m is the current entering terminal m of m. Then m is a locally no-gain element if, and only if, at each operating point voltage m of m, the incremental conductance matrix

$$\tilde{g} \stackrel{\Delta}{=} [g_{jk}] \stackrel{\Delta}{=} \left[ \frac{\partial g_{j}(v)}{\partial v_{k}} \right] \bigg|_{v} = v_{Q}$$

(38)

satisfies the following conditions:

(1)

$$g_{kk} > 0$$

for all  $k = 1, 2, ..., n-1$  (39a)

(2)

$$g_{jk} \leq 0$$

for all j, k = 1, 2, ..., n-1, where j  $\neq$  k (39b)

(3)

$$g_{kk} \ge -\sum_{j=1}^{n-1} g_{kj} \ge 0$$

for all  $k = 1, 2, ..., n-1$  (40a)

(4)

$$g_{kk} \ge -\sum_{\substack{j=1\\j\neq k}}^{n-1} g_{jk} \ge 0$$

for all  $k = 1, 2, ..., n-1$  (40b)

(5) For each  $\ell \times \ell$  principal submatrix  $^{13}$  G of G, the sum of the diagonal elements of G is strictly greater than the negative of the sum of the off diagonal elements, i.e.,

$$\sum_{j=1}^{\ell} \left( \mathcal{G}_{\ell} \right)_{jj} > - \sum_{j=1}^{\ell} \sum_{k=1}^{\ell} \left( \mathcal{G}_{\ell} \right)_{jk} \tag{41}$$

where  $\ell = 1, 2, ..., n-1$ .

#### Remark

Property 9 is a direct consequence of Corollary 7.1 with (32) replaced by

$$\delta i_k = g_k(\delta v) \stackrel{\triangle}{=} \sum_{j=1}^{n-1} g_{kj} \delta v_j$$

for  $k = 1, 2, ..., n-1$  (42)

The details for the proof of Property 9 are given in the Appendix.

From (39), the locally no-gain conductance matrix G is seen to have positive diagonal and non-positive off diagonal elements. A matrix with this property is referred to as a Z-matrix in [12] and an M-matrix in [13]. Equation (40) states that G is both a row and column dominant matrix. In [14] a matrix that satisfies both (39) and (40) is defined as being hyperdominant. (The column dominance is not specifically mentioned since the matrices considered in [14] are symmetric). Together (40) and (41) imply that G is positive definite. A matrix that satisfies conditions (1) through (5) of Property 9 will henceforth be called a locally no-gain conductance matrix.

$$\hat{A}_{\ell} = \begin{bmatrix}

a_{j_{1}j_{1}} & a_{j_{1}j_{2}} & \cdots & a_{j_{1}j_{\ell}} \\

a_{j_{2}j_{1}} & a_{j_{2}j_{2}} & \cdots & a_{j_{2}j_{\ell}} \\

\vdots & \vdots & & \vdots \\

a_{j_{\ell}j_{1}} & a_{j_{\ell}j_{2}} & \cdots & a_{j_{\ell}j_{\ell}}

\end{bmatrix}$$

where  $1 \le j_1 < j_2 < \cdots < j_\ell \le m$ .

Let  $A = [a_{jk}]$  be an m×m matrix. An  $\ell \times \ell$  principal submatrix  $A_{\ell}$  of A is obtained by deleting (m- $\ell$ ) columns and the corresponding (m- $\ell$ ) rows, i.e.,

Recall that an (n-1) × (n-1) matrix is realizable as the short circuit conductance matrix of a common-ground (n-1)-port resistance network containing only n-terminals if, and only if, the matrix is symmetric, dominant and every off-diagonal element is non-positive [15]. Hence, even if we assume that R is reciprocal, that is, the locally no-gain conductance matrix is symmetric, a realizable short-circuit conductance matrix need only satisfy conditions (1) through (4) of Property 9. Thus the requirements on a symmetric locally no-gain conductance matrix are stronger than the realizability criteria for a short-circuit conductance matrix. This unexpected result stems from the fact that the circuit used to realize a locally no-gain conductance matrix is required to be connected, as stated in Definition 6 while a circuit realization of a short-circuit conductance matrix is not, in general, required to be connected. It can be shown that every connected resistive (n-1)-port network containing n-1 or more positive linear two-terminal resistors has a short-circuit conductance matrix.

We can relate the locally no-gain requirements and the locally passive criteria by the following two corollarys to Property 9.

Corollary 9.1 Locally No-Gain and Locally Strictly Passive Resistors

A locally no-gain n-terminal resistor  $\mathbb{R}$  characterized by a  $\mathbb{C}^1$ -conductance representation  $\mathbf{i} = \mathbf{g}(\mathbf{v})$  is strictly locally passive.

<u>Proof:</u> It follows from Property 2 that  $\mathcal R$  is strictly locally passive if its incremental conductance matrix

$$\tilde{g}(\tilde{v}) = \left[\frac{\partial g_{j}(\tilde{v})}{\partial v_{k}}\right] \Big|_{\tilde{v}=\tilde{v}_{Q}}$$

is positive definite for all  $y = y_Q$ . Since the locally no-gain conductance matrix is positive definite at each possible operating point of Q, it follows that if Q is a locally no-gain element then it is strictly locally passive.

Observe that the converse of Corollary 9.1 is not true. For example, let  ${\cal R}$  be a 3-terminal resistor characterized by

$$i_1 = 3v_1 + v_2 \stackrel{\triangle}{=} g_1(v_1, v_2)$$

$i_2 = v_1 + 3v_2 \stackrel{\triangle}{=} g_2(v_1, v_2)$

Clearly  $\mathcal R$  is locally strictly passive but not locally no-gain.

## Corollary 9.2 Locally No-Gain and Strictly Passive Resistors

A locally no-gain n-terminal resistor characterized by a  $C^1$ -conductance representation  $\underline{i} = g(\underline{v})$  is <u>strictly passive</u> if, and only if, its constitutive relation passes through the origin.

Proof: This follows immediately from Corollaries 9.1 and 3.2.

¤

## Property 10. Locally No-Gain Resistance Matrix

Let  $\mathbb{Q}$  be an n-terminal resistor admitting an (n-1)-port  $C^1$ -resistance representation

$$y = r (i)$$

(43)

where  $i = [i_1, i_2, \dots, i_{n-1}]^t$  and  $v = [v_1, v_2, \dots, v_{n-1}]^t$  are the port-current and port-voltage vectors,  $v_k$  is the voltage across terminals k and k and k is the current entering terminal k of k as shown in Fig. 5, and v is a locally no-gain element then for each operating point current v of v, the incremental resistance matrix

$$\begin{array}{ccc}

& & \\

\mathbb{R} & & \\

& & \\

& & \\

\end{array} \begin{bmatrix}

\mathbf{r}_{jk}

\end{bmatrix} & & \\

& & \\

& & \\

\end{array} \begin{bmatrix}

\partial \mathbf{r}_{j}(\underline{i}) \\

\partial \mathbf{i}_{k}

\end{bmatrix} \\

& \\

\underline{i} = \underline{I}_{0}

\end{aligned} \tag{44}$$

must satisfy the following conditions:

- (1)  $r_{kk} > 0$  for all k = 1, 2, ..., n-1

- (2)  $0 \le r_{kj} \le r_{kk}$  for all k, j = 1, 2, ..., n-1 where  $k \ne j$

- (3)  $0 \le r_{jk} \le r_{kk}$  for all k, j = 1, 2,..., n-1 where  $k \ne j$

- (4)  $0 \le r_{jk} + r_{kj} < r_{kk} + r_{jj}$  for all k, j = 1, 2, ..., n-1 where k  $\neq$  j

- (5)  $0 \le r_{jk} + r_{kl} \le r_{kk} + r_{jl}$  for all j, k, l = 1, 2, ..., n-1 where  $j \ne k \ne l$

- (6)  $r_{kk}r_{j\ell} \ge r_{k\ell}r_{jk}$  for all j, k,  $\ell = 1, 2, ..., n-1$  where  $j \ne k \ne \ell$

- (7) In any  $n \times k$  submatrix of R, the maximum sum of the elements in each row of

the submatrix must occur at a row which contains a diagonal element.

#### Remark

Property 10 is a direct consequence of Corollary 8.1 with (36) replaced by

$$\delta v_k = r_k(\delta i) \stackrel{\triangle}{=} \sum_{j=1}^{n-1} r_{kj} \delta i_j \text{ for } k = 1, 2, ..., n-1$$

(45)

The details of the proof of Property 10 are given in the Appendix.

The inverse of the no-gain resistance matrix must be a no-gain conductance matrix. We have not been able to prove that conditions (1) through (7) of Property 10 are sufficient to insure this result. For a symmetric matrix representation it can be shown that all of the conditions are necessary in order to obtain a inverse matrix that has the hyperdominant property.

#### C. Weakly No-Gain Elements

Before we proceed to introduce the concept of weakly no-gain elements, let us first consider the following property, which can be considered as a generalization of Property 6.

Property 11 No-Gain Networks containing Two-Terminal Elements Only

A network containing nonzero independent voltage and current sources, two-terminal "strictly passive" resistors, and two-terminal "exclusively passive" resistors 14 which do not form loops and cutsets by themselves has the no-gain property.

<u>Proof:</u> Let N be a network satisfying the hypotheses and let Q be an operating-point of N. By Corollary 7.1, a strictly passive two-terminal resistor is a no-gain element. Hence it can be replaced by a two-terminal positive linear resistor having the same operating-point, as indicated by Theorem 1. Let  $(V_p, I_p)$  be the corresponding operating-point voltage and current of an "exclusively passive" two-terminal resistor  $R_p$ . Then  $V_p I_p \ge 0$ . Observe that  $R_p$  can be replaced by a two-terminal linear element having the same operating-point  $(V_p, I_p)$ , where the linear two-terminal element is defined by:

An element will henceforth be called an "exclusively passive element" if it is passive but not strictly passive.

- (a) a positive linear two-terminal resistor with a resistance equal to  $V_p/I_p \Omega$  if  $I_pV_p \neq 0$ , and equal to  $1\Omega$  if  $I_p=V_p=0$

- (b) a short circuit element if  $V_{D} = 0$

- (c) an open circuit element if  $I_p = 0$

Let  $\hat{N}$  be the circuit obtained from N by replacing each strictly passive two-terminal resistor by a positive linear two-terminal resistor having the same operating point, and each "exclusively passive" two-terminal resistor by either a positive linear resistor or an open or a short circuit element having the same operating-point. Then  $\hat{N}$  has the same operating-point Q as N. Since the exclusively passive elements in N do not form loops or cutsets, there are no  $\hat{S}$ -loops or  $\hat{O}$ -cutsets in  $\hat{N}$ -- $\hat{N}$  satisfies all conditions of Property 6 -- and hence the operating-point voltages and currents associated with Q possesses the no-gain property. Consequently, N is a no-gain network.

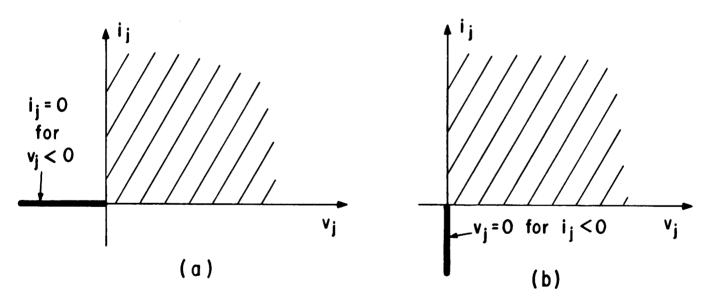

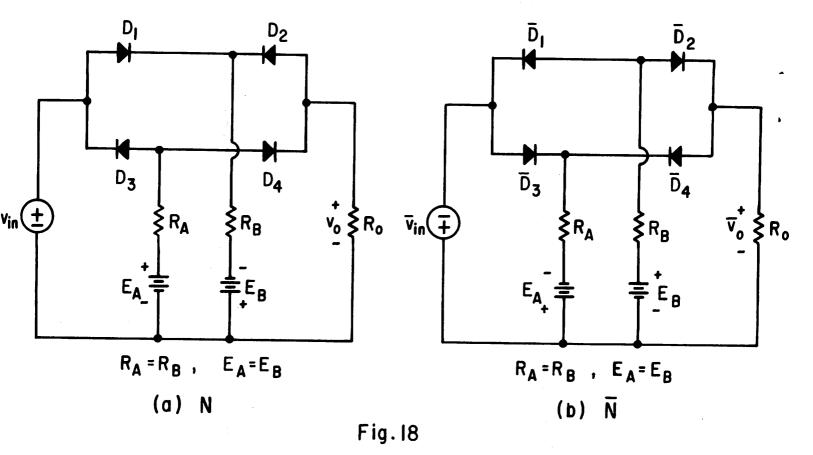

Observe that Theorem 1 implies that every no-gain resistor is at least strictly passive. This excludes many networks containing exclusively passive elements such as ideal diodes, ideal zener diodes and all kinds of three-terminal resistors having an input-output family of curves in the first quadrant plus a negative axis such as those shown in Fig. 6. However, Property 11 clearly demonstrates that the class of no-gain networks may include "exclusively passive" elements as well. This observation motivates the following definition.

#### Definition 7 Weakly No-Gain Elements

An n-terminal (n>2) resistor  $\mathbb R$  is said to be a <u>weakly no-gain</u> element if each connected network containing  $\mathbb R$ , positive linear two-terminal resistors, and nonzero independent voltage and current sources possesses the no-gain property. 15

To derive the basic properties of a weakly no-gain element, we need to develop the following two lemmas.

#### Lemma\_6

Let  ${\mathcal R}$  be a "weakly" no-gain n-terminal resistor imbedded in a network N

<sup>15</sup> Willson's definition of a no-gain element coincides with our definition of a "weakly no-gain element" [3]. However, his results are applicable only to networks containing no-gain elements as defined in our Definition 5, and therefore can not allow exclusively passive elements.

containing only positive linear two-terminal resistors and nonzero independent voltage and current sources. Let Q be an operating-point of  $\mathbb Q$ . Let us choose the terminal of  $\mathbb Q$  having the lowest potential as the datum node and label the remaining n-1 terminals of  $\mathbb Q$  so that the operating-point terminal voltages of  $\mathbb Q$  satisfy the inequality

$$V_{(1)} \ge V_{(2)} \ge \cdots \ge V_{(k)} \ge \cdots \ge V_{(n-1)} \ge 0$$

(46)

where  $V_{(1)}$  {resp.;  $V_{(2)}, V_{(3)}, \cdots$ } is the voltage between the highest {resp.; second highest, third highest,  $\cdots$ } and the lowest potential (datum) node of  $\mathbb{Q}$ . Let  $I_{(1)}, I_{(2)}, \cdots, I_{(n-1)}$  be the corresponding operating-point currents of  $\mathbb{Q}$ .

(a) If

$$V_{(1)} > V_{(2)} > \cdots > V_{(k)} > \cdots > V_{(n-1)}$$

(47)

Then the operating-point currents satisfy the following system of inequalities

$$I_{(1)} \geq 0$$

$$I_{(1)} + I_{(2)} \geq 0$$

$$\vdots$$

$$I_{(1)} + I_{(2)} + \cdots + I_{(k)} \geq 0$$

$$\vdots$$

$$I_{(1)} + I_{(2)} + \cdots + I_{(k)} + \cdots + I_{(n-1)} \geq 0$$

$$(48)$$

(b) If

$$V_{(1)} > V_{(2)} > \cdots > V_{(k)} = V_{(k+1)} > \cdots > V_{(n-1)}$$

(49)

Then the operating-point currents satisfy the following system of inequalities

$$I_{(1)} \geq 0 \tag{50a}$$

$$I_{(1)} + I_{(2)} \ge 0$$

(50b)

:

$$I_{(1)} + I_{(2)} + \cdots + I_{(k-1)} \ge 0$$

(50c)

$$I_{(1)} + I_{(2)} + \cdots + I_{(k-1)} + I_{(k)} + I_{(k+1)} \ge 0$$

(50d)

$$I_{(1)} + I_{(2)} + \cdots + I_{(k-1)} + I_{(k)} + I_{(k+1)} + I_{(k+2)} \ge 0$$

(50e)

:

$$I_{(1)} + I_{(2)} + \cdots I_{(k)} + \cdots + I_{(n-1)} \ge 0$$

(50f)

Proof: The proof of Lemma 6 is given in the Appendix.

Д

#### Lemma 7

Given any set of n-1 node-to-datum voltages satisfying (47) {resp.; (49)}, and any set of terminal currents satisfying (48) {resp.; (50)}, there exists a (not necessarily connected) n-terminal network containing  $m \le n-1$  positive linear two-terminal resistors and  $\ell \le n-1$  short circuit and open circuit elements which do not form  $\ell \le n-1$  open and  $\ell \le n-1$  short circuit and open circuit elements which same operating point voltages and currents.

Proof. The proof of Lemma 7 is given in the Appendix.

П

#### Property\_12 Criteria for Weakly No-Gain Elements

An n-terminal resistor  $\mathbb Q$  is a weakly no-gain resistor if, and only if, at each dc operating-point Q of  $\mathbb Q$ , there exists an n-terminal network  $N_Q$  having the same operating point Q, where  $N_Q$  contains  $m \le n-1$  positive linear two-terminal resistors and  $\ell \le n-1$  short circuit and open circuit elements which do not form  $\mathbb Q$ -loops and  $\mathbb Q$ -cutsets respectively, where  $m + \ell = n-1$ .

<u>Proof:</u> With Lemmas 6 and 7 replacing Lemmas 2 and 3, the proof of Property 12 parallels very closely with the proof of Theorem 1 and is therefore omitted.

¤

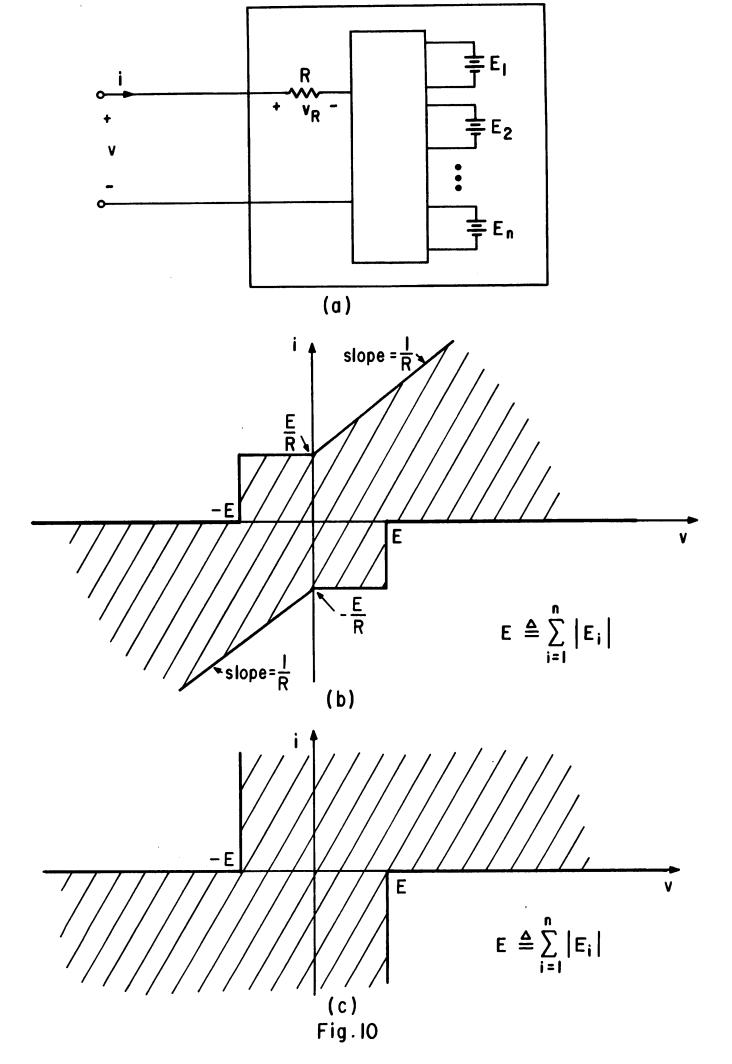

## IV. BOUNDING REGIONS FOR DRIVING-POINT AND TRANSFER CHARACTERISTIC PLOTS

We will now apply the results from the preceding section to show that the DP and TC plots of a resistive network containing only no-gain multi-terminal resistors and independent sources must lie within some specific bounding regions. To do this, we must first generalize the well-known "maximum and minimum voltage node" theorem [16] to allow networks containing multi-terminal resistors.

## Property 13. Maximum and Minimum Voltage Node Theorem

Let N be a connected resistive network containing only <u>no-gain</u> multiterminal resistors and independent dc voltage and current sources. Then the <u>highest potential node</u> (resp.; <u>lowest potential node</u>) must necessarily be connected to either a voltage source, or a current source.

<u>Proof.</u> Since all multi-terminal resistors are no-gain by hypothesis, it follows from <u>Theorem 1</u> that they can all be replaced by an appropriate interconnections of two-terminal positive linear resisters without affecting the node voltages. Hence the result follows immediately from the "maximum and minimum voltage node" theorem for networks containing two-terminal no-gain resistors and sources [16].

п

A dual version of <u>Property 13</u>, as well as of the following properties can be proved but are omitted to conserve space.

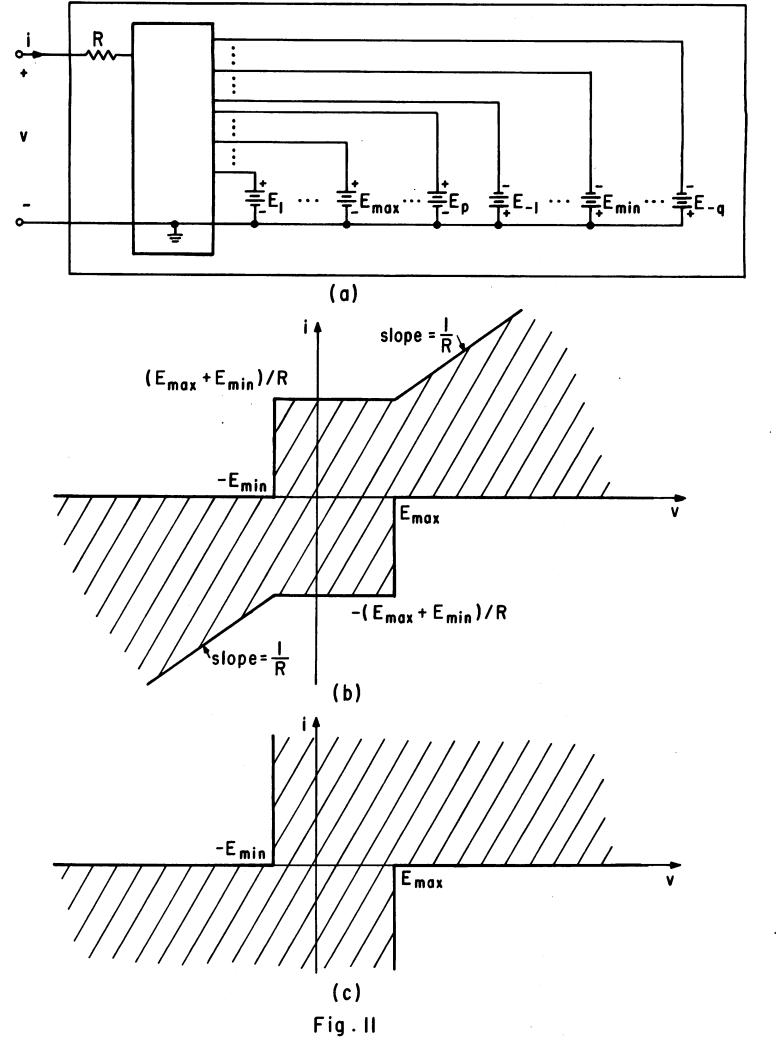

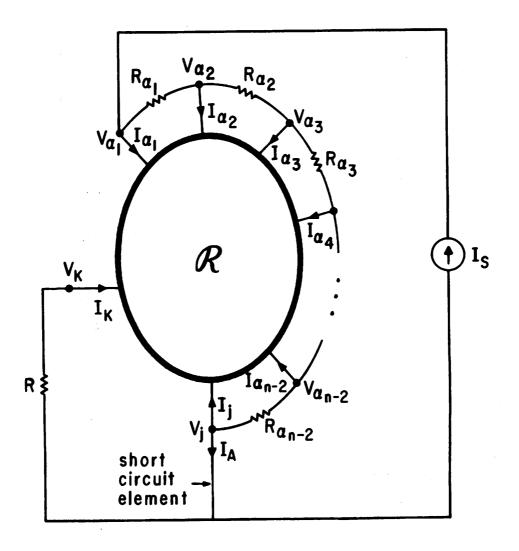

Property 14. Voltage Bound for No-Gain Networks with Grounded Sources

Let N be a connected resistive network containing only no-gain multiterminal resistors and grounded dc voltage sources. Then the node-to-ground voltage v of any node k is bounded by

$$- E_{\min} \leq V_{(k)} \leq E_{\max}$$

(51)

where  $E_{max}$  {resp.; -  $E_{min}$ } denotes the terminal voltage of the voltage source with the highest {resp.; lowest} node-to-ground voltage.

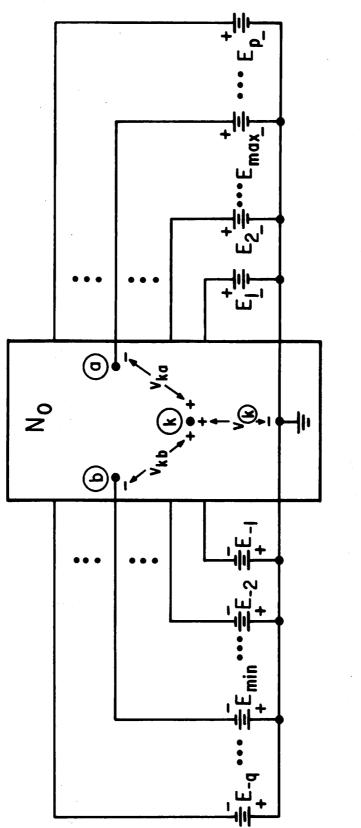

<u>Proof.</u> The network N can be represented with all voltage sources extracted as shown in Fig. 7, where  $N_0$  contains only no-gain multi-terminal resistors. It follows from the definition of  $E_{\max}$  and  $E_{\min}$  that node (a) is the highest-potential node while node (b) is the lowest-potential node.

Let (k) be an arbitrary node of  $N_0$ , then

$$v_{(k)} = v_{ka} + E_{max} = v_{kb} - E_{min}$$

(52)

It follows from Property 13 that

$$-(E_{\max} + E_{\min}) \le v_{ka} \le 0$$

(53)

$$0 \le v_{kb} \le (E_{max} + E_{min}) \tag{54}$$

Adding  $E_{\text{max}}$  to both sides of (53) and adding  $-E_{\text{min}}$  to both sides of (54), we obtain

$$-E_{\min} \le v_{ka} + E_{\max} \le E_{\max}$$

(55)

$$-E_{\min} \le v_{kb} - E_{\min} \le E_{\max}$$

(56)

П

Substituting either (55) or (56) into (52), we obtain (51).

# Corollary 14.1

The magnitude of the node-to-ground voltage of any connected network containing diodes, transistors, operational amplifiers,  $^{16}$  and other no-gain multi-terminal resistors which are biased by a set of complementary dc power supplies of  $\pm$   $E_{CC}$  volts with respect to ground cannot exceed  $E_{CC}$ .

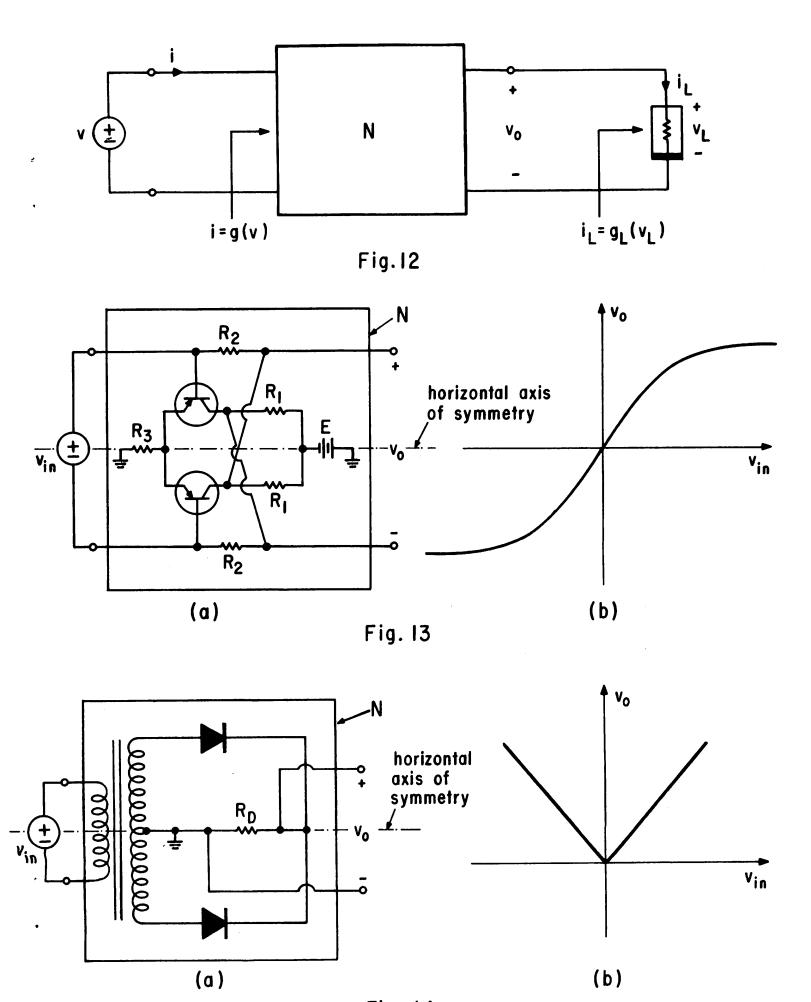

We are now ready to derive bounding regions for the  $\mathbf{v}_0$  -  $\mathbf{v}_s$  -  $\mathbf{v}_{in}$  TC plot of no-gain networks.

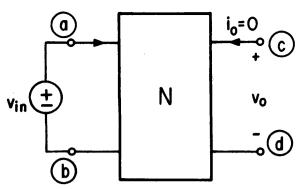

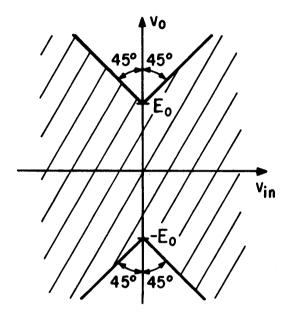

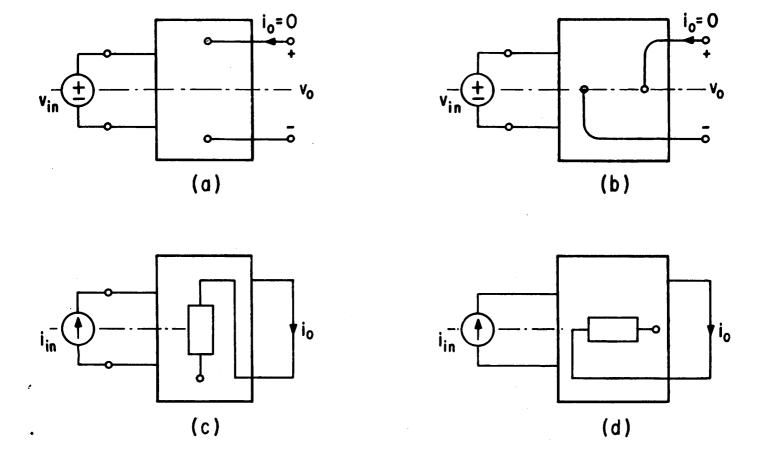

## Property 15. TC Plot Bounding Region for Ungrounded Two-Ports

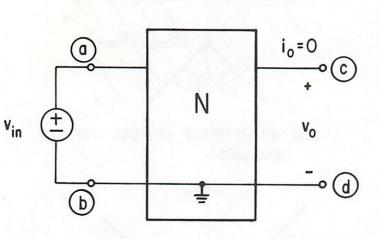

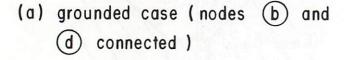

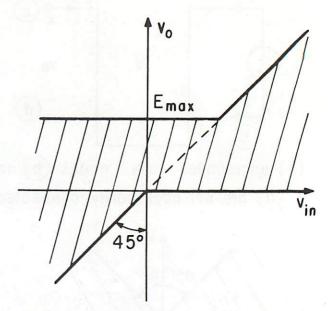

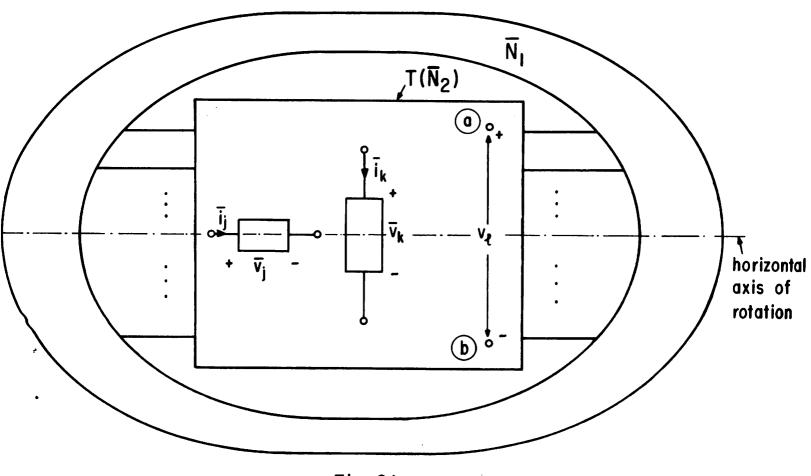

Let N be any connected network containing no-gain multi-terminal resistors and dc voltage sources as shown in Fig. 8(a), where nodes (b) and (d) are not necessarily connected to each other. Then we have:

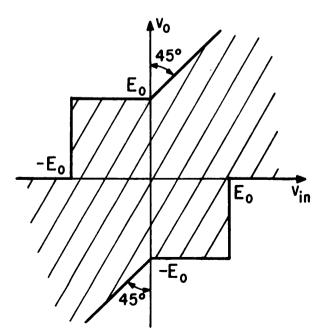

- (a) The TC plot must lie within the shaded region shown in Fig. 8(b), where  $\mathbf{E}_0$  denotes the sum of the voltage magnitudes of all internal voltage sources.

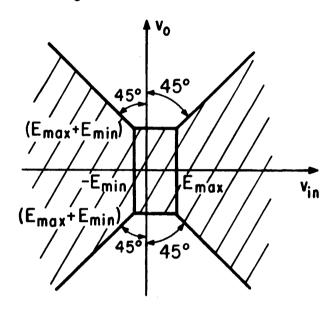

- (b) If the input terminal (a) and output terminal (c) are connected together, 17 then the bounding region in Fig. 8(b) shrinks to that shown in Fig. 8(c).

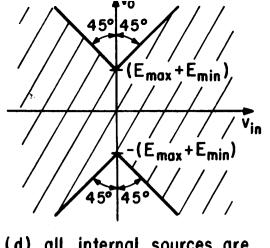

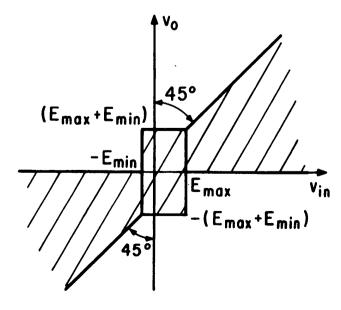

- (c) If all internal voltage sources are grounded as in Fig. 7, then the TC plot must lie within the shaded region shown in Fig. 8(d).

- (d) If all voltage sources (including the input voltage source  $\mathbf{v}_{in}$ ) are grounded, then the bounding region shown in Fig. 8(d) shrinks further to that shown in Fig. 8(e).

- (e) If all voltage sources (including the input voltage source v<sub>in</sub>) are grounded,

This somewhat specialized condition will turn out to be quite relevant to the proof of Property 17.

An operational amplifier here is considered as a six-terminal element with two of the six terminals being connected to two complementary power supplies, one with  $+ E_{CC}$  and the other with  $- E_{CC}$  volts with respect to ground [17].

and if the input terminal (a) and output terminal (c) are connected together, then the bounding region shown in Fig. 8(e) shrinks further to that shown in Fig. 8(f).

## Proof.

(a) Since N is a no-gain network, we have

$$|\mathbf{v_0}| \le |\mathbf{v_{in}}| + \mathbf{E_0} \tag{57}$$

where

$$\mathbb{E}_{0} \stackrel{\Delta}{=} \sum_{i=1}^{n} |\mathbb{E}_{i}| \tag{58}$$

and n denotes the number of internal voltage sources. The bounding region defined by (57) is precisely that shown in Fig. 8(b).

(b) Consider first the case  $0 \le v_{in} \le E_0$  and let  $v_{bd}$  denote the voltage between nodes (b) and (d); i.e.,

$$v_0 = v_{in} + v_{bd} \tag{59}$$

Since N contains only no-gain elements and dc voltage sources,

$$v_{bd} \ge -v_{in} - E_0 \tag{60}$$

where  $\mathbf{E}_0$  is as defined in (58). It follows from (59) and (60) that

$$v_0 \ge -E_0$$

whenever  $0 \le v_{in} \le E_0$  (61)

If  $v_{in} \geq E_0$ , then node (a) becomes the highest-potential node and hence

$$v_0 \ge 0$$

whenever  $v_{in} \ge E_0$  (62)

The bounding region in the fourth quadrant of Fig. 8(e) is precisely that defined by (61) and (62). A similar analysis shows that

$$v_0 \le E_0$$

whenever  $-E_0 \le v_{in} \le 0$  (63)

and .

$$v_0 \le 0$$

whenever  $v_{in} \le -E_0$  (64)

1

Equations (63) and (64) defined the shaded region shown in the second quadrant of Fig. 8(c). The bounding regions in the first and third quadrants follow from part (a).

(c) Since the node having the maximum or the minimum potential must be connected to a voltage source and since all internal voltage sources are connected to a common ground as in Fig. 7, the potential between the highest voltage node and the lowest voltage node cannot exceed  $|\mathbf{v}_{in}| + \mathbf{E}_{max} + \mathbf{E}_{min}$ . Hence,

$$0 \le v_0 \le |v_{in}| + (E_{max} + E_{min})$$

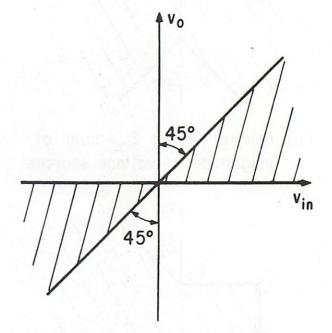

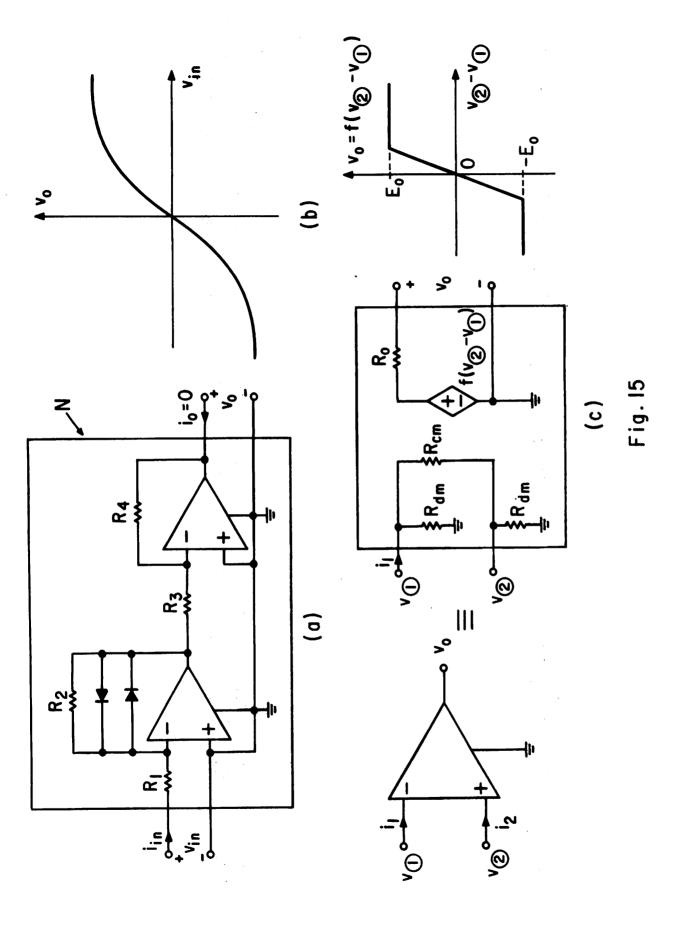

(65)