# Copyright © 1999, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# THERMAL EFFECTS IN DEEP SUB-MICRON VLSI INTERCONNECTS AND IMPLICATIONS FOR RELIABILITY AND PERFORMANCE

by

Kaustav Banerjee

Memorandum No. UCB/ERL M99/48

22 September 1999

COVER

# THERMAL EFFECTS IN DEEP SUB-MICRON VLSI INTERCONNECTS AND IMPLICATIONS FOR RELIABILITY AND PERFORMANCE

by

Kaustav Banerjee

Memorandum No. UCB/ERL M99/48

22 September 1999

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering

University of California, Berkeley

94720

# Thermal Effects in Deep Sub-Micron VLSI Interconnects and Implications for Reliability and Performance

by

#### Kaustav Banerjee

B.S. (St. Xavier's College, University of Bombay, India) 1990M.S. (Marquette University, Wisconsin, USA) 1993

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA AT BERKELEY

Committee in charge:

Professor Chenming Hu, Chair Professor Nathan W. Cheung Professor Tim Sands

#### The dissertation of Kaustav Banerjee is approved:

Chair Aug. 24, 1999

Date

Nothan Chang Aug. 26, 1999

Date

Jang D. L. S Ang 24 th, 1999

University of California at Berkeley

Fall 1999

# Thermal Effects in Deep Sub-Micron VLSI Interconnects and Implications for Reliability and Performance

Copyright © 1999

by

Kaustav Banerjee

#### Abstract

# Thermal Effects in Deep Sub-Micron VLSI Interconnects and Implications for Reliability and Performance

#### by Kaustav Banerjee

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California at Berkeley

Professor Chenming Hu, Chair

An investigation of thermal effects in deep sub-micron VLSI interconnect structures has been carried out and their implications on reliability and performance have been analyzed. Thermal effects are becoming an increasingly important issue in all high performance circuits due to increasing current density and power consumption. They are emerging as a key factor determining the design, performance, and reliability of future ICs.

This study begins with the development of suitable characterization and thermometry techniques to supplement the theoretical modeling and simulation work with experimental data. A novel thermometry technique, namely Transient Resistive Thermometry (TRT), together with a variation utilizing the Kelvin technique has been developed to facilitate systematic studies of thermal characterization in various interconnect structures in a modern VLSI technology. These techniques provide contactless temperature measurements by monitoring the temperature induced change of the resistivity of the material under study. They provide accurate estimation of spatially averaged temperatures with excellent temporal resolution within nanosecond timescales and also allow precise identification of thermal failures in the interconnect structures, thus helping the optimization of interconnect process design and reliability. A second thermometry technique called Scanning Joule Expansion Microscopy (SJEM) has also been advanced to facilitate thermal mapping of deep sub-micron VLSI structures with sub-100 nm spatial resolution.

2

The TRT technique has been used to characterize and model thermal effects in VLSI

metallization arising due to ultra short-duration high-current pulses during peak current and

electrostatic discharge events. A model that takes into account heat diffusion under non-steady

state conditions has been formulated to generate design guidelines for metal interconnects.

Several IC manufacturers including TI, IBM, and INTEL have incorporated this model in their

design process. Additionally, a new latent interconnect failure mode in AlCu lines has been

discovered that significantly degrades their electromigration performance.

The TRT technique has also been shown to be an effective characterization tool to study

the dynamic thermal response of low dielectric-constant materials used as inter-layer insulators in

advanced interconnect systems. It offers a unique way of comparing the thermal characteristics

(including thermal conductivity) of various dielectric films. The high-current behavior of thin

Titanium and Cobalt silicide films used in advanced CMOS technologies has also been

characterized and modeled using the TRT technique.

Using the TRT technique a new failure mode in deep sub-micron silicided barrier

contacts has been identified for the first time.

The impact of thermal effects on the silicide-Si contact-resistance of small-geometry

contact structures has been quantified. It has been found that contact-resistance sensitivity to

temperature and current is a strong function of the silicide thickness, and is independent of the

contact-plug material.

This research ends with an extensive study of circuit and interconnect performance

implications arising due to thermal effects. The increasing influence of thermal effects on the

design (driver sizing) and optimization of the interconnect length between repeaters for signal and

power lines has been demonstrated.

Professor Chenming Hu

Dissertation Committee Chair

То

Ma, Bapi, and Sheetal

#### **Acknowledgments**

My years at *Cal* will always have a special place in my memories. What an amazing place! From the early hours of a misty Sunday morning in mid-August 1993, when I first landed in Berkeley after an interesting drive from the San Francisco airport through University Avenue, I must admit that I have been captivated by this place. Apart from its academic excellence, its unique landscapes with the SF Bay on the west and the Berkeley Hills to the east, wonderful array of restaurants from around the world, cafes that are busier during the nights, musicians, fortunetellers, and hawkers, on Telegraph Avenue, the old bookstores, the activists of Sproul Plaza and People's Park, along with numerous radical characteristics of Berkeley make it a haven for so many world renowned academicians, including several Nobel Laureates, Turing Award and Field's Medal winners, and top-notch researchers and students from across the world. It is truly a University beyond compare, and I couldn't have picked a better place for my doctoral education and research.

During my exciting and eventful student life that began in St. Xavier's College, Bombay, I have met several outstanding students and professors, some of whom have left most indelible marks on my memory and have significantly influenced my thoughts and my personality. However, one individual who has inspired me the most is Professor Chenming Hu, my research advisor at Berkeley, an exceptionally gifted person with outstanding technical achievements and with an unusual flair for fine arts. He has truly been my mentor, philosopher, and guru. I would like to express my most sincere appreciation for him for giving me complete freedom to explore new ideas and for taking keen interest in my research projects and personal well being. I am grateful for all his support, encouragement, and invaluable advice.

I would also like to thank Professor Nathan Cheung and Professor Tim Sands, for serving in my dissertation committee. They have provided several constructive criticisms, which have in turn, helped me formulate my dissertation in its present form. I have always been very impressed with Professor Cheung's sense of humor that helped lighten up the atmosphere during several research meetings and discussions. Professor Sands is one of the most approachable faculties in Berkeley, and I have always enjoyed talking to him.

During the course of my stay at Berkeley I got the opportunity to interact with several other distinguished faculties, which helped me formulate new ideas and also look at problems from different perspectives. Some of these Professors at Berkeley with whom I have had several fruitful discussions in classrooms or during technical meetings are: Professor Jeff Bokor, Professor Richard White, Professor Michael Liebermann, Professor Jan Rabaey, Professor Andy Glaeser, Professor Jim Morris, Professor Eicke Weber, Professor Ron Gronsky, and Professor Arun Majumdar.

I would also like to thank Professsor Ken Goodson from Stanford University for several interesting discussions on thermal problems and for providing some thermal conductivity data. I must also acknowledge Dae-Yong Kim from Stanford for lending his TEM expertise. I would also thank Dr. Sven Rzepka, visiting scholar from the Technical University of Dresden, Germany, for several interesting discussions on thermal problems.

I would like to thank the U.S. Semiconductor Research Corporation for providing necessary funding at Berkeley during 1995-1998. I must also thank Texas Instruments Inc., Dallas, for supporting much of my research activities through summer internships and for a \$20,000 award during 1993-1997. In particular, I would like to thank Dr. Ajith Amerasekera and Dr. William Hunter for providing endless guidance and encouragement during various phases of this work. In fact, Ajith has been very closely involved in my projects, and I have really enjoyed co-authoring several research publications with him. He also provided several constructive comments after reading this entire manuscript.

I would like to acknowledge Dr. Joe W. McPherson, Dr. Charvaka Duvvury, Dr. Robert Havemann, Dr. Ping Yang, and Dr. Tim Rost, all from TI, for their enthusiastic support and collaborative involvement in some of my projects. I would also like to acknowledge several interesting technical discussions with Dr. Ih-Chin Chen, Dr. Girish Dixit, Dr. Amitava Chatterjee, Dr. Mark Rodder, Dr. Jorge Kittl, Dr. Sridhar Ramaswamy, Dr. Jerold Seitchik, Dr. Larry Ting, Dr. Alwin Tsao, and Paul Nicollian, from TI. It has indeed been a pleasure interacting with them.

I have also been very fortunate to be surrounded by several outstanding students at Berkeley, some of whom have become my closest friends and associates: Amit Mehrotra, Shaz Qadeer, Mukul Prasad, Amit Narayan, Premal Buch, Gurmeet Singh Manku, Alok Aggarwal,

Rajeev Murgai, Harmeet Singh, Sriram Rajamani, Amoolya Singh, Igor Kouznetsov, Jon Gudmundsson, Alexei Marakhtanov, Kedar Patel, Philip Chong, Michael Shilman, Subarnarekha Sinha, Heloise Hwawen-Hse, Ravi Gunturi, Luca Carloni, Marco Sgroi, Edoardo Charbon, Sunil Khatri, Sekhar Narayanaswami, George Varghese, and Nikhil Jakatdar to name a few.

I would also like to acknowledge my past and present colleagues and friends from the Device group and the Plasma lab: James Chen, Michael Orshansky, Jone Chen, Dennis Sylvester, Kai Chen, Qiang Lu, Barry Linder, William Wong, Sunder Kumar Iyer (SKI), Erin Jones, Bill En, Jiang Tao, and Xiang Lu. I would also like to thank Guanghua Wu and Masanobu Igeta from the mechanical engineering department for their help and collaboration in thermal microscopy project.

Infrastructure and support are important components of any organization. In this regard, I would like to thank Ruth Gjerde and Mary Byrnes of the EECS graduate office in 231 Cory Hall for all their help with administrative matters. I would also like to specially thank our group administrator Judy Fong for all her help with administrative issues, travel arrangements and reimbursements, and in dealing with funding agencies. She took care of all these important issues most efficiently and always with a smile. Another person at Berkeley who deserves special mention is Mr. Ted Goode, the International Student Advisor. He is one of the most knowledgeable and helpful legal staff in the International Student Center at the I-House and helped me a number of occasions during international travel, summer internships, and even during my change of Visa status after graduation.

I would also like to acknowledge a couple of friends outside the University but residents of the great city of Berkeley: Pradeep Kumar and Rizwan Rahmani. Pradeep always amazed me with his great sense of humor, and his culinary and entrepreneurial skills. I would like to thank Rizwan Bhai (along with Shaz) for all the good times we had in Berkeley and San Francisco, in particular, the late nights at Café Strada, and Au Coquelet Café in Berkeley and at Steps of Rome and Shalimar in San Francisco, appreciating Meer, Ghalib, Iqbal, Faiz, Momin, and other Urdu poets. These extracurricular activities and the discussions on all aspects of life (and some EE problems...) at Café Nefeli near Cory Hall made my Berkeley experience worthwhile.

vii

On the family front, I want to thank my parents for all their love and attention and for

providing constant encouragement and challenge to achieve "greater things" in life. I would also

like to thank my wife's parents, my brother, and my sister for their love and solidarity. Finally, I

want to express my deepest gratitude to my wife, Sheetal, for her endless love, and for gracefully

enduring these lost years of our lives. She has provided constant support, help, and

encouragement during the writing of this thesis.

August 24, 1999

Berkeley, California

dam-e-har-mauj mein hai, halqa-e-sad-kam-e-nahang dekhein kya guzray hai qatray pe guhar hone tak .....Ghalib

(A noose in every wave, infinite dragons in every noose Yearning to be a pearl, will I win or will I lose?)

# **Contents**

| Acknowledgments                                                            | iv   |

|----------------------------------------------------------------------------|------|

| List of Figures                                                            | xii  |

| List of Tables                                                             | xxiv |

| Chapter 1                                                                  |      |

| Introduction                                                               |      |

| 1.1 Thermal Effects in VLSI Interconnects: An Overview                     |      |

| 1.2 Trends in VLSI Scaling and Implications on Thermal Effects             |      |

| 1.3 Impact on Interconnect Reliability and Design                          |      |

| 1.5 Organization                                                           |      |

| -10 O-16                                                                   |      |

| Chapter 2                                                                  |      |

| Basic Concepts for Analyzing Self-Heating Effects in Metal Interconnects   | 12   |

| 2.1 DC Electrical Conductivity of a Metal                                  |      |

| 2.2 Physics of Joule Heat Generation                                       |      |

| 2.3 Fourier's Law and Thermal Conductivity                                 |      |

| 2.4 Heat Conduction Equation in a Metal Line Heated by an Electric Current |      |

| 2.5 Electrothermal Analog                                                  |      |

| 2.5.1 The Transmission Line Equation                                       |      |

| 2.5.3 Concept of Thermal Resistance (or Impedance)                         |      |

| 2.5.4 Concept of Thermal Capacitance                                       |      |

| 2.5.5 Thermal Time Constant                                                |      |

| 2.5.6 Electrothermal Analogs for VLSI Interconnect                         |      |

| 2.5.7 Thermal Circuit for Packaged VLSI Interconnect                       | 20   |

| Chapter 3                                                                  |      |

| Interconnect Heating and Failure under Short-Pulse Stress Conditions       | 20   |

| 3.1 Introduction                                                           |      |

| 3.2 Electrostatic Discharge (ESD) in Integrated Circuits                   | 30   |

| 3.3 ESD Reliability Due to Interconnect Failure                            | 3    |

| 3.4 Interconnect Failures Due to High Current Pulses: Prior Literature     |      |

| 3.5 Sample Fabrication                                                     |      |

| 3.6 Interconnect Thermometry Techniques                                    |      |

| 3.7 Resistive Thermometry                                                  |      |

| 3.8.1 Basic Concept                                                        |      |

| 3.8.2 System Design                                                        | 3    |

| 3.8.3 Equivalence of the Constant Current Square Pulse and ESD             | 42   |

| 3.9 Interconnect Heating and Failure under Short-Pulse Stress                        | 42  |

|--------------------------------------------------------------------------------------|-----|

| 3.9.1 Comparison with Electromigration                                               |     |

| 3.9.2 Temperature Calibration and Steady-State Measurements                          |     |

| 3.9.3 Pulsed Measurements                                                            | 44  |

| 3.10 Finite Element Simulations                                                      | 47  |

| 3.10.1 Simulator Calibration                                                         | 48  |

| 3.10.2 Simulation of Transient Interconnect Heating                                  | 49  |

| 3.11 Interconnect Heating and Failure Model under Short-Pulse Stress Conditions      |     |

| 3.12 Interconnect Design Rules for High-Current Robustness                           | 59  |

| 3.13 Failure Modes under High-Current Short-Pulse Stress                             | 60  |

| 3.13.1 Open Circuit Failure Mechanism                                                | 60  |

| 3.13.2 Latent Damage: Impact on EM Reliability                                       |     |

| 3.14 Summary                                                                         | 67  |

| Chapter 4                                                                            |     |

| Impact of Scaling and Low-k Dielectric on Thermal Characteristics of Interconnects   |     |

| 4.1 Introduction                                                                     |     |

| 4.2 Minimization of Interconnect (RC) Delay using Low-k Dielectric                   |     |

| 4.3 Sample Fabrication and Experiments                                               |     |

| 4.4 Thermal Characterization under DC Stress Conditions                              |     |

| 4.5 Thermal Characterization under Pulsed Stress Conditions                          |     |

| 4.5.1 Standard Dielectric Process                                                    |     |

| 4.5.2 Low-k Dielectric Process                                                       |     |

| 4.6 Implications of Interconnect Scaling                                             |     |

| Chapter 5                                                                            |     |

| Failure Mechanisms of Contacts and Vias under High Current Stress Conditions         | 83  |

| 5.1 Introduction                                                                     | 83  |

| 5.2 Prior Work                                                                       | 84  |

| 5.3 Sample Fabrication                                                               | 85  |

| 5.4 Transient Kelvin Thermometry (TKT) Technique                                     | 87  |

| 5.5 Characterization of Contact Structures                                           |     |

| 5.6 Contact Failure Mechanism                                                        |     |

| 5.7 Characterization of Via Structures                                               |     |

| 5.8 Summary                                                                          | 99  |

| Chapter 6                                                                            |     |

| Thermal Effects in Thin Silicide Films                                               | 101 |

| 6.1 Introduction                                                                     | 101 |

| 6.2 Sample Fabrication                                                               |     |

| 6.3 Characterization and Modeling of High Current Effects in TiSi <sub>2</sub> Films |     |

| 6.3.1 Characterization of High DC (steady state) Conduction                          | 104 |

| 6.3.2 Model for Resistance Variation under High DC Stress                            | 105 |

| 6.3.3 Characterization of High Pulsed Current Conduction                                       | 107 |

|------------------------------------------------------------------------------------------------|-----|

| 6.3.4 Model for Resistance Variation Under Pulsed Current                                      | 109 |

| 6.4 Technology and Process Dependence of High Current Conduction                               |     |

| 6.4.1 High Current Conduction in CoSi <sub>2</sub> Films                                       |     |

| 6.4.2 Comparison of Mo Implant and Ge Pre-Amorphization Implant (PAI)                          | 112 |

| 6.4.3 High Current Effects in TiSi <sub>2</sub> and CoSi <sub>2</sub> Films on Poly-Si         | 114 |

| 6.5 Failure Mechanisms                                                                         |     |

| 6.5.1 Failure Mechanisms of TiSi <sub>2</sub> and CoSi <sub>2</sub> films on n+ Si             |     |

| 6.5.2 Failure Mechanisms of TiSi <sub>2</sub> and CoSi <sub>2</sub> films on n+ poly-Si        |     |

| 6.5.3 Geometry and Pulse Width Dependence of I <sub>crit</sub>                                 |     |

| 6.6 Summary                                                                                    |     |

| Chapter 7                                                                                      |     |

| Impact of Thermal Effects on Small-Geometry Titanium Silicide-Si Contact Resi 7.1 Introduction |     |

| 7.1 Introduction                                                                               |     |

| 7.2 Contact Resistance in Deep Sub-Micron MOSFETS                                              |     |

| 7.4 Device Fabrication and Experiments                                                         |     |

| 7.5 Characterization of Thermal Effects on R <sub>c</sub>                                      |     |

| 7.5.1 Temperature and Low Current Effects on Contact Resistance                                |     |

| 7.6 Quantitative Model for TiSi <sub>2</sub> -Si Contact Resistance                            |     |

| 7.6.1 Carrier Transport Mechanisms                                                             |     |

| 7.6.2 Specific Contact Resistance under FE and TFE                                             |     |

| 7.6.3 Temperature Dependence of Specific Contact Resistance                                    |     |

| 7.6.4 Unified Quantitative Model for Contact Resistance                                        |     |

| 7.7 High Current Effects on Contact Resistance                                                 |     |

| 7.7.1 Self-Heating Effects on Contact Resistance                                               |     |

| 7.7.2 Polarity Dependence of High Current Behavior                                             |     |

| 7.8 Failure Mechanisms                                                                         |     |

| 7.9 Summary                                                                                    |     |

| Chapter 8                                                                                      |     |

| Thermal Characterization of Small Geometry Vias using Scanning Joule Expans Microscopy         |     |

| 8.1 Introduction                                                                               |     |

| 8.2 SJEM Experimental Setup                                                                    | 155 |

| 8.3 Via Fabrication and Sample Preparation                                                     |     |

| 8.4 Temperature Calibration                                                                    |     |

| 8.5 Self-Heating Analysis under Sinusoidal Bias                                                | 160 |

| 8.5 Self-Heating Analysis under Pulsed Bias                                                    |     |

| 8.6 Summary                                                                                    |     |

| -                                                                                              |     |

### Chapter 9

| Highly Accelerated Electromigration Tests for Interconnect Reliability Evaluation | 171 |

|-----------------------------------------------------------------------------------|-----|

| 9.1 Introduction                                                                  | 171 |

| 9.2 Sample Fabrication                                                            |     |

| 9.3 Results and Discussion                                                        |     |

| 9.4 Summary                                                                       |     |

| Chapter 10                                                                        |     |

| Implications of Thermal Effects on Interconnect Reliability and Performance       | 179 |

| 10.1 Introduction                                                                 | 179 |

| 10.2 Interconnect Design Rules: Current Approach                                  | 181 |

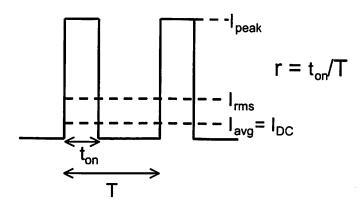

| 10.2.1 Average, RMS, and Peak Current Density                                     |     |

| 10.2.2 Electromigration and Self-Heating                                          |     |

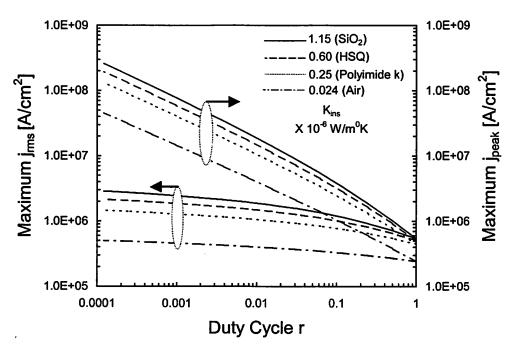

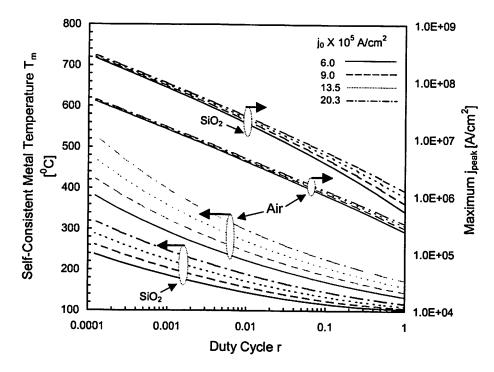

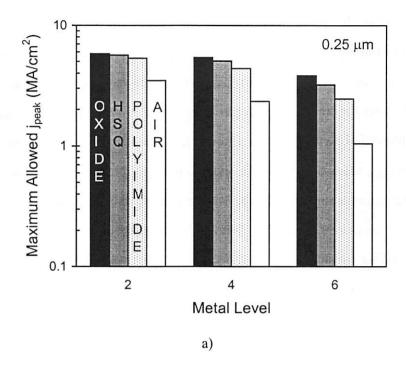

| 10.3 Thermal Effects in DSM Interconnects                                         | 184 |

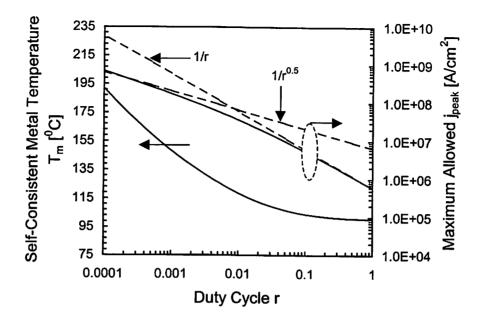

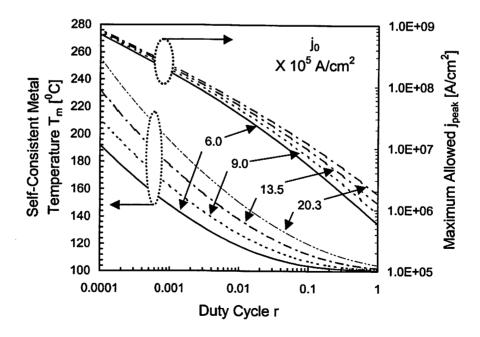

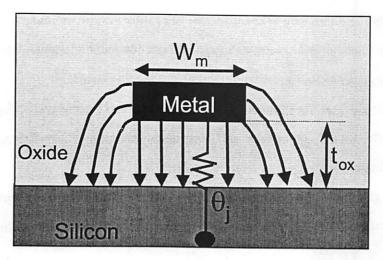

| 10.3.1 Self-Consistent Interconnect Design Analysis                               |     |

| 10.3.2 Technology Scaling Effects on Self-Consistent Design Rules                 |     |

| 10.4 Implications for Circuit Performance and Design                              | 195 |

| 10.4.1 Effects on Signal Line Length, and Driver Size Optimization                | 195 |

| 10.5 Thermal Effects in Real 3-D Interconnect Arrays                              | 201 |

| 10.6 Thermal Effects under ESD Conditions                                         | 204 |

| 10.7 Summary                                                                      | 205 |

| Chapter 11                                                                        |     |

| Conclusions and Future Directions                                                 | 206 |

| APPENDIX A                                                                        | 212 |

| APPENDIX B                                                                        | 216 |

| Bibliography                                                                      | 217 |

# LIST OF FIGURES

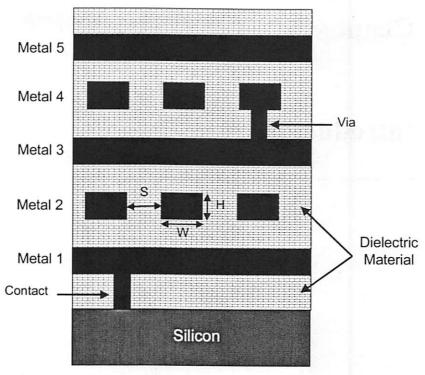

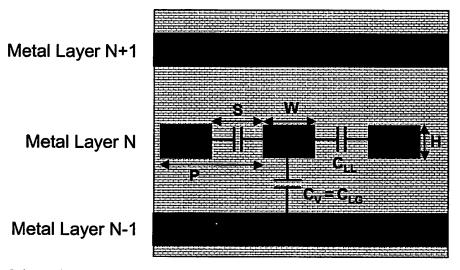

| riguic i.i | VLSI circuits. The metal pitch is defined as $(W + S)$ and the aspect ratio is defined as $(H/W)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

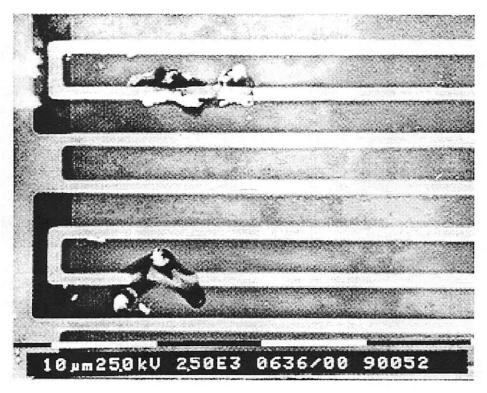

| Figure 1.2 | An ESD failure in an NMOS output transistor of an advanced CMOS process after a 3.5 kV HBM ESD stress. (Courtesy of Dr. Ajith Amerasekera, Texas Instruments Inc.)                                                                                                                                                                                                                                                                                                                                                                                                    |

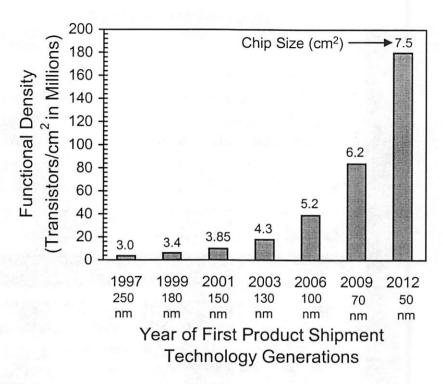

| Figure 1.3 | Present and projected functional density and chip size of microprocessors for different technology nodes and year of first product shipment as per NTRS [13]. The functional density is expected to increase from 3.7 million in 1997 to 180 million in 2012                                                                                                                                                                                                                                                                                                          |

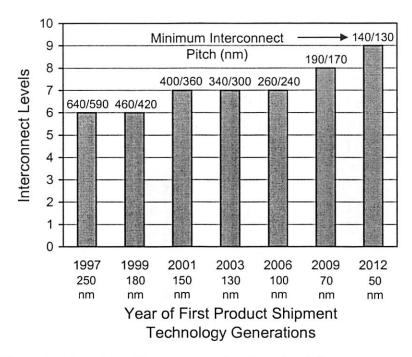

| Figure 1.4 | Present and projected interconnect levels and minimum contacted/non-contacted interconnect metal pitch of logic circuits for different technology nodes and year of first product shipment as per NTRS [13]                                                                                                                                                                                                                                                                                                                                                           |

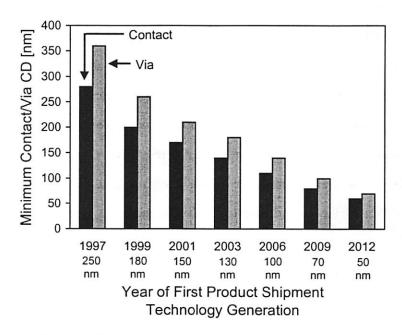

| Figure 1.5 | Present and projected minimum contact/via critical dimensions (CD) of logic circuits for different technology nodes and year of first product shipment as per NTRS [13].                                                                                                                                                                                                                                                                                                                                                                                              |

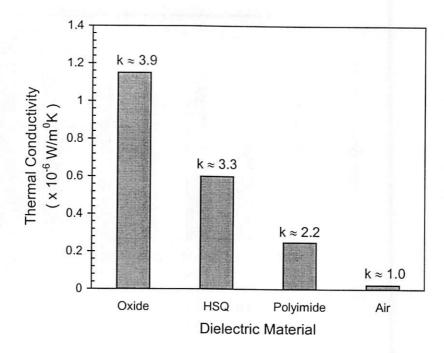

| Figure 1.6 | Thermal conductivity and approximate dielectric constants (k) of some insulating materials used (or being introduced) in high performance circuits6                                                                                                                                                                                                                                                                                                                                                                                                                   |

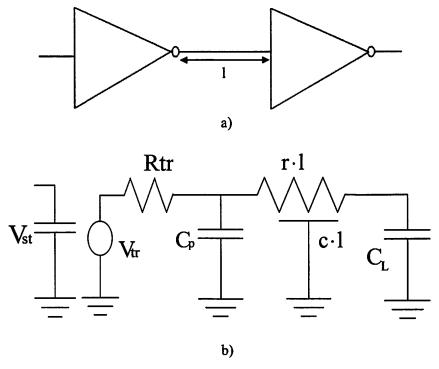

| Figure 1.7 | a) Schematic representation of an interconnect segment of length <i>l</i> between two inverters, and b) an equivalent distributed RC circuit                                                                                                                                                                                                                                                                                                                                                                                                                          |

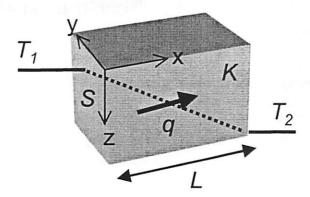

| Figure 2.1 | Heat transfer by conduction through a plane slab of cross-sectional area $S$ and length $L$ . The temperature on the left hand surface is $T_1$ and on the right hand surface is $T_2$ , with $T_1 > T_2$ , $q$ is the rate of heat transfer.                                                                                                                                                                                                                                                                                                                         |

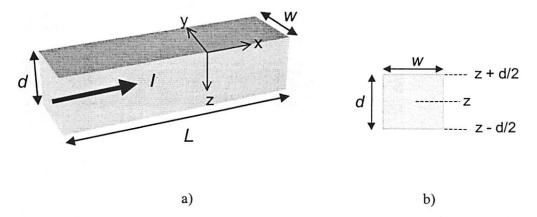

| Figure 2.2 | a) Schematic view of a metal line carrying current I. b) The cross sectional view17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

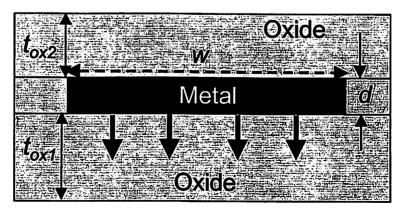

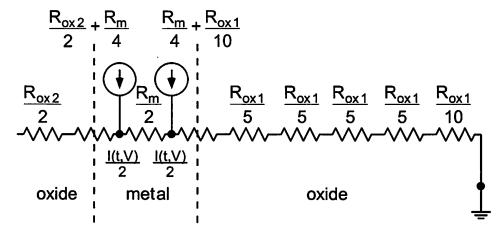

| Figure 2.3 | A 1-D example of heat flow, Joule heated interconnect line embedded in oxide, $w >> t_{ox1}$ , $t_{ox2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

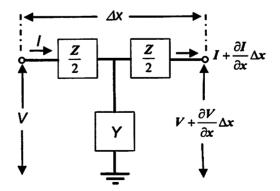

| Figure 2.4 | A single lumped parameter "Tee" section of a transmission line19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

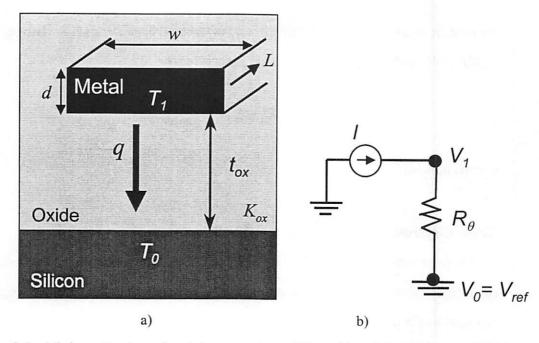

| Figure 2.5 | a) Schematic view of an interconnect metal line of length $L$ , width $w$ , and thickness $d$ embedded in oxide. The underlying oxide thickness is $t_{ox}$ . Heat flow $(q)$ is assumed to be 1-D and towards the underlying silicon which acts as the heat sink. The metal line heated by a current is at an average temperature $T_l$ , while the silicon is assumed to be at room temperature (or reference temperature) $T_0$ . b) Equivalent DC lumped thermal circuit. $R_\theta$ is the thermal resistance of the interconnect line to the silicon substrate. |

| Figure 2.6 | Distributed thermal circuit for the metal line of Figure 2.5 under DC (steady-state) conditions. $R_{ox2}$ and $R_{ox1}$ are the effective thermal resistance of the overlying and underlying oxide layers respectively. This circuit can be simulated using SPICE and solved for V(t), which is equivalent to solving for temperature                                                                                                                                                                                                                                      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

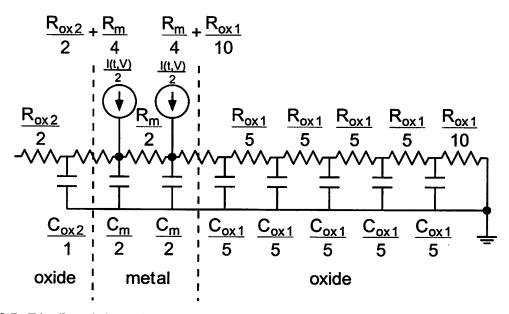

| Figure 2.7 | Distributed thermal circuit for the metal line of Figure 2.5 under AC (or transient) stress conditions. $R_{ox2}(C_{ox2})$ and $R_{ox1}(C_{ox1})$ are the effective thermal resistance (capacitance) of the overlying and underlying oxide layers respectively. This circuit can be simulated using SPICE and solved for V(t), which is equivalent to solving for temperature.                                                                                                                                                                                              |

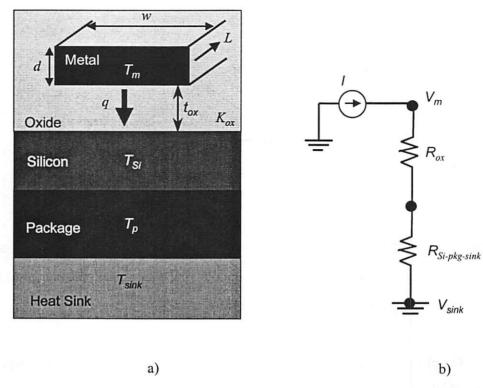

| Figure 2.8 | a) Schematic view of a packaged interconnect metal line of length $L$ , width $w$ , and thickness $d$ embedded in oxide. The underlying oxide thickness is $t_{ox}$ . Heat flow $(q)$ is assumed to be 1-D and towards the underlying heat sink. The metal line heated by a current is at an average temperature $T_m$ , while the heat sink is assumed to be at some temperature $T_{sink}$ . b) Equivalent DC lumped thermal circuit. $R_{ox}$ is the thermal resistance of the oxide layer, and $R_{Si-pkg-sink}$ is the thermal resistance from the silicon to the sink |

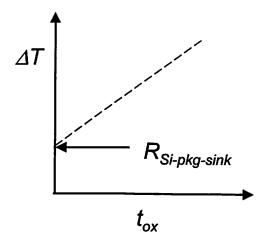

| Figure 2.9 | Temperature rise of the packaged interconnect line with respect to the heat sink plotted as a function of the underlying oxide thickness can provide the value of $R_{Si-pkg}$ .  28                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 3.1 | Equivalent circuit for the Human Body Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

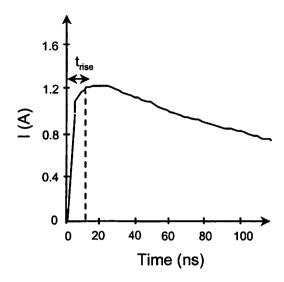

| Figure 3.2 | Current waveform for Human Body Model. The rise time of the waveform is $< 10$ ns and the decay time is $\sim 150$ ns31                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

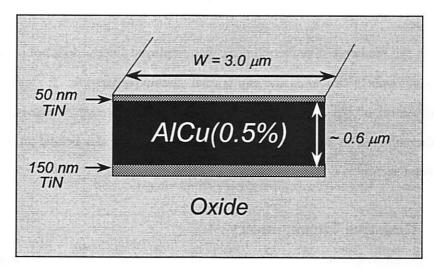

| Figure 3.3 | Schematic cross-sectional view of the multilayered TiN/AlCu(0.5%)/TiN metallization used in this study.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

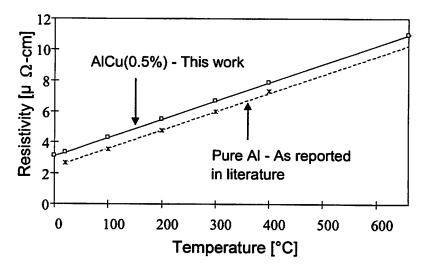

|            | Temperature dependence of resistivity remains linear up to the melt temperatures for pure Al and for AlCu(0.5%)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

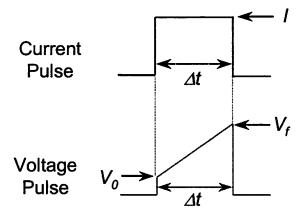

| Figure 3.5 | The current and the instantaneous voltage pulse across the metal line37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

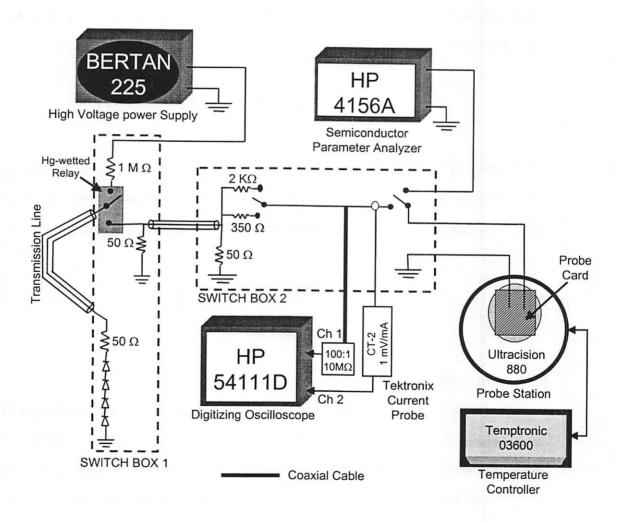

| Figure 3.6 | Block diagram illustrating the transient resistive thermometry system38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

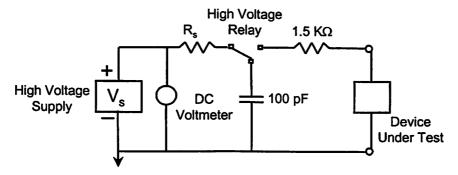

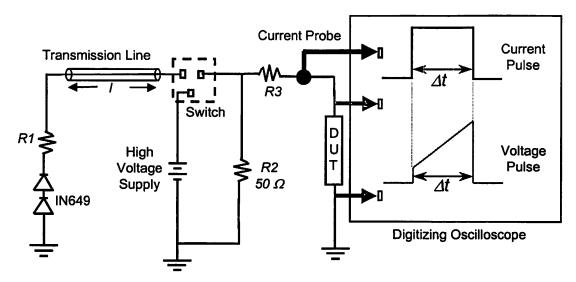

|            | A simplified schematic circuit diagram illustrating the transient resistive thermometry (TRT) technique employing a transmission line to generate short-duration constant current pulses                                                                                                                                                                                                                                                                                                                                                                                    |

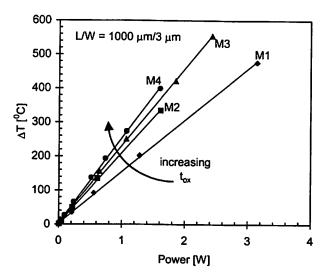

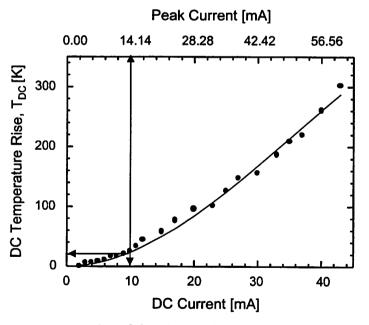

| •          | Self-heating of the quadruple level metal system under DC (steady-state) conditions. The effective thermal impedance of the interconnect to the Si substrate can be extracted from equation 2.37 ( $\Delta T = P \cdot R_{\theta}$ )                                                                                                                                                                                                                                                                                                                                        |

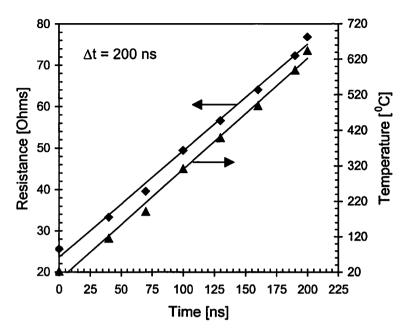

|            | The time dependence of resistance and temperature of a 3 µm X 1000 µm AlCu line during a 200 ns constant current pulse stress obtained using the TPT technique.                                                                                                                                                                                                                                                                                                                                                                                                             |

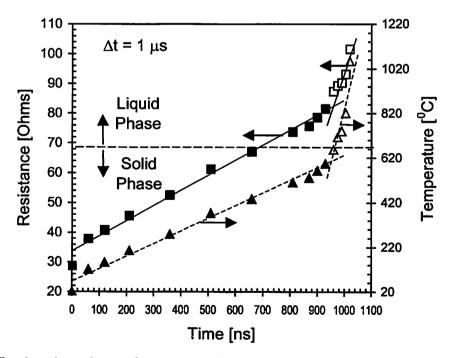

| Figure 3.10 | The time dependence of resistance and temperature of a 3 $\mu$ m X 1000 $\mu$ m AlCu line during a 1 $\mu$ s constant current pulse stress obtained using the TRT technique. The sharp rise in resistance beyond $\sim$ 950 ns indicates a phase change45                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

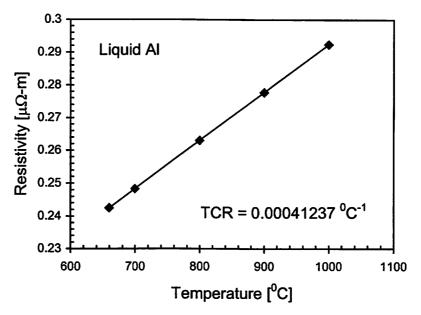

| Figure 3.11 | Temperature dependence of resistivity of liquid aluminum showing a linear behavior46                                                                                                                                                                                                  |

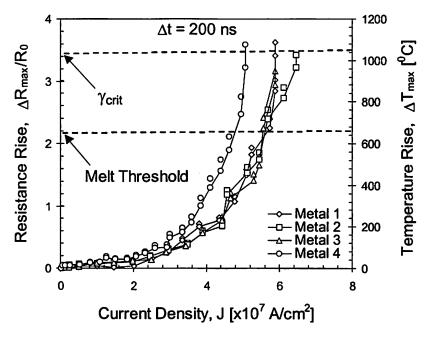

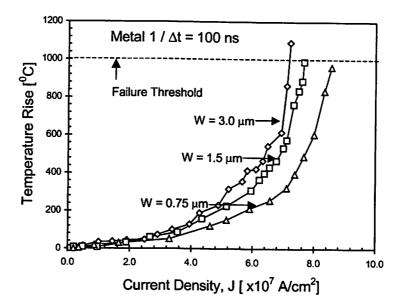

| Figure 3.12 | Maximum instantaneous resistance and temperature rise of the metal lines stressed by a 200 ns pulse, plotted against the current density J. The last data point on each curve indicates the final open circuit failure                                                                |

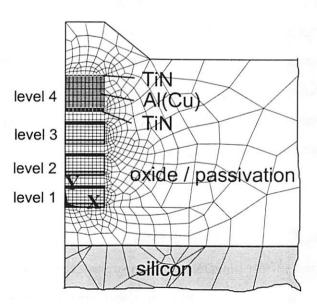

| Figure 3.13 | 2-D finite element model showing the generated mesh for the quadruple level test structure used in this study. W = 3 $\mu$ m for all levels, example shown for metal 448                                                                                                              |

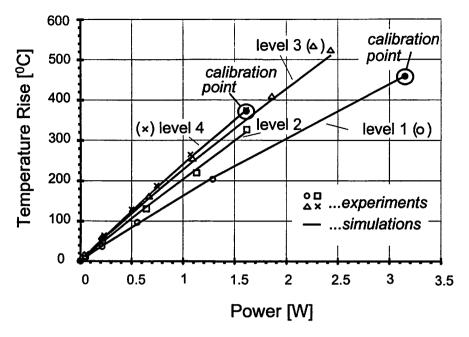

| Figure 3.14 | Calibration of the finite element model using DC self-heating data for the test structures. Excellent agreement between all experimental data and simulation results proves the accuracy of the model                                                                                 |

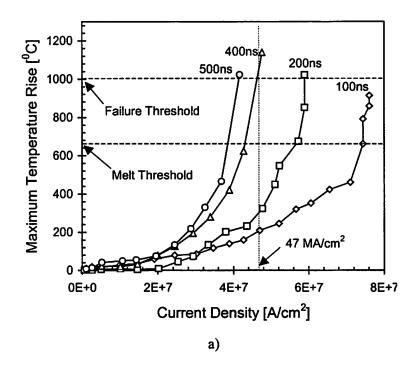

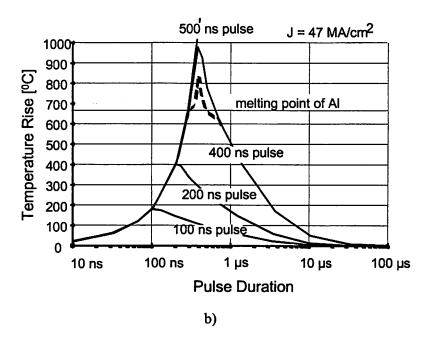

| Figure 3.15 | a) Experimental data summarizing the effect of pulse width on heating characteristics. The vertical dotted line shows the current density value (47MA/cm²) at which the transient heating during short pulses were simulated. b) Simulated temperature rise under transient currents. |

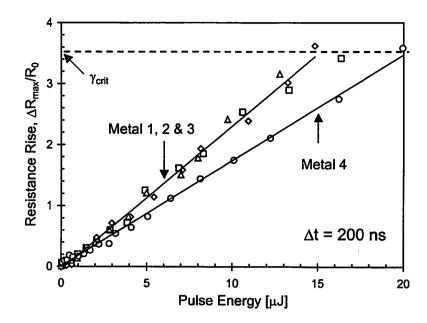

|             | Resistance rise ( $\gamma$ ) vs pulse energy for various metal lines stressed by a 200 ns pulse.                                                                                                                                                                                      |

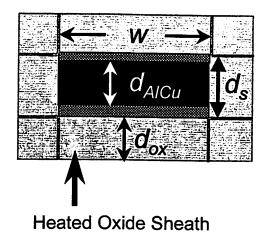

| Figure 3.17 | Schematic cross section of Metal line and the rectangular heated oxide sheath54                                                                                                                                                                                                       |

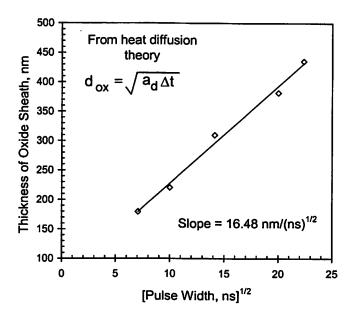

| Figure 3.18 | Pulse width dependence of the oxide sheath thickness54                                                                                                                                                                                                                                |

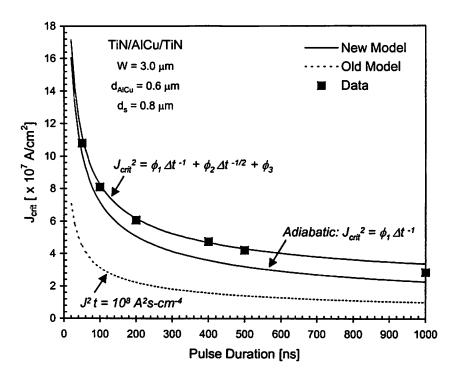

| Figure 3.19 | Pulse width dependence of $J_{crit}$                                                                                                                                                                                                                                                  |

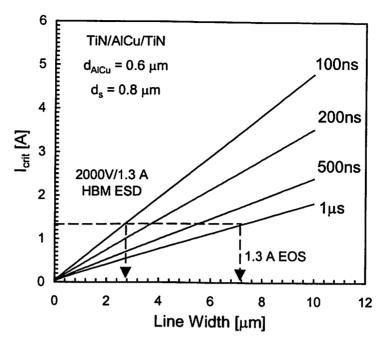

| Figure 3.20 | High-current short-pulse and EOS/ESD design guidelines for AlCu60                                                                                                                                                                                                                     |

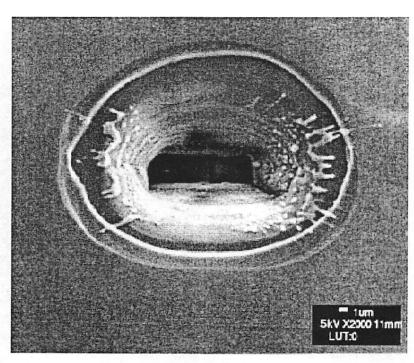

| Figure 3.21 | SEM micrograph showing open circuit failure mode of passivated TiN/AlCu/TiN metallization. The molten AlCu can be seen to have broken through the oxide/nitride passivation layer                                                                                                     |

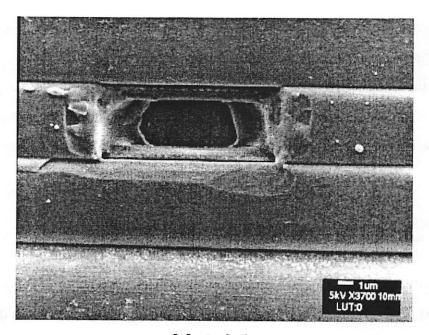

| Figure 3.22 | TEM micrograph of an AlCu line that has failed due to passivation fracture showing voids along the line                                                                                                                                                                               |

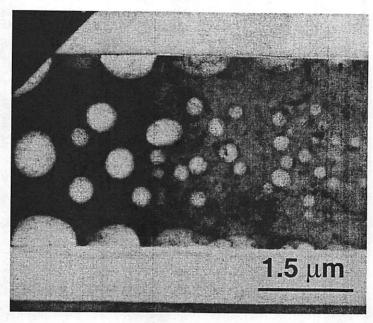

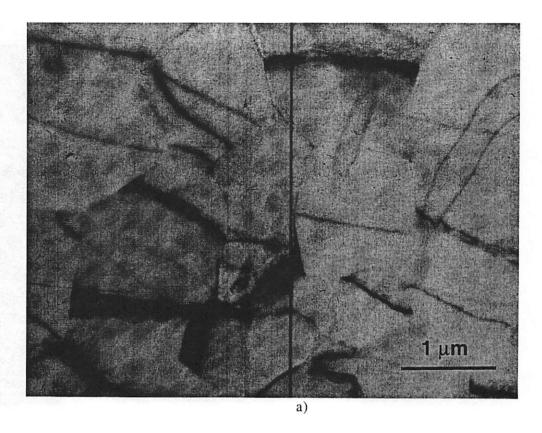

| Figure 3.23 | a) TEM micrograph showing the microstructure of unstressed AlCu line. b) The corresponding TEM diffraction pattern showing scattered spots arising due to small number of large grains                                                                                                |

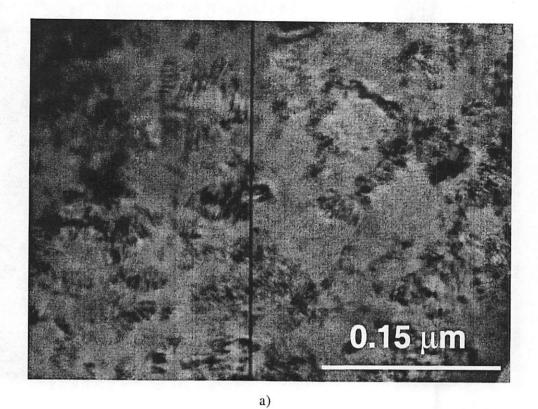

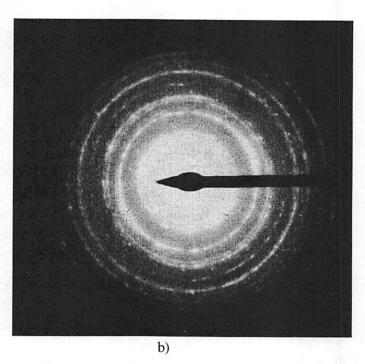

| Figure 3.24 | a) TEM micrograph showing the microstructure of a stressed AlCu line. b) The corresponding TEM diffraction pattern showing rings arising due to large number of small grains.                                                                                                         |

| Figure 4.1  | Schematic cross-sectional diagram of a multilevel interconnect system showing line to-line $(C_{LL})$ , the vertical layer-to-layer $(C_{\nu})$ , and line-to-ground $(C_{LG})$ capacitances                                                            |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

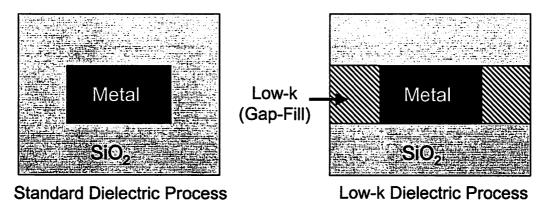

|             | Schematic cross section of the two intra-layer dielectric processes used in this study                                                                                                                                                                  |

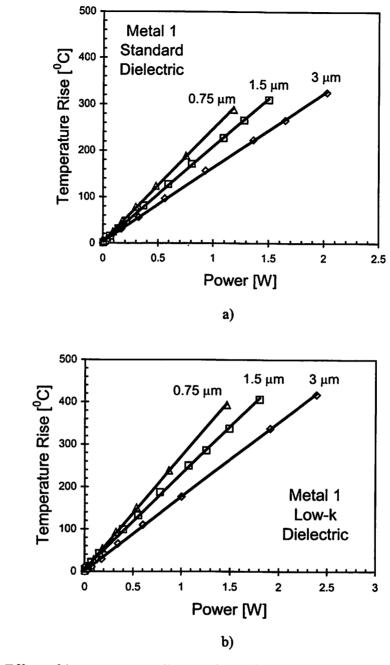

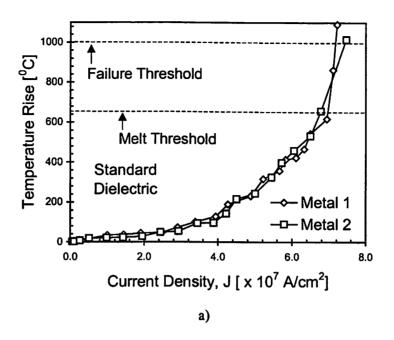

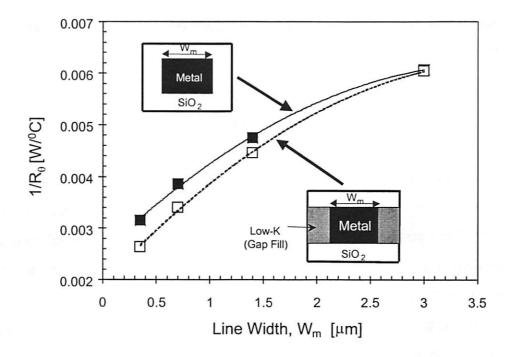

| Figure 4.3  | Effect of interconnect scaling on the self-heating of metal 1 lines under DC stress conditions for the a) standard dielectric process, and b) the low-k dielectric process                                                                              |

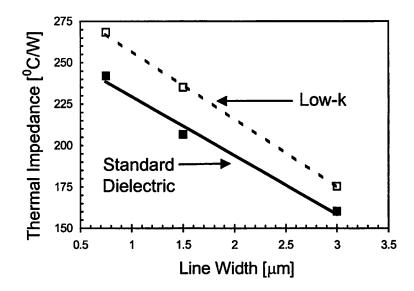

| Figure 4.4  | Effect of scaling and low-k dielectric on the thermal impedance of interconnects73                                                                                                                                                                      |

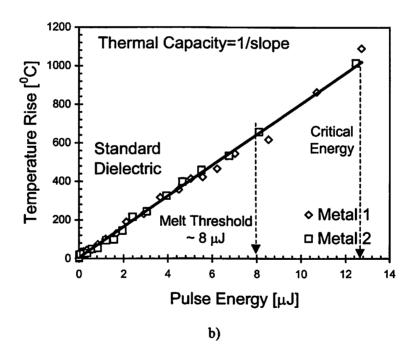

| Figure 4.5  | Self-heating behavior of 3.0 µm metal 1 and metal 2 lines for the standard dielectric process under a 100 ns pulse stress showing identical a) temperature rise, and by thermal capacity                                                                |

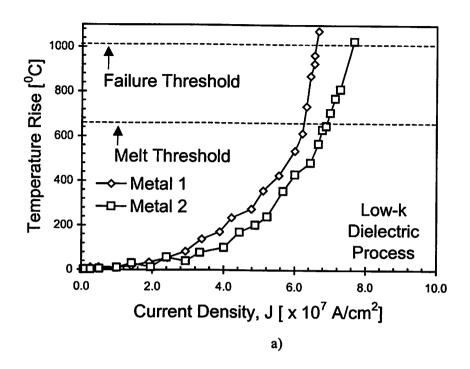

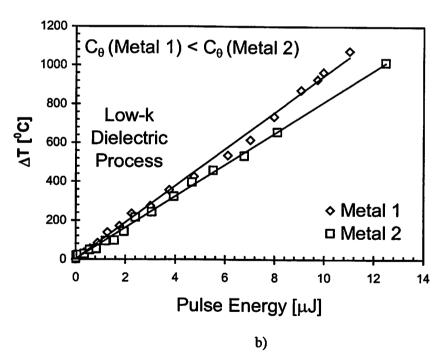

| Figure 4.6  | Self-heating behavior of 3.0 µm metal 1 and metal 2 lines for the low-k dielectric process under a 100 ns pulse stress showing different a) temperature rise, and by thermal capacity                                                                   |

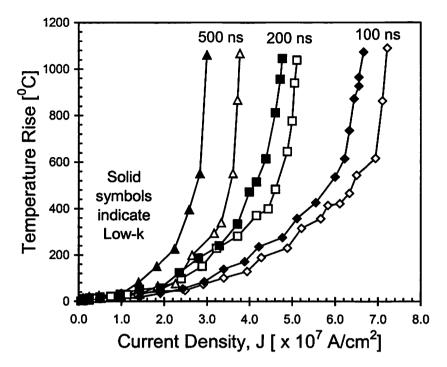

| Figure 4.7  | Effect of low-k dielectric on the self-heating behavior of 3 μm wide lines under different pulse durations.                                                                                                                                             |

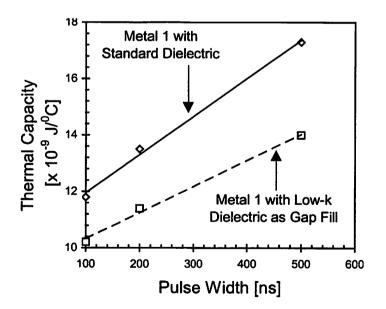

| Figure 4.8  | Increase in thermal capacity with pulse width is lower for a 3.0 µm metal line with low-k intra-layer dielectric process                                                                                                                                |

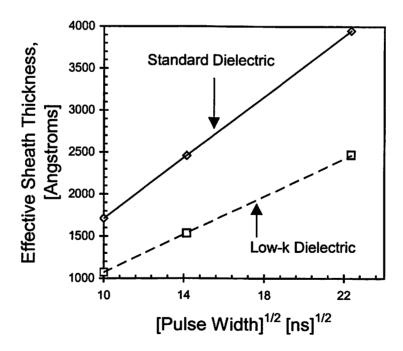

| Figure 4.9  | Effective thickness of the heated dielectric sheath around the 3.0 µm metal lines are lower for the low-k process.                                                                                                                                      |

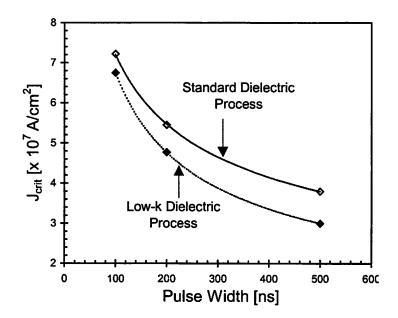

| Figure 4.10 | The critical current density in a 3.0 µm wide metal lead with the low-k process is smaller than that with a standard dielectric process                                                                                                                 |

| Figure 4.11 | Effect of interconnect scaling on their self-heating characteristics under short pulse stress conditions                                                                                                                                                |

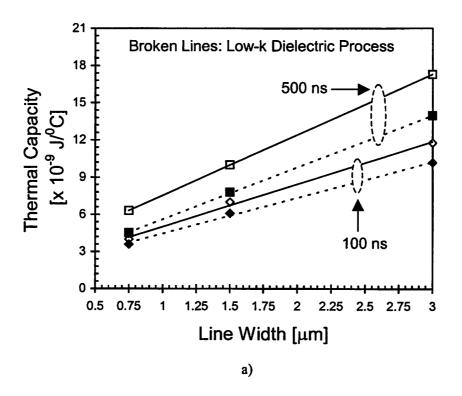

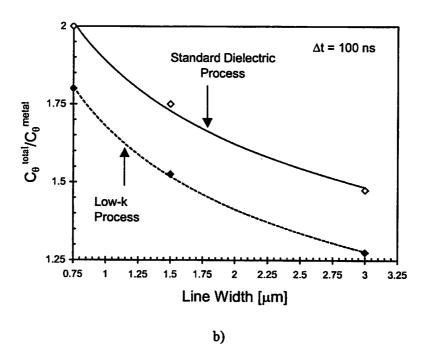

| Figure 4.12 | 2 Effect of interconnect scaling using low-k dielectric material on a) the thermal capacity of the metal lines under two different pulse widths, and b) the ratio of the total thermal capacity to the metal thermal capacity shown for 100 ns pulses81 |

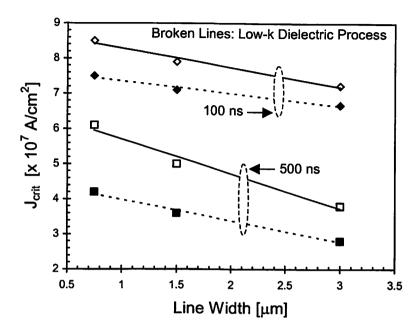

| Figure 4.13 | Effect of interconnect scaling using low-k dielectric material showing their increasing impact on $J_{crit}$ with pulse duration                                                                                                                        |

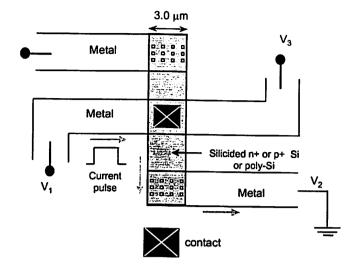

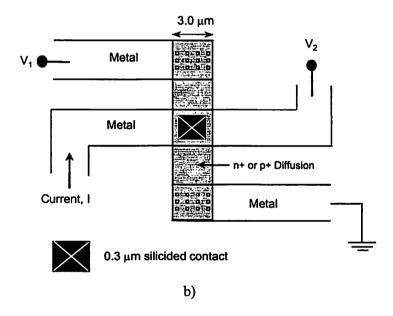

| Figure 5.1  | The layout of a Kelvin contact structure under study86                                                                                                                                                                                                  |

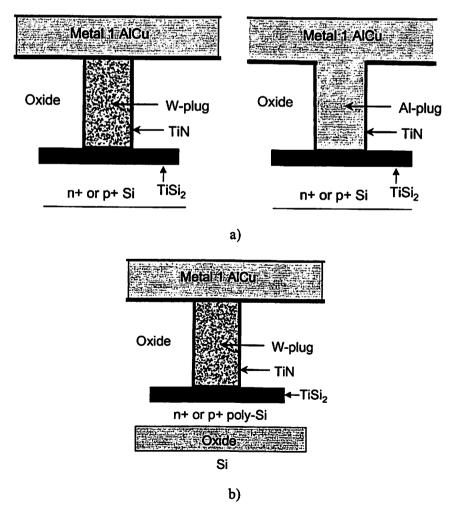

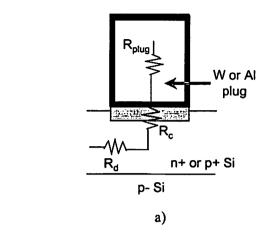

| Figure 5.2  | The schematic cross sectional view of the contact structures on a) Si and b) poly-Si                                                                                                                                                                    |

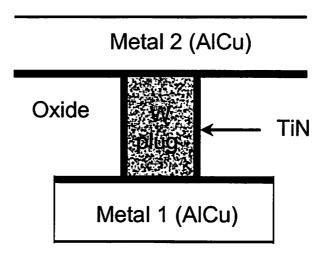

| Figure 5.3 The schematic cross sectional view of a via structure used in this study8                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

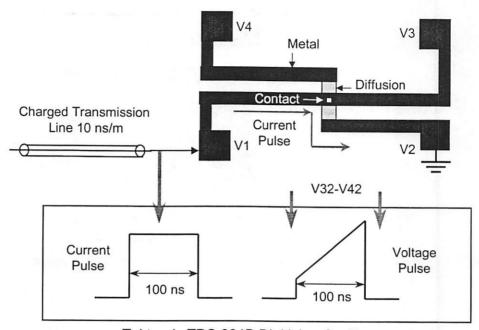

| Figure 5.4 The schematic view of the simplified TKT system.                                                                                                                                                     |

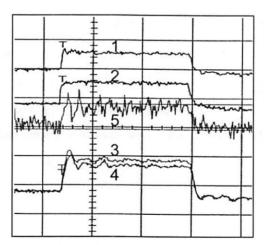

| Figure 5.5 Voltage pulse across contacts/vias captured using a difference math function in digitizing oscilloscope. The difference between pulse 3 and 4 is electronically calculated and displayed as pulse 5. |

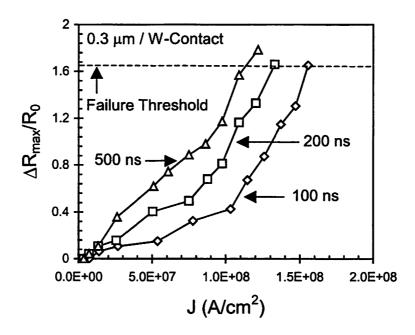

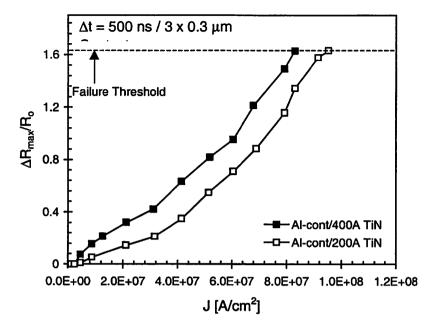

| Figure 5.6 Resistance rise factor as a function of current density for single 0.3µm W-contacts                                                                                                                  |

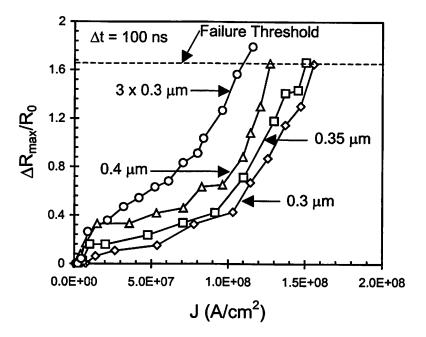

| Figure 5.7 Effect of contact size and number on the resistance rise factor for 100 ns pulses (resulshown for W)9                                                                                                |

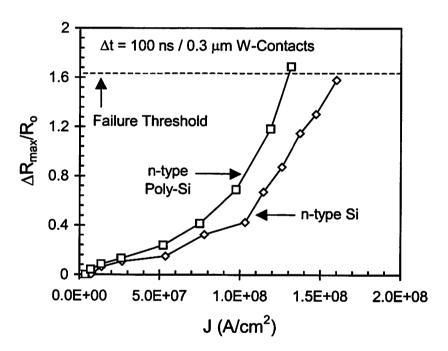

| Figure 5.8 Heating and failure of W-contacts on n type Si and Poly-Si.                                                                                                                                          |

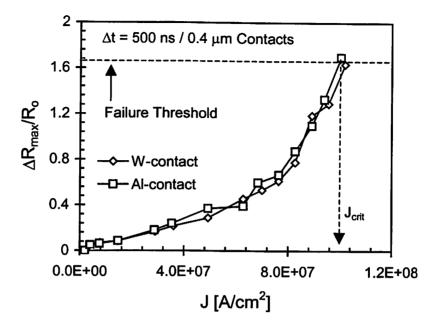

| Figure 5.9 Heating and failure of single 0.4 μm, W and Al contacts under 500 ns pulsed stres                                                                                                                    |

| Figure 5.10 Effect of TiN liner thickness on the robustness of 3X0.3µm Al contacts under 500 r pulsed stress9                                                                                                   |

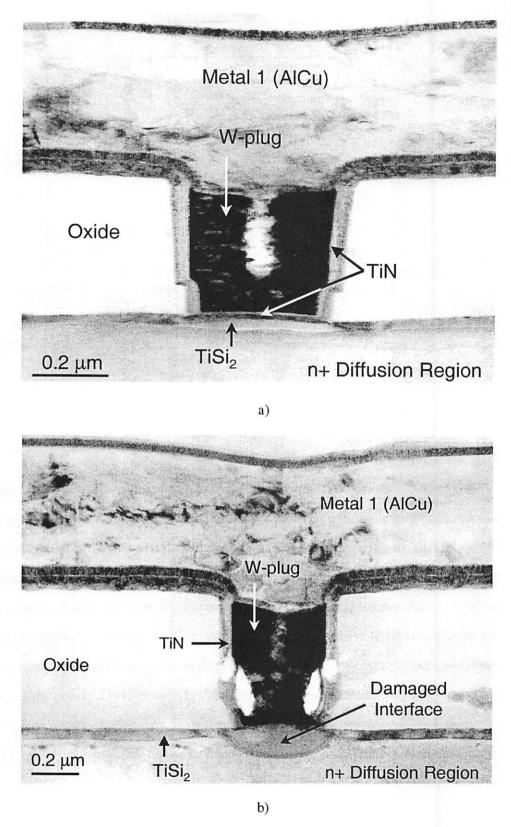

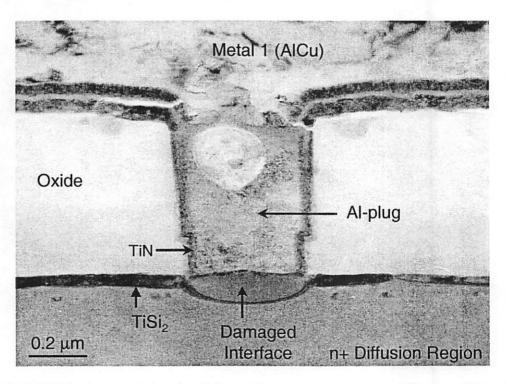

| Figure 5.11 TEM micrographs showing 0.3 μm W-contact structures to n+ Si with (a) unstresse TiN/TiSi <sub>2</sub> interface and (b) stressed TiN/TiSi <sub>2</sub> interface                                    |

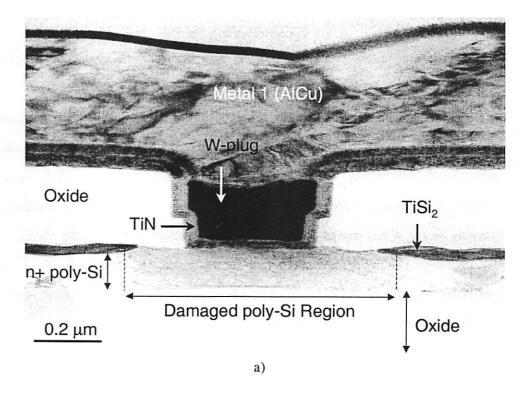

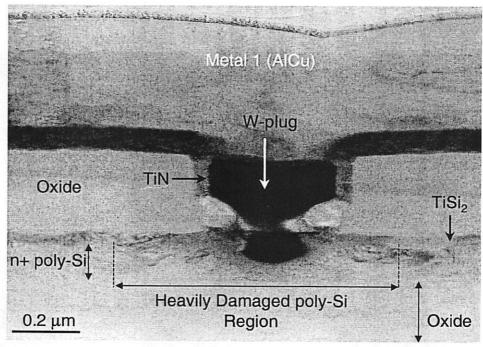

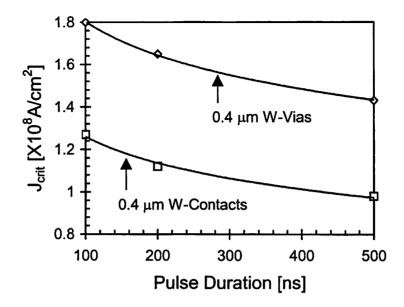

| Figure 5.12 TEM micrographs showing 0.2 μm W-contact structures to n+ poly-Si with stresse TiN/TiSi <sub>2</sub> interfaces with (a) 100 ns and (b) 500 ns pulses9                                              |

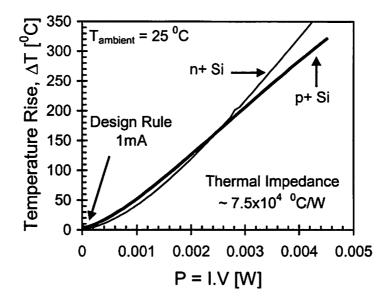

| Figure 5.13 TEM micrograph showing 0.4 μm Al-contact structure to n+ Si stressed by a 100 m pulse9                                                                                                              |

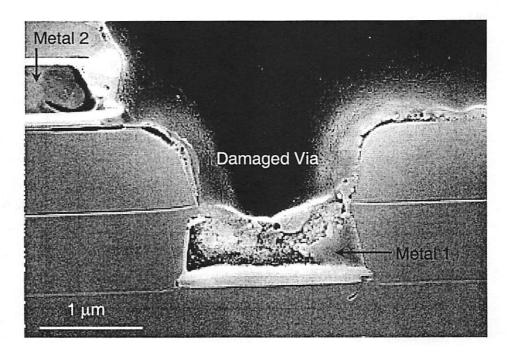

| Figure 5.14 SEM micrograph showing a 0.4 µm single W-via damaged under high pulsed currer stress.                                                                                                               |

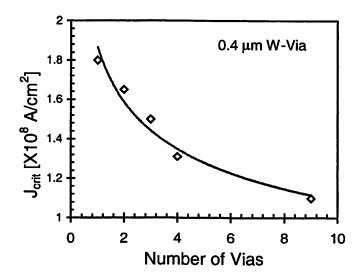

| Figure 5.15 Critical current density of 0.4 µm W via structures under 100 ns pulsed stress9                                                                                                                     |

| Figure 5.16 Critical current density to cause degradation/failure is higher for vias as compared t contacts.                                                                                                    |

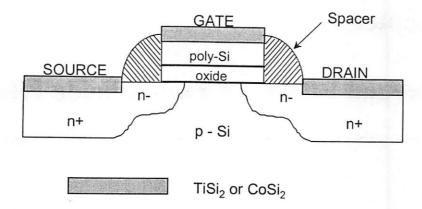

| Figure 6.1 Sample cross-section of a salicided LDD NMOSFET                                                                                                                                                      |

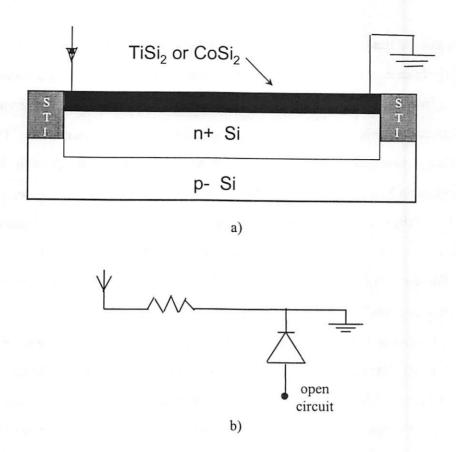

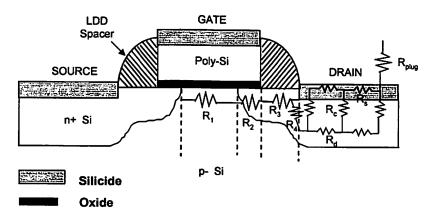

| Figure 6.2 a) Schematic cross section of silicide structures on n+ Si used in this study. b) In lumped equivalent circuit for the silicide structures                                                           |

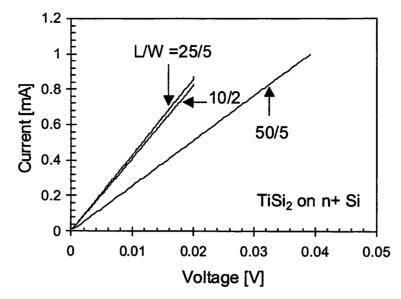

| Figure 6.3 Low current I-V characteristics for the TiSi <sub>2</sub> films on n+ Si showing ohmic behavior                                                                                                      |

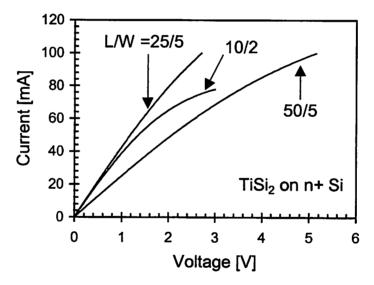

| Figure 6.4 High current I-V characteristics for the TiSi <sub>2</sub> films on n+ Si showing non-linea behavior                                                                                                 |

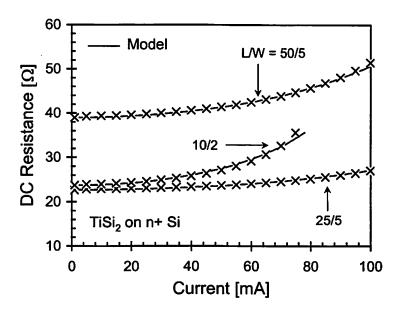

| Figure 6.5  | The model for resistance as a function of current through the silicide is shown to be in excellent agreement with data for various geometry                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

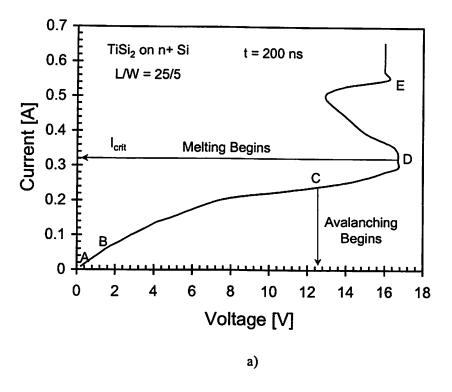

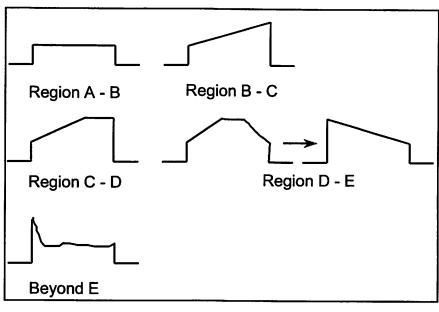

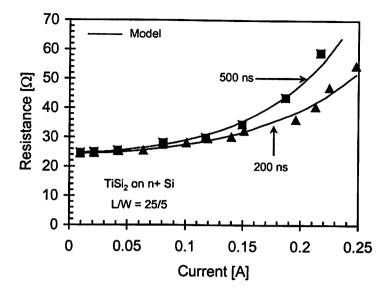

| Figure 6.6  | a) High current I-V characteristics for a TiSi <sub>2</sub> film under a 200 ns pulsed current stress. Voltage is measured at the end of the pulse. b) The voltage pulse shapes in the different regions of the I-V curve |

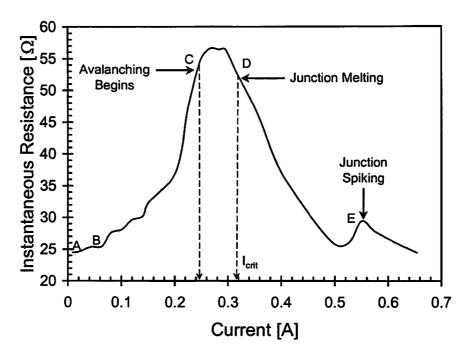

| Figure 6.7  | Instantaneous resistance of the silicide film as a function of the current amplitude for 200 ns pulses                                                                                                                    |

| Figure 6.8  | High current conduction model for TiSi <sub>2</sub> films under pulsed stress conditions110                                                                                                                               |

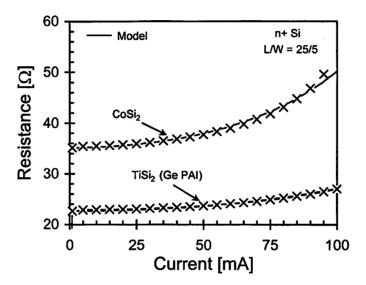

| Figure 6.9  | High current behavior of CoSi <sub>2</sub> and TiSi <sub>2</sub> films under DC stress conditions along with the model developed in section 6.3                                                                           |

| Figure 6.10 | Comparison of high current conduction between CoSi <sub>2</sub> and TiSi <sub>2</sub> films under a 200 ns pulsed stress condition                                                                                        |

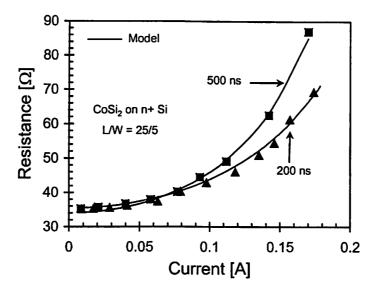

| Figure 6.11 | High current conduction model for CoSi <sub>2</sub> films under pulsed stress conditions112                                                                                                                               |

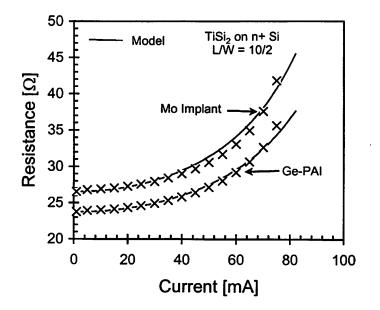

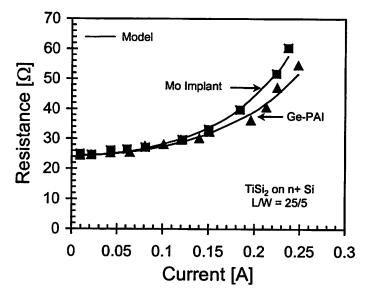

|             | P. High current conduction in TiSi <sub>2</sub> film under DC stress condition showing the effect of Mo implant                                                                                                           |

| Figure 6.13 | Effect of Mo implant on the high current conduction under a 200 ns pulse showing a stronger dependence of film resistance on the current                                                                                  |

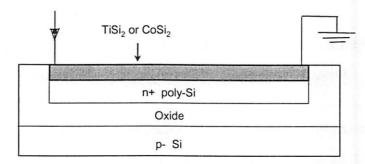

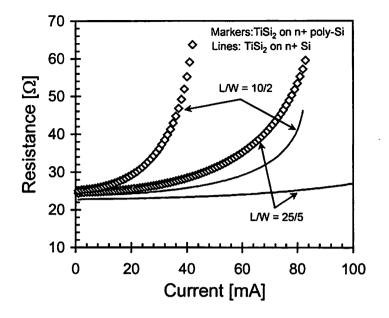

| Figure 6.14 | Silicide structures on n+ poly-Si used in this study                                                                                                                                                                      |

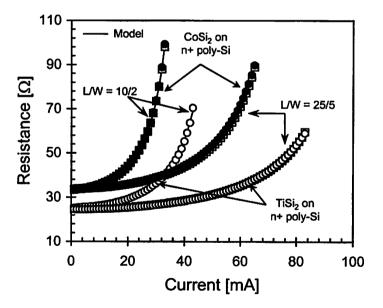

|             | High current conduction in TiSi <sub>2</sub> films on n+ poly-Si under DC stress displaying larger current sensitivity of resistance                                                                                      |

|             | Resistance sensitivity to current under DC stress is larger for CoSi <sub>2</sub> films, compared to that of TiSi <sub>2</sub> , formed on n+ poly-Si                                                                     |

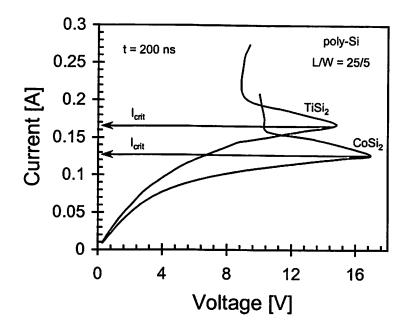

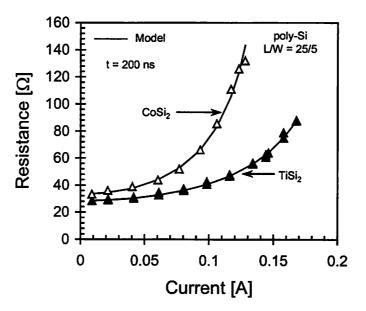

|             | The high current I-V curves for TiSi <sub>2</sub> and CoSi <sub>2</sub> films formed on n+ poly-Si under a 200 ns pulsed stress condition                                                                                 |

|             | High current conduction model under pulsed stress condition shown for TiSi <sub>2</sub> and CoSi <sub>2</sub> films on n+ poly-Si117                                                                                      |

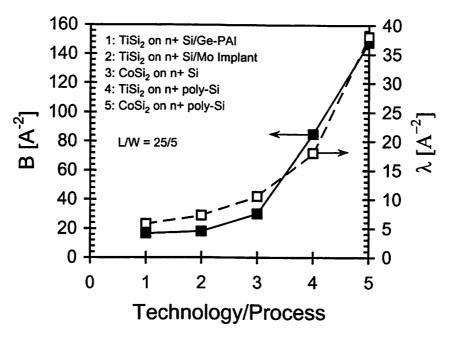

|             | Impact of salicide technology and process variations on the current sensitivity of resistance [109]                                                                                                                       |

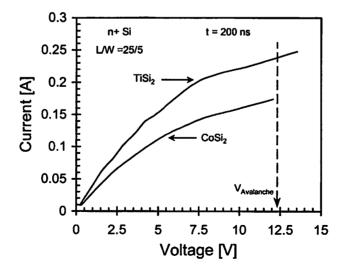

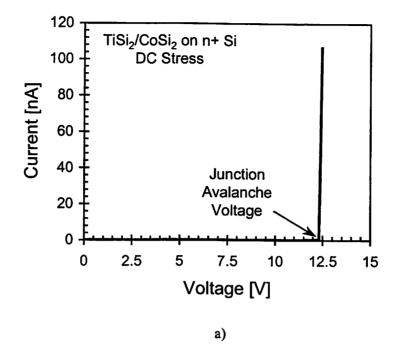

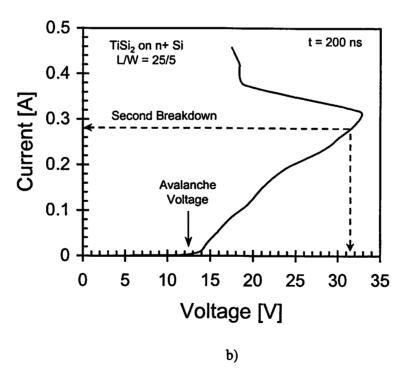

|             | a) The reverse-bias DC I-V characteristics of the p-n junction showing avalanche voltage of ~ 12.5 V. b) The I-V characteristics of the p-n junction under a 200 ns pulse stress                                          |

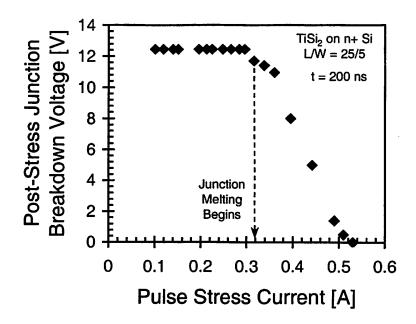

|             | l Junction avalanche voltage measured after each pulse of increasing amplitude                                                                                                                                            |

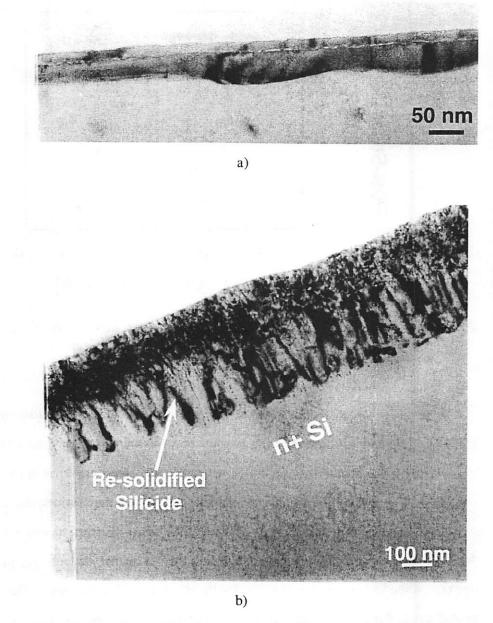

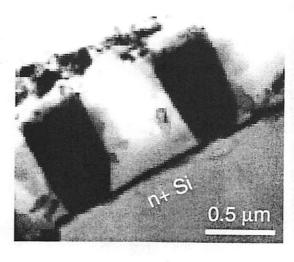

| Figure 6.22 TEM micrograph showing a) unstressed silicide film, and b) morpho in a silicide film upon re-solidification after being stressed past the crit 200 ns pulse.                                                                                     | tical point by a |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

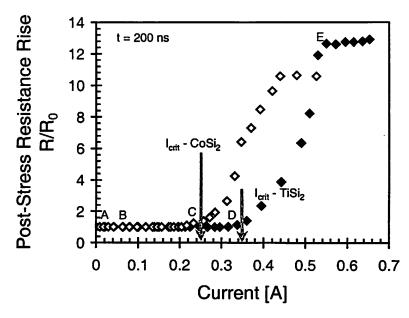

| Figure 6.23 The post-pulse resistance rise for TiSi <sub>2</sub> (solid markers) and CoSi <sub>2</sub> (e films formed on n+ Si under a 200 ns pulsed stress condition. The letter various regions in the high current curve from Figure 6.6(a) for the TiSi | ers indicate the |

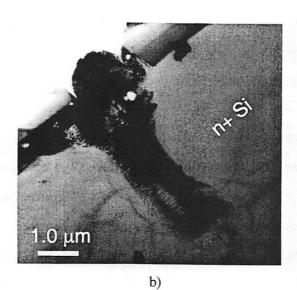

| Figure 6.24 TEM micrographs showing a) unstressed contacts and b) damaged contacts the substrate                                                                                                                                                             | -                |

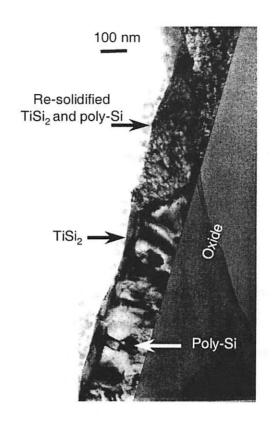

| Figure 6.25 TEM micrograph showing a TiSi <sub>2</sub> film on n+ poly-Si showing a sundergone morphological changes upon re-solidification.                                                                                                                 |                  |

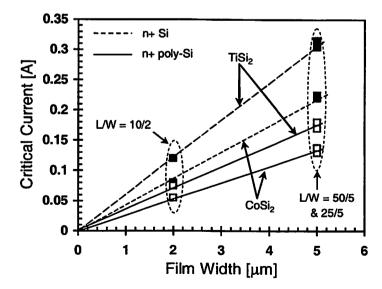

| Figure 6.26 Proportionality of $I_{crit}$ to the film width, W, shown for TiSi <sub>2</sub> and CoSi <sub>2</sub> and n+ poly-Si. The pulse duration was 200 ns.                                                                                             |                  |

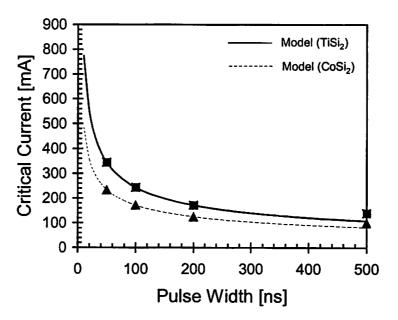

| Figure 6.27 Pulse width dependence of $I_{crit}$ for $L/W = 25/5$ , TiSi <sub>2</sub> and CoSi <sub>2</sub> films  The model is based on equation (6.8)                                                                                                      |                  |

| Figure 7.1 Schematic cross-section of a salicided LDD NMOSFET illustration resistances in the path of the drain current.                                                                                                                                     | _                |

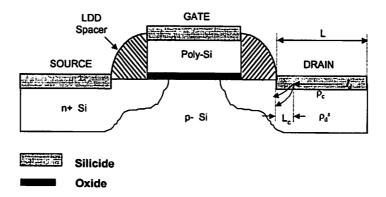

| Figure 7.2 Schematic cross-section of a salicided LDD NMOSFET illustration transfer length over which the current enters the diffusion from the silicity                                                                                                     | _                |

| Figure 7.3 a) Schematic cross-section of the contact structure used in this study, view of the Kelvin structure used for contact resistance measurements                                                                                                     | •                |

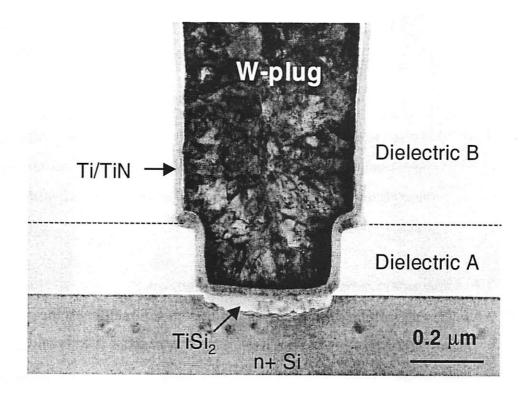

| Figure 7.4 TEM micrograph of a 0.3 $\mu$ m silicided ( $\sim$ 35nm) W-plug contact                                                                                                                                                                           | 135              |

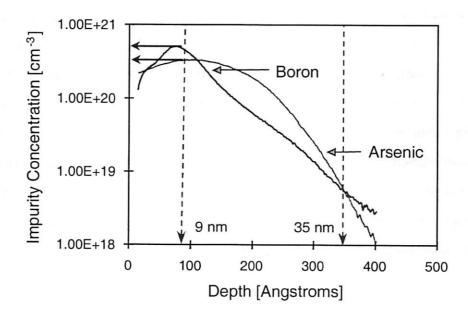

| Figure 7.5 The impurity doping concentration variation with depth obtained using                                                                                                                                                                             | SIMS135          |

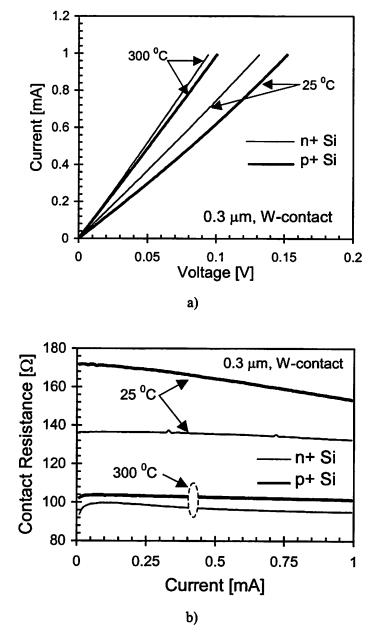

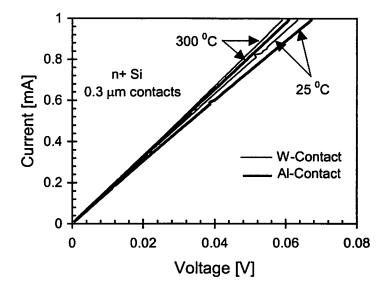

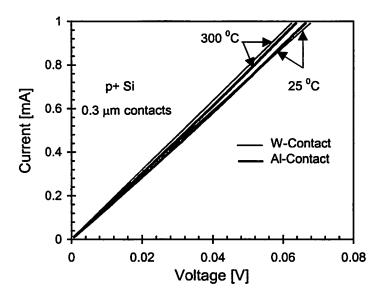

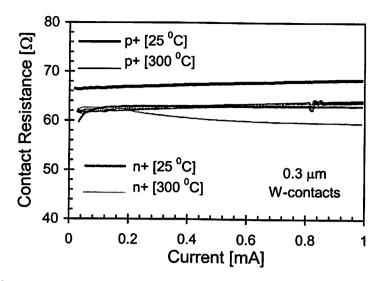

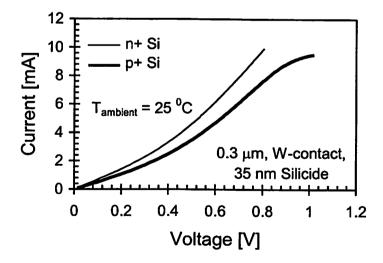

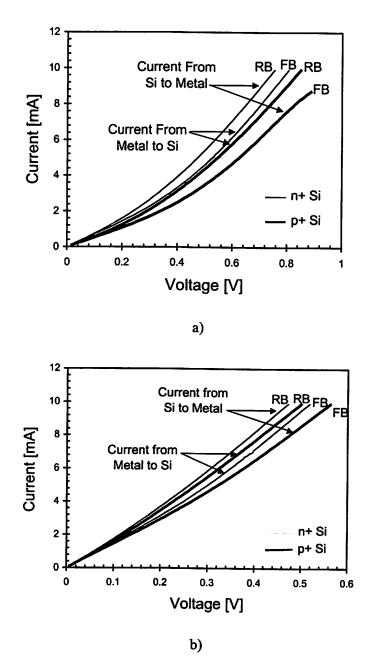

| Figure 7.6 a) I-V characteristics of W-contact structures with 35 nm silicide a temperatures. b) Contact resistance sensitivity with current (low current two different temperatures for W-contacts to n+ and p+ Si                                          | rent regime) at  |

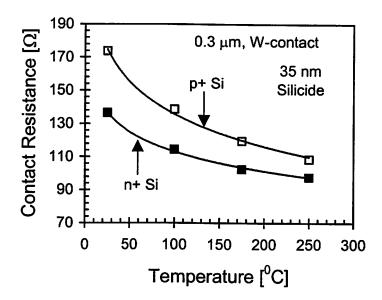

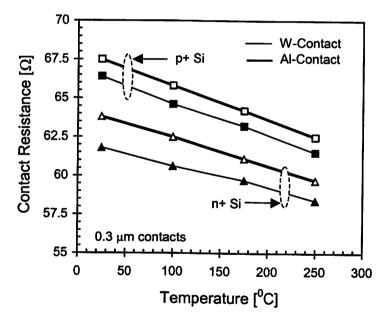

| Figure 7.7 Contact resistance variation with temperature for contacts to n+ and p contact shows larger temperature sensitivity                                                                                                                               | •                |

| Figure 7.8 I-V characteristics of W and Al plug contacts to n+ Si with 9-nm silicide equal contact resistance and are only slightly temperature sensitive                                                                                                    |                  |

| Figure 7.9 I-V characteristics of W and Al plug contacts to p+ Si with 9 nm silicidentical contact resistance values as compared to those of n+ Si and slightly temperature sensitive.                                                                       | -                |

| Figure 7.10 Contact resistance sensitivity with current (low current regime) at two different temperatures for W-contacts to n+ and p+ Si with 9 nm silicide                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7.11 Temperature sensitivity of the contact resistance of W and Al plug contacts with 9 nm silicide                                                                                                                                                                                                                                             |

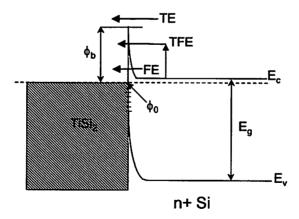

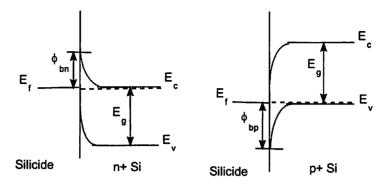

| Figure 7.12 Metal-Si energy band diagram illustrating various transport mechanisms. $\phi_b$ is the silicide-Si barrier height, and $\phi_0$ denotes the energy level at which the Fermi level is pinned.                                                                                                                                              |

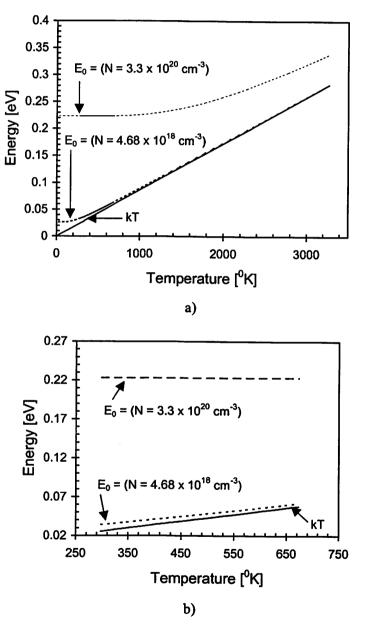

| Figure 7.13 Variation of $E_0$ with temperature shown for two different values of N for a) large temperature range and b) in the experimental temperature range. $E_{00}$ is assumed to be independent of temperature.                                                                                                                                 |

| Figure 7.14 Silicide-Si band diagram illustrating Fermi level pinning in contacts to n/p type Si.                                                                                                                                                                                                                                                      |

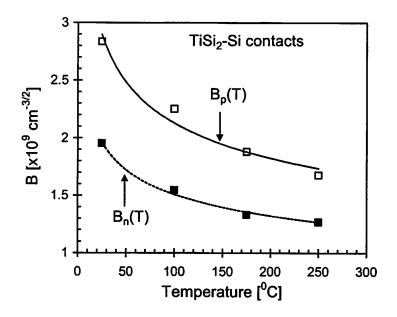

| Figure 7.15 Temperature dependence of B for n and p type Si                                                                                                                                                                                                                                                                                            |

| Figure 7.16 Forward bias I-V characteristics of n+ and p+ contacts in the high current regime becomes non linear due to severe self heating                                                                                                                                                                                                            |

| Figure 7.17 Thermal impedance of n+ and p+ contacts extracted from Figure 7.16 and Figure 7.7 at an ambient temperature of 25 °C are equal                                                                                                                                                                                                             |

| Figure 7.18 Biasing polarity dependence of Silicide-Si contacts under high current stress conditions for a) 35 nm silicide and b) 9 nm silicide                                                                                                                                                                                                        |

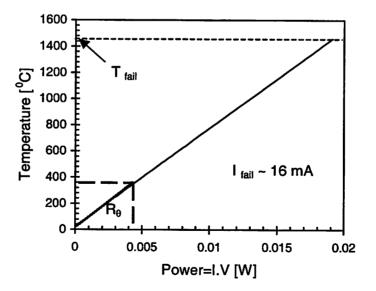

| Figure 7.19 Temperature rise at the point of failure under high current stress conditions is calculated from the thermal impedance in Figure 7.17151                                                                                                                                                                                                   |

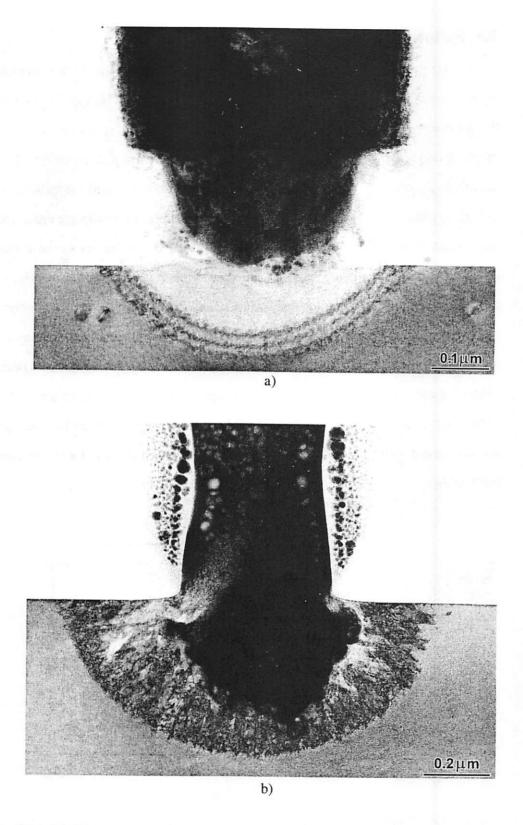

| Figure 7.20 TEM micrographs of 0.3 µm W-contacts showing progression of failure at the silicide-Si interface showing a) initiation of the failure and b) severe degradation152                                                                                                                                                                         |

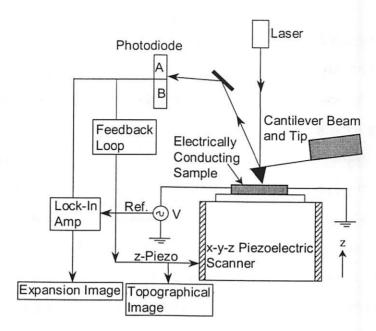

| Figure 8.1 Schematic diagram of the experimental setup used for the scanning Joule expansion microscopy (SJEM)                                                                                                                                                                                                                                         |

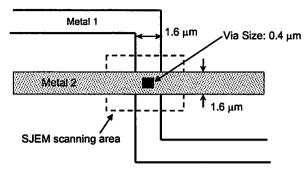

| Figure 8.2 Top view of the via structure showing the scanning area (15 μm X 15 μm) of the AFM tip in the SJEM experiments                                                                                                                                                                                                                              |

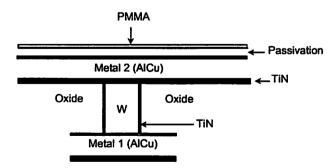

| Figure 8.3 Via cross section showing the thin layer of PMMA film coated over the passivation layers to enhance the expansion signal                                                                                                                                                                                                                    |

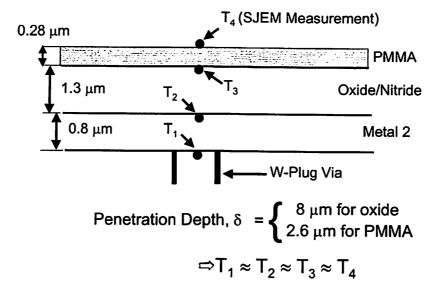

| Figure 8.4 A schematic diagram illustrating the equivalence of actual via temperature and measured temperature on PMMA film by SJEM. The penetration depths in the oxide and the PMMA film shown above were calculated at $f = 5$ KHz. For the metal film on top of the W-plug via, the thermal diffusivity ( $\kappa$ ) is even higher resulting in a |

|            | surface of PMMA film $(T_4)$ is expected to equal that on top of the via $(T_1)$                                                                                                                                                                                                                                                                                                                                                                  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

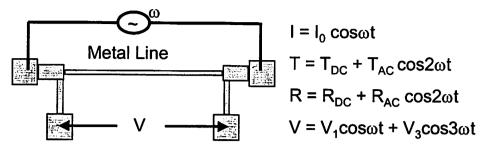

| Figure 8.5 | Schematic of the interconnect line heated by a sinusoidal current and the corresponding voltage across it                                                                                                                                                                                                                                                                                                                                         |

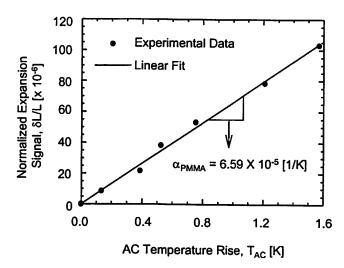

| Figure 8.6 | The thermal expansion coefficient of PMMA determined by measuring the expansion signal and calculating the corresponding AC temperature rise of an Al-Cu line from the measured amplitude of the $3\omega$ component of the voltage signal using the lock-in amplifier.                                                                                                                                                                           |

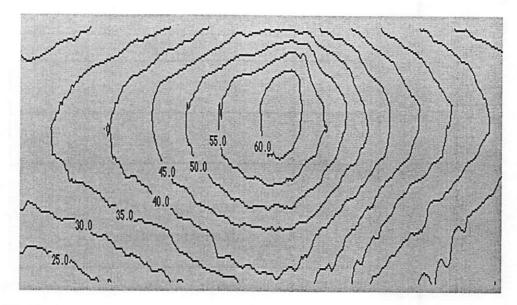

| Figure 8.7 | a) Temperature profile around the 0.4 $\mu$ m via sample measured by SJEM and b) magnified spatial temperature distribution along a micron length on top of the via. The corresponding peak current densities are: $j_{peak}(line) = 0.63 \text{ MA/cm}^2$ , and $j_{peak}(via) = 24 \text{ MA/cm}^2$ . The spatial resolution of temperature rise is $\sim 0.06 \mu$ m. The temperature gradient across the via is $\sim 6  ^{0}\text{K/}\mu$ m. |

| Figure 8.8 | The temperature contour map across the 0.4 $\mu m$ via sample measured by SJEM162                                                                                                                                                                                                                                                                                                                                                                 |

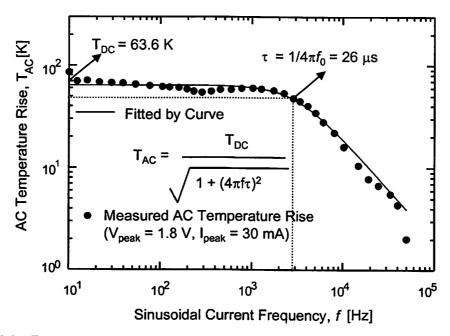

| Figure 8.9 | Experimental data showing extraction of a time constant $\tau = 26 \mu s$ for the via structure. Note that $\tau$ is a characteristic of the thermal system and is independent of the waveform                                                                                                                                                                                                                                                    |

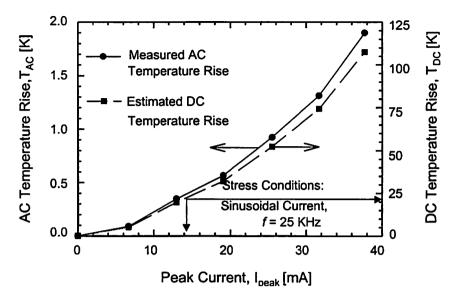

| Figure 8.1 | O The maximum AC temperature rise and the corresponding DC temperature rise under different sinusoidal current stress. The time to get one data point typically is around 15 minutes. The DC temperature rise was estimated from AC temperature rise using equation (8.15) and the analysis is described in the text                                                                                                                              |

| Figure 8.1 | 1 Average temperature rise of the via sample determined using resistive thermometry. The corresponding peak current values for the sinusoidal bias is also shown along the second x-axis based on $I_{peak} = \sqrt{2} I_{DC}$ .                                                                                                                                                                                                                  |

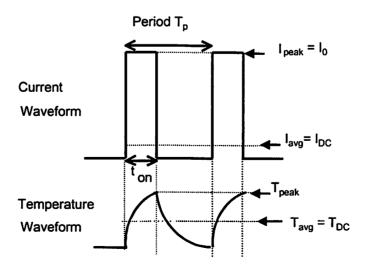

| Figure 8.1 | 2 The schematic waveforms of the pulsed bias and the corresponding temperature rise                                                                                                                                                                                                                                                                                                                                                               |

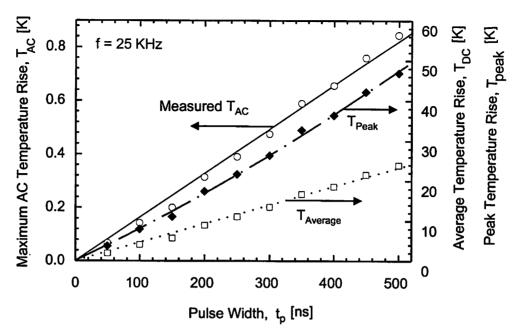

| Figure 8.1 | 3 The first harmonic, average and peak temperature rise as a function of the pulsed width of applied pulsed current. The stress condition corresponds to a current density of $2.65 \times 10^7$ A/cm <sup>2</sup> in the via and $3.47 \times 10^6$ A/cm <sup>2</sup> in the metal line                                                                                                                                                          |

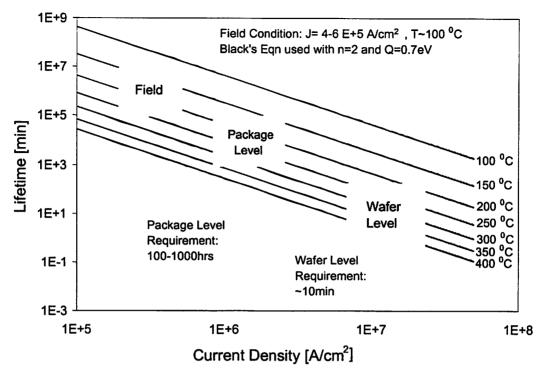

| Figure 9.1 | Typical lifetimes under field, package and wafer level stress conditions173                                                                                                                                                                                                                                                                                                                                                                       |

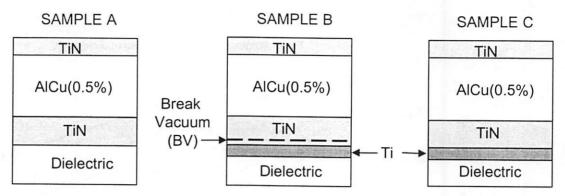

| Figure 9.2 | Schematic cross-sectional view of the three samples used in this study showing variation in barrier metal design. The dashed line in sample B indicates a break in vacuum.                                                                                                                                                                                                                                                                        |

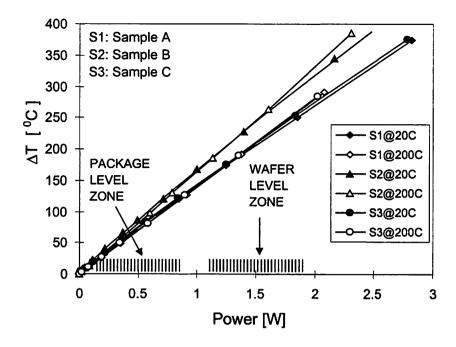

| Figure 9.3 | DC Joule heating results for the three samples at two different chuck temperatures.175                                                                                                                                                                                                                                                                                                                                                            |

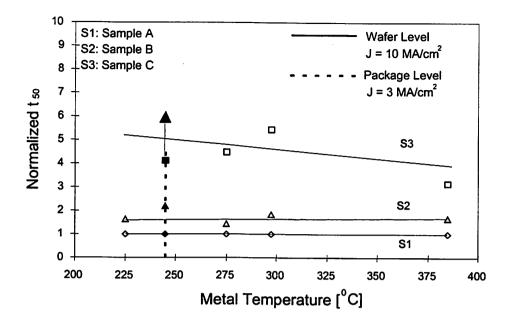

| Figure 9.4 Accelerated stress EM $t_{50}$ sensitivity with metal temperature. The solid symbols represent the normalized $t_{50}$ s at package level stress where $T_m = 245$ °C and $j = 3$ MA/cm <sup>2</sup> . The arrow is shown to indicate a greater than 4 normalized $t_{50}$ value176                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

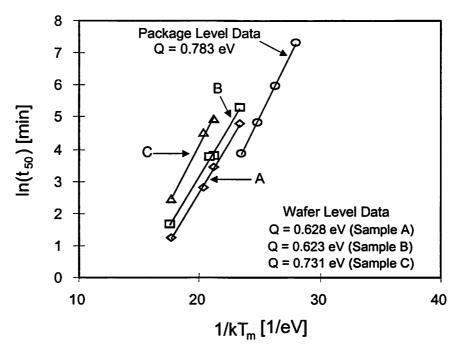

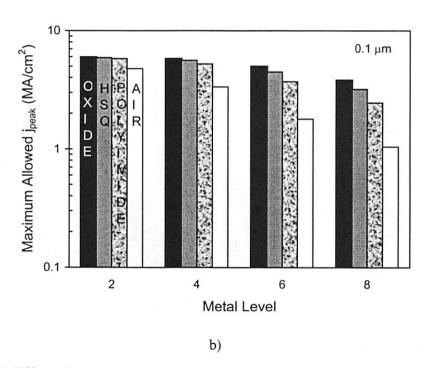

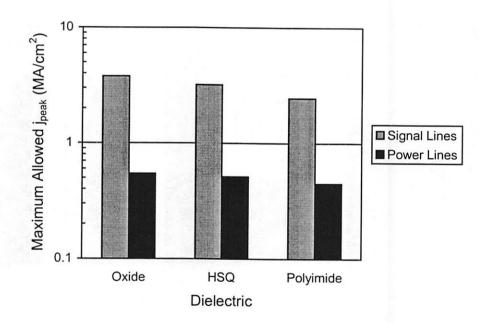

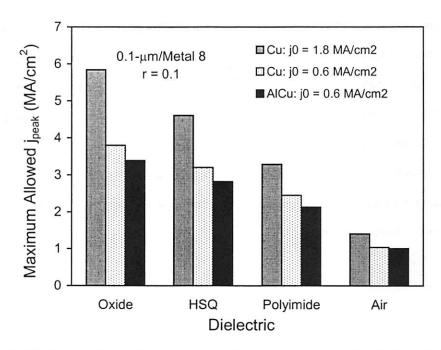

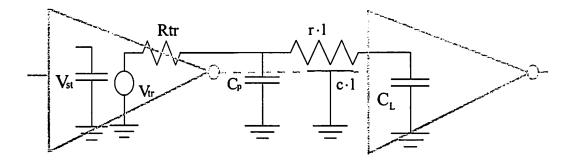

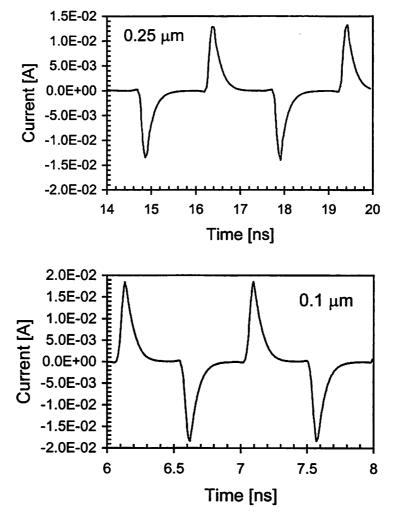

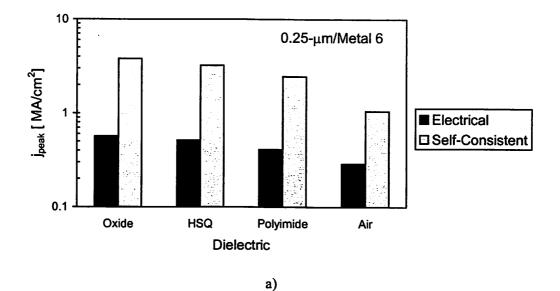

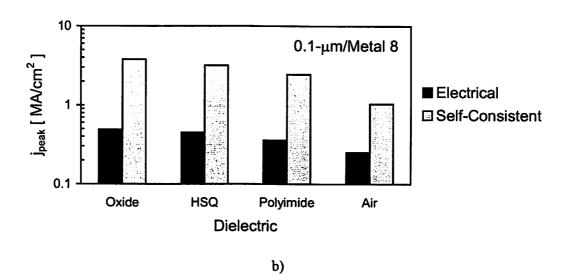

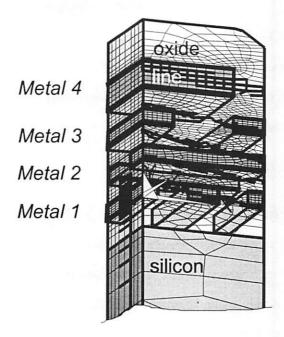

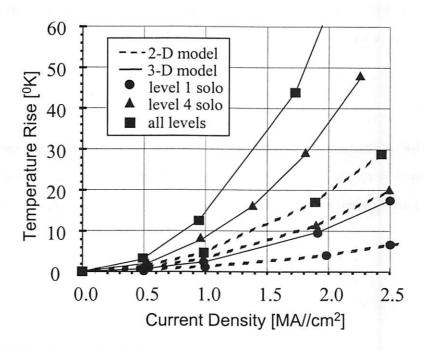

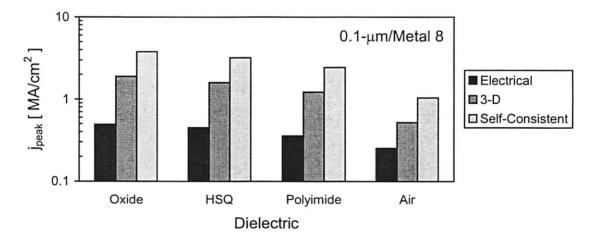

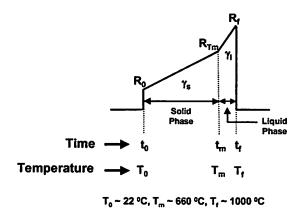

| Figure 9.5 Activation energy (Q) for electromigration under package level and wafer level stress conditions.                                                                                                                                                                                                                                                                                                                                       |