Copyright © 1997, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### SPEECH RECOGNITION FOR PORTABLE MULTIMEDIA TERMINALS

by

語を

Andrew Joseph Burstein

Memorandum No. UCB/ERL M97/14

21 February 1997

.

### SPEECH RECOGNITION FOR PORTABLE MULTIMEDIA TERMINALS

.

Copyright © 1996

by

Andrew Joseph Burstein

Memorandum No. UCB/ERL M97/14

21 February 1997

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### Abstract

### Speech Recognition for Portable Multimedia Terminals

by

Andrew Joseph Burstein

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Science University of California at Berkeley Professor Robert W. Brodersen, Chair

Portable multimedia terminals will require speech recognition for users to perform command and control operations. The speech recognition may either be implemented in software in computers on a high speed network, or in low-power hardware in the terminal itself. To facilitate the writing of applications using speech recognition, a new extension to the tcl language, along with a toolkit of classes, widgets, and applications, provide an easy to program API and a consistent user interface. This thesis also presents the architecture for low-power hardware to perform speech recognition and describes a custom CMOS IC that implements an important part of the speech recognition algorithm.

Robert W. Brodersen

Chairman of Committee

To my parents, Myra and Albert Burstein.

# TABLE OF CONTENTS

| Table of Conte                                | nts · · · · · · · · · · · · · · · · · · ·                                                                                                                                  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures                               |                                                                                                                                                                            |

| List of Tables ·                              | ix                                                                                                                                                                         |

| Acknowledgme                                  | nts · · · · · · · · · · · · · · · · · · ·                                                                                                                                  |

| CHAPTER 1.                                    | Introduction · · · · · · · · · · · · · · · · · · ·                                                                                                                         |

| 1.1<br>1.2                                    | InfoPad and Hand-Held Devices · · · · · · · · · · · · · · · · · · ·                                                                                                        |

| CHAPTER 2.                                    | Algorithm · · · · · · · · · · · · · · · · · · ·                                                                                                                            |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | Goals7RASTA-PLP8Hidden Markov Model11Multi-Layered Perceptron17Clustered Grammar24Recognition Results28Summary30                                                           |

| CHAPTER 3.                                    | Software:<br>User Interface and Applications                                                                                                                               |

| 3.1<br>3.2<br>3.3<br>3.4                      | Goals       31         Widgets in the SpRcg Toolkit       32         Speech Controlled Applications       36         Combining Handwriting and Speech Recognition       43 |

| CHAPTER 4.         | Software:                                                    |

|--------------------|--------------------------------------------------------------|

|                    | Programmer's Interface · · · · · · · · · · · · · · · · · · · |

| 4.1                | Overview & Goals                                             |

| 4.2                | Writing Applications for InfoPad 48                          |

| 4.3                | Low Level Implementation 50                                  |

| 4.4                | High Level Objects and Procedures: spRcg_gramDict            |

| 4.5                | Mega-Widgets · · · · · · · · · · · · · · · · · · ·           |

| 4.6                | GramCracker: A Tool to Build Vocabularies and Grammars 62    |

| 4.7                | Design Example · · · · · · · · · · · · · · · · · · ·         |

| CHAPTER 5.         | Low Power Memory Design 77                                   |

| 5.1                | Overview • • • • • • • • • • • • • • • • • • •               |

| 5.2                | Sram                                                         |

| 5.3                | How to use the Memories                                      |

| CHAPTER 6.         | Low-Power Speech Recognition Architecture                    |

| 6.1                | Goals                                                        |

| 6.2                | Previous Work 103                                            |

| 6.3                | Next Generation: Low Power 104                               |

| 6.4                | Front End 108                                                |

| 6.5                | MLP 109                                                      |

| 6.6                | Viterbi 110                                                  |

| CHAPTER 7.         | Low-Power Multi-Layer Perceptron Design 121                  |

| 7.1                | Architecture · · · · · · · · · · · · · · · · · · ·           |

| 7.2                | Summary of Low Power Techniques                              |

| 7.3                | Selecting Bit Sizes 130                                      |

| 7.4                | Interface                                                    |

| 7.5                | Results 132                                                  |

| CHAPTER 8.         | <b>Conclusion</b> 136                                        |

| 8.1                | Contribution · · · · · · · · · · · · · · · · · · ·           |

| 8.2                | Discussion & Future Work 136                                 |

| Bibliography · · · |                                                              |

| Appendix: Dired    | ctories · · · · · · · · · · · · · · · · · · ·                |

# LIST OF FIGURES

| CHAPTER 1. · |                                                              |

|--------------|--------------------------------------------------------------|

| Figure 1-1.  | Overview of InfoPad                                          |

| Figure 1-2.  | Difficulty of various speech recognizer types                |

| CHAPTER 2. · |                                                              |

| Figure 2-1.  | Choice of components in the SpRcg system                     |

| Figure 2-2.  | The role of front end signal processing                      |

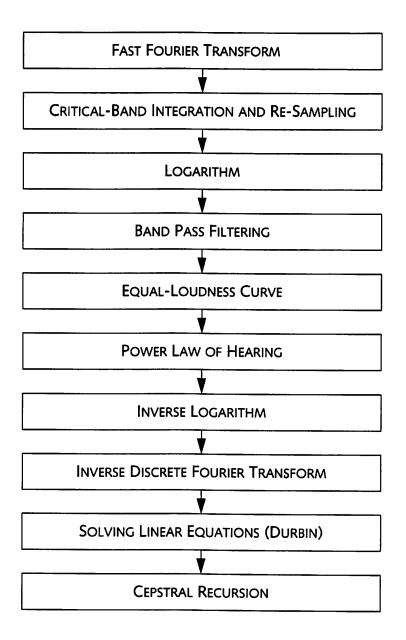

| Figure 2-3.  | Block diagram of RASTA-PLP 10                                |

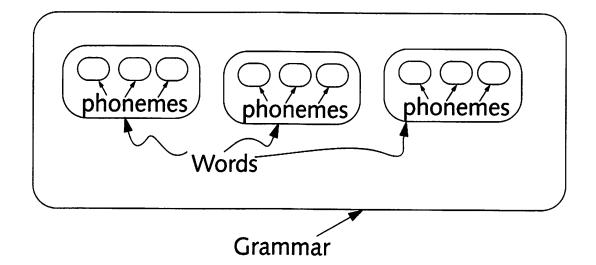

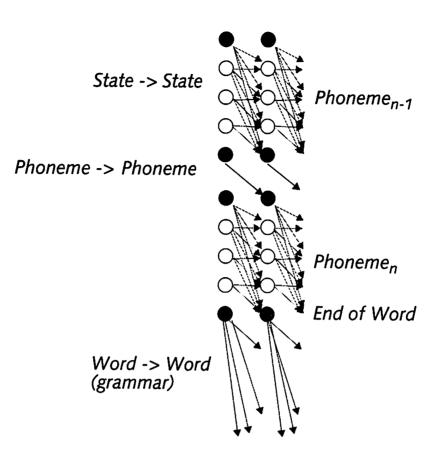

| Figure 2-4.  | Hierarchy in a hidden Markov model 12                        |

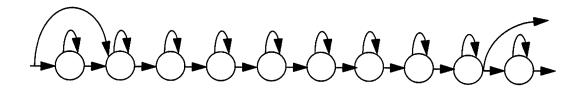

| Figure 2-5.  | 10 state hmm for the word "oh." 15                           |

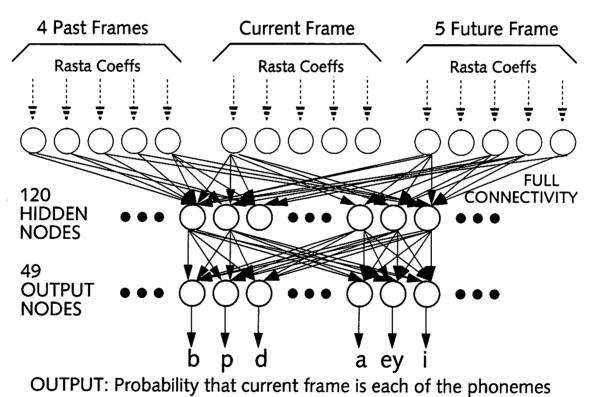

| Figure 2-6.  | Multi-layered perceptron to compute phoneme probabilities 19 |

| Figure 2-7.  | Hierarchy in the HMM 25                                      |

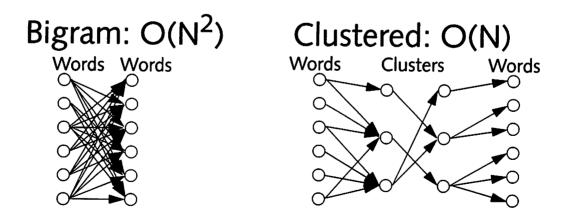

| Figure 2-8.  | Clustered grammar reduces complexity 25                      |

| Figure 2-9.  | Example of a grammar cluster. 27                             |

| CHAPTER 3. · |                                                              |

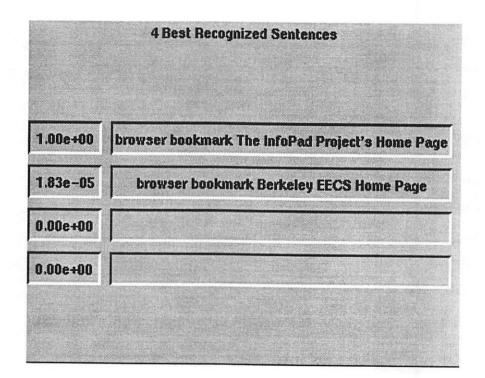

| Figure 3-1.  | spRcg_NBest widget 32                                        |

| Figure 3-2.  | SpRcg_controller widget 33                                   |

| Figure 3-3.  | spRcg_adapter widget 35                                      |

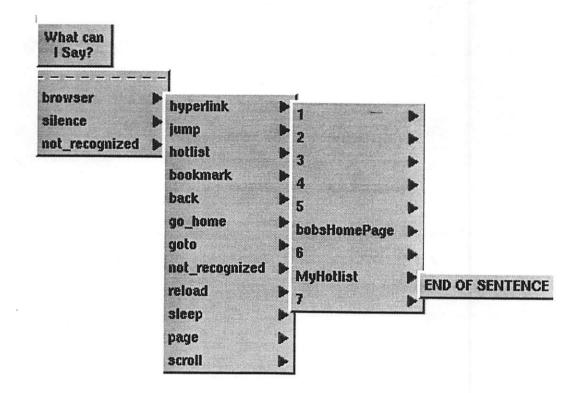

| Figure 3-4.  | Grammar cascade                                              |

| Figure 3-5.  | Web browser main display 37                                  |

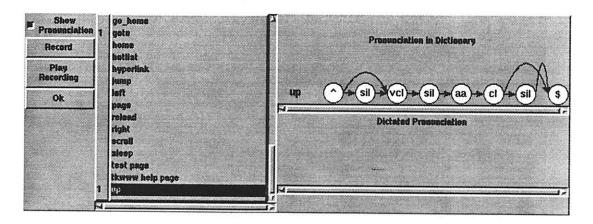

| Figure 3-6.  | Web browser control panels 41                                |

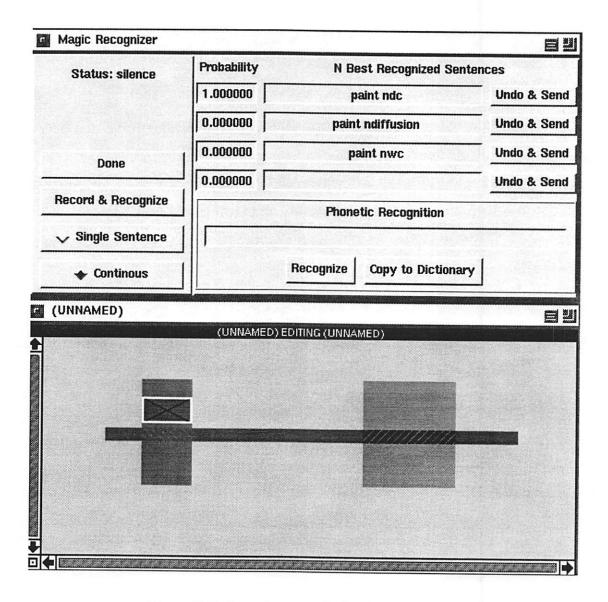

| Figure 3-7.  | Speech controlled ic layout editor. 44                       |

| CHAPTER 4.   |                                                              |

| Figure 4-1.  | Design trade-offs 47                                         |

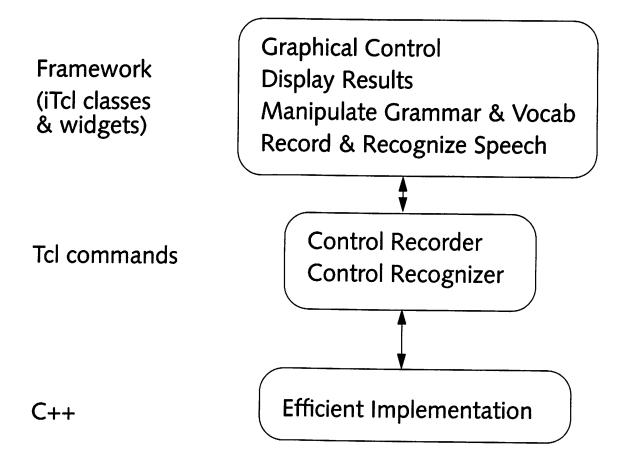

| Figure 4-2.  | Architecture of speech recognition software                  |

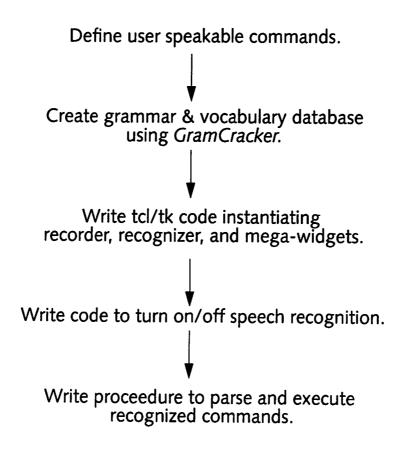

|          | Figure 4-3.                       | Process for adding speech recognition to a tcl/tk application                | 49 |

|----------|-----------------------------------|------------------------------------------------------------------------------|----|

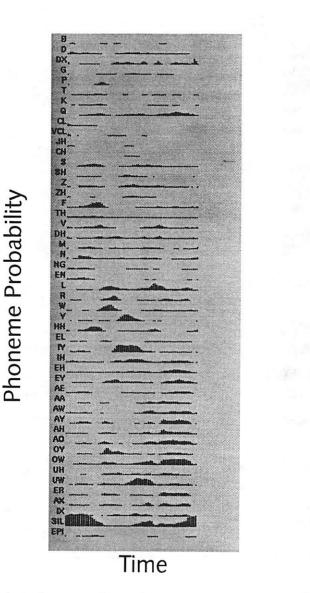

|          | Figure 4-4.                       | Output of MLP for an utterance of "reload."                                  | 63 |

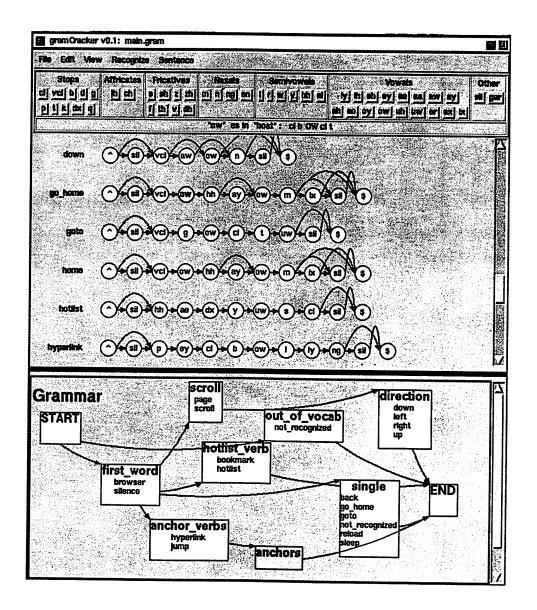

|          | Figure 4-5.                       | GramCracker displaying grammar for a WWW browser.                            | 64 |

|          | Figure 4-6.                       | Grammar cluster dialog                                                       | 65 |

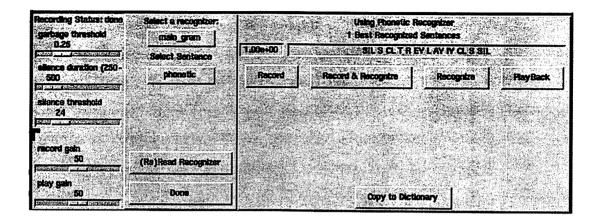

|          | Figure 4-7.                       | Performing phonetic recognition in GramCracker.                              | 66 |

|          | Figure 4-8.                       | GramCracker using the full vocabulary.                                       |    |

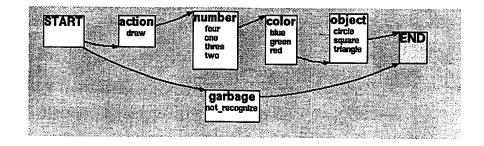

|          | Figure 4-9.                       | Demo grammar.                                                                |    |

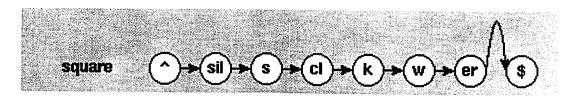

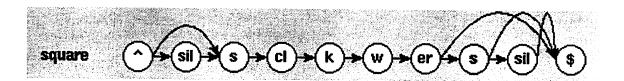

|          | Figure 4-10.                      | Transcribed pronunciation of "square." · · · · · · · · · · · · · · · · · · · | 68 |

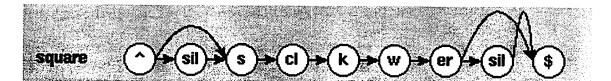

|          | Figure 4-11.                      | "Square" with optional starting and ending silence.                          | 69 |

|          | Figure 4-12.                      | "Square" with optional "s."                                                  |    |

|          | Figure 4-13.                      | Listing of demo grammar and dictionary file                                  | 70 |

|          | Figure 4-14.                      | Creating the speech objects and widgets.                                     | 71 |

|          | Figure 4-15.                      | Controlling recognition.                                                     | 72 |

|          | Figure 4-16.                      | Parsing the recognized sentences.                                            | 74 |

|          | Figure 4-17.                      | The rest of the application source code.                                     | 75 |

|          | Figure 4-18.                      | The finished demo application.                                               | 76 |

| CF       | IAPTER 5                          |                                                                              | 77 |

| <b>O</b> |                                   |                                                                              |    |

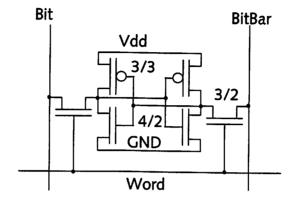

|          | Figure 5-1.                       | SRAM memory cell schematic.                                                  |    |

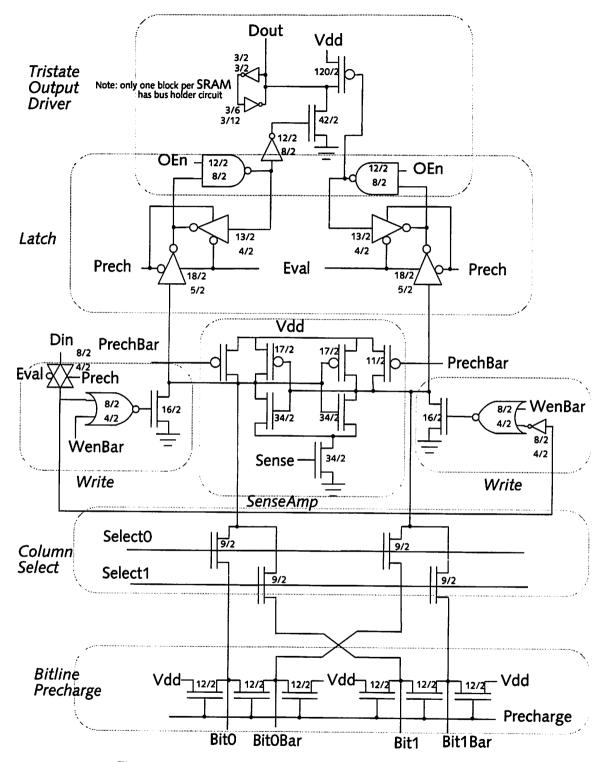

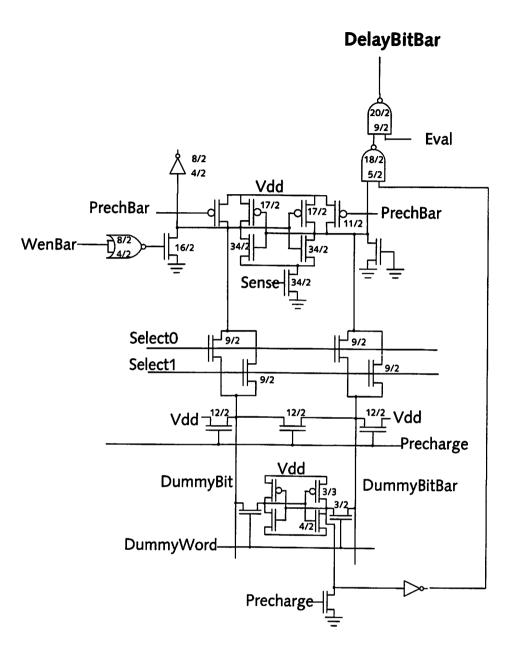

|          | Figure 5-2.                       | SRAM senseamp and write circuit diagram                                      |    |

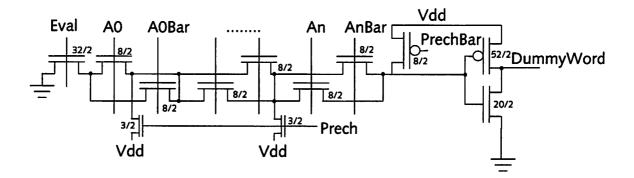

|          | Figure 5-3. $\mathbf{F}^{\prime}$ | SRAM dummy word driver.                                                      |    |

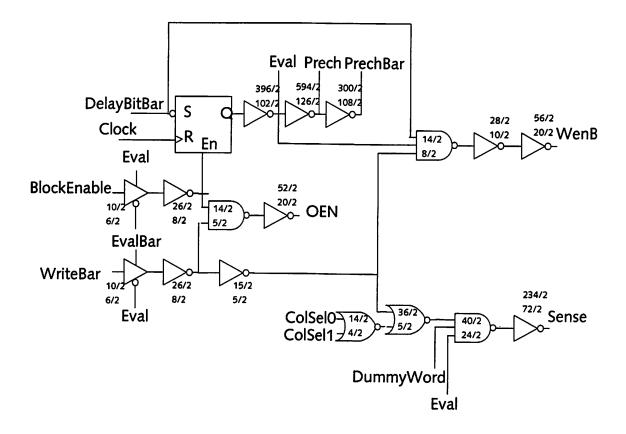

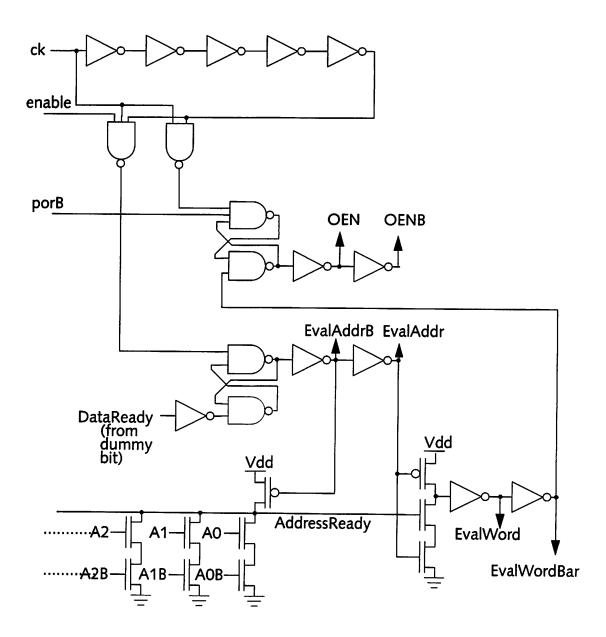

|          | Figure 5-4.                       | SRAM self-timing circuitry.                                                  |    |

|          | Figure 5-5.                       | SRAM control circuits.                                                       |    |

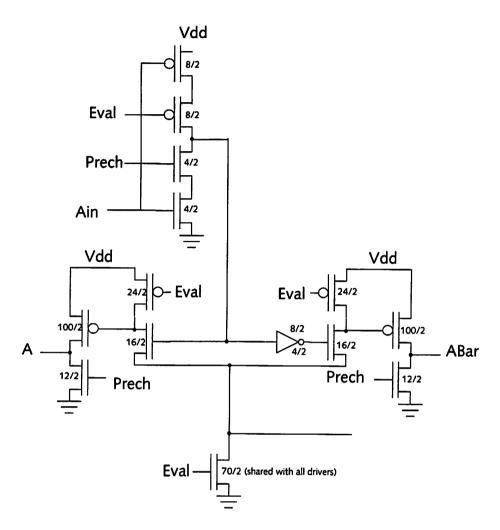

|          | Figure 5-6.                       | Address latch and driver.                                                    |    |

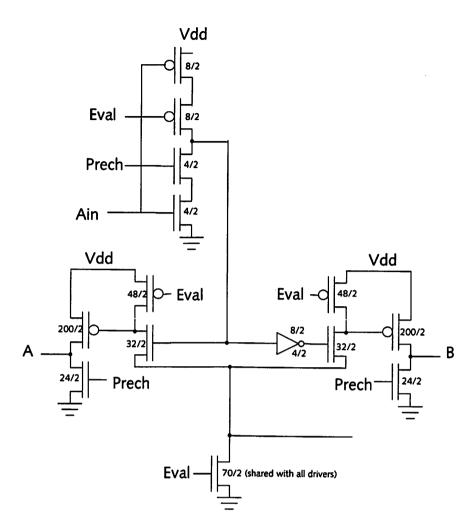

|          | Figure 5-7.                       | Column select latch and driver.                                              |    |

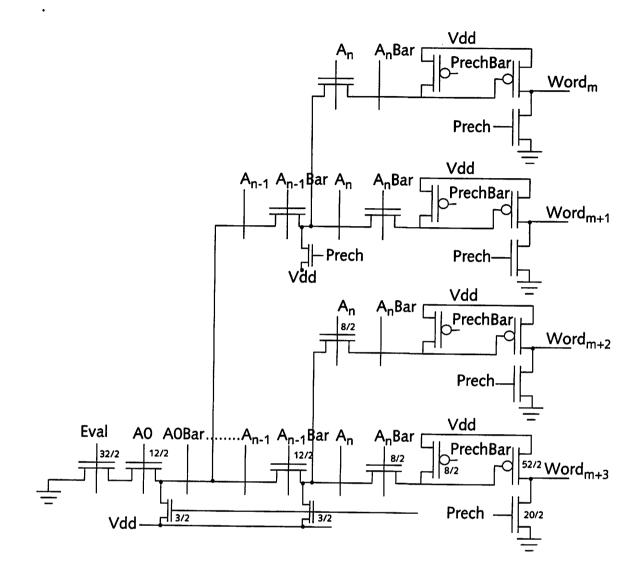

|          | Figure 5-8.                       | Tree-structured sram address decoder and row drivers.                        |    |

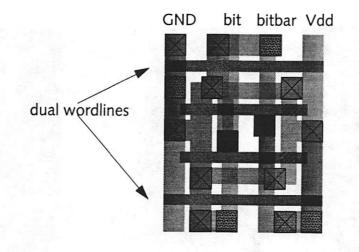

|          | Figure 5-9.                       | SRAM cell layout.                                                            |    |

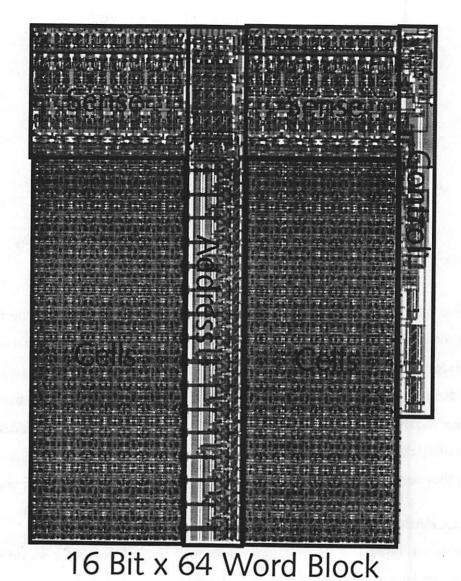

|          | Figure 5-10.                      | SRAM block layout.                                                           |    |

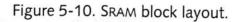

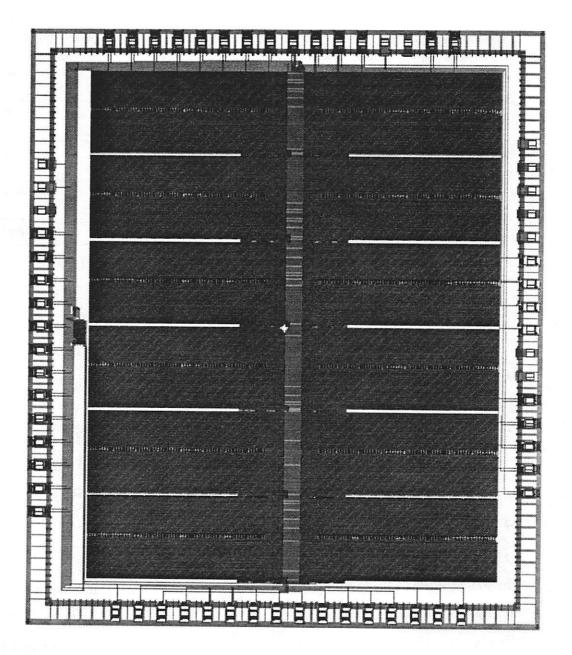

|          |                                   | Layout of 3 kWord x 32 bit sram integrated circuit                           |    |

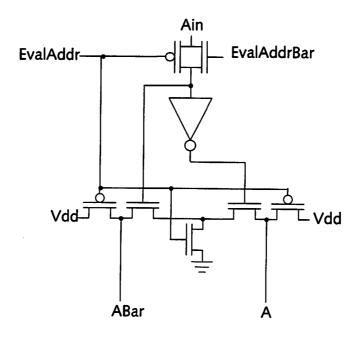

|          |                                   | ROM address latch.                                                           |    |

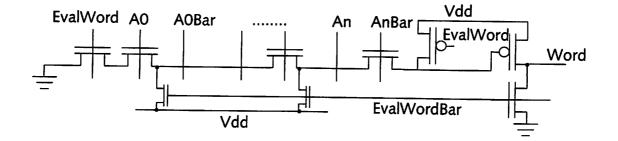

|          |                                   | ROM address decoder and wordline driver                                      |    |

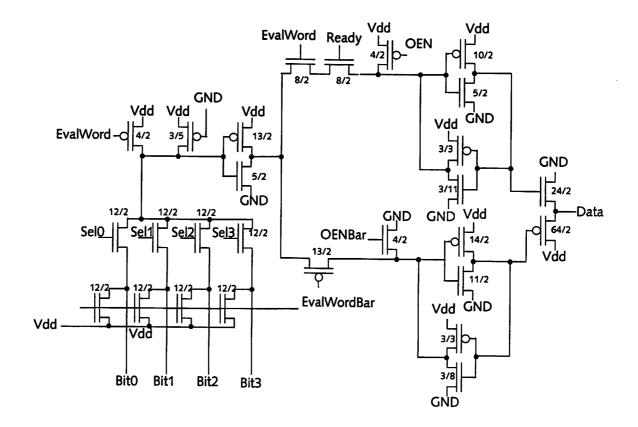

|          |                                   | ROM senseamp.                                                                |    |

|          | -                                 | ROM control circuits.                                                        |    |

|          | -                                 | Layout of 1024 word x 16 bit ROM block 1                                     |    |

|          |                                   | Sample parameters to synthesize a ROM 1                                      |    |

|          | Figure 5-18.                      | Example irsim commands to simulate ROM 1                                     | 02 |

| CH       | IAPTER 6.                         |                                                                              | 03 |

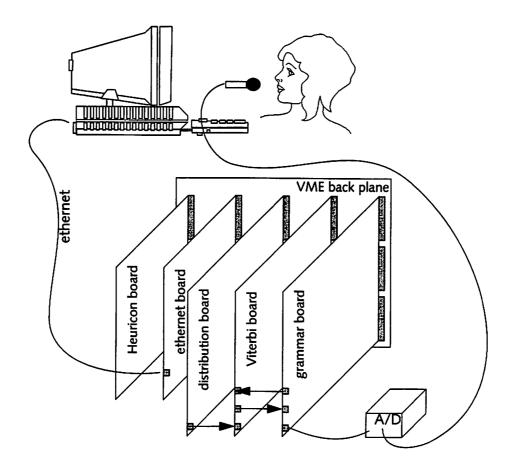

|          | Figure 6-1.                       | Previous UCB speech recognition hardware system 1                            | 04 |

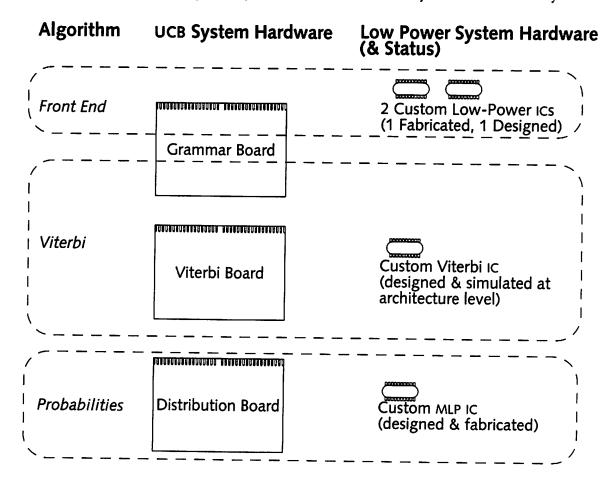

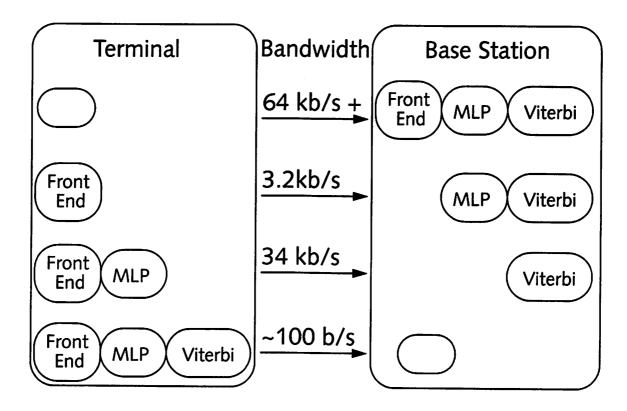

|          | Figure 6-2.                       | Comparison of hardware partitions                                            | 05 |

|          |                                   |                                                                              |    |

| Figure 6-3.  | Low-power system architecture.               | 107 |

|--------------|----------------------------------------------|-----|

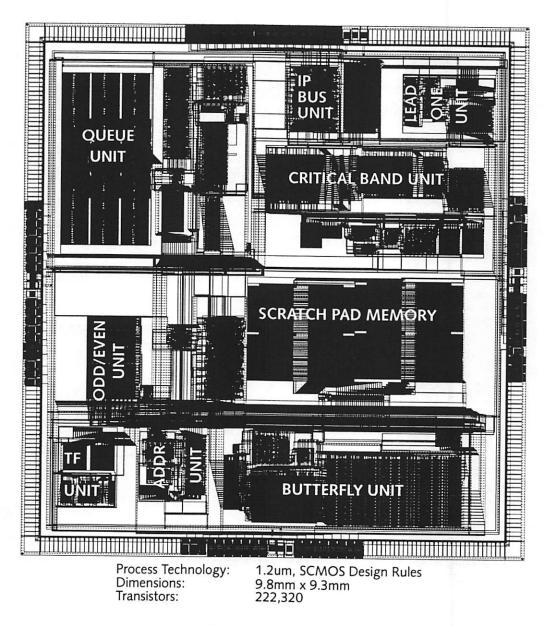

| Figure 6-4.  | SORASTA IC layout.                           | 108 |

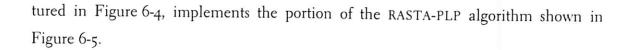

| Figure 6-5.  | Sorasta chip algorithm.                      | 109 |

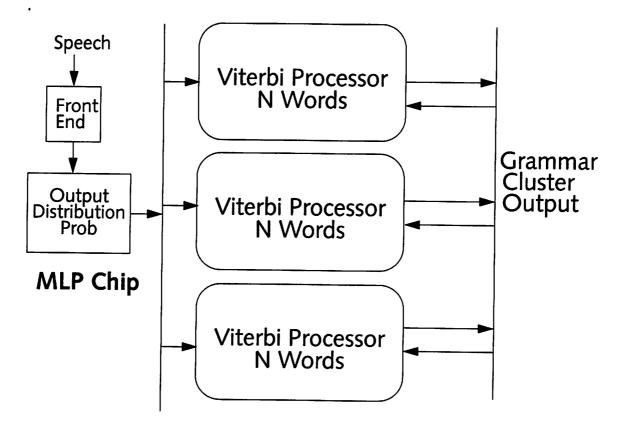

| Figure 6-6.  | Viterbi chip architecture and data flow      | 110 |

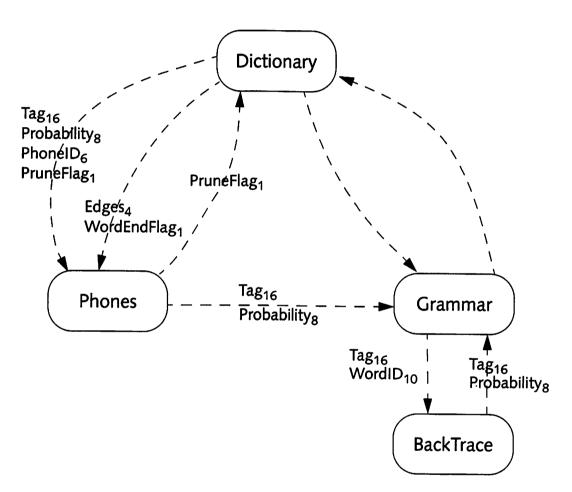

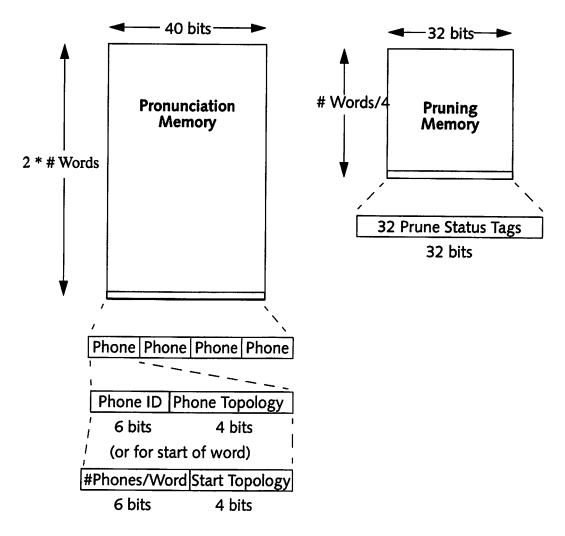

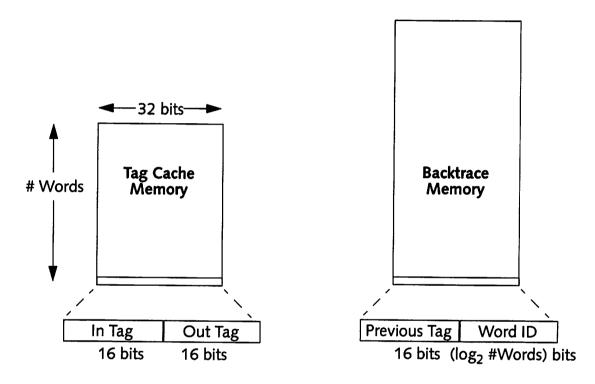

| Figure 6-7.  | Dictionary subsystem memories.               | 112 |

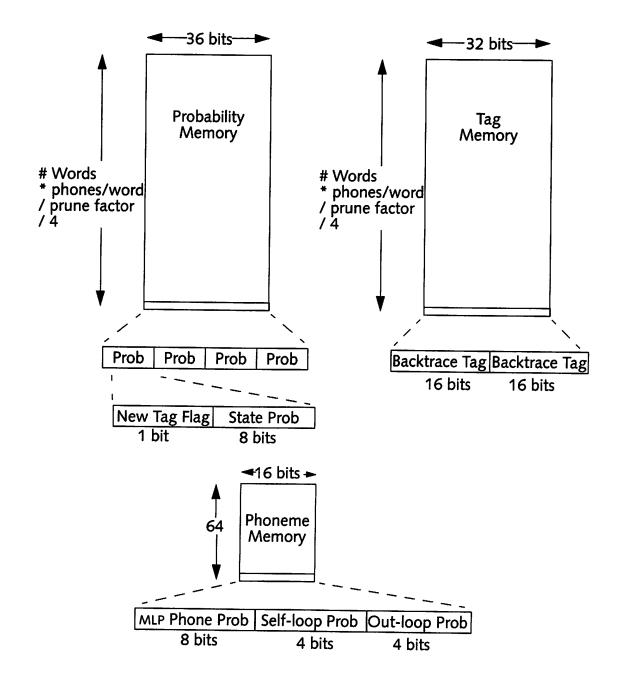

| Figure 6-8.  | Phone subsystem memories.                    | 113 |

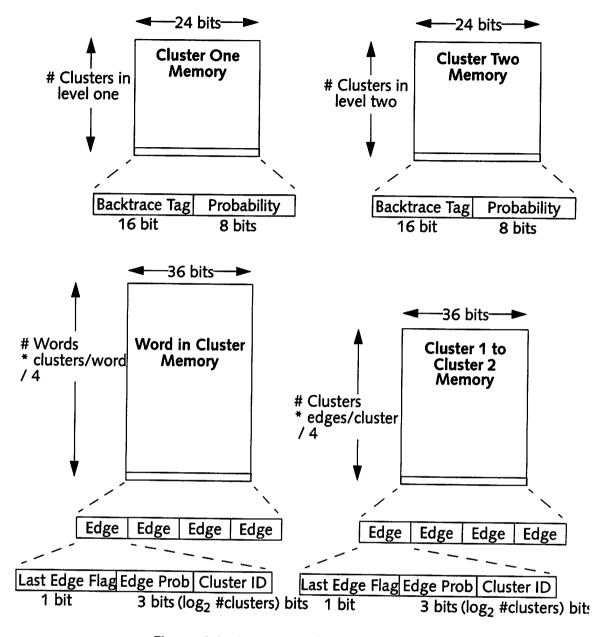

| Figure 6-9.  | Grammar subsystem memories                   | 115 |

| Figure 6-10. | Backtrace subsystem memories.                | 117 |

| CHAPTER 7.   |                                              | 121 |

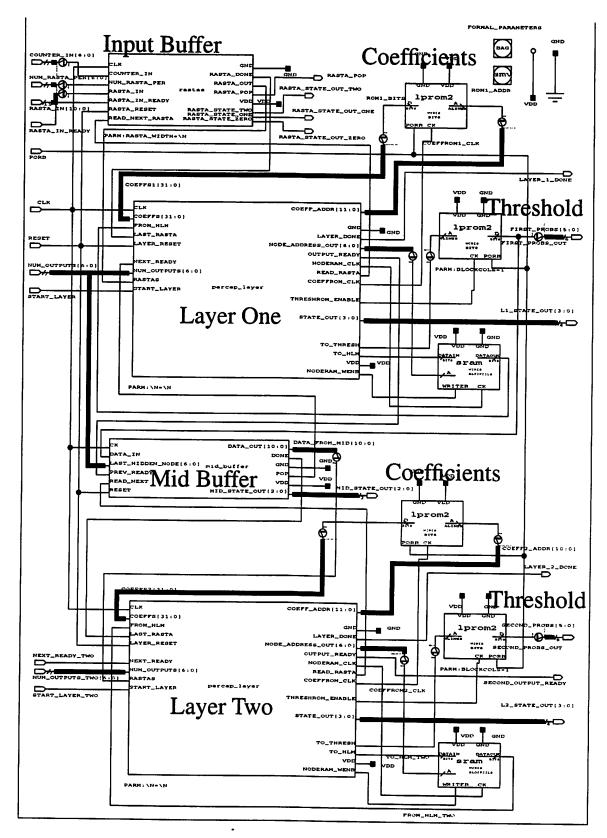

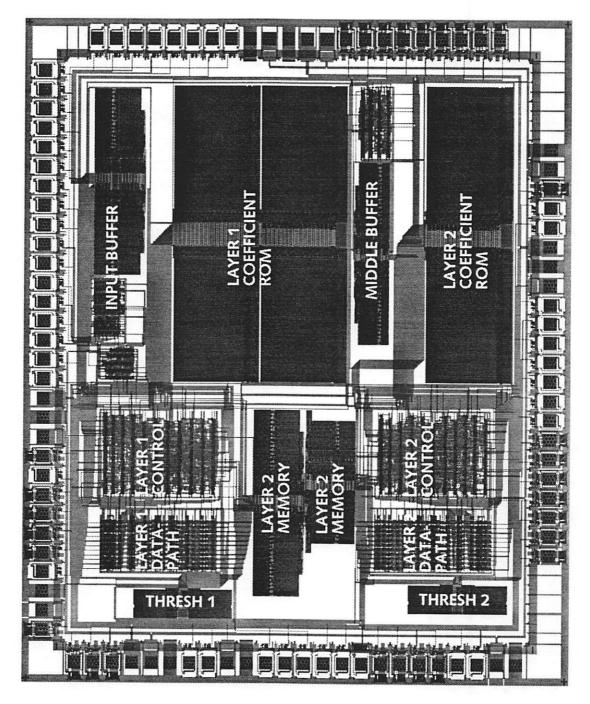

| Figure 7-1.  | MLP chip architecture.                       | 122 |

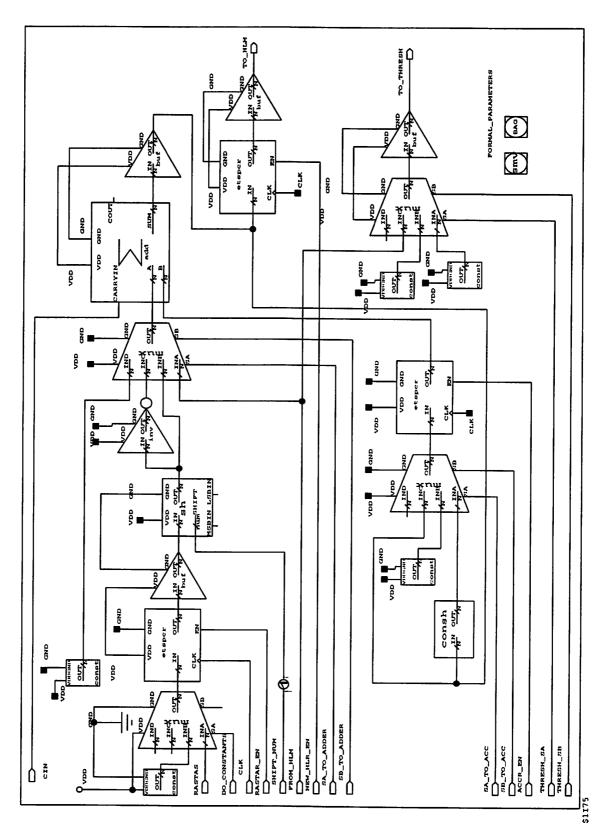

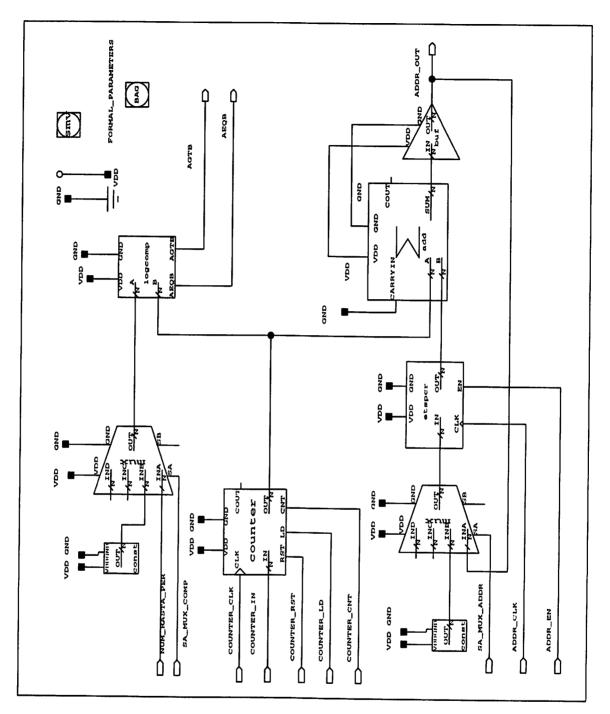

| Figure 7-2.  | Datapath for MLP layers.                     | 124 |

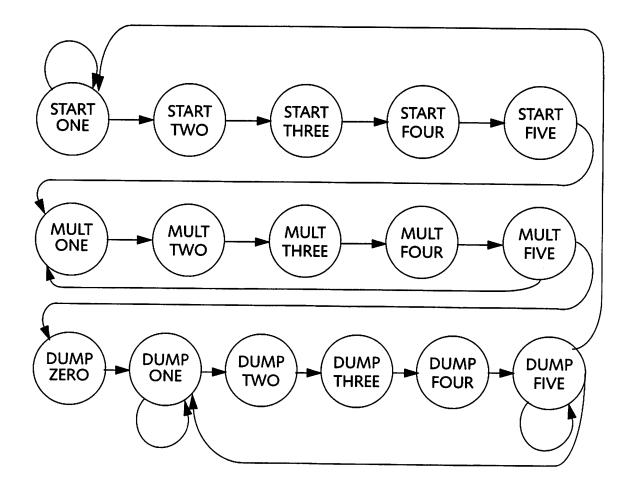

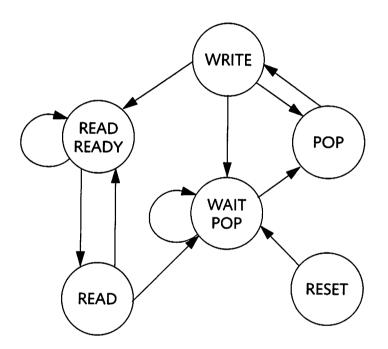

| Figure 7-3.  | State transition diagram of layer control.   | 125 |

| Figure 7-4.  | Input buffer control state diagram.          | 127 |

| Figure 7-5.  | Input buffer datapath                        | 128 |

| Figure 7-6.  | MLP chip layout.                             | 134 |

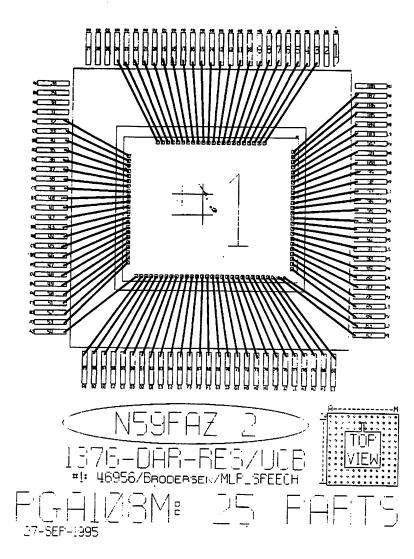

| Figure 7-7.  | MLP chip bonding diagram.                    | 135 |

| CHAPTER 8.   | •••••••••••••••••••••••••••••••••••••••      | 136 |

| Figure 8-1.  | Partitioning recognition across the network. | 138 |

.

# LIST OF TABLES

| Table 2-1.          | N-best digit recognition 16                         |

|---------------------|-----------------------------------------------------|

| Table 2-2.          | Breakdown of digit recognizer errors 17             |

| Table 2-3.          | MLP output scoring by phoneme. 22                   |

| Table 2-4.          | MLP Nth best results. 23                            |

| Table 2-5.          | N-best digit recognition using spRcg 29             |

| Table 2-6.          | SpRcg user test results. 29                         |

| Table 5-1.          | Voltage scaling a 128 word 12 bit 0.6 µm SRAM 94    |

| Table 5-2.          | SRAM speed and energy vs. size at 1.5V              |

| Table 5-3.          | ROM speed & energy vs. size and voltage 100         |

| Table 6-1.          | Comparison of memory sizes 106                      |

| Table 6-2.          | Memory sizes for various viterbi configurations 119 |

| Table 7-1.          | MLP ROM sizes 129                                   |

| Table 7-2.          | MLP RAM Sizes. 129                                  |

| Table 7-3.          | MLP chip outputs 130                                |

| Table 7-4.          | MLP chip inputs 131                                 |

| Table 7-5.          | MLP chip power supplies 132                         |

| Table 7-6.          | Parameter input values 132                          |

| Table 7 <b>-</b> 7. | MLP chip power consumption 133                      |

|                     |                                                     |

## ACKNOWLEDGMENTS

First and foremost I wish to thank my family. My parents Myra & Albert have given me unconditional love and support throughout my life. They deserve the credit for everything I have accomplished. My brother and sister-in-law Jeff & Cheryl always helped me to get away from it all on vacations, and lately provided a welcome distraction with my new nephew Gregory. I also wish to thank my grandparents, Selma & David Sole and Pauline & Aaron Burstein for never questioning how I could be 2 years away from graduation for 3 straight years. My only regret is my grandfather Aaron could not be with us at my graduation. My cousin (and friend) Beth Eilers has helped me survive this last, and hardest, year and a half. I am indebted to you all.

Next I wish to thank my many friends among my fellow graduate students. By far the best part of being at Berkeley was working and playing with this (by and large:-) great group of people. Among the many are Eric Boskin, who showed me it is possible to graduate. Sam Sheng, who didn't, but did help me out in just about every other way. Tony Stratakos and Dave Lidsky, who made me feel like a good teacher. Tom Burd, who expanded my vocabulary. The gang that's still haunting 550 Cory Hall — Jennie Chen, Shankar Narayanaswamy, Ian O'Donnell, Arthur Abnous, Craig Teuscher, Jeff Gilbert, Renu Mehra, Lisa Guerra, and Ole Bentz — and those who got away — Jane Sun, John Barry, Tony Stölzle, Monte Mar, Lars Thon, Sonia Sachs, and Anantha Chandrakasan to name a few — all made it worth while. Several members of the faculty and staff have helped me greatly. Professor Jan Rabaey helped me to learn a great deal while TAing 141 and 241, and let me teach some of the lectures. Professor Nelson Morgan helped me with my speech recognition research and generously agreed to be on my Quals and Thesis committees. Likewise, Professor Charles Stone donated his time for my Quals and Thesis committees. Kevin Zimmerman, our indefatigable system administrator has somehow managed to keep our computers running without losing his sanity or sense of humor (as far as I can tell).

Finally, I wish to thank my research advisor, Robert Brodersen. He has provided me with the best support and resources that a grad student could ever hope for. What's more, he has taught me the importance of having and communicating a vision, a lesson I will use for the rest of my life.

# 1 INTRODUCTION

This thesis describes the application of speech recognition to a new environment: handheld, multi-media, wireless computing. This chapter will first describe the InfoPad project, a large research project that is exploring this new environment. Then, this chapter describes the need for speech recognition in hand-held terminals.

#### 1.1 InfoPad and Hand-Held Devices

The recent explosive growth of the Internet and the World Wide Web (WWW) have shown that the ability to find and access information is at least as important as the ability to store information. The ability to create local copies of information on one's own hard disk is becoming increasingly irrelevant; the network itself is now the storage device. It makes more sense to retrieve the most up to date information from the source on demand, rather than store local copies that rapidly become obsolete and that fill expensive storage devices.

In addition to using the network to store data, it also makes sense to treat the network as a computational resource, rather than adding increasingly powerful processors and peripherals to portable computers. Attaching high speed computers to the network instead of placing them in portable devices has two advantages. The first is a reduction in power consumption and size. Portable devices are powered by batteries, so their hardware design must place as much emphasis on low power and low weight as it does on high computational throughput, leading to inevitable trade-offs. Non-portable hardware, in contrast, has much less severe penalties for power consumption and weight. Inevitably, non-portable hardware will be cheaper than portable hardware of the same computational power.

**High-Speed Fiber Backbone**

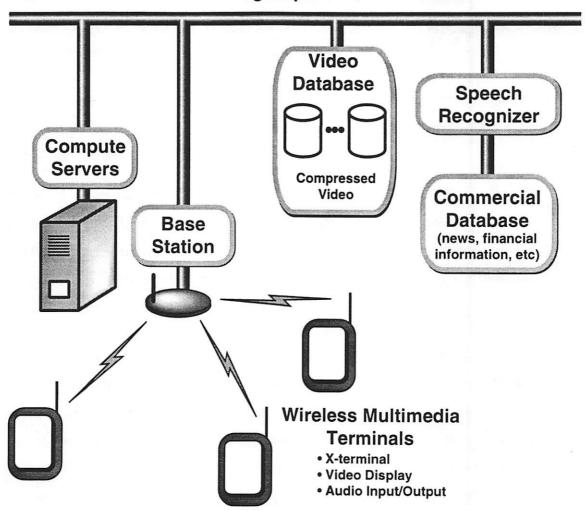

Figure 1-1. Overview of InfoPad.

The second advantage of attaching processing power to the network is availability. A processor in a laptop is available only to that laptop's user; further, it is the only processor available to that user. Most of the time, the user is not performing complex operations, so that processor is sitting idle, although it still adds to the weight, cost, and power consumption of the laptop. When the user does want to perform computations, s/he usually wants as much throughput as possible. On the other hand, if the user performs computations on a workstation on the network, other users can utilize that workstations processor when it would be otherwise idle. Even better, by using the techniques demonstrated by the Network of Workstations (NOW) project [18] a user can utilize the power of many workstations during those times s/he needs high computational throughput. Overall, leaving computational and storage assets on the network allows for the most economical design of hardware as well as the most cost effective sharing of resources.

With most or all storage and computational tasks left on the network, the portable device is reduced to an input and output device; connectivity and easy-to-use interfaces become paramount. The InfoPad system fulfills this role; it provides audio, text/graphics, and full motion video output; its input data types are pen and audio. InfoPad also has excellent network connectivity: pico-cell radio links provide 2 Mbit/second downlink bandwidth and 64kbit/second uplink bandwidth. See Figure 1-1 for an overview of InfoPad.

The InfoPad's I/O capabilities combined with its radio connectivity to network storage and computation make it seem to have the capabilities of a portable workstation with one interesting exception: it has no keyboard. The main reason for excluding a keyboard is size: the ultimate form factor for infopad will be tablet size, wafer thin, and entirely covered by the display. Another reason for excluding a keyboard is ease of use. Although many people use keyboards every day, most people are not prolific at typing; furthermore, an increasing number of those that are prolific are succumbing to repetitive stress injuries. In contrast, speaking and writing are nearly universal skills. A portable terminal with pen and speech input would be an ideal combination of small size and ease of use.

#### 1.2 Speech Recognition in InfoPad

#### 1.2.1 Software

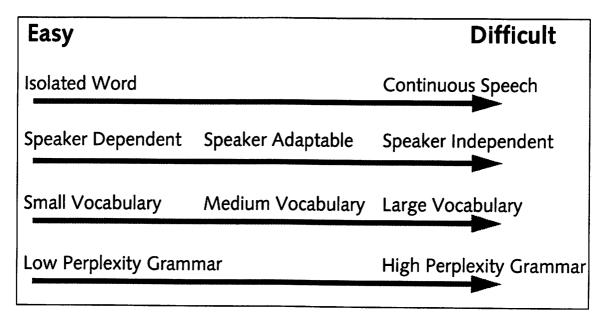

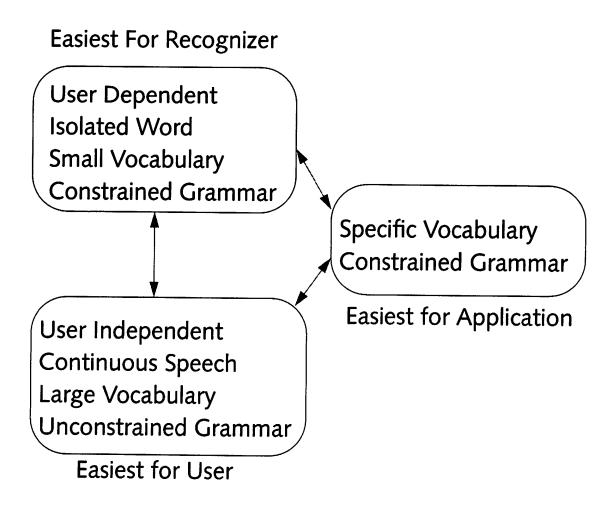

Replacing a keyboard with a speech recognizer is a difficult task. Despite steady advances in the state of the art of speech recognition, speech recognizers are still nowhere near as skillful as humans are at transcribing spoken words into written text. In order to improve recognition accuracy, it is helpful to relax one or more of the constraints on speech recognition as shown in Figure 1-2. The first constraint is to use isolated words, forcing speakers to pause between words, as opposed to continuous speech, in which words may be slurred together. The second constraint is speaker dependent recognition, which requires extensive training on every new speaker, as opposed to speaker independent recognition, which requires no new training for new users. In between these two extremes are speaker adaptable systems, which will work accepatably well without training on new users, but which will perform even better with more training. The third constraint is the size of the vocabulary, which measures the number of words the recognizer can understand at any given time. The fourth and final constraint is the perplexity of the grammar, a measure of how many words can follow another word in a sentence.

This thesis describes the implementation of a speech recognition system, called spRcg, for

Figure 1-2. Difficulty of various speech recognizer types.

use with portable terminals such as the InfoPad. In terms of Figure 1-2, the recognizer accepts continuous speech, is speaker independent (with speaker adaptable capabilities), uses small to medium vocabulary, and is optimized for constrained (low perplexity) grammars.

Speech recognizers output whole words or, in the case of continuous speech recognizers, whole sentences; keyboards output individual ascii characters. Given their differences, it is to be expected that programs can not simply swap out keyboard input and swap in speech recognition input. Furthermore, in order to make the recognition task as easy as possible on the vocabulary size constraint and the grammar perplexity constraint, it is desirable to pass information from the application back to the speech recognizer. For

these reasons, this researching includes the development of programming interfaces and toolkits to allow programmers to include speech recognition into their applications with minimal of effort.

Using speech recognition (along with handwriting recognition) in applications represents a paradigm shift from the window, icon, mouse, pointer (WIMP) strategy. As part of the research effort into developing a new user interface for portable terminals, the speech recognition software toolkit includes methods that allow users to control the speech recognizer and to correct recognition errors. Furthermore, as a demonstration of this new software, this research includes an application program, a speech recognition controlled World Wide Web browser.

#### 1.2.2 Hardware

One major contribution of the InfoPad project has been the advancement of low power integrated circuit design techniques. Although the InfoPad model calls for performing the majority of all computations on the network, there must always be some computations performed locally on the pad itself. InfoPad performs such tasks as multiplexing and demultiplexing packets, decoding vector quantized video, and updating frame buffers on full-custom, low-power CMOS integrated circuits. In fact, the low power design techniques that were applied to these chips were so successful that they consume a total of less than 5 mW, a trivial portion of the InfoPad's power consumption. This lower power design was so successful, that future versions of InfoPad will be able to have increased computational throughput while still maintaining extremely low power consumption.

In keeping with the low power design research of the InfoPad project, this thesis also describes work done to design a low power, custom CMOS IC implementation of Info-Pad's speech recognition algorithm.

Performing the recognition on the network is a practical solution, but there are also advantages to performing recognition in the portable device itself. The first advantage is bandwidth. Transmitting good quality speech to the network requires an uplink bandwidth of about 64 kbit/second. In contrast, transmitting pen data requires only about 2 kbit/second, so by far the majority of the uplink bandwidth is consumed by audio. If speech recognition was performed on the InfoPad terminal, then the uplink would only need to transmit an ascii representation of the recognized words, needing only a few hundred bits/second. This reduction in uplink bandwidth can reduce the needed complexity and power consumption of the InfoPad's radio, and could also allow operatation in regions with only low bandwidth radio links.

The second advantage is autonomy. If a future InfoPad has enough local computation to perform useful applications locally, as seems likely given current research into low power microprocessors [2][6], then an InfoPad could be used even when it is outside of an area that allows radio connections to the network. In these circumstances, the pad will need to perform speech recognition in order to be useful. However, general purpose microprocessors are not optimized for the tasks involved in speech recognition, so the lowest cost and lowest power implementation of speech recognition would be on custom hardware. One could also imagine the usefulness of a low power speech recognition chipset in devices other than InfoPad.

In addition to making a contribution to InfoPad and to speech recognition, the research described in this thesis also made contributions to the work in low power CMOS design. In particular, this thesis describes low power memory design techniques that are needed for low power speech recognition hardware, but which are also generally useful, having been incorporated in many of the InfoPad's custom chips.

# 2 ALGORITHM

#### 2.1 Goals

Many researchers are working to improve the recognition accuracy of speech recognition algorithms. The goals of this research is to use these algorithms wherever possible and to adapt them to the software and or hardware requirements of portable recognition wherever necessary.

Throughout the speech recognition research community, there are algorithms that are commonly used. For example, the Viterbi algorithm on hidden Markov models is widely used. This research seeks to use these "state of the art" algorithms for two reasons. First, because using them produces good results. Second, to demonstrate that the hardware, programming, and user interface techniques developed in the course of this work are applicable to widely used algorithms.

There is not a consensus in the speech recognition community on the relative merits of competing algorithms or variations on algorithms. For example, there are several popular front end signal processing algorithms, including RASTA [8][9] and LPC based cepstral coefficients. Variations on hidden Markov models abound, especially in regard to topologies and to classes of output probability distributions. Generally, when these variations exist, they each provide roughly equivalent recognition accuracy, or their relative merits have not yet been decided.

Usually, "relative merits" refers to recognition accuracy, or perhaps efficient implementation on general purpose hardware. Implementing speech recognition in low power hardware has a different set of criteria, so clear winners may be obvious in this context among otherwise equivalent algorithms.

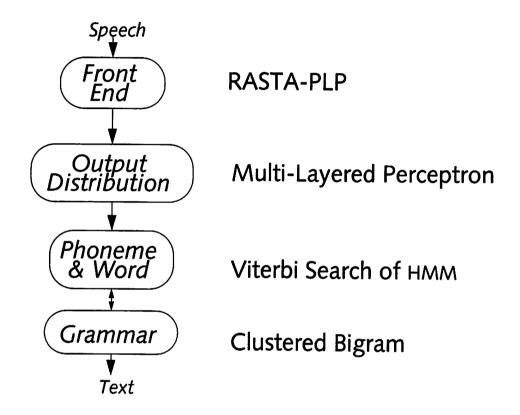

Figure 2-1 shows the components in a typical speech recognition system, as well as the specific choices of algorithm used in the spRcg speech recognition system. The following sec-

Figure 2-1. Choice of components in the SpRcg system.

tions describe each individual component.

#### 2.2 RASTA-PLP

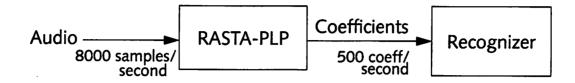

Speech recognizers use front end signal processing to reduce input data rates and to extract the parts of the audio signal that contain phonologically important information. The spRcg speech recognizer uses the RASTA-PLP [8][9] algorithm to perform front end signal processing

Figure 2-2. The role of front end signal processing.

The RASTA-PLP algorithm is based on the Perceptual Linear Predictive (PLP) algorithm, which applies psychoacoustic principles to an all-pole model of the auditory spectrum. The RASTA technique enhances the usefulness of PLP for speech recognition by removing the parts of the signal that are contributed by the acoustic channel - the microphone and room acoustics. These components of the signal contribute constant or slowly varying parts of each band, which are removed by the band pass filtering stage, as shown in Figure 2-3. Only the time varying part of the signal - which presumably contains the important parts of the speech signal, are left.

RASTA-PLP's advantages for the spRcg speech recognizer are twofold. First, the RASTA technique provides robust recognition even in varying acoustic environments. Since Info-Pad is portable, it records speech in a variety of environments, with little control over the relative placement of the microphone. Furthermore, it is helpful to be able to train on standard databases, which contain speech recording under ideal circumstances and with expensive (and carefully placed) microphones, and then be able to recognize speech in real world conditions.

The second advantage is coding efficiency. RASTA-PLP can achieve equivalent recognition accuracy using fewer coefficients than can other common algorithms such as cepstral analysis. Where cepstral analysis of speech sampled at 8 kHz typically uses 8 coefficients, RASTA-PLP can perform well with 5. With fewer coefficients to process, the output probability computation (in the case of spRcg, the output probability multi-layered percep-

Figure 2-3. Block diagram of RASTA-PLP.

tron) needs to perform fewer computation and fewer memory accesses, thereby saving power consumption in special purpose hardware.

#### 2.3 Hidden Markov Model

spRcg's speech recognizer is based on the hidden Markov model. Several excellent references describe hidden Markov models and their uses in speech recognition [11][12][19][26]. This section provides a brief overview, then presents the HMM used by the previous generation Berkeley speech recognition hardware as an example. The HMM in spRcg's speech recognizer is described later in this chapter.

#### 2.3.1 Algorithm

The hidden Markov model (HMM) describes a model for the process of generating speech; the Viterbi algorithm is used to recognize speech by finding the most likely path through an HMM for any given utterance.

An HMM is a graph, containing states connected by edges, that represents spoken language. The act of speaking is modeled by the process of traversing this graph, from one state to another, according to a random process determined by probabilities associated with the edges in the graph. The actual sounds of speech, or at least some coefficients derived from these sounds, are randomly generated according to probability distribution functions that are attached to the presently occupied states. The Markov model is "hidden" because the outside world cannot see which state is currently occupied; the outside world only sees the coefficients emitted by the HMM. The task of the Viterbi algorithm is to infer the most likely sequence of states through the HMM, given a particular HMM and given a particular sequence of coefficients

An HMM is a model of a spoken language, or of part of a spoken language. The knowledge incorporated into an HMM can be described at three levels: phonetic, word, and grammar (Figure 2-4). At the lowest level, the phonetic level, the HMM describes, in a statistical fashion, how the individual speech sounds of a language relate to the coefficients used to encode their acoustic expression. Phonemes are linguistic categories used to describe all of the sounds in a language. Different languages have different phonemes; even the phonemes in a particular language are subject to interpretation. For example, different systems use slightly different lists to describe the phonemes in English. The same phoneme

Figure 2-4. Hierarchy in a hidden Markov model.

can sound differently depending on such variable as where it occurs in a word, what are the surrounding phonemes, the speakers accent, and the speaker's intonation.

Phoneme models are themselves small HMMs. They can be connected together with edges to assemble larger HMMs that model words. In turn, the words can be connected by edges to form large HMMs that model the entire spoken language (or at least that part of it that the recognizer can recognize).

Speech recognition systems often distinguish phonemes on a different basis than do linguists. Meaning is less important; acoustics are more important. For example, coarticulation, the influence of one phoneme on a neighboring phoneme's pronunciation, can have a major effect on the acoustics of a phoneme. Speech recognizers often use multiple models to represent the same phoneme depending on its neighbors. Biphones are models of phonemes depending on one of their neighbors; left biphones are identified by the preceding phoneme, right biphones, the following phoneme. A triphone is a model of a phoneme with a particular phoneme preceding it and a particular phoneme following it. Different speech recognition systems are often distinguished by their choice of which phonemes, biphones, and triphones they use, in addition to the topology of the HMM used to model individual phonemes[12]. In terms of recognition accuracy, there is a trade-off between using a larger number of more specific phonemes and a smaller number of more general phonemes. If properly trained, more specific phonemes can provide greater recognition accuracy. On the down side, the greater the number of phoneme models, the less training data there is for each phoneme, until ultimately some of the phoneme models would be under-trained.

An alternative approach to using phonemes as the basic building blocks of the HMM is to use words as the basic building block. The trade-off is one of flexibility versus accuracy. A phoneme based recognizer is more flexible because once the phonemes are trained, models of new words can be assembled from existing phonemes without requiring any new training. Word models can have higher recognition accuracy because they implicitly train all of the phonemes in their proper context. However, adding new word models to a recognizer requires new training (and worse, gathering new training data). Furthermore, word models are harder to train than phoneme models because they typically have a smaller training set. SpRcg's speech recognizer uses phoneme models so that applications can create new words without requiring training.

#### 2.3.2 HMM for Berkeley Hardware

This section describes a speaker independent, continuous word digit recognizer that was developed to produce models for the previous generation speech recognition hardware [13][24][25]. It serves as a case study and illustrates one implementation of a speech recognizer, (although it is somewhat different from the one currently used in spRcg). The main distinguishing features of this recognizer were its use of word models and its use of discrete output probability distribution functions.

It is important to examine this previous generation speech recognition system because its implementation uncovered the bottlenecks inherent in speech recognition hardware. Examining this system lead to the software choices described in this chapter and the hardware choices described in Chapter 6.

#### 2.3.2.1 Data and Preprocessing

Training and test data came from the TIDIGITs[28] speaker independent, connected digit corpus, which contains samples of speaker saying sentences containing between one and seven digits. Both male and female speakers were used for training and testing, but no juvenile speakers were used.

Speech data was subsampled from 20kHz to 16kHz, then processed with a mel-frequency weighted cepstral analysis, which weights frequency bands by their psychoacoustic importance. The resulting cepstral coefficients were vector quantized (VQ)[7] because the HMM used discrete output probability distribution functions. Therefore, a clustering algorithm used the training data to produce four codebooks: power, power derivative, cepstrals, and cepstral derivatives. The two cepstral codebooks have 256 entries; the power codebooks, 16.

The VQ codebooks were generated by a clustering algorithm as follows. Each vector was normalized so that all of its dimensions had the same standard deviation, so that each dimension was treated as equally important when performing vector quantization. Next, an initial codebook was selected by randomly choosing vectors from the test data. The rest of the test data was categorized according to their closest entries in the codebook; all of the data for a particular entry formed a "cluster." After all the data was categorized, the geometric center of each cluster formed the entries in a new codebook. This clustering process was repeated iteratively until the net distortion, the sum of the euclidean distances from the vectors to their nearest codeword, stopped improving.

#### 2.3.2.2 Models

The vocabulary contains twelve words: the digits "one" through "nine," as well as separate models for "oh" and "zero" (even though they represent the same digit) and an explicit model for pauses between words..(The pause model was helpful because the transcription of the data often had explicit pauses. The word models also had built in transitions, as described below, to help with brief silences between words that were not transcribed as pauses.)

Figure 2-5. 10 state HMM for the word "oh."

Figure 2-5 shows the topology of the HMM of the word "oh." The states in the middle of the model have transitions to themselves and to the state immediately following. The first and last states are intended to model silence that may or may not occur between spoken words, so there are additional transitions—to the second state and from the second to last state—to bypass the first and last states (in case there is no silence). The topologies of the other digits' models are similar, except they have more states in the middle because the words are longer and contain more sounds. All the other digits' models have 15 states, except for "zero" and "seven" which have 20 states. The explicit silence model has two states.

Each state has four output probability distribution functions, one each for the cepstrals, cepstral derivative, power, and power derivative vectors. The first two contain 256 entries; the latter two, 16 entries. Since each quantized vector has its own output PDF, each vector is modeled as being independent of the others.

#### 2.3.2.3 Training and Recognition

The models were iteratively trained using the forward backward algorithm[19] until their recognition results on the test set showed no improvement. When training on a particular sentence, the word models are assembled in the same sequence as they were spoken in the sentence. Thus, the training data must be labelled, but it does not need to be segmented because the forward-backward algorithm automatically aligns the models with the speech. For each training sentence, the same word models are re-assembled into a new sentence before training.

Unlike the training HMMs, the recognition HMM contains the word models in an almost fully connected configuration. Thus, a sentence may contain any number of words and any word may follow any other word, with one exception: the word "oh" may not follow the word "zero." This rule eliminates an otherwise frequent error by the recognizer. It has little drawback because speakers generally use only one of the two versions of the digit o in a sentence. Otherwise, the grammar is completely uniform, with all word to word transitions probabilities identical.

Testing was performed on 28583 words contained in sentences of one to seven digits. In addition to Viterbi recognition, the models also used an N-Best algorithm to detect the 5 best sentence matches. Table 2-1 shows that using the two best sentences greatly decreases

| N-Best | Number of<br>Errors | Recognition<br>Accuracy |

|--------|---------------------|-------------------------|

| 1      | 478                 | .983                    |

| 2      | 240                 | .992                    |

| 3      | 191                 | .993                    |

| 4      | 169                 | .994                    |

| 5      | 154                 | .995                    |

Table 2-1. N-best digit recognition.

the number of errors, with rapidly diminishing results with larger values of N. The number of errors is the total number of insertions, deletions, and substitutions, as determined by a dynamic programming algorithm comparing the correct answer to the recognized sentence. The model for silence is not included in the error calculations because it does not affect the meaning of the sentence.

The errors in the most likely sentence are broken down in Table 2-2. Errors are sorted by word and by type. Since substitutions involve two words, the missing word and the added word, each substitution is in the table twice: once for the missing word and once for the added word. The word "oh" caused the most problems, being responsible for almost one third of all the errors. The word "oh" is probably the most difficult to recognize in a sentence because it is so brief in duration that it is easily slurred into the pronunciation of preceeding and following words.

| Word  | Insertions | Deletions | Substitutions<br>(missing) | Substitutions<br>(added) |

|-------|------------|-----------|----------------------------|--------------------------|

| oh    | 30         | 50        | 75                         | 64                       |

| one   | 4          | 8         | 13                         | 18                       |

| two   | 0          | 13        | 40                         | 27                       |

| three | 1          | 0         | 21                         | 18                       |

| four  | 4          | 7         | 24                         | 38                       |

| five  | 13         | 3         | 48                         | 24                       |

| six   | 2          | 4         | 5                          | 10                       |

| seven | 0          | 5         | 13                         | 7                        |

| eight | 3          | 24        | 23                         | 19                       |

| nine  | 6          | 5         | 20                         | 64                       |

| zero  | 0          | 7         | 7                          | 0                        |

| Total | 63         | 126       | 289                        | 289                      |

Table 2-2. Breakdown of digit recognizer errors.

These digit models were converted to a format readable by the UCB speech recognition hardware and were used to test the functionality of the system.

### 2.4 Multi-Layered Perceptron

#### 2.4.1 Overview

Every state in an HMM has an output probability distribution function (PDF) that maps input observations into probabilities. Instead of using conventional discrete or continuous probability functions, it is also possible to use a multi layered perceptron to perform this mapping. Using an MLP is not a radical departure - it is simply another statistical technique to compute probabilities based on a large set of training data. As a statistical technique, an MLP does have some advantages as part of a speech recognition system in general and as part of a low power system in particular.

A statistical model of speech should derive as much of its content as possible from training data. Applying outside constraints is fine as long as they are based on correct assumptions. However, constraints that are imposed to make the training and recognition task more computationally tractable will reduce the overall recognition accuracy because they prevent the models from identifying certain types of patterns in the data.

The first advantage of an MLP is its lack of a priori assumptions. Other statistical methods contain built in assumptions about the form and nature of the probability distribution, even before training begins. For example, consider a discrete probability distribution based on vector quantization. Vector quantization is based on some distortion metric that determines the relative importance of the coefficients. The choice of a distortion metric might be based on past experience or good heuristics, but inevitably it will assign importance to irrelevant data in some cases because all of the coefficients do not always have the same relative importance. Models that train on this vector quantized data will be limited in their accuracy because some of the quantization was based on unimportant data; the training process has no way to correct poor assumptions that are implicit in the distortion measure. For another example, consider a continuous probability distribution function made as a mixture of gaussians. Simply the choice of using gaussians places some constraints on the possible forms the PDF can take. Furthermore, many systems use diagonal covariance matrices (that is, assume the coefficients are independent random variables) in order to limit the parameters to a manageable number. However, speech coefficients are usually not independent of each other, so using a diagonal coefficient matrix causes the loss of valuable information - information an MLP could use.

A priori assumptions about the statistics of speech have a second drawback, one that is particularly important to low power hardware design. Namely, these assumptions force the recognizer to store a large number of redundant or irrelevant coefficients. For example, consider the PDF's included in a set of biphone models of a single phoneme in different contexts. These models should be somewhat different - which, after all, is the reason for having biphones in the first place. However, they should all have a great number of similarities since they model the same phoneme. Unfortunately, each phoneme must repeat this same information in its own PDF's, which means there must be more coefficients in total than are really needed.

For a more complete discussion of MLPs and their uses in speech recognition, see[1].

#### 2.4.2 Algorithm

A Multi-Layer Perceptron (MLP) is a stateless model that produces a set of outputs based on a set of inputs. In the case of the speech recognition system, the inputs are the coefficients from a frame of speech data, as well its context, which contains the coefficients from several preceding and following frames. The outputs of the MLP correspond to  $P\langle phoneme|data \rangle$ . Because standard HMMs expect  $P\langle data|phoneme \rangle$ , the MLP output can be converted as follows:

$P\langle data|phoneme\rangle = \frac{P\langle data\rangle}{P\langle phoneme\rangle} \cdot P\langle phoneme|data\rangle$

(except standard HMM's PDFs usually do not use the context as part of their inputs).

#### **120 INPUT NODES**

Figure 2-6. Multi-layered perceptron to compute phoneme probabilities.

The MLP contains three layers: the input layer, the hidden layer, and the output layer as shown in Figure 2-6. (By convention, some call this a three layer MLP while others would call it a two layer MLP because the input layer is really just a place holder for the input coefficients.) These inputs are organized by frame, with the earliest frame's coefficients feeding the left-most inputs; the last frame's feeding the inputs on the right. For speech sampled at 8kHz, there are 5 RASTA coefficients plus their first derivative with respect to time, as well as log power and its derivative, for a total of 12 coefficients per frame. After finishing its computation, the MLP left shifts the inputs by one frame, adding a new frame to the right and eliminated the left-most (oldest) frame. Although the MLP's input spans several frames, its output probabilities are considered to correspond only to the "current" frame, with the context frames only there to help the MLP identify the current frame. Furthermore, since the hidden and output layers of the MLP are memoryless, they do not make use of the fact that the inputs are shifted frame by frame. The phoneme probabilities could be computed in any order as long as the context is presented correctly; shifting the frames is simply a convenient way to compute the probabilities.

Each node in the hidden layer performs a multiply-accumulate function, followed by a nonlinear threshold function. The network is fully connected, meaning that every input has an edge, with its own coefficient, to every node in the hidden layer. After the input nodes have been assigned their coefficients, each hidden node multiplies the value of each input node by the coefficient on the edge connecting them, then accumulates these sums. Finally, each hidden node applies the nonlinear threshold function:

$$F(x) = \frac{1}{1+e^{-x}}$$

After the hidden layer has finished its computation, the output layer computes the phoneme probabilities. The output layer performs the same algorithm as the hidden layer does, except its inputs are the outputs of the hidden layer. Since the range of the threshold function is (0,1), the nodes' outputs are already in the proper form to represent probabilities. Each output node corresponds to a specific phoneme. The hidden nodes, in contrast, are not assigned any fixed representation; their "meanings" are determined automatically during training. As shown in Figure 2-6, the MLP in spRcg uses 120 input coefficients (from a 10 frame context), 120 hidden nodes, and 49 outputs. Larger MLPs give higher recognition accuracies, but this size MLP was chosen as a comprimise for ease of implementation in hardware and for computational complexity on a workstation.

#### 2.4.3 Training

The MLPs create their coefficients by training on a large set of speech data that has been phonetically labeled. In brief, training is as follows: For each frame of speech, the correct answers are presented at the outputs. The MLP then alters coefficients in a way that reduces the error, the difference between the computed output and the correct answer. This training algorithm is called error back propagation (EBP).[20]

SpRcg's MLPs were trained on the TIMIT training set, which contains 462 speakers saying 8 sentences each. This database is well suited to training MLPs because its data has already been segmented and phonetically transcribed. Furthermore, it contains a large number of American English speakers, grouped by dialect region, speaking a large number of words.

After each training iteration, the MLPs were cross validated against a test set by measuring their frame-by-frame phoneme identification. During the course of training, the gain term in the EBP was multiplied by 0.93 after each iteration. Training the MLP with 120 input and 120 hidden nodes took 40 iterations.

#### 2.4.4 Results

Table 2-3 shows the results of the MLP identifying phonemes frame by frame on the the TIMIT test set, which contains 168 speakers saying 8 sentences each. The first column is the name of the phoneme. The next three columns show the number of frames correctly identified, the total number of frames, and the percent correct on a frame by frame basis.

The first row of Table 2-4 shows the overall results of the MLP's frame-by-frame classification of phonemes. (When computing the score in Table 2-4, several sets of phonemes were considered equivalent, as described in [11]. Namely, ax and ah, ix and ih, aa and ao, zh and sh, en and n, el and l; and epi, vcl, cl and sil.) Usually, when the MLP's highest

| Phoneme | Correct | Total | Score   |

|---------|---------|-------|---------|

| b       | 885     | 1564  | 0.56586 |

| d       | 609     | 2030  | 0.30000 |

| dx      | 1279    | 1826  | 0.70044 |

| g       | 438     | 1323  | 0.33107 |

| р       | 2324    | 4217  | 0.55110 |

| t       | 3387    | 6704  | 0.50522 |

| k       | 3742    | 6250  | 0.59872 |

| q       | 2660    | 5852  | 0.45455 |

| cl      | 18934   | 24970 | 0.75827 |

| vcl     | 8155    | 14252 | 0.57220 |

| jh      | 1001    | 1880  | 0.53245 |

| ch      | 1275    | 2249  | 0.56692 |

| S       | 14400   | 24876 | 0.57887 |

| sh      | 3592    | 5579  | 0.64384 |

| Z       | 4898    | 10629 | 0.46081 |

| zh      | 58      | 636   | 0.09119 |

| f       | 4737    | 9399  | 0.50399 |

| th      | 106     | 2255  | 0.04700 |

| v       | 1114    | 4229  | 0.26342 |

| dh      | 749     | 3332  | 0.22479 |

| m       | 4141    | 9106  | 0.45476 |

| n       | 5641    | 12712 | 0.44375 |

| ng      | 951     | 2474  | 0.38440 |

| en      | 528     | 1656  | 0.31884 |

| 1       | 4117    | 11511 | 0.35766 |

| r       | 4845    | 10811 | 0.44815 |

| w       | 3483    | 5856  | 0.59477 |

| у       | 1034    | 2132  | 0.48499 |

| hh      | 1755    | 3824  | 0.45894 |

Table 2-3. MLP output scoring by phoneme.

| Phoneme | Correct | Total | Score   |

|---------|---------|-------|---------|

| el      | 1584    | 3171  | 0.49953 |

| iy      | 12620   | 16735 | 0.75411 |

| ih      | 3602    | 11213 | 0.32123 |

| eh      | 2642    | 11272 | 0.23439 |

| еу      | 5397    | 10604 | 0.50896 |

| ae      | 4748    | 10458 | 0.45401 |

| aa      | 2421    | 10691 | 0.22645 |

| aw      | 1435    | 3750  | 0.38267 |

| ay      | 7424    | 10982 | 0.67602 |

| ah      | 2210    | 7756  | 0.28494 |

| ao      | 4268    | 9257  | 0.46106 |

| оу      | 667     | 2242  | 0.29750 |

| ow      | 2416    | 7859  | 0.30742 |

| uh      | 198     | 1655  | 0.11964 |

| uw      | 2201    | 5564  | 0.39558 |

| er      | 8848    | 16349 | 0.54120 |

| ax      | 2318    | 6880  | 0.33692 |

| ix      | 4123    | 13035 | 0.31630 |

| sil     | 40657   | 47168 | 0.86196 |

| ері     | 767     | 1387  | 0.55299 |

Table 2-3. MLP output scoring by phoneme.

| Nth Best | Fraction<br>Correct |

|----------|---------------------|

| 1        | 0.56225             |

| 2        | 0.71125             |

| 3        | 0.78605             |

| 4        | 0.83243             |

| 5        | 0.86457             |

Table 2-4. MLP Nth best results.

probability output was not the correct phoneme, the correct output was still one of the few highest outputs. The subsequent rows show how often the correct phoneme was among the N highest outputs, for different values of N.

# 2.5 Clustered Grammar

#### 2.5.1 Grammar Bottleneck

As described in Chapter 5 and [3][4][5], the key to designing low-low power hardware is the ability to break up an algorithm into small, local, slowly running, parallel elements. Within an HMM, the grammar poses the biggest bottleneck while trying to parallelize the Viterbi search algorithm. Ideally, the task of recognizing speech with a large vocabulary model should be split over many individual processors, each searching through a subset of the overall vocabulary. Each of these processors would have modest speed requirements, and hence could operate at low voltages. Furthermore, each processor could have its own low power memories on-chip, greatly reducing interconnect capacitance, and hence power consumption. When performing a viterbi search within a phoneme or within a word model, all transitions are to a well defined set of nearby states, so the algorithm can easily be split.

However, the problem occurs at the grammar level, i.e. transitions between words. One of the most common statistical grammars, the bigram grammar, uses transitions between every pair of words. Thus, for a vocabulary of N words, there are N<sup>2</sup> transitions to be processed. For large vocabularies, this grammar processing will be the bottleneck. For example, in the UCB hardware system (see Section 2.3.2 and Section 6.2), grammar processing was the greatest bottleneck.

Word-pair grammars, which list all possible successors for a given word, can have a much lower number of edges. Thus, they are more suitable for a low power system. However, word-pair grammars are not ideal because they can have irregular structures. Since any word can still potentially connect to any other word, and to any number of other words, hardware devoted to grammar processing must retain a great deal of flexibility. In hardware design, flexibility means added size and complexity - hence it means added power consumption.

#### 2.5.2 Breaking the Bottleneck

The spRcg speech recognition system uses a clustered grammar, which can be considered a transformed version of the word-pair grammar. The clustered grammar gets its name

Figure 2-7. Hierarchy in the HMM.

because it requires each word in the vocabulary to be a member of one or more clusters. Grammar transitions occur between clusters, not between words.

Figure 2-8. Clustered grammar reduces complexity.

As shown in Figure 2-8, a bigram grammar can be transformed into a clustered grammar, greatly reducing the number of edges and hence reducing both the computational complexity and the amount of memory needed. Furthermore, since the bigram and clustered grammars are topologically equivalent, clustering the grammar causes no loss in recognition accuracy.

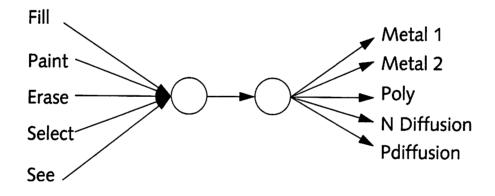

Clusters group words that are used interchangeably in the grammar. At the most general level, a cluster might represent a part of speech - noun, verb, adjective, etc. More specifically, words in a cluster will probably share more semantic similarities. For example, Figure 2-9 shows two clusters used in a vocabulary for an integrated circuit layout editing program. The cluster on the right contains various layers of an integrated circuit; on the left, possible actions that can be performed on layers.

Clustering does not impose a severe restriction on grammars. In fact, for the intended use of the spRcg speech recognizer—command and control of applications—clusters are a natural and easy way to create grammars. Languages for interacting with computer applications, as compared with natural languages - have highly regular grammars. First of all, programmers tend to create regular languages because they are easy to parse. Secondly, many speech commands to programs will duplicate menu functions, which are themselves regular and hierarchical.

### 2.5.3 Programming With Clusters

Furthermore, a clustered grammar fits well into an object oriented programming scheme. (See Chapter 4 for more on programming with spRcg.) One of the key attributes of object oriented programming is inheritance: when a new class is created, it can inherit properties and functions from one or more parent classes. The advantage of inheritance are extensibility - new classes can be added without having to rewrite a lot of existing code - and simplicity - by inheriting properties and data, new classes don't need to duplicate existing code.

For example, consider a programmer who must add capabilities for a third layer of metal to an integrated circuit layout editor. In an object oriented program, much of the work can be done by inheritance, since most of the properties of metal 3 are similar to the properties of other layers, in particular to the metal 2 layer. Thus, hypothetically, the program might have a Metal3 class that is a descendant of the EditableLayer class and the Wiring-Layer class.

What does this have to do with speech recognition? For a speech controlled program, the programmer must also add the words "metal three" to the appropriate places in the vocabulary. Since the programmer just added the word to the program, s/he probably doesn't have a large sample of training data to determine the proper bigram probabilities. Thus, using a bigram grammar is often not practical for applications programmers. Rather, the ideal situation is for the new word to be placed automatically into the proper grammar clusters as determined by its inheritance. For example, "metal three" would be inserted into the cluster shown in Figure 2-9 because of its inheritance from the EditableLayer class, and presumably would be inserted into other clusters appropriate to a member of the WiringLayer class.

Figure 2-9. Example of a grammar cluster.

Using this paradigm, grammar clusters correspond to object oriented classes. The words in a cluster can be children of that class. Alternatively they can be class member functions (such as fill, paint, erase, etc.).

Furthermore, by using instances of an object as members of a grammar cluster, the program can easily change its grammar while it is running to reflect new data. For an example of this technique, see the discussion of adding bookmarks to a world wide web browser application.

The grammar clusters themselves are not states in the HMM: they do not have output probabilities and there is no delay in traversing them. Rather, they are abstract place-holders like the start and end nodes in the word models.

Each cluster is instantiated twice in the HMM, once in the first layer, once in the second layer. Clusters in the first layer collect transitions from their member words, keeping the transition with the largest probability (in accordance with the Viterbi algorithm). Only after the frame has been processed, are the transitions computed from clusters in the first layer to clusters in the second layer, again according to the Viterbi algorithm. During the next frame, when a word starts, it receives its starting probabilities as stored in its clusters in the second layer. Thus, the first layer of cluster instances collect word ending transitions from the current frame, while the second layer of clusters store word ending transitions from the previous frame.

# 2.6 Recognition Results

Table 2-5 shows recognition results of the spRcg system on the TIDIGITs database using most likely pronunciation models. The higher error rates compared with Table 2-1 reflect the general purpose nature of the spRcg system. Namely its use of phonemes instead of word models and the fact that the phonemes where not trained on digits. Furthermore, the spRcg system uses 8 kHz sampling, compared to 16 kHz for the system of Table 2-1. Other work [14] has shown that a hybrid speech recognitions system similar to spRcg's can achieve as low as 0.9% error if it is trained on the TIDIGITs database itself.

It is also interesting to note that almost half of the errors involved the digit "nine." This suggests that a better pronunciation model for "nine" would have significantly improved the error rate. It also suggests that a pronunciation adaptation scheme, such as the one described in Section 3.2.3, could produce large improvements by allowing the user to correct a few problem words.

|           | N-Best | Number of<br>Errors | Recognition<br>Accuracy |  |

|-----------|--------|---------------------|-------------------------|--|

|           | 1      | 2092                | 0.85                    |  |

| Male      | 2      | 1851                | 0.87                    |  |

| //iaic    | 3      | 1791                | 0.87                    |  |

|           | 4      | 1462                | 0.90                    |  |

|           | 1      | 4038                | 0.72                    |  |

| Female    | 2      | 3814                | 0.74                    |  |

| I CITICIC | 3      | 3765                | 0.74                    |  |

|           | 4      | 3333                | 0.77                    |  |

Table 2-5. N-best digit recognition using spRcg.

The difference in recognition accuracy between men and women is hard to understand because the MLP was trained on both male and female speakers.

Table 2-6 shows percent error rates from a user test of three males and one female speaking typical command to navigate the World Wide Web browser described in Section 3.3.1. The subjects first performed the test, which consisted of 38 sentences, using the standard pronunciations, then repeated the test after customizing the pronunciations by speaking each word in the vocabulary once (using the widget described in Section 3.2.3). The numbers in the table reflect whether the entire command was correctly recognized.

| Speaker | Nth Best Task Error Rate (Percent) |    |    |            |    |    |    |    |

|---------|------------------------------------|----|----|------------|----|----|----|----|

|         | No customization                   |    |    | Customized |    |    |    |    |

|         | 1                                  | 2  | 3  | 4          | 1  | 2  | 3  | 4  |

| AB      | 16                                 | 5  | 3  | 3          | 21 | 11 | 5  | 5  |

| SS      | 26                                 | 13 | 8  | 8          | 24 | 18 | 13 | 13 |

| JC      | 34                                 | 29 | 24 | 18         | 21 | 18 | 18 | 18 |

| AS      | 34                                 | 21 | 18 | 13         | 18 | 13 | 11 | 11 |

| Average | 28                                 | 17 | 13 | 11         | 19 | 15 | 12 | 12 |

Table 2-6. SpRcg user test results.

The initial pronunciations were chosen to work well with the programmer (AB), so customization did not help for that subject. For the other subjects, customizations showed varying degrees of improvement in the first recognition result. In an actual application, the users would use the customizer to improve only those words that caused the most recognition errors, so recognition accuracy should go up with continued use.

A large proportion of the errors involved misrecognition of digits. So this test, along with the TIDIGIT test, suggests that future improvements should go towards improving digit recognition.

## 2.7 Summary

This chapter described the components of a speech recognizer in general, and the specific choices that were made for the spRcg speech recognition system. Most of the algorithms chosen—RASTA-PLP, Multi-Layer Perceptrons, and Hidden Markov Models—were chosen because they are both commonly used algorithms and are well suited to low-power hardware implementations. However, one part of the Hidden Markov Models—the grammar—had to be modified because it was the limiting factor in parallelizing the Viterbi algorithm.

# **3** SOFTWARE: USER INTERFACE AND APPLICATIONS

SpRcg provides a complete toolkit for incorporating speech recognition into applications programs. This chapter describes the components of spRcg's toolkit that are seen by the user, as well as applications that were written using this toolkit. The internal programming details of the toolkit are discussed in Chapter 4.

## 3.1 Goals

### 3.1.1 Creating a User Interface

The spRcg system's toolkit provides a standard user interface for all applications using speech recognition. Writing the demonstration applications helped to test the implementation of the toolkit and also gave feedback on what should be changed. Writing the applications also helped to develop the programming interface to the toolkit, described in Chapter 4.

### 3.1.2 Ease of Use

These applications and mega-widgets represent the first generation user interface for Info-Pad. As such, they provide valuable feedback from users on what constitutes a good user interface. As users work for the first time on computers without keyboards, they learn what sorts of feedback they require from applications that rely on recognition.

# 3.1.3 Enabling and Demonstrating InfoPad

In addition to demonstrating speech recognition, these applications are intended to demonstrate and test all of InfoPads capabilities, as well as making the InfoPad a useful, user friendly device. The World Wide Web browser in particular demonstrates the InfoPad's network connectivity and multimedia capabilities. The Web itself represents the (current) epitome of network connectivity and network based data access. The browser uses every form of InfoPad's input and output: handwriting recognition and speech recognition input, text, graphics, audio, and video output.

# 3.2 Widgets in the SpRcg Toolkit

### 3.2.1 Answer Widget

The spRcg\_NBestDisplay. provides feedback to the user about the speech recognizers

Figure 3-1. spRcg\_NBest widget.

NBest answers. If the recognizer never made mistakes, there would be no reason to display its output as text: the user already knows what s/he said, so the program should execute the user's command. However, if the recognizer occasionally misrecognizes or is unable to recognize a sentence, it is helpful to give the user feedback about what went wrong, as well as a way to correct the mistake. First of all, it reduces a user's frustration if s/he can see the mistake, rather than having to infer that the recognizer made an error based on its actions. Also, some recognition results might not have a visible effect. Thus the feedback allows the user to confirm whether the program executed the right command. Even better, spRcg\_NBestDisplay, can help the user correct recognition errors. With an NBest recognizer, if the first answer is incorrect, the correct answer is often one of the other possible sentences identified by the recognizer. If this is the case, the user can click on the correct response, causing the wrong answer to be undone, and the correct answer to be executed.

Providing textual output also helps the user adjust volume, silence, and garbage word settings. The user can quickly see if there are a lot of "not recognized" responses or if sentences are being cut off in the beginning or end and can adjust levels accordingly.

#### 3.2.2 Control Panel

The spRcg\_controller contains five sliders and two bars for controlling and displaying user-setable parameters.

| Recording Status: off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| garbage threshold<br>0.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| silence duration (250–2500<br>500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |