# Copyright © 1996, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# PROCESS VARIABILITY AND DEVICE MISMATCH

by

Manolis Terrovitis

Memorandum No. UCB/ERL M96/29

28 May 1996

# PROCESS VARIABILITY AND DEVICE MISMATCH

by

**Manolis Terrovitis**

Memorandum No. UCB/ERL M96/29

28 May 1996

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering

University of California, Berkeley

94720

# Acknowledgments

I wish to express my sincere gratitude to my research advisor Professor Costas J. Spanos for his support and guidance during this research. I am also grateful to Professor Robert G. Meyer for being a second reader of this thesis.

Many thanks are owed to Dr. Augustin Ochoa, formerly with ABB HAFO, Inc. for his substantial contribution to this project with many valuable discussions and suggestions. I thank Shehqing Fang and Guobin Wang of the Berkeley Microfabrication Laboratory for fabricating the test structures. I am also thankful to the Berkeley Microfabrication Laboratory for providing and supporting the testing equipment.

Finally I wish to thank my fellow graduate students and the rest members of the BCAM group. I am particularly grateful to Mark Hatzilambrou for many useful discussions on this research and for helping me to tapeout the layout. My thanks are extended to Rowen Chen, Herb Huang, Anna Ison, Nickhil Jakatdar, Jeff Lin, David Mudie, Xinhui Niu and Crid Yu, as well as the former BCAM students Eric Boskin, Tony Miranda, Sean Cunningham, Sherry Lee, Sovarong Leang, Dave Rodriguez and Shang-Yi Ma for providing a cooperative and supporting environment.

This work has been funded by ABB HAFO, Inc. and by the State of California MICRO program.

# **Abstract**

The different types of process variability that cause device mismatch are investigated. A model that relates the variance of mismatch with the area of the devices and the distance between them, presented for MOS transistors by M. Pelgrom et. al.[11] is adopted. It is rederived in order to examine how it could be extended to small dimension devices. Since the mechanisms that cause mismatch are the same for many different kinds of devices, modeling is examined first in general terms and then applied to individual devices. Translation of mismatch into circuit performance degradation is presented for some commonly used simple circuits.

A broad set of test structures was fabricated in the Baseline Process of the Berkeley Microfabrication Laboratory in order to: a) find the coefficients of the model discussed above, b) examine mismatch introduced by different environments around the devices and experimentally find the size and number of dummy devices needed for good matching, c) examine the effect of orientation on mismatch, and d) measure performance degradation in some simple circuits and compare with the predicted by circuit analysis. Results obtained by statistically processing electrical measurements are presented.

# **Table Of Contents**

| Chapter 1 | : Introduction                                            | 1  |  |  |

|-----------|-----------------------------------------------------------|----|--|--|

| 1.1       | Overview                                                  | 1  |  |  |

| 1.2       | Process Parameter Variability                             |    |  |  |

| 1.3       | Circuit Performance Variation                             |    |  |  |

| 1.4       | Thesis Organization                                       |    |  |  |

| Chapter 2 | : Theory of Mismatch                                      | 6  |  |  |

| 2.1       | Introduction                                              | 6  |  |  |

| 2.2       | Derivation of the Mismatch Model                          |    |  |  |

|           | 2.2.1 "Local value" of a Process Parameter                |    |  |  |

|           | 2.2.2 Local and Global Variation                          |    |  |  |

|           | 2.2.3 Mismatch Introduced by Local Variation              |    |  |  |

|           | 2.2.4 Mismatch Introduced by Global Variation             |    |  |  |

|           | 2.2.5 Total Mismatch Model                                |    |  |  |

| 2.3       | Specific Device Mismatch Models                           |    |  |  |

|           | 2.3.1 Resistors                                           |    |  |  |

|           | 2.3.2 Capacitors                                          |    |  |  |

|           | 2.3.3 Transistors                                         |    |  |  |

| 2.4       | Device Parameters of Small Dimension Devices              |    |  |  |

| 2.5       | An Extension of the Mismatch Model of a Process Parameter |    |  |  |

| 2.6       | Comments on the Extension of the Model                    | 30 |  |  |

| Chapter 3 | : Mismatch and Circuit Performance                        | 31 |  |  |

| 3.1       | Introduction                                              | 31 |  |  |

| 3.2       | Current Mirror                                            | 31 |  |  |

| 3.3       | Differential Pair                                         | 34 |  |  |

| 3.4       | D/A converter                                             | 36 |  |  |

| Chapter 4 | : Test Structures                                         | 40 |  |  |

| 4.1       | Introduction                                              | 40 |  |  |

| 4.2       | General Information                                       | 40 |  |  |

| 4.3       | Resistor Structures                                       | 43 |  |  |

|           | 4.3.1 Resistor Arrays for Edge Effects Observation        |    |  |  |

|           | 4.3.2 Polysilicon Resistor Mismatch Model                 | 44 |  |  |

|           | 4.3.3 N-Diffusion Resistor Mismatch Model                 |    |  |  |

|           | 4.3.4 P-Diffusion Resistor Mismatch Model                 |    |  |  |

|           | 4.3.5 Vertical Resistors                                  |    |  |  |

| 4.4       | Capacitor Structures                                      | 50 |  |  |

|            | 4.4.1                   | Capacitor Arrays for Edge Effect Observation | 50 |  |

|------------|-------------------------|----------------------------------------------|----|--|

|            | 4.4.2                   | Capacitor Mismatch Model                     | 51 |  |

| 4.5        | Transistor Structures   |                                              | 53 |  |

|            | 4.5.1                   | Two Dimensional Transistor Arrays            | 53 |  |

|            | 4.5.2                   | NMOS Transistor Mismatch Model (Group A)     | 54 |  |

|            | 4.5.3                   | NMOS Transistor Mismatch Model (Group B)     | 56 |  |

|            | 4.5.4                   | PMOS Transistor Mismatch Model (Group A)     | 57 |  |

|            | 4.5.5                   | PMOS Transistor Mismatch Model (Group B)     | 58 |  |

|            | 4.5.6                   | Orthogonal Experiment with NMOS Transistors  | 58 |  |

|            | 4.5.7                   | Orthogonal Experiment with PMOS Transistors  | 60 |  |

| 4.6        | Simple                  | e Circuits                                   | 61 |  |

|            | $4.6.\bar{1}$           | Differential Pairs                           | 61 |  |

|            | 4.6.2                   | Operational Amplifier                        | 63 |  |

| Chapter 5: | Meas                    | urements                                     | 66 |  |

| 5.1        | Introd                  | uction                                       | 66 |  |

| 5.2        | Equip                   | ment                                         | 66 |  |

| 5.3        | Measurement Methodology |                                              | 66 |  |

|            | 5.3.1                   | Resistors                                    |    |  |

|            | 5.3.2                   | Capacitors                                   |    |  |

|            | 5.3.3                   | Transistors                                  |    |  |

|            | 5.3.4                   | Differential Pairs and OPAMP                 | 70 |  |

| 5.4        | Measu                   | arement Problems                             | 71 |  |

| 5.5        | Resist                  | or Results                                   | 72 |  |

|            | 5.5.1                   | Resistor Arrays Edge Effects Observation     | 72 |  |

|            | 5.5.2                   | Polysilicon Resistor Mismatch Model          | 74 |  |

|            | 5.5.3                   | N-Diffusion Resistor Mismatch Model          | 77 |  |

|            | 5.5.4                   | P-Diffusion Resistor Mismatch Model          | 79 |  |

|            | 5.5.5                   | Vertical Resistors                           | 80 |  |

| 5.6        | Transi                  | istor Results                                |    |  |

|            | 5.6.1                   | PMOS Transistors Mismatch Model              | 81 |  |

|            | 5.6.2                   | Orthogonal Experiment with PMOS Transistors  | 86 |  |

| Chapter 6: | Conc                    | lusions and Future Work                      | 87 |  |

| 6.1        | Introd                  | luction                                      | 87 |  |

| 6.2        | Experiment Overview87   |                                              |    |  |

| 6.3        | Future                  | e Plans                                      | 88 |  |

| References |                         |                                              | 90 |  |

1

# Introduction

#### 1.1 Overview

The increasing requirement for a higher degree of integration and faster circuits, pushes the semiconductor industry to fabricate devices with ever smaller dimensions. Despite the sophisticated equipment used, we have limited control in processing structures so minute, and large variability in the process characteristics is introduced. The process variability causes circuit performance variability with obvious economic impact. In this thesis we attempt to acquire some insight on process variation and we focus on the variation of the behavior of identically designed devices.

This first chapter provides a short overview of the problem and presents a summary of the methods developed to cope with it. Finally the thesis organization is presented.

# 1.2 Process Parameter Variability

Integrated circuits consist of a number of interconnected devices (mainly Bipolar and FET transistors, resistors, and capacitors) on a silicon substrate. The devices are formed after a series of processing steps such as oxidation of silicon, deposition of metal or other materials, implantation, selective etching, etc. For the sake of simulation, the behavior of the devices can be modeled as a combination of circuit components such as ideal resistors, capacitors, inductors, and independent and dependent voltage and current sources. The value of each one of these components is a function of a set of variables called *device* parameters. Examples of device parameters are the threshold voltage of FET transistors, the device dimensions, the sheet resistance of a polysilicon line, etc. The value of each device parameter depends on physical quantities called process parameters. Examples of

process parameters are the thickness of the silicon oxide, the concentration of doping atoms in the silicon etc. The border between the device parameters and the process parameters is not firmly drawn. For example, the thickness of the oxide and the device dimensions can be considered both device and process parameters. The relation between process and device parameters is not explicit because it depends on factors that cannot be described with a single number, such as doping profiles, and in some cases the mechanism is not very well understood. Some of the models that circuit simulators such as SPICE use to accurately describe the devices are very complex, and some of the device parameters that they use have physical interpretations, while others do not and are empirically introduced. Generally, the device parameters of the accurate models are chosen to better match measurements of the actual device using optimization routines, rather than given as an explicit function of the process parameters [5].

The physical process parameters in a fabrication line are subject to variation. Systematic components of variation can be found across the die, across the wafer and across a whole batch. An attempt to assign different components of the variation to different pieces of the equipment has been presented before [6]. Some of the causes of variation are:

- Nonuniform implantation.

- Nonuniform deposition of a material such as photoresist, polysilicon, oxide and metal.

- Optical effects of the stepper such as diffraction, because the wavelength of the light source used is comparable to the size of the printed geometries.

- Different etching rate because of varying environment.

- Edge roughness because of etching imperfections.

- Polysilicon granularity.

- Variations of temperature, pressure, and concentration of gas in the furnace, which cause nonuniform oxidation and diffusion.

- Variation of the conditions in the plasma etching chamber, which cause non uniform plasma etching.

Chapter 1 3

- Misalignment.

- Recipe modification.

- Interruption of operation of the equipment because of maintenance or cleaning.

Statistical Process Control when properly used can greatly reduce variation and increase the efficiency of the fabrication line [7]. However, it is impossible to eliminate it completely. The unavoidable variation of the physical process parameters causes variation of the device parameters and deviation form the target values. This in turn results in variation of the circuit performance.

## 1.3 Circuit Performance Variation

Yield is defined as the percentage of the manufactured circuits that are functional and satisfy the performance specifications. There are two factors that determine the yield, the catastrophic failures and the process variation as described in Section 1.2. The part of the yield associated with each one of those is called catastrophic yield and parametric yield respectively. Catastrophic failures are caused either by random defect spots on the wafer that result in short-circuits and open-circuits, or by failure in the operation of specific structures such as contacts or vias. The catastrophic yield is usually dominant.

It is desirable to design circuits in a way that maximizes the parametric yield. A designer's experience and intuition is needed to find a robust topology that minimizes the effect of the process fluctuation on the performance. The sensitivity of a performance F to a process or device parameter p, defined as

$$S_p^F = \frac{dF/F}{dp/p} \tag{1.1}$$

has been used extensively as a measure of the effect of this parameter to the performance. However, combinations of variations among different parameters are often significant. A direct estimation of the parametric yield using the statistics of the process variation is needed. Furthermore, it is often desirable to optimize the design by changing the nominal values of the device parameters over which the designer has control (i.e., the dimensions

Chapter 1 4

of the devices) in order to maximize the parametric yield. This is referred to as design centering.

Several methods for the estimation of the parametric yield and the optimization of the design have been suggested [1]. Deterministic methods exhaustively explore the process parameter or device parameter space and have the basic disadvantage that the number of simulations needed increases exponentially with the number of the parameters. This is also known as 'the curse of dimensionality' and makes deterministic methods impractical for large circuits. Statistical methods on the other hand are based on the Monte Carlo analysis in which we repeatedly select random values for the device parameters and perform simulation. Using the actual distribution of the device parameters, emulates a pilot run in the production line. The basic advantage of the Monte Carlo analysis is that the number of simulations needed for a stipulated accuracy is independent of the number of the parameters. The accuracy, however, increases only with the square root of the number of the simulations.

Even though Monte Carlo analysis is much more efficient than the deterministic methods, the computational load required for large circuits is still impractical if high yield prediction accuracy is needed. A solution to this problem is to replace the whole circuit or a noncritical part of it with a behavioral model [3], [4]. This greatly diminishes the computational cost since the evaluation of the response of the behavioral model is much faster than the simulation. However, the use of behavioral models limits the generality of the method and reduces the accuracy of the parametric yield estimation. There exists a trade off between the generality and accuracy on the one side and the computational load on the other. The experience and intuition of the circuit designer can identify the weaknesses and the mechanisms of failure of the circuit and facilitate the statistical analysis.

Identically designed devices are often laid out close together. The proper operation of the circuit requires that they behave identically. Often the value of the device parameters is not as important for the performance as the matching among these devices. The difference in the value of a device parameter among identically designed devices is called *mismatch*.

It is related to the relative variation among the devices as opposed to the total variation over a wafer or a whole batch. Examples of circuits that need matched devices are current mirrors, where device mismatch results in current mismatch; the input differential stage of an OPAMP, where mismatch results in input offset; and many kinds of A/D converters, where mismatch introduces nonlinearities; multiplexers, etc. The subject of this thesis is the examination of the device mismatch using a set of test structures.

## 1.4 Thesis Organization

This thesis is organized as follows. Chapter 2 presents some theoretical background about device mismatch. It includes characterization and modeling of mismatch for MOS transistors, resistors and capacitors. Chapter 3 describes how knowledge of the statistics of mismatch can be translated to knowledge of the performance variation. Chapter 4 describes the test structures that were designed and fabricated in the Berkeley Microfabrication Laboratory in order to measure mismatch. Finally Chapter 5 describes measurement methodology and analysis of the data, and Chapter 6 presents the conclusions.

# **Theory of Mismatch**

## 2.1 Introduction

In this chapter we present some theoretical background about mismatch which is based mainly on [11] by Pelgrom et. al., but also on [8], [12] and [13]. While in [11], a mismatch model is derived in the spatial frequency domain, here we work in the distance domain. At the end of the chapter a possible extension of the derived models to small dimension devices is discussed.

## 2.2 Derivation of the Mismatch Model

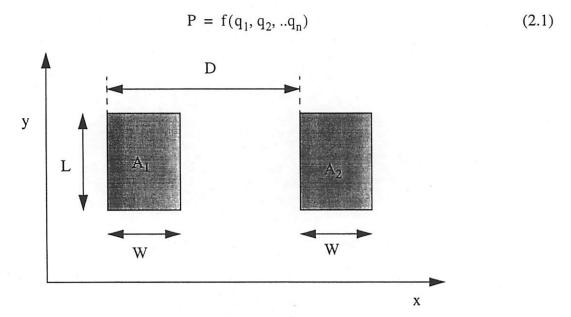

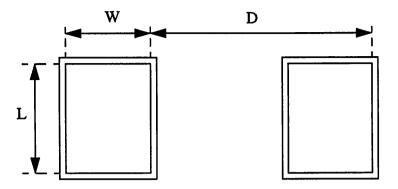

Consider a pair of identically designed rectangular devices, with dimensions W by L in distance D, as shown in Figure 2.1. Generally a device parameter P is a function of the local value of n process parameters  $q_1, q_2, ..., q_n$ .

Figure 2.1 A pair of identically designed devices.

The mismatch in the device parameter P between the two devices is given by equation (2.2).

$$\Delta P \cong \frac{\partial f}{\partial q_1} \Delta q_1 + \frac{\partial f}{\partial q_2} \Delta q_2 + \dots + \frac{\partial f}{\partial q_n} \Delta q_n , \qquad (2.2)$$

where  $\Delta q_i$ , represents the mismatch in the local value of the process parameter  $q_i$ .

Parameters  $q_i$  represent physical quantities such as implanted ion concentration, thickness of the oxide and dimensions of the devices. Because they are introduced by different mechanisms such as implantation, oxide growth, and etching of material, they can usually be considered uncorrelated. The mismatch in the device parameter P is a random variable whose variance can be expressed as

$$\sigma_{\Delta P}^{2} = \left(\frac{\partial f}{\partial q_{1}}\right)^{2} \sigma_{\Delta q_{1}}^{2} + \left(\frac{\partial f}{\partial q_{2}}\right)^{2} \sigma_{\Delta q_{2}}^{2} + ... + \left(\frac{\partial f}{\partial q_{n}}\right)^{2} \sigma_{\Delta q_{n}}^{2} . \tag{2.3}$$

If for some reason some of the  $q_i$  are correlated, correlation terms should be introduced in equation (2.3).

#### 2.2.1 "Local value" of a Process Parameter

We referred above to the local value of the process parameter in the device as a single number, but this is actually a function of the position within the device  $q_i(x, y)$ . It would be more rigorous to refer to the *effective value of*  $q_i$  in the device, and define this as the constant value of  $q_i$ , which would give the same value for P as the function  $q_i(x, y)$ , when the nominal values are used for the rest of the process parameters. It is reasonable to assume that this effective value is close to the average value of  $q_i(x, y)$ , in the area of the device, as given by the equation

$$q_{i,eff} = \overline{q_i} = \frac{1}{WL} \int_{0}^{WL} \int_{0}^{Q} q_i(x, y) dx dy . \qquad (2.4)$$

If  $q_i$  represents a dimension of the device, for example the length L, it is again reasonable to assume that the effective L is the average of L(x) across the width, as given below:

$$L_{\text{eff}} \cong \overline{L} = \frac{1}{W} \int_{0}^{W} L_{i}(x) dx$$

(2.5)

In order to support this claim with an example, we examine the effective value of the thickness of the oxide when the device parameter of interest is the capacitance of a poly 1 - poly 2 capacitor. The relation between the effective value of the thickness of the oxide  $t_{ox,eff}$  and  $t_{ox}(x, y)$ , which is the function of position, is

$$\varepsilon_{\text{ox}} W L \frac{1}{t_{\text{ox,eff}}} = \int_{0}^{WL} \int_{0}^{\infty} \varepsilon_{\text{ox}} \frac{1}{t_{\text{ox}}(x, y)} dx dy, \qquad (2.6)$$

where  $\varepsilon_{ox}$  is the dielectric constant of the silicon oxide. We express  $t_{ox}(x, y)$ , as follows

$$t_{ox}(x, y) = \overline{t_{ox}} + \omega(x, y), \qquad (2.7)$$

where

$$\overline{t_{ox}} = \frac{1}{WL} \int_{0.0}^{WL} t_{ox}(x, y) dx dy.$$

(2.8)

The value of  $\omega(x, y)$ , which represents the variation around the average, is a small portion of the average  $\overline{t_{ox}}$ , and we can write

$$\iint_{0}^{WL} \varepsilon_{ox} \frac{1}{\overline{t_{ox}} + \omega(x, y)} dx dy \cong \varepsilon_{ox} \frac{1}{\overline{t_{ox}}} \iint_{0}^{WL} \left(1 - \frac{\omega(x, y)}{\overline{t_{ox}}}\right) dx dy = \varepsilon_{ox} WL \frac{1}{\overline{t_{ox}}} . \quad (2.9)$$

From (2.9) and (2.6) follows that

$$t_{\text{ox eff}} \cong \overline{t_{\text{ox}}}$$

(2.10)

#### 2.2.2 Local and Global Variation

We are proceeding with an estimation of the quantities  $\sigma_{\Delta q}^2$  of the equation (2.3). The difference in the effective value of the process parameter q, as given in (2.4) is

$$\Delta q = \frac{1}{A} \left[ \int_{A_1} q(x, y) dx dy - \int_{A_2} q(x, y) dx dy \right], \qquad (2.11)$$

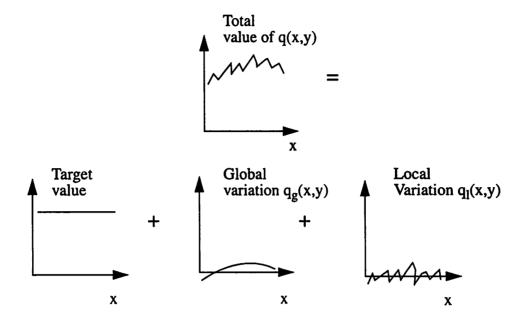

Figure 2.2 Decomposition of value of a process parameter into different components.

where  $A_1$  and  $A_2$  are the areas of the two devices as shown in Figure 2.1 and A=WL is the common magnitude of these areas.

There are two kinds of variation in the process parameters that cause mismatch. The first is short correlation distance variation, where the value of the process parameter at one point is uncorrelated with its value at any other point located further than a distance much smaller than the dimensions of the device. This kind will be referred to as local variation also. The spatial frequency spectrum of this component covers the whole spectrum and resembles white noise. Examples of mechanisms that cause short correlation distance variation are the grain nature of the polysilicon, the distribution of the oxide charges under the transistor gate, the distribution of ion-implanted, diffused or substrate ions, the local mobility fluctuations and the edge roughness. The second kind of process parameter variation is large gradients of variation across the wafer and will also be referred to as global variation. The spectrum of this component contains only low spatial frequencies. The two components are caused by different mechanisms and are uncorrelated. For example the global variation in the oxide thickness of poly1-poly2 capacitors is caused by temperature

or gas concentration variation across the surface of the wafer during oxidation, while the local variation is due to the granular nature of the polysilicon. The decomposition of the value of q(x,y) into the nominal (target) value, the global variation and the local variation is depicted in Figure 2.2, where only the x dimension is shown for convenience.

#### 2.2.3 Mismatch Introduced by Local Variation

We will examine first the effect of the short correlation distance variation.  $q_l(x,y)$  represents only the local variation part of the whole value of the process parameter. Equation (2.11) gives

$$(\Delta q_{l})^{2} = \frac{1}{A^{2}} \left[ \left( \int_{A_{l}} q_{l}(x, y) dx dy \right)^{2} + \left( \int_{A_{2}} q_{l}(x, y) dx dy \right)^{2} -2 \int_{A_{l}} q_{l}(x, y) dx dy \int_{A_{2}} q_{l}(x, y) dx dy \right].$$

(2.12)

The first term can be expressed as

$$\frac{1}{(WL)^2} \int_{y_b = 0}^{L} \int_{x_b = 0}^{W} \int_{y_a = 0}^{L} \int_{x_a = 0}^{W} q_l(x_a, y_a) q_l(x_b, y_b) dx_a dy_a dx_b dy_b . \qquad (2.13)$$

We assume now that the spatial random process  $q_l(x,y)$  is a wide sense stationary process so that the mean of  $q_l(x,y)$  is a constant  $\mu_{q_l}$  for all points (x,y), and the spatial autocorrelation between two points  $(x_a,y_a)$  and  $(x_b,y_b)$  depends only on the differences  $x_a-x_b$  and  $y_a-y_b$ :

$$R((x_a, y_a), (x_b, y_b)) = E(q_1(x_a, y_a)q_1(x_b, y_b)) = R(x_a - x_b, y_a - y_b)$$

(2.14)

Here, R() is the autocorrelation function and E() represents the expectation of a random variable. The physical meaning of this assumption is that the random behavior of  $q_l(x,y)$  is constant over the area where the two devices are laid out. We can assume that the mean  $\mu_{q_l}$  is zero, because if there exists a constant shift in the value of the parameter across the wafer, this can be assigned to the global variation. The expectation of the term in (2.13) is

$$\frac{1}{(WL)^2} \int_{y_b=0}^{L} \int_{x_b=0}^{W} \int_{y_a=0}^{L} \int_{x_a=0}^{W} R(x_a - x_b, y_a - y_b) dx_a dy_a dx_b dy_b.$$

(2.15)

Since the correlation distance is much smaller that the device dimensions, we can replace it with an impulse function

$$R(x_a - x_b, y_a - y_b) = \sigma^2 \delta(x_a - x_b, y_a - y_b), \qquad (2.16)$$

where  $\sigma^2$  is a positive constant. Using this and the basic property of the impulse function

$$\int_{Area} \delta(x, y) dx dy = \begin{cases} 1 & \text{if } (0,0) \in Area \\ 0 & \text{otherwise} \end{cases}$$

(2.17)

the quantity in (2.15) reduces to

$$\frac{\sigma^2}{WL} \tag{2.18}$$

The first and second terms of (2.12) both evaluate to the expression given in (2.18). Similarly, the third term of (2.12) can be expressed as

$$\frac{2}{(WL)^2} \int_{y_b = 0}^{L} \int_{x_b = D}^{D+W} \int_{y_a = 0}^{L} \int_{x_a = 0}^{W} R(x_a - x_b, y_a - y_b) dx_a dy_a dx_b dy_b$$

(2.19)

Since the devices do not overlap, the equation  $x_a = x_b$  cannot be satisfied in the area of integration, and, according to equation (2.17), the integral is zero. Combining the above results, the expectation of  $(\Delta q_1)^2$  is

$$\sigma_{\Delta q_1}^2 = \frac{S_{1, q}^2}{WL} , \qquad (2.20)$$

where  $S_{l,q}^2 = 2\sigma^2$  is a positive constant. This equation shows that the mismatch caused by short correlation distance variation is inversely proportional to the area of the devices.

If the process parameter q is one of the dimensions, W for example, similar analysis in one dimension gives

$$\sigma_{\Delta W_1}^2 = \frac{S_{1,W}^2}{L} , \qquad (2.21)$$

with  $S_{l, W}^2$  a positive constant. This equation shows that the mismatch introduced by edge roughness of the one side is inversely proportional to the length of the other side.

## 2.2.4 Mismatch Introduced by Global Variation

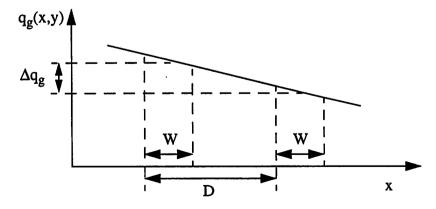

We proceed by examining the effect of the large gradients of variation. In this section  $q_g(x,y)$  represents only the global variation part of the whole value of the process parameter. We assume that the distance D between the two devices and the dimensions W and L are small enough to be able to consider that the variation is linear across the surface and it lies on a plane. Such a variation can be analyzed in two components, one parallel to the x-axis and one parallel to the y-axis, as in Figure 2.1. The y-component has the same effect on both devices and does not contribute to the mismatch. The effect of the x-component of the variation is shown in Figure 2.3. From this figure it is clear that

$$\Delta q_g = \lambda D, \qquad (2.22)$$

where  $\lambda$  is the slope of  $q_g(x)$ . In the absence of knowledge of the shape of the global distribution and the location of the pair of the devices in the die and the wafer,  $\lambda$  can be consid-

Figure 2.3 Effect of large gradient variation.

ered a zero mean random variable. A non zero mean would give a non zero mean for  $\Delta q_g$ . In this way previous knowledge of systematic behavior of the global variation can be used to predict the systematic part of the mismatch. Assuming that the variance of the slope is  $S_{g,q}^2$  the variance of  $\Delta q_g$  is

$$\sigma_{\Delta q_g}^2 = D^2 S_{g,q}^2$$

(2.23)

Common centroid geometry layout is extensively used to eliminate this part of the mismatch.

#### 2.2.5 Total Mismatch Model

Combining equations (2.20) and (2.23) we obtain the model for the variance of the combined local and global variation

$$\sigma_{\Delta q}^2 = \frac{S_{l, q}^2}{WL} + D^2 S_{g, q}^2$$

(2.24)

Of particular interest is the case at which a device parameter P does not depend on the dimensions and the process parameters on which it does depend are uncorrelated. Then the partial derivatives of relation (2.3) do not depend on W or L and a relation of the form (2.24), also holds for the device parameter:

$$\sigma_{\Delta P}^2 = \frac{S_{l,P}^2}{WI} + D^2 S_{g,P}^2 . \qquad (2.25)$$

If the process parameter q is one of the dimensions, for example W, similar analysis in one dimension gives

$$\sigma_{\Delta W}^{2} = \frac{S_{l, W}^{2}}{L} + D^{2} S_{g, W}^{2} . \qquad (2.26)$$

Switching W and L in the above equation gives the variance for  $\Delta L$ .

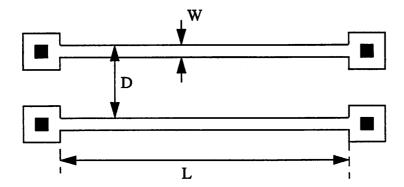

Figure 2.4 A pair of resistors.

# 2.3 Specific Device Mismatch Models

In this section we will apply the results of Section 2.2 in order to derive mismatch models for specific devices.

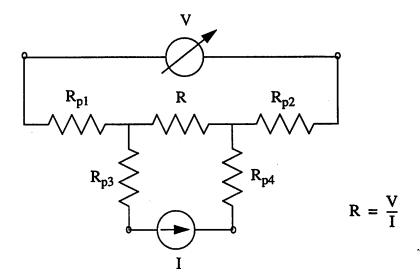

#### 2.3.1 Resistors

Consider a pair of resistors made of polysilicon, with dimensions W and L and distance D apart as shown in Figure 2.4.

We examine resistance mismatch of the main body of the resistors, the rectangular region W and L, neglecting the resistance of the contact and the resistance of the square around it. The value of the resistance is given by

$$R = R_s \frac{L}{W}, \qquad (2.27)$$

where R<sub>s</sub> is the sheet resistance. The mismatch in the value of R is

$$\Delta R = \frac{L}{W} \Delta R_s + \frac{R_s}{W} \Delta L - \frac{R_s L}{w^2} \Delta W , \qquad (2.28)$$

from which we obtain the relative mismatch

$$\frac{\Delta R}{R} = \frac{\Delta R_s}{R_s} + \frac{\Delta L}{L} - \frac{\Delta W}{W}.$$

(2.29)

The mechanism that determines  $\Delta L$  can vary depending on how the resistor is connected to the rest of the circuit (with contacts, or with wide lines of the same material as the resistor, the configuration around the contact, etc.). Generally  $\Delta L$  is about the same order of magnitude as  $\Delta W$ , and L is much longer than W; therefore, the second term of equation (2.29) can be omitted.  $\Delta W$  and  $\Delta R_s$  are uncorrelated, so that (2.29) gives

$$\frac{\sigma_{\Delta R}^2}{R^2} = \frac{\sigma_{\Delta R_s}^2}{R_s^2} + \frac{\sigma_{\Delta W}^2}{W^2}.$$

(2.30)

The sheet resistance  $R_s$  depends on the thickness of the conducting polysilicon layer and the concentration of the implanted ions in it. These two factors are uncorrelated and do not depend on the dimensions. The variance of  $\Delta R_s$  has the form of equation (2.25), and the variance of  $\Delta W$  is given by (2.26). Finally (2.30) can be written as

$$\frac{\sigma_{\Delta R}^2}{R^2} = \left(\frac{S_{l, R_s}^2}{WL} + S_{g, R_s}^2 D^2\right) + \frac{1}{W^2} \left(\frac{S_{l, W}^2}{L} + S_{g, W}^2 D^2\right), \tag{2.31}$$

where  $S_{l,R_s}^2$ ,  $S_{g,R_s}^2$ ,  $S_{l,W}^2$  and  $S_{g,W}^2$  are positive constants for a specific technology, representing local and global variation in  $R_s$  and W. This equation shows that when keeping L and D constant, for very small W, the variation in W dominates. For large W the difference in the sheet resistance dominates. For a specific L, the value of W at which both factors contribute equally to the mismatch depends on the specific technology. By grouping together the terms of the local variation and of the global variation (2.31) becomes

$$\frac{\sigma_{\Delta R}^2}{R^2} = \frac{1}{WL} \left( S_{l, R_s}^2 + \frac{S_{l, W}^2}{W} \right) + \left( S_{g, R_s}^2 + \frac{S_{g, W}^2}{W^2} \right) D^2, \qquad (2.32)$$

and for relatively large values of W we obtain the simplified version

$$\frac{\sigma_{\Delta R}^2}{R^2} = \frac{S_{l,R}^2}{WL} + S_{g,R}^2 D^2, \qquad (2.33)$$

with  $S_{l,R}^2$  and  $S_{g,R}^2$  positive constants characteristic of the technology.

Figure 2.5 A pair of capacitors.

Diffusion resistors are voltage dependent resistors. The width of the depletion region of the reversely biased diode between the resistor and the substrate varies according to the bias of the diode. The width and the thickness vary along the resistor. The effective width and thickness of the resistor depend on the voltage at its terminals. However, for almost zero voltage in both the terminals, similar analysis with the above shows that relations (2.32) and (2.33) hold. These relations should approximately hold also, when the voltage applied to the terminals of the resistors is held constant among different pairs.

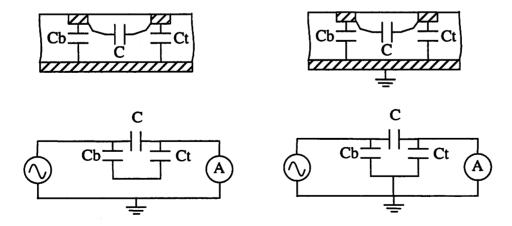

## 2.3.2 Capacitors

Consider a pair of poly 1 - poly 2 capacitors with dimensions W and L and distance D as shown in Figure 2.5. The value of the capacitance is given by

$$C = C_s WL, \qquad (2.34)$$

where  $C_s$  is the capacitance per unit area. Similar to the case for the resistors, the relative capacitance mismatch is

$$\frac{\Delta C}{C} = \frac{\Delta C_s}{C_c} + \frac{\Delta W}{W} + \frac{\Delta L}{L}.$$

(2.35)

In this case W and L are determined during the same processing steps; therefore,  $\Delta W$  and  $\Delta L$  cannot be considered uncorrelated. Equation (2.35) gives

$$\frac{\sigma_{\Delta C}^{2}}{C^{2}} = \frac{\sigma_{\Delta C_{s}}^{2}}{C_{s}^{2}} + \frac{\sigma_{\Delta W}^{2}}{W^{2}} + \frac{\sigma_{\Delta L}^{2}}{L^{2}} + \frac{2}{WL} r_{\Delta W, \Delta L} , \qquad (2.36)$$

where  $r_{\Delta W, \Delta L}$  is the correlation between  $\Delta W$  and  $\Delta L$ . This can be estimated as follows. The local part of variation or the edge roughness in  $\Delta W$  and  $\Delta L$  is uncorrelated, since the edges with length W and L are far apart compared to the small correlation distance. Only the global variation contributes to the correlation, and its effect can be captured by means of Figure 2.3, where now q is the dimension W or L. Similarly to equation (2.22),

$$\Delta W = \lambda_W D \tag{2.37}$$

and

$$\Delta L = \lambda_L D , \qquad (2.38)$$

where  $\lambda_W$  and  $\lambda_L$  are the slopes of the global variation of W and L.Therefore,

$$r_{\Delta W, \Delta L} = r_{\lambda_W, \lambda_L} D^2 , \qquad (2.39)$$

where  $r_{\lambda_W, \lambda_L}$  is the correlation of  $\lambda_W$  and  $\lambda_L$ , and this correlation is independent of the distance D.

The variance of  $\Delta W$  and  $\Delta L$  in (2.36) is given by (2.26). The capacitance per unit area depends on the thickness of the oxide and the value of the dielectric. These factors are uncorrelated, and they do not depend on the dimensions; therefore,  $\Delta C_s$  has the form of (2.25). Finally (2.36) can be written as

$$\frac{\sigma_{\Delta C}^{2}}{C^{2}} = \left(\frac{S_{l, C_{s}}^{2}}{WL} + S_{g, C_{s}}^{2}D^{2}\right) + \frac{1}{W^{2}}\left(\frac{S_{l, W}^{2}}{L} + S_{g, W}^{2}D^{2}\right) + \frac{1}{L^{2}}\left(\frac{S_{l, L}^{2}}{W} + S_{g, L}^{2}D^{2}\right) + \frac{2}{WL}r_{\lambda_{W}, \lambda_{L}}D^{2}$$

(2.40)

where  $S_{l, C_s}^2$ ,  $S_{g, C_s}^2$ ,  $S_{l, W}^2$ ,  $S_{g, W}^2$ ,  $S_{l, L}^2$  and  $S_{g, L}^2$  are positive constants for a specific technology, representing the local and global variation in  $C_s$ , W and L. This equation shows that with D constant, when W is very small, its variation dominates and when L is very small, its variation dominates. For large W and L it is the variation in the capacitance per unit area that dominates. Assuming square capacitors, the common size of W and L at which the variation in the dimensions and the variation in the capacitance per unit area contribute equally to the mismatch is technology specific. By grouping together terms of local and global variation we obtain

$$\frac{\sigma_{\Delta C}^{2}}{C^{2}} = \frac{1}{WL} \left( S_{1, C_{s}}^{2} + \frac{S_{1, W}^{2}}{W} + \frac{S_{1, L}^{2}}{L} \right) + \left( S_{g, C_{s}}^{2} + \frac{S_{g, W}^{2}}{W^{2}} + \frac{S_{g, L}^{2}}{L^{2}} \right) D^{2}$$

$$+ \frac{2}{WL} r_{\lambda_{W}, \lambda_{L}} D^{2} .$$

(2.41)

It is not meaningful to make one side extremely short and the reference to it is only academic. Similar analysis, however, could find application in matching the parasitic capacitance of interconnect lines.

For relatively large values of W and L, and for low correlation  $r_{\lambda_W,\,\lambda_L}$ , we obtain the simplified form

$$\frac{\sigma_{\Delta C}^2}{C^2} = \frac{S_{l,C}^2}{WL} + S_{g,C}^2 D^2, \qquad (2.42)$$

with  $S_{l,C}^2$  and  $S_{g,C}^2$  positive numbers.

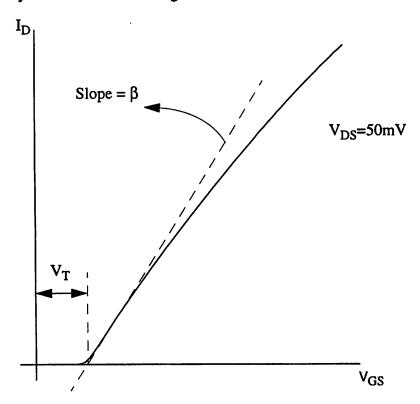

#### 2.3.3 Transistors

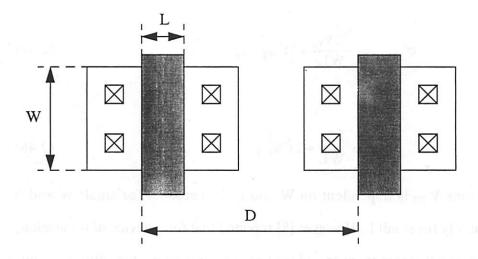

Consider now a pair of MOS transistors with channel width W and channel length L at distance D from each other, as shown in Figure 2.6.

Neglecting the channel length modulation, the drain current I of a MOS transistor is given by

$$I = \frac{\mu C_{ox}}{2} \frac{W}{L} (V_{GS} - V_T)^2 , \qquad (2.43)$$

**Figure 2.6** A pair of transistors.

where  $\mu$  is the mobility of the silicon under the gate,  $C_{ox}$  is the gate capacitance per unit area and  $V_{GS}$  is the gate-source voltage.  $V_{T}$  is the threshold voltage, which is affected by the body effect:

$$V_{\rm T} = V_{\rm T0} + \gamma (\sqrt{V_{\rm SB} + 2\Phi_{\rm P}} - \sqrt{2\Phi_{\rm P}}),$$

(2.44)

where  $V_{T0}$  is the threshold voltage without body effect,  $\gamma$  is the body effect factor,  $V_{SB}$  is the source-substrate voltage and  $\Phi_P$  is a logarithmic function of the doping concentration of the channel which can be considered constant. Hence the current mismatch is mainly caused by mismatch in  $V_{T0}$ ,  $\gamma$  and by the current factor

$$\beta = \frac{\mu C_{ox} W}{2} I \qquad (2.45)$$

The threshold voltage  $V_{T0}$  and the body effect factor  $\gamma$  are independent of W and L for relatively large dimensions. They depend on uncorrelated process parameters; therefore, the variances of  $V_T$ ,  $V_{T0}$  and  $\gamma$  are of the form of equation (2.25):

$$\sigma_{\Delta V_{T}}^{2} = \frac{S_{l, V_{T}}^{2}}{WL} + D^{2}S_{g, V_{T}}^{2}$$

(2.46)

$$\sigma_{\Delta V_{T0}}^2 = \frac{S_{l, V_{T0}}^2}{WL} + D^2 S_g^2, V_{T0}$$

(2.47)

$$\sigma_{\Delta \gamma}^{2} = \frac{S_{l, \gamma}^{2}}{WL} + D^{2}S_{g, \gamma}^{2}$$

(2.48)

For small dimensions  $V_{T0}$  is dependent on W and L. It increases for small W and it decreases exponentially for small L. However [8] reported that for a device of dimensions  $2\mu m \times 2\mu m$  the mismatch component introduced by the dimensions variation accounts only for 10% of the total threshold voltage mismatch. Therefore the model of equations (2.47) and (2.48) is valid for this range of dimensions. A discussion of threshold voltage matching of even smaller devices is included in sections 2.4 and 2.5.

The mismatch of  $\mu$  and  $C_{ox}$  has the form of equation (2.25) for the same reasons. The variations in W and L are independent since W is defined when the thick oxide is etched to open the active area and L is defined when the polysilicon is etched to form the gate. Using equations (2.25) and (2.26) we obtain the variance of the relative mismatch for the current factor

$$\frac{\sigma_{\Delta\beta}^2}{\beta^2} = \left(\frac{S_{l, \mu C_{ox}}^2 + S_{g, \mu C_{ox}}^2 D^2}{WL} + \frac{1}{W^2} \left(\frac{S_{l, W}^2}{L} + S_{g, W}^2 D^2\right) + \frac{1}{L^2} \left(\frac{S_{l, L}^2}{W} + S_{g, L}^2 D^2\right), \quad (2.49)$$

where  $S_{l,\,\mu C_{ox}}^2$ ,  $S_{g,\,\mu C_{ox}}^2$ ,  $S_{l,\,W}^2$ ,  $S_{g,\,W}^2$ ,  $S_{l,\,L}^2$  and  $S_{g,\,L}^2$  are positive constants for a specific technology, representing the local and global variation in  $\mu C_{ox}$ , W and L. For large W and L the mismatch in  $\mu C_{ox}$  dominates, while for small W or L the dimensions mismatch dominates. By grouping together terms of local and global variation the above equation becomes

$$\frac{\sigma_{\Delta\beta}^2}{\beta^2} = \frac{1}{WL} \left( S_{l, \mu C_{ox}}^2 + \frac{S_{l, W}^2}{W} + \frac{S_{l, L}^2}{L} \right) + \left( S_{g, \mu C_{ox}}^2 + \frac{S_{g, W}^2}{W^2} + \frac{S_{g, L}^2}{L^2} \right) D^2.$$

(2.50)

For relatively large values of W and L we obtain the simplified form

$$\frac{\sigma_{\Delta\beta}^2}{\beta^2} = \frac{S_{l,\beta}^2}{WL} + S_{g,\beta}^2 D^2, \qquad (2.51)$$

with  $S_{g,\beta}^2$  and  $S_{g,\beta}^2$  positive constants.

In order to find mismatch in the drain current in the saturation region we use (2.43) to obtain

$$\frac{\Delta I}{I} = \frac{\Delta \beta}{\beta} - \frac{2}{(V_{GS} - V_T)} \Delta V_T. \tag{2.52}$$

The threshold voltage and the current factor depend on common factors such as the gate oxide capacitance and the doping concentration of the channel, and we expect the two quantities to be correlated. However, [8] reported that both a theoretical expression and experimental results show that the value of the correlation coefficient is very close to zero. Therefore, (2.52) gives

$$\frac{\sigma_{\Delta I}^{2}}{I^{2}} = \frac{\sigma_{\Delta \beta}^{2}}{\beta^{2}} + \frac{4}{(V_{CS} - V_{T})^{2}} \sigma_{\Delta V_{T}}^{2}$$

(2.53)

Using (2.46) and (2.50) we obtain

$$\frac{\sigma_{\Delta l}^{2}}{I^{2}} = \frac{1}{WL} \left( S_{l, \mu C_{ox}}^{2} + \frac{S_{l, W}^{2}}{W} + \frac{S_{l, L}^{2}}{L} + \frac{4}{(V_{GS} - V_{T})^{2}} S_{l, V_{T}}^{2} \right) + \left( S_{g, \mu C_{ox}}^{2} + \frac{S_{g, W}^{2}}{W^{2}} + \frac{S_{g, L}^{2}}{L^{2}} + \frac{4}{(V_{GS} - V_{T})^{2}} S_{g, V_{T}}^{2} \right) D^{2}.$$

(2.54)

The simplified version for relatively large W and L is

$$\frac{\sigma_{\Delta I}^2}{I^2} = \frac{1}{WL} \left( S_{l, \beta}^2 + \frac{4}{(V_{GS} - V_T)^2} S_{l, V_T}^2 \right) + \left( S_{g, \beta}^2 + \frac{4}{(V_{GS} - V_T)^2} S_{g, V_T}^2 \right) D^2.$$

(2.55)

### 2.4 Device Parameters of Small Dimension Devices

It is possible that although a device parameter is independent of W and L when these dimensions are relatively large, it becomes a function of them when they are small. A typical example is the threshold voltage of a MOS transistor. In this case, knowledge of the partial derivative of the device parameter with respect to the dimensions - which will be a function of the dimensions - is needed to use (2.3) to predict mismatch of the device parameter. Also the rest of the partial derivatives that appear in (2.3) could be functions of the dimensions now.

For example, in order to predict threshold voltage mismatch behavior of submicron devices we could introduce into (2.3) two new terms, one for each dimension, using the slope of the experimentally obtained curves of the threshold voltage versus W and L. The partial derivatives with respect to the rest of the parameters could be arbitrarily assumed independent of the dimensions as a first approximation, and we could use the model for long dimensions to estimate their effect. Experimental mismatch measurement of threshold voltage of submicron devices are needed to verify the result.

The extension of the mismatch model presented in the next section could be incorporated in the above methodology.

## 2.5 An Extension of the Mismatch Model of a Process Parameter

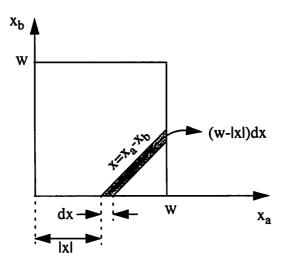

The above analysis of effective process parameter mismatch caused by local variation resulting in equations (2.20) and (2.21) is based on the assumption that the autocorrelation distance is small compared to the device dimensions. It is possible that this assumption is not true in the modern submicron technologies. In this section we will investigate how the above equations are modified when we relax this assumption. We preserve the assumption that the process parameter q(x,y) is a wide sense stationary spatial random process, so that the expectation of the first term of (2.12) is given by the quantity in (2.15). We can transform the quadruple intregral

Figure 2.7 Area of integration of the autocorrelation function.

$$\frac{1}{(WL)^{2}} \int_{y_{b}=0}^{L} \int_{x_{b}=0}^{W} \int_{y_{a}=0}^{L} \int_{x_{a}=0}^{W} R(x_{a}-x_{b}, y_{a}-y_{b}) dx_{a} dy_{a} dx_{b} dy_{b}$$

(2.56)

to a double integral by substituting  $x=x_a-x_b$  and  $y=y_a-y_b$ . The area of integration for  $x_a$  and  $x_b$  is depicted in Figure 2.7 and is the same for  $y_a$  and  $y_b$ . The new form of the integral is

$$\frac{1}{(WL)^2} \int_{y=-L}^{L} \int_{x=-W}^{W} R(x,y)(W-|x|)(L-|y|)dxdy , \qquad (2.57)$$

and since the autocorrelation function is even with respect to x and y

$$\frac{4}{WL} \int_{y=0}^{L} \int_{x=0}^{W} \left(1 - \frac{x}{W}\right) \left(1 - \frac{y}{L}\right) R(x, y) dx dy \qquad (2.58)$$

In order to find an estimation for this quantity we assume that R(x,y) has the rectangular form

$$R_{R}(x, y) = \begin{cases} \sigma^{2} & \text{if } |x| < d_{x} \text{ and } |y| < d_{y} \\ 0 & \text{otherwise} \end{cases}, \qquad (2.59)$$

where we consider different correlation distance for the x and the y direction in order to preserve generality. The quantity in (2.58) now becomes

$$I_{R}(W)I_{R}(L), \qquad (2.60)$$

where

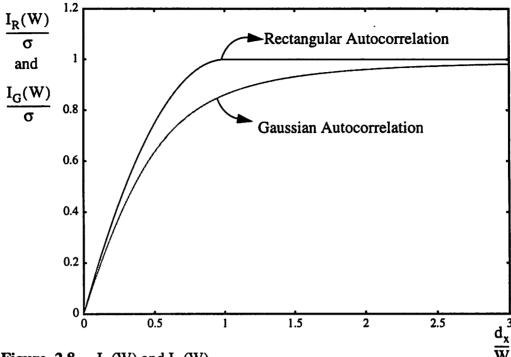

$$I_{R}(W) = \frac{2\sigma}{W} \int_{0}^{\min(W, d_{x})} \left(1 - \frac{x}{W}\right) dx . \qquad (2.61)$$

Performing the integration we obtain

$$I_{R}(W) = \sigma \left[ 2\frac{d_{x}}{W} - \left(\frac{d_{x}}{W}\right)^{2} \right] \quad \text{if } d_{x} < W$$

$$\sigma \quad \text{if } d_{x} > W$$

(2.62)

As a more realistic example of R(x,y) we consider a two-dimensional Gaussian function

$$R_G(x, y) = \sigma^2 \exp \left[ -\left( \frac{x^2}{d_y^2} + \frac{y^2}{d_y^2} \right) \right],$$

(2.63)

where again we assumed different correlation distance for the x and the y direction. A two dimensional Gaussian shape as an example of R(x,y) has also been suggested by Shyu, Temes and Kung in [12]. A Gaussian autocorrelation function corresponds to a Gaussian power spectral density, as opposed to the flat power spectral density implied by an impulse autocorrelation function. The quantity in (2.58) now becomes

$$I_{G}(W)I_{G}(L), \qquad (2.64)$$

where

$$I_{G}(W) = \frac{2\sigma}{W} \int_{0}^{W} \left(1 - \frac{x}{W}\right) \exp\left(-\frac{x^{2}}{d_{x}^{2}}\right) dx . \qquad (2.65)$$

Performing the integration we obtain

$$I_{G}(W) = \sigma \frac{d_{x}}{W} \left\{ \sqrt{\pi} \cdot \operatorname{erf}\left(\frac{W}{d_{x}}\right) + \frac{d_{x}}{W} \left[ \exp\left(-\frac{W^{2}}{d_{x}^{2}}\right) - 1 \right] \right\}, \tag{2.66}$$

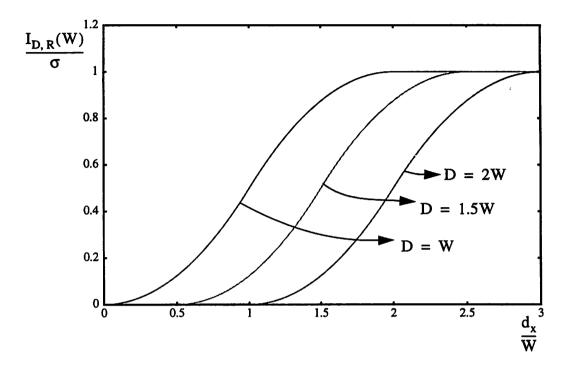

Figure 2.8  $I_R(W)$  and  $I_G(W)$ .

where erf(x) is the error function

$$\operatorname{erf}(x) = \frac{2}{\sqrt{\pi}} \int_{0}^{x} \exp(-\omega^{2}) d\omega. \qquad (2.67)$$

The value of  $I_R(W)$  and  $I_G(W)$  as a function of  $d_x/W$  is depicted in Figure 2.8.  $I_R(L)$  and  $I_G(L)$  versus  $d_y/L$  are similar. The expectation of the second term of (2.12) is equal to that of the first.

We proceed now to calculate the expectation of the third term of (2.12) as given by (2.19), which depends on the distance between the devices and is negative, which means that it improves matching. The quadruple integral

$$\frac{2}{(WL)^2} \int_{y_b = 0}^{L} \int_{x_b = D}^{D+W} \int_{y_a = 0}^{L} \int_{x_a = 0}^{W} R(x_a - x_b, y_a - y_b) dx_a dy_a dx_b dy_b$$

(2.68)

can be reduced to a double integral similar to (2.57):

$$\frac{2}{(WL)^2} \int_{y=-L}^{L} \int_{x=-W}^{W} R(x-D,y)(W-|x|)(L-|y|)dxdy$$

(2.69)

Since the autocorrelation R(x,y) is an even function of y, we have

$$\frac{4}{WL} \int_{y=0}^{L} \int_{x=-W}^{W} R(x-D, y) \left(1 - \frac{|x|}{W}\right) \left(1 - \frac{|y|}{L}\right) dx dy.$$

(2.70)

In order to find an estimation for this term we again use the rectangular autocorrelation function given by (2.59). The quantity in (2.70) now becomes

$$2I_{R}(L)I_{D,R}(W)$$

, (2.71)

where  $I_R(L)$  is as defined in (2.61) and evaluates to (2.62), and  $I_{D,R}(W)$  is given by

$$I_{D,R}(W) = \frac{1}{W} \int_{W}^{W} R_{R,x}(x-D) \left(1 - \frac{|x|}{W}\right) dx$$

, (2.72)

where

$$R_{R,x}(x) = \begin{cases} \sigma & \text{if } |x| < d_x \\ 0 & \text{otherwise} \end{cases}$$

(2.73)

This can be written as.

$$I_{D,R}(W) = \frac{\sigma}{W} \int_{\min(\max(-W, D-d_x), W)}^{W} \left(1 - \frac{|x|}{W}\right) dx$$

(2.74)

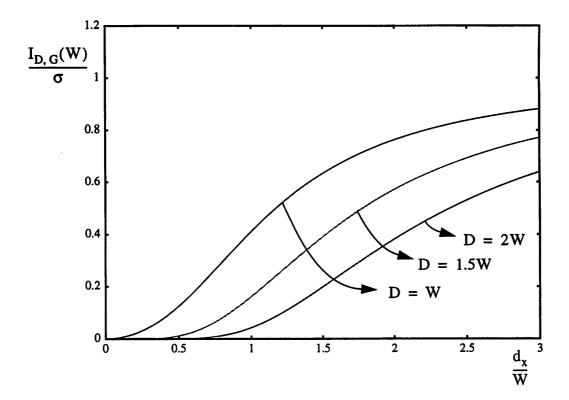

and is calculated and depicted in Figure 2.9 for different values of distance D.

Using the two-dimensional Gaussian autocorrelation function given by (2.63), the quantity in (2.70) has again the form

$$2I_{G}(L)I_{D,G}(W)$$

, (2.75)

where  $I_G(L)$  is given by (2.66) and  $I_{D,G}(W)$  is given by

$$I_{D,G}(W) = \frac{1}{W} \int_{-W}^{W} R_{G,x}(x-D) \left(1 - \frac{|x|}{W}\right) dx$$

, (2.76)

where  $R_{G,x}(x)$  is

Figure 2.9  $I_{D,R}(W)$ , for the rectangular autocorrelation function.

$$R_{G, x}(x) = \sigma \cdot exp\left(-\frac{x^2}{d_x^2}\right). \qquad (2.77)$$

After some calculations we obtain

$$\begin{split} I_{D,G}(W) &= \frac{\sigma d_x}{2W} \bigg\{ \sqrt{\pi} \bigg( 1 + \frac{W}{D} \bigg) \bigg[ erf \bigg( -\frac{D}{d_x} \bigg) - erf \bigg( -\frac{D+W}{d_x} \bigg) \bigg] \\ &+ \sqrt{\pi} \bigg( 1 - \frac{W}{D} \bigg) \bigg[ erf \bigg( -\frac{D-W}{d_x} \bigg) - erf \bigg( -\frac{D}{d_x} \bigg) \bigg] \\ &+ \frac{d_x}{W} \bigg[ exp \bigg( -\frac{(D+W)^2}{d_x^2} \bigg) - exp \bigg( -\frac{D^2}{d_x^2} \bigg) \bigg] \\ &+ \frac{d_x}{W} \bigg[ exp \bigg( -\frac{(D-W)^2}{d_x^2} \bigg) - exp \bigg( -\frac{D^2}{d_x^2} \bigg) \bigg] \bigg\} , \end{split}$$

which is depicted in Figure 2.10.

Figure 2.10  $I_{D,G}(W)$  for the two dimensional Gaussian autocorrelation.

Finally the total variance of the local mismatch is

$$\sigma_{\Delta q_1}^2 = 2I_R(L)[I_R(W) - I_{D,R}(W)]$$

(2.79)

for the rectangular autocorrelation and

$$\sigma_{\Delta q_1}^2 = 2I_G(L)[I_G(W) - I_{D,G}(W)]$$

(2.80)

for the Gaussian autocorrelation.

When the parameter q is dimension L, similar analysis in one dimension gives

$$\sigma_{\Delta L_1}^2 = 2[I_R(W) - I_{R, D}(W)]$$

(2.81)

for the rectangular autocorrelation and

$$\sigma_{\Delta L_1}^2 = 2[I_G(W) - I_{G, D}(W)]$$

(2.82)

for the Gaussian autocorrelation. When parameter q is dimension W

$$\sigma_{\Delta W_1}^2 = \frac{2I_R(L) \quad \text{if } D > d_x}{0 \quad \text{if } D < d_x}$$

(2.83)

for the rectangular autocorrelation and

$$\sigma_{\Delta W_1}^2 = 2I_G(L) \left[ 1 - \exp\left(-\frac{D^2}{d_x^2}\right) \right]$$

(2.84)

for the Gaussian autocorrelation. It is worth noticing that

$$1 - \exp\left(-\frac{D^2}{d_x^2}\right) \tag{2.85}$$

looks very similar to the step function in (2.83). The estimations of  $\sigma_{\Delta L}^2$  in (2.81) and (2.82) have the same step shape too; therefore, the variation in  $\Delta W$  and  $\Delta L$  has approximately the same dependence on L and W respectively.

For W and distance D much longer then the autocorrelation distance,  $I_{D,R}(W)$  and  $I_{D,G}(W)$  are zero.  $I_R(W)$  and  $I_G(W)$  are proportional to 1/W, and  $I_R(L)$  and  $I_G(L)$  are proportional to 1/L. Therefore (2.79) and (2.80) of the extended model agree with (2.20) of the model derived for long dimensions in the previous paragraph. The variance of  $\Delta W$  and  $\Delta L$  in equations (2.81)-(2.84) is proportional to 1/L and 1/W respectively, and the new model agrees with the previous model that resulted in equation (2.21).

For small dimensions there are two mechanisms through which matching becomes better than what (2.20) and (2.21) predict. First  $I_R(W)$  and  $I_G(W)$  reach a saturation level that can be observed in Figure 2.9 when W becomes very small, and similarly for L. Second, when D and W are small,  $I_D(W)$  becomes significant and reduces mismatch, as equations (2.79) and (2.80) show. Qualitatively, the same behavior is observed for the dimension mismatch in equations (2.81)-(2.84).

## 2.6 Comments on the Extension of the Model

We expect each process parameter to have its own autocorrelation distance, and saturation of mismatch to become significant at different values of the dimensions W and L for each one of those. The effect on the mismatch on a device parameter P is the weighted sum of the mismatch of many process parameters, as (2.3) implies. If the device parameter does not depend on the dimensions W and L, saturation is expected to appear gradually to its mismatch as W and L become small, and saturation in the mismatch of more process parameters becomes significant.

For the device parameters that are proportional or inversely proportional to W or L, the length or width mismatch term is multiplied by  $1/W^2$  or  $1/L^2$  respectively as can be seen in equations (2.30), (2.36) and (2.49). Therefore, even if the dimension mismatch itself becomes smaller than what (2.26) predicts, its effect becomes stronger, so we should expect that the matching of the device parameter will be worse than is predicted by the simplified equations (2.33), (2.42) and (2.51).

At this point we do not have sufficient information about the autocorrelation distance of any process parameters, and we are not able to predict if saturation actually appears in the mismatch of the smallest devices that can be fabricated today. Experimental data are needed to support the validity of the model.

# Chapter 3

# **Mismatch and Circuit Performance**

#### 3.1 Introduction

In this chapter we examine how device mismatch affects the circuit performance. Examples of performance degradation are input offset in operational amplifiers and differential pairs, current deviation in current mirrors, nonlinearity in A/D converters, etc. Some of the results of this chapter will be used in Chapter 5 to study the behavior of the simple subcircuits that we fabricated.

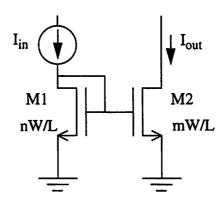

#### 3.2 Current Mirror

A MOS current mirror is shown in Figure 3.1. The W/L ratio between the two devices is n:m. The output current is ideally  $\frac{m}{n}I_{in}$  but because of device mismatch and channel modulation effects it is different in practice. In the following analysis we ignore channel modulation, which can be minimized by using the same  $V_{DS}$  for M1 and M2 as in the case of a cascode current mirror. When accuracy is needed we design many identical devices

Figure 3.1 A MOS current mirror.

connected in parallel instead of devices of different sizes. Therefore we shall consider that M1 and M2 are not single transistors but n and m, respectively, identically designed transistors connected in parallel. We shall also assume that M1 and M2 are laid out with common centroid geometry with common center of mass, in order to eliminate the effect of the large gradients of variation, as described in Section 2.2.4. The mismatch is assumed to be caused exclusively by the short correlation distance variation with correlation distance much smaller than the device dimensions. For a specific device parameter we assume the same mean and the same variance among all the devices. The square of the deviation of a process parameter from the mean is of the form of (2.13), and the variance of the deviation is of the form (2.15), or equivalently (2.18).

The well known relation that gives the current of a MOS transistor in the saturation region ignoring the finite output resistance is

$$I = \frac{\mu C_{ox} W}{2} (V_{GS} - V_T)^2 = \beta (V_{GS} - V_T)^2$$

(3.1)

where  $\mu$  is the mobility of the carriers,  $C_{ox}$  is the gate capacitance per unit area,  $V_{GS}$  is the gate-source voltage,  $V_{T}$  is the threshold voltage and

$$\beta = \frac{\mu C_{ox} W}{2 L} \tag{3.2}$$

is defined as the current factor. In the following analysis the differences in the process parameters  $\beta$  and  $V_T$  imply deviations from the common mean. The differences in drain currents and the gate source voltage imply deviations from the value these quantities would have if all the devices behaved identically and the process parameters of all of them were equal to the mean. Since to first order we ignore the large gradient variation, with the aid of equations (2.46) and (2.49) the variance of  $V_T$  and  $\beta$  is given by

$$\sigma_{V_{T}}^{2} = \frac{S_{l, V_{T}}^{2}}{2WL} \tag{3.3}$$

and

Chapter 3

$$\frac{\sigma_{\beta}^{2}}{\beta^{2}} = \frac{S_{l, \mu C_{ox}}^{2}}{2WL} + \frac{1}{W^{2}} \frac{S_{l, W}^{2}}{2L} + \frac{1}{L^{2}} \frac{S_{l, L}^{2}}{2W} , \qquad (3.4)$$

respectively. The coefficients  $S_{l, V_T}^2$ ,  $S_{l, \mu C_{ox}}^2$ ,  $S_{l, W}^2$ ,  $S_{l, W}^2$ , have been defined in Chapter 2. The coefficient of 2 in the denominator appears, because here we refer to the variance of a parameter and not the variance of the difference of the parameter between two devices, as was the case equations (2.46) and (2.49).

The variation in the current in terms of the variation in  $\beta$ ,  $V_{GS}$  and  $V_{T}$  is given by

$$\frac{\Delta I}{I} = \frac{\Delta \beta}{\beta} + \frac{2}{(V_{GS} - V_T)} (\Delta V_T - \Delta V_{GS}) . \qquad (3.5)$$

This relation, applied to the i-th of the n devices that comprise M1, gives:

$$\frac{\Delta I_{M1, i}}{I_{in}/n} = \frac{\Delta \beta_{M1, i}}{\beta} + \frac{2}{(V_{GS} - V_{T})} ((\Delta V_{T})_{M1, i} - \Delta V_{GS}) , \qquad (3.6)$$

where the index M1,i indicates the specific transistor to which the quantity refers. The total drain current of M1 is  $I_{in}$ , so the current variations  $\Delta I_{M1, i}$  add up to zero. Summing those relations for i=1 to n gives

$$0 = \frac{1}{\beta} \sum_{i=1}^{n} \Delta \beta_{M1, i} + \frac{2}{(V_{GS} - V_{T})} \left( \sum_{i=1}^{n} (\Delta V_{T})_{M1, i} - n \Delta V_{GS} \right)$$

(3.7)

or

$$\Delta V_{GS} = \frac{1}{n} \sum_{i=1}^{n} (\Delta V_{T})_{M1, i} + \frac{(V_{GS} - V_{T})}{2} \frac{1}{n\beta} \sum_{i=1}^{n} \Delta \beta_{M1, i} .$$

(3.8)

Similarly to (3.6) the variance of the current in each one of the m transistors that comprise M2 is

$$\frac{\Delta I_{M2, i}}{I_{out}/m} = \frac{\Delta \beta_{M2, i}}{\beta} + \frac{2}{(V_{GS} - V_{T})} ((\Delta V_{T})_{M2, i} - \Delta V_{GS}) , \qquad (3.9)$$

and the variation in Iout is

Chapter 3 34

$$\frac{\Delta I_{\text{out}}}{I_{\text{out}}} = \frac{1}{m\beta} \sum_{i=1}^{m} \Delta \beta_{\text{M2, i}} + \frac{2}{(V_{\text{GS}} - V_{\text{T}})} \left( \frac{1}{m} \sum_{i=1}^{m} (\Delta V_{\text{T}})_{\text{M2, i}} - \Delta V_{\text{GS}} \right), \quad (3.10)$$

and by using V<sub>GS</sub> from (3.8),

$$\frac{\Delta I_{\text{out}}}{I_{\text{out}}} = \frac{1}{m\beta} \sum_{i=1}^{m} \Delta \beta_{\text{M2, i}} - \frac{1}{n\beta} \sum_{i=1}^{n} \Delta \beta_{\text{M1, i}}

+ \frac{2}{(V_{\text{GS}} - V_{\text{T}})} \left( \frac{1}{m} \sum_{i=1}^{m} (\Delta V_{\text{T}})_{\text{M2, i}} - \frac{1}{n} \sum_{i=1}^{n} (\Delta V_{\text{T}})_{\text{M1, i}} \right).$$

(3.11)

Assuming that the variance is the same for the process parameters among all the devices and that the threshold voltage is independent of the current factor, as has been referred in Section 2.3.3, we obtain

$$\frac{\sigma_{I_{out}}^2}{I_{out}^2} = \left(\frac{1}{n} + \frac{1}{m}\right) \frac{\sigma_{\beta}^2}{\beta^2} + \left(\frac{1}{n} + \frac{1}{m}\right) \frac{4\sigma_{V_T}^2}{\left(V_{GS} - V_T\right)^2} . \tag{3.12}$$

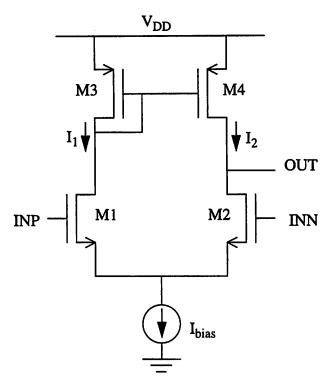

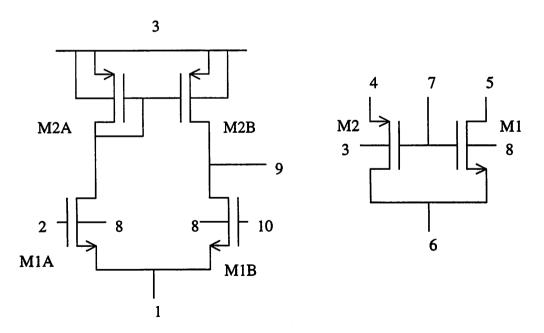

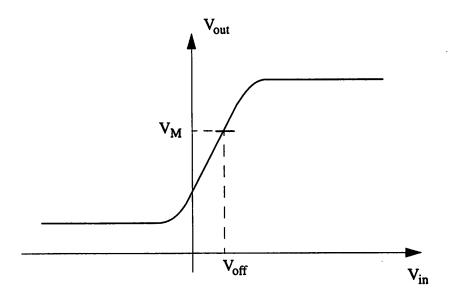

#### 3.3 Differential Pair

We consider now the differential pair shown in Figure 3.2. We shall estimate the variance of the input offset. As in the case of the current mirror we shall ignore the channel length modulation. The differential pair then has infinite voltage gain, and the offset is the value of the differential input signal which drives all four transistors to saturation. Therefore, the current of all four transistors is given by equation (3.1), and the relative difference in the current between a pair of transistors is given by (3.5). Using the latter we obtain an expression for the offset:

$$V_{\text{off}} = \Delta V_{\text{GS}}|_{1,2} =$$

$$\Delta V_{\text{T}}|_{1,2} + \frac{V_{\text{GS}} - V_{\text{T}}}{2}|_{1,2} \cdot \left(\frac{\Delta I}{I}|_{1,2} - \frac{\Delta \beta}{\beta}|_{1,2}\right),$$

(3.13)

where  $\mid_{1,2}$  indicates the M1, M2 device pair. Again, equation (3.5) gives

$$\frac{\Delta I}{I}\Big|_{3,4} = \frac{\Delta \beta}{\beta}\Big|_{3,4} + \frac{2}{V_{GS} - V_{T}}\Big|_{3,4} \cdot \Delta V_{T}\Big|_{3,4} . \tag{3.14}$$

Chapter 3 35

Figure 3.2 A differential pair.

Since

$$\left. \frac{\Delta I}{I} \right|_{1,2} = \left. \frac{\Delta I}{I} \right|_{3,4} \qquad , \tag{3.15}$$

we obtain

$$V_{\text{off}} = \Delta V_{\text{T}}|_{1,2}$$

$$+ \frac{V_{\text{GS}} - V_{\text{T}}}{2}|_{1,2} \cdot \left(\frac{\Delta \beta}{\beta}|_{3,4} - \frac{\Delta \beta}{\beta}|_{1,2} + \frac{2}{V_{\text{GS}} - V_{\text{T}}}|_{3,4} \cdot \Delta V_{\text{T}}|_{3,4}\right).$$

(3.16)

It is of practical importance to calculate the variance of the input offset. As explained in Section 2.3.3, the current factor and the threshold voltage can be considered uncorrelated. However, we expect some correlation between  $\Delta \beta|_{1,2}$  and  $\Delta \beta|_{3,4}$ , and between  $\Delta V_{T_{3,4}}$  and  $\Delta V_{T_{3,4}}$ . The local variation components are independent, since we assume short autocorrelation distance. If each one of the transistors M1, M2, M3 and M4 consists of many parallel connected devices and common centroid geometry is used for each pair,

Chapter 3 36

the effect of global variation can be neglected to a first order as discussed above, and the correlation can be considered zero. If M1, M2, M3 and M4 are single devices then similarly to Equation (2.22) we can write

$$\Delta V_{T}|_{1,2} = \lambda_{V_{T}}|_{1,2} D_{1,2}$$

(3.17)

and

$$\Delta V_{T}|_{3,4} = \lambda_{V_{T}}|_{3,4} D_{3,4} , \qquad (3.18)$$

where  $\lambda_{V_{7}}|_{1,2}$  and  $\lambda_{V_{7}}|_{3,4}$  are the slopes of the large gradients of variation, and  $D_{1,2}$  and  $D_{3,4}$  are the distances between the two transistors of each pair. The correlation is

$$r_{\Delta V_{T}} = E \left[ \lambda_{V_{T}} \Big|_{1,2} \cdot \lambda_{V_{T}} \Big|_{3,4} \right] D_{1,2} D_{3,4}, \qquad (3.19)$$

where E[] denotes the expectation of a random variable. It becomes small when the distances  $D_{1,2}$  and  $D_{3,4}$  are short, when we minimize the total dependence on the global variation, also. Considering relatively large W and L, a similar equation holds for the correlation of  $\Delta\beta$ . Finally the variance of the offset is

$$\sigma_{V_{off}}^{2} = \sigma_{\Delta V_{T}|_{1,2}}^{2} + \left(\frac{(V_{GS} - V_{T})|_{1,2}}{(V_{GS} - V_{T})|_{3,4}}\right)^{2} \sigma_{\Delta V_{T}|_{3,4}}^{2} + 2\frac{(V_{GS} - V_{T})|_{1,2}}{(V_{GS} - V_{T})|_{3,4}} r_{\Delta V_{T}}$$

$$+ \left(\frac{V_{GS} - V_{T}}{2}\Big|_{1,2}\right)^{2} \left(\frac{\sigma_{\Delta \beta|_{3,4}}^{2}}{\beta^{2}\Big|_{3,4}} + \frac{\sigma_{\Delta \beta|_{1,2}}^{2}}{\beta^{2}\Big|_{1,2}} - 2\frac{r_{\Delta \beta}}{\beta|_{1,2}\beta|_{3,4}}\right)$$

(3.20)

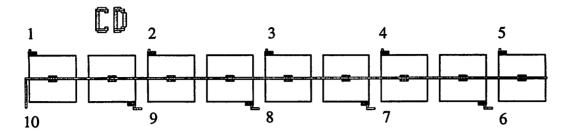

#### 3.4 D/A converter

The operation of a large family of D/A converters is based on arrays of identically designed devices. Depending on the number of devices that are "on", we obtain the several levels of the output signal. An "on" device is defined according to the kind of the converter. If it is a string of resistors with common current flowing through them, a resistor is considered on when the voltage drop across it contributes to the output. If the converter

Chapter 3

consists of many transistors with common drain and source, a transistor is on when the gate voltage is such that drives the transistor to saturation, and it contributes to the output current. Finally, if it is a charge redistribution D/A converter, the output is the common terminal of all the capacitors in the array, and a capacitor is on when the voltage on its other terminal changes in the second clock phase, according to a voltage reference.

Assuming that the D/A converter consists of N devices, there are N levels of the output signal corresponding to the situation where 0, 1,... N-1 of the devices are on. The full scale where all N of the devices are on is usually not available as an output. Assuming that k devices are on, the output is

$$A_0 = \sum_{i=1}^{k} a_i$$

$k = 0, 1 \dots N-1,$  (3.21)

where  $a_i$  is the contribution of each device to the output. The nominal values of the  $a_i$  are the same and equal to a. When k=0 the output is zero. By turning all the devices on we obtain the full scale output

$$A_{FS} = \sum_{i=1}^{N} a_i = \sum_{i=1}^{k} a_i + \sum_{i=k+1}^{N} a_i, \qquad (3.22)$$

and the ratio of the output over the full scale is

$$\frac{A_{o}}{A_{FS}} = \frac{\sum_{i=1}^{k} a_{i}}{\sum_{i=1}^{k} a_{i} + \sum_{i=k+1}^{N} a_{i}} . \tag{3.23}$$

Integral Nonlinearity at a step k (INL(k)) is defined as the discrepancy of the above quantity form the its expectation -which is also the nominal value - (k/N).

$$INL(k) = \frac{A_o}{A_{FS}} - \frac{k}{N}$$

(3.24)

Integral Nonlinearity (INL) of the D/A converter is defined as the maximum INL(k) for all the steps k.

In order to calculate the variance of the quantity in (3.23), we need to calculate the partial derivative with respect to the contribution  $a_i$  of the on and the off devices.

$$\frac{\partial}{\partial a_{i}} \left( \frac{A_{o}}{A_{FS}} \right) \Big|_{a_{i} \text{ is ON}} = \frac{\sum_{i=k+1}^{N} a_{i}}{\left( \sum_{i=1}^{k} a_{i} + \sum_{i=k+1}^{N} a_{i} \right)^{2}} = \frac{N-k}{N} \cdot \frac{1}{A_{FS}}$$

(3.25)

and

$$\frac{\partial}{\partial a_{i}} \left( \frac{A_{o}}{A_{FS}} \right) \Big|_{a_{i} \text{ is OFF}} = -\frac{\sum_{i=1}^{k} a_{i}}{\left( \sum_{i=1}^{k} a_{i} + \sum_{i=k+1}^{N} a_{i} \right)^{2}} = -\frac{k}{N} \cdot \frac{1}{A_{FS}}, \quad (3.26)$$

where the nominal values of a<sub>i</sub> are used for the evaluation.

Under the assumption of a common centroid geometry layout, the effect of the large gradients of variation can be ignored to the first order, and the short correlation distance noise dominates. The  $a_i$  can then be considered uncorrelated with equal variance  $\sigma_a^2$ . The variance of the ratio of the output over the full scale is

$$\sigma_{\frac{A_o}{A_{FS}}}^2 = \left[ k \left( \frac{\partial}{\partial a_i} \left( \frac{A_o}{A_{FS}} \right) \right|_{a_i \text{ is ON}} \right)^2 + (N - k) \left( \frac{\partial}{\partial a_i} \left( \frac{A_o}{A_{FS}} \right) \right|_{a_i \text{ is OFF}} \right)^2 \right] \sigma_a^2$$

(3.27)

or

$$\sigma_{INL(k)}^2 = \sigma_{\frac{A_o}{A_{FS}}}^2 = \frac{k(N-k)}{N} \cdot \frac{\sigma_a^2}{A_{FS}^2}$$

(3.28)

In terms of the nominal step size,

$$a = \frac{A_{FS}}{N} , \qquad (3.29)$$

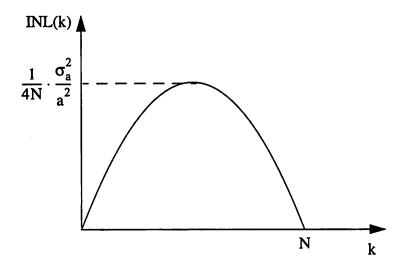

Figure 3.3 Variance of the integral nonlinearity at a step k.

we obtain

$$\sigma_{\text{INL(k)}}^2 = \frac{k(N-k)}{N^3} \cdot \frac{\sigma_a^2}{a^2} . \qquad (3.30)$$

This variance as a function of the step k is depicted in Figure 3.3. It is maximized when k=N/2

$$\max(\sigma_{\text{INL(k)}}^2) = \sigma_{\text{INL}\left(\frac{N}{2}\right)}^2 = \frac{1}{4N} \cdot \frac{\sigma_a^2}{a^2}. \tag{3.31}$$

Chapter 4 40

# Chapter 4

# **Test Structures**

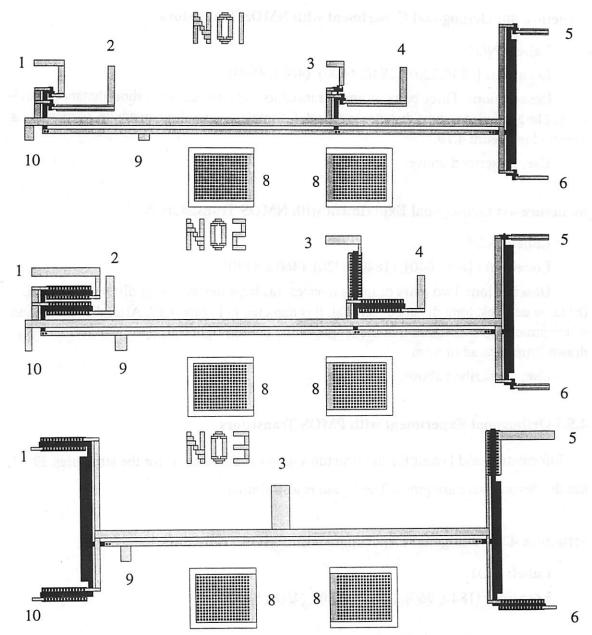

#### 4.1 Introduction

In this chapter we describe the test structures that we designed and fabricated in order to study variability. We used the Baseline Process of the Berkeley Microfabrication Laboratory. The minimum allowed polysilicon linewidth was  $2\mu m$ .

#### 4.2 General Information

These structures include:

- arrays of resistors and two dimensional arrays of transistors and capacitors to examine neighboring effects,

- arrays of pairs of transistors, resistors and capacitors of various sizes and distances, with which we will verify the validity of the mismatch models presented in chapter 2 and we will measure their coefficients,

- structures with which we will examine the effect of orientation in matching, and

- simple circuits, such as differential pairs and a two stage operational amplifier.

We will predict input offset based on the mismatch information of the individual devices using the methodology presented in chapter 3, and we will examine agreement with the measured values.

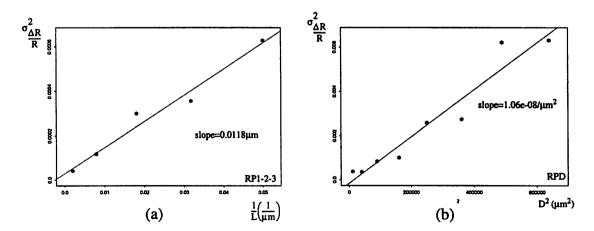

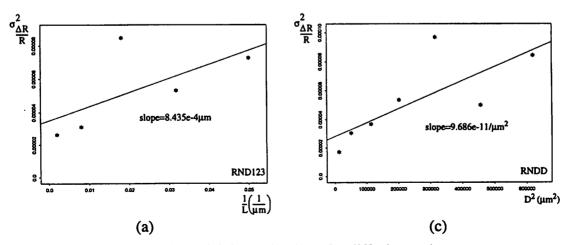

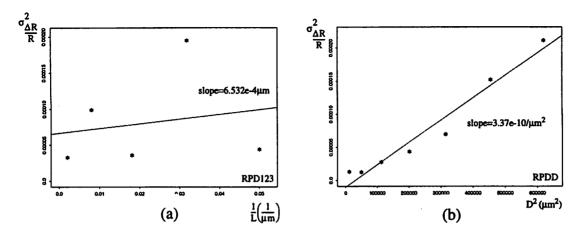

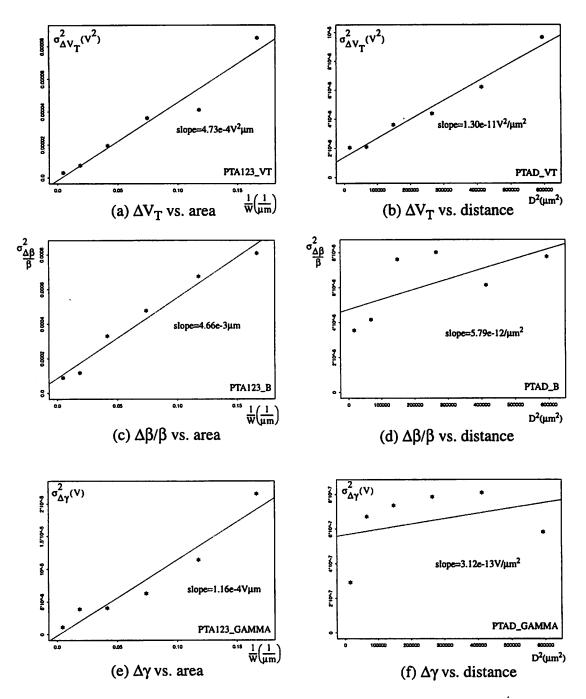

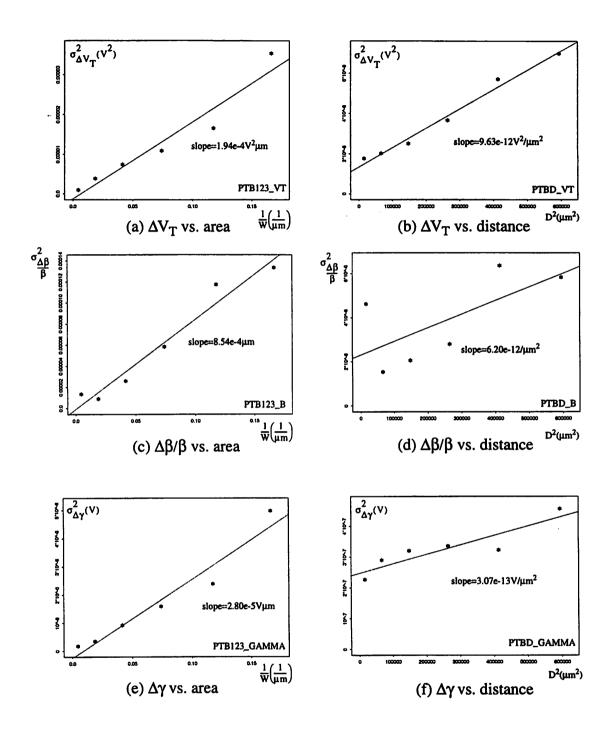

The area and distance coefficients to which we will refer are the coefficients  $S_A^2$  and  $S_D^2$  respectively of the mismatch model

$$\sigma_{\rm P}^2 = \frac{S_{\rm A}^2}{WL} + S_{\rm D}^2 \cdot D^2 \,, \tag{4.1}$$

presented in Chapter 2.  $\sigma_P^2$  is the variance of the mismatch, W and L represent the dimensions of the device, and D the distance between them.

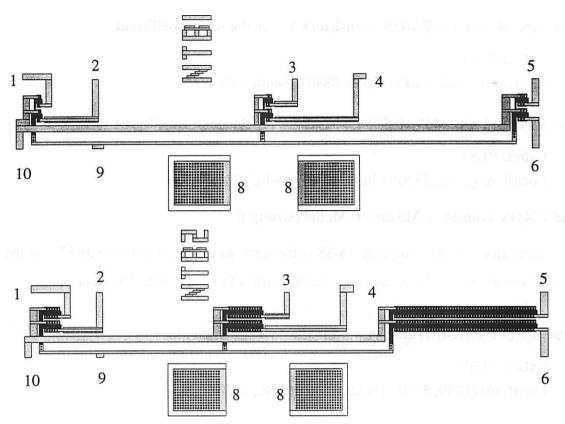

We used structures dedicated to the measurement of each coefficient. Arrays of pairs of small devices with minimum distance between the devices were used for the area coefficient in order to minimize the large gradient variation effect and emphasize the effect of the local variability. Arrays of large devices in long distances were used for the distance coefficient, to minimize the local variability effect and reveal the large gradient dependence.

In the transistor and the resistors structures for the area coefficient, one of the two dimensions is kept constant among the pairs. In this way the graph of mismatch versus area appears identical to the graph of the mismatch versus the varying dimension, and is not affected by discrepancies of the other dimension - which is common - from the nominal value.

In the transistor structures for the area coefficient, while the length L is kept constant, the widths W vary from pair to pair in a way that they are equally spaced on an axis  $1/\sqrt{W}$ . Graphs of mismatch standard deviation versus the inverse square root of the area and graphs of mismatch standard deviation versus the distance in [11] and [8], motivated us to distribute the widths in the this way. However, it is the mismatch variance, as given in (4.1) that is linearly dependent on the inverse area and the square of the distance. The measurements described in Chapter 5 showed that the error introduced in the estimation of the area coefficient by fitting a line between the mismatch standard deviation and the inverse square root of the area, and the distance coefficient by fitting a line between the mismatch standard deviation and the distance is in some cases significant. Mismatch variance versus inverse area will be used in Chapter 5 for the extraction of the area coefficient, although the points are not evenly distributed on the 1/area axis. The distance coefficient will be extracted from the graph of mismatch variance versus the square of the distance. For resistors, W is kept constant and L varies in a similar way.

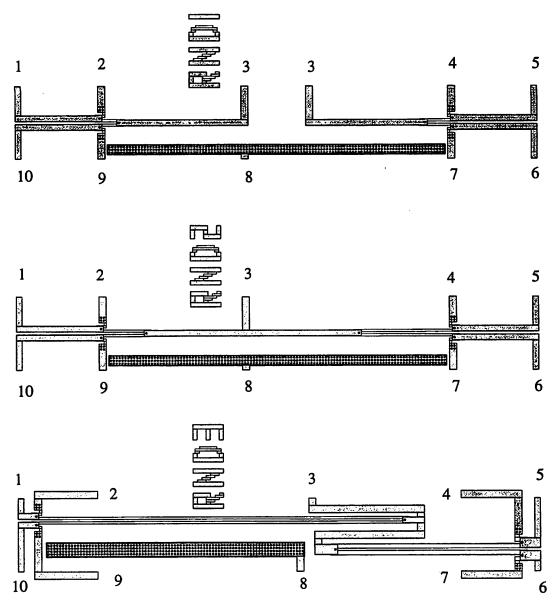

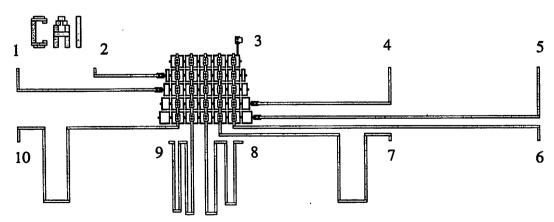

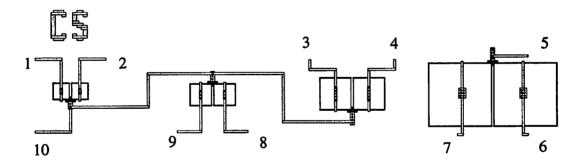

Figure 4.1 The common pad set of all the structures.

From the transistors, we will extract and examine variation in threshold voltage, current factor and body effect coefficient. The resistors with relatively low nominal value are measured with four point measurement while those will relatively high with two point measurement as is described in section 5.3.1.

All the structures are connected to the pad set shown in Figure 4.1. Only the number of the pad to which each wire is connected is shown in the layout of the structures below. The test structures are presented below in groups. For each test structure we present the identifying label printed next to it, its location on the chip, a short description, and a short reference to its use. The coordinates that describe the location are given with the convention that the leftmost bottom padset - that belongs to the scribe lane - has coordinates (0,0), the x-coordinate increases from the left to the right and the y-coordinate increases from the bottom to the top. More information about the organization of the die can be found in [19].

The use of a second metal layer has been avoided where possible, since there have been problems with it in the past in the Baseline Process of the Berkeley Microfabrication Laboratory. It has been used only for the two dimensional transistor arrays, i.e. the structures 23-26 below.

The structures 17 and 18 repeat 2 times in the die. All the rest structures repeat 3 times.

## 4.3 Resistor Structures

## 4.3.1 Resistor Arrays for Edge Effects Observation

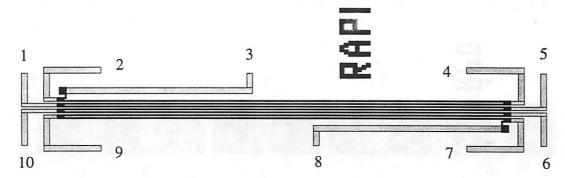

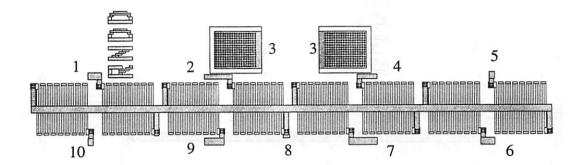

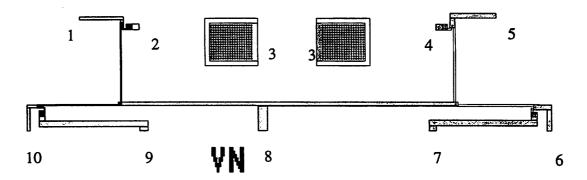

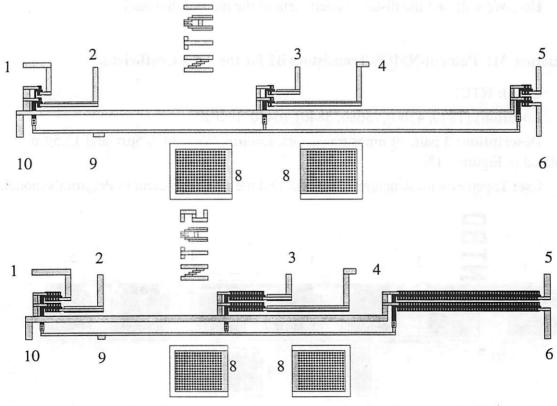

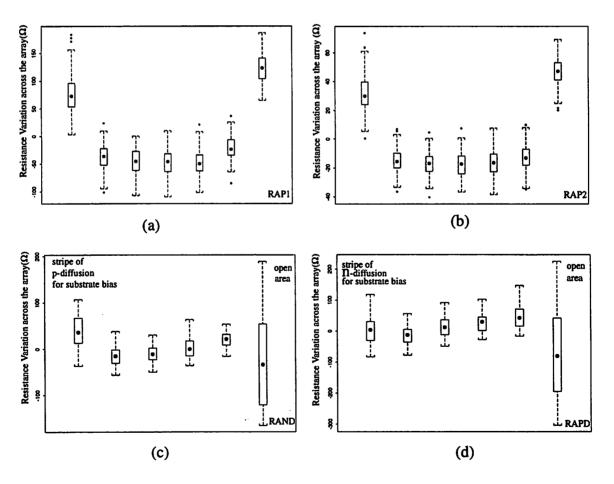

#### Structure 1: Array of polysilicon resistors 1.

Label: RAP1

Location: (920, 1280), (2760, 4800), (5520, 320).

**Description:** Array of 7 poly resistors, width=2μm, length=600μm distance=2mm, depicted in Figure 4.2. Four point measurements.

Use: We will observe if the resistors at the end of the array have different value than those in the middle.

#### Structure 2: Array of polysilicon resistors 2.

Label: RAP2

Location: (920, 1600), (2760, 5120), (5520, 640).

**Description:** Array of 7 poly resistors, width=4μm, length=600μm, distance=2μm. The layout is similar to this of structure 1.

Use: The same as for structure 1

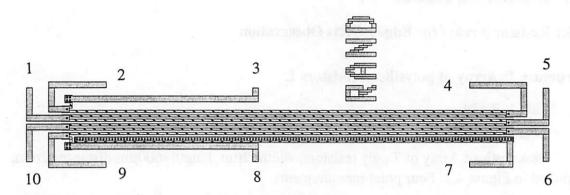

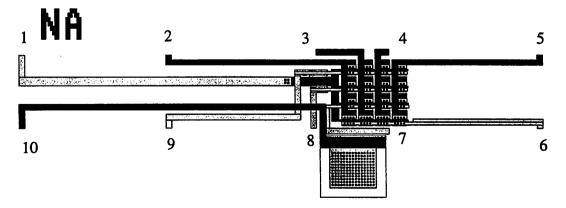

#### Structure 3: Array of N-diffusion resistors.

Label: RAND

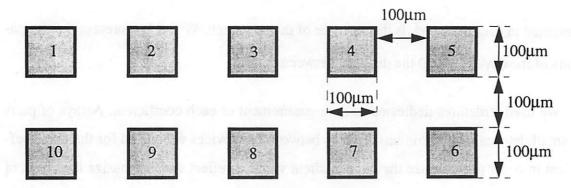

Location: (920,1920), (2760, 5440), (5520, 960).

**Description:** Array of 6 n-diffusion resistors, width= $3\mu$ m, length= $600\mu$ m, distance= $3\mu$ m, depicted in Figure 4.3.

Use: The same as for structures 1 and 2. We will also observe if the resistor who is closest to the diffusion stripe that biases the substrate has different value than the rest.

Figure 4.2 Array of Polysilicon Resistors 1.

Figure 4.3 Array of N Diffusion Resistors.

## Structure 4: Array of P-diffusion resistors.

The information about this structure is the same as for structure 3, but these are p-diffusion resistors. The layout is similar to this of structure 3, also.

Label: RAPD

Location: (920, 2240), (2760, 5760), (5520, 1280).

# 4.3.2 Polysilicon Resistor Mismatch Model

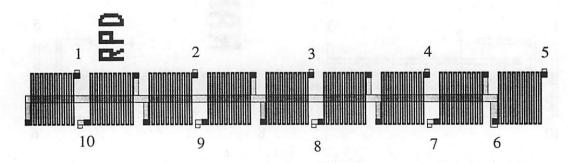

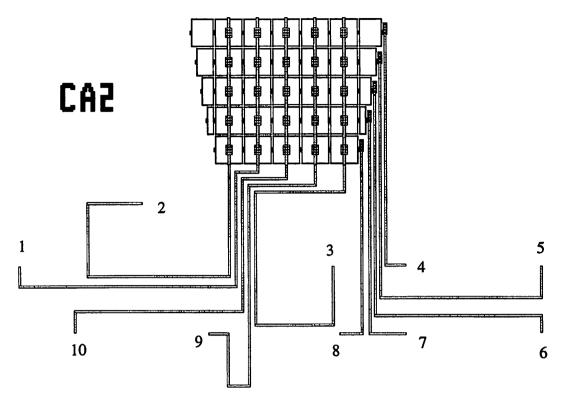

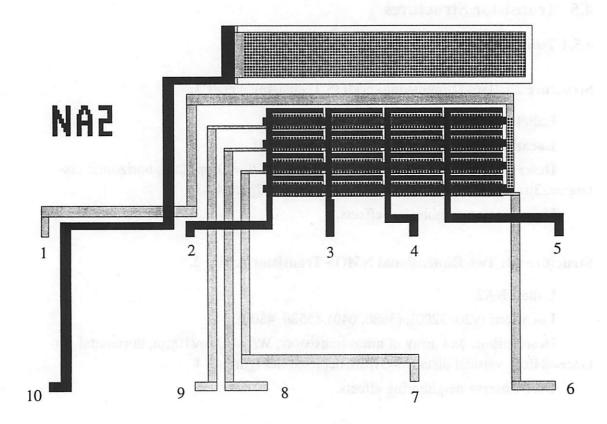

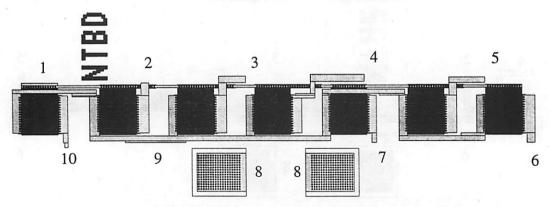

# Structure 5: Polysilicon Resistors for the Distance Coefficient.

Label: RPD

Location: (4600, 3520), (5520, 2560), (6440, 6080).

**Description:** Array of 9 poly resistors, width=2μm, length=1748μm folded, distance =100μm, depicted in Figure 4.4. Two point measurements.

Use: We will find the distance coefficient of the mismatch model.

Figure 4.4 Array of Polysilicon Resistors for the Distance Coefficient.

Figure 4.5 Pairs of Polysilicon Resistors 1, 2 and 3 for the Area Coefficient.

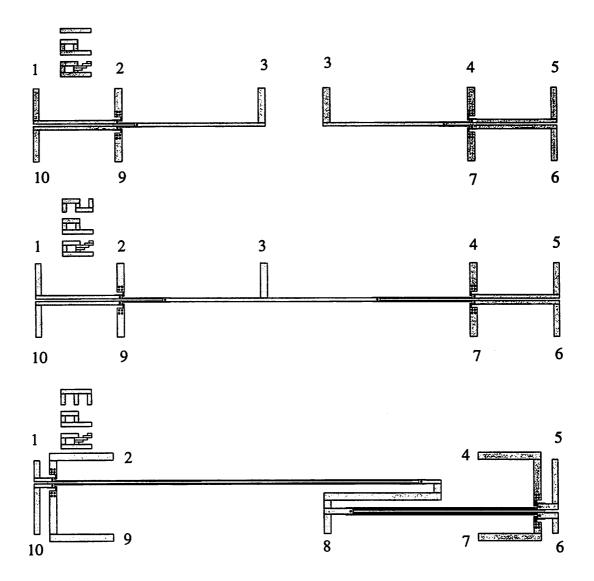

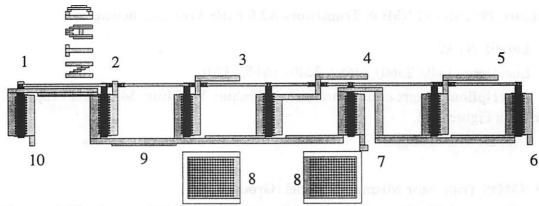

# Structure 6: Pairs of Polysilicon Resistors 1 for the Area Coefficient.

Label: RP1

Location: (4600, 2560), (5520, 1600), (6440, 5120).

**Description:** 2 pairs of poly resistors, width= $2\mu m$ , lengths= $20\mu m$  and  $31.5\mu m$ , distance= $2\mu m$ , depicted in Figure 4.5. Four point measurements.

Use: Together with the structures 7 and 8, we will find the area coefficient of the mismatch model.

Chapter 4 46

#### Structure 7: Pairs of Polysilicon Resistors 2 for the Area Coefficient.

Label: RP2

**Location:** (4600, 2880), (5520, 1920), (6440, 5440).

**Description:** 2 pairs of poly resistors, width=2μm, lengths=55.5μm and 125μm, distance=2μm, depicted in Figure 4.5. Four point measurements.

Use: Described above.

## Structure 8: Pairs of Polysilicon Resistors 3 for the Area Coefficient.

Label: RP3

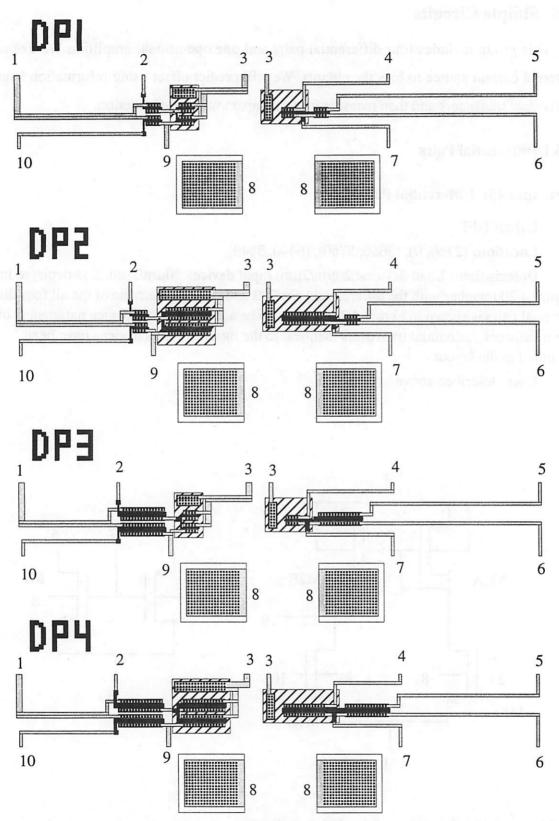

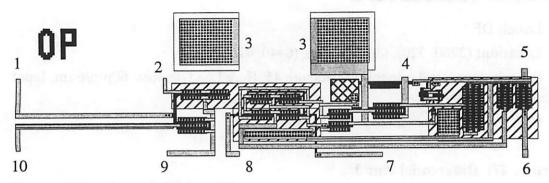

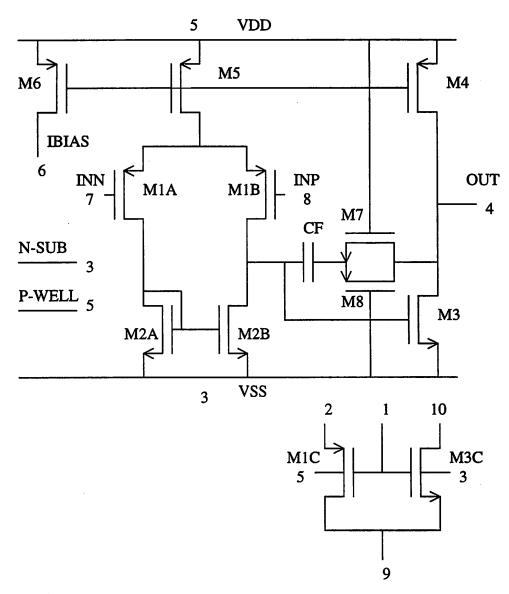

**Location:** (4600, 3200), (5520, 2240), (6440, 5760).