# **Automated Low-Power ASIC Design For Speech Processing**

## **Engling Yeo**

#### **ABSTRACT**

Recent developments in Hyper's design space exploration and high-level synthesis techniques have brought the realization of automated synthesis of memory-intensive, low-power implementations closer. This work describes the design path taken to synthesize the front end of a speech recognition chip. It starts from the Hyper high-level synthesis tool by looking at possible alternatives at the algorithmic level, as well as using suitable transformations on the control flow data graph (CDFG) representation within Hyper. The flowgraph is then mapped onto an architecture, and more power analysis provides feedback for possible power improvements. Finally, with the help of the LagerIV architectural-level tools, a silicon layout suitable for fabrication is generated

# **Table Of Contents**

| 1.0 | Intro | oduction                                                                | 2  |

|-----|-------|-------------------------------------------------------------------------|----|

|     | 1.1   | Prediction Model Fundamentals                                           | 3  |

|     |       | 1.1.1 Linear Prediction (LPC) Model                                     | 3  |

|     |       | 1.1.2 Bank of Filter Analysis and Perceptual Linear Prediction (PLP)    |    |

|     |       | 1.1.3 Relative Spectral, Perceptual Linear Predictive model (RASTA-PLP) | 8  |

|     | 1.2   | The Hyper synthesis Environment                                         | 9  |

|     | 1.3   | SPA - Stochastic Power Analysis                                         | 12 |

|     | 1.4   | LagerIV                                                                 | 13 |

| 2.0 | High  | Level Analysis                                                          | 15 |

|     | 2.1   | FFT  <sup>2</sup> , Power Spectrum                                      |    |

|     | 2.1   | 2.1.1 Radix 2 algorithm                                                 |    |

|     |       | 2.1.2 Radix-2-Winograd Algorithm                                        |    |

|     |       | 2.1.3 Split-Radix Algorithm                                             |    |

|     |       | 2.1.4 Choice of Algorithm for FFT                                       |    |

|     | 2.2   | Critical Band Filters                                                   |    |

|     | 2.2   | 2.2.1 Direct Computation                                                |    |

|     |       | 2.2.2 Improved Algorithm                                                |    |

|     | 2.3   | Modeling of Critical Band Filter outputs                                |    |

|     | 2.3   | 2.3.1 Estimation of temporal derivative                                 |    |

|     |       | 2.3.2 Equal Loudness preemphasis                                        |    |

|     |       | 2.3.3 Intensity-loudness Power Law                                      |    |

|     |       | 2.3.4 Natural Log                                                       |    |

|     |       | 2.3.5 Exponential                                                       |    |

|     | 2.4   | Inverse Discrete Fourier Transform, Autocorrelation Coefficients        | 36 |

|     | 2.5   | Durbin Analysis[3]                                                      | 37 |

|     | 2.6   | Cepstral Conversion                                                     | 38 |

|     | 2.7   | Clock Period                                                            | 38 |

|     | 2.8   | Behavioral Simulation of RASTA-PLP System                               |    |

| 2.0 |       | •••                                                                     | 40 |

| 3.0 |       | itecture                                                                |    |

|     | 3.1   | Clock Timing                                                            |    |

|     | 3.2   | Merging of Hardware EXUs                                                | 43 |

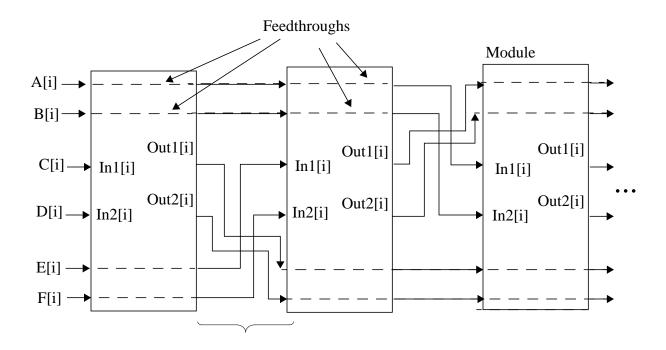

|     | 3.3   | Interconnect                                                            | 44 |

|     | 3.4   | Registers                                                               | 46 |

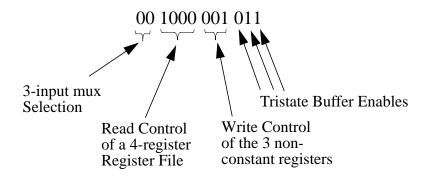

|     | 3.5   | Control Signals                                                         | 48 |

|     | 3.6   | Example of a typical Datapath cell: 16-bit Adder                        | 49 |

|     | 3.7   | Layout                                                                  | 54 |

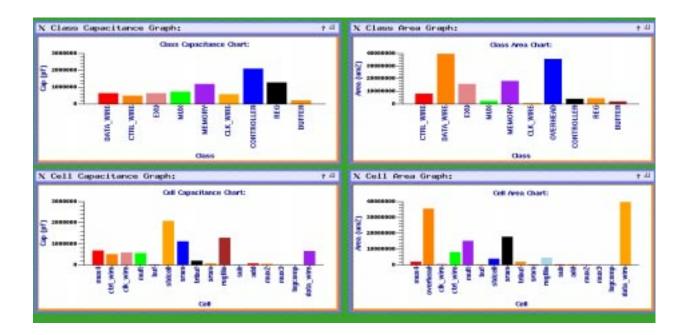

| 4.0 | SPA   | Analysis of FFT Architecture                                            | 57 |

| T.U |       | •                                                                       |    |

|     | 4.1   | Input Description                                                       |    |

|     |       | T.1.1 SOL IV ADE HAIISIAUVII                                            |    |

|     |          | 4.1.2   | Bdsyn to CDL translation                 | 61  |

|-----|----------|---------|------------------------------------------|-----|

|     | 4.2      | Simulat | tions                                    | 62  |

|     | 4.3      | Power A | Analysis                                 | 63  |

|     |          | 4.3.1   | Controllers and Registers                | 64  |

|     |          | 4.3.2   | Memories                                 |     |

|     |          | 4.3.3   | Interconnect, Data/Control Buses         | 69  |

|     |          | 4.3.4   | EXU                                      | 70  |

| 5.0 | Concl    | usion   |                                          | 73  |

| 6.0 | Refere   | ences   |                                          | 74  |

| Ann | andivas: | Silogo  | Descriptions                             |     |

| App | A        | _       | 2 Algorithm                              | 76  |

|     | В        |         | -Winograd Algorithm                      |     |

|     | C        |         | adix Algorithm                           |     |

|     | D        |         | l Algorithm for Critical Band Filtering  |     |

|     | E        | -       | ed Algorithm for Critical Band Filtering |     |

|     | F        |         | ng of Critical Band Filter Outputs       |     |

|     | г<br>G   |         | orithm                                   |     |

|     | Ü        | U       |                                          |     |

|     | Н        | •       | ential Algorithm                         |     |

|     | I        |         | Algorithm                                |     |

|     | J        |         | 's Algorithm                             |     |

|     | K        | Cepstra | l Analysis                               | 125 |

# List of Figures

| FIGURE 1.1  | Speech synthesis model based on LPC Model                              | 4  |

|-------------|------------------------------------------------------------------------|----|

| FIGURE 1.2  | Physiological model of the human ear                                   | 7  |

| FIGURE 1.3  | Non-Linear Transformation to Bark frequency.                           | 8  |

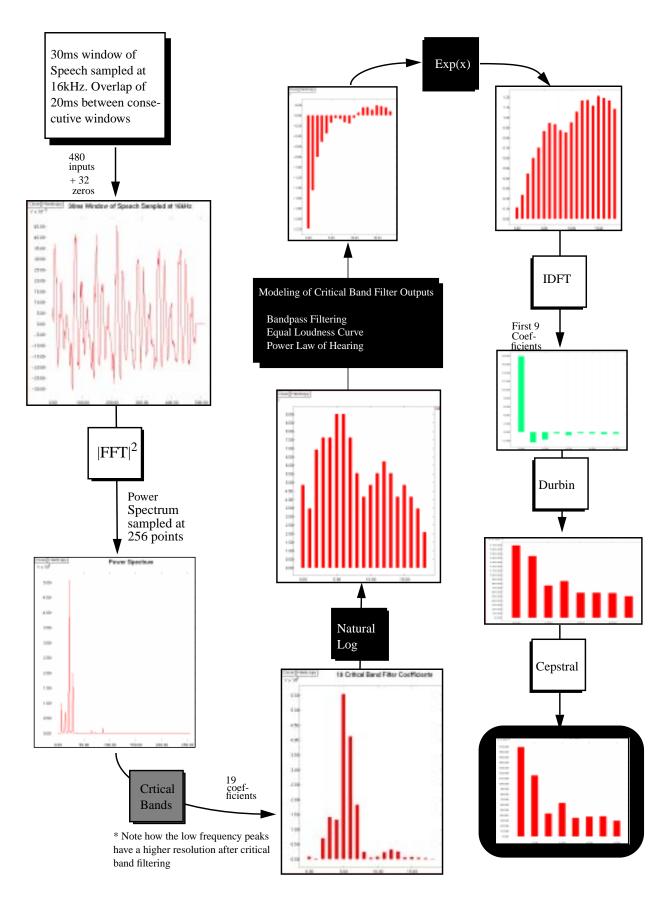

| FIGURE 1.4  | Flowgraph of RASTA-PLP                                                 | 9  |

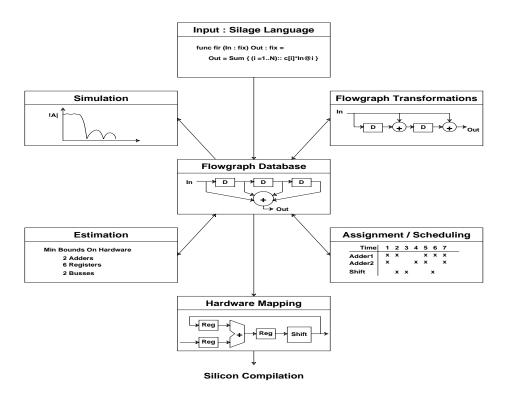

| FIGURE 1.5  | The Hyper synthesis environment                                        | 11 |

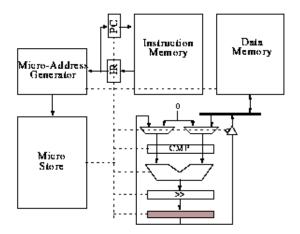

| FIGURE 1.6  | Architecture of micro coded instruction set processor                  | 13 |

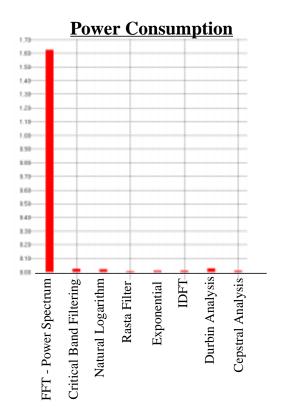

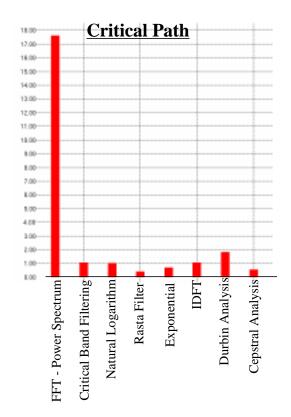

| FIGURE 2.1  | Initial Estimates of Blocks in RASTA-PLP                               | 16 |

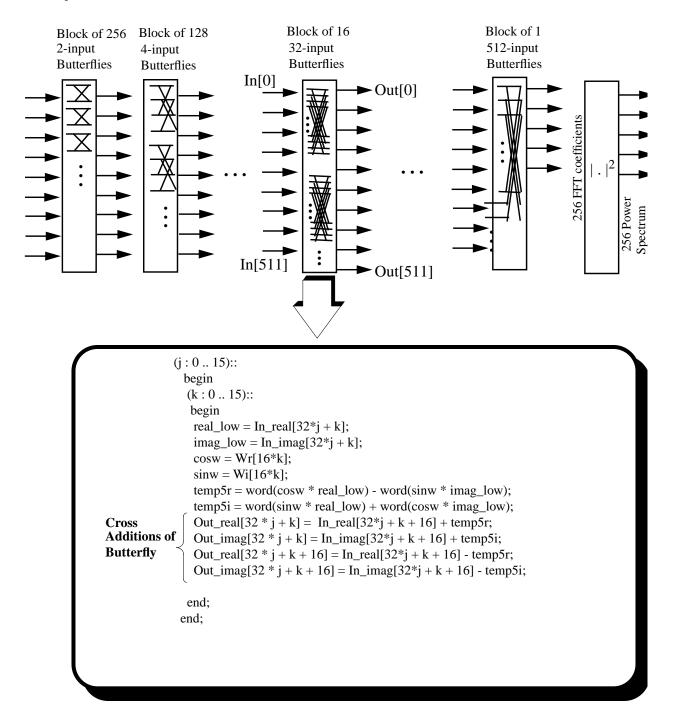

| FIGURE 2.2  | Radix-2 FFT. 9 stages of butterflies and a $ . ^2$ operation           | 18 |

| FIGURE 2.3  | In-place storage of Intermediate results                               |    |

| FIGURE 2.4  | Radix-2-Winograd Algorithm                                             | 21 |

| FIGURE 2.5  | Loop Unrolling during translation from Fortran code to Silage code     | 23 |

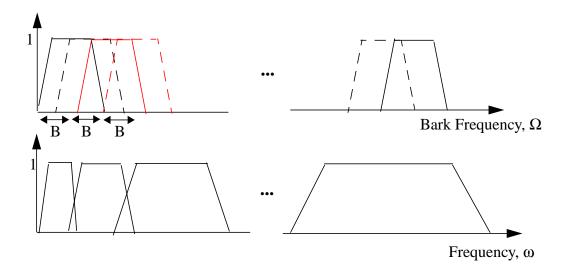

| FIGURE 2.6  | Critical Band Filters.                                                 | 27 |

| FIGURE 2.7  | Implementation of the Critical Band Filtering in Frequency             |    |

|             | Domain                                                                 | 28 |

| FIGURE 2.8  | Filtering that implements Estimation of the temporal derivative        | 32 |

| FIGURE 2.9  | 16-bit Log detector for MSB                                            | 34 |

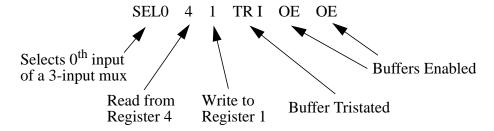

| FIGURE 2.10 | Behavioral Simulation of System                                        | 41 |

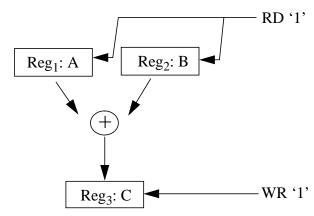

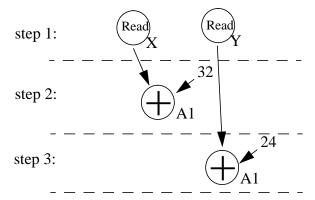

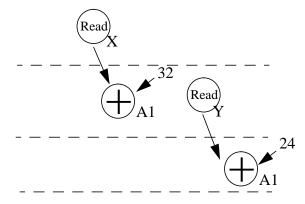

| FIGURE 3.1  | Example of an addition operation in one clock cycle                    | 42 |

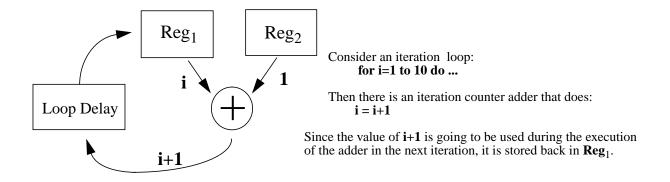

| FIGURE 3.2  | Typical Sentences within Nested Loops found in Silage description      |    |

|             | of the Critical Band Filters                                           | 44 |

| FIGURE 3.3  | Improved Scheduling of regular Silage code.                            | 46 |

| FIGURE 3.4  | Read/Write conflicts and constraints of Register files.                | 47 |

| FIGURE 3.5  | Race Conditions during simultaneous READ and WRITE                     | 48 |

| FIGURE 3.6  | Declaration of Modules in a Typical datapath cell of a 16-bit adder    | 50 |

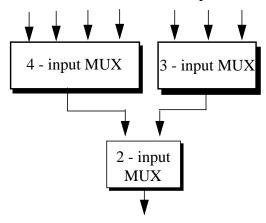

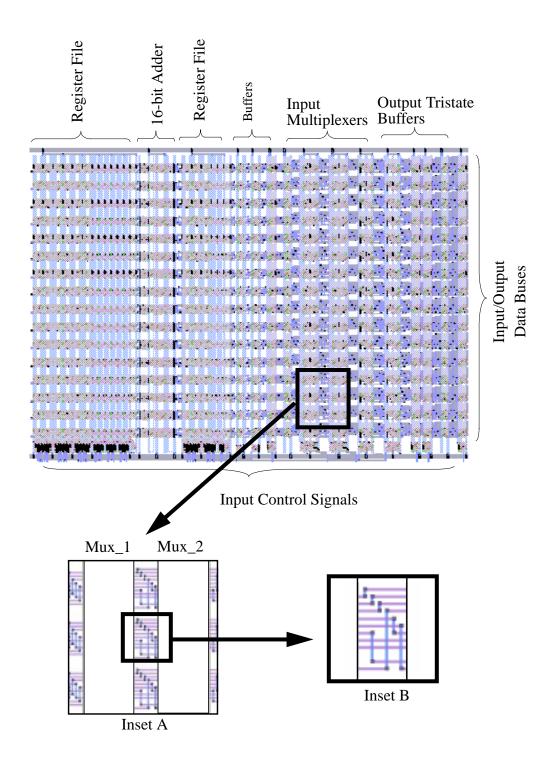

| FIGURE 3.7  | Selection of input from 7 input data buses.                            | 51 |

| FIGURE 3.8  | Placement strategy for a representative bit-slice of a datapath        |    |

|             | complex                                                                | 52 |

| FIGURE 3.9  | A 16-bit adder with input multiplexers, output buffers and register    |    |

|             | files                                                                  | 53 |

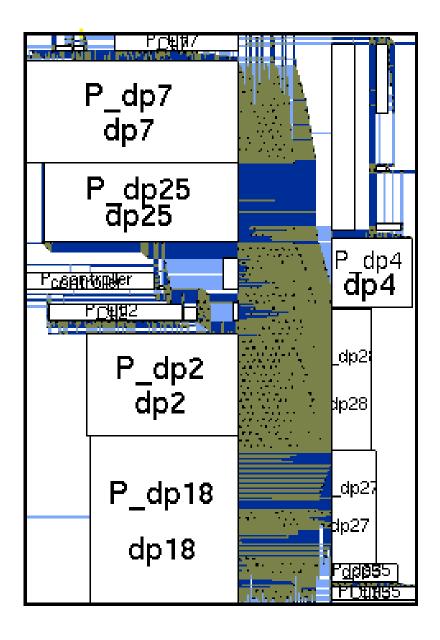

| FIGURE 3.10 | Layout of FFT                                                          | 55 |

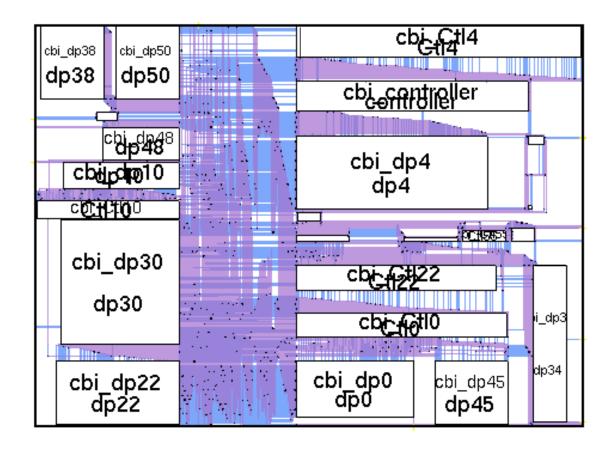

| FIGURE 3.11 | Layout of Critical Band Filters                                        | 56 |

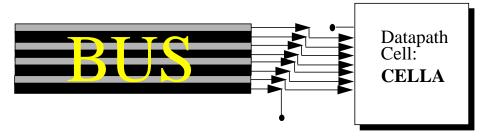

| FIGURE 4.1  | Hardwiring Connection between data bus and datapath cell, CELLA        | 59 |

| FIGURE 4.2  | Example of a 32-bit register file with 4 registers in both ADL and SDL |    |

|             | descriptions                                                           |    |

| FIGURE 4.3  | Approximately 3.2s segment of speech sampled at 16kHz                  |    |

| FIGURE 4.4  | Graphical Output of SPA Analysis for FFT block                         |    |

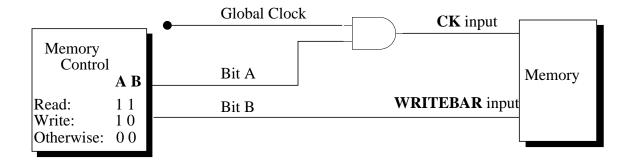

| FIGURE 4.5  | Gating CLK input to memory                                             | 68 |

# List of Tables

| TABLE 1.  | Comparison of counts before and after Common Subexpression            |    |

|-----------|-----------------------------------------------------------------------|----|

|           | Elimination                                                           | 19 |

| TABLE 2.  | Comparison of EXU counts for a 512-point FFT using Radix-2 and        |    |

|           | Radix2-Winograd                                                       | 21 |

| TABLE 3.  | Comparison of EXU counts for a 512-point FFT using Radix2-            |    |

|           | Winograd and Split-Radix Algorithms                                   | 24 |

| TABLE 4:  | Summary of algorithms used for  FFT 2 block                           | 25 |

| TABLE 5.  | Comparisons of EXU counts between algorithm for Critical Band         |    |

|           | Filtering                                                             | 30 |

| TABLE 6.  | Estimates obtained with Vdd=1.2V; Clock Period 550ns                  | 36 |

| TABLE 7.  | Variation of properties with clock rate for FFT block                 | 39 |

| TABLE 8.  | Estimates of individual blocks with Clock period 537ns, Vdd = 1.2V    | 40 |

| TABLE 9.  | Use of Registers in FFT and Critical Band Filters blocks              | 49 |

| TABLE 10. | Hardware Allocation for 16-bit Adder and related Control Signals and  |    |

|           | Registers                                                             | 51 |

| TABLE 11. | Hardware Allocation for  FFT 2 block                                  | 54 |

| TABLE 12. | Hardware Allocation for critical band filters block                   | 54 |

| TABLE 13. | Layout Dimensions using 1.2mm SCMOS Design Rules (1 = 0.6mm)          | 55 |

| TABLE 14. | Comparison between input languages to LagerIV and SPA                 | 57 |

| TABLE 15. | List of Control Variable differences between library cells written in |    |

|           | ADL and SDL                                                           | 59 |

| TABLE 16. | Operations used in VHDL to simulate bit operations                    | 61 |

| TABLE 17. | Output of SPA Analysis for FFT block                                  | 63 |

| TABLE 18. | Register Count obtained from Hyper Estimator based on CDFG            | 65 |

| TABLE 19. | Memory Accesses obtained from Hyper Estimator based on CDFG           | 65 |

| TABLE 20. | Effect of MIN-TERM parameter in ADL description                       | 66 |

| TABLE 21. | Power Breakdown of Memories                                           | 68 |

| TABLE 22. | Comparison of data wire area.                                         | 70 |

## 1.0 Introduction.

The objective of this work is to design the front end of a speech recognition system to handle the acoustic signal processing. The algorithm adopts a proposal by Hermansky et. al. [6], RASTA-PLP, which is a refinement over the standard linear prediction (LPC) model.

Speech-recognition systems comprise a wide collection of disciplines, including statistical pattern recognition, communication theory, signal processing, combinatorial mathematics, and linguistics, amongst others. Typically speech recognition starts with the digital sampling of speech. The next stage is the acoustic signal processing, which converts the speech waveform to some type of parametric representation. Most techniques include spectral analysis; e.g. LPC analysis, MFCC, cochlea modeling and many, many more. The next stage is recognition of phonemes, groups of phonemes and words. This stage can be achieved by many processes such as DTW (Dynamic Time Warping) [2], HMM (hidden Markov modelling)[2], NNs (Neural Networks)[2], expert systems [2] and combinations of techniques. HMM-based systems are currently the most commonly used and most successful approach.

Following the current wave of interest in low-power portable applications such as Berkeley's personal communications terminal, InfoPad, the power issues will be emphasized. A speech recognition system is an excellent substitute for the keyboard on portable devices that require human input.

Hyper's [1] hardware library of low-power cells are used in the design. The entire behavioral input description is done in Silage[4]. Employing different flowgraph transformations, various area, speed, and power optimization techniques were explored. The estimates provided by Hyper gave a quick comparison of the relative effectiveness between various sets of transformations.

After the scheduling and hardware mapping steps, architectural power analysis was done using SPA. It identifies the bottlenecks of power consumption. The information is used to suggest further improvements to the architecture.

As a final step, the architectural description is converted to silicon layout using the LagerIV CAD tools. Running IRSIM on the extracted layouts provides some power figures that can be compared with the SPA results.

### 1.1 Prediction Model Fundamentals

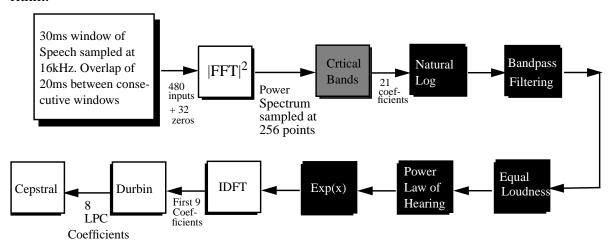

Some details of the algorithm are left out here, and described in more rigorous fashion in Chapter 2. This section is intended to give an overall view of the RASTA-PLP algorithm, leading to the block diagram in Figure 1.4. Chapter 2 will discuss the algorithm used to implement each of the blocks, as well as the design space exploration.

### 1.1.1 Linear Prediction (LPC) Model

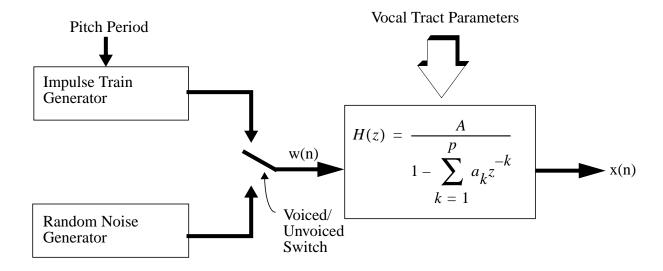

The greatest common denominator of all recognition systems is the acoustic signal processing. A common front-end is the linear predictive coding (LPC) analysis [2]. The analysis assumes that the speech synthesis consists of a digital filter, H(z), whose excitation source is chosen from either an impulse train (voiced speech) or a white noise generator (unvoiced sounds) depending on a voiced/unvoiced switch. The switch is controlled by the voiced/unvoiced character of the speech. The filter has an all-pole transfer function which is controlled by the vocal tract parameters characteristic of the speech being produced. The aim is therefore to predict the  $a_k$  coefficients of the filter H(z), also known as the LPC coefficients. Figure 1.1 shows a  $p^{th}$  order autoregressive (AR) transfer function, with p poles.

**FIGURE 1.1** Speech synthesis model based on LPC Model

From the transfer function, a given speech sample at time n, x(n) can be represented as a linear combination of the past p speech samples,

(EQ 1.1)

Hence, the autocorrelation function can be related by

$x^*$ : complex conjugate of x.

(EQ 1.2)

A  $p^{\rm th}$  order AR model has therefore, p unknowns,  $a_I$  through  $a_p$ . EQ1.3 shows p sets of EQ1.2 with the value of k ranging from 1 through p arranged in a matrix form. Since the speech samples are real the autocorrelation function is symmetric, i.e.  $r_x(k) = r_x(-k)$ . If there is a way to estimate the first p+1 entries  $(r_x(0)$  through  $r_x(p))$  of the short term autocorrelation function, the LPC coefficients can then be predicted by solving EQ1.3 with Durbin's algorithm[3] for Yule-Walker equations, since the  $p \times p$  matrix is Toeplitz symmetric:

(EQ 1.3)

The autocorrelation function is obtained by an inverse Fourier transformation of the power spectrum. The short term (20ms~30ms window) spectrum is approximated by a periodogram estimate[4], defined as

(EQ 1.4)

The Fourier transform of the speech samples is usually obtained with a 256-point or 512-point FFT on a speech input sampled between 8kHz to 16kHz. The transfer function of the vocal tract, H(z) is assumed to remain unchanged throughout the short time segment.

A very important LPC parameter set, which can be derived directly from the LPC coefficients, is the set of LPC cepstral coefficients,  $c_m$ . These are the coefficients of the Fourier transform representation of the log magnitude spectrum. Bogert et al. [17] observed that the logarithm of the power spectrum of a signal containing an echo hasa n additive periodic component due to

the echo, and thus its Fourier transform, the cepstrum, should exhibit a peak at the echo delay. The cepstral coefficients are associated with homomorphic analysis, which have been shown to be a more robust, reliable feature set for speech recognition than LPC [18].

The recursion used is given by the following equations, with A and  $a_m$  variables defined as in EQ1.1 and EQ1.3.

$$c_0 = \ln A^2$$

$$c_m = a_m + \sum_{k=1}^{m-1} \left(\frac{k}{m}\right) c_k a_{m-k} \qquad 1 \le m \le p$$

$$c_m = \sum_{k=1}^{m-1} \left(\frac{k}{m}\right) c_k a_{m-k} \qquad m > p$$

(EQ 1.5)

## 1.1.2 Bank of Filter Analysis and Perceptual Linear Prediction (PLP)

LPC models all frequencies equally well. Unfortunately, this is not consistent with the human auditory devices. It was shown by Hermansky [5] that recognizers equipped to utilize the perceptually based spectra deliver recognition accuracy comparable to that of LPC, but with smaller order autoregressive models, i.e. fewer LPC coefficients, thus gaining the advantage of a reduced computational load.

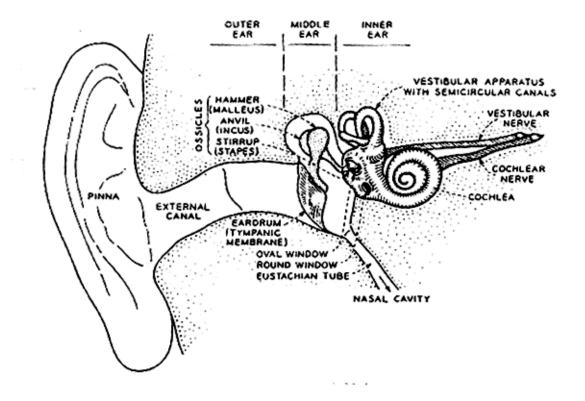

The frequency analysis step in human speech processing is performed by the inner ear. It is accomplished by waves travelling along the basilar membrane in the inner ear (cochlea). Higher frequencies resonate near the input while lower frequencies resonate progressively nearer the apex of the cochlea. The natural frequency scale of the ear, which corresponds to the total length (~35mm) of the basilar membrane, has a resolution of about 1.5mm, giving rise to about 24 "critical bands" which span the audible range of approximately 20Hz~20000Hz.

Automated Low Power ASIC Design for Speech Processing

FIGURE 1.2 Physiological model of the human ear

The PLP model suggests that the human perception of frequencies can be mimicked by passing the sampled speech through a bank of Q bandpass filters, giving the signals:

$$s_{i}(n) = s(n)*h_{i}(n) \quad \text{for } 1 \le i \le Q$$

$$= \sum_{m=0}^{M-1} h_{i}(m)s(n-m)$$

(EQ 1.6)

However, instead of using EQ1.6, the critical band filtering is done in the frequency domain. The same effect could be achieved by weighting the FFT coefficients according to the magnitude frequency response of a filter bank. The center frequencies of the filters are spaced equally on a Bark scale from 0Hz through 8Hz. Each filter spans a common bandwidth on a Bark

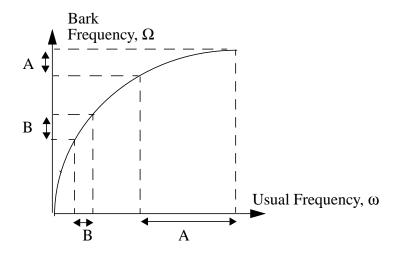

scale. The Bark scale is a non-linear transformation of the usual frequency scale, given below in EQ 1.7. From Figure 1.3, it is clear that for the same bandwidth in Bark scale, band A, which is centered at a higher frequency, spans a wider range of actual frequencies then band B. This mimics the progressively coarser resolution of human perception at increasing frequencies.

Frequency:  $\omega$  rad s<sup>-1</sup> Bark Frequency:  $\Omega$

(EQ 1.7)

**FIGURE 1.3** Non-Linear Transformation to Bark frequency.

## 1.1.3 Relative Spectral, Perceptual Linear Predictive model (RASTA-PLP)

The PLP model, however still suffers from linear distortions in the communications channel. A simple muffling of speech could change the LPC coefficients sufficiently to fail a recognizer trained on clean data. Hermansky et al. [6] proposed a refinement to LPC to make it more tolerant to channel modulation effects (convolutional noise). The following were added in their technique called RASTA-PLP (Relative Spectral, Perceptual Linear Predictive):

•Bandpass filtering estimates the temporal derivative of the Bark-scale-transformed spectrum by drawing a regression line through spectral values obtained in the last 5 consecutive windows.

•Add the equal loudness curve and raise the coefficients by power of 0.33 to simulate the power law of hearing. The raise power function is simplified by using a natural log, followed by a multiplication of factor 0.33, and an inverse logarithm (exponential function). i.e.  $c^{0.33} = \exp(0.33 * \log(c))$ .

The complete block diagram is shown in Figure 1.4. The non shaded blocks make up the most basic LPC analysis model. The critical band filtering block (medium shading) implements the PLP improvement, while the most heavily shaded blocks complete the RASTA-PLP algorithm.

**FIGURE 1.4** Flowgraph of RASTA-PLP

## 1.2 The Hyper synthesis Environment

The Hyper system is an integrated synthesis environment for real time applications. It uses the Silage[7] language for behavioral description input of the application. Silage is a signal-flow language developed especially for DSP specifications. It is an applicative language whose fundamental operation is function application. The term Static Single Assignment (SSA) is used to describe the computation method of Silage. SSA avoids any false dependencies between intermediate data, thus helping the exploitation of parallelism. Other advantages include built-in stream and temporal operators for handling of continuous streams of discrete-time inputs, and built-in data types that allow user specification of data bit widths.

Hyper parses the Silage description and compiles a Control/Data flow graph (CDFG). The CDFG represents the algorithm as a flow graph consisting of nodes, data edges, and control edges. The nodes represent primitive data operators such as adders, comparators and memory read/writes. The data edges represent data precedences between these nodes. Control edges are introduced to enforce extra precedence rules between nodes (e.g. the execution time of operation X has to trail the execution of operation Y by at least N clock cycles). Aside from the standard arithmetic operations, the CDFG allows a number of macro control flow operations such as loops and if-the-else blocks. The introduction of those control statements results in a hierarchical graph. The body of a loop or a conditional is represented by a sub-graph, which is contracted into a single node at the next higher hierarchy level. The hierarchical representation has the advantages of compactness and descriptiveness. It also preserves any structural hints from the designers.

The CDFG serves as a central database to which all other Hyper tools (Figure 1.5), such as min-bound estimations, flow graph transformations, and assignment/scheduling, refer when executed. The results of these operations are back annotated onto the database. The following is a brief description of each class of operations

- •.Memory Management: Performs memory moduleselection, memory merge and address generation. Memory module selection assigns an appropriate memory module from the hardware library for each array in the application. Memory merge allows 2 or more different arrays to be merged onto a single memory module. Address generation reads the memory address annotated on the array read/ write nodes in the CDFG and creates nodes that will be executed as any other data operation to generate the address.

- **Module Selection:** Selects an appropriate hardware library module for each flow graph operation.

- •Estimation: Derives the minimum and maximum bounds on the required hardware resources. This information will serve as an initial solution and will help select the next synthesis operation to perform.

**FIGURE 1.5** The Hyper synthesis environment

- **Transformation:** Manipulates the signal flow graph of the algorithm to improve the final implementation, without changing the input-output relation. Typical transformations are retiming, loop unrolling and common-subexpression elimination and pipelining.

- Allocation, Assignment and Scheduling: Selects the amount of hardware resources (execution units, registers and interconnect), needed for the execution of the algorithm. Bind each flow graph operation to a particular hardware unit and time slot.

- •Hardware Mapping: Maps the allocated, assigned and scheduled flow graph (called the decorated flow graph) onto the available hardware blocks. The result of this process is a structural description of the processor architecture in the SDL[8] language, which serves as the input to the LagerIV silicon assembly tool suite.

Furthermore, the Hyper simulator can be invoked after any of the synthesis steps (though Hardware Mapping does not alter the CDFG) to verify the functionality of algorithm and the correctness of the transformations performed. Also, when run in the Bit-True mode, which simulates with a fixed point representation of the data with bit-widths as specified by the user, the simulator can optimize and check the value of a number of performance parameters, such as the signal to noise ratio, or the effects of truncation on the transfer function.

Hyper allows the designer to play the area-time-power trade-off game. The effect of the various built-in transformations are easily reflected by the Estimator results. Also, Hyper provides comparisons between different algorithms pertaining to the same behavior.

## 1.3 SPA - Stochastic Power Analysis

SPA is a tool that allows a designer to obtain predictions of area and power consumption at the architectural level. The input to SPA is a register-transfer level description of the architecture to be analyzed and a set of input vectors. Both textual and graphical results are available, with area and power estimates broken down by hardware class and type of component.

The primary RTL input describes the architecture under consideration. Conceptually, this consists of the information displayed in Figure 1.6. In particular, it contains a (possibly hierarchical) description of datapath blocks used in the chip, as well as the interconnect network joining these blocks. SPA uses a textual architectural description language (ADL) for this purpose. The information about the interaction between the blocks is embodied in the control path of the chip. Using a control description language (CDL), the control flow of the design can be described as a set of state tables. These tables specify how the next state and outputs of the control module relate to the present state and inputs. In order to maintain a relatively high level of abstraction, CDL allows the user to specify control signals and states as enumerated (symbolic) types rather than bit vectors. For example, the instructions to a memory can take the form of "READ" or "WRITE" rather then obscure binary codes.

**FIGURE 1.6** Architecture of micro coded instruction set processor

SPA makes use of power and area models that are stored in a hardware library. Unlike the high-level power estimator used in Hyper which uses a white noise input to the design, SPA accounts for the effect of hardware activity on power consumption. It collects activity statistics for each bus and module through a complete functional simulation of the architecture.

SPA performs three types of analysis, interconnect analysis, area analysis, and power analysis. Interconnect analysis estimates the physical capacitance associated with wires in the design. The result of this is essential for analysis of both area and power. Power estimation is performed using the Dual Bit Type (DBT) [13] model for datapath and memory elements and the Activity-Based Control (ABC) [13] model for control path elements.

## 1.4 LagerIV

LagerIV is a CAD tool suite to enable rapid prototyping of Integrated Circuits. Designs can be described in high-level languages / descriptions and converted to layout for fabrication. The conversion is enabled by the use of structure processors and layout generators. A structure processor performs a description/netlist transformation on an Oct Structural Master View (SMV), and generates an Oct Structural Instance View (SIV). Structural processors used include **dpp** for datapath modules and **bdsyn** for control cells. A layout generator performs the physical place-

| ment and signal routing given an SIV netlist description and generates an Oct physical view and <b>Magic</b> output. Layout generators used include <b>Flint</b> and <b>Stdcell</b> . |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                                                                       |  |  |  |  |

## 2.0 High Level Analysis

The design path begins with a description of the algorithm for the various blocks in Silage. For each of the major blocks, several algorithms performing the same functionality are investigated. The Hyper simulator provides a functionality verification while the Hyper estimator gives an initial profile of each algorithm by estimating power consumption, memory accesses, area, etc.

Initial estimates of all the blocks (Figure 2.1) in the RASTA-PLP algorithm revealed the power consumption and critical path of the FFT block to be well above any other blocks. From a power prospective, that is where most of the design effort will be directed towards. In addition, other then the FFT and the Critical Band Filtering blocks, the remaining processes, such as the Exponential, Equal Loudness and Power Law blocks, have fairly straightforward and short computations, leaving less room for design space exploration. The main effort of the high level analysis is therefore pointed at the FFT and Critical Band Filtering blocks, while similar work on the remaining blocks will see less detailed. The emphasis on power continues down to the architectural design level. The selected algorithms for the FFT and the Critical Band Filtering blocks will be mapped onto a Register Transfer Level (RTL), and have their layouts generated eventually. Further architectural analysis of the FFT block will be provided by a power and area breakdown using SPA.

The use of Silage description has inherent advantages compared to more commonly known procedural languages such as C. However Silage requires the use of manifest loops and manifest array indices which, as will be seen, is an obstacle to the description of less structured, and less regular algorithms. In such cases, the appropriateness of a C++ input description approach will be explored.

The sampling rate of the speech input was chosen to be 16kHz. A 30ms window is applied on the sampled speech to obtain 480 data points. This is zero-filled to make up the 512 data points needed for a 512-point FFT. Consecutive 30ms-windows have an overlap of 20ms. The throughput of the RASTA front end must therefore be less than 10ms. In order to meet the time criteria, a

2-staged pipe-lining is used. The 512-point FFT takes up most of the first stage while the rest of the front-end is computed in the second stage.

**FIGURE 2.1** Initial Estimates of Blocks in RASTA-PLP block showing a disproportionately large amount of power consumed in the FFT block.

## 2.1 |FFT|<sup>2</sup>, Power Spectrum

The periodogram estimate of the power spectrum of a 30ms segment of speech consisting of M samples is defined as

where

(EQ 2.1)

$$X(e^{j\omega}) = \sum_{n=0}^{M-1} x(n)e^{-j\omega n}$$

(EQ 2.2)

The power spectrum can therefore be estimated by the magnitude square of the FFT of the input samples. The constant factor  $^{1}/_{M}$  is ignored in the computations as doing so will simply multiply every autocorrelation coefficient by a factor of M. Equation 1.3 remains unchanged, and therefore, does not affect the final cepstral values.

The 480 speech samples contained in the 30ms window are added with 32 zeros in order to make a Radix-2 FFT (512-point FFT) feasible. Since the inputs are all real, the power spectrum is symmetrical about  $w=\pi$ , or about the 256th point of the FFT. Thus only the first 256 output-coefficients are required, and they represent the power spectrum from 0 through 8kHz.

A number of FFT algorithms exists. It is found that algorithms that reduce the computation complexity in terms of number of additions and multiplications, will on the other hand, have less regularity in their structures. Memory address generation and number of memory accesses also proves to be a big issue since the memory size is massive (512 for each array). In particular, the following choices were examined:

- Radix 2 algorithm

- Radix 2-Winograd Algorithm

- Split Radix (2,4) Algorithm

## 2.1.1 Radix 2 algorithm

The  $2^9$ =512 point radix-2 FFT can be realized as a cascade of 9 blocks. Each block consists of repetitions of either a 2-input, 4-input,..., 256-input or 512-input butterfly respectively. There are 2 x 256 complex twiddle factors accounting for distinct values of  $\cos({}^{k\pi}/_{256})$  and  $\sin({}^{k\pi}/_{256})$ , for 0<=k<256. These are stored in two 256-word ROMs.

In Silage, each block is realized as a nested loop of depth 2. The code within Figure 2.2 shows that of a typical block. The last four statements in the deepest nest implements the cross additions (complex additions) in a butterfly. Later blocks have fewer butterflies with more inputs, so the *j* variable iterates over fewer values, while the k variable iterates over more values.

**FIGURE 2.2** Radix-2 FFT. 9 stages of butterflies and a  $|.|^2$  operation.

Note that the array address indices of inputs and outputs in the Silage statements differ only by either a constant addition or a constant multiple. Common subexpression elimination for the address generation of these array indices was therefore feasible. Instead of computing the value of, say (32 \* j + k + 16) and (32\* j + k) every time those address are needed, (32\* j + k) is computed only once during each iteration of the innermost loop, and 16 is added to this value also only once.

TABLE 1. Comparison of counts before and after Common Subexpression Elimination

| Module                       | Count Before CSE | Count After CSE |

|------------------------------|------------------|-----------------|

| Add                          | 38142            | 17150           |

| Multiply                     | 26624            | 12032           |

| Twiddle Factor Memories      | 4096             | 4096            |

| Estimated Energy Consumption | 12.7μJ           | 8.3µJ           |

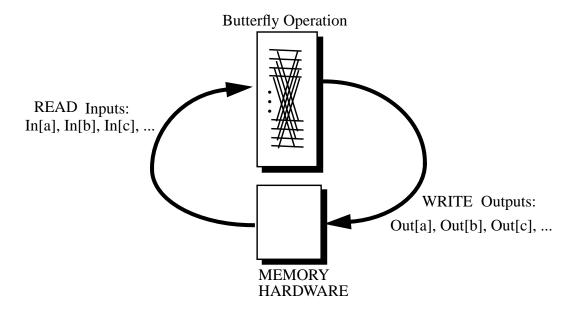

It is observed that each butterfly produces outputs which occupy exactly the same addresses as the inputs. The above example, for instance, obtains inputs from In[32\*j+k] and In[32\*j+k+16], and outputs to Out[32\*j+k] and Out[32\*j+k+16]. Thus, using only one pair of input memory hardware for the real and imaginary parts respectively, each iteration of the butterfly obtains a number of inputs from the memories and overwrites the inputs with its outputs. However, the description of such overwriting of array values will violate the static single assignment (SSA) checks in Silage. This problem is solved by using different array names in the Silage description for the outputs of each block, and then implementing in-place storage of these different arrays by manually altering the intermediate CDFG.

The simplicity of the radix-2 algorithm is attractive. However, at a clock period of 550 ns (Section 2.6 describes the choice of clock frequency), the critical path was 23807 cycles. This works out to ~10.3 ms which exceeds the required throughput of the RASTA front end. Although more pipe-lining might solve the throughput constraint, this will invariably increase the power consumption and area as additional hardware is required to handle the parallel computations of a pipelined algorithm.

**FIGURE 2.3** In-place storage of Intermediate results

## 2.1.2 Radix-2-Winograd Algorithm

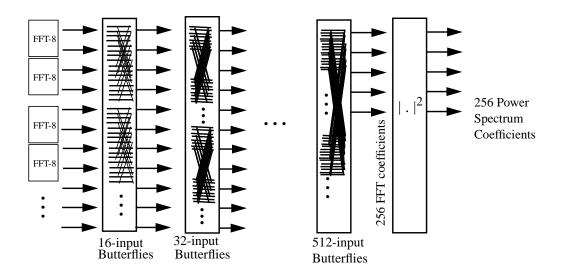

In the Radix-2-Winograd Algorithm, the first 3 blocks (2-input, 4-input, and 8-input) of the Radix-2 algorithm are replaced with a single block consisting of 32 Winograd 8-point FFTs [11]. The approach takes advantage of the fact that for the first 3 blocks of the Radix-2 algorithm, more then half the number of complex twiddle factors are either  $\pm$  1 or  $\pm$  j, while the rest of the them correspond to  $\exp(j\pi/4)$  and  $\exp(j\pi/4)$ . These last 2 terms, which have equal real and imaginary parts, constitute to the only non-trivial multiplication, a factor of 0.707106 ( $^1/_{\text{Sqrt}(2)}$ ). Each 8-point Winograd FFT, uses only 2 multiplications, compared to an 8-point Radix-2 algorithm which requires 8 multiplications. Also, instead of reading the twiddle-factors from memory, the only non-trivial twiddle-factor,  $^1/_{\text{Sqrt}(2)}$  is stored in a constant register. This eliminates the need for address generation of the twiddle factors as well as expensive memory accesses. Appendix B shows the Silage description of the Radix2-Winograd algorithm. The Winograd FFT, is described in Silage as the function *ffi8*. It is clean, has no iteration loops, and consists primarily of cheap additions and subtractions.

As a result, the critical path is reduced to 17607, a reduction of 26%. This proves to be critical, as it is possible to achieve a throughput below the 10ms criteria, without any further pipe-

lining. At the same time, the reduction in computational complexity also leads to a 20% reduction in power consumption.

TABLE 2. Comparison of EXU counts for a 512-point FFT using Radix-2 and Radix2-Winograd

| Module                            | Radix-2 | Radix2-<br>Winograd |

|-----------------------------------|---------|---------------------|

| Add                               | 14590   | 12230               |

| Subtract                          | 5632    | 4928                |

| Multiplie                         | 12032   | 9472                |

| Log Comparator                    | 2558    | 1670                |

| Transfer                          | 9990    | 7756                |

| Register Accesses                 | 109064  | 87233               |

| Memory Accesses                   | 20224   | 16128               |

| TOTAL EXU COUNT                   | 174090  | 139417              |

| CRITICAL PATH                     | 23807   | 17607               |

| ESTIMATED ENERGY CONSUMP-<br>TION | 8.3µJ   | 6.6µЈ               |

**FIGURE 2.4** Radix-2-Winograd Algorithm. The FFT-8 is handled by a Winograd small-N FFT.

## 2.1.3 Split-Radix Algorithm

The split-radix (radix-2 and radix-4) algorithm combines the relatively small number of addition terms in a radix-2 algorithm, and the smaller number of multiplications in a radix-4 algo-

rithm. At any stage, a N-DFT is decomposed into a  $^{N}/_{2}$ -DFT using radix-2, and two  $^{N}/_{4}$  DFT using radix-4.

$$X_{2k} = \sum_{n=0}^{\frac{N}{2}-1} W_{\frac{N}{2}}^{nk} \left( x_n + x_{\frac{N}{2}+n} \right)$$

$$X_{4k+1} = \sum_{n=0}^{\frac{N}{4}-1} W_N^{nk} W_N^{n} \left[ \left( x_n - x_{\frac{N}{2}+n} \right) + j \left( x_{n+\frac{N}{4}} - x_{n+\frac{3}{4}N} \right) \right]$$

(EQ 2.3)

$$X_{4k+3} = \sum_{n=0}^{\frac{N}{4}-1} W_N^{nk} W_N^{3n} \left[ \left( x_n + x_{\frac{N}{2}+n} \right) - j \left( x_{n+\frac{N}{4}} - x_{n+\frac{3}{4}N} \right) \right]$$

(EQ 2.4)

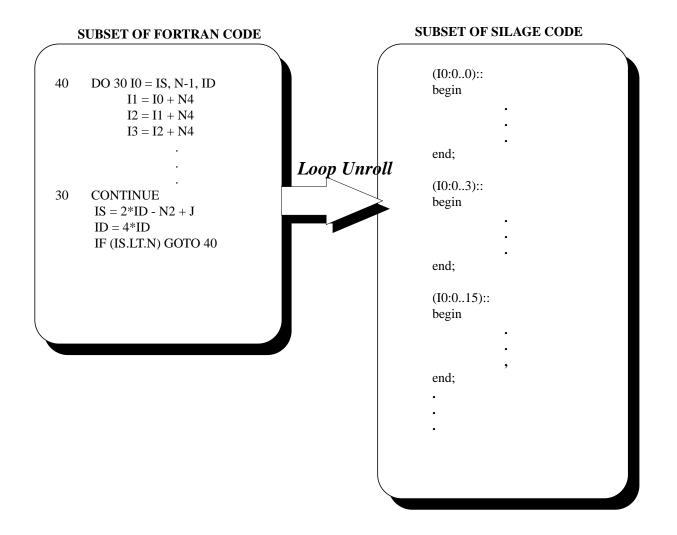

Due to asymmetry in the decomposition, the structure of the algorithm is more involved than either of the previous two algorithms. Appendix C shows the Silage description of the Split-Radix Algorithm. It is highly unstructured, and difficult to understand. Unlike the previous methods where each stage can be described as a recursive decomposition and therefore, as manifest loops, the split-radix algorithm distinguishes between the decomposition of  $X_{2k}$  and  $X_{4k+1}$ ,  $X_{4k+3}$ . A Fortran description written by Sorenson[12] implements the split radix in loops that have non-manifest, loop counters that have variable lower and upper bounds. A similar realization in Hyper is difficult with Silage as the input description language because the current Silage parser accepts only manifest loop counters. Therefore, a complete loop unroll of the Fortran code is necessary, resulting in a long and irregular series of loops.

On the other hand, the problems associated with the Split Radix algorithm may be solved if a C++ input description language to Hyper were available. Typical C++ syntax would allow both non-manifest loops and multiple assignments of variables. This would also solve the problem of having excessive arrays, which was the side-effect of the loop unrolling, which in turn, was needed to satisfy the manifest loops requirement in Silage.

(EQ 2.5)

**FIGURE 2.5** Loop Unrolling during translation from Fortran code to Silage code.

It was discovered that the split-radix algorithm enjoys more then a twofold reduction in critical path to 8307. The power consumption saw an impressive improvement of about 30%. Table 3 gives a comparison between Radix2-Winograd algorithm and the Split-Radix algorithm. It shows significant improvement in terms of number of additions and multiplications. Similar

Common Subexpression Elimination transformations as that described earlier in Section 2.1.1 were also employed to achieve the following figures.

TABLE 3. Comparison of EXU counts for a 512-point FFT using Radix2-Winograd and Split-Radix Algorithms

| Module                            | Radix2-<br>Winograd | Split-Radix |

|-----------------------------------|---------------------|-------------|

| Add                               | 12230               | 8818        |

| Subtract                          | 4928                | 4224        |

| Multiplies                        | 9472                | 6016        |

| Log Comparator                    | 1670                | 946         |

| Transfer                          | 7756                | 5277        |

| Register Accesses                 | 87233               | 62570       |

| Memory Accesses                   | 16128               | 12800       |

| TOTAL EXU COUNT                   | 139417              | 100651      |

| CRITICAL PATH                     | 17607               | 8307        |

| ESTIMATED ENERGY CONSUMP-<br>TION | 6.6µЈ               | 4.6µЈ       |

### 2.1.4 Choice of Algorithm for FFT

The Radix2-Winograd algorithm is chosen as the algorithm to implement the FFT due to its ability to meet the target throughput, as well as it overall regularity which simplifies the implementation and lowers amount of overhead.

The Radix2-Winograd algorithm is a swift and obvious improvement over the Radix-2 algorithm. With a little modification of the Silage description, a respectable amount of power savings is achieved. The extent of irregularity introduced by the Winograd-8-point FFT is also minimal. Recall that the 8-point Winograd FFT is implemented as a efficient code with mostly additions and subtractions which have a low cost of power consumption.

It is worth noting, however, that the initial Radix-2 algorithm is extremely regular. The Silage code basically implements each of the 9 blocks in the same way, differing only in the iteration bounds and constants in the array indices. In terms of architecture, the Radix-2 can be implemented easily with only one structural block that is repeated 9 times with the appropriate modification of the iteration bounds and other constant values.

The comparison between the Radix2-Winograd and the Split Radix algorithm, however, is less clear cut. While the Split Radix algorithm described in the last section has obvious gains in terms of both execution counts as well as power estimates, the description in Silage has been difficult, and even looks awkward when it finally works. Moreover, the less regular structure also makes it less desirable then the radix-2-Winograd algorithm. Section 3.3, will describe how regularity in the algorithm can translate to a more compact architecture with less interconnect overhead, leading consequently to reduced power consumption. Regular algorithms also typically require less control. Though there has been some effort to detect and quantify such useful properties of algorithms [15] and [16], transformations for enhancing these properties are largely unexplored. There is therefore reason to believe that the difference of power consumption between the Radix2-Winograd algorithm and the Split-Radix algorithm may not be as pronounced as the numbers suggested in Table 3.

Currently, work is being done to allow C++ as the input behavioral language for Hyper. This will allow a more concise description of the split radix algorithm, including provision for non-manifest loop counters that will make the difference in both description and implementation.

Table 4: Summary of algorithms used for |FFT|<sup>2</sup> block

| Algorithm                    | Power Reduction Technique                                                                                  | Incremental Power Improvement | Benefits/Disadvantages                |

|------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------|

| Radix -2 (Appendix A)        | Common Subexpression<br>Elimination                                                                        | 36% Power<br>Reduction        | Regularity of Structure               |

| Radix2-Winograd (Appendix B) | Partly Different Algorithm  Twiddle factors no longer need to be stored in arrays ==> Reduced Memory Power | 20% Power<br>Reduction        | Fewer Twiddle Factors Less Regularity |

Table 4: Summary of algorithms used for |FFT|<sup>2</sup> block

| Algorithm                | Power Reduction Technique                                                                                                                                        | Incremental Power Improvement                  | Benefits/Disadvantages                                                                                |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Split Radix (Appendix C) | Wholly Different Algorithm  Sizable reduction in additions and multiplications. Also reduced number of other EXU counts, e.g. memory accesses, comparators, etc. | 30% Power<br>Reduction over<br>Radix2-Winograd | Asymmetry of decomposition leads to difficult behavioral description in Silage.  Much less regularity |

## 2.2 Critical Band Filters

Zwicker [10] proposed that the bandwidths of the critical bands are approximately constant on the Bark scale,  $\Omega$  whose relation with the usual frequency scale,  $\omega = 2\pi f$ , was given in EQ 1.7. Schroeder's [9] proposal of the asymmetric critical band filtering function  $F(\Omega)$  (frequency response) in EQ 2.3 for a filter centered at  $\Omega_{o_i}$  is approximated by piecewise linear function given in EQ2.4.

$$10\log F(\Omega - \Omega_0) = 15.8 + 7.5(\Omega - \Omega_0 + 0.5) - 17.5\sqrt{1 + (\Omega - \Omega_0 + 0.5)^2}$$

(EQ 2.6)

Critical band filtering is done in the frequency domain since both the frequency response of the critical band filters as well as the FFT of the signal are known. The power spectrum consists of 256 distinct samples that span 0 through 8kHz. The frequency response of the bank of filters is sampled at a resolution of  $\frac{8kHz}{256} = 31.25Hz$ . The power spectrum coefficients are then

weighted correspondingly by the magnitude of these samples. The 19 bandpass filters, are centered at equal Bark intervals, **B**, and span the frequency interval 0 through 8kHz.

$$\Psi_{i}(\Omega) = \begin{cases} 0 & \text{for } \Omega - \Omega_{i} < -1.3 \\ 10^{2.5(\Omega - \Omega_{i}^{+0.5})} & \text{for } -1.3 < \Omega - \Omega_{i} <= -0.5 \\ 1 & \text{for } -0.5 < \Omega - \Omega_{i} <0.5 \\ 10^{-(\Omega - \Omega_{i}^{-0.5})} & \text{for } 0.5 <= \Omega - \Omega_{i} <2.5 \\ 0 & \text{for } \Omega - \Omega_{i} > 2.5 & \Omega_{i} = i \times \mathbf{B} \\ i \in [1, 19] \end{cases}$$

(EQ 2.7)

**FIGURE 2.6** Critical Band Filters. Filters are centered at equal Bark intervals, **B**.

In accord with the RASTA-PLP, the first sample (d.c.) is copied from sample at  $\Omega$ =B, and last samples (centered at 8kHz) is copied from sample at  $\Omega$ =19B to make a total of 21 samples spanning 0 to 8kHz.

## 2.2.1 Direct Computation

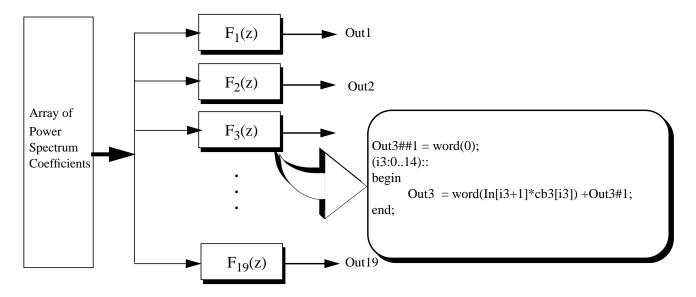

The initial algorithm for computing the critical-band outputs consists of 19 loops. Each loop essentially performs the critical-band masking. It uses an iterative multiply-add to sum the multiplication of the power spectrum coefficients with the height of the masking curve. A typical loop is shown in the inset of Figure 2.7.

**FIGURE 2.7** Implementation of the Critical Band Filtering in Frequency Domain. Inset shows description of a typical filter. cb3[i] is the height of the i<sup>th</sup> sample of the window centered at  $\Omega$ =3B (Bark frequency scale). The corresponding power spectrum coefficient, In[i], is weighted by the constant stored in cb3[i], and the product is updated to the iterating sum Out3.

In this algorithm, each filter in the bank of filters works independently of one another, and therefore appears to have a high degree of parallelism. In order to exploit any form of this concurrency property, there must be a way to simultaneously read more then one filter input, from the array of |FFT|<sup>2</sup> coefficients. The hardware used in Hyper does not allow multiple simultaneous read/writes from the same memory. Hyper does however permit partitioning of an array such that different ranges of elements of the array may reside in different memory hardware. Multiple simultaneous read/writes from the same array is thus possible as the data access will be made from different memories. Nevertheless, due to the overlap of frequencies between consecutive filter bands, some of the array elements of the power spectrum coefficients will have to be repeated in more then one partitioned memory. The total size of the partitioned memories will be necessar-

ily greater then 256, which is the number of distinct values in the array. In this case, increased concurrency is traded off for additional memory size, which can lead to higher power cost of memory accesses. The high level of concurrency is usually an important property, but here, where the 10ms limit is ample even when the filter outputs are computed serially (not concurrently), it would be a waste of power to operate the filter functions in parallel.

Besides requiring additional hardware, running the filters in parallel also required an excessive 832 reads (per set of sample inputs) from the 256 power spectrum coefficients. This is the result of the filters operating independently, and the extensive overlap between consecutive bands. Each power spectrum coefficient usually falls within the bandwidth of 3 or 4 neighboring filters. This undue number of reads is not power efficient as energy is required for additional address generation and memory accesses.

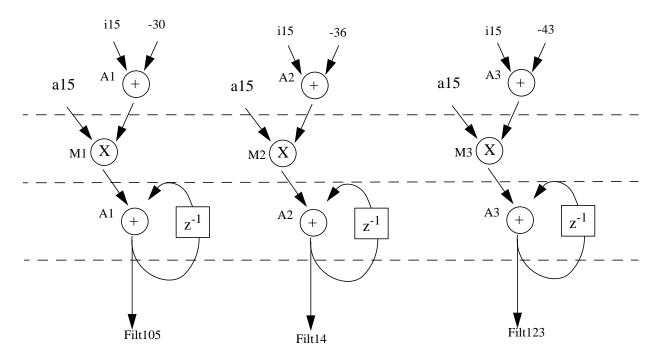

## 2.2.2 Improved Algorithm

To overcome the problem with excessive read operations, the 19 loops are taken apart, and replaced with 30 loops which represents the run-length of the overlapped power spectrum coefficients. For instance, if In[62] through In[72] fall within the windows centered at  $\Omega$ =11B, 12B, 13B, and 14B, the following loop covers part of the 11<sup>th</sup>, 12<sup>th</sup>, 13<sup>th</sup> and 14<sup>th</sup> critical bands:

```

/*

* In: 62..72::

*/

Filt11_6##1 = Filt11_4;

Filt12_5##1 = Filt12_3;

Filt13_3##1 = Filt13_1;

Filt14_1##1 = word(0);

(i17:62..72)::

begin

a17 = In[i17];

Filt116 = word(a17 * cb11[i17-36]) + Filt11_6#1;(1)

Filt125 = word(a17 * cb12[i17-43]) + Filt12_5#1;(2)

Filt133 = word(a17 * cb13[i17-52]) + Filt13_3#1;(3)

Filt141 = word(a17 * cb14[i17-62]) + Filt14_1#1;(4)

end;

```

where Filt11\_X, Filt12\_X, Filt13\_X, and Filt14\_X are the iterating sums for the 11<sup>th</sup>, 12<sup>th</sup>, 13<sup>th</sup>, and 14<sup>th</sup> critical bands respectively. This maneuver resulted in exactly 256 reads for the 256 power spectrum coefficients. Despite the increase from 19 loops to 30 loops, which would also require more control power due to increased control activity, the reduced EXU counts, primarily

due to reduced memory accesses, as well as address generation computations, overcomes this negative effect.

TABLE 5. Comparisons of EXU counts between algorithm for Critical Band Filtering

| Module                            | Original Direct<br>Computation                           | Improved Algorithm |

|-----------------------------------|----------------------------------------------------------|--------------------|

| Add                               | 2461                                                     | 1903               |

| Multiply                          | 832                                                      | 837                |

| Log Comparator                    | 832                                                      | 255                |

| Transfer                          | 5                                                        | 22                 |

| Register Accesses                 | 10011                                                    | 7584               |

| Memory Accesses                   | 1683                                                     | 856                |

| TOTAL EXU COUNT                   | 15824                                                    | 11715              |

| CRITICAL PATH                     | 3328                                                     | 1042               |

|                                   | (Filter outputs are computed serially, not concurrently) |                    |

| ESTIMATED ENERGY CONSUMP-<br>TION | 327nJ                                                    | 238nJ              |

The improved algorithm reads a single input, and computes the partial sum of several band coefficients. In the example above, each input read into *a17* is used to compute the four instructions (1), (2), (3), and (4). The partial sums can be done simultaneously. The assignments have no data-dependencies, lending to a certain amount of parallelism in the algorithm. In order to exploit this advantage, the number of EXU's will also need to be increased. This increases the switching capacitance of global signals such as CLK, and control signals, which are also routed to other parts of the circuit such as the global controller, and the power spectrum module (FFT block). Nevertheless, if the global signals are gated and turned off between the immediate completion of the critical-band filtering, and the next sample period (when the critical band would be in waiting mode), the reduced critical path would require fewer clock switches, and therefore a net power consumption of 27%!

As mentioned in Section 2.0, the remaining blocks will be analysed in a less detailed fashion since they are computationally far less complexed then the first 2 blocks that have been analyzed thus far. The remaining sections of the Chapter describes the Silage input for each of the blocks, concluding by a short discussion on selection of clock period and a table of estimates of important parameters such as critical path and power numbers, obtained at the chosen clock frequency.

## 2.3 Modeling of Critical Band Filter outputs

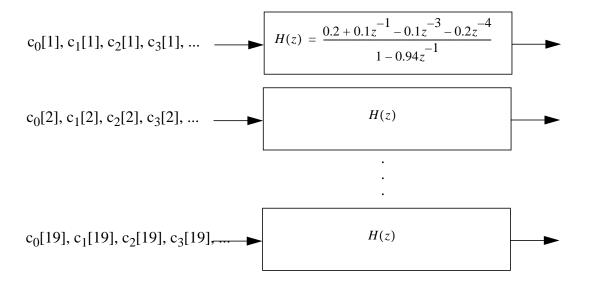

In order to improve the recognizer's tolerance to a changing communication channel, RASTA-PLP estimates the temporal derivative of the Bark-scale-transformed spectrum by drawing a regression line through the spectral values obtained in the last 5 consecutive input sets. Equal Loudness Preemphasis [19] and Intensity-loudness Power Law [21] both further simulate human hearing conditions.

Due to the simplicity of computations involved during Estimation of Temporal Derivative, Equal Loudness Preemphasis and Intensity-loudness Power Law, the Silage code for these 3 blocks are combined into one description given in Appendix F. The Natural Logarithm and Exponential algorithms assists in the implementation of the Power Law block, and allow the Equal Loudness Preemphasis filtering to be done simultaneously. Sections 2.3.2 and 2.3.3 show why. Appendix G and H list the Silage description for the Natural Logarithm and Exponential blocks respectively.

#### 2.3.1 Estimation of temporal derivative

Each of the 19 critical band coefficients is streamed into an averaging filter as shown in Figure 2.8. Since consecutive speech windows have a  $^2/_3$  overlap in time (20ms overlap of the 30ms window), there is a high correlation between the current and previous critical band outputs. The averaging removes some error due to possible changes in the channel. Silage description of the filter is achieved by one simple sentence for each filter:

$$Out = ((Out@1*0.94) + (0.2*In) + (0.1*In@1) - (0.1*In@3) - (0.2)*In@4));$$

(EQ 2.8)

$c_i[n]$  is the  $n^{th}$  critical band output at time i.

**FIGURE 2.8** Filtering that implements Estimation of the temporal derivative.

## 2.3.2 Equal Loudness preemphasis

The RASTA-PLP algorithm preempahsizes the sampled power spectrum with the 40dB simulated equal loudness curve. The transfer function of the filter [20] is given below in the normal frequency scale.

(EQ 2.9)

The function  $E(\omega)$  is an approximation to the nonequal sensitivity of human hearing at different frequencies [19] and simulates the sensitivity of hearing near the 40-db level.

The  $E(\omega)$  spectrum is similarly sampled at 19 equal Bark intervals,  $\Omega=B$ , corresponding to the middle frequency of each critical band. The Silage description for the equal loudness pre-

emphasis is therefore, nothing more then weighting each critical-band coefficient with a constant,  $E(\omega_i)$ , for  $\Omega_i(\omega_i)=i*B$  in accord to the Bark scale transformation given in EQ1.7.

### 2.3.3 Intensity-loudness Power Law

A cubic-root amplitude compression approximates the power law of hearing [21] and simulates the nonlinear relation between the intensity of sound and its perceived loudness. Together with the psychopathic equal-loudness preemphasis, this reduces the spectral-amplitude variation of the critical-band spectrum so that the following all-pole modeling can be done by a relatively low model order.

In order to simulate the power law of hearing, the critical band coefficients are raised to the power of 0.33. The equal loudness preemphasis and intensity-loudness Power Law are realized together by taking the natural log of the critical band coefficients, so that the constant multiplication in equal loudness preemphasis becomes a constant addition, which is cheaper computationally, while the raise power operation is equivalently realized by a constant multiplication. An exponential operation completes the manipulation, shown below:-

$$E(\Omega_i)~X^{0.33}(\Omega_i)~~Exp\{~[0.33*ln[X(\Omega_i)]]+ln[E(\Omega_i)]\} \label{eq:equation:equation:equation}$$

(EQ 2.10)

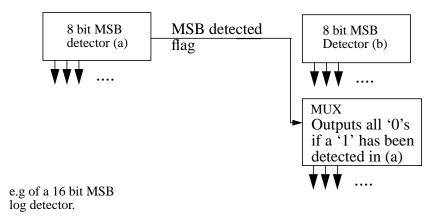

#### 2.3.4 Natural Log

The following describes how the natural log of a number, x is computed.

$$\begin{split} ln(x) &= ln\ (2^p * y) \\ &= p*ln(2) + ln(y) \\ &= p*ln(2) + a1*y + a2*y^2 + a3*y^3 + a4*y^4 + a5y^5 \\ a1 &= 0.99949556 \\ a2 &= -0.49190896 \\ a3 &= 0.28947478 \\ a4 &= -0.13606275 \\ a5 &= 0.03215845 \end{split}$$

where p = Most Significant Bit ==>  $1 \le y \le 2$ . This reduces the computation to a multiplication, p\* ln(2), while ln(y) is evaluated by polynomial expansion. The value of p is obtained by a

MSB detector, while y = (2P) is obtained by shifting the binary of x to the right p times. Two implementations of the MSB detector were examined. A log detector and a linear detector.

The log detector, with order  $O(\log n)$ , may speed up the computation for worst case inputs (Speed of MSB  $\alpha^{-1}/p$ ). However, from the view of power consumption, the log comparator is less efficient, as it will be comparing bits whose comparisons might have been omitted by the linear comparator. For example, the figure below shows a 16 bit MSB log detector used to detect the MSB of the bit string, 0000-0101-1011-0011. The bypass registers a '1' if a '1' bit has been detected in (a). The 8-bit MSB detector (b) will always perform its computations regardless of the output of detector (a). While gaining speed, this set-up does not consider the redundancies between (a) and (b).

**FIGURE 2.9** 16-bit Log detector for MSB

A linear MSB detector, on the other hand, omits all further operations after the first '1' has been detected, thereby conserving energy. An improved linear MSB detector combines the MSB detection and the division by  $2^P$  operation in a loop with n iterations (n= Bit length of x = 33) by taking advantage of the fact that a division by  $2^P$  is equivalent to P binary right shifts. The algo-

34

rithm starts with P1=n and maintains 2 copies of binary stream X1 and Y1, which are both set initially equal to x,

Eventually, at the end of n iterations, P1=p, and Y1 would have shifted left by p times such that Y1=y.

The combined MSB detector and division by 2<sup>P</sup>, therefore has a data-independent delay. This simplifies the design as the worst case input does not produce a delay that is any longer than a best case input. The critical path to compute the log for 19 critical band coefficients turned out to be 1027, which when run at a clock rate of 537ns, is only 0.551ms. This is not of much consequence considering the 10ms throughput time limit of the RASTA-PLP front end. It is chosen for its design simplicity and power advantages.

#### 2.3.5 Exponential

The following describes how the exponential of a number, x is computed.

Let

$$e^x = 2^p$$

$= 2^i * 2^f$  where i is an integer and  $0 \le f \le 1$  Polynomial Approximation:  $1 + b_1 f + b_2 f^2 + b_3 f^3 + b_4 f^4$  Shift  $b_1 = 0.693147$  And P is found by:  $b_2 = 0.240227$   $ln(e^x) = ln(2^p)$   $b_3 = 0.055504$   $a_4 = 0.009618$   $b_4 = 0.009618$   $b_4 = 0.009618$

${f f}$  is the decimal portion of P, with  $2^{{f f}}$  computed by polynomial approximation.  ${f i}$  is therefore the integer portion of P, and  $2^{{f i}}$  is realized by binary shifts. If x is negative, i will be negative, and

2<sup>i</sup> corresponds to i left shifts. Otherwise it is i right shifts. The critical path for computing 19 exponentials is 685, which, at a clock period of 550ns, is only 0.377ms. Again, well under the 10ms limit.

TABLE 6. Estimates obtained with Vdd=1.2V; Clock Period 550ns

| Computation Block                           | Critical<br>Path | Delay<br>(ms) | Power (µW) |

|---------------------------------------------|------------------|---------------|------------|

| Log                                         | 1027             | 0.55          | 21.2       |

| Rasta Filtering, Equal Loudness & Power Law | 389              | 0.21          | 7.85       |

| Exp                                         | 685              | 0.37          | 10.7       |

| Total                                       | 2101             | 1.13          | 39.8       |

# 2.4 Inverse Discrete Fourier Transform, Autocorrelation Coefficients

This far, the algorithm has only involved obtaining the power spectrum and reshaping it in such a way to mimic the human perceptual hearing. From the modeled power spectrum, the autocorrelation function is obtained through an inverse discrete Fourier Transform. Since the 21 critical band coefficients cover the frequencies  $0 \le \omega \le \pi$ , the IDFT is given by,

The power spectrum is real and even, which implies that the autocorrelation function is real. Ignoring all imaginary product terms,

$$r(n) = R_p(0) - R_p(20) + \sum_{k=1}^{19} R_p(k) \left( \cos\left(\frac{2\pi}{41}kn\right) + \cos\left(\frac{2\pi}{41}(40 - k)n\right) \right)$$

$$= R_p(0) - R_p(20) + \sum_{k=1}^{19} R(k)w_{n,k}$$

$$w_{n,k} = \cos\left(\frac{2\pi}{41}kn\right) + \cos\left(\frac{2\pi}{41}(40 - k)n\right)$$

However, only the first nine autocorrelation coefficients are needed for a 8<sup>th</sup> order LPC analysis. Therefore, instead of attempting to use a general n<sup>th</sup> order FFT (in this case, n=21)

which would compute all the 21 autocorrelation coefficients. It was decided that evaluating the first 9 coefficients by direct summation would simplify the design. The algorithm, as described in Silage, consists of a nested loop of depth 2 with the outer loop iterating from n=0 to n=8, and the inner loop iterating from k=1 to k=19. The  $w_{n,k}$  values are stored in a 2-dimensional 9 by 19 array. The result is a partial IDFT which uses 11.2 $\mu$ W, and takes 0.6ms to complete. The figures are insignificant when compared with the overall power consumption or throughput of the entire front-end. Even if the power consumption of the IDFT block could be improved by 30%, the net effect in the global picture would still be negligible. The Silage description for this block can be found in Appendix I.

## 2.5 Durbin Analysis[3]

Equation 1.3 is solved here to obtain 8 cepstral values. The autocorrelation coefficients are first normalized by  $^1/_{r(0)}$ . There is no loss of generality by doing so. The cepstral values are solved iteratively by the Durbin algorithm. This solves the equation in  $O(n^2)$  as compared to  $O(n^3)$  if a more general Gaussian elimination approach is taken. The normalization of the coefficients requires an inverse operation  $(x^{-1})$ . In addition, each iteration of the algorithm also requires the inverse of a variable  $\beta$ . The front-end was simulated over a large pool of speech samples and it was observed that the values of r(0) are always in excess of 15, while the values of  $\beta$  are always between 0.7 to 1.0. The inversions are done by non-restoring division. In order to simplify the design of the divider, the operands of the inverse are adjusted so that the quotient  $^x/_y$  observes the rule  $x \le y$ . In this way, the absolute value of the output of the divisor is strictly less than or equal to 1. Therefore, there is no integer bit in the divider.

As r(0) > 1,  $\frac{1}{r(0)}$  automatically satisfies the  $x \le y$  requirement. However,  $\frac{1}{\beta}$  is processed in the following manner:

where

is evaluated by the divider

Silage code for the Durbin's algorithm is given in Appendix J.

# 2.6 Cepstral Conversion

In accord with EQ 1.5, the Silage description in Appendix K uses a loop to iterate the summation. The gain is assumed, for simplicity, to be 1. So the first cepstral coefficient  $c_0 = \ln(1) = 0$ , a trivial solution. The  $\frac{1}{m}$  factor needed for computation of all other coefficients is obtained from the array *minverse*, which can be implemented on an srom.

### 2.7 Clock Period

The single most delay comes from a 33-bit by 25-bit multiplier in the Natural Log block. Operating at 1.2V, clock overhead is added and the minimum time estimated for completion of the multiply is 1033ns. This aside, all the other multipliers have fewer bit lengths and usually have a delay between 600ns to 750ns. The adders have even lower delays, with the largest 25-bit adder having a delay of only 294ns.

Using a multi-cycle system, the execution of each EXU is scheduled over sufficient number of clock cycles to achieve a stable output. For instance, the operation of a 25-bit adder may take 2 clock cycles, while that of a 32-bit multiplier may take 5 clock cycles. This allows better utilization of a shorter clock period, reducing the amount of redundant time where certain EXUs may idle while waiting for the next clock input, and the overall delay of the system. Also, a shorter clock period results in more available cycles within the 10ms limit that the design

throughput must conform to. The additional cycles could allow more resource sharing, thereby reducing the overall area.

Nevertheless, the increased clock frequency of a multi-cycle system also results in higher clock power and control power due to the higher switching activity. Such trends are visible in an experiment where the properties of the FFT block with respect to different clock periods are investigated using Hyper's estimator. Result are shown in Table 7.

TABLE 7. Variation of properties with clock rate for FFT block

|                                                     | Setup A                    | Setup B                | Setup C               | Trend of Property as Clock Frequency Increases |

|-----------------------------------------------------|----------------------------|------------------------|-----------------------|------------------------------------------------|

| Clock Period                                        | 0.9µs                      | 0.5µs                  | 0.1µs                 | Decrease                                       |

| Available Cycles within 10ms                        | 11111                      | 20000                  | 100000                | Increase                                       |

| Critical Path                                       | 15815<br>(Exceeds<br>10ms) | 18951                  | 49485                 | Increase                                       |

| Area                                                | 155.53 mm <sup>2</sup>     | 137.76 mm <sup>2</sup> | 33.11 mm <sup>2</sup> | Decrease                                       |

| ENERGY (nJ)                                         |                            |                        |                       |                                                |

| Registers                                           | 427                        | 431                    | 504                   | Increase                                       |

| Control                                             | 112                        | 134                    | 707                   | Increase                                       |

| Bus                                                 | 925                        | 870                    | 428                   | Decrease                                       |

| Clock                                               | 450                        | 508                    | 967                   | Increase                                       |

| Sub-Total of Register, Control, Bus and Clock Power | 1914                       | 1943                   | 2606                  |                                                |

Table 7 shows that using a faster clock, the control power as well as clock power are increased, as expected. Critical path also goes up as a result of EXU's which execute over multiple cycles, and also due to the use of fewer hardware units, which was made possible by the increased available cycles within the 10ms time margin. The decrease in bus power with a faster clock rate can be attributed to the reduced area, which meant shorter interconnects with less capacitance.

In view of the drive for low power, the clock period was set near the maximum value that would still meet the 10ms throughput criteria. The multi-cycle system was set up such that run-

ning at a clock period of 537ns ( $\sim 0.5*1033$ ns), most operations (which have execution delays less then 537ns) are executed over one clock period, while others such as the wide betwixt multiplications use 2 clock cycles.

The amount of time and energy consumed by each block is tabulated in Table 8.

TABLE 8. Estimates of individual blocks with Clock period 537ns,  $V_{dd} = 1.2V$

|                                                   | Critical<br>Path | Delay (ms) | No. of<br>Nodes | Active Area (mm²) | Power (µW) |

|---------------------------------------------------|------------------|------------|-----------------|-------------------|------------|

| FFT  <sup>2</sup>                                 | 17607            | 9.45       | 52184           | 15.48             | 624.05     |

| Critical Band Filter-<br>ing                      | 1043             | 0.56       | 4131            | 12.36             | 24.32      |

| Natural Log                                       | 1027             | 0.55       | 3098            | 13.23             | 21.18      |

| Rasta Filtering,<br>Equal Loudness &<br>Power Law | 389              | 0.21       | 1204            | 9.79              | 7.84       |

| Exponential                                       | 685              | 0.37       | 1673            | 6.72              | 10.70      |

| IDFT                                              | 1063             | 0.57       | 1603            | 7.18              | 11.24      |

| Durbin                                            | 1820             | 0.98       | 4851            | 20.86             | 26.54      |

| Cepstral Analysis                                 | 528              | 0.28       | 1105            | 17.19             | 9.53       |

| Total                                             |                  |            |                 | 102.81            | 735.40     |

# 2.8 Behavioral Simulation of RASTA-PLP System

The functionality of algorithm for each block is verified by invoking the Hyper simulator that translates the CDFG into C-code, which is then compiled and executed. The simulation data also allows the system designer to make appropriate decisions with regard to the bit widths as well as other observations such as those that allow the divider in the Durbin analysis block to be simplified (Section 2.5).

The simulation results for one particular 30ms window of speech, consisting of 512 samples obtained at 16kHz is shown on the following page:-