Copyright © 1995, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### LOW POWER ANALOG CIRCUITS FOR AN ALL CMOS INTEGRATED CDMA RECEIVER

by

Lapoe E. Lynn

Memorandum No. UCB/ERL M95/73

1 September 1995

# LOW POWER ANALOG CIRCUITS FOR AN ALL CMOS INTEGRATED CDMA RECEIVER

.

.

by

Lapoe E. Lynn /

Memorandum No. UCB/ERL M95/73

1 September 1995

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# **Acknowledgments**

It is not often that one gets the chance to reflect on all the people and factors that have contributed to what is, in a sense, the culmination of 18+ years of education. Therefore, while keeping in mind that there are many who must necessarily go unmentioned here (but whose influence is gratefully remembered), I would like to thank the following people for helping me arrive (finally!) at this point.

This research was conducted under the kind support of the Advanced Research Projects Agency (ARPA) in the form of an NDSEG Fellowship, as well as through ARPA contract #J-FBI 92-150 under the guidance of Professor Robert Brodersen. Thanks to Prof. Brodersen and Prof. Paul Gray for reviewing this write-up. Many thanks also go to Tom Boot, Peggy Brown, Elise Mills, and Heather Brown for their relentlessly efficient (and friendly!) administrative support.

An integral part of being a senior graduate student, although it is not necessarily included in the job description, is helping the younger students who follow after you. Not enough can be said about this function -- graduate school would have been useless for me, without the advice and guidance of my peers. I have been in the happy position of learning from some of the best and most generous. Dave Cline and Thomas Cho have each spent hours of their valuable time patiently helping me with ideas, pointing me towards papers, and even donating much of their test setup to me. However, my deepest gratitude must go to Samuel Sheng. Drawing on a breadth **and** depth of knowledge unlike any I have ever seen, Sam has lent me invaluable guidance, direction, support and friendship (despite being burnt-out like a used piece of charcoal!). The reference page for this work should have one large reference to [Sam Sheng's Brain] written in 42 point font across the center.

On a less technical front, without the love and support of friends and family, I would certainly never have finished this project, and would no doubt have long since collapsed into a burnt-out pile of wreckage. The playful antics of the RF group, the often distracting 550 gang, and the hard-core analog gurus of PRG group, all helped make work a fun place to be. And without friends like James Kao, Joy Ku, John Yen(bo), Aiting Tung, Chris Rivera, Jennifer Cheng, Sam Sheng, and Sally Chen, I probably would have long since lost my mind and moved back to Colorado.

Friends like Kevin Stone, Dipanwita Deb, Susanne Wong and Sekhar Narayanaswami, are the type of friends that you know will stick with you through the end of the world. Thanks to Sus for putting up with such an awful roommate, Dip for calling and calling... even though I always flaked, Sek and Kevin for making the long hours in Cory bearable. You guys are the best.

And finally, I have to thank the four people whose love has made me who I am, and whose strength has carried me to where I am now.

Helen, who has made the last year and a half the fullest and richest of my life. Helen, thank god you have a lot of patience and a good sense of humor! :)

Aenoch, who has watched over me as carefully as any big brother could. Hang in there, big guy.

And finally, I'd like to dedicate this work to my parents with all my love. Mom, Dad... believe it or not, you guys are pretty darn cool.

## **Table of Contents**

/

Table of Contents 1

List of Figures 3

Introduction 7

Motivation 9

Architecture 9 Chip Design 12 Process 14

Background 19

Analog to Digital Conversion 19 The Subranging Architecture 21 The Pipelined Architecture 22 The Sample and Hold Circuit. 24

VGA Circuit Design 29

Introduction 29 Amplifier Topology 30 Operational Amplifier Design 39 Optimizations 44

Table Of Contents

#### **Table of Contents**

### A to D Design 51

.

Introduction 51 Architecture 53 Comparator Design 57 A to D Optimizations 67

Results 75

Design Prototype 75

Conclusion 83

Appendix A 87

## Chapter 2

| FIGURE 1. | Superheterodyne Transceiver Architecture | 10 |

|-----------|------------------------------------------|----|

| FIGURE 2. | Subsampling Downconversion Illustrated   | 11 |

| FIGURE 3. | 4x oversampled sine wave 12              |    |

| FIGURE 4. | Integrated CDMA Receiver Chip 13         |    |

## Chapter 3

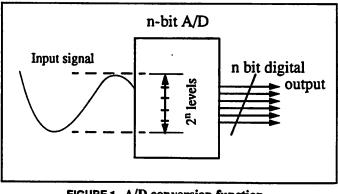

| FIGURE 1. | A/D conversion function 19                   |

|-----------|----------------------------------------------|

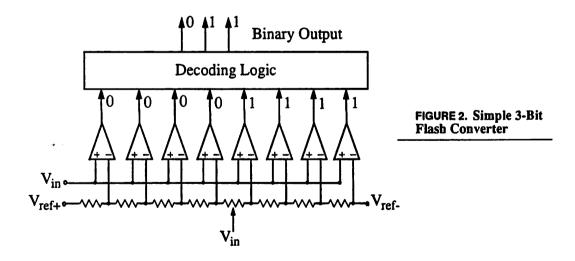

| FIGURE 2. | Simple 3-Bit Flash Converter 20              |

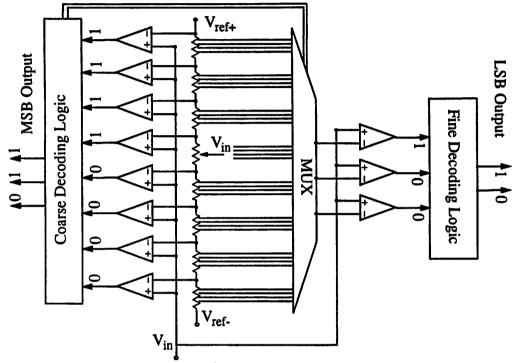

| FIGURE 3. | 3-Bit 2-Bit Subranging A/D architecture. 22  |

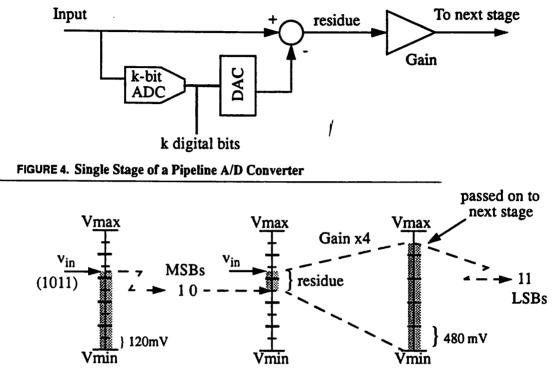

| FIGURE 4. | Single Stage of a Pipeline A/D Converter 23  |

| FIGURE 5. | 2 bit 2 bit Pipeline Conversion Example 23   |

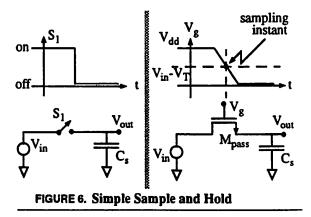

| FIGURE 6. | Simple Sample and Hold 24                    |

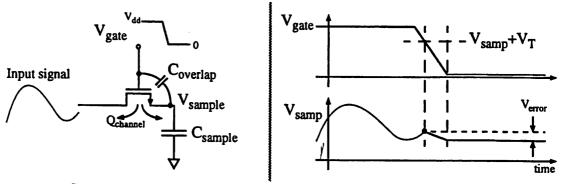

| FIGURE 7. | Sources of Error in Basic Sample and Hold 25 |

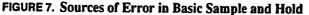

| FIGURE 8. | Bottom Plate Sample and Hold 26              |

### Chapter 4

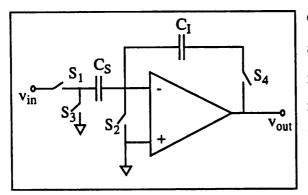

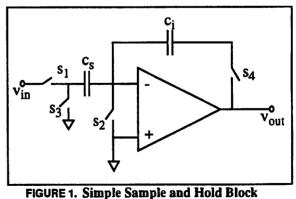

| FIGURE 1. | Simple Sample and Hold Block 30                                   |    |

|-----------|-------------------------------------------------------------------|----|

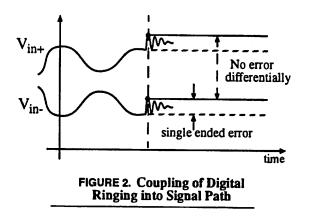

| FIGURE 2. | Coupling of Digital Ringing into Signal Path 31                   |    |

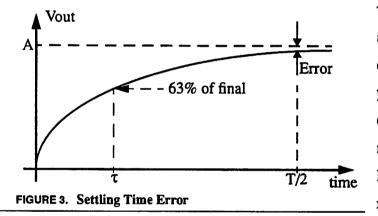

| FIGURE 3. | Settling Time Error 32                                            |    |

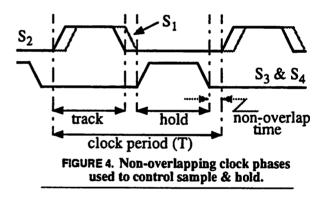

| FIGURE 4. | Non-overlapping clock phases used to control sample & hold. 33    |    |

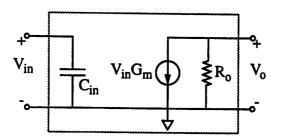

| FIGURE 5. | Two Port Representation of Operational Transconductance Amplifier | 34 |

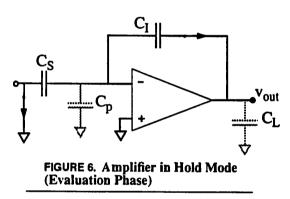

| FIGURE 6. | Amplifier in Hold Mode (Evaluation Phase) 35                      |    |

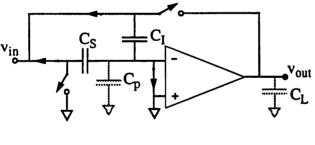

| FIGURE 7. | SHA topology sampling onto CI as well as CS. 36                   |    |

List of Figures

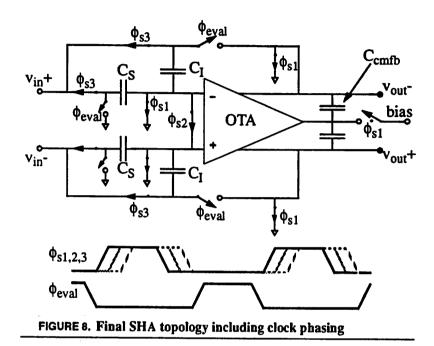

| FIGURE 8.  | Final SHA topology including clock phasing 37                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------|

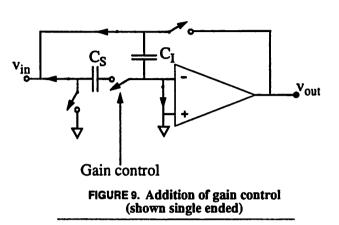

| FIGURE 9.  | Addition of gain control (shown single ended) 38                                                              |

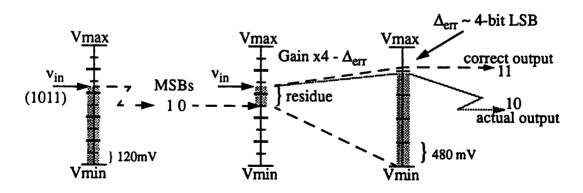

| FIGURE 10. | 2 bit 2 bit Pipeline Conversion Example with small gain error 39                                              |

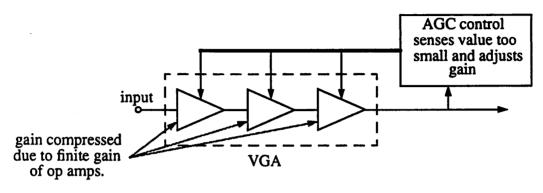

| FIGURE 11. | AGC compensation of gain errors by negative feedback control loop 40                                          |

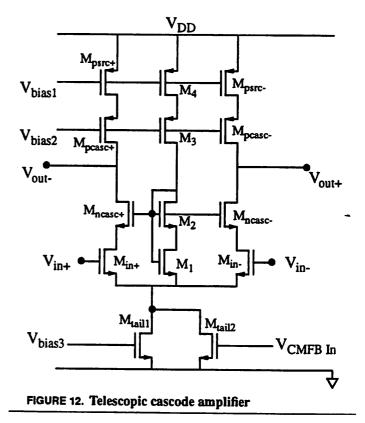

| FIGURE 12. | Telescopic cascode amplifier 41                                                                               |

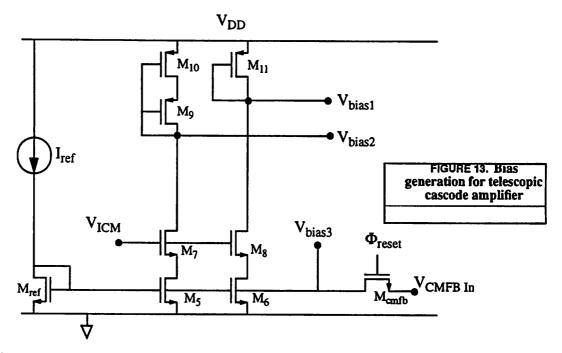

| FIGURE 13. | Bias generation for telescopic cascode amplifier 42                                                           |

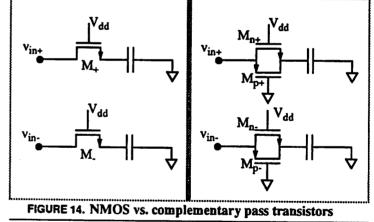

| FIGURE 14. | NMOS vs. complementary pass transistors 43                                                                    |

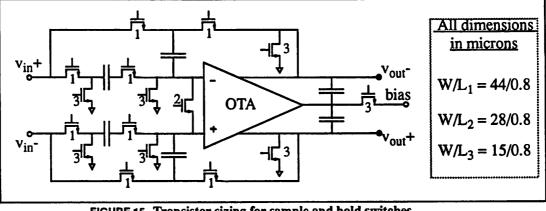

| FIGURE 15. | Transistor sizing for sample and hold switches 44                                                             |

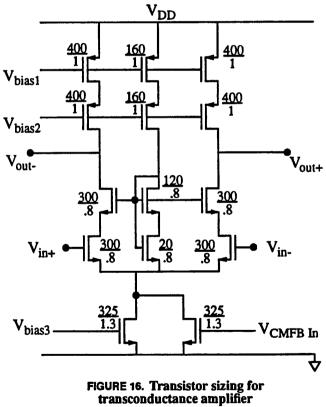

| FIGURE 16. | Transistor sizing for transconductance amplifier 46                                                           |

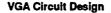

| FIGURE 17. | VGA Stage Transient Analysis Showing Reduction in Settling Time Due To<br>Signal Dependent Kickback Noise. 50 |

## Chapter 5

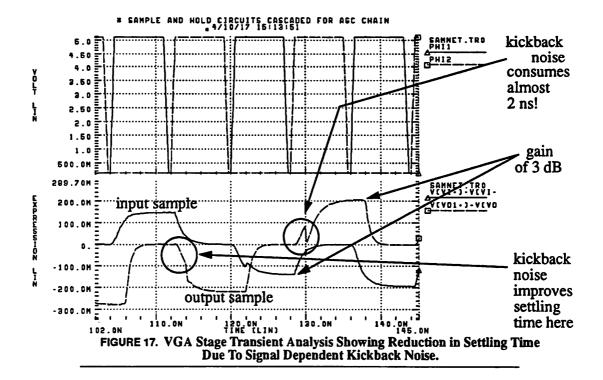

| FIGURE 1.  | Effect of spreading a transmit pulse 51                                                                                          |

|------------|----------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 2.  | Effect of spreading on transmit power spectrum 51                                                                                |

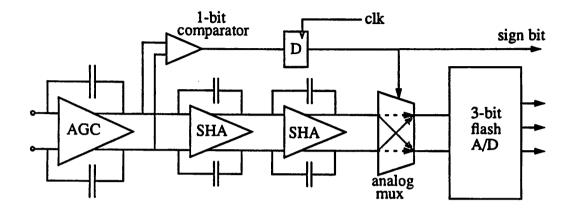

| FIGURE 3.  | Modified 1-bit to 3-bit pseudo pipeline architecture 54                                                                          |

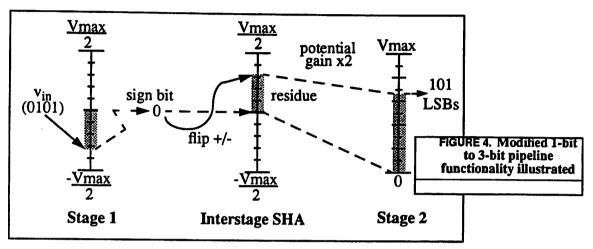

| FIGURE 4.  | Modified 1-bit to 3-bit pipeline functionality illustrated 55                                                                    |

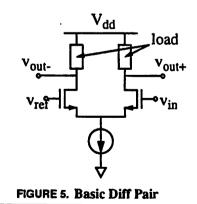

| FIGURE 5.  | Basic Diff Pair 57                                                                                                               |

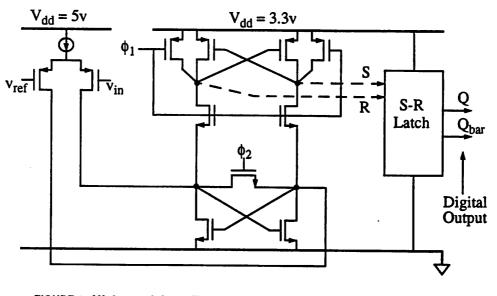

| FIGURE 6.  | High speed, low offset comparator (after [13]) 58                                                                                |

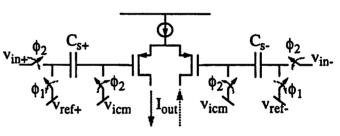

| FIGURE 7.  | Input sampling network (ISN) 59                                                                                                  |

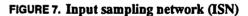

| FIGURE 8.  | Modified doubly-differential input stage 60                                                                                      |

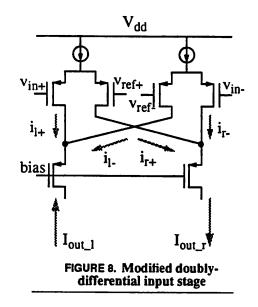

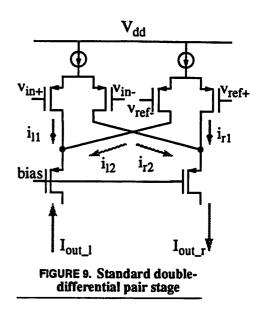

| FIGURE 9.  | Standard double-differential pair stage 61                                                                                       |

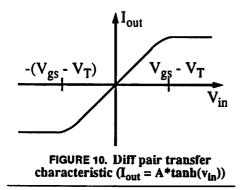

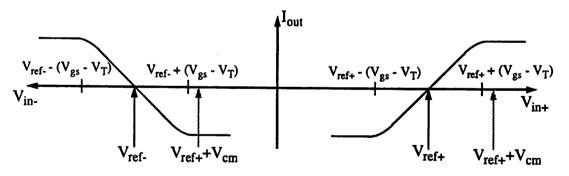

| FIGURE 10. | Diff pair transfer characteristic (Iout = $A^{*}tanh(vin)$ ) 61                                                                  |

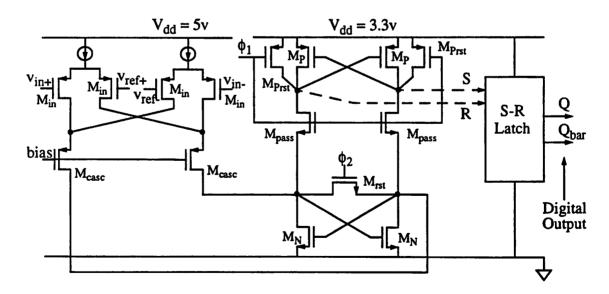

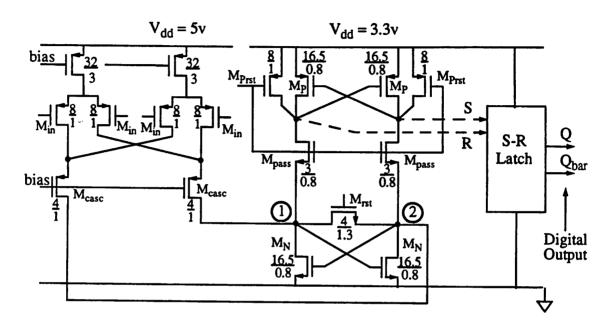

| FIGURE 11. | Final high-speed differential comparator 62                                                                                      |

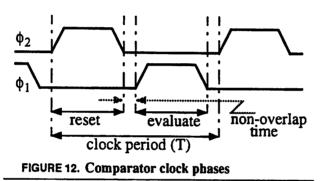

| FIGURE 12. | Comparator clock phases 63                                                                                                       |

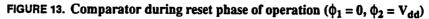

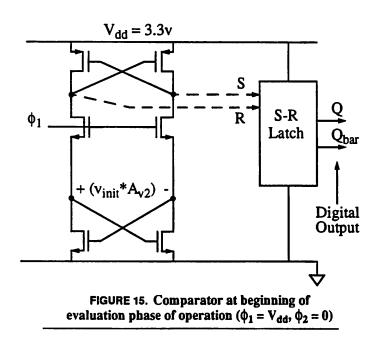

| FIGURE 13. | Comparator during reset phase of operation ( $\phi 1 = 0, \phi 2 = V dd$ ) 63                                                    |

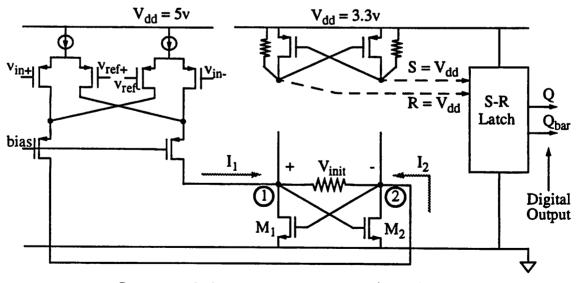

| FIGURE 14. | Comparator during reset phase of operation ( $\phi 1 = 0, \phi 2 = 0$ ) 65                                                       |

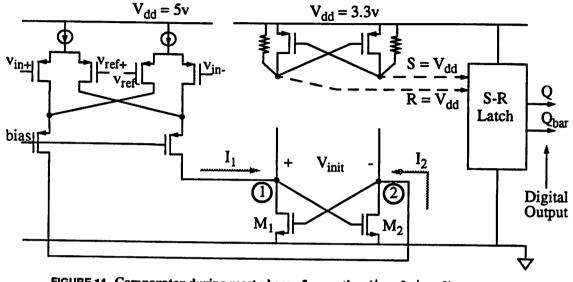

| FIGURE 15. | Comparator at beginning of evaluation phase of operation ( $\phi 1 = V dd$ , $\phi 2 = 0$ ) 66                                   |

| FIGURE 16. | Effect of common mode shift on output of modified input stage 67                                                                 |

| FIGURE 17. | Device sizes for comparator 69                                                                                                   |

| FIGURE 18. | Single Comparator Transient Analysis Showing Correct Digital Output<br>Based on Comparison of Input to Reference (top panel). 73 |

.

## Chapter 6

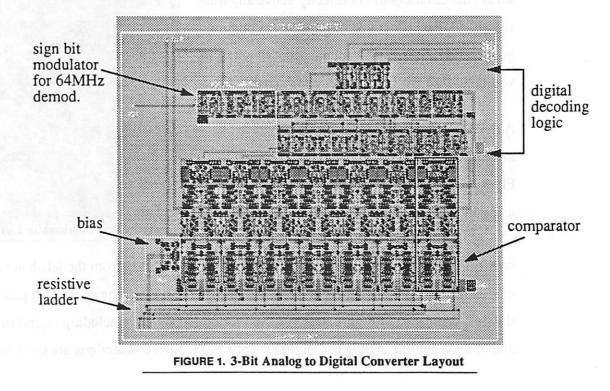

| FIGURE 1. | 3-Bit Analog to Digital Converter Layout 75                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------|

| FIGURE 2. | Comparator Layout 76                                                                                        |

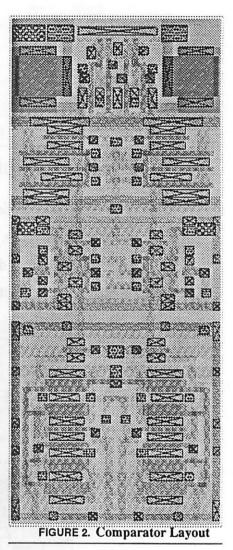

| FIGURE 3. | Prototype 3-Bit Flash A/D Chip Layout. (Preceeded by Sample and Hold<br>Circuit) 77                         |

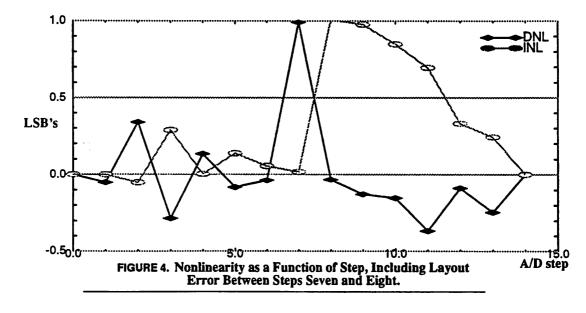

| FIGURE 4. | Integral Nonlinearity as a Function of Step, Including Layout Error Between Steps Seven and Eight. 78       |

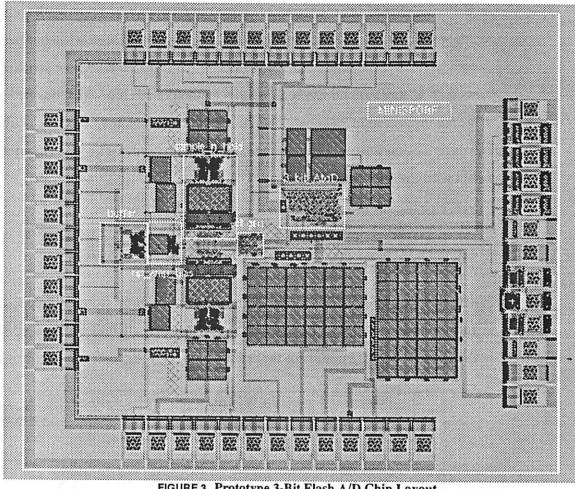

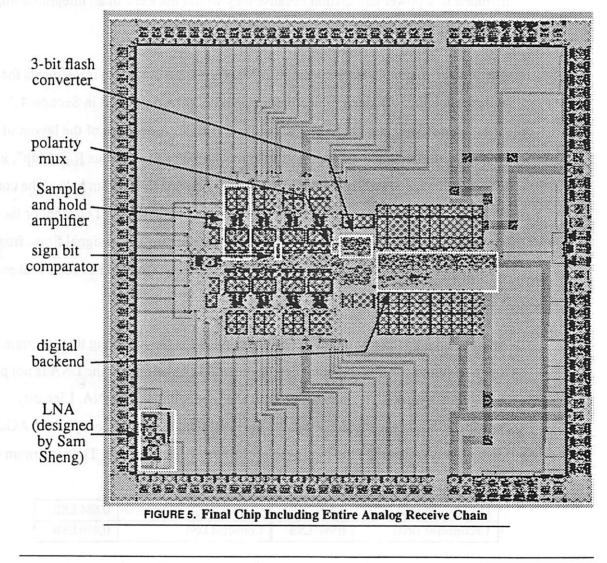

| FIGURE 5. | Final Chip Including Entire Analog Receive Chain 79                                                         |

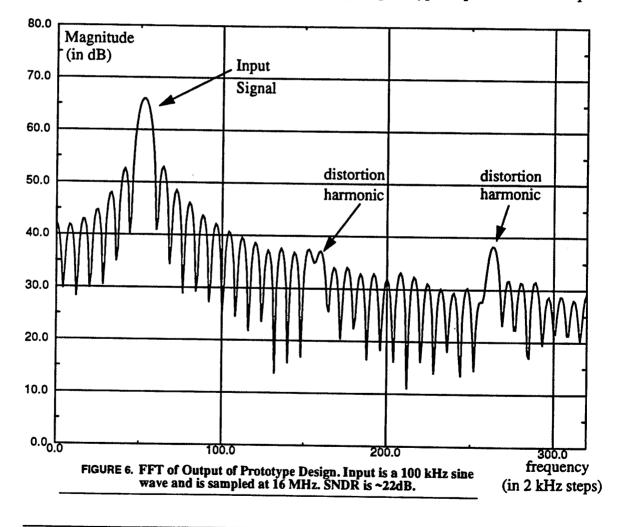

| FIGURE 6. | FFT of Output of Prototype Design. Input is a 100 kHz sine wave and is sampled at 16 MHz. SNDR is ~22dB. 81 |

-

• · · · ·

.

.

List of Figures

. 1

i

## **CHAPTER 1**

# Introduction

As interest in wireless portable computation has blossomed over the past several years, the electronics industry has seen the much anticipated debut of such products as the Apple Newton fall upon lethargic sales and widespread consumer dissatisfaction. These systems have attempted to provide a networked computing environment to individuals by basically building a small computer with a cellular phone connection to provide "connectivity" to the growing internet. However, portability requirements have severely limited the amount of computing resources that can be placed in such units; this fact, coupled with the use of a low-bandwidth wireless link have resulted in products that have failed to provide the quality of service necessary to please the modern-day consumer. An alternative is the UC Berkeley InfoPad.

The Infopad system places almost all of the user's computation in large, non-portable resources on a high-speed wired network, all of which is connected to the portable unit through a wideband wireless radio link. Such a system has many attractive advantages over current implementations. By moving a majority of the computation away from the portable unit, significant power savings can be achieved, extending battery lifetime for the user. Furthermore, since voice and pen recognition are also performed by the non-portable server, information passing over the wireless link is restricted to voice and video data. Since these forms of data are inherently resistant to bit errors (i.e. the human senses may not detect bit errors below a certain level), a higher bit-error rate can potentially be toler-

ated in the radio connection. The caveat to all of these advantages is that the requirements of the wireless radio link become much more severe. Supporting multiple users demanding multimedia (e.g. video) data rates results in a system which consumes a large amount of bandwidth. The UC Berkeley Infopad Project is an attempt to design such a system. Therefore, the design of the Infopad radio needs to simultaneously achieve high speed, wide bandwidth, extremely low power, and high integration.

The work presented here represents part of the effort to design and build the infopad radio receiver as a low-power, monolithic, single-CMOS-chip. In particular, this work focuses on the design and implementation of high speed, discrete-time variable gain circuits, as well as an extremely fast, low power 4 bit analog to digital converter for use in the integrated receiver chip.

# CHAPTER 2 Motivation

## 2.1 Architecture

In order for a true multimedia server to support video data to multiple terminals, a large amount of bandwidth is required. In fact, almost 100 MHz of bandwidth are specified for the system in order to support up to 50 users in a single cell (taking into account that high quality compressed video data rates require on the order of 1-2 Mb/sec). This is quite a sizeable amount of data, and in order to robustly support such a broadband transmission, a direct sequence spread spectrum modulation scheme was adopted [1]. While there are numerous reasons for taking advantage of the noise immunity and potential multipath interference rejection of a spread signal, the decision to transmit a CDM (Code Division Multiplexed) signal has several significant side effects on the design of the receiver circuitry (see [2], [3], and [4]). Perhaps the most obvious is that each user must now receive and decode a transmit pulse that has been modulated with a pseudorandom code, requiring high speed signal processing to despread the information. On the other hand, no frequency tuning in the receiver is required since the entire band is translated directly to baseband (actually, the signal is mixed to a low IF frequency where it is directly converted from analog to digital and mixed to baseband digitally). Also, since quantization noise is rejected by the spread spectrum processing gain, the resolution requirements on the ADC in the receiver are greatly reduced [5]. Table 1 is a summary of the specifications for the InfoPad

#### radio receiver design [1]. A standard superhetero-

#### **TABLE 1. System Parameters**

| Carrier Frequency                       | > 1 GHz                               |

|-----------------------------------------|---------------------------------------|

| Chipping Rate                           | 64 MChips/sec                         |

| Spreading Gain                          | 64 (18dB)                             |

| Raw User Data Rate                      | 2 Mbps                                |

| Symbol Rate                             | 1 Mbaud (DQPSK encoded)               |

| Rec'd Signal Strength<br>(into 50 ohms) | -80 dBm to -40 dBm<br>(dynamic range) |

| A/D Resolution                          | 4 bits                                |

| A/D Conversion Rate                     | 128 Msamples/sec                      |

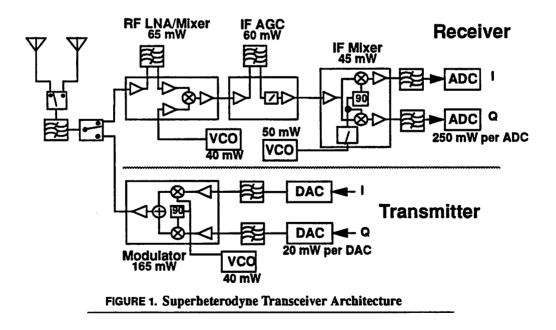

ment the receiver design presented above. A representative block diagram for such a receiver is shown in Figure 1 including a transmit section. Down conversion is performed in two steps before analog-to-digital conversion -- requiring two local oscillators, multiple mixer and

amplifier chips, and numerous

dyne architecture could certainly be used to imple-

discrete filter components. Clearly, such a design does not lend itself easily to a highly integrated, low-power implementation [6]. The power consumed by each active ele-

ment is included in Figure 1. The receiver alone consumes on the order of 750 mW of power, with a large portion of that going into the discrete A/D converters. By designing low-power A/D converters in CMOS technology and by switching to a quasidirect conversion architecture, higher integration and significant power savings can be achieved.

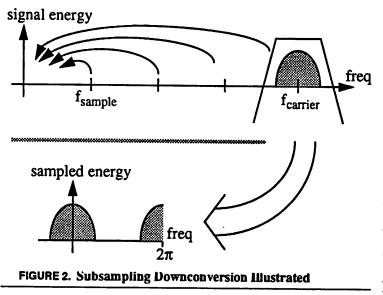

A homodyne conversion can be achieved by subsampling the RF carrier directly [7]. By constraining the subsampling rate to be an integer divisor of the carrier frequency, the RF signal is converted directly to a discrete-time baseband signal. Although energy from every integer multiple of the sampling frequency is mixed down to the discretetime baseband region, prefiltering can be applied to narrowband the noise around the RF carrier band. Figure 2 shows the process of subsampling in the spectral energy domain. The InfoPad CDMA radio uses this technique to replace the superhet archi-

tecture with a single simple CMOS sampling switch being driven by a crystal oscillator. The architectural change results in the elimination of two VCOs, two bipolar mixer chips, and a quadrature tank element, with significant savings in power, area, and com-

plexity. However, the InfoPad CDMA radio design does not *quite* follow this model exactly. In order to avoid the multitude of problems associated with direct conversion receivers, the subsampling mixers convert the RF signal to a low intermediate frequency of 64 MHz. This signal is directly converted to 4 bits of digital information at a 4x oversampling rate of 256 MHz, and is subsequently mixed to baseband digitally (a 4x oversampling ratio is required for the timing recovery loop). At such a high conversion rate, the design of a low-power CMOS A/D converter becomes quite challeng-

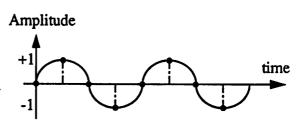

ing even for only 4 bits of resolution. Fortunately, as Figure 3 illustrates, a 64 MHz sine wave, sampled at 256 MHz consists of mostly zero samples. Therefore, by multiplying the input signal

(on a sample by sample basis) with the FIGURE 3. 4x oversampled sine wave values shown in Figure 3 (+1, 0, -1, 0, +1...), every other sample can be eliminated. The net result is that the analog to digital conversion only needs to take place at 128 Msamples/sec. (Still a formidable number for a low power CMOS converter!)

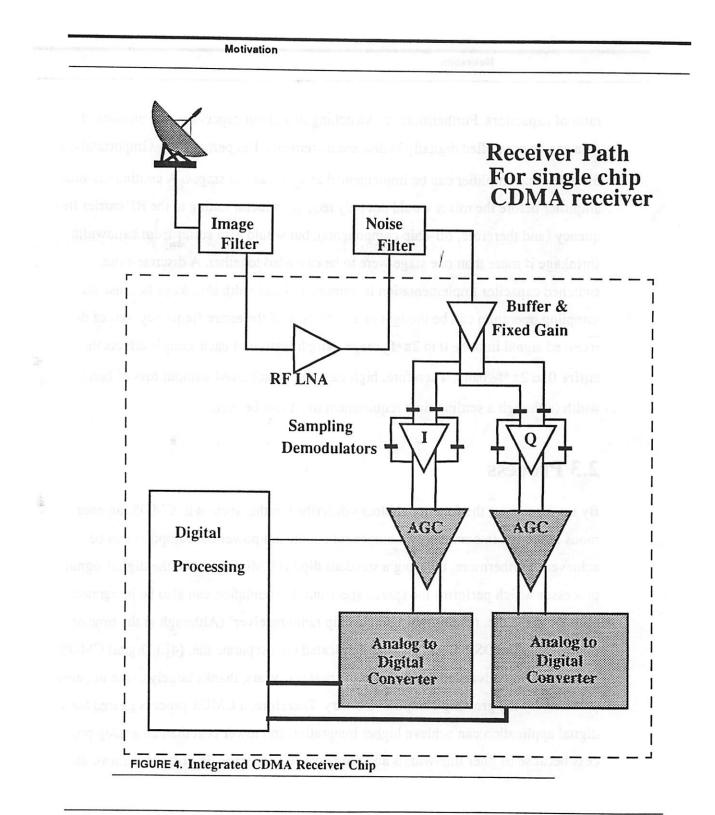

### 2.2 Chip Design

A block diagram of the fully integrated receiver chip is shown in Figure 4. The shaded blocks indicate the focus of this work. The automatic gain control circuitry could be placed either before or after the sampling demodulator blocks, but by placing the AGC *after* the subsample-mixing operation, the design moves to the discrete time domain. Discrete time amplifiers can implement precisely controlled gain determined by the

13

ratio of capacitors. Furthermore, by switching in and out capacitors, the amount of gain can be controlled digitally in discrete increments. But perhaps most importantly, a discrete-time amplifier can be implemented as a cascade of stages. A continuous-time amplifier before the mixer would not only require inductor tuning to the RF carrier frequency (and therefore, off-chip components), but would also suffer from bandwidth shrinkage if more than one stage were to be cascaded together. A discrete-time, switched capacitor implementation is immune to bandwidth shrinkage because the sampling operation can be thought of as a folding of the entire frequency axis of the received signal into the 0 to  $2\pi * f_S$  range. Amplification of each sample affects the **entire** 0 to  $2\pi * f_S$  band. Therefore, high gain can be achieved without loss of bandwidth (although a settling time requirement must still be met).

## 2.3 Process

By implementing the functional blocks described in this section in CMOS, an enormous reduction in complexity, component count, and power consumption can be achieved. Furthermore, by using a standard **digital** CMOS process, the digital signal processor which performs the spread spectrum demodulation can also be integrated onto the same die, resulting in a single chip radio receiver! (Although at the time of this writing, the DSP block has been fabricated on a separate die. [4].) Digital CMOS technology has advanced rapidly over the past few years, thanks largely to the impetus provided by the growing computer industry. Therefore, a CMOS process geared for a digital application can achieve higher integration and lower cost than an analog process because of finer line-widths and fewer processing steps. In order to achieve the eventual goal of a single-chip solution, the InfoPad CDMA radio has been designed in a standard digital CMOS process. Access to this 1.0 micron Hewlett-Packard technology was provided by the MOSIS service. Unfortunately (and perhaps not surprisingly), there are several pitfalls to designing high-performance analog circuits in a technology intended primarily for digital circuit design. Precision resistors, for example, are not available in this process. Transistor output impedance is lower than might be expected from an analog CMOS process of comparable minimum gate length. Bipolar transistors usually provide too little benefit, usually require static power consumption, and are too costly to justify in a digital design (many analog technologies at the time of this writing include the ability to implement bipolar and CMOS transistors -- and are called BiCMOS processes), but perhaps most importantly, a digital technology lacks a second layer of polysilicon which is used in analog designs to implement precision capacitors. Analog CMOS circuit designs utilize two layers of polysilicon, separated by a thin layer of dielectric oxide, to create the floating capacitors used in switched-capacitor and sample-and-hold circuits. The absence of a second layer of poly makes the creation of these capacitors difficult since the dielectric oxide separating the metal and polysilicon layers is typically quite thick, resulting in a capacitance-per-unit area 100 times smaller. Therefore, capacitors created in this technology from overlapping plates of metal and/or polysilicon consume a large amount of area; and perhaps even more importantly, each capacitor implemented in this fashion, includes a large parasitic capacitance to the substrate whose value is as large or even larger than the value of the desired capacitor.

| Parameter                   | Value                    | Parameter                   | Value                    |  |

|-----------------------------|--------------------------|-----------------------------|--------------------------|--|

| NMOS V <sub>T</sub>         | 0.74 volts               | PMOS V <sub>T</sub>         | -0.85 volts              |  |

| NMOS KP (µC <sub>ox</sub> ) | 119 μA/V <sup>2</sup>    | PMOS KP (μC <sub>ox</sub> ) | 34.0 μA/V <sup>2</sup>   |  |

| NMOS LD                     | 0.16 µm                  | PMOS L <sub>D</sub>         | 0.105 µm                 |  |

| NMOS delta_W                | 0.36 µm                  | PMOS delta_W                | 0.39 µm                  |  |

| NMOS gamma                  | 0.58 V <sup>1/2</sup>    | PMOS gamma                  | 0.50 V <sup>1/2</sup>    |  |

| NMOS lambda                 | 0.02                     | PMOS lambda                 | 0.085                    |  |

| Capacitance                 |                          |                             |                          |  |

| t <sub>ox</sub> 161 A       |                          | C <sub>ox</sub>             | 2.17 fF/µm <sup>2</sup>  |  |

| C <sub>poly-sub</sub>       | 0.058 fF/µm <sup>2</sup> | C <sub>M1-poly</sub>        | 0.055 fF/µm <sup>2</sup> |  |

| fringe per edge             | 0.043 fF/µm              | fringe per edge             | 0.049 fF/µm              |  |

| C <sub>M1-sub</sub>         | 0.031 fF/µm <sup>2</sup> | C <sub>M1-M2</sub>          | 0.035 fF/µm <sup>2</sup> |  |

| fringe per edge             | 0.044 fF/µm              | fringe per edge             | 0.046 fF/µm              |  |

| C <sub>M2-sub</sub>         | 0.015 fF/µm <sup>2</sup> | С <sub>M2-M3</sub>          | 0.035 fF/µm <sup>2</sup> |  |

| fringe per edge             | 0.035 fF/µm              | fringe per edge             | 0.049 fF/µm              |  |

| Sheet Resistance            |                          |                             |                          |  |

| R <sub>ndiff</sub>          | 2.4 ohms/sq              | R <sub>pdiff</sub>          | 2.0 ohms/sq              |  |

| R <sub>poly</sub>           | 2.2 ohms/sq              | R <sub>M1,M2</sub>          | 0.07 ohms/sq             |  |

#### TABLE 2. NOMINAL PROCESS SPECIFICATIONS

Table 2 is a summary of some of the key parameters associated with this process. A key point of interest is the fact that the NMOS transistors undergo a mask shrink during processing, resulting in an NMOS device with a minimum drawn gate length of 0.8 microns instead of the 1.0 micron drawn length of a minimum sized PMOS device. Therefore, an important design consideration is the asymmetry of the technology (i.e. the n-type transistors have a significantly higher  $f_T$  than the p-type devices not only due to a higher carrier mobility, but also due to a shorter minimum gate-length.

The following chapters will detail the design, implementation and testing of the AGC and A/D converter motivated in this section.

|                                        | Motivation |      |      |

|----------------------------------------|------------|------|------|

| ······································ |            | <br> | <br> |

|                                        |            | ,    |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        | N .        |      |      |

|                                        | · ·        |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

|                                        |            |      |      |

.

18

•;;

# CHAPTER 3 Background

This section is intended to give some background material on MOS switched capacitor sampling and A/D converter techniques (especially high-speed topologies). It is by no means a comprehensive discussion or tutorial on design of either type of circuit.

## **3.1 Analog to Digital Conversion**

In a world increasingly dominated by digital signal processing, analog to digital converters play an important role as the interface between "real-world" analog signals and the digital circuitry used to process them. Conceptually, an A/D converter takes an input signal and compares it to a set of predetermined equally-spaced reference values, outputting a digital code for whichever value is closest to the input signal. In this manner, an A/D converter quantizes the range of possible values a signal can take and approximates the real

signal level with one of the quantized values. This approximation function adds a natural error to the output of the A/D. Referred to as quantization noise, this error is determined by the resolution of the converter and has a major impact

FIGURE 1. A/D conversion function

on the design of the A/D. In fact, for each additional bit of digital output desired, the resolution required (i.e. the number of reference levels used for comparison) increases by a factor of two.

Figure 1 shows the basic functionality of an A/D converter block, including the division of the input range into  $2^n$  equally spaced levels. Clearly, in order to reduce the quantization noise introduced by the converter, more resolution is desirable. However, since complexity increases with both speed and resolution requirements, several different architectures of converters have evolved.

The most basic A/D architecture is the flash converter. A representative flash converter is a simple, logical extension of Figure 1. It consists of  $2^n$  comparators, each comparing the same input signal against one of  $2^n$  different reference voltages generated from

a resistive ladder bias. All of the comparators work in parallel, and are followed by digital logic converting their  $2^n$  outputs into an n-bit number. A simplified schematic of one possible implementation of a 3-bit flash converter is shown in Figure 2. (It should be noted that since the input signal is assumed to be within the  $V_{ref+}$  to  $V_{ref-}$  range, only  $2^n$ -1 references and comparators are really necessary.) Flash converters are fast, straightforward, and have very low latency; but they have the major drawback that size and power increase *exponentially* as the resolution is increased. A 12 bit converter requiring  $2^{12} = 4,096$  comparators is clearly a distasteful proposition at best! Therefore, alternative architectures have been developed for high accuracy conversion.

## **3.2 The Subranging Architecture**

Subranging and pipelined A/D converters represent two methods of reducing the area and power consumption of high resolution flash converters. A subranging architecture performs the conversion function in two steps using essential two flash converters -- a "coarse" and a "fine" converter. For example, an 5 bit comparator could be broken up into a 3 bit coarse comparison and a 2 bit fine comparison as shown in Figure 3. In this manner, the comparator count is reduced from  $(2^5-1) = 31$  to  $(2^3-1) + (2^2-1) = 10$ . Such a savings never comes without a cost, and indeed the subranging architecture suffers a speed hit when compared to a straightforward flash converter. The fact that the conversion must occur in two steps -- with the coarse comparison necessarily finishing before the fine conversion can begin -- decreases the maximum rate at which the subranging converter can be clocked.

#### FIGURE 3. 3-Bit -- 2-Bit Subranging A/D architecture.

### **3.3 The Pipelined Architecture**

Unlike the subranging A/D, the pipelined architecture eliminates the need for the coarse conversion to complete before the fine conversion can begin by latching the signal in between the two steps. This is exactly the same technique used in pipelining digital datapaths. By sampling and holding the signal in between functional blocks, the latency of the converter is increased, but the **throughput** is also increased. Furthermore, the pipelined converter can relax the offset requirements of the fine comparators by replacing the mux shown in Figure 3 with an analog subtracter. Once the most significant bits of the signal are known, they can be passed through a DAC and an analog representation of the MSB's

can be subtracted off from the signal. In this way, the residue that is left, which represents the LSBs of the signal, can be gained up to the original signal level. In Figure 5 for example, a 4 bit converter having an LSB size of 120 mV is broken up into a 2 bit -- 2bit pipeline. After passing through the first set of comparators, the difference between the input and the analog representation of the 2 MSBs is generated and amplified for conversion into the LSBs. In the final conversion step, the LSB size has changed to 480 mV. A sample block diagram of one stage of a pipeline A/D converter is shown in Figure 4. Multiple stages may be hooked up together, and any number of bits (limited by flash converter size) may be resolved in each stage. Finally, pipeline converters have one other feature which makes them very attractive to use -- namely, digital correction. Digital correction takes advantage of the gain between stages of a pipeline converter in order to reject the random offset inherent in all comparators. By using extra comparators to detect when the signal has been incorrectly evaluated in a previous stage, a properly implemented digital correction scheme can make the comparator offset in all but the very last stage of the pipeline irrelevant. Furthermore, the input-referred offset of the final stage gets divided by the sum of all the interstage gain preceding it. In other words, the required comparator offset for a 1-bit per stage, 10 stage pipeline converter would be  $2^{10} =$ 1024 times less stringent than the offset required of a flash converter! For a full explanation of the technique of digital correction, please see [8].

.

### 3.4 The Sample and Hold Circuit.

Almost all A/D converters not only convert an analog signal into a digital number, they also convert a continuous time waveform into a signal which is discrete in time. Therefore, the A/D converter samples the input signal at discrete instants of time usu-

ally at a fixed rate (the conversion rate). Sample and hold circuits typically precede A/D converters and perform the continuous-to-discrete-time conversion so that the converter does not have to deal with a rapidly changing signal -- instead, by sampling the

input signal before feeding it to the A/D, the sample and hold circuit (or S/H) provides the converter with signal which is stable and well-behaved.

The principle behind most CMOS S/H circuits is very analogous to the idea used in dynamic digital logic. One of the advantages of metal-oxide-semiconductor (MOS) technology over bipolar junction transistor technology is it's ability to store charge for relatively long periods of time. Dynamic logic families take advantage of this ability by passing "packets" of stored charge from one circuit to the next; storing each desired signal on parasitic capacitances available at each stage. S/H circuits mimic this technique, but utilize larger, more precisely controlled capacitors to manipulate the more delicate analog signals. A diagram of a simple sample and hold is shown in Figure 6. The natural characteristics of the MOS transistor make it an excellent choice for use as a switch. The right hand side of Figure 6 shows the circuit with a MOS pass gate used to replace the ideal switch. As long as transistor  $M_{pass}$  is on, the switch is closed, and the output voltage will track the input voltage. When the control voltage on the gate of  $M_{pass}$  drops below  $V_{in} + V_T$ , the transistor turns off, and a sample of charge  $V_{in}*C_S$  is stored on the sampling capacitor. The right hand side of Figure 7 shows the voltage across the sampling capacitor tracking the input waveform until the sampling instant. After the sampling instant has passed, the value on the capacitor is held constant, and should equal the value of the input at the sampling instant. However, as Figure 7 illustrates, the act of opening the switch can introduce an error into the sampled voltage. First of all, the overlap capacitance of the pass transistor provides a capacitively-coupled path for the control voltage to inject charge onto the sampling node. As the control voltage falls (turning off the pass transistor), a capacitive divider between  $C_{overlap}$  and  $C_{sample}$  is formed. The resulting error is given by:

$$\Delta v = -\left(\frac{C_{overlap}}{C_{sample}}\right) V_{dd}$$

(EQ 1)

Equation 1 assumes that the control voltage switches from the supply  $V_{dd}$  to ground, and does so quickly (the switching time is on the order of the RC time constant associated with the sampling capacitor and the on-resistance of the switch). Another source of error comes from the charge stored in the channel of the MOS transistor. Since the transistor is turned off quickly, the charge in the channel of the device is left to dis-

charge to either  $C_S$  or to the input. The amount that flows to  $C_S$  depends on the impulse response of the distributed resistance of the channel in series with the impedance on either side of it; however, a reasonable approximation

FIGURE 8. Bottom Plate Sample and Hold

٠.

assumes that 1/2 the channel charge flows to each side of the transistor for a fast  $V_{dd}$  to ground transition. The resulting error is:

$$\Delta v = -\frac{1}{2} \left( \frac{Q_{channel}}{C_s} \right) = -\frac{1}{2} \frac{\left( L_{eff} W C_{ox} \left( V_{dd} - V_{in} - V_T \right) \right)}{C_s}$$

(EQ 2)

The fact that the error introduced is dependent on the input voltage has dire consequences. The input dependence means that the error is no longer a DC offset phenomenon, and is therefore more difficult to remove for most systems.

Figure 8 shows an improved design for a sample and hold circuit. A technique known as bottom plate sampling is employed to remove the signal dependence in the error term. The operation can be understood as follows: At first,  $S_I$  and  $S_2$  are closed, allowing the input signal  $V_{in}$  to be sampled onto the capacitor  $C_S$ . When  $S_S$  and  $S_I$  are opened, an amount of charge proportional to the signal voltage and to the size of capacitor  $C_S$  is left floating on  $C_S$  exactly as in the previous circuit. However, if  $S_2$  is opened slightly before  $S_I$ , then the second switch determines the sampling instant. Since both drain and source of transistor  $S_2$  are at ground, no signal dependent charge injection is introduced. When  $S_I$  is subsequently turned off, the charge in the channel sees an open circuit on the other side of  $C_S$ and therefore all the charge *must* flow to the other side of the transistor to the input source (and again no error is introduced). Finally, both  $S_3$  and  $S_4$  switches close, and the high gain op amp is now closed in a negative feedback loop, forcing the voltage at the inputs to the same voltage. Therefore, the charge on  $C_S$  integrates out onto  $C_I$ . If no additional circuitry is provided to remove the residual charge on  $C_I$  after every cycle, then the circuit of Figure 6 implements an integrator function. However, if the charge on  $C_I$  is reset after every sample, then by carefully ratioing the sizes of the two capacitors, a voltage gain of  $C_S/C_I$  can be realized. Therefore, if  $C_S = C_I$ , then the output voltage should equal the input signal captured at the sampling instant.

Switched capacitor sampling circuits, while traditionally used as a unity gain sample and hold preceding an A/D converter, can be easily adapted to perform a straightforward gain function. By simply ratioing  $C_S$  and  $C_I$ , the sample and hold circuit in Figure 6 effects a gain of  $C_S/C_I$ . Pipeline A/D converters perform interstage gain in this manner, since the signal travelling down the pipeline is already discrete time. An added bonus is achieved by switching  $S_3$  to a reference voltage from a DAC instead of to ground (See section 3.3 on pipeline converters). The resulting output is  $(C_S/C_I)^*(V_{in}$ -  $V_{ref}$ ). Therefore, the interstage gain, and the subtraction of the MSBs can be efficiently combined into this one circuit.

# CHAPTER 4 VGA Circuit Design

## **4.1 Introduction**

A portable terminal such as the InfoPad must have variable gain placed in the receive path of its radio. The explanation for this requirement is simple: The "portability" of the terminal implies that the receiver may be moving at any given time. A moving terminal may be physically very close to the transmitter (and therefore receiving a strong signal), and then move very far away (where it receives a weak signal). Additionally, there may or may not be a direct line of sight (LOS) between transmitter and receiver -- where loss of LOS can cause severe degradation of received signal power. Wireless receivers must include circuitry to automatically adjust to these changes in environment. Simply put, the purpose of the automatic gain control circuit (AGC) is to automatically adjust the gain of the receive path so that the signal processed by the baseband circuitry appears to be of constant power regardless of the actual signal size at the antenna. If the signal level after the AGC is too large, then either the A/D or the AGC itself may begin to clip the waveform, resulting in severe distortion and loss of signal. (Although this is sometimes acceptable in certain phase-modulated systems). On the other hand, if the received signal is still too small after the last AGC stage, the A/D converter may not be able to resolve it (i.e. quantization noise will overwhelm the signal). In other words, the AGC and the A/D combine to detect a signal with a wide dynamic range. While it is true that bits in the A/D may be traded off for gain in the AGC (i.e. increased resolution in the A/D, beyond the minimum required for

SNR, allows it to detect a potentially smaller signal), higher resolution converters soon become prohibitively costly (in terms of power, area and complexity). Furthermore, the digital processing which follows the A/D (the spread spectrum demodulator in this case) must also process any additional bits added to the A/D -- again increasing power and area. In order to accommodate the entire 40 dBm of dynamic range in the received signal (see Table 1), the A/D converter would have to have 9 bits of accuracy (for a 0.3 volt signal). In the end, the A/D can not bear the full load of accepting an extremely wide dynamic range, leaving the AGC as an important part of the wireless receiver design.

Every AGC contains two critical blocks -- a variable gain amplifier (VGA) and the power detector circuit which feeds back the control signal(s) used to adjust the gain of the VGA. At the time of this writing, the power detector for the InfoPad AGC has not been implemented. However, the VGA has been designed and implemented with the eventual addition of the detector and the control loop in mind. Therefore, the rest of this chapter will describe the design of the VGA block for the InfoPad receiver.

## 4.2 Amplifier Topology

As mentioned before, the design of the InfoPad CDMA radio's VGA is a significant departure from traditional designs. Because of the inherent sampling incorporated into the mixing operation, a multi-stage cascade of dis-

crete-time amplifiers is used to replace a standard continuous-time VGA (variable-gain amplifier). Therefore, what was once an amplifier design problem involving a trade-off between gain and bandwidth becomes a sample-and-hold design requiring an op amp and a set of switched capacitors that can settle to four bits of accuracy within one clock period. Figure 1 shows a basic sample-and-hold amplifier as described in Section 3.4; it consists of an operational amplifier, sampling and integrating capacitors, and several switches made out of MOS transistors. However, such a simplistic design is inadequate for practical use. First, the design must be made differential. A differential circuit is necessary not only to reject charge injection from the switches (to first order, charge will inject equally into both paths becoming a common-mode offset), but perhaps more importantly, a differential topology is required to reject common mode noise coupling into the analog signal path (especially from the large digital signal processing block on chip used to demodulate the CDMA signal). Figure 2 shows how digital switching can cause common mode ringing on analog lines. If the sample is taken single-ended, a large error would result (often larger than the signal itself!). But a differential design with careful layout (so that parasitic

capacitance is balanced differentially) can maintain a small differential signal amidst such large common mode noise.

As mentioned before, signal dependent charge injection can be a malignant sideeffect of the sampling operation. The timing of the control voltages for

Chapter4

switches  $S_1$ ,  $S_2$ , and  $S_3$  in Figure 1 must be designed to effect the bottom-plate sampling described in Section 3.4. When performing bottom plate sampling, the operational amplifier shown in Figure 1 is used to drive the output to the correct value proportional to the input voltage. While quite effective for combatting signal dependent charge injection, there is another side effect to this topology. When the circuit is in track mode, the output no longer follows the input voltage. Therefore, when the hold phase arrives, the output must settle to the correct output voltage from some reset

value (usually zero). If the amplifier is appropriately designed with adequate phase margin, the settling curve follows an exponential curve with a single RC time constant, and a representative curve is

shown in Figure 3. Typically, only half of the clock cycle time is dedicated to the hold period (the other half goes to the tracking period). Therefore, the output has half of one cycle (T/2) to exponentially approach it's final value. Unfortunately, an infinite amount of time is required for an exponential curve to reach it's final *exact* value. This can be seen in Equation 3, where A is the final output value and the error goes to zero only for t = infinity:

$$V_{out} = A (1 - e^{-i/\tau})$$

(EQ 3)

Where  $\tau$  is the time constant of the circuit. Therefore, there will always be an error introduced into the signal due to incomplete settling. Fortunately, the situation is not quite as grim as it may seem. The settling error incorporated in Equation 3, Ae<sup>-t/ $\tau$ </sup>, is linearly proportional to the final value A if t is constant. In other words, if given the same amount of time to settle, the circuit will always settle to the same percentage of its final value. Therefore, the gain of the circuit will always be reduced by the constant factor e<sup>-t/ $\tau$ </sup>. As long as t

is constant, this gain compression does not introduce a real error into the signal. In fact, the actual **exact** value of the gain is rather unimportant since the negative feedback from the AGC control loop will try to force the output of the VGA to be constant regardless of

the gain of each stage. (Although the compression still causes a loss of gain in the signal path!) However, a real error does enter the signal path when the allowed time, t, is not constant. Timing jitter in the sampling instant provided by the edge of a clock causes t to vary somewhat from sample to sample, resulting in an error which is proportional to the jitter variation,  $\Delta t$ , and to the slope of the settling curve at the sampling instant. Given enough time or a very fast circuit, this error can be quite negligible (since the slope of the curve decreases with time). Unfortunately, the InfoPad design has neither of these luxuries. The 128 Msample per second requirement translates into a 7.8 nanosecond clock cycle time. At most half of this (and in reality, much less than half) can be used for settling time.

FIGURE 5. Two Port Representation of Operational Transconductance Amplifier Figure 4 shows clock phases for the circuit in Figure 1. The hold period (and therefore, the settling time) is reduced in length by the non-overlapping period between phases (necessary for proper sampling) as well as by the finite rise and fall time of the clock's

edges. The hold period for the InfoPad radio's clocks is about 2.5 ns. In order to both avoid degrading the SNR of the signal, as well as to avoid significant gain attenuation, a the settling error in the receiver VGA should be kept smaller than half the LSB of the 4 bit converter. In other words, the error must be less than 1 part in 32 (3.125%) of the signal level.

$$e^{-t/\tau} \le 0.03125$$

(EQ 4)

$$t/\tau = \ln\left(\frac{1}{0.03125}\right) \cong 3.47$$

(EQ 5)

Equation 4 and Equation 5 show that settling to this level of accuracy requires approximately 3.5 settling time constants. Plugging in t = 2.5 ns into Equation 5 gives  $\tau$  on the order of 0.7 ns. However, since the VGA design consists of more than one stage, each settling error will add to the others, resulting in a larger error. For example, in order to keep the error lower than one-half LSB for a four stage VGA, each stage would need to settle to less than 1 part in 128 (~0.8%) of the exact value. The result is a  $\tau$  on the order of 0.5 ns... or over 310 MHz of bandwidth. Therefore, a careful design of the amplifier is required with settling time (and therefore, closed loop bandwidth) as a primary design constraint. One of the main limiting factors in the design of a high speed sample and hold amplifier (referred to as an SHA) is the operational amplifier used to drive the output to it's final value. In order to achieve the fastest possible circuit, a single-stage transconductance topology has been chosen for the op amp. The details of the design of this operational transconductance amplifier (OTA) is described later in this chapter. But for the purposes of this section, it is enough to know

that the OTA can be modeled as a  $G_m$ transconductance with a high output impedance  $R_o$ , as illustrated in Figure 5.

Figure 6 shows the SHA during the evaluation phase of its operation.  $C_I$  encloses

the OTA in a series-shunt feedback loop with feedback factor:

$$f = \frac{C_l}{C_l + C_s + C_p + C_{in}}$$

(EQ 6)

Where  $C_p$  is the parasitic capacitance at the summing node,  $C_{in}$  is the input capacitance of the op amp, and  $C_L$  is the output load being driven. Given that the open loop gain of the amplifier is  $G_m R_o$ , the closed loop gain and bandwidth of the circuit can be determined. Including the capacitive divider before the input to the OTA, the closed loop gain becomes:

Chapter4

$$A_{CL} = \left(\frac{C_s}{C_s + C_P + C_{in} + C_I}\right) \left(\frac{A_{OL}}{1 + A_{OL}f}\right) = \left(\frac{C_s}{C_s + C_P + C_{in} + C_I}\right) \left(\frac{G_m R_o f}{1 + G_m R_o f}\right) \frac{1}{f}$$

(EQ 7)

$G_m R_o f$  is the loop gain, T, of the circuit, and f is given by Equation 6, leaving:

$$A_{CL} = \left(\frac{C_s}{C_s + C_p + C_{in} + C_l}\right) \left(\frac{C_l + C_s + C_p + C_{in}}{C_l}\right) \left(\frac{T}{1 + T}\right) = \frac{C_s}{C_l} \left(\frac{T}{1 + T}\right)$$

(EQ 8)

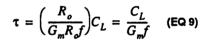

The loop gain term in Equation 8 is close to unity for large values of T. However, in an AGC, a small reduction in the gain is quite irrelevant since the overall gain in the receiver is affected very little by this variation because of the negative feedback of the control loop. Therefore, lower values of T are acceptable, and the closed loop gain of the amplifier in is close to (but not exactly)  $C_S / C_I$ . The settling time at the output node is determined by the output impedance of the closed-loop amplifier and by the output load. Therefore, the RC time constant at the output of the amplifier is given by:

FIGURE 7. SHA topology sampling

onto C<sub>1</sub> as well as C<sub>8</sub>.

Clearly, in order to maximize the speed of the amplifier, the feedback factor, f, should be made as large as possible, and the transconductance,  $G_m$ ,

should also be increased if possible.  $G_m$  is an op amp parameter, and is discussed in Section 4.3. However, the feedback factor, defined in Equation 6 relates directly to  $C_S$ and  $C_I$ . Unfortunately, in order to achieve a gain greater than one, the closed loop gain

of this topology,  $C_S / C_I$ requires that  $C_S$  be larger than  $C_I$ , reducing the feedback factor. An alternative topology is shown in Figure 7 in which the integrating capacitor is not only used to close the feedback loop around the OTA, but is also used as a second sampling

capacitor to capture a sample of charge from the input. During the track mode (as shown in Figure 7) the two capacitors are shorted together in parallel, effectively making one large sampling capacitor. When the hold, or integration phase arrives, the switches shown in the figure are reversed and the charge on  $C_S$  is transferred to  $C_I$ . The closed loop gain of the circuit is now  $\frac{C_S + C_I}{C_I}$ . In other words, the new topology achieves a larger loop gain for the exact same feedback factor and bandwidth (a gain of one has been added to the old  $C_S$  $/C_I$  gain term). Alternatively, the sampling capacitor can be made smaller for the same closed loop gain, but higher bandwidth. (e.g.  $C_S$  must equal  $C_I$  to effect a gain of two in the new topology, but in the previous design  $C_S$  had to be twice as large as  $C_I$  -- decreasing the feedback factor.) The final design of the SHA for the VGA is shown in Figure 8. The

#### VGA Circuit Design

center sampling switch across the op amp's inputs and an extra clock phase,  $\phi_{s2}$ , have been added to provide better charge injection matching from the sampling operation (charge injection from the center switch will be less dependent on geometry match-

ing than charge from two separate switches). Not shown in Figure 8 is the control for changing the gain of this stage. Figure 9 shows the single-ended version of how this control is accomplished. When the indicated switch is closed, then the circuit is essentially the same as the circuit in Figure 7 whose operation was just described as having a closed-loop gain of  $\frac{C_S + C_I}{C_I}$ . However, when the switch is opened,  $C_S$  is removed from the circuit. The closed-loop gain of the circuit now becomes  $C_I / C_I$ . Therefore, each stage of the final VGA consists of a SHA providing a gain of either  $\frac{C_S + C_I}{C_I}$ , or a gain of unity. This capacitive ratio can be chosen to be any value desired; however, increasing  $C_S$  also decreases the feedback factor and therefore the bandwidth (Equation 6 and Equation 9). Due to the extremely high speed requirements of the InfoPad environment, stages implementing only 3 dB each have been cascaded together to provide 12 dB of total gain. 3 dB of gain (or approximately 1.4x) requires a  $C_S$  equal to a little less than half of  $C_I$  (again, the exact value of the gain is unimportant).

Finally, the SHA design requires common mode feedback. Figure 8 shows capacitive common-mode feedback that has been added with a switch for reset during the sampling phase. This feedback is essentially the same technique used when the  $C_I$  loop is closed (except, of course that it is common mode), since the capacitors feed back the common mode output to the tail current source of the OTA (see next section).

## 4.3 Operational Amplifier Design

The heart of the sample-and-hold amplifiers described in the last section is the operational amplifier. As mentioned before, the high-speed requirements of the system dictate a simple, high-bandwidth design for the OTA. While most CMOS sample-and-hold amplifiers (for use in a pipeline A/D for example) use two-stage amplifiers to achieve higher gain, the InfoPad VGA design does not have this requirement. Interstage gain amplifiers in a

FIGURE 10. 2 bit -- 2 bit Pipeline Conversion Example with small gain error

#### FIGURE 11. AGC compensation of gain errors by negative feedback control loop

pipeline A/D require gain accuracy on the order of the resolution of the entire converter (in other words, each stage of an N-bit pipeline A/D must have gain precisely controlled to one part in  $2^N$ ) [9]. However, as mentioned before in Section 4.2, the negative feedback provided by the overall control loop compensates for any error in the gain of individual stages of the AGC. Therefore, in the trade-off between gain and bandwidth, a lower-gain-but-higher-bandwidth design has been chosen. The effects of gain compression from finite OTA gain are illustrated in Figure 10 for a pipeline stage and in Figure 11 for the InfoPad AGC.

A single-stage telescopic cascode topology is the fastest known op amp topology available in CMOS technology. The use of common gate cascode transistors eliminates the Miller effect at the inputs, and the low impedance seen looking into the source of a cascode transistor means the circuit is essentially a single-pole system. While a folded cascode has the advantage of increased headroom capability, the inclusion of PMOS transistors in a folded design adversely affects the non-dominant poles. This lower PMOS  $f_T$  limits the bandwidth when feedback is applied. Therefore, the telescopic cascode circuit in Figure 12 has been designed for use as an operational transconductance amplifier [3]. The input transistors and cascode transistors ( $M_{in+}$ ,  $M_{in-}$ ,  $M_{ncasc+}$ , and  $M_{ncasc-}$ ) are n-type devices to maximize the bandwidth of the amplifier. The width of the input devices is determined by a settling time optimization analysis presented later in

this chapter. PMOS transistors  $M_{psrc+}, M_{psrc-}, M_{pcasc+}$ , and  $M_{pcasc-}$  form a pair of active current source loads in order to achieve a high output impedance and therefore a high DC gain. The size of these devices is determined primarily by the required signal swing at the output of the OTA. The devices down the middle of the diagram in Figure 12 represent a high-swing bias circuit for the two NMOS cascode transistors.  $M_3$  and  $M_4$  are simply a cascoded PMOS current mirror

to bias the two NMOS transistors.  $M_1$  is forced to operate in the triode or linear range of operation by the diode connected transistor  $M_2$ . Therefore,  $M_1$  acts as a source degeneration for  $M_2$ , and the W/L ratio of  $M_1$  is chosen so that the voltage drop from drain to source will match the desired  $V_{ds}$  across the two input devices. This value,  $V_{ds\_input}$  should be as low as possible without pushing the input devices into the triode region of operation. Therefore, the final bias voltage at the gates of the NMOS cascode devices is designed so that the input transistors  $M_{in+}$  and  $M_{in-}$  have drain to source voltage:

$V_{ds\_input} = V_{ds\_l} = V_{dsat} + V_{margin}$ . A very aggressive margin of 150 mV has been chosen so that the available headroom for the signal to swing in the negative direction is maximized as long as  $M_2$  is designed properly to match the  $V_{gs}$  drop of the cascode transistors. Therefore, the design equations for  $M_1$  and  $M_2$  are:

$$W/L_2 = \left(\frac{W/L_4}{W/L_{psrc}}\right)(W/L_{ncasc})$$

(EQ 10)

$$I_{D1} = \mu C_{ox} (W/L_1) \left( (V_{gs1} - V_T) V_{ds1} - \frac{1}{2} V_{ds1}^2 \right)$$

(EQ 11)

Where Equation 11 can be solved for W/L<sub>1</sub> since  $I_{D1}$ ,  $V_{gs} - V_T$ , and the desired  $V_{ds1}$  are known. The bias circuitry for the PMOS current sources have been designed with the same technique, as shown in Figure 13. Figure 13 also shows the tail current source bias generated from an off-chip current source flowing into an NMOS diode. This diode serves as a reference for all currents used by the OTAs. The tail current source of the amplifier simply mirrors the current reference, and transistors  $M_5$ ,  $M_6$ ,  $M_7$  and  $M_8$  also mirror the

reference current for use in generating bias for the PMOS current source loads.  $M_7$  and  $M_8$ help to match the current being mirrored into the PMOS current sources with the current flowing in the tail source of the OTA by matching the  $V_{ds}$ across  $M_5$  and  $M_6$  to the

expected  $V_{ds}$  across the tail source (this is critical for matching the currents through the devices -- the extremely poor  $\lambda$  of the process means  $I_{ds}$  depends strongly on  $V_{ds}$ ). The tail current source, formed from transistors  $M_{taill}$  and  $M_{tail2}$ , is split into two parts so that half of the current source can be used for common mode feedback during the evaluation phase

of operation (during the reset phase, both  $M_{tail1}$  and  $M_{tail2}$  are connected to the reference voltage). The use of only half the transistor in the common mode feedback loop brings down the loop gain around the loop, and helps ensure stability. It also helps protect the circuit from charge injection and ringing from turning on and off the reset switch M<sub>cmfb</sub>.

FIGURE 15. Transistor sizing for sample and hold switches

## 4.4 Optimizations

Almost any wireless system is designed with the expectation that the received signal will be small. The loss in signal power suffered from transmission through the air usually means that the signal seen by the antenna is significantly smaller than the baseband circuitry (the A/D) can detect. Invariably, amplifiers must be inserted in the receive path of the signal in order to gain the signal up to a detectable level. At the time of this writing, a typical A/D converter might expect an input signal which had been amplified to a maximum range of about +/- 1 volt or even larger. However, sustaining such a large signal swing, especially in a switched-capacitor circuit (e.g. the

InfoPad's VGA), requires extra power and area. Also, slewing may begin to hinder the speed of operation for the circuit, and headroom limitations in the OTA may begin to cause distortion or clipping unless a wide-output swing topology is chosen (e.g. a folded cascode). Therefore, it is clearly advantageous to apply only enough gain to the signal so that it meets the minimum power level so that the A/D can accurately resolve it. Adding more gain than this minimum amount can help relax the accuracy requirements for the A/D, but might incur all the potential headaches just outlined. Therefore, in a somewhat backwards design approach, the signal swing at the input of the A/D has been chosen to just meet the minimum detectable signal given the estimated offset characteristics of the A/D (allowing, of course, for some extra margin). The entire receive path of the CDMA radio has thus been designed for a maximum signal swing of +/- 250 mVolts (differentially, this is -0.5 volts to +0.5 volts).

Maintaining a maximum signal swing at a low level has another advantage. Typically, the pass transistors used as sampling switches for the SHAs would necessarily have to be complementary in nature because of the larger signal swing. In other words, if  $v_{in+}$  and  $v_{in-}$  differ by a significant amount, then the on resistance of the two switches ( $M_+$  and  $M_-$  in Figure 16) may not match each other because of the different voltages biasing them ( $V_{dd} - v_{in}$ ) -- this can disastrously decrease the input bandwidth of half the sampling path resulting in signal distortion and introducing a phase error. Therefore, by choosing an appropriate common mode bias voltage ( $v_{icm} = 1.7$  to 2.5 volts in this case), all the switches in the SHA design (see Figure 8) may be constructed out of n-type devices. Not only does the elimination of the extra PMOS transistor for each pass gate simplify clock-

ing (a complimentary pass gate requires clk and  $\overline{clk}$ ), but also increases the sampling bandwidth of the network by reducing parasitic capacitance at the drain and source nodes. The input bandwidth of the sampling network is determined primarily by the on resistance of the switches, and by the size of the capacitors used to sample the signal. In the case of Figure 15, the worst case input bandwidth is given by:

$$\tau = \left[ (2R_{on1} \| R_{on1}) + \frac{1}{2}R_{on2} \right] (C_s + C_l) = \left( \frac{2}{3}R_{on1} + \frac{1}{2}R_{on2} \right) 3C_s$$

(EQ 12)

Where  $R_{on}$  is determined by:

$$R_{on} = \frac{1}{\mu C_{ox} (W/L) (V_{gs} - V_T)^{19}} \bar{\mu}$$

Clearly, minimizing  $C_S$  and

maximizing  $W/L$  and  $(V_{dd} - V_{bias1} - V_{bias2} - V_{bias2} - V_{bias2} - V_{bias2} - V_{bias2} - V_{out}$

network. Unfortunately, the

feedback factor defined in

Equation 6 will decrease if  $C_I$

is made small relative to the

parasitic and output load

capacitance on the OTA.

Therefore, a  $C_S = 150$  fF and

a  $C_I = 300$  fF have been cho-

sen. To meet the input bandwidth requirements of the system,  $V_{dd}$  has been chosen for 5 volt operation, with a  $V_{icm} = 2.5$  volts (although the OTA can operate at a supply voltage of 3.3 volts, and a common mode voltage of 1.7, the pass transistors used in the switch array <u>must</u> be driven by a 5 volt clock in order to maintain a sizeable ( $V_{dd} - V_{icm} - V_T$ ). Transistors have been sized for appropriate on-resistances, and their W/L ratios are shown in Figure 15. The resulting track bandwidth of the input network is on the order of 3 GHz! (Which was necessary for the sampling demodulator to admit a GHz bandwidth input, but was perhaps a little generous for the following stages).

Figure 16 shows the relative sizing of the devices used to implement the OTA. All dimensions are in microns. The numbers shown in the figure represent drawn geometries, and do not include lateral diffusion  $(L_D)$  or width shrinkage from implantation of the drain and source areas. As described in Section 2.3, the process used to fabricate the CDMA receiver chips is an asymmetric process -- all NMOS transistors undergo a mask shrink to improve maximum  $f_t$  of the n-type devices. Therefore, the actual drawn length of each NMOS transistor has been be decreased by 0.2 microns. (e.g. the input devices are 300/0.8 microns drawn instead of 300/1.0). The design process which yields the devices shown in Figure 16 proceeds as follows:

Recall that  $g_m = \frac{2I_D}{(V_{gs} - V_T)}$  for an MOS transistor. Therefore, in order to achieve maximum  $g_m$  (and therefore, maximum speed) for a constrained  $I_D$ , the current density<sup>1</sup> of the device,  $V_{gs} - V_T$ , should be minimized without forcing the transistor into the subthreshold

#### **VGA Circuit Design**

region of operation. For the OTA used in the InfoPad's CDMA radio, a  $V_{gs} - V_T = 150$  mV has been chosen. Once the current density has been fixed, the drain current through the device,  $I_D = \frac{\mu C_{ox} W}{2 L} (V_{gs} - V_T)^2$ , becomes proportional to the transistor's W/L ratio. Increasing the width of the input devices certainly improves the  $g_m$  of the OTA, but unfortunately the input and output parasitic capacitances also increase -- resulting in loss of feedback factor and an increased load that needs to be driven by the OTA. Equation 14 shows  $\tau$  as a function of the input device sizes without taking the dependence of part of  $C_{in}$  on W/L.

$$\tau = \frac{C_L}{G_m f} = \frac{C_L (C_l + C_s + C_p + C_{in})}{C_l [\mu C_{ox} (W/L) (V_{gs} - V_T)]}$$

(EQ 14)

By taking the increased self-loading of a large device into account, Equation 14 becomes:

$$\tau = \frac{C_L(C_l + C_s + C_p + WLC_{ox})}{C_l [\mu C_{ox}(W/L) (V_{gs} - V_T)]}$$

(EQ 15)

Taking the derivative of Equation 15 with respect to W, and setting the result equal to zero, results in a W/L which corresponds to a local minimum for  $\tau$  [10]. The result of the optimization performed on Equation 15 for this process is the two 300/0.8 micron input devices presented in Figure 16. The desired current level in the input devices can

Current density may be somewhat of a misnomer here since V<sub>gs</sub> - V<sub>T</sub> does not have the units of current per unit area. It does, however, refer to the fact that the V<sub>gs</sub> - V<sub>T</sub> of a MOS transistor is proportional to the square root of the drain current, I<sub>D</sub>, divided by the W/L ratio of the device.

now be determined from the relation:  $I_D = \frac{\mu C_{ox} W}{2} (V_{gs} - V_T)^2$ . From this analysis, a total tail current of 2 mA has been chosen. The sizes of all other devices in the circuit are simply chosen to meet the headroom required from the output signal swing. Finally, the tail current source has been designed with a non-minimum channel length in order to increase its output impedance (and therefore, the CMRR).

The designs discussed in the previous sections have been used to implement a small fourstage VGA. Each stage introduces a gain of either 0 dB or 3 dB into the signal path -resulting in a net controllable gain of 0 to 12 dB in 3 dB increments. The  $C_I$  and  $C_S$  used are 300 and 150 fF each respectively, and the transistor sizes are as shown in Figure 15 and Figure 16. See Section 6.1 for descriptions of the actual silicon die, and see Appendix A for relevant SPICE simulation decks.

SPICE simulations of the proposed VGA design (extracted from actual layout) revealed that the sample and hold stage met the speed and accuracy requirements dictated by the system while consuming only 10 mW of power per stage. However, when two or more stages are cascaded together, a kickback noise problem was encountered. The problem stems from the large parasitic capacitance associated with the bottom (closest to substrate) plate of the integrating capacitor  $C_I$ . At the end of each evaluation phase,  $C_I$  and its parasitic  $C_{Ip}$ , have charge equal to  $CV_{out}$  stored on them. As illustrated in Figure 7, when the next track phase arrives,  $C_I$  is switched to the input in order to sample the next value. Unfortunately, the charge stored on  $C_I$  and  $C_{Ip}$  is kicked back to the previous stage. The result is a signal dependent signal excursion at the beginning of the previous stage's set-

tling curve. These kickback excursions severely reduced the amount of time available to the circuit to settle to its final value. A transient analysis of two cascaded stages of the VGA is shown in Figure 17. The clock rate has been slowed to 64 MHz because of the severe error introduced into the signal at full speed due to incomplete settling. See Appendix A for SPICE decks *samnet.sp* and *samnet.spice*. Simulations show the VGA stages settling to the required accuracy when being clocked at 1/2 the original rate (64 MHz).

# CHAPTER 5 A to D Design

## **5.1 Introduction**

One of the inherent properties of a spread spectrum system is the trade-off between bandwidth and accuracy. More specifically, a direct sequence spread spectrum (DS-SS) system such as the InfoPad radio trades off extremely high speed for reduced resolution. In other words, by dividing each transmit pulse into 64 smaller pulses (called 'chips') the radio hardware must now run 64 times faster than might previously have been required if this "spreading" had not been performed. However, by using a correlator (essentially a matched filter) on the received signal to "de-spread" it, the noise power introduced by quantizing the analog signal into a digital code is reduced by a factor of 64 (or more accurately, the signal to noise power ratio (SNR) is increased by a factor of 64). This factor is called the spreading gain of the DS-SS system, and effectively adds 3 bits of resolution to the analog to digital conversion function. In other words, if the system's signal to noise

Analog Circuits for an All CMOS Integrated CDMA Receiver

#### A to D Design

requirements dictate that quantization noise can not exceed -77dB below the signal power, then the 12-bit A/D converter required for conventional systems only needs to have 9 bits of resolution in a spread spectrum environment (with a spreading gain of 64). Figure 1 and Figure 2 are rudimentary illustrations of the effects of spreading [11]. The spreading gain of the DS-SS matched correlator effectively adds 3 bits of resolution to the A/D converter; unfortunately, beyond a certain number of bits of resolution, the quantization noise becomes quite negligible compared to thermal noise and interference from other transmissions (the InfoPad system multiplexes several users into the same physical cell using orthogonal codes to distinguish one user from another -- in this type of system, called Code Division Multiplexing, each user receives interfering transmissions from all the other users). At the point where thermal noise and interference begin to dominate the signal to noise ratio, increasing the resolution of the converter provides no real benefit. Simulations in the U.C. Berkeley Ptolemy system have shown that an A/D converter with 4 bits of resolution (effectively 7 bits after de-spreading) is sufficient to bring quantization noise well below the interference noise floor [5]. As far as A/D converter technology goes, 4 bits could certainly be considered a fairly low resolution converter. Unfortunately, the spreading gain of the system also results in a 64-fold increase in sampling rate for the converter. Therefore, the rest of this chapter will detail the design of the 4-bit 128 Msamples/sec A/D converter for the InfoPad CDMA receiver with achieving low power as a key design constraint.

# **5.2 Architecture**

Of all the architectures for high speed A/D converters<sup>1</sup>, the flash architecture is the fastest. An N-bit flash converter, as described in Section 3.1, performs conversion simply by placing 2<sup>N</sup> comparators in parallel and determining where, among the 2<sup>N</sup> levels, the input lies. For a resolution as small a 4 bits, a flash architecture is a feasible option for a 128 Msample/sec converter. Unfortunately, the amount of hardware and power required for an N-bit flash A/D increases exponentially as 2<sup>N</sup>, making a full flash design less attractive because of the extremely low-power requirements of the system. However, even with a very high speed comparator design (see Section 5.3), exploration of subranging and pipeline A/D converters revealed that the 7.8 ns cycle time was insufficient for performing the extra functions required in these architectures (see Section 3.2 and Section 3.3, for a description of subranging and pipeline converters). Furthermore, the addition of a high speed sample and hold amplifier (SHA) in between stages of a pipeline converter increases the power consumption due to the static current in the operational amplifier. In fact, the increase in power consumption added by the insertion of a SHA in a pipeline far outweighs the power saved by reducing the number of comparators from 15 to 8 for a 4 bit converter<sup>2</sup>. The conclusion that might be drawn from this analysis is that the correct architecture to choose for the A/D converter topology is a flash. Indeed, for a stand-alone 4-bit CMOS converter

<sup>1.</sup> Although certain other A/D topologies, including delta-sigma and successive-approximation converters, may have high clock rates, the term "high speed" here refers specifically to a class of converters called 'nyquist rate' converters. Unlike oversampled converters (e.g. delta-sigma), this class of converters processes one data sample per clock period, achieving the fastest possible data conversion rate for a given clock speed.

<sup>2.</sup> Note that for higher resolution converters, the addition of a pipeline stage might very well reduce the overall power consumption of the A/D since the number of comparators increases exponentially with the number of bits, N.

FIGURE 3. Modified 1-bit to 3-bit pseudo pipeline architecture operating at 128 Msamples/sec, the flash design would almost certainly be the architecture of choice. However, by combining the A/D function with the AGC function, further improvements were possible. The final A/D design for the CDMA receiver pipelines one of the four bits, resulting in a 1-bit to 3-bit pipeline converter. This design is depicted in Figure 3. Since the InfoPad CDMA radio uses a discrete-time AGC immediately before the A/D converter. Each sample-and-hold amplifier in the AGC looks exactly like the interstage gain amplifier of a pipeline A/D. Therefore, the hardware to perform most of the pipelining function is already in place and could be used by the A/D at no extra cost. The AGC consists of several stages of gain, some of which must be small (for a reasonably fine gain resolution). Therefore, the interstage gain in the pipeline can be made from <u>multiple</u> sample-and-hold amplifiers, allowing the function of generating of a residue (input signal minus analog version of MSB output) to be pipelined itself. It was found that by placing two stages of 3dB gain in between the first comparator and the remaining 3-bit flash A/D, the residue generation

function could be split into two stages -- allowing enough time to generate a residue at 128 MHz.