## Copyright © 1995, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# A DATA-DRIVEN MULTIPROCESSOR ARCHITECTURE FOR HIGH THROUGHPUT DIGITAL SIGNAL PROCESSING

by

Kwok Wah Yeung

Memorandum No. UCB/ERL M95/54

10 July 1995

## A DATA-DRIVEN MULTIPROCESSOR ARCHITECTURE FOR HIGH THROUGHPUT DIGITAL SIGNAL PROCESSING

by

Kwok Wah Yeung

Memorandum No. UCB/ERL M95/54

10 July 1995

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering

University of California, Berkeley

94720

#### **Abstract**

#### A Data-driven Multiprocessor Architecture for High Throughput Digital Signal Processing

by

Kwok Wah Yeung

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California at Berkeley Professor Jan M. Rabaey, Chair

A data-driven multiprocessor architecture called PADDI-2 specially designed for rapid prototyping of high throughput digital signal processing algorithms is presented. Characteristics of typical high speed DSP systems were examined and the efficiencies and deficiencies of existing traditional architectures were studied to establish the architectural requirements, and to guide the architectural design. The proposed PADDI-2 architecture is a highly scalable and modular, multiple-instruction stream multiple-data stream (MIMD) architecture. It consists of a large number of fine-grain processing elements called nanoprocessors interconnected by a flexible and high-bandwidth communication network. The basic idea is that a data flow graph representing a DSP algorithm is directly mapped onto a network of nanoprocessors. The algorithm is executed by the nanoprocessors executing the operations associated with the assigned data flow nodes in a data-driven manner. High computation power is achieved by using multiple nanoprocessors to exploit the large amount of fine-grain parallelism inherent in the target algorithms. Programming flexibility is provided by the MIMD control strategy and the flexible interconnection network which can be reconfigured to handle a wide range of DSP algorithms, including those with heterogeneous communication patterns.

As a proof of concept, a single-chip multiprocessor integrated circuit containing 48 16-bit nanoprocessors was designed and fabricated in a 2-metal 1-µm CMOS tech-

nology. A 2-level, area-efficient communication network occupying only 17% of the core area provides flexible and high-bandwidth inter-processor communications. Running at 50 MHz, the chip achieves 2.4 GOPS peak performance and 800 MBytes per second I/O bandwidth. An integrated development system including an assembler, a VHDL-base system simulator, and a demonstration board has been developed for PADDI-2 program development and demonstration.

The benchmark results based on a variety of DSP algorithms in video processing, digital communication, digital filtering, and speech recognition confirm the performance, efficiency and generality of the architecture. Moreover, when compared with several competitive architectures that target the same application domain, PADDI-2 is in general about 2 to 3 times better in terms of hardware efficiency.

Jan M. Rabaey

Committee Chairman

To my loving family

ving family

## Table of Contents

| 1. | Intro | duction                                            | 1  |

|----|-------|----------------------------------------------------|----|

|    | 1.1   | Perspective                                        | 1  |

|    | 1.2   | Goals and Contributions                            | 3  |

|    | 1.3   | Overview                                           | 6  |

| 2. | High  | Speed Digital Signal Processing                    | 8  |

|    | 2.1   | Viterbi Detector                                   |    |

|    | 2.2   | Hidden Surface Processor for 3-Dimensions Graphics | 12 |

|    | 2.3   | High-Definition Digital Camera Processor           | 14 |

|    | 2.4   | Summary                                            | 17 |

| 3. | Hard  | lware Prototyping Approaches                       | 19 |

|    | 3.1   | Traditional Breadboarding                          |    |

|    | 3.2   | Application-Specific Integrated Circuits           | 21 |

|    | 3.3   | Programmable Multiprocessors                       | 22 |

|    |       | 3.3.1 Architectural Classification                 | 23 |

|    |       | 3.3.2 Programmable (Multi-)Processor Architectures | 27 |

|    | 3.4   | Summary                                            | 45 |

| 4. | PAD   | DI-2: Architectural Design                         | 48 |

|    | 4.1   | Architectural Requirements for Rapid Prototyping   | 48 |

|    | 4.2   | PADDI-2 Control Structure                          |    |

|    |       | 4.2.1 Comparisons                                  | 49 |

|    |       | 4.2.2 Distributed Data-Driven Architecture         | 55 |

|    |       | 4.2.3 Address Generator Example                    | 63 |

|    | 4.3   | Processing Element Architecture                    | 64 |

|    |       | 4.3.1 Homogeneous vs. Heterogeneous                | 64 |

|    |       | 4.3.2 Processing Element Complexity                | 66 |

|    |       | 4.3.3 Instruction Set Architecture                 |    |

|    | 4.4   | Communication Network                              | 71 |

|    | 4.5   | Memory Architecture                                | 77 |

|    | 4.6   | I/O Architecture                                   | 79 |

| 5. | PAD   | DI-2: VLSI Circuit Design                          | 83 |

|    | 5.1   | 48-Nanoprocessor Prototype Chip                                | 83  |

|----|-------|----------------------------------------------------------------|-----|

|    | 5.2   | Nanoprocessor Design                                           |     |

|    | 5.3   | Communication Network                                          |     |

|    | 5.4   | Scan Unit                                                      |     |

| 6. | PAD   | DI-2: Development System                                       | 99  |

|    | 6.1   | PADDI-2 Programming Model                                      |     |

|    | 6.2   | PADDI-2 Assembler Language                                     |     |

|    | 6.3   | PADDI-2 Application Development System                         |     |

|    | 6.4   | PADDI-2 DSP Prototyping Hardware System                        |     |

|    | 6.5   | Multi-PADDI-2 Board                                            |     |

|    | 6.6   | Mapping of DSP Algorithms onto PADDI-2                         | 112 |

|    |       | 6.6.1 Hidden Surface Processor                                 |     |

|    |       | 6.6.2 Viterbi Detector                                         | 114 |

|    | 6.7   | Benchmark Results                                              |     |

|    |       | 6.7.1 Comparisons                                              | 121 |

| 7. | Conc  | lusions                                                        | 124 |

| Aı | ppend | ix                                                             | 127 |

| •  |       | 48-Nanoprocessor PADDI-2 Chip Pin-List                         |     |

|    |       | PADDI-2 Instruction Mnemonics                                  |     |

|    | A.3   | Board Controller Registers                                     | 134 |

|    |       | Layout of PADDI-2 VME Board                                    |     |

|    |       | Nanoprocessor Assembler Programs for Hidden Surface Processors |     |

|    |       | Nanoprocessor Assembler Programs for Viterbi Detector          |     |

| Bi |       | aphy                                                           |     |

•

## List of Figures

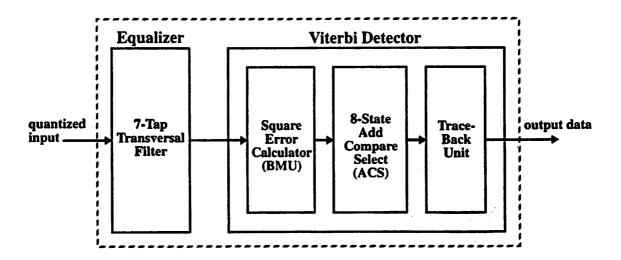

| Figure 2-1:  | Block Diagram of PRML and EPRML Viterbi Detector                           | 9          |

|--------------|----------------------------------------------------------------------------|------------|

| Figure 2-2:  | (a) Equalizer implemented as 7-Tap Transversal Filter.                     | 10         |

| Figure 2-2:  | (b) Block Diagram of Viterbi Detector.                                     | 10         |

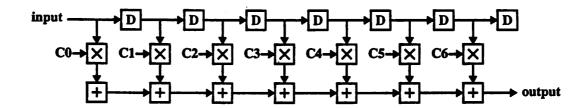

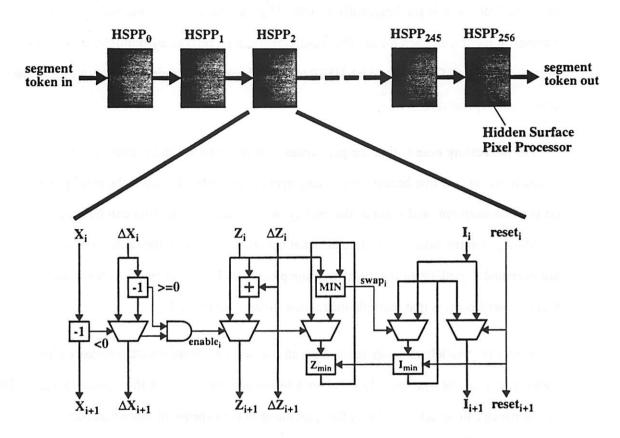

| Figure 2-3:  | 256-Pixel Hidden Surface Pixel Processing System.                          | 13         |

| Figure 2-4:  | HDTV Digital Camera Processor.                                             | 15         |

| Figure 2-5:  | Dynamic Contrast Compression.                                              | 15         |

| Figure 2-6:  | Edge Enhancement System                                                    | 16         |

| Figure 2-7:  | Adaptive Horizontal Contours.                                              | 16         |

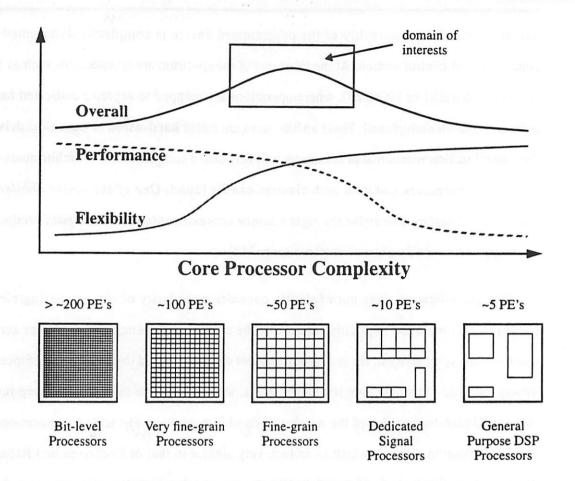

| Figure 3-1:  | Architectural Classification based on Control/Arithmetic Ratio             | 24         |

| Figure 3-2:  | Architectural Classification based on Processor Granularity                | 26         |

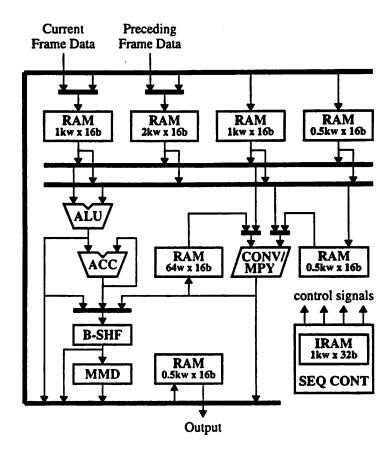

| Figure 3-3:  | Simplified Block Diagram of NEC Video Signal Processor                     | 31         |

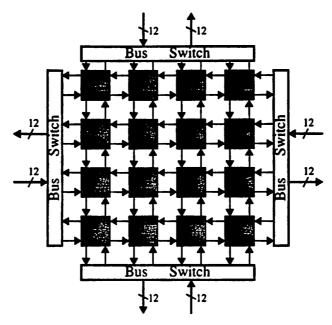

| Figure 3-4:  | Block Diagram of a 16-Processor DataWave Chip.                             | 33         |

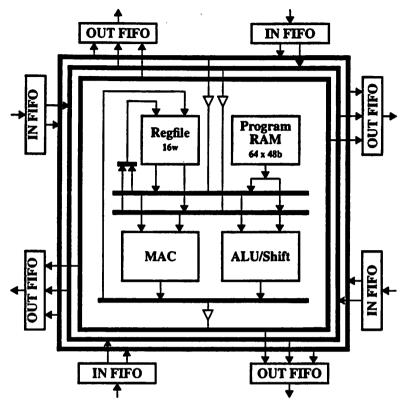

| Figure 3-5:  | Block Diagram of a DataWave Processing Element.                            | 34         |

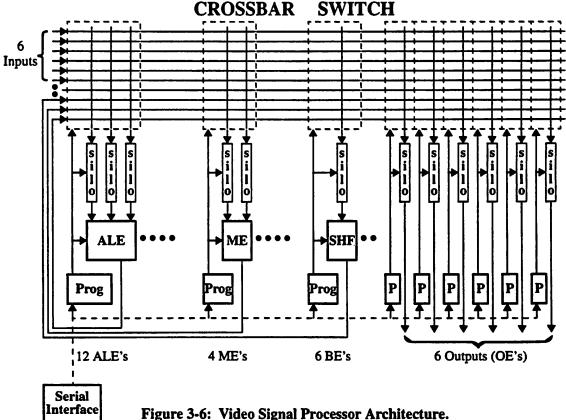

| Figure 3-6:  | Video Signal Processor Architecture.                                       | 36         |

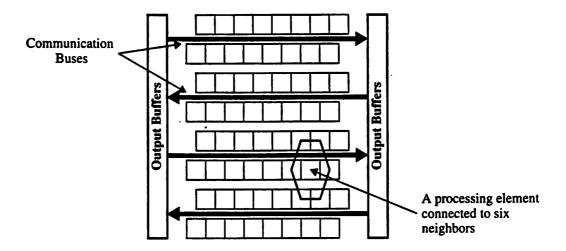

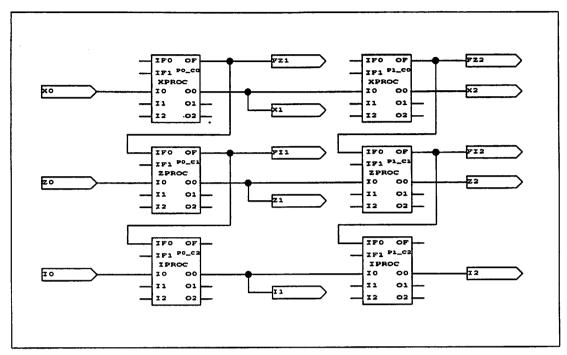

| Figure 3-7:  | Block Diagram of the Data-Driven VLSI Array Processors.                    | 38         |

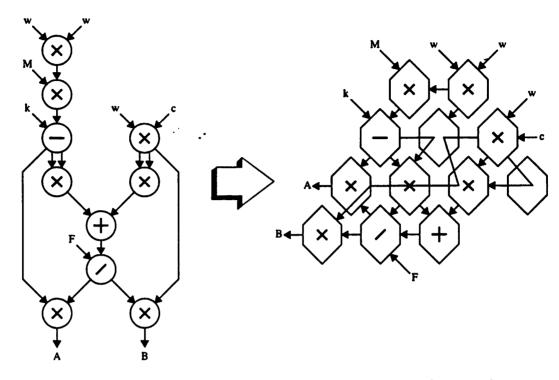

| Figure 3-8:  | Mapping of a Data Flow Graph onto a Hexagonally Connected Array            | 39         |

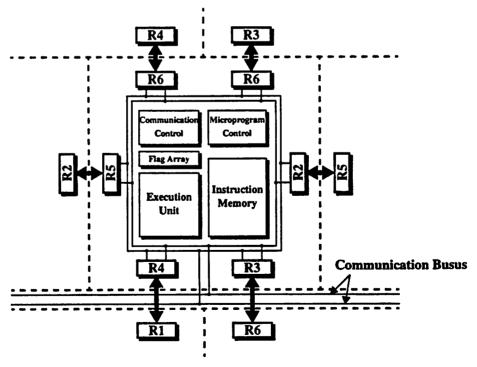

| Figure 3-9:  | Simplified Block Diagram of the Processing Element of the VLSI Array       | 39         |

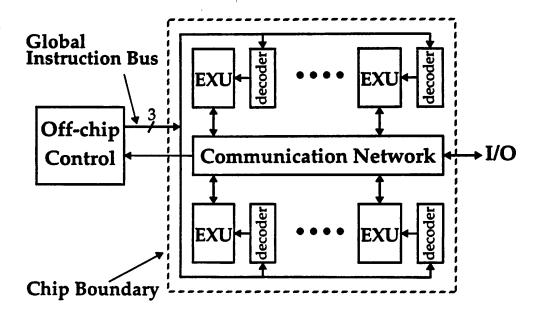

| Figure 3-10: | Block Diagram of PADDI Architecture                                        | 41         |

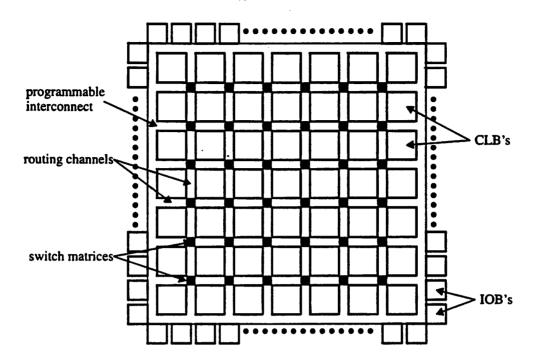

| Figure 3-11: | Basic Structure of XC4000 FPGA                                             | 44         |

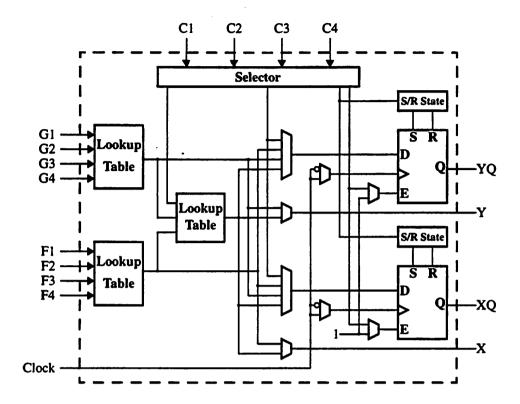

| Figure 3-12: | Simplified Block Diagram of XC4000 Configurable Logic Block                | 45         |

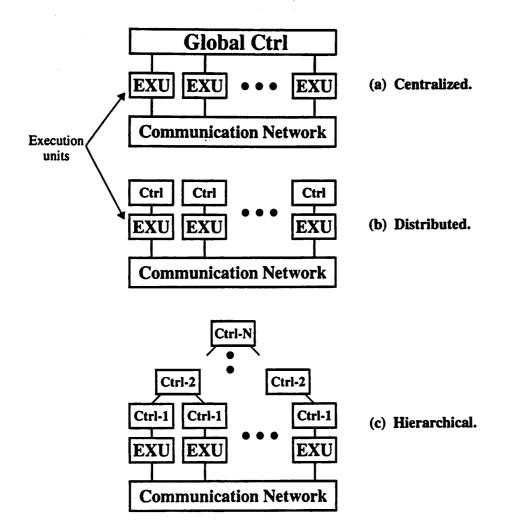

| Figure 4-1:  | Comparison of 3 Control Structures.                                        | 50         |

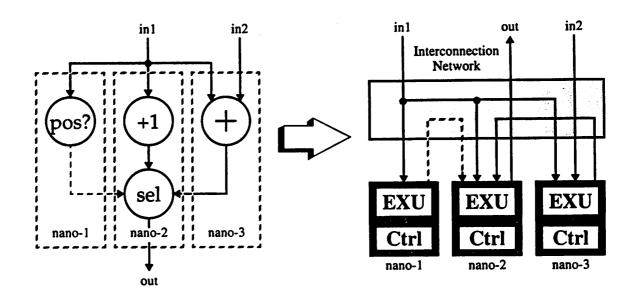

| Figure 4-2:  | Direct Execution of Data Flow Graph using a network of Nanoprocessors      | 55         |

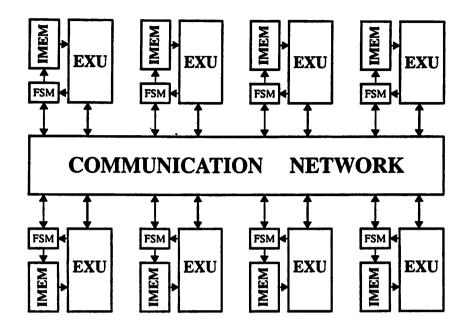

| Figure 4-3:  | MIMD PADDI-2 Architecture Model.                                           | 56         |

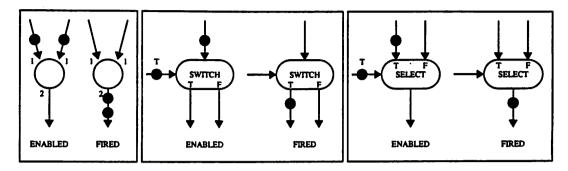

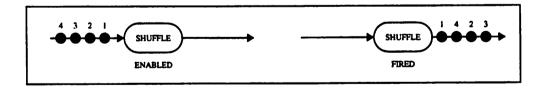

| Figure 4-4:  | Static Data Flow Model.                                                    | 58         |

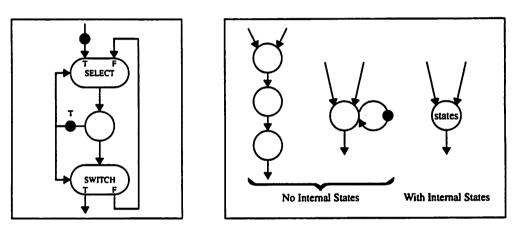

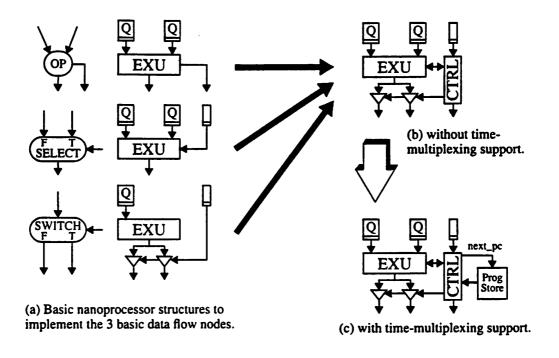

| Figure 4-5:  | Minimal Nanoprocessor                                                      | 61         |

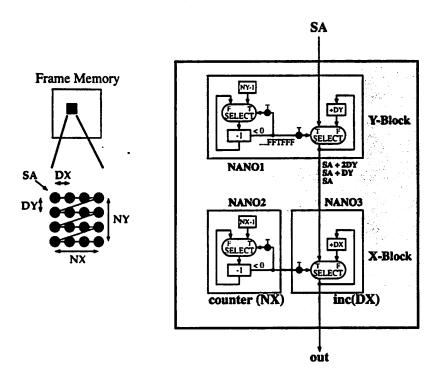

| Figure 4-6:  | 2-dimensional Space Address Generator using 3 Nanoprocessors               | 63         |

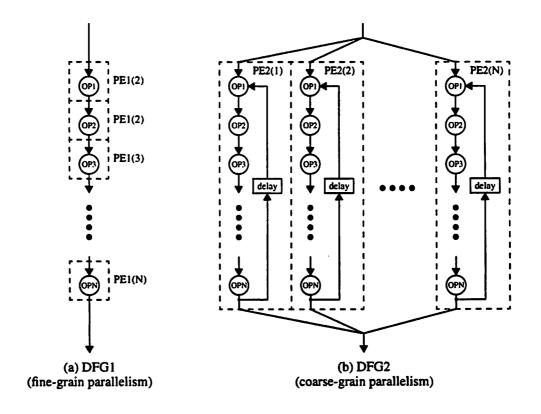

| Figure 4-7:  | Examples of data flow graphs with fine-grain and coarse-grain parallelisms | <b>6</b> 6 |

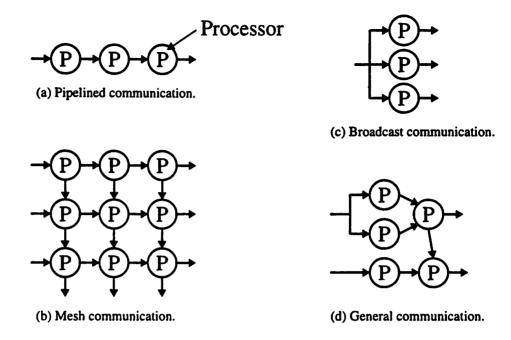

| Figure 4-8:  | Examples of data communication patterns.                                   | 73         |

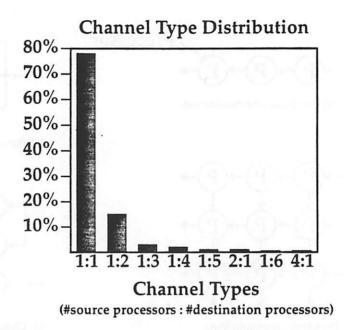

| Figure 4-9:  | Channel type distribution for a set high throughput DSP algorithms [27]    | 74         |

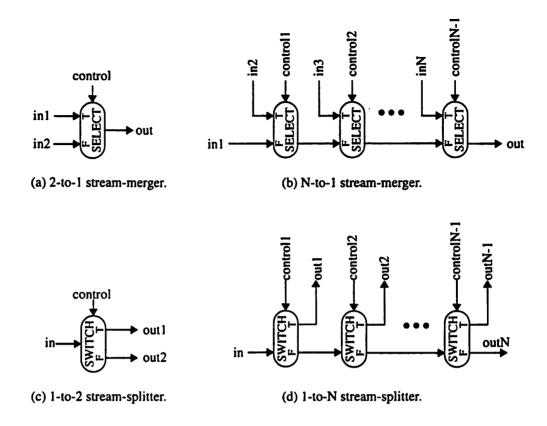

| Figure 4-10: | Examples of Dynamic Interconnection patterns implemented using SELECT ar   | ıd         |

|              | SWITCH operators.                                                          | 75         |

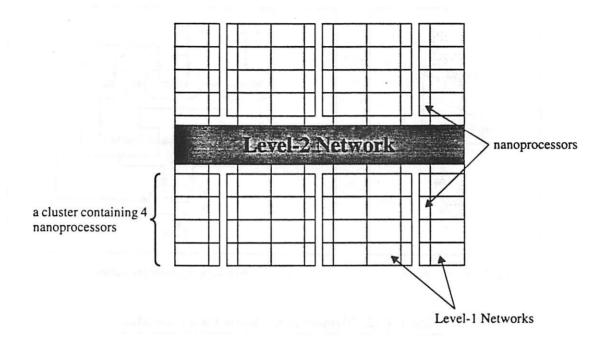

| Figure 4-11: | Basic Structure of the 2-level PADDI-2 Communication Network           | 77  |

|--------------|------------------------------------------------------------------------|-----|

| Figure 4-12: | Memory in the Static Data Flow Model                                   | 78  |

| Figure 4-13: | PADDI-2 Architecture Model with Memory Elements (ME)                   | 79  |

| Figure 4-14: | PADDI-2 I/O Architectures.                                             | 82  |

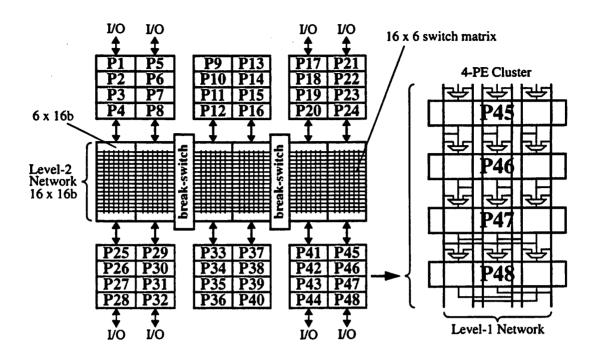

| Figure 5-1:  | Block Diagram of 48-Nanoprocessor PADDI-2 Chip                         | 84  |

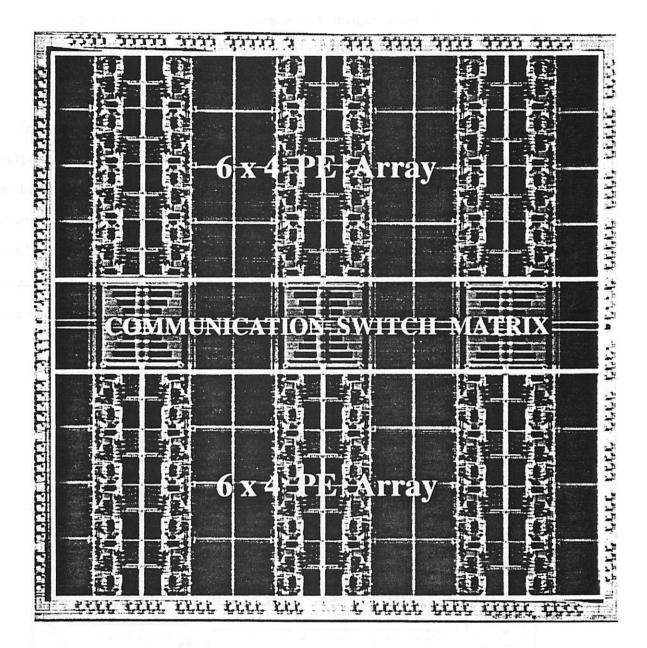

| Figure 5-2:  | Micrograph of 48-Nanoprocessor PADDI-2 Chip                            | 85  |

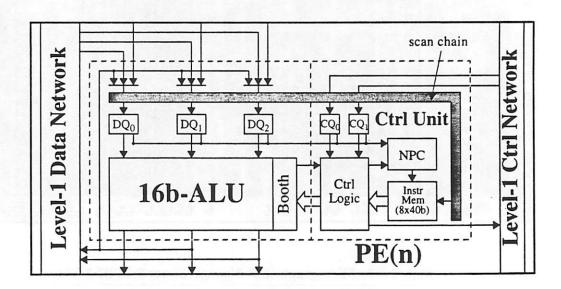

| Figure 5-3:  | Block Diagram of PADDI-2 Nanoprocessor.                                | 86  |

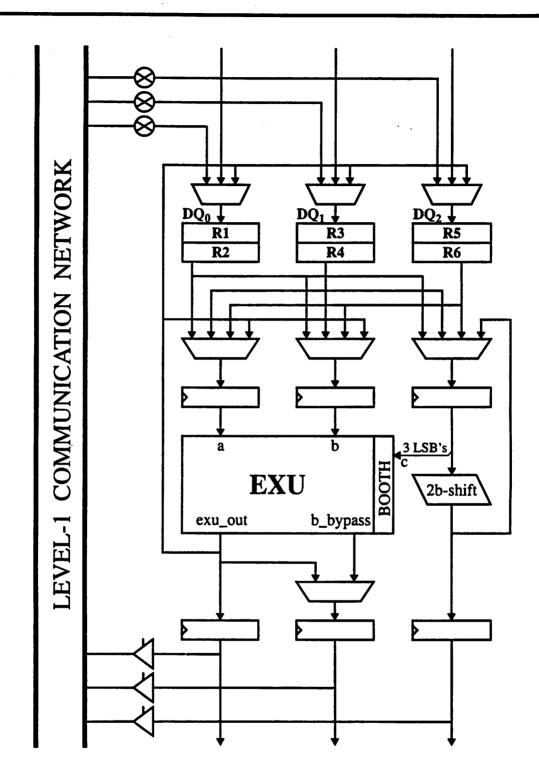

| Figure 5-4:  | Block Diagram of Nanoprocessor Execution Unit.                         | 88  |

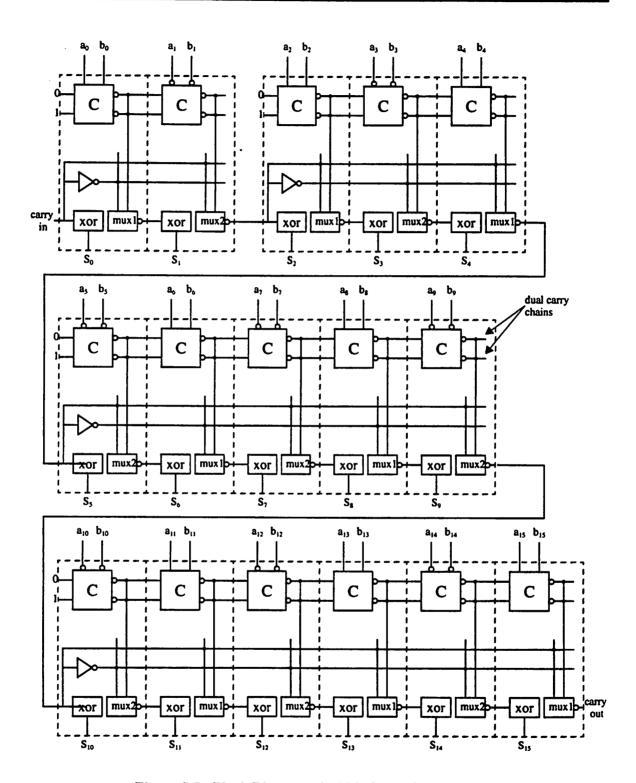

| Figure 5-5:  | Block Diagram of 16-bit Carry-Select Adder                             | 89  |

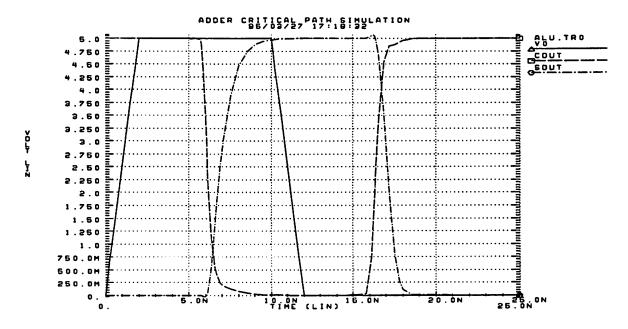

| Figure 5-6:  | SPICE Critical Path Simulation of 16-bit Carry-Select Adder            | 90  |

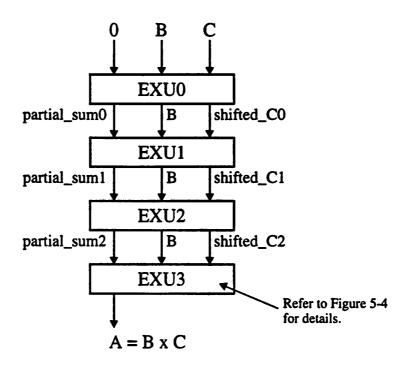

| Figure 5-7:  | An example of pipelined implementation of multiplication               | 91  |

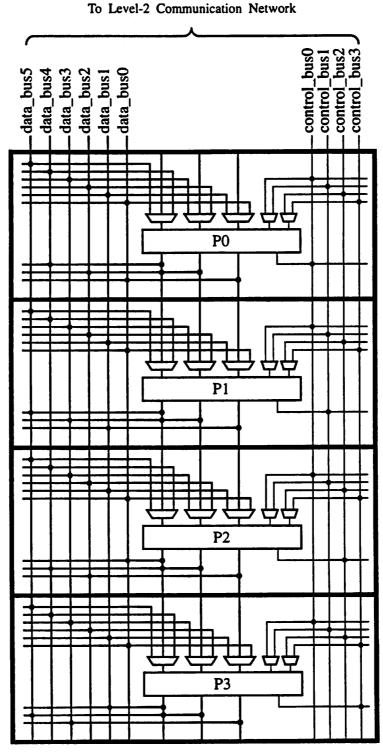

| Figure 5-8:  | Level-1 Communication Network.                                         | 93  |

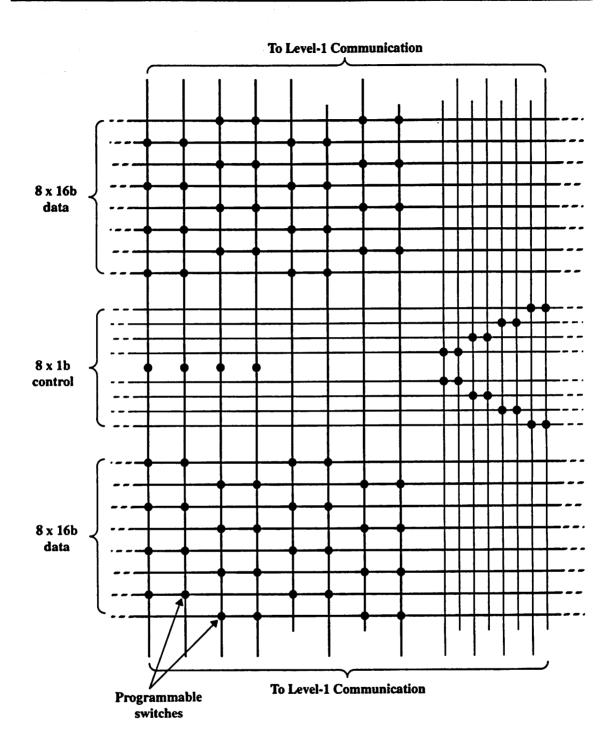

| Figure 5-9:  | Switch Matrix between Level-1 and Level-2 Communication Network        | 94  |

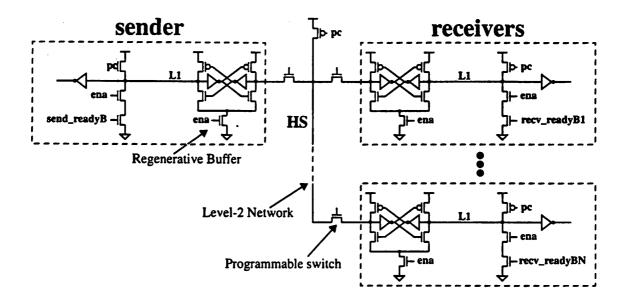

| Figure 5-10: | Dynamic WIRE-AND Handshake Circuit supporting Broadcasting             | 95  |

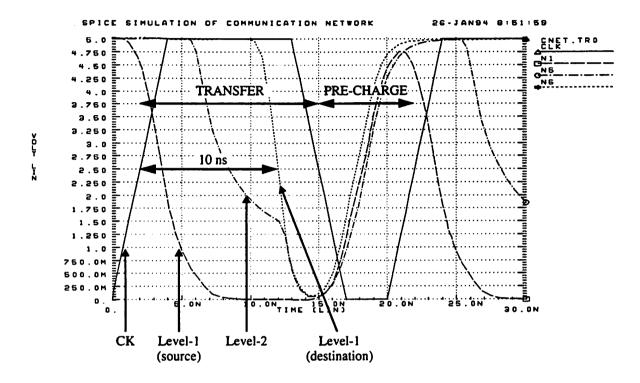

| Figure 5-11: | SPICE simulation of the propagation delay of the PADDI-2 communication |     |

|              | network                                                                | 96  |

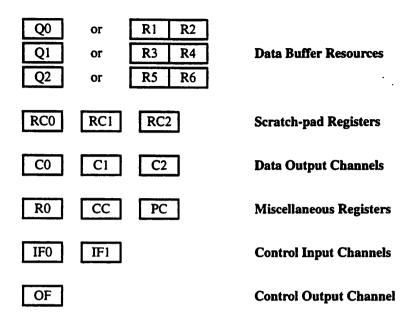

| Figure 6-1:  | Programming Resources of Nanoprocessor.                                | 100 |

| Figure 6-2:  | Program Structure of a PADDI-2 Assembler Program                       | 102 |

| Figure 6-3:  | Sample PADDI-2 Assembler Code implementing a counter                   | 104 |

| Figure 6-4:  | PADDI-2 Software Development System.                                   | 106 |

| Figure 6-5:  | Viewlogic Schematic of the Hidden Surface Processor                    | 107 |

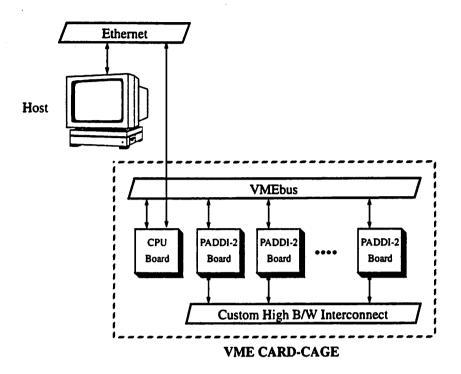

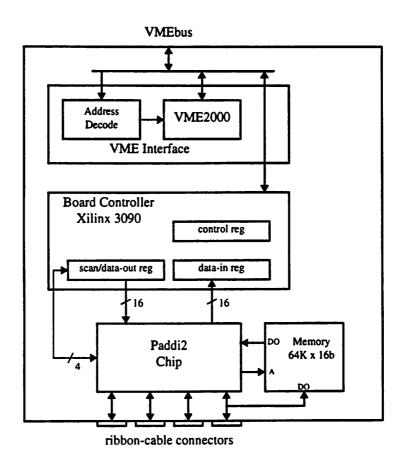

| Figure 6-6:  | PADDI2 DSP Prototyping Hardware System                                 | 108 |

| Figure 6-7:  | PADDI2 VME Board                                                       | 109 |

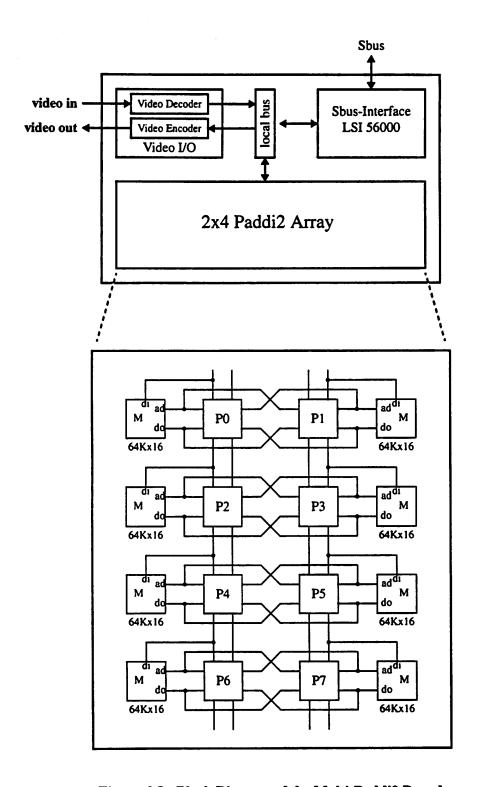

| Figure 6-8:  | Block Diagram of the Multi-Paddi2 Board.                               | 111 |

| Figure 6-9:  | Z-buffer algorithm for Hidden Surface Elimination                      | 113 |

|              | Logical Mapping of Hidden Surface Processor onto PADDI-2               |     |

| Figure 6-11: | Physical Mapping of Hidden Surface Processor onto PADDI-2 Chip         | 115 |

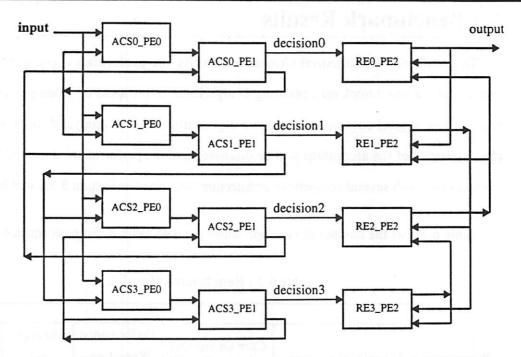

| Figure 6-12: | Block Diagram of 4-state Viterbi Detector.                             | 116 |

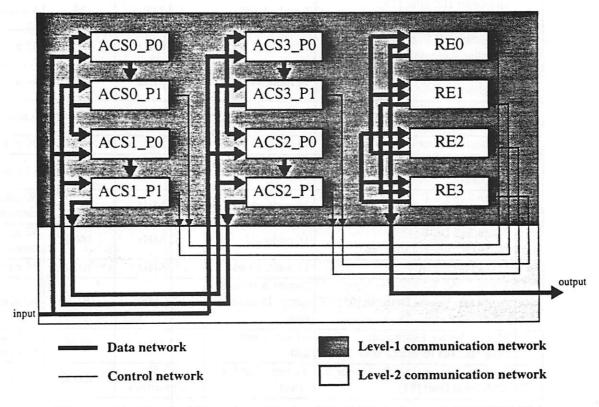

|              | Logical Mapping of 4-state Viterbi Detector onto PADDI-2.              |     |

| -            | Physical Mapping of 4-state Viterbi Detector onto PADDI-2 Chip         |     |

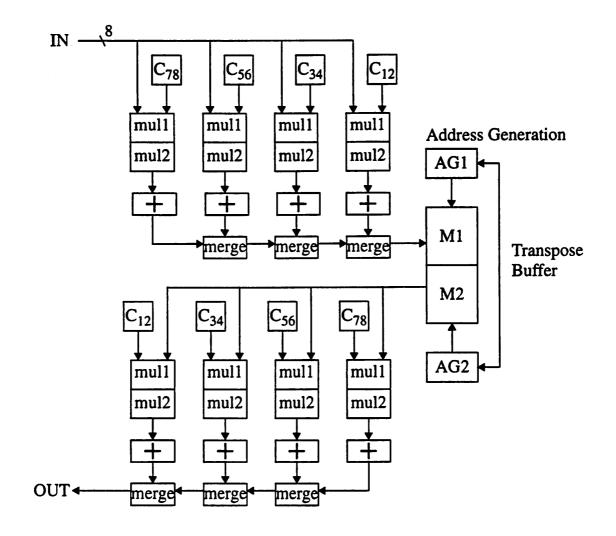

| Figure 6-15: | 2-D 8x8 Discrete Cosine Transform at 25 MHz sampling rate using 50     |     |

| -            | nanoprocessors                                                         | 120 |

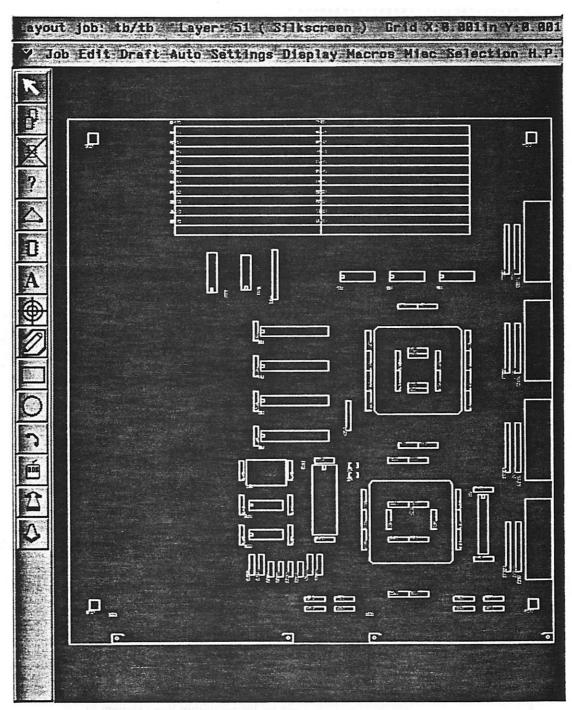

| Figure A-1:  | Layout of PADDI-2 VME Board                                            |     |

## List of Tables

| Table 3-1 :  | Single-chip Programmable (Multi-)Processor Architectures | 28  |

|--------------|----------------------------------------------------------|-----|

| Table 6-1 :  | Listing of Directives.                                   | 103 |

| Table 6-2 :  | Benchmark Results.                                       | 118 |

| Table 6-3 :  | Important IC parameters.                                 | 122 |

| Table 6-4 :  | Comparison of Hardware Requirements                      | 123 |

| Table A.1-1: | PADDI-2 Chip Pin-List.                                   | 127 |

| Table A.2-1: | PADDI-2 Instructions.                                    | 133 |

| Table A.3-1: | Board Controller Registers.                              | 134 |

| Table A.3-2: | Board Control Register.                                  | 134 |

### Acknowledgments

First, I would like to thank my advisor, Professor Jan Rabaey. The PADDI-2 project would not be possible without his vision, leadership, support, and patience. His vision and guidance was instrumental in the definition of this project and in every stage of its development. He is truly a great teacher and an exceptional researcher.

Professors John Wawrzynek, David Aldous, and Bernhard Boser all provided early guidance for my research as members of my Qualifying Exam Committee. Professors Wawrzynek and Aldous went above and beyond the call of duty by also serving on my dissertation committee and reviewing this thesis. Professor Wayrzynek's comments and suggestions have greatly improved the presentation of the benchmark results in this thesis.

I would like to thank a number of my coworkers who have contributed to the PADDI-2 project. Besides being a supportive office-mate, Arthur Abnous did a superb job in developing the assembler and the VHDL model of the PADDI-2 system. Nelson Chow and Stas Frumkin helped tremendously in debugging the PADDI-2 chip and in mapping the first couple of algorithms onto the chip. My sincere thanks to Matt Power who endured the tedious task of designing the test board on Racal. Stephen Okelo-odongo simulated the controller functions on the test board. Dev Chen, who designed the first-generation PADDI architecture, gave me valuable advice on research and life. I would also like to thank the other members of Jan's research group - Ole Bentz, Lisa Guerra, Sean Huang, Paul Landman, My Le, Seungjun Lee, David Lidsky, Renu Mehra, Miodrag Potkonjak, Roy Sutton, Ingrid Verbauwhede, and Engling Yeo - for providing an enjoyable research environment.

I would also like to express my gratitude to Sam Sheng, Kevin Zimmerman, Sue Mellers, and Brian Richards for supporting the computers, laboratory equipments, and CAD tools. On the administrative side, I would like to thank Tom Boot, Peggy Brown, and Corey Schafer.

My thanks also go out to Tom Burd, Andy Burstein, Anantha Chandrakasan, Phu Hoang, Timothy Hu, Gani Jusuf, Timothy Kam, Wook Koh, Monte Mar, Shankar Narayanaswamy, Eric Ng, Mani Srivastava, Lars Thon, Jane Sun, Greg Uehara, Scarlett Wu, and Robert Yu. They made the past couple of years in Cory so much more bearable. I specially would like to thank my coworker Cormac Conroy. Besides solving many of my technical problems, he has also corrected the zillions of grammatical errors in the draft of this thesis.

Lastly, I would like to recognize the members of my family. My sisters Winnie, Mindy and Cheryl have encouraged me every step of the way. To my parents, I owe more to you than I could ever repay. Thank you for your unconditional love and support.

And to my fiancee, Marlisa. Thank you for your love and warmth that keep me going through both good and bad time.

#### **CHAPTER 1**

#### Introduction

Leave the beaten track occasionally, and dive into the woods. You will be certain to find something that you have never seen before.

Alexander Graham Bell

#### 1.1 Perspective

Because of the numerous advantages in processing signals in digital form as opposed to analog form, e.g., accuracy, stability and repeatability, digital signal processing (DSP) has become and will remain a dominant force in signal processing and communications [73]. Impacts can be seen in practically every field, for example, consumer and home electronics, digital communications, medical, manufacturing, and defense. Typical applications are digital audio [5, 68], high definition digital television [53, 87], digital image and video processing [42], computer graphics [79, 81], speech recognition and synthesis [7, 82], mobile communications [44, 70], personal communications systems [15], robotics and electro-mechanical control, machine vision [11], sonar and radar [80], smart weapons, and target discrimination and tracking [65].

After identifying a new market, the designers of modern DSP systems are faced with two key problems: optimizing the performance and cost of the system, and shortening the design cycle. The latter can be equally if not more important than the former. Because of the inertia of customers against adopting new products and the continual shortening of product life cycles, short time-to-market is critical in order to capture market share of any products.

A design process typically goes through many iterations of the design-simulate-evaluate cycle. Traditional simulation methodology is based on software modelling of the system at various levels of abstraction. However, as the customer's demands on higher performance and DSP algorithms become more and more complex, software-based simulation can be the bottleneck in the design process.

Even with rapid advances in computer technology and high-level system modelling, software simulation cannot meet the throughput requirement of complex systems, especially real-time systems. For example, to simulate the high-definition color digital camera [60] on a 10-second video script requires a throughput on the order of GOPS. Furthermore, if the simulation is too slow for real-time playback, Giga-bytes of memories are needed to store the video for later playback. Very often, subjective and perceptual measures, the so-called "golden-eyes and golden-ears", as opposed to deterministic measures, e.g., signal-to-noise ratio and mean-square-error, are used to evaluate the quality of a design. Many hours of video scripts and tapes must be listened to and watched throughout the design cycle. In these cases, a real-time prototype is especially needed to enhance the ability of the designers to fine-tune many design parameters and to explore new design space.

In addition, it is not an easy task to model the behavior of the external world with which the system interacts. For example, to test out a new communication protocol, the channel characteristics under various traffic loads have to be modelled accurately. A hardware prototype operating in real-time can be hooked up to the actual physical channel and can provide the

designers accurate performance metrics under realistic operating conditions. In many cases, hardware prototypes are constructed solely to verify theoretical results with experimental data [95].

Although a real-time hardware prototype is clearly an invaluable tool for shortening the design cycle of complex DSP systems, previous approaches in hardware prototyping are not satisfactory and suffer from one or more of the following shortcomings: high development costs, insufficient computation power, slow turnaround, susceptibility to errors, difficulty in testing and debugging, inflexibility, limited scalability, restrictive programmability, and lack of compiler support. (More of these approaches will be discussed in Chapter 3.) The problem is aggravated when handling complex DSP algorithms with high sampling rates and heterogeneous data-flow patterns. This motivates us to research a high throughput programmable multiprocessor architecture called PADDI-2 that overcomes many of the aforementioned shortcomings and can handle rapid prototyping of these types of algorithms.

#### 1.2 Goals and Contributions

In this chapter, we have presented the needs for rapid prototyping in hardware that form the motivation for this research. The main goal of our research is to study and define an architectural template of a flexible field-programmable integrated circuit component that can be applied to rapid prototyping of a wide range of real-time high speed DSP systems. In addition to architectural level design, another goal is to realize the proposed architecture in silicon to study the important implementation-related issues which can have major impact on architectural choices.

The major contribution of this research is the design and implementation of a novel multiprocessor architecture called PADDI-2 [113, 114]. Characteristics of typical high speed DSP systems were examined to establish the architectural requirements. Multiprocessor architectures were classified based on the granularity of processing elements. The analysis of the classification

results lead to the investigation of multiprocessor architectures using fine-grain processing elements. This class of architectures provides a nice balance between flexibility and high computation power, both of which are essential for rapid prototyping of high throughput DSP algorithms.

The proposed PADDI-2 architecture is a multiple-instruction stream multiple-data stream (MIMD) multiprocessor architecture. It consists of a large number of simple processing elements called nanoprocessors interconnected by a flexible and high-bandwidth communication network. The basic idea is that a data flow graph representing a DSP algorithm is directly mapped onto a network of nanoprocessors. The algorithm is executed by the nanoprocessors executing the operations associated with the assigned data flow nodes in a data-driven manner. High computation power is achieved by using multiple nanoprocessors to exploit the large amount of fine-grain parallelism inherent in many target algorithms. Programming flexibility is provided by the MIMD control strategy and the flexible interconnection network which can be reconfigured to handle a wide range of DSP algorithms, including those with heterogeneous communication patterns.

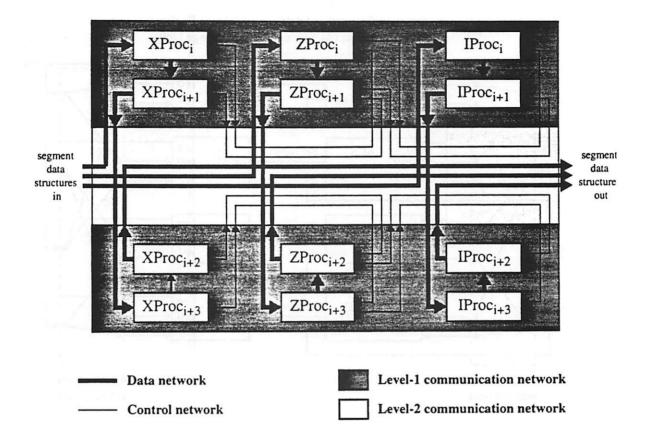

As a proof of concept, a single-chip multiprocessor integrated circuit was designed and fabricated in a 2-metal 1-µm CMOS technology [116]. It consists of 48 nanoprocessors organized in 12 clusters of 4 each. A 2-level, area-efficient communication network occupying only 17% of the core area provides flexible and high-bandwidth inter-processor communications. In addition to the direct interconnections between neighboring nanoprocessors, a total of 7.2 GBytes per second communication bandwidth is available in the Level-1 network for communications within the 12 clusters, and up to 4.8 GBytes per second bandwidth for inter-cluster communications can be supported by the Level-2 network. Hardware mechanisms handle data-driven operations and interprocessor synchronization. Running at 50 MHz, the chip achieves 2.4 GOPS peak performance and 800 MBytes per second I/O bandwidth. The chip was tested functional on second silicon and simple algorithms have been demonstrated. An integrated software environment which includes

an assembler and a VHDL-base system simulator has been developed to facilitate program development and debugging on PADDI-2. An SBus-based board containing eight PADDI-2 chips is being designed for demonstration of more complex DSP systems.

Although the concepts of fine-grain processing elements and MIMD multiprocessing have been around for a long time, we believe the idea of applying both concepts in our application domain is original. Existing architectures typically apply single-instruction stream multiple-data stream (SIMD) style of control for fine-grain processing elements and MIMD for coarser grain processing elements. By targeting only high throughput DSP algorithms with plenty of fine-grain parallelism, we argued that a local program store of small capacity (less than 8 instructions in our prototype chip) is sufficient and therefore the control overhead associated with the MIMD approach can be significantly reduced. In addition, thanks to rapid advances in VLSI process technology, device density has improved so much that area overhead due to MIMD control and elaborate interconnect network can be tolerated to a much larger extent.

PADDI-2 is an experimental architecture developed to prove that it makes sense to use the MIMD approach even for very fine-grain processing elements. The highly scalable MIMD architecture, a clean programming paradigm based on the data flow concept and a flexible interconnection network not only enhance programmability but also improve the computation throughput by making it easier to utilize the large processing power provided by the fine-grain processing elements.

Indeed, benchmark results based on a variety of DSP algorithms in image and video processing, digital communications, digital filtering, and computer graphics verify the performance and generality of the PADDI-2 architecture. Moreover, when compared with several competitive architectures that also target the same application domain, PADDI-2 is in general about 2 to 3 times better in terms of hardware efficiency. The benchmark results will be presented in Section 6.7.

#### 1.3 Overview

The following is a chapter by chapter outline of the remainder of this thesis.

#### Chapter 2 High Speed Digital Signal Processing

Chapter 2 introduces the class of real-time high speed DSP algorithms targeted by this research. Several typical applications in this class, including a Viterbi Detector for Disk-drives, a video engine for hidden surface removal for 3-D computer graphics, and a high definition digital color camera system, are examined. Their requirements on computation power, functional operations, data flow patterns, I/O and memory bandwidth, control functions, granularity, and amount of parallelism are discussed and summarized.

#### **Chapter 3** Rapid Prototyping Platforms

Efficiencies, limitations and trade-offs of existing hardware prototyping approaches are first discussed. It is then argued that approaches based on programmable, multiprocessing hardware offer the most cost-efficient solution to satisfy the performance and flexibility requirements. Programmable multiprocessor IC architectures for high throughput DSP are analyzed and classified according to the granularity of the basic processing elements and the control/arithmetic ratio. Representative architectures are cited and compared. Special attention is given to the architectures that exploit parallelism in DSP algorithms using very fine-grain processing elements.

#### Chapter 4 PADDI2: Architectural Design

The PADDI-2 architecture is presented in Chapter 4. First, the architectural requirements for rapid prototyping of DSP algorithms are summarized. Next, the control structure, processing element architecture, communication network design, memory and I/O architecture of the PADDI-2 architecture are described, and key design choices are explained. Various techniques used to achieve high performance are discussed, and alternative architectures are suggested and discussed.

#### Chapter 5 PADDI-2: Hardware Design

In Chapter 5, the VLSI design of the key components of the PADDI-2 chip, the processing elements, the communication network and the scan unit, are presented. Important circuit simulation results and testing/debugging strategies are also described.

#### Chapter 6 PADDI-2: Development System

The programmer model of PADDI-2 is first reviewed in Chapter 6. We then describe the development system of PADDI-2, which includes an assembler for low-level programming, a VHDL-base system simulator for simulation and debugging support, and a VME board for hardware demonstration and scan-testing. The architecture of a multi-PADDI-2 board currently being designed is also covered. We next present examples of the mapping of practical DSP algorithms onto the PADDI-2 architecture. The chapter is concluded by reporting and analyzing benchmark results of practical DSP applications, and comparing the results with several competitive architectures.

#### Chapter 7 Conclusions and Future Work

Chapter 7 concludes the dissertation. Alternative PADDI-style architectures are discussed and future research directions are mentioned.

#### **CHAPTER 2**

# High Speed Digital Signal Processing

In this chapter, several real-time, high speed DSP applications and their implementations in the fields of communications, computer graphics, and video processing are used to illustrate the application domain targeted by this research. Characteristics of the algorithms such as computation power, functional operations, data flow patterns, I/O and memory bandwidth, control functions, granularity and amount of parallelism are discussed. Typical features of the target algorithms are summarized. These applications will be referred to when architectures are evaluated and compared in the next chapter.

A common measure of the communication bandwidth requirement of an algorithm is the I/O bandwidth of the whole algorithm. A more realistic and also meaningful measure of the communication bandwidth requirement is the worst case I/O bandwidth of the whole system as well as all the sub-systems. For instance, if the algorithm is to implemented by a multiprocessor architecture, this measure defines the requirement on the inter-processor communication bandwidth. However, the latter is heavily dependent on the implementation, specifically, the hardware mapping of the algorithm.

In the following sections, the I/O bandwidth of the entire system, which is independent of the implementation, is used to gauge the communication bandwidth requirement of the algorithms. While the measure is simplistic, in many cases the measure correlates well with the actual bandwidth requirement of the algorithms.

#### 2.1 Viterbi Detector

In recent years there has been a wide interest in high speed implementations of the Viterbi algorithm, which is an optimum algorithm for estimating the state sequence of a finite state process given a set of noisy observations [11, 36]. Driving applications include convolutional decoders for error correction, trellis code demodulation for communication channels, and digital sequence detection for magnetic storage devices in the presence of inter-symbol interference. In this section, an integrated Viterbi detector for (extended) Class 4 Partial Response Maximum Likelihood (EPRML and PRML) channels is described [95].

Figure 2-1 shows the block diagram of the Viterbi detector IC. It includes an equalizer

Figure 2-1: Block Diagram of PRML and EPRML Viterbi Detector.

Figure 2-2: (a) Equalizer implemented as 7-Tap Transversal Filter.

Figure 2-2: (b) Block Diagram of Viterbi Detector.

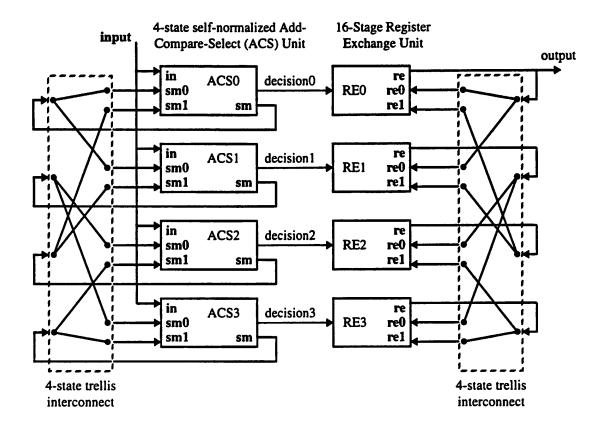

implemented as a 7-tap transversal filter, and a Viterbi detector with an 8-state Add-Compare-Select unit. Implementation examples of the equalizer block and the Viterbi detector block are shown in Figures 2-2 (a) and (b), respectively. The branch metric unit (BMU) calculates the branch metrics, which measure the likelihood of a state transition in the trellis diagram based on the square of the error between the observed input and the expected input. Associated with each

state is a state metric which can be viewed as the accumulated metric along the *most likely* path leading to that state. The state metrics of the two predecessor states of each state are added to the two corresponding branch metrics and then the minimum of the two sums, corresponding to the more likely transition, is chosen to update the state metric for the next iteration. The decision is sent to the trace-back unit.

A Register-exchange network is used for the trace-back unit because of its simplicity. Associated with each state is a register which contains the survivor path leading to that state. In every cycle, one of the two registers of the predecessor states is chosen depending on the decision output from the ACS unit. The content of the register is then shifted by one bit with the decision output as the shift input and stored for the next iteration. The length of the register determines the survivor path length, typically about 5 times of the memory length of the encoder process. The bit shifted out from either one of the states, say state0, is the decoder output.

The reported ASIC, implemented in 0.8-µm CMOS, achieves a channel decode rate of 48 Mb/s running at 48 MHz. Because of the high speed, dedicated multipliers, adders are used for the transversal filter and a parallel ACS architecture is used.

About 4 GOPS of computation power is required. The dominant operations are multiplication, addition, shift, compare and select. While communications between the functional blocks are strictly feed-forward and systolic, very irregular communication patterns are needed inside the Viterbi detector for implementing the connection pattern of an 8-state trellis. I/O bandwidth requirement is acceptable as long as the ACS unit or the Register-exchange unit fit into a single-chip. Since a Register-exchange unit is used to implement the trace-back unit, no large memory is needed. However, if a long survivor path length is desired, it is more economical to use memories to buffer the decision outputs from the ACS unit for trace-back [11]. The control for the algorithm is very simple because of the dedicated nature of the functional blocks.

Despite the complexity of the Viterbi algorithm, high speed implementation is achieved

because of the abundance of both spatial and temporal concurrencies. The equalizer is a feed-forward structure and can therefore be pipelined down to very low granularity. Performance is mostly limited by the single-delay recursion loops present in both ACS unit and the trace-back unit. Algorithmic techniques such as lookahead techniques [9] and block precessing techniques [10] can be applied to the Viterbi algorithm to expose more parallelisms and improve speed.

## 2.2 Hidden Surface Processor for 3-Dimensions Graphics

In 3-dimensional computer graphics, every polygon must be checked to determine whether it is visible or hidden from the viewer. A video processor, which eliminates hidden portions of surfaces using a Z-buffer algorithm on a raster scan-line basis, is described in this section [81].

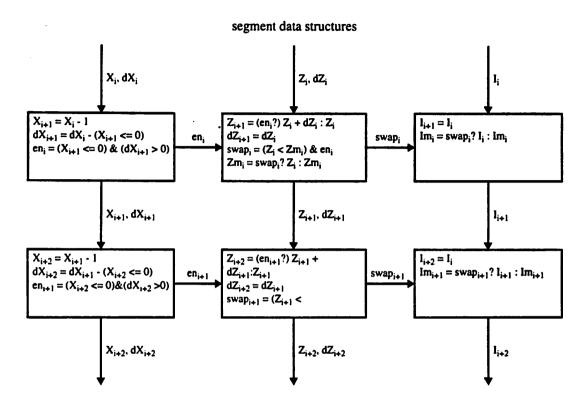

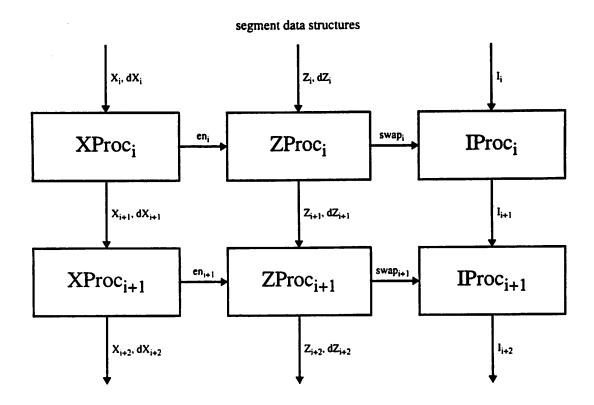

A system block diagram of the hidden surface processing system describing the detailed operations of each pixel processor is shown in Figure 2-3. Each pixel processor handles a single pixel and 256 processors connected in a linear array are needed to process a 256-pixel scan-line. Tokens of line segments are fed into one end of the array and processed systolically. A segment token consists of:

- X starting x-coordinate of the line segment.

- ΔX length of the line segment.

- Z z-coordinate at the starting x-coordinate.

- ΔZ tilt of the line segment.

- I intensity of the line segment.

Xi is decremented as it propagates through the array until it becomes zero. When Xi becomes negative,  $HSPP_i$  is at the beginning of the line segment. The subsequent HSPP's then decrement  $\Delta Xi$  until  $\Delta Xi$  also becomes negative. This indicates that the end of the line segment is reached. The enable flag, enable, is asserted if it is within the line segment, i.e., when  $X_i$  is negative and

Figure 2-3: 256-Pixel Hidden Surface Pixel Processing System.

$\Delta X_i$  is not.

Upon receiving the enable flag, the processor updates the locally stored  $\mathbf{Z}_{min}$  by comparing the incoming  $\mathbf{Z}$  with  $\mathbf{Z}_{min}$ . It also computes the new z-coordinate of the tilted line segment at the next pixel by summing  $\mathbf{Z}$  and  $\Delta \mathbf{Z}$ . If  $\mathbf{Z}_{min}$  has been updated, a swap flag,  $\mathbf{swap_i}$  is asserted and  $\mathbf{I}_{min}$  is simply updated with the incoming  $\mathbf{I}$ . After processing of all the segments in a scan line, a special *reset* token is sent down the array. This triggers the scan-out of the stored  $\mathbf{I}_{min}$ 's and resets  $\mathbf{Z}_{min}$  and  $\mathbf{I}_{min}$  so that processing of the next scan-line can begin.

The implementation reported can process one line segment token every 4 clocks at a 20 MHz rate for a 256-pixel scan line, corresponding to 5 millions line segments per second. On the order of 10 GOPS computation bandwidth is required. Only simple arithmetic and minimum operations

are used. Data flow is predominantly systolic. High I/O bandwidth is needed because of the large number of datums in each token. The requirement can be relaxed by multiplexing several datums onto the same bus. Control for each HSSP is simple because all branch instructions are replaced by conditional operations.

An interesting note is that the performance of the system can be improved by using branch instructions. This is true because first, many operations can be skipped if the pixel processor is not on the line segment, and second, the latency of the branch instruction can be hidden by careful scheduling. On the other hand, if conditional operations are used, the same number of operations are executed regardless of the location of the processor. The major problem associated with using branch instructions is that multiple instruction streams are needed.

Plenty of parallelism exists in the algorithm as all the operations can be easily pipelined. The tightest loop of the system only involves a minimum operation for the update of  $\mathbf{Z}_{min}$ . Higher performance can be achieved by further pipelining in the expense of more hardware.

#### 2.3 High-Definition Digital Camera Processor

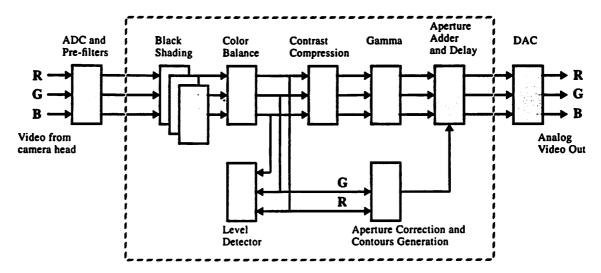

In this section, a fully digital video processor for HDTV cameras [60] is presented. The system block diagram of the video processor is shown in Figure 2-4. It has three 10-bit input and output channels (R, G, B) at 74.25 MHz and uses as much as 16-bit precision for internal calculations for higher accuracy. The processing functions include shading, aperture correction, color balance, gamma correction, and dynamic range compression. Block diagrams of the

Figure 2-4: HDTV Digital Camera Processor.

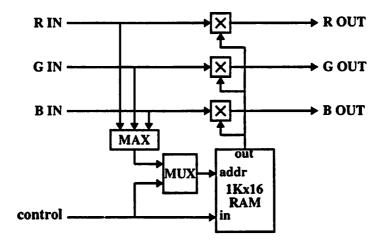

Figure 2-5: Dynamic Contrast Compression.

functional blocks are shown in Figure 2-5, 2-6 and 2-7. All the filter blocks and aperture processing blocks are transversal filters with a small number taps. The filter coefficients are fixed at run-time, but are important design parameters during algorithmic development. This application

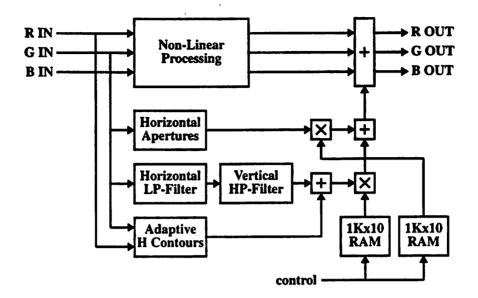

Figure 2-6: Edge Enhancement System.

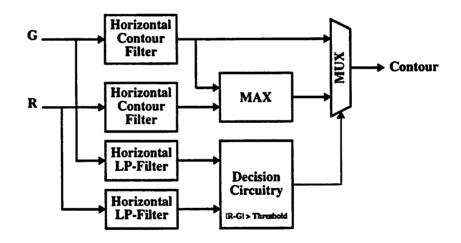

Figure 2-7: Adaptive Horizontal Contours.

is of particular interest because the types of processing performed are typical in many video processing applications.

At the pixel rate of 74.25 MHz, tenth's of GOPS are needed for each color component. Typical

operations include multiplication, addition, maximum and minimum operations, and memory read and write. Only simple branches are needed, some of which can be replaced by conditional operations, e.g., select operations. Data communications are straightforward (almost systolic) between functional blocks, but are heterogeneous inside the functional unit. I/O bandwidth requirement is large because of the high data rate and multiple I/O channels. Shift operations may be used to multiplex the three 10-bit color components onto two 16-bit I/O buses to save I/O bandwidth.

Several small (a few kilobytes) random-access memories, used as lookup tables, e.g., for non-linear processing, are accessed in parallel at the high data rate, resulting in high memory bandwidth requirement. A few large sequential-access memories (up to hundred's of megabytes) are used as video frame delays and line delays. The implementation uses distributed parallel memories to handle the memory bandwidth bottleneck. Again, control is very simple because of the dedicated nature of the functional units. Control is needed mainly to distinguish the normal data processing phase and the idle phase (the vertical blanking period), during which new system parameters and lookup tables may be updated. As in the previous examples, plenty of fine grain parallelism is available in the system and pipelining can be easily applied to boost the performance.

#### 2.4 Summary

In this section, common and pertinent characteristics of the algorithms discussed in the previous sections are summarized and analyzed below. Although only 3 representative algorithms are examined, the summary does give a general picture of the DSP algorithms in the application domain targeted by this research as follows:

- high computation requirement, on the order of 10 to 100 GOPS.

- moderate to high data rate, 10 to 100 MHz.

- high I/O bandwidth, 100 to 500 MByte/sec.

- varied requirements on memory bandwidth and memory capacity.

- both regular and irregular data flow.

- simple control functions.

- plenty of fine grain concurrencies, both temporal and spatial.

In general, the target DSP applications place tremendous demand on both computation and I/O bandwidth requirements. High data rate is needed, especially in video applications. Requirements on memory bandwidth and capacity vary depending on the individual applications. For instance, while the first two applications do not utilize any memory, the HDTV Camera system makes heavy use of memories, requiring up to a gigabyte per second memory bandwidth and hundreds of megabytes of memory capacity. While regular data flow pattern is common, a significant amount of heterogeneous data flow is present in general. Most applications are dominated by computation, requiring only simple looping and branching, and therefore simple control functions are sufficient. Abundance of both temporal and spatial concurrencies in the algorithms can be exploited by pipelining and parallelizing approaches.

#### **CHAPTER 3**

## **Hardware Prototyping Approaches**

In this chapter, efficiencies and limitations of existing hardware prototyping approaches are first discussed, leading to the conclusion that an approach based on programmable, multiprocessing hardware can satisfy the performance and flexibility requirements most cost-efficiently. Programmable multiprocessor IC architectures for high throughput DSP targeted by this research are then classified according to the granularity of the basic processing elements and the control/arithmetic ratio. Representative architectures are cited, analyzed and compared. Special attention is given to the architectural domain where the proposed PADDI-2 architecture belongs.

#### 3.1 Traditional Breadboarding

One of the mostly widely used hardware prototyping techniques is the traditional breadboarding approach in which hardware prototypes are built using off-the-shelf generic IC's. These pre-fabricated IC's range in complexity from TTL/ECL bit-slices and arithmetic units, to dedicated processors such as programmable transversal filter chips and video engines for specific

applications [40, 86, 112], to high performance domain specific processors such as general purpose video signal processors [45, 101, 102]. The main advantage of this approach is that design and testing of custom chips are not required. Good performance can be expected if the parts needed for the specific application are available. Another important advantage is that manufacturers of these generic parts very often accompany the hardware with software development systems for the designers to ease system design.

Despite its popularity, this approach suffers from many shortcomings. Perhaps the greatest drawback of all is the lack of flexibility. The prototype, once built, cannot be easily changed to handle other design alternatives. Although some degree of programmability is usually available for the more complex application-specific processors, e. g., to configure the number of taps of a transversal filter chip, the programmability is usually too limited for the system designers, especially if the type of processing is altered drastically. Another equally important problem is that a complete system is usually built from chips of very different architectures and/or programming paradigms. The heterogeneity makes programming a very tedious task, e.g., custom designed hardware and software interfaces between chips are often needed. To implement systems that require high speed operations, custom designed printed circuit boards are often needed, further increasing the development cost and time.

As an example, the hardware prototype of the high-definition digital camera system described in section 2.3 was designed using this approach. The prototype was constructed using mostly ECL components to achieve real-time HDTV video processing. Despite the fact that the prototype was specially designed to handle the processing functions of HDTV video, it still could not fulfil the needs of the system designers who constantly desired more programmability and flexibility in order to experiment with new sophisticated algorithms [30].

#### 3.2 Application-Specific Integrated Circuits

In order to achieve high performance, or in the absence of pre-fabricated IC's suited for the particular application in hand, some designers use application-specific integrated circuits (ASIC's) for hardware rapid prototyping [81, 82, 95]. The main advantages of this approach are higher performance and reduced chip count due to higher level of customization and integration. For example, several ASIC's were designed to build a connected speech recognition system capable of recognizing words out of a 60,000-word vocabulary [82]. Parts of the ASIC design may also be reused when IC's for the final product are developed.

Unlike the traditional breadboarding approach, the ASIC approach suffers from long turnaround time and high NRE costs mandated by the fabrication and design of custom IC's. Using gate-arrays for ASIC fabrication can shorten the turn-around time somewhat, depending on the process technology used, but some performance is sacrificed in general. ASIC's are more flexible than off-the-shelf components because programmability needed for the specific application can be designed in during chip design. However, the design still cannot be changed once the chip is fabricated and modifications are both costly and time-consuming. Sometimes the algorithm may change so drastically during system development that the ASIC can be rendered useless. In addition to the usual risk inherent in the design of a new custom chip, the overhead in chip testing and debugging always adds to the development time. Due to the custom IC design, special board-level design tailored to a particular application is often required.

Because ASIC design offers good performance and potential for system integration, there are widespread research activities aimed at improving the design time of ASIC's. Besides the conventional computer aided design tools for IC design, a very promising approach is to synthesize an ASIC from high-level design specifications [29, 31, 77, 83]. Not only is the design time reduced drastically, chip testing and trouble-shooting are also simplified because the circuits generated by the synthesis tool are correct by construction. For example, the synthesis tool called

HYPER [77] accepts specifications of DSP algorithms in high-level languages such as SILAGE [49] and VHDL [64], performs estimation, transformations, partitioning, assignment and scheduling, and generates silicon layout as the final product. Many researchers are also interested in extending the synthesis approach to the system level to achieve rapid prototyping of a complete system [96].

#### 3.3 Programmable Multiprocessors

Perhaps the biggest drawbacks of the hardware prototyping approaches using generic IC's or ASIC's are the long development time and large NRE costs due to the needs of custom printed circuit boards and/or overhead associated with ASIC fabrication. To overcome these problems, many system designers have turned to programmable hardware as their prototyping platforms [8, 56, 78, 85, 107]. As an example, the computation intensive speech recognition systems described in [8, 85] achieve real-time capability by using parallel commercial processors such as the 8 MFLOP AT&T DSP32C floating point digital signal processor and the 10 MIPS Weitek XL-8032 processors. Using existing hardware, this approach minimizes NRE costs and avoids tedious testing and debugging of hardware. Moreover, development time is reduced to the time needed for programming the hardware. By migrating the tasks of prototype development from hardware to software, flexibility, high reusability, modularity and ease of debugging are ensured. It is clear that compared to the breadboarding approach and the ASIC approach, programmable hardware satisfies the stringent performance requirement and offers the needed flexibility most cost-efficiently.

Even with rapid advances in processing technologies, a single chip is not able to deliver the GOPS's of computation throughput typically required by our target DSP algorithms, and therefore, almost without exceptions, multiprocessing based systems are needed. The use of programmable multiprocessor systems for rapid prototyping of DSP systems presents many challenges, due to the facts that the high computation requirement of the target DSP algorithms demands a large number

of processors, and that the high data rate puts tremendous pressure on inter-processor communication bandwidth. Memory bandwidth can also be the bottleneck in some applications.

How are large number of processing elements controlled and synchronized, SIMD or MIMD, centralized or distributed? What communication mechanisms and network topologies are appropriate for different classes of algorithms? What programming models should be used to ease programming and compilation? These issues, and many more, are the subjects of active researches [50]. Some of these issues will be revisited in Chapter 7, where the architecture of a system based on the PADDI-2 single-chip multiprocessor is described.

In this research, the focus is on the architectural design of the basic single-chip processing component, on top of which the complete multiprocessing system can be built cost effectively. Although it is obvious that chip-level architectural design is heavily influenced by the overall system architecture, there is still plenty of room for architectural innovations, since current IC process technologies enable integration of millions of transistors onto a small die, and further advancements can be expected.

We restrict our application scope to fixed-point DSP. Although floating-point DSP is much superior to fix-point in terms of dynamic range, fixed-point DSP is widely used because fixed-point hardware is both cheaper and faster than its floating-point counterpart. A good review of fixed-point DSP vs. floating-point DSP can be found in [62]. In the following sections, architectures of single-chip integer multiprocessors will be classified, analyzed and compared.

#### 3.3.1 Architectural Classification

"A good classification scheme should reveal why a particular architecture is likely to provide a performance improvement."

David Skillicorn, A Taxonomy for Computer Architectures

# Control Flow Microprocessors Driven General Purpose Signal Processors Dedicated Signal Processors Dedicated Multiprocessors Data Path Clusters Bit-Serial Data Flow Driven

Figure 3-1: Architectural Classification based on Control/Arithmetic Ratio.

Besides understanding past accomplishments, classifying architectures helps reveal missing gaps in the architectural spectrum that might not otherwise have occurred to a system designer. Moreover, a good classification scheme should give strong hints why or why not a particular architecture is likely to provide performance improvement over its counterparts [91].

Many taxonomies for computer systems have been proposed: from the classical Flynn's taxonomy based on parallelism within the instruction stream and data stream [35], to the elaborate extension by Skillicorn [91], to the taxonomy restricted to IC architectures suggested by Keutzer [55]. A comprehensive review of taxonomy for DSP architectures can be found in Chen's thesis [27]. We found that the classification scheme for DSP architectures described in [14] by Brodersen and Rabaey is simple and yet very powerful and relevant to the classification of single-chip processor architectures.

In their classification scheme, DSP architectures are classified based on the amount of operation sharing on an arithmetic unit, as shown in Figure 3-1. One end of the spectrum represents the traditional microprocessor architecture, where all arithmetic operations are time-multiplexed on a single general purpose ALU. This architecture is classified as **control flow**

driven, since the functionality of the programmed device is completely determined by the contents of the control section. At the other end of the spectrum are architectures such as systolic arrays (bit-parallel or bit-serial), where operations are mapped to separate dedicated hardware units and seldom multiplexed. These architectures are called hard-wired or data-flow driven and the control section is minimal or nonexistent. In between, a complete suite of architectures such as dedicated processors and data path clusters can be found. One of the major challenges in architectural design is to strike the right balance between control and data path sections for a given application and a given throughput range [14].

This classification does not explicitly consider granularity of the processing elements. However, it is included implicitly because as the control/arithmetic ratio decreases across the spectrum, the complexity of the processing element can be expected to decrease also. Since we are mostly interested in single-chip implementations, we can carry the inference one step further to classify IC architectures based the number of on-chip processing elements (or execution units). This classification scheme, which is, in fact, very similar to that of Brodersen and Rabaey's, is illustrated qualitatively in Figure 3-2. Clearly, the absolute number of processing elements depends strongly on the implementation, e.g., the process technology used and the design style. However, the general trend is still valid as one goes from one architectural domain to another across the spectrum.

In Figure 3-2, the rough trade-offs between performance and flexibility are shown. As the number of processing elements increases, the performance can be expected to improve accordingly. It is true that techniques such as pipelining can boost performance without increasing the number of processing elements<sup>1</sup>. However, the same techniques can conceivably be applied to all the architectures across the spectrum, resulting in similar performance improvement and therefore the general performance trend still holds. Another way to comprehend the trend is to

<sup>1.</sup> A detailed discussion of pipelines in single-chip DSP processors can be found in [33].

Figure 3-2: Architectural Classification based on Processor Granularity.

consider the complexity of the control section of the processing element. As the spectrum is transversed in the direction of decreasing processor complexity, the control section of the precessing elements become smaller and smaller. Eventually the control section can be eliminated entirely when the system is completely hard-wired. Simplification of the control section results in the availability of more silicon area for execution units and faster clock speed, and hence increased performance.

Unfortunately, the trend in flexibility is the reverse of the performance trend. While a control driven architecture such a microprocessor can be easily programmed for various tasks with the help of high-level language compiler, the programming of the data flow driven architectures such as a systolic processor array is much more involved. Not only do programs for a larger number of

processing elements need to be written, inter-processor communications and synchronization have to be carefully handled before the processing elements can work in harmony to produce the correct results. Sometimes the communication network between the processors can limit the application scope of the architecture, e.g., systolic processor arrays, which only support communication between neighboring processors, can only be applied to a certain class of algorithms [58, 100]. The problems are further aggravated if heterogeneous processing elements are used. The degree of inflexibility worsens as the relative size of the control section to the data path section decreases, i.e., as the processor complexity is reduced.

The problem of rapid prototyping poses the interesting challenge of designing architectures that can achieve the high performance of the data flow driven architectures and yet exhibit the flexibility of the control driven architectures. As illustrated in the classification scheme in Figure 3-2, we conjecture that the overall optimum may lie in the middle of the architectural spectrum where fine-grain processor elements are used. In the following section, representative architectures in each region of the spectrum are analyzed to support our conjecture.

# 3.3.2 Programmable (Multi-)Processor Architectures

In this section, single-chip processor or multiprocessor architectures with various processor complexity are studied. As the number of processing elements increases, the impact of the communication network on the efficiency of the architecture becomes more and more significant, and therefore architectures are further differentiated by the flexibility of their communication networks. Representative architectures in each architectural domain, as tabulated in Table 3-1, are chosen for detailed discussions. Using the algorithms described in Chapter 2 as the target applications, these architectures are analyzed and evaluated, with special attention given to architectures using fine-grain processing elements. This is by no means an elaborate list, however, many of the arguments can be extended to similar architectures within the same domain. These

| Processor Complexity    | Coarse                    | Medium     | Fine              | Very-fine                              | Ultra-fine    |

|-------------------------|---------------------------|------------|-------------------|----------------------------------------|---------------|

|                         | (~5 PE's)                 | (~10 PE's) | (~50 PE's)        | (~100 PE's)                            | (> ~200 PE's) |

| Local<br>Communications | -                         | _          | DataWave [88, 89] | Data-driven<br>Processor Array<br>[57] | -             |

| Flexible                | Commercial DSP Processors | NEC VSP    | VSP               | PADDI                                  | FPGA          |

| Communications          |                           | [45]       | [92, 102]         | [26, 27]                               | [39]          |

Table 3-1: Single-chip Programmable (Multi-)Processor Architectures.

case studies provide important lessons and hints on how to design a good architecture for rapid prototyping.

#### **Commercial DSP Processors**

Since their introduction more than a decade ago, single-chip commercial DSP processors have remained the most dominant force in DSP. This is not at all surprising considering their good programmability, low cost and rapid and consistent improvement in performance over the years. Moreover, the conventional wisdom in the general-purpose processor business that VLSI advances are going to roll over everything is a very strong driving force. DSP processors, equipped with special architectural features to facilitate the tasks of signal processing, usually have higher performance than a general-purpose microprocessor in the DSP application domain. However, the distinction between DSP processors and general-purpose microprocessors has blurred in recent years, thanks to advances in both processing technology and architectures in the general-purpose microprocessor arena. For example, the recently announced UltraSPARC is able to support real-time video compression (H.261) and decompression (MPEG-2), an application domain formerly monopolized by DSP processors [93].

Perhaps the most celebrated feature of a DSP processor is the Multiply-Accumulate (MAC) instruction, which is used heavily in DSP algorithms. Some people gauge the performance of a

DSP processor simply by its MAC time. Due to the high memory bandwidth requirement, DSP processors usually adopt the classic Harvard architecture and use parallel on-chip and/or off-chip memory banks. Instruction execution is typically pipelined to boost clock speed and provisions are made to enhance the efficiency of loop execution, for example, the REPEAT instruction provided by some processors of the TMS320 family. Other important architectural features include rich addressing modes, e.g., bit-reverse addressing for fast-fourier transform and modulo-mode addressing for circular buffering, multiple dedicated address generation units, hardware I/O support such as timers, DMA controllers, etc..

The performance of a processor can be given by the average number of instructions executed per clock (IPC<sup>2</sup>) multiplied by the clock frequency. Given that modern processors usually adopt simple instructions and pipelined execution to increase clock frequency, the throughput is limited by the small IPC. There are two reasons for the small IPC: first, there may not be enough instruction level parallelism in the algorithm so that data dependencies and branch latency cause stalls in the execution pipelines, and second, IPC is limited by the moderate number of execution units in the processor. The latter is due to the fact that a general-purpose processor is primarily designed for time-multiplexing operations on a few execution units. Valuable silicon area, which could have been used for execution units to increase performance, is wasted on such extraneousness as complex control logic and large instruction cache. As an example, if a processor is dedicated to repeating the few instructions in a simple inner loop of an algorithm so as to satisfy the computation requirement, an instruction cache is not needed.

The Viterbi detector described in Chapter 2 is a good example to demonstrate the inefficiency of a DSP processor in exploiting fine-grain parallelism. About 80 instructions are executed to produce one decoded bit. Even if we make the very aggressive assumptions that there are enough

<sup>2.</sup> To evaluate performance of processors with different instruction sets, one must also consider the average amount of work performed by an instruction, i.e., complex instruction set vs. reduced instruction set.

instruction level parallelism in the code, i.e., there are no stalls due to data dependencies or branch latency, and that the processor can execute 4 instructions per cycle at the clock frequency of 100 MHz, it will still take 20 cycles to process one sample, resulting in a decode rate of a mere 5 Mb/s.

To achieve higher performance, designers must resort to multiprocessing. Some modern DSP processors have special architectural features to aid multiprocessing. For example, the TMS320-C40 from Texas Instruments Inc., are equipped with 6 high-speed serial links such that many common network topologies, e.g., hexagonal array, can be easily realized. However, the major bottleneck for developing systems using parallel DSP processors is often the lack of system-level software support. One exception is the transputer developed by Inmos, Inc. [51]. The entire transputer system architecture, from processor architecture, to instruction set, to programming language, is specially designed for multiprocessing. Using a concurrent language called Occam, which is based on the concept of communicating sequential processes, designers can easily program a set of processes to run on different transputers and to communicate with each other via channels, supported in both hardware and software.

# **NEC VSP: a Dedicated Signal Processor**

Next in the spectrum is a class of dedicated DSP processors. Strictly speaking, these dedicated processors are not general-purpose processors because they are generally designed specially for a certain application domain, e.g., video processing. However, these processors are so flexible in terms of programmability that they can be applied to a wide range of algorithms within the application domain. Hence they are also known as application-specific processors. By focusing on an specific application domain, architectural features such as data path, memory organization and word width can be optimized more than a general-purpose processor. Consequently, a dedicated processor typically contains a higher number of processing elements or execution units, thus providing higher performance than a comparable general-purpose DSP processor.

A good example of a dedicated DSP processor is the super-high-speed video signal processor

Figure 3-3: Simplified Block Diagram of NEC Video Signal Processor.

(VSP) from NEC Corporation [45], which contains many architectural features typical of dedicated processors such as a large number of execution units, optimized data paths, parallel memories, and microprogram based control. As shown in the block diagram in Figure 3-3, the NEC VSP contains two main execution units: a convolver/multiplier and a data path consisting of dual ALU's, a barrel shifter and a minimum/maximum value detector optimized for video signal processing such as inter-frame difference and motion compensation. Seven on-chip data RAM's, most of which are dual-ported, are used to sustain high data bandwidth to and from the speedy execution units. A total of twelve address generators, one for each port of the RAM's, run independently in co-processor mode to reduce instruction bandwidth from the central microprogram based sequencer.

Using a 0.8-µm triple-metal BiCMOS process, the chip runs at a 250 MHz internal clock frequency, and achieves 500 MOPS for convolution and 250 MOPS for multiplication and other arithmetic operations. For example, an 8x8 2-dimensional DCT can be performed using a single chip in 16.8 µs, equivalent to a pixel rate of 3.8 MHz.

Although the performance of dedicated signal processors is generally superior to that of general-purpose DSP processors, it is still not enough to satisfy the throughput requirement of our target algorithms. Due to the typical use of concurrently operating hardware units, programming is not easy because thorough understanding of the architecture is needed in order to orchestrate the units to work together correctly and efficiently. Moreover, because of the restrictive application scope, the manufacturers are likely to allocate less resources to compiler development, making programming even more difficult. The programming issue is further aggravated if multiprocessing is applied to improve performance. Another problem with using dedicated signal processors for rapid prototyping is that since it is optimized for a specific application domain, the processor may not be efficient for general DSP algorithms. For example, it is not clear how well the NEC VSP can handle the many branch instructions needed in the Viterbi detector and hidden surface processor described in Chapter 2.

## DataWave: a Data-driven Array Processor

The DataWave [88, 89] belongs to a class of multiprocessor architectures called Wavefront Array Processors proposed by S.Y. Kung [58]. The wavefront array is an extension of the systolic array originally proposed by H. T. Kung [37]. Both systolic array processor and wavefront array processor achieve high performance through parallelism and pipelining using regularly, locally interconnected processing elements. However, the application is limited to a certain class of algorithms, such as regularly iterative algorithms [84] or the more general piecewise regular algorithms [100]. Examples are common in the areas of signal and image processing such as vector and matrix operations, sorting, and pattern recognition.

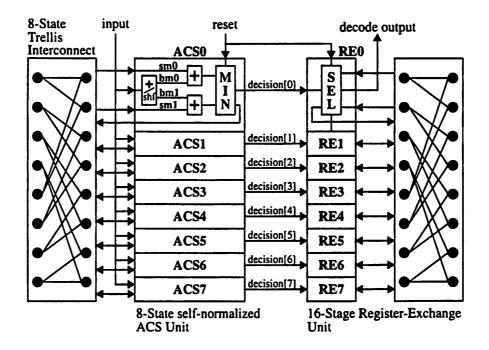

Figure 3-4: Block Diagram of a 16-Processor DataWave Chip.

The key difference between the two is that while all the operations in a systolic array are synchronized by a global clock, the wavefront array is asynchronous in that only the correct sequencing, not timing, is required. Hence, higher performance can potentially be achieved by the wavefront array by taking advantage of the differences in speed of the operations in the array. A serious problem with these array architectures, which is often overlooked by the designer, is that specially designed I/O units are often needed to provide enough data bandwidth to sustain the high performance [105].

As shown in the block diagram in Figure 3-4, a DataWave chip consists of 16 mesh-connected processing elements. Each processor independently executes a program stored locally, propagating data through the array in a wavefront-like manner. Instruction execution is data-driven, i.e., it is halted if any operands required are not available or if any inter-processor communications are blocked. Processing elements on the edge of the chip can communicate with another DataWave chip via the bus switch by time-multiplexing.

Figure 3-5: Block Diagram of a DataWave Processing Element.

Each processing element consists of a 4-port 16-word register file, an ALU, a multiply-accumulate unit, a 64x48b program store, and eight 8-deep FIFO's interconnected by three ring buses (Figure 3-4). Data path width is 16 bits with the exception of the accumulator which is 29-bit wide. A 5-stage pipeline is used to achieve a fast internal clock rate of 125 MHz in a 0.8-\mum 2-metal CMOS process technology. An ALU operation and a MAC operation can be launched every cycle, resulting in a total peak performance of 4 GOPS. Due to the deep pipeline, branch latency is 3 cycles. The input FIFO and output FIFO on each side of the cell smooth out data transmission between cells and implement an asynchronous interface to eliminate a global clock and the associated clock skew problems. A complete software environment including a compiler for static data flow programs and a graphical simulator was developed for the architecture to ease programming.

This architecture is of particular interest to us because the architecture, though developed independently, shared many commonalities with our proposed architecture, e.g., the use of homogeneous fine-grain processing elements for high throughput, data-driven execution and static data flow programming paradigm. Another interesting feature of this architecture is the use of asynchronous interprocessor communications to achieve scalability both physically and architecturally.

Although the DataWave has the appearance of a Wavefront Array Processor and can certainly function like one, it is intended for a wider range of video applications, not limited to the traditional application scope of a Wavefront Array Processor. For instance, non-local communications can be realized by routing data through the PE's, which can perform arithmetic operations and at the same time move data from an input FIFO to an output FIFO. Nonetheless, when tackling algorithms with irregular data flow, many PE's, which are fairly complex, are likely to be under utilized. Moreover, the long latency due to data propagation through processing elements may not be acceptable especially for applications with tight recursive loops<sup>3</sup>.

For example, while the mesh array topology can perform reasonably well for the hidden surface processor in section 2.2, it is not clear how well it can handle the many branch instructions and heterogeneous communications required in the Viterbi detector described in Section 2.1. Furthermore long latency is bound to hurt performance because of the single-delay recursive loop in the Add-Compare-Select unit. Finally, the DataWave architecture implements a computation array without any memory elements except for the small local register file. It will be interesting to see how memories are integrated into the system for memory intensive DSP applications.

<sup>3.</sup> Sometimes algorithmic transformation techniques such as the block processing technique can be applied to relief the recursive bottleneck [75].

## **Philips Video Signal Processor**

The Video Signal Processor (VSP), developed by Philips Research Laboratories, is a generalpurpose, programmable processor specially designed for efficient processing of real-time video signals using parallel, fine-grain processing elements [92, 102]. As shown in the block diagram in Figure 3-6, a VSP contains a total of 28 parallel processing elements: twelve Arithmetic Logic Elements (ALE's), four Memory Elements (ME's), six Buffer Elements (BE's) and six Output Elements (OE's), all of which are interconnected by a 28 by 60 by 12-bit crossbar switch matrix. Each processing element is connected to the switch matrix by one or more programmable-delay registers called silos. Implemented as 32 by 12-bit dual-port memories, the silos can realize sample delays, equalize pipeline delays, and are essential for achieving efficient cyclo-static program schedules.

Using the cyclo-static scheduling algorithm, the execution of instructions in the parallel processing elements can be scheduled to satisfy certain criteria such as optimal processor utilization. Overhead of multiprocessing such as synchronization is minimized because each processing element simply cyclically executes the instructions stored in its local 32-word program memory according to the schedule. Hence the VSP is conceptually a Very-Long-Instruction-Word (VLIW) processor. Conditional execution is provided to replace data dependent branch instructions, which are not allowed.

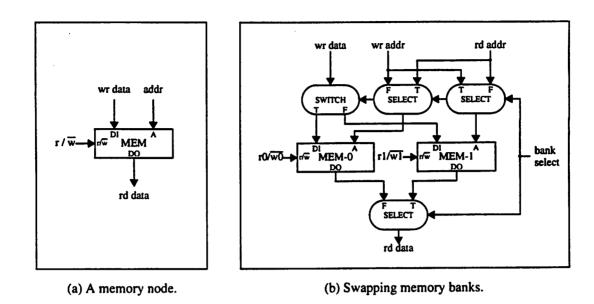

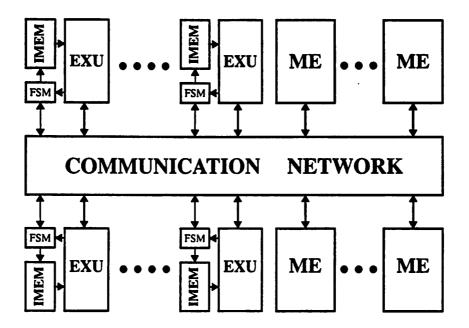

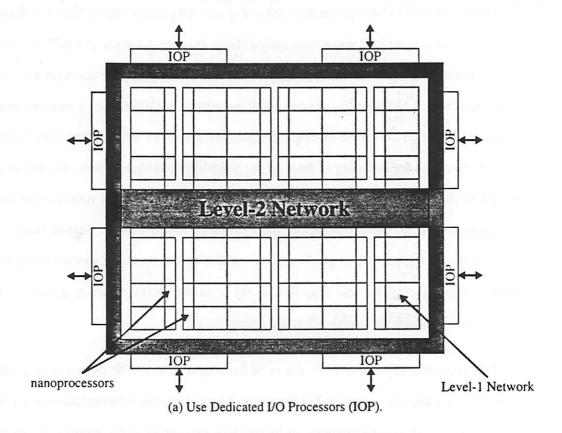

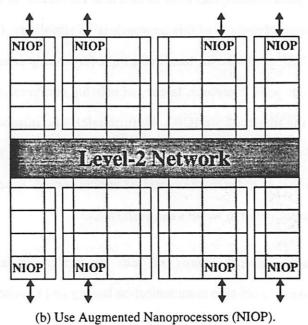

An ALE consists of 3 silos, 3 barrel shifters and a 12-bit ALU, and is capable of performing arithmetic, logic, compare and shift operations. Multiplication is implemented sequentially by the partial multiplication operations based on Booth encoding. The ME contains a 2k by 12-bit two-port SRAM, 3 silos and some logic for address calculation, and can perform a read and a write operation concurrently every clock cycle. A BE, consisting of a silo and a barrel shifter, is mainly used a *floating silo* in series with any other processing element when longer length of the silo is needed. In addition, the BE can perform shift operations thereby freeing an ALE. Running at a clock frequency of 54 MHz, the chip provide 1.5 GIPS peak, and the six OE and six input buses provide a combined I/O bandwidth of 7.7 Gb/sec.