# Copyright © 1995, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# AUTOMATIC SYNTHESIS OF CMOS ALGORITHMIC ANALOG-TO-DIGITAL CONVERTER

by

Gani Jusuf

Memorandum No. UCB/ERL M95/27

21 April 1995

# AUTOMATIC SYNTHESIS OF CMOS ALGORITHMIC ANALOG-TO-DIGITAL CONVERTER

by

Gani Jusuf

Memorandum No. UCB/ERL M95/27

21 April 1995

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# Automatic Synthesis of CMOS Algorithmic Analog-to-Digital Converter

Copyright 1993

by

Gani Jusuf

# Automatic Synthesis of CMOS Algorithmic Analog-to-Digital Converter

by

#### Gani Jusuf

Doctor of Philosophy in

Electrical Engineering and Computer Sciences

University of California at Berkeley

#### **ABSTRACT**

The steady decrease in technological feature size is allowing increasing levels of integration in analog/digital interface functions. These functions consist of analog as well as digital circuits. While the turn around time for an all digital IC chip is very short due to the maturity of digital IC computer-aided design (CAD) tools over the last ten years, most analog circuits have to be designed manually due to the lack of analog IC CAD tools. As a result, analog circuit design becomes the bottleneck in the design of mixed signal processing chips. One common analog function in a mixed signal processing chip is an analog-to-digital conversion (ADC) function. This function recurs frequently but with varying performance requirements. The objective of this research is to study the design methodology of a compilation program capable of synthesizing ADC's with a broad range of sampling rates and resolution, and silicon area and performance comparable with the manual approach.

The automatic compilation of the ADC function is a difficult problem mainly because ADC techniques span such a wide spectrum of performance, with radically different implementations being optimum for different ranges of conversion range, resolution, and power dissipation. We will show that a proper choice of the ADC architectures and the incorporation of many analog circuit design techniques will simplify the synthesis proce-

dure tremendously. Moreover, in order to speed up the device sizing, hierarchical optimization procedure and behavioral simulation are implemented into the ADC module generation steps.

As a result of this study, a new improved algorithmic ADC without the need of high precision comparators has been developed. This type of ADC lends itself to automatic generation due to its modularity, simplicity, small area consumption, moderate speed, low power dissipation, and single parameter trim capability that can be added at high resolution. Furthermore, a performance-driven CMOS ADC module generator, CADICS based on design rules and spice parameters has been developed. CADICS takes a set of input files and generates the complete ADC netlist, layout, and performance summary. A prototype of the automatically generated ADC has also been fabricated and tested.

Professor Paul R. Gray, Chair

# To my mother and Caroline

# **Acknowledgements**

No words could describe my appreciation for the support, guidance, encouragement, patience, and understanding given by Professor Paul R. Gray throughout this work and my years at Berkeley. I would also like to thank my other advisor, Professor Alberto Sangiovanni-Vincentelli for his valuable advice in both research and academic matters.

I would gratefully acknowledge all of my fellow students who have made my many years at Berkeley more enjoyable. From the old generation of graduate students, Steve Lewis, Sehat Sutarja, Beomsup Kim, and Yuh-Min Lin provided me with a lot of support when I started the research. Of the current generation, I have to thank Timothy Hu, Greg Uehara, Cormac Conroy, Dave Cline, Weijie Yun, Ken Nishimura, and Robert Neff for their help in maintaining a good balance between work and leisure. Many thanks have to be given to Ed Liu, Henry Chang, Umakanta Choudhury, Enrico Malavasi, and Eduardo Charbon for their support throughout this project. There are so many more people to thank without them this research would not have been possible.

This research was supported by SRC under contract number SRC-92-DC-008 and DARPA under contract number N00039-87-C-0182. Their support is gratefully acknowledged.

Finally, I would like to thank my wife, Caroline for encouraging and giving me moral support for all these years. My greatest thanks of all has to be given to my mother, without her I won't be where I am today.

# TABLE OF CONTENTS

| CHAPTER 1 |     | Introduction                                                                                                                   | 1 |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------|---|

|           | 1.1 | Background and Motivation 1                                                                                                    |   |

|           | 1.2 | Integrated Circuit Design Automation 2                                                                                         |   |

|           | 1.3 | Thesis Contribution 6                                                                                                          |   |

|           | 1.4 | Thesis Organization 7                                                                                                          |   |

| CHAPTER 2 |     | <b>Automatic Generation of Analog Blocks</b>                                                                                   | 9 |

|           | 2.1 | Introduction 9                                                                                                                 |   |

|           | 2.2 | Why Do Module Generation? 10                                                                                                   |   |

|           | 2.3 | Existing Analog Module Generators 13                                                                                           |   |

|           |     | <ul><li>2.3.1 Operational-Amplifier Module Generator. 13</li><li>2.3.2 Switched-Capacitor Filter Module Generator 14</li></ul> |   |

|           | 2.4 | Analog-To-Digital Conversion Module Generator 17                                                                               |   |

|           |     | 2.4.1 Overall Goals 17                                                                                                         |   |

|           |     | 2.4.2 Functionality 19 2.4.3 Characterization 19                                                                               |   |

|           |     | 2.4.3.1 Differential Non-Linearity (DNL) 23                                                                                    |   |

|           |     | 2.4.3.2 Integral Non-Linearity (INL) 23                                                                                        |   |

|           |     | 2.4.3.3 Gain Error 25                                                                                                          |   |

|           |     | 2.4.3.4 Offset Error 25                                                                                                        |   |

|           |     | 2.4.4 Signal-To-Noise Ratio 26                                                                                                 |   |

|           |     |                                                                                                                                |   |

|           |     | TABLE OF CONTENTS                                                                                                                                                                                                                                                                                |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |     | 2.4.5 Previous Work 28 2.4.5.1 Analog Cell Library 28 2.4.5.2 Performance-Driven Based on Standard Cells 28                                                                                                                                                                                      |

|           |     | 2.4.6 Methods of Attack 30                                                                                                                                                                                                                                                                       |

| •         | 2.5 | Summary 31                                                                                                                                                                                                                                                                                       |

| CHAPTER 3 |     | ADC Architectures Suitable for Automatic Compilation 33                                                                                                                                                                                                                                          |

|           | 3.1 | Introduction 33                                                                                                                                                                                                                                                                                  |

|           | 3.2 | A/D Conversion Architectures 34                                                                                                                                                                                                                                                                  |

|           |     | <ul> <li>3.2.1 Serial A/D Conversion Technique 34</li> <li>3.2.2 Successive Approximation A/D Conversion Technique 34</li> <li>3.2.3 Parallel A/D Conversion Technique 37</li> <li>3.2.4 Pipelined A/D Conversion Technique 38</li> <li>3.2.5 Oversampled A/D Conversion Technique 40</li> </ul> |

|           | 3.3 | Architecture Comparison 42                                                                                                                                                                                                                                                                       |

|           |     | Desired Properties 45                                                                                                                                                                                                                                                                            |

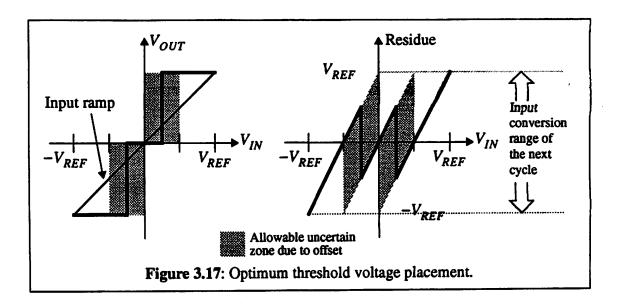

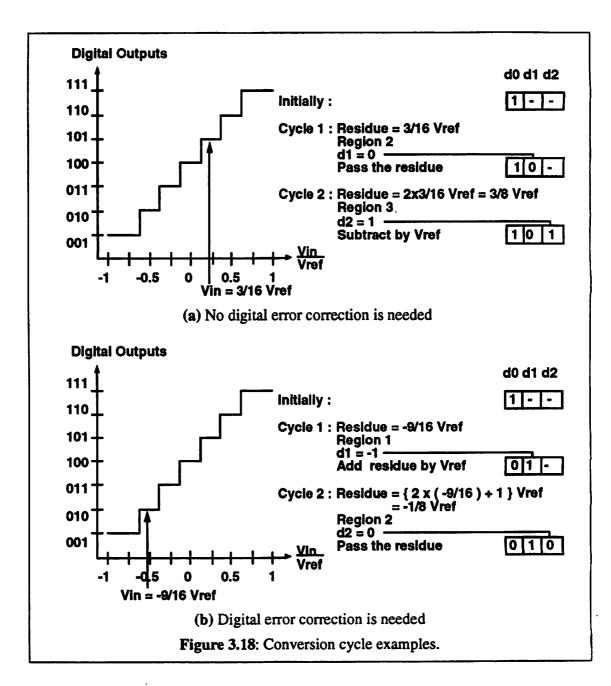

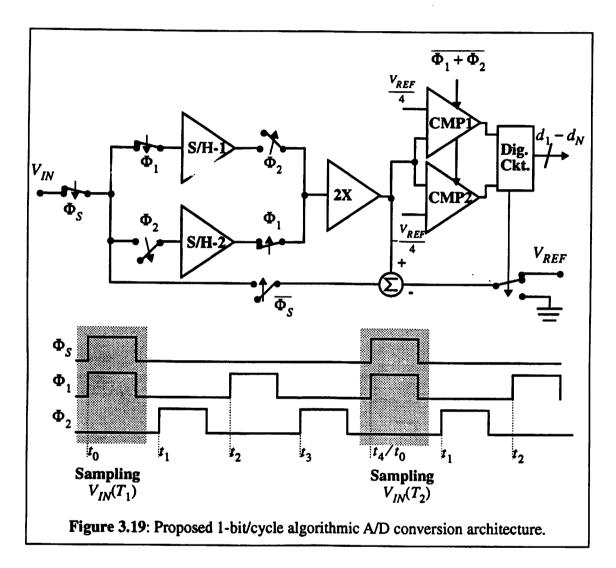

|           |     | An Improved Algorithmic A/D Converter 46 3.5.1 Algorithmic A/D Converter 47 3.5.2 Speed Improvement Solution 50 3.5.3 Comparator Offset Solution 55 3.5.3.1 Two-Comparator Scheme and Digital Error Correction 57                                                                                |

|           | 3.6 | 3.5.4 Proposed 1-Bit/Cycle Algorithmic A/D Converter 62<br>Summary 64                                                                                                                                                                                                                            |

| CHAPTER 4 |     | ADC Circuit Generation 67                                                                                                                                                                                                                                                                        |

|           | 4.1 | Introduction 67                                                                                                                                                                                                                                                                                  |

|           | 4.2 | Architectural Selection 67                                                                                                                                                                                                                                                                       |

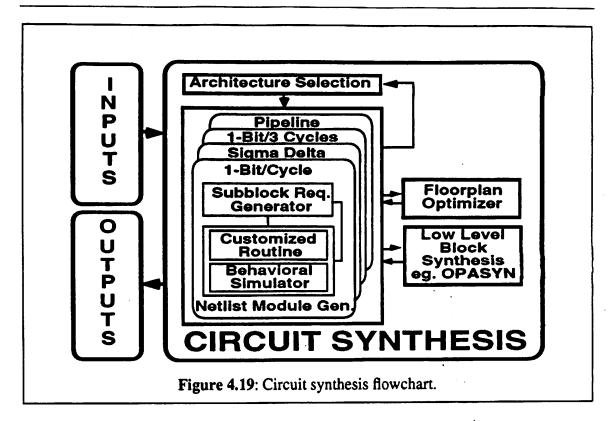

|           | 4.3 | Circuit Synthesis 71                                                                                                                                                                                                                                                                             |

|           |     | 4.3.1 Optimization Approaches 72 4.3.1.1 Global Optimization Approach 72 4.3.1.2 Hierarchical Optimization Approach 72                                                                                                                                                                           |

|           | 4.4 | Implementation 75                                                                                                                                                                                                                                                                                |

|           |     | 4.4.1 Inputs and Outputs 75 4.4.2 Optimization 77 4.4.3 Netlist Module Generator 83 4.4.3.1 Mapping Function 84                                                                                                                                                                                  |

|           |     | 4.4.3.2 Generating Operational Amplifiers 91 4.4.3.3 Generating Comparators 92 4.4.3.4 Generating Switch and Capacitor Sizes 93 4.4.3.5 Generating Digital Circuitry 93 4.4.4 Evaluator 93                                                                                                                                                                                                             |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 45  | 4.4.4.1 Behavioral Simulator 94 4.4.4.2 Floorplan Optimization 100 4.4.5 Scheduler 101 4.4.6 Quality of the circuit synthesis 101 Summary 102                                                                                                                                                                                                                                                          |

|           | 7.3 | Summary 102                                                                                                                                                                                                                                                                                                                                                                                            |

| CHAPTER 5 |     | <b>ADC Layout Generation</b> 105                                                                                                                                                                                                                                                                                                                                                                       |

|           | 5.1 | Introduction 105                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 5.2 | Approach 105                                                                                                                                                                                                                                                                                                                                                                                           |

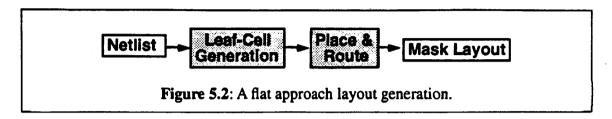

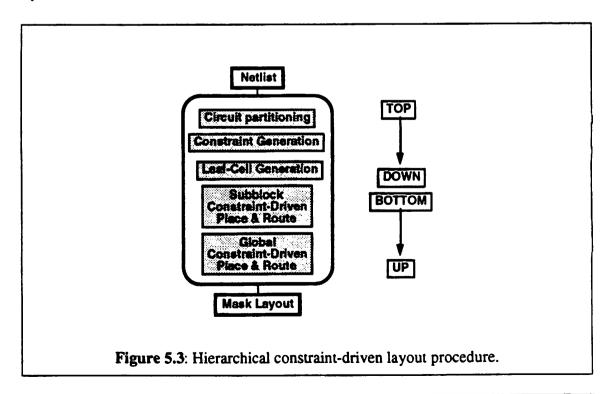

|           |     | <ul> <li>5.2.1 Flat Layout Procedure 106</li> <li>5.2.2 Hierarchical Constraint-Driven Layout 107</li> <li>5.2.2.1 Circuit Partitioning 108</li> <li>5.2.2.2 Constraint Generation 108</li> <li>5.2.2.3 Device Generation, Placement, and Routing 110</li> </ul>                                                                                                                                       |

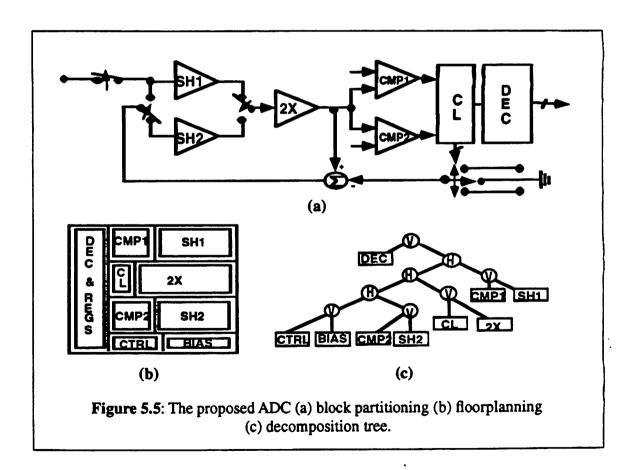

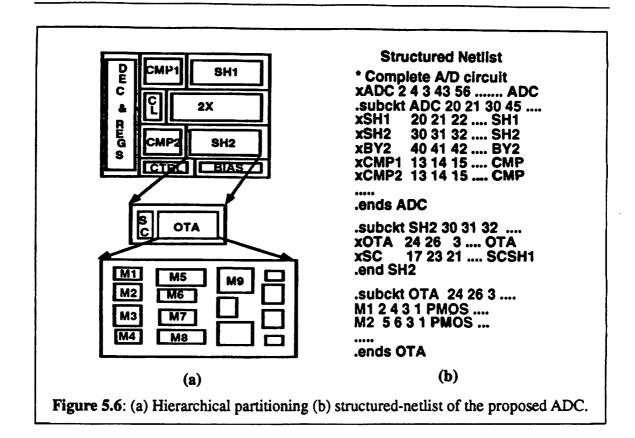

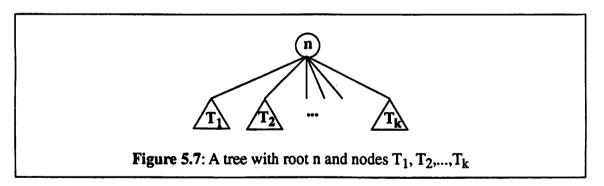

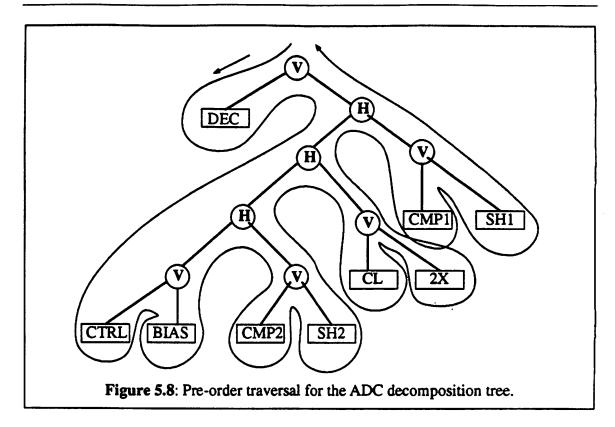

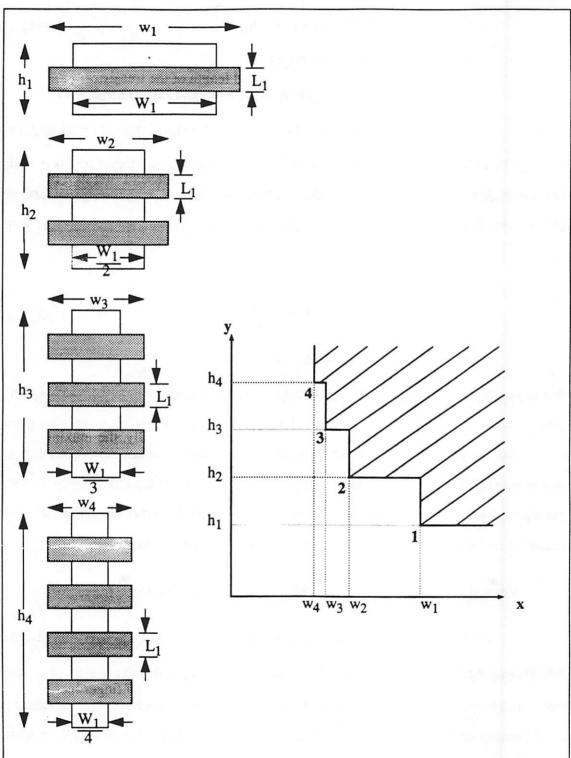

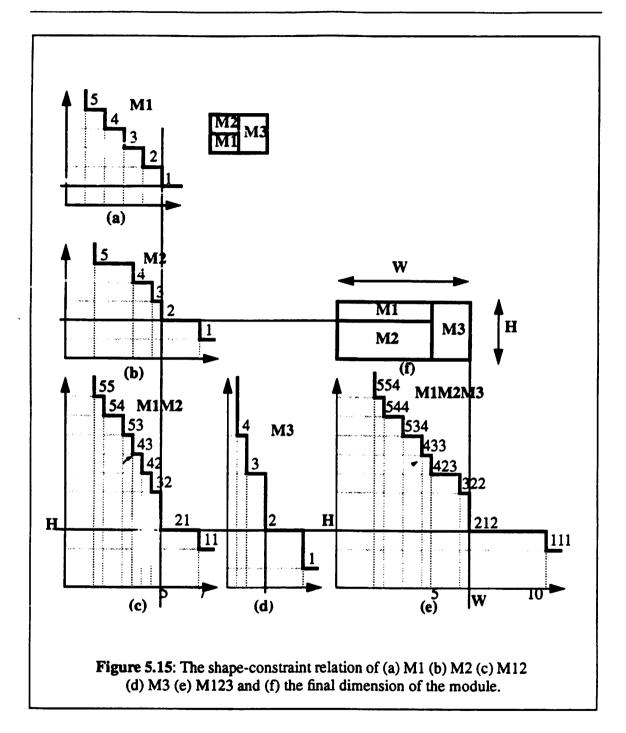

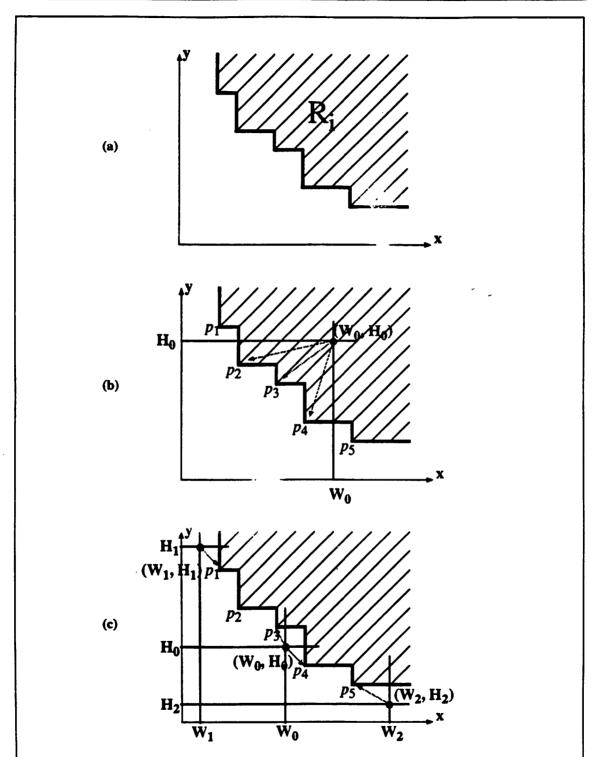

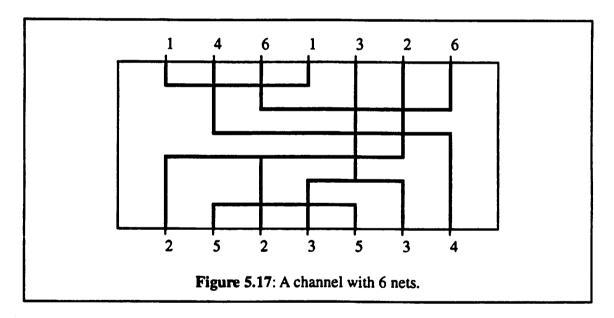

|           |     | Implementation 110  5.3.1 Circuit Partitioning and Floorplanning 110 5.3.1.1 Structured-Netlist 112  5.3.2 Floorplanning 112 5.3.2.1 Slicing Structure 113 5.3.2.2 Layout Style 115  5.3.3 Floorplan Optimization 117 5.3.3.1 Device Structure and Shape 117 5.3.3.2 Modified Stockmeyer's Algorithm 120 5.3.3.3 Channel Area Estimation 127  5.3.4 Data Structure 129  5.3.5 Routing 129  Summary 132 |

| CHAPTER 6 |     | Examples and Test Results 133                                                                                                                                                                                                                                                                                                                                                                          |

|           | 6.1 |                                                                                                                                                                                                                                                                                                                                                                                                        |

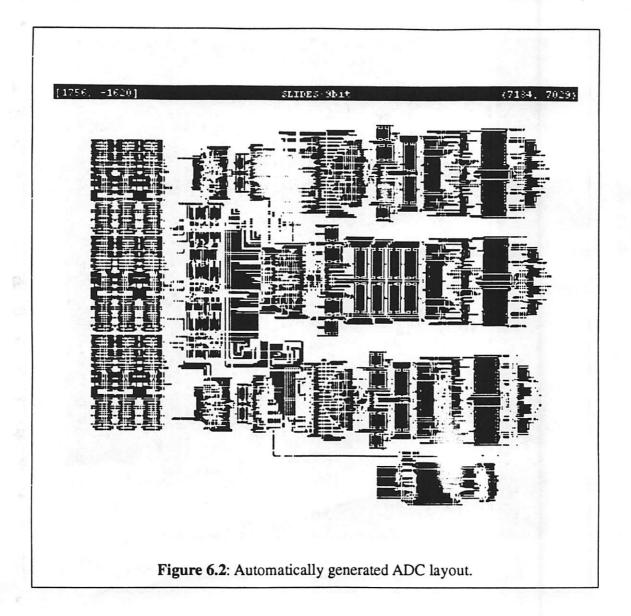

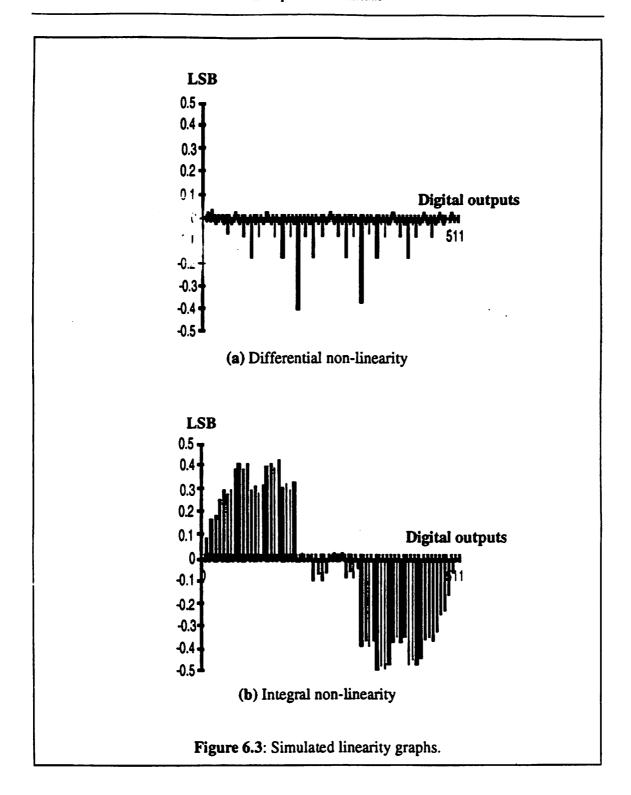

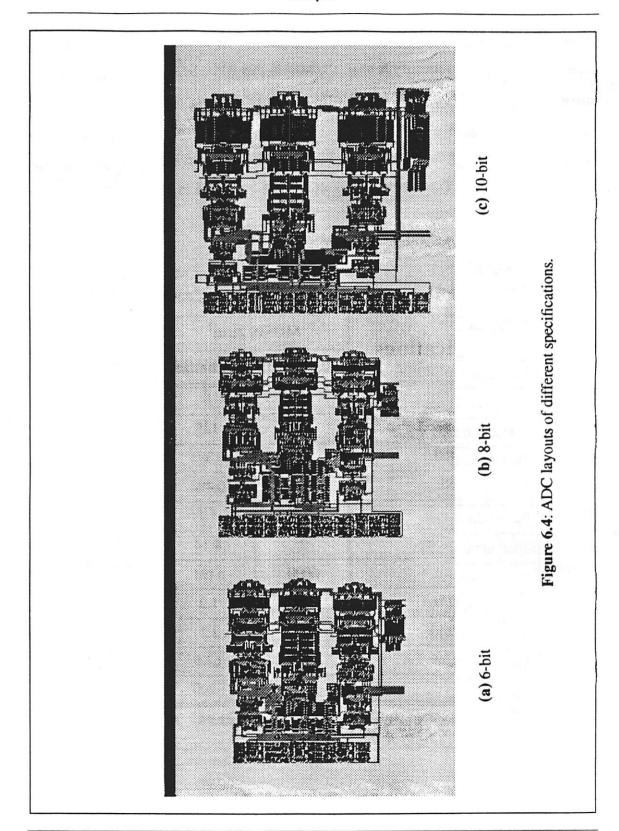

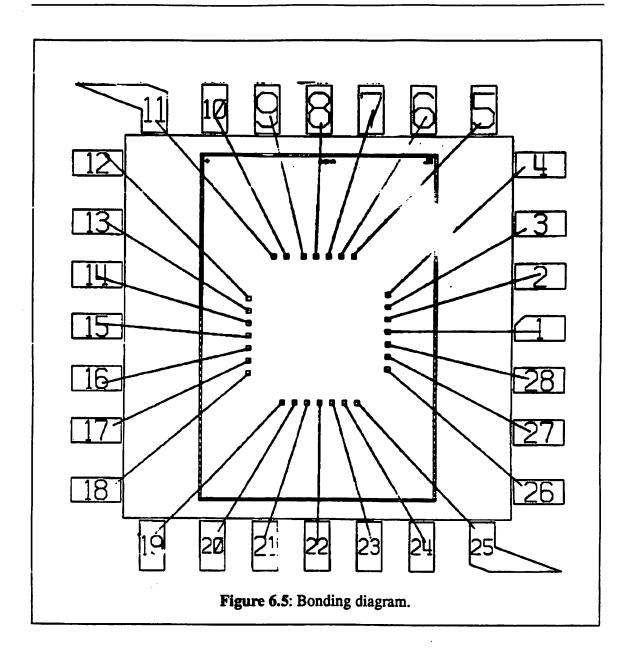

|           | 6.2 | Examples 133                                                                                                                                                                                                                                                                                                                                                                                           |

|           |     | 6.2.1 Manually Designed Example 133 6.2.2 Automatically Generated Examples 135                                                                                                                                                                                                                                                                                                                         |

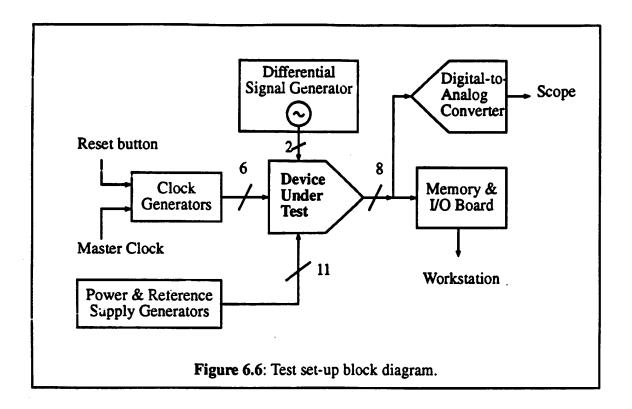

|           |     | Test Set-up 141                                                                                                                                                                                                                                                                                                                                                                                        |

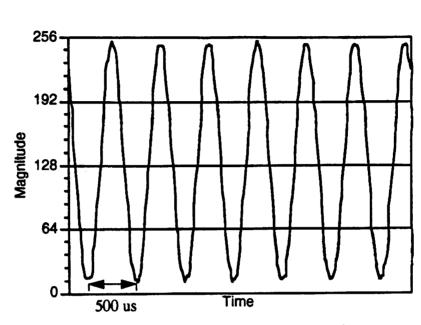

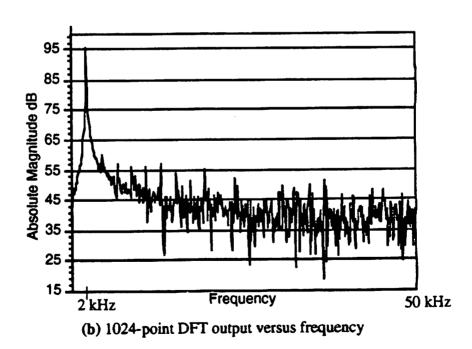

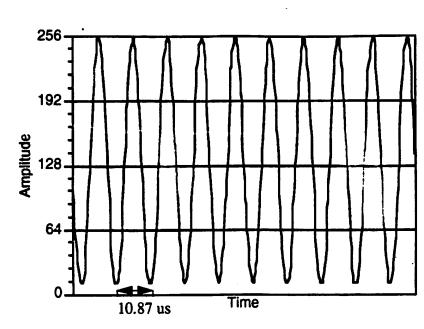

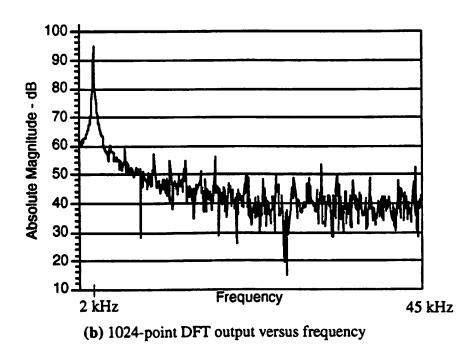

|           | 6.4 | Test Results 143                                                                                                                                                                                                                                                                                                                                                                                       |

|           |     | vii                                                                                                                                                                                                                                                                                                                                                                                                    |

**TABLE OF CONTENTS**

| TABLE OF CONTENTS |                                                                                                                                                                                                               |     |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| 6.5               | Summary 147                                                                                                                                                                                                   |     |  |  |  |

| CHAPTER 7         | Conclusion                                                                                                                                                                                                    | 149 |  |  |  |

| 7.1               | Summary of Research Results 149 7.1.1 An Improved Algorithmic A/D Conversion A rchitecture 149                                                                                                                |     |  |  |  |

| 7.2               | 7.1.2 ADC Module Generation 150 Future Work 153                                                                                                                                                               |     |  |  |  |

| BIBLIOGRAPHY      |                                                                                                                                                                                                               |     |  |  |  |

| APPENDIX A:       | Building Blocks                                                                                                                                                                                               | 163 |  |  |  |

| <b>A.</b> 1       | Introduction 163                                                                                                                                                                                              |     |  |  |  |

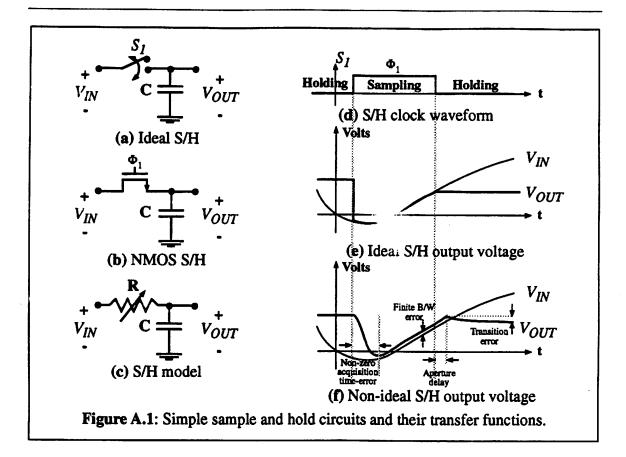

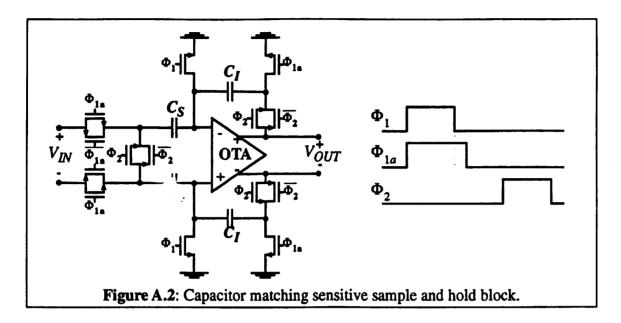

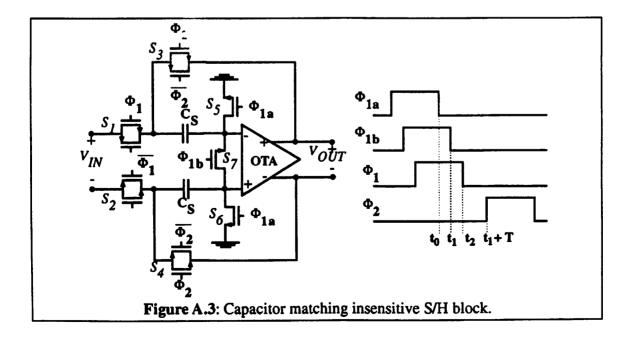

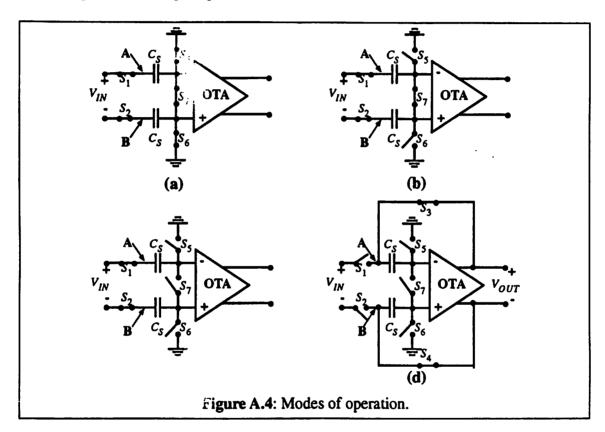

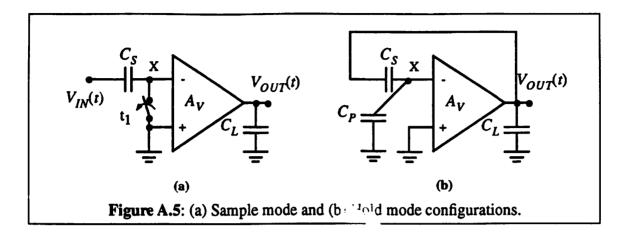

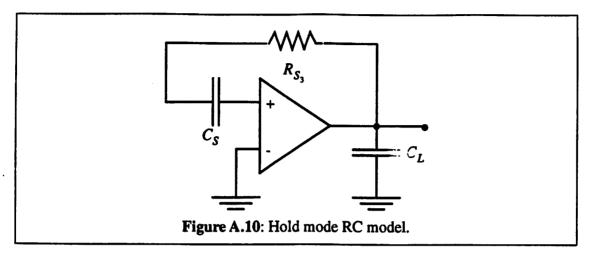

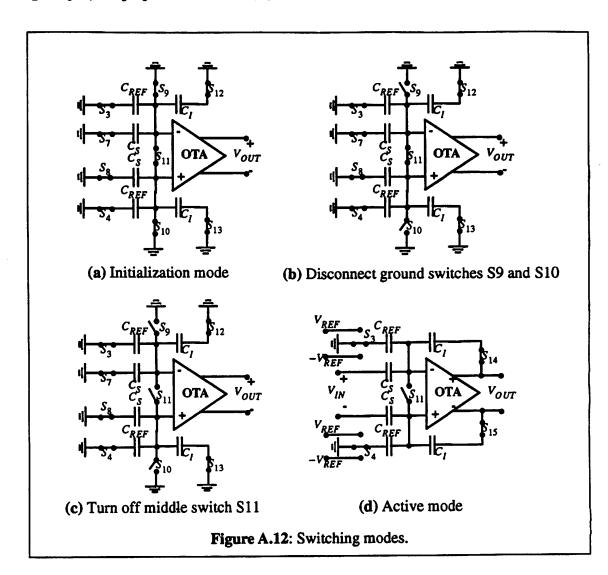

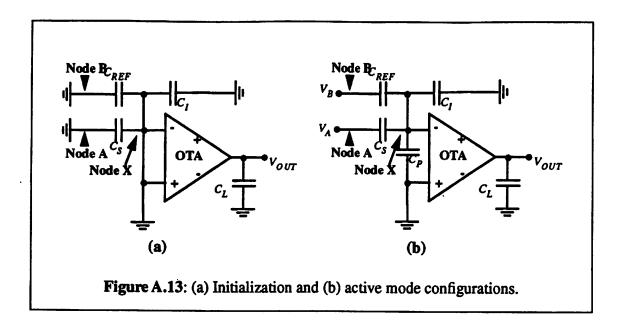

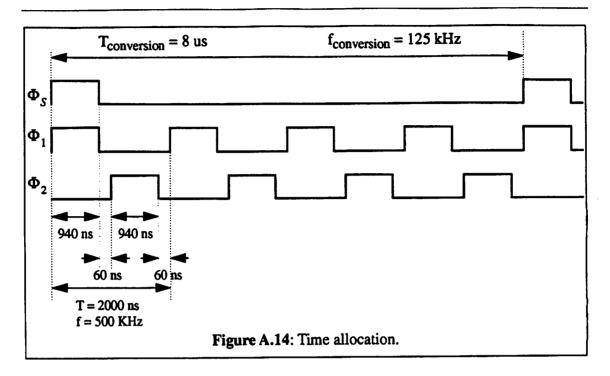

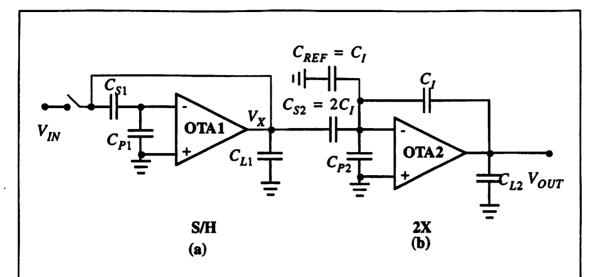

| A.2               | Sample and Hold Block 163 A.2.1 S/H Circuit 163 A.2.2 Switching Sequence 167 A.2.3 Transfer Function 168 A.2.4 Noise Source 170 A.2.5 Switch Size Calculation 172 A.2.6 Amplifier 181                         |     |  |  |  |

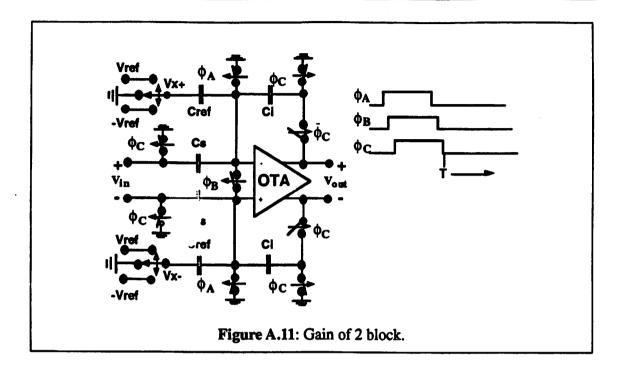

| ·                 | Gain of Two Block 181  A.3.1 2X Circuit 181  A.3.2 Switching Scheme 182  A.3.3 Transfer Function 183  A.3.4 Noise Source 185                                                                                  |     |  |  |  |

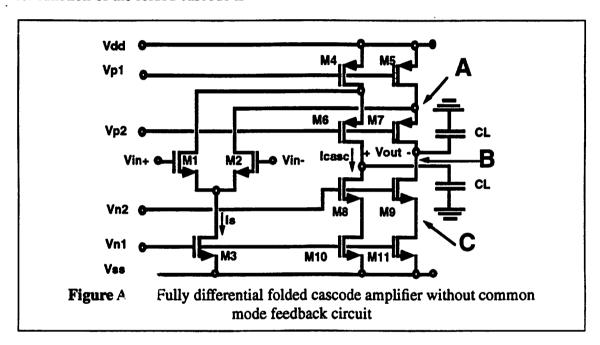

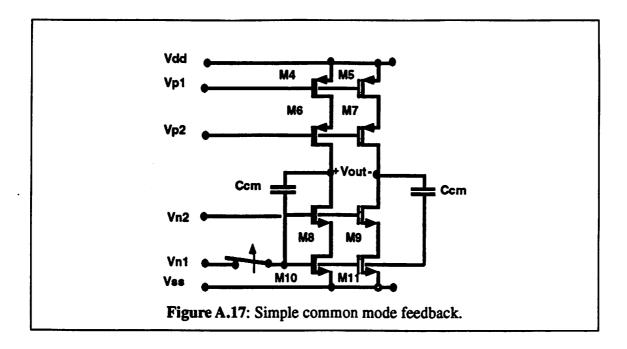

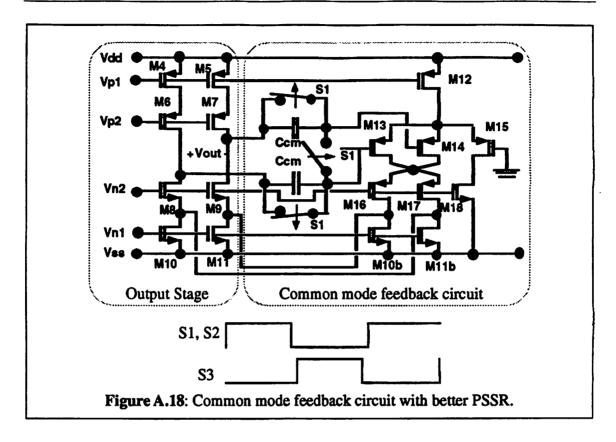

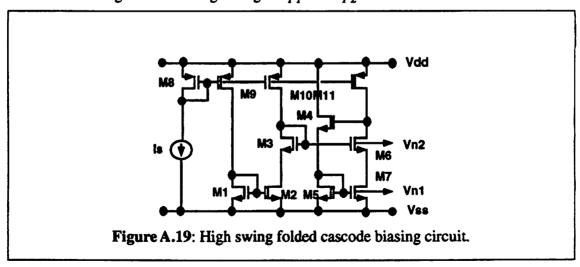

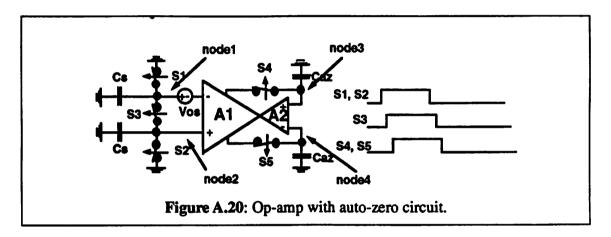

|                   | Amplifier 187  A.4.1 Amplifier Specifications 187  A.4.2 Basic Op-amp Topology 192  A.4.3 Common Mode Feedback Circuit 197  A.4.4 Biasing Circuit 198  A.4.5 Auto-Zero Circuit 200  A.4.6 Noise Reduction 202 |     |  |  |  |

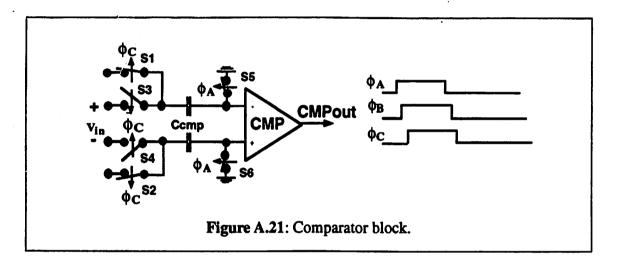

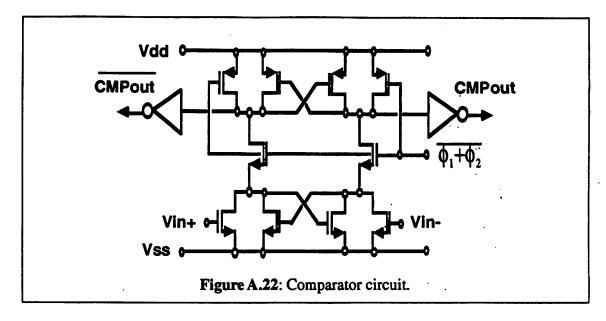

|                   | Comparator Blocks 203                                                                                                                                                                                         |     |  |  |  |

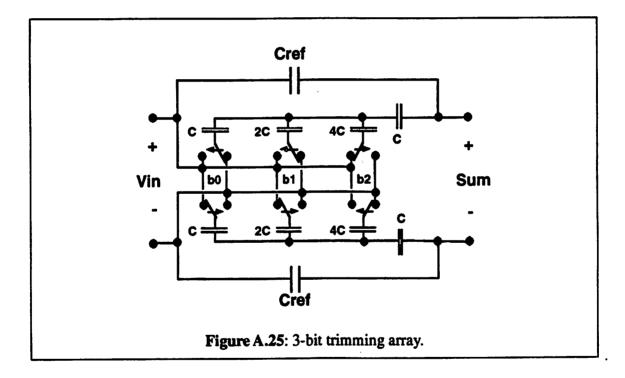

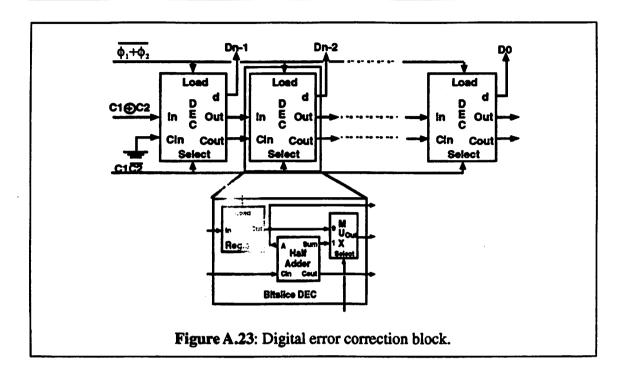

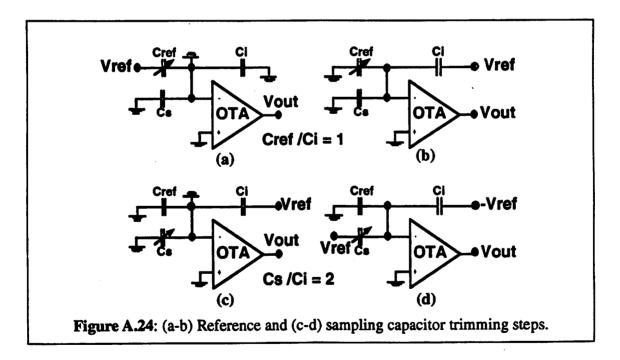

|                   | Digital Circuits 205 Trim Array 207                                                                                                                                                                           |     |  |  |  |

# **CHAPTER 1 Introduction**

# 1.1 Background and Motivation

Over the last two decades technology feature size has decreased allowing increasing levels of integration in analog/digital (A/D) interface functions. These functions are usually mixed analog-digital integrated circuits containing both analog and digital circuitry. Very high levels of integration have been achieved in mixed-signal IC's intended for high-volume manufacturers in dedicated high-volume applications, resulting in very low cost of manufacturing. These examples include telephony components such as modems and voice coder/decoders, interface components for local area networks and so forth. This cost reduction through higher level of integration has been more difficult to achieve in components with functionality specific to systems that will be manufactured in low to moderate volume applications. The sophisticated automatic synthesis tools that allow fast turn-around implementation of high-integration components in purely digital functions, such as gate array, standard cell, and field programmable logic arrays (FPLA's), do not as yet exist for analog and mixed signal components. One of the objective of the research described here is to make a contribution to that goal.

#### Introduction

There are several factors that complicate semi-custom analog and mixed signal design. Because of rapid evolution in technology, design techniques and tools must adapt to a rapidly changing technology base. Unfortunately, most analog IC products presently have to be designed manually by expert analog IC designers due to the lack of analog CAD tools. As a result, analog circuit design has become the bottleneck in the design of mixed analog/digital interface chips. This has seriously hampered the effort to reduce the product development time mentioned earlier. In the next section, a brief discussion of why digital CAD tools progress much faster than its analog counterparts will be presented. The progress in semi-custom applications is limited more by the lack of suitable analog CAD tools such as mixed signal simulator, design capture, synthesis tools for commonly used blocks, place and route, layout extraction, verification, and testing.

One common analog function in a mixed signal chips such a modems is an analog to digital conversion (ADC) block. This function recurs frequently but with varying performance requirements [CHEC78], [TOWN80], [OHAR87]. Efforts to automate the design of A/D conversion functions have been reported previously [ALLE86], [HELM87]; however, there are some shortcomings in the implementation of these tools which will be described in Chapter 2. Since the ADC block is one of the critical block in the design of mixed-signal chips, we are motivated to study the approach and implementation of an ADC synthesis tool so that it can be used to improve or speed up the turn around time of mixed signal chips

# 1.2 Integrated Circuit Design Automation

Integrated circ: design can be divided into two different classes: digital and analog circuits. The distinction on is mainly due to their differences in signal representations, sensitivity, and performance trade-off.

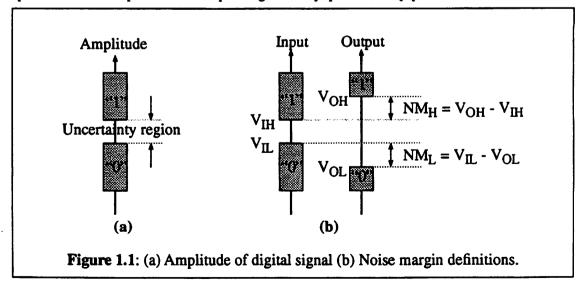

In digital circuits, signals are represented by a stream of discrete voltage levels which is usually represented in terms of binary numbers "1" or "0". These binary levels are usually representing a range of continuous voltages as shown in Figure 1.1(a). Typically we would like to minimize the uncertainty region shown in Figure 1.1(a) so that the allowable disturbance voltages (noise margins) at the input of a digital block can be maximized. Figure 1.1(b) shows how the noise margins are defined based on the range of the input voltages (V<sub>IL</sub>, maximum input voltage for logic "0" and V<sub>IH</sub>, minimum input voltage for logic "1") and output voltages ( $V_{\mbox{\scriptsize OL}}$ , maximum output voltage for logic "0" and VOH, minimum output voltage for logic "1"). In digital circuit, signal disturbance at the input of a block does not get forwarded to the output as it does in analog circuit. As a result, a substantial level of signal disturbances from noise coupling, power supply fluctuation, and random noise will not degrade the digital signal level as it passes a digital block. Furthermore, having these discrete signal representations allows digital circuits to have a standardized interface levels, which in turn gives a standard power supply requirement. As a result, digital circuits have only a small set of performance measures that need to be optimized such as power consumption, gate delay, power-delay product, and area.

#### Introduction

In analog circuits, signals are represented by continuous voltages, currents or charges as a function of time. Depending on the application, analog input signals can have a range from a few millivolts to several tens or even hundreds of volts. Signal disturbances which are tolerable in one application can be devastating in another. Moreover, power supply requirement will also vary depending on applications. Unlike digital circuits, analog circuits have no standardized interface levels or standard power supply requirements. As a result, analog circuits have a large set of performance measures that need to be optimized such as bandwidth, power dissipation, gain, offset, dynamic range, area, noise, supply rejection, overall accuracy, and many others. These performance measures of analog circuits depend more heavily on details of device behavior than do those of digital circuits.

With the distinctions mentioned above, we can now discuss the design automation of integration circuits which is a subset of Electronic Design Automation (EDA). The EDA effort started in early 1950's when digital computers were just becoming popular [GRAH53]. Since then, EDA has made tremendous progress and branched out into many different specialized fields over the last forty years. One of these specialized fields is integrated circuit design automation (ICDA). For the last 15 years, ICDA has evolved into two different fields: CAD for digital IC's and CAD for analog IC's. Digital IC CAD has advanced at a much faster rate than its analog counterpart for several reasons:

- 1. Complexity: Digital circuits are formed from a smaller number of primitives and are described by a much smaller number of performance parameters than analog circuits. Hence they are easier to design in many ways than analog ones since digital circuits have far fewer optimization constraints.

- 2. Number of generic primitive blocks: In digital domain there exist simple and generic block functions from which many higher level and complex digital

#### Integrated Circuit Design Automation

blocks can be implemented. Examples of these simple generic blocks are NAND and NOR gates. For analog circuits, such a simple and generic block does not exist.

3. Size of User Community Base: Measured economically by sales, purely digital integrated circuits are about 5 times larger than the mixed signal and analog applications. Furthermore, the digital domain is dominated by CMOS implementations of logic functions operating on 5 volts, with speed and logic density being the main performance parameters of interest. In the analog domain, the user base is highly fragmented into different technologies (CMOS, Bipolar, BiCMOS), various performance domains (high frequency, low power, high precision, high power, etc.), and supply voltage (30V, 12V, 5V, 3V, 1.5V to name the most important standards). As a result, the cost of the research and development of digital computer-aided design software can be amortized over a much larger base of potential users. On the other hand, the cost of the research and development of analog computer-aided design software, which tends to be specific to one technology, supply voltage, and performance domain, becomes very expensive because of the small user community.

Recently, there has been a surge of interest in the field of analog ICDA both from universities as well as commercial laboratories. With constant scaling in technology feature size, an important motivation drive in the 90's is to increase the level of integration in IC chips to reduce cost. This means that the inclusion of both analog as well as digital circuits into a single chip is a must. For this to be successful, improved maturity of EDA for analog integrated circuits is a necessary condition. With this impetus, hopefully, analog ICDA will progress at a much faster rate.

## 1.3 Thesis Contribution

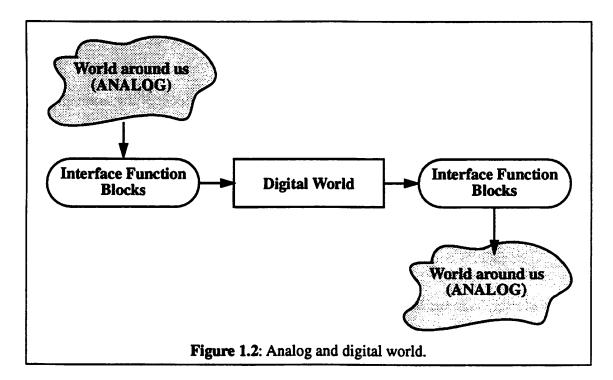

With the steady decrease in the cost of designing digital VLSI and the advancement of digital signal processing (DSP), more and more analog building block IC's will be replaced by more highly integrated mixed signal application specific integrated circuits commonly known as ASIC's. Some have suggested that analog circuit design will die as an IC implementation methodology and digital circuit design will take over. This belief is probably true in many IC applications where signal processing functions can be common to digital circuits. However, the world around us is still analog and anything interacts with environment needs some kind of interface blocks as shown Figure 1.2.

In order to make use of advancements in digital VLSI, we need to convert analog data into its digital representation. Thus inalog data has to be interfaced with special ion-verters in order to be processed digitally. Borrowing an example from [GRAY87] on the

#### Thesis Organization

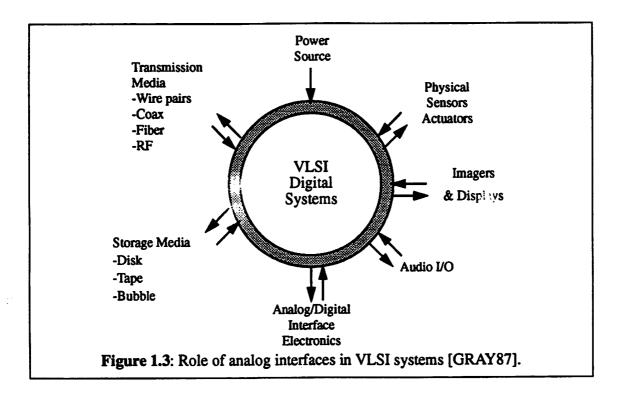

role of analog interfaces in VLSI systems, a VLSI digital system is like an egg and the analog interfaces is the eggshell as shown in Figure 1.3. As the egg is getting bigger (which is analogous to the advancement of digital VLSI system), the eggshell is getting thinner (which is analogous to more and more analog block functions being replaced by digital circuits). But the egg will never hatch! Thus the analog interface functions will remain as an important role in VLSI systems.

One of the most common blocks used in analog-digital mixed-signal IC's is an Analog-to-digital converter (ADC). Efforts to create better ADC blocks are actively pursued both in academic as well as industry sectors. In this thesis, we will present a new improved algorithmic ADC architecture that is capable of converting analog signal at a higher rate than previously reported algorithmic ADC architecture. We will also introduce a two-comparator scheme that allows us to use low-precision or simple comparators to do the comparison without affecting the overall performance of the A/D converter.

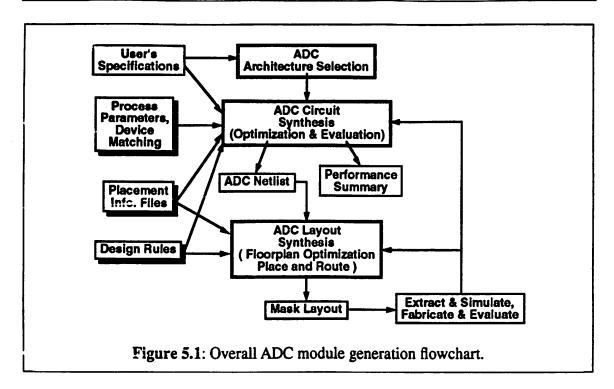

In the area of analog CAD, this thesis will present a methodology to approach and implement a module generation program for such a general function as A/D converters. We will discuss in detail how we implement a technology-independent ADC module generator, CADICS [JUSU90] that optimizes performance, silicon area, and power dissipation so that the resulting ADC's are comparable with a manual design. We will also show at the end that the methodology can also be applied for implementing a general mixed signal design automation system.

# 1.4 Thesis Organization

In the remaining of this thesis, the study and implementation of a performancedriven ADC module generator will be presented. In Chapter 2, a brief discussion of exist-

ing analog block module generators and a detailed discussion of ADC blocks, previous work in ADC module generation, and methods of attack will be presented. In Chapter 3, an architectural study of different A/D conversion techniques will be presented. Comparisons in architecture, performances, trade-off, and complexities will discussed in detail. An improved algorithmic ADC architecture will then be presented. Detailed implementations of the circuit and layout generations of the ADC module generator will be covered in Chapter 4 and 5 respectively. In Chapter 6, some examples and experimental results will be presented. In Chapter 7, a summary of research and a brief discussion as what the future direction will be discussed. Finally, an in depth discussion of the circuit design techniques for each functional block of the ADC is presented in the Appendix A.

# CHAPTER 2 Automatic Generation of Analog Blocks

## 2.1 Introduction

Automatic generation of analog blocks has become *very desirable* as system level designers try to shorten the turn-around time of designing mixed signal chips. Unfortunately, the lack of such tools forces the designers to utilize off the shelf components or pre-designed analog blocks that are optimized to certain applications. Efforts to come up with a general analog design framework that is capable of generating complete analog block layouts from high level specifications are currently being carried out [HARJ89], [DEGR87], [CHAN92], [GIEL92]. In this chapter, we will first discuss why module generation of specific analog functions is a good starting point to the realization of a general automatic analog design framework. Examples of existing analog block module generators will then be presented. The goals of analog-to-digital conversion (ADC) module generator developed will then be described.

# 2.2 Why Do Module Generation?

As mentioned in Chapter 1, the implementation of analog CAD tools, in general, is more difficult than the implementation of digital CAD tools, as is the analog design problem. Ideally we would like to have a general analog circuit framework similar to that of its digital counterparts. However, analog circuits in general require more design freedom in order to meet performance objectives. They often exploit the full spectrum of capabilities exhibited by individual devices. In analog circuits, the individual devices often have different sizes and electrical characteristics. These devices require optimization of different performance requirements. The importance of each performance requirement will depend on circuit applications.

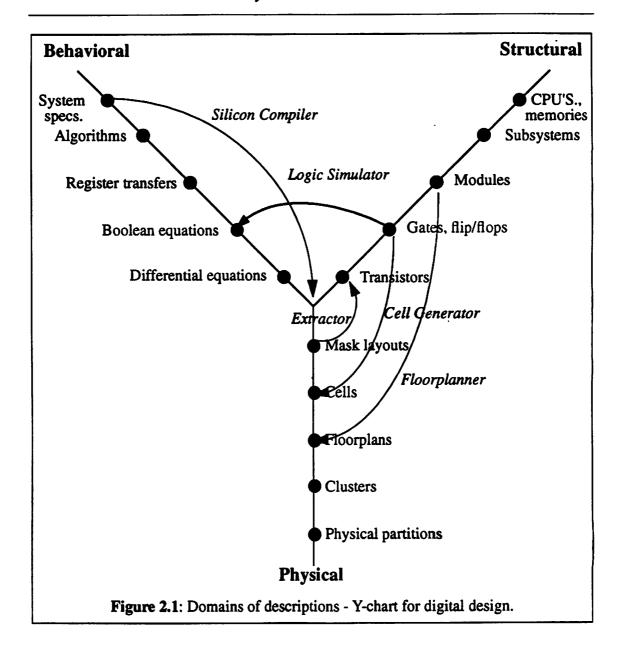

In digital design methodology, there are multiple abstraction levels that can be represented by a tri-partite representation of design (commonly known as the Y-chart [GAJS86]) as shown Figure 2.1. This unified model of design representation separates the structural, behavioral, and physical domains. The level of abstraction decreases as one moves toward the center vertex. The procedures to go from one level of abstraction to the next one are clearly defined since they can be structured on to several levels of hierarchy.

For analog design, there are few acceptable abstraction levels such as functional and behavioral. The rest of abstraction levels are not clearly defined. The procedures to move from one point to the next point in a domain will be different from one analog function to the next. Therefore, to come up with a general design methodology that can generate all possible analog blocks is very difficult if not impossible. Instead, a more realistic goal would be to have an analog design framework or mixed signal design framework that can generate different analog or mixed signal blocks. This kind of framework is basically an integration of all different CAD tools written specifically for analog or mixed signal blocks. An example of such a framework is currently being developed at U.C. Berkeley

## [CHAN92].

While it is sometimes possible to share CAD tools between digital and analog portions of a circuit, such as design rule checkers and extractors, many CAD tools must be designed for use primarily on analog circuits. Many existing analog CAD tools are the extension of the digital tools. Generic tools such as router, placement, and compactor that

can handle analog blocks are becoming hot research topic in university sectors. Examples of analog routers are constrained-driven channel router, ART [CHOU90] and constrained-driven maze router, ROAD [MALA90]. These routers are also capable of routing fully differential blocks that have become a common analog circuit design technique. Analog placement [CHAR92] and compaction [COHN91], [FELT92] tools have also been reported recently. All these tools are still developing to reach maturity so that they can be used as the generic tools in an automatic as well as manual block generation step.

Other possible tools in this mixed signal design framework would be module generators of different analog functions. It will be very desirable if we would be able to come up with a general design methodology for automatic generation of all analog blocks without the need of implementing different module generators for different analog blocks. Unfortunately, as it has been discussed in the previous chapter, analog circuit design is the most knowledge intensive process of IC design tasks. The quality of a design will depend a lot on the expertise level of circuit designers. This expertise is usually obtained over a long period of time from the experience of doing numerous circuit designs. In order to implement a general analog design framework, we need to be able to capture and formalize the existing design knowledge entirely into the program database. This job is an extremely difficult if not impossible task to do.

The automatic generation of known analog block functions seems to be a more feasible goal to do since capturing and formalizing design knowledge of a specific analog function is simpler and easier to do. As the need to automatically generate other analog functions rise, their module generators can be implemented. In the next section, existing module generators of two commonly used analog functions: switched-capacitor filter (SCF) and operational amplifier (op-amp) will be described.

#### **Existing Analog Module Generators**

# 2.3 Existing Analog Module Generators

#### 2.3.1 Operational-Amplifier Module Generator.

The operational amplifier is one of the basic building block used in many analog functions. Many efforts in the automatic generation of this block have been reported OASYS [HARJ87], IDAC-ILAC [DEGR87], OPASYN [KOH90]. All the module generators start with a given set of specifications for the op-amp and generate the device sizes.

The OASYS system is implemented using an expert system that decomposes a given set of op-amp specifications into several sub-modules' specifications for input stages, output stages, or biasing circuits. These sub-specifications are then used to search for the most suitable pre-defined sub-modules such as current sources, differential pairs, or individual transistors. When the sub-modules are found and their specifications are met, an op-amp will then be constructed by joining all the chosen sub-modules. This op-amp will then be synthesized to get the op-amp specifications and its device sizes.

The IDAC-ILAC and OPASYN systems have similar implementation approach. Both systems generate device sizes of the pre-stored op-amp topologies by optimizing using the analytical equations. Since OPASYN will be used later as a low-level synthesis tool for generating op-amps and comparators in our ADC module generator, we will elaborate on it more.

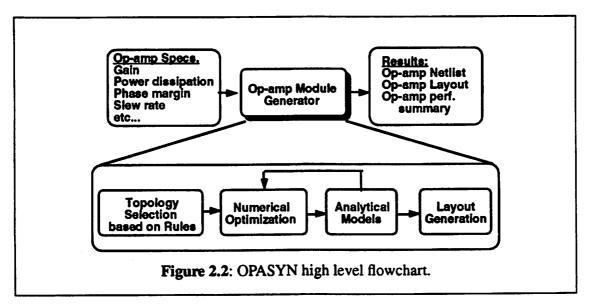

A typical set of input specifications for OPASYN would be open loop gain, power dissipation, unity gain frequency, phase margin, and slew rate. The outputs of the op-amp synthesis would be the op-amp netlist, layout, and performance summary. A simplified block diagram of the procedures used in OPASYN is shown in Figure 2.2. OPASYN first carries out a sequence of operations such as topology selection and numerical optimization to determine the device sizes. A netlist and performance summary will then be gener-

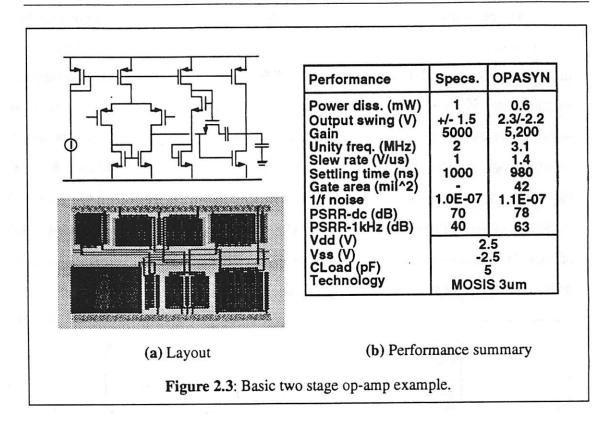

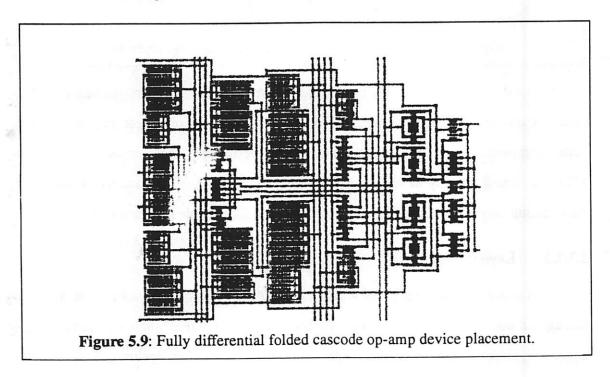

ated. The device sizes are then used to generate layout of the op-amp. Currently, the topology database of the netlist generator consists of an output buffer, a comparator, a single-ended basic two stage and a fully differential folded cascode op-amps. The layout generation takes the device sizes information generated by the circuit generator and outputs the complete layout of the block. Currently, the OPASYN layout generator does not support fully differential folded cascode op-amp layouts since specific routines for this op-amp topology need to be implemented. Efforts to enhance the layout generation capability of OPASYN are being done. As a result, the layout generator of OPASYN will not be used as a low level block layout generator in the ADC module generator, CADICS. The layout generation will be described in detail in Chapter 5. An example of a basic two-stage op-amp performance summary and layout are shown in Figure 2.3(a) and (b) respectively.

# 2.3.2 Switched-Capacitor Filter Module Generator

Filtering is one of the most common block used to precede or proceed a telecommunications or audio systems. For example, an anti-aliasing filter is usually used to filter

out of band signal in the front end of an A/D converter to prevent aliasing. A decimation filter is used to filter the out of band noise proceeding a sigma-delta modulator. One type of filter implementation is an analog sampled data system implemented in MOS technology commonly known as switched-capacitor filter (SCF). It is called SCF because the building block is a switched-capacitor integrator.

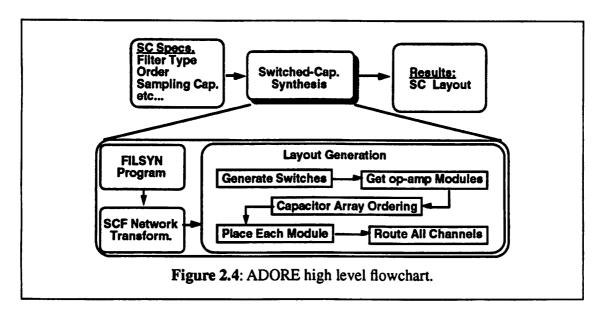

Many SCF synthesis programs [SANC85], [EATO87], [TRON87], [LUCA87], [YAGU86] have been reported in the literature. The popularity of SCF synthesis program is partially due to the fact that a straight-forward method or algorithm exists to synthesize an SCF from a given set of specifications. One of SCF module generators discussed here is ADORE [YAGU86] developed at U.C. Berkeley. ADORE is capable of generating switched-capacitor filter layout from a given set of specifications such as filter type, order, and frequency response.

## **Automatic Generation of Analog Blocks**

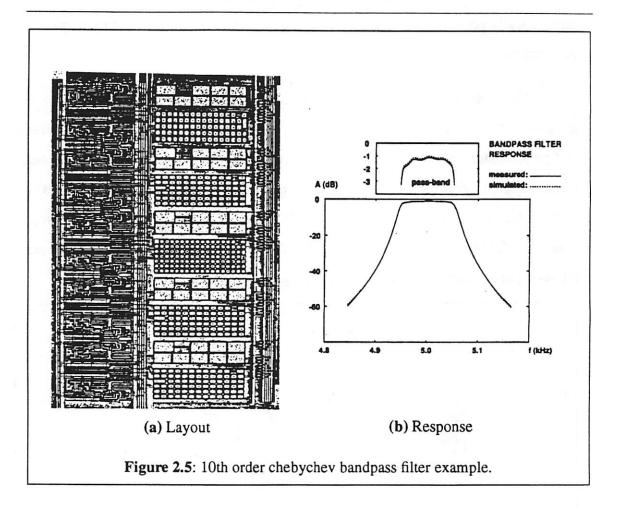

The overall steps of the module generation are as follows. Given a set of specifications of a filter, a continuous inductor-capacitor (LC) ladder filter is generated by using a filter synthesis program, FILSYN [SZEN77]. The resulting filter is then transformed into an equivalent SCF network. Capacitor ratio evaluation and dynamic range scaling maximization are carried out. The resulting netlist is then passed on to the layout generator to generate the complete layout of the SCF. The layout generator will undergo a series of operations such as generating switches, obtain op-amp module from the cell library, ordering capacitor array, placing all modules, and routing all channels. The high level flowchart of ADORE is shown in Figure 2.4. A 10<sup>th</sup> order Chebychev bandpass filter layout and frequency response are shown in Figure 2.5(a) and (b) respectively.

# 2.4 Analog-To-Digital Conversion Module Generator

## 2.4.1 Overall Goals

Analog to digital conversion function recurs frequently in mixed analog-digital chips with varying performance requirements depending on the applications [CHEC78], [TOWN80], [OHAR87]. Due to the non-existence of highly optimized ADC module generators, this analog block can become the bottleneck of the turn-around time for the overall design of the chips. Just like the op-amp and SCF module generators, we would like to

#### Automatic Generation of Analog Blocks

automatically generate A/D conversion block netlist and layout optimized to the given set of specifications.

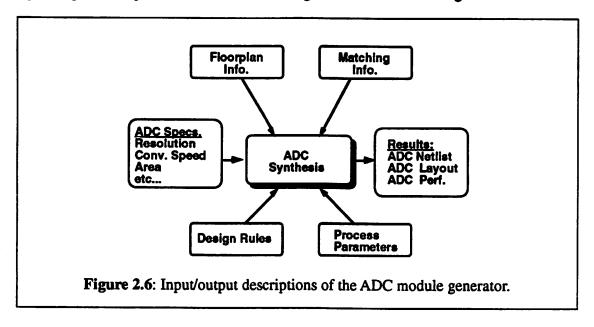

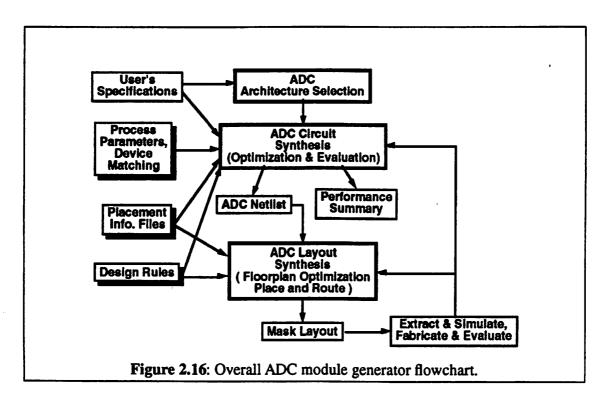

Therefore, it is very desirable to have an ADC module generator capable of generating A/D converters with a broad range of sampling rates and resolution, and silicon area and performance comparable with a manual approach. Moreover, the module generator has to be able to generate ADC's for different design rules. Finally, the resulting ADC has to be compatible with digital environment. We have developed a CMOS ADC module generator, CADICS [JUSU90] that fulfills all of the above requirements. The overall input/output descriptions of the ADC module generator is shown in Figure 2.6.

In the remainder of this chapter, a brief description of ADC function and characterization (mainly static ones) will be reviewed. Many terms defined here will be used throughout the remainder of this thesis. Finally, an overview of existing ADC module generators and our implementation methods will be discussed.

# 2.4.2 Functionality

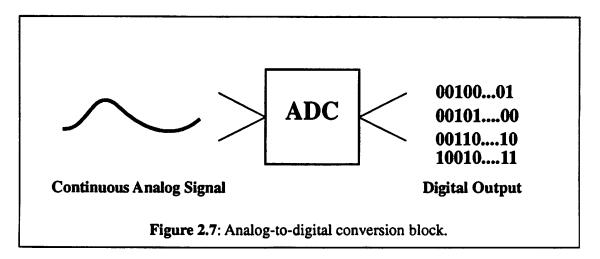

An N-bit 100kHz A/D converter is an electrical device which converts or encodes a continuous analog signal with a granularity of  $\frac{1}{2^N}$  into a digital representation with a finite number of binary bits, N as shown in Figure 2.7. The higher the number of bits, the more accurate the analog input signal can be represented. As the unit indicates 100 kHz specifies the rate at which the A/D converter performs the conversion. The most common performance specifications of an A/D converter are resolution, speed, linearity, and signal-to-noise ratio (SNR).

## 2.4.3 Characterization

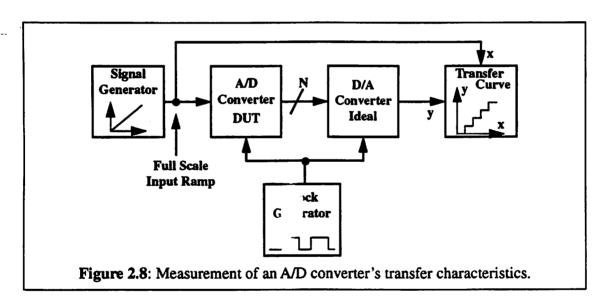

The evaluation of the performance of an A/D converter is very crucial both from the circuit design stand point as well as the requirements dictated by a particular application of the device. One of the most common tests an A/D converter undergoes is the measurement of its transfer characteristic with respect to a ramp input signal as shown in Figure 2.8 (i.e. analog voltage in - digital code out). For every analog input signal level, there exists a corresponding binary representation. Because of the finite number of bits.

there is a finite granularity in the digital approximation  $d_0, d_1, ..., d_{N-1}$  of the actual analog input signal  $V_{IN}$ .

$$V_{IN} = V_{FS} \left( \frac{d_0}{2^0} + \frac{d_1}{2^1} + \dots + \frac{d_{N-1}}{2^{N-1}} \right) + \varepsilon$$

(EQ 2.1)

Where  $V_{FS} = \text{full scale input signal} = \text{Max.} \|\pm V_{IN}\|$

$$d_i = i^{th} \text{ digit}$$

$\varepsilon$  = deviation of digital output from  $V_{IN}$

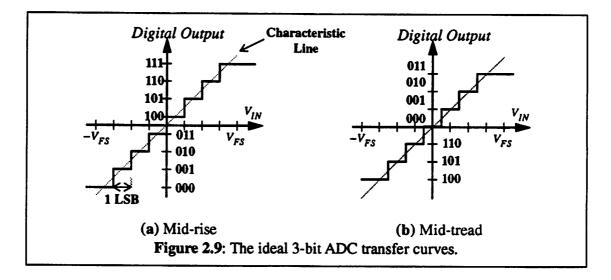

Quantization error is unavoidable when quantizing a continuous signal into a digital domain. The transfer curve shown in Figure 2.9(a) clearly shows each transition point of a continuous analog input signal corresponding to each digital output code change. The transfer curve looks like a stair case with steps at the analog transition points. This is due to the fact that digital output of a N-bit converter has a finite number of representations (2<sup>N</sup> distinct digital codes); whereas, the analog signal is continuous and hence has an infinite number of levels. Two possible *ideal* transfer curves of a simple 3-bit A/D converter

are shown in Figure 2.9.

The difference between the two depends on where the origin intersection is. The transfer curve shown in Figure 2.9(a) is referred to as *mid-rise* because the origin intersection occurs in the middle of a vertical transition between 2 different digital codes. On the other hand, the transfer curve shown in Figure 2.9(b) is referred to as *mid-tread* because it intersects the origin in the middle of the tread representing the digital code for zero volts input. Unlike a mid-rise case which has  $2^N$  digital output codes, a mid-tread case has only  $2^N - 1$  possible codes. The rest of the discussion will use the mid-rise transfer curve as an example.

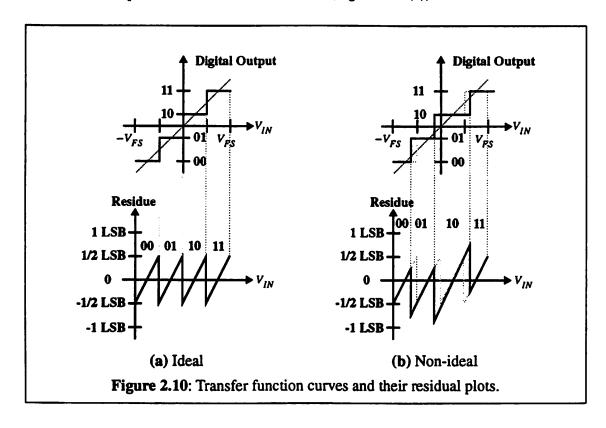

In reality the transfer curve is affected by many non-idealities contributed by non-ideal functional blocks. As a result, the transfer curve will have non-uniformly spaced steps as illustrated in Figure 2.10(b). Let 1 least significant bit (LSB) be the smallest quantization step for an N-bit conversion.

Let the input voltage range be between  $-V_{FS}$  and  $V_{FS}$ .

$$1 \text{ LSB} = \frac{2V_{FS}}{2^N} \tag{EQ 2.2}$$

Then the residual voltage can be written as

Residue =

$$\frac{(V_{IN} - V_{digital})}{1LSB}$$

(EQ 2.3)

$$V_{digital} = 2V_{FS} \left( \frac{d_0}{2} + \frac{d_1}{2^2} + \dots + \frac{d_{N-1}}{2^N} \right)$$

(EQ 2.4)

and plotted in Figure 2.10. Notice that the residual voltage for an ideal transfer curve fluctuates between  $\pm \frac{1}{2}$ LSB (Figure 2.10(a)); whereas, the non-ideal one fluctuates between  $\pm 1$ LSB for this particular transfer characteristic (Figure 2.10(b)).

## 2.4.3.1 Differential Non-Linearity (DNL)

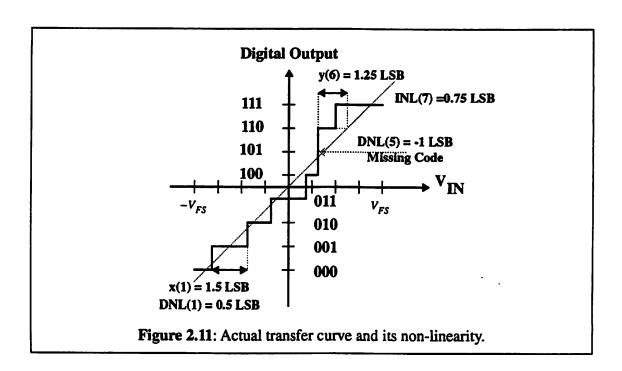

As mentioned earlier, the voltage difference between two consecutive transition voltages is the width of a quantization step. For an ideal transfer curve, the quantization steps are all equal to at least  $\pm \frac{1}{2}$ LSB or 1LSB in an absolute magnitude. For an actual transfer function curve as shown in Figure 2.11, the quantization steps are not uniform at all. As a measure of how much the actual quantization step width varies from the ideal step width of 1 LSB, differential non-linearity (DNL) is defined.

$$DNL(k) = x(k) - 1LSB (EQ 2.5)$$

Where k =the  $k^{th}$  digital code

$$k = 1, 2, \dots, 2^N - 1$$

x(k) = the actual step width of  $k^{th}$  digital code

DNL

$$(k) = 0$$

for  $k = 0$  and  $(2^{N}-1)$

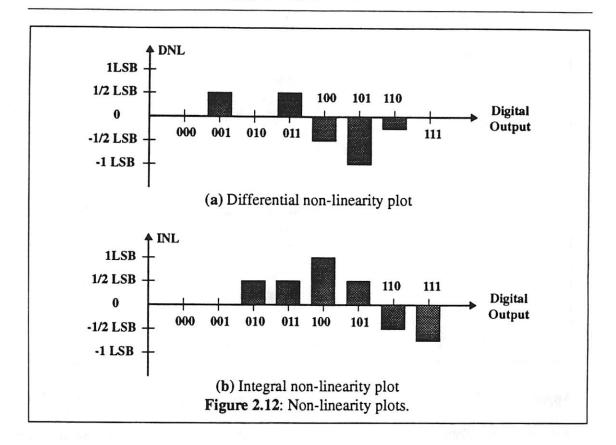

If x(k) is equal to zero, the corresponding DNL is going to be -1LSB. When this occurs, we have a *missing code*. Figure 2.11 shows that digital code 101 is skipped and therefore, it is *missing*. For illustration purposes, the DNL plot of transfer function curve shown in Figure 2.11 is shown in Figure 2.12(a).

## 2.4.3.2 Integral Non-Linearity (INL)

Integral non-linearity (INL) for each digital code is defined as the transition voltage between a code and the next code minus the input voltage corresponding to this code obtained from the characteristic line. It can be shown [LEWI87b] that

INL

$$(x) = \sum_{i=1}^{k-1} DNL(i)$$

(EQ 2.6)

Where

$$k = 1, 2, ..., 2^N - 1$$

$$INL(0) = 0$$

INL can also be defined as the deviation of the ideal intersection point on the characteristic line to the actual point, as shown in Figure 2.11.

INL

$$(k+1) \approx y(k) - \frac{1}{2}LSB$$

(EQ 2.7)

Where y(k) = the horizontal distance from the beginning

of code k to the ideal characteristic line

Figure 2.12(b) shows the INL plot of the respective DNL plot in Figure 2.12(a) according to EQ 2.6. The overall linearity of an A/D converter depends on the maximum absolute

Analog-To-Digital Conversion Module Generator

magnitude of DNL and INL.

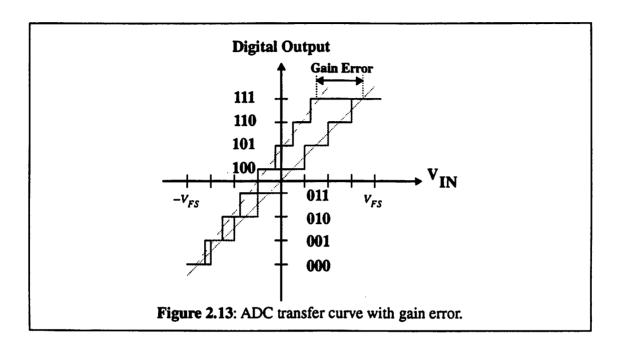

#### 2.4.3.3 Gain Error

Gain error occurs when a *gain* block in an A/D converter does not multiply the signal by the ideal value. This gain error will affect all the codes by the same percentage. As a result, the resulting digital code center line slope differs from the ideal one. If the gain is bigger/smaller than it is supposed to be, the slope is bigger/smaller than the ideal one as shown in Figure 2.13.

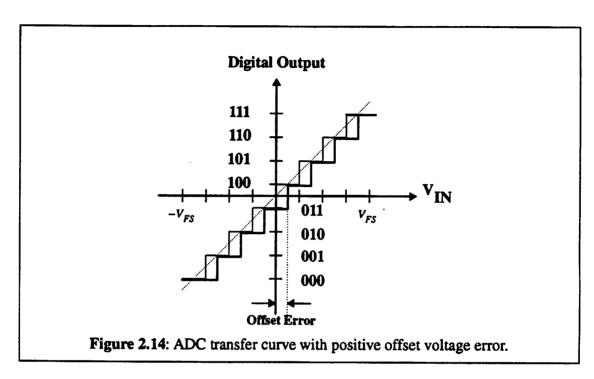

#### 2.4.3.4 Offset Error

Offset error can be viewed as having an additional input voltage source in the front of an A/D converter. A detailed explanation of this error will be described in Chapter 3 and

Appendix A. Thus, for an input voltage  $V_{IN}$ , the converter will treat it as if  $V_{IN} + V_{offset}$  were its input. Thus plotting the transfer curve with respect to the actual input voltage  $V_{IN}$ , the entire curve gets shifted to the right or left (depending on the sign of the offset voltage) by the exact amount of the magnitude of the offset. As an illustration, Figure 2.14 shows the effect of a positive offset on the transfer curve shown in Figure 2.9(a). Notice that the linearity and monotonicity of the A/D converter are not affected by the offset.

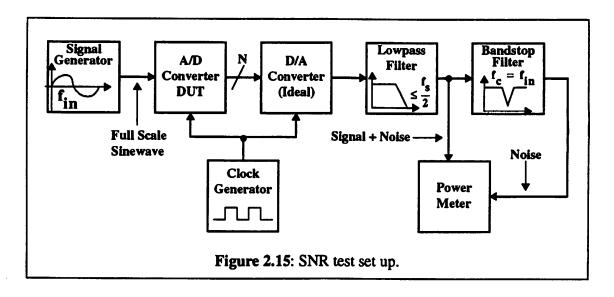

#### 2.4.4 Signal-To-Noise Ratio

Signal-to-noise ratio (SNR) falls into the dynamic characterization category. It is an important measurement for communication system performance, even though it is not always the most accurate standard for performance comparison between two systems. A typical SNR test configuration is shown in Figure 2.15. The SNR is the ratio of the mean square peak-to-peak amplitude of a sinusoidal input signal to the smallest quantization step width. If the full scale peak-to-peak amplitude is  $2V_{FS}$  then the theoretical limit of

maximum SNR for ideal A/D converter with zero DNL and INL can be found by the following equations [RABI76]:

$$Max SNR = \left[ \frac{\frac{V_{FS}^2}{2}}{\frac{(1LSB)^2}{12}} \right]$$

(EQ 2.8)

Max SNR =

$$1.5(2^{2N})$$

(EQ 2.9)

Or in a simplified form:

Max SNR =

$$6.02N + 1.76dB$$

(EQ 2.10)

#### 2.4.5 Previous Work

# 2.4.5.1 Analog Cell Library

In many mixed-signal chips today, standard off-the-shelf analog cells are often used in order to provide the analog functions needed. Unfortunately, these pre-designed, hard-coded cells do not offer flexibility of requirements and technological evolution. Cell libraries are usually optimized to a specific performance for a particular technology. As the technology feature size and process parameters change, these cells have to be regenerated again. To redesign the entire analog cell libraries will be very hard, tedious, error-prone, time consuming, and last but not least, it will require expert analog designers.

# 2.4.5.2 Performance-Driven Based on Standard Cells

The idea of analog-to-digital conversion module generation is not new. Allen and Barton [ALLE86] introduced a silicon compiler for successive approximation (SA) A/D and D/A converters. The basic approach of the program is a generalization of *standard cell* approaches as in digital block design automation by incorporating a family of analog standard cells. The program takes a set of input specifications such as type of block (ADC or

#### Analog-To-Digital Conversion Module Generator

DAC), number of bits, maximum tolerable differential non-linearity (DNL), and maximum tolerable integral non-linearity (INL). It then goes through a topological selection algorithm by first calculating non-linearity of each converter topology and then selecting what combination of resistors and capacitors is best to realize the input specifications while minimizing the passive component area. The non-linearity equations assume a worst case design. If the specifications cannot be met, it will give the user the best linearity available. If there exists a topology that meets the specifications, a layout will be generated. The layout procedure is based on digital placement and routing methods which uses fixed height of standard cells as well as parameterized cells into a predefined structure.

An analog silicon compiler was developed as a part of the CONCORDE system [HELM87]. The compiler is capable of generating successive approximation and serial A/D converters. The basic approach of this compiler is to use *pre-designed analog blocks* such as op-amps and comparators. No effort was made to optimize performance of the resulting A/D converters since no optimization was carried out. The layout procedure used many digital tools as such the SSTAR<sup>tm</sup> state machine compiler to generate the control logic. Special routines were developed to size the capacitor arrays and switches.

The two A/D conversion module generators described above have similarity in that they were implemented using *standard cell* approach. ADC module generators based on this approach will also have a limited range of sampling rate and resolution. Furthermore, area and power cannot be optimized with respect to the given specifications. As a result, the A/D converters generated will not be competitive with manual design. In other words, a performance-driven module generator based on based standard cells is directed toward reducing design cycle at the expense of area and performance.

#### 2.4.6 Methods of Attack

Unlike digital circuits, analog circuits in general require more design freedom in order to be applied effectively. They often exploit the full spectrum of capabilities exhibited by individual devices. In an analog circuit, the individual devices often have different sizes and electrical characteristics. These devices require optimization of different performance requirements. The importance of each performance requirement will depend on circuit applications.

For this reason alone, a performance-driven module generator based on design rules and spice parameters is a better approach. This type of module generators can be implemented using an expert system approach or a parameterized schematic of known architecture approach. Examples of expert system implementation for simple analog blocks such as operational amplifiers (op-amps) and comparators have been presented in earlier sections. Unfortunately, A/D converter is a much more complex function then opamps or comparators. There is no clear way as how to set the rules for this implementation so that the resulting A/D converters are of any use at all.

A parameterized schematic of known architecture implementation, on the other hand, is a better approach because it can generate highly-effective circuits based on known architectures for complex analog functions in a flexible environment by optimizing the device sizes with respect to various performance measures. [KOH90] and [DEGR87] have demonstrated the implementation of op-amps and other simple blocks.

Unlike switched-capacitor filter synthesis [YAGU86], [LUCA87], ADC synthesis does not have a well-defined procedure. The module generation of A/D conversion functions is a particularly difficult problem because of the wide spectrum of resolutions and sampling rates encountered in real applications, the trade-off between area versus power dissipation, and component matching requirements for different A/D conversion architec-

#### Summary

tures. Our approach for the module generation of A/D converters is to focus on *techniques* that allow design of circuits with efficiency comparable to the ones manually designed by skilled designers.

Because of the wide range of parameter spreads in analog integrated circuits, analog designers over the years have developed circuits which cancel out the first order variations in key parameters. This means, however that the analog circuits then become sensitive functions of second order variations of such parameters, for example the capacitor ratio matching in a gain of two block. We use many analog circuit design techniques (such as auto-zeroing circuits [DEGR85], capacitor trimming array [OHAR87], fully differential architecture, or even specifically designed 2-comparator scheme [JUSU90b]) to further reduce or overcome these second order effects so that the module generation procedures can be *simplified*.

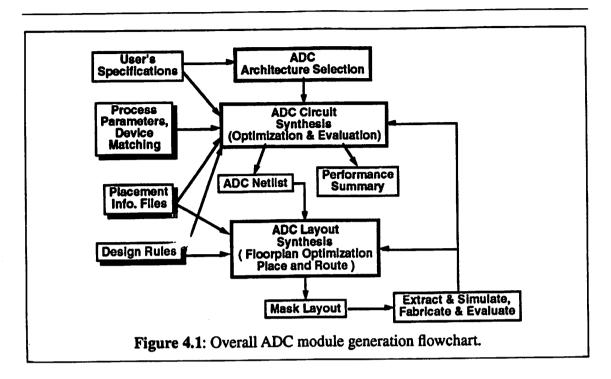

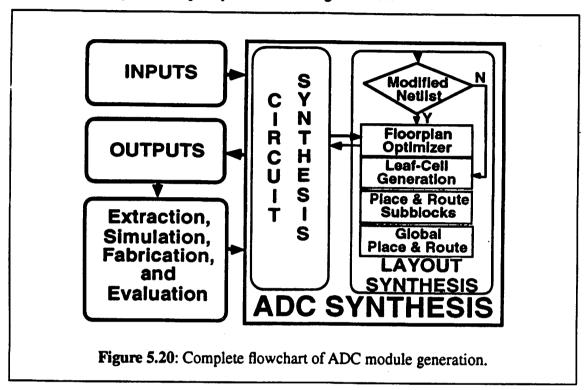

The overall implementation flowchart of our A/D conversion module generator is shown in Figure 2.15. The module generation will be divided into three major tasks: architecture selection, netlist generation, and layout generation. The flowchart shows other supporting inputs needed to carry out the job. Details explanation will be presented in Chapter 3, 4, and 5 of this thesis.

# 2.5 Summary

In summary, analog block generation is the bottleneck of the turn around time of mixed signal chips. While analog standard cell libraries will give short term solution, they do not offer flexibility to the change in technology feature size. On the other hand, performance-driven analog block module generator based on design rules and spice parameters will provide a long term solution. Since ADC functions are the most common analog

blocks in mixed signal chips, we chose to study the implementation of ADC module generator.

# CHAPTER 3 ADC Architectures Suitable for Automatic Compilation

# 3.1 Introduction

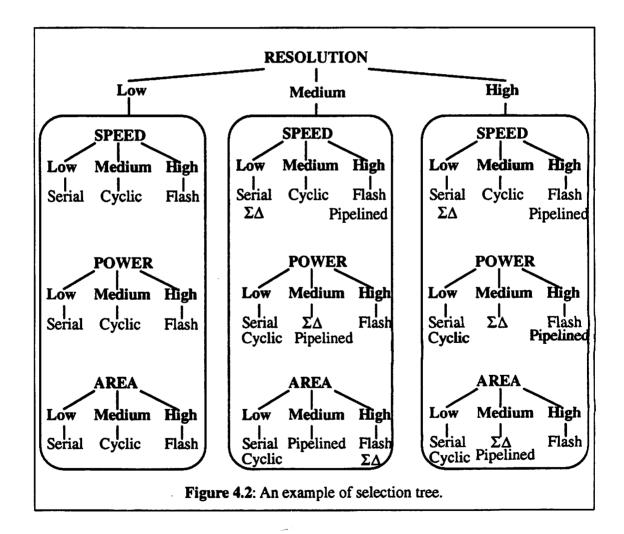

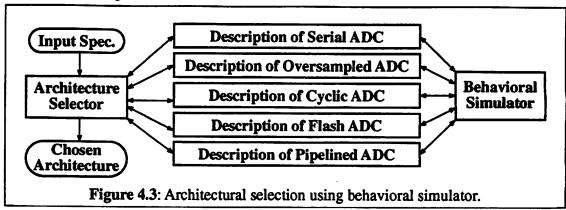

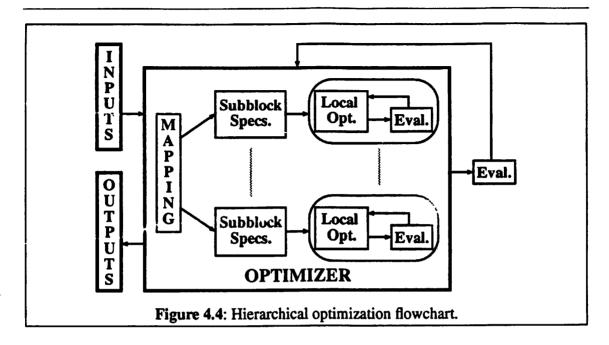

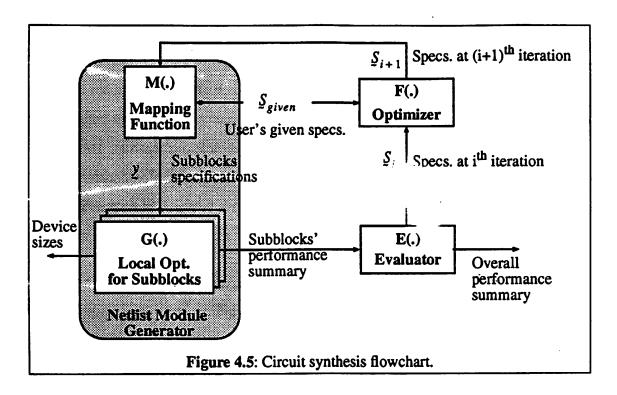

For A/D conversion functions, the realm of required performance maps into four distinct classes of realizations spanning the conversion rate spectrum (integrating, oversampling, successive approximation, and flash/pipeline architectures) and two distinct regions of accuracy or linearity (less than 10 bits and greater than 10 bits). Each of these requires a different implementation in order to be reasonably competitive with hand-crafted designs in terms of power dissipation and silicon area. Therefore, if not carefully planned, the generation of A/D conversion module generators will require the generation of an extremely large number of such module generators.

In the next section, five different ADC architectures (serial, successive approximation, flash, pipelined, and oversampling) will be briefly discussed. We will then point out the desired properties of ADC architecture from the module generation point of view. Finally, we will present an improved algorithmic A/D converter specifically designed to be implemented into our ADC module generator.

# 3.2 A/D Conversion Architectures

# 3.2.1 Serial A/D Conversion Technique

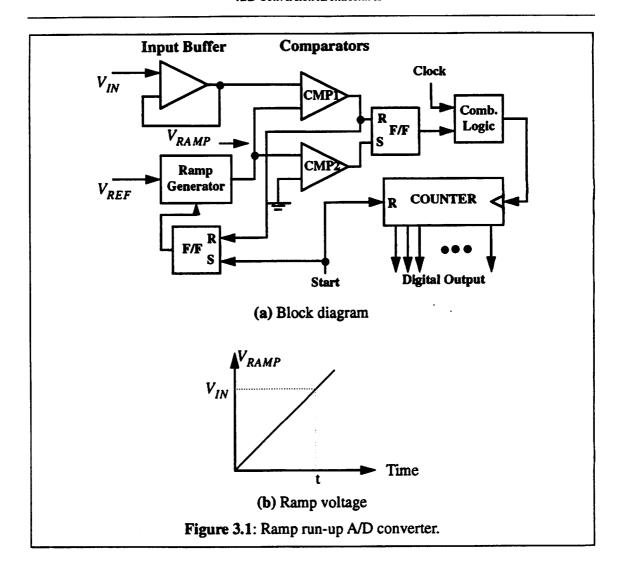

The serial A/D conversion technique has been used for many years. There are many different implementations of this technique such as dual slope, quad slope, charge balancing, voltage-frequency conversion, and others. Just to illustrate the idea, a ramp run-up implementation is shown in Figure 3.1. The basic operation of this implementation is as followed. When the *start* signal is high indicating the start of conversion, the ramp generator will start generating a ramp voltage  $V_{RAMP}$ .  $V_{RAMP}$  is then being compared to the input voltage,  $V_{IN}$  and the ground using two comparators: CMP1 and CMP2. As long as  $V_{RAMP}$  is larger than  $V_{IN}$  the counter will keep on incrementing its value. When  $V_{RAMP}$  is equal to or a little larger than  $V_{IN}$  at time t, the counter will stop incrementing and the ramp generator will stop ramping. The content of the counter will then be the digital representation of the analog input voltage.

The advantages of serial A/D conversion technique are that the implementation is very simple, the results an inherently monotonic, and linearity is independent of component matching. Unfortunately, this technique is very slow. As the number of resolution increases, the number of clock cycles per conversion increases exponentially as  $2^N$ , where N is the number of bits desired. As a result, this technique is usually used in low frequency (10 to 100 Hz) applications such as general purpose digital volt meters (DMV's) and very low cost instruments.

#### 3.2.2 Successive Approximation A/D Conversion Technique

The successive approximation (SA) A/D conversion technique is one of the most commonly used technique to implement A/D converters often used to interface analog sig-

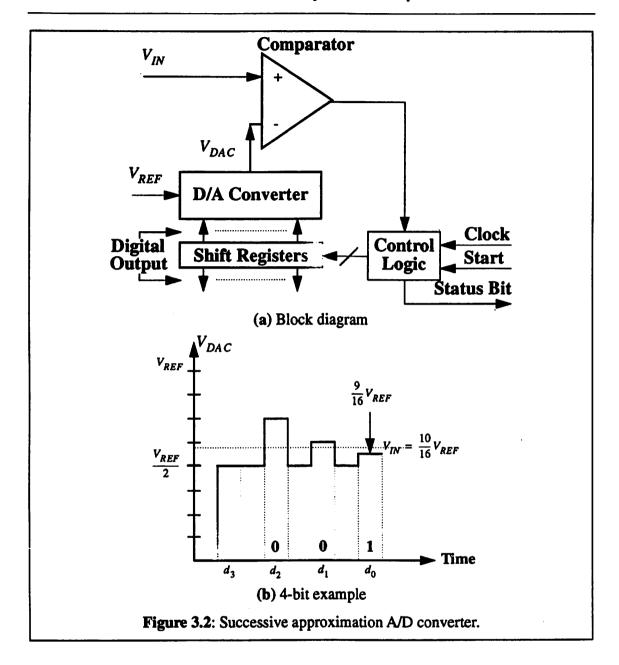

nals at voiceband and above with computer peripherals such as modems. The basic operation is to do binary search through 2<sup>N</sup> voltage levels by using a precision digital to analog converter (DAC). A simple SA A/D converter consists several basic building blocks (Figure 3.2(a)) such as comparator, digital to analog converter (DAC), control logic, and shift registers for the output codes.

At the start of a conversion, all the registers will be clear and the output of the DAC will have zero voltage. At the first cycle, the most significant bit will be determined

first by comparing the input voltage  $V_{IN}$  to  $V_{DAC}$ . If  $V_{IN}$  is larger than  $V_{DAC}$  then the comparator output will output a "1" or else "0". The output of the comparator is then fed into the control logic to determine if the digital output is zero or one. This digital output gets stored into the shift register which generates the digital code needed for the DAC to

#### A/D Conversion Architectures

do the binary search. At every iteration, 1 bit of digital code is obtained. Thus the operation is repeated N times to get N bits. Figure 3.2(b) illustrates what the DAC output level during the conversion for a 4-bit example.

This type of converter can give fairly high resolution and moderate conversion speed (10-100 kHz) since the conversion time is fixed and linearly increases as a the resolution requirement increases. Moreover, the speed is independent of input voltage and previous result. In the example above, we are assuming that the input voltage  $V_{IN}$  varies very slowly and noise disturbance is low to cause significant error in the conversion. If this is not true, then a sample and hold function is needed to sample and hold the input voltage until the conversion is completed.

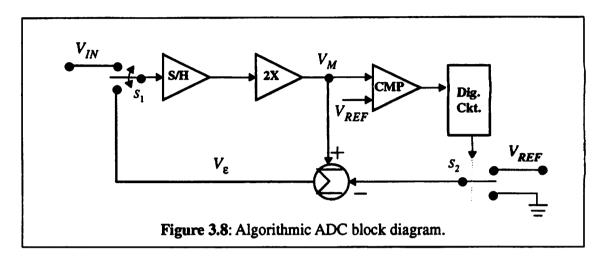

As mentioned above, the advantages of this particular A/D conversion technique are that it converts in N clock period where N is the number of desired bits and its building block is very simple. Unfortunately, the accuracy, linearity, and speed are affected by the DAC,  $V_{REF}$ , and comparator. For N-bit resolution, the DAC requires component to match to  $\frac{1}{2^N}$  and the comparator offset voltage cannot exceed  $\frac{V_{REF}}{2^{N+1}}$  for  $\frac{1}{2}$  LSB linearity. Examples of this technique are the traditional DAC-based [MCCR75] and algorithmic [OHAR87] A/D converters.

# 3.2.3 Parallel A/D Conversion Technique

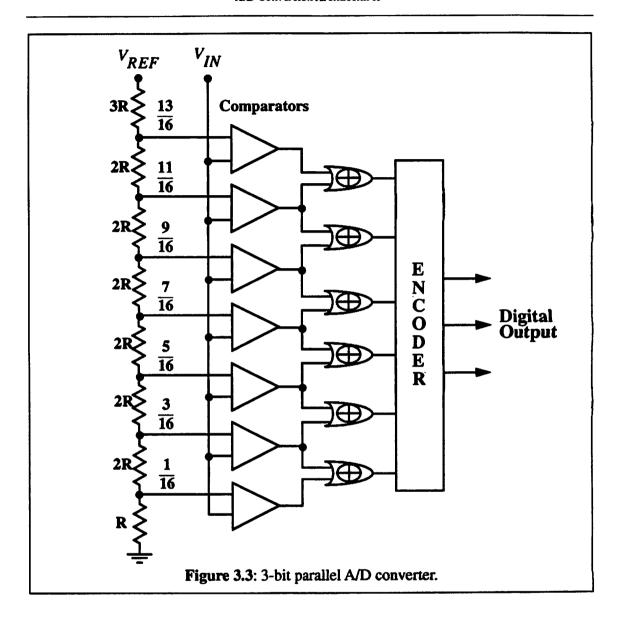

The parallel A/D converter, commonly known as flash A/D converter, is capable of converting in the shortest among different A/D conversion techniques. This type of converters is used mainly in video and radar processing with low resolution (up to 9 bits) and very high speed (10 MHz - 4 GHz). Figure 3.3 shows a 3-bit flash ADC block diagram with a resistive-DAC. The basic operation is as follows. An input voltage  $V_{IN}$  will be

compared to a bank of comparators that are tapped to a resistive-DAC for their threshold voltages. For a 3-bit resolution, usually it needs approximately  $2^3 - 1$  comparators as shown in Figure 3.3. The outputs of the comparators are then got encoded to get 3 bit digital output codes.

The obvious advantage of this approach is that no clock is needed to do the conversion and the conversion speed is limited by how fast can the comparators and digital circuitry switch. Uncertunately, this type of implementation is very costly. As the number of resolution increases the hardware requirement and area increases exponentially. For example for a 9-bit A/D converter will need  $2^9 - 1$  comparators with offset voltage of less than  $\frac{V_{REF}}{2^{10}}$  and resistor string to match to 0.1%. Over the years different implementations have been proposed to reduce the area penalty of this type of converter such as two-step flash [DOER88] and pipelining several stages of fewer bit of flash converter to obtain the desired resolution [LEW187].

# 3.2.4 Pipelined version Technique

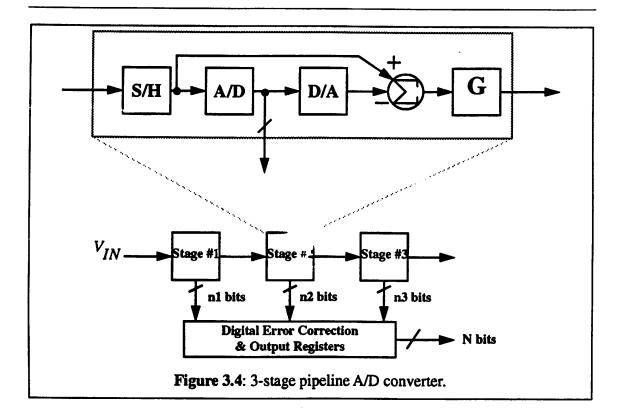

The pipelined A/D conversion technique employs multi stages of A/D converter block to do the conversion concurrently. Each stage consists of a sample and hold block (S/H), an A/D converter, DAC, summer ( $\sum$ ), and a gain block (G) as shown in Figure 3.4. The input voltage  $V_{IN}$  is sampled onto the S/H and is held while the first stage is doing the conversion of nI bit digital output. The resulting digital output is then passed onto the DAC to generate a quantized voltage of the input signal which will be subtracted from the held input signal. The residual is then amplified and passed on to the next stage. While the next stage is converting this residual voltage, the first stage is sampling a new input voltage. The resulting digital output from all stages will be accumulated and passed

out together. Therefore, each conversion can be done within one clock period. As a result, the conversion speed is much faster than the SA and serial A/D conversion techniques and almost as fast as the flash A/D conversion technique.

The big advantage of pipelining is that much less hardware is needed to achieve the same throughput as flash. This is true when the number of bit is greater than 6 bit or else the overhead cost of doing pipeline stages is not worthy. Another advantage is that

digital correction and self-calibration can be applied so that high precision comparators are not required. It turns out that depending on the number of bits desired, there is an optimum number of bits per stage [LEWI87b]. The major disadvantage is that it requires fairly fast analog inter-stage proces— and a sample and hold function to hold the analog signal.

# 3.2.5 Oversampled A/D Conversion Technique

Unlike the A/D conversion techniques described earlier, oversampled A/D converters operate at non-Nyquist sampling rate (i.e. sampling at well above the Nyquist rate). The ratio of the sampling frequency to the Nyquist rate is commonly called *oversampling ratio*. The basic idea of this technique is to quantize an analog signal coarsely at a sampling rate much higher than the Nyquist rate of the signal. A filter in a feedback configuration is arranged to spread out the quantization noise in the entire frequency band. The

#### A/D Conversion Architectures

resulting coarse digital output is then passed through a digital processing block (decimation filter) to obtain more accurate digital representation of the given analog signal and therefore, filtering the out of band quantization noise.

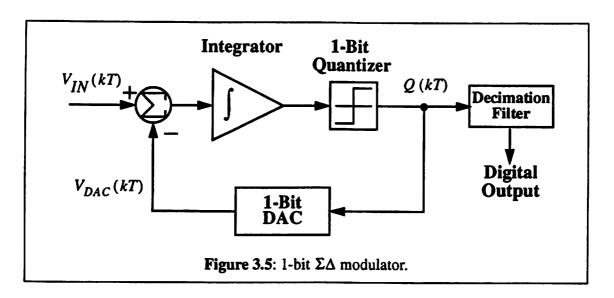

One implementation of oversampled A/D converter is a 1-bit sigma-delta modulator shown in Figure 3.5. It consists of a summer, an integrator, a 1-bit quantizer, and a 1-bit D/A converter in a feedback loop and a decimation filter. The input voltage  $V_{IN}(kT)$  is subtracted by the quantized analog voltage  $V_{DAC}(kT)$  and then integrated by the integrator. The integrated difference is then quantized by a comparator to give a logic "1" or "0". This digital output is then fed back into the DAC to generate the new DAC voltage. If the DAC is an ideal DAC, the error at the input to the integrator would be equal to the quantization error. Since the modulator is running at a much higher frequency than the Nyquist rate, the quantization error will depend on the oversampling ratio. Thus, the resolution of oversampled A/D converter will depend on the oversampling ratio. For example, sampling at two times the Nyquist rate will increase the SNR by 3 dB which translates roughly to an increase of  $\frac{1}{2}$  LSB in overall accuracy [CAND81]. The final digital output can be obtained by feeding the digital output of the 1-bit quantizer into a decimation filter.

The big advantage of this approach is that component matching can be relaxed while maintaining linearity since a simple comparator can be used as the quantizer. The anti-aliasing filter needed at the front-end of the modulator can be implemented much cheaper since the transition band of the filter can be much wider than the one for Nyquist rate A/D converters. Furthermore, the majority of the building blocks can be implemented digitally so that integrating both the converter and the digital signal processing on to a single chip is very easy and cheap in CMOS technology.

Unfortunately, this technique has a lower throughput and consumes more area (due

to extra digital processing block) than the successive approximation (SA) approach. As the conversion speed is getting faster, the sampling clock requirement becomes extremely high making it difficult to generate. There have been a great interest from the academics as well as commercial laboratories to produce high resolution A/D converters using this particular technique. Effort to improve the quantization noise reduction in the baseband in order to minimize oversampling ratio has led to using higher order modulators such as  $2^{nd}$  [CAND85],  $3^{rd}$  [MATS87],  $4^{th}$  [OPTE91], or even  $5^{th}$  order  $\Sigma\Delta$  modulators. As technology feature size scales down, these higher order implementations become more economical due to higher density bringing this type of converter performance approaches those of SA.

# 3.3 Architecture Comparison

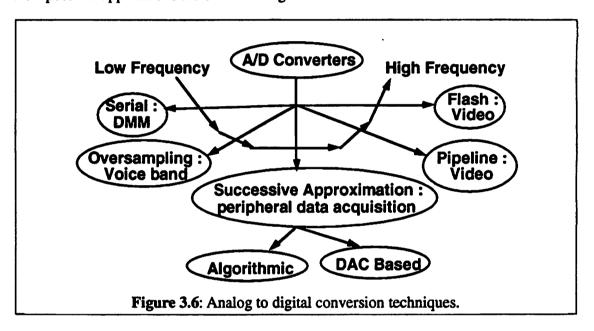

The five A/D conversion techniques can be summarized as follows. For a low frequency spectrum, the serial technique is very suitable. This technique is usually used for very low speed applications such as the digital multimeter (DMM). For low to mid fre-

quency range, A/D converters are usually implemented using oversampled or successive approximation techniques. These types of A/D converters are usually used for voiceband and peripheral data acquisition products. At the very high frequency range, two techniques: pipeline and flash are commonly used. These types of A/D converters are very suitable for video application products. The summary of different ADC techniques and their possible applications are shown in Figure 3.6.

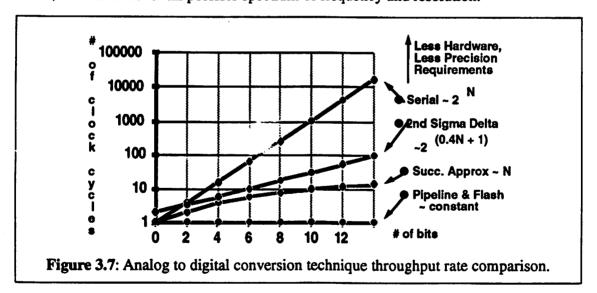

The requirements of each technique are different in that each one has its own advantages over the other. For example, if we compare the number of bits versus the number of clock cycles needed to do the conversion, the serial A/D conversion technique requires the most number of clock cycles as the resolution increases. The number of clock cycles needed increases exponentially with exponential constant of N where N is the number of bits. For a second order sigma delta modulator, the number of clock cycles per conversion can be approximated to be  $2^{(0.4N+1)}$ . For successive approximation technique, the number of clock cycles needed grows linearly as the number of resolution increases.

Finally, for pipelined and flash techniques, the number of clock cycles stays constant independent of the number of resolution. Figure 3.7 compares the number of clock cycles needed versus the number of resolution for the five A/D conversion techniques.

Referring back to Figure 3.7, the pipelined and flash A/D conversion techniques are capable of the fastest conversion and the serial one is the slowest. However, there is trade-off among these techniques, in that the pipelined and flash techniques require high precision and more hardware requirements than to successive approximation technique. As we move from the both of the chart, the serial technique requires the least hardware and the least precision requirements; whereas, the flash technique requires the most hardware and the highest precision of them all. In other words, all the techniques mentioned above complement each other. Therefore, in order to make a complete ADC module generator, one has to cover all possible spectrum of frequency and resolution.

#### **Desired Properties**

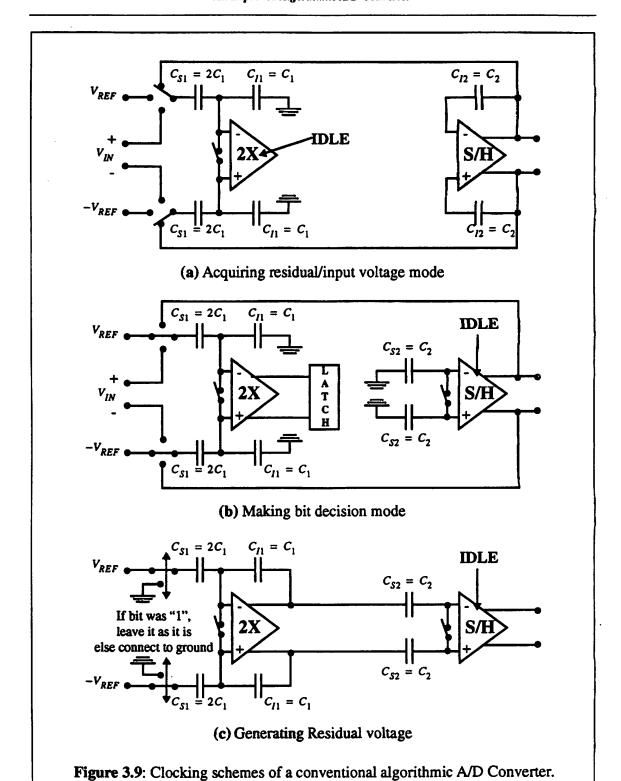

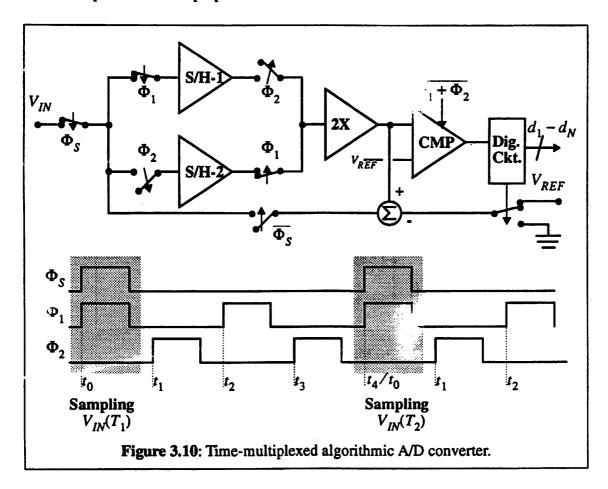

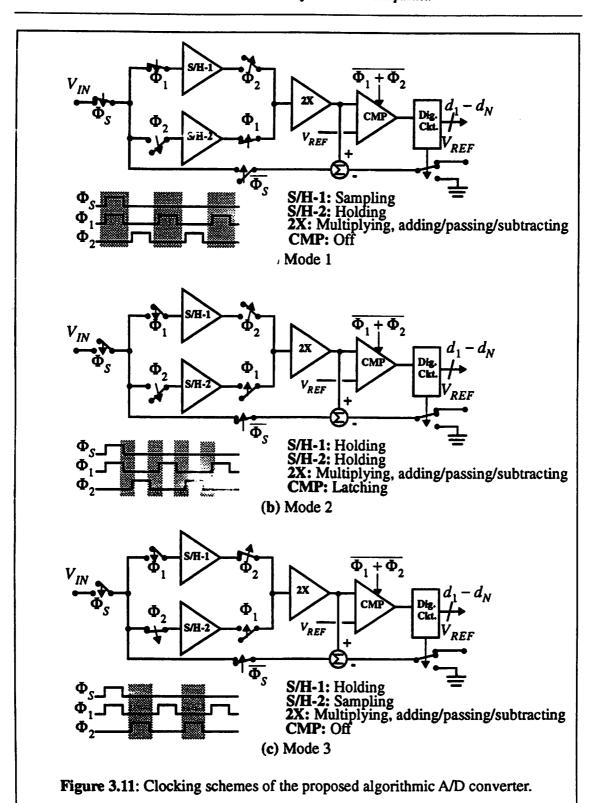

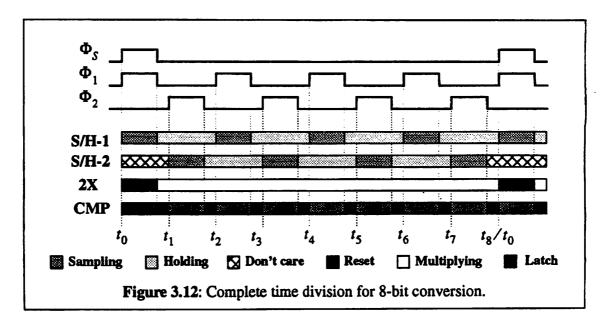

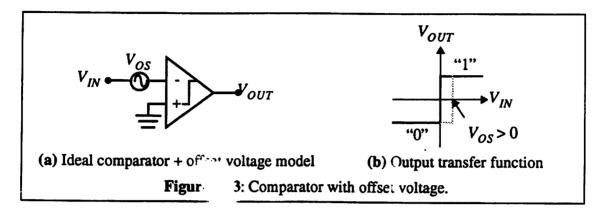

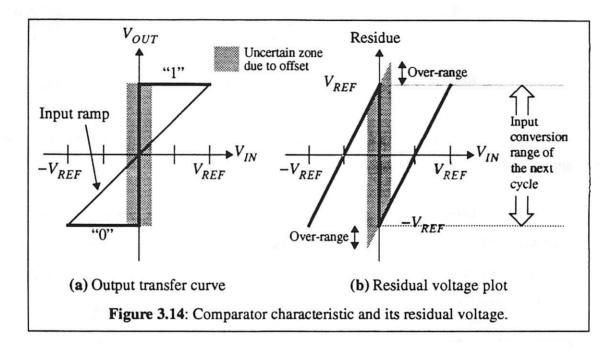

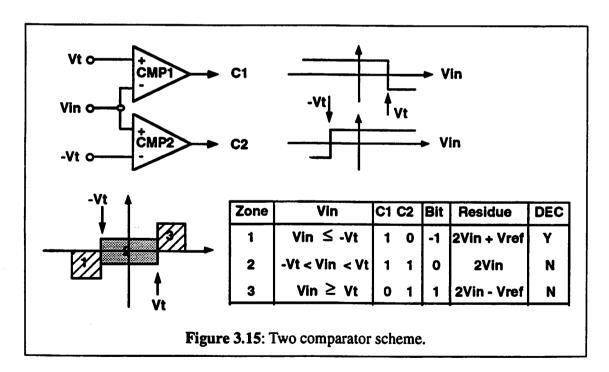

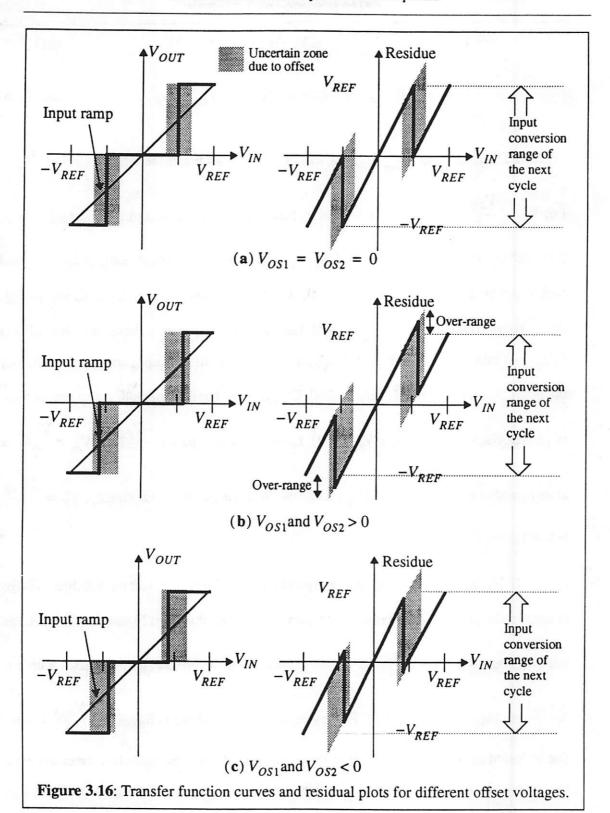

# 3.4 Desired Properties