## Copyright © 1995, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# CONSTRAINT-DRIVEN ANALYSIS AND SYNTHESIS OF HIGH-PERFORMANCE ANALOG IC LAYOUT

by

Edoardo Charbon

Memorandum No. UCB/ERL M95/115

19 December 1995

# CONSTRAINT-DRIVEN ANALYSIS AND SYNTHESIS OF HIGH-PERFORMANCE ANALOG IC LAYOUT

Copyright © 1995

by

Edoardo Charbon

Memorandum No. UCB/ERL M95/115

19 December 1995

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### Abstract

Constraint-Driven Analysis and Synthesis of High-Performance Analog IC Layout

by

# Edoardo Charbon Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California at Berkeley

Professor Alberto Sangiovanni-Vincentelli, Chair

Performance in analog circuits is often critically linked to the physical implementation and the technology used for fabrication. While for digital circuits several synthesis techniques have been proposed and are of common use, in the analog domain, most of the high performing systems and chips are designed largely by hand.

In this prospective we have proposed a methodology for the semi-automated synthesis of full-custom analog IC layout at medium to high frequencies. The methodology guarantees that all performance constraints be met when feasible, otherwise infeasibility is detected as soon as possible, thus providing a robust and efficient design environment. In the proposed approach, performance specifications are translated into lower-level bounds on parasitics or geometric parameters, using sensitivity analysis. Bounds can be used by a set of specialized layout tools performing stack generation, placement, routing, compaction and extraction. For each tool, a detailed description is provided of its functionality, of the way constraints are mapped and enforced, and of its impact on the design flow.

A major advantage of the methodology is the reduction of time-consuming redesign loops often needed in purely bottom-up approaches, provided that accurate models for all relevant parasitics are available. For this reason, a wide variety of compact and highly sophisticated parasitic models has been generated to cover a sufficiently wide frequency spectrum. The effects of currents generated by high-speed digital switching circuits and the mechanisms governing noise injection have also been modeled and used to drive the design towards viable solutions.

A considerable number of examples drawn from industrial applications has been generated and fabricated in various technologies to illustrate the effectiveness of the approach.

Professor Alberto Sangiovann)-Vincentelli Dissertation Committee Chair

### **Contents**

| Lis | st of | Figure | es                                                  | x  |

|-----|-------|--------|-----------------------------------------------------|----|

| Lis | st of | Tables | i                                                   | xv |

| 1   | Intr  | oducti | on                                                  | 1  |

|     | 1.1   | Compu  | uter-Aided Design of Engineering Systems            | 1  |

|     | 1.2   | Physic | al Assembly of Analog and Mixed-Signal ICs          | 2  |

|     | 1.3   | Botton | n-Up vs. Top-Down Approaches                        | 3  |

|     | 1.4   | Genera | alized Constraint-Driven Layout Design              | 4  |

|     | 1.5   | Theore | etical Aspects of Constraint-Based Approaches       | 6  |

|     | 1.6   | Organi | ization of the Dissertation                         | 7  |

| 2   | Lite  | rature | Survey                                              | 8  |

|     | 2.1   | The O  | rigins of Computer-Aided-Design                     | 8  |

|     |       | 2.1.1  | Circuit Simulation                                  | 8  |

|     |       | 2.1.2  | Digital Timing Analysis and Event-Driven Simulation | 9  |

|     |       | 2.1.3  | Circuit Optimization                                | 10 |

|     | 2.2   | Early  | Work in Computer-Aided-Design for Analog ICs        | 11 |

|     |       | 2.2.1  | Silicon Compilation                                 | 11 |

|     |       | 2.2.2  | Knowledge-Based Techniques                          | 11 |

|     |       | 2.2.3  | Algorithmic Methodologies                           | 12 |

|     | 2.3   | The F  | irst Complete Design Systems                        | 12 |

|     |       | 2.3.1  | IDAC/ILAC                                           | 12 |

|     |       | 2.3.2  | OPASYN                                              | 13 |

|     |       | 2.3.3  | OASYS/ACACIA                                        | 14 |

|     | 2.4   | Evolut | tion of Approaches                                  | 15 |

|     |       | 2.4.1  | Silicon Compilation and Module Generation           | 15 |

|     |       | 2.4.2  | Knowledge-Based Systems                             | 16 |

|     |       | 2.4.3  | Hybrid and Human-Driven Systems                     | 17 |

|     | 2.5   | Const  | raint-Based Approaches                              | 19 |

|     |       | 2.5.1  | Foundations                                         | 19 |

|     |       | 2.5.2  | First Constraint-Driven Design Tools                | 19 |

|     |       | 252    | Later Implementations                               | 10 |

| 3 | Gen  | eralize | ed Constraint Generation                                  | 21        |

|---|------|---------|-----------------------------------------------------------|-----------|

|   | 3.1  | Proble  | m Formulation                                             | 22        |

|   | 3.2  | Mappi   | ng Specifications onto Layout Constraints                 | 23        |

|   | 3.3  | Metho   | ds for the Evaluation of Sensitivities                    | <b>25</b> |

|   | 3.4  | Constr  | raint Generation Engine                                   | 26        |

|   |      | 3.4.1   | Absolute Parasitic Constraints                            | 26        |

|   |      | 3.4.2   | Constraints on Mismatch                                   | 27        |

|   |      | 3.4.3   | Device and Interconnect Symmetry                          | 31        |

|   | 3.5  | Const   | raint Generation: A Case Study                            | 36        |

| 4 | Plac | cement  | <b>t</b>                                                  | 40        |

|   | 4.1  | Evolut  | tion from the Digital to the Analog Domain                | 41        |

|   |      | 4.1.1   | Placement Problem Formulation                             | 41        |

|   |      | 4.1.2   | Constructive or Schematic-Driven Techniques               | 43        |

|   |      | 4.1.3   | Branch-and-Bound Search and Partitioning-Based Techniques | 44        |

|   |      | 4.1.4   | Quadratic Optimization-Based Techniques                   | 45        |

|   |      | 4.1.5   | Iterative Improvement Techniques                          | 46        |

|   | 4.2  | Simula  | ated Annealing and Analog Placement                       | 48        |

|   |      | 4.2.1   | Terminology                                               | 48        |

|   |      | 4.2.2   | Characterizing Analog Constraints                         | 50        |

|   |      | 4.2.3   | Slicing-Tree vs. Flat Representation of the Workspace     | 53        |

|   | 4.3  | Modif   | ying Basic Algorithms                                     | 54        |

|   |      | 4.3.1   | Standard Features                                         | 54        |

|   |      | 4.3.2   | Modifications of the Standard Features                    | 59        |

|   |      | 4.3.3   | Configuration Space                                       | 60        |

|   |      | 4.3.4   | Cost Function                                             | 62        |

|   |      | 4.3.5   | Move-Set                                                  | 65        |

|   | 4.4  | Modul   | le Generation                                             | 70        |

|   |      | 4.4.1   | Terminology                                               | 71        |

|   |      | 4.4.2   | Stack-Generation Algorithm                                | 71        |

|   |      | 4.4.3   | Analog Constraints and Computational Cost                 | 74        |

|   |      | 4.4.4   | Importance of Creating Alternative Modules                | 76        |

|   |      | 4.4.5   | Module Replacement Criteria                               | 78        |

|   | 4.5  | Perfor  | rmance Models and Constraint Enforcement                  | 81        |

|   |      | 4.5.1   | Deterministic Model                                       | 82        |

|   |      | 4.5.2   | Non-Deterministic Parasitic Constraint Enforcement        | 87        |

|   | 4.6  | Subst   | rate-Aware Placement                                      | 90        |

|   |      | 4.6.1   | Modeling Switching Noise                                  | 91        |

|   |      | 4.6.2   | Modifying the Original Placement Algorithm                | 92        |

|   |      | 4.6.3   | Advanced Features: Thermal Analysis                       | 97        |

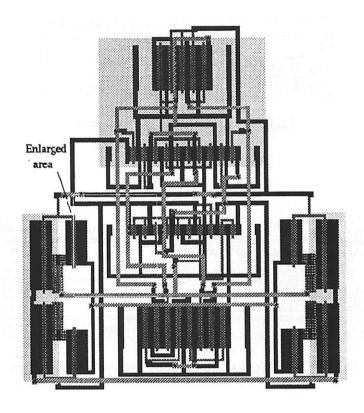

|   | 4.7  |         | ment with Analog Constraints: A Case Study                | 97        |

|   |      | 4.7.1   | Module Generation                                         | 97        |

|   |      | 4.7.2   | Placement Algorithm                                       | 100       |

|   |      |         |                                                           |           |

| 5 | Rou | ting 10                                                              | 2  |

|---|-----|----------------------------------------------------------------------|----|

|   | 5.1 | Performance-Driven Analog Routers                                    | 3  |

|   | 5.2 | Maze Routing and the A* Algorithm                                    | 4  |

|   | 5.3 | Routing of RF Circuits and MMICs                                     | 7  |

|   | 5.4 | Parasitic Modeling and Constraint Generation                         | 9  |

|   | 5.5 | Routing Phases                                                       | 3  |

|   |     | 5.5.1 Constructive Routing                                           | 3  |

|   |     | 5.5.2 Refinement                                                     | 5  |

|   | 5.6 | RF and Microwave Routing: A Case Study                               |    |

| 6 | Syn | abolic Compaction 12                                                 | 3  |

|   | 6.1 | Compaction Problem Formulation                                       | 4  |

|   | 6.2 | Compaction with Analog Constraints                                   | 6  |

|   | 6.3 | Constraint Enforcement Techniques                                    |    |

|   | 0.0 | 6.3.1 DRC                                                            |    |

|   |     | 6.3.2 Constraints on Stray Capacitances                              |    |

|   |     | 6.3.3 Preservation of Electrostatic Shields                          |    |

|   |     | 6.3.4 Symmetry Constraints                                           |    |

|   | 6.4 | Algorithmic Considerations                                           |    |

|   | 6.5 | Wire Length Minimization                                             |    |

|   | 6.6 | Compaction with Analog Constraints: A Case Study                     |    |

| 7 | E+  | raction 13                                                           | 0  |

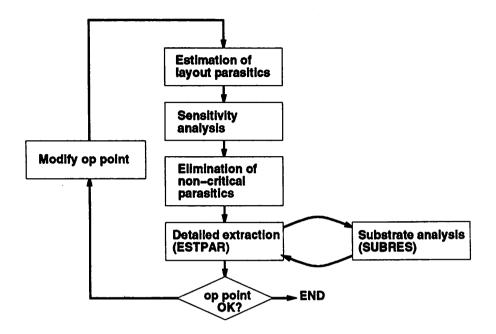

| • | 7.1 | General Extraction Methodology                                       |    |

|   | (.1 | 7.1.1 Extraction Tools and Organization                              |    |

|   |     |                                                                      |    |

|   | 7.2 | 7.1.2 Constraint-Based Schematic Simplification                      |    |

|   | 1.2 | <u> </u>                                                             |    |

|   |     | •                                                                    | _  |

|   |     |                                                                      |    |

|   |     | 7.2.3 Parallel Lines on the Same Layer                               |    |

|   | ~ 0 | 7.2.4 Interconnect Lines on Different Layers                         | _  |

|   | 7.3 | Technology Gradient Effects: Mismatch Modeling                       | -  |

|   | 7.4 | RF Parasitic Modeling                                                |    |

|   |     | 7.4.1 Modeling Single Interconnect Lines                             |    |

|   |     | 7.4.2 Modeling Coupled Microstrip Lines                              |    |

|   |     | 7.4.3 Modeling Microstrip Discontinuities                            |    |

|   |     | 7.4.4 Modeling 3-D Discontinuities                                   |    |

|   | 7.5 | Superconductor Parasitic Modeling                                    |    |

|   |     | 7.5.1 Analytical Model Generation for Superconducting Inductances 15 |    |

|   |     | 7.5.2 Modeling a Single Line                                         |    |

|   |     | 7.5.3 Modeling Coplanar Lines                                        |    |

|   |     | 7.5.4 Modeling Non-overlapping Lines                                 |    |

|   |     | 7.5.5 Modeling Overlapping Lines                                     |    |

|   |     | 7.5.6 Model Characterization                                         | 57 |

|   |     | 7.5.7 Example of Complete Superconductor Extraction                  | 58 |

| 8            | Subs | trate- | Aware Analysis and Optimization                            | 159   |

|--------------|------|--------|------------------------------------------------------------|-------|

|              | 8.1  | Import | tance of Substrate in Mixed-Signal Systems                 | 160   |

|              | 8.2  | Modeli | ing Substrate Transport and Thermal Behavior               | 163   |

|              |      | 8.2.1  | Background                                                 | 163   |

|              |      | 8.2.2  | Green's Function-Based Methods: Basics                     | 167   |

|              |      | 8.2.3  | Using the Green's Function in Substrate Analysis           | 168   |

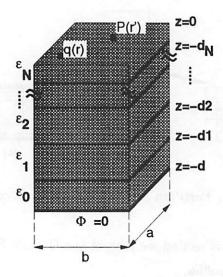

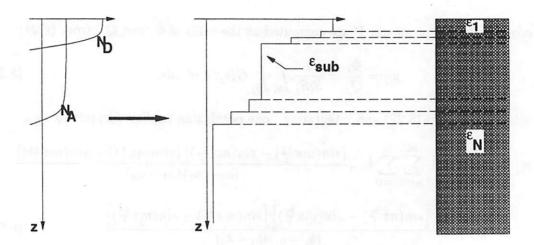

|              |      | 8.2.4  | Computing the Green's Function in Multi-Layered Substrates | 170   |

|              |      | 8.2.5  | Substrate Extraction Algorithm                             | 174   |

|              |      | 8.2.6  | Thermal analysis                                           | 176   |

|              |      | 8.2.7  | Schemes for Efficient Solution of Large Substrate Problems | 177   |

|              | 8.3  | Switch | ing Noise Sources                                          | 179   |

|              |      | 8.3.1  | Substrate Injection Mechanisms                             | 180   |

|              |      | 8.3.2  | Substrate Reception Mechanisms                             | 184   |

|              | 8.4  | Substr | ate Conductivity and Technology                            | 185   |

|              | 8.5  | Techni | iques for Substrate-Aware Optimization                     | 188   |

|              |      | 8.5.1  | Constraint Generation for Substrate Parasitic Effects      | 188   |

|              |      | 8.5.2  | Substrate Transport Evaluation in Iterative Algorithms     | 191   |

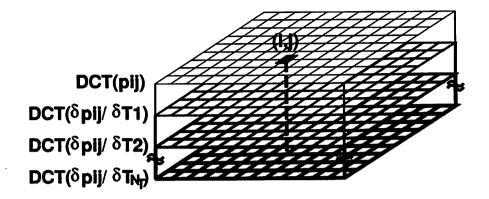

|              |      | 8.5.3  | Template-Based Substrate Extraction                        | 197   |

|              |      | 8.5.4  | Evaluating Effects of Scaling and Technology Migration     | 203   |

| 9            | Exp  | erime  | ntation                                                    | 211   |

|              | 9.1  |        | g Benchmark Library                                        | 211   |

|              |      | 9.1.1  | COMPL                                                      |       |

|              |      | 9.1.2  | FASTCOMP                                                   | 214   |

|              |      | 9.1.3  | MPH                                                        | 216   |

|              |      | 9.1.4  | Other CMOS Benchmarks                                      | 221   |

|              | 9.2  | Mixed  | -Signal Benchmark Library                                  | 222   |

|              |      | 9.2.1  | The RAMDAC System                                          |       |

|              |      | 9.2.2  | The $\Sigma - \Delta$ Converter System                     | 237   |

|              | 9.3  | RF an  | d Microwave Benchmark Library                              |       |

| 10           | Con  | clusio | ns                                                         | 250   |

|              | 10.1 | Concl  | usions                                                     | . 250 |

|              | 10.2 | Future | e Work                                                     | . 251 |

| A            | Con  | verge  | nce of Modified Placement Algorithms                       | 253   |

|              |      | _      | ication of Search Space                                    | . 253 |

|              |      |        | rate-Aware Placement                                       |       |

| В            | Con  | npacti | on Roundoff Calculations                                   | 255   |

| $\mathbf{C}$ | Gre  | en's F | unction Related Theory                                     | 258   |

| -            |      |        | Zero Depth Contact Calculation                             | . 258 |

|              |      |        | g Coefficient of Induction Matrix                          |       |

|              |      |        |                                                            |       |

| $\mathbf{D}$ | Sensitivity Analysis                                   | <b>261</b>  |  |

|--------------|--------------------------------------------------------|-------------|--|

|              | D.1 Canonical Representation of Performance            | <b>26</b> 1 |  |

|              | D.2 Coefficient of Potential and Technology Parameters | 262         |  |

| $\mathbf{E}$ | RF Parasitic Models                                    | 265         |  |

|              | E.1 Closed Form Expressions for Microstrip Lines       | 265         |  |

|              | E.2 Microstrip Line Discontinuities                    |             |  |

|              | E.3 3-D Discontinuities                                | 267         |  |

| F            | Superconducting Models                                 | 268         |  |

|              | F.1 Single Line                                        | <b>26</b> 8 |  |

|              | F.2 Coplanar Lines                                     | <b>269</b>  |  |

|              | F.3 Non-Overlapping Lines                              | 269         |  |

|              | F.4 Overlapping Lines                                  | 269         |  |

| G            | Software Availability                                  | 270         |  |

| Bi           | Bibliography 27                                        |             |  |

# List of Figures

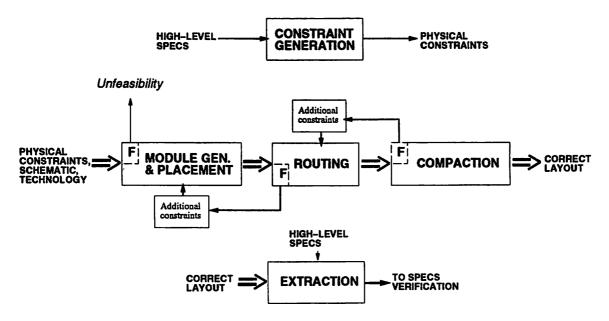

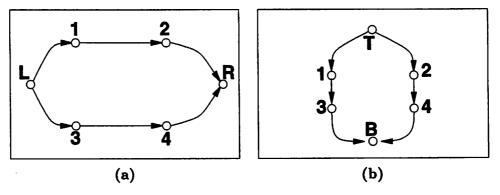

| 1.1  | Constraint-driven layout design: Traditional design partition into tasks has been modified by adding information paths between layout phases      | 4          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.2  | The organization of each layout phase. The internal feedback path provides                                                                        | _          |

|      | information to the constraint generator. External feedback paths provide information on the reasons of failure to meet performance specifications | 5          |

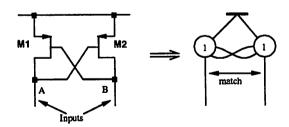

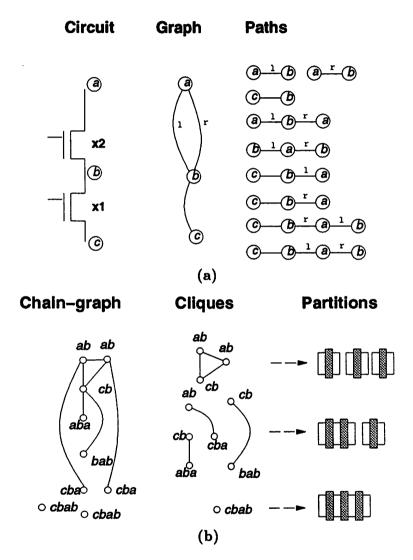

| 3.1  | Pseudo-code of the graph-based symmetry constraint generator                                                                                      | 33         |

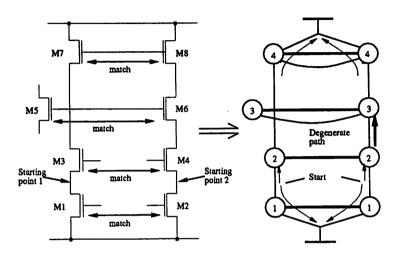

| 3.2  | Degenerate path                                                                                                                                   | <b>3</b> 5 |

| 3.3  | Semi-degenerate path                                                                                                                              | <b>3</b> 5 |

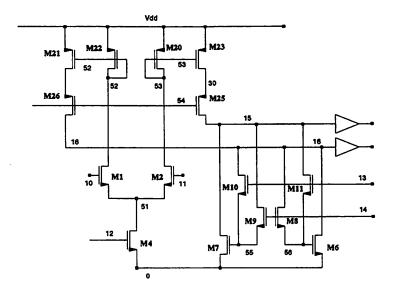

| 3.4  | Clocked comparator COMPL                                                                                                                          | 36         |

| 4.1  | Object definition                                                                                                                                 | 41         |

| 4.2  | Pseudo-code of a generic iterative algorithm                                                                                                      | 47         |

| 4.3  | Pseudo-code of a generic SA algorithm                                                                                                             | 48         |

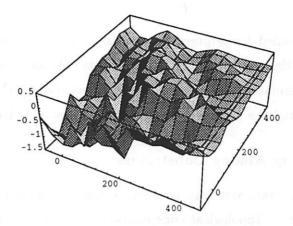

| 4.4  | Normalized energy landscape in typical placement problem                                                                                          | 49         |

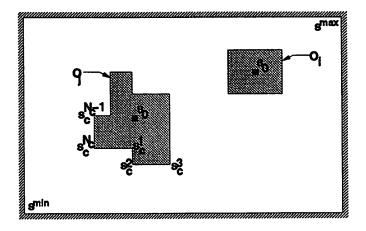

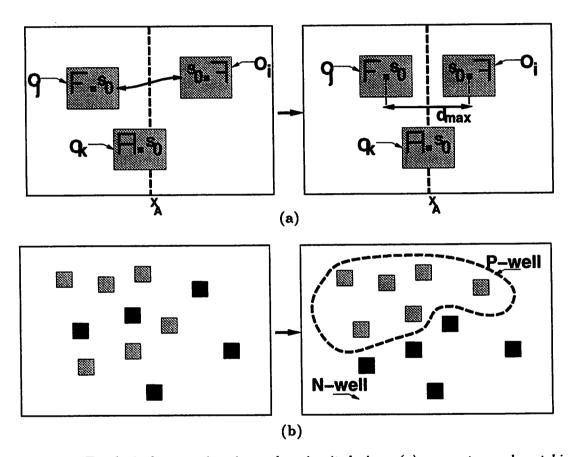

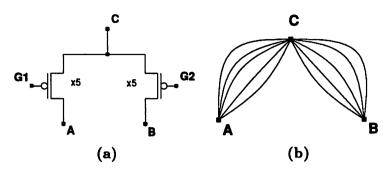

| 4.5  | Topological constraints in analog circuit design: (a) symmetry and matching;                                                                      |            |

|      | (b) well minimization                                                                                                                             | 51         |

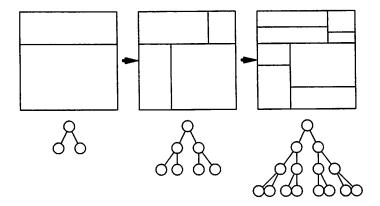

| 4.6  | Slicing-tree space representation for layout optimization algorithms                                                                              | 53         |

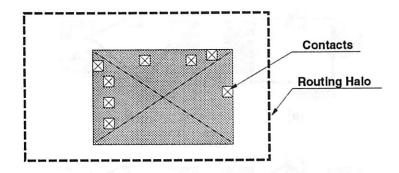

| 4.7  | Accounting for routing channels: the Halo algorithm                                                                                               | 55         |

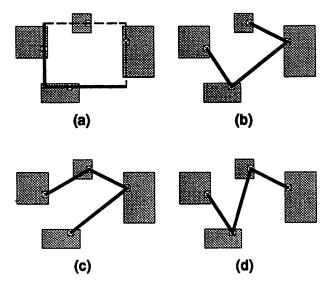

| 4.8  | Routing estimation techniques                                                                                                                     | 56         |

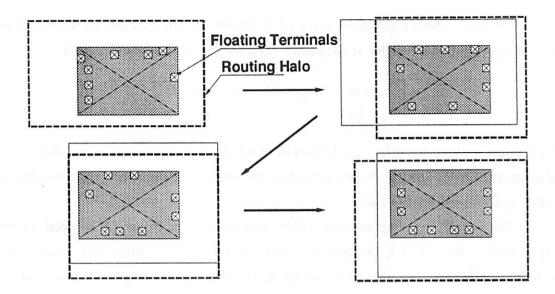

| 4.9  | Dynamically adjustable terminals in modules                                                                                                       | 57         |

| 4.10 |                                                                                                                                                   | 59         |

| 4.11 | Dynamically adjustable modules available to the placement tool                                                                                    | 60         |

| 4.12 | Library of CMOS modules                                                                                                                           | 61         |

| 4.13 | SA and well definition                                                                                                                            | 63         |

| 4.14 | Placement using virtual symmetry axes                                                                                                             | 64         |

| 4.15 | Abutment and separation of modules                                                                                                                | 66         |

| 4.16 | Updating symmetry axes during the annealing                                                                                                       | 67         |

|      | Updating well regions during the annealing                                                                                                        | 67         |

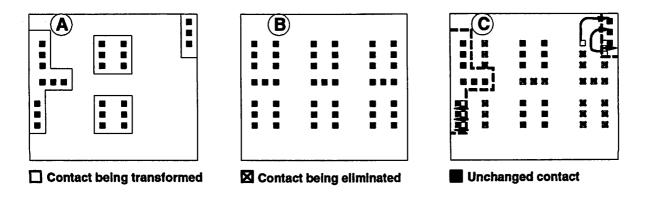

|      | Updating contact locations                                                                                                                        | 68         |

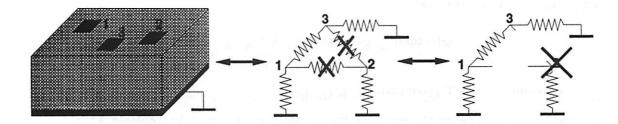

| 4.19 | Modeling contacts within modules                                                                                                                  | 68         |

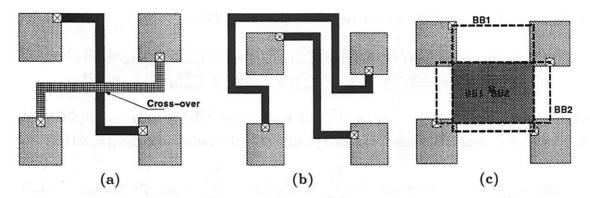

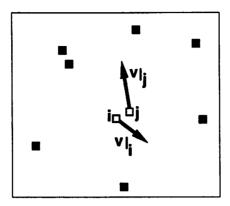

|      | Contact resistance as a function of relative position within a module                                                                             | 69         |

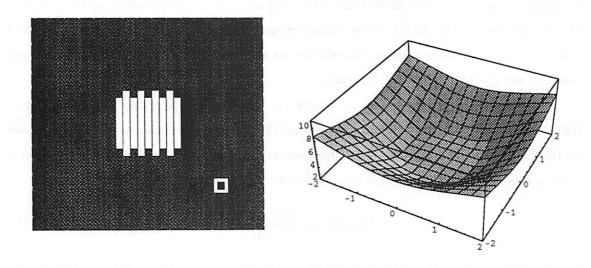

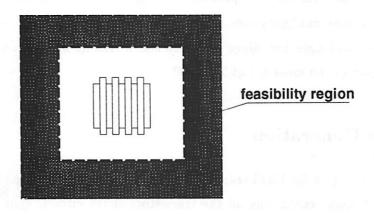

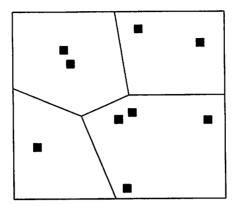

|      | Derivation of feasibility region for the contact realization                                                                                      | 69         |

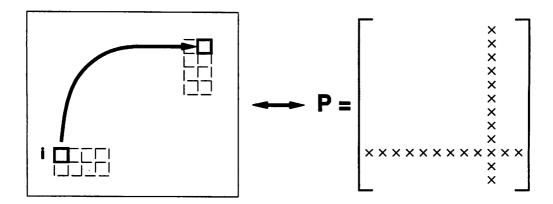

| 4.22 | (a) Mapping of a circuit schematic onto a graph; (b) Chaining algorithm in       |           |

|------|----------------------------------------------------------------------------------|-----------|

|      | LDO (Courtesy of Enrico Malavasi)                                                | <b>72</b> |

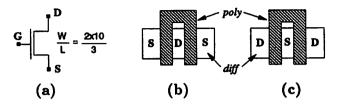

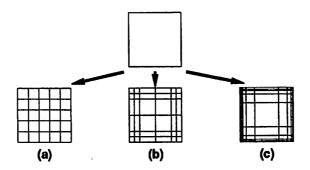

| 4.23 | Splitting of large transistors (Courtesy of Enrico Malavasi)                     | 73        |

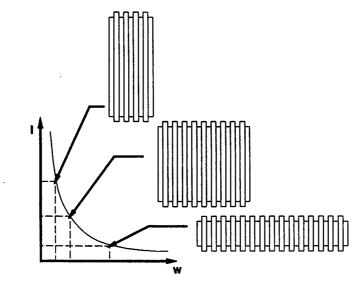

|      | (a) Transistor split in two modules; (b) Layout minimizing the capacitance       |           |

|      | of net $D$ ; (c) Layout minimizing the capacitance of net $S$                    | <b>75</b> |

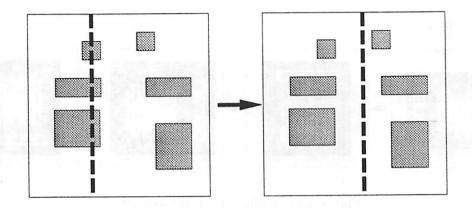

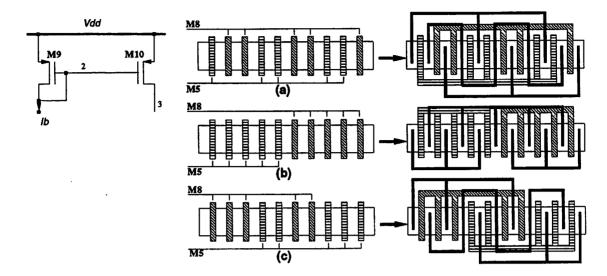

| 4.25 | Enforcement of symmetry in LDO: (a) first alternative based on a common-         |           |

|      | centroid design style; (c) second fully symmetric layout; (b) trade-off          | 77        |

| 4.26 | Example of a folded cascode opamp. The bubbles represent all sub-circuits        |           |

|      | created by the module generator on the ground of well type                       | 78        |

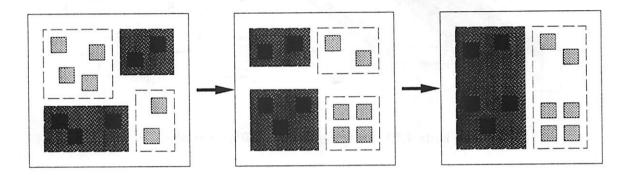

| 4.27 | Alternative implementations of the differential pair and its active load         | 79        |

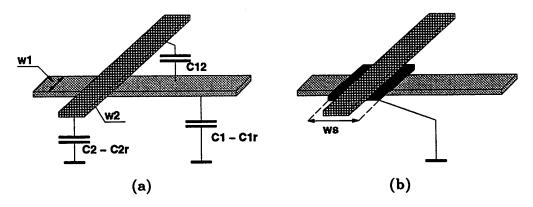

|      | Alternative implementations of interconnect: (a) on metal1 or metal2; (b)        |           |

|      | on metal1 and poly; (c) on metal1 and metal2                                     | 83        |

| 4.29 | Puppy-A's shaping function with twofold interconnect implementation              | 85        |

|      | Coupling (a) without and (b) with vertical shielding. Indirect shielding effects |           |

|      | due to the presence of the other interconnect have been added to the cross-over  |           |

|      | capacitance models                                                               | 85        |

| 4.31 | (a) Cross-coupling between MET1 and MET2 interconnect; (b) configuration         |           |

|      | avoiding cross-over; (c) heuristic for crossover probability estimation          | 87        |

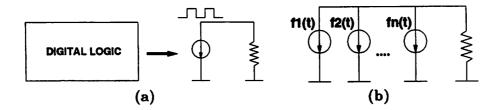

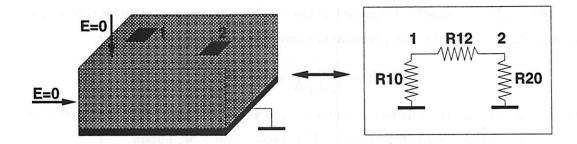

| 4.32 | (a) Simple injection model; (b) Proposed injection model                         | 92        |

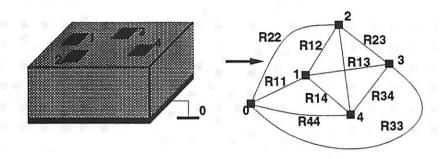

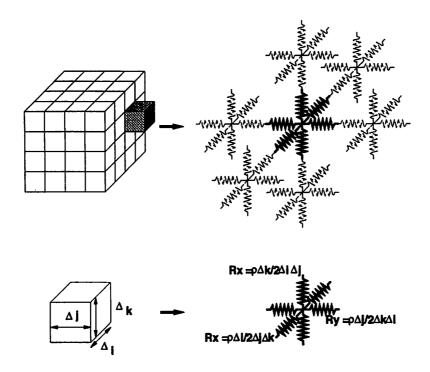

| 4.33 | Mapping of substrate onto fully connected graph $G_S(V, E)$                      | 93        |

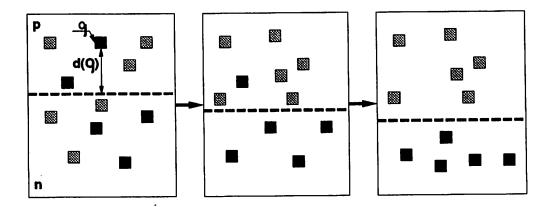

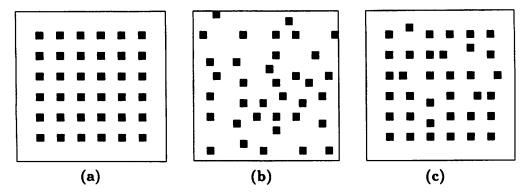

| 4.34 | (a) Initial contact grid; (b) Reshuffling of contacts at high temperatures; (c)  |           |

|      | Resulting grid at lower temperatures                                             | 94        |

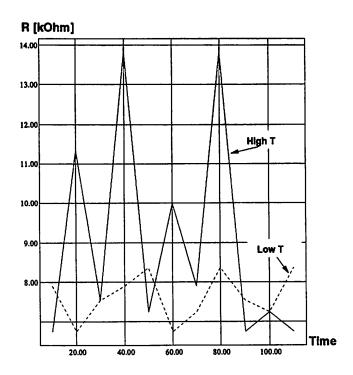

| 4.35 | Resistive network reacting to high-temperature and low temperature contact       |           |

|      | reshuffling                                                                      | 95        |

| 4.36 | Heuristic for the combined use of Sherman-Morrison and gradient-based meth-      |           |

|      | ods                                                                              | 95        |

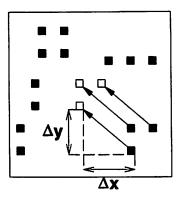

| 4.37 | Small number of contacts translating within the workspace                        | 96        |

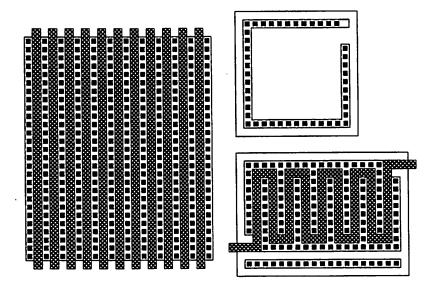

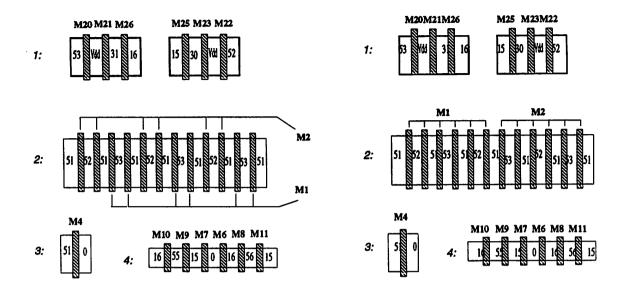

|      | Clocked comparator COMPL - Two alternative full-stacked implementations.         | 98        |

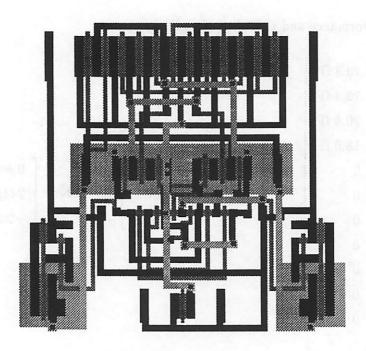

| 4.39 | Placement of comparator COMPL obtained with PUPPY-A                              | 100       |

|      |                                                                                  |           |

| 5.1  | Propagation of path length estimate from source s to target t through node x     | 105       |

| 5.2  | Generic A* routing algorithm                                                     | 106       |

| 5.3  | Grid allocation in a typical maze router                                         | 106       |

| 5.4  | Flow diagram of the tool                                                         | 109       |

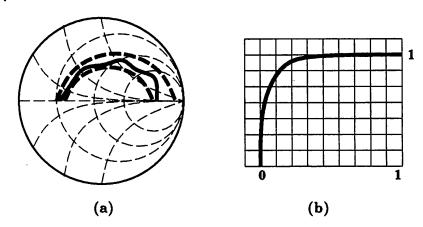

| 5.5  | (a) Microwave specification; (b) Flexibility function for constrained optimiza-  |           |

|      | tion                                                                             | 110       |

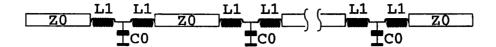

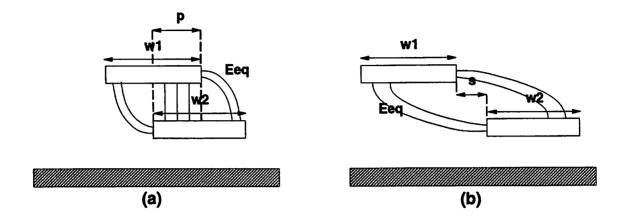

| 5.6  | Interconnect model for microstripline with multiple bends                        | 112       |

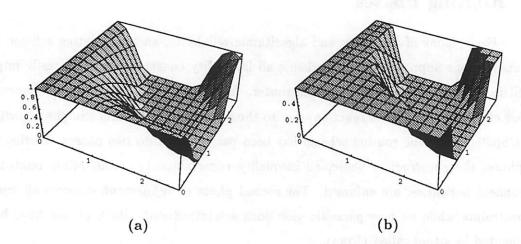

| 5.7  | Expansion of wiring in the workspace (a) with coarse and (b) with tight con-     |           |

|      | straints                                                                         | 114       |

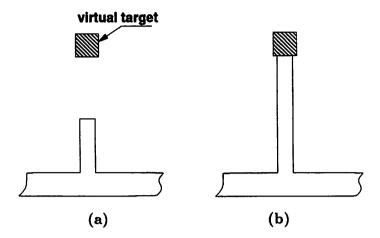

| 5.8  | Stub construction: (a) development from source; (b) completion                   | 115       |

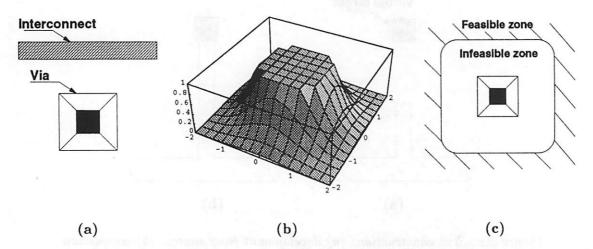

| 5.9  | Effects of a via structure on a to-be-built interconnect line. (a) Structure     |           |

|      | set-up; (b) Interconnect characteristic impedance deviation as a function of     |           |

|      | the location relative to the via; (c) Feasibility zone                           | 116       |

|      | Distributed parasitics acting on interconnect determine feasibility zones        | 117       |

| 5.11 | Refinement algorithm in CORAL                                                    | 118       |

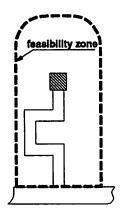

| 5.12 | Expansion of a stub within feasibility zone                                                                                                                             | 119         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

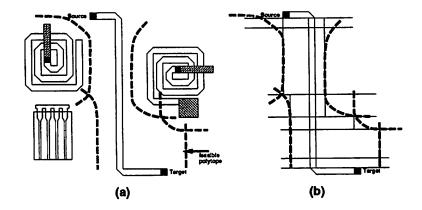

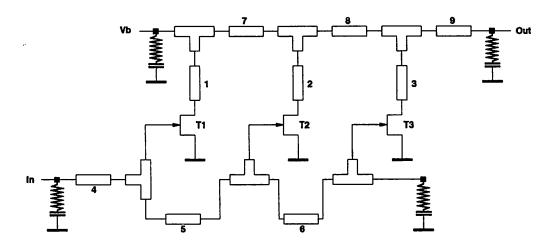

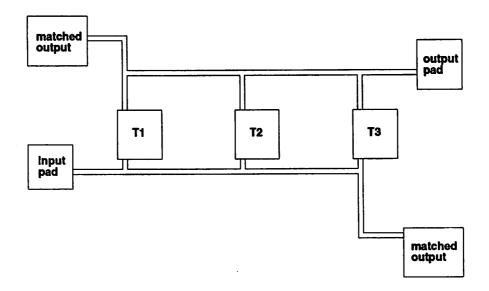

|      | Schematic of TWA                                                                                                                                                        | 119         |

|      | Layout after CORAL's constructive routing                                                                                                                               | 121         |

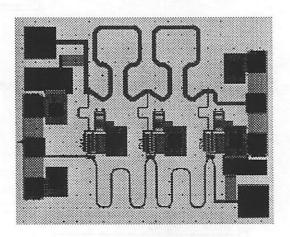

|      | Final layout of TWA                                                                                                                                                     | 122         |

|      | Manual layout of TWA                                                                                                                                                    | 122         |

| 6.1  | Mono-dimensional compaction algorithm                                                                                                                                   | 125         |

| 6.2  | Orthogonal mono-dimensional compaction iterations                                                                                                                       | 125         |

| 6.3  | Iterative mono-dimensional compaction algorithm                                                                                                                         | 126         |

| 6.4  | Constraint graphs associated with (a) horizontal and (b) vertical constraints. The symbols L/R and T/B relate to the left/right and top/bottom coordinates respectively | 127         |

| 6.5  | Topological and parasitic Constraints: (a) symmetry and matching; (b) par-                                                                                              |             |

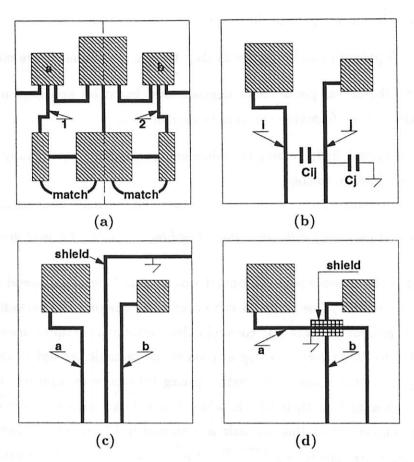

|      | asitic; (c) lateral shielding; (d) vertical shielding                                                                                                                   | 129         |

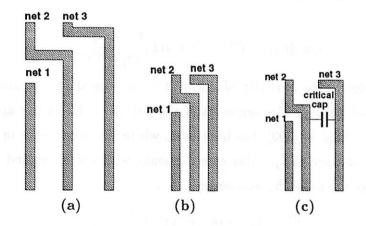

| 6.6  | Required spacing for controlling capacitive coupling                                                                                                                    | 129         |

| 6.7  | Algorithm for the insertion of additional spacing for wire decoupling                                                                                                   | 130         |

| 6.8  | Pseudo-code of procedure modify-graph                                                                                                                                   | 131         |

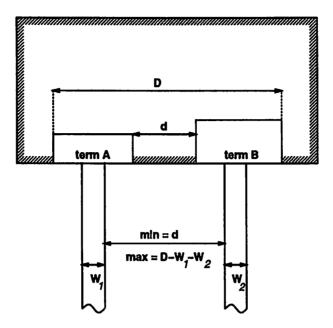

| 6.9  | Minimum and maximum wire spacing constraints deriving from connections                                                                                                  |             |

|      | to fixed-distance terminals                                                                                                                                             | 132         |

| 6.10 | Compacted layout of COMPL with all analog constraints enforced                                                                                                          | <b>13</b> 8 |

| 7.1  | Methodology of selective extraction                                                                                                                                     | 140         |

| 7.2  | Simple interconnect line                                                                                                                                                | 144         |

| 7.3  | Crossover configuration                                                                                                                                                 | 144         |

| 7.4  | Parallel interconnect lines                                                                                                                                             | 145         |

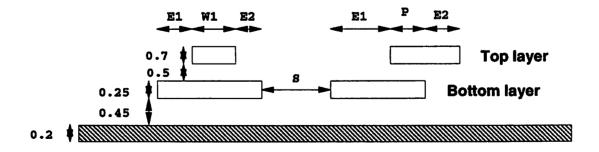

| 7.5  | Interconnect lines on different layers: (a) non-overlapping; (b) overlapping.                                                                                           | 146         |

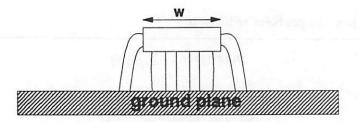

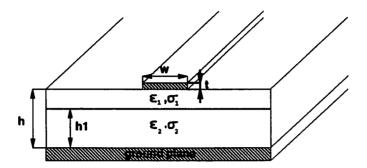

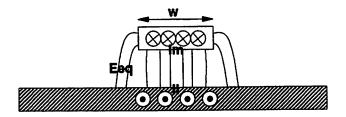

| 7.6  | Single microstrip line over lossy substrate                                                                                                                             | 150         |

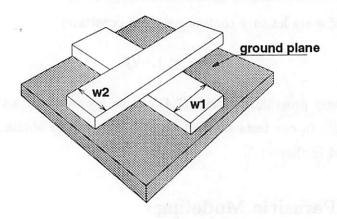

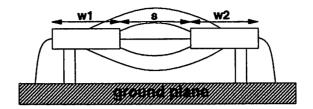

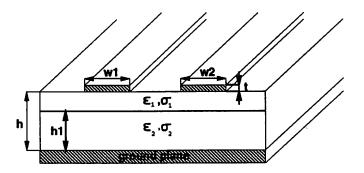

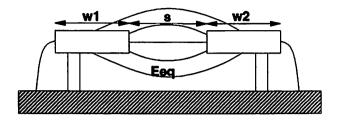

| 7.7  | Coupled microstrip lines                                                                                                                                                | 151         |

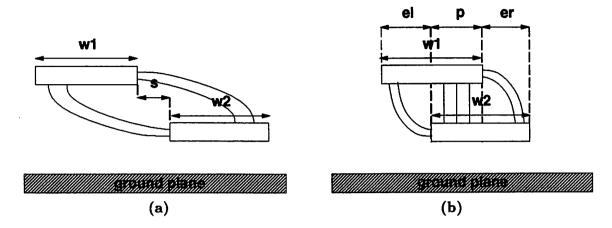

| 7.8  | Typical Discontinuities in RF and microwave circuits                                                                                                                    | 152         |

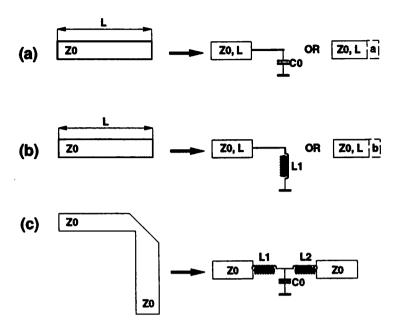

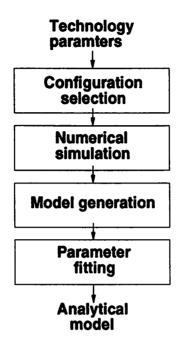

| 7.9  | Analytical model generation for superconducting inductances                                                                                                             | 154         |

| 7.10 | Single line                                                                                                                                                             | 155         |

| 7.11 | Coplanar lines                                                                                                                                                          | 156         |

| 7.12 | (a) Overlapping; (b) Non-overlapping lines                                                                                                                              | 157         |

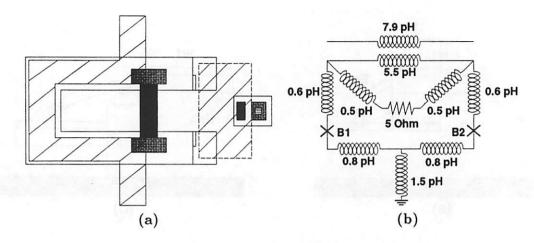

| 7.13 | (a) Layout of a two-junction SQUID; (b) Extracted schematic using INDEX                                                                                                 | 158         |

| 8.1  | Main and spurious currents in an inverter during transition                                                                                                             | 161         |

| 8.2  | Impact of spurious noise signals to a differential pair                                                                                                                 | 162         |

| 8.3  | Substrate modeling using RC mesh (Courtesy of Ranjit Gharpurey)                                                                                                         | 166         |

| 8.4  | Substrate boundaries and contact resistance modeling                                                                                                                    | 169         |

| 8.5  | Partition schemes for substrate contacts                                                                                                                                | 171         |

| 8.6  | Multi-layer doping profiles (Courtesy of Ranjit Gharpurey)                                                                                                              | 172         |

| 8.7  | Discretization of non-abrupt doping profiles                                                                                                                            | 174         |

| 8.8  | Pseudo-code of the substrate resistance extraction algorithm                                                                                                            | 175         |

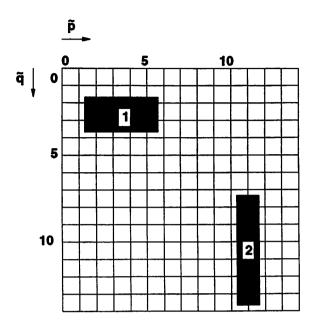

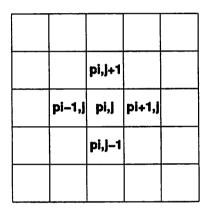

| 8.9  | Discretization of the substrate surface                                                                                                                                 | 176         |

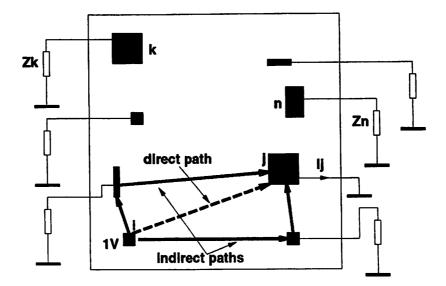

|      | Direct and indirect current-flow paths (Courtesy of Ranjit Gharpurey)                                                                                                   | 177         |

| 8.11 | Pseudo-code of the simplified substrate extraction scheme                              | 179 |

|------|----------------------------------------------------------------------------------------|-----|

|      | Partitioning of substrate for the simplification algorithm                             | 180 |

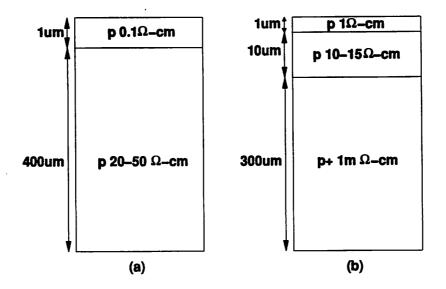

|      | Typical IC substrates: (a) high-resistivity; (b) low-resistivity                       | 181 |

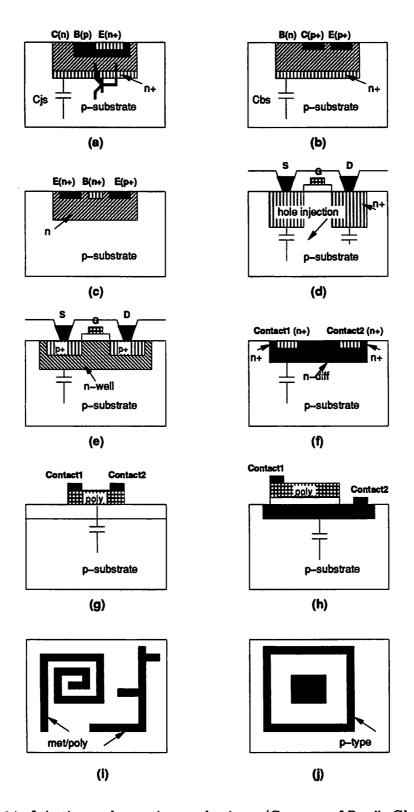

|      | Injection and reception mechanisms (Courtesy of Ranjit Gharpurey)                      | 182 |

|      | Body Effect in MOSFETs (Courtesy of Ranjit Gharpurey)                                  | 184 |

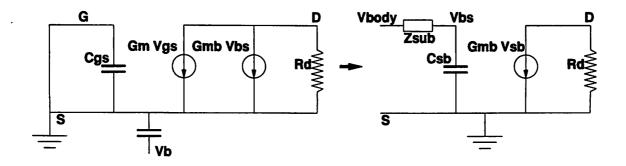

|      | Storing one DCT for nominal parameter set and a number of DCTs for each                |     |

|      | computed sensitivity                                                                   | 187 |

| 8.17 | Pseudo-code of the substrate sensitivity extraction algorithm                          | 188 |

|      | The principle and modeling of local generators                                         | 189 |

|      | Constraint check                                                                       | 191 |

|      | Contact transformation and modifications in the potential matrix                       | 192 |

|      | Sensitivity of resistive macro-model from transformation of a component and            |     |

| •    | its contacts                                                                           | 194 |

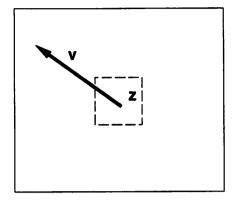

| 8.22 | Single contact moving in direction v by an infinitesimal amount                        | 195 |

|      | Computation of $\delta p_{ij}$                                                         | 195 |

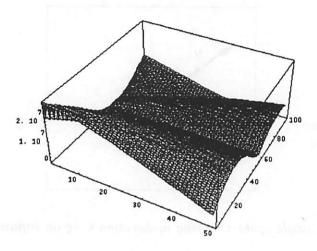

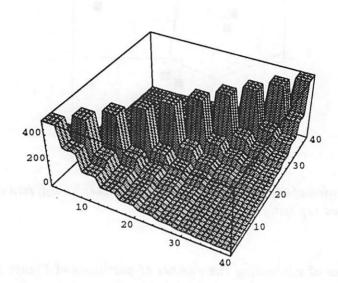

|      | 200x200 DCT of the Green's Function for a commercial substrate                         | 196 |

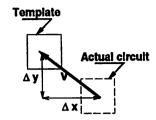

|      | Computation of update matrix $\delta c$ based on contact displacement relative to      |     |

| 0.20 | template                                                                               | 197 |

| 8.26 | Pseudo-code of the template-based substrate extraction algorithm                       | 197 |

|      | Speed-up mechanism for the extraction of large substrates                              | 198 |

|      | Elimination of all non-critical conductances and contacts                              | 199 |

|      | Pseudo-code of the modified template-based substrate extraction algorithm .            | 201 |

|      | Similar landscape and displacement of contact i and j                                  | 202 |

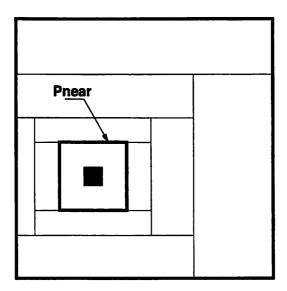

|      | Partitioning of substrate to minimize the number of different contacts for             | 202 |

| 0.01 | which $\nabla_{\mathbf{v}}\mathbf{c}$ need be computed explicitly                      | 203 |

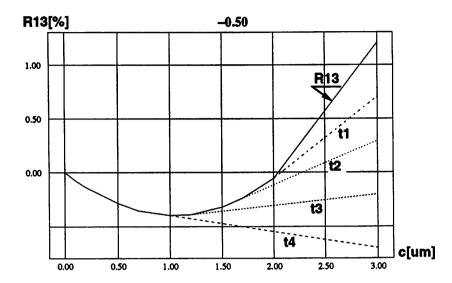

| 8 32 | Accuracy in function of the distance of the true contact from the pre-computed         | 200 |

| 0.02 | contact                                                                                | 204 |

| 8.33 | (a) Two-dimensional scaling in the event of re-design; (b) Three-dimensional           | 20. |

| 0.00 | scaling in technology migration                                                        | 204 |

| 8.34 | Plot of the dependence of each component of the $\overline{R}$ matrix as a function of | _0  |

| 0.01 | the contact layer depth                                                                | 205 |

| 8.35 | Plot of the dependence of $\overline{R}$ as a function of the contact layer depth and  |     |

| 0.00 | related sensitivities                                                                  | 206 |

| 8.36 | Scaling in x- and y-direction. Relocation of contacts and area scaling                 | 207 |

|      | Sensitivity of entry $Y_{55}$ in a 10x10 grid as a function of a translation in (a)    |     |

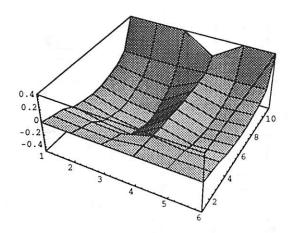

| 0.0. | x- and (b) y- direction of all the contacts in the grid                                | 208 |

|      | a and (o) g an economic of an inc constant we she give the entire terms of             |     |

| 9.1  | Complete layout of COMPL, (a) without enforcement, (b) with enforcement of             |     |

|      | analog constraints                                                                     | 214 |

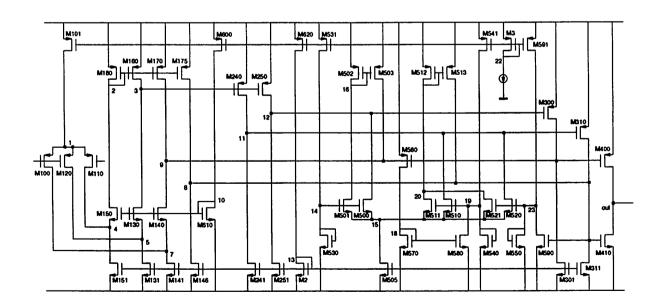

| 9.2  | Schematic of the clocked comparator FASTCOMP                                           | 21  |

| 9.3  | Complete layout of FASTCOMP, with enforcement of all analog constraints .              | 217 |

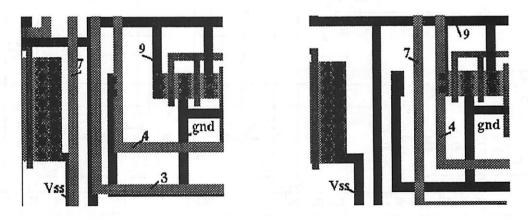

| 9.4  | Details of the routing of FASTCOMP. Left: no parasitic constraints enforced.           |     |

|      | Right: all parasitic constraints successfully enforced                                 | 217 |

| 9.5  | Schematic of MPH                                                                       | 218 |

| 9.6  | Complete layout of MPH, obtained enforcing all analog constraints                      | 220 |

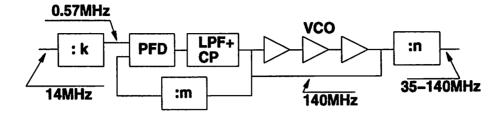

| 9.7  | PLL schematic                                                                  | 223         |

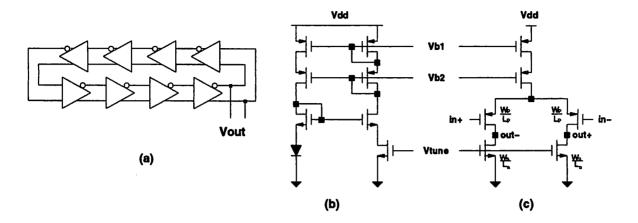

|------|--------------------------------------------------------------------------------|-------------|

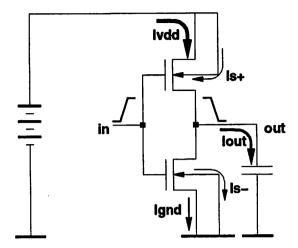

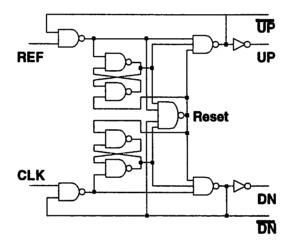

| 9.8  | VCO block diagram and schematic of one delay cell                              | 224         |

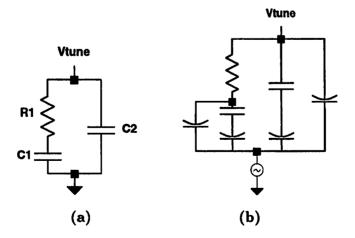

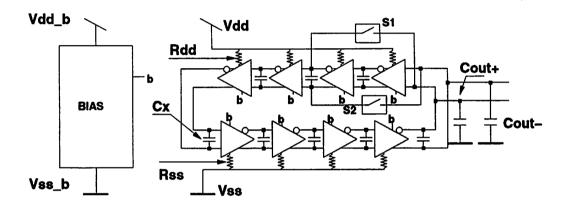

| 9.9  | PFD schematic                                                                  | <b>224</b>  |

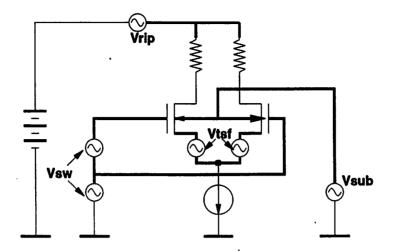

| 9.10 | LPF schematic: (a) no substrate coupling; (b) with substrate coupling          | 224         |

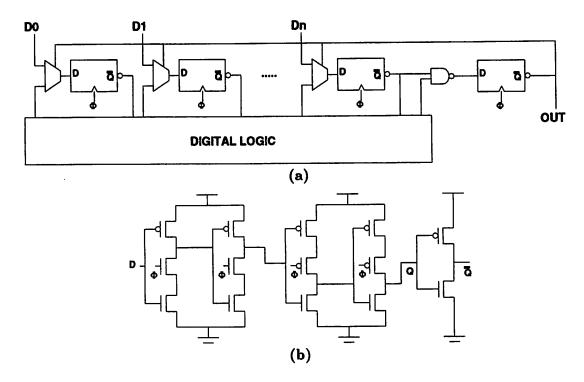

| 9.11 | Programmable divider: (a) block diagram; (b) single-phase flip-flop            | <b>225</b>  |

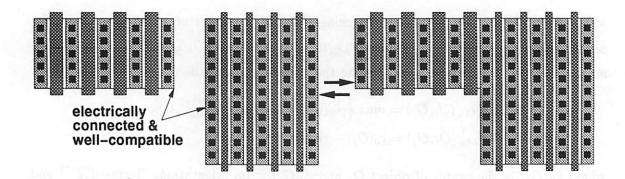

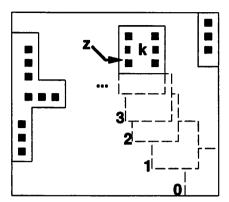

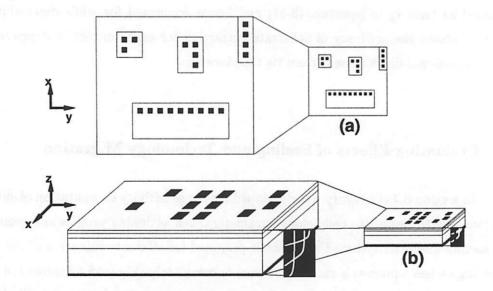

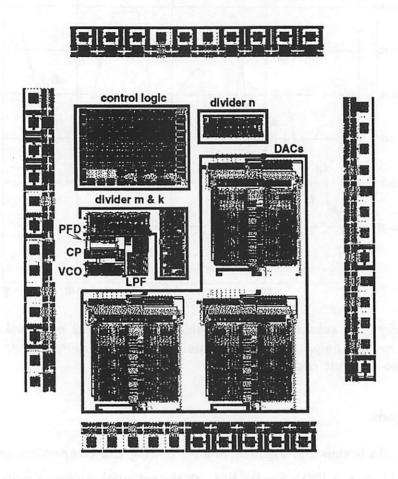

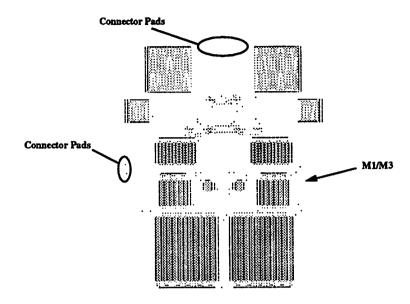

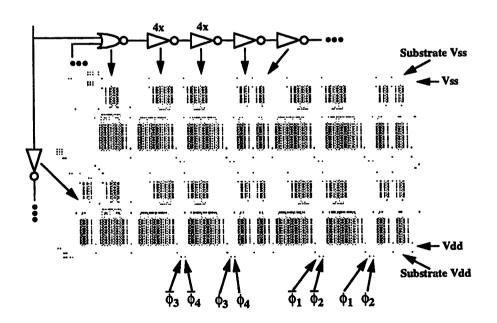

| 9.12 | VCO architecture generated by VCOGEN                                           | 227         |

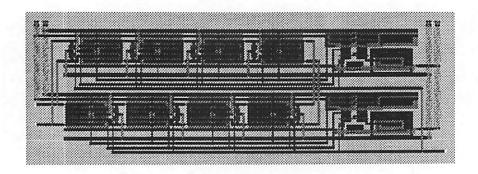

| 9.13 | Layout of eight-stage VCO                                                      | <b>228</b>  |

| 9.14 | (a) Charge pump (CP); (b) Low-pass filter (LPF)                                | 229         |

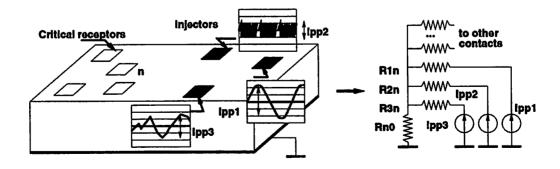

| 9.15 | (a) Output signal of divider; (b) Injected current; (c) Model for substrate    |             |

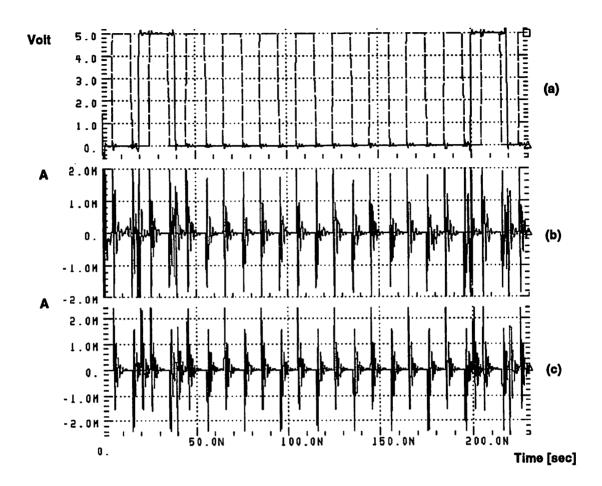

|      | injection                                                                      | 231         |

|      | Evaluation of peak-to-peak switching noise at the receptor site                | 231         |

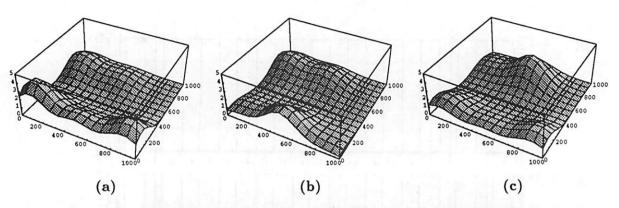

| 9.17 | Estimated level of switching noise signal amplitude as a result of the cumula- |             |

|      | tive injection of the dividers during the annealing: (a) high temperature; (b) |             |

|      | medium temperature; (c) low temperature                                        | 232         |

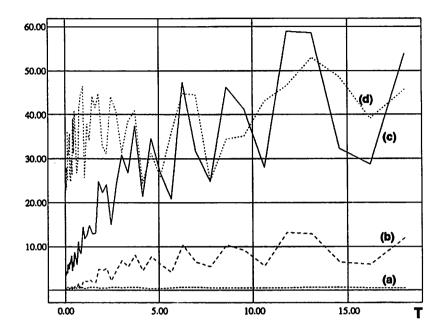

| 9.18 | Error in substrate injection estimation using: (a) combined heuristic; (b)     |             |

|      | gradient-based method only. Evolution of total substrate violations using: (c) |             |

|      | combined heuristic; (d) no substrate control                                   | 233         |

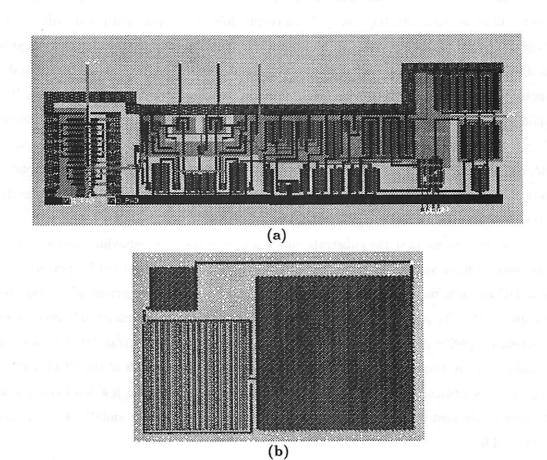

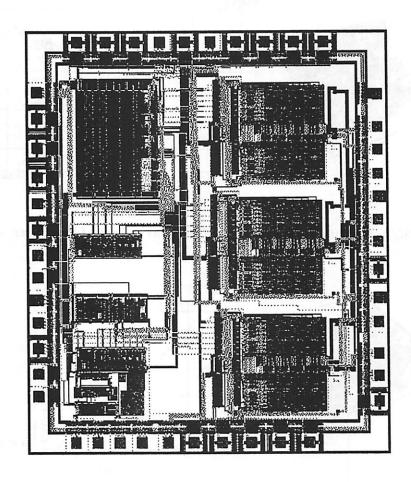

|      | Placed PLL within the RAMDAC                                                   | 234         |

|      | Placed and routed PLL within the RAMDAC                                        | <b>23</b> 5 |

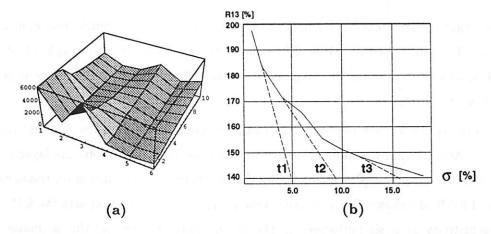

|      | Dependence from doping levels: (a) sub-set of R; (b) sensitivity               | 235         |

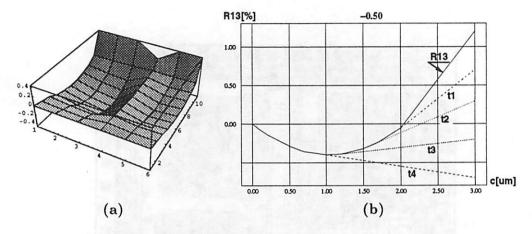

|      | Dependence from contact depth: (a) sub-set of $\mathbf{R}$ ; (b) sensitivity   | 236         |

|      | Dependence from doping profiles: (a) sub-set of R; (b) sensitivity             | 236         |

|      | $\Sigma$ - $\triangle$ Converter architecture                                  | 237         |

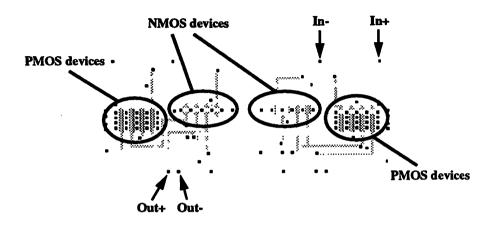

|      | Schematic of the OTA                                                           | 238         |

|      | Schematic of the bias circuitry                                                | 239         |

|      | Schematic of the comparator used in the $\Sigma - \Delta$ Converter            | 240         |

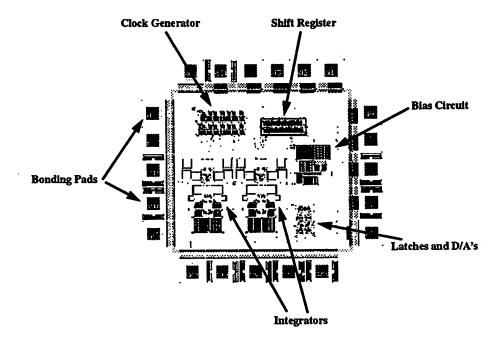

|      | Schematic of clock generator                                                   | 241         |

|      | Schematic of latch                                                             | 241         |

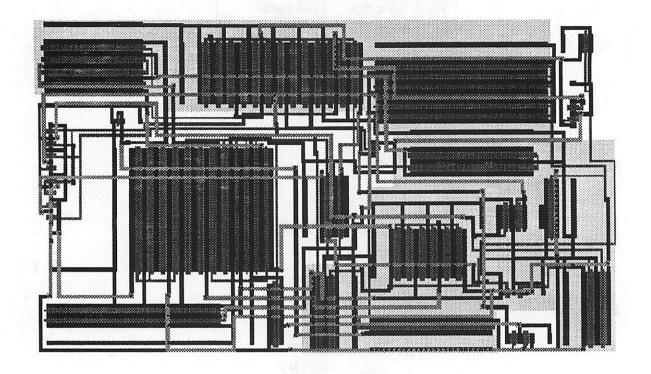

|      | Placement by PUPPY-A of the OTA (Courtesy of H. Chang and E. Felt)             | 242         |

|      | Placed, routed, compacted OTA (Courtesy of H. Chang and E. Felt)               | 243         |

| 9.32 | Layout of the clock generator (Courtesy of H. Chang and E. Felt)               | 243         |

|      | Layout of the latch (Courtesy of H. Chang and E. Felt)                         | 244         |

|      | Layout of $\Sigma - \Delta$ Converter (Courtesy of H. Chang and E. Felt)       | 245         |

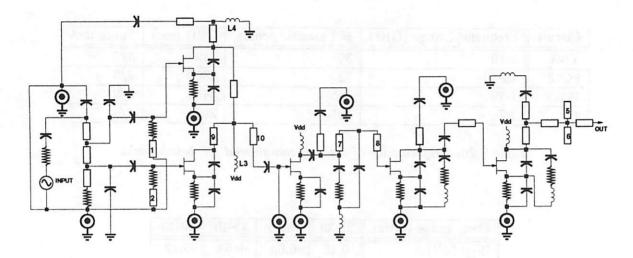

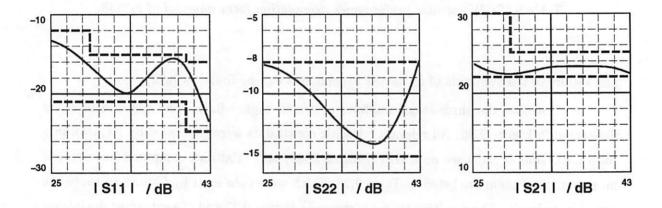

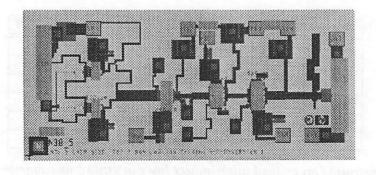

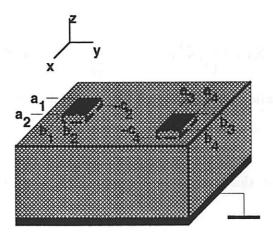

|      | Schematic of PCN38                                                             | 248         |

|      | Performance of PCN38                                                           | 248         |

| 9.37 | Final layout of PCN38                                                          | <b>24</b> 8 |

| C.1  | Non-zero depth contacts and dimensions                                         | 259         |

| F.1  | General configuration                                                          | <b>26</b> 8 |

### List of Tables

| 3.1        | Notation for parasitics and performance functions                                                                                                                                                                               | 32  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1<br>4.2 | Capacitances in the stacks generated for the clocked comparator COMPL<br>Conditions of operation for the placement tool used in the synthesis path. The symbols P, S and M denote parasitic, symmetry and matching constraints, | 98  |

|            | respectively                                                                                                                                                                                                                    | 101 |

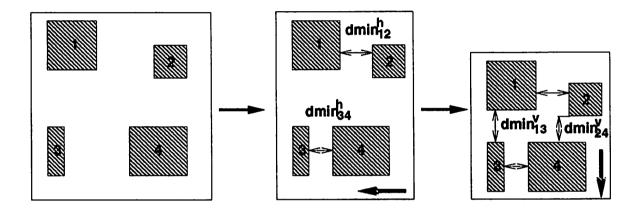

| 5.1        | Performance specifications for TWA                                                                                                                                                                                              | 120 |

| 5.2        | Constraints on critical interconnect lines                                                                                                                                                                                      | 120 |

| 5.3        | CPU times required for the synthesis of TWA on a DEC Station 5000/240.                                                                                                                                                          | 121 |

| 5.4        | Estimated performance of circuit TWA after layout completion                                                                                                                                                                    | 121 |

| 6.1        | Comparison of CPU time for graph + LP vs. LP alone                                                                                                                                                                              | 135 |

| 7.1        | Comparison between extracted and hand-computed parasitics                                                                                                                                                                       | 158 |

| 8.1        | Substrate extraction in presence of varying technology parameters using method I (full extraction) and method II (sensitivity-based extraction)                                                                                 | 207 |

| 8.2        | Mean and variance of the entries of matrix $\overline{\mathbf{R}}$ as a function of depth variance. All values are referred to a mean depth of $1\mu m$ . The execution times are                                               |     |

|            | reported for a uniform 10x10 contact grid                                                                                                                                                                                       | 209 |

| 8.3        | Selection of most suitable technology based on the probability of satisfying all                                                                                                                                                |     |

|            | constraints on substrate coupling resistances                                                                                                                                                                                   | 210 |

| 9.1        | COMPL: bounds on capacitive and resistive parasitics                                                                                                                                                                            | 212 |

| 9.2        | Conditions of operation for the routing and compaction tools used in the syn-                                                                                                                                                   |     |

|            | thesis path. The symbols P, S and M denote parasitic, symmetry and match-                                                                                                                                                       |     |

|            | ing constraints, respectively. The net scheduling is based on a cost function                                                                                                                                                   |     |

|            | which accounts for the "difficulty" of enforcing a set of desired constraints                                                                                                                                                   |     |

|            | on a given net                                                                                                                                                                                                                  | 213 |

| 9.3        | COMPL: performance                                                                                                                                                                                                              | 213 |

| 9.4        | COMPL: CPU time for each layout phase                                                                                                                                                                                           | 213 |

| 9.5        | FASTCOMP: bounds on capacitive and resistive mismatch                                                                                                                                                                           | 216 |

| 9.6        | FASTCOMP: performance                                                                                                                                                                                                           | 218 |

| 9.7        | FASTCOMP: CPII time for each layout phase                                                                                                                                                                                       | 218 |

| 9.8  | MPH: performance                                                                      | 219         |

|------|---------------------------------------------------------------------------------------|-------------|

| 9.9  | MPH: CPU time for each layout phase                                                   | <b>220</b>  |

| 9.10 | Nominal performance of benchmark circuits                                             | <b>221</b>  |

| 9.11 | Constraint generation for the given benchmark circuits                                | 222         |

|      | Measure of success of the performance-driven methodology                              | 222         |

|      | PLL specifications                                                                    | 226         |

| 9.14 | Parameter constraints obtained for the VCO by behavioral optimization of              |             |

|      | the PLL                                                                               | <b>226</b>  |

| 9.15 | Constraints obtained by the sensitivity analysis                                      | 227         |

| 9.16 | CPU times for the design and module generation obtained on a DEC Station              |             |

|      | 5000/125 and on a DEC AlphaServer 2100 5/250 (†)                                      | <b>22</b> 8 |

| 9.17 | Placement statistics obtained on a DEC AlphaServer 2100 5/250                         | 232         |

|      | Noise injector and receptor statistics in the components of the PLL                   | 234         |

| 9.19 | CPU times on a DEC AlphaServer 2100 5/250 for the trend analysis for                  |             |

|      | the proposed experiments on the PLL with 311 noise sources / receptors.               |             |

|      | The CPU times include DCT, parameter and sensitivity computation. For                 |             |

|      | the calculation of 311 contacts the inversion of matrix P was performed in            |             |

|      | 1525.0 seconds                                                                        | 237         |

| 9.20 | $\Sigma$ – $\triangle$ Converter design specifications                                | <b>23</b> 8 |

| 9.21 | Design constraints for the integrator                                                 | 240         |

|      | Design constraints for the comparator                                                 | 240         |

| 9.23 | Estimated man-time for an unexperienced tool-user to perform the layout of            |             |

|      | the $\Sigma - \Delta$ Converter (Courtesy of H. Chang and E. Felt)                    | 244         |

|      | $\Sigma - \triangle$ Converter experiment results                                     | 246         |

|      | Analytical models used in synthesis for parasitic control                             | 246         |

|      | Performance of a set of commercial RF benchmarks                                      | 247         |

|      | Worst-case performance degradation form nominal of PCN38                              | 247         |

| 9.28 | Constraints on critical interconnect lines in PCN38 as computed using PAR-            |             |

|      | CAR. Terms of type $\triangle L_{xy}$ denote a bound to the maximum attainable length |             |

|      | mismatch between nets $x$ and $y$                                                     | 247         |

#### Acknowledgements

This work is the result of the efforts and dedication of many people who have contributed in many ways to my endeavor and whom I gratefully acknowledge. My sincere thanks go to my advisor, Prof. Alberto Sangiovanni-Vincentelli who taught me how to conduct serious and rigorous research, in an exceptional environment such as that of the cad group at Berkeley. His vision and outstanding background was a continuous inspiration for finding new and creative solutions to manifold problems. A special sense of appreciation goes to professors Paul Gray, Robert Meyer and Theodore van Duzer for their competence and continuous support during my years at Berkeley.

I would like to thank my wife Tokiko for her continuous and unconditional support, her humor, her kindness, and her love that have made my life meaningful, through happy and difficult phases of my journey in the United States. I thank my mother and my sister for their support to my non easy decision to leave my country and for being at my side during all my studies in this faraway land.

A special thank goes to Denis Baggi and Arokia Nathan, who are mainly responsible for my decision to undertake an academic career abroad and whose advises have proven to be an indispensable tool of survival in such a different environment. I am very grateful to Enrico Malavasi, my mentor and personal friend, for the technical support and a genuinely constructive criticism he brought in much of my work on layout for analog ICs. I would also like to present a special thank to Ranjit Gharpurey, for his competent advice in the research on substrate analysis and Peter Xiao for his work in superconducting modeling.

I gratefully thank Umakanta Choudhury, Albert Ruehli, Steve Seda, Roberto Guerrieri, John Cohn, Gary Holmlund, Bruce Donecker, and the people of The HP-EEsof Labs in Santa Rosa for the useful technical discussions that inspired much of my work.

I am also in debt with the people of my research group, Giorgio Casinovi, Andrea Casotto, Henry Chang, Steven Edwards, Eric Felt, Alper Demir, Gani Jusuf, Desmond Kirkpatrick, Sriram Krishnan, Alan Kramer, Luciano Lavagno, Chris Lennard, Ed Liu, Robert Neff, Tom Shiple, Greg Uehara, and Tiziano Villa, who contributed to my research with useful discussions, suggestions, and the great work that made Berkeley famous.

I will never forget Paolo Giusto, Andre Nieuwland, Christian Olivier, Jaijeet Roychowdhury, Sunil Khatri, Amit Narayan, and Rajeev Murgai, relentless bachelors, who made me enjoy life like no one before. And of course how to forget the Japanese connection, Nagisa Ishiura, Toshi and Keiko Hattori, Masahiko and Kazuyo Takahashi, Jun Kuroiwa, Atsushi Takahara, Key and Rikako Suzuki, the kindest and most sincere people I ever met.

A special acknowledgement goes to my *Italian family* in the United States, namely Paolo Miliozzi and Ana,  $I\alpha\sigma\omega\nu$   $B\alpha\sigma\iota\lambda\epsilon\iota\sigma\nu$ , and Luca Carloni, friends and colleagues with whom I have had the most exciting and animated political discussions in years.

My friends here in the Bay Area and back in Switzerland have constantly followed and supported my endeavors. Among them I gratefully thank Philippe Schönborn, Remedio and Jacqueline, with whom I shared the happiest moments of the last years, Fabrizio and Linda Della Corte, the closest friends I have from Ticino, Vigyan Singhal, the best roommate I ever had, Luigi Semenzato, the best windsurfer in town, Daniel Engels, the Tahitian emigré, Attila Jurecska, the toughest Hungarian on the planet, the Ranjans and the Sanghavis, who desperately but unsuccessfully tried to invite all of us to their traditional weddings in India, and last but not least Slobodan Simic, Sante Gnerre and the Italian crowd, to whom I will always be grateful for the wonderful time spent together.

I would also acknowledge the good work of our secretaries, Flora Oviedo and Kia Cooper, and our grant administrator, Elise Mills, whom I will always remember as the best and most supportive staff I ever had.

In the course of these years, several institutions supported this research, either directly or indirectly. The Swiss National Science Foundation, Asea Brown Boveri and the Lehmann Foundation contributed substantially to the research that led to this dissertation. Their support was indispensable and is greatly appreciated.

### Chapter 1

### Introduction

Ed ecco verso noi venir per nave

un vecchio, bianco per antico pelo,

gridando: "Guai a voi, anime prave!

Non isperate mai veder lo cielo:

i' vegno per menarvi a l'altra riva

ne le tenebre etterne, in caldo e 'n gelo."

Dante Alighieri, "Inferno", Canto III

### 1.1 Computer-Aided Design of Engineering Systems

The main objective of the discipline known as Design Technology is the creation of methodologies and tools for the design of engineering systems, helping human designers build functionality while satisfying intended performance specifications. Over the past three decades, the development of computer aids for the design of electronic systems (CAD) has been one of the fastest growing areas of activity. In particular, CAD for the physical assembly of electronic systems, either in the form of an integrated circuit (IC) or of a printed circuit board (PCB), has become one of the largest research areas in the field.

Electronic ICs have rapidly evolved from the relatively low complexity of the early days to the high sophistication of today. The task of circuit designers has become increasingly difficult, hence the need for more advanced design supports. In particular, the study of effective methodologies for the physical assembly of high-speed analog and mixed-signal

ICs and of tools supporting it has been a very active topic of research in the past decade. This subject is also the central topic of this dissertation.

### 1.2 Physical Assembly of Analog and Mixed-Signal ICs

In analog systems signals are continuous functions of time. By contrast, in digital systems each signal is represented by a sequence of finite number of binary digits; therefore, these signals can take on discrete values only. Due to the binary nature of signals, digital circuits are realized using gates with only two states, each state being defined in some range of the continuous signal. This makes digital circuits to a large degree immune to various noise and parasitic sources inherent to ICs. Hence, the design effort can be directed mainly towards trade-offs between power consumption, speed, and area.

Analog circuits in general require more design freedom in order to be applied effectively, since the full spectrum of capabilities exhibited by individual devices is exploited. In most analog circuits individual devices have substantially different sizes and electrical characteristics. These circuits require optimization of various performance measures. As an example, among the performance measures for operational amplifiers are gain, bandwidth, noise, power supply rejection, dynamic range, offset voltage, etc. The importance of each performance measure depends on circuit application. For this reason, fine tuning plays a crucial role in the design of analog circuits.

Because of the rather wide range of parameter spreads in ICs, active and passive components, analog designers developed circuits which cancel out the first order variations in key parameters. However, new dependencies from second order variations of design parameters have become dominant. Typical examples are the matching of input devices in differential pairs, or capacitor matching in switch capacitor filters. Sensitivities to second order variations require much more care especially during the circuit's physical assembly, due to the numerous non-idealities and parasitics it may introduce.

For these reasons designing CAD tools for analog applications is, in general, a difficult task. Consequently, while it is sometimes possible to share CAD tools between the digital and analog portions of a circuit, such as design rule checkers, extractors and data bases, there are many tools that must be designed for use primarily on analog circuits. A general and consistent methodology is required to properly guide the tools towards the satisfaction of all specifications at the system level. In addition, design failures must be

interpreted effectively so as to organize appropriate re-design schemes.

Research on analog CAD systems has progressed at a considerably slower pace than that on their digital counterparts. Part of the reason has been the intrinsic difficulty of defining and controlling performance in analog circuits. High performance can be achieved by taking advantage of the physical characteristics of integrated devices and of the correlation between electrical parameters and their variations due to statistical fluctuations of the manufacturing process. Device matchings, parasitics, thermal and substrate effects must all be taken into account. The nominal values of performance functions are subject to degradation due to a large number of parasitics which are generally difficult to estimate with the proper accuracy before an actual layout is completed.

Another reason might be the present difficulty to identify a level of abstraction where generic models such as the ones developed for digital synthesis can be derived. All these concerns need be addressed in each phase of the design with care, since severe performance degradation, even if localized only in some components, can often jeopardize the functionality of the whole system.

### 1.3 Bottom-Up vs. Top-Down Approaches

The approach generally adopted by designers consists of building complex layouts bottom-up, starting from the simplest components of the systems and estimating all component specifications using rough approximations mostly derived from experience. This approach often results in a series of time-consuming design loops, hence multiple re-designs are needed for the whole system.

It is our believe that the design loops could be drastically reduced if a top-down approach were used. In a top-down approach the order of the synthesis phases is reversed. First, top-level specifications are rigorously mapped onto constraints on the physical details of the layout, in such a way that the satisfaction of the low-level constraints implies satisfaction of the overall system specifications. Then, the entire physical assembly, partitioned in its basic steps, module generation, placement, routing and compaction, is performed enforcing all physical constraints. A bottom-up verification step based on extraction concludes the assembly.

There are several advantages to this approach. First, a tight control of performance can be maintained in each phase of the physical assembly independently, hence specification

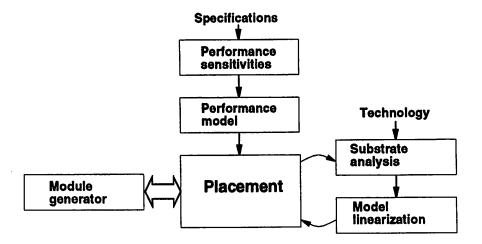

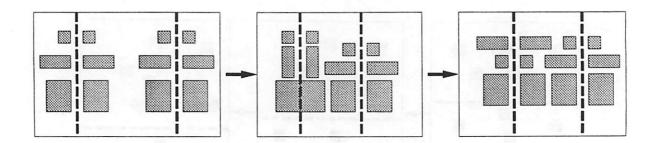

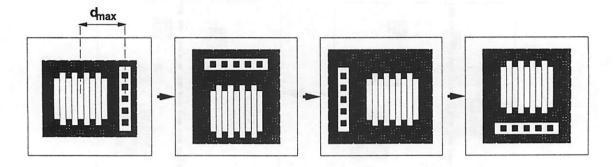

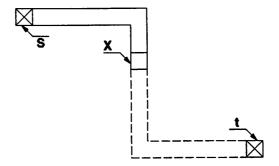

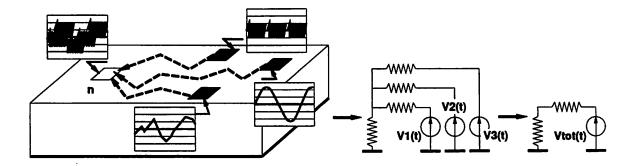

Figure 1.1: Constraint-driven layout design: Traditional design partition into tasks has been modified by adding information paths between layout phases.

violations can be identified early, thus enhancing the robustness of the process. Second, all physical constraints are derived so as to minimize the effort that each layout tool requires for its enforcement, hence improving its efficiency. Finally, due to the generality of the constraint generation process, the scheme can be easily extended to encompass a wide variety of non-idealities usually encountered in layout.

The scheme, called *constraint-driven layout design*, was originally formulated for a class of layout problems and then generalized by us to the extent of physical assembly for analog and mixed-signal ICs. This dissertation presents the generalized constraint-driven layout design methodology and the techniques used for each phase of the physical assembly.

### 1.4 Generalized Constraint-Driven Layout Design

The design flow of the constraint-driven physical assembly system is illustrated in Figure 1.1. First, high-level specifications are translated into a set of bounds on low-level physical constraints. A priori parasitic estimates are used to determine feasible bounds. Among all possible sets of bounds, the one maximizing the flexibility of the tool to be used

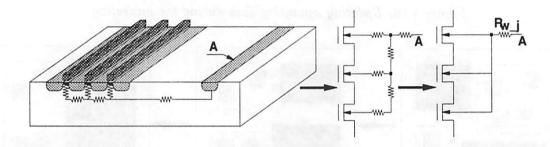

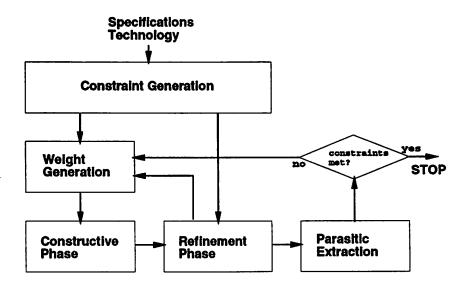

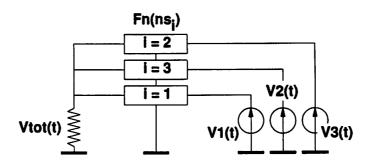

Figure 1.2: The organization of each layout phase. The internal feedback path provides information to the constraint generator. External feedback paths provide information on the reasons of failure to meet performance specifications.

is chosen. Flexibility is a function which measures how easily the tool is able to meet the given set of constraints.

Then at each step, the existence of a feasible configuration is tested, feedback paths are provided to resolve situations of infeasibility. These situations can occur as the result of partially inaccurate estimations on parasitics and other circuit non-idealities at early layout phases due to incomplete information about the physical implementation. In these cases, mechanisms are provided for the re-generation of constraints by correcting a priori estimations.

Each layout phase is organized as illustrated in Figure 1.2. The design task is constrained by a set of input specifications, which are either high-level performance specifications or additional design constraints introduced by other layout phases. Constraints are translated into a set of bounds on parasitics by a *constraint generator*, based on estimates of the feasible values of each parasitic. These bounds drive each tool independently. The

resulting layout is then analyzed to check whether performance specifications have actually been met. If some constraints have been violated, the values of the extracted parasitics can provide more accurate estimates to the constraint generator. The constraint generator also executes the feasibility check. In fact, low-level bounds must be feasible, i.e. they must lay between the minimum and maximum possible values estimated for the parameters. Such early detection of infeasibility provides an efficient control of design iterations, thus minimizing overall computation time. Feedback control paths provide previous design phases with information on those critical parasitics for which it was not possible to determine feasible bounds with the current configuration.

### 1.5 Theoretical Aspects of Constraint-Based Approaches

Any constraint-based approaches to design have the following requirements. First, a performance model must exist in some well defined form. Second, a rigorous method must be used for obtaining a set of constraints on parameters which are controlled during design and/or fabrication. Choudhury [1] used a linear performance model based on sensitivity analysis and formulated the constraint generation process in a form of a constrained quadratic programming approach. The generalization of this approach to encompass a large number of diverse constraints and a wide range of tools was first proposed by us in [2] and will be discussed in this dissertation in full detail.

With this formulation, all performance functions can be represented in a compact and rigorous way, as long as they are continuous and sufficiently regular in an interval around their nominal value. Accurate and efficient calculation of sensitivities is key to the viability of the approach. For this reason a great importance will be given to the accuracy and efficiency issues associated with parasitic estimation and performance evaluation.

We will discuss techniques for the calculation of constraints suitable for all the phases of the physical assembly and for their enforcement at all levels of design. Moreover, constraint-based techniques will be proposed and evaluated for the simplification of layout analysis both at the schematic and at the physical extraction level.

### 1.6 Organization of the Dissertation

In chapter 2 the state-of-the-art in CAD tools and systems for analog and mixed-signal circuits is surveyed. Chapter 3 presents an overview of sensitivity analysis and of the techniques for the mapping of high-level specifications onto low-level physical constraints. All the details of the constraint generator PARCAR are described in this chapter. In chapters 4, 5 and 6 the physical design tool-set is presented. Chapter 7 deals with the final extraction and verification steps in the design loop, while chapter 8 addresses issues related to the synthesis and analysis of ICs in the presence of substrate-related interference currents. Experimental results on industrial-strength benchmarks are reported in chapter 9, followed by conclusions in chapter 10.

### Chapter 2

### Literature Survey

"O tu ch'onori scienzia e arte, questi chi son c'hanno cotanta onranza, che dal modo de li altri li diparte?".

E quelli a me: "L'onrata nominanza che di lor suona sù ne la tua vita, grazia acquista in ciel che sì li avanza".

Dante Alighieri, "Inferno", Canto IV

### 2.1 The Origins of Computer-Aided-Design

#### 2.1.1 Circuit Simulation

The last three decades have seen a tremendous increase in the complexity and sophistication of electronic systems. Designing to realize functionality while meeting a set of performance specifications, soon required tools capable of overcoming relatively inaccurate and lengthy hand analysis. Not surprisingly the first developed computer aids addressed the problem of circuit simulation and verification.

In the early 1950's digital computers started being actively utilized, for the solution of simultaneous algebraic equations describing linear electrical networks in sinusoidal steady state [3]. However only a decade later, the first viable programs were developed for the simulation of circuits in time-domain. Net1 [4] and Sceptre [5] used explicit-integration

and predictor-corrector techniques in the solution of integral-differential equations of non-linear systems. To maintain stability however, very small time steps were needed, hence significantly increasing the time needed to converge to a solution. Only in the mid 1960's, with the introduction of implicit integration schemes, that superior performance could be achieved. In implicit integration, the set of integral-differential equations turns to a set of static algebraic equations for each given time point. The program TRAC [6] implemented these techniques. Almost simultaneously, a second-order implicit-integration scheme was proposed which proved a better performance relative to TRAC. This research led to CIRPAC [7] and to other modifications to the method that included variable order and variable time-step implicit integration routines [8].

In the late 1960's, Howard developed a program that solved numerically a set of simultaneous nodal equations. A simple non-linear device model was used and the equations were linearized at the equilibrium using iterative methods based on Newton-Raphson and excursion limiting techniques [9]. In an independent research effort starting from a theoretical base took place at approximately the same time. Hachtel proposed a new formulation of network equations based on the Sparse-Tableau concept [10]. This approach, allowing the use of efficient techniques for the solution of large systems of linear equations, led to the development of ASTAP [11].

The experience accumulated from these research teams was eventually incorporated in the CANCER [12] and the SLIC [13] projects. With the formalization of Modified Nodal Analysis and the development of sparsity-aware pivoting and matrix reordering techniques, the CANCER project evolved into the SPICE program [14].

### 2.1.2 Digital Timing Analysis and Event-Driven Simulation

Following the enormous success of SPICE and the increasing importance of electrical simulation in circuit design, research in the field developed in two main directions: large-scale simulation and optimization. Early techniques, reviewed in [15], gave way to approaches purposedly relaxing accuracy to achieve greatly improved simulation speed [16]. These methods, conceived for digital timing analysis, soon showed limitations in accurately simulating the effects of feedback. It was the study of numerical limitations in timing analysis that led to new techniques based on relaxation in both space and time domain. The main advantage of relaxation-based approaches is the ability of exploiting time sparsity, us-

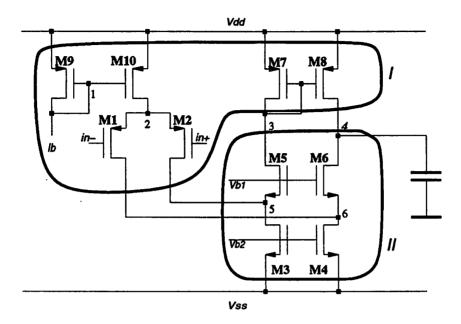

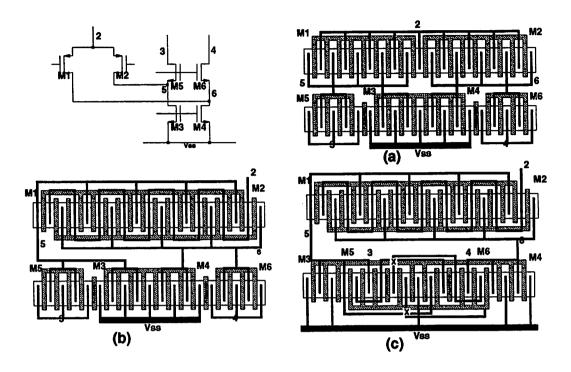

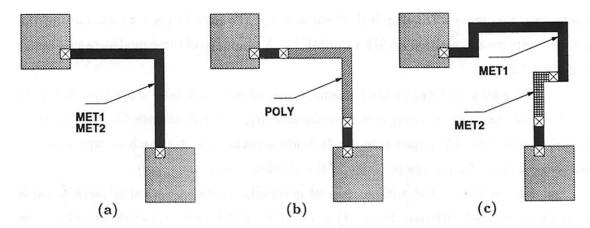

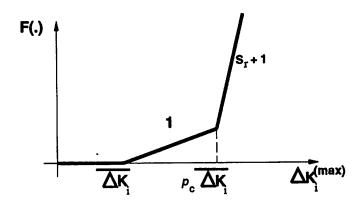

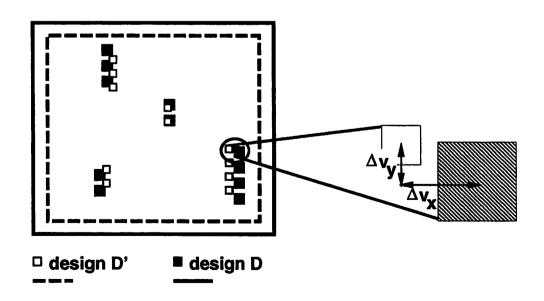

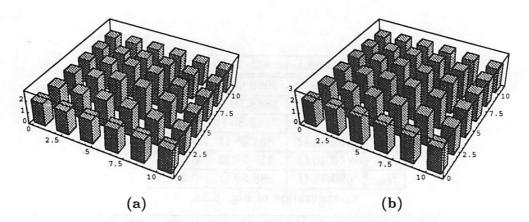

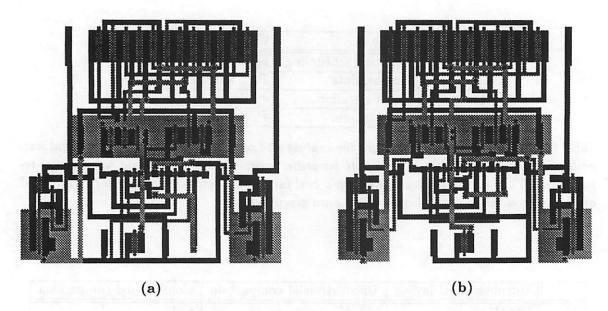

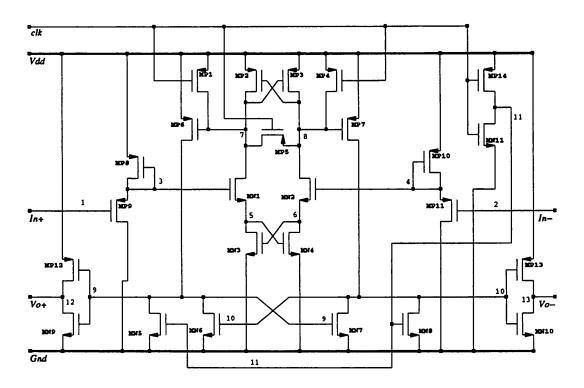

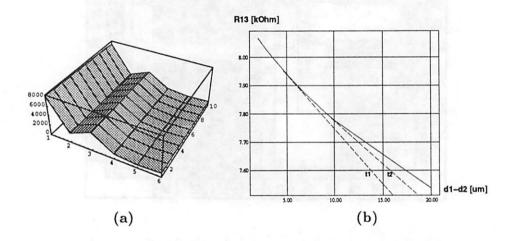

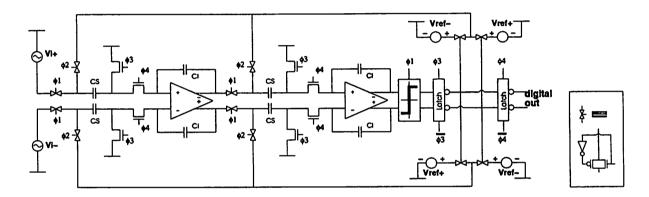

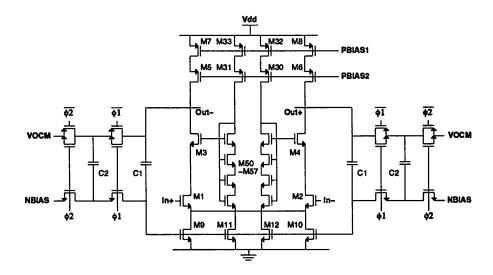

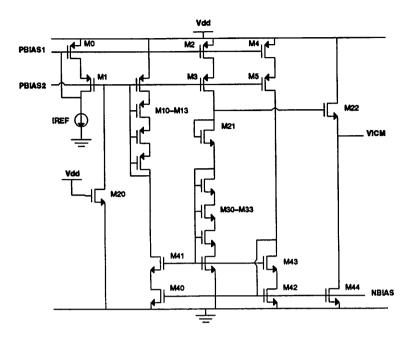

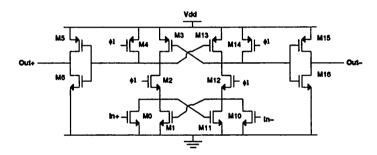

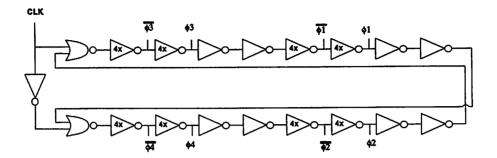

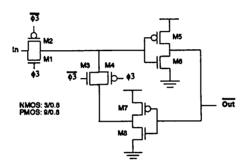

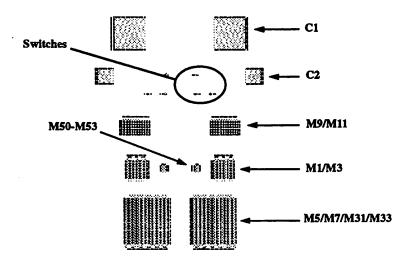

ing the event-driven selective trace techniques first developed in digital simulators. Shortly after the development of timing simulation, mixed-mode or hybrid event-driven simulators emerged, resulting in extensive research in the field [17, 18, 19]. For a review in the field see e.g. [20, 21, 22].