# Copyright © 1993, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# DESIGN-ORIENTED MIXED-LEVEL CIRCUIT AND DEVICE SIMULATION

by

David Alan Gates

Memorandum No. UCB/ERL M93/51

23 June 1993

# DESIGN-ORIENTED MIXED-LEVEL CIRCUIT AND DEVICE SIMULATION

Copyright © 1993

by

David Alan Gates

Memorandum No. UCB/ERL M93/51

23 June 1993

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### **Abstract**

## Design-Oriented Mixed-Level Circuit and Device Simulation

bу

#### David Alan Gates

Doctor of Philosophy in Electrical Engineering

University of California at Berkeley

Professor Ping K. Ko, Chair

Integrated circuits (ICs) are the building blocks of modern computing and communication systems. The design of high complexity ICs has been enabled by the development of a large number of computer-aided design (CAD) tools for IC design (ICCAD). Mixed-level circuit and device simulation has begun to find its place as a CAD tool for the development of new IC technologies. In this dissertation, problems associated with providing support for mixed-level circuit and device simulation in an expanded role as an ICCAD tool are investigated.

Four issues of concern for a mixed-level simulator have focused this research: reliability, utility, portability, and performance. A new mixed-level circuit and device simulator called CIDER has been developed to address these concerns. The first three concerns are addressed in a serially executing version of CIDER. To obtain reliable simulation results, new models for physical effects that are important in present-day IC technologies are included in CIDER. An enhanced user-interface has been developed to increase the utility of CIDER. Finally, CIDER has been ported to a variety of engineering workstations.

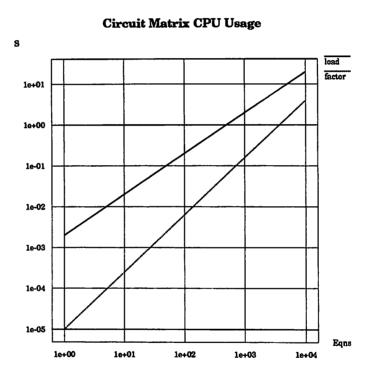

The final concern, performance, is addressed in a version of CIDER that runs on distributed-memory multicomputers. The need for parallel computing is established by measuring the serial performance of CIDER. Single workstations are roughly 10 to 100 times too slow to support design of reasonably sized circuits.

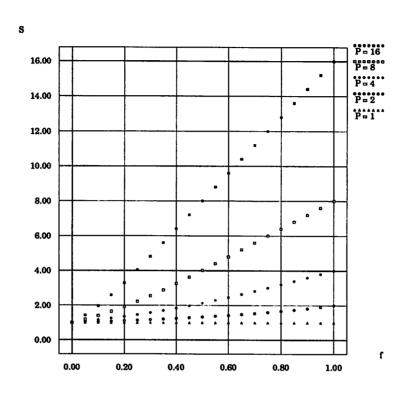

Algorithms for exploiting parallelism in mixed-level simulation are reviewed, and an architecture is proposed for a parallel circuit and device simulator. A limited form of the proposed approach has been implemented on two multicomputers: a hypercube supercomputer and a cluster of engineering workstations. On a set of benchmark

circuits, a best speedup of 12 on 16 processors of the hypercube is achieved. Unfortunately, the implemented approach has a number of limitations that are identified here for the first time.

Several applications of CIDER are presented that demonstrate the new parallel capability. In each application, the circuits contain multiple numerically modeled devices. The hypercube version of CIDER is used to simulate these circuits in a reasonable amount of time. New insight into these circuits is obtained by examining simulation results.

Ping K. Ko Thesis Committee Chairman

## **Contents**

| Li | ist of         | Figur  | res                                                      | iv |

|----|----------------|--------|----------------------------------------------------------|----|

| Li | List of Tables |        |                                                          | vi |

| 1  | Intı           | roduct | ion                                                      | 1  |

|    | 1.1            | Motiv  | ation                                                    | 1  |

|    | 1.2            | Resea  | rch Goals                                                | 3  |

|    | 1.3            | Organ  | nization of the Dissertation                             | 5  |

| 2  | Mix            | ed-Le  | vel Circuit and Device Simulation                        | 7  |

|    | 2.1            | Overv  | riew                                                     | 7  |

|    | 2.2            | Circui | it Simulation                                            | 7  |

|    |                | 2.2.1  | Circuit Description and Equation Formulation             | 8  |

|    |                | 2.2.2  | The Circuit Operating Environment                        | 9  |

|    |                | 2.2.3  | DC Analysis                                              | 9  |

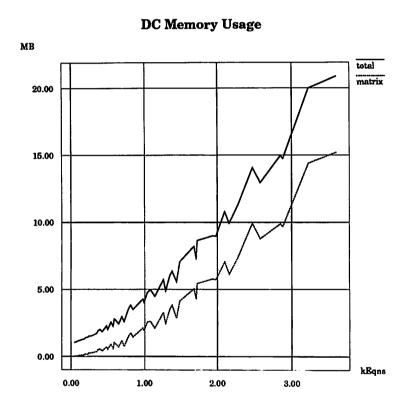

|    |                | 2.2.4  | Transient Analysis                                       | 11 |

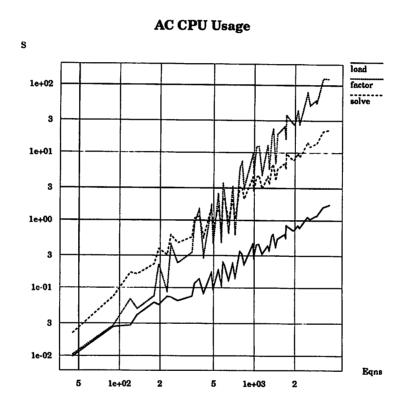

|    |                | 2.2.5  | Small-Signal AC Analysis                                 | 12 |

|    |                | 2.2.6  | Visualization and Representation of Circuit Behavior     |    |

|    | 2.3            | Device | e Simulation                                             |    |

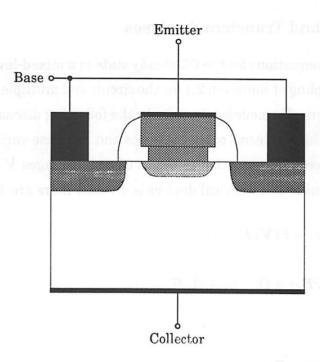

|    |                | 2.3.1  | Device Description                                       | 14 |

|    |                | 2.3.2  | Semiconductor Device Equations                           | 15 |

|    |                | 2.3.3  | External Device Boundary Conditions                      | 17 |

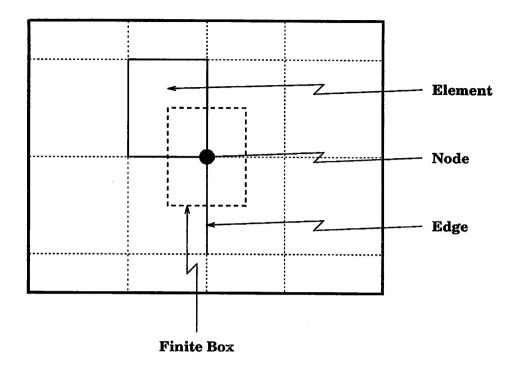

|    |                | 2.3.4  | Scaling and Space Discretization                         | 18 |

|    |                | 2.3.5  | DC and Transient Analyses                                | 20 |

|    |                | 2.3.6  | Small-Signal AC Analysis                                 | 22 |

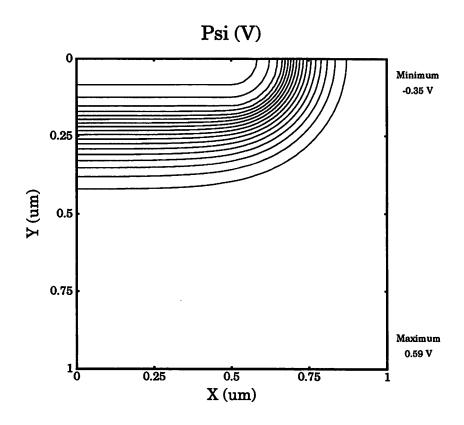

|    |                | 2.3.7  | Visualization and Representation of Device Behavior      |    |

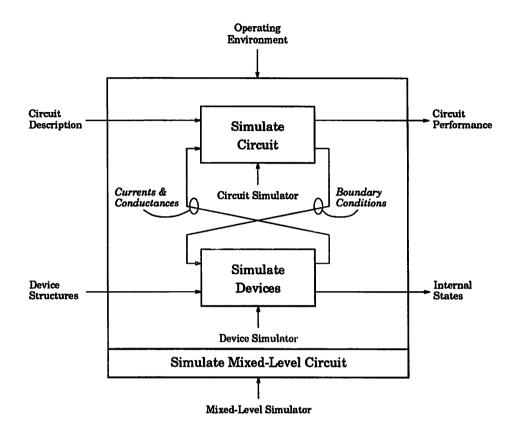

|    | 2.4            | Mixed  | l-Level Circuit and Device Simulation                    |    |

|    |                | 2.4.1  | Coupled Circuit and Device Description                   |    |

|    |                | 2.4.2  | Coupled Operating Conditions                             | 28 |

|    |                | 2.4.3  | DC and Transient Analyses                                |    |

|    |                | 2.4.4  |                                                          |    |

|    |                | 2.4.5  | Visualization and Representation of Mixed-Level Behavior |    |

|    | 2.5            |        | nary                                                     |    |

#### CONTENTS

| 3 | Per         | formance Analysis of CIDER 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3  |

|---|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 3.1         | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3  |

|   | 3.2         | Runtime Breakdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4  |

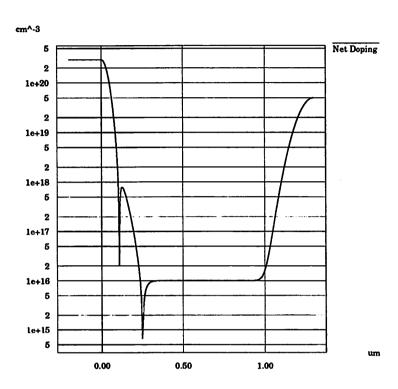

|   | 3.3         | Device-Level Resource Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5  |

|   |             | 3.3.1 One-Dimensional Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5  |

|   |             | 3.3.2 Two-Dimensional Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _  |

|   | 3.4         | Benchmark Circuit Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|   | 3.5         | Performance Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -  |

|   |             | 3.5.1 Estimated Problem Specifications 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _  |

|   |             | 3.5.2 Estimated Resource Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|   |             | 3.5.3 Assessment of Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _  |

|   | 3.6         | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _  |

|   |             | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _  |

| 4 |             | allel Circuit and Device Simulation 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|   | 4.1         | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _  |

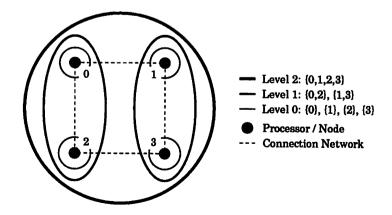

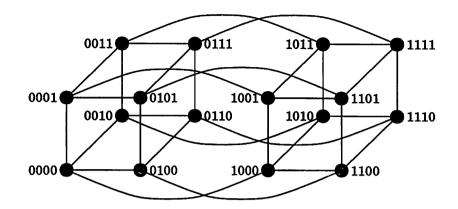

|   | 4.2         | Terminology for Parallel Computer Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 4.3         | Obtaining High Parallel Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

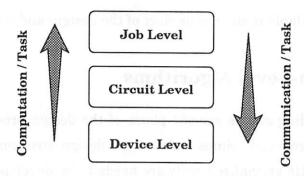

|   | 4.4         | Available Parallelism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|   | 4.5         | Design-Level Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _  |

|   | 4.6         | Circuit-Level Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|   |             | 4.6.1 Parallel Model Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   |             | 4.6.2 Parallel Sparse System Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -  |

|   | 4.7         | Device-Level Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8  |

|   |             | 4.7.1 Parallel Element Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9  |

|   |             | 4.7.2 Distributed Multifrontal Factorization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1  |

|   | 4.8         | Mixed-Level Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4  |

|   |             | 4.8.1 Previous Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5  |

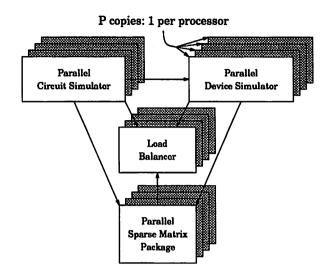

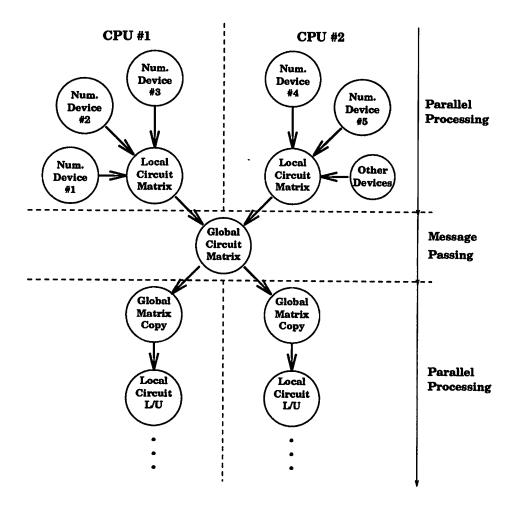

|   |             | 4.8.2 Proposed Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5  |

|   |             | 4.8.3 Advantages and Disadvantages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8  |

|   |             | 4.8.4 Software Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9  |

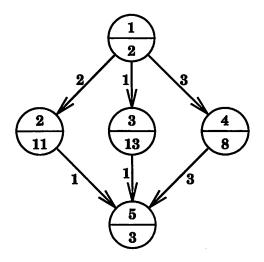

|   | 4.9         | Mixed-Level Partitioner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1  |

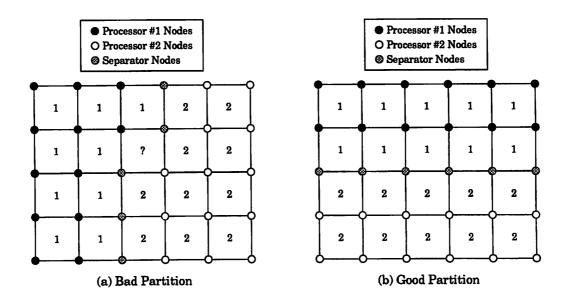

|   |             | 4.9.1 Multi-Level Partitioning Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1  |

|   |             | 4.9.2 Solution Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )2 |

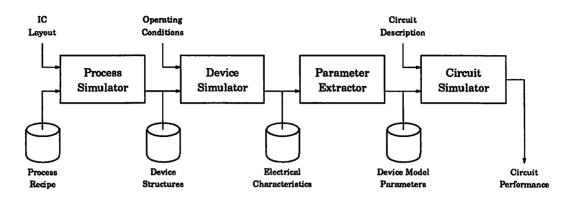

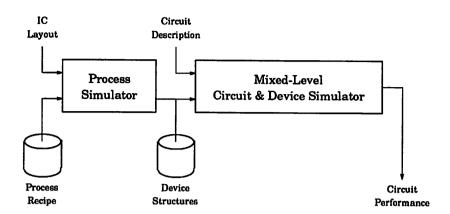

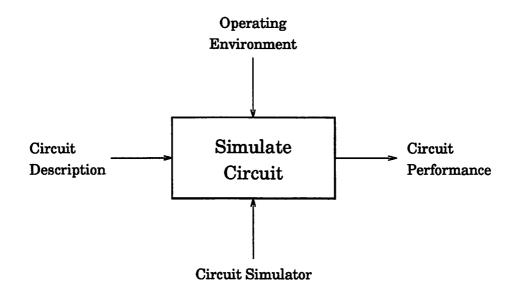

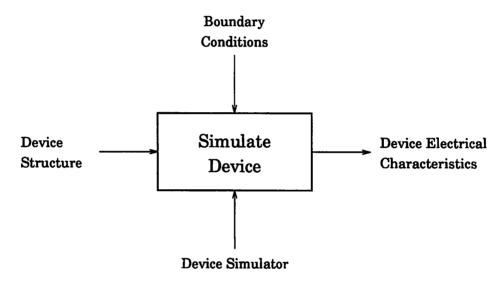

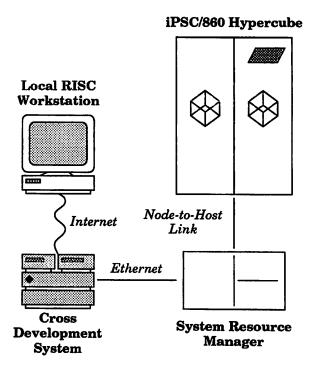

|   |             | 4.9.3 Trial Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | )4 |