## Copyright © 1992, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## A UNIFIED SIGNAL TRANSITION GRAPH MODEL FOR ASYNCHRONOUS CONTROL CIRCUIT SYNTHESIS

by

Alexandre Yakovlev, Luciano Lavagno, and Alberto Sangiovanni-Vincentelli

Memorandum No. UCB/ERL M92/78

20 July 1992

# A UNIFIED SIGNAL TRANSITION GRAPH MODEL FOR ASYNCHRONOUS CONTROL CIRCUIT SYNTHESIS

by

Alexandre Yakovlev, Luciano Lavagno, and Alberto Sangiovanni-Vincentelli

Memorandum No. UCB/ERL M92/78

20 July 1992

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## A UNIFIED SIGNAL TRANSITION GRAPH MODEL FOR ASYNCHRONOUS CONTROL CIRCUIT SYNTHESIS

by

Alexandre Yakovlev, Luciano Lavagno, and Alberto Sangiovanni-Vincentelli

Memorandum No. UCB/ERL M92/78

20 July 1992

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

This work is supported by the University of Colorado subcontract grants BS0016421 and BS0036038.

## A Unified Signal Transition Graph Model for Asynchronous Control Circuit Synthesis

Alexandre Yakovlev

Dept. of Computing Science

The University

Newcastle upon Tyne, NE1 7RU

United Kingdom

Luciano Lavagno

Dept. of Electrical Engineering

University of California

Berkeley, CA 94720

Alberto Sangiovanni-Vincentelli Dept. of Electrical Engineering University of California Berkeley, CA 94720

July 20, 1992

#### **Abstract**

Characterization of the behavior of an asynchronous system depending on the delay of components and wires is a major task facing designers. Some of these delays are outside the designer's control, and in practice may have to be assumed unbounded. The existing literature offers a number of analysis and specification models, but lacks a unified framework to verify directly if the circuit specification admits a correct implementation under these hypotheses.

Our aim is to fill exactly this gap, offering both low-level (analysis-oriented) and high-level (specification-oriented) models for asynchronous circuits and the environment where they operate, together with strong equivalence results between the properties at the two levels. One interesting side result is the precise characterization of classical static and dynamic hazards in terms of our model. Consequently the designer can check the specification and directly decide if the behavior of any implementation will depend, e.g., on the delays of the signals described by such specification.

We also outline a design methodology based on our models, pointing out how they can be used to select appropriate high and low-level models depending on the desired characteristics of the system.

#### 1 Introduction

Formal methods and CAD support for synthesis of asynchronous control circuits have become an important issue in VLSI design, as designers are tackling the most difficult problems of system-level design, such as inter-component interfacing, where asynchronous circuits are inevitable.

The asynchronous circuit designer must face two major problems in his work:

- Specify in a clear and unambiguous way the desired behavior of the system.

- Implement that behavior correctly. The asynchronous circuit behavior depends heavily on the *delay* of the components and the interconnecting wires. Only some of these delays are under the designer's control, and can be used (often with a non-trivial effort) to achieve a correct implementation of the specified behavior. Some delays depend on the *environment*, and/or some signals must travel on long busses, and no reliable assumption can be made on those delays.

The existing literature describes models to solve both these problems separately. Namely a number of high-level specification techniques for control-oriented asynchronous circuits have recently become available (see, for example, [4, 15, 16], [25, 11, 12]). Among them Signal Transition Graphs (STGs) based on Petri nets as an underlying formalism, have captured wide attention, due to a simple yet powerful mechanism to describe explicitly the major aspects of asynchronous control circuit behavior, such as concurrency, causality and conflict ([20] and [5]). Furthermore, all these models (unlike

older ones, as Flow Tables [22]) allow to specify the system in its interaction with the environment, which is also crucial for control, reactive hardware.

On the other hand, a number of *analysis* models (see [3] for a thorough review) allow the designer to verify, for example, if the circuit will or will not have *hazards* during its operation, or if, depending on the relative magnitude of the delay of two components, it may "hang" forever in an invalid state. In classical, informal terms, a circuit that operates correctly independently of the delays of each component is called *speed-independent*, while one that operates correctly independent of the delays of each interconnecting wire is called *delay-insensitive*.

These circuit models, though, are defined only for circuits built out of components whose output signal behavior can be characterized as a *Boolean function* of a set of input signals. Such class of circuits excludes some very useful components, for example fair arbiters, that cannot be described by such interconnections of Boolean functions. Moreover it does not allow for *behavioral abstraction*, by modeling some component using *non-determinism* rather than explicitly describing its operation in detail. For example, it is much easier to describe a CPU interacting with a bus interface as a device that can non-deterministically read or write, rather than deterministically describe its instruction memory, program counter, etc. Modeling the CPU as alternating between read and write cycles may not be acceptable either, since the interaction between successive, pipelined cycles can be non-trivial.

Moreover there is no known general methodology to decide whether a given STG specification admits an implementation that is, for example, hazard-free, or speed-independent, or delay-insensitive. And there is no satisfactory characterization of the above properties if the delays are pure (i.e. a translation in time of the input waveform) rather than inertial (i.e. short "pulses" are not transmitted). The only effort in this direction, to the best of our knowledge, is the so-called Change Diagram representation, that was shown in [25] to be formally equivalent to hazard-free circuits under the unbounded inertial gate delay model. Change Diagrams, however, are not general enough, in that they can represent concurrency and causality, but not conflict, i.e. they can model only deterministic behavior, and as such the description, for example of a bus protocol with different read and write phases is awkward and imprecise, as we informally argued above.

Furthermore the classical definition of a "valid" Signal Transition Graph specification is unnecessarily restrictive, as [28] showed by presenting some useful, correctly implementable behaviors that cannot be described using the constrained STGs used by Chu in [5]. For example Chu required the Petri net underlying the STG to be safe, live and free-choice, in order to ease the STG analysis/synthesis task. This requirement is not part of the STG definition per se, and has nothing to do with a deeper characterization of the STG behavior as, say, speed-independent or delay-insensitive.

In this paper we approach the problems mentioned above in the most general way, in the following steps.

- Give a general, low-level model of the *structure* and *behavior* of an asynchronous structure (where with the term "asynchronous structure", or sometimes "asynchronous system", we mean an interconnection of basic components that may be more complex than standard logic gates). This model, called Asynchronous Control Structure (ACS), allows multi-output components, non-determinism, etc. The *structure* of the ACS is a labeled, directed graph, while its *behavior* is described by a state-transition-like representation, that describes the events that can occur in every state, and the corresponding next state of the system (Arc-Labeled Transition System, ALTS). We need a structural model because fundamental aspects of asynchronous design, such as delays, are associated with the structural components of the system.

- Describe how a special case of ACS, where each component has one output and is described by a Boolean function, corresponds to the classical model of an asynchronous circuit. The corresponding ALTS behavior specification now is determined by those Boolean functions changing the values of the circuit outputs in response to input and output signal transitions.

- Relate the local and global properties of the ALTS of a circuit with known low-level properties of the circuit, such as

hazards, speed-independent operation, etc., both under inertial delays and pure delays. In order to establish formally

this correspondence, we will have to introduce some auxiliary formalisms that capture the "history" of the circuit, beside

its "current state", and show how this "history" relates to significant properties of the state-based ALTS description

- Give a general high-level model of the behavior of an asynchronous system (the associated structure will be described

using the same graph-like representation as in the low-level model). This model, the Signal Transition Graph, will

not have unnecessary restrictions superimposed, to allow us to prove the correspondence between low-level ALTS

properties (and hence circuit properties) and high-level STG properties.

At this point the designer can use the framework to verify if a specification meets some circuit-level requirements, or, conversely, given a set of circuit-level properties, what class of specifications needs to be used.

| ACS  | Asynchronous Control Structure        | Structural model of asynchronous systems                    |

|------|---------------------------------------|-------------------------------------------------------------|

| BACS | Binary Asynchronous Control Structure | Binary version of ACS                                       |

| TS   | Transition System                     | Uninterpreted state-transition based behavioral model       |

| ALTS | Arc-Labeled Transition System         | TS with transitions interpreted as signal value changes     |

| STD  | State-Transition Diagram              | ALTS with binary-labeled states                             |

| CD   | Cumulative Diagram                    | Cumulative history of transitions in the system             |

| ALC  | Asynchronous Logic Circuit            | Structural/behavioral model of asynchronous circuits        |

| PD   | Pure Delay                            | All input changes are transmitted to the output             |

| ID   | Inertial Delay                        | Pulses shorter than the delay magnitude are not transmitted |

| PN   | Petri net                             | Uninterpreted event-based behavioral model                  |

| STG  | Signal Transition Graph               | PN with transitions interpreted as signal value changes     |

Table 1: Principal abbreviations used in the paper

Note that the paper is not concerned with the details of how each component will be implemented in a specific technology. The main concern is to analyze properties that are common to every implementation of the specified behavior, using a model that is general enough to abstract various different implementation techniques, but detailed enough to have practical relevance. Such component implementation issues are dealt with elsewhere (see, for example, [8], [13], [1]).

The paper is organized as follows. Section 2 defines the low-level structural and behavioral model of asynchronous systems, called Asynchronous Control Structure and Arc-Labeled Transition System, together with the related trace and partial order models. Section 3 describes Asynchronous Logic Circuits, a special cases of Asynchronous Control Structures, and relates properties of the two, underlining the effects of the inertial/pure delay model dichotomy. Section 4 defines Signal Transition Graphs as interpreted Petri nets and describes the problem of their implementation in Asynchronous Logic Circuits. Section 5 presents a classification of Signal Transition Graphs according to the corresponding Asynchronous Logic Circuit properties. Section 6 compares the Change Diagram model proposed in [25] with the STG model. Section 7 outlines a design methodology based on our models. Section 8 concludes the paper.

To help the reader remember the numerous abbreviations used throughout the paper, we have collected them in Table 1, together with a brief summary of their meaning.

#### 2 A Low-level Structural and Behavioral Model for Asynchronous Systems

This section introduces a low-level, *state-transition-based*, model of asynchronous systems. It has two *components*: a *structural* component called Asynchronous Control Structure (ACS) and an associated *behavioral* component to describe its evolution in time, the Arc-Labeled Transition System (ALTS).

The combination of the two (ACS and ALTS) is somewhat similar<sup>1</sup> to a network of interacting asynchronous Finite State Machines (the structure, describing who communicates with whom) together with a State Table describing the behavior of the entire system, where each state is the product of the states of each machine, and transitions correspond to allowed change of values on the interconnecting signals.

The properties of the model are characterized using the concept of Cumulative Diagram, that records the history of changes of each signal in the Asynchronous Control Structure. We then give an example of the power of our model using an asynchronous fair arbiter, that would be impossible to describe using "standard", Boolean-function based, models of asynchronous circuits.

#### 2.1 Asynchronous Control Structures

The notion of Asynchronous Control Structure (ACS) is a generalization of the "interconnection structure" of an asynchronous control circuit. It removes the usual structural limitation (used, e.g. by [17] or [22]) that each component has exactly one output signal. Thus an ACS structure can represent an arbitrary interconnection of modules, with the only restriction that no two modules can drive a single signal<sup>2</sup>. The *behavior* of this interconnection of modules will be described using an Arc-Labeled Transition System, as shown in Section 2.2.

<sup>&</sup>lt;sup>1</sup>This analogy should not be taken literally, and is only given to help the reader understand the general idea of the approach.

<sup>&</sup>lt;sup>2</sup>I.e. no wired-or or wired-and constructs are allowed, but note that at this level of abstraction they can still be modeled using discrete gates.

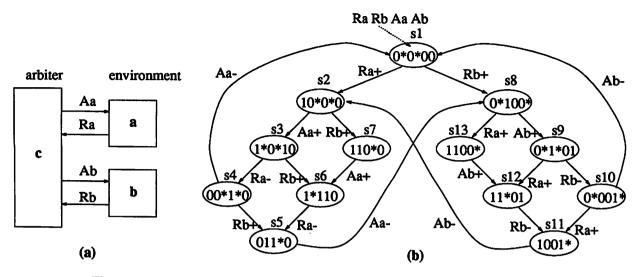

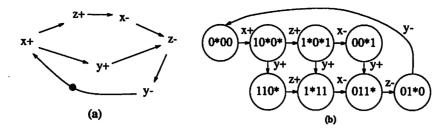

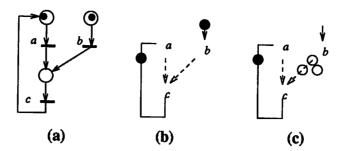

Figure 1: A Binary Asynchronous Control Structure and its State Transition Diagram

Formally, an Asynchronous (Discrete) Control Structure (ACS) is a directed graph  $\langle V, H, Y, \rho \rangle$ , where V is a finite set of *nodes*, associated with the abstract discrete components of the ACS,  $H, H \subseteq V \times V$  is a finite set of *arcs*, standing for the *interconnections* between the components,  $Y = \{y_1, ..., y_n\}$  is a finite set of finite-state *variables*, or *signals*, and  $\rho : H \to Y$  is a *labelling* (total) function, associating every arc with a variable. Any two arcs labelled with the same variable must have the same source node (i.e. they represent a branching interconnection), so formally  $\forall (v_1, v_2), (v'_1, v'_2) \in H$  we must have  $\rho(v_1, v_2) = \rho(v'_1, v'_2) \Rightarrow v_1 = v'_1$ .

We also denote the sets of input and output interconnections for a component v as:  $I^H(v) = \{(v', v) \in H\}$ , and  $O^H(v) = \{(v, v') \in H\}$ , respectively. The sets of input and output signals, or simply inputs and outputs, for a component are denoted:  $I^Y(v) = \{y : \rho^{-1}(y) \in I^H\}$ , and  $O^Y(v) = \{y : \rho^{-1}(y) \in O^H\}$ , respectively.

A simple example of an ACS is described in Figure 1.(a). Here  $V = \{a, b, c\}$ ,  $H = \{(c, a), (a, c), (c, b), (b, c)\}$ ,  $Y = \{R_a, R_b, A_a, A_b\}$ , and  $\rho(c, a) = A_a$ ,  $\rho(a, c) = R_a$ ,  $\rho(c, b) = A_b$ ,  $\rho(b, c) = R_b$ . Furthermore  $I^H(c) = \{(a, c), (b, c)\}$ ,  $I^Y(c) = \{R_a, R_b\}$ , and so on.

For every variable  $y \in Y$ ,  $S(y) = \{y^0, y^1, ..., y^k\}$  is called the set of variable values, or states.

An ACS  $(V, H, Y, \rho)$  is called a *Binary Asynchronous Control Structure* (BACS) if  $\forall y : S(y) = \{0, 1\}$ . Hence, for a BACS, the set of allowed changes can be denoted as  $Y \times \{+, -\}$ , where "+" stands for a signal change from 0 to 1, and "-" for a signal change from 1 to 0. The *behavior* of a BACS is defined by a *binary transition system*, called state transition diagram, which is introduced in the following section.

## 2.2 Transition Systems and State Transition Diagrams

This section describes how the interconnected components of an ACS behave in time, that is how the variables associated with them change, using some key concepts from [10].

A Transition System (TS) is a pair (S, E), where S is a set of *states*, and  $E, E \subseteq S \times S$ , is a set of *transitions*. Note that we do not restrict S and E to be finite. The directed graph representation of a TS is as usual: states are vertices and transitions are arcs. For example, in Figure 1.(b)  $S = \{s_1, \ldots, s_{13}\}$  and  $E = \{(s_1, s_2), (s_1, s_3), \ldots\}$ . We denote  $(s_1, s_2) \in E$  by  $s_1 E s_2$ .

An Arc-Labelled Transition System (ALTS) is a quadruple  $\langle S, E, A, \delta \rangle$ , where  $\langle S, E \rangle$  is a TS, A is a finite alphabet of actions and  $\delta: E \to A$  is a (total) labelling function, which assigns each transition a single action name in A. Each action name represents a change of value of a variable in the associated ACS, and each (possibly infinite) path along the graph represents a valid sequence of such changes in time. Thus the ALTS describes the complete allowed behavior of the associated ACS. For example, in Figure 1 we have  $A = \{R_a^+, R_a^-, A_a^+, A_a^-, R_b^+, R_b^-, A_b^+, A_b^-\}$ , where we use  $A_a^+$  to denote the change of signal  $A_a$  from 0 to 1, and  $A_a^-$  to denote the change from 1 to 0. Furthermore  $\delta(s_1, s_2) = R_a^+$ ,  $\delta(s_2, s_7) = R_b^+$ , and so on.

For a BACS with a set of variables Y (|Y| = n) we define a Binary (encoded) Transition System, or State Transition Diagram (STD),  $\langle S, E, \lambda \rangle$ , where  $\langle S, E \rangle$  is a TS and  $\lambda : S \to \{0, 1\}^n$  is a (total) labelling function such that each state is encoded with a binary vector consisting of the values of Boolean variables. The *i*-th component of the vector associated with

each state s is denoted as  $\lambda(s)_i$ , but for simplicity, unless it creates confusion, we generally use the simpler notation  $s_i$ . An STD is called *contradictory* if  $\lambda$  is not injective. Hence for a non-contradictory STD we can identify the state with its binary label.

For every STD arc, connecting a pair of states s and s', we allow s and s' to differ in one and only one component, say the i-th. This component variable,  $y_i$ , is called *excited* in state s and its value  $s_i$  is marked with a "\*" in s. Since there can be several outgoing arcs from each state, a number of variables can be excited in it. The variables that are not excited in a state are called *stable* in it. We assume that transitions between the states can have *arbitrary but finite delays*, and that these delays are associated with the delays of the components in the modeled BACS (similar to the *gate delay model* in asynchronous circuits, Section 3.2). We call an STD *initialized* if it has an explicit initial state. For example, in Figure 1.(b)  $Y = \{R_a, A_a, R_b, A_b\}$ , and  $\lambda(s_1) = 0000$ ,  $\lambda(s_5) = 1000$  and so on. Furthermore,  $R_a$  and  $R_b$  are excited and  $A_a$  and  $A_b$  are stable in  $s_1$ .

Note that every STD can be also interpreted as an Arc-Labelled Transition System, with the following labelling (consistent, since exactly one variable changes in every arc of an STD):

$$\forall e = (s, s') \in E : \delta(e) = \begin{cases} y_i^+ & \text{if } s_i = 0 \text{ and } s_i' = 1 \\ y_i^- & \text{if } s_i = 1 \text{ and } s_i' = 0 \end{cases}$$

The following important property of any STD comes directly from its definition:

Property 2.1 No state in an STD can have two outgoing transitions labelled with the same variable but with different signs.

We can now examine more in detail the meaning of Figure 1. It represents the interconnection of an *arbiter* and two other components (the arbiter's *environment*), that independently of each other may request access to a single resource, with signals,  $R_a$  and  $R_b$ . The arbiter grants access with  $A_a$  and  $A_b$  (which are mutually exclusive).

Note that this BACS/STD pair specifies a *fair* behavior, because if the arbiter receives a request at one input, say  $R_a$ , while it is processing a previous request from  $R_b$ , then it must, after finishing the transaction for  $R_b$ , respond to  $R_a$  before it can react to a new request from  $R_b$  again. Our abstract arbiter is capable of distinguishing the order in which the two, possibly concurrent, requests arrive at its inputs, by going to two different states ( $s_7$  and  $s_{13}$ ), labelled with the same vector 1100 (hence the STD is contradictory).

#### 2.2.1 Reachability and Unique Action Relations

Intuitively, a state  $s_2$  of a TS  $\langle S, E \rangle$  is reachable from a state  $s_1$  if there exists a directed path from  $s_1$  to  $s_2$ . More formally, the *direct reachability* relation is simply given by the set E. For any pair of states  $s, s' \in S$ , the state s' is called reachable from s if there is a finite length (including zero length) sequence of transitions leading from s to s'. Therefore reachability is given by reflexive and transitive closure of E, i.e.  $E^*$ . In the example of Figure 1.(b) all states are mutually reachable.

Similarly for any ALTS  $\langle S, E, A, \delta \rangle$  we can define the reachability through a sequence of actions. Specifically, for direct reachability through action  $a, a \in A$ , we have sE(a)s' if sEs' and  $\delta(s,s')=a$ . For example in Figure 1.(b) we have  $s_1E(R_a^+)s_2$ . For general reachability through a sequence of actions,  $sE(\alpha)s'$  would imply that there is a finite sequence of action names  $\alpha \in A^*$ ,  $\alpha = a_1, a_2, ..., a_m$  such that  $sE(a_1)s^1, s^1E(a_2)s^2, ..., s^{m-1}E(a_m)s'$ . We can sometimes use the notion of an allowed sequence from a state, i.e.  $\alpha$  is allowed from s if  $\exists s'$  such that  $sE(\alpha)s'$ . So  $R_a^+, A_a^+, R_b^+$  is allowed in  $s_1$ , but it is not allowed in  $s_2$  in Figure 1.(b)

Note also that among the various arcs labelled with the same action in Figure 1.(b), some of them actually represent exactly the same "event". For example, arcs  $(s_2, s_3)$  and  $(s_7, s_6)$  both represent the same event, the arbiter acknowledging request  $R_a^+$  from the environment. Now we make this intuitive idea more formal, because it will become important when we relate *state-based* models, such as the State Transition Diagram, with *event-based* models, such as the Signal Transition Graph, where the notion of *unique occurrence of an event* is explicit.

For an ALTS  $(S, E, A, \delta)$ , we define a pairwise relation  $\sim^1$  on the set E of arcs as  $(s_1, s_1') \sim^1 (s_2, s_2')$  if  $\delta(s_1, s_1') = \delta(s_2, s_2')$  and  $s_1' \neq s_2$  and  $s_1 E s_2$  (i.e. there exists an arc  $(s_1, s_2) \in E$ ). Let  $\sim$  be the equivalence relation formed by the reflexive, symmetric and transitive closure of  $\sim^1$ . We call  $\sim$  the unique action relation. We can easily see that Unique-Action Relation partitions the set E into a set of Unique-Action Relation-classes,  $[E]^A$ . Each such class,  $[e]^a$ , is called an action. The set of actions with the same name, a, is called the action set of the name a and denoted as  $[E]^a$ . This notion will be useful later, when we shall associate the transitions of an STG with the transitions of the corresponding STD.

For example, in Figure 1.(b) we have  $(s_2, s_7) \sim^1 (s_3, s_6)$ , and  $(s_3, s_6) \sim^1 (s_4, s_5)$ , hence, by transitivity,  $(s_2, s_7) \sim (s_4, s_5)$ . Also  $(s_1, s_8) \sim^1 (s_2, s_7)$ . Then  $[e]_b^{R_b^+} = \{(s_1, s_8), (s_2, s_7), (s_3, s_6), (s_4, s_5)\}$ . In this very simple case, each action set has a single element,  $[E]_b^{R_b^+} = \{[e]_b^{R_b^+}\}$  and so on.

For an action  $[e]^a$ , the set, always forming a connected subgraph, of states which are the sources for the transition arcs in  $[e]^a$  is called *excitation region* for action  $[e]^a$ . So in Figure 1.(b) the excitation region of  $[e]^{R_b^+}$  is  $\{s_1, s_2, s_3, s_4\}$ , and they correspond to the states where the label bit for  $R_b$  has value 0 and is tagged with "\*".

#### 2.2.2 Interleaving Semantics of Concurrent Actions

Throughout this paper we assume that the actions associated with a set of arcs outgoing from the same state can be performed in the modeled system *concurrently*, i.e. independently of each other. See for example  $R_a^+$  and  $R_b^+$  in  $s_1$  in Figure 1.(b), which are "produced" by different and independent components. Since our model is *entirely asynchronous*, we must assume that the changes of corresponding variables can occur in time in any order.

Our low-level behavioral model, on the other hand, requires that a single variable changes for every transition. We then choose to model such concurrency by interleaving, i.e. considering all possible alternative chain orderings compliant with the partial order between possibly concurrent actions (in Figure 1.(b) this corresponds to paths  $s_1$ ,  $s_2$ ,  $s_7$  and  $s_1$ ,  $s_8$ ,  $s_{13}$ ). Such a modeling is convenient yet sometimes problematic, because it hides the semantic distinction between true concurrency and "shuffled" alternative selections. This distinction can be made explicit only in models with explicit causality notions, and we postpone it until Section 4, where we will consider Signal Transition Graphs.

#### 2.2.3 Properties of Transition Systems and State Transition Diagrams

In this section we analyze a set of behavioral properties of Transition Systems and State Transition Diagrams that we will show later been connected with corresponding, important properties of asynchronous systems. For example, the property of confluence below is closely connected to the requirement that the "long term behavior" of the system must not be influenced by the relative magnitude of the delay of two components. No matter who "wins the race", we must still be able to reach the same state in the future. Similarly, local confluence will be shown to be related to the classical concept of static hazards in a circuit.

Following [10], we call an ALTS  $(S, E, A, \delta)$ :

- confluent, if  $\forall s, s1, s2 \in S$ , if  $sE^*s1^3$  and  $sE^*s2$ , then  $\exists s3 \in S$  such that  $s1E^*s3$  and  $s2E^*s3$ .

- locally confluent, if  $\forall s, s1, s2 \in S$ , if  $sEs1^4$  and sEs2, where  $s1 \neq s2$ , then  $\exists s3 \in S$  such that s1Es3 and s2Es3. If such s3 is unique, then the ALTS is called *uniquely locally confluent*.

So, Figure 1.(b) is confluent (all pairs of states can reach any state), but not locally confluent, due to  $s_1$ ,  $s_2$  and  $s_3$  ( $s_1 E s_2$ ,  $s_1 E s_3$ , but there is no common immediate successor of  $s_2$  and  $s_3$ ).

Keller, in [10], gave three sufficient conditions for local confluence (and hence confluence) of an ALTS. An ALTS is:

- deterministic, if  $\forall s, s1, s2 \in S$  and  $\forall a \in A$ , if sE(a)s1 and sE(a)s2, then s1 = s2 (i.e. for each action there can be only one outgoing transition from a state that is labeled with it).

- commutative, if  $\forall s \in S$  and  $\forall a, b \in A$ , if ab and ba are allowed in s, then  $\exists s'$  such that sE(ab)s' and sE(ba)s' (i.e. if the effect of interleaving two transitions both allowed in a state and not mutually exclusive is the same).

- persistent, if  $\forall s \in S$  and  $\forall a, b \in A, a \neq b$ , if a and b are allowed in s, then ab is allowed in s (i.e. if no transition can disable another one).

It was proven in [10] that if an ALTS satisfy all these conditions together, then it is both Locally Confluent and Confluent. The definition of STD implies that if an STD satisfies these conditions, then it is uniquely locally confluent.

The ALTS in Figure 1.(b) is deterministic and persistent, but not commutative (due to  $s_1$ ,  $R_a^+$  and  $R_b^+$  again). So, being confluent, it shows that Keller's conditions are only sufficient.

Now, even though our state-based model has no "direct" idea of causality between actions, we can still locally verify if some action has "a unique set of predecessors", that can somehow be identified with its causes. Hence we define the property of strict causality of an ALTS, which, as the Unique Action Relation, will become more clear when we introduce our event-based model, where such causality is explicit.

<sup>&</sup>lt;sup>3</sup>I.e.  $s_1$  is reachable from s.

<sup>&</sup>lt;sup>4</sup>Le. there is an arc  $(s, s_1) \in E$ .

Let  $S = \langle S, E, A, \delta \rangle$  be an ALTS and let  $[E]^A$  be its set of actions. Let  $S([e]^a)$  denote the excitation region for action  $[e]^a \in [E]^A$ . Let  $\pi(s_1, s_2)$  be a directed path of states between  $s_1$  and  $s_2$ .

An ALTS is called strictly causal for action  $[e]^a$  and state  $s \in S$  if:

- $\forall s_1, s_2 \in S([e]^a), s_1 \neq s_2$ , such that  $\exists \pi(s, s_1), \pi(s, s_2)$ , with  $\pi(s, s_1) \cap S([e]^a) = \emptyset$  and  $\pi(s, s_2) \cap S([e]^a) = \emptyset$  (i.e.  $s_1$  is the first state in  $\pi(s, s_1)$  where  $[e]^a$  is excited, and similarly for  $s_2$ ),

- $-\exists s_3 \in S([e]^a)$  (possibly coincident with  $s_1$  or  $s_2$ ) such that:

- \*  $\pi(s, s_3) \cap S([e]^a) = \emptyset$  and

- \*  $\exists \pi(s3, s1)$  such that  $\pi(s3, s1) \subseteq S([e]^a)$ .

I.e.  $s_1$  and  $s_2$  have a common "ancestor", through states where  $[e]^a$  is also excited, which is a successor of s and where  $[e]^a$  is also excited for the first time.

An ALTS is called *strictly causal* if it is strictly causal for all actions  $[E]^A$  in and all states in S.

This definition means, informally, that each excitation region of each action has a single "top" state (or a "cycle" of such states, as in the example below), where it becomes excited for the first time, and all other states in the region (which is connected by definition) are successors of it through paths within the region. So actions leading into this "top" state (or cycle) can be informally identified with its causes.

On the other hand, if the ALTS is not strictly causal, it means that some action has "many alternative ways" of becoming allowed.

The ALTS in Figure 1.(b) is strictly causal, because, for example, for action  $[e]^{R_a^+}$  the states in its excitation region  $\{s_1, s_2, s_9, s_{10}\}$  form a cycle. So, for example, from state  $s_4$  we can reach both  $s_1$  and  $s_8$  (through  $s_5$ ), and in this case the third state in the definition coincides with  $s_1$ , whence  $s_8$  is reachable without leaving the excitation region. Similarly for all other triples of states and actions.

Finally, when analyzing the behavior of an ALTS we are interested in checking if we have a point where future behaviors diverge completely. Such behavior is, in general, not desirable, and hence the *liveness* of an ALTS is important to check. We define it only for *finite* ALTS. For a *finite* ALTS, with the reachability relation  $E^*$  between states, we define the mutual reachability relation between any two states,  $s, s' \in S$  if both  $sE^*s'$  and  $s'E^*s$  hold for them. This is an equivalence relation, so it gives rise to a set of equivalence classes. Built for a given initial state, these classes form a partial order induced by the reachability relation. The *maximal* classes in this partial order are called *final classes* (i.e. once we enter one of these classes, we can never leave it).

A finite ALTS is live if it forms a single equivalence class for any initial state. Such a TS is represented by a strongly connected graph. In a live ALTS, for every state  $s \in S$  and every action name  $a \in A$ , there exists a state  $s' \in S$ , reachable from s, in which a is allowed. The ALTS in Figure 1.(b) is obviously live.

#### 2.3 Trace Models

For an ACS defined by an ALTS we can define another representation, called Trace Structure, or Trace Model (see [23])<sup>5</sup>, of its behavior. This representation will be needed in Section 5.3, because delay-insensitive circuits were defined in the literature using Trace Models, so in order to define delay-insensitivity within our framework we must relate Trace Models with Arc-Labelled Transition Systems.

A Trace Model representation of the behavior (described by an Arc-Labeled Transition System) of a structure (described by a Binary Asynchronous Control Structure) is a pair  $\langle A, \Sigma \rangle$ , where  $\Sigma \subseteq A^*$  is a *prefix-closed* set of *traces*, or strings of actions. This model is defined with respect to a given initial state, and represents the execution *history* of the ALTS. Each trace then stands for a (possibly infinite) sequence of actions that can be performed on the variables of the ACS. The set of traces in  $\Sigma$  contains those traces that are allowed by the behavioral specification.

For a BACS with an associated initialized STD and a set of variables Y, we can also think about a Binary Trace Model, which is a pair  $(Y, \Sigma)$ , where  $\Sigma \subseteq (Y \times \{+, -\})^*$  is a prefix-closed set of traces, or strings of signal changes as allowed by the STD.

In the example in Figure 1, initialized in state  $s_1$ , we have  $A = \{R_a^+, R_a^-, A_a^+, A_a^-, R_b^+, R_b^-, A_b^+, A_b^-\}$ , and  $\Sigma = \{\epsilon, R_a^+, R_b^+, R_a^+ R_b^+, R_b^+ R_a^+, R_b^+ A_a^+, R_b^+ A_b^+, R_a^+ A_a^+, R_b^+ A_b^+, R_b^+$

<sup>&</sup>lt;sup>5</sup>We are forced to introduce this term here, as a synonym of the more common "Trace Structure", only to avoid confusion with the abbreviation of the term "Transition System" (TS).

The following property of the Binary Trace Model generated from an STD is the result of Property 2.1 and of the definition of STD.

**Property 2.2** In a Binary Trace Model  $(Y, \Sigma)$ , for every trace in  $\Sigma$  and any variable  $y \in Y$ , all the occurrences of y have alternating signs, i.e. between any two consecutive changes of the same sign there is at least one opposite change.

#### 2.4 Cumulative Diagrams

In order to characterize classes of behaviors of asynchronous systems, we need the concept of history of the execution of a state-based specification. The complete history of the system is represented by a set of traces, where each trace records exactly the order of occurrences of actions. The state of the Arc-Labeled Transition System, on the other hand, describes only the final result of such execution. In this section, following [17], we will describe a model to describe this history, where only the number of occurrences of each action is recorded, called a Cumulative Diagram (CD). Hence this representation will be of intermediate "precision" between a Trace Model and an ALTS.

The Trace Model description of the operation of an initialized ALTS contains all the traces of the ALTS starting from its initial state. The mechanism of trace generation induces a natural mapping between traces and sets of states, where each trace maps to the set of states where the ALTS may be at the end of its generation. Note this mapping is *functional* if the ALTS is *deterministic*. In this case, the state in which the ALTS arrives for a given trace with respect to an initial state is uniquely determined through the reachability relation.

On the other hand, for any ALTS (not just deterministic ones) we can think about another mapping from the set of traces. This mapping defines, for every trace  $\alpha \in \Sigma$ , a multiset of action names  $\mu$ , with the multiplicity of each name  $a \in A$ ,  $\mu(a)$ , equal to the number of occurrences of a in  $\alpha$ . A multiset obtained in this way is called a *cumulative state*. It is convenient to represent a cumulative state by a *vector* of natural numbers with dimension |A|.

We can easily see from the above definition that a cumulative state defines a class of equivalence between traces of the ALTS which are simple permutations of each other (note that not every permutation may be a valid trace). Let  $[\alpha]$  be such equivalence class for trace  $\alpha$ . Every trace  $\beta \in [\alpha]$  brings the ALTS to the same cumulative state  $\mu$ . Therefore we can identify this  $\mu$  with  $[\alpha]$ . Now it should be clear that for every deterministic, commutative and persistent ALTS, where all the traces in  $[\alpha]$  bring the ALTS in the same state, there exists a *functional mapping* between cumulative states and ALTS states.

The set of cumulative states generated by an ALTS through its Trace Model model (denoted by  $[\Sigma]$ ) is a partial order. This order is a subset of the natural integer vector ordering and is built upon the *prefix order* between traces up to permutations. Formally,  $[\alpha] \sqsubseteq [\beta]$  if  $\forall \alpha \in [\alpha] \exists \beta \in [\beta]$  such that  $\alpha$  is a prefix of  $\beta$ .

The partial order of cumulative states, built as above, is called the Cumulative Diagram (CD) (more precisely, we will use its Hasse diagram, where the reflexive and transitive edges have been removed).

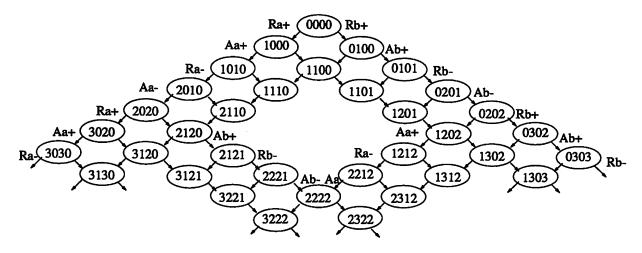

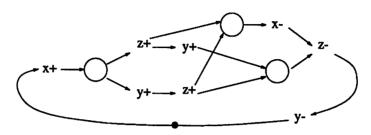

For example, Figure 2 contains an initial fragment of the CD for the ALTS described in Figure 1. Note that the CD model cannot describe the local divergence after traces  $R_a + R_b +$  and  $R_b + R_a +$ . In fact both traces lead to the same cumulative state 1100, that corresponds to states  $s_7$  and  $s_{13}$  in Figure 1.(b). This also illustrates that the mapping between CD states and STD states in general is a relation, not a function.

The above definitions are easily adapted to the case of a BACS and its STD. By Property 2.1, we can change the notion of cumulative state and build the CD for a set of variable names Y rather than their changes  $Y \times \{+, -\}$ . This modified version of CD is isomorphic to the original version because all the changes of the same variable are linearly ordered (see also Property 2.2).

Now we have all the necessary information to define the notion of speed-independent and semi-modular behavior, which are crucial (as we will see in Section 3.6) for more practical purposes, such as the analysis and synthesis of asynchronous control circuits.

### 2.5 Speed-independence and Semi-modularity

The intuitive notion of speed-independent behavior can be more formally described using *confluence*, that ensures that the "long term" behavior of the modeled asynchronous system does not depend on the winner of a race between concurrent transitions. In this section we give a set of *alternative* definitions of a set of ALTS properties. These properties will be shown to correspond to:

- · interesting circuit properties, such as the absence of hazards in Section 3, and

- high-level specification properties in Section 5.

Figure 2: The Cumulative Diagram of Figure 1

So this section provides the desired bridge between the two domains.

Let us first recall some definitions from lattice theory. Let C be a partial order. An element  $z \in C$  is a zero element if for all  $c \in C$  we have  $z \sqsubseteq c$ . An element  $c \in C$  is a greatest lower bound (g.l.b.) of two elements  $c_1, c_2 \in C$ , denoted  $c = c_1 \sqcap c_2$ , if  $c \le c_1$ ,  $c \le c_2$  and  $c' \le c_1 \land c' \le c_2 \Rightarrow c' \le c$ . Similarly we can define the least upper bound (l.u.b.) of a pair of elements, denoted  $c = c_1 \sqcup c_2$  by replacing  $\le$  with  $\ge$ . A lattice is a partial order where every pair of elements has a g.l.b. and a l.u.b. A lattice is distributive if the g.l.b. and l.u.b. operations are mutually distributive. An element  $c_1$  of a partial order C covers another element  $c_2$  of C if  $c_2 \le c_1$  and there is no  $c_3$  such that  $c_2 \le c_3 \le c_1$ . A lattice is semi-modular if for every pair of elements  $c_1$  and  $c_2$  that cover a third element  $c_3$  (then obviously  $c_3 = c_1 \sqcap c_2$ ), they are both covered by  $c_1 \sqcup c_2$ .

- An ALTS (STD) is called Speed-independent-1 if it is confluent.

- A finite ALTS (STD) is called Speed-independent-2 with respect to a state if the CD generated for this state is a lattice with a zero element, according to the partial order defined in Section 2.4. The ALTS (STD) is called Speed-independent-2 if it is Speed-independent-2 with respect to every state in S.

- A finite ALTS (STD) is called Speed-independent-3 ([19]) with respect to a state s if it has a single final equivalence

class when initialized in s (Section 2.2.3). The ALTS (STD) is called Speed-independent-3 if it is Speed-independent

with respect to every state in S.

For example, the ALTS in Figure 1.(b) satisfies Speed-independent-3, because it is finite and it has a single final equivalence class for every initial state. We can easily see that the TS is confluent, and hence Speed-independent-1. Furthermore its CD, represented in Figure 2, is a lattice (zero is cumulative state 0000), so the STD is Speed-independent-2.

It can be shown that, despite our intuition, the definitions above are not strictly equivalent for a given finite ALTS (STD). Speed-independent-1 is equivalent to Speed-independent-3 in the finite case, while Speed-independent-1 and Speed-independent-2 are equivalent if (but not only if) the given finite ALTS (STD) is deterministic, commutative and persistent:

#### **Proposition 2.1**

- A finite ALTS (STD) is Speed-independent-2 if it is Speed-independent-1 and persistent.

- An ALTS (STD) is Speed-independent-1 if it is Speed-independent-2, deterministic and commutative.

The example in Figures 1 and 2 shows that our conditions for the equivalence between Speed-independent-1 and Speed-independent-2 are only *sufficient* and *not necessary*, because this ALTS is both Speed-independent-1 and Speed-independent-2 but *not commutative*.

Semi-modularity, that we will relate to hazard-freeness, is a stronger property than speed-independence. Again, two alternative definitions can be formulated.

An ALTS (STD) is called Semi-modular-1 if it is locally confluent.

• A finite ALTS (STD) is called Semi-modular-2 with respect to a given state if the CD generated for this state is a semi-modular lattice with a zero element, according to the partial order defined in Section 2.4. The ALTS (STD) is Semi-modular-2 if it is Semi-modular-2 for every state in S.

A Proposition analogous to Proposition 2.1 can also be shown to hold about Semi-modular-1 and Semi-modular-2.

The ALTS in Figure 1.(b) is not locally confluent, hence not Semi-modular-1. It is not Semi-modular-2 either, because the corresponding CD in Figure 2 is not semi-modular, due for example to cumulative states 1110 and 1101, that both cover 1100, but are not covered by their least upper bound 2222 (recall that covering means being immediately above in the partial order).

A last class of ALTSs, significant because of some interesting results on sufficient conditions for its synthesis with realistic logic gates ([8]), is connected with the definition of *strict causality* (or, informally, of a "unique set of actions causing an action") described in Section 2.2.3.

- An ALTS (STD) is called Distributive-1 if it is strictly causal and locally confluent.

- A finite ALTS (STD) is called *Distributive-2* with respect to a given state if the CD generated for this state is a distributive lattice with a zero element, according to the partial order defined in Section 2.4. The ALTS (STD) is Distributive-2 if it is Distributive-2 for every state in S.

A Proposition analogous to Proposition 2.1 can also be shown to hold about Distributive-1 and Distributive-2.

It should be obvious that the following inclusion holds for the classes of ALTSs (STDs): Distributive  $\subset$  Semi-modular  $\subset$  Speed-independent.

#### 3 Modeling Asynchronous Logic Circuits

In this section we will show how "real" asynchronous circuits, built out of gates and wires, fit as a special case of our Binary Asynchronous Control Structures and State Transition Diagrams.

We will use two different delay models, pure and inertial, to describe the behavior of the circuit, and characterize circuit properties such as hazards in terms of ALTS properties such as local confluence.

#### 3.1 A Low-level Model for Asynchronous Logic Circuits

Here, as in Section 2.1, we describe a circuit as the conjunction of a *structure* (a graph) and a *behavior* (a set of Boolean functions and delays).

An Asynchronous Logic Circuit (ALC, [19], [17]) is a triple (X, Z, F), where X is a set of input signals (|X| = m), Z is a set of output signals (|Z| = n),  $F = \{f_1, f_2, ..., f_n\}$  is a set of Boolean functions, the circuit element functions, such that for each  $i \in \{1 ... n\}$ ,  $f_i : \{0, 1\}^{d_i} \to \{0, 1\}$ , where  $d_i$  is the number of inputs of element  $z_i$ . We denote by  $Y = X \cup Z$ , the set of signals of the ALC. The structure of an ALC can be represented by a directed graph with one node for each variable, and an arc connecting the node corresponding to each input of  $f_i$  with the node corresponding to  $y_i$ .

Structurally, an ALC is a special case of a BACS. The difference is that every structural component of the ALC is uniquely associated with a single variable, thus implying that each component,  $v_i$ , has only one output,  $\{y_i\} = O^Y(v_i)$ . The value of this output can be characterized either by the value of the corresponding Boolean function  $f_i$  (if  $y_i$  is an output signal) or by the value of the signal itself (if  $y_i$  is an input signal).

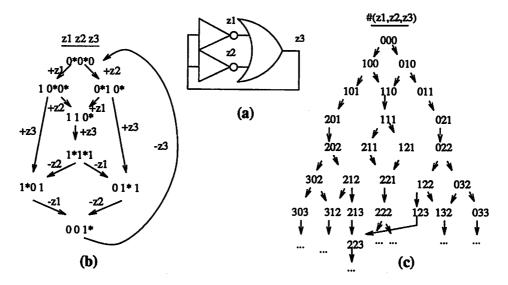

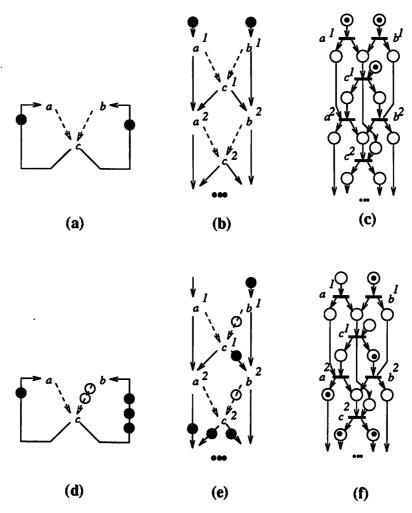

An ALC is *initialized* if its initial state is defined, as a binary vector  $s0 \in \{0, 1\}^{n+m}$ . An ALC is *autonomous* if  $X = \emptyset$ . Figure 3.(a) describes a very simple autonomous ALC, where  $Z = \{z_1, z_2, z_3\}$  and  $f_1 = \overline{z_3}$ ,  $f_2 = \overline{z_3}$ ,  $f_3 = z_1 + z_2$ .

## 3.2 Taxonomy of Models for Asynchronous Logic Circuits

An initialized ALC produces a dynamic behavior, resulting from the transitions of both input and output signals. The input signals are changed by the environment and the output signals are changed by the ALC. The output values are determined by two factors. The first factor is the *evaluation* of the Boolean function associated with the element. The second factor is the inherent *switching delay* of the physical logic gate, which must be taken into account by the model.

<sup>&</sup>lt;sup>6</sup>We associate a node with each input of an ALC to provide the way of modeling the input wires of the circuit as components with potential delay properties.

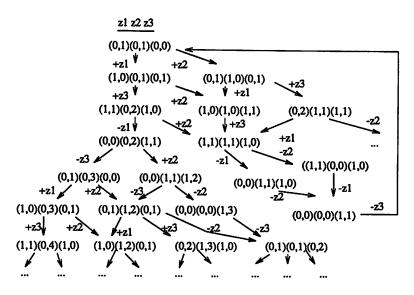

Figure 3: A circuit, its State Transition Diagram and its Cumulative Diagram with Inertial Delays

Therefore the dynamic behavior of the ALC is modeled through a number of abstractions, which can be classified as follows:

- 1. Delay model of an element (delay model "in small", see Section 3.3):

- pure delay model,

- inertial delay model.

- 2. Delay model of the circuit (delay model "in large"):

- feedback delay model ([9]), assuming that there are delays only in the feedback wires.

- gate delay model, ([19]), assuming that only the logic elements have finite delays.

- gate and wire delay model, ([3] and [4]) assuming that both gates and wires have finite delays.

- 3. Environment behavior model (input change constraints):

- fundamental mode, assuming that inputs can change their values only after the circuit has reached a stable state, where none of its variables is excited.

- input-output mode, allowing the environment to change the input values in some states, not necessarily stable, in accordance with some protocol of interaction between the ALC and the environment. The fact that input values may change in some states, autonomously or in consequence of some output change, is explicitly indicated in the model (reactive behavior).

- 4. Circuit switching semantics ("race" model):

- general multiple winner, assuming that any subset of the set of unstable signals may win the race due to a concurrent switching process.

- extended multiple winner, where all concurrently changing signals go through a third, undefined, state before reaching their final value.

Brzozowski and Seger ([3]) showed that General Multiple Winner and Extended Multiple Winner yield equivalent results, but the latter allows more efficient analysis of the circuit hazards than the latter. Ternary simulation, can be used to analyze a circuit with the Extended Multiple Winner model, but only in a rather limited case, the Fundamental Mode operation. The ternary simulation of the dynamic behavior of an ALC in I/O mode (or of an autonomous ALC)

cannot give meaningful results for such effects like hazards or speed-independence<sup>7</sup>. Due to these reasons our analysis assumes the General Multiple Winner race model and I/O mode.

#### 3.3 Delay Models of an Asynchronous Logic Circuit element

Let an ALC (X, Z, F) be initialized in some state s. Every element  $z_i$  of the circuit is modeled as a sequential composition of a delay-free logic function evaluator and a delay block. For every element  $z_i$  we call it (and the corresponding output variable) stable in s if its current value  $s_i$  is equal to the value of its function  $f_i$ . Otherwise we call it excited. We assume that if a variable is excited, then this variable may change its state after some finite time interval, which we call the element delay. For example, in the circuit in Figure 3.(a), initialized in state 000,  $z_3$  is stable while  $z_1$  and  $z_2$  are excited. What happens next, whenever  $z_1$  or  $z_2$  changes value, depends on whether we use the pure or inertial delay model.

#### 3.3.1 Inertial Delay Model

In the Inertial Delay model (ID), an excited variable may change its state after a finite delay. This means that for any excited variable  $z_i$  there are two possibilities. One is that its value, 0 or 1, changes to the opposite, i.e. to 1 or 0, after a finite but unbounded amount of time. The other possibility is that the value of its function  $f_i$  is changed before  $z_i$  manages to change, so that the previous value appears at the input of the delay block. In this case the output  $z_i$  of the element ceases to be excited and retains its previous value, which becomes stable (hence the term "inertial"). Speaking in more quantitative terms, the ID model means that if an element has a switching delay of d time units, pulses generated by the logic evaluator with duration less than d are filtered out, while pulses longer than d units appear at the output  $z_i$  shifted in time by d units.

Since we are dealing with completely asynchronous circuits, we cannot precisely say whether in the second situation above the element has or has not produced a short pulse at its output. We shall therefore regard this behavior (when  $f_i$  changes before  $z_i$ ) as anomalous or hazardous.

#### 3.3.2 Pure Delay Model

We can alternatively assume that the delay block of each element is not inertial when it becomes excited, i.e. it cannot filter out the pulses whose duration is less than a given value d (this behavior is close to reality for long wire delays). Therefore, even though the function value changes before the output  $z_i$  has changed, the element remains excited, and just shifts in time the complete sequence of its "expected" output transitions. With this Pure Delay model (PD), the value of the element in state s of the ALC, must be modeled by a pair,  $(r_i^s, \tau_i^s)$ , where the first component is the current binary value of  $z_i$ , i.e.  $r_i^s \in \{0, 1\}$ , while the second component is the excitation number (recording how many excitations have been registered by the functional evaluator since the element was last stable),  $\tau_i^s \in \{0, 1, 2, ...\}$ . In this model, the state of the ALC is a vector of length |Y|, with each component being of the above form.

We can now define an element  $z_i$  to be *stable*, according to the PD model, in state s if  $\tau_i^s = 0$ . Otherwise it is *excited*. The normal operation of the element is described by the following sequence of transitions:  $(r_i^s, 0) \to (r_i^s, 1) \to (\overline{r_i^s}, 0)$ . The hazardous operation, on the other hand, is described by the following sequences of transitions: either  $(r_i^s, \tau_i^s) \to (r_i^s, \tau_i^s + 1) \to (\overline{r_i^s}, \tau_i^s)$  (if  $\tau_i^s > 0$ ) or  $(r_i^s, \tau_i^s) \to (r_i^s, \tau_i^s + 1) \to (r_i^s, \tau_i^s + 2)$ .

Now, with this definition of the behavior of each gate, we can describe the operation of the entire circuit for both the ID and the PD models.

#### 3.4 Circuit Behavior Description with Inertial Delays

Let us consider, as an example, the circuit shown in Figure 3.(a). If we assign the all zero vector as the initial state of this ALC, variables  $z_1$  and  $z_2$  are excited in this state. As usual, we designate this fact by labelling the value of an excited variable with an asterisk (\*). Therefore the initial state is marked as  $0^*0^*0$ . Using the ID model of an element we can think about two possible states directly reachable from this state through the element normal switching behavior,  $10^*0^*$  and  $0^*10^*$ . Although variables  $z_1$  and  $z_2$  are excited concurrently and can switch independently, our interleaving semantics of concurrent actions

<sup>&</sup>lt;sup>7</sup>Although some results on speed-independence can be obtained through such technique [3], they are meaningful only for a very restrictive modeling conditions. Namely, the circuit must operate in Fundamental Mode, and it is regarded as Speed-independent if its final equivalence class consists of a *unique* stable state. The existence of cyclic final equivalence classes cannot be detected by such ternary simulation, because each cyclically changing variable would have an *undefined* value.

requires that the first of the above two states is reached if variable  $z_1$  changes before  $z_2$  (and vice-versa). In both cases variable  $z_3$  now becomes excited.

We can thus use a depth-first search procedure to generate the set of states reachable from the initial state. This set, together with the relation of direct reachability between states, can be represented by a graph, which satisfies our definition of an STD. Note that the transitions in this graph are labelled by the changes of variable values. Since the number of signals in the ALC is fixed (|Y| = n + m), it is obvious that the size of the STD, in terms of the number of its state labels, is bounded by  $2^{n+m}$ .

Proposition 3.1 The STD for any ALC, under the ID element model, is deterministic, commutative and non-contradictory8.

This Proposition follows directly from the ID model of an element and the uniqueness of the result of Boolean function evaluation for any given binary encoded state.

Therefore determinacy and commutativity are the intrinsic properties of the STD description for any ALC obtained using the ID model. This implies that *confluence and local confluence* are determined (up to sufficiency) by how the circuit satisfies the *persistency* condition.

We can now define speed-independence, semi-modularity, and so on for an ALC modeled with Inertial Delays. Let  $C = \langle X, Z, F \rangle$  be an ALC modeled with inertial delay and let  $S = \langle S, E, \lambda \rangle$  be its associated STD. According to the classification of Section 2.5 and Proposition 3.1:

- 1. C is Speed-independent if the STD S is confluent.

- 2. C is Output-persistent if it is Speed-independent and for each pair of edges  $s_1 E(y_1^*) s_2$  and  $s_1 E(y_2^*) s_3$ , if  $y_1 \in \mathbb{Z}$ , then  $y_1^*$  is enabled in  $s_3$  (i.e. no output signal can ever be disabled).

- 3. C is Semi-modular if the STD of S is locally confluent.

- 4. C is Distributive if the STD of S is strictly causal and locally confluent.

Analogous definitions exist for a BACS (except for Output-persistent).

Output-persistency guarantees that no transition of an output signal will ever be disabled, thus guaranteeing a correct behavior for them (recall that disabling a transition means possibly causing a spurious pulse on the signal).

Obviously ID-Distributive CID-Semi-modular CID-Output-persistent CID-Speed-independent.

Note that Semi-modular as defined above is equivalent to the "operational" definition due to Muller ([19]). An ALC is called Semi-modular with respect to a given state if the STD built from this this state has no transition from a state where some  $z_i$  is excited to another state where  $z_i$  is stable but has the same value. So an ALC is Semi-modular if its STD is persistent.

Also, note that Proposition 2.1 and 3.1 immediately imply that for an ALC with the ID model Speed-independent-1 (confluence) is implied by Speed-independent-2 (lattice), and similarly for Semi-modular-1 and Semi-modular-2 and Distributive-1 and Distributive-2.

The STD and an initial fragment of the CD for the ALC example in Figure 3.(a) is shown in Figure 3.(b) and (c). The STD is live, Speed-independent but not Semi-modular (persistency is violated in states  $1^*01$  and  $01^*1$ , where  $z_2$  and  $z_1$  are disabled after the transition  $z_3^+$  from states  $10^*0^*$  and  $0^*10^*$ , respectively). It is confluent but not locally confluent. Furthermore it is strongly connected, thus having single final equivalence class, and it contains only non-transient cycles of states. The CD is a lattice (one can easily prove that every pair of cumulative states has its least upper bound in the CD), but not semi-modular. It has a zero element, the empty multiset (or all zero vector).

#### 3.5 Circuit Behavior Description with Pure Delays

Throughout this section we will refer to properties of the ALC under consideration when analyzed with the Inertial Delay modes by prefixing them with ID. Properties without the prefix, on the other hand, refer to the ALC analyzed with the Pure Delay model.

An Asynchronous Logic Circuit can be analyzed with the Pure Delay model in a similar way as in the Inertial Delay case, by building its CD with a depth-first search procedure, from the initial state. According to the notation introduced earlier, each state, s, is labelled by a vector of |Y| = n + m pairs  $(r_i^s, \tau_i^s)$ , where the first component is the binary value on the output of the delay block,  $z_i$ , and the second component is the number of potential changes that the element will generate on its own

<sup>&</sup>lt;sup>8</sup>Being non-contradictory, we can identify each state of the STD with its unique binary vector code.

before it will become stable. Let us call such a vector the PD-vector. This graph does not satisfy the definition of an STD, given in Section2.2, because the label is not binary. Nevertheless, it satisfies the definition of an ALTS, and again, due to the unique evaluation of the Boolean functions describing the ALC, we can make use of the fact that every state in set S is uniquely labelled by the PD-vector, and show that the following Proposition holds.

Proposition 3.2 The ALTS for any ALC, under the PD element model, is deterministic, persistent and non-contradictory.

Equality between PD-vectors requires also equality of the second component, so commutativity does not hold in this case. However, due to non-inertiality of elements behavior, we can claim persistency, because every element records its excitation, and cannot be disabled by changing the value at the output of its Boolean evaluator.

The latter detail drastically changes the role of the CD that can be built from the ALTS associated with the ALC. Such a CD is no longer a description that can be meaningfully used for characterizing the confluence properties of the ALC behavior.

The definition of a bounded circuit becomes crucial in such characterization. The PD model of an ALC (PD-ALC) is called k-bounded (or simply "bounded") if for every reachable state s in the associated ALTS,  $\forall z_i: \tau_i^s \leq k$ . An immediate consequence of boundedness is the finiteness of the ALTS of a PD-ALC.

The following Proposition is the implication of the fact that a PD-modeled ALC can accumulate unbounded "switching events" in its elements if its operation is cyclic.

Proposition 3.3 The PD model of an ALC, which is ID-live9 and non-ID-persistent, is unbounded.

This is true because in a live, non-persistent ID model of a circuit there is no bound to the number of times the circuit can reach a state s where a variable  $y_i$  becomes disabled before it has a chance to fire. So every new arrival in this state will increment the corresponding  $\tau_i^s$ .

- The PD model of an ALC is called Speed-independent if the associated ALTS is finite and confluent.

- The PD model of an ALC is called Semi-modular if the associated ALTS is finite and locally confluent.

- The PD model of an ALC is called Distributive if the associated ALTS is finite, strictly causal and locally confluent.

Analogous definitions exist for a BACS.

This definition and Proposition 3.3 imply the following important result.

Theorem 3.4 The PD-model of an ALC, which is ID-live, is PD-Speed-independent iff it is ID-Semi-modular<sup>10</sup>.

This theorem in practice claims that for the PD model of an asynchronous circuit, speed-independence amounts to semimodularity, if one considers a cyclically operating circuit. This result provides a crucial justification for the restriction to semi-modularity, when we look for necessary and sufficient conditions for the hazard-free, speed-independent implementation of an ALC.

Note also that this equivalence result strongly favors the use of semi-modularity rather than speed-independence as the characterization of a "correct" circuit in the ID case. The ID model can be too optimistic in many practical cases, so a design made for semi-modularity (or output-persistency) will be more "robust" with respect to technology changes, different implementations of other components of the system, and so on.

Obviously PD-Distributive CPD-Semi-modular.

Our ALC example in Figure 3.(a) generates the ALTS whose initial fragment is shown in Figure 4. This ALTS is persistent but non-commutative. It is infinite and not locally confluent. The PD-ALC is unbounded, therefore it is not Speed-independent.

Our analysis of ID and PD models of ALCs has an important by-product. It gives concise and general characterization of hazards in the ALCs behavior.

<sup>9</sup> I.e. the STD of the same circuit, modeled with Inertial Delays, is live. That is, it forms a single equivalence class for any initial state (Section 2.2.3).

Figure 4: Cumulative Diagram for Pure Delay Model

#### 3.6 On Static and Dynamic Hazards of Asynchronous Logic Circuits

The traditional definition of hazards ([22]) assumes two types of hazards, *static* and *dynamic*. Static hazards are again of two types, 0-1-0 and 1-0-1, and they model the behavior of an element which generates spurious pulse at its output. The dynamic hazards, 0-1-0-1 and 1-0-1-0, model the erroneous behavior of an element that should switch from 0 to 1 or 1 to 0, respectively, but during this process returns back to its previous state.

Leaving aside the question of how dangerous such hazards are in an asynchronous context, we can identify how this behavior can be analyzed at our ID and PD modeling level.

For a given ALC, the ID model, represented by the STD, can only depict static hazards. They are present if the ID-ALC is non-persistent. An element whose excitation is disabled, without switching, in state 0(1) is defined to have an 0-1-0 (1-0-1) static hazard<sup>11</sup>. Hence, if the ALC is ID-Semi-modular (or ID-Output-persistent), then it is free from hazards.

For a given ALC, the PD model, represented by its ALTS, can describe all hazards, characterized as follows. An element whose excitation number  $\tau_i^s$  is greater than 1 has a hazard. The rank, k, of this hazard is equal to  $\tau_i^s$ .

This characterization allows us to define not only "standard" static or dynamic hazards, but any dynamic hazardous behavior that can be generated by the circuit element. In fact, the "standard" static hazard corresponds to  $\tau_i^s = 2$ , while the "standard" dynamic hazard to  $\tau_i^s = 3$ .

### 4 A High-level Behavioral Model for Asynchronous Systems

The previous Sections discussed various inter-related models of Asynchronous Control Structures and Logic Circuits, and the relationship between model properties, such as confluence, and circuit properties, such as hazards.

In this section we develop a very general, *event-based*, model of BACS and ALC that, unlike STDs and Trace Models, has an explicit notion of *causality* and *concurrency*. So for example we will be able to distinguish the cases where events a and b are truly concurrent, independent of each other, and the case where either a can happen, and then cause b, or b can happen, and then cause a (an example of this distinction will be given in Figure 6).

The model, called Signal Transition Graph (STG), is based on interpreted Petri nets, and is a development of similar, but less general, models presented by [20] and [5].

We first recall some basic definitions from the theory of Petri nets then establish relationships between STGs and the models described in the previous Sections.

<sup>&</sup>lt;sup>11</sup>Strictly speaking, this is not a hazard in the "ideal" model, because the output of the delay block does not change. Due to the physical considerations above, though, this kind of situation can actually generate a spurious pulse on the output.

#### 4.1 Petri Nets

Petri nets are a widely used model for concurrent systems, because they have a very simple and intuitive semantics, that directly captures concepts like causality, concurrency and conflict between events.

A Petri net (PN) is a triple  $\mathcal{P} = \langle T, P, F \rangle$ . T is a non-empty finite set of transitions. P is a non-empty finite set of places  $F \subseteq (T \times P) \cup (P \times T)$  is the flow relation between transitions and places<sup>12</sup>.

A PN marking is a function  $m: P \to \{0, 1, 2, \ldots\}$ , where m(p) is called the number of *tokens* in p under marking m. A marked PN is a quadruple  $\mathcal{P} = \langle T, P, F, m_0 \rangle$ , where  $m_0$  denotes its initial marking. A transition  $t \in T$  is *enabled* at a marking m if all its predecessor places are marked. An enabled transition t may fire, producing a new marking m' with one less token in each predecessor place and one more in each successor place (denoted by m[t > m')).

A sequence of transitions and intermediate markings  $m[t_1 > m_1[t_2 > \dots m']$  is called a *firing sequence from m*. The set of markings m' reachable from a marking m through a firing sequence is denoted by [m]. The set  $[m_0]$  is called the reachability set of a marked PN with initial marking  $m_0$ , and a marking  $m \in [m_0]$  is called a reachable marking. A PN marking m is *live* if for each  $m' \in [m]$  for each transition t there exists a marking  $m'' \in [m']$  that enables t. A marked PN is live if its initial marking is live.

A marked PN is k-bounded (or simply "bounded") if there exists an integer k such that for each place p, for each reachable marking m we have  $m(p) \leq k$ . A marked PN is safe if it is 1-bounded. A transition  $t_1$  disables another transition  $t_2$  at a marking m if both  $t_1$  and  $t_2$  are enabled at m and  $t_2$  is not enabled at m' where  $m[t_1 > m']$ . A marked PN is persistent if no transition can ever be disabled at any reachable marking.

A PN is a Marked Graph if every place has exactly one predecessor and one successor. A Marked Graph is persistent for every initial marking  $m_0$ , furthermore every strongly connected marked graph has at least one live and safe initial marking. A PN is *free-choice* if any two transition with a common predecessor place have only one predecessor.

A marked Petri net  $\mathcal{P}=\langle T,P,F,m_0\rangle$  generates an Arc-Labeled Transition System (ALTS) ( $[m_0>,E,T,\delta)$  (Section 2.2) as follows. For each edge  $(m_1,m_2)\in E$ , where  $m_1[t>m_2$ , we have  $\delta(m_1,m_2)=t$ . Under this mapping, each Unique-Action Relation-class  $[e]^t$ , with e=sE(t)s' corresponds to a particular firing of a transition t.

The following Proposition is an obvious consequence of the PN firing rule and of the results in [10]:

#### **Proposition 4.1**

- 1. The ALTS corresponding to a marked PN is finite if and only if the PN is bounded.

- 2. The ALTS corresponding to a marked bounded live PN is live.

- 3. The ALTS corresponding to a marked PN is deterministic and commutative.

- 4. The ALTS corresponding to a marked persistent PN is persistent, locally confluent and confluent.

#### 4.1.1 Cumulative Diagram of a Petri Net

As in Section 2.4, we can define the Cumulative Diagram (CD) of a Petri net, and analyze its properties as a lattice. This will be useful in order to establish the desired correspondence between PN properties and circuit properties.

According to [26], we define the Cumulative Diagram of a marked PN as follows. Given a firing sequence  $m_0[t_1 > m_1[t_2 > \dots m]$  of a marked PN  $\mathcal{P} = \langle T, P, F, m_0 \rangle$ , the corresponding firing vector is a mapping  $V: T \to \{0, 1, 2, \dots\}$  such that for each transition t, V(t) is the number of occurrences of t in the sequence.

Let V be the set of all firing vectors of P. We define a mapping  $\mu: V \to [m_0 > that$  associates each firing vector with the final marking of the corresponding firing sequence. Note that the mapping is well defined, since in any marked PN the marking reached after a sequence of transition firings from  $m_0$  depends only on the number of occurrences of each transition in the sequence, not on the *order* of occurrence.

The set V, called the Cumulative Diagram of P, was shown in [26] to be a partial order when we define  $V_1 \sqsubseteq V_2$  if:

- $V_1(t) \leq V_2(t)$  for all t and

- marking  $\mu(V_2)$  is reachable from marking  $\mu(V_1)$ .

The following Theorem was proved in [2]:

<sup>&</sup>lt;sup>12</sup>A PN can be represented as a directed bipartite graph, where the arcs represent elements of the flow relation.

Theorem 4.2 The ALTS of a PN is confluent if the net is free-choice, bounded and live.

The following Theorems were proved in [26]:

Theorem 4.3 The CD of a marked PN is a semi-modular lattice with a zero element if the net is persistent.

#### Theorem 4.4

- 1. The CD of a marked PN is a distributive lattice with a zero element if the net is safe and persistent.

- 2. The CD of a Marked Graph is a distributive lattice with a zero element.

- 3. Let  $\mathcal{P}$  be a PN whose CD  $\mathcal{V}$  is distributive. There exists a safe and persistent PN  $\mathcal{P}'$  whose transitions are labelled with the transitions of  $\mathcal{P}$  and whose CD is isomorphic to  $\mathcal{V}$ .

- 4. Let  $\mathcal{P}'$  be a safe persistent PN, let  $\mathcal{V}$  be its CD. There exists a safe Marked Graph  $\mathcal{P}''$  whose transitions are labelled with the transitions of  $\mathcal{P}'$  and whose CD is isomorphic to  $\mathcal{V}$ .

- 5. Let S be a finite distributive ALTS with a set of labels T. There exists a safe persistent PN  $\mathcal P$  and a safe Marked Graph  $\mathcal P''$  whose transitions are labelled with those in T and whose CDs are isomorphic to the CD generated by  $\mathcal S$ .

#### 4.2 Signal Transition Graphs

Interpreted Petri nets, where transitions represent changes of values of circuit signals, were proposed independently as specification models for Asynchronous Logic Circuits by [20] (where they were called Signal Graphs) and [5] (where they were called Signal Transition Graphs, STGs). Both papers proposed to interpret a PN as the specification of an ALC  $C = \langle X, Z, F \rangle$  (where Y denotes, as usual,  $(X \cup Z)$ , by labelling each transition with an element of  $Y \times \{+, -\}$ . A label  $y_i^+$  means that signal  $y_i \in Y$  changes from 0 to 1, and  $y_i^-$  means that  $y_i$  changes from 1 to 0, while  $y_i^+$  denotes either  $y_i^+$  or  $y_i^-$ .

An STG is a quadruple  $\mathcal{G} = (\mathcal{P}, X, Z, \Delta)$  where  $\mathcal{P}$  is a marked PN, X and Z are (disjoint) sets of input and output signals respectively and  $\Delta : T \to (X \cup Z) \times \{+, -\}$  labels each transition of  $\mathcal{P}$  with a signal transition. An STG is autonomous if it has no input signals (i.e.  $X = \emptyset$ ).

Both [20] and [5] gave also synthesis methods to translate the PN into an STD (called Transition Diagram in [20] and State Graph in [5]) and hence into an ALC implementation of the specified behavior.

Given an STG  $\mathcal{G} = \langle \mathcal{P}, X, Z, \Delta \rangle$  and the ALTS  $([m_0 >, E, T, \delta)$  corresponding to its PN  $\mathcal{P}$ , we define the associated STD  $\mathcal{S} = \langle [m_0 >, E, \lambda \rangle$  as follows. For each  $m \in [m_0 >$ , we have  $\lambda(m) = s^m$ , where  $s^m$  is a vector of signal values. Let  $s_i^m$  denote the value of signal  $y_i$  in marking m.

Obviously the STD labelling must be *consistent* with the interpretation of the PN transitions, so we must have for all arcs e = (m, m') in the STD:

- if  $\Delta(\delta(e)) = y_i^+$ , then  $s_i^m = 0$  and  $s_i^{m'} = 1$ .

- if  $\Delta(\delta(e)) = y_i^-$ , then  $s_i^m = 1$  and  $s_i^{m'} = 0$ .

- otherwise  $s_i^m = s_i^{m'}$ .

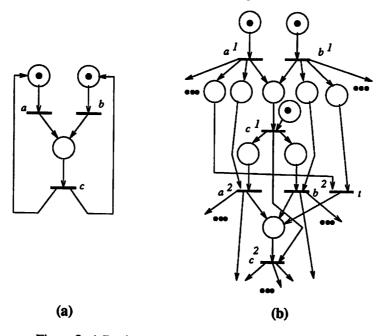

Figure 5 shows an example of an STG and the corresponding STD. Note that for historical reasons PN transitions are denoted by the corresponding labels and PN places are denoted by circles PN places with only one predecessor and one successor are generally omitted. So in Figure 5.(a) the initial marking of the PN (corresponding to the leftmost state in Figure 5.(b)) appears on the edge between  $y^-$  and  $x^+$ .

An STG is defined as *valid* if its STD is *finite* (i.e. the PN is bounded) and has a *consistent labeling*. In this paper we will only consider valid STGs (otherwise their interpretation as control circuit specifications would lose its meaning).

One consequence of this requirement is similar to Property 2.1:

Property 4.1 In a valid STG, for all firing sequences of its PN, the signs of the transitions of each signal alternate.

Figure 5: A Signal Transition Graph and its State Transition Diagram

Figure 6: A Persistent Signal Transition Graph with non-persistent underlying Petri net

Two STG markings  $m_1$  and  $m_1'$  are equivalent if for each finite firing sequence  $m_1[t_1 > m_2[t_2 > \dots$  there exists a firing sequence  $m_1'[t_1' > m_2'[t_2' > \dots$  such that  $\Delta(t_i) = \Delta(t_i')$  for all i. This relation partitions the set of reachable markings into equivalence classes. The equality between STG markings (and hence STD states) in the following will always be modulo this equivalence  $^{13}$ .

An STG is persistent if for each reachable marking  $m_1$ , if  $t_1$  is enabled in  $m_1$  and  $m_1[t_2 > m_2$ , with  $\Delta(t_1) \neq \Delta(t_2)$ , then there exists a transition  $t_3$  enabled in  $m_2$  such that  $\Delta(t_1) = \Delta(t_3)$ . An STG is output persistent if the above definition holds for all  $t_1$  such that  $\Delta(t_1) \in Z$ .

Note that this definition of STG persistence allows a case like that in Figure 6 to be treated as persistent, even though the underlying PN is not persistent. So PN persistency is a stronger condition than STG persistency. Only the transition labeling  $\Delta$  that maps two different PN transitions into  $y^+$  (and similarly for  $z^+$ ) "erases" the distinction that was present between the PNs underlying Figures 6 and 5.(a), so that the two STGs generate isomorphic STDs. This Figure illustrates clearly the "semantic gap" arising from using a purely interleaving semantics (as in the STD) versus using a true concurrent semantics (as in the STG).

The following Theorem is a direct consequence of the results in [26]:

#### Theorem 4.5

- 1. For every deterministic, commutative and persistent STD  $\mathcal S$  there exists an STG whose PN is persistent, bounded and generates  $\mathcal S$ .

- 2. For every distributive STD S there exists an STG whose PN is a safe Marked Graph and generates S.

- 3. For every distributive STD S there exists an STG whose PN is safe, persistent and generates S.

## 4.3 Signal Transition Graphs and Asynchronous Logic Circuits