# Copyright © 1992, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

by

Phu D. Hoang

Memorandum No. UCB/ERL M92/68

30 June 1992

by

Phu D. Hoang

Memorandum No. UCB/ERL M92/68

30 June 1992

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

by

Phu D. Hoang

Memorandum No. UCB/ERL M92/68

30 June 1992

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

by

#### Phu D. Hoang

#### **ABSTRACT**

The goal of this research is to develop a set of Computer-Aided Design (CAD) tools to support the real-time implementation of Digital Signal Processing (DSP) applications onto multiple programmable processors. The work has resulted in a complete DSP design environment, called McDAS, which can compile high level DSP applications directly down to parallel code for MIMD multiprocessors.

One of the major challenges of the research is the assignment and scheduling of tasks onto the processors in such a way as to maximize the throughput of the resultant implementation while considering interprocessor communication delays and resource constraints imposed by the target architecture. The scheduler in McDAS exploits pipelining, retiming, and parallel execution simultaneously, allowing the environment to efficiently support a wide range of applications with different types of concurrency. Users can invoke the scheduler with different architecture configurations to explore implementation trade-offs.

The code generator is similarly retargetable to different multiprocessor architectures as well as core processors. Data buffers and synchronizations are automatically inserted to ensure correct execution. The final implementation can be used for simulation speedup or real-time processing.

The results on a set of benchmarks demonstrate McDAS's ability to achieve near optimal speedups across a wide range of applications.

Jan M. Rabaey

Thesis Committee Chairman

#### **ACKNOWLEDGEMENT**

So many people have enriched my life during my years at Berkeley. First of all, I am indebted to my research advisor Jan Rabaey for his generous support and encouragement of my work, and for allowing me the freedom to be involved in other projects in addition to my main research. Of these ventures, working on the HYPER high level synthesis project has been the most rewarding. Thank you, Jan, for your advice, for your vision, for your unmatched programming style, for everything.

I would also like to thank Professors Edward Lee and Sadashiv Adiga, who served on my qualifying exam committee, as well as my thesis committee. Professor Lee, in particular, sparked my interest in DSP multiprocessor scheduling, and continued to provide invaluable guidance to me during our many discussions. Thank you, Edward, for all of your help.

My first two years, and my masters thesis, were with the Optimization CAD group, headed by Professor Polak. I would like to thank him for his help and guidance.

The BJgroup headed by Professors Brodersen and Rabaey was an excellent environment for research. I thank Professor Brodersen for sharing his deep knowledge and experience in VLSI Signal Processing. Special thanks to Miodrag Potkonjak, Paul Landman, Sean Huang, Lisa Guerra, Ingrid Verbauwhede, Wook Koh, Alfred Yeungk, and Mani Srivastava for their endless reviews of my work.

The friends that I have made at Berkeley will forever enrich my life. Miodrag Potkonjak was and will always be a friend, a teacher, and a brother. My first roommate, David Sze, was always there when I needed him. To him, my deepest appreciation. To my great friend John Coble: Hail to the Redskins!! Away from home, my Vietnamese friends at Berkeley were my family. Thank you, Quyen, Hung, Dinh, Tai, Khanh, Chris, Quan, and Johnny, for all the dinners, movies, and late-night card games.

To my best friend Quyen: All my warmth and love. Thank you for your patience, your forgiveness, your caring, and your belief in me. The last two years have been wonderful.

My brothers and sisters are a source of inspiration. Thank you each and every one of you for spoiling me all of these years.

Lastly, I would like to dedicate this thesis to my parents, who I love more than anything in this world. To my father, for his infinite love and sacrifice. To my mother: I am 1 year, 1 month, and 27 days late. I wish you were here to celebrate with me today.

# TABLE OF CONTENTS

| 1 I | INTRODUCTION                                                                                                                                                      | 1              |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.1 | OVERVIEW                                                                                                                                                          |                |

| 1.2 | APPLICATION DOMAIN                                                                                                                                                | 2              |

| 1.3 | CONTRIBUTION                                                                                                                                                      |                |

| 1.4 |                                                                                                                                                                   |                |

| 2 H | BACKGROUND                                                                                                                                                        | 9              |

| 2.1 | BASIC CONCEPTS  2. 1. 1 Performance  2. 1. 2 Concurrency  2. 1. 3 Granularity                                                                                     | 9<br>9         |

| 2.2 | MULTIPROCESSOR ARCHITECTURE  2. 2. 1 A Taxonomy  2. 2. 2 MIMD Computers  2. 2. 3 DSP Multiprocessor Systems                                                       | 15<br>15       |

| 2.3 | PARALLEL PROGRAMMING                                                                                                                                              | 23<br>23       |

| 2.4 | MULTIPROCESSOR SCHEDULING  2. 4. 1 Classification  2. 4. 2 Complexity Analysis  2. 4. 3 Basic Multiprocessor Scheduling  2. 4. 4 Multiprocessor Scheduling in DSP | 30<br>33<br>33 |

| 2.5 | COMPARISON                                                                                                                                                        |                |

| 2.6 | SUMMARY                                                                                                                                                           | _              |

| 3 T | THE McDAS ENVIRONMENT                                                                                                                                             |                |

| 3.1  | McDAS SYSTEM OVERVIEW                              | 44  |

|------|----------------------------------------------------|-----|

| 3.2  | SILAGE                                             | 47  |

| 3.3  | FLOWGRAPH DEFINITION                               | 51  |

|      | 3. 3. 1 Flowgraph Model                            |     |

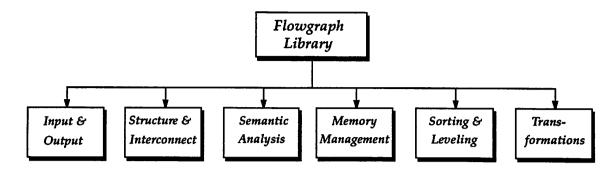

|      | 3. 3. 2 Flowgraph Library                          |     |

| 3.4  | ARCHITECTURE DATABASE                              | 55  |

| 3.5  | SUMMARY                                            | 57  |

| 4 \$ | SILAGE TO FLOWGRAPH TRANSLATION                    | 59  |

| 4.1  | BASIC TRANSLATION                                  | 59  |

|      | 4. 1. 1 Handling of Delayed Signals                |     |

|      | 4. 1. 2 Generation of Arrays                       |     |

| 4.2  | CDFG OPTIMIZATION                                  | 63  |

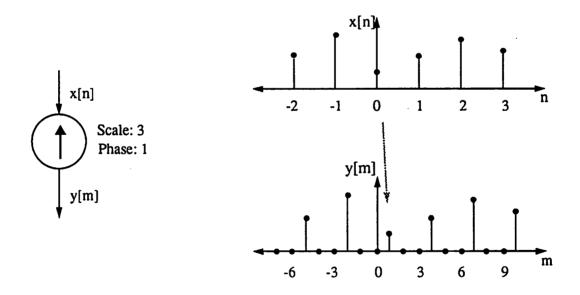

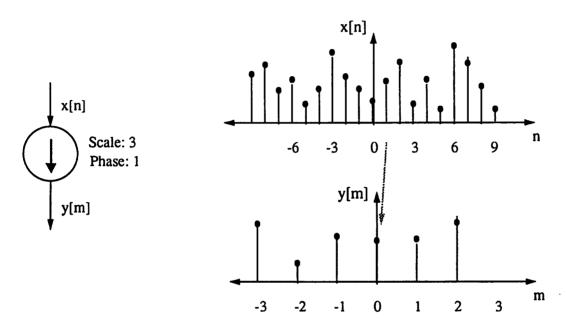

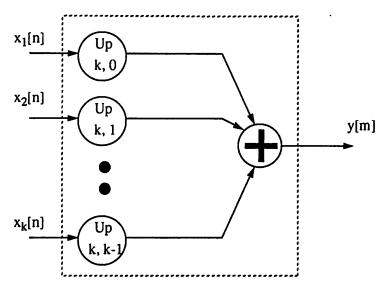

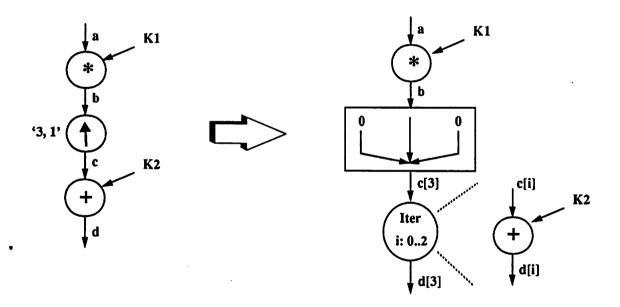

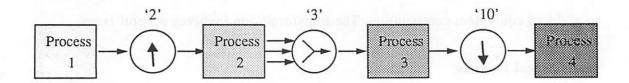

| 4.3  | MULTIRATE APPLICATIONS                             | 64  |

|      | 4. 3. 1 Introduction                               |     |

|      | 4. 3. 2 Multirate Transformation                   |     |

| 4.4  | SUMMARY                                            | 72  |

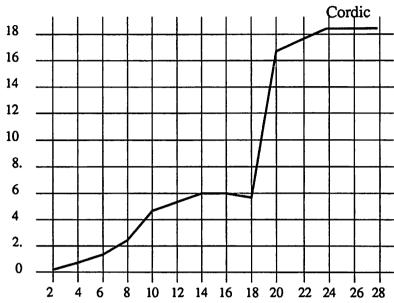

| 5.1  | A MOTIVATING EXAMPLE                               |     |

| 5.2  | COMPUTATION MODEL                                  | 76  |

|      | 5. 2. 1 A Multiprocessor Schedule                  |     |

|      | 5. 2. 2 Evaluation of a Schedule                   | 81  |

| 5.3  | ARCHITECTURAL SUPPORT                              | 82  |

|      | 5. 3. 1 Processor Characteristics                  |     |

|      | 5. 3. 2 Multiprocessor Topology                    | 83  |

|      | 5. 3. 3 Interprocessor Communication               | 84  |

| 5.4  | ESTIMATING COMPUTATION TIMES & MEMORY REQUIREMENTS | 86  |

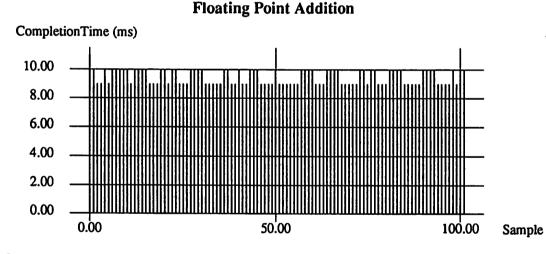

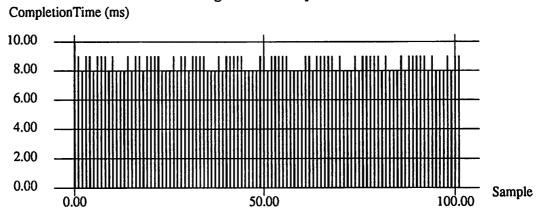

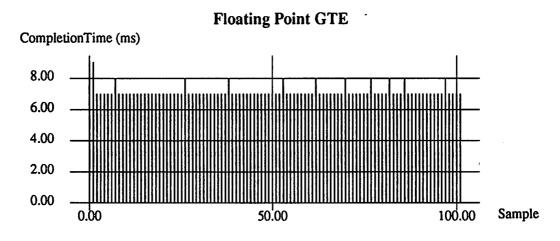

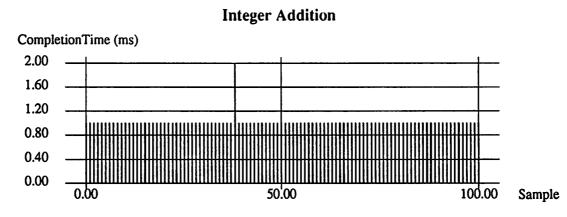

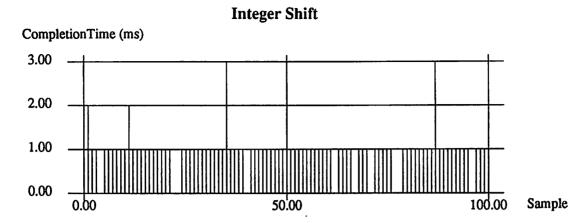

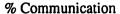

|      | 5. 4. 1 Operator Benchmarking                      |     |

|      | 5. 4. 2 Model Construction                         | 93  |

|      | 5. 4. 3 Limitation of the Technique                | 95  |

|      | 5. 4. 4 Memory Estimation                          | 96  |

| 5.5  | ESTIMATING COMMUNICATION DELAYS                    |     |

| 5.6  | SUMMARY                                            | 101 |

| 6 9  | CHEDULING                                          | 102 |

|      |                                                    |     |

| 0.1  | PROBLEM DEFINITION                                 | 104 |

|                  | <ul><li>6. 1. 1 Problem Formulation</li><li>6. 1. 2 Previous Approaches</li></ul> |         |

|------------------|-----------------------------------------------------------------------------------|---------|

|                  | 6. 1. 3 Our Scheduling Strategy                                                   |         |

| 6.2              | SCHEDULING FOR FIXED THROUGHPUT                                                   |         |

|                  | 6. 2. 1 Definitions                                                               |         |

|                  | 6. 2. 3 Node Scheduling                                                           |         |

|                  | 6. 2. 4 Complexity Analysis                                                       |         |

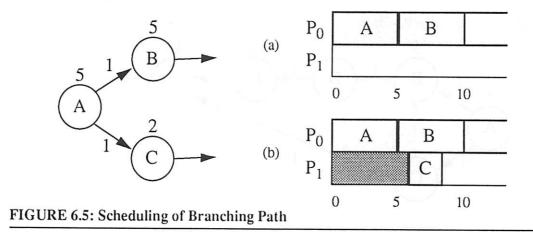

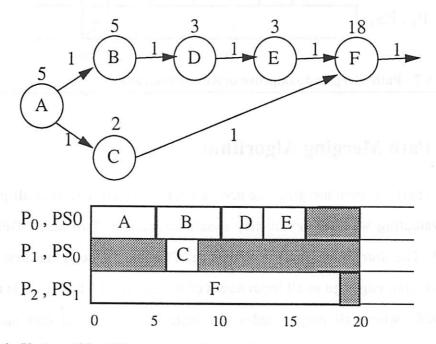

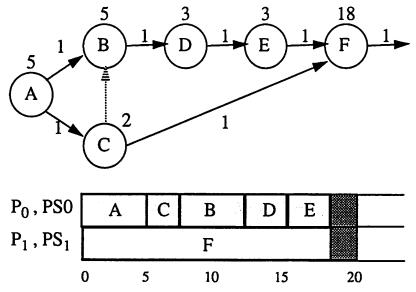

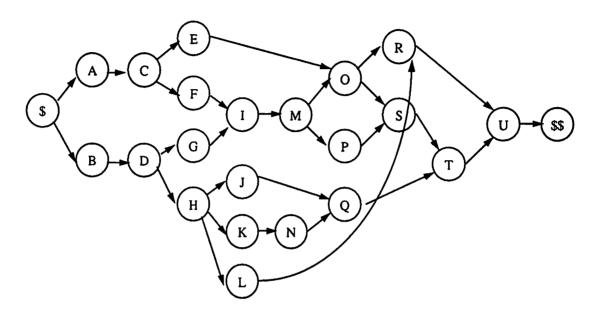

| 6.3              | PATH MERGING                                                                      | 116     |

|                  | 6. 3. 1 Problem Definition                                                        |         |

|                  | 6. 3. 2 Path Merging Algorithm                                                    |         |

|                  | 6. 3. 3 Complexity Analysis                                                       | 122     |

| 6.4              | RETIMING                                                                          |         |

|                  | 6. 4. 1 Problem Definition                                                        |         |

|                  | 6. 4. 2 Retiming Algorithm                                                        |         |

|                  | 6. 4. 3 Complexity Analysis                                                       |         |

| 6.5              | NODE DECOMPOSITION                                                                |         |

|                  | 6. 5. 1 Bottleneck Node Decomposition                                             |         |

|                  | 6. 5. 2 Critical Cycle Decomposition                                              |         |

| 6.6              | SCHEDULING FOR MAXIMUM THROUGHPUT                                                 |         |

|                  | 6. 6. 1 Bounded Search Heuristic                                                  |         |

| 6.7              |                                                                                   |         |

| 0.7              | SUMMARY                                                                           | 134     |

| 7 C              | CODE GENERATION                                                                   | 137     |

| 7.1              | OVERVIEW                                                                          | 138     |

| 7.2              | MEMORY MAPPING                                                                    | 140     |

|                  | 7. 2. 1 The FIFO Communication Model                                              |         |

|                  | 7. 2. 2 Local Synchronization                                                     |         |

|                  | 7. 2. 3 Shared Memory Implementation                                              |         |

|                  | 7. 2. 3. 1Centralized Shared Memory                                               |         |

|                  | 7. 2. 4 Message-Passing Implementation                                            |         |

| 7.3              | CODE EMISSION                                                                     | 148     |

|                  | 7. 3. 1 Circular Buffering                                                        |         |

|                  | 7. 3. 1. IInterprocessor Communication                                            | 149     |

|                  | 7. 3. 1. 2State Variables.                                                        |         |

|                  | 7. 3. 2 C Code Emission                                                           |         |

|                  | 7. 3. 3 Floating-Point & Fixed-Point Simulation                                   |         |

| 7.4              |                                                                                   |         |

| / . <del>+</del> | SUMMARY                                                                           | ・・・・コンソ |

| 8 S    | SCHEDULING RESULTS                                                       | 161 |

|--------|--------------------------------------------------------------------------|-----|

| 8.1    | TARGET ARCHITECTURES                                                     | 161 |

|        | 8. 1. 1 The Sequent Symmetry Multiprocessor                              |     |

|        | 8. 1. 2 The SMART Multiprocessor                                         |     |

| 8.2    | RESULTS                                                                  |     |

| 0.2    | 8. 2. 1 Scheduling a Histogram Computation on the Sequent Multiprocessor | 165 |

|        | 8. 2. 2 Scheduling a Cordic Computation on the SMART Multiprocessor      |     |

|        | 8. 2. 3 Scheduling Different Applications                                | 174 |

|        | 8. 2. 4 Scheduling Applications with Global Recursions                   | 177 |

| 8.3    | SUMMARY                                                                  |     |

| 9 (    | CONCLUSION                                                               | 181 |

|        |                                                                          |     |

| 9.1    | SUMMARY                                                                  | 181 |

| 9.2    | FUTURE RESEARCH                                                          | 183 |

|        | 9. 2. 1 Data Dependency Analysis                                         | 184 |

|        | 9. 2. 2 DSP Code Generation                                              |     |

|        | 9. 2. 3 Computation and Memory Estimation                                |     |

|        | 9. 2. 4 Scheduling for Heterogeneous System                              |     |

|        | 9. 2. 5 Scheduling Data-dependent Computations                           | 187 |

|        | 9. 2. 6 Loop Transformations                                             | 188 |

| 9.3    | SUMMARY                                                                  | 191 |

| 10     | REFERENCES                                                               | 193 |

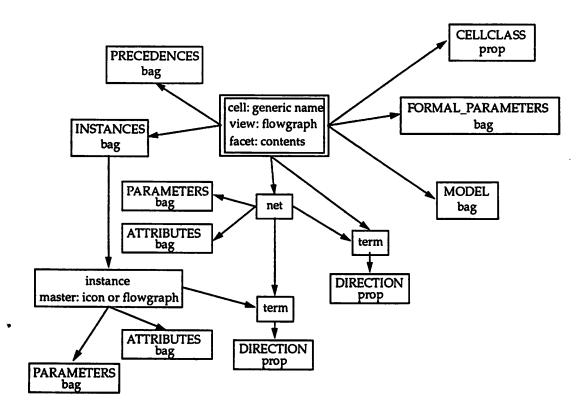

| Apj    | pendix A: Flowgraph Implementation                                       | 205 |

|        | Flowgraph Structure                                                      |     |

| 4 1. 1 | A.1.1 AFL Format                                                         |     |

| •      | A.1.2 OCT Format                                                         |     |

| ۸.2    |                                                                          |     |

|        | C Data Structure                                                         |     |

| A.3    | A Sample AFL Flowgraph                                                   | 213 |

| Apı    | pendix B: Silage To Flowgraph Implementation                             | 219 |

| B.1    | Silage Frontend                                                          | 219 |

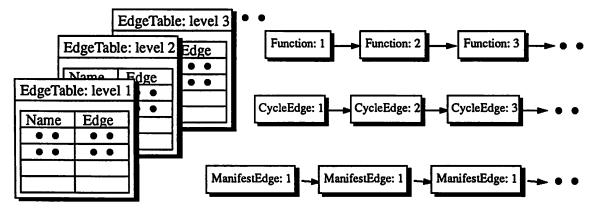

| B.2    | CDFG Generator                                                           | 221 |

|        | B.2.1 The Algorithm                                                      |     |

|        | B.2.2 The Data Structure                                                 | 225 |

|        |                                                                          |     |

| App    | pendix C: Code Generation Results                                        | 227 |

| C.1 | Histogram Silage Code              | 228 |

|-----|------------------------------------|-----|

|     | Histogram C Code                   |     |

| App | pendix D: McDAS User's Manual      | 243 |

| D.1 | McDAS Compilation Manager          | 244 |

| D.2 | Silage To Flowgraph Translator     | 246 |

| D.3 | Scheduler for Sequent              | 248 |

| D.4 | Scheduler for SMART                | 250 |

| D.5 | Scheduler for Ideal Multiprocessor | 252 |

| D.6 | Code Generator for Sequent         | 254 |

| D.7 | Silage Syntax                      | 256 |

1

## INTRODUCTION

#### 1.1 OVERVIEW

In recent years, a significant improvement in the computing power of programmable digital signal processors has been observed. New advances in architecture and technology have enable DSP processors to achieve throughputs up to 16.7 MIPS and 50 MFLOPS [Mot90]. Their high-speed performance, programmability, and low cost have already made them the ideal implementation medium in a number of real-time applications such as speech detection [Dau87] and speech encoding [Alr86]. Unfortunately, we have concurrently experienced an even greater increase in the computational requirements of DSP applications. For instance, a computation rate of 1 GFLOPS is typical for High Definition Television (HDTV) applications [Fre89]. In addition, the applications themselves are also becoming increasingly more complex, utilizing nested loop structures or multi-dimensional vector computations. Examples of this can be found in Code-Excited Linear Prediction coders [Cam90], CCITT Standard Visual Telephony [CC189], and JPEG and MPEG image compression algorithms [Wal89]. Currently, the only means to meet the high throughput demands of these applications is with special purpose hardware, which can be quite expensive and time consuming to build at the prototyping stage.

Given the success of the DSP processor, one approach to obtaining a greater computational power while maintaining a rapid prototyping capability is to employ multiple DSP processors working in parallel. As an example, a system of 20 Motorola DSP96002 DSP's can yield a peak throughput rate of 334 MIPS and 1 GFLOPS [Mot90]. Already we can see a number of academic and industrial DSP multiprocessor projects. These will be reviewed in Section 2.1.3.

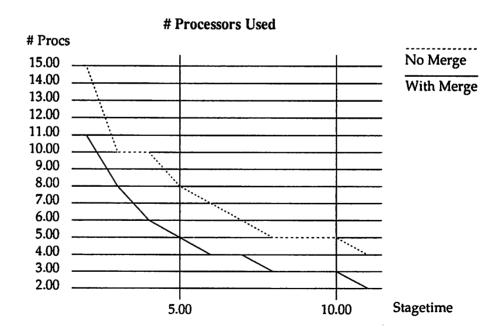

The major obstacle to the prevalent use of these multiprocessor systems, however, has been the absence of an adequate Computer Aided Design (CAD) environment to help system designers quickly design, simulate, and prototype their applications. In this thesis, we present a DSP design environment, called McDAS, which can generate efficient code for MIMD multiprocessors given a behavioral input description. The description is architecture-independent in that the designer does not have to tailor his specification to comply to a particular target architecture or execution scheme. The partitioning and scheduling of the application onto the processors, as well as the code generation, are completely automated. This allows the designer to devote all of his effort to designing and optimizing the application itself.

In the remainder of the chapter, the domain of DSP applications supported by McDAS is characterized, and arguments are given to justify why multiprocessors are good target implementations. A summary of the contributions of the thesis is presented, followed by an outline of the remainder chapters of the thesis.

### 1.2 APPLICATION DOMAIN

Our applications consists of medium to large-grain, synchronous digital signal processing systems. The term "medium to large-grain" indicates that the number of operations in the application is several (> 2) orders of magnitude greater than the number of processors available. Applications which do not fit this category are termed

fine-grain. The inherent overhead in programmable processors often precludes a high throughput implementation of fine-grain applications.

The term "synchronous" means that the amount of input samples consumed by each task in the application, and the amount of output samples generated, are known at compile time and invariable at run time. This fixed execution pattern allows a multiprocessor scheduler to produce a schedule at compile time, eliminating the run time scheduling overhead. Asynchronous systems, on the other hand, allows the production or consumption of samples in tasks to depend on the value of some data. This yields an execution pattern that is unpredictable, making high quality compile-time scheduling difficult. These applications will not be addressed in this thesis.

Medium to large-grain synchronous systems cover the majority of the common signal processing applications. These include filters, digital audio, speech processing, telecommunications, robotics, sonar, radar, and image processing. A close examination of the nature of the computations involved reveals that almost all applications contain some amount of concurrency, and most contain a substantial amount. For instance, all DSP applications are executed in an infinite time loop, giving rise to temporal concurrency which can be exploited by pipelining (see Section 2.1). In addition, many exhibit spatial concurrency which is amenable to parallel execution. The concurrency may not be easily detected however, as it can exist at different levels of granularity. For spatial concurrency at a large granularity or block level, there can be parallel tasks operating on the same data. At a fine granularity level, there can be operations performed on each element of a vector or matrix in parallel. Similarly, temporal concurrency can exist at the block level, or lower, such as between iterations of a serial loop.

### 1.3 CONTRIBUTION

We are interested in an implementation medium that can be used to quickly prototype a wide range of DSP applications. Employing multiple DSP processors in parallel is an attractive option in terms of cost, design time, and performance. The low cost and programmability of a DSP processor makes it an ideal processing element, and the abundance of available concurrency in DSP applications makes leads naturally to parallel processing.

While these powerful DSP multiprocessor engines are attractive, they are seldom used in the DSP community due to the lack of software tools to support the automatic scheduling and compilation of the input program onto the multiple processors. Currently, users of these machines have to partition their applications by hand, usually without any regard for optimization. The necessary interprocessor communication and synchronization are then determined, and finally, code is handwritten for each processor. This is a painstaking and error-prone process which is also likely to be suboptimal. The contribution of this thesis, hence, is a DSP design environment to automate this process.

## 1. 3. 1 Multiprocessor Scheduling

A key component in the system is the multiprocessor scheduling algorithm. The goal of the algorithm is to find a mapping of tasks onto processors in such a way as to maximize the throughput of the resultant implementation. All types of concurrency execution are employed to achieve the speedup. This includes pipelining, retiming, and parallel execution. Furthermore, the scheduler can traverse the application to any level of granularity, allowing concurrency detection to take place at a granularity level suitable with the available hardware resources. For example, for multiprocessor systems with few number of processors, the concurrency exploited is at a large

granularity. For systems with a large number of processors, the concurrency is exploited at a finer granularity level to fully utilize all the available processors. By considering granularity in conjunction with concurrency, the algorithm is able to efficiently schedule a wide range of DSP applications.

A scheduling algorithm is only useful if it is able to consider constraints imposed by the target architecture, specifically, the number of available processors and the amount of available memory in each processor. The scheduler uses these parameters as bounds to prune the search space to yield only feasible schedules. In addition, interprocessor communication delays can often take a significant portion of the overall execution time, and is therefore tightly integrated in the scheduling process to yield a high quality solution. The ability to take as inputs architectural descriptions allows the scheduler to be retargetable to different multiprocessor systems.

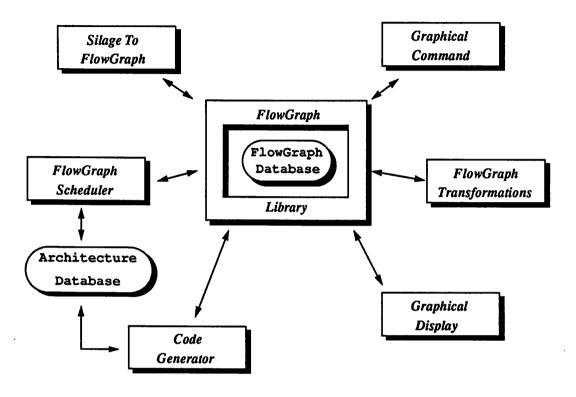

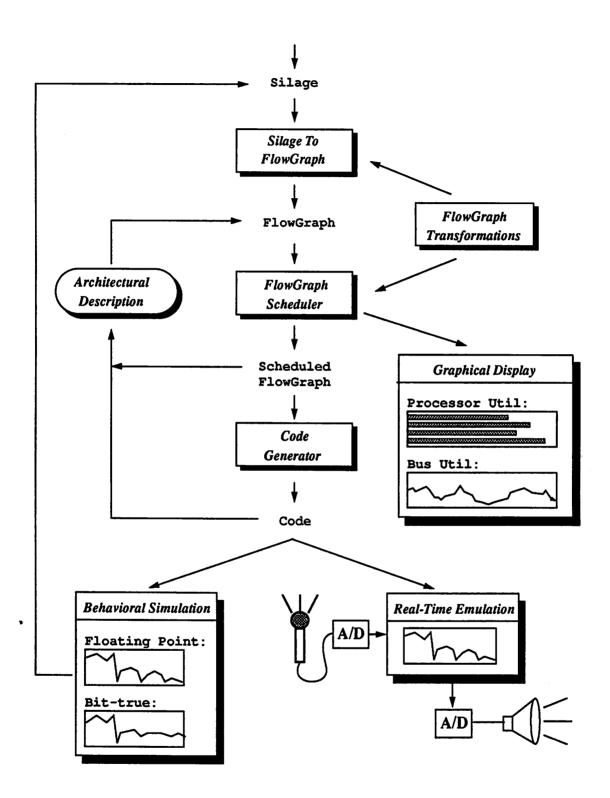

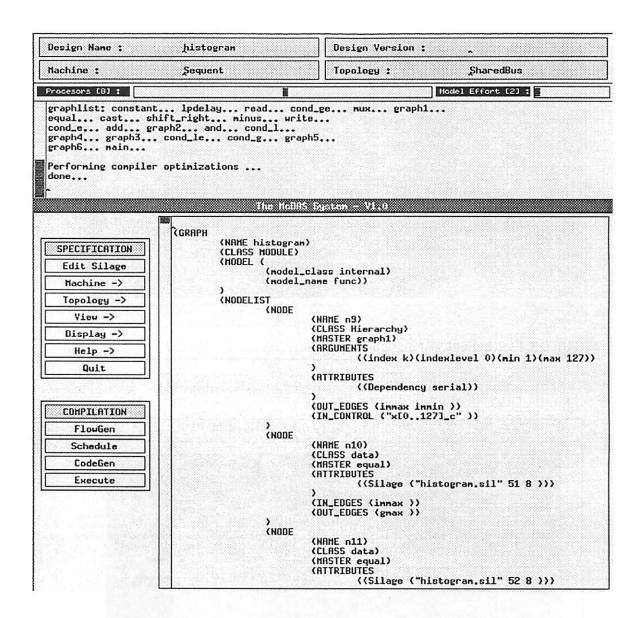

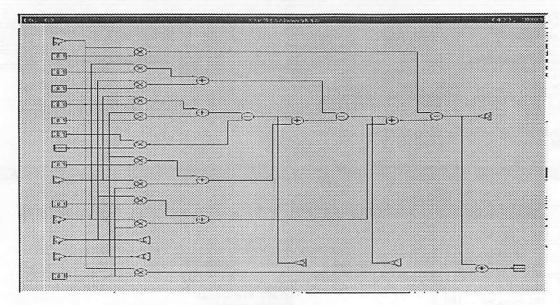

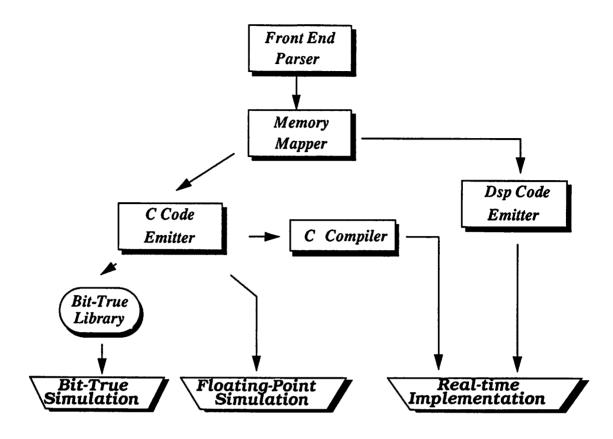

#### 1. 3. 2 Design Environment

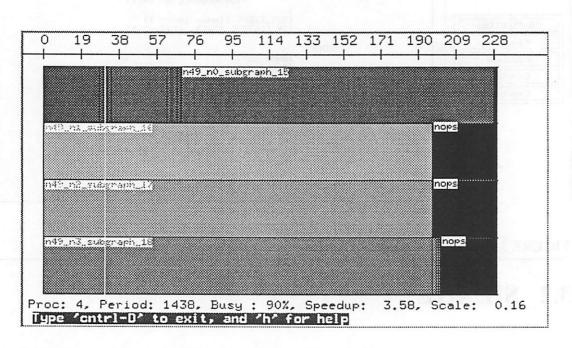

The McDAS environment augments the scheduler with a set of parsing and code generation tools to facilitate the prototyping process. The input textual description is parsed into a flowgraph representation, where concurrency is exposed explicitly. The flowgraph is hierarchical, structuring the application into many levels of granularity. The flowgraph serves as a central database on which all tools interact. This clean interface makes the system very modular, and allows new tools to be easily integrated. To schedule, the user only has to enter the processor count and the topology of the architecture and invoke the scheduler. Different implementations can be entered and scheduled to explore the design space. This is aided with a history mechanism for easy backtracking. Each scheduling result can be displayed with graphical tools showing processor assignment and utilization, as well as memory and bus usage. Finally, once a schedule is determined, code can be generated for each processor. The code generator supports functional simulation and real-time implementation. For simulation, C code is

emitted with bit-true or floating point data types to allow for the assessment of quantization and truncation effects. The code generator is similarly designed to be easily adaptable to different memory architectures and different processor instruction sets.

#### 1. 3. 3 Estimation

For the scheduling algorithm to perform well, accurate estimates of the computation and memory costs of the tasks are vital. A methodology for estimating computation times and memory requirements of operations is developed. The technique relies on benchmarking a target architecture with a set of programs to obtain execution times and memory usage of primitive operations. These values are then accumulated systematically to obtain estimates for large tasks. Results demonstrate that the technique is able to yield estimates to within 5% of the measured values.

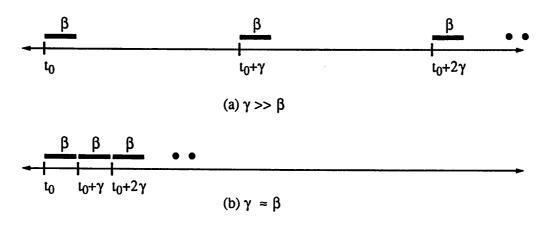

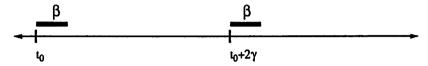

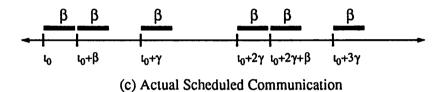

A detail model of the interprocessor communication process has also been developed. Each communication is explicitly scheduled on the appropriate bus or buses to take into account delays due to bus congestion. This technique enables the scheduler to accurately estimate the arrival time of a data to a processor given the time of the transfer, the source processor, and the state of the routing network. This parameter is critical to the scheduler in deciding which node-processor assignment is optimal.

### 1.4 PLAN OF THESIS

The remainder of the thesis is composed of eight chapters, organized as follows:

In Chapter 2, background material and previous work on parallel computation, multiprocessor architectures, multiprocessor compilers and scheduling theory are presented.

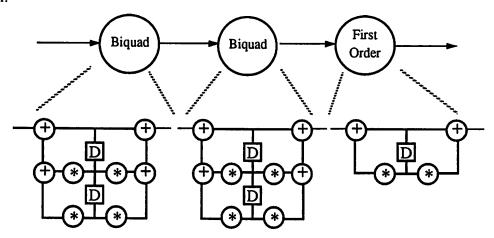

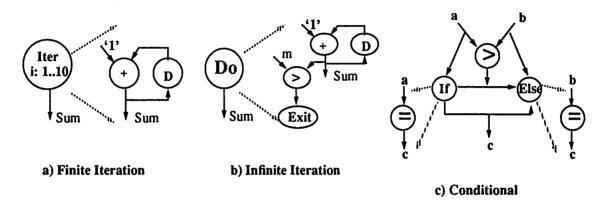

In Chapter 3, the McDAS DSP design environment is described in detail, and an overview of the entire compilation process is given. We will describe the input language Silage, as well as the hierarchical flowgraph format. Details are given as how certain hierarchical constructs such as function calls, loops, and conditionals are represented in the flowgraph. Finally, the parameters necessary to characterize a target architecture is presented.

In Chapter 4, we describe our front-end parser which translates a Silage textual description into a flowgraph. The organization of the program is presented, along with its features. The strategy for deriving data dependencies between operations, especially between array accesses and loop iterations, is outlined. A set of standard compiler optimizations which is incorporated into the parser is described. These include such transformations as dead-code elimination, common subexpression elimination, and manifest expression evaluation. Finally, a transformation to convert a multirate flowgraph to a single rate flowgraph via node clustering is presented.

In Chapter 5, the model of parallel computation in the McDAS environment is given. First, an example is given to motivate the model. The computation model is then presented, and a multiprocessor schedule is defined and interpreted. Thirdly, the architecture and the interprocessor communication model are discussed. Next, techniques for estimating computation times and memory requirements of DSP tasks are presented. We verify our estimations with actual measurements and discuss the limitation of the approach. Finally, the strategy for estimating interprocessor communication delay is presented.

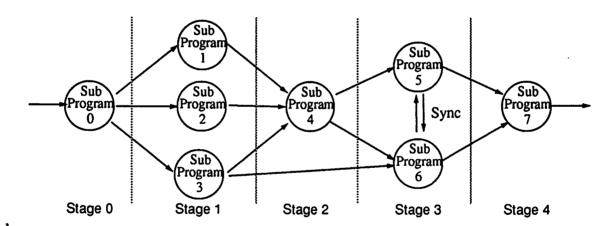

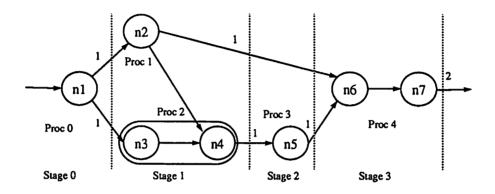

In Chapter 6, we present our scheduling algorithm under two performance objectives: a) Given a fixed available sample period, determined the minimum number of processors needed, b) Given a fixed amount of processors, determine the fastest throughput implementation. The details of the node-processor assignment strategy is described, emphasizing how it can simultaneously consider pipelining and parallel

execution. The algorithm is then extended to perform retiming when flowgraph cycles are present. The granularity issue is addressed with the node decomposition flowgraph transformation. We show how node decomposition combined with pipelining and parallelism allow our scheduler to exploit block level parallelism, data parallelism, block level pipelining, and loop pipelining, all in a unified manner. The results of the scheduling are shown for a wide set of examples.

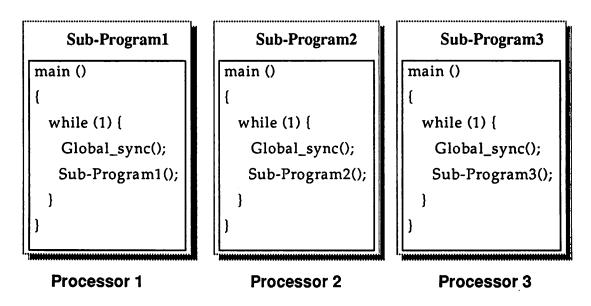

In Chapter 7, the code generation strategy is introduced. The first phase is the memory mapper phase, which allocates buffers for interprocessor communication and determines local and global synchronizations. We discuss how different memory architectures affect the interprocessor communication strategy. The organization of the code emitter is then described, detailing our implementation of buffers, I/O, and sample delays. Finally, a mechanism for performing fixed-point and floating-point simulations from the same C code is presented.

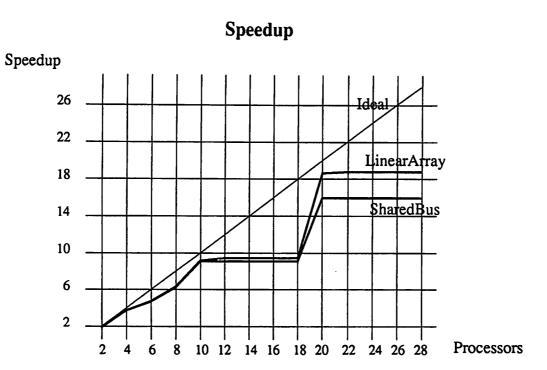

In Chapter 8, we describe two multiprocessor systems which have been targeted by McDAS. The first system is the Sequent system, a shared-bus multiprocessor machine composed of 14 PE's. The second system is the SMART system, a configurable bus machine composed of 10 PE's. Results obtained from scheduling different applications on both architectures are analyzed and compared.

Finally, in Chapter 9, we conclude the thesis, and point out directions for future research.

2

## BACKGROUND

In this chapter, the previous work in multiprocessor architecture, parallel languages and compilers, and multiprocessor scheduling theory is presented and analyzed. In Section 2.1, a number of key concepts and terminologies in parallel computing is introduced. In Section 2.2, a classification of computers is presented and their target applications described. The section ends with a detail look at multiprocessor systems for DSP applications. In Section 2.3, the software aspects of multiprocessing is treated, including parallel languages and compiler systems. Again, the section ends with a discussion on multiprocessor software systems for DSP. Section 2.4 reviews the research efforts in the area of multiprocessor scheduling, concentrating on those useful for DSP. Finally, the McDAS environment and its scheduling algorithm are compared with other systems in Section 2.5.

#### 2.1 BASIC CONCEPTS

#### 2. 1. 1 Performance

In parallel computation, multiple processing units are employed to achieve a higher computational performance over a single processor. The performance gain can be a reduction in *latency*, defined as the time elapsed between the arrival of an input

sample, and the availability of the corresponding output, or an increase in throughput, defined as the rate at which the system can process incoming input data.

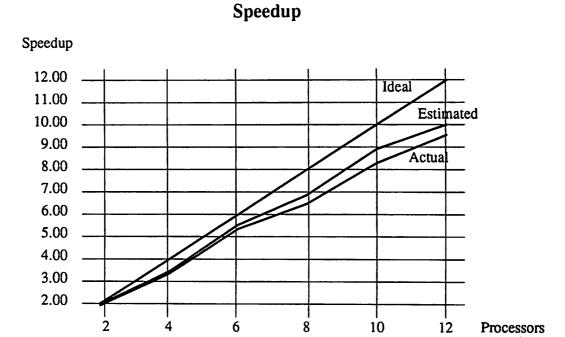

The performance gain is measured by the speedup over a single processor implementation. There are two types of speedup: Execution speedup or Latency speedup, and throughput speedup. Execution speedup on n processors is given as the execution time of an application on one processor over the execution time of the same application on n processors. Throughput speedup is given as the increase in the rate at which a system can process incoming data. The maximum achievable execution or throughput speedup for n processors is n.

Two criteria which can indirectly affect the speedup of an implementation are the *load balancing* and the *interprocessor communication overhead*. Load balancing tells how even the distribution of work is across the processors. When the load is unbalanced, lightly loaded processors sit idle waiting for the heavily loaded processors to finish. The lightly loaded processors are inefficiently used, resulting in poor speedup. Other measures equivalent to load balancing are maximizing processor utilization and minimizing idle time.

Interprocessor communication results when processors need to exchange data. The time devoted to these transfers can be substantial, especially in applications that are communication intensive. To minimize communication overhead, tasks that communicate heavily are put in the same processor, eliminating the communication. Note that this goal tries to cluster tasks together, while load balancing attempts to disperse tasks to different processors. A good schedule must consider both criteria to be effective. Another overhead which can arise is the synchronization overhead. Processors usually need to synchronize when they communicate, and thus minimizing communication also indirectly minimizes synchronization.

In this thesis, the performance speedup will be the main criteria for evaluating the quality of a multiprocessor implementation.

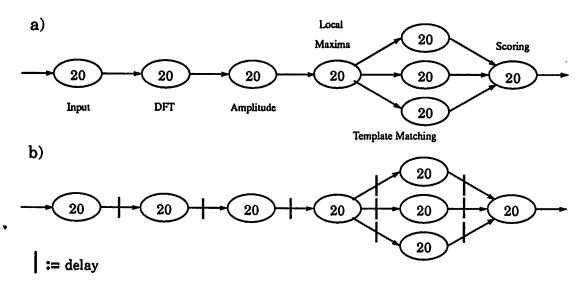

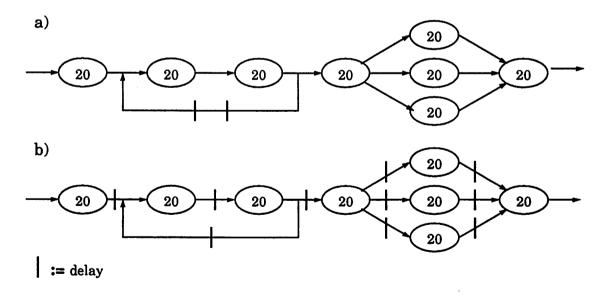

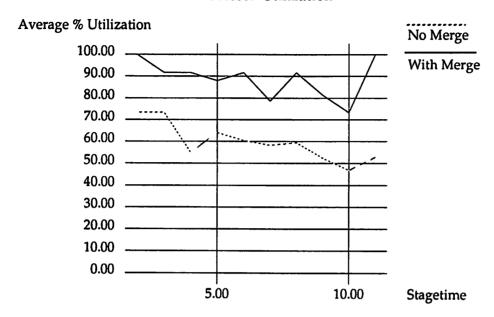

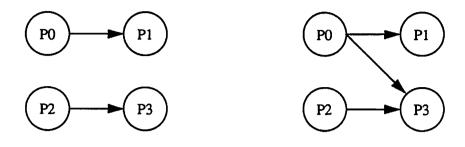

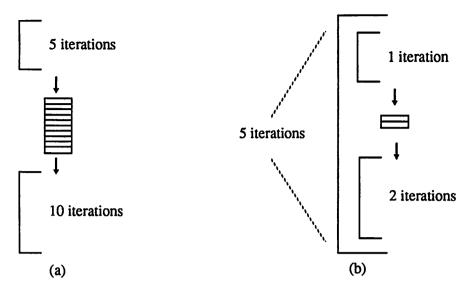

#### 2. 1. 2 Concurrency

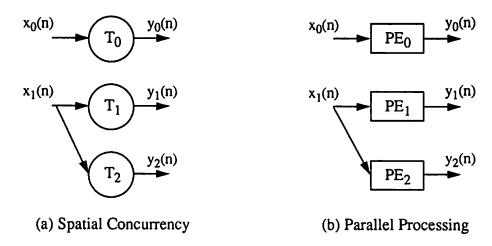

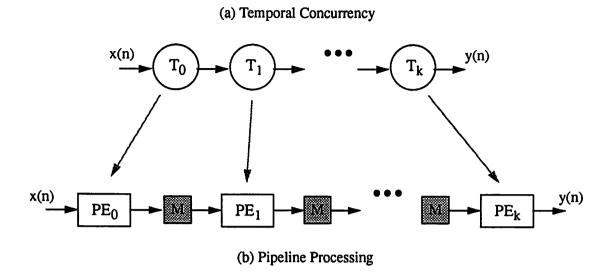

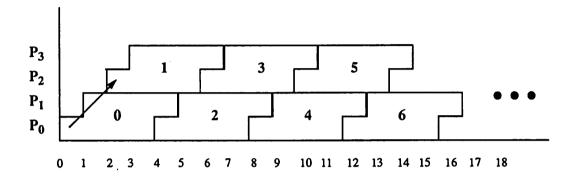

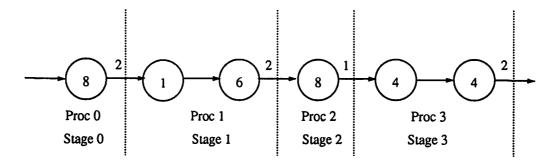

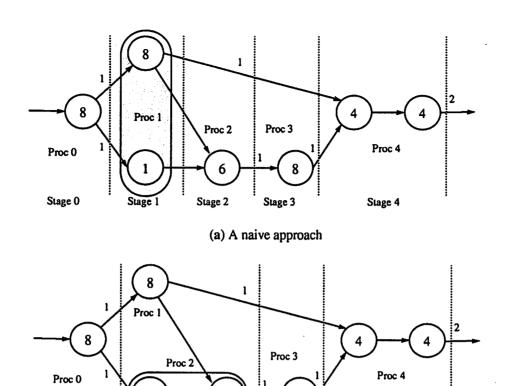

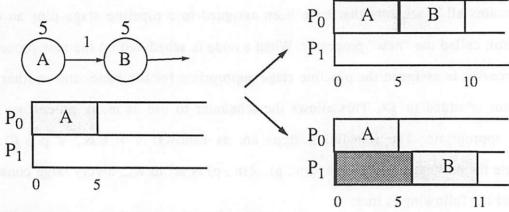

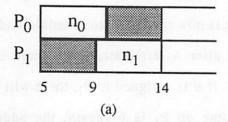

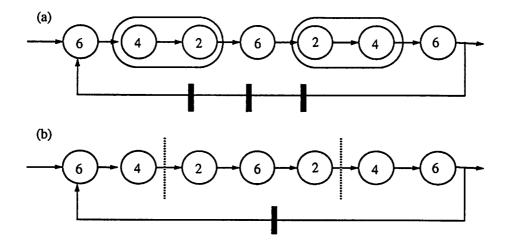

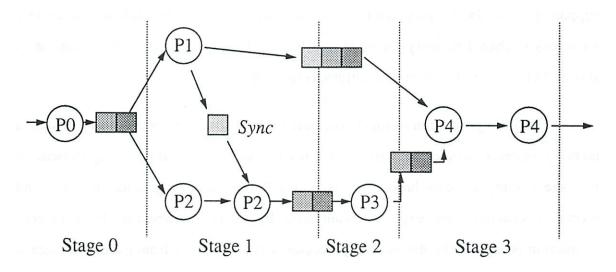

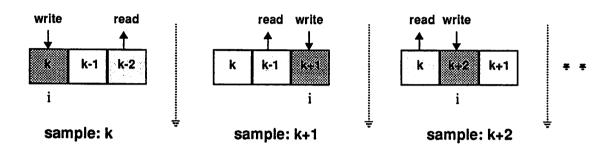

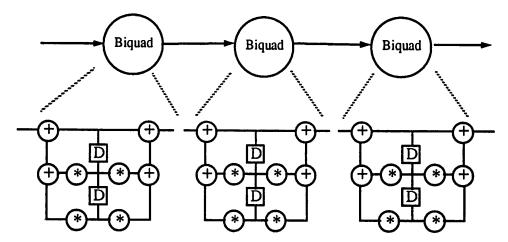

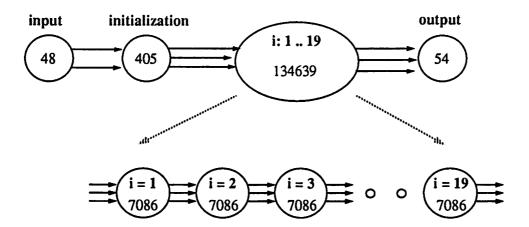

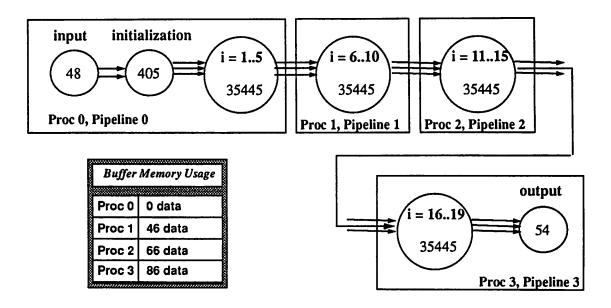

The performance gain is obtained by exploiting the concurrency available in the application. There are two types of concurrency available, each giving rise to a corresponding concurrent processing methodology. There is spatial concurrency (parallelism) (Figure 2.1a), where there are tasks which can be executed by several processors simultaneously without affecting the resultant output. This methodology is called parallel processing (Figure 2.1b). There is temporal concurrency (Figure 2.2a), where there is a chain of tasks which is embodied in an infinite time loop. Concurrent processing of these tasks involves dividing the chain into stages, with every stage handling results obtained from the previous stage. This methodology is called pipelining or pipelined processing, and is illustrated in Figure 2.2b. Pipeline processing

FIGURE 2.1: Parallelism and Parallel Processing

is possible in DSP applications due to the inherent nature of signal processing to repeat the same computation to each sample of the input stream. Note that for pipelining to work, buffer memories must be inserted between the stages to store intermediate values.

FIGURE 2.2: Pipeline Concurrency and Pipeline Processing

Algorithmically, each pipelining operation corresponds to an insertion of a sample delay into the computation. Thus, in a computation pipelined into k stages, each output sample y(n) corresponds to the resultant output of the input sample x(n-k). In the Z domain, the output is  $Y(z) = T_k(z) \cdots T_1(z) z^{-k}X(z)$ . The  $z^{-k}$  latency is called sample latency. In general, exploiting parallelism reduces latency, and exploiting pipelining increases the throughput. The simultaneous application of both parallel and pipeline processing can significantly improve both the latency and the throughput of a system.

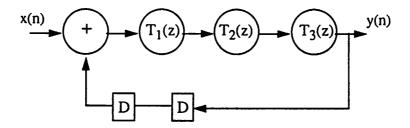

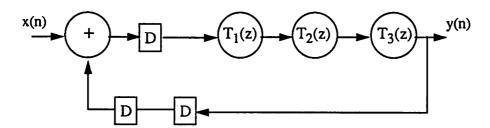

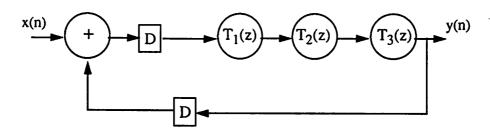

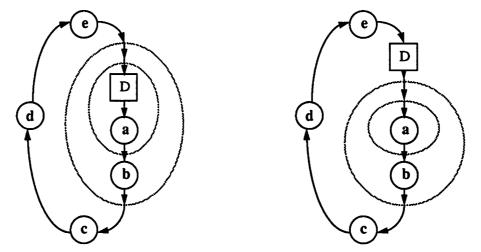

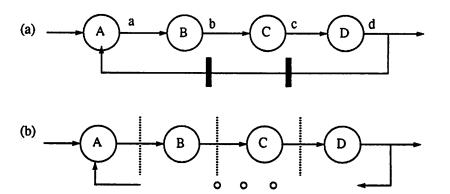

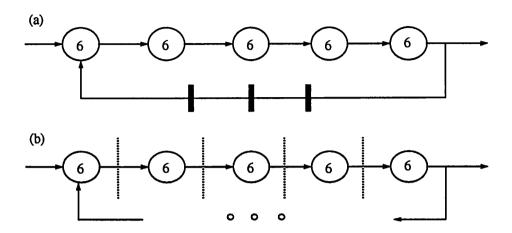

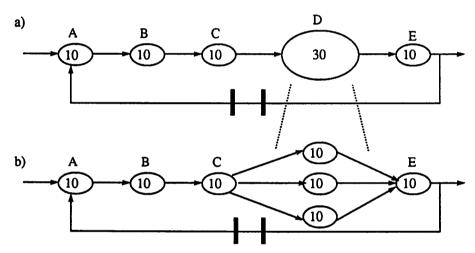

Some applications may possess feedback or recursion, that is, when the processing of a sample is dependent of the resultant processing of a previous sample. This shows up in a flow graph as a cycle with one or more sample delays, as shown in Figure 2.3(a). Inside a cycle, pipelining can alter the functionality of the algorithm, which is undesirable. Let  $T(z) = T_3(z)T_2(z)T_1(z)$ . In Figure 2.3(a), the Z domain output is  $Y(z) = T(z) [z^{-2} Y(z) + X(z)]$ . The output for Figure 2.3(b) is  $Y(z) = T(z) [z^{-3} Y(z) + z^{-1} X(z)]$ , which is different from the output in Figure 2.3(a). One technique which allows us to effectively pipeline the cycle while maintaining the correct functionality is the retiming transformation. Retiming involves the rearranging of delays within cycles to achieve better performance. It has been used extensively in optimizing circuit

(a) Flow graph with feedback

(b) Delay insertion changes the functionality

(c) Retiming retains same algorithm

#### FIGURE 2.3: Retiming

performance [Lei83], but is of great value in signal processing as well. Figure 2.3(c) shows a retiming of the flow graph. The output is  $Y(z) = T(z) [z^{-1} X(z) + z^{-2} Y(z)]$ . This is the same computation as in Figure 2.3(a) if the input stream is delayed by a sample. The use of pipelining, parallelism, and retiming exploits all types of concurrency available in DSP applications.

#### 2.1.3 Granularity

The concurrency in DSP applications can exist at all levels of granularity, from the largest block level granularity to the finest data level granularity. At the block level, spatial concurrency gives rise to block level parallelism, where there are independent tasks simultaneously processing their input data. At the data level, spatial concurrency takes the form of data parallelism or data partitioning, where identical operations are applied to each member of the vector or a matrix. Temporal concurrency at the block level is amenable to block level pipelining, while at a lower loop level granularity, loop pipelining or loop winding[Gir87] can be employed. The ability to exploit different types of concurrency at different granularity levels allows the consideration of all of the above techniques in a unified manner. It should be noted that combining data parallelism with retiming can improve the throughput of recursive applications. This will be expanded further in later sections.

The optimal granularity level exploited by a scheduler should be dictated by the number of processors present and the communication overhead. The greater the number of processors available, the smaller the granularity level should be. This guarantees that enough concurrency is exhibited to be used by all the processors. Beyond a certain granularity however, the large number of operations present may significantly slow down the scheduler. Furthermore, the interprocessor communication cost begins to play a dominant role in the overall execution time. In particular, it may take less time to execute two nodes in one processor than to spread them to two processors and suffer the communication overhead. This saturation effect has been observed by a number of researchers [Chu80] [Kri87]. In [Sar89] Sarkar attempts to capture this trade-off by assigning a cost to a granularity level equal to the maximum of the flow graph critical path and the flow graph communication overhead. If the granularity is too fine, the overhead term will be large, causing the cost to be large. If the granularity is too coarse, the critical path term will be large, also causing the cost to

be large. The cost will be minimum at an optimal intermediate granularity. The overhead term is calculated as the sum of the scheduling overhead of a node, over all nodes in the flow graph, plus the input and output communication overhead. A similar technique was used by McCreary and Gill [McC89]. They first cluster nodes into a hierarchy of clans, defined as a group of nodes with the same input and output nodes. Traversing the clan hierarchy bottom up, they determine whether it is cheaper to execute the clan in one processor or not. If it is, the nodes in the clan are clustered. The cost function is the execution time of the nodes, as well as the input and output communications.

These work are significant as they recognize the importance of granularity in multiprocessor scheduling. However, their approach separates the granularity determination and the scheduling itself. As a result, their modelling of the communication costs is done without knowing in detail the activities on the bus. We believe that granularity determination is best done in conjunction with the scheduling process, in an iterative manner. In this way, the scheduler can decide to change the granularity of the flow graph based on previous scheduling results.

## 2.2 MULTIPROCESSOR ARCHITECTURE

## 2. 2. 1 A Taxonomy

There has been a rapid growth in the number of proposed and constructed architectures over the past 10 years. Flynn [Fly72] originally proposed a taxonomy to organize computers based on their processing of instructions and data. There are four classifications:

- 1. SISD Single Instruction, Single Data

- 2. SIMD Single Instruction, Multiple Data

- 3. MISD Multiple Instruction, Single Data

- 4. MIMD Multiple Instruction, Multiple Data

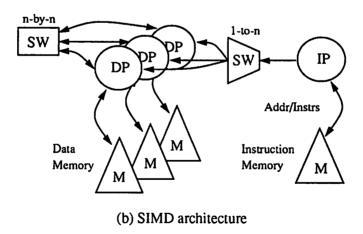

SISD architectures represent the standard von Newmann organization of most uniprocessor-based computers today. SIMD architectures incorporate an array of processing elements all executing the same instructions from a central controller. These are used to process elements of arrays in parallel. The SIMD technique can be found in vector or array processors of today's supercomputers [Nag84][Che84]. A number of SIMD computers have also been built to tackle problems with a massive amount of parallelism such as image and video processing, computer graphics, database, and simulations. Perhaps the most well known SIMD computer is the Connection Machine from Thinking Machines Inc.[Thi87], which can be configured with 65, 536 processors. Execution on MISD architectures would involve having multiple simultaneous instructions on the same piece of data. Pipeline machines are often mentioned to be of this style. The last category describes MIMD machines, which we commonly refer to as multiprocessor computers. These computers contain processors, each with its own independent controller. This enables the processors to execute different instructions on different data.

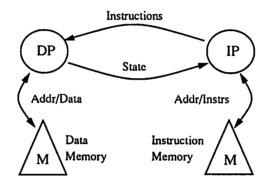

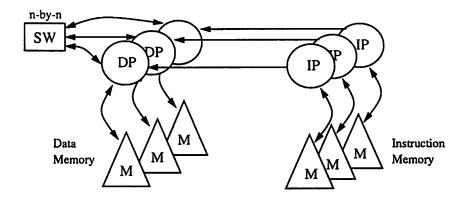

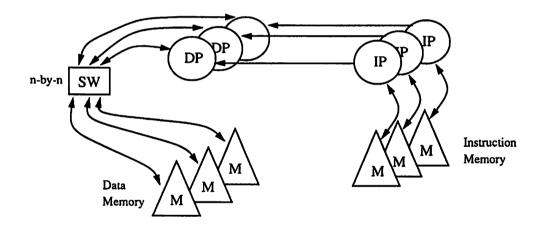

Recently, Skillicorn [Ski88] presented an extension to Flynn's taxonomy to classify the growing number of multiprocessor architectures more discriminantly. It is a two-level hierarchy in which the upper level classifies architectures based on the number of processors for data and for instructions, and the interconnection between them. A lower level can be used to distinguish variants even more precisely; it is based on a state machine view of the processors. In the taxonomy, there are four types of functional units from which any abstract machine can be constructed. These are:

- 1. IP An instruction processor to process instructions

- 2. DP A data processor to process data

- 3. M A memory hierarchy to store data

- 4. SW A switch to provide connectivity between other functional units

There are three different forms of switches. A 1-to-n switch connects 1 unit to n devices of another set of units. An n-to-n switch connects the ith unit of one set of functional units to the ith unit of another. This is equivalent to a 1-to-1 switch replicated n times. An n-by-n switch connects any device of one set of functional units to any other device of a second set.

With these definitions, a large number of architectures can be described precisely. Figure 2.4a shows the arrangement of a uniprocessor machine, while Figure 2.4b shows the abstract machine for an SIMD machine.

(a) Von Newmann SISD architecture

FIGURE 2.4: Skillicorn's Taxonomy for Computer Architectures

Skillicorn's classification allows for a much more detail discrimination of the large number of MIMD architectures that are available. These range from the familiar

shared memory and message passing computers to the exotic graph reduction [Dar81] and dataflow [Gur80] machines. In this thesis, we will be concern only with the first two architectures.

#### 2. 2. 2 MIMD Computers

The ability for each processor of an MIMD machine to autonomously work on a separate part of the problem makes MIMD machines much more general than SIMD machines. Unfortunately, the generality comes with a cost. Cooperating to solve a problem usually requires a tight interaction among the processors. SIMD machines achieve this via the common instruction flow. Since MIMD processors are independently controlled, communications and synchronizations among the processors are necessary. Extra time and resources must be reserved for these operations. The more processors that are used, the more the overhead incurred. Beyond a certain point, the addition of more processors may even decrease the performance due to the excessive overhead. This phenomenon is the saturation effect alluded to earlier. Since multiprocessing makes sense only when the speedup achieved outweighs the overhead paid in communications, MIMD machines tend to exploit parallelism at a coarser granularity than SIMD machines. As a result, the number of processors in MIMD systems (2-100) is usually much less than SIMD systems (100-100,000). With fewer 'processors, each core processor can afford to be much more powerful. There are two common methods for processors in MIMD computers to exchange data, via message passing and through shared memory. This gives rise to two classifications for MIMD computers: Multicomputers and multiprocessors.

#### 2. 2. 2. 1 Multicomputers

A multicomputer system consists of a number of processors that communicate asynchronously by sending and receiving messages across a network. There are no global or shared system resources. Each processor has its own private address space, its

own local memory and hardware support to transmitting and receiving messages. Using Skillicorn's classification, the multicomputer has a structure as shown in Figure 2.5.

FIGURE 2.5: An Abstract machine for a multicomputer

The send and receive constructs not only perform the communication, they also synchronize the data transfer to ensure the receive process only starts after the send process has completed. The processor interconnection can range from a set of connected buses to an elaborate nationwide network. Messages may be broken up into packets and routed through the network to the destination processor. The most well-known multicomputer is the Intel iPSC system [Int86]. In this system, processors are connected in a hypercube topology. A hypercube of dimension d has 2<sup>d</sup> processors, each one in direct link with d neighbors. Other topologies include the ring, tree, and mesh. Multicomputers are attractive because their interconnection and communication strategy can handle a large number of physically distributed processors, enabling a large user group and fault-tolerance. However, the cost of constructing and routing messages at run-time can be substantial. Multicomputers are also known as loosely-coupled systems or distributed systems.

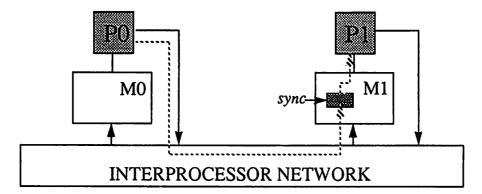

#### 2. 2. 2. Multiprocessors

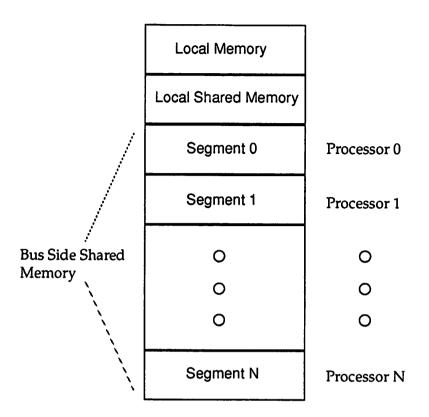

A multiprocessor system consists of a number of processors which communicate through shared resources. The programmer sees a single address space that all processors can access. To communicate, the sender writes the data to a specific memory location and the receiver reads the data from the location. This process must be done carefully to ensure correct data transfer. Firstly, the sender and the receiver must agree at compile-time what memory location will be used to implement the writing and reading. Secondly, they must synchronize so that the receiver processor only reads the data after the sender has completed the write. Multiprocessors are attractive because of their similarity to the uniprocessor from the programmer's point of view. Multiprocessors are also called tightly-coupled systems to reflect their resource sharing. An abstract multiprocessor machine is shown in Figure 2.6.

FIGURE 2.6: An Abstract machine for a multiprocessor

Multiprocessors can be further divided into two groups depending on whether the shared memory is centralized or distributed. In a centralized memory multiprocessor system, the single address space is also realized by a single memory space. If many processors shared the same data, only one copy of the data needs to be present in memory. The biggest drawback of a centralized memory is the memory access contention by the processors. Reads and writes to the same location must be queued,

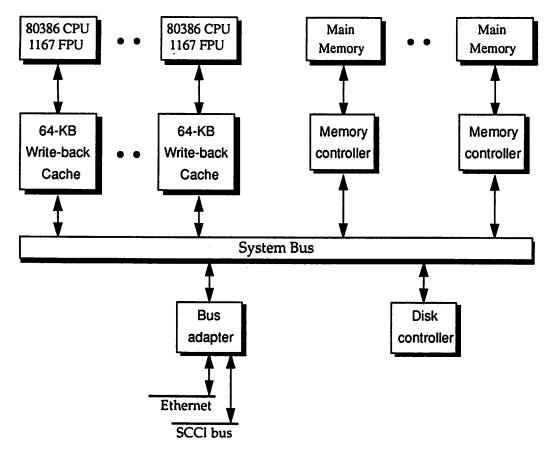

slowing down the system's performance. To alleviate this problem, caching can be used to reduce accesses to the central memory. However, the presence of caches in a multiprocessor system introduces the problem of *cache coherence*, which is, how to make sure a read always delivers the most recent value. Various techniques to solve this problem can be found in [Arc86][Rav83][Pap84]. One example of a centralized memory multiprocessor system is the Symmetry computer from Sequent Computer Systems [Ost86]. The Symmetry system has up to 30 Intel 30386 processors, connected by a single shared 64-bit wide bus. Each processor has a floating point co-processor and a 64KB write back cache. The memory system can have up to 6 controllers with up to 240MB total main memory.

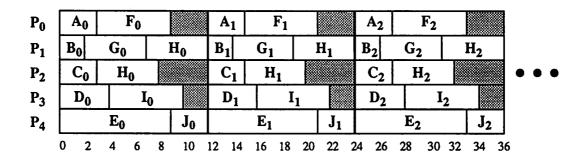

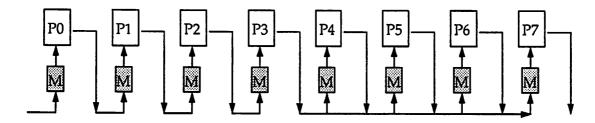

Extending the caching idea one more step, we get the distributed memory multiprocessor system. Here, the single address space is divided into sections, with each section assigned to a different processor. The shared memory is distributed so that the memory implementing a processor's section is physically located next to the processor. This locally resident memory effectively behaves as the processor's cache in that reading from this memory does not access any shared resources. However, since the memory is shared memory, the source processor can directly write data into the destination processor's section of memory. Thus, one possible distributed memory communication scheme is to have all writes go through the network, and have all reads be local. This global-write-local-read communication scheme can dramatically reduce the number of network accesses. The trade-off is that for broadcast data, all destination processors must have its own copy of the data in its section of memory. Figure 2.7 shows the global-write-local-read scheme on a distributed memory multiprocessor. This scheme can be found the distributed memory architecture of the SMART multiprocessor from U.C. Berkeley [Koh89].

FIGURE 2.7: Global-write-local-read Communication Scheme

#### 2. 2. 3 DSP Multiprocessor Systems

DSP Multiprocessors are multiprocessors constructed from DSP processors. These specialized processors are designed to maximize throughput in data intensive real-time applications. As such, they boast features like two or more concurrent memory accesses in one cycle, a floating point multiply-accumulate operation in one cycle, and zero-overhead hardware looping[Att88]. To maintain the high throughput support, DSP multiprocessors are designed to allow efficient interprocessor communication. Over the years, many DSP multiprocessor systems have been proposed or built. A few will be described here as a representative sample. One such system is the DADO2 DSP Multiprocessor system developed at AT&T Bell Laboratories for performing speech recognition [Sto85]. The DADO2 is composed of 15 processing elements (PE) connected in a binary tree topology. Each PE is comprised of an Intel 8751 processor, an AT&T DSP32 signal processor, and 64 Kbytes of local memory. The machine is used to implement various Dynamic Time Warping algorithms [Sak78] to perform the pattern matching necessary in speech recognition. Another system is the family of DSP multiprocessors designed at Georgia Tech [Bar91]. The first generation DSMP-I is composed of 16 AM29325 processors connected in a 2-dimensional grid. Each processor is capable of 5MFLOPS. The DSMP-II consists of 2 to 16 AT&T DSP32 processors connected in a ring. Each processor has a peak rate of 8MFLOPS. The DSMP-III currently under design would contain 16 to 128 TI TMS320C40 processors connected in a 3-dimensional grid. Each C40 processor is capable of 40 MFLOPS and has 6 communication ports. Lee and Bier at UC Berkeley proposed a multiprocessor architecture MOMA, for Maintains Ordered Memory Accesses [Lee90]. The special feature of this architecture is a central controller, which grants access to the shared memory bus in a prespecified, compiler-determined order. This guarantees synchronization, since whenever two processors must synchronize on a shared location, the writer is always granted control before the reader. One high performance multiprocessor machine which finds application in DSP is the WARP systolic machine from Carnegie Mellon University [Ann87]. It is also a linear array of 10 processor cell, each equipped with a large local data memory and capable executing at 10MFLOPS. The cells are connected in a ring architecture where each cell can transfer up to 80 Mbytes/sec to its neighbor cell. The large memory and I/O bandwidth enables the WARP machine to efficient support fine-grain data-parallelism.

#### 2.3 PARALLEL PROGRAMMING

While programming a uniprocessor machine has become standard practice, programming a multiprocessor system is still new and complex. The most efficient algorithms on serial machines may no longer be the most efficient for parallel machines. The programmer must now decompose the algorithm into parallel parts, map these onto the processors, layout the memory organization, and schedule the interprocessor communications. Even worse, these parallel programs often must undergo a major change or even be rewritten from scratch in order to run on a different multiprocessor.

#### 2. 3. 1 Parallelizing Compilers

To alleviate this burden, attempts have been made to design compilers that map existing sequential programs onto vector computers or multiprocessors. Most

supercomputer manufacturers such as Cray[Che84], Hitachi[Nag84] provide such compilers. In addition, there are a number of experimental work from third-party vendors and universities[Kuc84][Dav86][All87]. Perhaps the most notable work is the University of Illinois's Parafrase [Kuc84] and Stanford's SUIF projects [May91], which detects parallelism from Fortran programs and generates parallel code. This is done as a 3-phase process. The first phase involves an extensive data dependency analysis of the program to build a data dependency graph. The second phase applies various optimizations which can exploit the architecture. For computers with vector instruction sets, vector optimization or vectorization is appropriate. For multiprocessors, concurrent constructs are derived. Some optimizations available are scalar expansion, loop interchanging, fission by name, loop fusion, loop collapsing, and strip mining [Pad86]. Finally, the last phase generates the parallel code.

The hardest phase of the process is the data dependence detection, which translates into an integer programming problem [May91]. Since there are no efficient algorithm known for solving integer programming problems [Kan87], many compilers assume a data dependence whenever the dependence cannot be determined in a reasonable time. For special case inputs, efficient algorithms are available to determine exact dependence [Li90][May91].

• While the performance of these compilers are improving, they rest solely on their ability to extract parallelism from the program, which can be severely limited by the semantics of the language used and the possible unnecessary sequential organization of the code.

#### 2. 3. 2 Parallel Languages & Block Diagrams

Most programs for uniprocessors were written using Fortran, C, Pascal, or other conventional imperative languages. These languages were designed to let programmers manipulate data stored in the memory of a von Newmann computer. This

programming style translates a computational task, which may contain a large amount of concurrency, into a series of sequential memory fetches, stores and arithmetic operations. This artificial sequential ordering, termed the "von Newmann bottleneck" by Backus[Bac78], makes these languages unattractive for parallel programming. In addition, the close interaction of the language to the underlying memory storage allows routines to modify memory in very subtle ways. The use of "call-by-reference" allows a routine to modify parameters in the calling program. Also, most languages allow global variables that can be modified by any routine at any time. These side effects may inadvertently establish data dependencies between routines which were not intended.

Applicative (also called functional or data flow) languages have been proposed as a paradigm for parallel programming. It is an attempt to capture the flavor of a graphical flow graph in a linear textual form. In data flow, a program is interpreted as a flowgraph, with nodes and edges. Nodes represent instances of functions and arcs represent the flow of data between nodes. Data flow languages sequence program actions by a simple data availability firing rule: When a node's inputs (arguments) are available, the function associated with the node can be fired, i.e. applied to the arguments. After firing, the results are available at the node's outputs, and these may allow other nodes to fire. Thus, a node's outputs are only dependent on the node's inputs. There is no side effect to obscure data dependency. The main advantage resulting from this is that nodes which are not connected by a directed path are independent and can be executed in parallel. To enforce the data flow semantic, these languages possess properties such as a single assignment convention, a pass-by-value function call, an absence of global variables, a lack of history sensitivity, and others[Ack82]. Two examples of data flow languages include Val from MIT[Ack79] and Id from UC Irvine[Arv78]. These were developed in conjunction with the data flow computer projects at the respective universities. Silage[Hil85] is an applicative language developed especially for specifying DSP systems. It is the input language for the McDAS environment and will be described in more detail in a later chapter.

LUSTRE [Roc91] is a synchronous data flow language used to describe hardware controlled by a global clock. It has been used for high level synthesis in conjunction with the ESTEREL language [Ber91] used to describe controllers. Sprite [Kro92] combines applicative and functional constructs of applicative languages with operational constructs of sequential languages for high level synthesis. For real-time programming, the SIGNAL functional language [Gue91] is based on synchronous multiple-clocked flows of data and events. Still others such as Lucid[Ash77] and FP[Bac78] were designed to possess certain mathematical properties of functional application which make them amenable to program verification.

Instead of working on textual languages which represent flow graphs, some designers have chosen to work on the signal flow graphs themselves. Flow graphs or block diagrams have been used by engineers for years to represent their systems, whether it be in VLSI, parallel computation, DSP, or robotics. Recently, flow graphs are finding use as a tool for specification of computations, especially in the digital signal processing and VLSI design domain. In such a graphical design system, the user construct a design by connecting functional blocks together into a signal flow graph, using a graphical schematic editor. The blocks can have arbitrary functionality and may be defined in a standard library or by the user. Each block has associated with it code that implements the necessary processing functions. In the field of VLSI design, these graphical design systems are abundant. Examples can be found in the OCT environment at UC Berkeley[Har86], the System Architect's Workbench at Carnegie Mellon University[Wal87], and commercial tools from CAD vendors like Synopsys, Valid, Xilinx, etc.

It is very interesting to note that there are many models of computations which can be expressed with the same block diagram representation. These include dataflow, time-driven, control/data flow, and hybrid dynamical systems, all with very different execution semantics[Lee89a]. A block-diagram description is thus only complete when

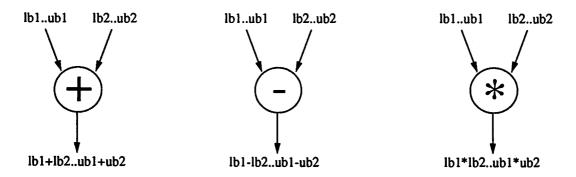

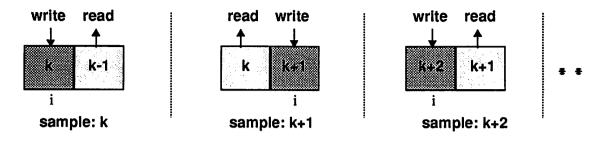

a model of computation is included. Furthermore, in constructing the flow graphs, subtle semantic inconsistencies between parts of the flow graph can be inadvertently created such as nodes with different rate inputs for example. In [Lee89b], Lee shows how these inconsistencies can lead to deadlocks and unbounded memory requirements. In this thesis, we are primarily interested in a special case of data flow, called synchronous data flow (SDF)[Lee87b]. In synchronous data flow, the number of data samples produced and consumed by every node on each firing is known at compile time. For signal processing, most applications fall into this category. Knowing the data rates permits the scheduling of synchronous data flow graphs onto multiprocessors to occur at compile time, eliminating the run-time scheduling overhead. SDF also allows inconsistencies to be found at compile time[Lee89b].

Many block diagram based DSP design systems for uniprocessors have been developed. These include Blosim[Mes84], BOSS[Sha87], and Gospl[Cov87]. All of these systems contain a library of common DSP blocks such as filters, FFT, equalizers, decimators, etc. as well as arithmetic blocks such as adders, magnitude, log, etc. Associated with each block are its simulation code and real-time code. The simulation code is usually implemented in a high level language with emphasis on portability and user interface, whereas real-time code is more concerned with exploiting hardware, efficiency and throughput. Program construction is done by concatenating the code associated with each block. Due to the explicit concurrency exposed in flow graph descriptions, the extension to multiprocessor implementation was inevitable. In the next section, we concentrate on design systems for multiprocessor digital signal processing.

## 2. 3. 3 Multiprocessor Design Environments for DSP

In this section, we discuss some multiprocessor design environments for DSP users. By design environment, we mean a software system which aid the user in

developing real-time DSP applications, from algorithmic design and simulation to implementation on real-time hardware.

Most multiprocessor DSP design environments currently available are block-diagram based. Examples of these systems include the Gabriel system from UC Berkeley[Lee89c], the Block Diagram Compiler (BDC) from Lincoln Labs[Zis87], the ZC compiler from Carnegie Mellon[Pri91], the cyclo-static scheduler from Georgia Institute of Technology[Sch85], and the Signal Processing WorkSystem-MultiProx (SPW-MP) system from Comdisco Systems, Inc. The block diagram construction processor is similar to uniprocessor design systems. After the block-diagram is created, the application is scheduled onto the target multiprocessor using a multiprocessor scheduling algorithm. Once a schedule is found, code is generated for each processor based on the processor assignments. Extra code is inserted to perform interprocessor communication and synchronization. Each program can then be downloaded to its corresponding processor to be executed.

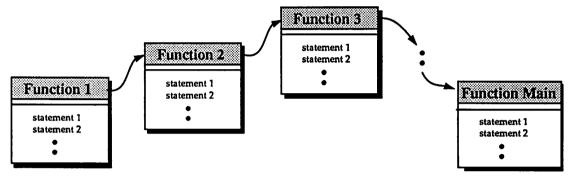

There are a few multiprocessor DSP design environments, including McDAS, which allow users to specify their descriptions using a DSP applicative language. Textual descriptions are not as illustrative as a graphical interface, but allows for more flexibility and cleaner specification of hierarchical structures such as iterations, recursion, etc. They also prohibit inconsistencies through well-defined syntax. These systems will have to initially translate the textual program into a flow graph description to expose concurrency. After the scheduling is done, code is generated using standard compiler's code generation techniques. In the past, the code synthesized from block-diagram systems were considered superior to these compiler generated code due to their hand-optimized libraries. With the recent advances in DSP compilers technology however, the advantage is rapidly diminishing [Tex92][Gen89]. Furthermore, library blocks with pre-defined code cannot be split into smaller tasks, and must be considered by the scheduler as atomic entities. This prevents the scheduler from exploiting

concurrency inside these blocks, restricting the smallest exploitable granularity level to the size of the largest block. In flow graphs built from textual descriptions however, there is no such artificial granularity boundary. The scheduler is free to exploit whatever granularity level it desires. Finally, many block diagram systems describe their library blocks with sequential code such as C or Fortran. This leads to a discrepancy between the data flow semantical model at the top level and the control flow semantical model of the blocks. While it is possible to define an interface semantic policy, it is implementation dependent and not portable. A completely textual description ensures the same semantical model at all levels of hierarchy.

The major difference among all of these systems, whether graphical or textual, lie in the multiprocessor scheduling strategy. In the next section, we review the current approaches.

## 2.4 MULTIPROCESSOR SCHEDULING

Multiprocessor scheduling consists of assigning tasks to processors, specifying the order in which the tasks are executed on each processor, and specifying the time at which they begin execution. There is a myriad of scheduling algorithms, with all different kinds of assumptions and approaches. The basic problem can be stated as follows. Consider a set of P processors, and a directed graph G = (N, E).  $N = \{n_1, n_2, ..., n_k\}$  are the nodes of G, and  $E = \{e_1, e_2, ..., e_m\}$  are the edges of G. The nodes represent computational tasks, and the edges define a relation on these tasks.  $n_i \rightarrow n_j$  implies there is an arc from  $n_i$  to  $n_j$ , and that the task  $n_i$  must finish before  $n_j$  can begin. Associated with each task  $n_i$  is a execution time, or node weight  $w_i$ . Beyond this problem definition, different assumptions are made and different goals are pursued, leading to a number of different classification of scheduling techniques.

#### 2. 4. 1 Classification

We discuss here the numerous approaches to classifying multiprocessor scheduling techniques. This is not meant to be exhaustive, but is meant to provide a better appreciation of the different scheduling applications.

#### 2. 4. 1. 1 Preemptive vs. Non-preemptive

In non-preemptive schedulers, once a processor is allocated to a task, it executes the task to completion. Preemptive schedulers allow a processor to halt execution of a task to begin processing a new task. The interrupted task is continued at a later time, either by the original processor or a different one. Preemption requires runtime task switching but may lead to better load balancing. Non-preemption has no runtime overhead, but performance can be affected by the task size.

#### 2. 4. 1. 2 Dynamic vs. Static

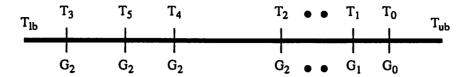

A scheduling taxonomy was introduced by Lee[Lee89d] to classify schedulers according to whether three components of the scheduling task, being processor assignment, order assignment, and time assignment, are to be performed at run-time or at compile time. Figure 2.8 shows the properties of the four classes. A Fully dynamic

|                   | Node-Assignment | Node-Ordering | Node-Timing  |

|-------------------|-----------------|---------------|--------------|

| fully dynamic     | run-time        | run-time      | run-time     |

| static-assignment | compile-time    | run-time      | run-time     |

| self-timed        | compile-time    | compile-time  | run-time     |

| fully static      | compile-time    | compile-time  | compile-time |

FIGURE 2.8: Scheduling taxonomy by Lee.

scheduler performs all operations at run-time[Bok81]. When all inputs to a node are available, the node is assigned to an idle processor, which executes it. A static assignment scheduler determines which node is assigned which processor at compiletime, usually base on interprocessor communication costs[Sto77][Bok81]. The exact order and timing is determined at run-time depending on which input data to which node is available. A fully static scheduler determines everything at compile-time, so there is no run-time scheduling and synchronization overhead. However, in order to determine the exact time to execute nodes, the exact execution time of each node must be known. Since this is rarely possible in a real life environment, we can decide the order of the node execution of each processor at compile time, and let the processor execute the nodes when possible. This is the approach of a self-timed scheduler. Selftimed schedulers allow the execution time of nodes to be non-exact and uses synchronization to ensure correct execution. Lee concluded that for signal processing, self-timed scheduling is the most attractive, although any fully static scheduling algorithm can be converted to a self-timed algorithm if synchronization costs are addressed.

## 2. 4. 1. 3 Single-execution vs. Iterated-execution

Most applications outside of signal processing assume that the application is to be executed once on some input set. For these, only spatial concurrency is available, and the standard scheduling objective is to minimize the execution time of the application. In signal processing, applications are executed indefinitely on a stream of input samples. Hence, both spatial and temporal concurrency are available. If we repeat the minimum execution time schedule for each sample, we obtain a minimum latency implementation. More often however, the goal is to maximize the system throughput, with latency being a secondary objective. The approach above does not exploit the available temporal concurrency to increase throughput through pipelining. With both

concurrency, we can employ both pipelining and parallel processing to achieve the throughput speedup.

#### 2. 4. 1. 4 Variable Granularity vs. Fixed Granularity

Most scheduling algorithms to date assume the granularity of the given flow graph is fixed. They do not know about and therefore will not exploit any potential concurrency that may exist inside the nodes in the flow graph. In the case where the granularity is too coarse for the given number of processors, there will not be enough concurrency to fill all the processors, resulting in poor processor utilization. Schedulers which can accept hierarchical flow graphs and can traverse different granularity levels do not run into this difficulty.

#### 2. 4. 1. 5 Others

There are still many other criteria which separate scheduling algorithms from one another. One criteria is whether or not communication overhead is taken into account. Most earlier scheduling algorithms do not consider communication overhead, yielding results which are often unusable. With the types of communication intensive applications that can exist, it is no longer feasible to ignore this important criteria. Another classification is whether the scheduler assumes a finite resource limit or an infinite one. Some scheduling techniques use as many processors as necessary to achieve their goals. Others have no consideration for memory usage limits. Even if these techniques are good, they would need to be modified to be practical. Finally, other key points of a scheduling algorithm is whether it can accept different types of processors in the system, whether it can efficiently handle special types of tasks such as data-dependent loops and conditionals, whether it can configure the architecture topology as it schedules, and so on.

In our application of real-time signal processing, the performance constraint forbids any excessive run-time overhead. As a result, preemptive and dynamic

scheduling must be ruled out. The scheduling algorithms that we will discuss in the remainder of the section are all non-preemptive and static (fully static or self-timed) algorithms. In order to perform the scheduling at compile-time, we must model the events which will take place at run-time, and make scheduling decisions based on them. As a result, static algorithms are much more complex than their dynamic counterparts. A measure of algorithm complexity is briefly introduced in the next section.

## 2. 4. 2 Complexity Analysis

A key issue in the study of multiprocessor scheduling is the amount of computation time needed to find a suitable schedule. In computer science, an algorithm is said to be *efficient* if it requires an amount of time that is bounded by a polynomial expression of its input size. An *inefficient* algorithm is one which essentially requires an enumeration of all possible solutions before the best solution can be selected. Solutions of this type can be characterized by algorithms whose running times are exponential in the input size. These algorithms belong in a large family of seemingly intractable problems called *NP-complete* problems. Discussions on NP-completeness is discussed in more details in [Coo71][Kar72][Gar79]. For our purpose, it is only necessary to know that most of the problems of interest in multiprocessor scheduling are NP-complete [Len78][Ull75]. Since it is infeasible to enumerate all possible schedules in a reasonable time on present day computers, it is necessary to use heuristics to find a close to optimal solution to our scheduling problem. All techniques discussed below use some form of heuristic to arrive at their solutions.

## 2. 4. 3 Basic Multiprocessor Scheduling

Multiprocessor scheduling has its roots in management science and operations research studies, which are mainly concerned with assigning jobs to resources in the most efficient manner. If jobs are equated to programs and resources are equated to

processors, then the extension is apparent. A good overview of multiprocessor scheduling can be found in [Cof76] and [Gon77].

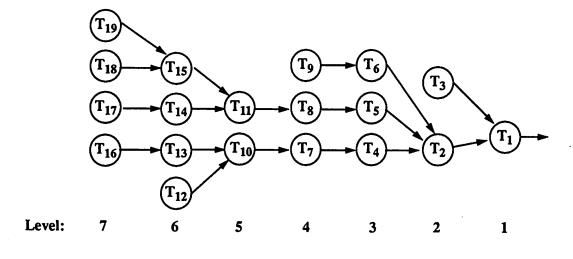

Perhaps the most frequently cited reference in multiprocessor scheduling is the work by T.S. Hu [Hu61] which presents a solution to the basic scheduling problem. Hu assumes all nodes have equal execution times, the precedence relationship is in form of a tree, and no communication overhead. The Hu algorithm labels each node with a *level* equal to the longest distance from the node to completion. The algorithm then schedules nodes with the highest levels first. An illustration of Hu's algorithm is shown in Figure 2.9. When trying to minimize execution time with the assumptions above, this

| P <sub>2</sub> | T <sub>19</sub> | T <sub>16</sub> | T <sub>15</sub> | T <sub>11</sub> | Т8             | T <sub>5</sub> | T <sub>2</sub> | Т1 |

|----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----|

| P <sub>1</sub> | T <sub>18</sub> | T <sub>14</sub> | T <sub>13</sub> | T <sub>10</sub> | T <sub>7</sub> | T <sub>4</sub> |                |    |

| Po             | T <sub>17</sub> | T <sub>12</sub> | T <sub>9</sub>  | T <sub>6</sub>  | T <sub>3</sub> |                |                |    |

| 0              | )               | 1               | 2               | 3               | 4              | 5              | 6              | 7  |

FIGURE 2.9: Hu's algorithm showing optimal schedule on 3 processors

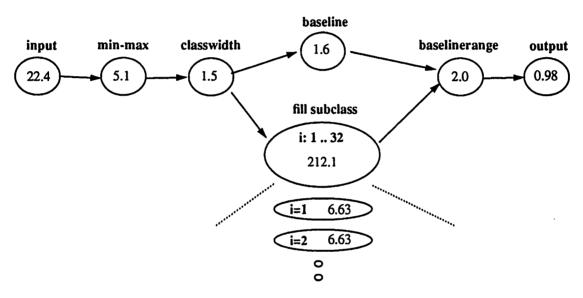

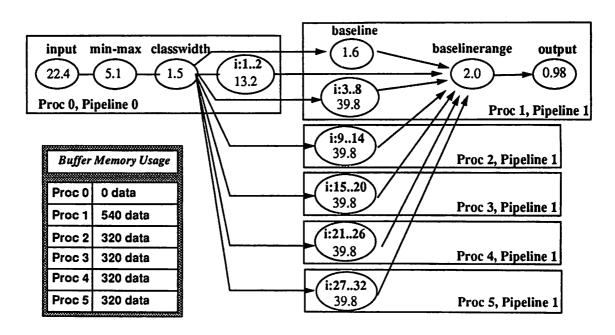

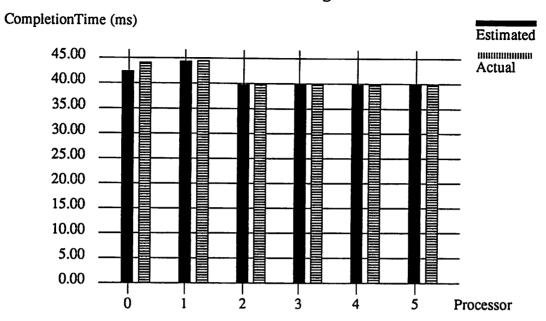

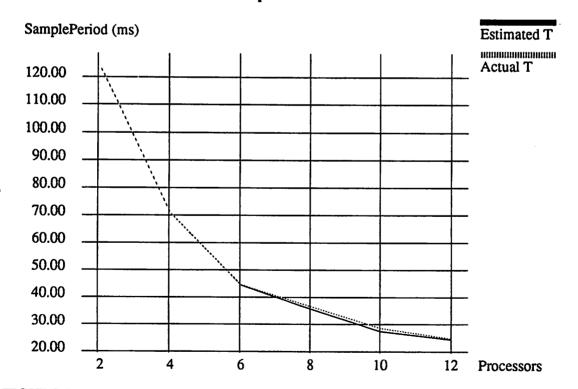

algorithm is actually optimal. However, relaxing the assumptions to arbitrary execution times and general precedence, the problem becomes NP-complete, and algorithms using the same technique above as heuristics became known as *critical path methods* or