## Copyright © 1992, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# SYNTHESIS OF SEQUENTIAL CIRCUITS FOR VLSI DESIGN

by

Pranav N. Ashar

Memorandum No. UCB/ERL M92/62

5 June 1992

# SYNTHESIS OF SEQUENTIAL CIRCUITS FOR VLSI DESIGN

by

Pranav N. Ashar

Memorandum No. UCB/ERL M92/62 5 May 1992

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### Synthesis of Sequential Circuits for VLSI Design

Pranav N. Ashar

University of California Berkeley, California Department of Electrical Engineering and Computer Science

#### Abstract

Synthesis of VLSI circuits involves transforming a specification of circuit behavior into a mask-level layout which can be fabricated using VLSI manufacturing processes. Optimization strategies are vital in VLSI synthesis in order to meet desired specifications. The first-order optimization criteria in this process are typically all or a desired subset of area optimality, speed and testability. There are several steps in the synthesis of mask-level layout descriptions from specifications of circuit behavior. The steps involved in the transformation from the RT-level to a gate-level circuit are collectively known as logic synthesis. VLSI circuits are sequential circuits, i.e. they contain memory or storage elements, namely flip-flops or latches, as well as combinational (or switching) circuitry. Considerable progress has been made in the understanding of combinational logic optimization in the recent past. Consequently a large number of university and industrial CAD programs are now available for the optimal logic synthesis of combinational circuits. The understanding of sequential circuit optimization, on the other hand, is considerably less mature. The presence of internal state adds considerably to the complexity of the optimization problem. Synthesis tools are required to automatically encode the symbolic internal states. This encoding determines the complexity and the structure of the sequential circuit realizing the state machine, and therefore has a profound effect on its area, testability and performance. Techniques for the optimal synthesis of sequential circuits are presented in this thesis. Algorithms are presented for finite-state-machine decomposition using information available at the symbolic state graph level, for symbolic state graph extraction from logic-level descriptions, for the synthesis of sequential circuits for enhanced testability under the single and multiple stuck-at fault models, and for sequential logic verification. These algorithms have been implemented in a sequential synthesis program called FLAMES.

rof. Arthur Richard Newton

Thesis Committee Chairman

#### Acknowledgements

To Richard Newton I owe gratitude for having the confidence in me to take me on as his graduate student, and for standing by me through the good times and the bad. At various times, and on occasion all together, he has been my professional, philosophical and emotional guide.

Much of my work was inspired by ideas that originated with Srinivas Devadas. He has been both, a close research associate and an even closer personal friend. I have learnt a great deal from him. But, most of all, it has been his example of single minded dedication to work that I have tried to emulate. It has been a pleasure working with him.

The example set by Professors Robert Brayton, Donald Pederson and Alberto Sangiovanni-Vincentelli in the CAD group has been inspiring. I have benefited enormously by virtue of my association with them. Professors Robert Brayton, Jan Rabaey and Don Glaser served on my qualifying exam committee, and Professors Robert Brayton and Don Glaser are co-signees on my dissertation. I am grateful to them for sparing the time from their busy schedules.

Kurt Keutzer, Tony Ma, Richard Rudell and Albert Wang, now all at Synopsys, but at some time or the other associated with the CAD group at Berkeley, have always been forthcoming with useful advice, help and ideas. I also have had the opportunity to interact with Tim Cheng at AT&T, Gary Hachtel and Fabio Somenzi at the University of Colorado, Boulder, Jim Kukula visiting MIT from IBM, Wayne Wolfe at Princeton University, and Ray Wei at Cadence.

My research was supported in part by financial assistance from the Defense Advanced Research Projects Agency under contracts N00014-87-K-0825 and N00039-87-C-0182, from AT&T Bell Laboratories and from Semiconductor Research Corporation, and by equipment grants from Digital Equipment Corporation. Their support is gratefully acknowledged.

It is difficult to imagine a CAD group without Kia Cooper, Elise Mills and Flora Oviedo. Their unquestioning help ensured that the graduate students could concentrate on research. Brad Krebs, Mike Kiernan and Kurt Pires were instrumental in maintaining the computing environment for the CAD group. I would like to thank them, in particular, for taking the time to attend to my individual needs. Over the years, Brad has received considerable help from the students in the group who have taken time off their own research

for the benefit of the community. Wendell Baker has always been magnanimous with his time. The environment for software development created by David Harrison, Peter Moore, Tom Quarles, Rick Rudell and Rick Spicklemier among others, tailored to meet the specific needs of our group, was instrumental in making my programming tasks considerably simpler. Also crucial to me were the TeX and Postscript based document preparation tools that were maintained by Rick Spicklemier et al. And, a huge thanks to Richard Newton for introducing all of us to Macintoshes, and to Brian Okrafka for handling the installation and maintenance of software on them.

The four years at Berkeley would have been routine without the company of the so many interesting, smart and diverse people that I had the opportunity to form close personal and professional relationships with. I am grateful to them for giving me this opportunity, and I hope, possibly in vain, that I contributed as much to them as they did to me. Given the nature of graduate school, it is common to interact with people at various stages of completion of their degrees. Over four years therefore, one can make an extremely large number of friends. At the risk of missing out some names and making this paragraph read like a roster of names, I would like to acknowledge the friendship, support and advice I received over the years from Abhijit, Alan, Alex Gollu, Alex Saldanha, Albert, Andrea, Arvind, Bill, Brian Lee, Brian Okrafka, Cho, Chuck, Cormac, Dev, Ellen, Gary, Greg Whitcomb, Hamid, Herve', Jaijeet, Karti, Ken, Luciano, Mark, Mitch, Narendra, Rajiv Ramaswami, Rajeev Murgai, Ramin, Rick McGeer, Rick Spicklemier, Rick Rudell, Sharad, Srini, Theo, Tim Kam, Tiziano, Tom Quarles, Tom Shiple, Tony, Umakanta, Vijay, Wayne, Wendell and Yoshi. Relationships with some were very special to me. I would like to say to these people that I am indebted to them for life, and that the memories of the times spent with them at Berkeley will always be with me, cherished forever and relived again and again.

This dissertation is dedicated to my Parents, Rajni and Navin.

## Contents

| A  | cknov  | vledge  | ments                                           | i   |

|----|--------|---------|-------------------------------------------------|-----|

| Τε | able c | of Con  | tents                                           | iii |

| Li | st of  | Figure  | es                                              | vii |

| Li | st of  | Tables  | 3                                               | ix  |

| 1  | Intr   | oducti  | on                                              | 1   |

|    | 1.1    | Comp    | uter-Aided VLSI Design                          | 1   |

|    | 1.2    |         | ynthesis Pipeline                               | 2   |

|    | 1.3    | Seque   | ntial Logic Synthesis                           | 3   |

|    | 1.4    |         | Work in Sequential Logic Synthesis              | 5   |

|    | 1.5    | Recent  | Developments                                    | 6   |

|    |        | 1.5.1   | State Encoding                                  | 6   |

|    |        | 1.5.2   | Finite State Machine Decomposition              | 9   |

|    |        | 1.5.3   | Sequential Resynthesis at the Logic-Level       | 9   |

|    |        | 1.5.4   | FSM Verification                                | 10  |

|    |        | 1.5.5   | Sequential Synthesis for Testability            | 10  |

|    | 1.6    |         | iew of Dissertation                             | 12  |

| 2  | Basi   | c Defi  | nitions and Concepts                            | 14  |

|    | 2.1    | Definit | tion of Terminology                             | 14  |

|    |        | 2.1.1   | Two-Valued Logic                                | 14  |

|    |        | 2.1.2   | Multi-Valued Logic                              | 15  |

|    |        | 2.1.3   | Finite Automata                                 | 16  |

|    |        | 2.1.4   | Testing                                         | 17  |

|    | 2.2    | A Rev   | iew of the Basic Concepts in State Encoding     | 18  |

|    |        | 2.2.1   | Input Encoding Targeting Two-Level Logic        | 19  |

|    |        | 2.2.2   | Output Encoding Targeting Two-Level Logic       | 21  |

|    |        | 2.2.3   | Input-Output Encoding Targeting Two-Level Logic |     |

CONTENTS

| 3 Algorithms for FSM Decomposition |     |                                                                      |                |  |  |  |  |  |  |

|------------------------------------|-----|----------------------------------------------------------------------|----------------|--|--|--|--|--|--|

|                                    | 3.1 | Introduction                                                         | 28             |  |  |  |  |  |  |

|                                    | 3.2 | Basic Definitions                                                    | 30             |  |  |  |  |  |  |

|                                    | 3.3 | Exact Procedure for Two-Way General Decomposition                    | 32             |  |  |  |  |  |  |

|                                    |     | 3.3.1 The Cost Function                                              | 32             |  |  |  |  |  |  |

|                                    |     | 3.3.2 Decomposition, Factorization and Partitioning                  | 33             |  |  |  |  |  |  |

|                                    |     | 3.3.3 Generalized Prime Implicants, Prime Generation and Constrained | 00             |  |  |  |  |  |  |

|                                    |     | Covering                                                             | 37             |  |  |  |  |  |  |

|                                    |     | 3.3.4 Correctness of the Exact Algorithm                             | 41             |  |  |  |  |  |  |

|                                    |     | 3.3.5 Algorithm for Checking Encodability                            | 43             |  |  |  |  |  |  |

|                                    | 3.4 | Arbitrary Topologies                                                 | 48             |  |  |  |  |  |  |

|                                    | 3.4 |                                                                      |                |  |  |  |  |  |  |

|                                    |     |                                                                      | 49             |  |  |  |  |  |  |

|                                    |     | 3.4.2 Parallel Decompositions                                        | 52             |  |  |  |  |  |  |

|                                    |     | 3.4.3 Arbitrary Decompositions                                       | 54             |  |  |  |  |  |  |

|                                    |     | 3.4.4 Exactness of the Decomposition Procedure                       | 54             |  |  |  |  |  |  |

|                                    | 3.5 | Heuristic Procedure for Two-Way General Decomposition                | 55             |  |  |  |  |  |  |

|                                    |     | 3.5.1 Overview                                                       | 55             |  |  |  |  |  |  |

|                                    |     | 3.5.2 Minimization of Covers and Removal of Constraint Violations    | 56             |  |  |  |  |  |  |

|                                    |     | 3.5.3 Symbolic-expand                                                | 56             |  |  |  |  |  |  |

|                                    |     | 3.5.4 Symbolic-reduce                                                | <b>5</b> 8     |  |  |  |  |  |  |

|                                    | 3.6 | Relation to State Assignment                                         | 59             |  |  |  |  |  |  |

|                                    | 3.7 | Results                                                              |                |  |  |  |  |  |  |

|                                    | 3.8 | Conclusions                                                          | 64             |  |  |  |  |  |  |

| 4                                  | Syn | thesis from Logic-Level Descriptions                                 | 66             |  |  |  |  |  |  |

|                                    | 4.1 | Introduction                                                         | 66             |  |  |  |  |  |  |

|                                    | 4.2 | Implicit STGs                                                        | 68             |  |  |  |  |  |  |

|                                    |     | 4.2.1 Implicit State-Enumeration                                     | 68             |  |  |  |  |  |  |

|                                    |     | 4.2.2 Implicit State-Traversal                                       | 71             |  |  |  |  |  |  |

|                                    | 4.3 | Optimization Strategies                                              | 72             |  |  |  |  |  |  |

|                                    |     | 4.3.1 Synthesis Results Using Implicit State-Enumeration             | 73             |  |  |  |  |  |  |

|                                    | 4.4 | Conclusions                                                          | 75             |  |  |  |  |  |  |

| _                                  | _   |                                                                      |                |  |  |  |  |  |  |

| 5                                  |     | edundant Interacting Sequential Circuits                             | 77             |  |  |  |  |  |  |

|                                    | 5.1 | Introduction                                                         | 77             |  |  |  |  |  |  |

|                                    |     | 5.1.1 Organization of the Chapter                                    | 78             |  |  |  |  |  |  |

|                                    | 5.2 | A Review of Redundancies in Single Finite-State Machines             | 79             |  |  |  |  |  |  |

|                                    |     | 5.2.1 Eliminating Isomorph-SRFs                                      | 81             |  |  |  |  |  |  |

|                                    |     | 5.2.2 Eliminating Invalid-SRFs                                       | 81             |  |  |  |  |  |  |

|                                    |     | 5.2.3 Eliminating Equivalent-SRFs                                    | 82             |  |  |  |  |  |  |

|                                    | 5.3 | Controllability and Observability Based Synthesis                    | 84             |  |  |  |  |  |  |

|                                    |     | 5.3.1 Redundancies in a Cascade                                      | 84             |  |  |  |  |  |  |

|                                    |     | 5.3.2 Exploiting Don't-Care Inputs for the Driven Machine            | 86             |  |  |  |  |  |  |

|                                    |     | 5.3.3 Exploiting Don't-Care Outputs for the Driving Machine          | 92             |  |  |  |  |  |  |

|                                    |     | 5.3.4 State Minimization Under Don't-Care Sets                       | Q <sub>4</sub> |  |  |  |  |  |  |

CONTENTS

|   |     | 5.3.5 Boolean Relations                                                   |

|---|-----|---------------------------------------------------------------------------|

|   |     | 5.3.6 Associating Redundancies and Don't-Care Sets 95                     |

|   |     | 5.3.7 A Synthesis Procedure for Irredundant Cascaded Machines 98          |

|   | 5.4 | Generalization to Multiple Interacting Finite-State Machines 104          |

|   |     | 5.4.1 Generalization of Observability and Controllability Don't-Cares 104 |

|   | 5.5 | Invalidity and Conditional Compatibility Based Synthesis 105              |

|   |     | 5.5.1 Exploiting Compatibility Between States                             |

|   |     | 5.5.2 Exploiting Invalidity of States and Edges 109                       |

|   |     | 5.5.3 Preventing Isomorphism                                              |

|   |     | 5.5.4 Searching for Unreachability and Compatibility                      |

|   |     | 5.5.5 The Optimization Procedure                                          |

|   |     | 5.5.6 Completeness of the Algorithm                                       |

|   | 5.6 | Results                                                                   |

|   | 5.7 | Conclusions                                                               |

|   |     |                                                                           |

| 6 |     | thesis for Multiple-Fault Testability 120                                 |

|   | 6.1 | Introduction                                                              |

|   | 6.2 | Synthesis Procedures for Nonscan Single-Fault Testability                 |

|   | 6.3 | Multiple-Faults in Combinational Circuits                                 |

|   | 6.4 | Multiple-Faults in Sequential Circuits                                    |

|   | 6.5 | Fully Multiple-Fault-Testable Sequential Circuits                         |

|   | 6.6 | Highly Multiple-Fault-Testable Sequential Circuits                        |

|   | 6.7 | Conclusions                                                               |

| 7 | Log | ic Verification Using General BDDs 132                                    |

|   | 7.1 | Introduction                                                              |

|   | 7.2 | Basic Definitions                                                         |

|   |     | 7.2.1 Binary Decision Diagrams                                            |

|   |     | 7.2.2 Binary Decision Diagram Operations                                  |

|   | 7.3 | General BDDs                                                              |

|   | 7.4 | Satisfiability/Equivalence Checking Via Input Smoothing                   |

|   |     | 7.4.1 Equivalence Checking                                                |

|   | 7.5 | Input Smoothing in General Binary Decision Diagrams                       |

|   |     | 7.5.1 A Branching Strategy for Smoothing Replicated Inputs 139            |

|   |     | 7.5.2 Smoothing by Addition of Extra Variables                            |

|   |     | 7.5.3 Smoothing Inputs Using Circuit Transformations                      |

|   | 7.6 | Implicit State Space Traversal Using General BDDs 143                     |

|   |     | 7.6.1 The Transition Relation Method                                      |

|   |     | 7.6.2 Using General Binary Decision Diagrams                              |

|   |     | 7.6.3 Variant Methods                                                     |

|   | 7.7 | Replicating and Ordering Circuit Inputs                                   |

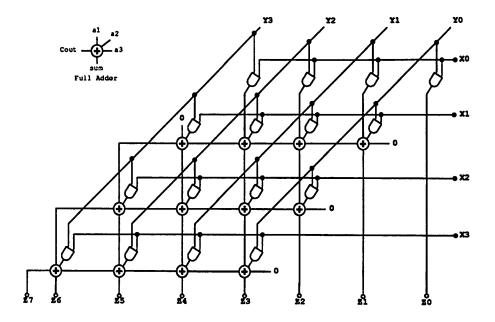

|   |     | 7.7.1 Replicating Inputs to a Multiplier                                  |

|   |     | 7.7.2 A General Algorithm to Replicate and Order Inputs 148               |

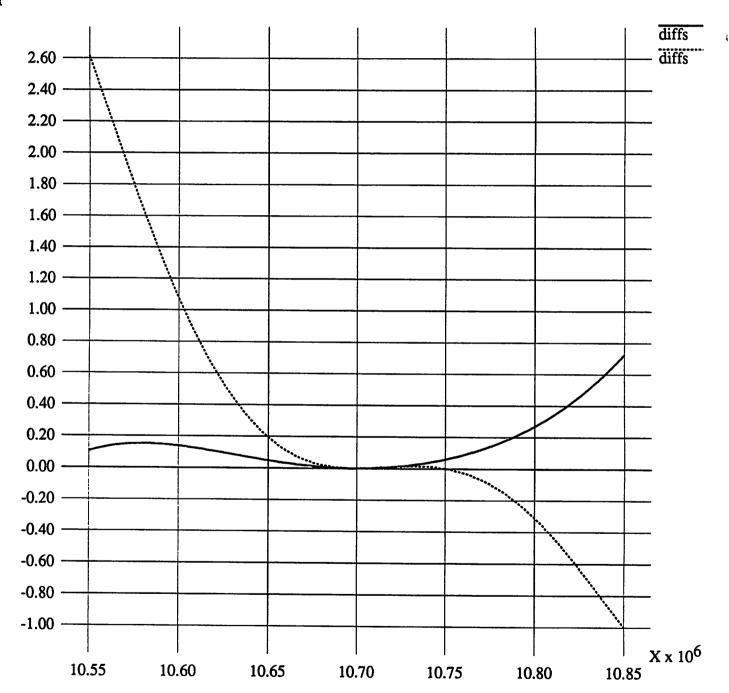

|   | 7.8 | Results                                                                   |

|   |     | 7.8.1 Combinational Circuit Verification                                  |

|   | 7.8.2 Sequential Circuit Traversal |

|---|------------------------------------|

|   | 7.9 Conclusions                    |

| 8 | Conclusions and Future Work        |

| A | FLAMES                             |

|   | A.1 Introduction                   |

|   | A.2 Organization of FLAMES         |

|   | A.3 A Synthesis Strategy in FLAMES |

# List of Figures

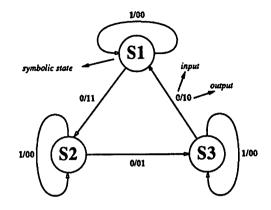

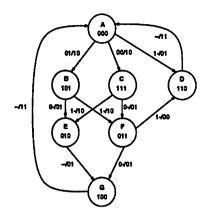

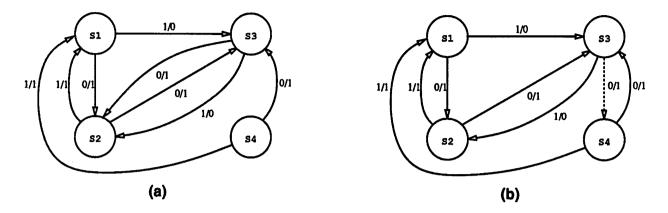

| 1.1  | An example of a State Transition Graph (STG)                        | 3  |

|------|---------------------------------------------------------------------|----|

| 2.1  | An example of a symbolic cover and its one-hot coded representation | 15 |

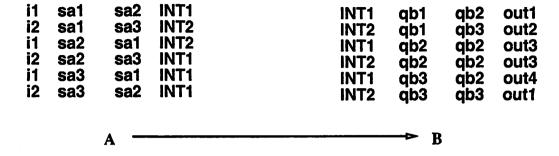

| 2.2  | A symbolic tabular representation of a finite-state machine         | 19 |

| 2.3  | Codes satisfying input constraints                                  | 19 |

| 2.4  | Two-level implementation of encoded finite-state machine            | 20 |

| 2.5  | Example of the effects of dominance relationships                   | 21 |

| 2.6  | Example of the effects of disjunctive relationships                 | 22 |

| 2.7  | Merging cubes to form larger cubes                                  | 23 |

| 3.1  | A STT representation of a finite-state machine                      | 31 |

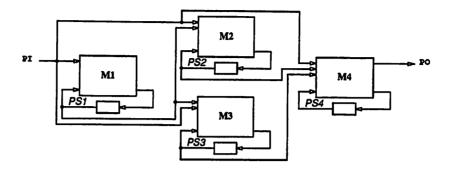

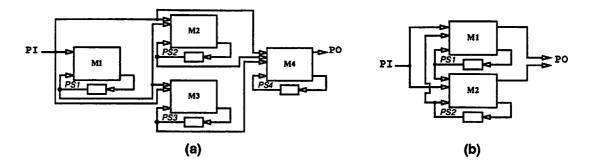

| 3.2  | General decomposition topology                                      | 32 |

| 3.3  | Examples of cube merging                                            | 38 |

| 3.4  | An example of an input constraint violation                         | 40 |

| 3.5  | Example of a general decomposition                                  | 43 |

| 3.6  | Encodability check graph for the decomposition in Figure 3.5        | 45 |

| 3.7  | Adding a new edge                                                   | 46 |

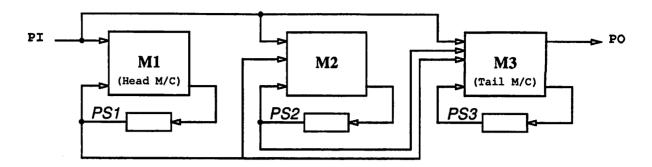

| 3.8  | Topology for three-way cascade decomposition                        | 48 |

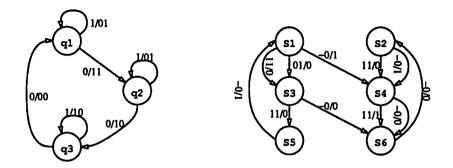

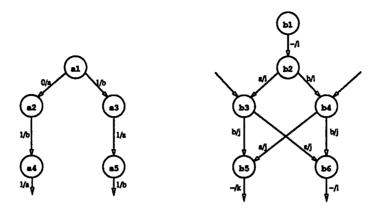

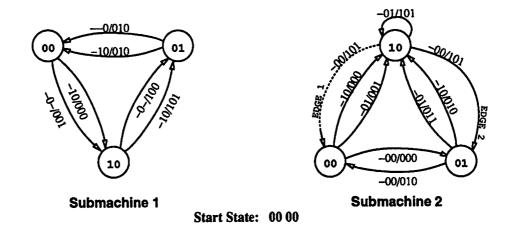

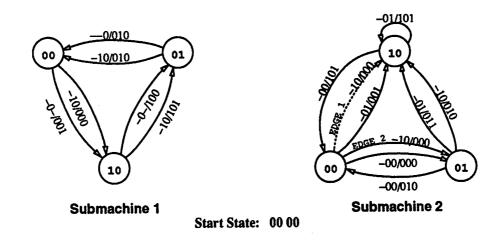

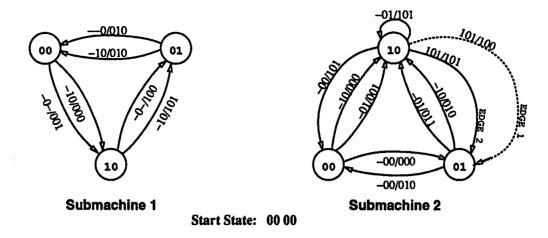

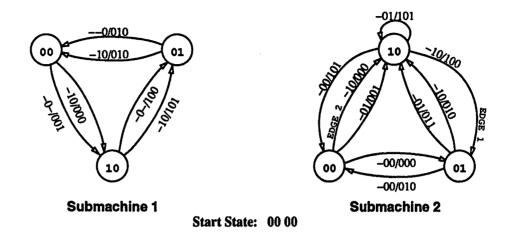

| 3.9  | An Example of a two-way cascade decomposition                       | 50 |

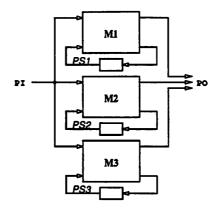

| 3.10 | Topology for three-way parallel decomposition                       | 51 |

| 3.11 | An example of a two-way parallel decomposition                      | 52 |

| 3.12 | An arbitrary decomposition topology                                 | 54 |

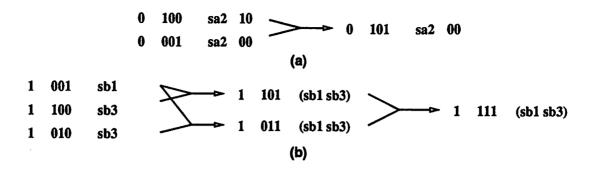

| 4.1  | Implicit state-enumeration procedure                                | 68 |

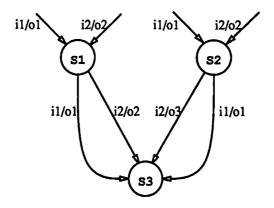

| 4.2  | An example STG                                                      | 70 |

| 4.3  | STG for first output of Figure 5.2                                  | 71 |

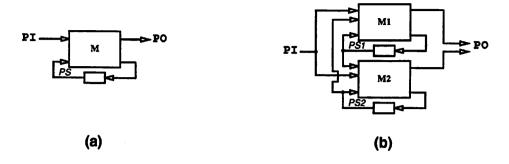

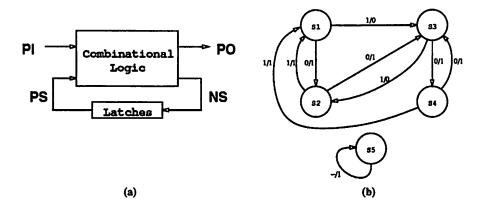

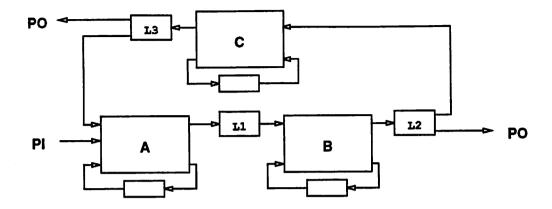

| 5.1  | A sequential circuit                                                | 79 |

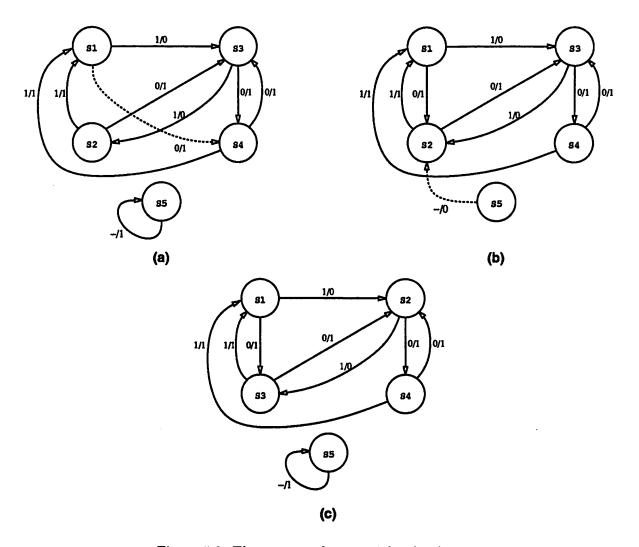

| 5.2  | Three types of sequential redundancies                              | 80 |

| 5.3  | An equivalent-SRF                                                   | 83 |

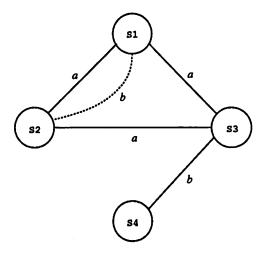

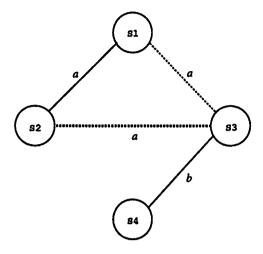

| 5.4  | Interacting finite-state machines                                   | 85 |

| 5.5  | Input don't-care sequences                                          | 87 |

| 5.6  | Conditional compatibility                                           | 91 |

| 5.7  | Output expansion                                                    | 92 |

| LIST OF FIGURES | viii |

|-----------------|------|

|-----------------|------|

| 5.8  | Output don't-care sequences                                        | 102 |

|------|--------------------------------------------------------------------|-----|

| 5.9  | FSMs communicating via their present states                        | 105 |

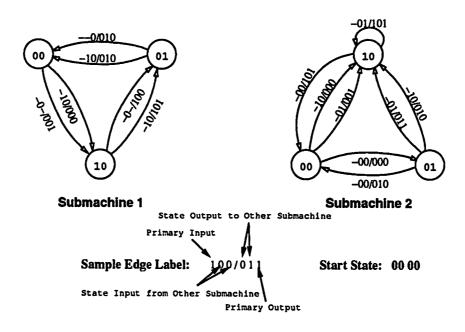

| 5.10 | The state graphs of two fault-free interacting FSMs                | 106 |

|      | A fault causing interchange of unconditionally compatible states   | 107 |

|      | A fault causing interchange of conditionally compatible States     | 107 |

|      | A fault causing corruption of only an unspecified edge             | 108 |

|      | State graph of a decomposed machine in which isomorphism can occur | 110 |

| 6.1  | A sequential circuit                                               | 122 |

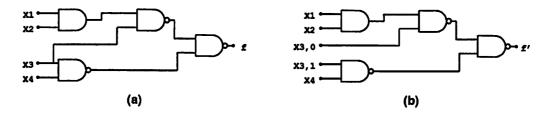

| 6.2  | A multiple fault in a two-level circuit                            | 124 |

| 7.1  | Relaxing the ordering constraint                                   | 136 |

| 7.2  | Multiple instances of a variable along a BDD path                  | 137 |

| 7.3  | Example of input replication                                       | 138 |

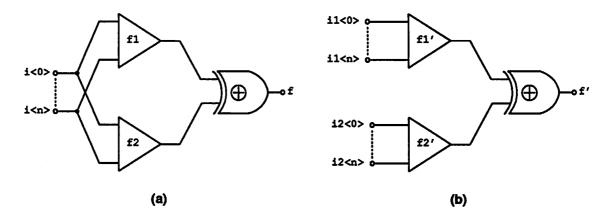

| 7.4  | Equivalence checking                                               | 139 |

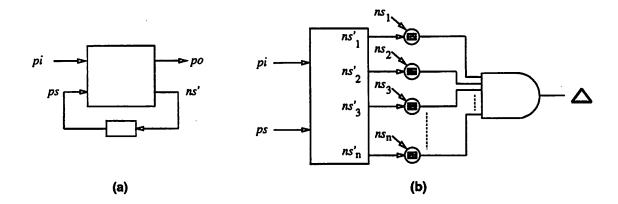

| 7.5  | A Sequential circuit and its transition relation                   | 143 |

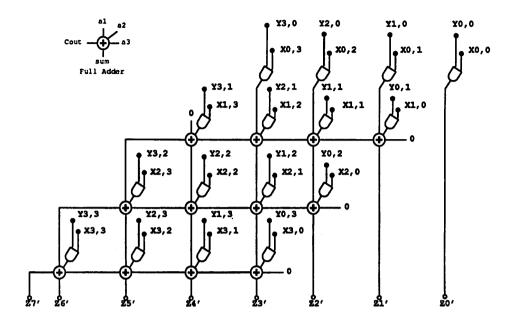

| 7.6  | A 4 × 4 multiplier                                                 | 147 |

| 7.7  | A $4 \times 4$ multiplier with inputs replicated                   | 148 |

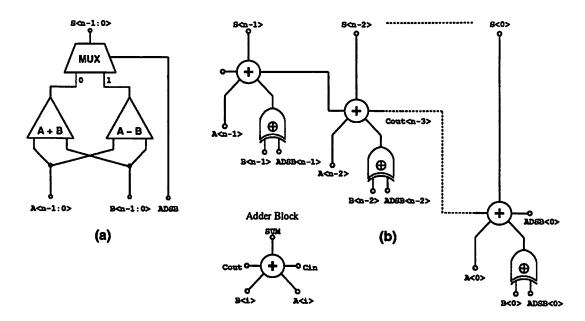

| 7.8  | Two versions of the adder-subtractor                               | 149 |

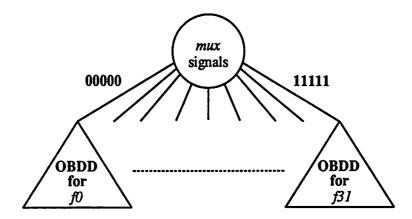

| 7.9  | An outline of the OBDD for ach32                                   | 152 |

## List of Tables

| 3.1 | Statistics of the encoded prototype machines                                | 60  |

|-----|-----------------------------------------------------------------------------|-----|

| 3.2 | Results of the heuristic two-way decomposition algorithm                    | 63  |

| 3.3 | Comparison of literal counts of multilevel-logic implementations            | 63  |

| 3.4 | Results of the exact decomposition algorithm                                | 63  |

| 4.1 | Results using implicit state enumeration                                    | 74  |

| 4.2 | Results obtained by synthesizing from ISTGs                                 | 75  |

| 5.1 | Full testability via optimal synthesis of interacting sequential machines   | 117 |

| 7.1 | Equivalence checking applied to combinational circuits not amenable to OBDD |     |

|     | representation                                                              | 150 |

| A.1 | Organization of FLAMES                                                      | 160 |

### Chapter 1

### Introduction

#### 1.1 Computer-Aided VLSI Design

Computer-Aided Design (CAD) of microelectronic circuits is concerned with the development of computer programs for the automated design and manufacture of integrated electronic systems, with emphasis today on Very Large Scale Integrated (VLSI) circuits. Automated VLSI design is referred to as VLSI synthesis. Synthesis of VLSI circuits involves transforming a specification of circuit behavior into a mask-level layout which can be fabricated using VLSI manufacturing processes, usually via a number of levels of representation between abstract behavior and mask-level layout. Optimization strategies, both manual and automatic, are vital in VLSI synthesis in order to meet required specifications. However, the optimization problems encountered in VLSI synthesis are typically NP-hard. Therefore, solutions to the optimization problems incorporate heuristic strategies, the development of which requires a thorough understanding of the problem at hand. Thus, automatic optimization-based VLSI synthesis has evolved into a rich and exciting area of research.

Direct application of synthesis in industry has been a significant driving force for research in CAD. Simple marketing principles dictate that, other factors being equal, a product available sooner would capture a larger share of the market and would remain in use longer. The desire to reduce the time to design and manufacture has led to the initial investment of considerable money and effort into the development of CAD tools capable of producing designs competitive with the best manual designs. Today, constantly shrinking geometries and increasingly reliable manufacturing processes have led to complex

systems being implemented on a single chip, making the use of CAD tools commonplace and mandatory. In its turn, the rapid automation of the VLSI design phase has allowed companies to keep pace with advances in other areas of VLSI like computer architecture and manufacturing, leading to a symbiotic relationship. As a consequence of this rapid development in VLSI technology, it is currently possible to produce application-specific integrated circuits (ASICs), microprocessors and other types of circuits that contain millions of transistors.

#### 1.2 The Synthesis Pipeline

There are several steps in the synthesis of mask-level layout descriptions from specifications of circuit behavior. Behavioral synthesis begins with a programming-language-like description of the functionality and converts it to a register-transfer-level (RT-level) description that implements the desired functionality. Among the issues involved at this stage are the temporal scheduling of operations and the allocation of hardware. For instance, decisions regarding the number of arithmetic units in a digital signal processor are made in this step.

The steps involved in the transformation from the RT-level to a gate-level circuit are collectively known as *logic synthesis*. Switching and automata theory form the cornerstones of logic synthesis. Even though obtaining *some* gate-level circuit from a RT-level description is straightforward, it is nontrivial to obtain a gate-level circuit that conforms to the desired specifications. The first-order optimization criteria in this process are typically all or a desired subset of area optimality, speed and testability.

Once the gate-level circuit has been obtained, mask-level layout is derived using layout synthesis (physical design) tools. The physical design styles of choice are typically gate array, sea-of-gates, standard-cell and programmable gate array. Programmable gate array is popular for extremely rapid prototyping of designs. Standard-cell is the design style of choice in mostly-custom designs like microprocessors, where only a portion of the chip is synthesized automatically. Gate array and sea-of-gates offer superior performance and integration density compared to programmable gate array and standard-cell design styles and are chosen when the complete chip is synthesized automatically.

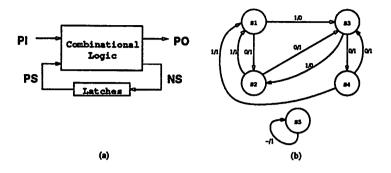

Figure 1.1: An example of a State Transition Graph (STG)

#### 1.3 Sequential Logic Synthesis

Almost all VLSI circuits are sequential circuits, i.e. they contain memory or storage elements in the form of flip-flops or latches as well as combinational (or switching) circuitry. An RT-level description can be implemented using either synchronous or asynchronous sequential logic. While asynchronous design has certain advantages, design automation for the reliable asynchronous implementation of complex functionality is still in its infancy. The synchronous design paradigm is followed throughout this thesis.

Considerable progress has been made in the understanding of combinational logic optimization in the recent past and consequently a large number of university and industrial CAD programs are now available for the optimal synthesis of combinational circuits [15, 12, 55, 29]. These optimization programs produce results competitive with manually-designed logic circuits. For a review of current combinational optimization techniques, the reader is referred to [17, 19].

The understanding of sequential circuit optimization, on the other hand, is considerably less mature. The presence of internal state adds considerably to the complexity of the optimization problem. While the primary inputs and outputs are typically binary vectors at the RT-level, internal states are represented in symbolic form.

Sequential circuits are most often modeled using Finite-State Machines (FSMs). A FSM is a mathematical model of a system (in our case, a switching circuit) with discrete inputs, discrete outputs and and a finite number of internal configurations or states. The state of a system completely summarizes the information concerning the past inputs to the system that is needed to determine its behavior on subsequent inputs. It is convenient

to visualize a FSM as a directed graph with nodes representing the states and the edges representing the transitions between states. Such a graph is known as a State Transition Graph (STG). An edge in the STG is labeled by the input causing the transition and the output asserted on the transition. A FSM can also be equivalently represented in tabular form by a State Transition Table (STT), each row of which corresponds to an edge in the STG. To deal with complexity, VLSI circuits are invariably specified in a hierarchical fashion. Large sequential circuits are typically modeled by smaller, interacting FSMs.

Synthesis tools are required to encode the internal symbolic states of FSMs as binary strings. This encoding determines the complexity and the structure of the sequential circuit which realizes the FSM, and therefore has a profound effect on its area, testability and performance. Stated differently, synthesis tools have the freedom of encoding states in such a way that the design constraints are satisfied. The notion of structure is generally associated with the manner in which a machine can be realized from an interconnection of smaller component machines as well as with the functional interdependencies of its state and output variables. It may be desirable, for example, to construct the circuit with the minimum amount of logic, or to build it from an interconnection of smaller circuits to obtain superior performance.

A second degree of freedom available to sequential synthesis tools is based on the fact that the STG corresponding to a given functionality is not unique; transformations to the STG like state splitting, state merging or STG partitioning enable moving from one STG to another without changing the functionality. These transformations guide the encoding of states in a particular direction, in many cases into directions that would not have been taken otherwise. Such transformations are sometimes necessary to achieve the desired objectives.

Research into such transformations is exactly what has motivated the work presented in this thesis. In particular, transformations that guide the synthesis of interconnected FSMs have been investigated. Topics that have been covered under this general guideline include FSM decomposition, state transition graph extraction, the use of don't-cares in interacting sequential circuits, and the synthesis of interacting sequential circuits for single and multiple fault testability.

#### 1.4 Early Work in Sequential Logic Synthesis

Work in sequential logic synthesis dates back to the late '40s and '50s when discrete off-the-shelf components (relays and vacuum tubes) were used. In the 1960's, small-scale integrated circuits(SSI) became popular and much of the work in that period was motivated by the need to reduce the number of latches in the circuit since that meant a reduction in the number of relatively expensive chips on the circuit board. Also, since combinational logic synthesis was still in its infancy, techniques for state encoding and FSM decomposition were unable to target the combinational logic complexity of the sequential circuit effectively.

The minimization of the number of states in completely specified FSMs was first investigated by Moore [88], Huffman [63, 64] and Mealy [84]. This work was later extended to the reduction of states in incompletely specified machines by Ginsburg [53] and Unger [89]. An interesting technique for deriving maximal compatibles in state reduction using Boolean algebra was reported in a short communication by Marcus [82].

The relationship between state encoding and the structure of the resulting sequential circuit was first investigated in terms of the algebraic theory of partitions by Hartmanis [58, 59] and later by Hartmanis and Stearns [102, 60]. Contributions to machine-structure theory were also made by Karp [65], Kohavi [68], Krohn and Rhodes [70], Yoeli [109, 110] and Zeiger [111]. The concept of state splitting to augment the possibilities of finding desirable decompositions and state assignments was developed, among others, by Hartmanis and Stearns [60], Zeiger [111] and Yoeli [109]. The book by Hennie [61] provides a lucid and intuitive description of the above contributions.

State encoding was treated from a different point of view by Armstrong [2] and Dolotta and McCluskey [43]. The procedure of Armstrong formulated the state encoding problem as one of assigning codes so that prederived adjacency relationships between states are satisfied in the Boolean domain. To a certain extent, the procedure of [2] inspired some state assignment algorithms developed in recent work (e.g. Devadas et al [36]) for targeting multilevel implementations.

#### 1.5 Recent Developments

#### 1.5.1 State Encoding

A number of significant new results have been obtained in the area of sequential logic synthesis in the last five years (e.g. [36, 86, 87, 96]). An important development in state encoding was the step from predictive to exact approaches for state encoding targeting two-level implementations. A fundamental result which made this possible was the establishment of a link between the size of a minimized symbolic tabular representation of a FSM and the maximum number of product terms required in a Programmable Logic Array (PLA) implementing the same FSM after encoding the states in the work by De Micheli et al [86]. The approach followed in [86] involved a two-step process. In the first step, the STT of the FSM is symbolically minimized using a two-level multiple-valued minimization program like ESPRESSO-MV [94]. This minimization step generates constraints that the state codes must satisfy if the PLA resulting from the encoding is to have as small or an equal number of product terms as the minimized STT. Obtaining a state encoding that satisfies the constraints forms the second step of the procedure. Since symbolic minimization by itself cannot account for the interactions in the next-state plane of the encoded FSM, the approach of [86] effectively approximated the state encoding problem as one of input encoding.

States appear both in the input and output planes of the PLA and therefore state encoding is actually an input-output encoding problem. The interactions between product terms in the next-state plane can occur either due to dominance or disjunctive relationships between state codes. If the code for state  $s_1$  dominates the code for state  $s_2$ , the input parts of the cubes asserting the next-state  $s_1$  can be used as don't-cares in order to optimize the cubes asserting the next-state  $s_2$ . Similarly, if the code for state  $s_1$  is the disjunction of the codes for states  $s_2$  and  $s_3$ , the input part of the cubes that assert the next-state  $s_1$  can be optimized using the input parts of the cubes asserting the next-states  $s_2$  and  $s_3$ .

Work by De Micheli [85] was the first to take advantage of interactions between product terms in the next-state plane. In particular, it attempted to maximize the cardinality reductions due to dominance relationships between state codes by reducing the problem to one of heuristically finding the order in which states should be encoded. Further understanding of interactions in the output plane led to the work of Devadas and Newton [41] in which a procedure was presented for encoding states to achieve the minimum product-term count. By means of this procedure, relationships between codes arising due to the

interactions in the input plane and due to both dominance and disjunctive relationships in the output plane can be handled simultaneously. The search for all possible relationships and their effects is carried out by modifying the classical Quine-McCluskey [90, 83] prime implicant generation and covering. The notion of Generalized Prime Implicants (GPIs) was introduced in [41] for that purpose. GPIs correspond to a weaker form of primality than conventional prime implicants in that for the same symbolic cover, the set of GPIs contains the set of conventional prime implicants and is much larger than it. The advantage of GPIs is that they allow interactions in the output plane to be handled formally. While the use of GPIs leads to an exact procedure, their use is only viable for small FSM examples.

State encoding targeting multilevel implementations is an even more difficult problem. The main reason for this is that combinational optimization of multilevel circuits is itself not an exact science. Even so, certain optimization strategies like common-factor extraction are fundamental to multilevel optimization and a number of predictive state encoding procedures have been proposed that maximize the gains due to these basic strategies. Devadas et al [36] proposed an algorithm for state encoding in which the likelihood of finding common subexpressions and common cubes in the logic prior to optimization is enhanced by minimizing the distance in the Boolean space between chosen states. A variation on this approach was followed in subsequent work by other researchers [74, 107]. However, in [74], the emphasis was on the general encoding problem, including both inputs, outputs and state variables, while the emphasis in [107] was on encoding for optimization by kernel-based combinational optimization tools. Recently, attempts have been made to extend the encoding paradigm followed for two-level circuits to multilevel circuits. In the work of Malik et al [71], techniques were proposed for optimizing multilevel circuits with multiple-valued input variables. As in the two-level case, these optimizations lead to constraints on possible binary encodings for the multiple-valued variables that must be satisfied if the effects of the optimizations are to be preserved after encoding.

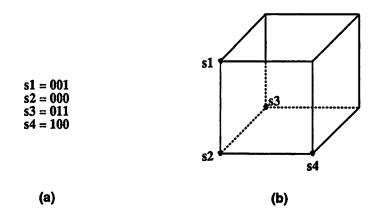

One of the important steps in the encoding of symbolic states in a FSM is the satisfaction of encoding constraints. In the most general case, these constraints consist of both input and output constraints. In the case of input constraints, one is given a constraint matrix, C, each column of which corresponds to a state and each row to a constraint. The goal is to find an encoding matrix E where each row in E corresponds to the binary code chosen for a state, such that the constraints implied by C are satisfied and the number of columns in E is minimum. Satisfying the input constraints entails obtaining state codes

such that for each row in C the states present in the row form a face in the Boolean n-space and the states absent from the row are excluded from that face. This problem is called the face-embedding problem. Output constraints, on the other hand, force bitwise dominance and disjunctive relationships between the state codes.

Finding a minimum-length encoding satisfying the constraints is an NP-hard problem [95]. De Micheli et al [86] provided a number of results for reducing C without violating the original set of constraints and proposed a row-based encoding algorithm. According to this algorithm, E is constructed row by row with the invariant that the constraints corresponding to the rows of C are not violated by the portion of E constructed thus far. Columns are added to E when necessary. This algorithm was found to be effective only for small examples. Column-based algorithms were proposed by De Micheli [85] and Devadas et al [42]. In a column-based algorithm, E is constructed one column (one bit) at a time. None of these algorithms guarantee a minimum-length encoding. The work by Villa et al [106] includes an algorithm for obtaining the minimum length encoding satisfying all input constraints. This work represents a refinement of the methods developed previously [85, 86].

An alternate approach to constraint satisfaction uses the notion of dichotomies. A dichotomy is defined as a disjoint two-block partition on a set, in our case the set of states. The notion of dichotomies was first introduced for hazard-free state encoding of asynchronous circuits by Tracey [105]. Dichotomies were revisited for constrained state encoding by Ciesielski et al [108]. The main result of that work was to show that the minimum number of bits required to encode a set of constraints is equal to the minimum number of prime dichotomies required to cover all the seed dichotomies. An implementation based on graph coloring was suggested for this approach. An alternate implementation of the dichotomies approach based on prime generation and classical unate covering [93] was done by Saldanha et al [95]. It was also shown in that work how output constraints could be handled using dichotomies. In this case, the generation of primes was carried out using the same approach as used by Marcus [82] for generating maximal compatibles in state minimization.

In other work on constraint satisfaction [41], it was shown that if the encoding length were known a priori, all constraints can be represented by Boolean equations. While this idea is attractive in theory, a naive representation of all constraints involved as Boolean equations can lead to an intractable satisfiability problem. Simulated annealing has also

been used successfully for constraint satisfaction [36, 74, 106].

#### 1.5.2 Finite State Machine Decomposition

FSM decomposition can be used to obtain partitioned sequential circuits with the desired interconnection topology. Sequential circuit partitioning can lead to improved performance, testability and ease of floor-planning. Decomposition at the STG-level allows a larger solution space to be searched for partitioning sequential circuits than techniques that operate at the logic level. However, the drawbacks of the above approaches which operate at the STG level is that it is difficult to accurately predict the effect of an operation at the symbolic level on the cost of the resulting logic.

In recent work on FSM decomposition, Devadas and Newton [40] recognized that many FSMs possess isomorphic subgraphs in their STGs. The implementation of multiple instances of such isomorphic subgraphs (called *factors* in [40]) as a single separate submachine distinct from the parent machine can lead to reduced area and improved performance. The authors also demonstrated that this decomposition approach leads to an encoding strategy that takes advantage of some interactions in the next-state plane.

#### 1.5.3 Sequential Resynthesis at the Logic-Level

The observation that significant gains could be accrued by optimizing certain sequential circuits at the logic-level was made by Leiserson et al [72] for systolic arrays. Systolic arrays are sequential circuits which are capable of operating at very high clock frequencies because they are designed as highly pipelined structures with very little logic between pipeline latches on any path in the network. This design methodology implies that the number of latches is usually very large. Given an initial design, the problem of retiming or relocating these latches so that the number of latches is minimized, with the circuit still satisfying the clock frequency requirement and with the functionality of the circuit remaining unchanged, was formulated as an integer programming problem in that work. The work of Malik et al [79] extended the ability to retime latches to a larger class of circuits. In that work, the general problem of state encoding was reduced to one of latch retiming. While this notion is certainly attractive in theory, it was found that most sequential circuits implementing control-type functions are not amenable to global optimization by latch retiming because of the tight feedback paths they possess. The reason that latch

retiming was successful for systolic arrays was that most of the latches are used as pipeline latches and very few of them are in unique feedback loops.

#### 1.5.4 FSM Verification

In order to validate the complex transformations involved in logic synthesis, it is important to be able to verify the equivalence of the input/output behavior of two implementations of a FSM. Clearly, exhaustive enumeration of all sequences of states and edges in the two implementations is not a viable proposition. In the work of Devadas et al [35], implicit cube-enumeration was used to avoid exhaustive search. In this approach, the verification is carried out as a two step process. A path is first enumerated on one of the FSMs, with the primary input combinations on this path being cubes in general. This path is then simulated on the second FSM to check if the same output sequence is produced as in the first FSM. Podem-based [54] justification techniques are used for implicit cube-enumeration. Ghosh et al [52] proposed a variation on [35] in which the next-state space as well as the primary-input space is enumerated implicitly. While this approach still basically involves a depth-first search, some states can be visited together.

The recent work of Coudert et al [28] pioneered the use of characteristic-function-based representations of sequential machines using binary decision diagrams, and the associated techniques for range computation for application in FSM verification. The fundamental contribution of this research was to illustrate that an implicit breadth-first traversal of the state space is sufficient for FSM verification. This technology was improved considerably in the work by Touati et al [104] leading to its application to, among other things, the computation of equivalent states in sequential circuits [75].

#### 1.5.5 Sequential Synthesis for Testability

Ensuring the correctness of chips leaving the fabrication line is universally recognized as a key area. The typical testing methodology involves applying a series of test-vectors as inputs to the fabricated die and comparing the output produced against the expected output. The die is deemed defective and discarded if even one of the outputs so produced is different from the expected output. One of the reasons why defective die are not detected by this process is that the defect only modifies redundant portions of the die. Such a defect causes the functionality of the chip to remain unchanged leaving the fault

undetectable or *redundant*. The inability to detect die with redundant faults can lead to erroneous conclusions about the quality of the fabrication process and the quality of the masks. A circuit with no undetectable faults under a given fault model is said to be fully testable under that fault model.

The intimate relationship of logic synthesis to the testability of combinational circuits under the stuck-at-fault model has been known for some time [67, 14, 10, 56] and a number of synthesis procedures have been proposed for realizing fully testable implementations of combinational circuits [10, 56, 99]. An important contribution in that regard was that of Bartlett et al [10] in which a link was established between combinational testability and don't-care-based combinational logic optimization. In the work by Hachtel et al [57], a procedure was proposed for the synthesis of fully multiple-fault testable multilevel circuits based on the results of Kohavi [67] for multiple faults in two-level circuits.

However, since VLSI circuits in general are sequential circuits, they contain memory or storage elements in addition to combinational circuitry. Many latches occupy feedback paths that feed an output of the combinational portion of the circuit back into one of its inputs. Such latches are usually neither directly observable nor controllable. In the context of testing, this implies that for a sequential circuit to be fully testable it is not sufficient for merely the combinational portion to be fully testable; rather, for a fault to be detected, the fault effect must be propagated to those outputs that are observable, and the fault must be excited from those inputs that are controllable. As a result, the testing problem for sequential circuits is more complicated than in the combinational case.

A design-for-testability (DFT) engineering solution, called Scan Design [44], can be used to convert a sequential circuit testing problem to a combinational circuit testing problem by making the latches directly accessible. In the IBM approach [44], the latches are linked to form a serial shift register for scanning a set of values into and out of the latches. In other approaches, parallel load/unload techniques are used (e.g. [91]). Given the large number of latches in a typical chip, allowing parallel access to all the latches is not feasible, so the usual approach followed today is to allow serial access to all the latches. This approach involves tailoring the whole design around the testing methodology and the special latches required. In addition, a performance penalty is involved because of the complex nature of the latches. Another drawback associated with this approach is in the large testing time required since each test vector must be scanned serially in and out, one bit at a time.

In contrast to scan design, non-scan testing methodology involves testing sequential circuits without necessarily making all the latches directly accessible. The non-scan testing effort relies on the philosophy that logic present in a circuit plays a useful role only if it has an effect on what is seen at the observable outputs, based on what is applied at the accessible inputs. Therefore, a fault in such logic should be testable without making the latches accessible. In fact, if a fault cannot be tested in this manner, the associated logic is redundant and should not have been used in the first place. In non-scan testing, a sequence of test vectors has to be applied in general to detect each fault. An important development in non-scan sequential testing was the definition [39] of sequential redundancies with associated don't-cares which, if used optimally, would result in a fully testable sequential circuit, without direct access to any internal storage. Other techniques employing circuit partitioning accompanied by encoding constraints have been proposed for non-scan sequential testability [38]. Techniques for partial scan in which a subset of latches is made scannable have also been proposed (e.g. [1, 78]).

#### 1.6 Overview of Dissertation

The goal of this work is to develop new techniques for the synthesis of sequential logic circuits. The basic terminology used in the dissertation is defined in Chapter 2. Chapter 2 also contains a detailed review of the basic concepts related to state encoding. This review has been included to facilitate the understanding of Chapter 3.

In Chapter 3, a new approach to FSM decomposition is presented. By virtue of this procedure, it is possible to target logic-level optimality of the partitioned sequential circuit. For the cost function chosen, the algorithm presented in this chapter can be used to obtain a decomposition with minimum cost. In many ways, state encoding and FSM decomposition are two sides of the same coin. FSM decomposition can be viewed as a structural transformation of the FSM that guides the subsequent steps of state encoding in the desired direction. Based on this premise, one state encoding strategy involves decomposing the FSM prior to performing the actual encoding. Variations on the decomposition strategy proposed in Chapter 3 can be used for that purpose.

In a common design scenario, one is required to redesign a sequential circuit for which a logic-level description is already available. In such a situation, it is necessary to extract the STG efficiently from the logic-level description. In Chapter 4, a procedure for extracting symbolic information from logic-level descriptions of sequential circuits is presented. The novelty of this procedure lies in the fact that detection of some equivalent states and detection of edges that can be combined in a two-level representation of the STG is performed during the extraction process itself. As a result, this procedure avoids having to extract an intermediate representation in which the fanout of equivalent states and combinable edges are enumerated separately.

The work presented in Chapter 5 is concerned with the synthesis for testability of sequential circuits represented as interacting FSMs. In particular, procedures are presented for synthesizing interacting sequential circuits that are sequentially non-scan single-fault testable without any associated area penalty. In Chapter 6, a procedure is presented for synthesizing multiple-fault-testable sequential circuits.

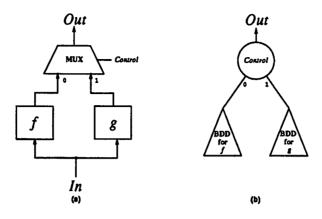

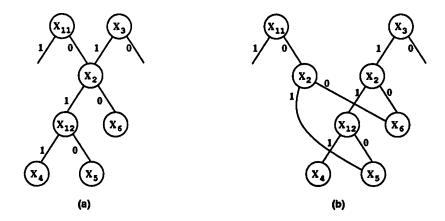

Verifying the equivalence of two logic circuits is crucial since the validity of complex logic transformations must be checked at all times. The work presented in Chapter 7 is concerned with techniques for using general Binary Decision Diagram (BDD) representations for verifying combinational and sequential logic circuits. Unlike reduced, ordered BDDs, general BDDs are not canonical but are much more compact.

Chapter 8 concludes the dissertation. Most of the ideas presented in this dissertation have been implemented in the sequential synthesis system FLAMES. Implementation details of FLAMES are included as Appendix A.

## Chapter 2

## Basic Definitions and Concepts

Most of the terminology used in this dissertation is standard and in common use in the synthesis and testing communities [69, 17, 19]. This chapter is devoted to the definition of the nontrivial terminology and an elucidation of some of the basic concepts.

#### 2.1 Definition of Terminology

#### 2.1.1 Two-Valued Logic

A binary variable is a symbol representing a single coordinate of the Boolean space  $(\epsilon.g.\ a)$ . A literal is a variable or its negation  $(e.g.\ a\ or\ \overline{a})$ . A cube is a set C of literals such that  $x\in C$  implies  $\overline{x}\notin C$   $(e.g.,\{a,b,\overline{c}\})$  is a cube, and  $\{a,\overline{a}\}$  is not a cube). A cube (sometimes called a **product term**) represents the conjunction, *i.e.* the Boolean product of its literals. The trivial cubes, written 0 and 1, represent the Boolean functions 0 and 1 respectively. An **expression** (also called a **sum-of-products**) is the disjunction, *i.e.* a Boolean sum, f, of cubes. For example,  $\{\{a\},\{b,\overline{c}\}\}$  is an expression consisting of the two cubes  $\{a\}$  and  $\{b,\overline{c}\}$ .

A cube may also be written as a bit vector on a set of variables with each bit position representing a distinct variable. The values taken by each bit can be 1, 0 or 2 (don't-care), signifying the true form, negated form and non-existence respectively of the variable corresponding to that position. A minterm is a cube with only 0 and 1 entries. Cubes can be classified based on the number of 2 entries in the cube. A cube with k entries or bits which take the value 2 is called a k-cube. A minterm thus is a 0-cube. A cube

| 1-00 | (inp1, inp3) | out3 | 100 | 1-00 | 101 | 001 | 100 |

|------|--------------|------|-----|------|-----|-----|-----|

| 111- | (inp1, inp3) | out3 | 011 | 111- | 101 | 001 | 011 |

| 101- | (inp1, inp2) | out2 | 110 | 101- | 110 | 010 | 110 |

| 1-01 | (inp1, inp3) | out1 | 101 | 1-01 | 101 | 100 | 101 |

| 0    | (inp1)       | out1 | 111 | 0    | 100 | 100 | 111 |

|      | (a)          |      |     | -    | (b) |     |     |

Figure 2.1: An example of a symbolic cover and its one-hot coded representation

$c_1$  is said to **cover (contain)** another cube  $c_2$ , if  $c_1$  evaluates to 1 for every minterm for which  $c_2$  evaluates to 1. A **super-cube** of a set of cubes,  $c_i$ , is defined as the smallest cube containing all the minterms contained in  $c_i$ . The **on-set** of a function f is the set of minterms for which the function evaluates to 1, the **off-set** of f is the set of minterms for which f evaluates to 0, and the **don't-care set** or the **DC-set** is the set of minterms for which the value of the function is unspecified. An **implicant** of f is a cube that does not contain any minterm in the off-set of f. A **prime-implicant** of f is an implicant which is not contained by any other implicant of f.

#### 2.1.2 Multi-Valued Logic

In general, a logic function may have symbolic (also known as multiple-valued) input or output variables in addition to binary variables. Like binary variables, a symbolic variable also represents a single coordinate, with the difference that a symbolic variable can take a subset of values from a set, say  $P_i$ , that has a cardinality greater than two. Let  $X_i$  be a symbolic input variable for the function f, and let  $S_i$  be a subset of  $P_i$ . Then  $X_i^{S_i}$  represents the Boolean function

$$X_i^{S_i} = \begin{cases} 0 & \text{if } X_i \notin S_i \\ 1 & \text{if } X_i \in S_i \end{cases}$$

$X_i^{S_i}$  is called a literal of the variable  $X_i$ . The definition of a cube (product-term) remains unchanged; it is the Boolean product of literals. A minterm or 0-cube is now defined as the cube in which all variables take only a single value. A cube covers (contains) a minterm if it evaluates to 1 for that minterm. A cube  $c_1$  covers (contains) another cube  $c_2$  if  $c_1$  evaluates to 1 for all the minterms for which  $c_2$  evaluates to 1. When an output variable, say  $Y_j$ , is symbolic it implies that  $Y_j$  can take a value from a set  $P_j$ , of values when the input is some minterm. A function in which some variables are symbolic is known as a symbolic

cover. An example of a symbolic cover with one symbolic input and one symbolic output is shown in Figure 2.1(a). In the example, the symbolic input variable takes values from the set  $\{inp1, inp2, inp3\}$  while the symbolic output variable takes a value from the set  $\{out1, out2, out3\}$ . A convenient method for representing a symbolic variable that can take values from a set of cardinality n is to use an n-bit vector to depict a literal of that variable such that each position in the vector corresponds to a specific element of the set. A 1 in a position in the vector signifies the presence of an element in the literal while a 0 signifies the absence. This method of representation is commonly known as one-hot. An example of a one-hot representation for the symbolic cover of Figure 2.1(a) is shown in Figure 2.1(b).

#### 2.1.3 Finite Automata

A Finite-State Machine is represented by its State Transition Graph (STG) or equivalently, by its State Transition Table (STT). A STG is denoted by G(V, E,W(E)), where V is the set of vertices corresponding to the set of states S, where ||S|| is the cardinality of the set of states of the FSM, E is the set of edges such that an edge  $(v_i)$  $v_i$ ) joins  $v_i$  to  $v_i$  if there is a primary input minterm that causes the FSM to evolve from state  $v_i$  to state  $v_i$ , and W(E) is a set of labels attached to each edge, each label carrying the information of the value of the input that caused the transition and the values of the primary outputs corresponding to that transition. The input combination and presentstate corresponding to an edge, e, or a set of edges is (i, s), where i and s are cubes. The fanin of a state, q is a set of edges and is denoted fanin(q). The fanout of a state q is denoted fanout(q). The output and the fanout state of an edge  $(i, s) \in E$  are o((i, s)) and  $n((i, s)) \in S$  respectively. Given  $N_i$  inputs to a machine,  $2^{N_i}$  edges with minterm input labels fan out from each state. A STG where the next-state and output labels for every possible transition from every state are defined corresponds to a completely specified machine. An incompletely specified machine is one where at least one transition edge from some state is not specified.

A STT is a tabular representation of the FSM. Each row of the table corresponds to a single edge in the STG. Conventionally, the left most columns in the table correspond to the primary inputs and the right most columns to the primary outputs. The column following the primary inputs is the present-state column and the column following that is the next-state column.

In all of the work reported here, a starting or initial state (also called the reset state) is assumed to exist for a machine. Given a logic-level description of a sequential machine with  $N_b$  flip-flops,  $2^{N_b}$  possible states exist in the machine. A state which can be reached from the reset state via some input vector sequence is called a valid state (or a reachable state). The corresponding input vector sequence is called the justification sequence for that state. A state for which no justification sequence exists is called an invalid state (or an unreachable state). Two states a and b are equivalent if the output sequence produced starting from a is the same as the output sequence produced starting from a input sequence.

A differentiating sequence for a pair of states  $q_1, q_2 \in Q$  of a machine M is a sequence (or string) of input vectors such that the last vector produces different outputs when the sequence is applied to M, when M is initially in  $q_1$  or when M is initially in  $q_2$ . Two states  $q_1, q_2$  in a completely specified machine M are equivalent (written as  $q_1 \equiv q_2$ ), if they do not possess a differentiating sequence. If two states  $q_1, q_2$  in an incompletely specified machine M do not possess a differentiating sequence, they are said to be compatible (written as  $q_1 \cong q_2$ ).

A State Transition Graph  $G_1$  is said to be isomorphic to another State Transition Graph  $G_2$  if and only if they are identical except for a renaming of states.

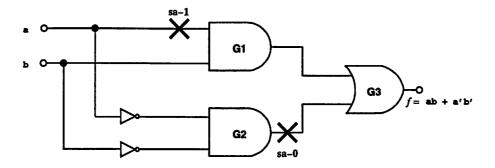

#### 2.1.4 Testing

Testing is concerned with the detection of defects (faults) on a chip. Test generation is used to obtain a compact set of inputs that can be applied to the chip to detect the presence of defects. Unless otherwise mentioned, the fault model assumed is the stuck-at model. In the stuck-at fault-model, a defect forces one or more inputs/outputs of a gate in the circuit to constant zero or constant one. If a gate output or primary input has multiple fanout, each fanout can be stuck-at a constant, independent of the other fanouts. In the single-fault model, only one wire is affected at a time. In the multiple-fault model, multiple wires are affected at the same time.

There are two kinds of untestable faults in a circuit. A fault is combinationally testable if there exists an input that can propagate the effect of the fault to the outputs of the combinational logic. Otherwise, the fault is said to be combinationally redundant or untestable. A finite-state machine is assumed to be implemented by combinational logic

and feedback registers. Tests are generated for faults in the combinational logic part. A fault is said to be **sequentially redundant** or **untestable** if the fault is combinationally testable and the effect of the fault cannot be propagated to a primary output by the application of a primary input sequence.

An edge in the STG of a machine is said to be corrupted by a fault if either the fanout state or output label of this edge is changed because of the existence of the fault. A path in the STG is said to be corrupted if at least one edge in the path has been corrupted.

If a fault is propagated to the next-state lines of a machine, it results in a faulty next-state, rather than a fault-free (or true) next-state. The fault is deemed to have produced a faulty/fault-free state pair.

To detect a fault in a sequential machine, the machine has to be placed in a state which can excite the fault and then the fault effect must be propagated to a primary output. These tasks are called **state justification** and **fault excitation-and-propagation**, respectively.

A primitive gate in a logic network is called **prime** if none of its inputs can be removed without causing the resulting circuit to be functionally different. The gate itself is **irredundant** if its removal causes the resulting circuit to be functionally different. A gate-level circuit is said to be **prime** if all the gates are prime and **irredundant** if all the gates are irredundant. It can be shown that a gate-level circuit is prime and irredundant if and only if it is 100% testable for all single stuck-at faults [10].

### 2.2 A Review of the Basic Concepts in State Encoding

A review of previous work in state encoding was presented in Chapter 1. To aid the understanding of the material in Chapter 3, a more detailed review of recent work in that area is presented here.

A finite-state machine is a logic function with symbolic inputs and outputs, with the additional caveat that the same symbols appear in the input and output planes. Therefore, state encoding considered in its entirety is an input-output encoding problem and it cannot be approximated by either a purely input encoding problem or a purely output encoding problem.

The main difficulty in state encoding lies in the need to predict the effects of the complicated logic optimization steps which follow the encoding process. A major con-

| 0 (s1, s2, s4) s2 1 |

|---------------------|

| 1 (s2, s4) s1 1     |

| 1 (s1, s3) s4 0     |

| 0 (s3) s3 0         |

| - (- )              |

|                     |

| (b)                 |

|                     |

Figure 2.2: A symbolic tabular representation of a finite-state machine

Figure 2.3: Codes satisfying input constraints

tribution in that regard was that of De Micheli et al [86] in which a new paradigm was proposed for state encoding. It was suggested that state encoding be viewed as a two-step process. In the first step, a tabular representation of the FSM is optimized at the symbolic level. This optimization step generates constraints on the relationships between codes for different states. In the second step, states are encoded in such a way the constraints are satisfied. Satisfaction of the constraints guarantees that the optimizations at the symbolic-level will be preserved in the Boolean domain. The accuracy with which optimization at the symbolic-level can mimic optimizations in the Boolean domain is then a major issue.

#### 2.2.1 Input Encoding Targeting Two-Level Logic

The initial effort in state encoding using the two-step paradigm was targeted toward obtaining optimal two-level implementations of encoded FSMs. A technique (implemented in the program ESPRESSO-MV [26] by Rudell et al) for minimizing two-level covers with symbolic variables is known as symbolic or multiple-valued minimization [94].

0 -1- 011 0 1 --1 100 0 1 --0 001 1 0 -0- 000 1

Figure 2.4: Two-level implementation of encoded finite-state machine

An example tabular representation of a FSM is shown in Figure 2.2(a). A symbolic minimization of this FSM leads to the cover shown in Figure 2.2(b). It can be seen that the minimized cover is output-disjoint and all the reduction in the cardinality of the symbolic cover is due to relationships in the input part, *i.e.* due to the fact that some states fan out to the same next state for certain primary inputs.

The goal in deriving constraints from the minimized symbolic cover is to encode the states in such a way that the cardinality of the resulting two-level Boolean implementation is no greater than the cardinality of the minimized symbolic cover. A sufficient condition that ensures the preservation of the cardinality of the symbolic cover <sup>1</sup> during the transition from the symbolic to the Boolean domain is to ensure that each multiple-valued input literal in the minimized symbolic cover translates into a single cube in the Boolean domain. In other words, given a multiple-valued literal, the states present in it should form a face in the Boolean n-space in such a way that the face does not include the states absent from the same multiple-valued literal. Such constraints are called face-embedding or input constraints, and the process of obtaining these constraints and satisfying them is known as input encoding.

Codes satisfying the face-embedding constraints implied by the minimized symbolic cover of Figure 2.2(b) are shown in Figure 2.3(a). As can be seen in the figure, three binary variables are required to satisfy the face-embedding constraints. Figure 2.3(b) shows the location of these codes in the Boolean n-space and shows that they satisfy the face-embedding constraints. The cover obtained after substitution of the state codes in the symbolic cover and a two-level Boolean minimization is shown in Figure 2.4. While two-level symbolic minimization by definition [94] can be used to explore all optimization possibilities in the input plane, it is intrinsically incapable of optimizations involving a sharing of logic among different next-state symbols. Since the work by De Micheli et al [86] obtained the encoding constraints using two-level symbolic minimization, it effectively approximated the

<sup>&</sup>lt;sup>1</sup>minimized using ESPRESSO-MV

Figure 2.5: Example of the effects of dominance relationships

state encoding problem as one of input encoding.

#### 2.2.2 Output Encoding Targeting Two-Level Logic

There are two types of interactions in the next-state plane that lead to cardinality reductions in the minimized two-level Boolean cover. The first type involves the bitwise dominance of the code of one state by the code of another. A binary vector  $v_1$  is said to dominate another binary vector  $v_2$  if in every bit that  $v_2$  has a 1,  $v_1$  also has a 1. An example is shown in Figure 2.5. A cover with a symbolic output part is shown in Figure 2.5(a) and the codes for the symbols  $s_1$  and  $s_2$  are shown in Figure 2.5(b). Since the code for the symbol  $s_1$  dominates the code for  $s_2$ , the input cubes asserting  $s_1$  can be used as don't-cares in order to reduce the cardinality of the cover for  $s_2$ , as shown in Figure 2.5(c). The use of dominance constraints in state encoding was explored by De Micheli [85]. In that work, the problem of exploiting the dominance constraints was reduced to one of heuristically ordering the states. The ordering of states dictated the dominance relationships between states. Satisfying these dominance relationships (which should not conflict) results in some reduction of the overall cover cardinality. The basic intuition used in the ordering was that a next-state with a large cover be optimized under as large a don't-care set as possible.

A limitation of this approach is that minimum cardinality cannot be guaranteed because all possible dominance relations are not explored, nor is an optimum set selected. A more basic shortcoming is that dominance relations are not the only kind of relationships between symbolic values that can be exploited. After a symbolic cover has been encoded, it represents a multiple-output logic function and minimizing a multiple-output function entails exploiting other sharing relationships rather than just the dominance relationship.

The second type of interaction in the next-state field has to do with disjunctive relationships between state codes. A disjunction of two Boolean vectors is the bitwise-or of the two vectors. If the code of a state, say  $s_1$  is equivalent to or is dominated by the disjunction of the state codes of two or more state variables, then the cardinality of the cover

|                                  | s1 = 00<br>s2 = 01<br>s3 = 11                       | s1 = 11<br>s2 = 01<br>s3 = 10           |

|----------------------------------|-----------------------------------------------------|-----------------------------------------|

|                                  | Codes                                               | Codes                                   |

| 101 s1 1<br>100 s2 1<br>111 s3 1 | 1–1 00 1<br>100 01 1<br>111 11 1<br>Minimized Cover | 10- 01 1<br>1-1 10 1<br>Minimized Cover |

| (a)                              | (b)                                                 | (c)                                     |

Figure 2.6: Example of the effects of disjunctive relationships

for the next-state  $s_1$  can be reduced by using the on-sets of the covers for the codes of the next-states involved in the disjunction. As an example, consider the cover in Figure 2.6(a) with symbolic values in the output part. In Figure 2.6(b), the code for the symbol  $s_1$  is the disjunction of the codes for symbols  $s_2$  and  $s_3$ . The cardinality of the cover of the on-set for the symbol  $s_1$  is effectively zero. When the disjunctive relationship is absent as in the codes shown in Figure 2.6(c), the cardinality of the cover of the on-set of the symbol  $s_1$  is one. Note that the reduction in the cardinality in Figure 2.6(b) is for the dominating state and not the dominated state, and is therefore not due to the dominance relationships described previously.

A method for exploring all possible dominance and disjunctive relationships implicitly but exhaustively was proposed by Devadas and Newton [41]. The basic approach involved a modification of the prime-implicant generation and covering procedures fundamental to two-level Boolean minimization [90, 83]. The definition of the notion of Generalized Prime Implicants (GPIs) was the key contribution in that regard.

#### Generalized Prime Implicants