## Copyright © 1992, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# DESIGN AND EVALUATION OF DIRECTORY-BASED CACHE COHERENCE SYSTEMS

by

Brian Walter O'Krafka

Memorandum No. UCB/ERL M92/4

6 January 1992

# DESIGN AND EVALUATION OF DIRECTORY-BASED CACHE COHERENCE SYSTEMS

by

Brian Walter O'Krafka

Memorandum No. UCB/ERL M92/4

6 January 1992

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# DESIGN AND EVALUATION OF DIRECTORY-BASED CACHE COHERENCE SYSTEMS

by

Brian Walter O'Krafka

Memorandum No. UCB/ERL M92/4

6 January 1992

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# Design and Evaluation of Directory-Based Cache Coherence Systems Brian Walter O'Krafka

Department of Electrical Engineering and Computer Sciences, University of California, Berkeley.

#### **Abstract**

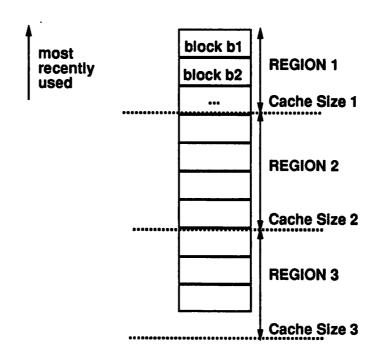

A cache coherence scheme is a critical part of a shared memory multiprocessor because it relieves the programmer of the burden of moving shared data among local and remote memories. In this dissertation several new techniques are described for implementing and evaluating the performance of cache-coherent multiprocessors. The first contribution of this work is a generalization of shared bus stack simulation techniques that supports directory-based cache coherence schemes. This is desirable because stack simulation permits the evaluation of multiple cache sizes in a single simulation run. Results are presented for three benchmark programs, three directory methods, and multiple cache, block and multiprocessor sizes. The results quantify the tradeoffs between network traffic and miss ratio that are possible by varying the number of updates in a competitive directory scheme. These results extend previous studies of shared bus architectures by accounting for point-to-point network traffic and larger numbers of processors. A second contribution is an approximation technique for analyzing interconnection networks as open, acyclic networks of finite queues. The technique combines the algorithms used in the Bell Laboratories Queueing Network Analyzer with a known algorithm for approximating the effect of finite buffers. The combined algorithm permits analysis of queueing networks with hundreds of queues and is applicable to a broad class of interconnection network, including hypercubes, meshes, tori and Delta networks. Using traffic estimates from cache simulations, this analysis technique is applied to a number of alternative networks. Good cache and network performance requires good synchronization support. The latter part of this dissertation describes several efficient implementations of fetch&op synchronization primitives. The implementations are suitable for hardware or software, and can be easily modified to support multiprefix operations.

Professor A. Richard Newton

Dissertation Committee Chairman

#### Acknowledgements

Writing this dissertation has been an intensely arduous yet intensely rewarding experience. Many of the rewards have been due to interactions with some extremely talented people. My advisor, Professor Richard Newton, gave me the resources and motivation to study multiprocessor memory systems. Richard's advisorship has taught me a lot about independent research and creative thought, for which I am thankful. The other members of my dissertation committee, Professor Abhiram Ranade and Professor Ronald Wolff, provided valuable comments that improved this work. Their participation is gratefully acknowledged. I also received technical support from several students in the Computer Science Division. Mike Carlton was a source of good ideas about cache coherence and simulation. M. T. Raghunath gave me an education in multiprocessor networks. Bob Boothe provided help with benchmark validation. The help of all three is greatly appreciated.

Others provided moral support and friendship. Mark Beardslee, Brian Lee and Gregg Whitcomb endured my griping during many lunch hours and coffee breaks. Wendell Baker, Abhijit Ghosh and Chuck Kring relieved the monotony of focussed research by participating in numerous discussions on cold fusion, Republican politics and other diverse topics. I am deeply grateful for the opportunity to work with these fellow students.

This dissertation would not have been completed without the support of my family. The energy and enthusiasm of my wife, Audrey, were frequent sources of encouragement. My daughters Anne and Catherine added an extra dimension to my life that has relieved much of the tension of graduate study. Their arrival into our family will be the most memorable part of my experiences at Berkeley. Anne, Catherine, Audrey and I all received a great deal of support from our parents in Canada, for which we are grateful.

This work was supported in part by the Natural Sciences and Engineering Research Council of Canada, Digital Equipment Corporation, and the Defense Advanced Research Projects Agency (under contract N00039-C-87-0182). Their support is gratefully acknowledged.

## **Contents**

| Ta | able o  | f Contents                                                        | 3  |

|----|---------|-------------------------------------------------------------------|----|

| Li | st of l | Figures                                                           | 4  |

| Li | st of   | Tables                                                            | 5  |

| 1  | Intr    | oduction                                                          | 1  |

|    | 1.1     | The Goal: Cost-Effective Acceleration of Engineering Applications | 1  |

|    | 1.2     | Multiprocessor Systems                                            | 2  |

|    |         | 1.2.1 Programming Paradigms                                       | 3  |

|    |         | 1.2.2 Architectures                                               | 5  |

|    | 1.3     | Multiprocessor Cache Coherence                                    | 7  |

|    |         | 1.3.1 Formal Notions of Cache Coherence                           | 7  |

|    |         | 1.3.2 Cache Coherence Strategies                                  | 10 |

|    |         | 1.3.3 Performance Evaluation of Cache Coherence Strategies        | 12 |

|    | 1,4     | Organization of the Dissertation                                  | 16 |

|    | 1.5     | Contributions                                                     | 17 |

| 2  | Dire    | ectory-based Cache Coherence Strategies                           | 18 |

|    | 2.1     | Overview                                                          | 18 |

|    | 2.2     | The Censier and Feautrier Directory Scheme                        | 18 |

|    | 2.3     | Efficient Directory Implementations                               | 20 |

|    |         | 2.3.1 Schemes that Restrict List Length                           | 21 |

|    |         | 2.3.2 Schemes that Reduce List Granularity                        | 21 |

|    |         | 2.3.3 Schemes that Store Lists Per Cache Block                    | 22 |

|    | 2.4     | Conclusions                                                       | 24 |

| 3  | Wor     | kload Characterization                                            | 26 |

|    | 3.1     | Overview                                                          | 26 |

|    | 3.2     | Previous Work                                                     | 26 |

|    | 3.3     | Stack Simulation of Directory Methods                             | 32 |

|    |         | 3.3.1 Introduction                                                | 32 |

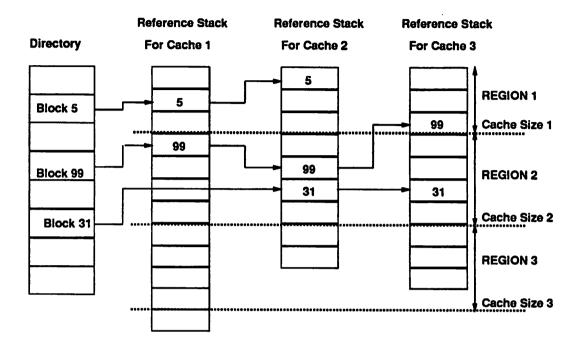

|    |         | 3.3.2 Multiprocessor Stack Simulation                             | 34 |

|    |         | 3.3.3 Protocols                                                   | 45 |

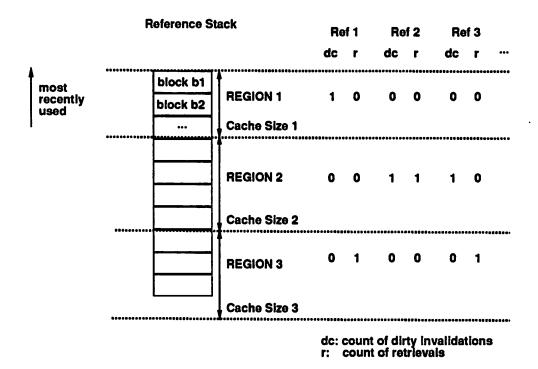

|   |      | 3.3.4    | Stack Simulation of Directory-based Coherence Protocols      | 45  |

|---|------|----------|--------------------------------------------------------------|-----|

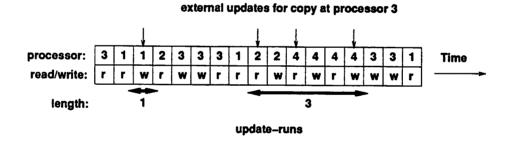

|   | 3.4  |          | ating Competitive Directory Methods                          | 49  |

|   | 3.5  | Simula   | ation Methodology                                            | 50  |

|   |      | 3.5.1    | Metrics                                                      | 51  |

|   |      | 3.5.2    | Simulated Architecture                                       | 51  |

|   |      | 3.5.3    | Benchmarks                                                   | 54  |

|   | 3.6  |          | ical Results                                                 |     |

|   | 5.0  | 3.6.1    | Misses and Traffic                                           | 56  |

|   |      | 3.6.2    |                                                              | 56  |

|   |      | 3.6.3    | Performance of the Competitive Protocol                      | 62  |

|   |      | 3.6.4    | Coherence Traffic Versus Multiprocessor Size                 | 69  |

|   | 3.7  |          | Synchronization Behavior                                     | 69  |

|   | 3.7  | Conciu   | asions                                                       | 73  |

| 4 | Netv | vork Pe  | rformance Analysis                                           | 74  |

|   | 4.1  | Overvi   | ew                                                           | 74  |

|   | 4.2  | Previo   | us Work                                                      | 74  |

|   |      | 4.2.1    | Network Design                                               | 75  |

|   |      | 4.2.2    | Performance Analysis Via Simulation and Stochastic Modelling | 81  |

|   |      | 4.2.3    | Performance Analysis Via Formal Properties                   | 85  |

|   |      | 4.2.4    | Focus of this Research                                       | 86  |

|   | 4.3  | An An    | alytic Modelling Technique                                   | 86  |

|   |      | 4.3.1    | Overview                                                     | 86  |

|   |      | 4.3.2    | The Queueing Network Analyzer                                | 87  |

|   |      | 4.3.3    | Altiok and Perros' Finite Buffer Approximation               | 94  |

|   |      | 4.3.4    | Merging the Algorithms                                       | 98  |

|   |      | 4.3.5    | Two Moment Approximations of Blocking Distributions          | 100 |

|   |      | 4.3.6    | Iterating QNA and the Finite Buffer Algorithm                | 102 |

|   |      | 4.3.7    | Virtual Cut-through Flow Control                             | 103 |

|   |      | 4.3.8    | Virtual Channels                                             | 105 |

|   |      | 4.3.9    | Convergence and Computational Complexity                     | 107 |

|   | 4.4  | Numer    | ical Results                                                 | 108 |

|   |      | 4.4.1    | Methodology                                                  | 108 |

|   |      | 4.4.2    | Results                                                      | 110 |

|   | 4.5  |          | sor Utilization of Caching Schemes                           | 119 |

|   |      | 4.5.1    | Methodology                                                  | 119 |

|   |      | 4.5.2    | Numerical Results                                            | 121 |

|   | 4.6  |          | sion                                                         | 123 |

| _ | _    |          |                                                              |     |

| 5 | •    | chroniza |                                                              | 125 |

|   | 5.1  | Overvi   |                                                              | 125 |

|   | 5.2  |          | us Work                                                      | 125 |

|   |      | 5.2.1    | Overview                                                     | 125 |

|   |      | 5.2.2    | Read, Write and Fetch&ops                                    | 129 |

|   |      | 5.2.3    | Lock Implementations                                         | 129 |

|   |      | 524      | Barrier Implementations                                      | 121 |

|    |             | 5.2.5 Implementation of Multiprefix Operations             | 132 |

|----|-------------|------------------------------------------------------------|-----|

|    |             | 5.2.6 Combining                                            | 135 |

|    |             | 5.2.7 Summary                                              | 137 |

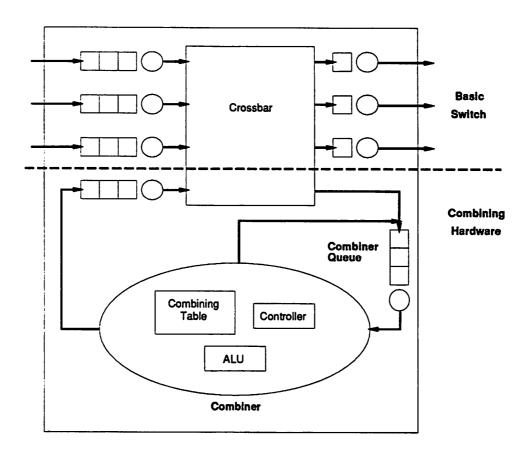

|    | 5.3         | Efficient Implementation of Dynamic Combining              | 137 |

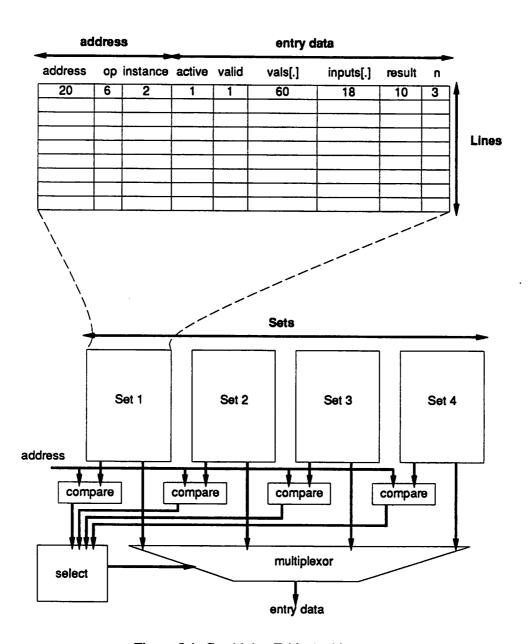

|    |             | 5.3.1 Efficient Dynamic Combining in Hardware              | 138 |

|    |             | 5.3.2 Efficient Dynamic Combining in Software              | 142 |

|    |             | 5.3.3 Modifications to Support Static Combining            | 146 |

|    | 5.4         | Conclusions                                                | 147 |

| 6  | Con         | clusions and Future Work                                   | 149 |

| Ū  | 6.1         | Conclusions                                                | 149 |

|    | 6.2         | Future Work                                                |     |

|    | 0.2         | Tudio Work                                                 | 151 |

| Bi | bliogr      | aphy                                                       | 152 |

| A  | Geo         | metric Queue Models                                        | 165 |

|    | A.1         | GEO+1 <sup>k</sup> /GEO+1/1/N Queue Model                  | 165 |

|    | A.2         | GEO2+1 <sup>k</sup> /GEO+1/1/N Queue Model                 | 169 |

|    | A.3         | Distribution of the Minimum of Two GEO2+1 Random Variables | 173 |

| В  | Que         | ueing Models for Specific Interconnection Networks         | 175 |

|    | B.1         | Notes for All Models                                       | 175 |

|    | B.2         | Unidirectional Three Dimensional Torus                     |     |

|    | <b>B.3</b>  | Bidirectional Three Dimensional Torus                      | 177 |

|    | <b>B</b> .4 | Three Dimensional Mesh                                     | 177 |

|    | B.5         | Hypercube                                                  | 177 |

|    | <b>B.6</b>  | Radix-2 Delta                                              | 177 |

|    | <b>B</b> .7 | Radix-4 Delta                                              | 183 |

|    | ВЯ          | Radix-8 Delta                                              | 102 |

# **List of Figures**

| 1.1  | Components of a Multiprocessor System                               | 2        |

|------|---------------------------------------------------------------------|----------|

| 1.2  |                                                                     | 5        |

| 1.3  |                                                                     | 6        |

| 1.4  | The Restrictiveness of Strong Ordering                              | 3        |

| 2.1  | Tags for Basic Censier and Feautrier Protocol                       | 9        |

| 2.2  | Small Tag Fields                                                    | <u>)</u> |

| 2.3  | Decentralized Linked List Directory                                 | 3        |

| 2.4  | Centralized Linked List Directory                                   | 1        |

| 2.5  | Memory-Mapped Linked List Scheme                                    | 5        |

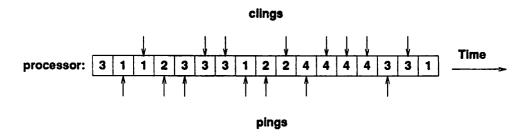

| 3.1  | The Ping/Cling Locality Model                                       | )        |

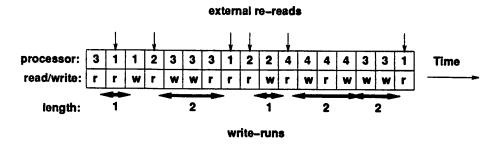

| 3.2  | The Write-run Model                                                 | l        |

| 3.3  | Uniprocessor Stack Simulation                                       | 3        |

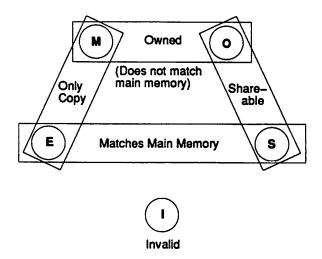

| 3.4  | MOESI States                                                        | 5        |

| 3.5  | Stack Algorithm for MOESI Protocols                                 | 2        |

| 3.6  | Multiprocessor Stack Simulation                                     | 3        |

| 3.7  | Write Routine for Invalidation Protocol                             | 1        |

| 3.8  | Write Routine for Update Protocol                                   | 1        |

| 3.9  | Write Routine for Competitive Protocol                              | 5        |

| 3.10 |                                                                     | 3        |

| 3.11 | The Update-run Model                                                | )        |

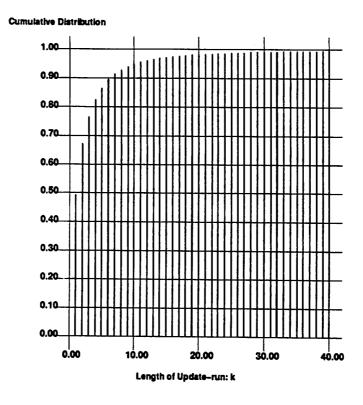

| 3.12 | Cumulative Distribution of Update-run Length                        | l        |

| 3.13 | Fraction of Updates that Occur at $k$ 'th Position in an Update-run | 2        |

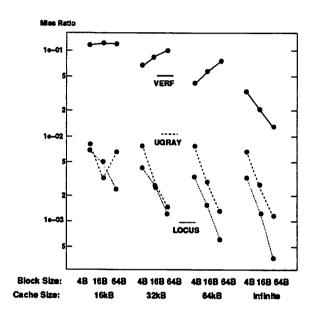

| 3.14 | Miss Ratios for Invalidation Protocol                               | 7        |

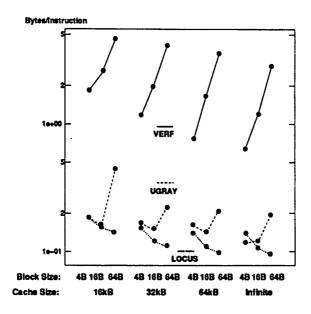

|      | Traffic for Invalidation Protocol                                   | 3        |

| 3.16 | Miss Ratios for Update Protocol                                     | )        |

| 3.17 | Traffic for Update Protocol                                         | )        |

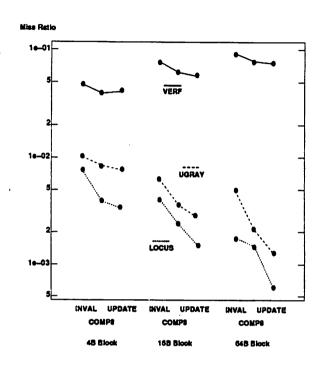

|      | Miss Ratios for Competitive Protocol                                | )        |

|      | Traffic for Competitive Protocol                                    | l        |

|      | Comparison of Miss Ratios for All Protocols                         | <u>)</u> |

| 3.21 | Comparison of Traffic (Volume) for All Protocols                    | 3        |

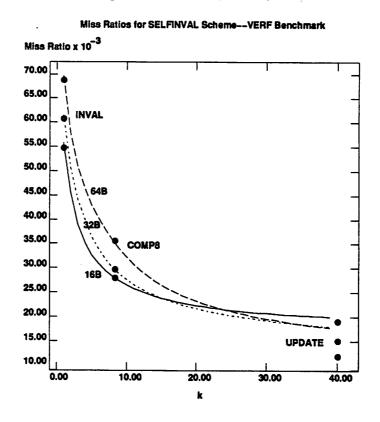

|      | Miss Ratios Versus Self-Invalidation Threshold (VERF)               | 3        |

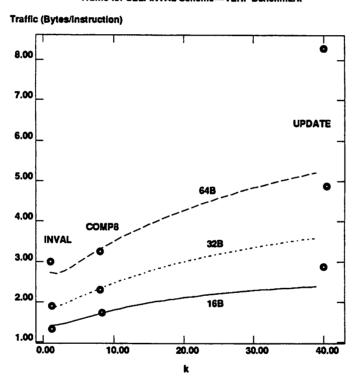

| 3.23 | Traffic Versus Self-Invalidation Threshold (VERF)                          | 64  |

|------|----------------------------------------------------------------------------|-----|

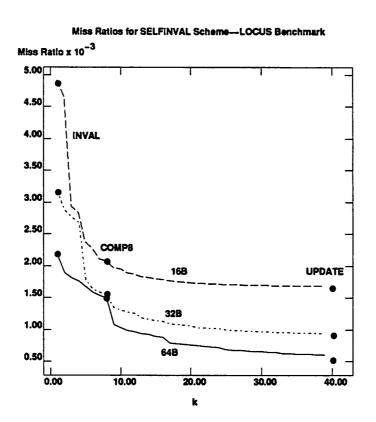

| 3.24 | Miss Ratios Versus Self-Invalidation Threshold (LOCUS)                     | 65  |

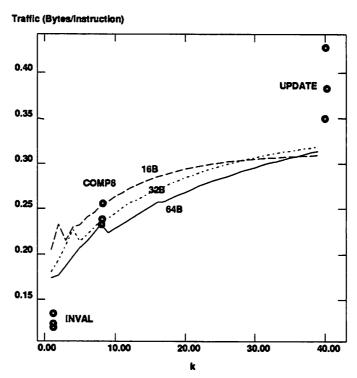

|      | Traffic Versus Self-Invalidation Threshold (LOCUS)                         | 66  |

|      | Miss Ratios Versus Self-Invalidation Threshold (UGRAY)                     | 67  |

| 3.27 | Traffic Versus Self-Invalidation Threshold (UGRAY)                         | 68  |

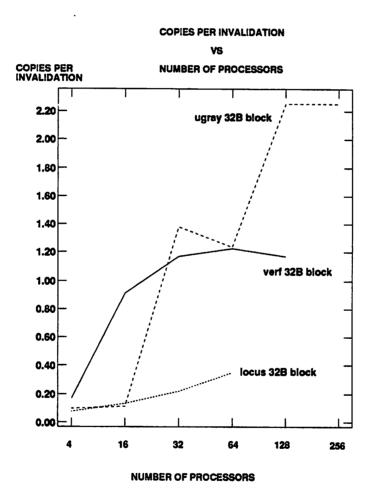

|      | Copies Per Inval Versus Multiprocessor Size                                | 70  |

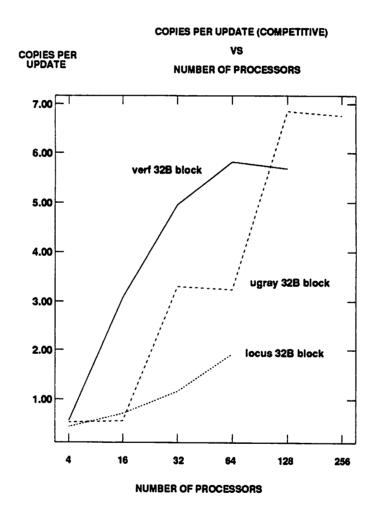

|      | Copies Per Update Versus Multiprocessor Size                               | 71  |

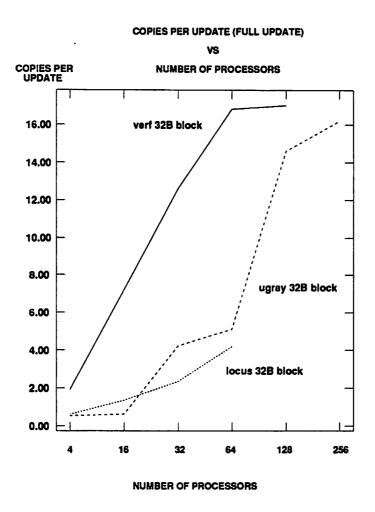

| 3.30 | Copies Per Update Versus Multiprocessor Size                               | 72  |

|      |                                                                            |     |

| 4.1  | Structure of a Network Switch                                              | 75  |

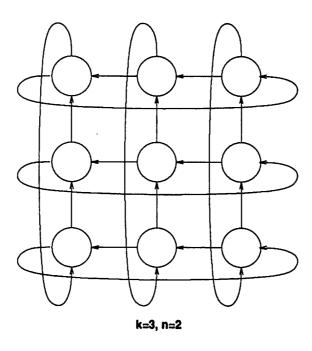

| 4.2  | Unidirectional k-ary n-cube Network                                        | 76  |

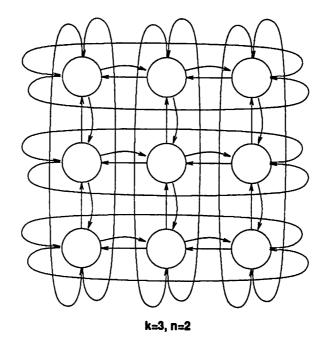

| 4.3  | Bidirectional k-ary n-cube Network                                         | 77  |

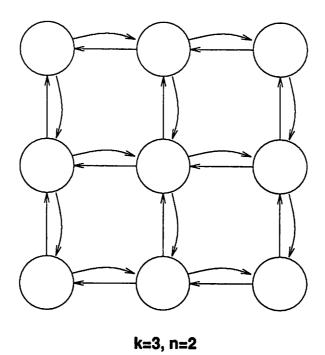

| 4.4  | k-ary n-dimensional Mesh                                                   | 77  |

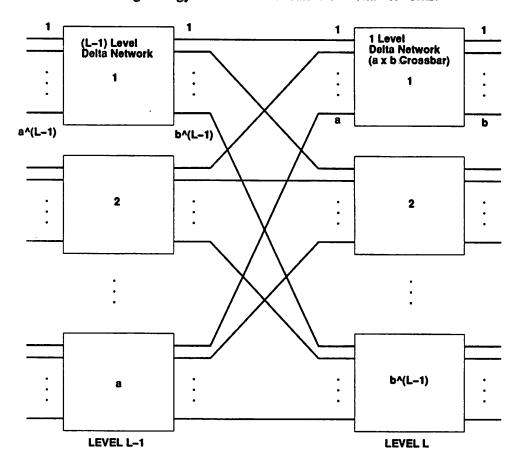

| 4.5  | Recursive Structure of Delta Networks                                      | 78  |

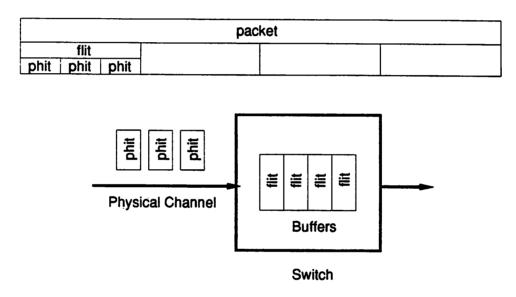

| 4.6  | Packet-switching Terminology                                               | 79  |

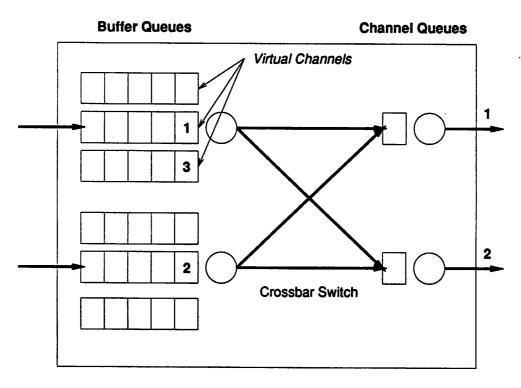

| 4.7  | A Network Switch with Virtual Channels                                     | 80  |

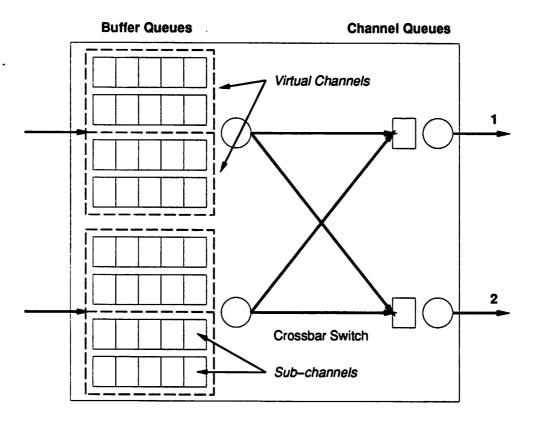

| 4.8  | Virtual Channels and Sub-channels                                          | 82  |

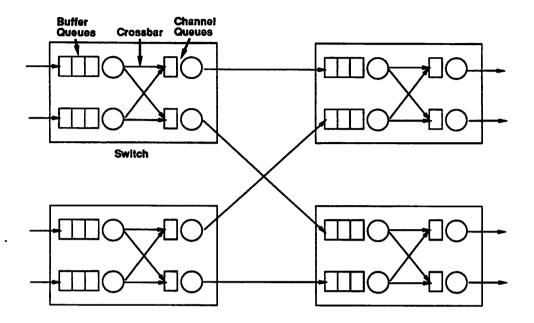

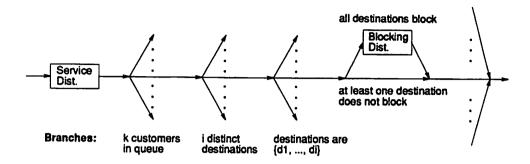

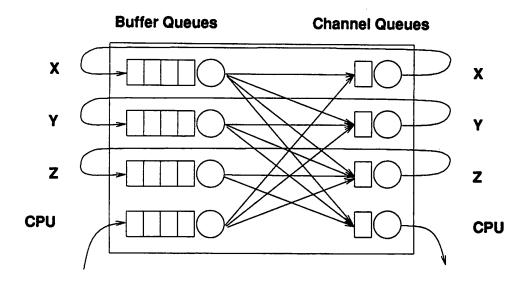

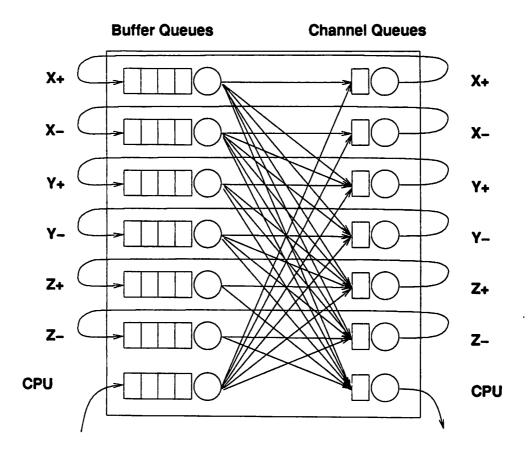

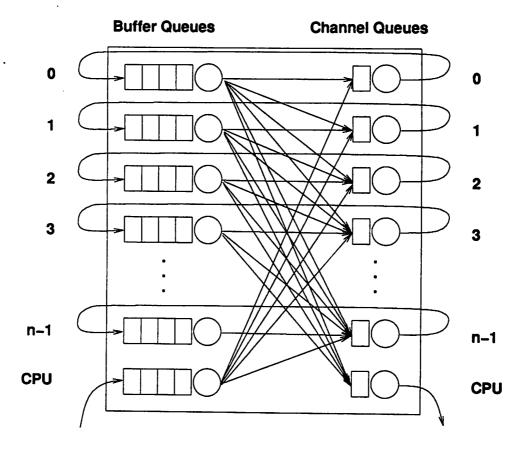

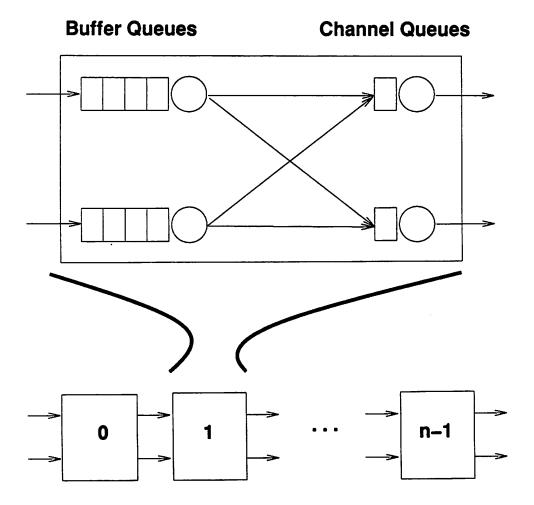

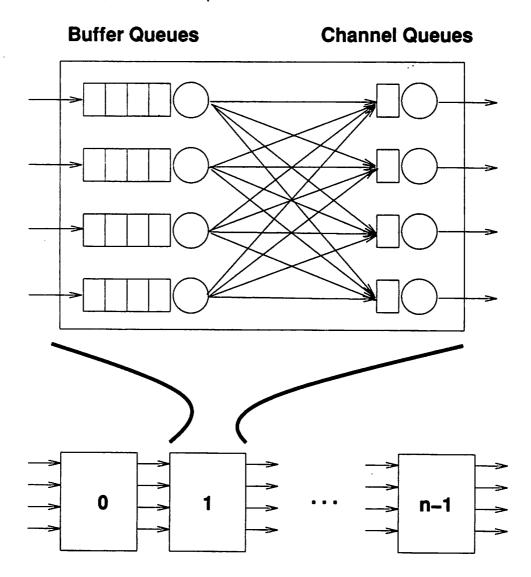

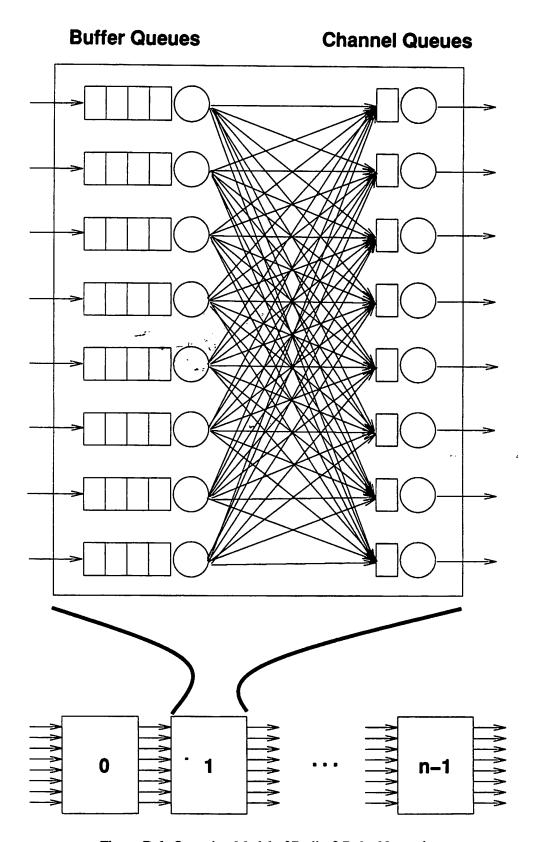

| 4.9  | Queueing Model of a Delta Network                                          | 88  |

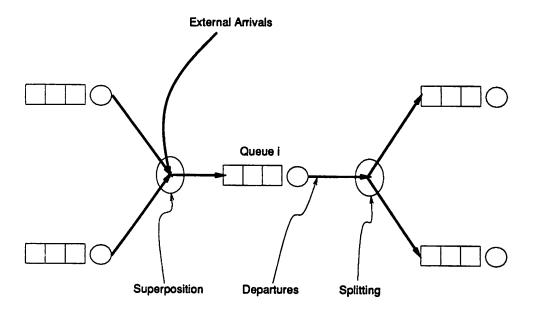

| 4.10 | Superposition, Departures and Splitting of Point Processes                 | 89  |

| 4.11 | Summary of QNA Algorithm                                                   | 94  |

| 4.12 | Coxian Representation of Adjusted Service Distribution                     | 97  |

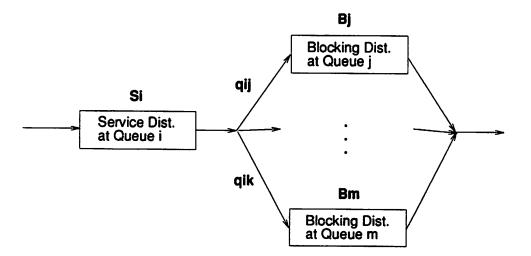

| 4.13 | Coxian Representation of Blocking Delay                                    | 98  |

| 4.14 | Summary of Finite Buffer Algorithm                                         | 99  |

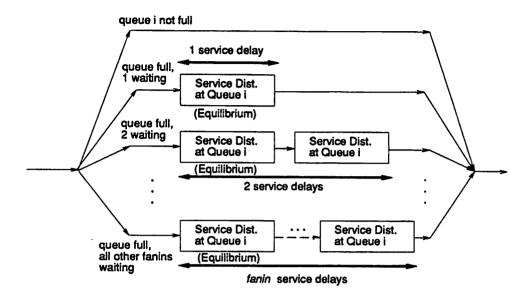

| 4.15 | Combining QNA and the Finite Buffer Algorithm                              | 104 |

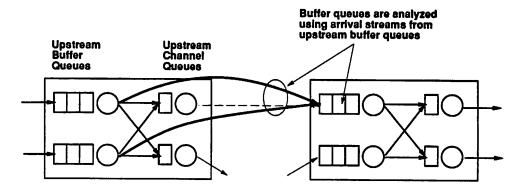

| 4.16 | Arrivals in Buffer Queue Analysis Bypass the Upstream Channel Queue        | 105 |

| 4.17 | Blocking Delay Distribution with Virtual Channels                          | 106 |

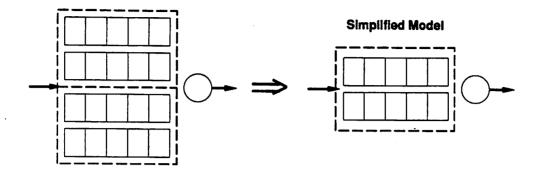

| 4.18 | Multiple Virtual Channels Approximated as One                              | 108 |

| 4.19 | Simplified Model of Direct k-ary n-cube Under Uniform Load                 | 110 |

| 4.20 | Simplified Model of a Delta Network Under Uniform Load                     | 111 |

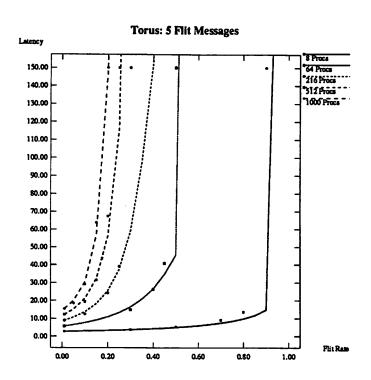

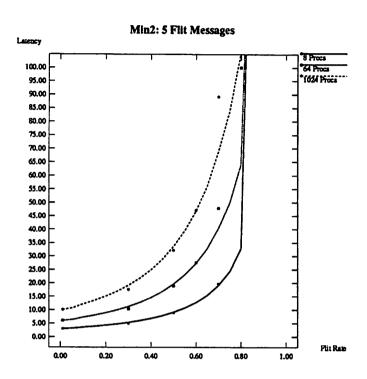

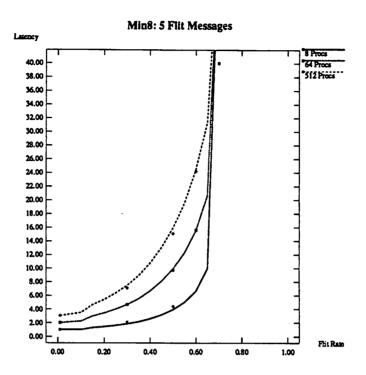

| 4.21 | 3-D Torus Network Performance (5 Flits/Packet)                             | 112 |

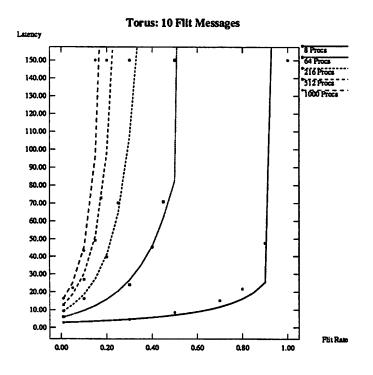

|      | 3-D Torus Network Performance (10 Flits/Packet)                            | 112 |

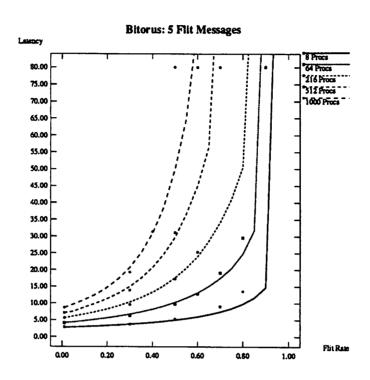

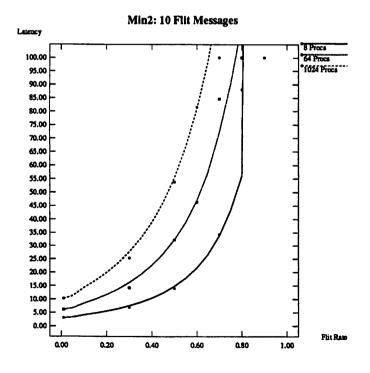

| 4.23 | 3-D Bidirectional Torus Network Performance (5 Flits/Packet)               | 113 |

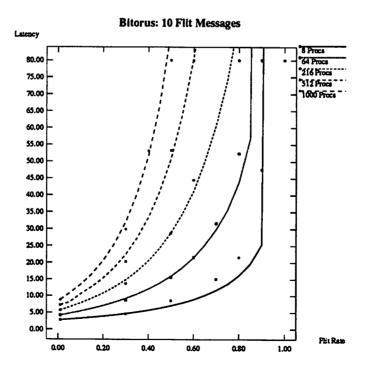

|      | 3-D Bidirectional Torus Network Performance (10 Flits/Packet)              | 113 |

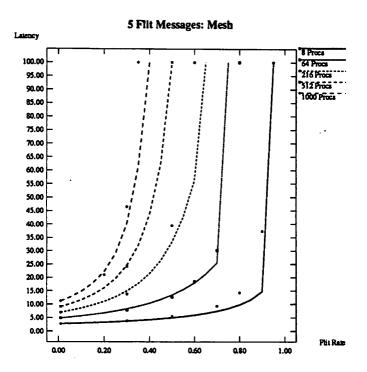

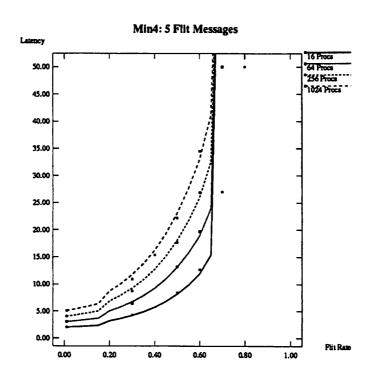

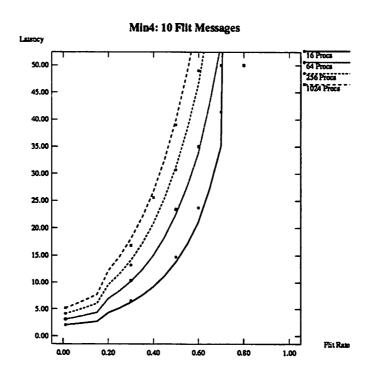

|      | 3-D Mesh Network Performance (5 Flits/Packet)                              | 114 |

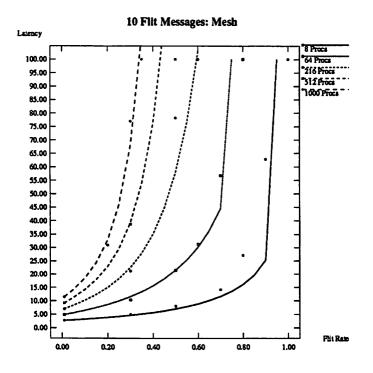

|      | 3-D Mesh Network Performance (10 Flits/Packet)                             | 114 |

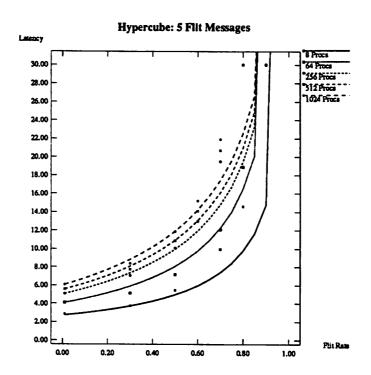

| 4.27 | Hypercube Network Performance (5 Flits/Packet)                             | 115 |

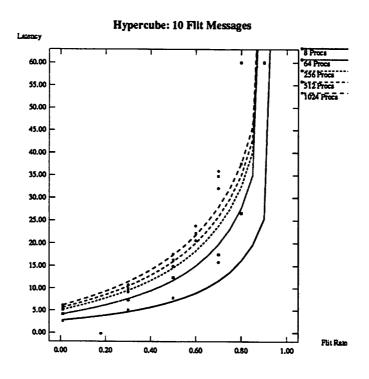

|      | Hypercube Network Performance (10 Flits/Packet)                            | 115 |

|      | Radix-2 Delta Network Performance (5 Flits/Packet)                         | 116 |

|      | Radix-2 Delta Network Performance (10 Flits/Packet)                        | 116 |

|      | Radix-4 Delta Network Performance (5 Flits/Packet)                         | 117 |

|      | Radix-4 Delta Network Performance (10 Flits/Packet)                        | 117 |

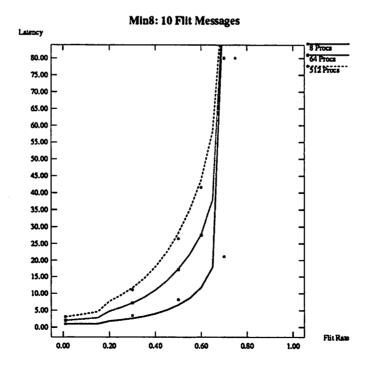

|      | Radix-8 Delta Network Performance (5 Flits/Packet)                         | 118 |

|      | Radix-8 Delta Network Performance (10 Flits/Packet)                        | 118 |

|      | Algorithm for Estimating Processor Utilization with Non-Zero Network Delay | 120 |

|      |                                                                            | 140 |

| 5.1 | Example of a Multiprefix Operation                       | 128 |

|-----|----------------------------------------------------------|-----|

| 5.2 | Pseudo-code for Combining Barrier Algorithm              | 133 |

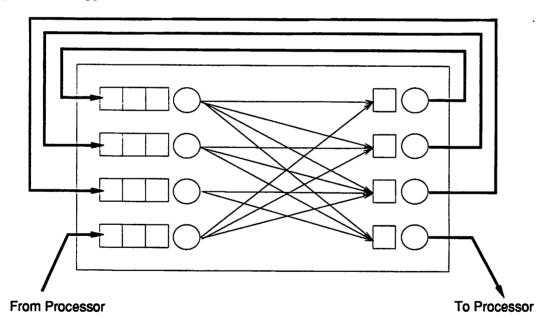

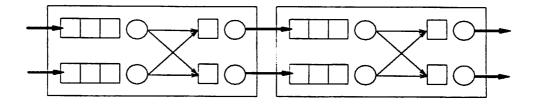

| 5.3 | Combining Switch Architecture                            |     |

| 5.4 | Combining Table Architecture                             |     |

| 5.5 |                                                          |     |

| 5.6 |                                                          |     |

| 5.7 | Software Combining Algorithm: Interrupt Handler for Root |     |

| B.1 | Queueing Model of a Unidirectional 3-D Torus Network     | 176 |

|     | Queueing Model of a Bidirectional 3-D Torus Network      |     |

|     | Queueing Model of a Hypercube Network                    |     |

|     | Queueing Model of Radix-2 Delta Network                  |     |

|     | Queueing Model of Radix-4 Delta Network                  |     |

| B.6 | Queueing Model of Radix-8 Delta Network                  | 184 |

## **List of Tables**

| 1.1        | Analytic Models                                       | 4  |

|------------|-------------------------------------------------------|----|

| 1.2        | Analytic Models (continued)                           | 5  |

| 3.1        |                                                       | 27 |

| 3.2        | Trace-driven Multiprocessor Cache Studies (continued) | 28 |

| 3.3        |                                                       | 29 |

| 3.4        | MOESI Cache Responses to Processor Requests           | 37 |

| 3.5        | MOESI Cache Responses to Network Requests             | 38 |

| 3.6        |                                                       | 39 |

| 3.7        |                                                       | 39 |

| 3.8        | Transaction Types                                     | 3  |

| 3.9        | Transaction Formats                                   | 3  |

| 3.10       |                                                       | 5  |

| 3.11       |                                                       | 6  |

| 4.1        | Published Network Performance Studies                 | 33 |

| 4.2        | Published Network Performance Studies (continued)     | 34 |

| 4.3        | Processor Utilizations for VERF, 4 Byte Path          | 22 |

| 4.4        | Estimated Traffic Increases for Large Multiprocessors | 23 |

| B.1        | Routing Parameters for 3-D Torus                      | 16 |

| <b>B.2</b> | Routing Parameters for Bidirectional 3-D Torus        | 78 |

| <b>B.3</b> | Routing Parameters for a Hypercube                    |    |

| D A        | Pouting Personatery for a Humorouha (continued)       |    |

## Chapter 1

## Introduction

#### 1.1 The Goal: Cost-Effective Acceleration of Engineering Applications

In this dissertation techniques are described for the design and evaluation of directory-based cache coherence schemes for large, shared memory multiprocessors. "Large" here implies a machine composed of several hundred uniprocessors, each with the power of a state-of-the-art workstation. The main goal is to show that directory-based coherence strategies are feasible and desirable for machines of this scale, and that their implementation complexity is modest.

Although impressive gains continue to be made in uniprocessor performance, multiprocessors remain an important research area for many reasons. One reason is that faster computers enable new problems to be solved and more design options to be explored. Another reason is that the computing requirements of many engineering problems continue to grow at least as fast as the number of compute cycles that become available. As an example, advances in integrated circuit densities demand computer aided design (CAD) tools that support design problems that grow at the same rate as uniprocessor MIPS ratings. Faster CAD programs also reduce the time to get a product to market, which is crucial for many products.

In this chapter, the state of multiprocessor design is reviewed, with a focus on open problems in scalable cache coherence. It begins with a broad review of the main components of a multiprocessor system: programming paradigms and architectures. The review shows why shared memory is a desirable architectural abstraction for a variety of programming models. Unfortunately, ideal shared memories with unlimited concurrent access must be approximated using collections of single-ported memories interconnected by a network. It is therefore attractive to provide a cache memory at each processor to avoid costly data transfers across the network. If multiple cached copies of shared-writeable data are permitted, some mechanism must ensure that the processors see a coherent view of memory: this is the cache coherence problem. An introduction to multiprocessor cache coherence is provided in Section 1.3, with an emphasis on issues that are not well understood. The specific problems addressed in this work are listed in the final section, along with a summary of the contributions and an outline of the dissertation.

#### 1.2 Multiprocessor Systems

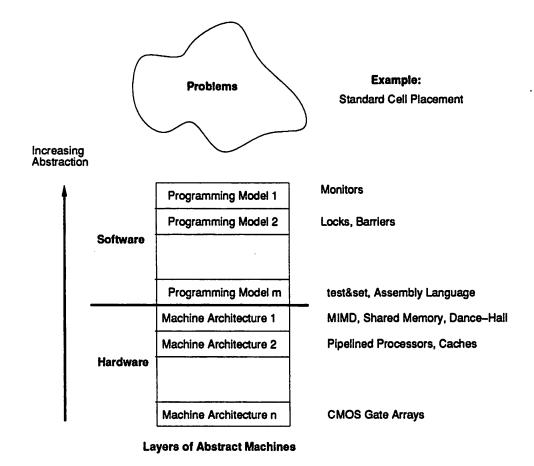

A multiprocessor system is a layered set of abstract machines, with higher level abstractions layered above lower level abstractions (Figure 1.1). The highest level abstractions are im-

Figure 1.1: Components of a Multiprocessor System

plemented in software, and provide programming models with which a programmer can solve a problem. The lower levels are hardware implementations of more primitive parallel machines; the

topmost architecture furnishes a platform on which higher level programming models are built. A typical set of layers would be a monitor-based programming language [AS83] implemented on a cache-coherent "dance-hall" architecture (processors and memories on opposite sides of a multistage network) implemented in CMOS using pipelined network elements. The role of a multiprocessor architect is to devise machine architectures that are sufficiently abstract to simplify implementation of the software layers, and sufficiently simple to permit a fast, cost-effective implementation. The state of multiprocessor design is reviewed in this section by examining programming paradigms and machine architectures in greater detail. The purpose of the review is to show that cache coherent, shared memory architectures make good platforms for implementing a wide variety of programming models.

#### 1.2.1 Programming Paradigms

Good programming paradigms simplify the task of writing parallel programs. The broad variety of computational problems has resulted in a broad variety of programming paradigms, including: functional and logic programming, data-parallel programming, parallel loops, shared memory, and message passing [AS83, BST89, CG89, Hud89, Sha89].

The functional and logic programming models belong to the larger class of declarative programming models, in which computations are described solely via single assignment expressions [Hud89]. Functional languages are based on function application, while logic programs are composed of relations. Prohibiting multiple assignments to variables is equivalent to prohibiting side effects, which makes declarative languages suitable for formal analysis. It also fosters a programming style that exposes more parallelism than imperative languages. In spite of these advantages the use of declarative languages has been minimal. This has been due to the lack of good compilers and the fact that these languages make a significant departure from traditional imperative languages. Recent improvements in compilation techniques and attempts at standardizing a general purpose functional language (Haskell [HW88]) may result in greater interest in this class of language in the future. Declarative programming models are the most abstract in that all notions of a multiprocessor implementation–multiple processes running on distinct processors, an interconnection network, distributed memory–are completely avoided.

In the data parallel (or collection-oriented [SB91]) model, parallelism is expressed as the application of operations to large collections of data. For example, an addition operation could be applied to a collection of pairs of numbers to add two vectors, or it could be applied in tree fashion

to find the sum of a list of numbers. This computational model is surprisingly useful given its simplicity, and is common in many languages for massively parallel computers [SB91]. Collection-oriented constructs are typically embedded in existing languages such as C, FORTRAN, and Lisp. They are also a natural component of functional languages. Like the declarative model, data-parallel programming models abstract the most cumbersome implementation issues. The implementation of multiple processes on distinct processors is usually abstracted in a more restrictive way, however, by assuming a single flow of control (single instruction stream, multiple data stream (SIMD)).

Parallel loops is a programming paradigm that is often used in parallelizing scientific applications (usually written in FORTRAN) [D+88, A+88b]. In this model, loops with few dependencies among iterations are distributed among multiple processors for parallel execution. Typically, most or all of the parallelization is performed automatically, so the notions of multiple processes, interprocess communication, and distributed memory are abstracted.

The shared memory programming model provides the programmer with a set of processes that can issue reads and writes to a globally shared memory, such that any number of reads and writes to distinct addresses can be performed simultaneously [May90]. Variations in the way in which simultaneous reads and writes to the same address are resolved create a family of shared memory models. In the most restrictive model, exclusive read/exclusive write (EREW), simultaneous accesses to the same address are not allowed. In the least restrictive model, concurrent read/concurrent write (CRCW), the accesses are performed simultaneously, with the effect of the writes being the same as if they were serialized. Basic read and write primitives can be augmented with more sophisticated access instructions such as fetch&op [KRS86]. A fetch&op instruction with target address addr and value v causes the contents of addr, say x, to be replaced with x op v, and returns x. Simultaneous fetch&op instructions with the same target address are satisfied concurrently, with the results corresponding to some arbitrary serialization. Concurrent fetch&op instructions can be viewed as performing a data parallel operation in which a collection of numbers, the v's, are operated on and all partial results are collected. The shared memory model abstracts the implementation of a physical multiprocessor memory. Unlike the preceding programming models, multiple interacting processes are an explicit part of the shared memory paradigm.

The *message passing* programming model [Hoa78] is the least abstract model because it makes explicit the notion of a collection of distinct processes operating on distinct, distributed memories and interacting through a network. Like the data-parallel and shared memory models, message passing primitives are usually embedded in traditional imperative languages.

#### 1.2.2 Architectures

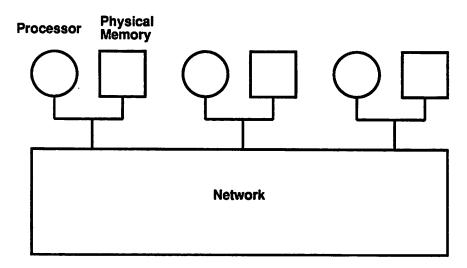

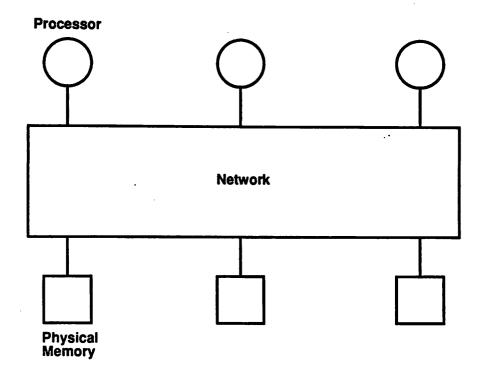

At some level a programming model must be implemented on an abstract machine supported directly in hardware. Virtually all hardware architectures share the basic structure of Figure 1.2 or Figure 1.3: collections of serial processing elements and memories interconnected by a network. The most basic programming model supported by this hardware is the message passing model, in which processes running on different processing elements communicate by messages through the network. This basic architecture can be augmented with additional hardware to support higher level programming abstractions. Shared memory can be approximated with hardware that maps a global shared address space onto multiple physical memories. Data parallel computation can be supported by forcing all processing elements to execute a single instruction stream in lock-step [Hil85]. Data flow computation can be supported by adding complex associative memories [AN87, GKW85].

Figure 1.2: Basic Multiprocessor Organization: Distributed Main Memory

Since a particular programming paradigm is best-suited to a particular class of problem, it is desirable to support as many paradigms as possible on a single architecture. Very specialized hardware, however, is often useful for only a single programming model. The most obvious example is the complex hardware provided in traditional data flow computers. Data parallel architectures like the Connection Machine are an extreme example in which the hardware supports only a single instruction stream.

Specialized hardware is often not necessary for good performance. There is growing evidence that higher level programming models can be efficiently emulated on much simpler architec-

Figure 1.3: Basic Multiprocessor Organization: "Dance-Hall" Arrangement

tures. For example, reasonably efficient techniques have been published for compiling functional, logic programming, data parallel, and parallel loop computations onto shared memory and, in some cases, message passing architectures [Hud89, Sha89, SB91, H+91, D+88]. The Monsoon data-flow architecture is an interesting attempt to support data-flow computation at a much lower level than previous generation data-flow architectures (MIT Tagged Token Machine and Manchester Data-Flow Machine). Instead of providing complex token matching hardware, Monsoon efficiently supports a multithreaded abstract machine in which conventional uniprocessors are augmented with hardware to permit efficient context switches of very lightweight processes (or threads). Recent work suggests that even this may not be necessary [C+91].

It therefore seems unnecessary to go far beyond a shared memory or message passing architecture to support a broad variety of programming models. There are good reasons, however, to provide hardware support for shared memory. One is that the shared memory *programming model* is much less cumbersome than message passing for many applications. This includes the implementation of operating systems, debuggers, and higher level programming models. Another reason is that emulating shared memory on a message passing architecture has a high cost that cannot be avoided without hardware support. This is because multiple emulation instructions must be used

for each shared access in the shared memory program, and many shared memory programs issue frequent shared accesses [DR<sup>+</sup>87, EK88]. Furthermore, shared memory programs exhibiting good speedups (or, equivalently, high processor utilization) have few free cycles available for emulation.

There are many open research issues concerning the design of a shared memory for hundreds or thousands of processors. One of the most important is the provision of cache memories at each processor. A cache at each processor permits many memory accesses to be satisfied locally by buffering data as it is referenced. Unlike uniprocessor systems, however, a multiprocessor with caches requires a mechanism to ensure that multiple cached copies of the same data remain coherent. The design and evaluation of a particular class of coherence schemes is the topic of this dissertation. The following section reviews previous work in cache coherence in greater detail.

#### 1.3 Multiprocessor Cache Coherence

There are numerous ways to ensure that multiple cached copies of data are consistent. In fact, there are numerous ways in which the notion of "coherent" can be interpreted. The most common interpretations are presented in the following section. Techniques for enforcing these coherence standards are reviewed in Section 1.3.2. The final part of this section summarizes previous work in evaluating multiprocessor cache performance. The discussions in these sections identify problems in directory-based cache coherence that are addressed in this dissertation.

#### 1.3.1 Formal Notions of Cache Coherence

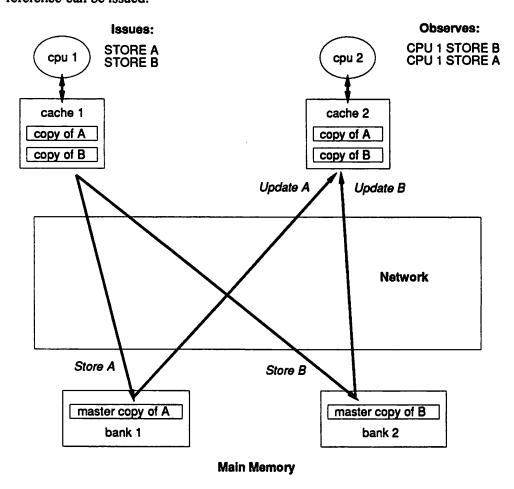

A set of multiprocessor caches is often defined to be coherent if the value returned on a LOAD instruction is always the value written by the latest STORE instruction with the same address [CF78]. This definition is unsatisfactory for two reasons. First, it is ambiguous with respect to the temporal occurrence of LOAD's and STORE's. When is a LOAD or a STORE determined to have taken place: when initiated by a processor, processed by a cache controller, or propagated to all cached copies? The second reason is that the definition is based on a notion of processors issuing and completing shared references in lock-step. This is overly restrictive because it requires all processors to observe the same interleaving of all references from all processors. This restrictiveness severely reduces the amount of pipelining and reordering that can be applied to shared references, with a subsequent loss in performance. To illustrate this, consider a processor that issues STORE A followed by STORE B (cpu 1 in Figure 1.4). Assume that STORE's are considered complete

once they have been propagated to all copies. If the addressed memory locations reside in different memory banks on the other side of a complex network, they may be propagated to copies out of order if STORE A is delayed. If this occurs, it is possible for another processor to observe STORE A before the STORE B, which violates the definition. The most straightforward implementation of this definition, then, requires each processor reference to be completed at the main memory before a new reference can be issued.

Figure 1.4: The Restrictiveness of Strong Ordering

The above definition of coherence is closely related to Lamport's sequential consistency. A multiprocessor is sequentially consistent if "the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in the order specified by its program [Lam79]." The simplest way to implement sequential consistency is that described above, in which each processor issues LOAD's and STORE's in program order and ensures that all copies are updated (or invalidated) for each

reference before issuing the next [SD87]. Accesses in a multiprocessor that satisfy these restrictions are said to be *strongly ordered*. More complex implementations of sequential consistency have been proposed [AH90, A+89], but it is unclear whether significant improvements in performance are possible.

The restrictiveness of sequential consistency can be relaxed by using a weaker notion of coherence that exploits some knowledge about how synchronization is performed in the programming paradigms of interest. These weaker notions of coherency are, in decreasing restrictiveness:

- 1. processor consistency

- 2. weak consistency

- 3. release consistency

A multiprocessor is *processor consistent* if "the result of any execution is the same as if the operations of each individual processor appear in the sequential order specified by its program [Goo89]." This relaxes the requirement of strong ordering that the same *interleaving* of all processor references is observed by all processors. It exploits the fact most synchronization algorithms designed using sequential consistency still perform correctly under processor consistency. Programs can be constructed, however, that behave differently under sequential and processor consistency.

A multiprocessor is weakly consistent if [D+86]:

- 1. accesses to global synchronizing variables are strongly ordered;

- 2. no access to a synchronizing variable is issued in a processor before all previous global data accesses have been performed;

- 3. no access to global data is issued by a processor before a previous access to a synchronizing variable has been performed.

Synchronizing variables are variables that are used in synchronization operations, such as locks, barriers, test-and-set, and fetch-and-add. Weak consistency exploits the fact that most parallel programs do not perform synchronization using LOAD and STORE accesses to the shared memory, but use special synchronization primitives corresponding to the operations just listed. Access to mutually exclusive data can only be acquired by references to synchronization variables, so intervening references can be pipelined as long as they are not initiated until the last synchronization access completes, and as long as they are completed before the next synchronization access is initiated.

Release consistency is an optimization of weak consistency requiring a further classification of synchronization accesses into acquire accesses and release accesses. These are described in [GGH91] as follows:

An acquire synchronization access (e.g., a lock operation or a process spinning for a flag to be set) is performed to gain access to a set of shared locations. A release synchronization access (e.g., an unlock operation or a process setting a flag) grants this permission.

With this differentiation, it is not necessary to impose Condition 2 of weak consistency on an acquire, or Condition 3 on a release.

The relative performance of these consistency models was examined in [GGH91] using simulations of three parallel applications on a small number of processors (16). The study showed that all three weak consistency models provide substantial benefits over a strongly ordered system. Weak consistency and release consistency performed similarly, and provided performance only marginally better than processor consistency. These results are intuitive for weak and release consistency since synchronization references tend to be infrequent, so the time spent waiting for outstanding accesses to complete at synchronization points should be minimal.

#### 1.3.2 Cache Coherence Strategies

In the previous section several definitions of coherence were described. In this section strategies for enforcing these standards are presented. The strategies fall into three classes:

- 1. software methods;

- 2. snooping bus protocols;

- 3. directory methods;

In software methods, a compiler manages the cache using special cache control instructions. The simplest class of software methods requires a programmer to explicitly identify shared-writeable data so that it will not be cached. The penalty for this simplicity is a significant increase in average memory access time and network traffic [ON90]. More sophisticated software methods use compile-time analysis to identify certain parallel programming constructs and insert cache management instructions. Typical instructions include cache-flush, selective invalidation, cache-bypass, and main memory update. Two types of programming construct are typically recognized: critical sections [Smi85] and parallel loops [CV90].

In critical section schemes, the compiler ensures that all data modified within a critical section is reflected in main memory when the critical section is left. This is typically done with cache invalidation or update instructions at every point where a process leaves a critical section. If invalidations are used, all modified cache blocks are written back to main memory.

Most work on software methods has focussed on parallel DO-loops, usually in the context of parallelizing FORTRAN compilers [CV90]. These schemes are similar to the critical section technique described above, except that coherence instructions are placed at the end of loops. The best loop and critical section schemes use sophisticated compiler analysis to perform selective invalidation [CV88, CKM88].

Software schemes have the advantage of requiring minimal hardware support. This is offset by the disadvantages of known techniques. The most significant is that many engineering applications are not easily coded in a FORTRAN-like programming model because they make extensive use of pointer-based data structures; for these applications parallelized loops are not applicable. The critical section schemes are more suitable, but they must be very conservative to deal with arbitrary pointer use. Furthermore, some of the more sophisticated software methods require substantial hardware support for selective invalidation [CV90]. Unfortunately, relatively little is known about the relative performance of software and hardware coherence techniques. Some comparisons have been reported in [OA89, MB90], but all of these focus on parallelized loops.

Snooping bus protocols exploit the broadcast capability of a shared bus, which enables each cache to efficiently monitor and disseminate shared access information. Many snooping bus protocols have been proposed and implemented; a good summary is in [AB86]. Unfortunately, the number of high performance processors that can reside on a bus is limited. Attempts have been made to extend snooping bus protocols to larger numbers of processors using collections of busses interconnected in hierarchies [Wil87, MA89, T+90], and multidimensional meshes [GW88]. These extensions have the disadvantages that they are network-specific and rely on broadcasting for some steps in their protocol. Some are also extremely complex. No results have been published comparing the performance of extended snooping bus schemes with alternative coherence strategies.

Directory-based coherence protocols rely on a (conceptually) centralized set of "book-keeping" information, the directory, which maintains the status of all cached shared-writeable data. The directory maintains for each block of main memory a list of the caches with copies. Cache accesses that affect directory state and/or other caches are required to consult the directory to ensure that the directory and other cached copies remain consistent.

One of the earliest directory schemes, due to Censier and Feautrier [CF78], implemented the copy lists using bit vectors. With this organization, the directory can be interleaved with the main memory to get sufficient bandwidth. The main disadvantage of this scheme is the high cost of implementing bit vectors at each main memory block for a large number of processors. Several techniques for reducing the overhead have been proposed. Archibald and Baer [AB84] suggest the use of only a single cache identifier per main memory block, and the use of broadcasts when more than a single copy is required. Agarwal et. al. [A+88a] generalize this to their  $Dir_iB$  and  $Dir_iNB$  schemes. In a  $Dir_iB$  scheme, i cache identifiers are provided for each block, and broadcasting is used when the number of copies exceeds i. The  $Dir_iNB$  scheme is similar to  $Dir_iB$ , except that instead of resorting to broadcasting, identifier memory is "recycled" by invalidating older copies. A number of techniques have recently been proposed for reducing directory overhead without the performance penalties of the  $Dir_iB$  and  $Dir_iNB$  schemes. These techniques, including one developed as part of this research, are described in Chapter 2.

Directory methods are attractive because they apply to a broad class of interconnection network, are conceptually straightforward, and do not require broadcasts. The main disadvantage of early directory methods, efficient implementation of the directory, can now be overcome with the techniques described in Chapter 2. A secondary disadvantage of directory schemes is that a directory controller can become a bottleneck if many copies of a block must be invalidated or updated on a shared write. There is a growing amount of empirical evidence, however, to suggest that this is not a problem in practice [WG89a, ON90, C+90, SWG91]. Results in Chapter 3 confirm this.

#### 1.3.3 Performance Evaluation of Cache Coherence Strategies

A cache coherence strategy is effective only if its overhead does not outweigh its benefit. Overhead in coherence schemes takes the form of extra network traffic, stolen cache cycles, stolen main memory cycles, and extra cache misses due to invalidations. The overhead of competing schemes can be estimated with several performance evaluation techniques: analytic models, simulation with synthetic workloads, and trace driven simulation.

Analytic models are desirable because of their simplicity, reduced computational requirements, and the insight they provide. Most analytic models of multiprocessor caches take a relatively small number of parameters representing the workload and simulated architecture, and produce estimates of maximum speedup and the frequencies of various coherence operations. Typical workload

parameters include miss ratios for shared and local data, the fraction of references to shared data, the fraction of writes to shared data, and the average number of copies of shared data. Common architectural parameters include network path width, cache block size, and memory latencies. The structure of most analytic models is as follows:

- 1. Estimate the relative frequency of various network transactions (messages that are issued by a processor into the interconnection network).

- 2. Estimate the arrival rate of network traffic by assuming some network delay.

- 3. Use the arrival rates to estimate the actual network delay with some congestion model.

- 4. If the estimated network delay does not match the assumed network delay, return to Step 2, and repeat the process until convergence is reached.

The main differences in models are in the number of workload and architectural parameters, the algorithm used to estimate the frequency of transactions in Step 1, and the congestion model in Step 3. Tables 1.1 and 1.2 categorize some published analytic models according to these criteria.

There are several common techniques for estimating the frequency of various network transactions. The simplest is to simply guess some values, or derive them algebraically from more fundamental parameters. Another technique is to construct a stochastic model of program behavior and either solve it directly or simulate it. Both of these methods must be validated against real programs to verify their accuracy. The most common way to do this is trace-driven simulation. Traces can be acquired during an execution of a program on a particular parallel machine, or they can be generated during the cache simulation by simulating the processors.

There are many ways to estimate network congestion. The simplest is to use a known model for the network of interest. Published network models that could be used here are reviewed in Chapter 4. Unfortunately, most known models do not account for several important behavioral features. Network congestion can also be estimated with an "application specific" model. These are usually constructed as a network of queues or a stochastic Petri net, both of which can be solved using standard techniques [ABC86]. A third way to estimate network congestion is by simulation.

As the tables show, only a few models have been validated against real parallel programs. It is difficult to make believable cache design choices using models that have not been validated against real parallel programs, so most models in Tables 1.1 and 1.2 are of limited use. In particular, recent cache studies using reference traces from real parallel programs indicate that most early

Table 1.1: Analytic Models

| Model               | Network <sup>a</sup>            | Determination of<br>Transaction<br>Frequency | Congestion Model                            | Notes                                                                    |

|---------------------|---------------------------------|----------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------|

| [V <sup>+</sup> 88] | bus                             | algebraic                                    | closed queueing network (MVA <sup>b</sup> ) | block on write,<br>continuous time,<br>not validated<br>with traces      |

| [VJS89]             | hierarchical<br>bus             | algebraic                                    | closed queueing<br>network (MVA)            | block on write,<br>continuous time,<br>not validated<br>with traces      |

| [VH86]              | bus                             | algebraic                                    | generalized timed Petri nets                | block on write, continuous time, not validated with traces               |

| [LV88a]             | multicube                       | algebraic                                    | closed queueing<br>network (MVA)            | continuous time,<br>not validated<br>with traces                         |

| [NP85]              | multistage                      | algebraic                                    | Kruskal/Snir<br>[KS83],<br>simulation       | RP3 model [P+85],<br>software coherence,<br>not validated<br>with traces |

| [OA89]              | multistage,<br>bus,<br>crossbar | algebraic                                    | open and closed<br>queueing networks        | continuous time, validation against 4 cpu traces                         |

<sup>&</sup>lt;sup>a</sup>N/A means not applicable. <sup>b</sup>MVA denotes Mean Value Analysis [ABC86].

Table 1.2: Analytic Models (continued)

| Model               | Network <sup>a</sup>                  | Determination of<br>Transaction<br>Frequency | Congestion Model                                            | Notes                                              |

|---------------------|---------------------------------------|----------------------------------------------|-------------------------------------------------------------|----------------------------------------------------|

| [Dub85]             | N/A                                   | algebraic                                    | N/A                                                         | not validated with traces                          |

| [DB82]              | N/A                                   | Markov chain                                 | N/A                                                         | not validated with traces                          |

| [YBL89]             | packet-switched<br>bus                | Markov chain                                 | open and closed<br>queueing networks<br>(MVA <sup>b</sup> ) | not validated<br>with traces                       |

| [YF82]              | non-blocking                          | algebraic                                    | open and closed<br>queueing networks<br>(custom solution)   | not validated<br>with traces,<br>block on write    |

| [Pat82]             | circuit switched<br>delta or crossbar | algebraic                                    | known models                                                | not validated<br>with traces,<br>ignores coherence |

| [BD81]              | crossbar                              | algebraic                                    | closed queueing<br>network<br>(custom solution)             | not validated<br>with traces                       |

| [PP84]              | bus                                   | algebraic                                    | customized<br>bus model                                     | not validated with traces                          |

| [A <sup>+</sup> 85] | bus                                   | algebraic                                    | stochastic<br>Petri nets                                    | not validated with traces, continuous time         |

| [AB86]              | N/A                                   | simulation of synthetic workload             | N/A                                                         | not validated<br>with traces                       |

<sup>&</sup>lt;sup>a</sup>N/A means not applicable. <sup>b</sup>MVA denotes Mean Value Analysis [ABC86].

cache models were overly pessimistic in their assumptions about reference locality and contention for shared data [EK88].

Calibration with real programs can take place at Step 1 as described above, or can be applied to the entire modeling process with detailed simulations of the entire multiprocessor. As mentioned, the most common technique for validating models is trace-driven simulation. A detailed comparison of trace-driven multiprocessor studies is deferred to Chapter 3. The comparison shows, however, that most studies on directory-based coherence focus on invalidation protocols, most consider relatively small numbers of processors (32 or fewer), and few consider the impact of alternative interconnection networks. There is a need to investigate different directory protocols and a wider variety of interconnection networks. There is also a need to consider machines with larger numbers of processors. One of the reasons existing work has had a narrow focus is the high cost of detailed multiprocessor simulation. More efficient techniques are needed to reduce this cost.

#### 1.4 Organization of the Dissertation

This dissertation builds upon existing work on directory-based cache coherence by developing more efficient techniques for performance evaluation and by applying them to a broader class of architectures. The overall performance methodology is based on that described in Section 1.3.3, in which the workload is characterized and iteratively applied to a network model. The dissertation is organized as follows.

In Chapter 2 a more detailed description of cache coherence strategies is provided. The strategies are suitable for multiprocessors with hundreds of processing elements, with a focus on simple and efficient directory-based techniques. A new efficient directory implementation is introduced.

A trace-driven analysis of directory-based coherence schemes is presented in Chapter 3. An efficient stack simulation technique is used that permits multiple cache sizes to be evaluated in a single simulation run. Quantitative data for invalidation, update and competitive directory protocols are presented. In addition, a new technique is introduced that permits efficient evaluation of a spectrum of competitive protocols. These techniques are applied to three benchmark programs for several cache, block and multiprocessor sizes.

The results in Chapter 3 are obtained under the assumption of zero miss penalty. The impact of non-zero miss penalties are considered in Chapter 4, which presents a comparison of a broad class of interconnection network. The comparison is based on new, efficient analytic models.

The results in Chapter 3 are obtained with the additional assumption of ideal synchronization support for locks and barriers. This assumption is justified in Chapter 5, in which known synchronization techniques are reviewed. Several new techniques are presented for the implementation of fetch&op and barrier primitives in a broad class of interconnection network.

Chapter 6 concludes with a summary of important results and a discussion of future research issues.

#### 1.5 Contributions

The contributions of this work are:

- A detailed study of directory-based cache coherence schemes using execution driven simulation of several benchmark programs. This study provides quantitative comparison data for update, invalidation, and competitive directory protocols. An efficient stack simulation technique is used that permits data for multiple cache sizes to be obtained in one simulation run. Efficient ways of storing a global directory are developed and compared using new and previously published results.

- 2. Efficient analytic models for evaluating a broad class of packet-switched interconnection networks. The class includes hypercubes, indirect binary cubes, meshes, and k-ary n-cubes. The techniques are used to compare the most promising interconnection networks using workload data obtained from the cache study in 1.

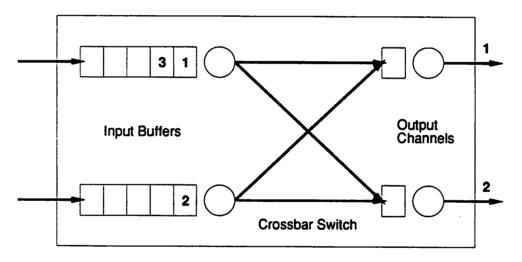

- 3. An implementation technique for incorporating fetch&op primitives in the kxk cross-bar switches used to build meshes, Delta networks, k-ary n-cubes, and many other networks.

## Chapter 2

# **Directory-based Cache Coherence Strategies**

#### 2.1 Overview

This chapter is a review of directory-based coherence schemes that are suitable for machines with hundreds or thousands of processors. It begins with a detailed description of the Censier and Feautrier directory scheme, from which most of the other schemes are derived. As mentioned in the introduction, the main weakness of this scheme is the excessive amount of memory required to implement the directory. A secondary weakness is that directory controllers may be locked out for long periods of time when large numbers of invalidations or updates must be issued. All of the schemes described in this chapter overcome the first weakness, and a few attempt to overcome the second. One of the refined schemes is a contribution of this dissertation.

The goal of the chapter is to show that hardware coherence techniques exist that are of reasonable complexity and require a reasonable amount of hardware for implementation. The contribution of this chapter is the "tag cache" directory implementation.

## 2.2 The Censier and Feautrier Directory Scheme

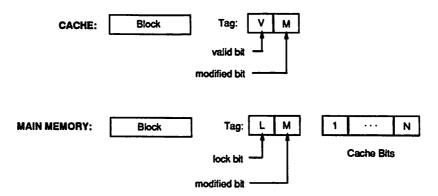

In this scheme physical memory is divided into blocks of fixed size. Each block of main memory is associated with a directory entry (or tag) containing N presence bits where N is the number of processors in the system, a single bit indicating whether or not the block is modified, and a lock bit (Figure 2.1). The bit vector implement a list of all cached copies. Using the notation

Figure 2.1: Tags for Basic Censier and Feautrier Protocol

of [AB84], a block is always in one of these three states:

- 1. ABSENT: no cache holds a copy (all cache bits in the directory entry are 0, and the modified bit is 0; lock bit is 0);

- 2. PRESENT: one or more caches hold copies, and the block is unmodified (one or more cache bits in the directory entry are 1, and the modified bit is 0; lock bit is 0);

- 3. PRESENTM: exactly one cache has a copy and it is modified (exactly one cache bit is 1 and modified bit is 1; lock bit is 0);

- 4. LOCKED: an operation on this block is currently in progress (lock bit is 1);

In like manner, each cache block is associated with a cache directory entry consisting of a valid bit and a modified bit (Figure 2.1). Cache blocks may be in one of these states:

- 1. INVALID: the contents of the cache block are invalid (valid bit is 0);

- 2. VALID: the contents of the cache block are valid and unmodified (valid bit is 1 and modified bit is 0):

- 3. VALIDM: the contents of the cache block are valid and modified (valid bit is 1 and modified bit is 1). This state implies that this cache has the only valid copy of the block in the entire multiprocessor.

The coherence protocol is defined by the actions taken by cache and memory controllers for each combination of processor request, cache block state, and main memory state. If a processor issues a read and the local cache block of the data is valid, no main memory access is needed and

the data is read from the cache. If a block for the referenced data does not exist, a block must be assigned and its old data displaced to main memory. The missed reference is then handled as if the block was invalid: a read transaction is issued to the main memory. If the main memory block is in an unmodified state, the block contents are returned to the requesting memory controller. If the main memory block is modified, the block contents are read from the single "owning" cache, written to main memory, and forwarded to the requester. In all of these cases the cache and main memory entries have their states updated to VALID and PRESENT, respectively.

When a processor issues a write, it can only be satisfied locally if the local cache block is VALIDM. If the local cache state is VALID, an invalidate transaction is sent to the main memory which, if other caches have copies (ie: main memory state is PRESENT or PRESENTM), issues invalidations to them. If the local cache misses or the block is invalid, the controller issues an invalidate-fetch transaction to the main memory. A fetch is required here so that the portion of the block untouched by the write is made valid. The main memory sends invalidations to caches with copies. If the block is modified, the main memory also fetches the current data, updates itself, and forwards the data to the requester. The states of cache and main memory blocks are updated to VALIDM and PRESENTM, respectively.

The main memory is always notified of block replacements so that the appropriate cache bit is cleared. If a cache replaces a VALIDM block, the block must be written back and the main memory state changed to ABSENT.

The Censier and Feautrier scheme is well-suited to large multiprocessors because it does not depend on the use of broadcasts (and hence does not depend on a particular network), and permits the main memory and its directory to be interleaved. Although the communication overhead could be excessive if many blocks reside in many caches, the scheme's greatest drawback is the severe memory overhead introduced by the large number of cache bits in the main memory tags. As an example, a system with 100 processors requires a 102 bit tag, dictating a block size in excess of 125 bytes for tag overhead to be less than 10%. Systems built using this consistency scheme are not easily expanded because the tag length is dependent on the number of processors.

## 2.3 Efficient Directory Implementations

The severe memory overhead of the basic Censier and Feautrier scheme can be overcome in many ways. The techniques fall into three categories:

- 1. Restrict the length of the copy lists.

- 2. Reduce the granularity of the copy lists: have each cache identifier refer to a group of caches rather than a single cache.

- 3. Use a hierarchical directory.

- 4. Store the copy lists per cache block rather than per main memory block.

#### 2.3.1 Schemes that Restrict List Length

It has been empirically observed for invalidation protocols that a small number of cache identifiers are sufficient most of the time [A+88a]. The most basic list reduction scheme exploits this by providing only a single cache identifier per main memory block. When more than a single copy is required broadcasts are used [AB84]. Agarwal et. al. generalize this to their  $Dir_iB$  and  $Dir_iNB$  schemes [A+88a]. In a  $Dir_iB$  scheme, i cache identifiers are provided for each block, and broadcasting is used when the number of copies exceeds i. The  $Dir_iNB$  scheme is similar to  $Dir_iB$ , except that instead of resorting to broadcasting, identifier memory is "recycled" by invalidating older copies. Although directory overhead is reduced, for small block sizes it is still considerable. For example, one ten bit cache identifier creates 7.8% overhead for a 16B block size. The performance of these schemes has been evaluated using trace-driven simulation in [C+90]. The results indicate that a full directory permits up to twice the processor utilization than a  $Dir_iNB$  scheme with  $i \le 4$ . This is largely because of contention for synchronization variables. With various software optimizations, the performance with limited identifiers comes within 10 % of a full directory scheme.

[CKA91] describes a variation of the above schemes called a *limitless* directory. A limitless directory is a  $Dir_iNB$  scheme modified so that directory overflows interrupt the local processor, which maintains long directory entries in local main memory.

#### 2.3.2 Schemes that Reduce List Granularity

Weber and Gupta propose the use of directory entries of a single size, but further reduce tag overhead with the use of *coarse vectors* and multicast invalidations [G+90b]. [BH89] describes a similar idea, and discusses a particular implementation of a multistage interconnection network that supports efficient multicast operations; this multicast optimization is similar to one proposed by Stenstrom [Ste89] for his decentralized linked list protocol (described in Section 2.3.3 below).

#### 2.3.3 Schemes that Store Lists Per Cache Block

Another way to reduce directory overhead is to exploit the fact that tags are needed to record the locations of only those blocks residing in caches. Since the total number of cache blocks is typically much smaller than the total number of main memory blocks, tag overhead can be greatly reduced. For example, a 64 processor machine with 32 kilobyte caches and 32 megabytes of distributed main memory requires only 1.6 megabytes of full length tags (assuming they are 100 bits in length), to store directory information for the  $64 \times 32K \div 16 = 128K$  cache blocks. Alternatively, 25 megabytes of full length tags are needed if one tag is provided per main memory block.

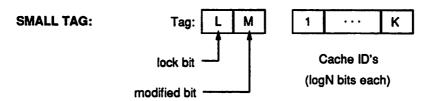

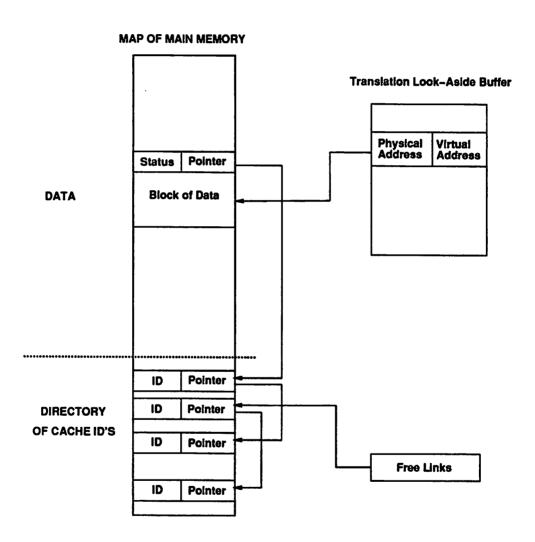

In one class of these schemes [ON90, LY90, Ste89] copy lists are stored in associative memories accessed by block address. The scheme described in [ON90] was proposed as part of this research. In this scheme, two *tag caches* of different tag sizes are provided at each bank of the distributed main memory: a large cache with small tags capable of holding the identifiers of a small number of cached copies (Figure 2.2), and a small cache with full-sized tags (Figure 2.1).

Figure 2.2: Small Tag Fields

The coherence protocol for this scheme is similar to the basic Censier and Feautrier protocol with the exception that tags must be allocated from a tag cache as needed; when no tags are free, a cached block must be invalidated and its tag re-allocated. When a block is first referenced, it is allocated a small tag. When the number of copies of a block exceed the number of copies supported by the small tags, a large tag is allocated and the small tag is freed. A least-recently-used (LRU) replacement strategy may be used to select tags for re-allocation.

Similar schemes were independently published in  $[G^+90b]$  and [Ste89]. In  $[G^+90b]$  a tag cache is called a *sparse directory*. Instead of using two tag sizes, the scheme in  $[G^+90b]$  uses copy lists with coarse granularity, as described in Section 2.3.2. The scheme described in [Ste89] differs from the other two in that full size directory tags are kept at the caches instead of the main memory. The main memory, however, stores a cache identifier with each block to point to the cache with valid directory data.

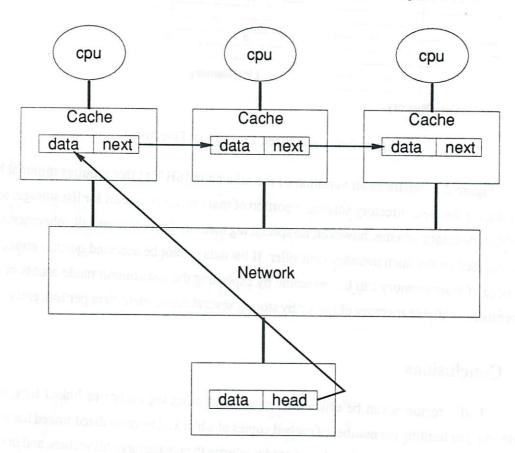

The complexity of storing lists as bit vectors in associative tables is greatly reduced by

using linked lists. These can be organized in a centralized or decentralized fashion. Decentralized linked list schemes include the Scalable Coherent Interface protocol [IEE90] and the Stanford linked list protocol [ $T^+90$ ]. In these schemes tag overhead is reduced by storing single identifier tags at the caches and maintaining copy information in distributed linked lists (Figure 2.3). As in the [Ste89] scheme, the main memory holds a pointer to the head of the copy list for each block. In the basic protocol, invalidations are performed by having each member of the list invalidate their copy and remove themselves from the list (at the main memory). This is done serially, so the time to perform j invalidations takes the time of 2j network transactions. In contrast, the centralized directory schemes issue invalidations serially at the controller, but they can traverse the network and be processed in parallel. Optional variations of the SCI protocol have been proposed to reduce serialization, but they require complicated checks to avoid dangling list segments.

Figure 2.3: Decentralized Linked List Directory

The performance problem of simple decentralized schemes and the complexity of higher performance decentralized linked list schemes can be overcome by centralizing the linked lists at

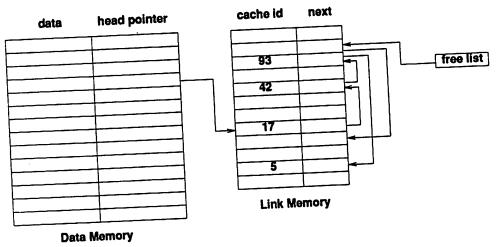

the memory controllers [SH91a]. The scheme in [LY90] stores list entries in an associative table, similar to a tag cache, but relies on compiler support to manage the directory. Figure 2.4 illustrates the centralized linked list scheme due to [SH91b]. Here links are stored in a special memory and managed by the main memory controller. Whenever the supply of links is exhausted, one or more links in use are reclaimed by invalidating the appropriate copies; the link pool is made sufficiently large, however, that this should be rare.

Figure 2.4: Centralized Linked List Directory

Figure 2.5 illustrates an variation of the scheme in [SH91a] that requires minimal hardware. Like the limitless directory scheme a portion of main memory is used for list storage; unlike the limitless directory scheme, however, no special tag memory is needed, and all coherence activities are handled by the main memory controller. If list data cannot be accessed quickly enough, the slow speed of main memory can be overcome by exploiting the fast column-mode access of many commercially available memory chips, or by storing several cache identifiers per link entry.

## 2.4 Conclusions

Full directories can be efficiently constructed using tag caches or linked lists, without broadcasting or limiting the number of cached copies of a block. The centralized linked list schemes are the most attractive because they do not need hardware to manage large bit vectors, and they avoid the complications of decentralized linked list schemes. The memory-mapped decentralized linked list scheme is especially attractive because of its low implementation cost: a slightly more complex controller and several additional registers.

Figure 2.5: Memory-Mapped Linked List Scheme

## Chapter 3

# **Workload Characterization**

## 3.1 Overview

Workload characterization using references from benchmark programs has been extensively used for uniprocessor cache studies [Smi82] and more recently for multiprocessor caching schemes [AG88, SA88, WG89b, ON90]. This chapter begins with a review of previous work. Following this, known stack simulation techniques are extended to support the evaluation of directory methods. These techniques are applied to three benchmark programs to evaluate invalidation, update and competitive directory protocols. An additional technique is described that is used to evaluate numerous competitive schemes from the results of a single simulation run of an update protocol.

The goal of the chapter is to show that directory-based cache coherence is very effective at reducing average memory access time and network traffic. The contributions of this chapter are: extensions to a stack simulation algorithm that support directory schemes, an algorithm for determining competitive protocol performance from an update protocol simulation, and quantitative performance data for three benchmark programs.

## 3.2 Previous Work

Many recent studies present empirical data on multiprocessor performance based on traces of parallel programs (Tables 3.1 and 3.2); some of the benchmarks used in these studies are described in Table 3.3. The tables show that all studies of directory methods with non-bus networks consider invalidation protocols only, and most consider 32 or fewer processors. The MIT and

Table 3.1: Trace-driven Multiprocessor Cache Studies

| Study                | Focus                  | Benchmark         | Number    | Notes               |

|----------------------|------------------------|-------------------|-----------|---------------------|

|                      |                        | Set               | of Procs. | 1.000               |