## Copyright © 1991, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# TECHNIQUES FOR TEST GENERATION AND VERIFICATION OF VLSI SEQUENTIAL CIRCUITS

by

Abhijit Ghosh

Memorandum No. UCB/ERL M91/73

3 September 1991

## TECHNIQUES FOR TEST GENERATION AND VERIFICATION OF VLSI SEQUENTIAL CIRCUITS

by

Abhijit Ghosh

Memorandum No. UCB/ERL M91/73

3 September 1991

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# TECHNIQUES FOR TEST GENERATION AND VERIFICATION OF VLSI SEQUENTIAL CIRCUITS

by

Abhijit Ghosh

Memorandum No. UCB/ERL M91/73

3 September 1991

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering

University of California, Berkeley

94720

## List of Tables

| 2.1 | Statistics for example circuits                           |

|-----|-----------------------------------------------------------|

| 2.2 | Test generation results for circuits                      |

| 2.3 | Time profiles for example circuits                        |

| 2.4 | Comparisons with STALLION and CONTEST                     |

| 2.5 | Number of clock cycles needed for testing                 |

| 2.6 | Test generation results for ISCAS sequential benchmarks 4 |

| 3.1 | Statistics for example circuits                           |

| 3.2 | Test generation results for circuits                      |

| 3.3 | Time profiles for example circuits                        |

| 3.4 | Comparisons with STEED                                    |

| 3.5 | Clock cycles needed for testing                           |

| 4.1 | Statistics for example circuits                           |

| 4.2 | Test generation results for circuits                      |

| 4.3 | Results of logic optimization                             |

| 5.1 | Comparison of implicit and explicit state techniques      |

| 5.2 | Verification of machines using traversal                  |

| 5.3 | Verification of machines using enumeration-simulation     |

| 5.4 | Comparison of times for verification                      |

| 6.1 | Example circuits                                          |

| 6.2 | Synthesis results using FLAMES                            |

| 7.1 | Experimental results                                      |

| 7.2 | Comparison with exact minimization                        |

| 7.3 | Comparison with exact function minimization               |

| CONTENTS                      |            |  |

|-------------------------------|------------|--|

| 8 CONCLUSIONS 8.1 Future Work | 175<br>180 |  |

| Bibliography                  |            |  |

.

•

•

,

## List of Figures

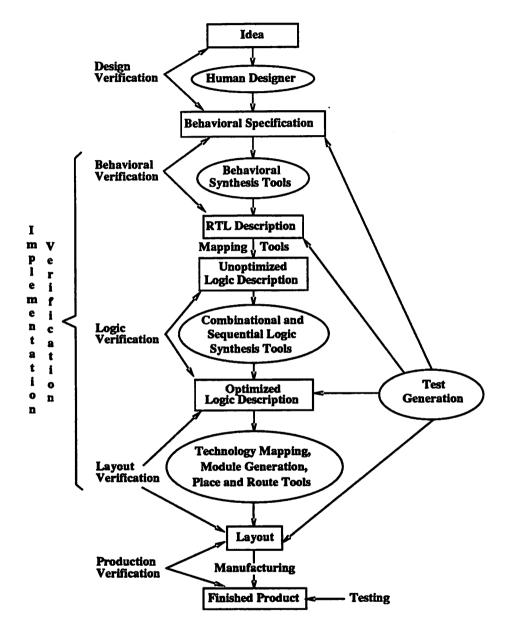

| 1.1  | A typical synthesis pipeline                            |

|------|---------------------------------------------------------|

| 2.1  | A general synchronous sequential circuit                |

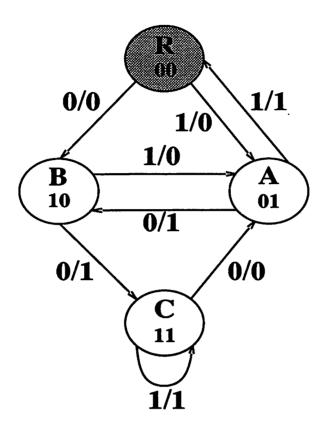

| 2.2  | An example State Transition Graph                       |

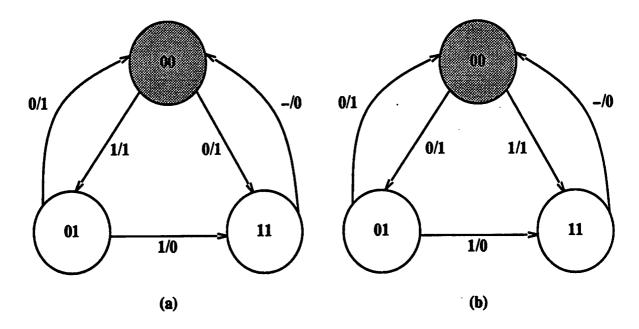

| 2.3  | STG of faulty machine                                   |

| 2.4  | A machine illustrating problem with initialization      |

| 2.5  | Cover enumeration example                               |

| 2.6  | ON and OFF-sets for NS lines of example machine         |

| 2.7  | Justifying state A                                      |

| 2.8  | Fault-free state justification                          |

| 2.9  | Justification algorithm                                 |

| 2.10 | ON and OFF-set for PO of example machine                |

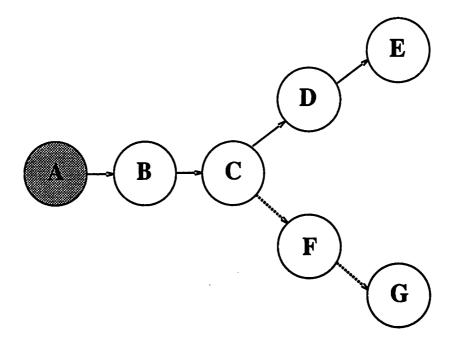

| 3.1  | An example RTL description                              |

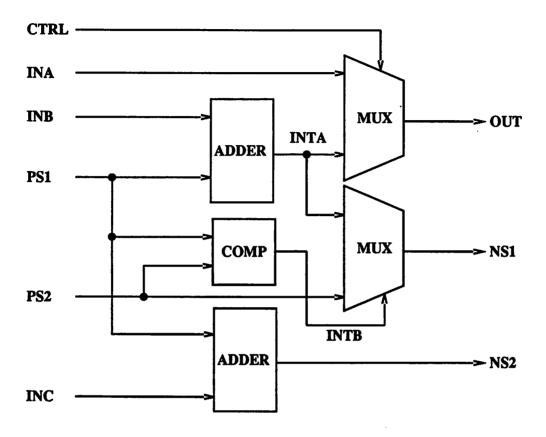

| 3.2  | An example circuit                                      |

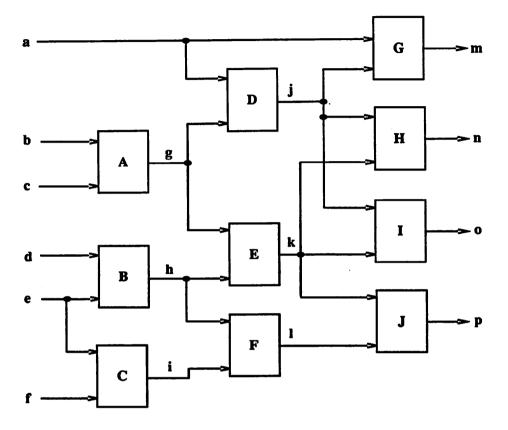

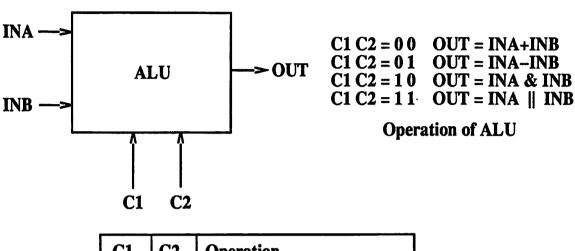

| 3.3  | An ALU and its model                                    |

| 3.4  | List of primitives used in test generation              |

| 3.5  | Main justification procedure                            |

| 3.6  | Procedure for justifying a state                        |

| 3.7  | Circuit to illustrate justification and differentiation |

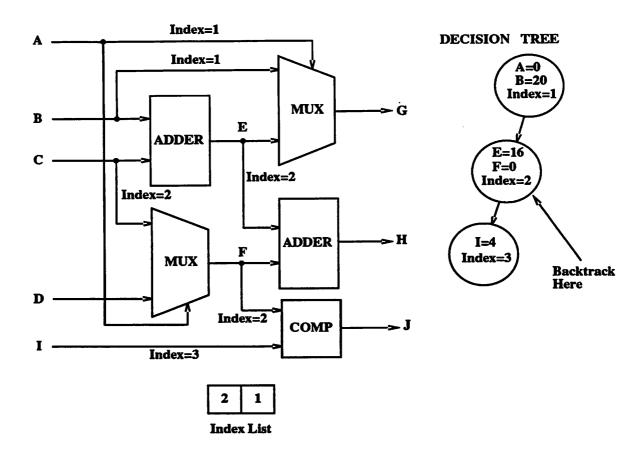

| 3.8  | Circuit to illustrate indexed backtracking              |

| 3.9  | Circuit illustrating conflict resolution                |

| 3.10 | Procedure for state differentiation                     |

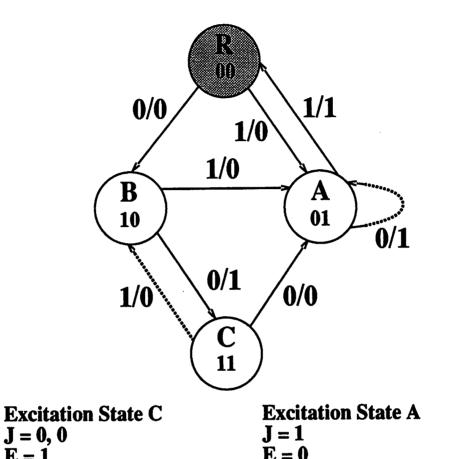

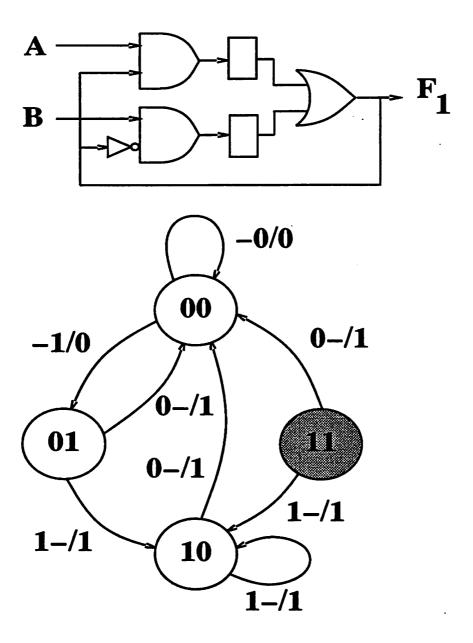

| 4.1  | An example STG                                          |

| 4.2  | The STG of an implemented machine 8                     |

| 4.3  | Equivalent-SRF                                          |

| 4.4  | Invalid-SRF                                             |

| 4.5  | Isomorph-SRF 88                                         |

| 4.6  | Complicated equivalent-SRF                              |

| 4.7  | Two-level cover of the FSM                              |

| 4.8  | An implementation of a sequential circuit               |

| 4.9  | Partitioned logic blocks                                |

LIST OF FIGURES vii

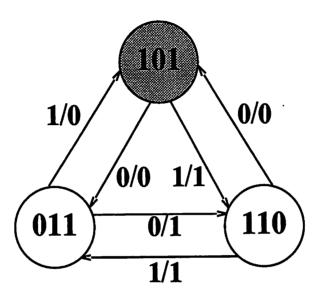

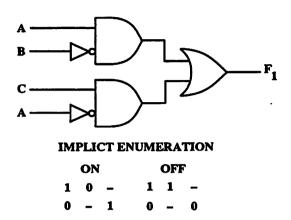

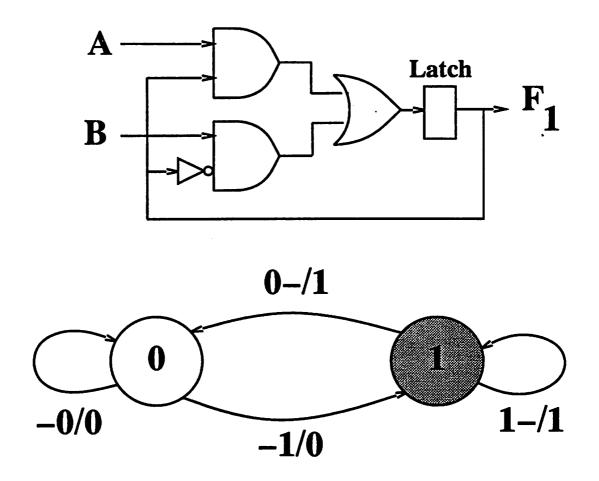

| 5.1  | Circuit illustrating explicit and implicit enumeration                 |

|------|------------------------------------------------------------------------|

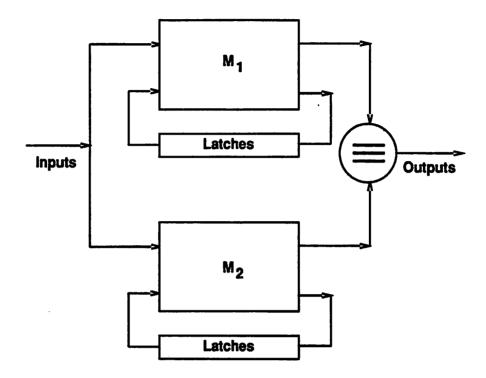

| 5.2  | Product machine                                                        |

| 5.3  | A cascade of two machines                                              |

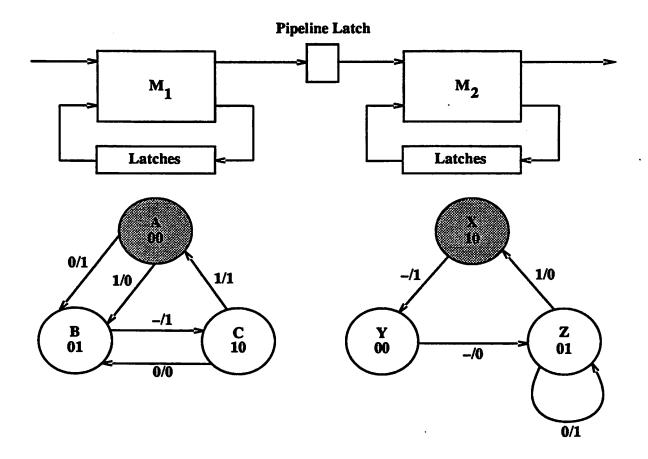

| 5.4  | STGs using explicit and implicit state enumeration                     |

| 5.5  | Main verification procedure using traversal 114                        |

| 5.6  | Procedure for traversing the STG of a machine                          |

| 5.7  | The STG of a product machine                                           |

| 5.8  | Parts of the STG enumerated during traversal                           |

| 5.9  | Final STG after traversal                                              |

| 5.10 | ON and OFF-sets of the PO and NS lines of a machine 123                |

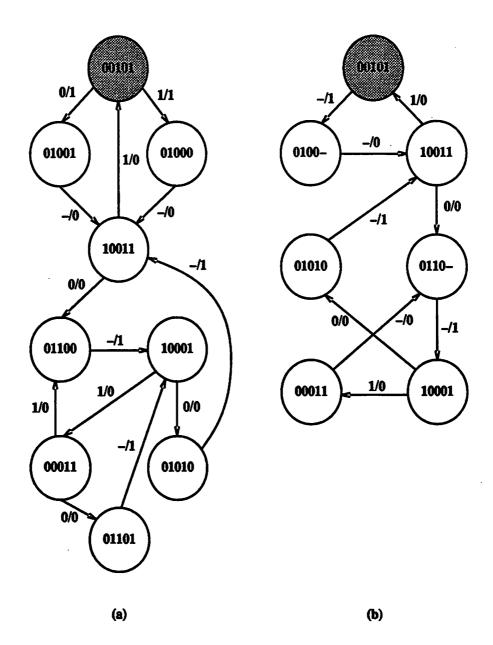

| 5.11 | State Transition Graph enumeration algorithm                           |

| 5.12 | Example to illustrate STG enumeration                                  |

| 5.13 | Machines illustrating difference between traversal and enumeration 129 |

|      |                                                                        |

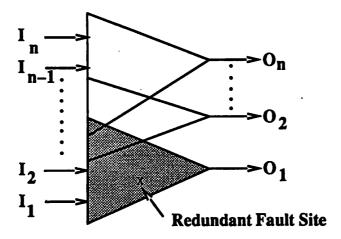

| 6.1  | Combinational logic block of a sequential circuit                      |

| 6.2  | Sequential circuit before retiming                                     |

| 6.3  | Sequential circuit after retiming                                      |

| 6.4  | Example State Transition Graph                                         |

| 6.5  | FSM with an encoder-decoder                                            |

| 6.6  | FSM decomposition types                                                |

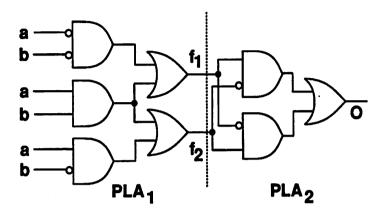

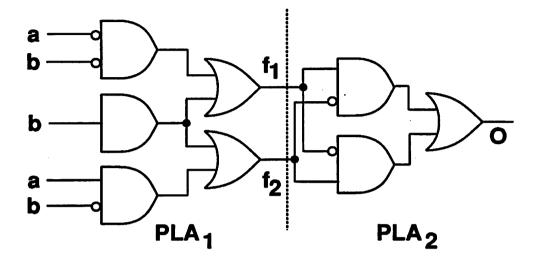

| 7.1  | PLA driving another PLA                                                |

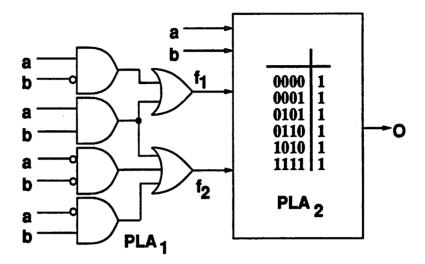

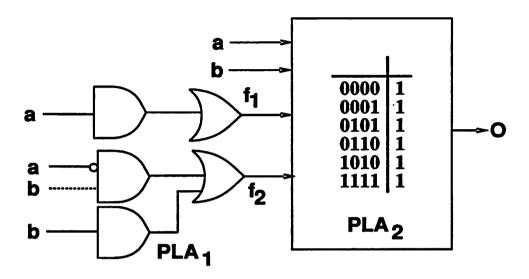

| 7.2  | Truth table of $PLA_1$                                                 |

| 7.3  | Boolean relation for $PLA_1$                                           |

| 7.4  | Representation of don't-cares                                          |

| 7.5  | Main minimization procedure                                            |

| 7.6  | Truth table for $PLA_2$                                                |

| 7.7  | Interconnected PLA network                                             |

| 7.8  | Example Boolean relation                                               |

| 7.9  | Truth table for $PLA_2$                                                |

| 7.10 | Interconnected PLA network                                             |

| 7.11 | Function cover after Expand                                            |

| 7.12 | Network after Expand                                                   |

| 7.13 | Function cover after Irredcover                                        |

|      | Network after Expand-Irredcover                                        |

| 7.15 | PLA <sub>1</sub> after Expand and Irredcover                           |

| 7.16 | PLA <sub>1</sub> after Reduce                                          |

|      | Cube-based specification of a Boolean relation                         |

|      |                                                                        |

## **Contents**

| Acknowledgements |                   |                                                    |      |  |  |  |  |  |  |

|------------------|-------------------|----------------------------------------------------|------|--|--|--|--|--|--|

| Tε               | Table of Contents |                                                    |      |  |  |  |  |  |  |

| Li               | st of             | Figures                                            | vi   |  |  |  |  |  |  |

| Li               | st of             | Tables                                             | viii |  |  |  |  |  |  |

| 1                | INT               | PRODUCTION                                         | 1    |  |  |  |  |  |  |

|                  | 1.1               | IC Design Systems                                  | 2    |  |  |  |  |  |  |

|                  | 1.2               | Implementation Verification                        | 5    |  |  |  |  |  |  |

|                  | 1.3               | Testing                                            | 6    |  |  |  |  |  |  |

|                  | 1.4               | Synthesis For Testability                          | 8    |  |  |  |  |  |  |

|                  | 1.5               | Organization of this Dissertation                  | 9    |  |  |  |  |  |  |

| 2                | TE                | ST GENERATION FOR SEQUENTIAL CIRCUITS              | 10   |  |  |  |  |  |  |

|                  | 2.1               | Preliminaries                                      | 11   |  |  |  |  |  |  |

|                  | 2.2               | Previous Work                                      | 18   |  |  |  |  |  |  |

|                  | 2.3               | Test Generation Strategy                           | 20   |  |  |  |  |  |  |

|                  | 2.4               | Cover Extraction and Combinational Test Generation | 25   |  |  |  |  |  |  |

|                  | 2.5               | Justification                                      | 28   |  |  |  |  |  |  |

|                  | 2.6               | State Differentiation                              | 33   |  |  |  |  |  |  |

|                  | 2.7               | Identification of Redundant Faults                 | 35   |  |  |  |  |  |  |

|                  | 2.8               | Test Generation Results Using STEED                | 37   |  |  |  |  |  |  |

|                  | 2.9               | Conclusions                                        | 42   |  |  |  |  |  |  |

| 3                | SEC               | QUENTIAL TEST GENERATION USING RTL DESCRIPTIONS    | 44   |  |  |  |  |  |  |

|                  | 3.1               | Preliminaries                                      | 45   |  |  |  |  |  |  |

|                  | 3.2               | Previous Work                                      | 49   |  |  |  |  |  |  |

|                  | 3.3               | Global Strategy for Test Generation                | 50   |  |  |  |  |  |  |

|                  | 3.4               | State Justification                                | 57   |  |  |  |  |  |  |

|                  | 3.5               | Indexed Backtracking                               | 64   |  |  |  |  |  |  |

|                  | 3.6               | Conflict Resolution                                | 68   |  |  |  |  |  |  |

|                  | <b></b>           | 3.6.1 Assembling the equations                     | 69   |  |  |  |  |  |  |

iv CONTENTS

|   | 3.7        | State Differentiation                                       | 72  |

|---|------------|-------------------------------------------------------------|-----|

|   | 3.8        | Test Generation Results Using ELEKTRA                       | 76  |

|   | 3.9        | Conclusions                                                 | 79  |

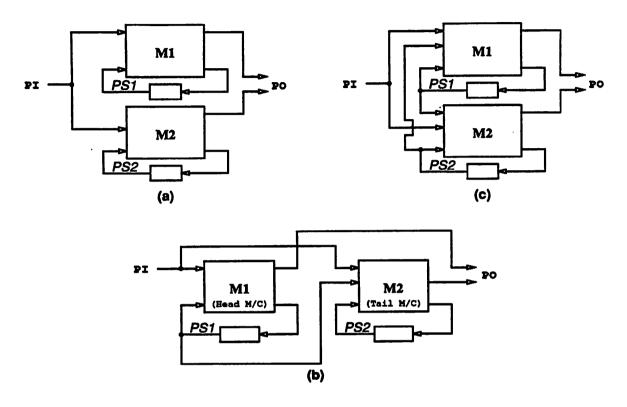

| 4 | SEC        | QUENTIAL SYNTHESIS FOR TESTABILITY                          | 8:  |

|   | 4.1        | Preliminaries                                               | 82  |

|   |            | 4.1.1 Eliminating Sequential Redundancies Using Don't-Cares | 88  |

|   | 4.2        | Previous Work                                               | 91  |

|   | 4.3        | Theoretical Results                                         | 92  |

|   |            | 4.3.1 An Unconditional Testability Theorem                  | 93  |

|   |            | 4.3.2 Logic Partitioning                                    | 94  |

|   | 4.4        | The Synthesis and Test Strategy                             | 97  |

|   | 4.5        | Detection of Invalid States                                 | 99  |

|   | 4.6        | Detection of Equivalent States                              | 101 |

|   | 4.7        | Experimental Results                                        | 101 |

|   | 4.8        |                                                             | 103 |

| 5 | VEI        | RIFICATION OF SEQUENTIAL CIRCUITS                           | 10  |

|   | 5.1        | Preliminaries                                               | 107 |

|   | <b>5.2</b> | Previous Work                                               | 110 |

|   | <b>5.3</b> | Implicit State Transition Graph Traversal                   | 111 |

|   |            | 5.3.1 Incompletely-specified machines                       | 119 |

|   | 5.4        |                                                             | 121 |

|   | 5.5        |                                                             | 129 |

|   | 5.6        |                                                             | 132 |

| 6 | SYN        | NTHESIS OF SEQUENTIAL CIRCUITS                              | 134 |

|   | 6.1        | Previous Work                                               | 136 |

|   | 6.2        | Optimizing Sequential Circuits                              | 137 |

|   | 6.3        |                                                             | 145 |

|   | 6.4        |                                                             | 148 |

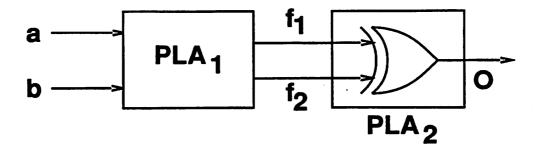

| 7 | HE         | URISTIC MINIMIZATION OF BOOLEAN RELATIONS                   | 150 |

|   | 7.1        | Definitions                                                 | 153 |

|   | 7.2        |                                                             | 155 |

|   | 7.3        |                                                             | 155 |

|   | 7.4        | Network Formation                                           | 158 |

|   | 7.5        |                                                             | 161 |

|   | 7.6        |                                                             | 164 |

|   | 7.7        |                                                             | 166 |

|   | 7.8        |                                                             | 168 |

|   | 7.9        |                                                             | 169 |

|   |            | _                                                           | 171 |

|   |            |                                                             | 174 |

## Acknowledgments

I am grateful to my research advisor, Prof. A. Richard Newton, for his guidance, inspiration, criticism, and constant support during my study at Berkeley. I am also grateful to Prof. Srinivas Devadas of MIT for providing similar guidance, impetus, direction, and necessary criticism during my research.

I would like to thank Prof. Robert K. Brayton and Prof. Alberto Sangiovanni-Vincentelli for many stimulating discussions on test generation, verification, and logic synthesis. Special thanks to Prof. Brayton for being on my qualifying examination and thesis committees. I would also like to thank Prof. Jack Silver of the Mathematics Department for being on my qualifying examination and thesis committees and for his helpful suggestions.

Being a part of the CAD-group at Berkeley has been a unique experience. Various people have contributed in different ways to make this experience enjoyable and edifying. I would like to thank my erstwhile colleagues Jeff Burns, George Jacob, Karti Mayaram, Theo Kelessoglou, and Don Webber for answering many of my questions when I was a newcomer in the group. Special thanks to all the unix-experts, namely, Wendell Baker, Brad Krebs, Chuck Kring, and Rick Spicklemier for pulling me out of trouble many a times. I would like to thank Pranav Ashar, Brian Lee, Bill Lin, Abdul Malik, Rajeev Murgai, Brian O'Krafka, Alex Saldanha, Hamid Savoj, Ellen Sentovich, Narendra Shenoy, K.J. Singh, Hérve Touati, Yosinori Watanabe, and Greg Whitcomb for many interesting discussions on a wide variety of topics. Special thanks to Rajeev Murgai for reading prepublication manuscripts. Hi-Keung Tony Ma has been very helpful both inside and outside the department. In addition to giving me his software, fixing bugs for me, and his healthy criticism, he has also been a great tennis and badminton partner. Thanks also to Wayne Christopher, Andrea Casotto, Mark Beardslee, Chris Lennard, Jaijeet Roychowdhury, and Lorraine Layer for their friendship. I would also like to thank Kia Cooper, Elise Mills, and Flora Oviedo for their help with travel grants, mailings, and in general making my life easier.

There are some wonderful people who have been instrumental in making my life, especially in Berkeley, very pleasurable. I would like to thank them for what they have done for me — David, Paul, and Laurent for being silly and for their interest in agriculture; Lorna, Salima, Eliane, and Romella for their friendship, support, and love; Roberto and the rest of the gang for the parties in SF; Brinda for many entertaining and scintillating moments;

and Rhonda, Barbara, Micheline, Deborah, Cheryl, Ceri, Cynthia, Marilyn, Silvia, Sara, Martha, Kathy, Claudia, Giovanna, Susanna, Babu, Noeman, Rabi, Smarajit, Prashanta, Harald, Kinsuk, Kamal, Hitesh, Milind, Steve, James, Aditya, Ahmed, Joseph, Marco, and the rest of the group for being such good friends. Special thanks to my host family, Bob and Linda Mahley, for their help and their love.

I would like to thank my family, especially my parents and my uncle, for their monumental support, encouragement, and enthusiasm in the work that I was doing. Without their help, this work might not have been possible.

This research was supported in part by the Defense Advanced Research Projects Agency under contract JFBI90-073, Digital Equipment Corporation, and AT&T Bell Laboratories. Their support is gratefully acknowledged.

### Techniques for Test Generation and Verification of VLSI Sequential Circuits

## Abhijit Ghosh

Ph.D.

Department of Electrical Engineering and Computer Science

#### Abstract

Very large-scale integrated circuits contain thousands of circuit components within a very small area. The design of such circuits is a complicated and time consuming process, and automatic design tools are used wherever possible to help or complement the designer. In addition to performance, the reliability of the manufactured product is of utmost importance. Testing is the process of ensuring that there are no defects in the manufactured circuit. One of the key problems in testing is that of automatic test pattern generation, especially for sequential circuits. Two new test generation algorithms for sequential circuits have been developed as a part of this dissertation. The first one uses novel ideas and heuristics for circuits described at the gate level. The second one uses and exploits the properties of higher level descriptions, namely, Register-Transfer level descriptions, for efficient test generation.

The design process involves the transformation of a design from one representation to another or a transformation within the same representation, using automatic optimization tools. The probability of introducing errors in a circuit during the design phase is high. Therefore, automatic tools that verify that the current representation of a circuit is the same as the original representation are needed. An algorithm for verification of sequential circuits described at the gate level has been developed. This algorithm uses implicit enumeration of the input as well as the state space.

To ease the task of test generation, it is necessary to synthesize circuits to be fully and easily testable, and these are the objectives of the synthesis for testability process. A new approach to synthesis for testability for sequential circuits is presented. It uses logic partitioning and exploits invalid and equivalent-state don't-cares to obtain a fully testable implementation of a circuit. An associated problem is that of minimization of Boolean relations. An algorithm to obtain a minimal implementation of a Boolean relation is presented. This algorithm uses well known testing techniques for logic optimization.

Prof. A. Richard Newton Thesis Committee Chairman

## Chapter 1

## INTRODUCTION

Very Large Scale Integrated (VLSI) circuits are an integral part of any modern electronic system. Such circuits contain from thousands to millions of transistors, diodes, and other devices, resistors, capacitors, and interconnections within a very small area. The design of such circuits is a complicated and time consuming process. Synthesis refers to the process of (automatically) designing or re-designing a circuit from a specification of the circuit. There are many sources of error that can produce an incorrectly functioning circuit. One of them could be an error in the specification. Design verification is the process of determining whether what the designer specified is what she/he wants. Once the specification is verified, an implementation of the circuit is derived. The error that produces an incorrectly functioning circuit could be in the design phase where either a human designer or an automatic design tool makes an error (probably due to an undetected bug). Implementation verification is the process of determining whether the designed circuit is the same as what was specified. Logic verification, which is a part of implementation verification, is the process of verifying the equivalence of two logic-level circuits, usually the optimized and the unoptimized ones. If an implementation of a design is correct and there are no manufacturing defects, then the manufactured circuit should function as per specifications. However, the manufacturing process may introduce defects in the circuit (e.g., short circuits, open circuits, missing transistors, etc.). Even though a circuit has no manufacturing defects, it may become defective due to a variety of reasons (e.g., physical or thermal stress, radiation, etc.) during the operation of the circuit. Production verification is the process of verifying whether the manufactured circuit is the same as what was specified. Testing, which is a part of production verification, is the process of determining whether a fabricated circuit is defective, and if so, identifying the location of the defect.

VLSI circuits can be divided into two classes – combinational circuits (without memory) and sequential circuits (with memory). Techniques for the automatic synthesis and verification of both kinds of circuits have been under investigation for a long time. Until recently, combinational circuits have received the bulk of researchers attention. Today, there are techniques that can synthesize [15, 16, 57] and generate tests [60, 65, 84, 91, 94, 119] for combinational circuits efficiently. There has been some effort in solving the sequential logic synthesis and test problem using combinational techniques [56, 87, 89]. The focus of this dissertation is the testing and logic verification of digital synchronous sequential logic, and the relationship of these techniques to synthesis of such circuits.

With the advances in integrated circuit (IC) technology, the number of devices that can be put on a chip has increased rapidly. This has greatly increased the complexity of the synthesis, verification, and testing process. It is necessary to find new synthesis strategies to synthesize circuits with minimal area, maximal performance, and improved testability. Previous approaches are not effective for these large circuits for a variety of reasons. However, without high-quality logic synthesis and verification tools, it might not be possible to design, implement, and market a reliable product. In this chapter the major issues involved in synthesis, verification, and testing are presented. In Section 1.1 a typical synthesis system is described. Issues in design verification and testing are the topics of Sections 1.2 and 1.3 respectively.

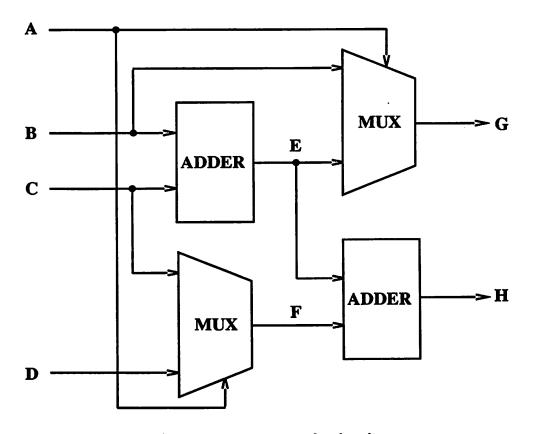

## 1.1 IC Design Systems

Synthesis involves a series of alternate mapping and optimization steps. These steps in a typical synthesis process are shown in Figure 1.1. Starting with an idea about what the designer wants, a behavioral description of the circuit in a high-level language like ELLA [104], VHDL [113], or ISPS [12] is written. The first step in the synthesis process is to convert the behavioral specification into a Register-Transfer level (RTL) description of the circuit. This process could be as simple as mapping the behavioral specification to a Register-Transfer level description. However, during the conversion process, in addition to mapping, behavioral synthesis tools [41, 69, 80, 111, 128, 132, 134] can be used to optimize the circuit to use the minimum amount of hardware within the required performance constraints. The design space is large and the tools explore various design trade-offs and try to produce

Figure 1.1: A typical synthesis pipeline

an optimal solution. It should be noted that the use of behavioral synthesis tools in the industry is currently quite limited.

After a Register-Transfer level description has been obtained, it is mapped into logic equations using mapping tools like BDSYN described in [122]. The next step is logic

synthesis, which is an optimization step. Typically, a Register-Transfer level description is an interconnection of pre-defined modules like adders, multipliers, or finite state machines that implement controllers. This description often has redundant logic, and the task of logic synthesis tools [10, 15, 16, 40, 57] is to transform this description into a more optimal description of the circuit in terms of logic gates. The goal of logic optimization is to minimize the area while meeting the performance constraints. Another objective is to improve the testability of the circuit [45, 49].

The result of logic optimization is an optimized gate-level or logic-level description of the circuit. The next step in the synthesis process is to produce a mask-level description or a layout of the circuit in a given technology. Technology mapping [39, 82] refers to the mapping of an arbitrary logic-level description into an implementable logic network using a set of gates from a standard library of gates. This process involves both mapping the logic description into an implementable network, as well as optimizing the mapped description in order to meet area and performance constraints. Module generators [55, 109] may be used to produce a layout for each module in the design. Finally, the modules or gates are placed and routed using placement and routing tools like [31, 33, 114, 121]. This is both a mapping and an optimization phase that produces the final mask-level description of the circuit. This description can be used to manufacture the final product.

In a typical design process, the designer might have to iterate over these steps before an acceptable final circuit is produced. This is because constraints imposed on the design are not satisfied in the first pass. Information from any level could be fed back to a higher level to enable the tools working at that level to come to better decisions in order to satisfy the design constraints. For example, a behavioral synthesis tool might not know the cost of a module (in terms of area and performance) when it chooses the module. After layout, the cost of the module can be accurately estimated and used by the synthesis tools to make a better decision. The synthesis process can be made fully automatic. However, designer intervention and insight is often necessary to produce high-quality circuits. The synthesis process involves the solution of many optimization problems, most of which are conjectured to be intractable. Therefore, most tools use heuristics to obtain close-to-optimum solutions.

### 1.2 Implementation Verification

During the design phase many descriptions of the same circuit are produced. For example, starting from the behavioral description of the circuit, the RTL description, the logic-level description, and, finally, the mask-level description are produced. In addition, optimization tools produce many alternate designs at the same level. If the steps of synthesis are performed manually, there is always a high probability of introducing errors. Since bug-free software cannot be guaranteed, there is also a chance that automatic synthesis tools will produce an erroneous result for a particular circuit. Design errors might also be introduced due to the misunderstanding and the resulting misuse of an automatic tool. Since the probability of introducing errors is non-zero in both the automatic and the manual design environment, it is necessary to verify, at each design step, that the resulting description and the original description are identical. Manual verification is not possible due to the size of the circuits and due to the relatively high probability of error during verification. Reliable, automatic, and *independent* verification tools are necessary to ensure the correctness of the final design.

As shown in Figure 1.1, verification tools can be used at various steps in the design process. Design verification has relied mostly on simulation, though formal methods are slowly emerging [70]. The problem of verifying the equivalence of a behavioral description and an RTL description (behavioral verification) has been the subject of extensive investigation (e.g., [4, 24, 42, 59]). Algorithms for verifying the equivalence of an RTL description and a logic-level description for both combinational and sequential circuits are presented in [46, 92]. Algorithms for verifying equivalence of alternate logic-level descriptions for circuits (logic verification) are presented in [36, 46, 92, 94]. Algorithms for verifying the equivalence of logic-level descriptions and layout (layout verification) can be found in [27, 29, 28], and algorithms for verifying timing behavior can be found in [110].

A decision problem [61] is a problem that has a yes or a no answer. Some decision problems form an equivalent class called non-deterministic polynomial-time complete (NP-complete). The characteristic of these problems is that a solution to any problem can be transformed into a solution to another problem in polynomial time. Also, no known polynomial-time algorithm can solve any of the problems. In addition, these problems are not provably intractable. Many optimization problems can be transformed into decision problems, and the corresponding decision problem can be proved to be NP-complete (e.g.,

the Traveling Salesman Problem). There is another class of decision problems that are not NP-complete, but are at least as hard as NP-complete problems. Such problems are called NP-hard.

The logic verification problem can be stated in the following manner. Given two circuits  $\mathcal{A}$  and  $\mathcal{B}$ , are  $\mathcal{A}$  and  $\mathcal{B}$  identical, *i.e.*, under all input conditions, do  $\mathcal{A}$  and  $\mathcal{B}$  produce the same outputs, and if not, then under what conditions do  $\mathcal{A}$  and  $\mathcal{B}$  produce different outputs? This is a decision problem and can be proved to be NP-hard. Despite its complexity, it is possible to verify a large class of practical circuits (e.g., [30, 36, 46, 94]). In this dissertation, the problem of verification of logic-level sequential circuits is examined, new approaches are developed, and their merits and demerits are evaluated in the light of previous approaches.

### 1.3 Testing

Implementation verification ensures that the design process is error free. However, manufacturing defects are almost invariably introduced. No manufacturing process can guarantee 100% yield, and therefore some manufactured circuits are bound to have defects. The types of defects depend on the technology. Across various technologies, the most common types of defect during manufacturing are short-circuits, open-circuits, open bonds, open interconnections, bulk shorts, shorts due to scratches, shorts through dielectric, pin shorts, cracks, and missing transistors [21]. Also, the larger the circuit in terms of area, the greater the chances of it having a defect. It is necessary to separate the bad circuits from the good ones after manufacture. From the point of view of economics, it has been shown that the cost of detecting a faulty component is lowest before the component is packaged and becomes a part of a larger system. Therefore testing is a very important aspect of any VLSI manufacturing system.

There are two aspects to testing; one is fault detection and the other is fault diagnosis. In fault detection only the presence of a fault is detected, but in diagnosis the exact location of the fault has to be identified. The testing process involves the application of test patterns to the circuit and comparing the response of the circuit with a pre-computed expected response. Any discrepancy constitutes an error, the cause of which is said to be a physical fault [21]. Such faults, for digital circuits, can be classified as logic or parametric [21]. A logic fault is one which causes the logic function of the circuit element (elements) or

1.3. TESTING 7

an input signal to be changed to some other function. Parametric faults alter the magnitude of a circuit parameter causing a change in some factor such as circuit speed, current, or voltage levels. In this dissertation the focus is only on the detection of logic faults.

Testing must be performed throughout the life of a circuit, since faults may be introduced in the circuit during assembly, storage, and service. The most commonly occurring faults during storage and service are due to temperature, humidity, aging, vibration, and voltage or current stress [21].

Generation of test patterns is a very important problem and has been under investigation for a long time [1, 60, 65, 84, 90, 95, 108, 119, 123]. As shown in Figure 1.1, test generation may be performed at various levels during the design process. The average case complexity of test generation, the fault model, and the fault coverage obtained depends on the representation used. An important issue is the fault model used in test generation. Physical faults are often modeled as logic faults. By doing so, the problem of fault analysis becomes a technology-independent logic problem. In addition, tests derived for logic faults may be useful for physical faults whose effect on circuit behavior is not well understood or too complex to be analyzed otherwise. The main requirement for the fault model is that the model should be able to capture the change in functionality caused by most of the commonly occurring physical defects in the circuit. The fault model used most often in practice today is the *single stuck-at* fault model, where a single gate input or output in the circuit gets stuck at a 1 or 0 value.

Another important issue in test pattern generation is fault diagnosis. It is not only important to identify the presence of a fault, but also to locate the fault and find a reason for the fault. Fault location, which is one aspect of fault diagnosis, is used to debug circuits and fix manufacturing errors. Tests for one fault can simultaneously detect other faults in the circuit. Two faulty circuits might also have identical responses for a particular test pattern. Therefore a test set has to be derived which not only identifies all the faults, but can also help in locating the fault from the analysis of the response.

Tests are applied to circuits using Automatic Test Equipment (ATE). This equipment is usually very expensive. The amount of time that each circuit requires for testing is therefore very important. This time is determined by the amount of time required to apply the test vectors and the time required to compare the data with the expected response.

Test generation for combinational circuits as well as sequential circuits is an NP-hard problem [85]. There is no known polynomial-time algorithm that can be used to

generate tests for circuits. However, for a large class of circuits, it is possible to generate tests efficiently using various heuristic search techniques.

The problem of test generation is intimately related to the problem of verification. In fact, for both combinational and sequential circuits, the problem of test generation can be formulated as a verification problem and vice versa. The test generation problem can be converted into the problem of verifying whether the fault-free and faulty circuits are identical. If they are not, the test pattern is the (sequence of) input vector(s) that differentiates the two circuits. On the other hand, the problem of verification can be converted into finding a test for a fault, assuming one circuit is a true circuit and the other circuit is a faulty circuit. If no tests can be found, the circuits are identical.

In this dissertation, two new test generation algorithms are presented. The first one uses purely gate-level information to generate tests for sequential circuits. Using better techniques and heuristics, the algorithm can handle larger circuits than previous approaches. The second algorithm uses RTL information for test generation and can be applied to circuits that cannot be handled using a purely gate-level approach.

### 1.4 Synthesis For Testability

Generating tests for sequential circuits is a difficult problem. The algorithms that will be presented in Chapters 2 and 3 provide means for handling large circuits. However, some circuits have redundant faults, and while generating tests for such circuits, a significant fraction of the test generation time could be spent in the identification of redundant faults. The task of test generation will be greatly simplified if circuits are synthesized to be fully and easily testable.

It is well known that optimal logic synthesis can produce fully testable combinational circuits [13]. Similar results were derived for sequential circuits in [49]. These methods rely on extracting a set of don't-care conditions for the circuit and using the don't-cares during logic optimization to derive a fully testable implementation of the circuit. The primary issue in this approach to synthesis for testability is the efficient derivation of the don't-care conditions. For sequential circuits, these don't-cares have been traditionally obtained from the State Transition Graph [49]. Recently, State Transition Graph traversal techniques based on Binary Decision Diagrams have been used to derive the set of don't-cares [87]. Another major issue is the exploitation of these don't-cares in logic synthesis. As has been

shown in [18], traditional don't-cares cannot be used to capture all forms of incomplete specification. The solution to this is the use of Boolean relations [18] in synthesis. In this dissertation, both of these issues are addressed. An algorithm for efficient determination of the don't-cares needed for synthesizing a fully testable machine is presented. In addition, a logic partitioning scheme is outlined that can help in reducing the size of the don't-care set. Also, a procedure that uses testing techniques for the minimization of Boolean relations is presented.

## 1.5 Organization of this Dissertation

In Chapter 2, a test generation algorithm for sequential circuits specified at the gate level is presented. This algorithm is extended to consider circuits described at the RT level in Chapter 3. In Chapter 4, algorithms for synthesizing circuits to ensure full testability are presented. Chapter 5 deals with the verification of sequential circuits. Efficient algorithms for traversal and enumeration of State Transition Graphs using techniques similar to those in Chapter 2 are presented. In Chapter 6, the use of compact STGs for synthesis is indicated. In Chapter 7, the problem of minimization of Boolean Relations arising in synthesis for testability is addressed. Conclusions are presented in Chapter 8.

## Chapter 2

## TEST GENERATION FOR SEQUENTIAL CIRCUITS

Test generation for sequential circuits has long been recognized as a difficult problem [21, 75, 102]. In particular, unstructured, random, sequential digital designs are very difficult to test. The test generation problem is difficult mainly because the input space that must be searched to obtain a test vector sequence is huge. Since most circuits have a large number of inputs, it is not possible to enumerate the input space explicitly. The structure of the circuit must be exploited to search the input space implicitly and reduce the complexity of the search process for the expected cases. Another difficulty in circuits without reset lines is the necessity of initializing the latches to a known value. One common approach to improving the testability of the circuit is to add extra test points to improve the controllability and observability of internal nodes of the circuit, thereby easing the task of test generation (e.g., [135]). However, this method is not systematic and relies greatly on the ingenuity of the designer. This approach also has its associated area and performance penalty.

The problem of test generation for combinational circuits is NP-hard. However, by exploiting the structure of logic functions and using the power of modern computers, it is possible to generate tests for most combinational circuits. Therefore, a popular approach to solving the testability problem for sequential circuits has been the Scan Design methodology [2, 56]. In this approach all the memory elements of the machine are made scannable, i.e., their values can be directly controlled and observed. The problem of sequential test

2.1. PRELIMINARIES 11

generation is thereby converted into the problem of combinational test generation. Though this eases the task of test generation greatly, two major drawbacks of this approach are the associated area and performance penalties. The latches are special Scan latches and are usually larger than normal non-scan latches. The increased area may lead to either degraded performance or reduced circuit yield. The specific penalty that is most important is very technology (e.g., CMOS or bipolar) and design style (e.g., static or dynamic) specific. Also, for circuits with a large number of latches, the total time required to test the circuit using Scan is large. Since tester time is costly, this translates into higher cost for the manufactured product, often doubling the cost of a complex chip. Scan design also constrains the design to be fully synchronous and free of critical races in the normal operation of the circuit. In situations where there is a strict area and power budget, Scan design cannot be used. Even though the problem of non-scan sequential test generation is difficult, there are a large number of circuits for which non-scan test generation can be quite effective. Therefore adopting the Scan design methodology without investigating non-scan test generation may incur unnecessary area and performance penalties.

The rest of this chapter is organized as follows. In Section 2.1, the problem of test generation for non-scan sequential circuits is examined and some basic definitions are presented. In Section 2.2, previous work in this area is reviewed and their merits and disadvantages are pointed out. In Section 2.3, the overall test generation strategy is outlined. Section 2.4 deals with cover extraction and combinational test generation. In Section 2.5, the justification procedure is presented, followed by the differentiation procedure in Section 2.6. Identification of redundant faults is the topic of Section 2.7. Finally, results using this test pattern generation strategy are presented in Section 2.8. Conclusions are presented in Section 2.9.

#### 2.1 Preliminaries

A sequential circuit is a circuit with memory [83]. Such circuits are capable of storing information and performing some mathematical or logical operations upon the stored information. A *finite state machine* is an abstract model describing the behavior of a sequential circuit. Formally, a finite state machine  $\mathcal{M}$  is defined as a 5-tuple [83]:

$$\mathcal{M} = (\mathcal{I}, \mathcal{S}, \mathcal{O}, \delta, \gamma)$$

where  $\mathcal{I}$  is a finite, non-empty set of input symbols,  $\mathcal{S}$  is a finite, non-empty set of states,  $\mathcal{O}$  is a finite, non-empty set of output symbols,  $\delta: \mathcal{I} \times \mathcal{S} \to \mathcal{S}$  is the next-state function, and  $\gamma$  is the output function. For a Mealy machine [83],  $\gamma: \mathcal{I} \times \mathcal{S} \to \mathcal{O}$ , while for a Moore machine [83],  $\gamma: \mathcal{S} \to \mathcal{O}$ . Note that a Mealy machine is more general than a Moore machine, and any Moore machine can be converted into a Mealy machine with the same number of states and state transitions. The algorithms described in this dissertation are applicable to both Mealy and Moore machines.

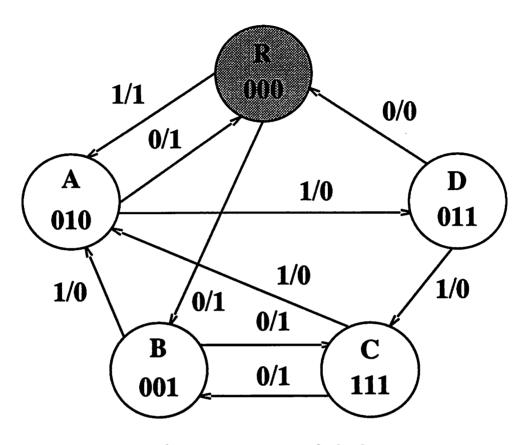

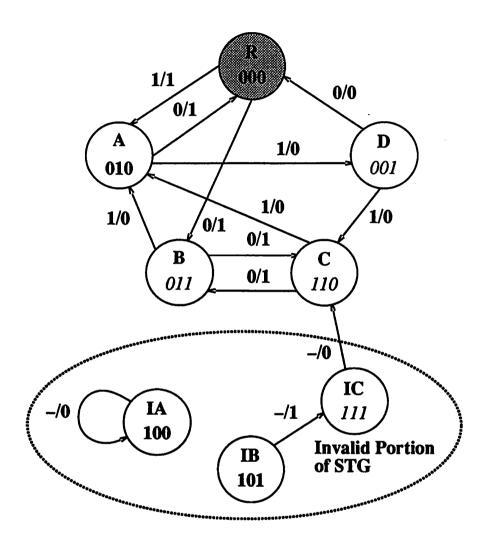

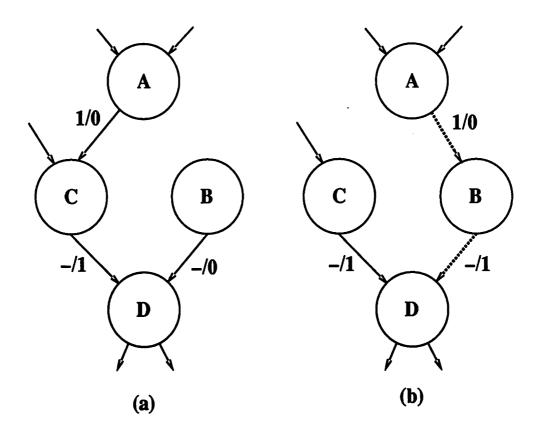

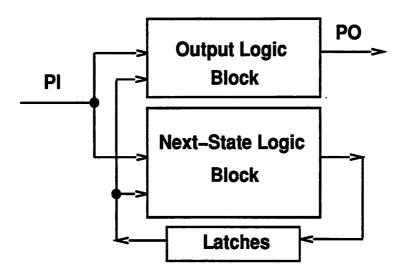

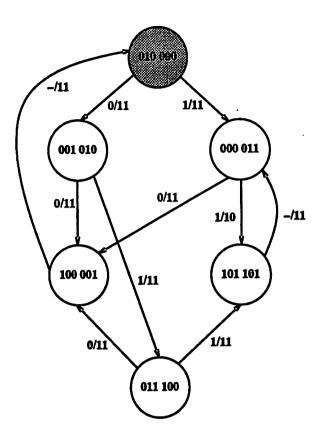

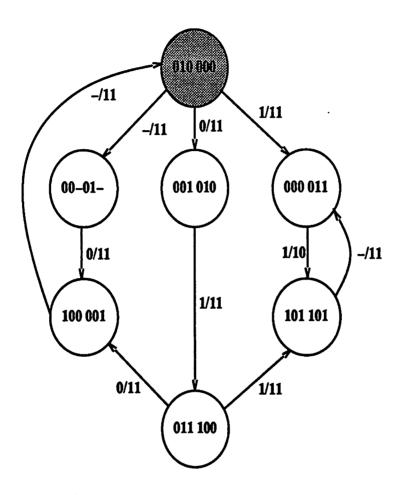

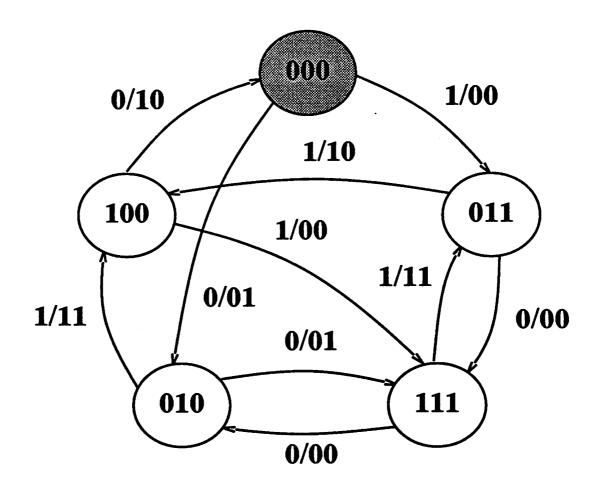

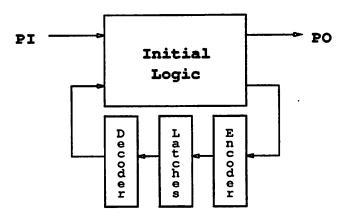

Sequential circuits are often referred to as finite state machines, or simply machines. A sequential circuit is said to be synchronous if the internal state of the machine changes at specific instants of time as governed by a clock. A general synchronous sequential circuit at the logic level is shown in Figure 2.1. It consists of a combinational logic block and state registers (latches or flip-flops) that hold the state information. The combinational logic block is an interconnection of gates that implements the mapping between the primary input (PI) and present-state (PS), and primary output (PO) and next-state (NS). The behavior of this circuit is often represented using a State Transition Table (STT) or a State Transition Graph (STG) [83], as in Figure 2.2. The names synchronous sequential circuit, finite state machine, and machine will be used interchangeably throughout this dissertation. Most of the remaining definitions in this section are taken from [49, 63, 83].

In general, a state is a symbol indicating the internal state of the machine. For the circuit of Figure 2.1, a state is a bit vector of length equal to the number of memory elements (latches or flip-flops) in the sequential circuit. Each state has a unique bit vector representing that state, and this bit vector is known as the state code. The process of assigning a code to each state is known as state assignment or state encoding. A state with only 0s and 1s as bit values is called a minterm state. In general, a state could be a cube, i.e., the values in the different bit positions may be 0, 1 or - (don't-care). A cube state therefore represents a group of minterm states.

A state is said to cover another state if the value of each bit position in the first state is either a — (don't-care) or is equal to the value of the corresponding bit position in the second state. For example, state 110 is covered by state 11—. State 11— also covers state 111. State Transition Graph enumeration is the process of deriving the STG description of a machine from its logic-level description. There are various methods for doing this and one such method will be presented in this chapter.

To illustrate the problem of test generation, consider a sequential circuit, like the

Figure 2.1: A general synchronous sequential circuit

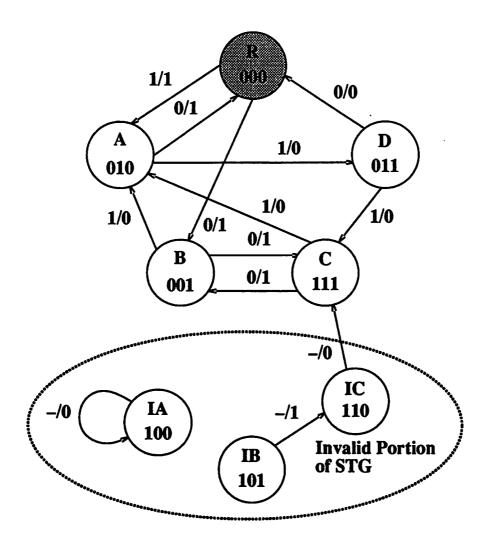

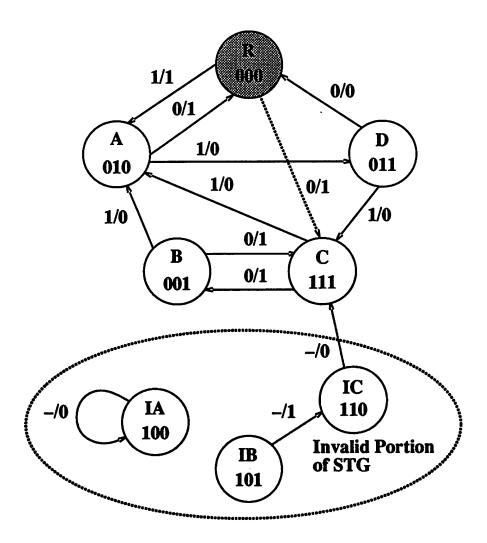

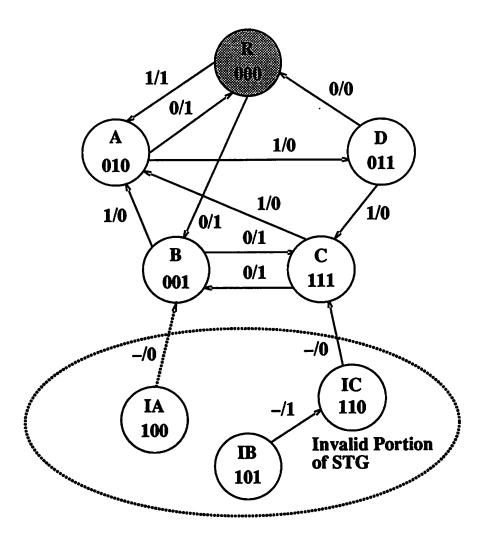

one shown in Figure 2.1, whose STG is shown in Figure 2.2. Assume that the present-state and the next-state lines are neither directly controllable nor observable. The objective of test generation is to find a sequence of vectors that when applied to the primary input, will produce different responses in the correct and the faulty circuit. A fault often manifests its effect by changing the STG of the machine. Consider a fault in the circuit that changes the behavior of the circuit from that shown in Figure 2.2 to that shown in Figure 2.3. The faulty STG is characterized by corrupted edges. An edge in the State Transition Graph is said to be corrupted by a fault if a different output is asserted by the edge or the faulty machine goes to a different next state. Therefore the effect of the fault can be propagated to the primary outputs or next-state lines by the input vector corresponding to the corrupted edge, with the present-state lines set to the fanin state of the edge. An input vector to the combinational logic part of the faulty machine that excites and propagates the effect of the fault either to the primary output or the next-state lines is called an excitation vector for the fault. The present-state part of the excitation vector is the state whose fanout edge is corrupted by the fault and is called the excitation state. In Figure 2.3, the corrupted

Figure 2.2: An example State Transition Graph

edges are shown using dotted lines. The excitation states are states A and C. Note that the excitation vector is a combinational test for the fault.

Most sequential circuits have a starting state, the state to which the machine goes upon power-up. Often, the machine can be set to this state very easily (for example, by using a reset line). The starting state of the machine is called its reset state. All test vector sequences are applied with the machine starting in the reset state. For the machine used in this example, state  $\mathcal{R}$  is the reset state. Throughout this dissertation the reset state will be indicated by a shaded circle in the figures. All states in the machine reachable from the reset state using an input sequence of any length, and the reset state are said to be valid states.

Having determined the excitation state, the next step in test generation is to take

E = 1

Test = J + E = 0, 0, 1

Figure 2.3: STG of faulty machine

D = 1

Test = J + E + D = 1, 0, 1

the machine from the reset state to the excitation state. The process of finding an input sequence which takes the machine from the reset state to the excitation state is called state justification. The corresponding input sequence is called the justification sequence, and the set of states and edges traversed during justification constitute the justification path. State justification may be forward or backward, depending on whether the search is conducted from the reset state to the excitation state or vice versa. A justification sequence for state C is the input vector sequence  $\{0,0\}$  which takes the machine from state R through

state  $\mathcal{B}$  to  $\mathcal{C}$ . A justification sequence for state  $\mathcal{A}$  is  $\{1\}$ .

If state C is used as the excitation state, then on applying the input vector 1 (the excitation vector) with the machine in state C, the true (or fault-free) machine asserts the output 1 while the faulty machine asserts the output 0. Therefore the effect of the fault is observable at the POs, and a test sequence can be formed by concatenating the justification sequence and the excitation vector. In this case, the test sequence is  $\{0,0,1\}$ . The situation is different if state A is used as the excitation state. The true and faulty circuits assert the output 1 in state A on application of the excitation vector 0. However, the true machine goes to state  $\mathcal{B}$ , while the faulty machine stays in state  $\mathcal{A}$ . States  $\mathcal{B}$  and  $\mathcal{A}$  are called the true/faulty or fault-free/faulty state pair. In order to propagate the effect of the fault to the POs, it is necessary to differentiate between state B in the true machine and the state A in the faulty machine. A differentiating sequence for a pair of states  $(S_1, S_2)$ in a sequential circuit is a sequence of input vectors, such that if the sequence is applied to the circuit when the circuit is initially in  $S_1$ , the last vector in the sequence produces a different primary output combination than if the circuit were initially in  $S_2$ . The process of finding such a sequence is called state differentiation. In this example, a differentiating sequence is the single vector  $\{1\}$ , where state  $\mathcal{B}$  in the fault-free machine asserts the output 0 while the state A in the faulty machine asserts the output 1. The test sequence is obtained by concatenating the justification sequence, the excitation vector, and the differentiating sequence. In this case it is  $\{1,0,1\}$ .

Justification and differentiation are the bottlenecks in test pattern generation for sequential circuits. Determining the justification sequence for a state is conjectured to be an NP-hard problem and so is finding a differentiating sequence for a state pair. For both these steps, the entire STG of the machine might have to be enumerated (especially if the excitation state is not reachable from the reset state or if the true/faulty states are equivalent).

It can be shown that a fault in a general, fully specified, synchronous sequential circuit, like the one shown in Figure 2.1, may require a test sequence of up to  $2^{n+1} - 1$  input vectors, where n is the number of memory elements in the machine. To show this, consider the true and faulty machines and their STGs. Each of these STGs can have a maximum of  $2^n$  states. The two STGs can be concatenated, and a test (if it exists) will be the differentiating sequence for the two reset states. Since there can be  $2^{n+1}$  states in the concatenated machine, the longest differentiating sequence can have as many as  $2^{n+1} - 1$

vectors [83]. This shows that the search space for sequential test generation is very large. In fact, if there are i primary inputs, then the total search space is  $2^{i+n+1}$ . To add to the complexity of test generation, some faults in the circuit may be redundant, *i.e.*, the behavior of the circuit does not change in the presence of the fault. There are two classes of redundancies [90] in a sequential circuit — combinational redundancies and sequential redundancies. For a combinationally-redundant fault (CRF), the effect of the fault cannot be propagated to the primary outputs or the next-state lines, beginning from any state and using any input vector. A sequentially-redundant fault (SRF) is a fault which cannot be excited or whose effect cannot be propagated to the primary outputs using any sequence of input vectors starting from the reset state of the machine. Since such faults are very difficult to identify, large amounts of effort can be spent in trying to generate tests for them.

For the combinational logic (Figure 2.1) in the sequential circuit, there are p primary inputs, n present-state and next-state lines, and q primary outputs. The combinational logic implements a multiple-output Boolean function,  $f:B^{p+n}\to B^{q+n}$ , where  $B=\{0,1\}$ . Each of the primary outputs or next-state lines are single-output functions of p+n variables.  $B^{p+n}$  is referred to as the input space and  $B^{q+n}$  is referred to as the output space for the function [16]. The ON-set,  $X_{ON}\subseteq B^{p+n}$ , of a primary output or next-state line is the complete set of input values such that the primary output or next-state line is 1. Similarly, the OFF-set,  $X_{OFF}\subseteq B^{p+n}$ , is the complete set of input values for which the corresponding line is 0. The set of cubes C, is said to be a cover for a ON-set if  $X_{ON}\subseteq C$  and C does not intersect  $X_{OFF}$ .

The fanout of a gate  $\mathcal{G}$  (or a wire) is defined as the set of gates that use the value generated by  $\mathcal{G}$  as an input. The **transitive fanout** of  $\mathcal{G}$  is defined recursively as follows. If  $\mathcal{G}$  is a gate generating only a primary output, then its transitive fanout is the null set. Else, the transitive fanout of  $\mathcal{G}$  is the union of the fanouts of  $\mathcal{G}$  and the transitive fanout of every element in the fanout of  $\mathcal{G}$ .

The initial state of the machine before a test vector is applied or right after it is powered up may or may not be known. The fault model used in test generation also varies. The following assumptions are made regarding the sequential circuit to be tested:

1. The machine is assumed to have a reset state, R. All test sequences are applied with this state as the starting state.

- 2. The fault model is assumed to be single stuck—at. Since the state justification and differentiation parts of the test generation algorithm are independent of the fault model, the algorithm is not restricted to only this fault model. Other fault models like multiple stuck-at, bridging faults, etc., may be used with minor modifications to the procedure described.

- 3. The memory elements are considered as distinct logic primitives and faults inside the memory elements are not considered. However, all faults on present-state and nextstate lines are considered. In general, these faults model a large fraction of the faults inside the memory elements.

#### 2.2 Previous Work

Initial work in tackling the problem of test generation involved the use of both random [20, 118] and deterministic techniques [95, 97, 108, 123]. In random test pattern generation techniques, a sequence of random patterns is generated and applied to the circuit. In general, all primary inputs to the circuit are excited equally, i.e., the average number of transitions on each primary input is the same over a long period of time. In some random test pattern generators, inputs are assigned different weights and inputs with more weights are exercised more frequently than others [118]. Different distributions can be used for the random number generator from which the random patterns are derived. Though the test generation time is small, the fault coverage obtained is not satisfactory. Also, the number of test vectors required is often too large to be used as a practical test set. Moreover, redundant faults cannot be identified.

Some test generation algorithms were developed that use the iterative array model [21] of the circuit and combinational test generation techniques to generate tests for sequential circuits [95, 97, 108, 123]. All these approaches start with one copy of the combinational logic block of the machine and use combinational test generation algorithms like PODEM [65] or FAN [60] to find a test for the fault. If a test is not found, another copy of the circuit is added and the process continues. The major drawback of this approach is the complexity of finding a test vector in an iterative array model of the circuit. Since the length of the test vector is not known a priori, a large amount of effort may be wasted in trying to generate tests in an iterative array model with an inappropriate number of copies of the circuit. In

[21], it was shown that the complexity of the extended D-Algorithm is  $4^n$  where n is the number of latches in the circuit. Though minimum length test vectors are produced, this approach can only be applied to small sequential circuits.

A heuristic, simulation-based test pattern generation algorithm is described in [1]. Starting with an initial vector, the final test sequence is derived using a fault simulator. For each vector applied, a cost function is computed which indicates whether the fault is excited or if the effect of the fault is propagated closer to a primary output. This cost function guides the selection of subsequent test vectors to be applied. The process continues until the fault is detected or a limit is reached. This is a pseudo-random approach and therefore does not guarantee that a test will be found, even when one exists. Also, redundant faults cannot be identified. However, this approach does not require the existence of a reset state. The simulation-based algorithm can find input vector sequences that set the required latches to a known value. However, there is a danger in not assuming a reset state for a certain class of circuits. Figure 2.4 shows a machine whose latches cannot be initialized using the simulation technique of CONTEST. In such a case, CONTEST would indicate that 100% of the faults in the circuit are untestable. In real life, the designer would ensure that the machine starts in one of the valid states, and assuming any of the valid states as reset state, 100% fault coverage can be obtained. It has also been shown [34] that even if a machine has a synchronizing sequence, then a fault may prevent the initialization of some latches in the circuit making the task of test generation difficult, if not impossible.

Recently, there has been considerable progress in this area. A PODEM-based deterministic approach to sequential test generation is described in [90]. This approach uses the iterative array model for fault excitation and propagation and makes intelligent use of a partial State Transition Graph (STG) of the circuit while generating justification sequences for the faults under test. Before test generation, the STG of the fault-free machine is extracted using the STG enumeration technique of [46]. The STG is used for finding justification sequences for the excitation states. Fault excitation and propagation is performed using the iterative array model of the circuit, considering the effect of the fault in each time frame. This approach can test circuits more efficiently than the approaches described previously in this section. However, this approach is not applicable to circuits with more than 100 latches. For such circuits, only a partial STG can be generated. Since the excitation states for the faults are not known a priori, the parts of the STG to be enumerated are not known. Therefore, a significant number of excitation states might not be justifiable.

Figure 2.4: A machine illustrating problem with initialization

### 2.3 Test Generation Strategy

Three major characteristics of the test generation algorithm to be described distinguish it from previous approaches. They are:

- Decomposition of the testing problem into three subproblems of derivation of the excitation state, state justification, and state differentiation. As will be seen later, this decomposition makes the reuse of information possible, thereby improving the efficiency of test generation.

- Fault-free state justification and differentiation.

- Selective enumeration of the state transition graph, as required for test generation.

In this section the overall test pattern generation strategy that uses these ideas is presented.

Information about state transitions in sequential machines is traditionally represented using State Transition Graphs. It is also possible to represent this information using the ON-sets and OFF-sets of all the next-state lines and the primary outputs. Connectivity (i.e., connectivity between states) can be represented by the ON and OFF-sets of the

next-state lines only.

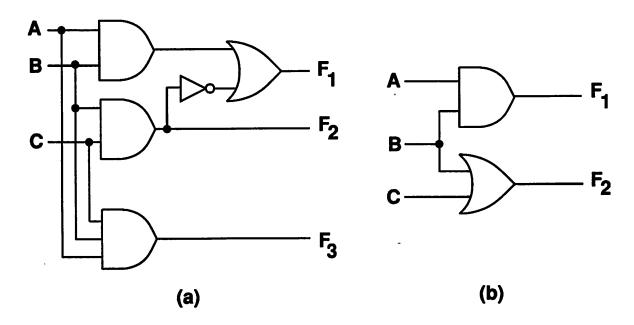

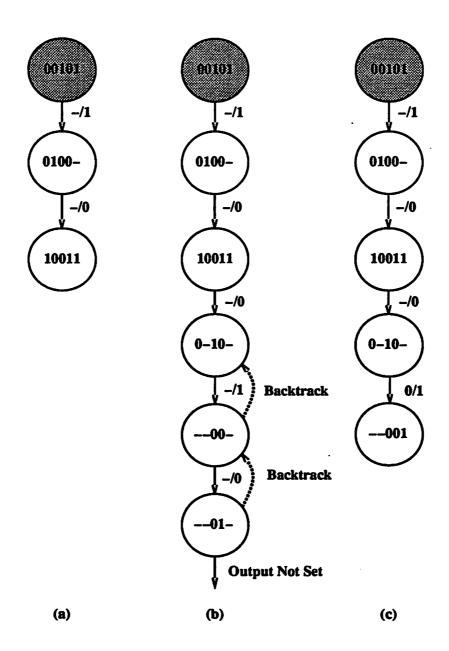

The first step in test generation is the enumeration of the partial or complete (memory and CPU time permitting) ON and OFF-sets of each next-state line and primary output of the sequential circuit to be tested. Cover enumeration can be performed using a PODEM-based [65] or D-Algorithm-based [115] enumeration algorithm. A limit on the number of cubes in each ON or OFF-set can be placed. This limit is used to restrict the amount of memory and CPU time used for enumeration. Cover enumeration is fast and full covers of moderately large circuits can be extracted easily.

Given the complete (or partial) covers, test generation is a three-step process. These three steps are:

- 1. Derivation of the excitation state for a fault using combinational test generation, treating the present-state (PS) lines also as primary inputs (PIs) and the NS lines also as POs.

- 2. State justification.

- 3. State differentiation.

In theory, the justification sequence should be derived using the faulty machine. Also, the differentiating sequence should be derived using the fault-free and the faulty machines. It has been observed that a fault typically modifies a few edges in the State Transition Graph. If a justification or differentiating sequence is derived using the fault-free machine, the probability of that sequence being valid in the faulty machine is high. Therefore, the fault-free state justification and differentiation heuristic is used. There are several advantages of using this heuristic. Firstly, covers of the fault-free circuit can be used to generate these sequences on demand, and covers do not have to be extracted for each fault. Secondly, parts of the justification and differentiating sequence can be reused, saving time. Consider the examples used to illustrate the problem of test generation in Figures 2.2 and 2.3. The fault-free justification sequences derived for state  $\mathcal A$  and  $\mathcal C$  are  $\{1\}$  and  $\{0,0\}$  respectively and both are valid in the faulty machine. A fault-free differentiating sequence between state  $\mathcal B$  and  $\mathcal A$  is  $\{1\}$ , and it is also valid in the faulty machine. Of course, there are faults that modify the STG drastically, but test generation for such faults is relatively simple.

After combinational test generation, the excitation vector is examined to see if the present-state part of the excitation vector covers the reset state. If the excitation state covers the reset state, then the fault can be excited from the reset state of the machine. If not, the excitation state is justified using a backward justification algorithm. Backward justification is performed by first finding all the fanin states of the excitation state (states that have an edge in the STG going from them to the excitation state) using repeated cube intersections. If the reset state is a member of the set of fanin states, then a one vector justification sequence is found. Otherwise, the process is repeated for some state in the fanin of the state being currently justified. Once a justification sequence is found, it is fault simulated to see if the required state is justified. If the required state is justified, then the justification sequence is a valid justification sequence in the faulty machine. If the required state is not justified, then some edge in the justification path must have been corrupted. A part of the justification sequence can then be used as a justification sequence for the state whose fanout edge was corrupted by the fault. State differentiation can then be performed between the corresponding true and faulty states. Thus, only one fault-free justification has to be performed to obtain a true and faulty state pair (cf. Section 2.5).

If the effect of the fault under test has been propagated to the primary outputs by the combinational test vector and if the excitation state can be justified in the faulty machine, then a successful test for the fault has been generated. If, however, the effect of the fault is propagated only to the next-state lines, then the fault-effect has to be propagated to some primary output by state differentiation. This is performed by first finding an input vector that produces a different output on at least one primary output line for the true and the faulty states. Such a vector constitutes a single-vector differentiating sequence between the true and faulty states. If a single-vector differentiating sequence cannot be found, all the fanout states of the true and faulty states are found using repeated cube intersections. Then, for each pair of fanout states a single-vector differentiating sequence is sought. If no such pair exists, then a pair of states fanning out from some fanout state pair is picked and differentiation between this pair is attempted. This differentiating sequence obtained is valid under fault-free conditions. After the differentiating sequence is obtained, the entire test sequence is fault simulated to see if the fault under test is detected. As shown later, experimental evidence gathered to date indicates that most of the time, the sequence generated is actually a test for the fault.

If a test is not valid for the fault under consideration, then the fault-free differentiating sequence is not a valid differentiating sequence under faulty conditions. Sometimes a fault-free differentiating sequence might not be obtainable because the true and faulty states are equivalent in the true machine. For such rare cases, the covers of the ON and OFF sets of the PO and NS lines are extracted assuming that the fault is present in the circuit. Differentiation is now attempted using the true and the faulty covers of the circuit. The differentiating sequence obtained can be guaranteed to be valid under faulty conditions (cf. Section 2.6).

At this point it is necessary to look at the assumption of having a reset state in more detail. The reset state acts as a reference state from which all test vectors are applied. The justification procedure looks for a sequence of vectors that will take the machine from this reference state to the fault excitation state. If there is no such reference state, it might not be possible to justify excitation states by the procedure outlined here. In Section 2.2, the problem of not assuming a reset state for the test generator CONTEST was presented. In addition, to ensure that the machine starts in some proper state, most designers incorporate a reset state. Therefore, the assumption of having a reset state is realistic. This reference state can be produced in a variety of ways. It could be provided as a reset line that sets the machine to a particular state or it could be derived by applying a sequence of vectors (called the synchronizing sequence) to the machine that will take the machine, irrespective of its starting state, to a known state. However, faults can invalidate a synchronizing sequence and make it impossible to generate tests. In general, the reset state can be a cube state, i.e., there might be don't-care entries in the reset state. Such a reset state is interpreted to mean that all the minterm states covered by the cube reset state are valid reset states for the machine, as the machine can be driven to any of those states using a known sequence of input vectors. For a certain class of circuits, like microprocessors, only the latches in the controller are initialized first, and then the other registers in the processor are initialized. These other registers can be set to any value by selecting the right inputs during the initialization phase. For such circuits, the reset state is a cube state.

As in some combinational test generators [20] and in some sequential test generators [118], random test vector generation is used as a front end to the deterministic test generation algorithm. Random vector test generation helps in detecting some of the easy to detect faults without much effort and therefore reduces test generation time. However, unlike combinational circuits where sometimes a large percentage of the faults can be detected using random techniques, for sequential circuits, only a moderate percentage of the faults can be detected.

The test generation algorithm based on the ideas presented above is as follows:

- Extract the complete or partial covers of the ON-set and OFF-set of primary outputs and next-state lines.

- 2. Generate a (new) combinational test vector for the fault under test. If test vectors for the fault have already been generated and some of the excitation states were not justifiable, the new test vector has the present-state part disjoint from the present-state part of all such previously generated test vectors. If no new test vector can be found, then exit without a test.

- 3. Generate a (new) fault-free justification sequence  $J_S$  for the excitation state. If no new justification sequence is found, go to Step 2.

- 4. Fault simulate the potential justification sequence  $J_S$ . If it detects the fault, generate a test sequence  $T_S$  directly from  $J_S$ . If it is a valid justification sequence, then go to Step 5. If it is not a valid justification sequence, then find the *first* state whose fanout edge was corrupted by the fault. Use part of  $J_S$  as the justification sequence for that state, and try to differentiate between the new true and faulty state pair.

- 5. Generate a fault-free differentiating sequence  $D_S$  for the true-faulty state pair. Concatenate  $J_S$ , the excitation vector, and  $D_S$  to obtain the test sequence  $T_S$ . Fault simulate  $T_S$ . If the fault under test is detected, exit with test vector  $T_S$ . If the fault is not detected, try to generate another  $D_S$ . If unsuccessful or if  $D_S$  is not found, go to Step 6.

- 6. Extract the faulty cover of the PO and NS lines. Set the unspecified inputs in the justification sequence to 1 or 0 and simulate the circuit to derive a true and faulty state pair. Generate a differentiating sequence  $D_S$  under faulty conditions. Concatenate  $J_S$ , the excitation vector, and  $D_S$  to obtain the test sequence  $T_S$ . Fault simulate  $T_S$  to find other faults that this sequence detects.  $T_S$  is guaranteed to be a test for the fault under consideration. Exit with test vector  $T_S$ . If  $D_S$  cannot be found and all possible assignments to unspecified inputs have been exhausted, go to Step 3. Else, set the unspecified inputs in the justification sequence to a different value and repeat this step.

By checking for the validity of the justification sequence before state differentiation, the need for generating more than one justification sequence in each pass of the algorithm is obviated. The algorithm is complete, i.e., if a test exists for a fault, then given enough time and memory the algorithm will find it.

Since justification and differentiating sequences are derived using the fault-free machine, a significant fraction of these sequences can be reused and are therefore stored. In effect, parts of the State Transition Graph (STG) that are required for test generation are explicitly enumerated. Enumeration of only the required parts of the STG results in significant memory and CPU time savings over the approach of [90].

An important part of any test pattern generator is the fault simulator used to grade the test patterns. Significant amount of research has been done in this area. To date, there exist efficient algorithms for fault simulation, both for combinational and sequential circuits [6, 88, 99, 107, 120, 130]. Since the focus of this research was the development of efficient test pattern generation algorithms, a simple, parallel, event-driven sequential fault simulator was used to grade the test patterns. More sophisticated fault simulation algorithms like concurrent fault simulation can help in speeding up the total time required for test pattern generation.

Finally, though covers are used for justification and differentiation, it is also possible to use alternate representations, like reduced, ordered Binary Decision Diagrams [26], for the implementation of the general principles presented in this section and the three sections that follow.

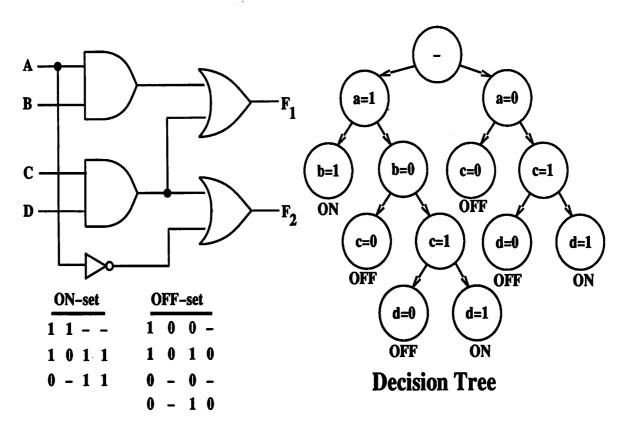

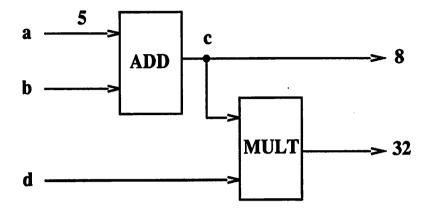

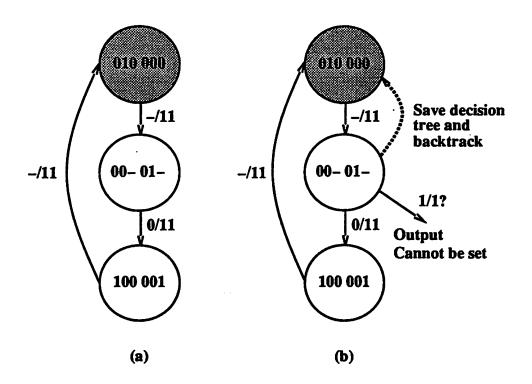

### 2.4 Cover Extraction and Combinational Test Generation

The input to the test generator is the combinational logic specification of the finite state machine with the latch inputs and outputs properly identified. For each primary output and next-state line, the ON-set and OFF-set are derived by setting the corresponding line to a 1 or 0 and using PODEM [65] to implicitly enumerate the input combinations that can set the line to a 1 or 0. For example, for the circuit shown in Figure 2.5,  $F_1$  is set to 1 and the backtrace procedure of PODEM sets input A to 1 and then input B to 1. Upon simulation, it is found that  $F_1$  is 1 and therefore 11 - - is a cube in the ON-set of  $F_1$ . Both the inputs and their values are stored in a decision tree. After the output is set to a value, the last decision in the tree is reversed, *i.e.*, B is assigned the value 0. In order to set  $F_1$ , more inputs have to be set. The backtrace procedure identifies input C and sets it to 0. Upon simulation, the value of  $F_1$  is determined to be 0, and therefore