Copyright © 1991, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### AUTOMATED DESIGN MANAGEMENT USING TRACES

by

1

Andrea Casotto

Memorandum No. UCB/ERL M91/22

15 March 1991

### AUTOMATED DESIGN MANAGEMENT USING TRACES

by

Andrea Casotto

Memorandum No. UCB/ERL M91/22

15 March 1991

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### AUTOMATED DESIGN MANAGEMENT USING TRACES

by

Andrea Casotto

Memorandum No. UCB/ERL M91/22

15 March 1991

.

## **ELECTRONICS RESEARCH LABORATORY**

.

College of Engineering University of California, Berkeley 94720

#### **Automated Design Management Using Traces**

Andrea Casotto

Department of Electrical Engineering and Computer Sciences, University of California, Berkeley.

#### Abstract

The productivity of modern CAD systems can be increased with a layer of software, called the "automatic design manager," whose goal is to provide services such as automatic sequencing and scheduling of the tools, coordination of team design and tracking of the design activity for documentation purposes.

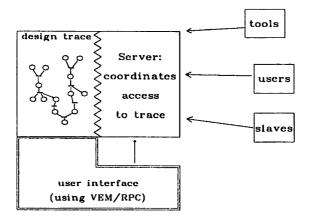

An automatic management system for CAD is proposed, based on the idea that CAD tools can leave a "trace" of their execution. The trace is represented as a bipartite directed and acyclic graph in which the nodes represent either design data or CAD transactions. The trace is both a record of the design activity and a graph representing the dependencies among the design objects. The architecture of the system is distributed: a server manages the trace, while a number of clients can concurrently interact with the trace through the server. The system supports the notion of measurement on the design data, necessary to provide even more services such as tracking of design specifications, validation of design data, design estimation. The system is non-intrusive, because it does not affect the way designers interact with the tools.

The design manager has been implemented in a system called VOV. This prototype has been tested by many designers, including novices and experts. The results of these tests are reported.

al-

Professor Alberto Sangiovanni-Vincentelli Thesis Committee Chairman

#### Acknowledgements

Finally a pause, a blank page to reflect upon the many people to whom I owe thanks.

My advisor, Alberto Sangiovanni-Vincentelli. He directed me towards design management and made available the resources for this research. Although I could never get enough of his time, I need to thank him for his guidance and his trust. I thank my other advisor, Prof. Richard Newton, for steering me away from the formalism of Petri nets and for his poignant criticism. He has contributed to form a large part of the ideas presented in this thesis. I consider myself lucky to work with these two stars of the CAD world. I only regret not having been able to defeat either of them in a tennis match.

Prof. Randy Katz is acknowledged for suggesting the use of the word "trace" in the context of design management and for helpful discussions in the early stages of this research. I thank Prof. John Wawrzynek for being the first to trust VOV and to use it in his classes. Prof. Alice Agogino has been kind accepting to be on my dissertation committee.

My office mates Mark Beardslee, Mitch Igusa and Chuck Kring, have been patient and helpful, they have tolerated my demos and even tried the earliest and buggiest versions of the system. Chuck has been especially cruel in dissecting a draft of this thesis, and I owe it to him if this thesis is now much more readable. The *Octtools* developers, in particular Rick Spiekelmier and David Harrison, have produced a tremendous amount of great code that now is also part of VOV. I thank them all. Gregg Whitcomb has invested a lot of energy into maintaining g++, which made the development of VOV so much simpler.

The students in CS292i, who were the first to use VOV in Spring 90, and the students in CS250, who were the first to use the assistant in Fall 90, have been instrumental in the progress of this research.

Flora Oviedo, Irena Stanczyk-Ng, and Elise Mills, who really run the show here in Cory Hall, have always been helpful in all office related matters. SRC has provided financial support throughout my five and a half years as Graduate student.

# Contents

| Ta | Table of Contents |                            |                                                |    |  |  |

|----|-------------------|----------------------------|------------------------------------------------|----|--|--|

| 1  | Introduction      |                            |                                                |    |  |  |

|    | 1.1               | A char                     | acterization of electronic design              | 3  |  |  |

|    | 1.2               | Requir                     | ements of an automatic design manager          | 7  |  |  |

|    | 1.3               | Background on the Octtools |                                                |    |  |  |

|    |                   | 1.3.1                      | The Octtools                                   | 10 |  |  |

|    |                   | 1.3.2                      | Brief history of VOV and the Octtools          | 13 |  |  |

| 2  | Previous Work     |                            |                                                |    |  |  |

|    | 2.1               | Repres                     | entation of the design activity                | 16 |  |  |

|    |                   | 2.1.1                      | Ad-hoc models for VLSI design                  | 16 |  |  |

|    |                   | 2.1.2                      | General models for design activity             | 20 |  |  |

|    |                   | 2.1.3                      | Design environments                            | 33 |  |  |

|    | 2.2               | Intrusi                    | veness of implementation                       | 34 |  |  |

|    | 2.3               | Classif                    | ication of tools and data                      | 35 |  |  |

|    | 2.4               | Artific                    | ial intelligence techniques                    | 37 |  |  |

|    | 2.5               |                            | in data management                             | 38 |  |  |

|    | 2.6               | Comm                       | ercial systems                                 | 40 |  |  |

|    | 2.7               | Conclu                     | usion of the survey                            | 41 |  |  |

| 3  | The               | Design                     | Trace                                          | 43 |  |  |

|    | 3.1               | Design                     | management based on design traces              | 43 |  |  |

|    |                   | 3.1.1                      | Non-intrusive tracing                          | 44 |  |  |

|    |                   | 3.1.2                      | The trace                                      | 45 |  |  |

|    |                   | 3.1.3                      | An example trace                               | 48 |  |  |

|    | 3.2               | The tra                    | ace as a definitional language                 | 50 |  |  |

|    |                   | 3.2.1                      | Backtracking                                   | 51 |  |  |

|    | 3.3               |                            |                                                | 52 |  |  |

|    |                   | chitecture                 | 53                                             |    |  |  |

|    |                   | 3.4.1                      | Communication between the tools and the server | 55 |  |  |

|    |                   | 3.4.2                      | Affinity of transitions                        | 57 |  |  |

|    | 3.5               | Interac                    | tive tools                                     | 59 |  |  |

|    |                   |                            |                                                |    |  |  |

|    | 3.6  | The firing rule                                  |                                                    | 60       |

|----|------|--------------------------------------------------|----------------------------------------------------|----------|

|    | 3.7  | Trace versus Petri net                           |                                                    | 61       |

|    | 3.8  | Sets of nodes                                    |                                                    | 62       |

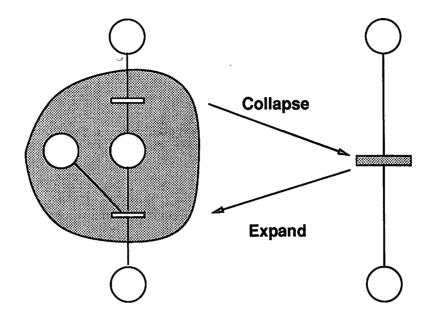

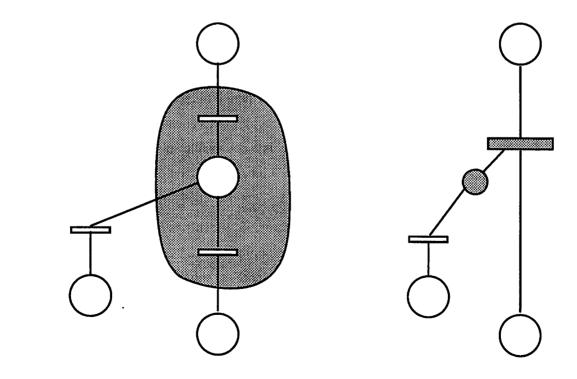

|    |      | 3.8.1 Hierarchy in the trace                     |                                                    | 64       |

|    | 3.9  | Services                                         | s                                                  | 67       |

|    |      | 3.9.1                                            | Service: Design documentation                      | 67       |

|    |      | 3.9.2                                            | Service: data monitoring                           | 70       |

|    |      | 3.9.3                                            | Service: retracing                                 | 70       |

|    |      | 3.9.4                                            | Service: Conflict detection                        | 73       |

|    |      | 3.9.5 Management of refinements and alternatives |                                                    | 74       |

|    |      | 3.9.6 Archiving                                  |                                                    | 76       |

|    | 3.10 | Use of r                                         | measurements                                       | 76       |

|    | 3.11 | The assi                                         | istant                                             | 78       |

|    | 3.12 | Support                                          | of design methodology                              | 84       |

|    | 3.13 | Iteration                                        | n in design                                        | 85       |

|    | 3.14 | Principl                                         | es that guided the development of VOV              | 87       |

|    |      | 3.14.1                                           | Simplicity                                         | 87       |

|    |      | 3.14.2                                           | Non-intrusiveness                                  | 89       |

|    |      | 3.14.3                                           | Distributed resources, localization of information | 89       |

|    |      | 3.14.4                                           | Focus on users                                     | 90       |

|    |      | 3.14.5                                           | Emphasis on team design                            | 91       |

|    |      | 3.14.6                                           | No restriction to data visibility                  | 92       |

|    |      | 3.14.7                                           | Ignore design hierarchy                            | 92       |

| .1 | 1    |                                                  |                                                    | 96       |

| 4  | -    | Itementation                                     |                                                    | 97       |

|    | 4.1  | 4.1.1                                            | Attributes of nodes                                | 97<br>97 |

|    |      |                                                  | Attributes of places and transitions               | 97<br>97 |

|    |      | 4.1.2                                            | Canonical names for files                          | 99       |

|    |      | 4.1.3                                            | The representation of the trace                    | 99<br>99 |

|    | 4.2  |                                                  | •                                                  | 102      |

|    | 4.2  |                                                  |                                                    | 102      |

|    |      |                                                  | Robustness and safety                              | 102      |

|    | 4.2  | 4.2.2<br>Sefere                                  | re architecture                                    | 103      |

|    | 4.3  |                                                  | The hierarchy of classes                           | 105      |

|    |      | 4.3.1                                            |                                                    | 100      |

|    |      | 4.3.2                                            |                                                    | 110      |

|    | 4.4  |                                                  |                                                    | 110      |

|    |      | 4.4.1                                            | Server latency                                     | 111      |

|    |      | 4.4.2                                            | Capsule overhead                                   | 112      |

|    |      | 4.4.3                                            | Trace size                                         | 112      |

|    |      | 4.4.4                                            | Small designs                                      |          |

|    |      | 4.4.5                                            | Large designs                                      | 113      |

| 5 |      |                |                                                 |     |  |

|---|------|----------------|-------------------------------------------------|-----|--|

|   | 5.1  | Statisti       | cs on the design                                | 115 |  |

|   | 5.2  | BRIC .         |                                                 | 117 |  |

|   | 5.3  | Floorpl        | anning an FPU                                   | 118 |  |

|   | 5.4  | -              | lation of VOV                                   | 119 |  |

|   | 5.5  | -              | n a VLSI design course                          | 120 |  |

|   |      | 5.5.1          | The laboratory exercises                        | 120 |  |

|   |      | 5.5.2          | The final project                               | 126 |  |

|   |      | 5.5.3          | Comment                                         | 127 |  |

|   |      | 5.5.5          |                                                 | 127 |  |

| 6 | Con  | Conclusion 12  |                                                 |     |  |

| Α | Tuto | 'utorial 1     |                                                 |     |  |

|   | A.1  | Introdu        | lction                                          | 132 |  |

|   | A.2  |                | RIAL: Design of a seven segment display driver  | 133 |  |

|   |      | A.2.1          | Start mini-VOV                                  | 133 |  |

|   |      | A.2.2          | Enter the assistant                             | 134 |  |

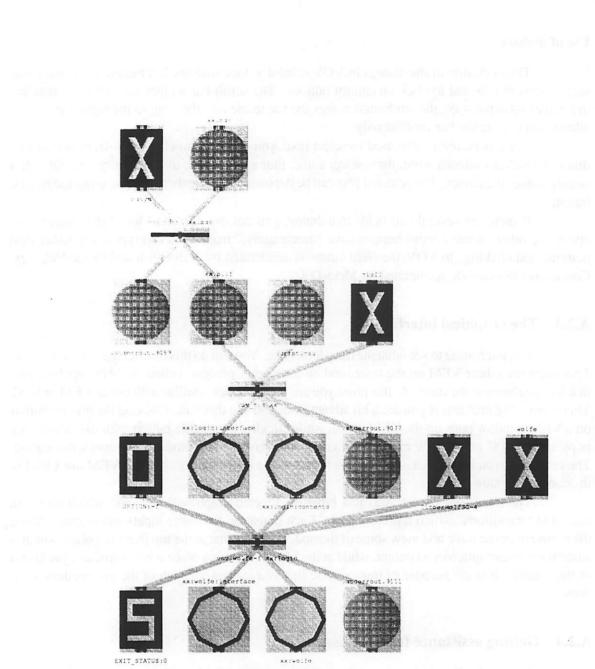

|   |      | A.2.3          | The graphical interface                         | 135 |  |

|   |      | A.2.4          | Getting assistance from the assistant           | 135 |  |

|   |      | A.2.5          | Your turn to act intelligent                    | 135 |  |

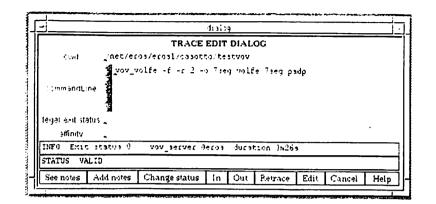

|   |      | A.2.5<br>A.2.6 |                                                 | 138 |  |

|   |      | A.2.7          | The trace as a dependency graph                 |     |  |

|   |      | A.2.7          | Validity of nodes                               | 140 |  |

|   |      | A.2.9          | Automatic retracing                             | 142 |  |

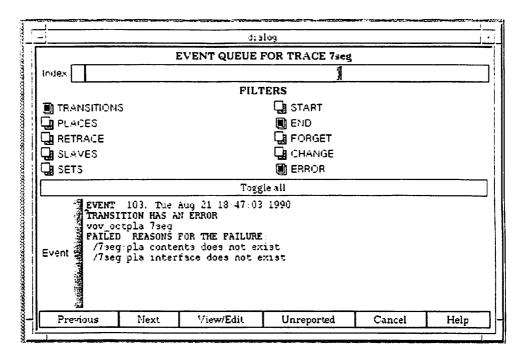

|   |      |                | Review what has happened                        | 142 |  |

|   |      |                | Possible problems                               | 144 |  |

|   |      |                | Substitution a transition                       | 145 |  |

|   |      |                | Check the results                               | 145 |  |

|   |      |                | Try something new                               | 145 |  |

|   |      |                | Suspension or end of the exercise               | 148 |  |

|   | A.3  |                | RIAL: Second part                               | 148 |  |

|   |      | A.3.1          | What does vov_mini really do                    | 148 |  |

|   |      | A.3.2          | Add many slaves to your server                  | 149 |  |

|   |      | A.3.3          | Start the server                                | 150 |  |

|   |      | A.3.4          | Clients                                         | 150 |  |

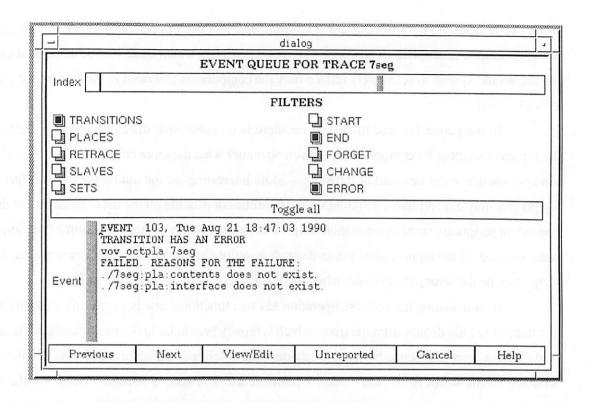

|   |      | A.3.5          | The event queue and the journal                 | 151 |  |

|   |      | A.3.6          | The event queue                                 | 151 |  |

|   |      | A.3.7          | The trace                                       | 151 |  |

|   |      | A.3.8          | Annotations                                     | 152 |  |

|   |      | A.3.9          | Affinity of transition, interactive transitions | 152 |  |

|   |      | A.3.10         | Graphical interface using vem/RPC               | 153 |  |

|   |      |                | Status of the trace                             | 153 |  |

|   |      |                | Protection                                      | 154 |  |

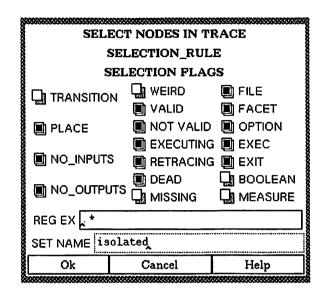

|   |      |                | Sets                                            | 154 |  |

|   |      |                | Forgetting nodes                                | 154 |  |

|   |      | A.3.15         | Moving stuff around the file system             | 154 |  |

|   |      |                |                                                 | 107 |  |

.

and a second s • 1.1 .... and a second n an Alexandria Alexandria Alexandria Alexandria Alexandria Alexandria en ale en estado en el constructione en el construction na series de la companya de la comp Nome de la companya d Nome de la companya d • 1 - Sector State • • • • LSI Bibliography 9SI B Quick Tool Overview • SSI ļ٨

11 M 1

•

· · ·

# Chapter 1

# Introduction

The complexity of modern human artifacts such as microprocessors, aircraft, and satellites, demands the power of computer tools to assist the designers in many of the design tasks. This is particularly true in the electronic industry, which routinely deals with millions of components. In recent years, CAD systems have come a long way towards freeing the designers from the complexity of design, but designers now have to cope with the ever growing complexity of the CAD systems themselves.

Electronic design is the focus of this dissertation, because of the training of the author. However, an ill concealed ambition of this work is to be applicable in other domains of automatic design, that is wherever computers are used to assist the designers.

A "CAD system" is a collection of software programs that perform many tasks related to the analysis and synthesis of electronic systems, such as integrated digital circuits, microprocessor and printed circuit boards. Each autonomous component in a CAD system is a "tool." CAD systems typically include, among others, tools to describe the behavior of electronic components, to simulate a circuit, to synthesize logic equations, to generate, optimize, and verify layout.

CAD systems take many forms, varying in user interface, capabilities, target technology, the number and complexity of the tools, and the way in which the tools communicate with each other. However, all systems seem to share this unwanted characteristic: they are difficult to learn, to use, and to master. There is a need for a new layer of software that can help the designers cope with the tools in a CAD system. This new software is the "automatic design manager." A design manager provides new forms of automation of the design activity: protection of the integrity of the design data, guidance for the novice designer, and advice for the cxpert.

The focus of an automatic design manager is directed more towards the design method-

ology than towards the pursuit of the design solution. "Design methodology" is the sequencing of the design tasks and the ordering in which the CAD tools are used, while the definition of "design solution" is left for now to the intuition of the reader.

The interest developed by the CAD community in automatic design management has strong industrial roots, namely the need to increase the productivity of CAD systems. But besides the utilitarian interest, design management also raises some genuinely theoretical questions regarding our understanding of the design process itself, as presented in the following sections and in the survey of previous work.

The breadth of this young discipline is such that the relevant literature is hardly bounded. Adjacent disciplines from which design management borrows freely include operating systems, data management, system modeling, and information modeling.

The system presented in this dissertation is a concrete proposal for an automatic design manager. A prototype of the system, implementing all of its essential features, has been developed, and it has been tested by many designers with various degrees of experience. This prototype is called VOV.<sup>1</sup> Sometimes the name "VOV" is used to refer to the abstract proposed system, rather than to the prototype.

This dissertation starts with an enumeration of the issues related to an effective use of CAD systems. An even superficial overview reveals that the issues are many and that they appear to be heterogeneous: automation of the design flow, bookkeeping of design alternatives, automatic documentation, coordination of team design, guidance for the inexperienced designer, and others. No issue has been discarded a priori, and an attempt has been made to provide a framework in which all these issues can find a natural setting.

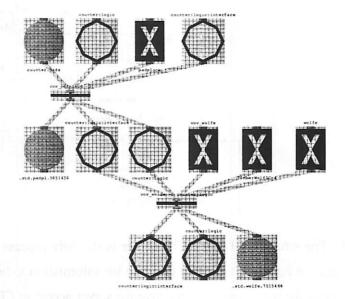

VOV's distinctive feature is that it does not attempt to *lead* the designers, telling them what is legal and what is not. Instead, the system *follows* the designers and keeps a *trace* of their activity. The trace is a graph that is used at once as the historical record of the design process, as a representation of the dependencies among the design data and as an executable program to sequence and schedule the tools. The trace is built automatically and non-intrusively with information generated by the tools at runtime. The server/client architecture used for the system is important to support multi-user designs and distributed processing.

The trace is the basis to provide many design management services: the consistency of the design data can be monitored and maintained, the design flow can be automated, concurrent tasks

<sup>&</sup>lt;sup>1</sup>VOV is also the name of an Italian liquor similar to a mixture of eggnog and rum, consumed preferably hot, in a cold winter day, and appreciated for its reinvigorating gusto.

| Table of acronyms |                                     |  |

|-------------------|-------------------------------------|--|

| ASIC              | Application Specific IC             |  |

| CAD               | Computer Aided Design               |  |

| IC                | Integrated Circuit                  |  |

| VLSI              | Very Large Scale Integration        |  |

| ADM               | Automatic Design Manager/Management |  |

| DMS               | Design Management System            |  |

Table 1.1: Acronyms used in this dissertation.

can be coordinated, and novice designers can be guided. The trace also integrates the notion of *measurement* on the design data, to provide other services such as tracking of design specifications and performance estimation.

Some issues that are often associated with design management are only indirectly addressed in this research. For example, there is no concern about management of human resources, about how to keep designers motivated and productive, how to schedule the work week, or how to complete a project on time and on budget. Nevertheless, an ADM can have an indirect but significant influence on these issues, if it makes the design activity faster, cheaper, and less frustrating.

The next Section contains some introductory comments on design and on the list of requirements for an automatic design manager. Chapter 2 contains a survey of previous work in design management. Chapter 3 contains a detailed description of the design trace and of its uses. Some implementation details are presented in Chapter 4, of interest to those who intend to implement their own trace-based design management system. Finally, the results obtained during the use of VOV in real designs can be found in Chapter 5. Appendix A consists of a tutorial introduction to VOV. A brief synopsis of the tools mentioned in the examples is found in Appendix B.

#### 1.1 A characterization of electronic design

The services provided by an automatic design manager depend greatly on the interpretation given to the notion of design. The dictionary (the on-line Webster's 7th Dictionary) suggests that a design is "a mental project or scheme in which means to an end are laid down." This is enough to agree on the fact that design is the conjunction link between some goals and their satisfaction, but it says nothing on how such a link is generated.

The goals of design are usually described as a set of constraints that must be satisfied si-

multaneously. Some constraints define the desired behavior and functionality of the solution, while others may be more domain specific. For example, in the design of an electronic system, domain specific constraints may be the minimum frequency of the operating clock, the maximum dissipated power, or the range of operating temperatures. Some design problems are characterized by the availability of a *cost function* that can be used to rank the proposed solutions by their estimated cost. These design problems are referred to as *optimization problems*, because their goal is to find a solution that minimizes the cost function.

The availability of complex and powerful CAD systems adds a new dimension to design. Design is now more than just a search of a solution to a given set of constraints; it is also a search for a methodology to produce such solution. The methodology should be automated, in the sense of minimizing the manual intervention of the designers, and it should take full advantage of the power of the tools. Contrast this with Bushnell's specific definition of VLSI design [10]:

VLSI chip design is essentially a search process in the design space at the floorplanning level, to find a floorplan that will lead to a correct and reasonably compact integrated circuit layout. (page 48)

We believe that design is also a search in the "methodology space." The designer has to describe not only "what" he wants, but also "how" he is going to get it. In electronic design this amounts to choosing an appropriate sequence of tool invocations.

Complex designs are often partitioned into smaller designs, which in turn may still be too complex and require further partitioning. This process adds a hierarchical structure to design. Depending on the strategy used to traverse the hierarchy, one talks about different design styles: in *top-down* design the focus is on how the constraints for the top-level problem are converted into constraints for the subproblems, while in *bottom-up* design the subproblems are solved before the top-level problem. It is also common to hear the loosely defined terms *yo-yo design*, and *meet-in-the-middle design*, which prove that reality is always more complicated than we would like it to be, and requires some acrobatic balance between the two extremes of top-down and bottom-up design styles.

Design need not be a linear process; instead, it is often iterative, because many actions need to be repeated to refine and optimize the design data, and tentative, because many alternatives are often explored [31].

Particularly stimulating and provoking is Sequin's definition of design: "design equal documentation" [45]. Documentation constitutes a fundamental aspect of design, especially in the context of a company that wants to protect itself against the risk of seeing large chunks of know-how

depart together with its transient designers. Equally important is the role played by documentation in the context of team design, as a communication medium between the components of the team. Designers, however, often perceive documentation as a distraction from their pursuit of the design goals, and tend to avoid it; hence the need to provide tools to support automatic documentation of the design process.

Design is the act of conceiving a plan with some purpose in mind. A plan is the final product of design, not an input or a constraint. Thus, design is *goal-directed* more than it is *plan-directed*. The designers are going to do whatever is necessary to achieve their goals. They can adopt a predefined design methodology (a plan) as long as they are performing routine activities. But if their design has some new or unique feature that stresses the limitations of the existing design methodology, the designers will not hesitate to change their course of action to achieve their goal.

During the design activity, a plan can be a useful resource but only a weak one. This notion of a plan as a weak resource is borrowed from Alison Lee's research on the use of the history mechanism as a means of support for human-computer interaction [35]. Lee's attention is on short-term interactions, such as a session with a UNIX shell, such as csh. This type of interaction is found to have two properties: it is *recurrent*, because users frequently repeat their actions, especially the most recent ones, and it is *situated*, in the sense that the actions *are never planned in a strong sense* because *the circumstances of the actions are never fully anticipated and are continuously changing*. Lee suggests that a history facility is the appropriate resource to *relate knowledge and action*. Such a facility consists of four components:

The *collection* component records past user-computer interactions into a history. The *presentation* component displays the history. The *selection/modification* component allows the user to copy (and possibly modify) a history item. The *submission* component allows the user to *use* the selected history item in the context of the current situation. ([35], page 4)

The history facility has many uses: it allows the *reuse* of an history item to reduce the number of keystrokes; it offers *navigation* information by reporting to the user *where they have been* and where they are, or *reminders* on the status of the system; it provides *examples* on how some commands can be sequenced to achieved certain goals; it can be the foundation for some automation services, such as *macro facilities*, automatic *playback* of command sequences, *prediction* of the next user command.

Computer aided design is also a form of human-computer interaction that, just like Lee's interactions, is repetitive and situated (goal directed). To be accurate, it should be pointed out that

computer aided design is a *long-term* interaction and that it normally involves a *team* of designers, but neither fact affects the role of history as portrayed by Lee.

In the next chapter we show that there is a common thread that unifies most of the previous work in design management, that is the focus on planning, expressed by the attempt to capture the complexity of the design activity a-priori. VOV is the only ADM that focuses on the design history as the fundamental vehicle of interaction with the designers.

Design is not always a creative process. Often design can reliably develop along a predefined plan, following a well established *routine*. One such example taken from the *Octtools* is the design of a standard-cell circuit starting from its behavioral description: an effective methodology calls for the execution of three automatic tools, bdsyn, misII, and wolfe, with each tool allowing just a few options to tune its behavior to the specific circuit. This methodology can be described in a UNIX script that captures the known capabilities of the tools and that makes them readily available to the users. For a routine activity, a simple script can be a very effective design management tool.

If design was purely routine, the design management problem would have been solved in large part with existing techniques, such as scripts or other programs. The need for a more sophisticated system exists because, although a fraction however large of the design is normally routine, it is the remaining fraction that is the most challenging one, the one the designers need most help with, and the one that cannot be captured in an a-priori plan. Our experience with the *Octtools* confirms that all designs have had some unique feature that required a special and innovative solution: a new tool was needed, or the capabilities of some tool had to be stretched, or new testing strategies had to be invented. Unpredictability of the methodology is a characteristic of many designs.

Finally, we consider the role of computers in the design process, and in particular the new opportunities offered by computers in terms of management of the design activity.

VLSI design is probably the most extensively computerized form of design. Almost all the design information is stored in a computer memory, and most of the design activity consists of the execution of computer programs. This extensive use of computers in VLSI design has two notable consequences. First, it accentuates the iterative and tentative character of design by making it easier for the designers to explore many alternatives. Second, it makes it possible to obtain a great deal of data about the design process in a non-intrusive way, that is without disrupting the activity of the designers. Intrusive systems that require the designers to explicitly record their decisions and their actions, only add burden onto the designers and are often rejected.

One kind of information that can easily be collected is the design history. Computers

allow, in principle, the recording of every keystroke and mouse movement, as a way to capture the complete history of a design. A more economical approach is to record all the tool invocations, which is precisely what is captured by the design trace. The design history is an objective way to document the design, because it records what has happened, although it does not always record why it has happened.

In conclusion, the design history is not only a candidate to provide many useful services, as supported by Lee [35], but it is also easy to collect automatically. That is why the design history, captured by the design trace, is the focus of this research.

#### 1.2 Requirements of an automatic design manager

An automatic design manager is a layer of software that assists the designers in their interaction with complex CAD systems. In this section we present a list of requirements of an ADM. The satisfaction of most or all of the items in the list is essential for the success of the ADM, that is for its acceptance in the users' community.

The first requirement is **user friendliness**, which requires an understanding of the users of the system. There is a variety of categories of potential users, and each category has different needs. Expert designers require a system that is powerful and non-intrusive, novice designers ask for simplicity and a high degree of automation, while project managers want to be able to exert control over the design process. Friendliness also implies a good user interface, a robust implementation, and a predictable behavior. Programmability of the user interface is important to give extensibility and power to the system.

Some may contend that the first requirement for an ADM should be a clear model of the design activity, complemented by a solid and effective set of algorithms that operate on the model. Models and algorithms are fundamental, but they require experimental validation, which is only possible with a strong user interface. Since an ADM is necessarily in close interaction with its users, its success is more dependent upon its user interface rather than upon its fundamental model or its algorithms. In fact, even good algorithmic solutions for design management can be made completely useless by a poor user interface.

An ADM should be **adaptable** and allow all existing tools to be easily integrated, because large and small corporations that may use the system wish to protect their current investment in CAD tools. The tool set may change because of the introduction of new versions of some tools, or of altogether new tools possibly coming from many different vendors, and the ADM should effortlessly allow such additions and changes.

As the tool set may change, so may the **design methodology**. The ADM must continue to assist the designers especially in the uncertain times in which the design methodology is evolving. Established design methodologies should also be supported, by offering a language to describe them and a technique to apply them in a design. Support can take the form of non-intrusive advice, as favored by expert designers, or of strict enforcement, as preferred by the project managers.

The most challenging requirement derives from the large set of **services** that should be provided by an ADM. The services fall into one of two categories: protection and automation. A service provides protection if it prevents or corrects errors related to the consistency of the design data. An important protection service is the coordination of team design, or, more generally, the **coordination of concurrent activities**. When many designers work on the same design, it is necessary to coordinate the efforts of each person in the team to avoid conflicts, duplication of effort, or waste of time. Coordination of team design is easily achieved by a *locking* mechanism that gives privileged access to some design data or resources to one designer at a time. The locking mechanism is conceptually simple, and its effectiveness depends on its *granularity*.

Another protection service is **consistency maintenance**, which is based upon the notion of *dependency* among the design data. For example, the extracted view of a circuit is normally derived from the layout view, and therefore it depends upon it. If the layout is modified, the extracted view is no longer up-to-date and must be regenerated. The ADM should recognize dependencies between objects, it should detect when consistency is lost and it should be able to perform the appropriate actions to recover consistency.

A related service is the **bookkeeping of the design data**. For each piece of data, we want to know how it has been obtained and whether it is referenced in other parts of the design. CAD systems compound the bookkeeping problem, because they allow the exploration of many design alternatives, leading to an inflation in the number of pieces of data that have to be managed.

All the protection services are made more difficult by the heterogeneity of the design data. Data are often stored in different databases and accessed using different procedures. In the *Octtools* for example, there is a coexistence of *facets*, which are the storage unit in the database OCT, and UNIX files, either executables or data files. An ADM should not make assumptions about databases.

The basic automation service is the **automation of the design flow**, that is the automatic sequencing, scheduling and execution of CAD tools. The ADM should know how to invoke each tools, taking care of all the options and of all the input and output data. Upon completion, it should check whether the tool was successful. The value of an ADM can be increased by some **job con**-

trol capabilities such as the dispatching of jobs to various machines on a local network, and the possibility of terminating jobs that are taking "too long," maybe because they are stuck in infinite loops.

There should be no need to stress the importance of **documentation of the design process**, but this service is often overlooked. The ADM should maintain a detailed history of the design, by keeping track of what has been done, by whom, and when. The system should also allow free annotation of the design.

Another service is assistance to novice designers, whereby the ADM guides the inexperienced user through the CAD system and offers advice on what to do next to achieve a design goal, or on how to fix a problem.

**Design estimation** is the capability of predicting the outcome of a design methodology without actually running the tools; it is an important component in **design decision support**, for example because it can help the designers choose one methodology instead of another. Estimation provides tentative answers to questions about the performance of some tools, such as *how fast will this chip be if I use this tool?*, or about the design process itself as in *how long will it take to route this chip?* Any estimation is a difficult task in itself and is best performed by specialized tools. An ADM should however recognize the importance of estimation in design, and it should be able to provide the estimation tools with the information they need.

The verification of design specifications is an essential element in the design activity, because it determines whether the design goals have been achieved and therefore whether the design activity can been terminated.

Upon completion, a design is normally archived so that it can be recalled at a later time. Archiving can be expensive; it requires the storage of all the design data and of all versions of the tools used in the design, and possibly even of a copy of the current operating system, as a form of protection against software evolution that are not backward-compatible. It is the ADM's job to indicate which data and which tools should be archived.

Finally, there is the important problem of coping with complexity: CAD systems may consist of more than a hundred tools, and some designs may produce many thousands of design objects. An ADM should be aware of this complexity and be efficient and responsive when dealing with very large designs.

#### **1.3 Background on the** Octtools

This research is based in large part on a CAD system developed at UC Berkeley and known as the *Octtools*. University software has some characteristics that make it a tough challenge for an automatic design manager, much tougher than the challenge represented by other industrial systems. University software is, first of all, the product of innovative research; its development often terminates once the research contributions have been made. Only occasionally the software is engineered and supported in order to provide an enabling platform for new research, or for educational purposes. University software tends to be relatively fragile, unsupported, undocumented, and rapidly changing, if compared with industrial strength systems. A design manager that successfully confronts all these difficulties in an imperfect CAD system, should stand a good chance in the world of commercial CAD systems.

Despite the historical symbiosis between VOV and *Octtools*, it should be emphasized that there is no dependency of one on the other and that the concepts in VOV are also applicable outside *Octtools*.

The next section is a brief introduction to the *Octtools*; it is included because some familiarity with this CAD system is useful to understand both the examples used in this thesis and VOV's implementation.

#### **1.3.1 The** Octtools

The Octtools are a set of loosely connected tools that operate with OCT, a system for data representation and storage management. [27]. OCT features a simple procedural interface and a general entity-relationship based data model that captures the information commonly used for the design of VLSI chips. Although OCT is not truly object-oriented in the C++ sense [48], it relies on the concept of data objects and relationships among them to represent the design. OCT objects have a *type* and a set of type specific *attributes*. The following objects are the most commonly used by the Octtools:

Facets: the facet is the fundamental unit for storing and manipulating design data in OCT. It has three main attributes called cell, view and facet. The cell represents the name of the design object described by the facet, for example it could be "2-INPUT-NAND". A cell can have many views to describe various aspects of it. For example the "physical" view can be used to describe the geometric layout of the cell, while the "logic" view describes its logic behavior. A view can have several facets, which are different representations of the view. The *Octtools* use only two facets: the "contents" facet, which contains the actual definition of the view, and the "interface" facet, which contains an abstraction of the view. It is convention to refer to OCT facets with the notation cell:view:facet, although often the last attribute is not mentioned and we just say cell:view.

- **Instances:** facets can be instantiated within other facets using the instance object. The instantiated facet is called the *master* of the instance.

- **Terminals and nets:** these objects are used to represent connectivity information. A terminal represents a connection point for facets and instances, a net represents a connection between terminals.

- Layers, Boxes, Paths and Polygons: these geometric objects are used to described the physical layout of a cell.

Bags and Properties: bags are used to group objects, properties to annotate them.

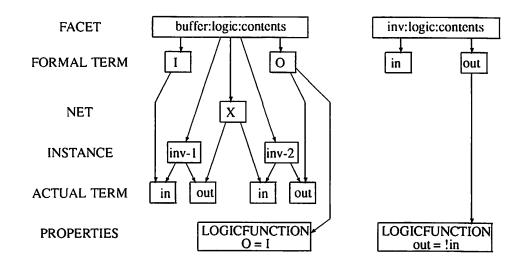

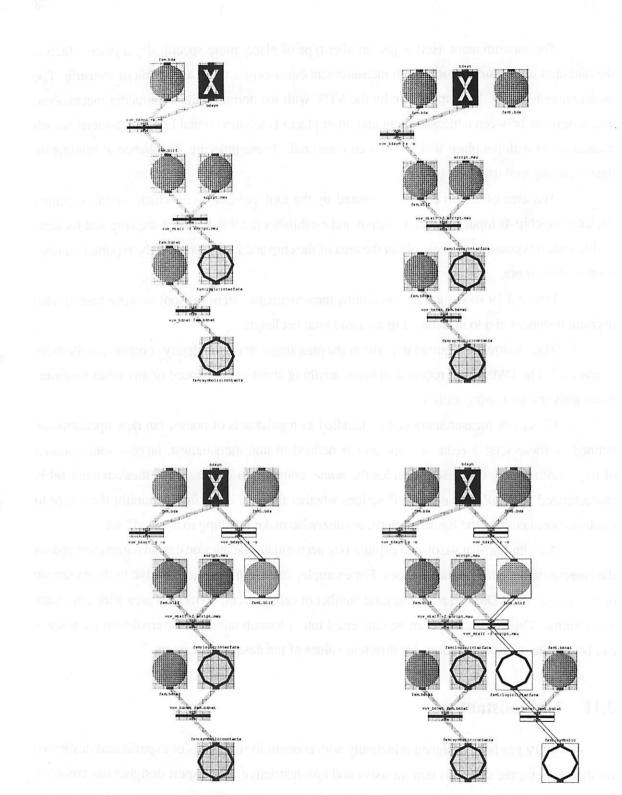

OCT supports the relationship "contains" and "is contained by," represented by a directed, unnamed arc. For example, in Figure 1.1 the net "X" is contained by the facet buffer:logic:contents and contains two terminals.

In order to allow flexibility of the data manager with respect to evolving needs in the design methodologies, OCT provides only a set of general *mechanisms* to allow creation, editing and retrieval of objects. This mechanism is independent of any particular design methodology or representation. Several *policies of use* have been chosen to specify how the mechanisms are to be used [32]. Adherence to these policies is the condition under which all of the *Octtools* can work on each other's output. This is the key to the success of the system.

VEM is the users' main channel of interaction with OCT because it provides the capability to view graphically and edit OCT facets. It also supports a remote procedure call protocol (RPC) that enables other OCT applications to register commands that can be invoked from within VEM.

A major feature of the *Octtools* is the capability to synthesize layout starting from a high level description of a combinational logic cell. The behavior of the cell is described using the language BDS. The program bdsyn translates the BDS description into a multi-level network of logic gates, stored in an ASCII format called BLIF. The program misII is used to optimize the BLIF description to minimize the area or the delay through the network. Depending upon the

Figure 1.1: A buffer can be built as a chain of two inverters. The OCT objects that describe the buffer are shown here. The inverter is represented by the graph on the right: there are two terminals attached to the facet, and the output terminal contains a property that describes the logic behavior of the inverter. The graph on the left represents the buffer. The net "X" connects the output terminal of the first inverter to the input terminal of the second.

desired design style, misII will perform a *technology mapping* of the logic network. For example, if a standard cell circuit is desired, then misII will use a description of a standard cell library to implement the logic network using the gates available in that library. A netlist of standard cells produced by misII can be placed and routed with wolfe. Alternatively, misII can map the logic network into a more restricted library of gates that are implemented with GEM, a gate-matrix module generator. A PLA can be obtained directly from a BDS description using octpla.

The logic simulator musa is a multi-level simulator of combinational and sequential circuits. It performs switch-level simulation and also understands higher level models, such as buffers, RAM's and various types of latches. The typical usage of musa requires the preparation of a *simulation script* containing the commands to be executed as well as the tests that have to be verified.

The Octtools emphasize symbolic layout, which allows the specification of the topology of the cell to be decoupled from concerns about low level design rules. These concerns are resolved by the compactor spares, a tool that spaces the layout to minimize the area of the cell while respecting all the layout rules.

A subsystem called Mosaico is available to place and route macro-cell chips. A pad frame is built with padplace, and the core of the chip is placed using puppy, a program based on Simulated Annealing. Once a satisfying placement is obtained, Mosaico routes the chip by invoking a sequence of tools to perform channel definition, global routing, two-layer detailed routing, and via minimization. The resulting symbolic layout is finally processed by the compactor.

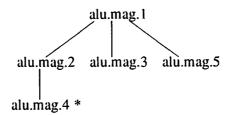

#### 1.3.2 Brief history of VOV and the Octools

In Berkeley, the *Octtools* are the third generation integration environment, built upon the experience gained with Ruby [19] in 1981-1982 and Squid [32] in 1982-1984. OCT, a revision of the Squid architecture, was available in prototype form in early 1986. The development of the OCT-based tools started in earnest in the spring semester of 1986, and proceeded at an intense pace for about two years. In the Spring of 1988, the tools were introduced in a VLSI design class at UC Berkeley, then taught by Prof. Randy Katz. This first semester was particularly hard on the students, because the tools were fragile and not sufficiently tested. As the tools became more robust in the course of the following semesters, more fundamental problems started to emerge, problems related to the interaction of the students with the tool set as a whole: students were oblivious of some tools, they did not seem to learn how to use some common and powerful options, they were forgetting to run the tools in the right sequence and they were destroying each other's data when trying to cooperate on the same project.

As a teaching assistant in the second semester in which the tools were used in the class, the writer had a direct relationship with the students and came to understand their difficulties. Also, as an author or coauthor of several of the tools that were being used (e.g. musa and the Mosaico set), the writer was well aware of how much potential was not being used, of how much effort is required to write CAD tools, of the extreme variability of user interfaces offered by the tools.

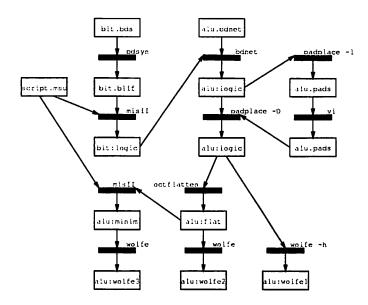

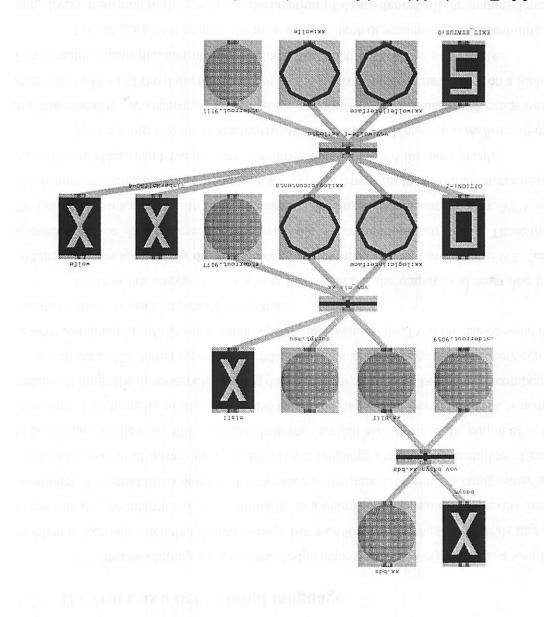

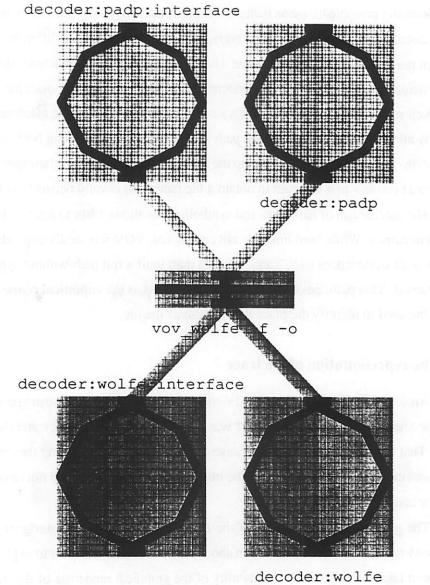

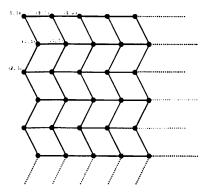

In Fall 88, we prepared some hand drawn "roadmaps," such as the one shown in Figure 1.2, to help the students understand the the design flow. These roadmaps were bipartite directed graphs, with nodes representing either data or tools. The students found this representation very useful and asked for more roadmaps. In January 1989 the development work on VOV began, as a way to automate the roadmaps. In the Spring semester 1990, VOV was introduced in an advanced graduate course on VLSI design, taught by Prof. John Wawrzynek. The eight students in the class cooperated in a design of a large chip for music generation called BRIC. VOV was used in conjunction with a large set of tools, including the *Octtools*, some commercial software such as

Figure 1.2: Roadmaps such as this are the precursors of the design trace.

Verilog, and some new tools especially written to address some of the peculiar problems in BRIC. The designers of BRIC provided a number of encouraging comments and suggestions on how to improve the user interface.

As the design of BRIC was proceeding, and the first feedback from real users was coming in, the VOV assistant took form. The first use of the assistant in a class was in the Fall 90, in an introductory graduate class on VLSI design. Once again, this class was taught by Prof. John Wawrzynek. The results of these experiments are reported in the Chapter 5.

# Chapter 2

# **Previous Work**

Electronic design management is a young discipline and still lacks a precise identity. It is also a broad discipline, including many issues relevant to other more specialized disciplines such as operating systems, data management, system modeling, office automation and user interfaces. The earliest work that can be considered specific to design management was published around 1985-86 [4, 16, 11, 30, 33], while the roots can be traced back to studies on system modeling, data-flows and Petri nets, in the seventies and before. Work in the neighboring field of office automation goes back to the late seventies, but it is only marginally relevant because of the substantial difference between office routine and design.

In the carly eighties CAD researchers in Berkeley [41, 45] forecast the need to move beyond tool development and onto design management. But it was not until later in the decade, after the realization of complex CAD systems, that the need for design management became concrete and pressing, and researchers could move from abstract speculations on design management to proposals for practical engineering solutions. In Berkeley, the *Octtools* have played a key role in making this research possible. The system proposed here can be seen as a modern descendent of the make.chip utility first reported by Berkeley researchers in 1981 [41].

In this chapter, the contributions of previous work and the current trends in design automation are reviewed. This survey tries to avoid the tedium of a chronological exposition, preferring instead to present a few "cross sections" of the relevant literature, with each cross section looking at a particular issue in design management. The first and most substantial cross section looks at the fundamental problem of representation of the design activity. The second compares the intrusiveness of the proposed systems, the third analyzes the possibility of a taxonomy of design tools and design data. The trend towards the use of artificial intelligence techniques and some relevant issues in data management are each given a section. Finally some commercial systems are looked at.

#### 2.1 Representation of the design activity

The choice of a model for the representation of the design activity is a central issue in design management. With great generality, a CAD system can be thought of as a system of asynchronous concurrent processes, and the design activity can be thought of as the interaction between the designers and those processes. In this section we review the many models that have been proposed.

A preliminary key to interpret the various models can be found in an early study in the context of office automation. In [53] Zisman analyzes three models for asynchronous concurrent processes: finite state machines, partial orderings, and Petri nets. He finds that finite state machines are inadequate, because if the processes can be performed in any order the number of states grows exponentially with the number of processes. Partial orderings also lack modeling power due to inability to express the possibility that tasks should be performed one at a time but in any order. Zisman concludes that only Petri nets have sufficient modeling power and that both FSM and partial orderings are nothing else but restricted forms of Petri nets.

In electronic design, a consensus seems to be emerging towards the use of bipartite graphs or of Petri nets to describe the CAD transactions and their inputs and outputs [3, 34, 6, 13, 39, 49], but other models have also been proposed.

We propose a classification that separates the models that are specific to VLSI design from those that are more generally applicable to other forms of design. In the second class we find models based on directed graphs, others based on bipartite graphs, state machine models, and the blackboard model. Finally, a mention is given to those systems that evade this simple classification.

#### 2.1.1 Ad-hoc models for VLSI design

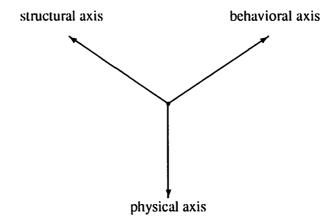

Since its conception [20], Gajski's *Y*-chart model of the design activity in VLSI has been accepted with favor [21]. The Y-chart is not properly a model for asynchronous concurrent processes, but it has been used as a conceptual foundation to build such models. In the Y-chart, shown in Figure 2.1, three semiaxes in a plane represent all the possible states of definition of a VLSI system during the design process. The behavioral axis represents the degree of definition of the behavior of the circuit. The closer to the origin a point lies along this axis, the more complete the

Figure 2.1: The Y-chart: a model for conceptual understanding of VLSI design, sometimes used also for design management.

behavioral representation. Similarly, the structural axis and the physical axis represent the degree of definition of the components used in the system and of their physical implementation. The design process is represented as a trajectory in the plane, moving from one axis to another and spiraling towards the origin, the point that represents the complete specification of behavior, structure and physical implementation of the system, and therefore the termination of the design process. The Y-chart has been used to compare qualitatively the performance and operation of various CAD systems and silicon compilers [9, 21].

Although not always explicitly, some management systems are based on the Y-chart and stress the importance of the trichotomy of design into behavioral, structural and physical domain. One example is Zimmerman's Playout [52, 46]. In Playout, the design flow is rigidly structured, because the system supports only a particular style of top-down design, on the assumption that such style leads to better designs and to fewer design iterations. CAD tools are grouped into six *toolboxes*, one for each step in the design flow: schematic entry, repartitioning, shape function generation (a step unique to Playout), chip planning, cell synthesis, and chip assembly. A central data manager provides permanent storage and supports communication between toolboxes, but each toolbox also has its own special data structures that are shared by all the tools in the toolbox. Each toolbox is a separate unit, typically a single UNIX process; it has its own *controller*, whose role is not clear, and its own user interface. A separate agent, the *Design Manager*, keeps track of the design process and

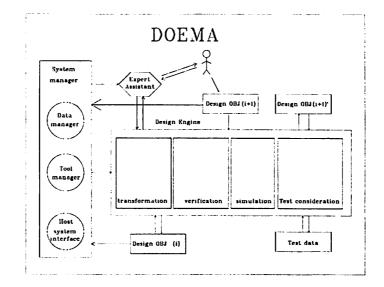

Figure 2.2: The DOEMA model.

directs the database manager.

The design flow is described by a bipartite directed graph, but the system internally does not use the graph. Some nodes in the graph represent the toolboxes, other nodes represent *data types*, which are either used or generated by the toolboxes. The graph is partitioned into three domains, behavioral, structural or physical. The toolboxes that span a domain boundary (e.g. behavior to structure) are those that perform a synthesis step. It is not clear if the graph represents the design history or if it is just a plan of how a design should be done. The notion of iteration, represented by cycles in the graph, is not clear. Parallel arcs represent alternatives, but there is no distinction between compatible or exclusive alternatives. Playout deserves attention more as a platform for tool integration and for the tools in its toolboxes than for its contribution to a conceptual understanding of VLSI design.

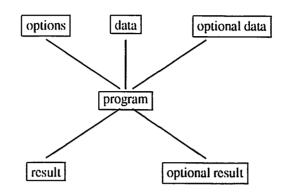

Another example of a speculative system is the conceptual framework for ASIC design proposed by Leung et al. [36]. Leung's goal is to bridge the gap between VLSI designers and VLSI technology, especially in ASIC design. Design is seen as a *decision making process*, which lies somewhere in the gray area between "Art" and "Science," between "creation" and "mechanical transformation." Modern CAD systems, Leung says, should first of all offer support for this decision making process.

The proposed *unified conceptual model* for ASIC design is shown in Figure 2.2. It is called DOEMA, as in Design Object, Design Engine, System Manager and expert Assistant, and it does

not meet many of the requirements for an ADM, most of which are also listed in [36]: simplicity, completeness, compatibility with existing tools, flexibility, case of use. The model consists of three major units: the design engine, the system manager and the expert assistant. The design engine operates uniformly on all design object at all levels of abstraction. The main purpose of the engine is to invoke the appropriate tool to transform an abstraction of a design object into another more detailed abstraction. The engine also takes care of verification, simulation and testing. The system manager provides an integrated environment in which the engine operates, offering services such as tool management, data management and interfacing with the operating system, but the authors of [36] do not elaborate on the details of how such an environment could be implemented. The function of the expert assistant is to make the designer aware of all the possible alternatives, to both enable and help the decision making process. The assistant is an expert system based on two types of knowledge: one to determine the available alternatives and one to determine when alternatives should be considered.

DOEMA sounds like a designer's wish list: it would be nice to have a a set of tools that operate uniformly at all levels of abstraction, a smart assistant and a versatile system manager. However, there is little or no indication that tool sets are about to become so well structured, and the claims about simplicity and versatility of the proposed model are not supported by any data. The DOEMA is a weak conceptual model of the design activity, and is of little use in the context of modern VLSI design.

Another system that emphasizes the decision making process in design is Yoda, by Dewey and Director [18]. The observation that early design decisions are the most important in terms of the performance of the final chip, leads Dewey to the notion of *Conceptual Design*, that is "the process of analyzing the outcome of alternative design decisions and their ramifications *before* actually undertaking specific design and fabrication steps." Conceptual design replaces the expensive trialand-error approach of traditional design; its final product is a *design plan*, which is a set of *design decisions*, each consisting of a choice of one of the possible *design options* for each of the relevant *design issues*. Design decisions are related to each other by a set of ordering and consistency constraints. The designer is assisted in the decision process by a set of performance predictors and by advice generated by a rule-based expert system. Yoda is a particular instance of the proposed system for support of conceptual design, specialized to the design of digital filters, and it appears to be successful in its restricted domain. The generalization of Yoda to other forms of design appears to be difficult because of the challenges associated with the acquisition of the knowledge base and with the development of accurate prediction models.

#### 2.1.2 General models for design activity

In this section we review some of the models that, although in large part originated in the context of VLSI design, do not rely on any specific characteristic of VLSI design, except perhaps the fact that it is already automated to a large extent. We review four types of models of the design flow. Two represent the design flow explicitly using either a directed graph or a bipartite directed graph. The others represent the flow implicitly, and they are the blackboard model and a state machine model.

#### **Directed graphs**

Knapp [33] reported some of the earliest works on VLSI design to give importance not only to the data but also to the operations of tools on the data. Knapp proposes the use of a bipartite acyclic directed graph for the representation of the circuits to be designed (the data), while the tool flow is represented by a simple directed graph, called *plan*; the nodes in the plan represent *abstract design states* while the arcs represent *abstract operators*. A design state consists of a set of assertions on the design, while an operator describes operations on the design state. An operator *O* is described by five entities,

$$O = \{F, E, Pre, Add, Del\}$$

where F is the executable code of the operator, E is a set of estimators for the operator, Pre is the set of assertions that must be true in order to allow the operator to execute, Add is the set of the assertions that become true upon execution of the operator and Del the set of assertions that become false. For example, the plan to produce a standard cell implementation of a combinational logic circuit starting from a set of logic equations consists of three nodes and two arcs, as shown in Figure 2.3. The first arc represent the logic minimizer, which requires the existence of a set of logic equation (precondition) to produce a set of 2-level logic equations (postcondition). The new state after the execution of the minimizer is described by the simultaneous existence of the initial logic equations and the new two-level form. The second arc represents the layout tool, which requires the existence of the two-level logic equations, an assertion that is true for the intermediate state in Figure 2.3, to produce a new state characterized by the existence of a standard-cell layout.

Knapp is aware of the difficulties related to the development of exact and complete descriptions of what each program does and favors instead a simpler description of the behavior of each operator based on the preconditions Pre, and of the postconditions Add and Del. The design

| logic n | ninimizer layo        | ut tool               |

|---------|-----------------------|-----------------------|

| Log.Eq  | Log.Eq<br>2-Level Eq. | Log.Eq<br>2-Level Eq. |

|         | 2-Level Eq.           | Std-Cell Layout       |

Figure 2.3: A plan produced by the DPE to transform a set of logic equations into standard-cell layout is represented by a directed graph in which nodes represent design states and arcs represent operators.

flow representation is both an executable plan and a design history; it is created as a plan, and it progressively becomes history as each tool is run. A Design Planning Engine uses artificial intelligence techniques to build a design plan tailored to each specific design. Such engine requires information provided by estimators that predict the performance of the various operators. These estimators need not be particularly accurate, but they should be at least *monotonic*, which means that for any given set of designs, the predictions should yield the same ordering as the corresponding actual performance measures.

One limitation of this model is that the notion of multiple inputs and outputs from a tool is not captured graphically, but through an overloading of the meaning of design state as an arbitrarily complex set of assertions. This can also lead to an exponential explosion in the number of states required to describe even simple notions, such as the existence of design objects. Consider a set of n design objects, each of which may or may not exist, independently from all the others. The assertion that an object exists can be either true or false, and the number of distinct states required to describe the existence of all objects is therefore  $2^n$ .

Knapp's monolithic view of the design activity represents a case of premature pursuit of a totally automatic design system. His results are scarce, because the system requires idealized tools such as the "almost monotonic" predictors of the performance for each tool.

In contrast with Knapp's proposal, the Methodology Management System (MMS) developed at MCC [3] inverts the roles of nodes and arcs in the directed graph describing the design flow. In the MMS, nodes represent tools and arcs represent *dependencies* between tools. In most cases, a dependency represents a file that is created by a tool and used by another tool. In general,

```

(deftool bdsyn (bds-file blif-file & optional collapse )

(version 1.1 )

(tool-name "bdsyn" ) ;actual name of executable

(doc "Behavioral synthesis tool. See 'man bdsyn'" )

(args

;<value> <default> <description> <label> <use-flag>

(nil nil "do not clean-up evaluation" "-b" nil )

((format nil "-c~A" collapse) nil "how much collapse to do" nil nil)

(nil nil "suppress vector notation for one-bit values" "-o" nil)

(nil nil "print table of non-assigned variables" "-n" nil)

(nil nil "change SELECTALL's to SELECT's" "-s" nil)

(nil nil "provide periodic updates of progress" "-u" nil)

(nil nil "assign 'dont cares' to zero" "-z" nil)

)

(input-file bds-file nil "BDS file to be translated" " " )

(output-file blif-file nil "BLIF format file" ">")

)

```

Figure 2.4: Example of Process-Tool definition in the MCC's MMS.

however, an arc can represent any abstract form of temporal dependency between two tools. Timestamps are associated with each node and each arc in the graph. As shown in Figure 2.4, the graph is represented implicitly using LISP functions, with a LISP function associated with every tool in the tool set. Complex tasks can also be represented with LISP functions that combine various tools together. A separate tracing mechanism generates a textual log of the design activity, which is used only for documentation, and not, for example, to enable the replay of tasks.

By operating in a LISP environment, MMS can be extended and tailored to satisfy the particular needs of each design. But the need to maintain a detailed LISP description of the behavior of each tool opens the door to problems in the maintenance of the system. Compare, for example, the MMS description of the tool bdsyn shown in Figure 2.4 to the usage message produced by the tool itself and shown in Figure 2.5. The MMS description is a redundant repetition of information already easily available from the tool. It is also incomplete, because it does not mention the options -d and -e nor the legal arguments for the option -c, and it is slightly inaccurate, because it changes the meaning of the option -b. These are only minor flaws in the encapsulation of one tool, bdsyn, but imagine repeating the comparison for tens of tools and then remember that the tools are often changing; the result is a complex problem of consistency maintenance, between what the tools really do and what the MMS thinks they can do.

```

bdsyn [-bcdenosuz] [filename]

-b Turn off internal minimizing

-c [n] Specify less collapsing of logic

0 No collapsing

1 Local collapsing only

Give a dump of tokens during the parsing

-d

-e [n] Specify execution level (0,..., 13)

1 then dump

0 PARSE only

2 through FOR

2 through FOR3 then dump4 through EVAL5 then dump6 through LEAVE7 then dump8 through VERSION9 then dump10 through CLEANUP11 then dump12 through LIF13 then dump

3 then dump

Give information about unspecified variables

-n

Omit the trailing <0> for 1-bit variables

-0

Map all SELECTALL's to SELECT's

-s

-u

Give updates as to progress of execution

Set DONT CARE's equal to zero

-z

```

Figure 2.5: The usage message produced by the tool bdsyn is more detailed than the MMS Process-Tool definition.

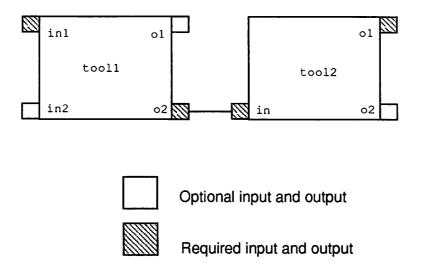

A model that bridges the gap between directed graphs and bipartite directed graphs is described in the Task Manager by Chiueh, Katz and King [15]. Once again, an acyclic directed graph is used, but this time the nodes in the graph are complex entities with many ports. Each node represents a *task* and its ports represent the input and output data of the task. The ports are characterized by a number of attributes that specify, for example, the type of data and whether it is required or optional. Directed arcs connect an output of a task to an input of another task, as shown in Figure 2.6, so that complex tasks can be built by combining elementary tasks in a hierarchical fashion. This model fits in a four-layered scheme in which the entire *design process* is seen as consisting of several *design activities*, which are in turn composed by *design tasks*, which are a sequence of *tool invocations*.

Chiuch et. al. [15] embrace the notion that design is unpredictable, that it cannot be planned a-priori, but they do not carry this notion to its full extent. In fact, they restrict the unpredictability only at the level of a *design activity*, while they claim that design tasks can be planned. Within a task, the system knows at any time which tools can be invoked. The list of legal transaction is presented to the designer who chooses the one to perform next. The invocation of an unexpected tool within a task is possible, but it causes the system to react with a warning to the designer, al-

Figure 2.6: A node in the Task Manager is a complex entity, with one port for each input and output. Complex tasks can be described hierarchically by using arcs to join outputs of a subtask to the inputs of other subtasks.

though no other record of the exception is maintained. To support the design activities, the system maintains the *Activity History*, a possibly branching sequence of history records, each logging the invocation of a task and its inputs and outputs.

Within an activity, backtracking is provided by the possibility of storing *design points*, which are essentially copies of all the data that is relevant to an activity at a particular point in time. If the designer performs a task, and then decides to invalidate it, he can backtrack by asking the system to recover any of the previous design points. Although conceptually viable, this technique can become prohibitively expensive unless it is complemented by a sophisticated mechanism to reduce the redundancy in the storage of two adjacent design points, but there is no concern for this problem in [15].

The Task Manager, if implemented, could be vulnerable to the problem of using multiple representations for the design tasks: while the user interacts with the system by means of a graphical representations of the tasks, the system itself operates internally on LISP-like expressions. Multiple representations must be kept consistent and for complex CAD systems this might become an unwieldy job. Furthermore, there is the problem, already mentioned in the case of MCC's MMS, of keeping the task descriptions up-to-date with the tool set.

#### **Bipartite directed graphs**

The use of a bipartite graph to represent a design flow has been proposed by many independent researchers. In many cases the bipartite graph is an extension to the Petri net model.

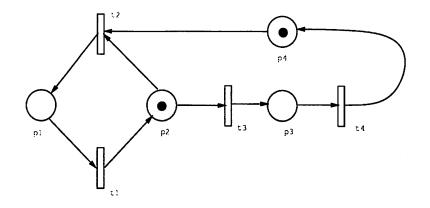

Since their first appearance in 1962, in Carl Adam Petri's dissertation, Petri nets have been used extensively to model systems that exhibit asynchronous and concurrent activities. Many examples of such uses can be found in the excellent tutorial by Tadao Murata in the IEEE Proceedings [40].

Following Di Janni [30], a marked Petri net PN is defined as a set of five entities:

$$PN = \{P, T, I, O, M\}$$

where

| $P = \{p_1, p_2, \ldots, p_n\}$   | is a finite set of places      |

|-----------------------------------|--------------------------------|

| $T = \{t_1, t_2, \ldots, t_m\}$   | is a finite set of transitions |

| $I:T\to P^\infty$                 | is the input function          |

| $O:T\to P^\infty$                 | is the output function         |

| $M: P \to \{0, 1, 2, 3, \ldots\}$ | is the marking function        |

The places in a Petri net are conventionally used to represent data. The transitions represent operations on the data. The directed arcs represent the relations of inputs and outputs between data and operations. The marking function represents the number of *tokens* associated with each place, and M(p) = k means that place p holds k tokens. The number of tokens in a place is normally interpreted as the availability of that number of the item associated with that place.

The behavior of a Petri net is characterized in large part by its *firing rule*. A transition *t* is said to be *enabled* if all of its input places contain at least one token. Only enabled transitions can fire, but the actual firing is determined by external factors not necessarily represented by the net. If a transition fires, one token is removed from each of the input places and one token is added to each of the output places. Situations of conflict arise whenever the firing of a transition disables another transition. If more than one transition is enabled, it is undetermined which one will fire first, but certainly one will fire before all the others, because simultaneous firings are not allowed.

Theoreticians have studied many behavioral properties of Petri nets, such as *reachability* of a marking from an initial marking, *boundedness* of the number of tokens held by places, and