# Copyright © 1990, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# COMBINATIONAL LOGIC OPTIMIZATION TECHNIQUES IN SEQUENTIAL LOGIC SYNTHESIS

by

Sharad Malik

Memorandum No. UCB/ERL M90/115

28 November 1990

# COMBINATIONAL LOGIC OPTIMIZATION TECHNIQUES IN SEQUENTIAL LOGIC SYNTHESIS

by

Sharad Malik

Memorandum No. UCB/ERL M90/115

28 November 1990

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### Combinational Logic Optimization Techniques in Sequential Logic Synthesis

Sharad Malik

University of California Berkeley, California Department of Electrical Engineering and Computer Science Computer Science Division

#### Abstract

Designing an integrated circuit with over one hundred thousand components is a significantly complicated task; impossible to handle without computing aids. Computer-aided design tools are used in all aspects of the design: logical design of functional units, physical design of gates and modules, placement and interconnect routing, logical and timing verification, and management of design data. Of these, the automatic design of the logic components, referred to as logic synthesis, was the last to come about; an indication of the inherent difficulty of this task. There was a lack of sophisticated logic optimization techniques needed to generate high quality results. This prompted research in this area and as a result there are now several commercially available design aids. Thus far, logic synthesis has largely concentrated on combinational logic. This is an incomplete view, since digital circuits are, in general, sequential in nature. This thesis attempts to overcome this limitation. It presents techniques for the optimization of sequential logic circuits. In particular, it considers extensions of known combinational logic optimization techniques that are applicable in sequential logic synthesis. The contributions are in two areas. In the first part it is shown how existing combinational logic optimization techniques can be directly applied in the expanded context of sequential logic synthesis. The presented approach maximally exploits combinational logic optimization techniques, i.e. it can potentially detect any logical relationships that exist between any two gates in the circuit, they need not be part of the same combinational logic block. In the second part, techniques for the optimization of multi-level circuits with multiple-valued inputs are presented. Logic optimization techniques used in multi-level circuits have been extended to handle multiple-valued inputs. In addition to being a significant result in its own right, this has direct application in the state assignment problem in sequential logic synthesis. In both these areas. theoretical results are presented and implementation issues and practical experiences discussed.

rof. Robert K. Brayton

Thesis Committee Chairman

## Acknowledgements

And its been this way for five long years Since we signed our souls away.

Jethro Tull, "War Child"

The five years that I have spent as a graduate student at Berkeley have been, at some time or the other, tough, exciting, fun and depressing. If I have made it through this, it is only because of the support, encouragement and friendship of several people. I got by with a little help from my friends, nay, with lots of help from my friends.

There are two people without whom this thesis would never have been possible; Bob Brayton and Alberto Sangiovanni-Vincentelli. They introduced me to the field of logic synthesis and have taught me most of the things that I know about this subject.

Bob has been my research advisor for the last two and a half years. The time that I have spent working on research with him has been extremely exciting – Bob's enthusiasm and desire to pursue the unknown has been truly inspirational for me. From him I have also tried to learn mathematical precision, both in the formulation and solution of problems, as well as in written and oral exposition. I consider myself truly fortunate for having worked with him.

I owe a lot to Alberto. First and foremost for giving me the opportunity to be part of the excitement of the cadgroup, without which none of the work I have been involved in would have been possible. I have profited from his advice, both technical and professional. From Alberto I have learnt, (at least I think so!) the need for systematic rigor in research, and clarity and focus in presentation. He has gone through multiple drafts of my writings and several rehearsals for my presentations; painstakingly pointing out what needs to be done differently and why. Thanks Alberto.

Two other people have had a significant impact on my research career. Kurt Keutzer introduced me to intensity in research, with his work hard and play hard attitude. He has also shown me the planning and organization that goes into a successful research career <sup>1</sup>. I am indebted to Rick Rudell for guiding me in my early years in graduate school; for being forever willing to help me in my work. This support was very important for me. From him I have tried to learn the importance of practical concerns in the application of research ideas.

<sup>&</sup>lt;sup>1</sup>This is no way implies that I support his views on any matter!

I would like to thank Randy Katz for support during the initial stages of my graduate student life. Randy encouraged me to pursue the path I thought best for my research, I am thankful for that. Thanks are also due to him for serving on my qualifying exam committee. I would also like to thank Prof. Dorit Hochbaum for sparing the time to serve on both my qualifying exam as well as thesis committees.

Several people have made a direct contribution to the work in this thesis. All the work was done with Bob and Alberto; it is impossible to separate out their contributions. Luciano Lavagno was responsible for the implementation of MIS-MV, without him it may not have become a reality. The initial work in retiming and resynthesis was done with the assistance of Ellen Sentovich. The work on the performance optimization of pipelined circuits was done with the assistance of Kanwar Jit Singh.

Cadgroup provided the unique environment for most of my work. Profs. Brayton, Newton, Pederson and Sangiovanni-Vincentelli deserve special thanks for their efforts in establishing this environment for us, the students in the group. The funding for my research was provided by DARPA, NSF and industrial grants from AT&T, Bell Northern, California Micro, IBM, Intel and Motorola. I gratefully acknowledge that. Thanks also to Digital Equipment Corporation for the equipment used. Brad Krebs and Beorn Johnson provided ready assistance with any hardware and software problems. Rick Spickelmier provided ample assistance with tools he did and didn't write. I had many useful and enjoyable interactions with other members in the group. In alphabetical order they are: Pranav Ashar, Wendell Baker, Srinivas Devadas, Tim Kam, Luciano Lavagno, Bill Lin, Rick McGeer, Cho Moon, Rajeev Murgai, Alex Saldanha, Hamid Savoj, Ellen Sentovich, Narendra Shenoy, Kanwar Jit Singh, Arvind Srinivasan, Hervé Touati, Tiziano Villa, and Albert Wang. Rick McGeer deserves special mention. His firm belief that research must be fun helped keep the right perspective on things. Thanks to Ellen for carefully reading through this manuscript and in clarifying the ideas presented in the appendix. Thanks also to Umakanta Choudhury for letting me commandeer his LaTex book during the writing of this thesis.

There are several researchers outside of Berkeley that I wish to thank. Al Dunlop provided me with the opportunity to spend a fruitful summer at AT&T Bell Labs., Murray Hill. Len Berman and Larry Carter arranged for me to spend some time at IBM Research Division, Yorktown Heights. I thank Tzvi Ben-Tzur, Len Berman, Randy Bryant, Giovanni De Micheli, Gary Hachtel, Bob Kurshan, Naotaka Maeda, and Louise Trevillyan for time spent in technical interactions.

Kathryn Crabtree was a wonderful source of support, providing encouragement when things were not going right. And without her, I couldn't have figured out the Berkeley bureaucracy in a million years. Flora Oviedo provided valuable assistance with things administrative as well as a ready smile to brighten up the cloudiest of days. Ted Goode was always extremely helpful at the foreign students office, never letting me feel that I was a "non-resident alien".

Ashi and Jean Malik provided me with the home away from home, giving me love, support and good food, as and when needed. Thanks a lot guys. Thanks also to the Becks; Fred and Polly, Dan and Annette, and Louie for making me feel part of the family. Ruth Brayton was wonderful as my local Mom, giving affection and good advice in equal measure.

Life in Berkeley would not have been the same without my buddies, who made life enjoyable even when it was trying hard to be otherwise. Tons of thanks to Jhingu, Khedkar, Huzur, K. J., Munnu, Savita, Madhu, Mots, Asha, Tarun, Shashi, Keshav, Nandu, Vedant, Ajay Amar, Murgai, Ashok Singhal, and Jaggu for providing the much needed support mechanism. Thanks also to my roommates, Tom Chen, Huzur and D. G. for putting up with my idiosyncrasies.

In its own way Berkeley made life enjoyable and interesting. Telegraph Avenue chipped in with Café Med and Moe's. Sam and Andy and the rest of the crew at Coffee Connection made the afternoon bianco ritual a pleasure. The 49er's and the A's kept the morale up with their spectacular efforts.

My aunt and uncle, Mrs. and Mr. V. N. Bakshi provided me with encouragement and the environment to pursue my academics in Delhi. My sisters Madhuri and Payal contributed in their own little way by putting up with me at home, hoping that some day I would be normal. It is not possible to thank the next three people enough with mere words. Nonetheless, thanks to Aarti for all her love and willingness to undertake a difficult journey with me. Thanks to Mom for her love and sacrifices that have made all this possible. And last but not the least, thanks to Darshan Uncle, for being more than a father to me. It is to him that I dedicate this thesis.

# Contents

| Ta | able o                        | of Contents                                       | 7  |  |  |  |  |  |  |

|----|-------------------------------|---------------------------------------------------|----|--|--|--|--|--|--|

| Li | st of                         | Figures                                           | ix |  |  |  |  |  |  |

| Li | st of                         | Tables                                            | x  |  |  |  |  |  |  |

| 1  | Intr                          | roduction                                         | 1  |  |  |  |  |  |  |

|    | 1.1                           | VLSI Design and Logic Synthesis                   | 1  |  |  |  |  |  |  |

|    | 1.2                           | Sequential Logic Synthesis                        | 4  |  |  |  |  |  |  |

|    |                               | 1.2.1 Problem Classification                      | 5  |  |  |  |  |  |  |

|    |                               | 1.2.2 Previous Work                               | 10 |  |  |  |  |  |  |

|    | 1.3                           | Thesis Overview                                   | 15 |  |  |  |  |  |  |

| Ι  | Re                            | timing and Resynthesis                            | 17 |  |  |  |  |  |  |

| 2  | Bas                           | Basic Ideas                                       |    |  |  |  |  |  |  |

|    | 2.1                           | Clocking Methodology                              | 20 |  |  |  |  |  |  |

|    | 2.2                           | Overview                                          | 21 |  |  |  |  |  |  |

|    | 2.3                           | Theoretical Formulation                           | 22 |  |  |  |  |  |  |

|    |                               | 2.3.1 Retiming: An Overview                       | 23 |  |  |  |  |  |  |

|    |                               | 2.3.2 Extensions to Retiming                      | 26 |  |  |  |  |  |  |

|    |                               | 2.3.3 Conditions for Peripheral Retiming          | 31 |  |  |  |  |  |  |

|    |                               | 2.3.4 Computing the Path Weight Matrix            | 38 |  |  |  |  |  |  |

|    |                               | 2.3.5 Solving the Path Weight Matrix              | 42 |  |  |  |  |  |  |

|    |                               | 2.3.6 Legal Resynthesis Operations                | 42 |  |  |  |  |  |  |

|    | 2.4                           | Peripherally Retimable Circuits: General Topology | 46 |  |  |  |  |  |  |

|    | 2.5                           | Optimizing Sequential Circuits                    | 49 |  |  |  |  |  |  |

|    | 2.6                           | Computing Equivalent States Across Optimizations  | 52 |  |  |  |  |  |  |

| 3  | Implications and Applications |                                                   |    |  |  |  |  |  |  |

|    | 3.1                           | Relationship to Logic Testing                     | 57 |  |  |  |  |  |  |

|    | 3.2                           | Relationship to State Assignment                  | 60 |  |  |  |  |  |  |

|    | 3.3                           | Performance Optimization                          | 67 |  |  |  |  |  |  |

vi *CONTENTS*

|            |                          | 3.3.1                  | Two Problems in Performance Optimization              | 68  |  |  |  |  |  |

|------------|--------------------------|------------------------|-------------------------------------------------------|-----|--|--|--|--|--|

|            |                          | 3.3.2                  | Main Results                                          | 71  |  |  |  |  |  |

| <b>4</b> · | Pra                      | ctical I               | Experiences                                           | 79  |  |  |  |  |  |

|            | 4.1                      | Implen                 | nentation Issues                                      | 79  |  |  |  |  |  |

|            |                          | 4.1.1                  | Growing Pipelined Sub-Circuits from a Seed            | 79  |  |  |  |  |  |

|            |                          | 4.1.2                  | Clustering Combinational Logic Blocks                 | 84  |  |  |  |  |  |

|            | 4.2                      | Experi                 | mental Results: Area Optimization                     | 87  |  |  |  |  |  |

|            |                          | 4.2.1                  | Experimental Circuits                                 | 87  |  |  |  |  |  |

|            |                          | 4.2.2                  | Experimental Procedure and Results                    | 88  |  |  |  |  |  |

|            |                          | 4.2.3                  | Analysis of Experimental Results                      | 88  |  |  |  |  |  |

|            | 4.3                      | Experi                 | mental Results: Performance Optimization              | 96  |  |  |  |  |  |

|            |                          | 4.3.1                  | Example Circuits and Experimental Procedure           | 96  |  |  |  |  |  |

| II         | H:                       | ndlin                  | g Symbolic Inputs                                     | 99  |  |  |  |  |  |

|            | 110                      | an Carrie              | 5 Symbolic Inputs                                     | 00  |  |  |  |  |  |

| 5          |                          |                        | el Logic Minimization                                 | 101 |  |  |  |  |  |

|            | 5.1                      |                        | Level Optimization Techniques                         | 102 |  |  |  |  |  |

|            | 5.2                      |                        |                                                       | 103 |  |  |  |  |  |

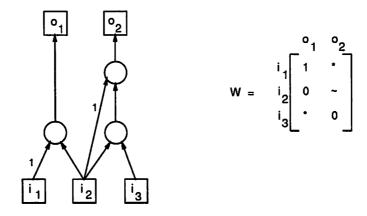

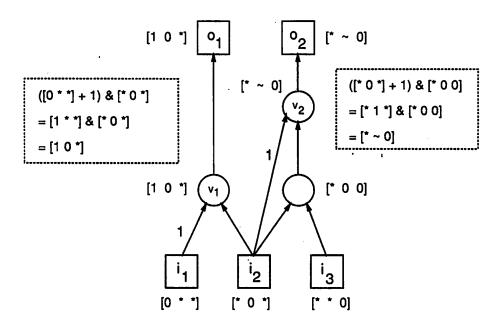

|            | 5.3                      |                        | and Function Representation                           | 103 |  |  |  |  |  |

|            | 5.4                      |                        | t Decomposition Using Kernels                         | 106 |  |  |  |  |  |

|            |                          | 5.4.1                  | Kernels and Kernel Intersections                      | 106 |  |  |  |  |  |

|            |                          | 5.4.2                  | Kernels and Multiple-Valued Variables                 | 109 |  |  |  |  |  |

|            | 5.5                      |                        | Decomposition Using Common Cubes                      | 120 |  |  |  |  |  |

|            |                          | 5.5.1                  | Common Cube Extraction with Binary Variables          | 120 |  |  |  |  |  |

|            |                          | 5.5.2                  | Common Cube Extraction with Multiple-Valued Variables | 121 |  |  |  |  |  |

|            | 5.6                      | Circuit Simplification |                                                       |     |  |  |  |  |  |

|            | 5.7                      | Logic `                | Verification                                          | 125 |  |  |  |  |  |

| 6          | Practical Experiences 12 |                        |                                                       |     |  |  |  |  |  |

|            | 6.1                      | Implem                 | nentation Issues                                      | 127 |  |  |  |  |  |

|            |                          | 6.1.1                  | Size Estimation in Algebraic Decomposition            | 128 |  |  |  |  |  |

|            |                          | 6.1.2                  | Incompletely Specified Literals                       | 129 |  |  |  |  |  |

|            |                          | 6.1.3                  | Satisfiable Constraint Matrices                       | 132 |  |  |  |  |  |

|            |                          | 6.1.4                  | The Encoding Problem                                  | 136 |  |  |  |  |  |

|            | 6.2                      | Exper                  | imental Results                                       | 137 |  |  |  |  |  |

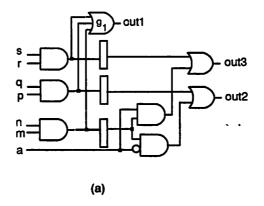

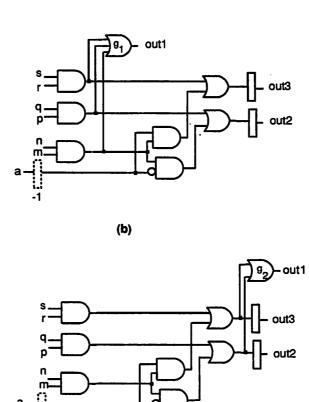

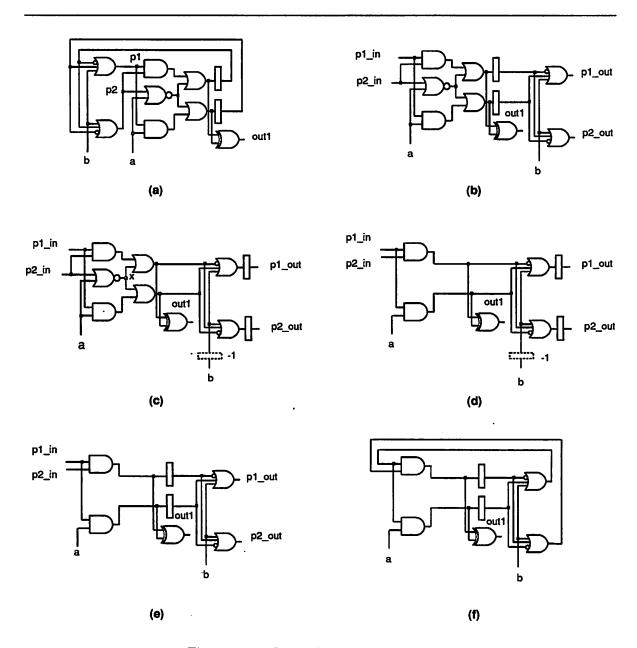

|            |                          | 6.2.1                  | An Example MIS-MV Run                                 | 142 |  |  |  |  |  |

| 7          | Con                      | clusio                 | ns                                                    | 149 |  |  |  |  |  |

| A          | Disc                     | crete N                | Mappings and Boolean Functions                        | 151 |  |  |  |  |  |

|            | A.1                      | Introd                 | uction                                                | 151 |  |  |  |  |  |

|            |                          |                        | n Functions: A Review                                 | 152 |  |  |  |  |  |

|            |                          |                        | Boolean Algebras                                      | 152 |  |  |  |  |  |

|            |                          |                        |                                                       | 154 |  |  |  |  |  |

| CONTENTS |   | vi |  |

|----------|---|----|--|

|          | • |    |  |

•

|         | Discrete Mappings                            |     |

|---------|----------------------------------------------|-----|

|         | Compact Representations of Boolean Functions |     |

|         | Expressions Representing Discrete Mappings   |     |

| A.6     | Conclusions                                  | 161 |

| Bibliog | graphy                                       | 163 |

viii CONTENTS

. Oglar, olivit

And the second of the second o

# List of Figures

| 1.1  | General Sequential Circuit                                | 5         |

|------|-----------------------------------------------------------|-----------|

| 1.2  | Symbolic Specification of Logic: An Example               | 9         |

| 1.3  | State Transition Tables and Graphs                        | 13        |

| 2.1  | Edge Triggered and Transparent Latches                    | 20        |

| 2.2  | Sequential Circuits and Communication Graphs: An Example  | 24        |

| 2.3  | Retiming: An Example                                      | <b>25</b> |

| 2.4  | Legal Retiming: An Example                                | 26        |

| 2.5  | Example: Use of a Negative Latch                          | 27        |

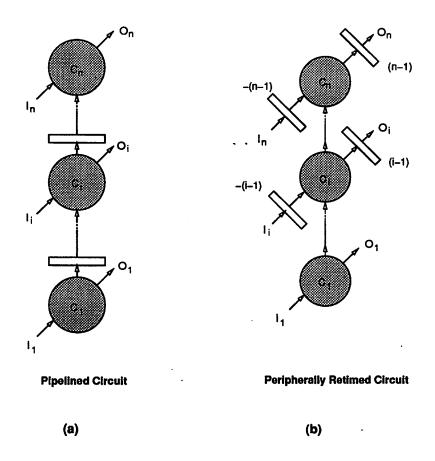

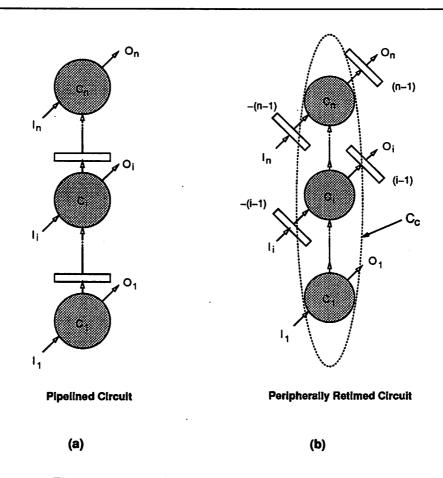

| 2.6  | Peripheral Retiming                                       | 29        |

| 2.7  |                                                           | 29        |

| 2.8  | Circuit with no peripheral retiming: Example 1            | 31        |

| 2.9  | Circuit with no peripheral retiming: Example 2            | 32        |

| 2.10 | Path weight matrix: Example                               | 33        |

| 2.11 | Computing the Path Weight Matrix                          | 39        |

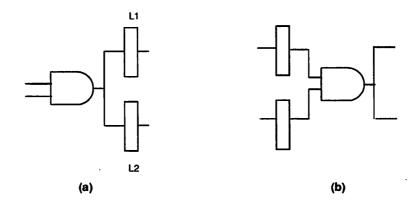

| 2.12 | Operators "+" and "&"                                     | 40        |

| 2.13 | Computing the Path Weight Matrix: Example                 | 41        |

| 2.14 | Solving the Path Weight Matrix                            | 43        |

| 2.15 | Introducing Pseudo-dependencies with Negative Path Weight | 47        |

|      | Pipelined Circuits and their Retiming                     | 48        |

| 2.17 | Acyclic Circuit with no Peripheral Retiming               | 50        |

| 2.18 |                                                           | 51        |

| 2.19 |                                                           | 53        |

| 2.20 | The Equivalent State Problem: An Example                  | 55        |

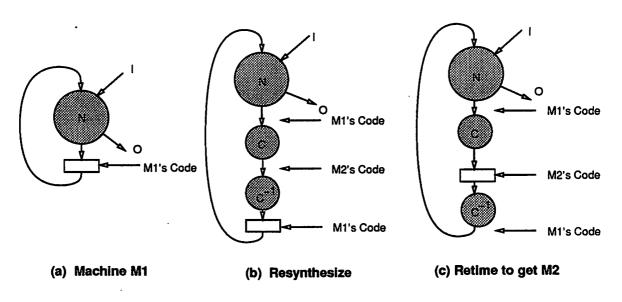

| 3.1  | Impact on Transition Behavior                             | 61        |

| 3.2  | Obtaining Equivalent FSM Implementations                  | 62        |

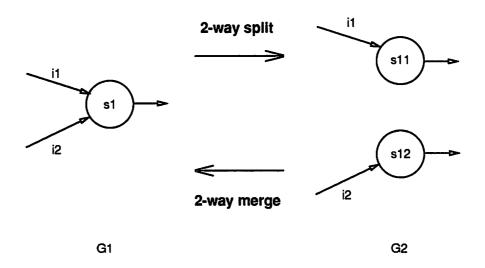

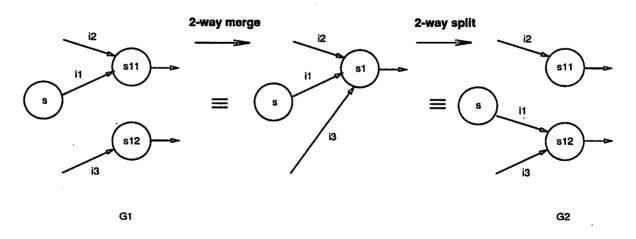

| 3.3  | 2-way split and merge                                     | 63        |

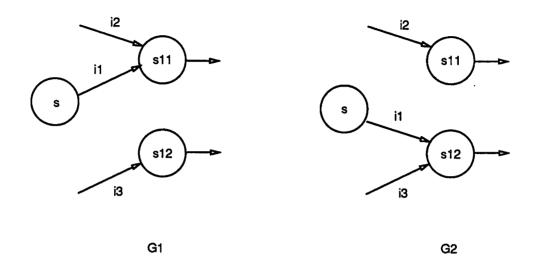

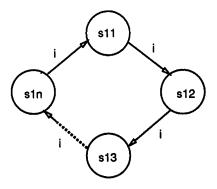

| 3.4  |                                                           | 64        |

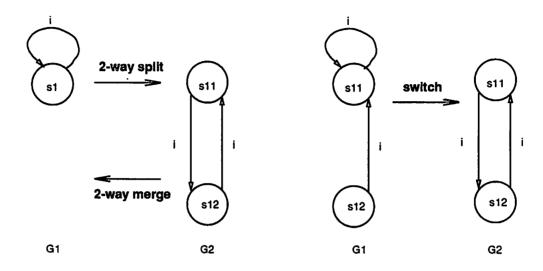

| 3.5  | Switch using 2-way merge and split                        | 64        |

| 3.6  |                                                           | 65        |

| 3.7  | Non-CP Transformations                                    | 66        |

| 3.8  | Obtaining Equivalent FSM Implementations                  | 67        |

| 3.9  | Peripheral Retiming of Pipelined Circuits   | 70  |

|------|---------------------------------------------|-----|

| 3.10 | Blocked Latch Motion                        | 73  |

| 4.1  | Growing Pipelined Circuits from a Seed      | 80  |

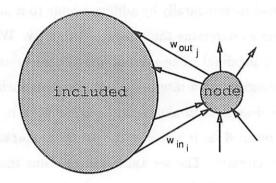

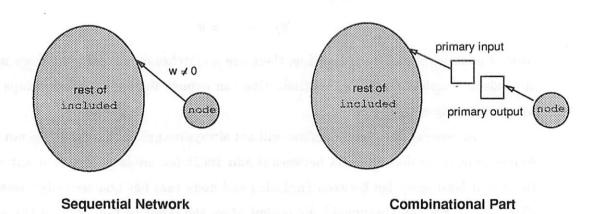

| 4.2  | Adding node to included                     | 82  |

| 4.3  | Adding an Edge with $w \neq 0$ to included  | 82  |

| 4.4  | Clustering Combinational Logic Blocks: I    | 85  |

| 4.5  | Clustering Combinational Logic Blocks: II   | 86  |

| 4.6  | Summary of the Experimental Procedure       | 89  |

| 4.7  | Register Outputs Form a High Fanout Cutset: | 90  |

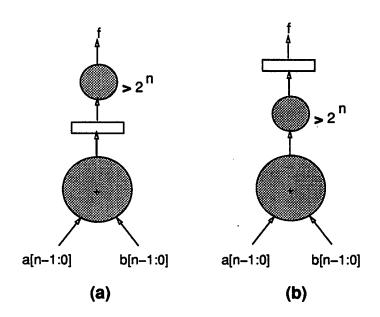

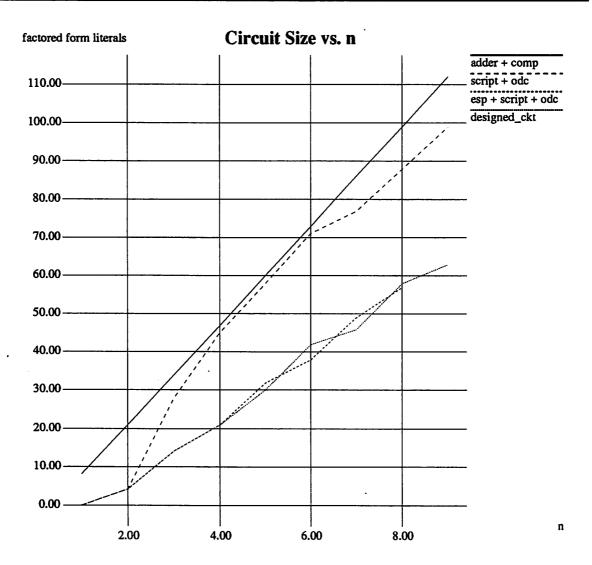

| 4.8  | Example Circuit: add_comp                   | 92  |

| 4.9  | Experimental Results for add_comp           | 94  |

| 4.10 |                                             | 95  |

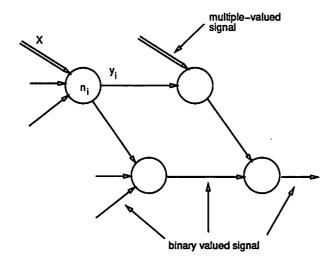

| 5.1  | Representing Circuits as MV-networks        | 105 |

| 6.1  | Algorithm sa_encoding                       | 138 |

| 6.2  | keyb: Initial Circuit                       | 143 |

| 6.3  | keyb: Circuit after Node Simplification     | 144 |

| 6.4  | keyb: Circuit after Algebraic Decomposition | 145 |

| 6.5  | keub: Circuit after Encoding                | 147 |

# List of Tables

| 4.1 | Experimental Results: Performance Optimization of Pipelined Circuits | 97  |

|-----|----------------------------------------------------------------------|-----|

| 6.1 | Input Encoding Comparison                                            | 141 |

xii LIST OF TABLES

to a section of the fitting is a commence to the fitting of the fitting of the section of Comments.

edicki to this

a restriction of relief and an particle

# Chapter 1

# Introduction

Imperious Prima flashes forth Her edict "to begin it": In gentler tones Secunda hopes "There will be nonsense in it."

- Lewis Carroll, "Alice in Wonderland"

This thesis examines the problem of automatically synthesizing digital logic circuits. In particular, logic circuits with memory elements are considered; i.e. circuits that exhibit sequential behavior. This introductory chapter is organized as follows. First, the role of logic synthesis in the design of VLSI (Very Large Scale Integration) circuits is explained. Next, the problem domain of sequential logic synthesis is introduced. A classification of problems in this area is presented and previous work done for these problems is described. Then the scope of this thesis is defined with respect to these problems. This chapter concludes with the organization of the rest of the thesis.

#### 1.1 VLSI Design and Logic Synthesis

The design of a digital logic system goes through several stages. The typical design flow is as follows:

**Design Specification** The desired behavior of the system is specified at some level of abstraction. The exact level of detail may vary depending on the designers and the specific system being designed.

**Design Partition** Typically systems being designed are sufficiently complex to merit being broken up into smaller sub-systems in order to make the design task more tractable.

Logic Design Here the sub-system specifications are given structure. They are converted to interconnected logic elements such as gates, logic modules (e.g. adders) and memory elements. Part of the design specification typically includes some constraints that the final design must meet, such as chip area and delay through the logic. Since the design may not be ready for physical layout, the area and delay are approximated at this level.

Physical Design After the individual components and their interconnections for each integrated circuit (IC) in the system have been specified, they have to be mapped to a physical layout that specifies the individual transistors and their interconnection. In addition, all the IC's in the system need to be placed and interconnected on a collection of printed circuit boards.

Several iterations through one or more of these stages may be needed before the design meets its specification.

While the above design flow has remained largely unchanged, integrated circuits have seen a rapid increase in complexity over the last two decades. Crossing the 100,000 mark in the number of transistors per IC (or chip) marked the entry into the era of very large scale integration (VLSI). Since then it has been possible to design and manufacture IC's with a few million transistors. The complexity presented in the design of circuits involving such a large number of components cannot be managed without computing aids of some sort. As a result a wide variety of Computer Aided Design (CAD) tools have been developed for helping designers with various aspects of the design. These tools perform two kinds of tasks:

- Routine Tasks: Several tasks in the design process are routine (e.g. design rule checking). These can be easily and efficiently automated making the task at hand faster and less error prone.

- 2. Searching Large Design Spaces: The large number of components result in a combinatorial explosion when we consider the possibilities at several stages in the design process. Physical placement and routing is a classic example of this. Design tools per-

form an efficient search of the solution space which would not be possible for human designers.

In either case, these tools result in vastly reduced design time. This translates into cheaper design costs as well as faster time to market a product. These advantages have made CAD tools an integral part of VLSI design. The following areas have been addressed by design tools. They are stated here in rough chronological order of development.

Verification At several stages during the design, parts of the circuit need to be checked to assure that they meet the timing and/or logical requirements for the design. Traditionally, this has been done by simulating the circuit. Logic and timing simulators have been developed that are capable of handling significantly complex circuits. In recent years, formal verification techniques are gradually replacing simulation for logic verification.

Physical Design The circuit designer's view of the integrated circuit is a geometric view of overlapping polygons representing transistors and their interconnects. Physical design tools enable design of gates comprising of several transistors, modules consisting of several gates, the placement of these modules and gates in a two dimensional plane and the routing of interconnections between these for each IC, and placement and routing of IC's on printed circuit boards.

Design Management and Tool Integration Efficient management of the large amount of data needed to store the different parts of the design in its various stages is a formidable task. Design management tools handle the large databases needed for this purpose. These databases also permit various tools working on a design to communicate with each other since all of them now interface with the same database.

Synthesis The logic design phase was the last to see some degree of automation. This is an indication of its inherent difficulty and complexity. Currently, this is also the most time consuming part of the design process. Synthesis efforts can be classified into two categories based on their starting and ending points.

Behavioral Synthesis A description of the input-output behavior of the system is converted to structure in the form of interconnected blocks of combinational logic and memory elements. The blocks of combinational logic may have some known functionality, e.g. a 16-bit adder, or may be specified as logic equations. It has been difficult for design tools to achieve design quality comparable to that attainable by human designers. As such these design tools are mainly of research interest and this phase is still dependent on the skill of designers. (In [53] a review of this subject is presented.)

Logic Synthesis The translation of memory elements and combinational logic blocks (described as equations) into a set of interconnected primitive elements such as gates and latches is termed logic synthesis. These primitive elements may be part of a pre-designed library that is used in conjunction with a particular design style (such as standard cell, sea of gates etc.). Since logic synthesis tools must produce results that are comparable with those produced by human designers, design optimization is a very important part of any tool. The metrics used to evaluate the result are the size of the resulting circuit (which will impact the final area), its delay (which determines the throughput or performance) and its testability. These metrics will be examined in Section 1.2.1.

#### 1.2 Sequential Logic Synthesis

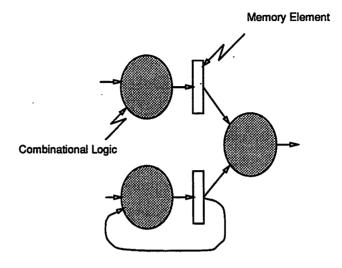

The work presented in this thesis is concerned with design aids for synthesis. In particular logic synthesis involving memory elements is considered, which is termed sequential logic synthesis. Figure 1.1 shows a general schematic of a sequential digital logic circuit. This has two parts; combinational logic and memory elements. The blocks of combinational logic each compute an arbitrary Boolean logic function. Each block consists of logic gates, such as AND, OR, NOT, connected to implement this function. Typically the interconnection of these gates within a combinational logic block is acyclic. The memory elements are used to store data between successive computations of the logic blocks. Thus their introduction results in the circuit storing the past history of inputs. As a result they are thought of as exhibiting sequential behavior, i.e., the circuit operates on input sequences and produces output sequences. This is in contrast to a combinational logic circuit, which has no memory and therefore produces a single output for a single input. The memory elements are referred to as latches since they latch in the data present at their inputs. (A note on the drawing conventions used in the sequel. Combinational logic is drawn using conventional gate symbols or shaded ovals. Latches are depicted by rectangles.) This research focuses on

Figure 1.1: General Sequential Circuit

a special class of digital circuits, viz. synchronous digital circuits. These circuits have the property that all memory elements latch in their data synchronously with respect to a clock signal that is common to the circuit. A large percentage of all circuits designed fall into this category. Most existing research efforts in this area may be classified as combinational logic synthesis since they deal with only the combinational parts of the design. The memory elements are considered as if sacred and are not modified after their initial introduction. This has traditionally been the case because combinational logic optimization has been well-studied in the past and those results can be exploited here. Very little work that exploits the ability to modify the memory elements has been done. The techniques proposed in this thesis go beyond combinational logic optimization inasmuch as they consider altering the combinational parts as well as the memory elements during design optimization.

#### 1.2.1 Problem Classification

This section examines the various problems that arise in design optimization during sequential logic synthesis. These may be classified along three orthogonal axes.

#### 1: Optimization Criterion

Traditionally, the most important optimization criterion during IC design has been minimizing the size of the resulting circuit. The size is measured in terms of the area occupied by the layout. The reason for this pre-occupation with minimum area circuits has been the correlation between the area and the cost of the final circuit. In IC manufacture, the yield (or the percentage of non-faulty components) is an exponentially decreasing function of the size of the IC [54]. Thus, larger circuits tend to have smaller yields which results in higher cost per working component. However, in recent years the increasing maturity in IC fabrication has resulted in more stable processes which have increased the size of circuits capable of being manufactured with acceptable yields. As a result, area optimization has become less important. However, to say that area optimization is not important any longer is inaccurate. With increasing silicon real estate being available, the demands for it have also increased. Designers are putting more and more functionality on a single chip, and would like to have additional area available for adding resources, such as on-chip memory.

There has been an increasing demand for higher performance from circuits in the past decade. This arises due to higher computational needs for complex computations as well as increased volume of information being processed. In the context of synchronous sequential circuits, the performance of a circuit is measured in terms of the cycle time of its system clock. This determines the throughput of the circuit. If a synthesis tool does not address the issue of meeting the performance constraint on a design, then it is counterproductive to the very use of synthesis. Designers would (and do) spend a significant amount of time correcting the output of synthesis tools in order to meet the timing constraints. Currently, for most applications it seems that performance is the paramount optimization metric.

Once a circuit is manufactured, it needs to be tested to ensure that it has no manufacturing defects. These tests are input stimuli that distinguish between good and faulty circuits. Traditionally, testing has been considered to be a post design activity, i.e. tests are determined only after the circuit design is complete. Recent research has shown that testability considerations can be included as part of the design process. The resulting circuits have higher coverage of potential faults as well as shorter test sequences in comparison with those designed without these considerations. The final design is evaluated in terms of its testability, which is measured as some function of the fault coverage and

length of tests. Thus, in addition to area and performance, testability has emerged as an important optimization criterion.

It should be pointed out that in a typical design scenario the desired metric is some combination of performance, area and testability. The testability requirements are specified in terms of the minimum acceptable coverage under some fault model. Typically the performance constraints come from the system specification and it does not pay to do any better than what is required. The optimization goal then is to minimize the area, maximize the testability (providing at least the minimum acceptable coverage) and meet the specified performance constraint.

A final caveat: The word optimization is used in logic synthesis much in the same way as it is in the context of optimizing compilers than in the strict mathematical sense, i.e., the quality of the output is improved with respect to some metric as opposed to finding some global maximum or minimum.

#### 2: Input Specification

Inputs may be specified in several different ways to a logic synthesis system. The most common way is to specify a set of Boolean equations that describe the combinational logic blocks and the memory elements connecting the logic blocks. Equivalently, the combinational logic blocks may be specified as an interconnection of logic gates. These two specifications are considered equivalent since there always exists a trivial mapping that converts one to the other. This form of the specification is referred to as a Boolean specification. The specification is said to be mapped if the gates and memory elements in the specification refer to specific members of some cell library. In general, mapped specifications are outputs of synthesis systems; however they may also be inputs. An instance of the mapped specification occurs in technology re-mapping of a design. Here, an already existing design needs to be re-implemented in a new technology. Logic synthesis may be used to improve the absolute quality of the previous design or to modify the implementation to exploit/suit the new technology.

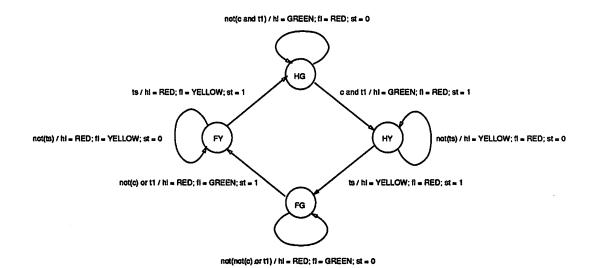

The system being described typically captures some real life situation. In additional to variables that have binary or Boolean values, the specification may include symbolic variables that represent the real-life variables. As an example, Figure 1.2 has a description

of the classic Mead Conway traffic light controller [55] in the BDS language taken from [69] <sup>1</sup>. The actual syntax and description is not significant here, what should be noted is the use of non-binary-valued variables. Here the state variable representing the state of the traffic lights is represented in symbolic form and can take on four possible values. Similarly, the output variables representing the highway and farm lights can take on three values. Since the logic is explicitly specified, this description is considered to be at the logic level even though it involves symbolic variables. This form of specification is referred to as a symbolic specification.

Since signals in a digital circuit can have only binary values 2 the symbolic variables need to be encoded using binary-valued variables. The process of encoding replaces a symbolic variable with a set of binary-valued variables known as encoding variables. Each value of the symbolic variable is mapped to some binary pattern of the encoding variables under the encoding. For example, in the case of the traffic light controller, the four state values HG, HY, FG, FY may be represented as the bit patterns 00, 01, 10, 11 on two binaryvalued encoding variables. The resulting Boolean logic depends on the choice of encoding. Thus, the area, performance and testability of the circuit may depend on the choice of encoding. This gives rise to the encoding problem in logic synthesis wherein an encoding needs to be determined for a symbolic variable such that the resulting logic is optimal under some metric. The versions of the problem where the symbolic variables are inputs or outputs of the combinational logic are referred to as the input and output encoding problems respectively. When the symbolic variable is the state of a finite state machine, then this variable is both an input as well as an output of the finite state machine combinational logic. The additional constraint on the encoding is that the same encoding be selected both for the input as well as the output variable. In this case the encoding problem is referred to as the input-output encoding, or the state assignment problem. This taxonomy was first introduced in [56].

#### 3: Structure of Target Logic

Combinational logic is implemented as a set of interconnected logic gates. The depth of the logic circuit is the maximum number of gates along any path from an input

<sup>&</sup>lt;sup>1</sup>This description has been slightly modified to highlight the symbolic nature of the variables.

<sup>&</sup>lt;sup>2</sup>While circuits using multi-valued logic have been proposed, they have not yet become a practical reality. Thus, it is fair to say that signals in digital circuits are binary-valued.

```

MODEL traffic_light

! control for highway and farm lights

hl, fl

st<0>.

! to start the interval timer

nextState =

c<0>,

! indicating a car on the farm road

ts<0>, tl<0> ! timeout of short and long interval timers

presentState ;

ROUTINE traffic_light_controller;

nextState = presentState; st = 0;

SELECT presentState FROM

[HG]: BEGIN

h1 = GREEN; f1 = RED;

IF c AND t1 THEN BEGIN

nextState = HY; st = 1;

END;

END;

[HY]:BEGIN

hl = YELLOW; fl = RED;

IF ts THEN BEGIN

nextState = FG; st = 1;

END;

END;

[FG]: BEGIN

hl = RED; fl = GREEN;

IF NOT c or t1 THEN BEGIN

nextState = FY; st = 1;

END;

END;

[FY]:BEGIN

hl = RED; fl = YELLOW;

IF ts THEN BEGIN

nextState = HG; st = 1;

END;

END;

ENDSELECT;

ENDROUTINE;

ENDMODEL;

```

Figure 1.2: Symbolic Specification of Logic: An Example

to an output of that circuit. Circuits of depth two are treated rather specially. These two-level circuits can be implemented easily as programmable logic arrays (PLA's) which have a very regular and compact layout. This feature made this form of logic a popular choice in the early days of CAD tools since they could do a reasonably good job of generating the mask layout automatically. In addition, work had already been done in understanding and optimizing two-level logic (e.g. [61]).

However, there exist some logic descriptions such as adders and parity trees which have no compact two-level representation. These must be implemented as circuits of depth greater than two, referred to as multi-level logic. For most circuits, permitting multiple levels in the logic results in smaller circuits. In addition, large PLA's tend to be slow because of long diffusion lines that need to be discharged <sup>3</sup>. Even though multi-level logic typically has more gates from an input to output than two-level logic, yet it may be faster since it does not have the problem of long diffusion lines. Finally, it is noted that two-level logic is always an option even with multi-level logic, since it is just a special case. These factors result in multi-level logic being preferred to two-level logic.

#### The Problem Space

The three issues described above, viz. optimization criterion, input specification and structure of target logic, form orthogonal axes that help define the space of problems in sequential logic synthesis. Since each of the three axes permits several possibilities, the complete problem space is their cartesian product. For example, one point in this space is the area optimization problem for two-level logic implementation with Boolean input specification.

In the next section, the previous work done in this general area is described, as well as how it relates to these problems. This will establish the open problems and provide the motivation for the work presented in this thesis.

#### 1.2.2 Previous Work

There has been a substantial amount of work in the various problems described in Section 1.2.1. Rather than describe the previous work separately for each of the individual problems, the main approaches that have been used are examined, and it is shown how

<sup>&</sup>lt;sup>3</sup>This problem is partially solved in pre-charged PLA's with metal lines; however at the expense of more complex clocking schemes and/or additional area.

they apply for the various problems. Where the volume of literature in a particular area is extensive, only a few representative works have been cited.

#### Combinational Logic Optimization

Combinational logic optimization is used in sequential logic synthesis as follows. The combinational logic blocks are first separated from the memory units, optimized individually and then reconnected. The largest volume of work done in logic synthesis is in this area, perhaps because this has the largest impact on the quality of the final results.

The earliest work in combinational logic optimization can be found in the work of Quine [61] in minimizing the product terms in two-level representations of logic functions. Two-level logic optimization for minimum area has since then been very well-studied. Both exact [61, 52, 20, 64] as well as heuristic solutions [9] have been presented. The results in [63] show that exact solutions can be obtained for significantly large examples by using practically efficient algorithms. In addition, the heuristic algorithms produce results that match or are close to the exact solutions. For all practical purposes this problem is considered to be solved.

Multi-level combinational logic optimization has also gained significant maturity in the past decade. The problem here is significantly more complicated than in two-level logic since the possibilities of restructuring the logic are limitless in comparison. Nonetheless, algorithms and programs that handle both area [21, 12, 8, 32, 60, 7] and performance optimization [77, 73, 57, 6, 21, 32] have been developed. However, unlike two-level minimization, the exact algorithms [62] work only on very small circuits, so it is not known how close the state of the art is to the global optimum.

#### Symbolic Minimization and Encoding

The state assignment problem has been well-studied since the 60's [39, 37, 1]. However, the first attempt to relate the problem with the final logic implementation was made by DeMicheli et al. [59] in 1984 for two-level logic. Actually, the solution presented there was the input encoding approximation to the state assignment problem. This was then generalized in [56] to include output constraints for two-level logic. The general paradigm followed there was to first perform a symbolic minimization of the logic description, and then use this to generate constraints that the encoding must satisfy. The approach used

in [79] is similar. Both of these techniques are heuristic in nature. In [30] exact solutions to this problem have been provided, however these are not practical for any but the smallest of circuits.

In the case of multi-level logic the approaches have not been as rigorous as those for the two-level case. Again this can be attributed to the greater flexibility permitted by multi-level logic. The approaches to the encoding problems here tend to be predictive inasmuch as they select an encoding that is likely to result in smaller logic [25, 34, 45]. Symbolic minimization for multi-level logic has not been proposed thus far.

#### Retiming

Retiming was introduced as a technique to improve the performance of systems at the micro-architectural level [44, 43]. This approach exploits the ability to change the positions of latches in the circuit. If we restrict ourselves to edge-triggered latches, then the cycle time of the system is the longest combinational delay between latches. Thus, it is possible to minimize the cycle time by finding positions of latches that minimize the longest combinational path between any two latches. It has been only recently that this work has been used at the logic level [58]. Retiming does not modify any combinational logic in the circuit. Thus, with respect to sequential circuit optimization the two techniques of combinational logic optimization and retiming may be viewed as duals of each other. Combinational logic optimization considers the latch positions to be fixed and modifies the positions of latches.

#### **Using State Transition Behavior**

Sequential systems may be described by specifying their transition behavior in the form of state transition graphs (STG's) or equivalently as state transition tables. Figure 1.3 shows the state transition table and graph for the traffic light controller described in Figure 1.2. In the state transition table, each row describes a transition in the underlying finite state machine. The transition is from present state PS under the input vector IN to next state NS and the output produced is OUT. In the STG, the vertices represent the states. The arcs represent the transitions. The labels of the form 'input/output' on each arc represent the input vector that causes the transition and the output value produced. This is the

State Transition Graph: Example

| PS | IN                | NS | OUT .                         |

|----|-------------------|----|-------------------------------|

| HG | (not(c and t1)    | HG | hl = GREEN; fl = RED; st = 0  |

| HG | c and t1          | HY | hl = GREEN; fl = RED; st = 1  |

| HY | not(ts)           | HY | hi = YELLOW; fi = RED; st = 0 |

| HY | ts                | FG | hl = YELLOW; fl = RED; st = 1 |

| FG | not(not(c) or t1) | FG | hl = RED; fl = GREEN; st = 0  |

| FG | not(c) or t1      | FY | hl = RED; fl = GREEN; st = 1  |

| FY | not(ts)           | FY | hl = RED; fl = YELLOW; st = 0 |

| FY | ts                | HG | hi = RED; fi = YELLOW; st = 1 |

State Transition Table: Example

Figure 1.3: State Transition Tables and Graphs

same as a symbolic description of the system, since the state is represented symbolically (unencoded) at this level. It is possible to use information about the transition behavior to optimize the final circuit implementation. For example, information about equivalent states may be exploited by modifying a transition to a state s to go to an equivalent state s' [46] or by merging equivalent states into a single state as is done in state minimization. Alternatively, the finite state machine (FSM) may be decomposed into a set of interacting FSM's. There has been a lot of work done in FSM decomposition [38, 29, 2].

There is potential for exploiting more information at this level than would be possible at the gate level. For example, information about equivalent states may be very difficult to extract at the logic level. However, the general problem with this approach is that it is not possible to accurately predict the impact of modifications made at this level on the gate-level implementation. Researchers have proposed using different criteria such as the number of edges [29] or the number of states [22] in the STG as a measure of the complexity. However, none of these is a consistent reflection of the gate-level complexity. The technique presented in [2] is an exception to this. Here a reasonable estimate of the area and/or delay is included in the decomposition technique. However, this is restricted to two-level implementations.

It may seem that even if the input specification is in the form of a gate-level netlist, it may be advantageous to extract its transition behavior and use that in addition to any other techniques that can be exploited at the gate level. The problem in doing that is the combinatorial explosion involved in the extraction. Extracting the STG for any sequential circuit with more than a few latches and inputs is generally considered infeasible.

#### Synthesis for Testability

Research in synthesis for testability started with work that related area optimization of combinational circuits with the *single-stuck-at* fault model in testing [3]. Here it was shown that a *prime and redundant* circuit is fully testable under the single-stuck-at fault model. Later in [36] a synthesis method for fully testable circuits under the *multiple-stuck-at* fault model was developed. Synthesis techniques for fully testable sequential circuits have been presented in [27, 28, 23]. The relationship between circuit performance and testability was established in [40]. Here it was shown that testability need not be sacrificed for higher performance. The problem of delay-fault testability was tackled in [24]. Here, synthesis

techniques for robust-path and gate-delay-fault testable circuits were presented.

There are two aspects of improving the testability properties of a circuit. The first is increasing its testability; this has been described in the previous paragraph. The second is making it more easily testable. This implies reducing both the computing time it takes to derive these tests (e.g. [19]) as well as the time it takes to run these tests on the circuit (e.g. [27]).

#### 1.3 Thesis Overview

Since multi-level logic is the most prevalent target implementation, the work presented in this thesis will focus on this form of logic implementation. An attempt is made to build on previous work done in combinational logic synthesis and see the natural extension of well-understood ideas there in the expanded context of multi-level sequential logic synthesis.

The thesis is divided into two parts. In the first part, it is demonstrated how the dual ideas of retiming and combinational logic optimization can be combined in such a way as to maximize the use of combinational logic optimization. The results here apply to both area and performance optimization. While synthesis for testability is not directly considered, the relationship between the ideas presented here and the testability of the resulting circuits is examined.

The second part presents techniques for the symbolic minimization of multi-level circuits with symbolic inputs. This has direct application in the state assignment problem for multi-level logic.

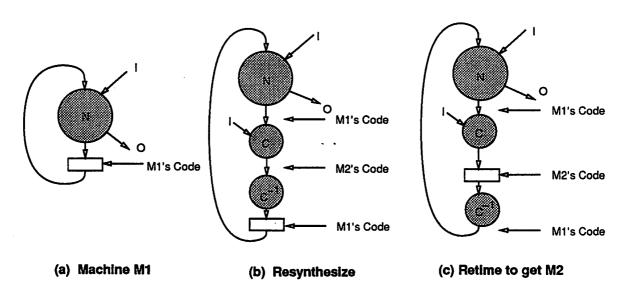

Chapter 2 describes the theoretical results developed in combining retiming and combinational logic optimization. The procedure that utilizes both these techniques is called retiming and resynthesis. Sequential sub-circuits for which all the latches can effectively be ignored are considered. This enables them to be considered as combinational circuits. For these circuits all the latches can be migrated to the periphery of the circuit by a procedure that is an extension of retiming. One of the main results of this chapter are the necessary and sufficient conditions on sub-circuits for which this is possible. This result enables us to use combinational logic optimization beyond latch boundaries; in fact it pushes combinational optimization to its limits in the context of sequential circuits.

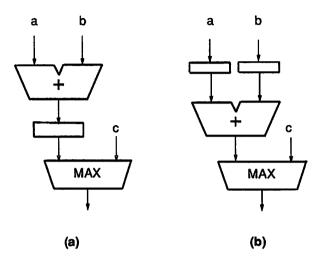

In Chapter 3 the implications and applications of these ideas are described. The

relationship of retiming and resynthesis to logical testing and state assignment is examined. Then it is shown how these ideas can be applied towards the performance optimization of sequential circuits. A special class of sequential circuits is considered, viz. pipelined circuits. Here the equivalence between the performance optimization problem for pipelined circuits and that for combinational circuits is established.

Chapter 4 discusses the issues involved in the practical implementation of retiming and resynthesis as part of a sequential logic optimization system, SIS [70]. Specific algorithms are presented as well as the experiences with using these on some real designs.

The second part of the thesis considers the symbolic minimization of multi-level circuits with multiple-valued inputs. Chapter 5 presents extensions of the various multi-level optimization techniques used with Boolean circuits to handle multiple-valued inputs. The main contribution of this chapter is the technique for factorization of logic expressions with multiple-valued variables. This was the missing link in the multi-level optimization of circuits with multiple-valued inputs. It is then shown how the results of symbolic minimization can be used to tackle the input encoding problem. This can be used to approximate the state assignment problem; an approximation that is valid when the primary output logic dominates the next state logic.

The implementation of these issues uncovers some interesting problems. These practical issues are considered in Chapter 6 along with experimental results for the input encoding of some real designs.

Finally, Chapter 7 summarizes what has been learned from this work and considers future directions in this area.

# Part I Retiming and Resynthesis

## Chapter 2

## **Basic Ideas**

"You can draw water out of a water-well," said the Hatter; "so I should think you could draw treacle out of a treacle-well - eh, stupid?"

- Lewis Carroll, "Alice in Wonderland"

Over the last decade combinational logic optimization has attained a significant level of maturity. (Some of the work done in this area was reviewed in Chapter 1.) The problems and approaches there are well understood: almost fully in the two-level logic case, and to a lesser extent in the multi-level logic case. However, in sequential logic optimization their utility is restricted to individual portions of combinational logic. Logical relationships are not exploited between gates that are separated by latch boundaries. What is desirable is the ability to use the ideas in combinational logic optimization beyond latch boundaries. In this direction we would like to push combinational logic optimization to its limits, i.e., capture all the logical relationships that exist between gates in a sequential circuit even though they may not belong to the same block of combinational logic. This thought direction is a very natural one; it stems from the desire to build on what is already known and forms the motivation behind the work presented in this part of the thesis. First the application domain of these ideas is specified as a class of sequential circuits with specific clocking methodologies. Then the suggested approach is described, which is termed retiming and resynthesis since it combines retiming with resynthesis of combinational logic. (Most of the work presented in this chapter was first reported in [49]).

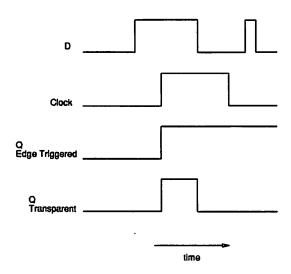

Figure 2.1: Edge Triggered and Transparent Latches

#### 2.1 Clocking Methodology

As mentioned in Chapter 1, only synchronous sequential circuits are considered, i.e., all memory elements latch their data synchronously with respect to a clock signal common to the circuit. Within synchronous circuits there is flexibility as to when the data is latched with respect to the clock edge. This is illustrated in Figure 2.1. Let D be the input and Q the output of the latch. In edge-triggered latches the data present at the clock edge (the rising edge in this case) is latched and available at Q. In transparent or level-sensitive latches, the latch is transparent during the time the clock is high, i.e. the data input is available at the output. The data value at the end of the clock high period is latched.

This work is restricted to an edge-triggered clocking methodology. Thus, the word "latch" in the following exposition refers to an edge-triggered latch or a flip-flop. It may seem that this restriction is a fairly strong one given the designers' wisdom that transparent latches result in higher performance. This fact is illustrated through examples in [65], where it is shown that by appropriately selecting the clocking parameters it may be possible to clock a synchronous system with transparent latches significantly faster than one with edge-

2.2. OVERVIEW 21

triggered ones. While that may sometimes be the case, a large fraction of ASIC (Application Specific Integrated Circuit) designs are done using edge-triggered latches [5]. The principal reason for this is the ease of analysis of circuits with edge-triggered latches. There are no complex "time borrowing" scenarios and designers do not have to worry about "short paths". Since ASIC's are the application domain where synthesis is the predominant design methodology, this does not seem too restrictive.

Retiming algorithms have this restriction <sup>1</sup> and since this work uses retiming, it is inherited. Current developments in exploiting retiming techniques with transparent latches [71] could enable retiming and resynthesis to be applied to circuits with transparent latches.

#### 2.2 Overview

Sub-circuits in a sequential circuit are characterized for which the latches can effectively be ignored and thus the sub-circuit can be considered as a combinational block. This permits existing combinational logic optimization techniques to be used on it. This approach is more powerful than combinational logic optimization, since it examines interactions between portions of logic separated by latches. As a result, the optimization process makes full use of dependencies between gates. Moreover, it is guaranteed that it is complete, i.e., the largest sub-circuit for which this can be done is determined. This ensures that no optimization that can be obtained by considering interactions between gates is missed. Converting this sub-circuit to a combinational logic block can be viewed as a retiming process in which all the latches are pushed to the periphery of the sub-network. However, this technique is more powerful than conventional retiming in that it permits negative latches to be pushed to the periphery. This is equivalent to temporarily "borrowing" latches from the environment, and is a legitimate operation as long as these latches are "returned" to the environment at the end of the optimization process. This additional allowance is more powerful since it permits a larger portion of the logic to be viewed as a single block than is permitted by conventional latch movements using retiming. Next, this combinational logic block may be resynthesized according to a specified cost function. This could be minimizing the area, the delay or meeting a particular area/delay tradeoff. Conditions are specified

<sup>&</sup>lt;sup>1</sup>Retiming algorithms need this restriction in order to compute the cycle time of the circuit in polynomial time.

for the legal redistribution of latches in this circuit, i.e., conditions under which the latches borrowed from the environment can be returned. The redistribution can be done while satisfying constraints such as minimizing the number of latches subject to a specified cycle time (if these constraints are satisfiable) by using the algorithms described in [43]. Since the optimization algorithms work directly on the gate-level netlist, they use the gate-level complexity as their cost function, unlike algorithms that work on state transition graphs.

#### 2.3 Theoretical Formulation

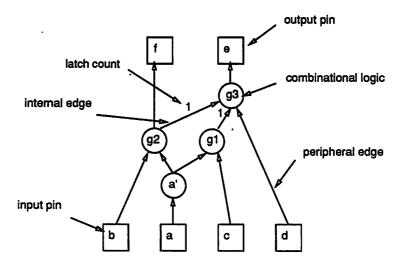

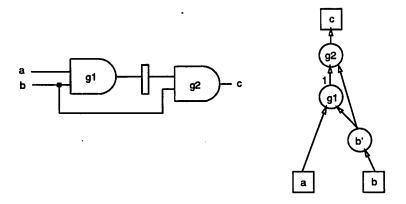

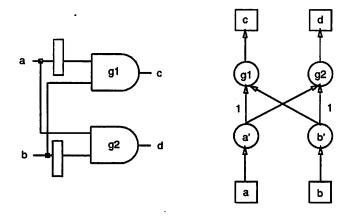

Let us first focus our attention on sequential circuits whose underlying topology is acyclic. (These are also referred to as feed-forward circuits.) These circuits are modeled by a directed acyclic graph called a communication  $graph^2$  where each vertex v represents either

- a) an input/output pin or

- b) a combinational logic block.

The input/output pins correspond to the primary inputs and primary outputs of the circuit. The granularity of the combinational logic block may vary: it may be a single gate or a larger module such as an adder. The vertices in the graph are connected by directed edges. A restriction is placed that each input pin has no incoming edges and exactly one outgoing edge (a single-output source), and that an output pin has no outgoing edges and exactly one incoming edge (a single-input sink). If a primary input is used in more than one place in the circuit then this is captured by introducing a dummy vertex in the graph that handles the multiple out-edges. (The out-edges are also referred to as fanout.) An internal edge connects vertex u to vertex v if both u and v represent combinational logic blocks, and the logic represented by v explicitly depends on the value computed at u. A peripheral edge connects either an input pin to the logic block that uses that input or connects a logic block that computes the value of an output to the corresponding output pin. Each edge e has a corresponding weight w(e) representing the number of latches between the two vertices it connects. An example of a sequential circuit and its communication graph is shown in Figure 2.2. Note that the multiple fanout of primary input a is handled through the internal vertex a' in the graph. For simplicity in the figure, if the edge weight is 0 then

<sup>&</sup>lt;sup>2</sup>This is related to the definition of a communication graph presented in [44].

the edge label is omitted. A sequential circuit is alternatively referred to as a sequential network. The terms circuit, network, and graph are used interchangeably whenever there is no ambiguity.

A path between two vertices  $v_1$  and  $v_2$  in the graph is a sequence of consecutive edges from  $v_1$  to  $v_2$ . The weight of a path is the sum of the weights of all the edges along the path. In Figure 2.2, the path from input b to output f has weight 0, while the path from b to e has weight 1.

### 2.3.1 Retiming: An Overview

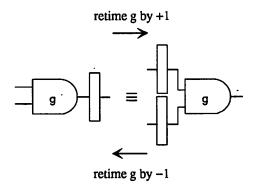

The cycle time of a synchronous sequential circuit is determined by the length of the longest path between any two latches in the circuit. The concept of retiming exploits the ability to move the latches in the circuit in order to decrease the length of the longest path in the circuit while preserving its functional behavior. Retiming algorithms were first proposed by Leiserson et al. [44, 43]. To illustrate this with a small example, consider Figure 2.3. The circuit on the left is functionally equivalent to the circuit on the right since delaying the output of gate g by a cycle is equivalent to delaying each of its inputs by a cycle. The movement of latches during retiming is quantified by an integer L(v) (called the lag of v) for each vertex v, which represents the number of latches that are to be moved in the circuit from each out-edge of vertex v to each of its in-edges. Thus, in Figure 2.3 the circuit on the right is obtained from the circuit on the left by retiming g by +1. Similarly, in obtaining the circuit on the left from that on the right g has been retimed by -1. For input and output pins the lag is 0. Consider an edge e(u, v) in the circuit. Let w(e) be the weight of the edge in the graph before retiming and  $w_r(e)$  be the weight after retiming.  $w_r$  is determined from w and the lags by the following equation:

$$w_r(e) = w(e) + L(v) - L(u)$$

This is used to prove a simple result that will be used frequently in the sequel.

**Lemma 2.3.1** (Leiserson and Saxe) Let p be a path between input i and output j. Let W(p) be the weight of this path. Let r be a retiming and  $W_r(p)$  be the weight of this path after retiming. Then,  $W(p) = W_r(p)$ .

Proof.

$$W(p) = \sum_{path \ i_i \to o_i} w(e)$$

## **Sequential Circuit**

## **Communication Graph**

Figure 2.2: Sequential Circuits and Communication Graphs: An Example

Figure 2.3: Retiming: An Example

$$W_r(p) = \sum_{path \ i_i \to o_j} w_r(e) = \sum_{path \ i_i \to o_j} (w(e) + L(v) - L(u))$$

This sum telescopes:

$$W_r(p) = \sum_{path \ i_i \rightarrow o_j} w(e) + L(o_j) - L(i_i)$$

Since  $L(o_j) = L(i_i) = 0$ ,

$$W_r(p) = \sum_{path \ i: r o i} w(e) = W(p)$$

The following definition is from [44].

**Definition 2.3.1** A legal retiming is the assignment of an integer L(v) to each vertex in the communication graph such that for each edge e,  $w_r(e) \ge 0$ .

For a legal retiming, the edge weights of the retimed graph must be non-negative; indicating a non-negative number of latches on each edge. Thus, there exists a real physical circuit corresponding to this graph. This is not possible with negative edge weights in the retimed circuit since there is no physical circuit component corresponding to a negative latch. A legal retiming has been shown [44] to generate a circuit that is functionally equivalent to the original circuit. Figure 2.4 shows a legal retiming on the communication graph of Figure 2.2. Here, the lag of g1 is +1 and the lag for all other vertices is 0.

Figure 2.4: Legal Retiming: An Example

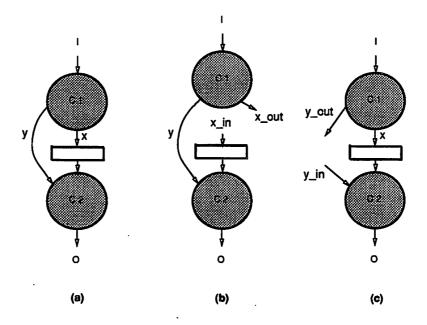

## 2.3.2 Extensions to Retiming

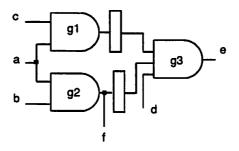

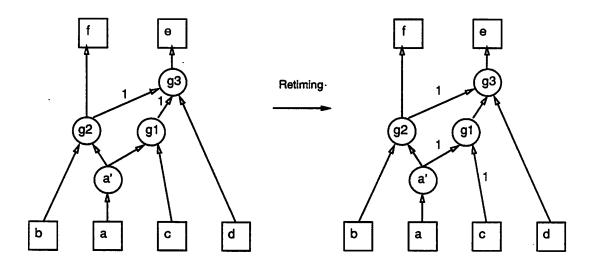

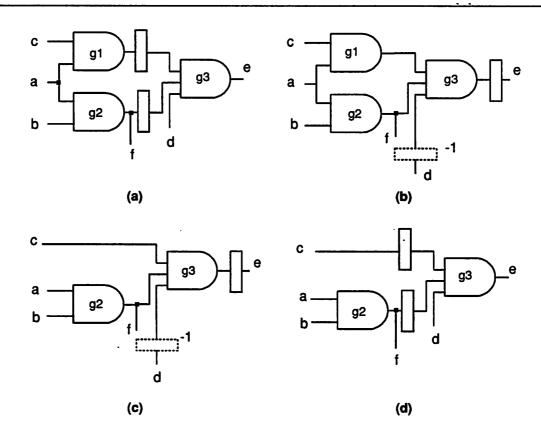

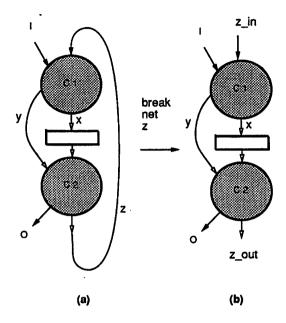

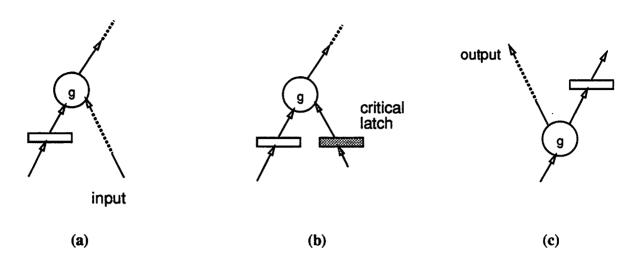

It is now shown how retiming can be extended by introducing the concept of a "negative" latch, i.e., an edge weight in the graph that is negative. Negative edge weights are permitted on peripheral edges only. Allowing a negative edge weight n on a peripheral edge is equivalent to "borrowing" n latches from the environment. The latches may be "returned" by a subsequent retiming step, whereby n latches are forced to each edge with weight -n. The observation that the peripheral edge weights can temporarily take on negative values allows retiming operations and subsequent optimizations that would otherwise not be possible. This is illustrated with the circuit in Figure 2.5(a). Consider the latch on the connection between g2 and g3. In order to move this latch from its present position either g3 is retimed by -1 (for forward motion) or g2 retimed by +1 (backward motion). If g3 is retimed by -1, this will result in an edge weight of -1 at input d. If g2 is retimed by +1 this will result in an edge weight of -1 at output f. Thus, neither of these retimings is legal. However, if this "illegal" retiming were permitted temporarily, then it is possible to gain additional advantage over what is permitted by just legal retimings. Figure 2.5(b) shows the circuit after g3 has been retimed by -1. The edge weight of -1 on input d is

Figure 2.5: Example: Use of a Negative Latch

represented by the latch in dotted lines and with the label -1 on it. At this point, all the gates in the circuit are part of a single combinational logic block. For this logic block, it can be shown that the functionality remains unchanged if the connection from a to g1 is deleted, i.e., this connection is redundant or in testing parlance, untestable for a stuck-at-1 fault in the context of this combinational logic block. Thus, this connection may be deleted and g1 replaced by a wire. This simplified circuit is shown in Figure 2.5(c). Note that this connection (from a to g1) is not redundant in the context of the original combinational block (consisting of g1 and g2) defined by the original position of latches. Only after we could view all the gates as part of a single combinational logic block was this redundancy exposed. Of course, this circuit still is not realizable since there is a negative latch at input d. This situation can easily be rectified by retiming g3 by +1. This annihilates the negative latch at input d resulting in the circuit in Figure 2.5(d). This example illustrates the advantage gained by permitting illegal retimings temporarily. Later in this section it is shown why this is a legitimate operation.

Let us now go back and see what enabled us to eliminate g1 in the previous example. Once we were able to consider all three gates in the circuit as part of a larger combinational block, we could use the combinational optimization technique of redundancy removal to detect and delete the redundant connection. This is precisely what we were looking for, i.e., a way to consider and exploit logical relationships between gates that extend beyond latch boundaries. Ideally, we would like to push out all the latches in the circuit to the peripheral edges. This results in no latches on any of the internal edges and thus all the gates are part of the same combinational logic block. This permits the use of any combinational logic optimization technique on this larger combinational block. The notion of a peripheral retiming does precisely this.

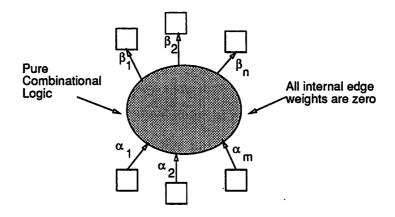

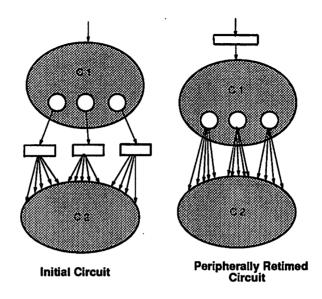

**Definition 2.3.2** A peripheral retiming is a retiming such that for each internal edge e,  $w_r(e) = 0$ .

This is graphically shown in Figure 2.6. After peripheral retiming, there are  $\alpha_i$  latches at input pin i,  $\beta_j$  latches at output pin j, and no latches on any internal edge.

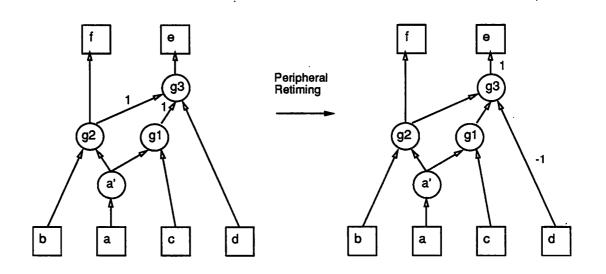

The circuit in Figure 2.5(b) is a peripheral retiming of the one in Figure 2.5(a). The same peripheral retiming is shown in terms of the communication graph in Figure 2.7.

The condition that  $w_r(e)$  is 0 for all internal edges forces all latches to the pe-

Figure 2.6: Peripheral Retiming

Figure 2.7: Peripheral Retiming: Example

ripheral edges. Note that the definition permits negative weights on the peripheral edges, which corresponds to the negative latch concept presented earlier. Permitting negative latches temporarily on peripheral edges is a legitimate operation as shown by the following theorem. Functional equivalence here refers to the equivalence of the finite automata corresponding to the initial and final circuits.

**Theorem 2.3.1** A circuit that undergoes a peripheral retiming, combinational optimization and a subsequent legal retiming is functionally equivalent to the original circuit.

**Proof.** Let  $C_1$  be the original circuit and  $C_2$  be the peripherally-retimed circuit obtained with retiming r. Let  $\alpha_i$  and  $\beta_j$  be the number of latches at the  $i^{th}$  input and  $j^{th}$  output pin in  $C_2$ . Let  $C_3$  be the circuit obtained after combinational resynthesis,  $\mathcal{R}$ , on the interior combinational logic and let  $C_4$  be the circuit obtained after a legal retiming l on  $C_3$ .

Let  $\alpha_{min} = |min(0, \alpha_i)|$  over all  $\alpha_i$  and let  $\beta_{min} = |min(0, \beta_i)|$  over all  $\beta_i$ . Consider the circuit  $C_5$  obtained from  $C_1$  by adding  $\alpha_{min}$  latches at each input pin and  $\beta_{min}$ latches at each output pin.  $C_5 \equiv \text{delay}(C_1, \alpha_{min} + \beta_{min})$ , i.e. given an input-output vector sequence  $(\mathcal{I}, \mathcal{O})$  for  $C_1$ , the input sequence  $\mathcal{I}$  results in the output sequence  $\mathcal{O}$  delayed by  $\alpha_{min} + \beta_{min}$  cycles in  $C_5$ . Let  $C_6$  be the circuit obtained by retiming  $C_5$  with r. This is a peripheral retiming of  $C_5$  with  $\alpha_i' = \alpha_i + \alpha_{min}$  and  $\beta_j' = \beta_j + \beta_{min}$ . Note that this is a legal retiming since there are no negative latches, as  $\alpha'_i$  and  $\beta'_i$  are non-negative and there are no other latches in the circuit. Here recourse is taken to the results in [44] that show functional equivalence with legal retimings to claim that  $C_6$  is equivalent to  $C_5$  3. Combinational resynthesis,  $\mathcal{R}$ , of the interior combinational logic of  $C_6$ , resulting in the circuit  $C_7$ , obviously does not change its functionality since none of the functions of any primary outputs or latch inputs are changed by this. Now, retiming l is applied to  $C_7$  to result in  $C_8$ . Note that since l was a legal retiming for  $C_3$  it must result in at least  $\alpha_{min}$  latches at each input pin and  $\beta_{min}$  latches at each output pin. Also, by transitivity,  $C_8$  is equivalent to  $C_5$ . Hence,  $C_8 \equiv \text{delay}(C_1, \alpha_{min} + \beta_{min})$ . Let  $C_9$  be obtained from  $C_8$  by removing  $\alpha_{min}$ latches from each input pin and  $\beta_{min}$  latches from each output pin. Thus,  $C_9 \equiv \text{delay}(C_1,$ 0) i.e.  $C_9$  is equivalent to  $C_1$ . Note that  $C_9$  is identical to  $C_4$  because the same resynthesis  $\mathcal{R}$  and final retiming l were applied in order to obtain them, ensuring that they have the same gate and latch netlists. Thus,  $C_4$  is equivalent to  $C_1$ .

<sup>&</sup>lt;sup>3</sup>Functional equivalence here is subject to being able to get the two circuits in equivalent states. The problem of finding equivalent states for the original and retimed circuits has been looked at in [76] and is discussed in Section 2.6.

Figure 2.8: Circuit with no peripheral retiming: Example 1

## 2.3.3 Conditions for Peripheral Retiming

Not all circuit topologies permit a peripheral retiming. Two such topologies are now considered.

Consider the circuit in Figure 2.8 and its corresponding communication graph. All attempts to move the latch (either backward or forward) to the periphery result in a negative weight on the edge between b' and g2. In fact, as will be shown later in this section, this circuit cannot be peripherally retimed. Examining the circuit gives us some insight into why this is so. The output c depends on the value of input b at two different times. Let us assume that a peripheral retiming were possible. Then in the peripherally retimed circuit c would depend only on one time value of b since all paths from b to c would have the same number of latches, viz.  $\alpha_b + \beta_c$ . This would not capture the correct behavior and is the reason why no peripheral retiming exists.