# Copyright © 1989, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# SELF-TIMED INTEGRATED CIRCUITS FOR DIGITAL SIGNAL PROCESSING

Copyright © 1989

by

Gordon Merrill Jacobs

Memorandum No. UCB/ERL M89/128

30 November 1989

# SELF-TIMED INTEGRATED CIRCUITS FOR DIGITAL SIGNAL PROCESSING

Copyright © 1989

by

Gordon Merrill Jacobs

Memorandum No. UCB/ERL M89/128

30 November 1989

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# SELF-TIMED INTEGRATED CIRCUITS FOR DIGITAL SIGNAL PROCESSING

Copyright © 1989

by

Gordon Merrill Jacobs

Memorandum No. UCB/ERL M89/128

30 November 1989

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## Self-Timed Integrated Circuits for Digital Signal Processing

by

#### Gordon Merrill Jacobs

#### **Abstract**

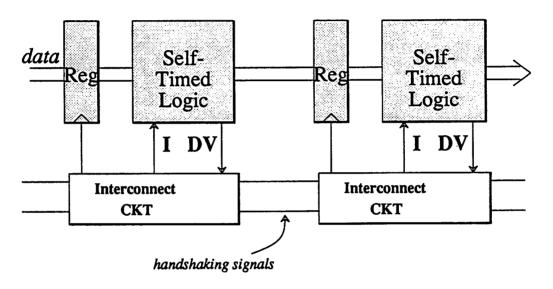

As the clocking rates of large digital Integrated Circuits (ICs) continue to increase, the global synchronization of the circuits becomes an increasingly difficult design problem. While scaling the feature size of an IC technology has traditionally been the method for obtaining increased performance, limitations in the wiring layers can prevent taking full advantage of the faster devices used in the circuit. At the board level, asynchronous interfaces have been introduced in places where synchronization becomes problematic. A natural extension to this idea is to extend the use of asynchronous circuits to within an IC. Self-timed circuits are introduced as a means for implementing asynchronous ICs. Self-timed circuits, in addition to performing computation, generate completion information that can be used by appropriate interconnection blocks to oversee the transfer of data between stages without the use of any global clock signal.

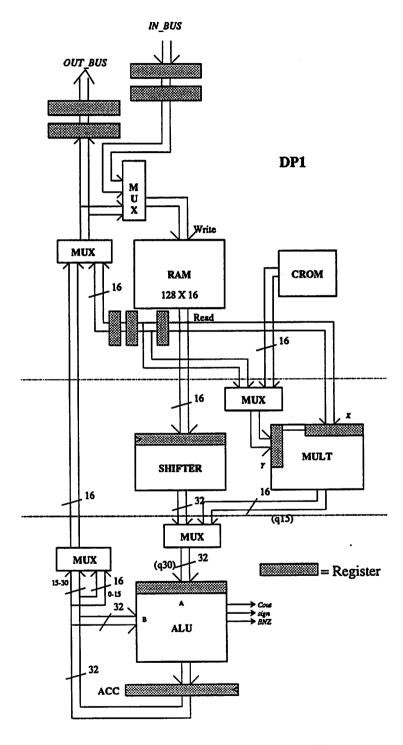

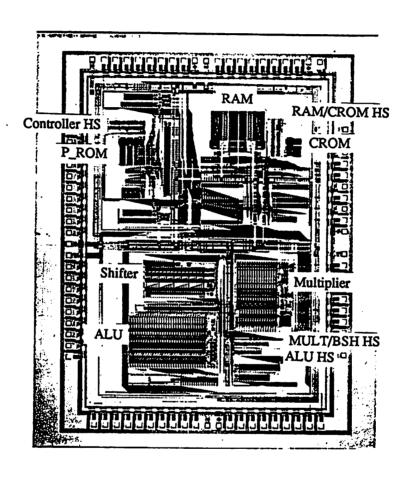

As a design example, a complete micro-processor based digital signal processor (DSP) was designed and fabricated using self-timed circuits following a 4-cycle handshaking protocol to provide fully asynchronous operation without a global clock. The DSP is mask programmable and it was fabricated in  $2\mu m$  N-well CMOS in an active area of 6.6mm x 4.7mm. The processor showed reliable operation at power supply voltages between 3.5V and 7V, illustrating how self-timed circuitry adjusts to variations in environment (and processing) while still operating correctly.

This report starts by introducing previous approaches to asynchronous processors followed by an explanation why it is both necessary and feasible to implement them in

IC form. A survey of self-timed circuitry is then presented along with a description of a synthesis method for generating the interconnection or "handshake" circuits required to implement the correct handshaking protocol for data transfers. Details of the DSP design are given along with experimental results. Finally, some conclusions about the work are drawn.

Robert W. Brodersen

Chairman of Committee

Robert W. Brodersin

#### Acknowledgments

I'd like to express my deepest gratitude to Professor Bob Brodersen who has done so much for me since we met way back in 1976. Throughout both my Masters and Ph.D. research, Bob has been a source for many good ideas, financial support and counseling. Without his friendship, the work would not have been nearly as enjoyable.

The collective group of students under Prof. Brodersen known as "bobsgroup" provided much help to me throughout my research. I thank them for all of the useful discussions. Outside of our immediate group, Professor David Messerschmitt and Teresa Meng contributed many interesting ideas and developed for the most part, the synthesis program used for the handshaking circuits. Thanks to the CAD group for helping me learn programming.

Thanks also to Professors Paul Gray and David Hodges who have made me feel more like a peer than a lowly grad student since my return to school.

The guys at Teknekron CSD also deserve a big thanks for giving me support over the years. It has been a pleasure working with Amine Haoui, Nan-Sheng Lin, and Roger Strauch in parallel with my research at UCB.

Last, but not least, thanks to Mom and Dad for encouraging me to do what I want to do in life, and for absorbing all of the complaints along the way. To the boys in Chicago, and you know who you are, your faith in my abilities on and off campus beats all.

## Contents

| List of Figures   Vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ac  | knov  | vledgments                                 | i   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------------------------------|-----|

| 1 Introduction       1. Definition of self-timed       2. Background       4. 2.1 Early Work       4. 2.1 Early Work       4. 2.2 Arbiters and Metastability       6. 2.3 Data Flow Computers       6. 2.4 Systolic Arrays       8. 2.4 Systolic Arrays       8. 2.5 Wavefront Arrays       8. 3. The Self-timed Model       8. 4. Scope         2 Motivations for using Self-Timed Techniques       1. Design Issues       1. 2. Scaling and Technological Reasons       1. 2. 2. A real scaled process       1. 2. 2. A real scaled process       1. 2. 2. A real scaled process       1. 2. 3. Interconnect       1. 2. 4. Clock Distribution       2. 3. Summary       3. Summary       3. 3. 3. 2. DCVSL Description       3. 3. 2. DCVSL Description       3. 3. 2. Dcvsciption       3. 3. 3. 3. 3. 3. Alternatives to DCVSL       3. Alternatives to DCVSL       5. 3. Alternatives to DCVSL       5. 3. 3. Sample-Set Differential Logic (SSDL)       5. 5. 3. 3. 5. 5. 5. 5. 5. 5. 5. 5. 5. 5. 5. 5. 5. | Та  | ble o | f Contents                                 | iii |

| 1. Definition of self-timed       6         2. Background       6         2.1 Early Work       6         2.2 Arbiters and Metastability       6         2.3 Data Flow Computers       6         2.4 Systolic Arrays       8         2.5 Wavefront Arrays       8         3. The Self-timed Model       8         4. Scope       9         2 Motivations for using Self-Timed Techniques       11         1. Design Issues       12         2. Scaling and Technological Reasons       15         2.1 Scaling Laws       16         2.2 A real scaled process       16         2.3 Interconnect       17         2.4 Clock Distribution       2         3. Summary       33         3 Realization of Self-Timed Circuits       33         1. Completion Signals       30         2. DCVSL Description       30         2.1 Completion Signal Generation in DCVSL       31         2.2 Charge-Sharing       4         2.3 Design and Layout Issues       4         3. Alternatives to DCVSL       5         3.1 Sample-Set Differential Logic (SSDL)       5                                                                    | Lis | st of | Figures                                    | vii |

| 2. Background       4         2.1 Early Work       4         2.2 Arbiters and Metastability       6         2.3 Data Flow Computers       6         2.4 Systolic Arrays       5         2.5 Wavefront Arrays       8         3. The Self-timed Model       8         4. Scope       9         2 Motivations for using Self-Timed Techniques       11         1. Design Issues       11         2. Scaling and Technological Reasons       12         2.1 Scaling Laws       12         2.2 A real scaled process       14         2.3 Interconnect       14         2.4 Clock Distribution       2         3. Summary       3         3 Realization of Self-Timed Circuits       3         1. Completion Signals       3         2. DCVSL Description       3         2.1 Completion Signal Generation in DCVSL       3         2.2 Charge-Sharing       4         2.3 Design and Layout Issues       4         3. Alternatives to DCVSL       5         3.1 Sample-Set Differential Logic (SSDL)       5                                                                                                                     | 1   | Intro |                                            | 1   |

| 2.1       Early Work       4         2.2       Arbiters and Metastability       6         2.3       Data Flow Computers       6         2.4       Systolic Arrays       8         2.5       Wavefront Arrays       8         3.       The Self-timed Model       8         4.       Scope       9         2       Motivations for using Self-Timed Techniques       1         1.       Design Issues       1         2.       Scaling and Technological Reasons       1         2.1       Scaling Laws       1         2.2       A real scaled process       1         2.3       Interconnect       1         2.4       Clock Distribution       2         3.       Summary       3         3       Realization of Self-Timed Circuits       3         1.       Completion Signals       3         2.       DCVSL Description       3         2.1       Completion Signal Generation in DCVSL       3         2.2       Charge-Sharing       4         2.3       Design and Layout Issues       4         3.       Alternatives to DCVSL       5         3.1       Sample-Set                                                 |     | 1.    |                                            |     |

| 2.2       Arbiters and Metastability       6         2.3       Data Flow Computers       6         2.4       Systolic Arrays       8         2.5       Wavefront Arrays       8         3.       The Self-timed Model       8         4.       Scope       9         2       Motivations for using Self-Timed Techniques       12         1.       Design Issues       13         2.       Scaling and Technological Reasons       15         2.1       Scaling Laws       16         2.2       A real scaled process       16         2.3       Interconnect       17         2.4       Clock Distribution       2         3.       Summary       30         3.       Realization of Self-Timed Circuits       31         1.       Completion Signals       32         2.       DCVSL Description       33         2.1       Completion Signal Generation in DCVSL       33         2.2       Charge-Sharing       4         2.3       Design and Layout Issues       4         3.       Alternatives to DCVSL       5         3.1       Sample-Set Differential Logic (SSDL)       5                                        |     | 2.    |                                            |     |

| 2.3       Data Flow Computers       6         2.4       Systolic Arrays       8         2.5       Wavefront Arrays       8         3.       The Self-timed Model       8         4.       Scope       9         2       Motivations for using Self-Timed Techniques       12         1.       Design Issues       12         2.       Scaling and Technological Reasons       12         2.1       Scaling Laws       13         2.2       A real scaled process       14         2.3       Interconnect       14         2.4       Clock Distribution       22         3.       Summary       33         3.       Realization of Self-Timed Circuits       33         2.       DCVSL Description       30         2.1       Completion Signals       30         2.2       Charge-Sharing       40         2.3       Design and Layout Issues       41         3.1       Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                         |     |       | 2.1 Early Work                             | 4   |

| 2.4       Systolic Arrays       3         2.5       Wavefront Arrays       3         3.       The Self-timed Model       4         4.       Scope       5         2       Motivations for using Self-Timed Techniques       1         1.       Design Issues       1         2.       Scaling and Technological Reasons       1         2.1       Scaling Laws       1         2.2       A real scaled process       1         2.3       Interconnect       1         2.4       Clock Distribution       2         3.       Summary       3         3       Realization of Self-Timed Circuits       3         1.       Completion Signals       3         2.       DCVSL Description       3         2.1       Completion Signal Generation in DCVSL       3         2.2       Charge-Sharing       4         2.3       Design and Layout Issues       4         3.       Alternatives to DCVSL       5         3.1       Sample-Set Differential Logic (SSDL)       5                                                                                                                                                       |     |       | 2.2 Arbiters and Metastability             | 6   |

| 2.4       Systolic Arrays       8         2.5       Wavefront Arrays       8         3.       The Self-timed Model       8         4.       Scope       9         2       Motivations for using Self-Timed Techniques       12         1.       Design Issues       12         2.       Scaling and Technological Reasons       12         2.1       Scaling Laws       13         2.2       A real scaled process       14         2.3       Interconnect       14         2.4       Clock Distribution       22         3.       Summary       33         3.       Realization of Self-Timed Circuits       35         1.       Completion Signals       35         2.       DCVSL Description       36         2.1       Completion Signal Generation in DCVSL       33         2.2       Charge-Sharing       4         2.3       Design and Layout Issues       4         3.       Alternatives to DCVSL       5         3.1       Sample-Set Differential Logic (SSDL)       5                                                                                                                                          |     |       | 2.3 Data Flow Computers                    | 6   |

| 2.5       Wavefront Arrays       3         3.       The Self-timed Model       4         4.       Scope       5         2       Motivations for using Self-Timed Techniques       1         1.       Design Issues       1         2.       Scaling and Technological Reasons       1         2.1       Scaling Laws       1         2.2       A real scaled process       1         2.3       Interconnect       1         2.4       Clock Distribution       2         3.       Summary       3         3       Realization of Self-Timed Circuits       3         1.       Completion Signals       3         2.       DCVSL Description       3         2.1       Completion Signal Generation in DCVSL       3         2.2       Charge-Sharing       4         2.3       Design and Layout Issues       4         3.       Alternatives to DCVSL       5         3.1       Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                 |     |       |                                            |     |

| 3. The Self-timed Model       8         4. Scope       9         2 Motivations for using Self-Timed Techniques       12         1. Design Issues       12         2. Scaling and Technological Reasons       13         2.1 Scaling Laws       14         2.2 A real scaled process       14         2.3 Interconnect       14         2.4 Clock Distribution       2         3. Summary       3         3 Realization of Self-Timed Circuits       3         1. Completion Signals       3         2. DCVSL Description       3         2.1 Completion Signal Generation in DCVSL       3         2.2 Charge-Sharing       4         2.3 Design and Layout Issues       4         3. Alternatives to DCVSL       5         3.1 Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                  |     |       |                                            |     |

| 4. Scope       9         2 Motivations for using Self-Timed Techniques       12         1. Design Issues       12         2. Scaling and Technological Reasons       15         2.1 Scaling Laws       16         2.2 A real scaled process       16         2.3 Interconnect       16         2.4 Clock Distribution       22         3. Summary       33         3. Realization of Self-Timed Circuits       35         1. Completion Signals       36         2. DCVSL Description       36         2.1 Completion Signal Generation in DCVSL       36         2.2 Charge-Sharing       4         2.3 Design and Layout Issues       4         3. Alternatives to DCVSL       5         3.1 Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                                                   |     | 3.    |                                            |     |

| 1. Design Issues       1.         2. Scaling and Technological Reasons       1.         2.1 Scaling Laws       1.         2.2 A real scaled process       1.         2.3 Interconnect       1.         2.4 Clock Distribution       2.         3. Summary       3.         3. Gompletion of Self-Timed Circuits       3.         1. Completion Signals       3.         2. DCVSL Description       3.         2.1 Completion Signal Generation in DCVSL       3.         2.2 Charge-Sharing       4         2.3 Design and Layout Issues       4         3. Alternatives to DCVSL       5         3.1 Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |       | Scope                                      | 9   |

| 1. Design Issues       1         2. Scaling and Technological Reasons       1         2.1 Scaling Laws       1         2.2 A real scaled process       1         2.3 Interconnect       1         2.4 Clock Distribution       2         3. Summary       3         3. Completion of Self-Timed Circuits       3         1. Completion Signals       3         2. DCVSL Description       3         2.1 Completion Signal Generation in DCVSL       3         2.2 Charge-Sharing       4         2.3 Design and Layout Issues       4         3. Alternatives to DCVSL       5         3.1 Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2   | Mot   | ivations for using Self-Timed Techniques   | 11  |

| 2. Scaling and Technological Reasons       15         2.1 Scaling Laws       15         2.2 A real scaled process       16         2.3 Interconnect       16         2.4 Clock Distribution       21         3. Summary       32         3. Realization of Self-Timed Circuits       33         1. Completion Signals       34         2. DCVSL Description       36         2.1 Completion Signal Generation in DCVSL       36         2.2 Charge-Sharing       4         2.3 Design and Layout Issues       4         3. Alternatives to DCVSL       5         3.1 Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |       | Design Issues                              | 11  |

| 2.1       Scaling Laws       15         2.2       A real scaled process       14         2.3       Interconnect       14         2.4       Clock Distribution       2         3.       Summary       3         3.       Realization of Self-Timed Circuits       3         1.       Completion Signals       3         2.       DCVSL Description       3         2.1       Completion Signal Generation in DCVSL       3         2.2       Charge-Sharing       4         2.3       Design and Layout Issues       4         3.       Alternatives to DCVSL       5         3.1       Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |       | Scaling and Technological Reasons          | 12  |

| 2.2 A real scaled process       1-         2.3 Interconnect       1-         2.4 Clock Distribution       2-         3. Summary       3-         3 Realization of Self-Timed Circuits       3-         1. Completion Signals       3-         2. DCVSL Description       3-         2.1 Completion Signal Generation in DCVSL       3-         2.2 Charge-Sharing       4-         2.3 Design and Layout Issues       4-         3. Alternatives to DCVSL       5-         3.1 Sample-Set Differential Logic (SSDL)       5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |       | 2.1 Scaling Laws                           | 13  |

| 2.3       Interconnect       1-         2.4       Clock Distribution       2-         3.       Summary       3-         3       Realization of Self-Timed Circuits       3-         1.       Completion Signals       3-         2.       DCVSL Description       3-         2.1       Completion Signal Generation in DCVSL       3-         2.2       Charge-Sharing       4-         2.3       Design and Layout Issues       4-         3.       Alternatives to DCVSL       5-         3.1       Sample-Set Differential Logic (SSDL)       5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |       | 2.2 A real scaled process                  | 14  |

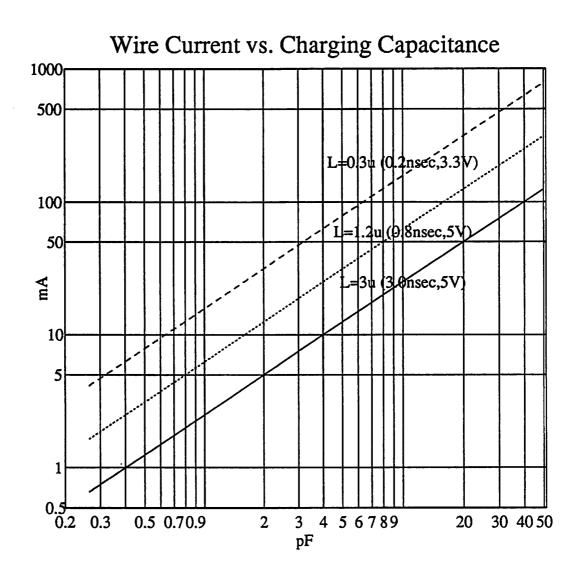

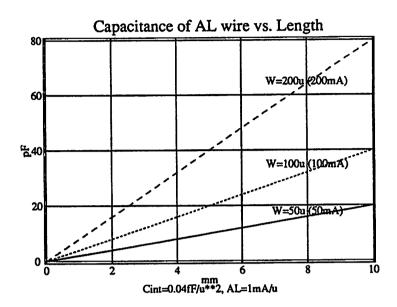

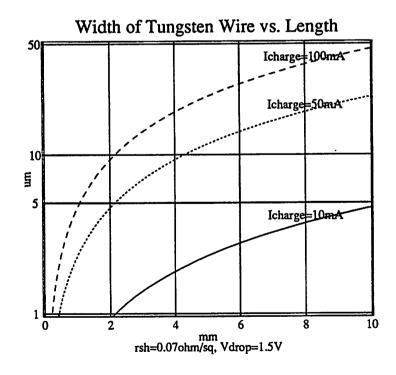

| 2.4 Clock Distribution       2         3. Summary       3         3 Realization of Self-Timed Circuits       3         1. Completion Signals       3         2. DCVSL Description       3         2.1 Completion Signal Generation in DCVSL       3         2.2 Charge-Sharing       4         2.3 Design and Layout Issues       4         3. Alternatives to DCVSL       5         3.1 Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |       |                                            |     |

| 3. Summary       3.         3. Realization of Self-Timed Circuits       3.         1. Completion Signals       3.         2. DCVSL Description       3.         2.1 Completion Signal Generation in DCVSL       3.         2.2 Charge-Sharing       4         2.3 Design and Layout Issues       4         3. Alternatives to DCVSL       5         3.1 Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |       |                                            |     |

| 1. Completion Signals       3.         2. DCVSL Description       3.         2.1 Completion Signal Generation in DCVSL       3.         2.2 Charge-Sharing       4.         2.3 Design and Layout Issues       4.         3. Alternatives to DCVSL       5.         3.1 Sample-Set Differential Logic (SSDL)       5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 3.    |                                            |     |

| 1. Completion Signals       3.         2. DCVSL Description       3.         2.1 Completion Signal Generation in DCVSL       3.         2.2 Charge-Sharing       4.         2.3 Design and Layout Issues       4.         3. Alternatives to DCVSL       5.         3.1 Sample-Set Differential Logic (SSDL)       5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3   | Rea   | lization of Self-Timed Circuits            | 35  |

| 2. DCVSL Description       3         2.1 Completion Signal Generation in DCVSL       3         2.2 Charge-Sharing       4         2.3 Design and Layout Issues       4         3. Alternatives to DCVSL       5         3.1 Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •   |       |                                            | 35  |

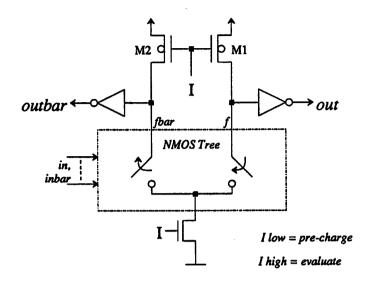

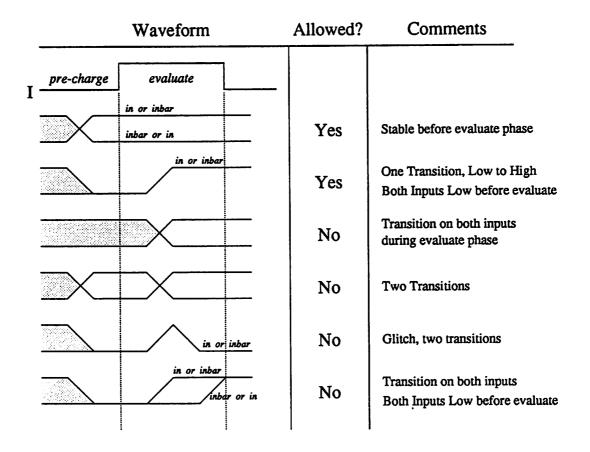

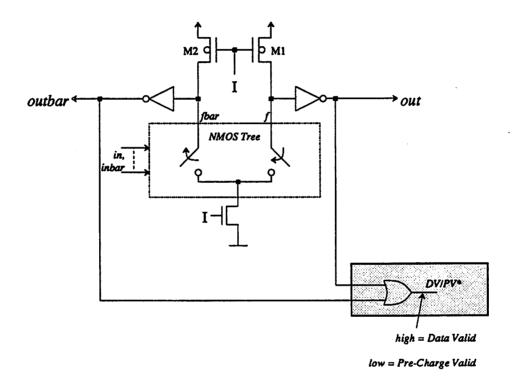

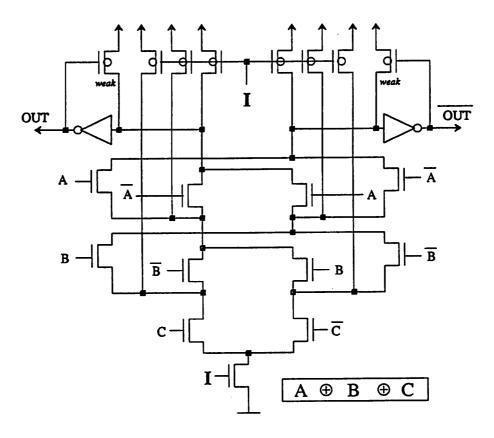

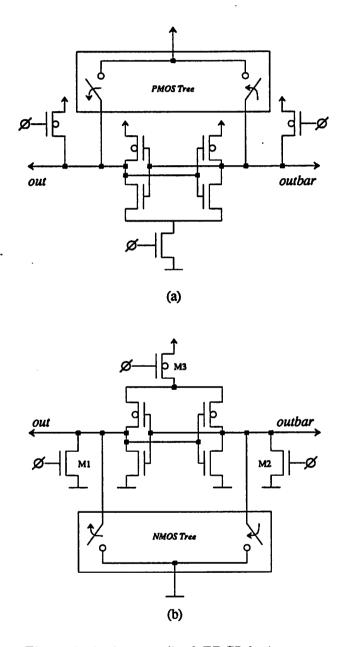

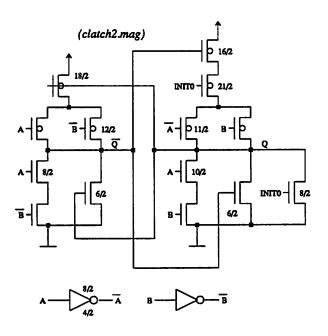

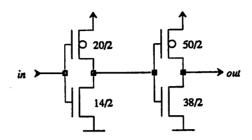

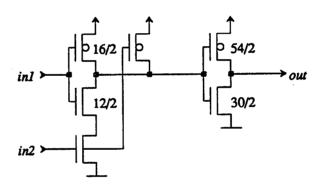

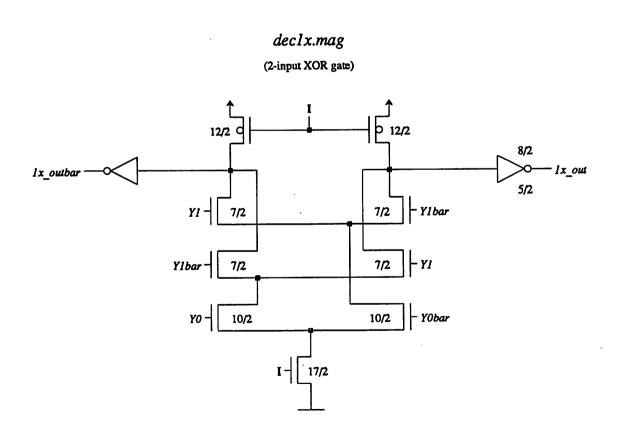

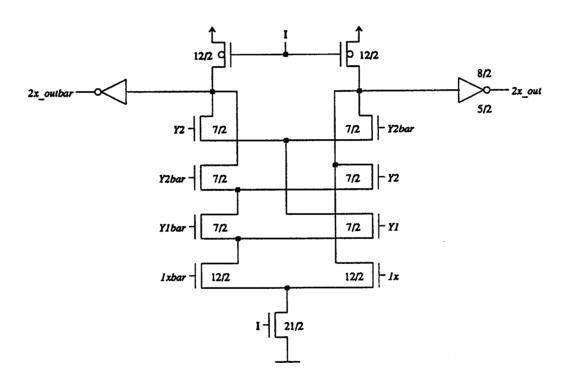

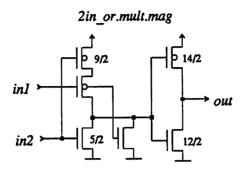

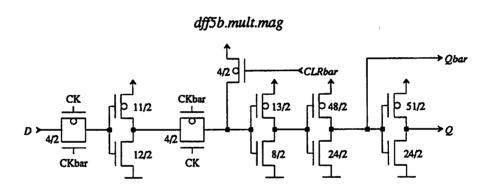

| 2.1       Completion Signal Generation in DCVSL       33         2.2       Charge-Sharing       4         2.3       Design and Layout Issues       4         3.       Alternatives to DCVSL       5         3.1       Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |       | DCVSI Description                          | 36  |

| 2.2       Charge-Sharing       4         2.3       Design and Layout Issues       4         3.       Alternatives to DCVSL       5         3.1       Sample-Set Differential Logic (SSDL)       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | ۷.    | 2.1 Completion Signal Constation in DCVSI. | 38  |

| 2.3 Design and Layout Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |       | 2.1 Chargo Sharing                         | 41  |

| 3. Alternatives to DCVSL 5 3.1 Sample-Set Differential Logic (SSDL) 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |       | 2.2 Design and Layout Issues               | 44  |

| 3.1 Sample-Set Differential Logic (SSDL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 2     |                                            |     |

| 3.1 Sample-Set Differential Logic (SSDL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | J.    | 2.1 Sample Set Differential Logic (SSDI)   | 57  |

| 3.2 Enabled/disabled CMOS Differential Logic (EDCL) 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |       |                                            | 51  |

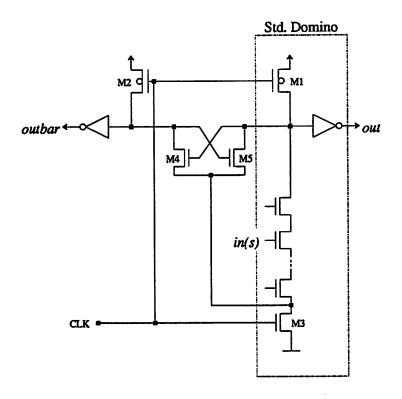

| 3.3 Latched Domino CMOS Logic (Ldomino) 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |       | 2.2 Intehed Domino CMOS Logic (I domino)   |     |

| 4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 1     |                                            |     |

| 4 | Han        | dshaking Circuit Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 65  |

|---|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

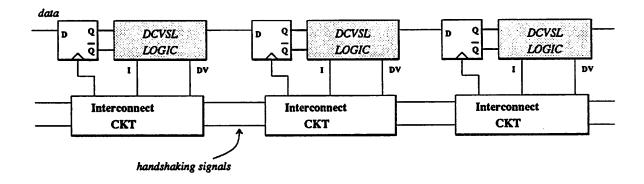

|   | 1.         | Partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66  |

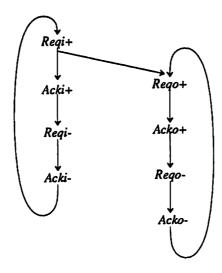

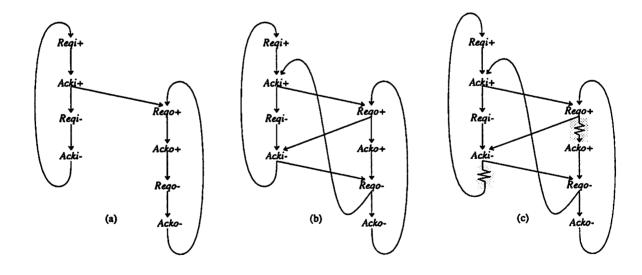

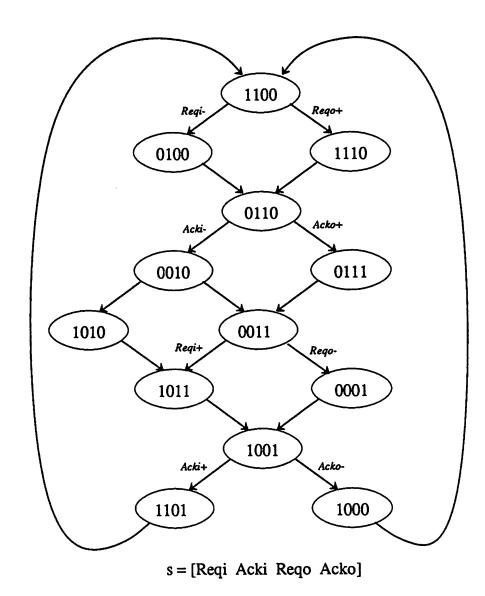

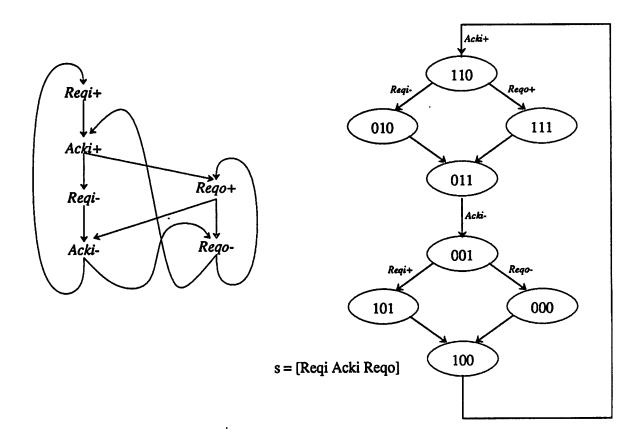

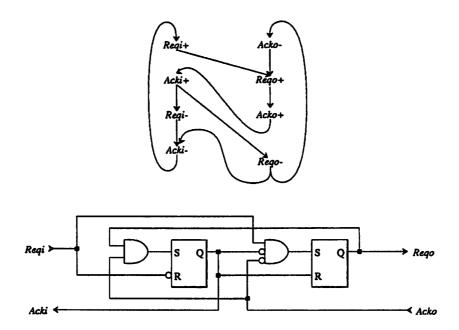

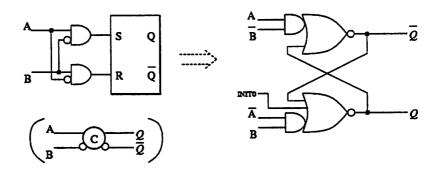

|   | 2.         | STG's for Describing Sequential Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67  |

|   |            | 2.1 Synthesis using STGs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69  |

|   |            | 2.2 4-cycle protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71  |

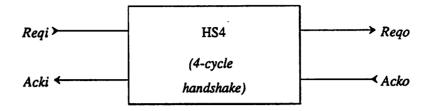

|   | 3.         | 4-cycle Handshake Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 72  |

|   | <b>J</b> . | 3.1 Other HS4 circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|   |            | 3.2 Assumptions on Delay Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

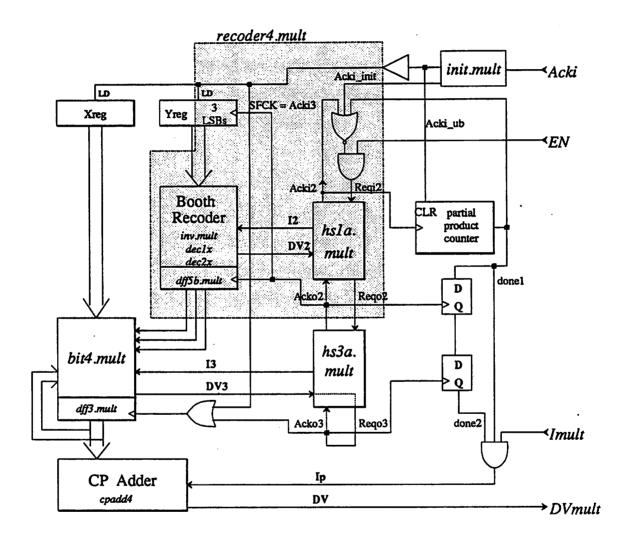

|   | 4          | Higher level description for synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|   | 4.         | Other Common Handshake Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|   | 5.         | Other Common nandshake Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

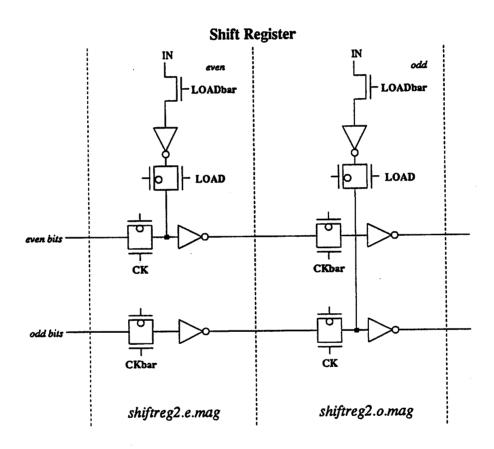

|   |            | 5.1 Sequential HS circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00  |

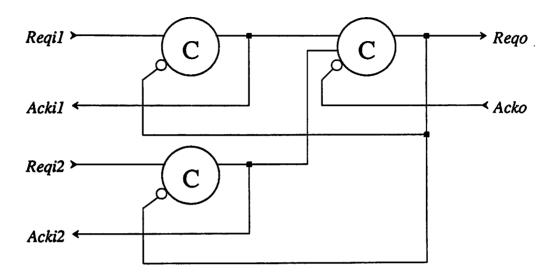

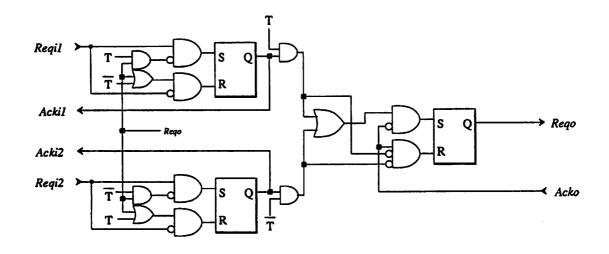

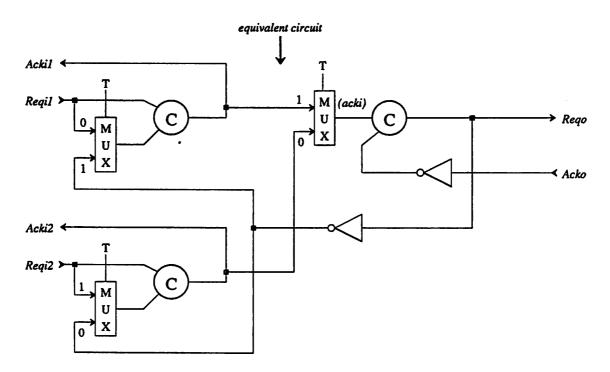

|   |            | 5.2 2-Source, 1-destination HS circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 96  |

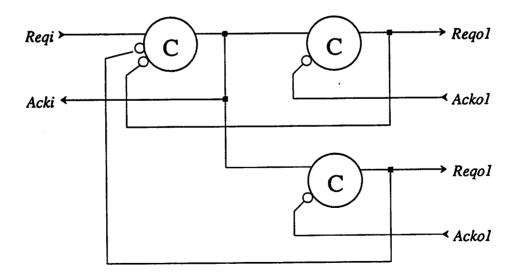

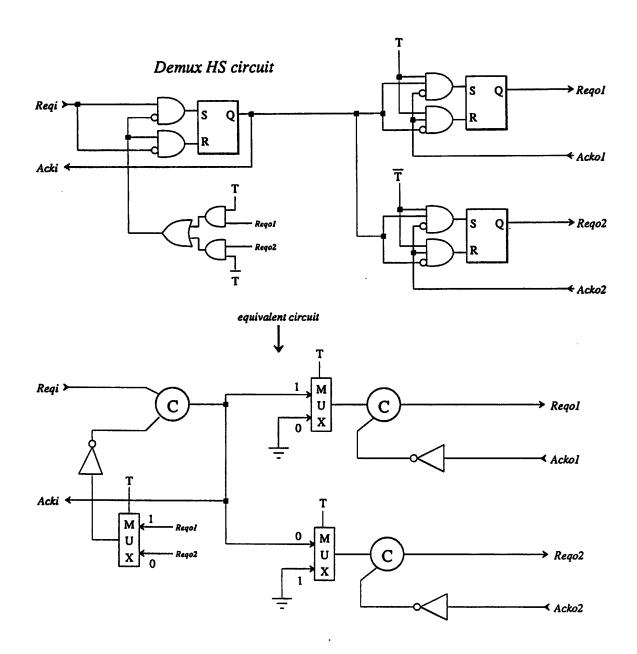

|   |            | 5.3 1-Source, 2-destinations HS circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00  |

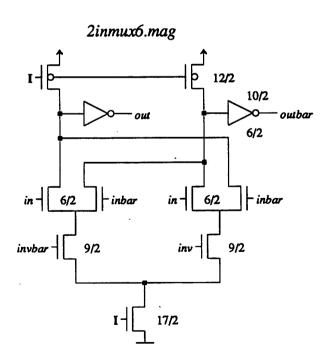

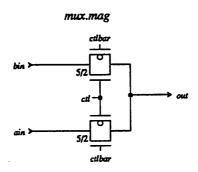

|   |            | 5.4 2-in Multiplexer HS circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00  |

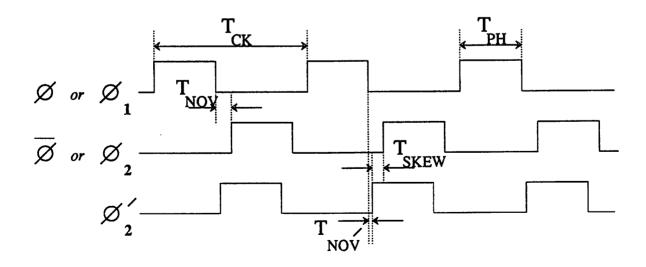

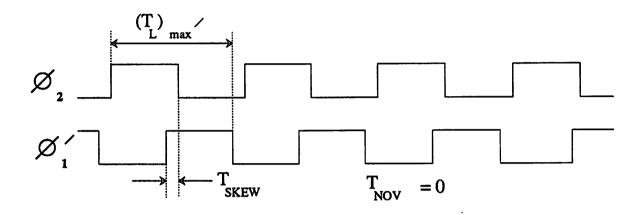

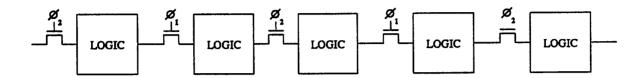

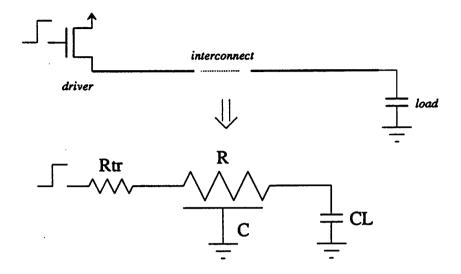

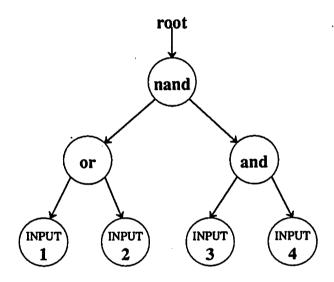

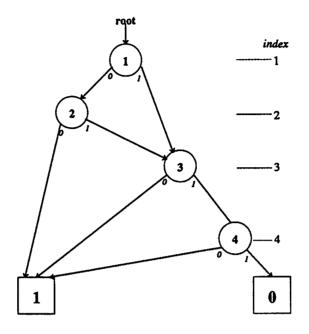

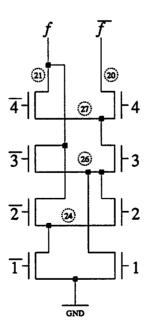

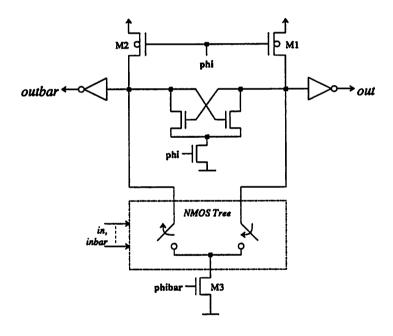

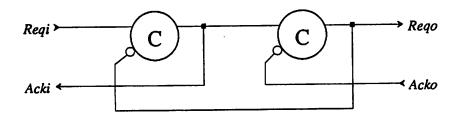

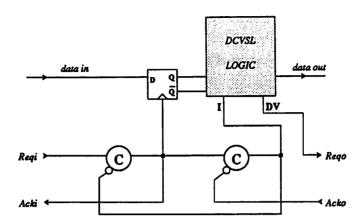

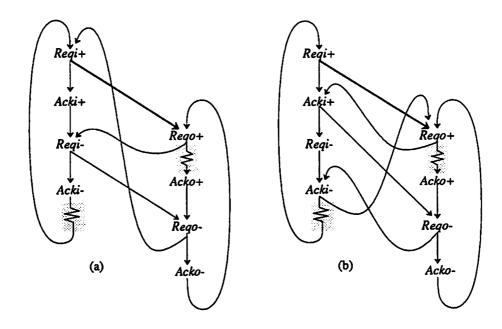

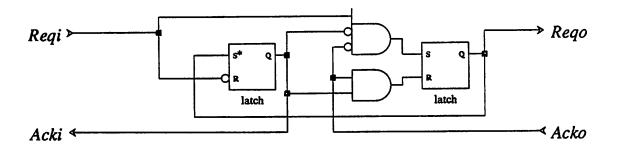

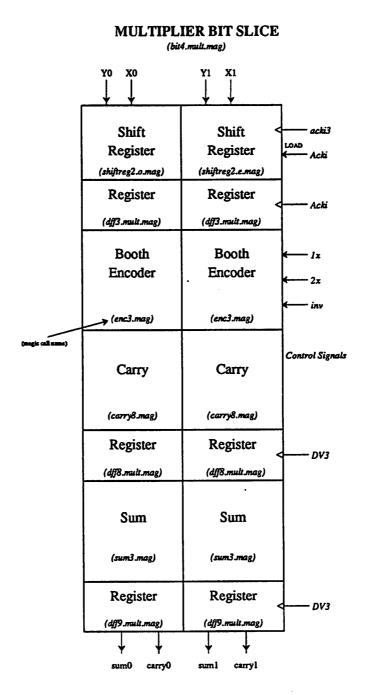

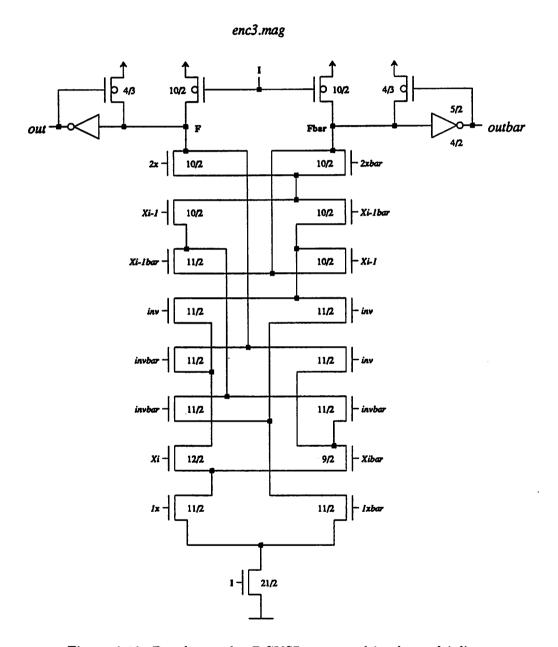

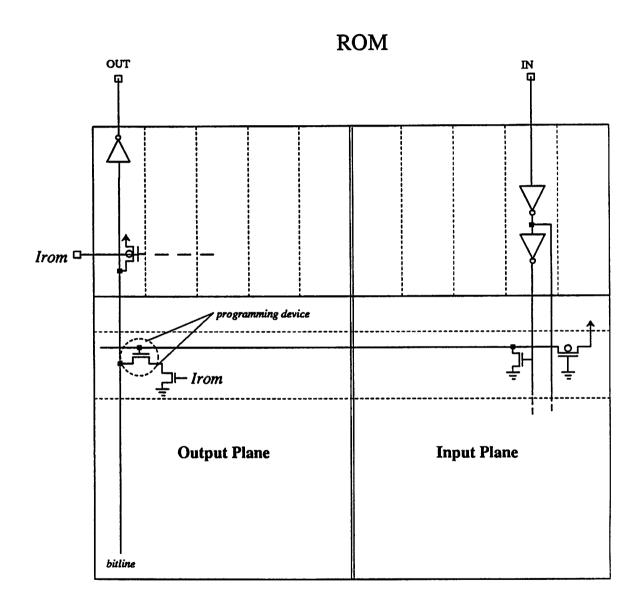

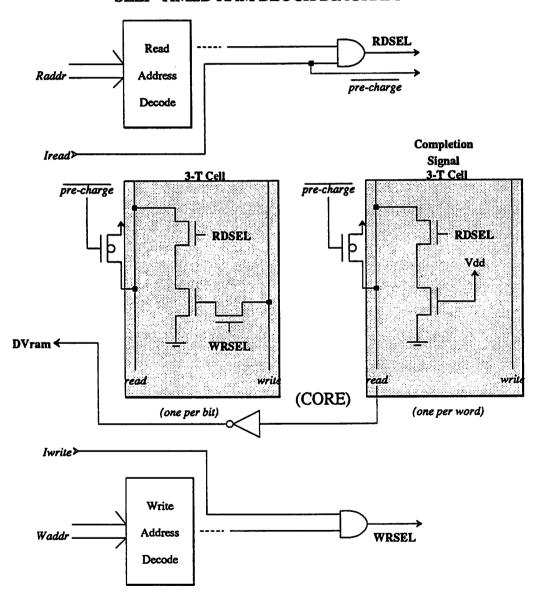

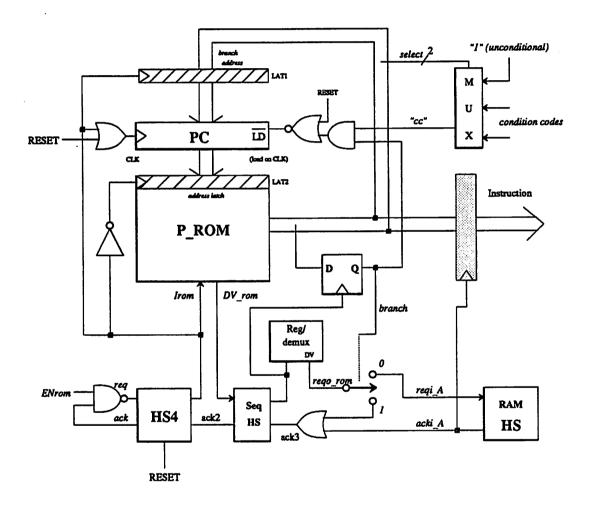

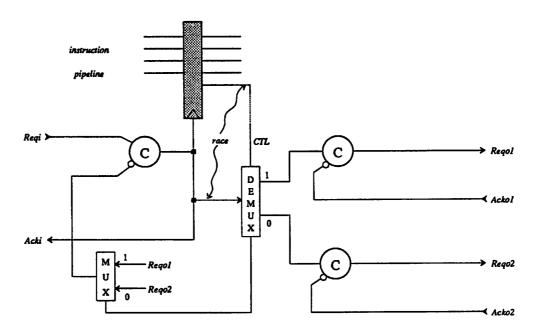

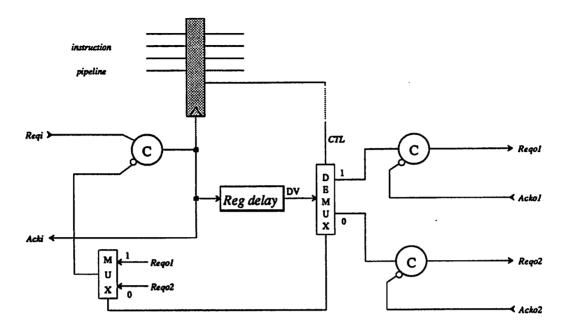

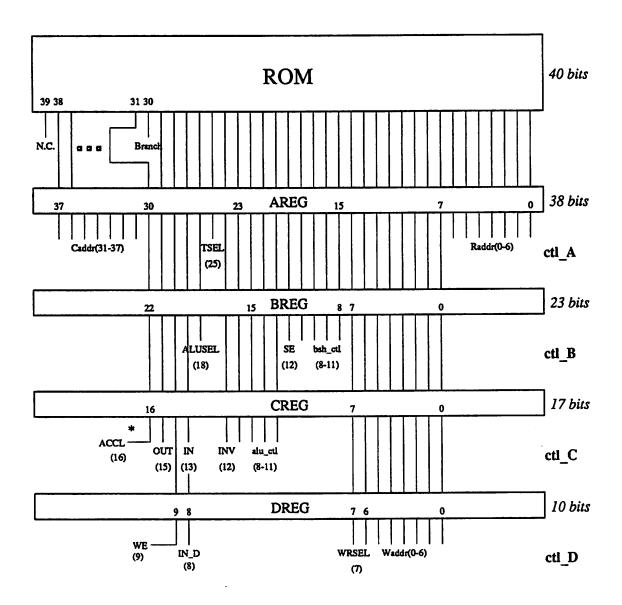

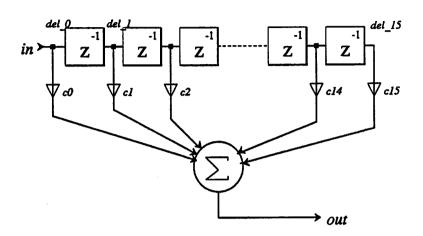

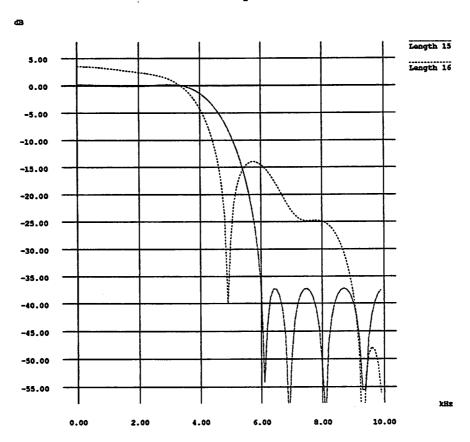

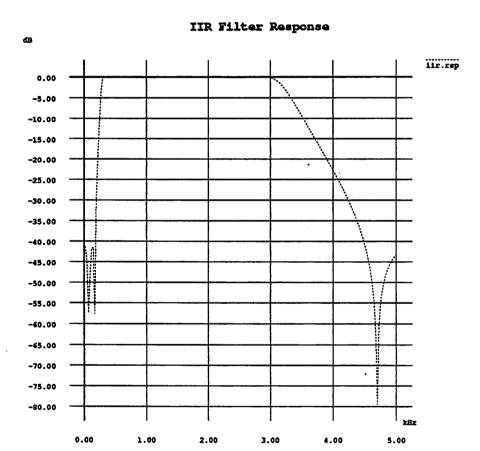

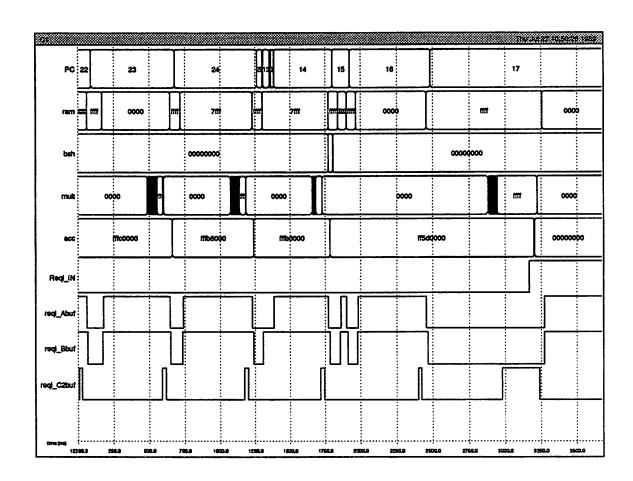

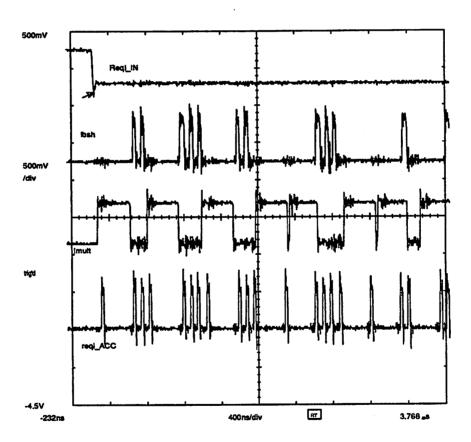

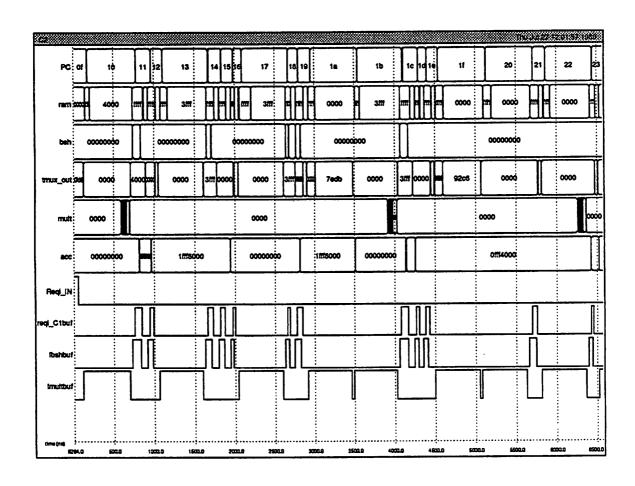

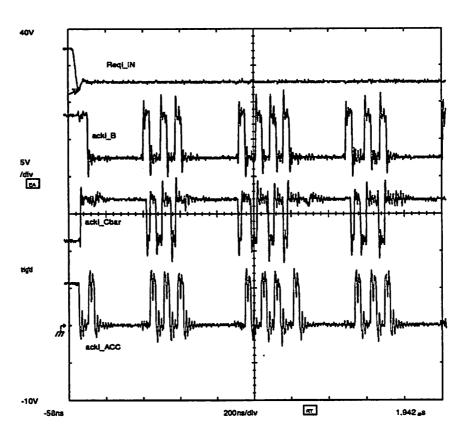

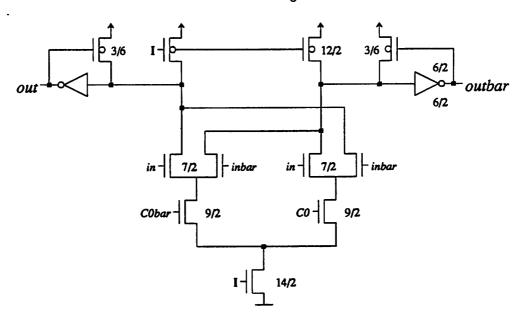

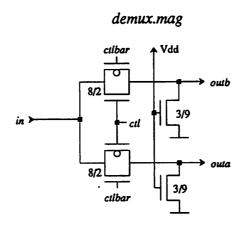

|   | _          | 5.5 2-out Demultiplexer HS circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 91  |