# Copyright © 1989, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# THE APPLICATION OF KNOWLEDGE-BASED SYSTEMS TO DESIGN VERIFICATION

Copyright © 1989

by

Ricky Lee Spickelmier

Memorandum No. UCB/ERL M89/126

29 November 1989

# THE APPLICATION OF KNOWLEDGE-BASED SYSTEMS TO DESIGN VERIFICATION

Copyright © 1989

by

Ricky Lee Spickelmier

Memorandum No. UCB/ERL M89/126

29 November 1989

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# THE APPLICATION OF KNOWLEDGE-BASED SYSTEMS TO DESIGN VERIFICATION

Copyright © 1989

by

Ricky Lee Spickelmier

Memorandum No. UCB/ERL M89/126

29 November 1989

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### The Application of Knowledge-Based Systems to Design Verification

#### Ricky Lee Spickelmier

University of California Berkeley, California Department of Electrical Engineering and Computer Science

#### **Abstract**

As a circuit design proceeds, it is continually checked by the designer for errors, by visual inspection, by simulation, or by using other verification tools (such as electrical rule checkers). Before most designs can proceed to fabrication, they must go through a formal design review where other designers analyze the design and look for errors. Errors found during the verification process range from easily recognizable problems, such as a power supply short, to a CMOS static gate having N and P cores that are not logical duals, to hard-to-recognize problems, such as those dealing with charge sharing and race-conditions.

A circuit critic is a tool that finds errors in a circuit design and may recommend corrections. There are three main uses of a circuit critic: finding errors not easily found by other verification tools (e.g. timing, charge sharing), finding errors for novices, and checking design style compliance. There are many errors that novice designers can make as they do circuit designs. Novices learn the circuit configurations that lead to these errors by experience. A circuit critic can have the patterns that describe these errors in it and the novice can use the critic to check the circuit. Many design styles have a set of rules, that if followed will produce a "correct" design. A circuit critic can check for compliance with these rules.

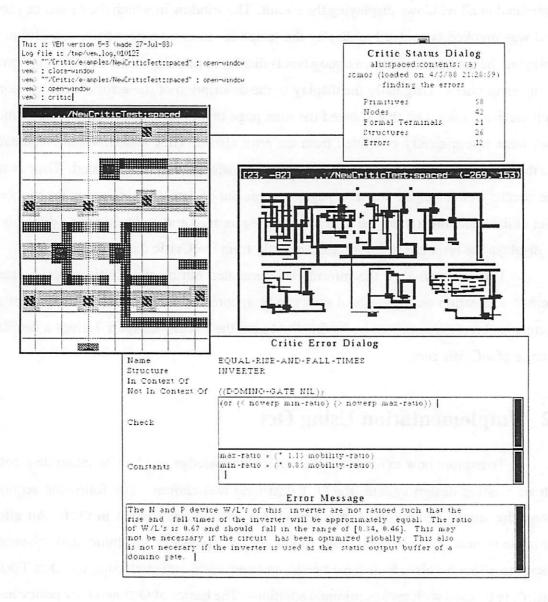

The work presented in this dissertation focuses on exploring the ideas of technology independence of critics, tight integration with a CAD system, and the representation of knowledge for the critic. To explore these ideas a test-bed, called **Critic**, was developed. **Critic** reads a description of the technology and design style to be used in the check and is tightly integrated into the Berkeley Design Environment, both in terms of the data input to the system and the control of **Critic**. An example of the use of **Critic** and the results of using **Critic** are presented.

Professor A. Richard Newton Thesis Committee Chairman

## **Contents**

| Table of Contents |                        |                                    |     |  |  |

|-------------------|------------------------|------------------------------------|-----|--|--|

| 1                 | Intr                   | oduction                           | 1   |  |  |

| 2                 | Ove                    | rview and Previous Work            | 6   |  |  |

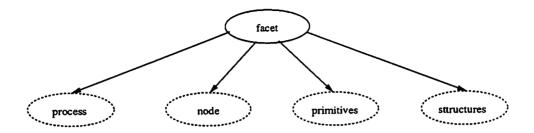

| 3                 | Primitives             |                                    |     |  |  |

|                   | 3.1                    | Overview                           | 21  |  |  |

|                   | 3.2                    | Representation                     | 21  |  |  |

|                   | 3.3                    | Built-in Primitives                | 30  |  |  |

| 4                 | Structures             |                                    |     |  |  |

|                   | 4.1                    | Overview                           | 33  |  |  |

|                   | 4.2                    | Representation                     | 34  |  |  |

|                   | 4.3                    | Finding Structures                 | 38  |  |  |

|                   | 4.4                    | Displaying Structures              | 64  |  |  |

| 5                 | Errors                 |                                    |     |  |  |

|                   | 5.1                    | Overview                           | 65  |  |  |

|                   | 5.2                    | Representation                     | 65  |  |  |

|                   | 5.3                    | Finding Errors                     | 75  |  |  |

|                   | 5.4                    | Displaying Errors                  | 76  |  |  |

| 6                 | Critic 7               |                                    |     |  |  |

|                   | 6.1                    | Overview                           | 79  |  |  |

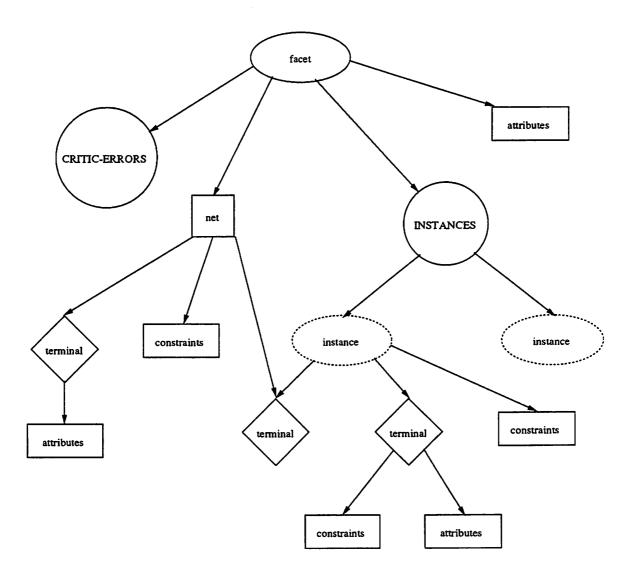

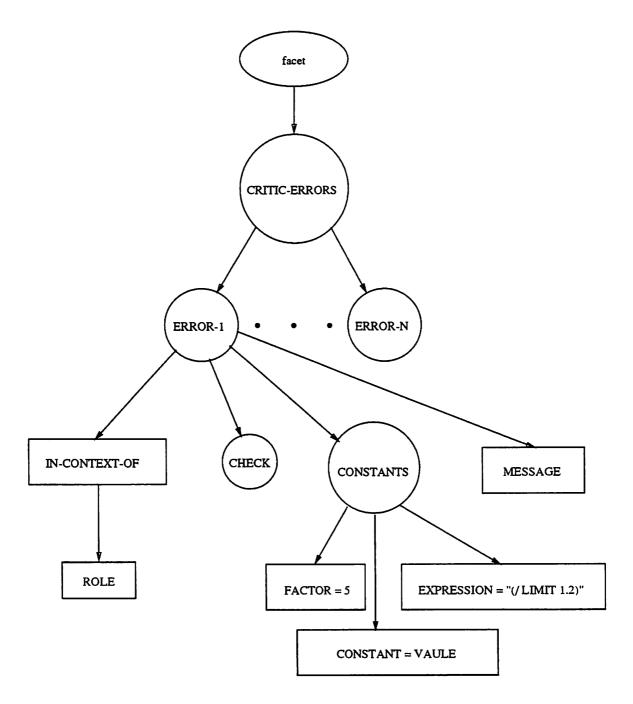

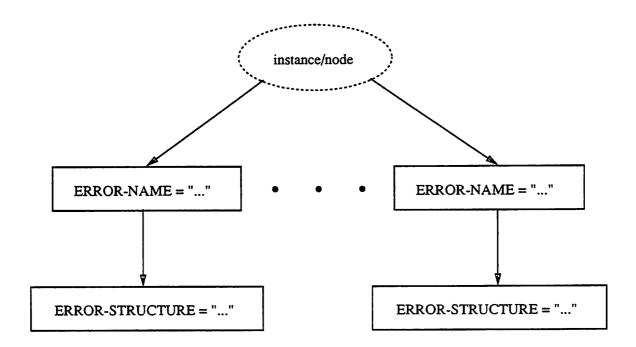

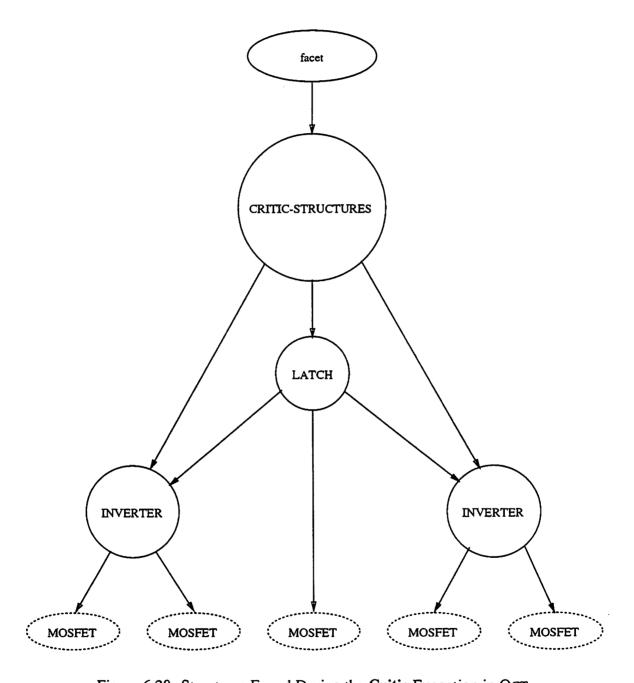

|                   | 6.2                    | Implementation Using Oct           | 97  |  |  |

|                   | 6.3                    | Browsing the Critic Knowledge Base | 108 |  |  |

|                   | 6.4                    | Knowledge Base Documentation       | 111 |  |  |

| 7                 | Example and Results 11 |                                    |     |  |  |

|                   | 7.1                    | Example Critic Run                 | 112 |  |  |

|                   | 7.2                    | Statistics                         | 116 |  |  |

|     | 7.3           | Knowledge Collection | 117 |

|-----|---------------|----------------------|-----|

| 8   | B Conclusions |                      | 118 |

| A   | Rule          | set Documentation    | 124 |

| Bil | Bibliography  |                      |     |

## Acknowledgements

First, I would like to thank my research advisor, Professor Richard Newton, for his direction, support, and employment throughout my long stay at Berkeley.

I would like to thank the past and present members of the Berkeley CAD group for making my long stay at Berkeley a pleasant experience, in particular, my friends: Wendell Baker, Giles Billingsley, Jeff Burns, Professor Ron Gyurcsik (and Peggy), David Harrison, Mark Hofmann, Tom Laidig, Brian Lee, Grace Mah, Karti Mayaram, Peter Moore, Tom Quarles, Fabio Romeo, Richard Rudell, Professor Res Saleh, and Ellen Sentovich.

I would like to thank my friends at Tektronix for putting up with me over many summers, especially Randy Young, Ian Getreu, and John Crawford, who continued to let me work at Tektronix for eight summers (probably four summers longer than they should have). My employment at Tektronix led directly to my desire to attend Berkeley.

I had many interesting discussions with circuit designers from industry. Of those, I would especially like to thank Karlheinz Horniger from Seimens and Pat Bosshart from Texas Instruments. I also had many helpful discussions with Professor Hugo DeMan of the Catholic University at Leuven.

Margo Seltzer helped me finish my thesis by bugging my about my progress, I am indebted to her. Cindy Mason has been a good friend over the entire Ph.D process, I can't thank her enough for her encouragement. I wish her the best of luck in finishing her thesis.

I would like to thank my friends in the Experimental Computing Facility at Berkeley for providing me with a place to relax and for bugging me to finish during the last few months of thesis writing. I would especially like to thank Mark Hastings, Anne Hendry, Phil Lapsley, Jonathan Lee, and Kurt Pires. It would have been difficult to finish without

their help.

The following people provided much needed editorial comments on drafts of my thesis: Paul Cohen, Professor Ron Gyurcsik, David Harrison, Theologos Kelessoglou, Professor Don Pederson, Professor Peter Pirolli, and Pete Simanyi.

The financial and equipment support provided by the Semiconductor Research Corporation, the Digital Equipment Corporation, Tektronix, Texas Instruments, and the XEROX Corporation (University Grant Program) is greatfully acknowledged.

Finally, I would like to thank myself for finishing. It took far longer than it should of, but now it's done!

## Chapter 1

## Introduction

As a circuit design proceeds, it is continually checked by the designer for errors either by visual inspection, by simulation, or by using other verification tools. Errors found during the verification process range from easily recognizable problems, such as a power supply short or a CMOS static gate having N-type and P-type cores that are not logical duals, to hard-to-recognize problems such as those dealing with charge sharing and race conditions. As circuits get larger and more complex, more errors and more types of errors are found. The size and complexity of current circuit designs take them far beyond the realm of manual verification. To simplify the problems inherent in large and complex designs, tools have been created to automate the verification process. Another way to deal with the complexity is to introduce design styles. Design styles consist a set of rules for circuit construction that if followed will eliminate certain classes of errors[24, 40]. Simple design styles can be composed of a small set of rules, such as limiting the number of series connected MOSFETs in a CMOS static-gate. Other more complex design styles exist. One such design style is used for NORA logic[24]. NORA is a design style for dynamic CMOS with complementary clocks of arbitrary skew. There are nine rules that must be followed when designing NORA circuits. By following these rules, no race conditions (because of clock skew) can exist in the circuit. Thus by following a set of rules, many problems associated with dynamic design can be eliminated. However, the rules further complicate the design process, and tools have been developed to check for compliance with the design style rules.

#### **Circuit Critics**

Many types of CAD tools can show errors, but not look for errors. For example, simulation results can show that a circuit is functioning incorrectly, but the designer then must choose what test vectors to give to the circuit and what nodes to plot to track down the error. A circuit critic looks for errors or "bad design style" in circuit designs[47, 48, 15, 14, 3, 68, 35] and may, in fact, suggest an approach to correction of the errors. There is a large amount of knowledge about how circuits should be properly designed and what might cause problems. Circuit critics are tools that use this knowledge to critique a circuit design. There are three main uses of a circuit critic: finding errors not easily found by other verification tools, finding errors commonly overlooked by novices, and checking design style compliance.

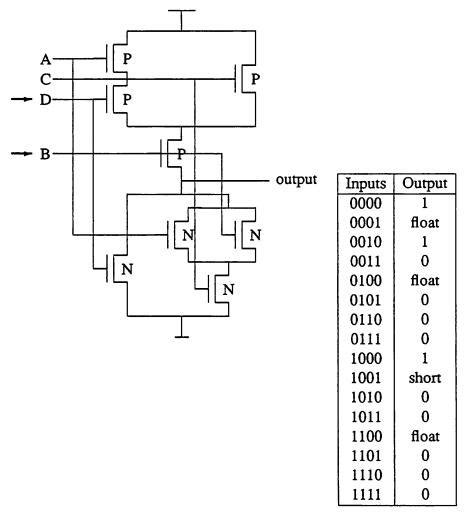

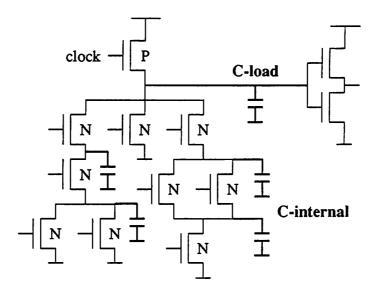

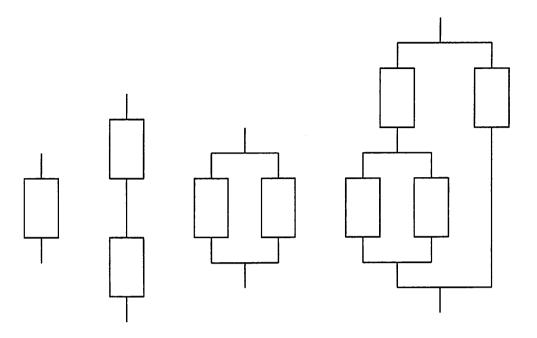

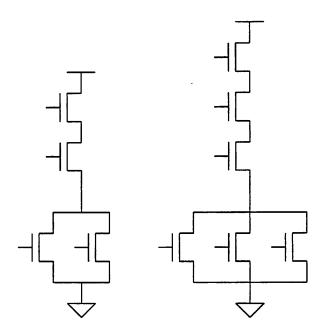

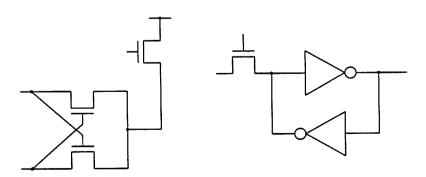

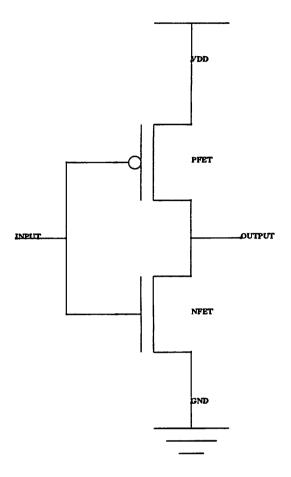

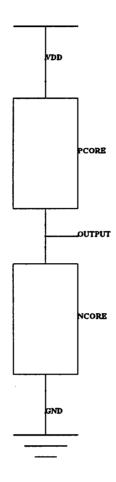

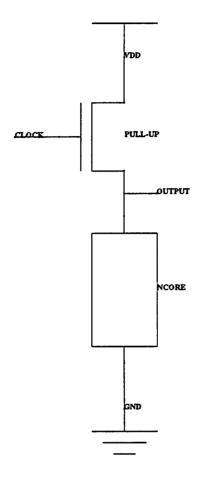

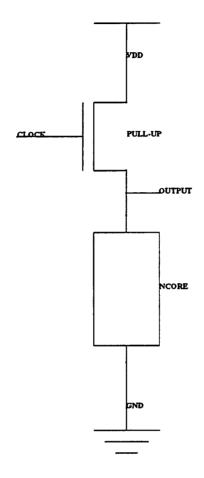

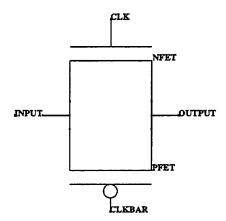

Many errors are easily handled by circuit critics but can be difficult to find using other verification techniques. For example, if the inputs to the P-type and N-type cores of a CMOS static-gate are connected incorrectly, the supplies may be shorted or the output node of the gate may float (see Figure 1.1). Unless the designer happened to test the circuit with the proper set of test vectors such that the inputs to the gate (possibly many levels into the circuit) caused the error, the error would not be found. As another example, if the internal capacitance of a dynamic gate is too large compared to the load capacitance, the load capacitance may not be charged to the full value and thus may not turn on the load devices (see Figure 1.2). While this error can be found using simulation, it is rare that all outputs of dynamic-gates would be plotted in a simulation run, and thus the error would have to be tracked down based on some error detected on the nodes plotted.

Novices learn how to design circuits by experience. Along the way they create designs with errors that an experienced designer would not make. The description of these errors are be given to a circuit critic, and a novice uses the critic to not only find errors, but to help in the learning process.

Another use of circuit critics is in enforcing design style compliance. Many design groups have a set of rules for design that if followed will eliminate certain classes of errors. A circuit critic can use the rules to verify that a circuit complies with the design style [15, 14].

Figure 1.1: Incorrectly Connected Gate

Figure 1.2: Possible Charge Sharing Problem

### Scope

The work in this dissertation explores data representations for circuit critiquing programs that are technology and design style independent. and the tight integration of these programs into CAD systems. The work in representation covers methods for representing the knowledge used by circuit critiquers to find errors in a circuit and methods for representing the circuits. Representation of knowledge explores how process, design style, and technology specific information can be represented along with how to represent the rules used for finding errors in the circuit. Both external representations (what the user sees and creates) and internal representations (what the algorithms of the critiquer work on) are presented. The use of existing forms of representation, in particular, text-based formats and circuit design databases, along with generalizing descriptions from examples is explored. The purpose of technology and design style independence is to reduce the work needed to check a circuit designed in a new technology and design style. The work in integration partially overlaps the area of representation since the facilities provided by the CAD system affect how to represent data. The integration work covers the use of the facilities provided by a CAD system to control the execution of the critic and how the results of the critic execution can be presented.

#### **Outline of the Dissertation**

The remainder of this dissertation is composed of eight chapters and one appendix. In Chapter 2 an overview of circuit critiquing and background on previous work is given. The representation of primitive circuit elements in explored in Chapter 3. How collections of primitive circuit elements are represented and searched for in a circuit design is presented in Chapter 4. The representation of error checks and how errors are located in a circuit design is explored in Chapter 5. Critic, a test bed for the ideas presented in the previous chapters, is described in Chapter 6. An example of the use of Critic and results for the use of Critic, using a CMOS technology description, in a VLSI design course are are given in Chapter 7. Conclusions and directions for future research are presented in Chapter 8. The appendix contains an example of automatically generated ruleset documentation.

## Chapter 2

## **Overview and Previous Work**

In this chapter an overview of circuit critiquing and a summary of previous work in the area of circuit critics is presented. The chapter is divided into three sections: an overview of critiquing, a description of the basic flow of critics, and a description of the previous work in circuit critics.

#### Overview

Verification and analysis tools have been used to automate the task of searching for and finding many types of errors. However, many of these tools tend to miss the class of errors that can be attributed to 'experience'. The errors in this class are encountered as designers learn their craft. The designers remember the reasons why these errors occurred and make sure they do not introduce them again (either by never introducing them or by looking at their design at various stages to see if they have introduced these errors). These errors are generally referred to as *rules of thumb*. While most of these errors have good theoretical foundation for why they occur, they are usually thought of as something not to do, without much thought as too why they are bad. As examples of errors that fit this classification: don't put more than N mosfets in series in a CMOS static gate, don't put more than M pass gates in series without intervening level-restoring logic, and do not use this two-phase gate if the clocks overlap by more than X nanoseconds. The problem with these types of errors is that they are rarely written down and thus new designers must rediscover

them, either by peer review or by discovering the error and the cause in their design (by the use of verification and analysis tools).

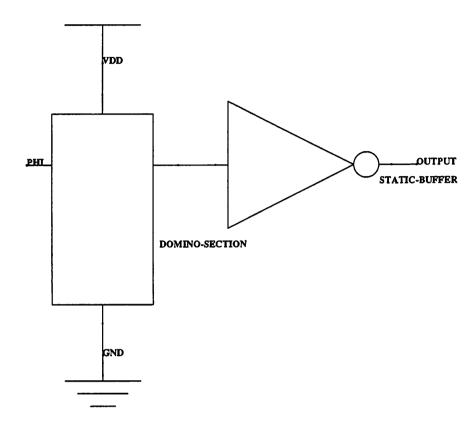

One method of reducing the complexity of design to manageable levels is to develop design styles<sup>1</sup>. Design styles are a set of rules for circuit construction that if followed will eliminate certain classes of errors, such as DOMINO[40] and NORA[24] for dynamic CMOS logic. Design styles can be composed of a small set of simple rules, such as limiting the number of series connected MOSFETs in the N-type core of a CMOS static-gate. Most companies have design styles that place restrictions on designs, e.g. only a finite number of transistor sizes allowed, certain circuit configurations not allowed (various XOR's and LATCHes fall into this category). Other more complex design styles exist.

One such design style is used in NORA logic [24]. NORA is a design style for dynamic CMOS with complementary clocks of arbitrary skew. There are nine rules that must be followed when designing NORA circuits. By following these rules, no race conditions because of clock skew can exist in the circuit. The following are two example rules:

- If the number of static inversions between two dynamic blocks is even, the two dynamic blocks must be complementary. This implies that alternating N and P blocks must be used for direct connections between dynamic blocks.

- If the number of static inversions between two dynamic blocks is odd, the two dynamic blocks must be of the same type.

Other design styles insure that a circuit can be tested[17, 41]. Level-sensitive design[17] is a such a design style. Circuit critics can verify compliance with a particular design style. This type of analysis is called *verification*.

#### **Basic Flow**

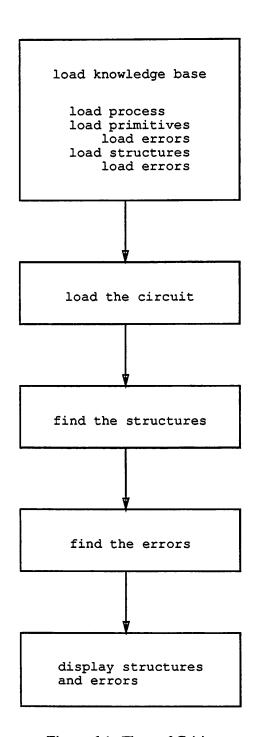

The flow of a circuit critic can be broken into a several phases, some of which are optional. These phases are:

1. Loading of the description of the technology and design style.

<sup>&</sup>lt;sup>1</sup>Design styles are also known as design methodologies or structured design.

- 2. Loading of a description of the circuit to be checked.

- 3. Extracting the structure.

- 4. Locating the errors.

- 5. Presentation of the results.

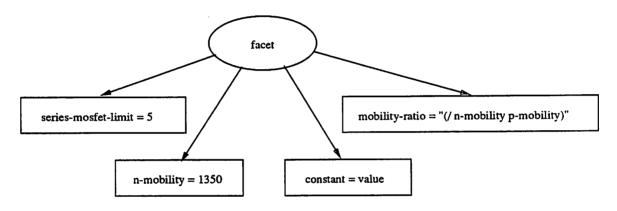

#### Loading the Description of the Technology and Design Style

In this phase of the flow, a description of the technology and the design style is loaded into the program, either explicitly or implicitly. An implicit loading means that the knowledge is an integral part of the program. The description includes information about the primitives of the technology, the structures can that can be composed out of the primitives, and the possible errors that might occur when designing using the design style. In addition, to simplify the structure and error descriptions, common constants and subexpressions are separated out. These constants and expressions are usually directly related to the process and design style being checked, such as the threshold voltage of MOSFETs, the maximum number of series connected MOSFETs that is allowed for the design style, or the maximum allowed clock skew.

While this information is needed for a circuit critic, some circuit critics are have this information hardwired for a particular technology and/or design style and thus skip this phase. In these critics the information is implicit in the program. When the description is implicit, using the critic to check a new technology or design style could require rewriting a large portion of the program. If the description is explicitly represented, the amount of work necessary to check a new technology or design style depends on the degree of separation between the program and the description.

#### **Loading the Circuit**

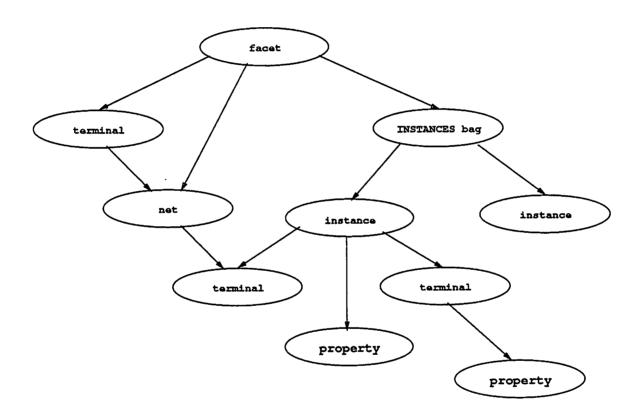

Loading the circuit entails reading in the description of the circuit from a text description or a data base, along with processing any extra annotation associated with the circuit. For most critics, the circuit description is represented as a netlist of primitives,

where a primitive can range from a single MOSFET to an entire logic block. Along with each primitive are attributes, such as the width and length of a MOSFET, that modify the default attributes of the primitive. Depending on the complexity of the design system used with the critic, the netlist can be in some standard textual format, such as SIM, SPICE[60], and EDIF[2] netlist formats, or can be retrieved from a common design database (e.g. OCT[28]).

Many design databases and some textual formats (such as EDIF) allow for the addition of arbitrary annotation. Designers of critics can develop *policies* for storing additional information in the database. These policies describe how the additional information should be stored and interpreted. This additional information can include what regions of the circuit to check, what errors to check or not check on a per element or region basis, and other forms of control. Besides directing the control of the critic, annotation can be used to give the error checks extra information. For example, one critic, QCRITIC[3], uses the results of a SPICE simulation to help in finding errors.

#### **Extracting the Structure**

The complexity of large circuit designs makes it difficult, if not impossible, to design at the level of the primitive components. Instead primitive components are grouped together into higher level components and these higher level components are grouped into higher level components, and so on. This is the basis of hierarchical design. Structure extraction is either the process of taking a collection of interconnected primitives and finding the higher level structures that were originally used in the design, or the process of finding new structures not intended or expected (such as unexpected storage elements). By extracting the structures in a design a designer can easily see if the circuit has been implemented correctly. Structure extraction is also known as *gate recognition* and *decompilation*[25, 66, 49]. Another form of structure extraction is that of extracting the symbolic representation from the layout[46].

A major use of structure extraction is to simplify the process of finding errors or verifying the correctness of a design. Most descriptions of errors in a design are not represented in terms of the low level primitives, but in terms of the structures that are composed of the primitives. Rather than have the error check specify how these structures

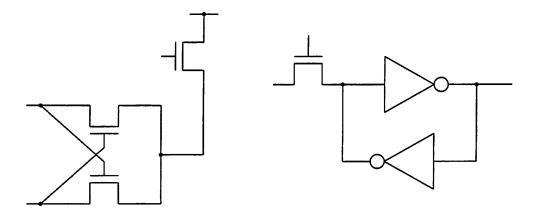

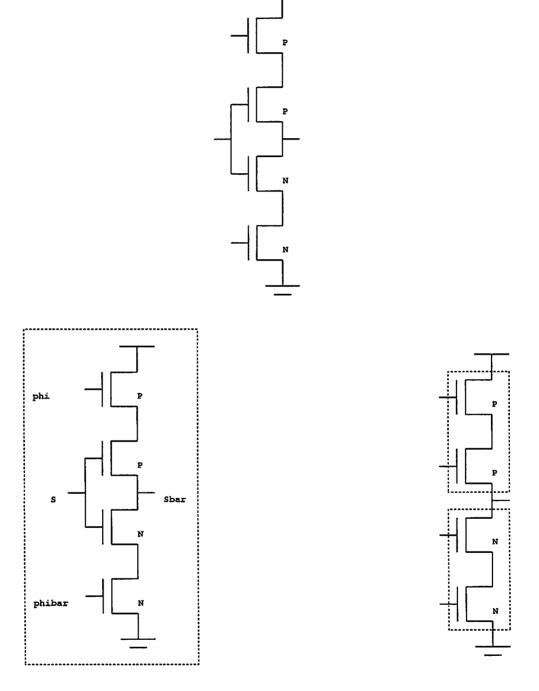

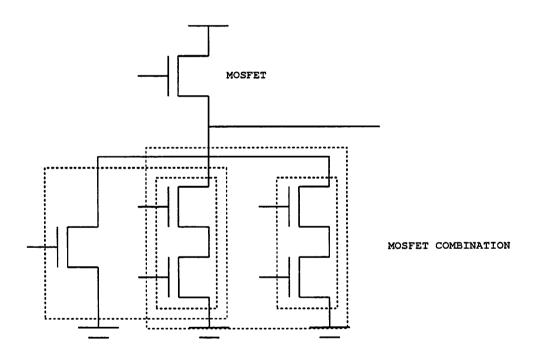

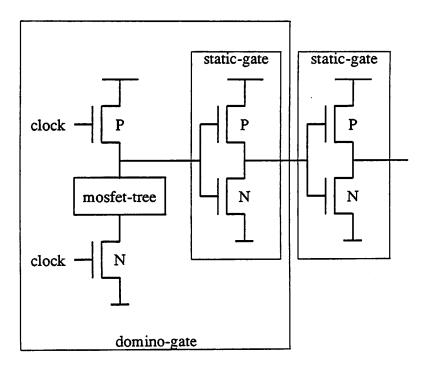

Figure 2.1: XOR and LATCH

are composed (and be responsible for finding them), a structure extraction can be performed before the error checks (or sometimes during the check), allowing the error checks to be specified more simply in terms of the structures.

#### **Finding Errors**

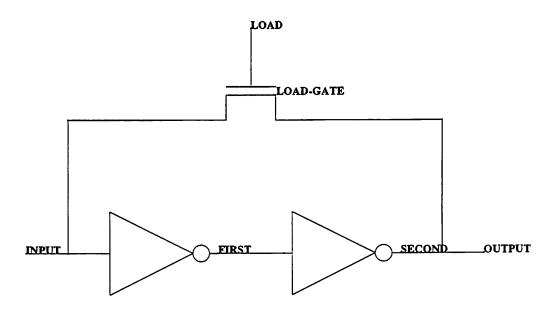

The primary purpose of circuit critics is to find errors (or verify that there are no errors) in the circuit design. There are two types of errors that can be flagged: the presence of something that should not exist or a set of attributes that violate one or more constraints. An example of the former is an illegal XOR configuration and an example of the latter is a LATCH that can not change state because of a weak load gate (see Figure 2.1).

Depending on what is allowed in error check specifications, pattern matching could be required. In RUBICC[47], the same rule language used for finding structures is used in the error check and thus the same pattern matching operations can be used (in practice the amount of actual pattern matching was limited since the structure finding phase found most of the structures of interest). Another, QCRITIC[3], has no structure finding phase so errors contain the patterns needed to find the elements needed for the error check.

#### **Presenting the Results**

After the structures and errors have been found in the circuit description they are presented to the designer for action. The information can be presented textually or

graphically. If the netlist is in the form of a textual description, the output is usually a textual description of the elements in error. If the data is stored in a common design database and there is an editor for that database, then the information can be graphically displayed (where appropriate). This can be further improved if the critic can run from the graphics editor and as errors are found the user can make modifications to the circuit to fix the error. If the critic is integrated with a common database and graphics editor, a whole range of possibilities arise for the presentation of results. The editor can be used to step through the structures and errors found in the design. The editor can highlight the objects in the structure or in error and zoom to the region. If the editor supports dialog facilities, dialog boxes of textual information can be supplied to describe the structure or error (detailed information about why the object is in error).

#### **Previous Work**

In the past few years many programs for circuit critiquing have been developed [23, 14, 47, 3, 68, 10]. Most of these have been developed to solve a particular design problem facing the organization which developed the critic. One critic[14] was designed to check compliance with a complex design style. Another was designed to check for common errors made by novices[47].

This previous work can be broken into two distinct classes: work in which developing a critic was the major focus, and work in which a critic (or multiple critics) is a part of a larger task.

#### **RUBICC - Rule Based IC Critiquer**

RUBICC[47], developed by Lob and Newton at the University of California at Berkeley, checks two-phase dynamic NMOS circuits. RUBICC is written in HPRL[43, 42, 12], which is an extension to LISP that supports frame-based knowledge and both forward and backward chaining rule systems. Although RUBICC does not have an explicit separation between the knowledge about the technology and design style being checked and the program, the technology and design style constants are broken out. RUBICC has three distinct

phases: primitive classification, structure finding, and error checking.

In the primitive classification phase, the MOSFET primitives are classified into the actual function they perform, such as pass gate, driver, and load. The classification is determined by how the primitive is connected to other devices, supplies, and clocks. The major reason for classifying primitives is to simplify the structure finders and error checks. This is analogous to the reason for having structure finding to simplify the error checks.

In the structure finding phase, complex structures are built out of the primitives and other structures in a bottom up fashion. RUBICC does not try to determine an ordering for the structure finding rules, and instead uses the order in which the rules were entered into the system.

In the error finding phase, the same pattern matching that was performed in the structure finding phase is used to find the errors. Again, the error checks are ordered, because of interaction among the rules. The existence of one error may negate the need to check for certain other types of errors. For example, the fact that the widths and lengths of a MOSFET are wildly out of range will negate most other error checks that use the MOSFET widths and lengths in their calculations.

Figure 2.2 shows a RUBICC rule for checking an error associated with a dynamically clocked gate. Each rule is composed of a single form that contains the name of the rule, the type of the rule (forwards or backwards chaining), the types of database elements to be used in the pattern matching portion of the rule, the premise (tests to be performed and patterns to match), and the conclusion (actions to be performed if the premise is true). The type form lists the types of objects to be used in the rule and the variables to be assigned to them. In the example rule, two objects, each of a different type (precharger and driver), are being used, assigned to the variables pre and dr respectively. The premise form describes a set of tests, each of which must evaluate to true. In the example rule there are two forms, one that does pattern matching and another that checks constraints. The pattern matching section can either match an item directly in the database or force a backward chaining rule to fire. The constraints section uses the variables matched in the pattern matching phase. In the example rule the conclusion section evaluates a form that creates an error frame in the database.

Note that the example rule required detailed knowledge of the syntax of the un-

Figure 2.2: Example RUBICC Rule

derlying rule system. However since many of the rules have the same basic form, previous rules can be used as templates for new rules.

#### **DIALOG**

DIALOG[15, 14], developed by DeMan, et. al. at the Catholic University at Leuven, was originally designed to check for design style violations in CMOS NORA[24, 33] circuits. DIALOG uses a special purpose language for describing the errors (LEXTOC). This language can be interpreted in LISP or translated into PASCAL and compiled. LEXTOC is used for both describing the structures to be found during the run and the errors to be checked. The language provides basic data types and constructs for describing structures and errors; where the language does not provide the necessary expressiveness, the designer can escape to LISP. The circuits are described using an *Invariant Network Representation (INR)* and LEXTOC allows the rules to transform the circuit from one form of the INR to another; which another name for structure extraction. Figure 2.3 shows an example of a DIALOG rule for finding a structure (called a *composition* rule) and Figure 2.4 shows an example of a DIALOG error check rule. In [14] the comment "Notice the simplicity of expressing knowledge in this system" is made. While LEXTOC does make it possible to describe a wide range of structures and error checks, it requires the person who creates the ruleset to learn a new language, one different from what a circuit designer is used to.

```

(RULE c2mos-definition

(IF

((PROPERTY fibar-cloctor (clocktransistor ctl))

(PROPERTY ptype ct1)

(RELATION inout n1 ct1)

(PROPERTY fi-clocktor (clocktransistor ct2))

(RELATION inout n1 ct2)

(PROPERTY ntype ct2)

(RELATION input n2 ct1)

(RELATION input n3 ct2)

(RELATION inout n4 ct1)

(RELATION inout n5 ct2)

)

THEN

((IF (COMPLEMENT (LOGFUN (gnd n5) ((ntype e)))

(LOGFUN (vdd n4) ((ptype e))))

(CLUSTER ell (n4 vdd) ((ptype e)))

(CLUSTER el2 (n5 gnd) ((ntype e))))

THEN

((MERGE varc2mos ell el2 ct1 ct2)

(ASSIGN fi-c2mos varc2mos)

(ASSOCIATE output varc2mos n1)

(CREATE (c2mos varc2mos))))))

```

Figure 2.3: Example DIALOG Structure Finding Rule

Figure 2.4: Example DIALOG Error Check Rule

If the goal is "finderror" and

the process is "Super-High Three" and

there is a PNP substrate transistor and

the voltage at the emitter is greater than or equal to

the voltage at the collector + 25

Then record an error

Figure 2.5: English Version of QCRITIC Rule

DIALOG was also extended to cover the RUBICC rules described in [47].

#### **QCRITIC - Quick CRITIC**

QCRITIC[3], developed by Bergquist and Sparkes at Tektronix, is used for checking bipolar analog circuits. QCRITIC is written in OPS83[21], an AI language that allows simple frame-based knowledge and (the description of) forward chaining rules. QCRITIC loads a set of OPS83 rules that describe the errors to check, but does not do any structure extraction. The error checks work directly at the level of primitives in the circuit (transistors, resistors, capacitors), using pattern matching to find needed collections of elements. QCRITIC uses extra circuit annotation in the form of simulation information from the SPICE[60] circuit simulator. For example, it may use the maximum voltages between nodes to determine if the breakdown voltages for devices have been exceeded (or devices have entered saturation) or use the maximum current into a terminal to see if the current is out of range.

Figure 2.5 shows a 'human-readable' example QCRITIC rule. In this rule a check is made to see if the voltage across the collector and emitter terminals is greater than the breakdown voltage. The check is composed of test and action sections. In the test section, four clauses are used. The first verifies that the current phase of the critic run is the 'finderror' (or error checking) phase. The second makes sure the process of the circuit being checked is 'Super-High Three' (the name of a bipolar process used at Tektronix). The third clause is used to find all PNP substrate transistors. The final clause checks the voltage difference between the collector and emitter of the transistor.

It is important to note (and will be discussed in more detail in the following chapters) that this check contains not only the error check to be performed, but also contextual and rule system semantic information.

#### **Design Advisor**

DESIGN ADVISOR[68] is a critic for checking logic gate and latch level designs for NCR's design system. DESIGN ADVISOR employs artificial intelligence techniques to the critiquing problem and uses the Proteus system[59] for representing knowledge and finding errors in a design. DESIGN ADVISOR uses *truth maintenance*[16] techniques to allow the system to support multiple possibilities for why an error might occur. The use of truth maintenance also permitted the retraction of faulty assumptions made during the check.

DESIGN ADVISOR uses the same input representations as other tools in the NCR tool suite and has a graphical interface to display the errors found in the circuit. The program has rules for checking testability, manufacturability, performance, and overall design quality for the NCR gate array design system.

Figure 2.6 shows an example DESIGN ADVISOR rule. This rule checks for phase skew caused by differing numbers of loads on the inverting and non-inverting outputs of a two-phase clock driver. The connection form finds a component of type 'pc12' (two-phase clock driver) and binds the name of the driver to '?pc12-name', the input to '?pc12-in', and the two outputs to '?pc12-ph1' and '?pc12-ph2'. The fanout-cnt forms return the number of connections to the clocks bindings to '?ph1-cnt' and '?ph2-cnt'. The unless form returns true if the counts are not equal; if the counts are equal, the action is evaluated. The action triggers the storage/presentation of the error.

#### **ESTA**

ESTA[10], developed by P. Camurati, et. al. at the Politecnico di Torino, is a program for verifying that circuits have been designed following the rules for Design For Testability[17, 1]. Designing a circuit for testability means adding extra circuitry (usually latches), and making connections in order to improve the ability of the circuit to be tested. ESTA is written in PROLOG[11]. As an example of testability rules:

```

((connection ?pc12-name:pc112 ?pc12-in ?pc12-ph1 ?pc12-ph2)

(fanout-cnt ?pc12-ph1 ?ph1-cnt)

(fanout-cnt ?pc12-ph2 ?ph2-cnt)

(unless (= ?ph1-cnt ?ph2-cnt))

-->

(phase-skew ?pc12-name))

```

Figure 2.6: Example DESIGN ADVISOR Rule

A latch X may gate a clock Ci to produce a gated clock Cy which drives another latch Y if, and only if, clocks Cy and Ci are not functionally dependent.

This rule may be violated if and only if:

There are two SRL's and a combinations network connected in such a way that the input clock of the second latch is fed by the output of the combinational network one of whose inputs is the output of the first latch.

This rule is coded in PROLOG for ESTA as follows:

#### **CRITTER**

Critter[35], developed by Kelly and Steinberg at Rutgers University, is a program for comparing the specification of a design with its behavior. It can symbolically

determine the outputs based on the input specification and can take an output specification and determine the inputs required. When give both the inputs and the outputs Critter can derive the outputs from the inputs and compare them with the expected outputs. Critter works on netlists of instances of *modules*. Each module is described by two parts, a set of operating conditions and a set of input/output mappings. The operating conditions are a set of constraints on the inputs that must be satisfied before the module will work. Example constraints might be the set up time for a latch or the skew of two signals. The input/output mappings describe the effect of the inputs on the outputs.

#### **Palladio**

Palladio[8, 9], developed by Brown, et. al. at XEROX PARC, is a knowledge-based VLSI design assistant. Palladio directs a designer by helping incrementally refine a design from a high level description. Each step in the refinement is directed by a design assistant that 'knows' how to correctly go from one level of abstraction to another. As the refinement continues, the system follows rules that force each step to produce a legal (correct) design. As examples, as high level blocks are chosen the system makes sure that are no clocking problems or deadlock conditions, as specific devices are chosen the system makes sure there are no charge sharing problems or illegal logic levels, and as the final geometry is generated the system verifies that everything is design rule correct. Palladio can also make sure that components are correctly connected together at the same level of abstraction. For example, here are two of the rules for composing elements at the level of clocked switches and gates (known as the CSG level in Palladio):

A control input of a steering switch or a steering net can be connected only to an output of a restoring logic gate.

An output of a clocking switch can be connected only to an input of a restoring logic gate.

Palladio is implemented in LOOPS, an exploratory programming language embedded in Interlisp[71] that supports procedural programming, access-based programming, rule-base programming, and object-oriented programming[5, 70].

#### **SCHEMA**

SCHEMA[74, 73], developed by Zippel at MIT, is an integrated system for designing circuits. It is a synthesis system with critiquing and analysis for feedback. The basic concepts of SCHEMA are: the internal semantics of the system should match the semantics of the circuit designer (allowing it to better explain what was going on), components should be specified in terms of electrical parameters rather than device sizes, and a single design repository and description language.

As part of the process, SCHEMA, had an analysis phase the would verify the correctness of the design, *i.e.* did the design meet the specified constraints, where there design errors. The critiquing phase would check for errors such as:

"Does this inverter have a trip point of 2.3 volts?"

"Does the bootstrapped node boot?"

#### **Current Work**

Current work in the area of checking circuits is heading towards formal verification. DIALOG[7] is moving from a rule-based approach to one based on a formal specification of correct digital circuits. PRIAM[50] verifies that a circuit functions according to the specifications, and tries to modify the circuit such that it meets specifications. Work is continuing in the area of extracting structure from netlists[72, 32].

#### **Problems**

There are some short comings that exist in the work on many of the previous and current circuit critics. In particular, many systems are developed for a particular technology and/or design style, the description of the circuit, primitives, structures, and errors is based on the syntax of the implementation, and can contain implementation-specific information, and the critics are not integrated into larger design systems.

Many critics are hardwired with specific knowledge of the primitives, structures, and types of errors for a particular technology or design style, for example, RUBICC can

only check two-phase dynamic digital CMOS circuits, DIALOG was developed MOS circuits, and Critter only works for digital circuits. This makes it difficult for the system to be modified to check different technologies and design styles<sup>2</sup>. Critics should be independent of the technology and design style. This allows the system to move to new technologies and design styles with minimum effort; a new set of descriptions of the primitives, structures, and errors of the technology and design style, but no changes to the system itself.

Many critics require that the circuits and knowledge about the technology and design style be described using a language that is based on the underlying implementation. Some critics also require the use of implementation-specific functions in the description of the structures and errors. This can be seen in the example structure error check descriptions given in the previous section.

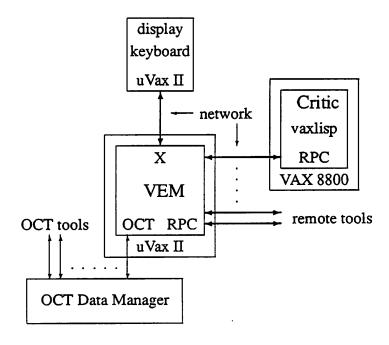

Many systems are stand-alone, they read in the circuit description, find the structures and errors, and then output their results. While they may be part of a larger set of tools for design, they are not integrated into a design system (DESIGN ADVISOR being an exception). This makes it difficult to provide such useful features as storing the results with the circuit, and displaying the structures and errors in the context of the circuit. Integration into a design system simplifies the use of the system by making the input, output, and control look the same as other parts of the system. Depending on the flexibility of the design system, the technology and design style knowledge, along with the circuit, can be described in the database of the design system, the structures and errors can be back-annotated to the database, and the display facilities used for displaying circuits can be used to display the structures and errors found during the run.

<sup>&</sup>lt;sup>2</sup>Changing to slightly different design styles within a particular technology has been accomplished[7].

## Chapter 3

### **Primitives**

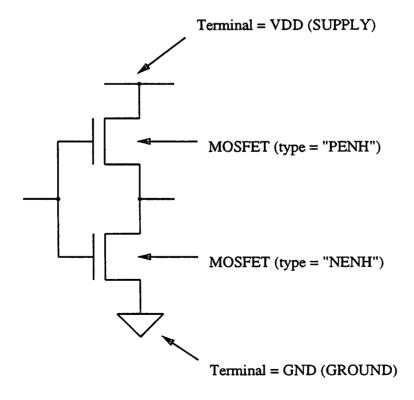

#### 3.1 Overview

To critique a circuit, the human or computer program performing the analysis must understand the primitive elements that have been used to represent the circuit. In MOS designs, these are usually MOSFETs of various types and sizes, and capacitors. In higher-level designs, these primitives can be logic gates, registers, or ALUs. To understand the primitives, the descriptions of what they look like, what attributes they might have, and how they might be used in the representation of higher-level structures must be made available. In this chapter, how primitives can be represented in a critic tool (both in terms of their definition and in terms of their representation in the circuit) and how to handle the attributes associated with primitives is presented.

#### 3.2 Representation

Before a circuit critic can process a circuit containing primitives and compositions of primitives in higher-level structures, primitives must be defined. This can either be done by hardwiring the definition into the critic, as has been the case for critics for a specific design style and technology, or the primitives can be described in such a way that new and different types of primitives can ber defined and added easily. A further refinement of the latter would have the primitive definition in a form that allows easy entry, browsing and

editing of these definitions as well.

Before exploring the forms of representations for primitives, what actually needs to be represented must first be determined. This information can then be used to guide the implementation choice.

#### Attributes

Structure finders and error checks use attribute information associated with the primitives for finding structures and errors. The attribute information can be fixed, as in the type of an item, or it can be calculated, as in the W/L of a MOSFET, the beta-ratio of a MOSFET static-gate, or the sink current for a pin. The representation must allow the specification of fixed attributes along with the specification of calculated ones. Since there are calculated attributes, the representation must also specify how to interpret the instructions for calculating the attribute.

#### **Terminals**

Information about the terminals of the primitive must be included in the representation. The information that needs to be specified is the names of the terminals, the types of the terminals (input, output, bidirectional, *etc.*), and the permutability of the terminals.

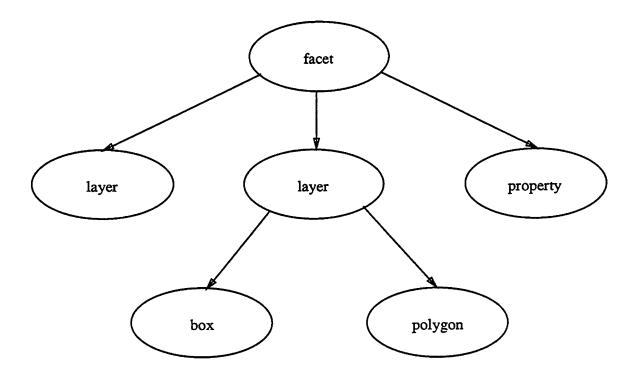

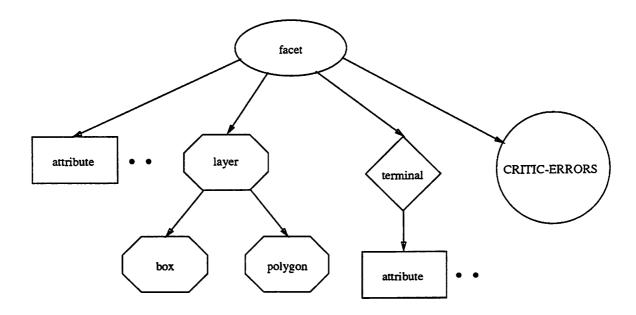

#### Retrieval from a Database

In order to process a circuit description, the description must be interpreted. Simple text-based descriptions are read from a file and parsed. Integrated CAD systems store circuits in a database and thus the representation must provide enough information for the system to read instances of the primitive from the database. This can be as simple as making one database call or making multiple calls, one for the instance of the primitive, one for each attribute, and one for each terminal.

#### Display

The representation should provide enough information to allow the CAD system to be able to display the primitive. It is important to be able to display an item in error

rather than just output the name of the item in error.

#### **Approaches**

There are two representation forms, the external form and the internal form. The external form is used by the user of the system and any tools that are not integral to the system (i.e. a browser, documentation generator). Thus the external form must be understandable, readable, and modifyable by the user. The internal form is used by the system and thus must be efficient and fit the algorithms used. For example, an external representation might have indirect pointers via names for representing connectivity (as in textual netlist formats), while a critic, which needs to be able to traverse the connectivity graph quickly, would have direct pointers between elements that are connected.

The representation must also be independent of the details of the underlying system. For example, if the underlying system is a rule-based system, none of the rule system syntax or semantics should be in the external representation. This facilitates changing the underlying system without changing the representation the user sees, and the user is not required to learn the specific syntax of the underlying system.

The definition of a primitive must contain several features, from the simple, such as the name, to the complex, such as permutability information and how to calculate attributes of the primitive. Primitives should have the following:

type: The classification of elements in the database is determined by their type.

terminals: Terminals are used to connect the element to other elements via nets. The critiquer must know what terminals exist and if they are logically or electrically equivalent.

attributes: primitives may be further classified based on what the values of their attributes are. For example, the primitive BJT may have the attribute TYPE with values NPN and PNP. The use of attributes are particularly important for use in finding higher-level structures and errors. For example, a CMOS inverter is made up of two MOSFETS, but with different attributes. Besides having simple attributes, like the TYPE example above, there can be complex attributes that can be functions of other attributes on the

primitive. The simplest example is that of the attribute for the W/L ratio of a MOSFET. This attribute is composed of two other attributes, the width of the MOSFET and the length of the MOSFET.

The description of a primitive is straightforward and can be easily described by a simple language. Often an existing language can be used, sometimes a language from the domain. Many CAD tools use the SIM[26] or SPICE[60] netlist formats to ease the creation and modification of data and to allow the data to be used by other tools. There is no such language available for describing the information necessary for the primitive. Many critics use a language from an AI system[43, 42, 12, 59, 19]. To make the system independent of the underlying system, a simple language was developed. Examples of using the language are shown below:

```

(defprimitive type

(terminals list of terminals)

(permutable list of permutable terminals)

(attributes list of attributes))

(defprimitive bipolar-transistor

(terminals emitter base collector)

(attributes area type))

(defprimitive mosfet

(terminals gate drain source)

(permutable drain source)

(attributes width length (w/l (/ width length)) type))

```

While this language is simple and provides enough expressibility for defining primitives, it does require the person installing or using the critiquing program to define the primitives and enter them into the system. Another approach is to find a representation that matches one already in use in the design system that is already used by the design groups. This allows the definition of the primitives "by example". "By example" in this case means using the description of a primitive that has already be done for other parts of the system. The best case would be using the basic leaf-cell definitions used to design circuits. These leaf-cells have information about the type of the primitive, the terminals on the primitive (and any attributes the terminals might have, such as type and direction), permutability information, and attribute information.

#### **Permutability**

Many elements have sets of terminals that are electrically or logically equivalent. These terminals are called permutable. For example, the inputs to a NAND gate are logically permutable and possibly electrically permutable if you ignore capacitance and timing concerns[61], and the *source* and *drain* of a MOSFET are electrically permutable. Choosing the best way to represent elements and terminals is important[65, 66]. This determines the number of rules in the system, the complexity of the rules, the size of the database and the overall performance of the system. There are two basic formats: one is simple and allows for easily understood rules, and the other is more complex but allows for more compact rule sets when terminal permutability is needed. The simple case, to be called the non-permutable case from now on, represents each terminal on an element as an attribute of the element, so one item in the data base can describe an element. The second case, to be called the permutable case from now on, represents each terminal on an element as a separate item in the data base with pointers linking the element and its terminals.

Each of the following examples is in the format used by OPS5[19] for representing the rules. OPS5 is a production system that was used in this work for testing out ideas on permutability, representing structures and errors, and finding them (see Chapters 4 and 5). In OPS5, the database is called *working memory* and the rules and patterns used to match the database are called *productions*. A production has the following form<sup>1</sup>:

```

rule: (p lhs --> rhs)

```

lhs: pattern+

**pattern:** (type ^slot-name slot-value)

type: the name of a data type declared to OPS5.

slot-name: the name of a field in the data type type.

slot-value: constant — variable — constraint

constant: a constant value, the slot must have this value.

<sup>&</sup>lt;sup>1</sup>See [19] for a more detailed description of the format.

variable: <variable-name>; if the variable has not been assigned the variable takes on the value of the slot. If the variable has been assigned, the slot must have this value.

constraint: conditionals (not equal, less than, greater than, etc.).

**rhs:** action+

action: operations to perform: add to the data base, modify data, delete data, output, request input, etc.

Using the OPS5 notation, the non-permutable representation for a MOSFET is:

```

(mosfet ^gate <gate> ^drain <drain> ^source <source>)

```

and the permutable representation is:

```

(mosfet ^source/drain <term> ^gate <gate>)

(terminal ^parent <term> ^type source/drain ^terminal <drain>)

(terminal ^parent <term> ^type source/drain ^terminal <source>)

```

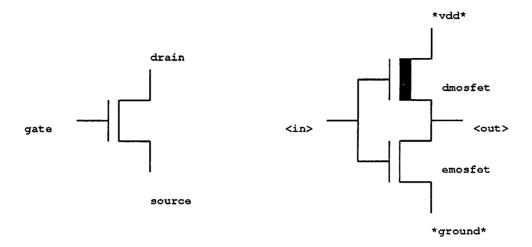

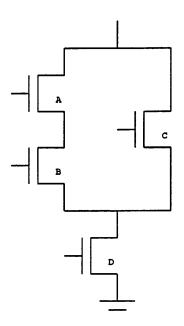

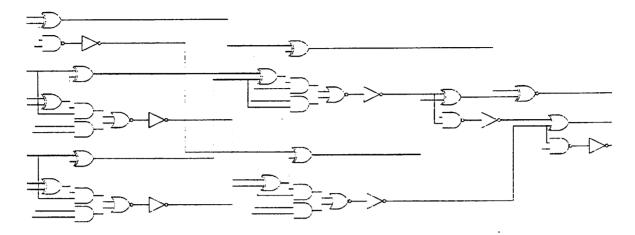

The following rules show the patterns to match an **inverter** made of a depletion-enhancement MOSFET pair (see Figure 3.1). Since the non-permutable format does not allow permutable terminals, four rules must be used to match all possible terminal permutations (2 allowed permutations per MOSFET and 2 MOSFETs). In general, for the non-permutable format, if M gates with N permutable terminals need to be matched,  $(N!)^M$  rules will be needed to match all combinations<sup>2</sup>.

```

(p inverter-0

(dmosfet ^gate <out> ^drain *vdd* ^source <out>)

(emosfet ^gate <in> ^drain <out> ^source *ground*)

-->

(make inverter ^input <in> ^output <out>))

(p inverter-1

(dmosfet ^gate <out> ^drain *vdd* ^source <out>)

(emosfet ^gate <in> ^source <out> ^drain *ground*)

-->

(make inverter ^input <in> ^output <out>))

```

<sup>&</sup>lt;sup>2</sup>For each gate with N permutable terminals the number of possible terminal permutations is N! and since the terminals of each gate can permute independently of the others, each gate multiplies the effect, giving  $(N!)^M$ .

Figure 3.1: Inverter Example

```

(p inverter-2

(dmosfet ^gate <out> ^source *vdd* ^drain <out>)

(emosfet ^gate <in> ^drain <out> ^source *ground*)

-->

(make inverter ^input <in> ^output <out>))

(p inverter-3

(dmosfet ^gate <out> ^source *vdd* ^drain <out>)

(emosfet ^gate <in> ^source <out> ^drain *ground*)

-->

(make inverter ^input <in> ^output <out>))

```

The following rule is equivalent to the four **inverter** rules above, but uses the permutable format. Note that the **inverter** created by this rule uses the non-permutable format since it does not have permutable terminals.

```

(p inverter

(dmosfet ^source/drain <sdl> ^gate <out>)

(terminal ^parent <sdl> <term> << drain source >> *vdd*)

(terminal ^parent <sdl> <> <term> << drain source >> <out>)

(emosfet ^source/drain <sd2> ^gate <in>)

(terminal ^parent <sd2> <term> << drain source >> <out>)

(terminal ^parent <sd2> <term> << drain source >> *ground*)

-->

(make inverter ^input <in> ^output <out>))

```

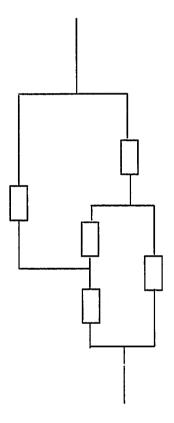

The non-permutable format requires M working memory elements and  $(N!)^M$  rules for M elements with N permutable terminals. The permutable case requires one rule and an extra working memory element for each permutable terminal, for a working memory size of  $M \times (N+1)$ . The RETE match algorithm used in OPS5[20] has a lower and upper bound of time per rule firing of  $O(log_2R)$  and O(R) for rules, and O(1) to  $O(W^{2C-1})$  for working memory elements (where C is number of patterns in a rule, R is the number of rules, R is the number of working memory elements). As can be seen, increasing the size of the working memory has a much worse effect on worst-case performance than increasing the number of rules. Tests with OPS5 on circuit examples show this and show that better performance is obtained when more rules are added to the system rather than when more working memory elements are added to the system. Thus the non-permutable format is faster than the permutable format.

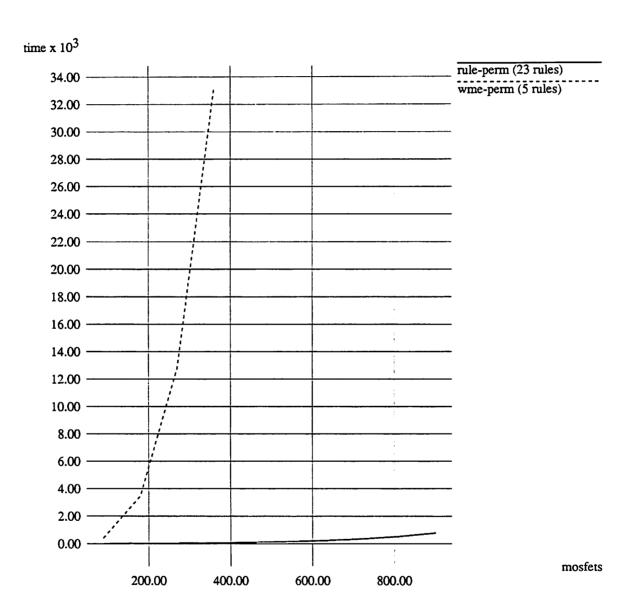

The following tables and graph show the results of experimenting with the two permutability formats. The experiment was to find latches that were composed of nand gates which were composed of MOSFETs. OPS5 on a VAX 11/785 was used for the experiments.

**Count:** the number of MOSFETs in the working memory.

WME count: the number of working memory elements at the start. The same as the MOS-FET count for the permutable rules format, three times the MOSFET count for the permutable working memory format (1 for each MOSFET and 1 for each of the 3 terminals).

**CPU time:** the time to find all the structures.

firings: the number of rules that fired.

firings/sec: the number of rules fired per CPU second.

memory: the maximum amount of memory used by OPS5 while finding the structures.

For M subpatterns with N permutable terminals in each subpattern, there will be  $(N!)^M$  pattern sets. Thus a basic CMOS inverter would have  $4(2!^2)$  pattern sets. Most

Figure 3.2: Time to Find NAND Gates and Latches

| Count | WME count | CPU time (sec) | firings | firings/sec | memory (MBytes) |

|-------|-----------|----------------|---------|-------------|-----------------|

| 90    | 90        | 4.6            | 49      | 10.6        | 1.3             |

| 180   | 180       | 14.9           | 98      | 6.5         | 1.3             |

| 270   | 270       | 32.1           | 147     | 4.5         | 1.3             |

| 360   | 360       | 58.4           | 196     | 3.3         | 1.3             |

| 450   | 450       | 95.1           | 245     | 2.5         | 1.4             |

| 540   | 540       | 150.6          | 294     | 1.9         | 1.4             |

| 630   | 630       | 231.4          | 343     | 1.4         | 1.5             |

| 720   | 720       | 347.3          | 392     | 1.1         | 1.6             |

| 810   | 810       | 519.5          | 441     | 0.8         | 1.7             |

| 900   | 900       | 772.3          | 490     | 0.6         | 1.8             |

Table 3.1: Finding NAND Gates and Latches - Non-permutable Format (23 rules)

| Count | WME count | CPU time (sec) | firings | firings/sec | memory (MBytes) |

|-------|-----------|----------------|---------|-------------|-----------------|

| 90    | 270       | 394.6          | 49      | 0.1         | 1.5             |

| 180   | 540       | 3466.1         | 98      | 0.02        | 2.0             |

| 270   | 810       | 12790.0        | 147     | 0.01        | 3.0             |

| 360   | 1080      | 33155.6        | 196     | 0.006       | 4.4             |

Table 3.2: Finding NAND Gates and Latches - Permutable Format (5 rules)

structure definitions contain two to four subpatterns that contain two permutable terminals, so the number of pattern sets does not grow too big  $(2!^4 = 16)$ .

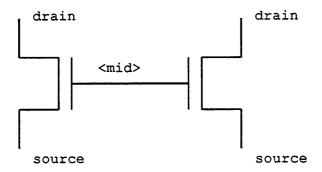

A point worth noting is that if some of the terminals that permute are not used in the pattern definition, then the number of patterns can be reduced. For example, if a pattern is looking for two MOSFETs that are connected together by their gates and is not concerned with what is connected to the source and drain terminals, then only 1 pattern is needed (see Figure 3.3). If information about how the source and drain were connected, 4 patterns would be needed.

Note that the ideas developed for permutability in this chapter apply equally well to the permutability of terminals in structures.

### 3.3 Built-in Primitives

While a circuit critic should not have knowledge of the different types of primitives for the various technologies and design styles (e.g. MOSFETs, registers), there are a

```

(p interesting-combination

(emosfet ^gate <mid>)

(emosfet ^gate <mid>)

-->

...)

```

Figure 3.3: Unused Permutable Terminals

number of primitives that are independent of the particular design style or technology. To simplify many of the structure finders and error checks these primitives should be known to the critic. The ones of particular importance are: **Node**, **Port**, **Supply**, **Ground**, and **Clock**.

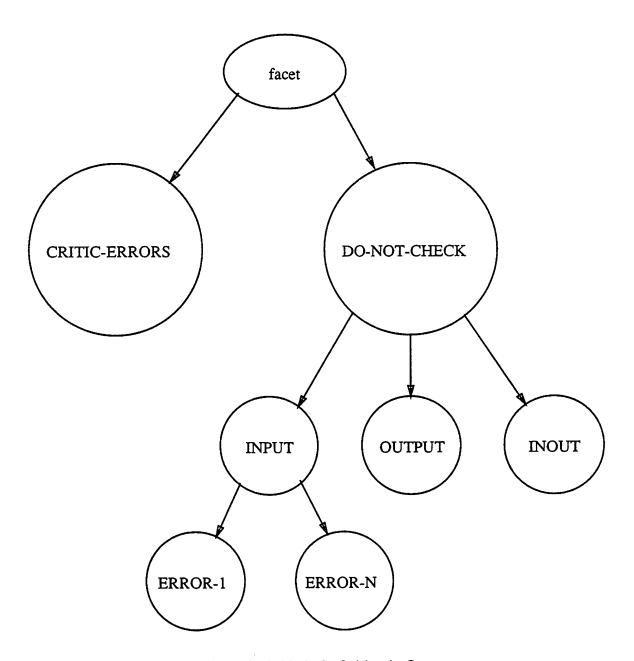

Nodes are used for tying together the various primitives defined for the technology and design style. The major purpose of the built-in node primitive is as a holder for node-based errors. Each technology or design style has a number of errors that are not associated with structures or primitive elements, but with the node itself. For example, no dc path to ground, multiple static outputs driving the same node, shorted supplies, or a node that is not testable.

Ports are used to connect the primitive elements and structure to the nodes. The purpose of a built-in port primitive is to allow for the special handling of external connections to circuits. These can simply be the formal terminals of a cell, the primary inputs and output of a logic network, or the pads for a chip. Many error checks are modified or do not apply based on whether the primitive element or structure being checked is connected to

one of these ports. For example, no dc path to ground does not apply to the inputs of cells. Also, special error checks are required when the inputs/outputs are pads.

Supplies, Ground, and Clocks are used to represent the power supplies, and time dependent signals input the to circuit. The one problem with supplies and clocks is that they have to be generic enough to handle all possible types of supplies and clocks that might exist for a wide range of technologies and design styles. It could easily be argued that these are design style and technology specific and should be in the definition of the primitives for the particular knowledge base. In the work for this dissertation, they were built-in primitives, but in hindsight, this may have been a mistake. Some technologies have multiple supplies (e.g. ECL), and some have complex supplies (e.g. ramps, sinusoidal, piece-wise linear). Clocks are even far more complex. Some technologies have no clocks, and some have multiple clocks. Clocks can many different attributes: rise and fall time, duty cycle, pulse width, etc. Of the design styles with multiple clocks, there are questions about whether the clocks overlap or not. Trying to fit all these various attributes in a coherent manner into a single supply and a single clock primitive was too ambitious a design goal.

# Chapter 4

# **Structures**

### 4.1 Overview

The complexity of large circuit designs makes it difficult, if not impossible, to design at the level of the primitive components. Instead, primitive components are grouped together into higher level components ('structures') and these higher level components are grouped into still higher level components, and so on. This is the basis of hierarchical design. The goal of hierarchical design is to reduce design complexity by representing structures by a simple abstraction of their detail at the higher level and/or by re-using a particular structure (regularity). Structure extraction is the process of taking a collection of interconnected primitives and finding the higher level structures that were originally used in the design or finding new structures not intended or expected (such as unexpected storage elements). By extracting the structure of a design a designer can easily see if the circuit has been implemented correctly.

A major use of structure extraction is to simplify the process of finding errors or of verifying the correctness of a design. Most descriptions of errors in a design are not represented in terms of the low level primitives, but in terms of the structures that the primitives make up. Rather than have the error check specify how these structures are composed and be responsible for finding them, a structure extraction can be performed before the error checks or sometimes during the check, allowing the error checks to be specified more simply in terms of the structures.

# 4.2 Representation

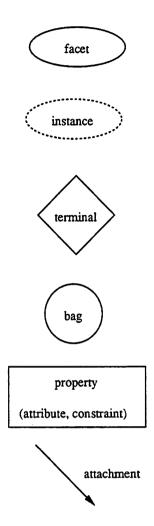

There are many approaches to representing structures. However, before these approaches can be explored, the necessary basic concepts to be represented must be determined. These concepts can then be used to explore and compare various representations and implementations. Structures require the specification of the attributes associated with the structure and the attributes of the components of the structure, the terminal information of the structure, the connectivity and composition, how the structure can be stored in the database, and finally how it can be presented to the user.

#### **Attributes**

The information needed for the representation and the reasons for needing it are the same as that needed for primitives (see Chapter 3). The only difference is that most of the attributes for structures will be calculated based on the values of the attributes of the components of the structure. Thus a method of referring to attributes on the components is necessary.

#### **Terminals**

The information needed for the representation of terminals of structures is the same as that needed for primitives (see Chapter 3).

### Composition

The representation must be able to describe the composition of the structure (i.e. what items make up the structure) and the constraints on the composition of the structure (i.e. connectivity, constraints on attributes).

#### **Database Storage**

If the structures are to persist across runs of the critic or if other tools are to be used to present the results of the critic, the structures must be stored in the database.

#### **Display**

Once the structures have been found, there must be a way to present this information to the user. If the system is part of a larger integrated system, the display of the structures may be taken care of once a method of making them persist is developed.

### **Approaches**

Two approaches were explored for representing structures: textual and graphical. To explore the textual approach for representing structures, a language was developed for describing the structures. There were three portions to the description: finding the structure, calculating attributes for the structure, and use of the structure in finding higher level structures. The "how to find the structures" portion consisted of what primitives and other structures made up the structure being defined, what constraints each component had, how the components were interrelated by connectivity and attributes, and how the structures were used in other structure definitions.

An important feature of the language was to remove all system internal information and lower-level system syntax and semantics from the language. By removing this information, the language would be independent of a particular implementation. The features of the language are as follows:

**name:** The name of the structure (e.g. INVERTER, LATCH). This is used for documentation and for definitions of structures that contain structures of this type.

**comments:** Comments about the structure, *e.g.* "This latch operates based on....". This is purely for documentation.

**components:** Describes the components that make up the structure and how they are interelated. The components are described as a set of one or more patterns.

actions: Describes the actions to be performed when the structure is found in the database.

Used mainly for the calculation of attributes of the new structure:

```

(let <w/l> (compute (<width> // <length>)))

```

terminals: A list of the external ports of the structure.

permutable-terminals: A list of the terminals of the structure that can permute.

**structure:** Describes the structure to be created when the components are found in the database.

The following is an example of a structure defined using the language:

```

(defstructure

(name inverter)

(components (depletion-mosfet (name <load>)

(drain *vdd*)

(gate <out>)

(source <out>))

(enhancement-mosfet (name <driver>)

(drain <out>)

(gate <in>)

(source *ground*)))

(terminals input output)

(actions (let <b-r> (compute (<driver:width> // <driver:length>)

// (<load:width> // <load:length>))))

(structure (inverter (input <in>)

(output <out>)

(beta-ratio <b-r>))))

```

The language described above for structure definitions has the advantage of being human readable, however it is not based on an existing circuit description language or database format. In Heckel's book, *The Elements of Friendly Software Design*, "Speak the Users Language" is listed as one of his important principles if the design of successful user interfaces[30]. In describing structures to the critic, it would be advantageous to be able to use existing cell designs rather than having to enter descriptions of the cells in the structure description language. Structures should be 'described by example'. 'Described by example' means the ability to enter cell designs using standard graphics editors and have them be directly used by the circuit critic for structure definitions.

### **Processing**

To simplify the definition of the structures, the order in which the definitions are stored and read by the critic should not be specified. Since some structure definitions depend on others they must be processed in a specific order, *i.e.* the items used in a definition must be defined before the definition that uses them. A simple levelizing routine is all that is needed to determine an ordering based on dependencies between structure definitions. The algorithm has a best case complexity of  $O(n)^1$ , where n is the number of structures defined, and a worst case complexity of  $O(n^2)^2$ . Most rule sets would have n < 50 structures defined, so the time to process the rule set is acceptable<sup>3</sup>. The following pseudo-code shows a simple algorithm for levelizing the structure dependencies:

```

list = list of structure types;

ordered-list = empty;

foreach primitive definition {

add primitive ordered-list;

}

forever {

if list is empty return ordered-list;

item = first element in list;

if depend(item) subset-of ordered-list {

/* dependencies have been satisfied */

add-to-end item ordered-list;

} else {

add-to-end item list;

}

}

```

<sup>&</sup>lt;sup>1</sup>All structures are defined in the order of use by other structures, *i.e.* all structures are defined before they are used, no forward references.

$<sup>^{2}</sup>$ The structures are defined in the opposite order of use by other structures, *i.e.* structures are used before they are defined.

<sup>&</sup>lt;sup>3</sup>If the time gets too large, a better algorithm could be used, the structures could be partially ordered, or the results of a levelizing could be saved for future use.

# 4.3 Finding Structures

In building a system for finding structures in the database, there are several questions to answer: should the search go top-down or bottom-up, should the search be rule-based or algorithmic; if rule-based, should the rules be ordered a priori or change as the database changes; should pattern matching be done; how should the pattern-matching be done; and should finding series-parallel groups of elements be treated the same as finding structures.

To minimize the amount of code that needed to be written to explore some of the ideas in representing and searching for structures, the system was originally built on top of OPS5. This allowed the use of an existing rule system and pattern matcher, along with a language for describing structures. However, after using OPS5, problems were encountered in two areas. First, translating a primitive or structure description to an OPS5 representation required the addition of OPS5 specific information. Not just the expected syntactic changes, but information regarding semantics. For example, OPS5 would allow both components of the following pattern (used for matching two parallel elements) to match the same element in the database:

```

(element ^top <net1> ^bottom <net2>)

(element ^top <net1> ^bottom <net2>)

```

the following additional information would have to be added to force the components to match different elements in the database:

```

(element ^name <name> ^top <net1> ^bottom <net2>)

(element ^name <> <name> ^top <net1> ^bottom <net2>)

```

Each additional component for element would require more complex checks:

```

(element ^name <> <name1> <> <name2> .... <> <nameN> .... )

```

Second, the OPS5 rule sequencing (conflict resolution) was different than the sequencing required for searching for the structures, so extra patterns and rules were needed to direct the searching of OPS5. Since there is no way to statically declare rule ordering in OPS5, the ordering was always determined at run-time. In order to get the desired rule

order, the ruleset was split into 'rulesets'. Rulesets are usually set up by putting a 'ruleset' pattern in each rule. The ruleset pattern has one attribute which is the name of the ruleset.

In order to allow a ruleset to run, an element is placed in working memory that has the name of the current ruleset. To go to the next ruleset, the current element is removed and a new one with the name of the next ruleset is added. There are a couple of ways to do this sequencing of OPS5 rulesets: one is to have a set of rules that know how to switch from one rule set to another, *i.e.* one rule for each ruleset transition; another is to build a queue of rulesets and have a generic rule that pops a ruleset name off the queue and causes that ruleset to be run. This corresponds to having the control knowledge is in the data or in the ruleset. The following shows an example rule with a ruleset pattern and a rule for switching between rulesets. Both rules match data in the database, but OPS5 will always fire the one that is more specific, *i.e.* has more components. The first rule fires until there are no more inverters to find, then only the second rule matches the database and it is allowed to fire.

```

(p

(ruleset ^name find-inverters)

(mosfet ^type nmos ...)

(mosfet ^type pmos ...)

...)

(p

(ruleset ^name find-inverters)

->

(delete 1)

(make ruleset ^name find-latches))

```

The following shows the initializing of a stack of rulesets and the generic rule for popping the stack. This scheme works because OPS5 will use the most recently added item when it looks for rules to fire, thus rules from the most recently added ruleset will be considered first. This has the disadvantage that all rules in all rulesets are looked at to determine which one to fire.

```

(make ruleset ^find-latches)

(make ruleset ^find-inverters)

```

```

(ruleset)

->

(delete 1))

```

### **Top-Down Versus Bottom-Up**

The process of extracting structures can be a top-down or bottom-up process. In a bottom-up process the structures that are composed entirely of primitives are found and then structures that use the recently found structures (and possibly other primitives) are found, and so on. The contents of the database drives the process of extraction. In a topdown process, the search begins by looking for the set of top level structures (structures that are not used in any other structure descriptions), for each top level structure the critic searches for its component structures, and so on, until primitives are being searched for. For example, if the structure types to be searched for are latches and inverters, and the primitives are enhancement and depletion mode MOSFETs, then the top-down search would start out trying to find all latches. Since latches are composed of inverters and there are no inverters in the circuit, the inverter structure descriptions would be used to search for inverters. The constraints on the connectivity of the inverters in the latch would be passed down. The inverter descriptions are composed of MOSFETS, which are primitives, so the downward process stops. In a bottom-up search, all structures would be searched for, but only the inverter description would be used since it is composed entirely of primitives. Once inverters are found, the latch description may be used since its components have been found. In the bottom-up process, all structures of a given type can be found before going on to another, or as structures are found other structure descriptions that reference them can be used. For example, all inverters can be found before any latches are searched for, or as soon as an inverter is found, latches can be searched for.

# **Ordering**

There are two ways to manage the rules used for finding structures. The list of rules to be fired and their order can be statically determined at the time that the knowledge base is loaded, or the list of rules and their order can be dynamically determined based on