Copyright © 1988, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### AUTOMATIC SYNTHESIS AND LAYOUT OF SWITCHED-CAPACITOR FILTERS

.

by

Hormoz Yaghutiel

Memorandum No. UCB/ERL M88/56

16 August 1988

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### Automatic Synthesis and Layout of Switched-Capacitor Filters

Hormoz Yaghutiel

Ph.D.

Department of Electrical Engineering and Computer Science

#### Abstract

Design cycle time for complex analog and mixed analog/digital Integrated-Circuits (IC's) is expected to be drastically reduced with the help of computer-aided design tools. Unfortunately, very few steps have been taken towards automatic generation of efficient analog circuits. An important class of analog IC's whose manual design is particularly time consuming is switched-capacitor filters. This thesis describes a switched-capacitor filter module generator which can produce optimized layouts for these circuits. thus saving large amounts of manual design time. Previous efforts in the area of reducing design cycle times have often resulted in increased areas and reduced performance in comparison with manual designs. The system described in this thesis exploits various degrees of freedom in the design of switched-capacitor filters to generate efficient circuits. Special emphasis has been placed on the physical design aspect of module generation. due to the heavy dependence of analog performance on fine details of layout. Experimental results for this system indicate that generation of area-efficient switched-capacitor filters with good quality is possible in reasonable CPU times.

Alberto Sangiovanni-Vincentelli Thesis Committee Chairman

#### Acknowledgments

I wish to express my deepest gratitude to my advisor Professor Alberto Sangiovanni-Vincentelli for his continuous support during the course of my Ph.D. studies, and to Professor Paul Gray for his guidance in the field of analog integrated circuit design. I would also like to thank them along with Professor Shoshichi Kobayashi for serving on my dissertation committee. The help of Professors Robert Brodersen and David Hodges is also gratefully acknowledged. I am also indebted to DARPA for financial support received under Grant N00039-87-C-0182.

The help and friendship of many fellow students have contributed to this work and made my years at Berkeley more enjoyable. Homayoon Ansari, Farhad Ayrom, Hamid Bahadori, Saman Behtash, Jeff Burns, Giorgio Casinovi, Andrea Casotto, Ramin Esmail-Beygui, Tammy Huang, Reza Kazerounian, Young Kim, Ramin Khalili, Haideh Khorramabadi, Davar Khoshnevisan, Ken Kundert, Steve Lewis, Kartikeya Mayaram, Linda Milor, Omid Razavi, Dave Riley, Fabio Romeo, Hamid Savoj, Shahram Shahruz, Scott Shen, Hyunchul Shin, Jyuo-Minh Shyu, Sehat Sutarja, Chorng-kuang Wang, Ray Wei, and Nick Weiner are just a few of the names that come to mind.

My most sincere thanks to my best friend Susie, who has endured many of the hardships all along with me. Finally, I like to thank my parents for their support and patience during these long years.

# Contents

.

| Table of Contentsi |      |                                                               | ii |

|--------------------|------|---------------------------------------------------------------|----|

| 1                  | Intr | oduction                                                      | 1  |

|                    | 1.1  | Motivation                                                    | 1  |

|                    | 1.2  | Analog Versus Digital                                         | 2  |

|                    | 1.3  | CAD and Design Automation                                     | 3  |

|                    | 1.4  | CAD Systems for Analog IC Design                              | 5  |

|                    | 1.5  | Contribution of the Thesis                                    | 10 |

|                    | 1.6  | Organization of the Thesis                                    | 11 |

| 2                  | Syn  | thesis of Switched-Capacitor filters                          | 13 |

|                    | 2.1  | Introduction                                                  | 13 |

|                    | 2.2  | LDI Bottom-Plate Integrator                                   | 15 |

|                    | 2.3  | Stray-Insensitive Switched-Capacitor Filters                  | 17 |

|                    | 2.4  | Design Methods                                                | 20 |

|                    | 2.5  | A Synthesis Procedure for SC Ladder Filters                   | 21 |

| •                  | 2.6  | Review of Automatic Synthesis Systems                         | 34 |

| 3                  | Lay  | out Strategies for Switched-Capacitor Filters                 | 36 |

|                    | 3.1  | Introduction                                                  | 36 |

|                    | 3.2  | Considerations for the Layout of Switched-Capacitor Filters . | 37 |

|                    |      | 3.2.1 Capacitor Ratio Accuracy                                | 37 |

|                    |      | 3.2.2 Techniques for Improving Power Supply Rejection         | 40 |

|                    |      | 3.2.3 Fully-Differential Versus Single-Ended Architectures .  | 40 |

|                    | 3.3  | Systems for Automatic Layout of Switched-Capacitor Filters    | 43 |

|                    | 3.4  | A New Approach to Automatic Layout of Switched-Capacitor      |    |

|                    |      | Filters                                                       | 47 |

|                    |      | 3.4.1 Floor-planning strategy                                 | 47 |

|                    |      | 3.4.2 The Input Format                                        | 51 |

|                    |      | 3.4.3 Flow of the System                                      | 53 |

56 **Generation of Capacitor Arrays** 4 56 4.1 57 4.2 Problem Formulation 57 4.2.14.2.2 60 4.2.3Computational Complexity 65 4.2.466 Generation of Symbolic Matrices 70 4.3 70 4.3.1 Problem Formulation 71 4.3.275 4.3.3 · 77 Generation of Mask Layouts from Symbolic Matrices . . . . 4.4 78 Area/Perimeter Constant Fractional Capacitors . . . . . . 4.583 5 Placement and Routing Issues 83 5.1 84 5.285 5.2.1Op-Amp and Switch Ordering ..... 90 5.2.2 92 5.2.393 Channel Routing 5.3 94 5.4 97 **Experimental results** 6 **Conclusions and Future Directions** 112 7 114 Bibliography

iii

S

# Chapter 1

# Introduction

#### 1.1 Motivation

Recently, there has been an increasing interest in the development of Computer-Aided Design (CAD) tools for analog Integrated Circuits (ICs). This can be attributed partly to the need, as dictated by economic factors, to integrate digital and analog functions on the same chip. Such chips open up applications in telecommunications, data storage, speech processing, robotics, and other analog fields. Design time for complex digital ICs has been dramatically reduced with the help of CAD tools. Without such tools for analog circuits, which typically occupy a small area of the chip, the analog design can become a bottle-neck for the overall design of the chip.

In some applications such as filtering, there is a choice between a digital or an analog solution. For the current 1.25 micron CMOS technologies, a well designed analog circuit typically occupies smaller area and consumes less power than its digital counterpart. The digital circuit, on the other hand, is capable of realizing more accuracy. These trade-offs are usually over-shadowed by the fact that most IC designers are oriented towards digital design, and more effort is required for analog design. Development of CAD tools, and in particular design automation tools, for analog ICs will greatly reduce the design effort and amount of expertise needed. An important class of analog ICs whose manual design and layout are particularly time consuming are Switched-Capacitor (SC) filters [1]. In this thesis we focus on automatic synthesis, and specifically physical design of these filters.

#### 1.2 Analog Versus Digital

In analog systems the signals, which are in the form of voltages. currents. and charges, are continuous functions of time. By contrast, in digital systems each signal is represented by a sequence of finite number of binary digits: therefore, these signals can take on discrete values only. Due to the binary nature of signals, digital circuits are realized using gates with only two states, each state being defined in some range of the continuous signal. This makes digital circuits to a large degree immune to various noise sources inherent in integrated circuits. Then the design effort can be directed mainly towards trade-offs between power consumption, speed, and area. Since in digital circuits, devices act as switches moving information between storage elements, they can often have the minimum size permissible in the process; only those devices on critical paths or driving large loads need to have radically different sizes.

Analog circuits in general require more design freedom in order to be applied effectively. They often exploit the full spectrum of capabilities exhibited by individual devices. In an analog circuit the individual devices often have substantially different sizes and electrical characteristics. These circuits require optimization of various performance measures. As an example, among the performance measures for operational amplifiers are gain. bandwidth, noise, power supply rejection, dynamic range, offset voltage, and so on. The importance of each performance measure depends on circuit application. For this reason, fine tuning plays a crucial role in design of analog circuits.

Because IC wafer fabrication processes do not produce active and

V.

ĩ

passive devices with the same stability and accuracy as discrete components, analog designers over the years have developed circuits which cancel out the first order variations in key parameters. This means, however that the analog circuits then become sensitive functions of the second order variations of such parameters, for example the matching of input devices in differential pairs, or capacitor matching in SC filters. Sensitivities to second order variations impose constraints on design and specially layout of analog circuits. These constraints are in general not present in digital design.

#### **1.3** CAD and Design Automation

The continued shrinking of device dimensions has made it possible to integrate more functions on the same chip. This increased complexity has in turn necessitated development of CAD tools to assist designers and reduce design cycle times and costs. Development of efficient CAD tools has depended on structured design strategies to reduce the complexity of IC design. Some properties motivating these strategies are [2]:

- **Modularity** Modularization involves dividing a system into a set of "well formed" modules such that the interactions between these modules are well characterized. For example from a layout point of view. the phrase "well formed" corresponds to a well defined physical interface that indicates the position. name, layer, type. size. and signal type of external interconnections. Modularity helps the designer to clarify and document an approach to a problem, and also allows a designer to be of more utility by checking attributes of a module as it is constructed. The ability to divide a task into a set of well-defined modules also aids in a team design where a number of designers have a portion of a complete chip to design.

- Hierarchy The use of hierarchy involves dividing a module into submodules and then repeating this operation on the submodules until the com-

plexity of the submodules is at an appropriately comprehensible level of detail. Hierarchy also refers to the abstraction levels through which a design must pass. For example, the various abstraction levels in digital design are behavioral, register-transfer, logic-gate, switch, transistor. and mask-layout.

- Regularity The use of iteration to form arrays of identical cells is an example of the use of regularity in an IC design. However, extended use may be made of regular structures to simplify the design process. For example if one was constructing a "data-path," the interface between modules (power, ground, clocks, busses) might be common but the internal details of modules may differ according to function.

- Locality By defining well-characterized interfaces for a module. we are effectively stating that the internals of the module are unimportant to any exterior interface. In this way we are performing a form of information hiding that reduces the apparent complexity of that module.

These properties have been extensively used in the development of strategies and tools for simulation. synthesis. layout, and testing of digital circuits. For example simulation tools have been developed for every level of design hierarchy. This makes it possible to verify the functionality of large digital designs by simulating entire systems at behavioral level, the complex modules at logic-gate level, and so on. As another example, the combination of modularity and regularity has contributed to development of standaid-cell and gate-array layout styles. These styles have proven more amenable to design automation than irregular structures.

Modularization is a common practice in manual design of analog circuits. For example, an A/D converter is usually described in terms of its operational amplifiers. comparators. matching capacitors, matching resistors, and switches rather than the individual devices making up the circuit. Hierarchy is also employed in analog circuit design. An A/D converter is

ţ

ì

composed of common functional blocks such as operational amplifiers and comparators. These functional blocks are themselves composed of simpler common blocks such as current mirrors and differential pairs. At the lower end of the hierarchy we find individual devices such as transistors. resistors. and so on.

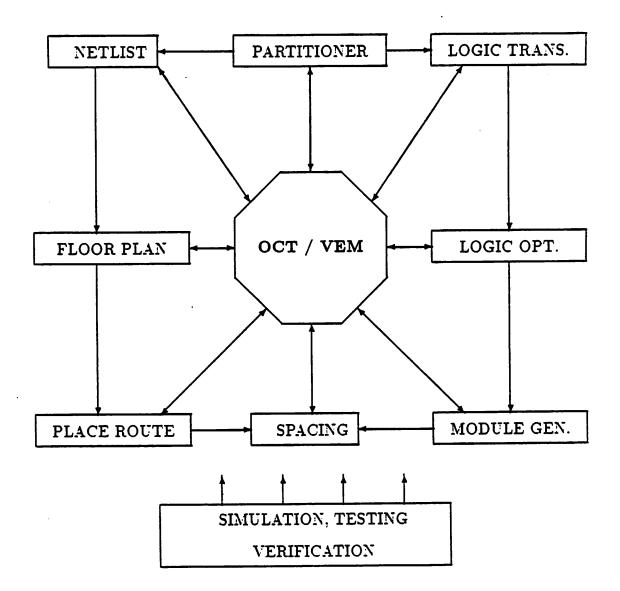

These properties serve as motivation for development of analog synthesis environments similar to the ones existing for digital design. An example of a digital synthesis system is the work done at Berkeley. This system accepts a behavioral or algorithmic description of a digital system and produces a circuit mask layout through four synthesis steps: behavioral, structural, logic [3], and layout [4]. A more detailed structure of this system is presented in figure 1.3. In this system the various modules communicate through the Oct data manager [5].

Since analog problems are very different from digital, their design automation requires new methodologies and development of new tools. In the next section the proposed approaches to automatic synthesis of analog circuits will be discussed.

#### 1.4 CAD Systems for Analog IC Design

The field of CAD for analog circuits has progressed at a considerably slower rate than has been the case for digital. Part of the reason has been the heavier dependence of analog performance on fine details of layout and device behavior. Another reason might be the present difficulty to identify a level of abstraction where generic models such as the ones developed for digital synthesis can be derived. While for digital circuits. several steps have been taken towards automatic generation of efficient circuits. for analog functions only few results are available. So far most of the work has been directed mainly towards reducing design cycle time, often at the expense of area and performance.

The system reported by Allen [6] can generate layout for some range

Figure 1.1: The Berkeley Synthesis System.

6

ç

È

of linear. nonlinear. continuous and discrete-time ICs. Among its capabilities are SC filters and successive approximation A/D and D/A converters [7]. It can also produce circuit simulation files for the generated circuits. These circuits are realized in a standard cell layout style by interconnections of fixed and programmable pre-designed blocks.

In another system [8]. a library of analog standard cells contains the most common circuit elements including analog switches, operational amplifiers, comparators, peak detectors, current controlled oscillators. D/Aconverters and delay cells. These cells have fixed heights with power supply rails running along the top and bottom. To generate more complex analog functions, these cells are automatically placed and routed in a standard cell layout style. Isolation of digital and large swing analog signals from sensitive analog signals has been achieved by special design of library cells and by a placement strategy to guarantee the containment of sensitive nets in a local routing channel.

In the methodology for layout generation of analog circuits presented in [9], the circuit is partitioned into functional blocks consisting of library cells previously developed. The automatic placement and routing is again performed in a standard cell layout scheme. This system allows the user to provide an incomplete specification of the basic cells required for the design. It then scans the library for the best match between the specified description and the cells in the library.

DeGrauwe [10] reported a system which generates device dimensions and bias currents for a library of analog schematics as a function of technology and desired specifications. The basic library includes 12 transconductance amplifiers, 5 voltage references, 4 operational amplifiers. 3 low-noise BIMOS amplifiers, 1 quartz oscillator and 2 oversampling A/D converters including a digital decimation filter. In this approach the expert knowledge for each type of circuit is hard coded in the framework and also analytical equations are derived for each circuit in the library, which is then used to optimize the performance of the circuit. In the knowledge-based approach to analog synthesis reported in [11]. circuit schematics including device sizes are produced for common analog functional blocks. The framework is based on the idea that the circuit topologies are selected from among fixed alternatives: they are not constructed transistor-by-transistor for each new design. A topology for a high-level module is specified as an interconnection of subblocks, not as an interconnection of transistors. Based on this approach a prototype op-amp synthesis system has been presented.

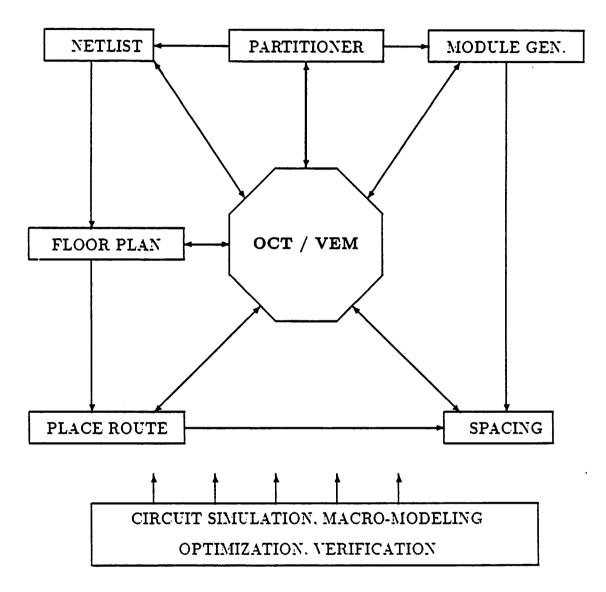

The approach we have adopted to automatic synthesis of analog circuits, is to focus on techniques that allow design of circuits with efficiency comparable to the ones manually designed by skilled designers. To realize this goal the problem of automatic synthesis is decomposed into three closely coupled stages. In the first stage the components of the design are chosen to meet the given performance specifications. For example these components for a telecommunication chip could be an A/D converter with specified accuracy and speed. a set of switched-capacitor filters, and a DSP processor. In the second stage the components are synthesized by module generators to meet the goals set in the first stage [12,13]. In parallel with the first two stages, simulation has to be performed at the system and component level [14,15, 16.17] (figure 1.2).

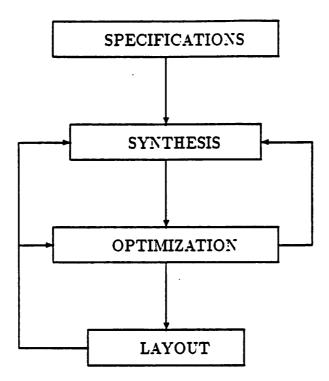

This process can be hierarchical in the sense that the modules such as SC filters can be designed with a similar process. The components of the filter are chosen and designed to meet the specifications and then can be automatically generated, placed, and routed (figure 1.3). The only difference is modules such as SC filters and A/D converters are well studied and much is known about the effects of the component selection and architecture on the system level performance.

Optimization is an important part of module generation [18]. Most often the synthesis step does not take into account the second order effects. In the optimization step the design parameters are fine tuned so that the synthesized circuit with parasitic effects included. meets the specifications.

8

ł

i.

Figure 1.2: An analog synthesis system.

Figure 1.3: The process of module generation.

In this thesis the module generation aspect of a synthesis system is studied.

#### 1.5 Contribution of the Thesis

Filtering is an important operation in many electronic systems. In audio, telecommunications and a wide spectrum of other applications filters have been used extensively for pre- and postprocessing of signals. SC filters are analog sampled data ICs implemented in MOS technology. They are capable of precision frequency-selective filtering and can be integrated with digital LSI circuits. Since their advent in the late seventies, these filters have matured to a great degree.

Since SC filters can be integrated with digital circuits, they are in direct competition with digital filters. SC filters are generally smaller and consume less power than similar digital filters in the context of current 1.25 ŝ

micron technologies. and unlike digital filters, they do not require the large front end A/D converters. As a result of the analog nature of SC filters. their performance is heavily dependent on fine details of device behavior and layout. This combined with their time varying nature has made their manual design and layout particularly time consuming, therefore making them a prime candidate for design automation.

A number of systems have been reported for automatic synthesis of these filters. Some of these systems are capable of producing layouts for the generated filters. However, they all have limited use as a result of their layout strategies. These limitations will be discussed in detail in chapter 3. Our goal in this project was to study the feasibility of a fairly general automated layout system for SC filters with very little sacrifice of area efficiency or performance. This study led to the development of a technology and topology independent system for generation of efficient single-ended SC filters. The main body of the thesis is dedicated to presenting this layout system.

#### **1.6** Organization of the Thesis

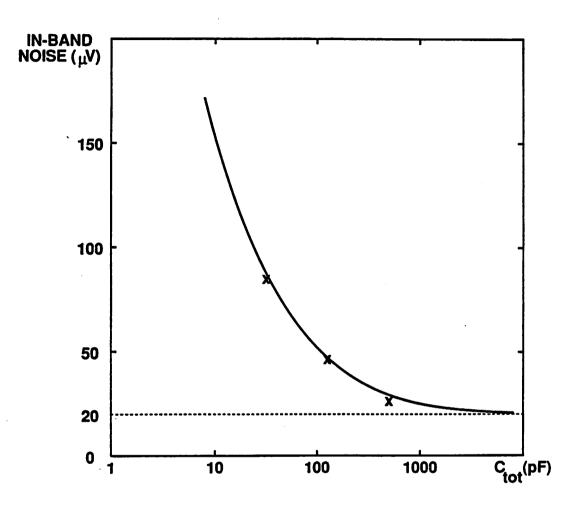

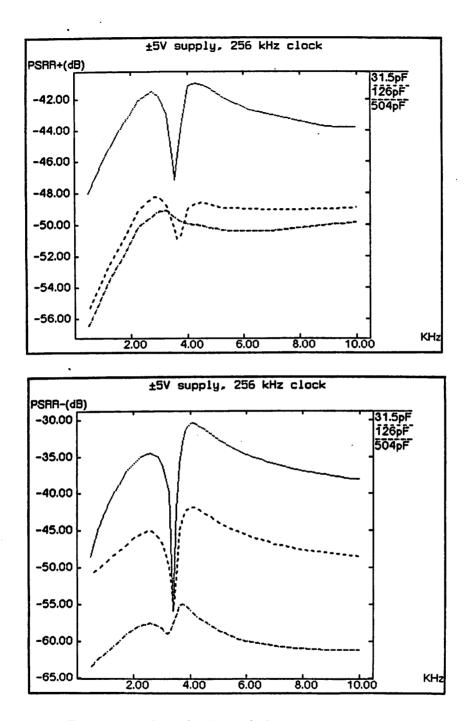

In chapter 2, the principles of operation of SC filters are reviewed. It is followed by a discussion of current approaches to synthesis of these filters. Then a step-by-step procedure for synthesis of SC ladder filters is presented. The final section of this chapter is a survey of tools for synthesis of these filters. In chapter 3. I introduce our strategy for automated layout of SC filters. I begin this chapter with discussing the issues involved in the layout of SC filters. Next, I present a survey of reported SC layout tools. Then, the merits of the new layout strategy are discussed. It is followed by our choice of input format. Finally the organization of the layout system is reviewed. To exploit this strategy, we have solved a set of layout problems. This is the topic of the next two chapters. In chapter 4, the problems associated with generating area/perimeter constant capacitor layouts to meet the proposed layout strategy are discussed in detail. To solve these problem, several algorithms are developed. In this chapter the performance of each algorithm is analyzed both mathematically and experimentally. In chapter 5, the placement and routing stages of layout generation are presented. First algorithms for linear placement of modules to minimize the routing area and improve the quality of the routing are presented. Then, the features of MIGHTY [19]. the channel router employed by the system, are discussed. I finish this chapter by presenting the method we have developed to shield the unwanted crossovers in the routing channels. In chapter 6, experimental results on a set of prototype filters generated using the layout system and fabricated in a 3 micron CMOS technology are discussed. As a consequence of our experiments, we observed a trade-off between the total capacitance and power supply rejection of the filters. Chapter 7 is a discussion of extension of ideas of this thesis to other applications, such as fully-differential architectures and A/D converters.

ć

## Chapter 2

# Synthesis of Switched-Capacitor filters

#### 2.1 Introduction

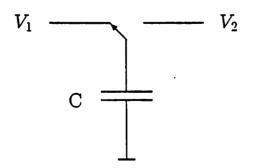

The basis for operation of switched capacitor filters originated from the observation that if a capacitor is periodically switched between two voltage sources, it acts as a resistor between the two sources [20]. In other words, the switches transform the capacitor, a non-dissipative memory element. into a dissipative memoryless one. In Figure 2.1 capacitor C is periodically switched between two voltage sources  $V_1$  and  $V_2$ . Then the average current

Figure 2.1: A switched capacitor.

flowing from  $V_1$  to  $V_2$  is  $C(V_1 - V_2)f_c$  where  $f_c$  is the switching frequency. Therefore the switched capacitor behaves like a resistor having a value  $\frac{1}{Cf_c}$ . This idea was later incorporated into the development of circuit techniques in MOS technology where the fundamental precision of the analog quantity was defined by the ratio of two on chip MOS capacitors. These circuits are typically comprised of capacitors, operational amplifiers, and clock-controlled switches. With proper process design, the monolithic MOS capacitor shows very stable characteristics with respect to changes in temperature and voltage. While the absolute value of the capacitance exhibits random processing variations of the order of 10-20 percent, with proper layout techniques, the MOS capacitor ratio can be made accurate to within 0.1 percent.

Initial SC filters suffered from sensitivity to non-linear parasitic capacitances associated with various nodes in the circuit. For this reason, the capacitors had to be designed substantially larger than these parasitics in order to maintain the analog precision. This contributes to large filter areas and severely limits the frequency range of operation of the filter by heavily loading the operational amplifiers. This shortcoming was overcome by the advent of parasitic-insensitive circuit techniques [21]. This chapter starts with presenting a parasitic-insensitive SC integrator. followed by discussing the general parasitic-insensitivity condition for two phase SC filters.

There have been a number of design techniques reported for SC filters. The two most common SC filter realizations are cascade of second order sections and ladder-type designs. In section 2.4 the two techniques are discussed.

The sampled-data nature of SC filters calls for their design to be carried out in the discrete frequency (z) domain [22]. Nevertheless, a common practice in the design of SC filters is to evaluate the filter's capacitor ratios directly from the time constants associated with the continuous active filter having the desired frequency response. The frequency response of the resulting SC filter closely approximates the desired response if the filter time constants are many times smaller than the sampling frequency. This ĩ

assumption is supported by the following argument:

To avoid aliasing effects, the incoming signals to SC filters should be band-limited to less than half the sampling frequency. This is typically carried out by a continuous-time active pre-filter. In order to ease the pre-filtering requirements, the frequency range of operation of the filter is kept many times smaller than the sampling frequency.

The approximation method of synthesis is illustrated in section 2.5 by presenting an approach to the deign of ladder-type filters. First. a systematic approach to map the continuous LC ladder filter to interconnections of integrators is presented. This section also deals with mapping of finite transmission zero elements into capacitive coupling of integrators. Then, mapping of continuous element values into capacitor ratios is discussed. It is followed by discussion of optimization of dynamic range and capacitor ratio spread via circuit transformations. The factors involved in choosing the switching scheme will also be studied. Finally adjustment of capacitor ratios for design centering is considered.

In some cases the designs resulting from approximate synthesis are not acceptable. One solution is to fine-tune the capacitor ratios to match the desired response. This can be achieved by using mathematical programming techniques [23]. Another approach is to design the filter directly in the z-domain. These techniques have been employed in the development of a number of automatic SC filter synthesis systems. In the final section, these systems will be discussed.

#### 2.2 LDI Bottom-Plate Integrator

A switched-capacitor filter can be viewed as an active RC filter. where each resistor has been replaced by a combination of a capacitor and few switches. The switches are implemented by MOS transistors with clock controlled gates. Since the basic building block of an active RC filter is

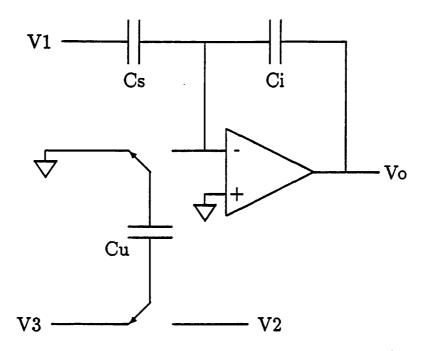

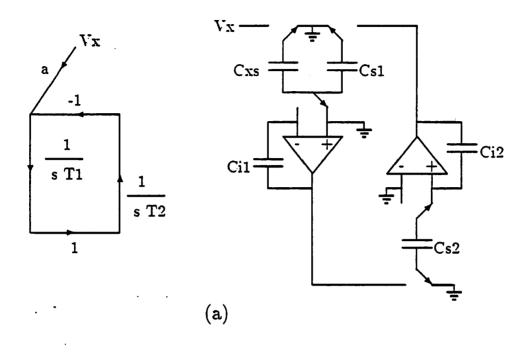

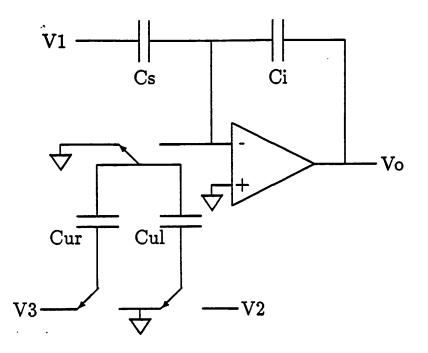

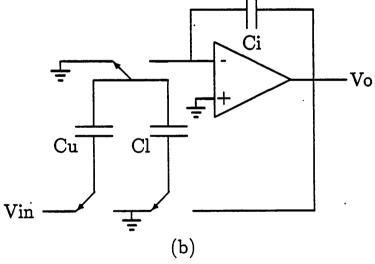

Figure 2.2: A switched-capacitor integrator/summer.

active integrator/summer, we can gain insight into the operation of SC filters by examining an SC implementation of integrator/summer (figure 2.2). Assuming ideal elements, the circuit of figure 2.2 can be described by the following z-transform equation [24]:

$$V_o = -\frac{C_s}{C_i}V_1 + \frac{\frac{C_u}{C_i}}{1 - z^{-1}}(z^{-\frac{1}{2}}V_3 - V_2)$$

(2.1)

If the fastest fluctuations of the input voltage are much slower than the clock frequency, namely  $sT \ll 1$ , where T is one clock period. then

$$1 - z^{-1} = 1 - e^{-sT} \approx sT,$$

$z^{-\frac{1}{2}} \approx 1 - \frac{sT}{2} \approx 1.$

Substituting these approximate expressions in Equation 2.1 we find:

$$V_o \approx -\frac{C_s}{C_i} V_1 + \frac{C_u}{sTC_i} (V_3 - V_2)$$

(2.2)

£

The above expression shows that this circuit acts as an integrator/summer with a time constant of  $\frac{C_u}{TC_i}$  for the range of frequencies  $s \ll \frac{1}{T}$ . Thus, the operation of the circuit depends on the capacitor ratios and not on their absolute values. This remains true when several integrating blocks are interconnected to form more complicated circuits. As discussed earlier, an accuracy of the order of 0.1% can be achieved for the ratio of two on chip MOS capacitors [25]. The clock frequency can also be controlled very accurately. Thus, the time constants of SC filters can be realized with excellent accuracies.

The most common use of SC filters has been in the voice band applications, where the required filter time constants are on the order of 10 Krad/sec. Integrated active RC filters requiring such time constants. take up prohibitively large silicon areas, typically hundreds of times larger than what would be required for SC implementation of these filters.

For sufficiently large op-amp gains. this SC integrator is insensitive to the harmful effects of stray capacitances between various nodes of the circuit and ground. For this reason, this integrator known as LDI bottom plate integrator. has been extensively used in the design of practical SC filters. In the following section the general condition of stray-insensitivity for SC filters will be presented.

## 2.3 Stray-Insensitive Switched-Capacitor Filters

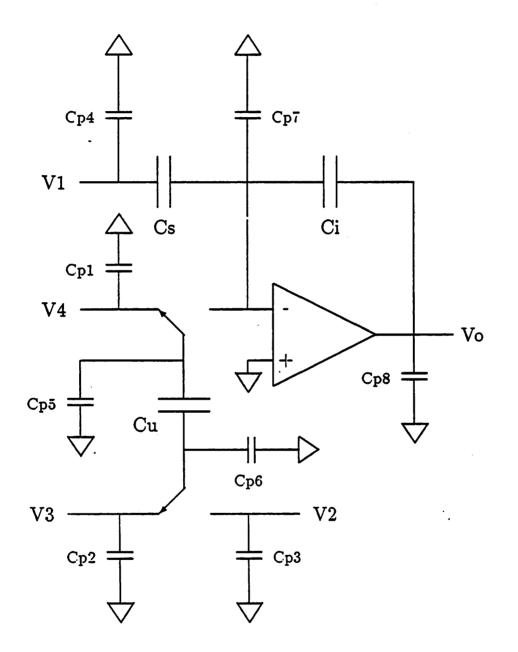

In SC filters. parasitic capacitances exist at every node of the circuit. Each parasitic capacitance affects some performance parameter of the filter. Consider again the SC integrator/summer discussed above, where the parasitic capacitances associated with each node are represented by a single lumped capacitor from that node to the ground (figure 2.3). The parasitics  $C_{p1}, C_{p2}, C_{p3}, C_{p4}$ , and  $C_{p8}$  add to the capacitive loading of the various oper-

Figure 2.3: An integrator/summer with nodal parasitic capacitances.

ational amplifiers. They should be taken into account when designing the op-amps. The parasitics  $C_{p5}$  and  $C_{p6}$  must be included in calculating the RC time constants when designing the switch sizes. Parasitic capacitance  $C_{p7}$  is generally comprised of a component to the negative supply and a component to the positive supply. Therefore, this parasitic is critical in determining the power supply rejection (PSR) of the integrator and hence, that of the entire SC filter.

If the op-amps and switches are designed correctly, the parasitics mentioned so far. except for  $C_{p5}$ , do not affect the fundamental precision of the filter. However, if  $V_4$  is used as an inverting input to the integrator.  $C_{p5}$  is charged in parallel with  $C_s$ , thus changing the gain constant associated with that input. So, it becomes apparent that  $V_4$  should be connected to analog ground if the integrator is to be parasitic-insensitive. In that case,  $C_{p5}$  is switched between analog ground and the virtual ground of the amplifier, and has no effect on the frequency response of the filter. Thus, this integrator becomes to a first order parasitic-insensitive, if  $V_3$  and  $V_2$  are used as the non-inverting and inverting inputs of the integrator, respectively.

In general the stray insensitivity condition for a two phase SC network can be stated as following [26,27]:

The frequency response of a two phase SC filter is to a first order *parasitic-insensitive* if every capacitor terminal is EITHER connected to an input source, op-amp input. op-amp output, or the ground. OR switched between an op-amp input and the ground. an op-amp output and the ground, two op-amp outputs. an op-amp output and an input source. or an input source and the ground.

In the remaining of this chapter, only parasitic-insensitive SC structures will be discussed.

#### 2.4 Design Methods

While a number of design methods such as SC N-path [28] and multiple-loop feedback [29,30] have been reported for SC filters, the majority of practical designs and all of the automatic synthesis tools are based on one of the following two approaches:

- Cascade first and second-order sections (biquads) to obtain the desired filtering function [31.32]. This is the most straight-forward method to apply.

- Design the SC filter based on the doubly-terminated LC ladder network [33.34].

The popularity of cascade design method has been mainly due to the following:

• Any transfer function of the form:

$$H_{c}(s) = \frac{N_{c}(s)}{D_{c}(s)} = \frac{b_{m}s^{m} + b_{m-1}s^{m-1} + \dots + b_{1}s + b_{0}}{s^{n} + a_{n-1}s^{n-1} + \dots + a_{1}s + a_{0}},$$

or

$$H_d(z) = \frac{N_d(z)}{D_d(z)} = \frac{c_m z^m + c_{m-1} z^{m-1} + \dots + c_1 z + c_0}{z^n + d_{n-1} z^{n-1} + \dots + d_1 z + d_0}$$

can be realized as cascade of first and second order sections.

- A large number of easy-to-design-and-tune SC biquad structures have been reported [35.31.32.27]. The majority of these structures are based on the active RC realization of biquads, which have been thoroughly studied in the literature.

- Different biquad sections can be clocked at different rates. Thus, we can make very efficient use of the silicon area by using multiple clock rates [36].

The main drawback of the cascade design approach is that the resulting designs are inherently more sensitive to component variations than are the SC ladder topologies. A well designed SC ladder filter has minimum sensitivity to element variations in the pass-band. In fact, their analog prototypes have zero sensitivity when the power transfer is matched between the source and load. For this reason SC ladder structures are preferred over cascade designs for high order and high Q filters.

The most widely used strategy to derive parasitic-insensitive SC filters from the LC ladder prototypes is based on the simulation of the voltagecurrent relations of the analog filter. These filters can be designed on the basis of simple approximations which are valid for clock frequencies much larger than the fastest fluctuations of the input voltage. In case the deviation of the frequency response from ideal resulting from an approximate design is not acceptable, an exact but more complicated design strategy may be used [37,38,34,39,40]. An alternative approach is to fine-tune the capacitor ratios of the approximate design to meet the desired frequency response. This will be illustrated in the following section.

A systematic procedure for the design of cascaded SC filters has been proposed in [32]. In the following section a step-by-step procedure for the design of parasitic-insensitive SC ladder filters based on the simulation of the voltage-current relations of the analog filter will be presented.

## 2.5 A Synthesis Procedure for SC Ladder Filters

There is a large body of knowledge and experience with passive ladder networks. Thus, it is natural to design SC filters to emulate the behavior of these networks. A method which retains the low-sensitivity properties of ladder networks, is to simulate the voltage-current relations of the passive ladder networks via signal flow graphs. This simulation will result in

SC networks comprising damped and lossless integrator and/or second order resonator sections.

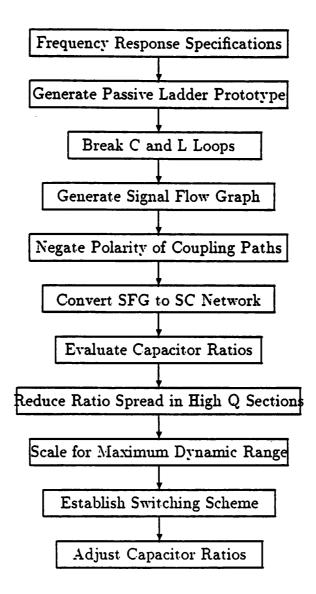

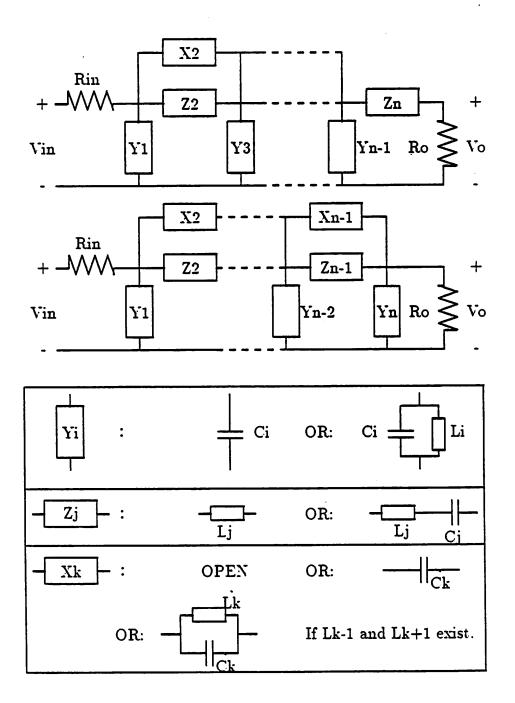

The first step in the synthesis of SC ladder filters (figure 2.4) is to realize the passive ladder network to meet the given frequency response specifications. In this approach, the filter synthesis program Filsyn [41] has been employed for this purpose. Figure 2.5 shows the general form of passive ladder networks transformable to SC ladder filters through the steps outlined in this section. Before mapping the passive ladder into interconnections of integrators, the L and C loops which might exist in the passive filter should be broken. Inductor loops can result in unstable D.C. conditions [24], while breaking the capacitor loops will result in fewer number of op-amps in the SC implementation of the filter [33]. These loops can be broken through the Thevenin equivalent circuit transformations shown in figure 2.6. The transformed network can be realized as a leapfrog interconnection of integrators (figure 2.7). The time constant associated with each integrator is proportional to a corresponding capacitor or inductor value of the transformed passive network. Namely:

$$au_i = RC_i \quad \text{or} \quad au_i = \frac{L_i}{R},$$

where R is a free parameter which is later used to optimize the capacitor ratio spread of the resulting SC filter. The resistive terminations are simulated as feedbacks closing around the integrator whose one input is the input of the filter and the integrator whose output is the output of the filter. The gain constant associated with a resistive termination  $R_t$  has a value of  $\frac{R_t}{R}$  if the integrator corresponds to an inductor or  $\frac{R}{R_t}$  if it corresponds to a capacitor. The voltage-controlled voltage sources are simulated as feed-forward and feedback paths between the integrator outputs. A step whose importance becomes clear shortly, is to negate the polarity of the coupling paths which feed into the outputs of the integrators. This can be easily accomplished by reversing the polarity of every signal coming into and going out of one of the two integrators incident to a coupling path (figure 2.8). This operation does

Figure 2.4: The synthesis steps for SC ladder filters.

Figure 2.5: The general form of passive ladder networks.

٤

Ł

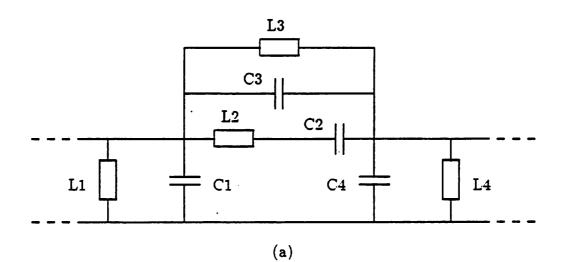

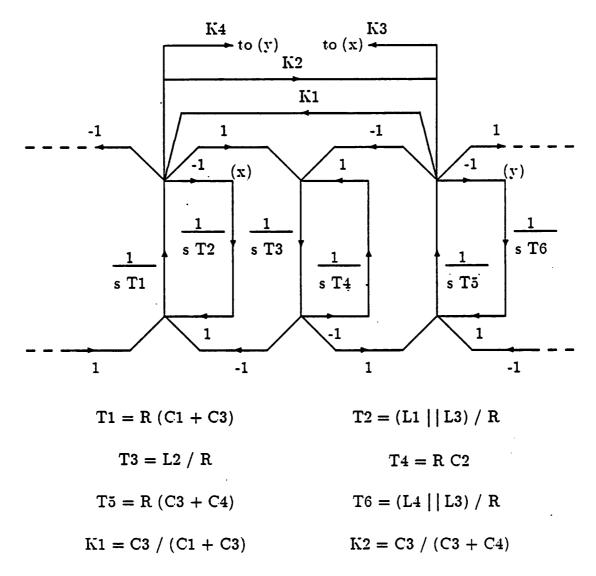

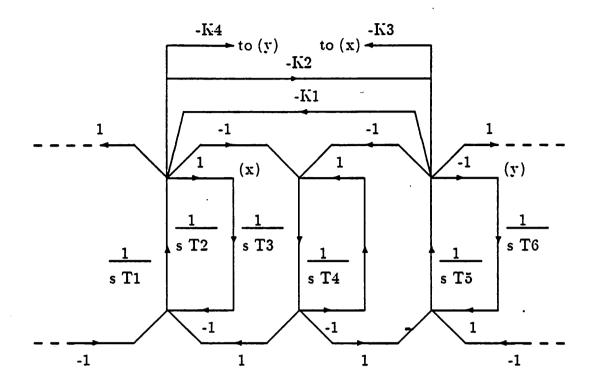

L2C2 + +L1 || L3 -C1 + C3 L4 || L3  $C3 + C4^{-1}$ V1  $\mathbf{V4}$ C3  $V4 \frac{C3}{C1 +}$ L1 L4 $V4 \frac{L1}{L1 + L3}$ V1C3 C3  $L_{4} + L_{3}$ V1C3 + C4 (b)

Figure 2.6: (a) A section of a passive ladder network containing capacitor and inductor loops. (b) Its Thevenin equivalent circuit.

K3 = L1 / (L1 + L3) K4 = L4 / (L4 + L3)

Figure 2.7: A signal flow graph representation of the passive ladder segment of figure 2.6.

Figure 2.8: Changing the polarity of coupling paths.

not change the transfer function of the filter since all the loop gains remain the same.

At this point, the resulting Signal Flow Graph (SFG) can be used to generate an SC ladder filter. This is done by implementing each integrator as an LDI SC integrator/summer discussed previously. All the coupling paths which feed into the outputs of the integrators in the SFG have negative values. Thus, they can be realized via the summing capacitors. Those coupling paths feeding into the input of the integrators can be realized via the sampling capacitors. For a clocking period T, ratios of integrating to sampling capacitors become:

$$\frac{c_{I_i}}{c_{s_i}} = \alpha \frac{\tau_i}{T},$$

where  $\alpha = 1$  if the above ratio doesn't correspond to a resistive feedback path. Otherwise,  $\alpha = \frac{R_t}{R}$  or  $\alpha = \frac{R}{R_t}$  if the integrator emulates an inductor or a capacitor, respectively. The ratio of a summing to an integrating ca-

pacitor is simply the absolute value of the gain constant associated with the corresponding path. There is a degree of freedom in choosing the switching phases. This will be discussed later.

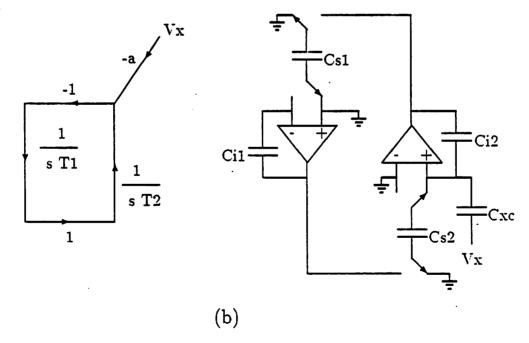

If the filter contains high Q resonator sections, the capacitor ratio spread can be reduced by converting the switched-capacitor inputs of an integrator into continuous couplings at the input of the other integrator of the same resonator [24] (figure 2.9). This transformation is expected to improve the noise performance of the filter by reducing the number of switches in the circuit. One drawback is the settling behavior of the op-amps within the filter becomes more complex as a result of additional continuous coupling paths.

The generated SC filter can now be scaled for maximum dynamic range. The idea behind scaling comes from the following observation:

If all the branches connected to the output of an op-amp in an SC filter are multiplied by some factor  $k_i$ , the output voltage of that opamp is reduced by the same constant factor without affecting any other charges or voltages in the filter.

It has been shown that for maximum dynamic range, all op-amp outputs should be scaled such that each ( at its own maximum frequency ) saturates for the same input voltage level [42]. It should be noted that the logarithmic sensitivity of the filter to element variations remains unchanged by the above scaling operation. Scaling for maximum dynamic range can be performed in the following manner:

- 1. Set the amplitude of the input voltage sweep to the largest value for which the output op-amp does not saturate.

- 2. For each op-amp *i*. excluding the output op-amp, calculate  $V_{i,s}$ , the maximum value of the output voltage over all frequencies. This value usually occurs near a passband edge.

Figure 2.9: Circuit transformation for reducing capacitor ratio spread in high Q resonators. (a) Before transformation. (b) After transformation.

Figure 2.10: The SC integrator of figure 2.2 after scaling for maximum dynamic range.

3. For each op-amp *i* as above, multiply all the capacitors connected or switched to its output by  $k_i = \frac{V_{i,s}}{V_{i,m}}$ , where  $V_{i,m}$  is the saturation voltage of op-amp *i*.

As a result of scaling operation. some integrators might require additional switched capacitors to accommodate different gains for different input polarities (figure 2.10).

At the next step, the value of the impedance scale R is evaluated to minimize the maximum capacitor ratio. Let us assume the set of capacitor ratios related to parameter R are given by:

$$\{ \{\frac{a_i}{R}\}, \{b_j R\} \} \ i = 1, \cdots, n, j = 1, \cdots, m,$$

where  $a_i$ 's and  $b_j$ 's are constant parameters. Then,  $R_{opt}$  the optimum value of R is given by:

$$R_{opt} = \sqrt{\frac{\max_{j \in m}(b_j)}{\max_{i \in n}(a_i)}}.$$

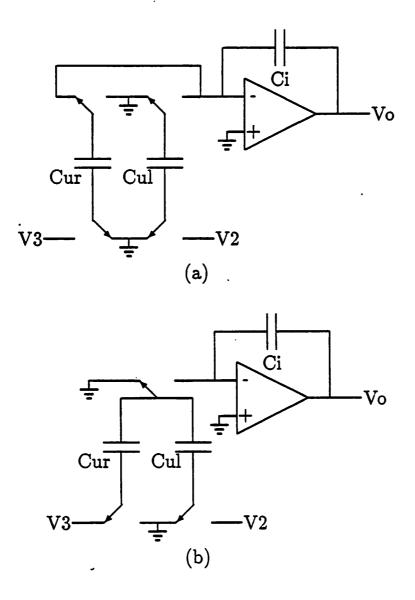

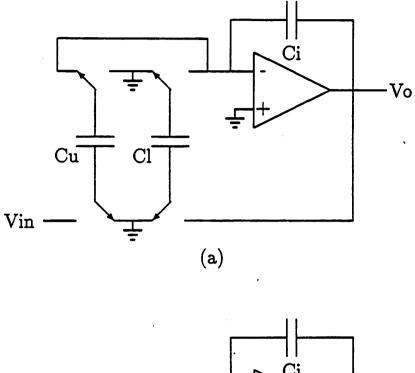

As mentioned before, there is some degree of freedom in choosing the switching scheme. In figure 2.11a. both switched-capacitors  $C_{ur}$  and  $C_{ul}$ implement inverting inputs to the integrator. In figure 2.11b. the clock phases of the top and bottom switches of  $C_{ur}$  have been swapped. so that a single switch can be used at the input of the integrator for both switched capacitors. This reduces the channel charge injection into the input of the integrator. This step does not affect the transfer function of the filter as long as there is no resistive feedback path around the integrator. For damped integrators. the clock phasing determines whether the feedback loop is delay free or it takes a full clock cycle to go around a loop (figure 2.12). Choi [24] has shown that using full delay termination in one end and zero delay at the other end of the SC filter (complex conjugate terminations) can result in better approximation of the desired frequency response. Then, according to the arguments above, the switching scheme should be established for minimum number of switches connected to the input of each amplifier. and if possible, for complex conjugate terminations.

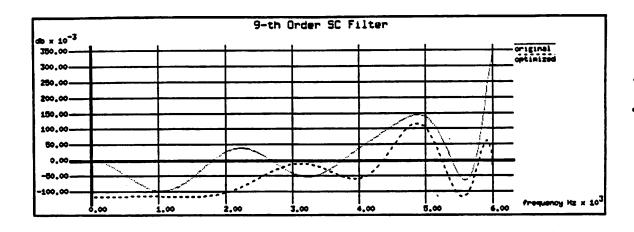

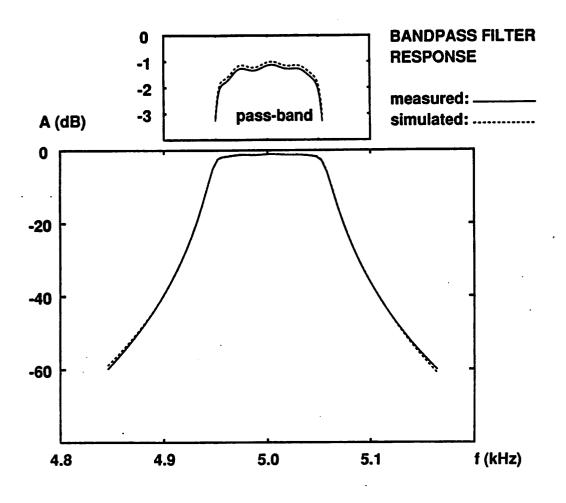

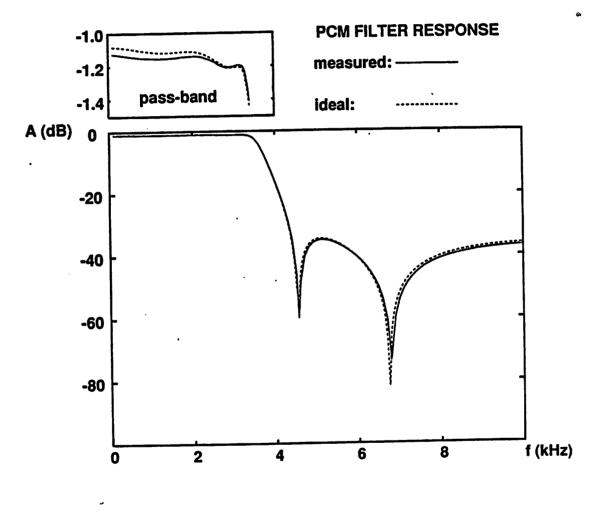

As a result of the approximate nature of the design. the generated SC filter might not meet the frequency response specifications. In order to meet the specifications, the capacitor ratios can be adjusted with the help of mathematical programming techniques [23]. Figure 2.5 shows the effect of optimization on the pass-band response of a ninth order low-pass SC ladder filter designed according to the steps above. The clock frequency is 64 KHz. The specifications require 0.25 dB passband ripple with cut-off frequency at 6 KHz. The bandstop requirement are: -26 dB at 7.5 KHz, -45 dB at 9 KHz. and -80dB at 18 KHz. The approximate design easily met the bandstop specifications. However, the original passband ripple was 0.44 dB which is unacceptable.

The process above has been incorporated into a program for automatic synthesis of SC ladder filters. Other such efforts are described in the next section.

Figure 2.11: Reducing the number of input switches. The circuit of Figure (b) has one less switch than the circuit of Figure (b).

Figure 2.12: (a) Full delay termination. (b) Zero delay termination.

Figure 2.13: Pass-band response of the optimized SC ladder filter.

### 2.6 Review of Automatic Synthesis Systems

The system reported by Eaton [43] is capable of synthesizing parasitic insensitive low-pass SC ladder filters for classical designs (e.g. Butterworth, Chebychev, elliptic, etc.). The generated filters are scaled for maximum dynamic range. In this system there is a choice of either an approximate LDI or an exact [39] design methodology.

The system reported by Assael [44], is capable of synthesizing lowsensitivity low-pass and bandpass SC ladder filters for standard polynomial approximations and also for elliptic filters. The capacitor values are evaluated for maximum dynamic range. An approximate LDI or an exact bilinear designs are possible with this system.

Sanchez-Sinecio [45] reported a program for synthesis of biquad SC filters. The program accepts either a frequency specification. an s-domain transfer function, or a z-domain transfer function for the filter. It permits trade-offs between sensitivity, dynamic range, and total capacitance of the filter.

Another program for synthesis of biquad SC filters has been re-

ported in [46]. The program accepts an amplitude frequency specification for the filter. Then, it evaluates the poles and zeros of the classical type transfer function to meet the desired frequency response. The dynamic range of the filter is optimized by pairing the poles and zeros of the transfer function and ordering of the resulting biquad stages. Finally, the SC filter topology and capacitor ratios are evaluated for each biquad section.

While there is some optimization performed in the reported synthesis systems, there are many more degrees of freedom yet to be explored. An example for this is the optimal choice of the integrating capacitor values. These values affect, among many, the area, noise, and power supply rejection of the filter. An optimal decision requires accurate measures of the performance criteria. This is possible only after a layout is generated for the filter and the parasitics are extracted from it. Then, an optimization step can be used to produce more efficient circuits.

# Chapter 3

# Layout Strategies for Switched-Capacitor Filters

### 3.1 Introduction

The performance of analog ICs depends heavily on fine details of layout. This has been part of the reason why manual layout has been the most time consuming aspect of the design cycle for most analog ICs and in particular SC filters. The development of a number of automatic layout systems for these filters is thus motivated. As it will be discussed later in this chapter. an important shortcoming of earlier systems is that they do not make as efficient use of the area as does manual layout. Area directly translates into cost. and also larger area prevents integration of more functions on the same chip. In order to approach the area efficiency of manual layouts. a strategy with three basic characteristics has been adopted. The heart of this strategy is the use of a layout floor-plan patterned after a style widely used in manual layout of these filters. The second aspect of this strategy is to take advantage of the flexibility inherent in the design of ratio-accurate capacitors to obtain more area efficient layouts. The final aspect is to route all the signals including the sensitive signals automatically to obtain more area-efficiency and extend the capabilities of the system to a larger class of circuits.

This chapter starts with a review of technological considerations for the layout of SC filters. An important decision is the choice between a single-ended or a fully differential architecture. These architectures are introduced and compared in the last part of this section. Previous work in the area of automatic layout of SC filters will be discussed in Section 3.3. The final section describes an automatic layout system based on the approach discussed above. This section starts with introducing the floorplanning strategy. Then the choice of input format is discussed. Finally, the organization of the layout system is presented.

# 3.2 Considerations for the Layout of Switched-Capacitor Filters

#### **3.2.1** Capacitor Ratio Accuracy

To a first order the value of a monolithic MOS capacitor with a rectangular shape of dimensions W and L is given by:

$$C = \frac{\epsilon_0 \epsilon_{or} W^2 L}{t_{or}}.$$

(3.1)

If the variables are statistically independent, then the normalized standard deviation in the capacitor value is

$$\frac{\sigma_C}{C} = \left[ \left( \frac{\sigma_{\epsilon_{ox}}}{\epsilon_{ox}} \right)^2 + \left( \frac{\sigma_{tox}}{t_{ox}} \right)^2 + \left( \frac{\sigma_W}{W} \right)^2 + \left( \frac{\sigma_L}{L} \right)^2 \right]^{\frac{1}{2}} . \quad (3.2)$$

The errors associated with the first two terms of the equation above are referred to as *oxide* effects, and the errors associated with the last two terms are called the *edge* effects. For large capacitors the oxide effects are dominant while for small capacitors, the edge effects are dominant. To avoid systematic errors resulting from process variations and mask moverments, MOS capacitors are often realized as parallel connections of several smaller identical units commonly referred to as "unit-capacitors" [25]. Then, the the ratio

Figure 3.1: Accurate capacitor ratioing.

of the area of the capacitor to the total perimeter of the plate defining the capacitor is constant for each capacitor in the set of ratioed capacitors. This eliminates the effects of systematic errors on the ratio of nearby MOS capacitors having identical unit-capacitors. Then the only remaining sources of error are the random process variations. With this strategy, capacitor ratio-accuracies of the order of 0.1 percent are achievable, even though the absolute values of monolithic capacitors typically vary by  $\pm 20$  percent.

Let us derive a relationship between ratio accuracy and the shape of a unit capacitor. With a procedure similar to the one given in [47] it can be shown that for a  $W \times L \ \mu m^2$  MOS capacitor C, with all the systematic errors reduced to zero, the normalized standard deviation from nominal capacitor value can be given by:

$$\frac{\sigma_C}{C} = \sqrt{K_e \frac{L + W}{L^2 W^2} + K_o \frac{(L + W)^2}{L^2 W^2}} ,$$

where process-dependent, geometry-independent parameters  $K_e$  and  $K_o$  are edge-effect and oxide-effect factors respectively. Now, consider an array of two capacitors  $C_m$  and  $C_n$ , made of parallel connections of m and n identical unit capacitors C, respectively. Let us denote  $r = \frac{C_m}{C_n} \ge 1$  to be the ratio of the two capacitors. Since we have assumed that systematic errors have been reduced to zero,  $C_m$  and  $C_n$  are statistically independent. Then, for small deviations from nominal values we can write:

$$\sigma_r = \frac{m}{n} \sqrt{\left(\frac{\sigma_{C_m}}{C_m}\right)^2 + \left(\frac{\sigma_{C_n}}{C_n}\right)^2}$$

Recognizing that  $C_m = mC$ ,  $\sigma_{C_m}^2 = m\sigma_C^2$ , and similarly for  $C_n$ , we obtain:

$$\sigma_r = \frac{m \, \sigma_C}{n \, C} \, \sqrt{\frac{1}{m} + \frac{1}{n}} \; .$$

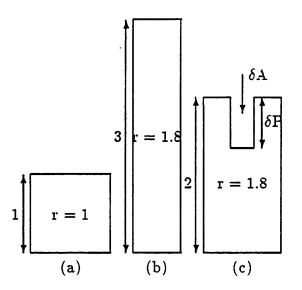

For a given C, the minimum  $\sigma_r$  is achieved when  $L = W = \sqrt{\frac{t_orC}{\epsilon_0\epsilon_{os}}}$  (square geometry). If typical values of  $K_o$  and  $K_e$  are known for a given process, then the size of square unit capacitor to result in a  $\sigma_r$  for a given ratio  $\frac{m}{n}$  can be evaluated. In some cases, the unit capacitor size required to achieve the noise and PSR requirements of the filter is larger than the value determined above. Then, there would be a degree of freedom in choosing the shape of the unit-capacitor to guarantee the same capacitor ratio accuracy. The minimum side dimension of such rectangular unit-capacitors can be evaluated by substituting  $W = \frac{t_{or}C}{\epsilon_0\epsilon_{ox}L}$  in the equations above and solving for the value of L which results in a given  $\sigma_r$ . The layout system to be described, takes advantage of flexible unit-capacitor shapes to obtain more area-efficient layouts.

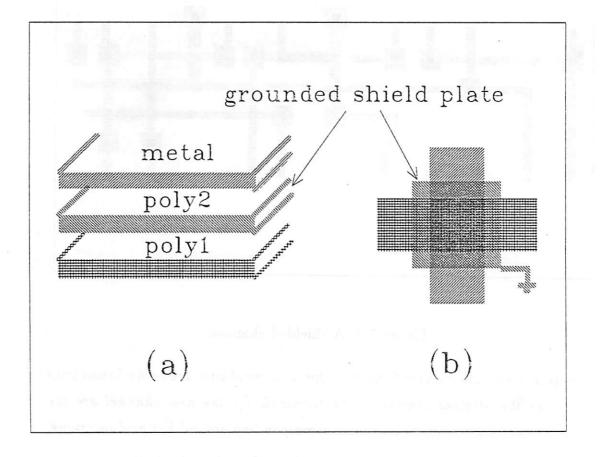

### 3.2.2 Techniques for Improving Power Supply Rejection

As we have seen in the previous chapter, the parasitic capacitance  $C_{p7}$  (figure 2.3) is of critical importance in determining the PSR of an SC filter. To a first order, the ratio of this capacitor to the integrating capacitor determines the low frequency PSR. To minimize the contribution of the capacitors to  $C_{p7}$ , only the top-plates of the capacitors should be connected to the summing nodes of the op-amps. This could also reduce leakage current effects. Another procedure is to place a grounded well under the capacitors to shield the capacitor plates from substrate noise. In order to minimize the contribution of the switches to  $C_{p7}$ , a number of measures can be taken:

- If possible, the interconnect lines which are connected to the summing nodes of the amplifiers should be shielded.

- In CMOS technologies, one should use single-channel switches for the top-plates, and full transmission gates for the bottom plates.

- For each integrator, use only one set of top-plate switches. These switches should be as small as possible.

In some applications such as high Q bandpass filters, the PSR of the filter might be poor even with the above provisions. For them, a fully-differential architecture is desirable. This will be discussed in the next section.

## 3.2.3 Fully-Differential Versus Single-Ended Architectures

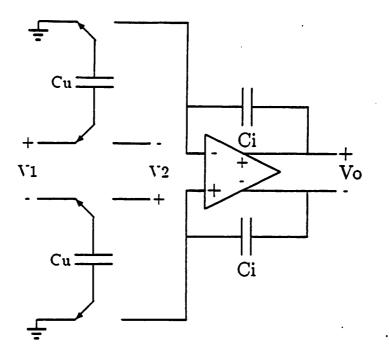

Every SC filter can be implemented in either a single-ended or a fully differential architecture [48,24]. In the latter, the effective signal swing is doubled relative to the former, by the use of a differential output integrator (figure 3.2). In fully-differential architectures, the signals injected due to power supply variations and clock charge injections are greatly reduced due

Figure 3.2: A fully-differential SC integrator.

to balanced signal paths. The disadvantages of fully-differential technique are filter areas are larger than single-ended versions. and differential to single ended conversion is necessary in most applications.

In this section, the requirements for the layout of both architecture are examined. I start by listing the requirements common to both architectures:

- In order for two capacitors to track, their unit-capacitors should be of the same size and shape.

- All the capacitors belonging to the same integrator have to be accurately ratioed with the integrating capacitor of that integrator.

- It is desirable to place the tracking capacitors close to each other to reduce the effects of uniform thickness gradient on matching of capacitors.

- The lower plate of each capacitor must be connected to a voltage source

or switched between voltage sources, so that the nonlinear parasitic capacitance between the lower plate and the substrate does not effect the filter response. Therefore, only the top-plate of each capacitor can be connected or switched to the summing inputs of an op-amp.

Requirements particular to a single-ended architecture are:

- The non-inverting op-amp inputs should be kept at a constant voltage. and cannot be connected to a signal voltage: otherwise, the filter response will be sensitive to the parasitic capacitances associated with the inverting input.

- The parasitics associated with the wiring to summing nodes should be reduced, or if possible, eliminated. These parasitics distort the frequency response. and degrade the power supply rejection and noise of the filter.

Requirements particular to fully-differential architecture are:

- The parasitic capacitances due to switches, bus lines, and substrate connected to the inverting input of each op-amp should match those connected to the non-inverting input of the same op-amp.

- Each pair of differential capacitors should have identical layouts. and should be placed close to each other.

- In a truly differential architecture, the layout should be insensitive to mask movements: namely, a pair of differential elements. should have identical layouts in lieu of mask movements.

We conclude that the constraints on signal routing are very different for the two architectures. It will be shown later that it is possible to obtain area-efficient layouts with good performance for single-ended filters by using standard routing tools: however, this is not the case for fully-differential architectures. For these architectures. new routing tools are needed to maximize the symmetry of the differential signals while minimizing the routing area. To take advantage of existing routing tools. we placed our initial effort on generating layouts for single-ended architectures. the subject of the remaining of this thesis.

# 3.3 Systems for Automatic Layout of Switched-Capacitor Filters

A number of automatic layout systems for switched-capacitor filters have been described previously.

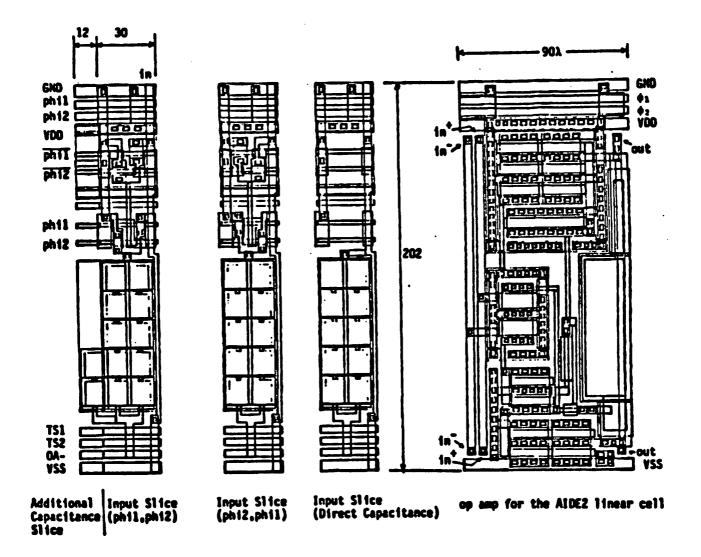

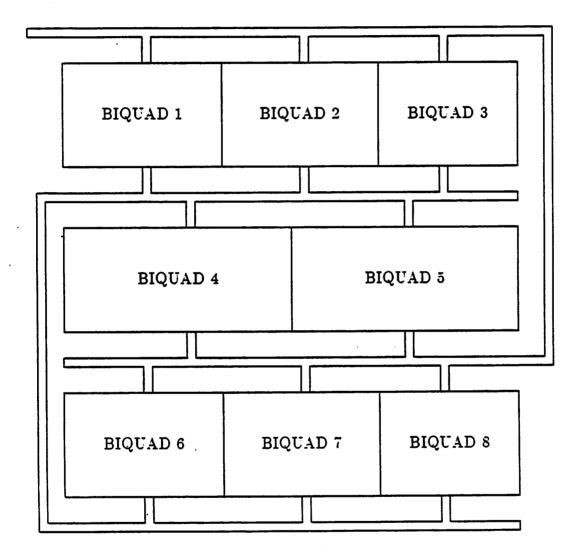

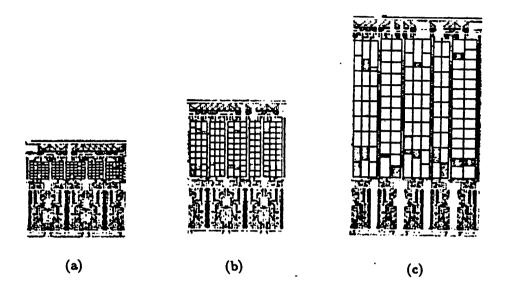

Allen [6] reported the first system for automatic layout of SC filter. This system uses a standard-cell layout scheme for placing and routing fixed height bi-quad sections to generate the filter layout (figure 3.3). Each parameterized bi-quad section is made up of two op-amp sections. cascaded with a number of capacitor tile sections. In this approach, the summing node connections (sensitive signals) are hidden inside the bi-quad sections to ease the task of placement and routing. An important shortcoming of this and other similar parameterized bi-quad/integrator layout approaches is that they do not make as efficient use of the silicon area as does manual layout. This is partly due to the semi-rigid structure of the bi-quad sections which leaves only few parameters adjustable for area optimization, and also due to the large area used up by signal bussing. Another characteristics is the use of a large number of leaf cells which must be regenerated for each new technology.

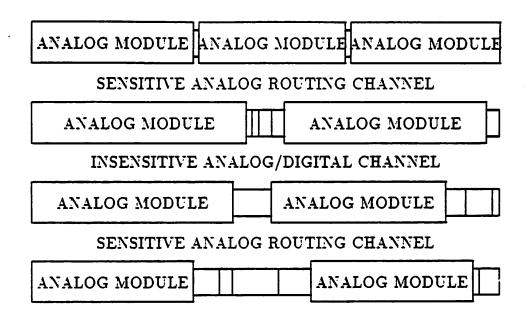

In the analog standard cell system reported by Kimble [8] the signals are routed in alternating sensitive and insensitive channels (Figure 3.4). In this system the channel router routes certain classes of nets before others to achieve higher performance.

In the system reported by Pletersek [49], the signals are routed in

Figure 3.3: Parameterized bi-quadratic structure reported in [6]

44

Figure 3.4: Standard-cell layout scheme reported in [8]

separate analog and digital channels to reduce the cross-talk between analog and digital signals (figure 3.5). The sensitive signals are hidden inside predesigned bi-quad sections. These sections are blocks of fixed height with variable widths depending on the total number of unit-capacitors associated with that block. This is another example of parameterized bi-quad approach.

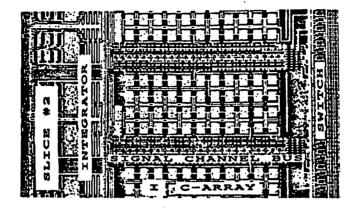

In the gate-array style strategy reported by Sigg [50], the capacitor top-plate as well as the interconnection masks are automatically generated for an otherwise pre-designed array of integrators (figure 3.6). While the fabrication turn-around time for generated filters is short, the gate-array nature of the system results in very large areas as compared to manual layouts.

In summary the above systems have one or more of the following limitations:

- The area of a generated filter is much larger than that of a compact custom layout of the same filter in the same technology.

- The system is designed around one technology or. if it is technology

Figure 3.5: Standard-cell layout scheme reported in [49]

Figure 3.6: Gate-array style layout scheme reported in [50] independent adopting the system to a new technology requires a large effort.

• The system works only with a library of elements specifically designed for it.

In the next section, our layout strategy for a technology-and-topologyindependent system capable of producing area efficient layouts will be presented.

# 3.4 A New Approach to Automatic Layout of Switched-Capacitor Filters

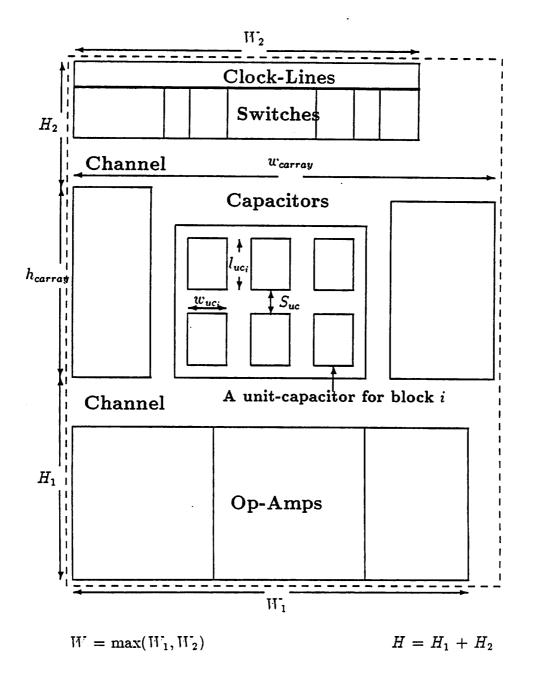

#### 3.4.1 Floor-planning strategy

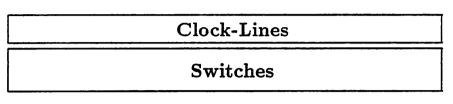

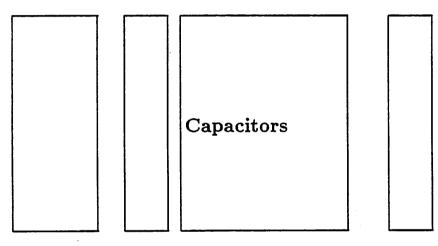

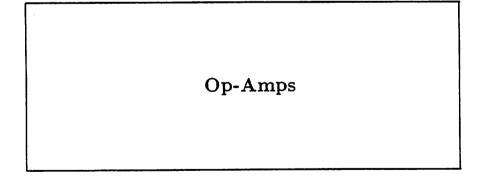

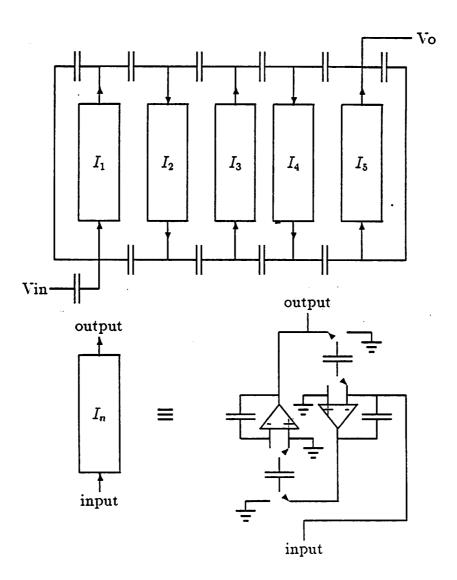

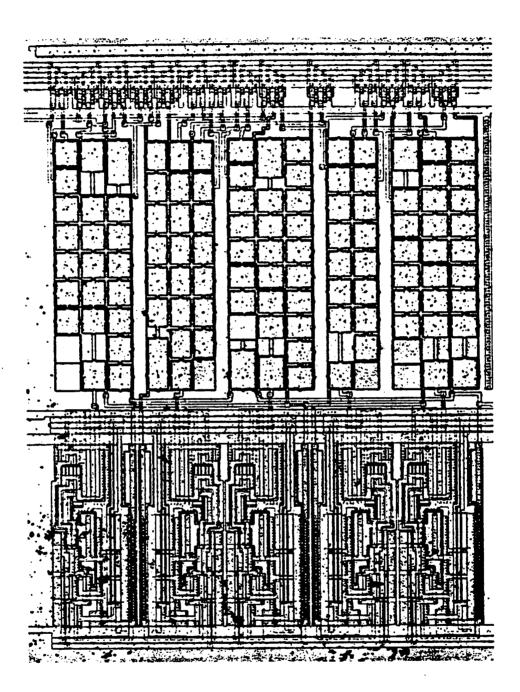

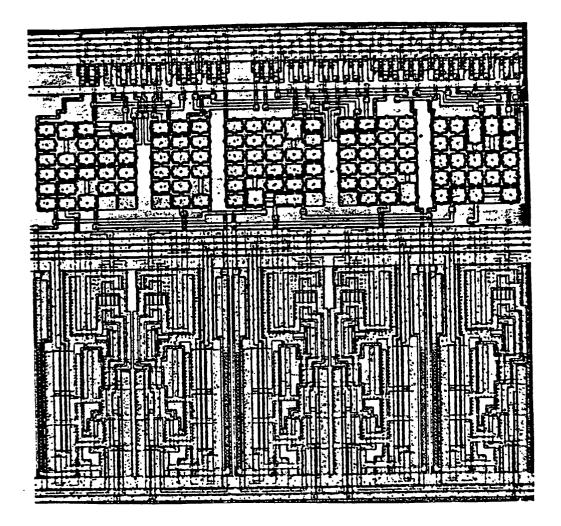

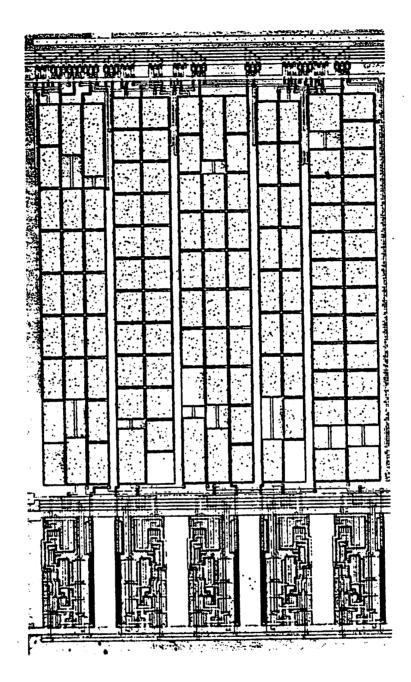

The basic floor-plan consists of an array of capacitors located in between an array of operational amplifiers and an array of switches (Figure 3.7). This arrangement of operational amplifiers and switches is guided by

## Top Routing Channel

**Bottom Routing Channel**

Figure 3.7: The Floor-Planning Strategy.

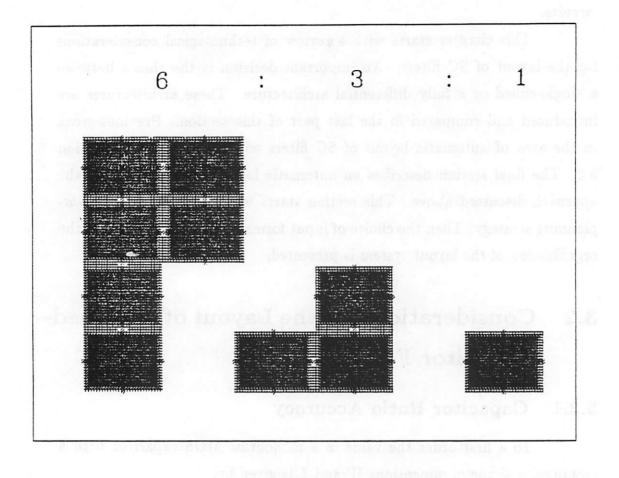

the bus sharing of the modules in their respective arrays. Each set of capacitors belonging to the same integrator makes up one capacitor block. The capacitors in the same block have identical unit capacitors; however, unit capacitors of different capacitor blocks need not be identical. The size of the unit-capacitor for each block is that of the smallest capacitor in that block. While the unit-capacitor area is constant, its aspect ratio can be manipulated to obtain more compact layouts.

The signals are routed in two channels, one between the capacitor blocks and operational amplifiers (op-amp channel), and another between the switches and capacitor blocks (switch channel). The spacing between capacitor blocks are used as route-through channels for connections between the op-amp and switch channels. Both terminals of each capacitor directly connected to the input of an op-amp are incident to the op-amp channel. Similarly, both terminals of each capacitor switched to the the input of an op-amp are incident to the switch channel. The clock lines run above the switches away from switch channel.

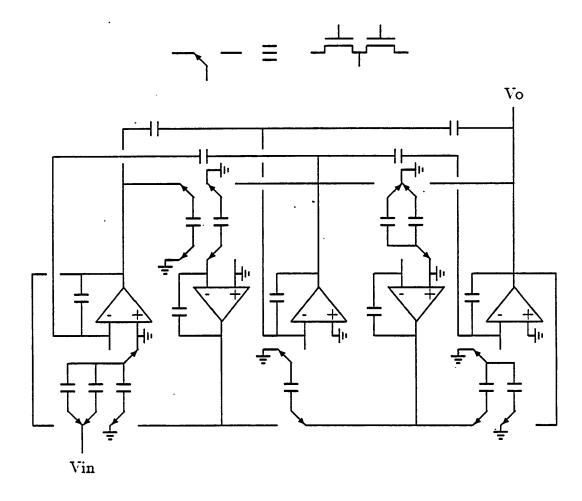

The op-amps can be chosen from any standard cell library, as long as all the op-amps used in the same layout have the same height, share the same busses, and have input and output terminals on the same side. These conditions are not restrictive since a large number of industrial opamps used in SC applications are designed in this manner. The switches also have the same height, but possibly variable widths. Each switch should have on one side terminals connecting to the clock lines, and on the other side terminals connecting to op-amps or capacitors. Generation of compact layouts, entirely from the individual transistor dimensions and spacing rules, for these switches is possible because of their simple structures. An example of a scalable double-throw CMOS switch is shown in figure 3.8.

This floor-planning strategy serves many purposes:

• By using a channel router, and capacitor and switch generators. the entire layout of a filter, except for the op-amps, can be generated from

#### Figure 3.8: An example of a scalable switch.

connectivity information, spacing rules, and capacitor and switch sizes.

- Any circuit comprising switches, capacitors and op-amps, with any number of clock phasings can be implemented in this floor-planning style.

- The routing area, and the quality of routing can be optimized by ordering modules in their respective arrays.

- The degrees of freedom in the layout of capacitor blocks can be utilized to obtain more compact layouts.

- By proper design of the capacitor blocks, the capacitor top-plates which belong to the same net can be shared inside the capacitor block. This reduces the number of sensitive signals in each channel.

- The clock lines are separated from analog signal lines to reduce the coupling of digital and analog signals.

• Since the capacitors and most of the routing areas are separated from the switches and op-amps. a grounded well can be placed under the capacitors and large area of the routing channels to isolate the capacitor plates and most of the signal lines from substrate noise.

To utilize effectively this floor-planning strategy, we had to solve many problems, including the generation of capacitor blocks to meet the floor-planning strategy, and ordering the modules to reduce area and improve performance. These are the topics of Chapters 4 and 5.

#### 3.4.2 The Input Format

The system requires the following information for layout compilation:

- A SPICE-like input file for describing the circuit connectivity, capacitor values, switch sizes and library pointers.

- A file for specifying various technology dependent information such as spacing rules.

- The bounding box and terminal locations for each library element specified in the circuit file.

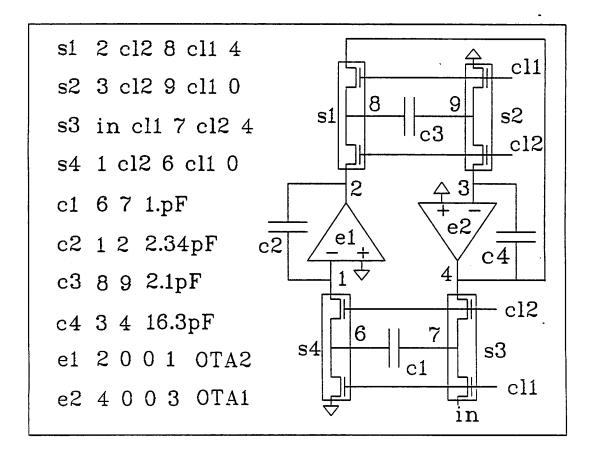

The format of the circuit file, which resembles that of SPICE [51], was chosen for simplicity. ease of use. and generality. Each element in the circuit is specified by an element card that contains the element name, the circuit nodes to which the element is connected, and parameter value(s) or library pointer for the circuit element. Nodes are name or number fields, and the datum (ground) node must be numbered zero (0). The first letter of the element specifies the element type. There are five types of elements allowed in the circuit file: capacitors. op-amps, switches, input elements, and output elements. The input and output elements specify respectively the input and

Figure 3.9: An example of a circuit file.

output nets of the filter. An example of a circuit file for a second order filter is shown in figure 3.9.

Since the system is designed to be technology independent, it requires new information for every new technology. A set of generic layers and design rule parameters have been defined to allow for various possibilities in generating layouts for the capacitors. switches, and generating the wiring. The mapping of technology parameters to this set is possible through the technology file.

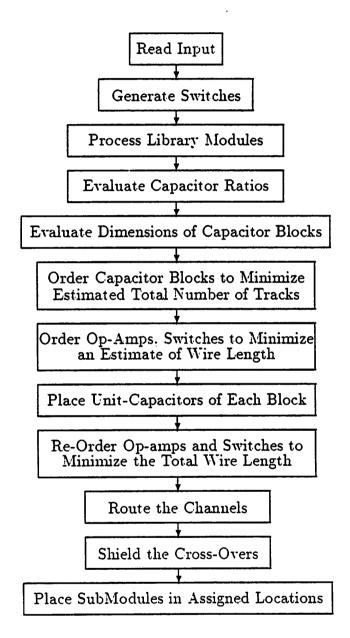

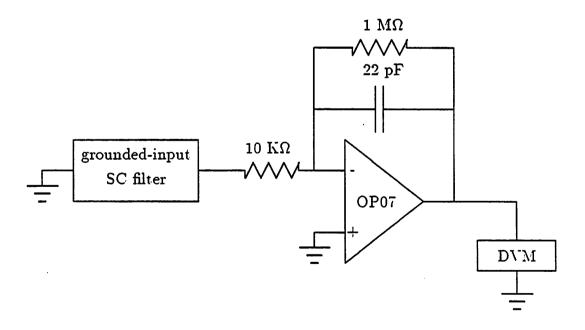

#### 3.4.3 Flow of the System

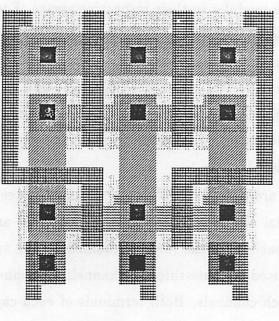

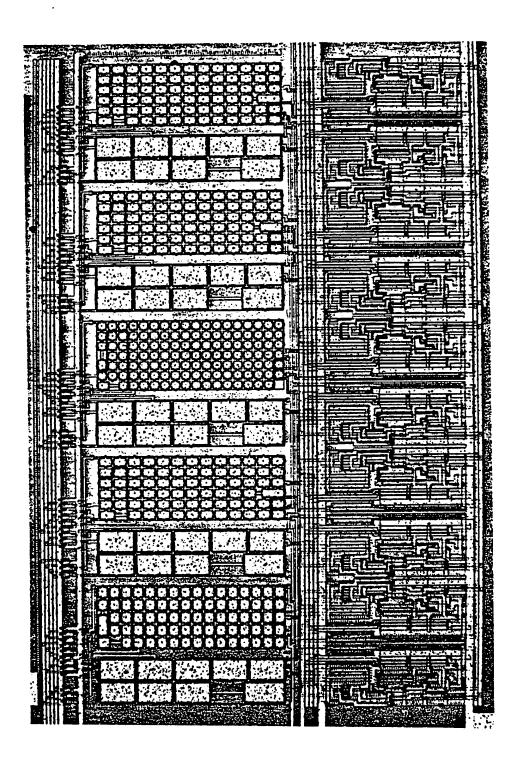

The system goes through several optimization stages, as shown in figure 3.10, before producing the final mask layout. The program starts with processing the input information. In the circuit file the capacitor nodes are not yet committed to be the top-plate or the bottom-plate. This is because such information is automatically extracted from circuit connectivity. The capacitor top-plate is designated to be the node directly connected or switched to an input of an op-amp. The bottom-plate is the node directly connected or switched to an output of an op-amp or a voltage source. All the capacitors with top-plates associated with the same op-amp input are assigned to the same integrating block. For each capacitor in an integrating block the ratio of its value to that of the smallest capacitor in the block is evaluated. Then, the size of the unit-capacitor for each integrating block is that of the smallest capacitor in the block. If no library names are specified for the switches. the layout for each unspecified switch is generated from technology information and the switch sizes. N-channel double throw switches are generated for those connecting the top-plates of the switched capacitors to the summing nodes of the op-amps or to the ground. Complementary double throw switches are generated for all other ones.

The capacitor arrays are generated in three stages. In the first stage the aspect ratio of the unit capacitors and the number of unit capacitors

Figure 3.10: The organization of the layout system.

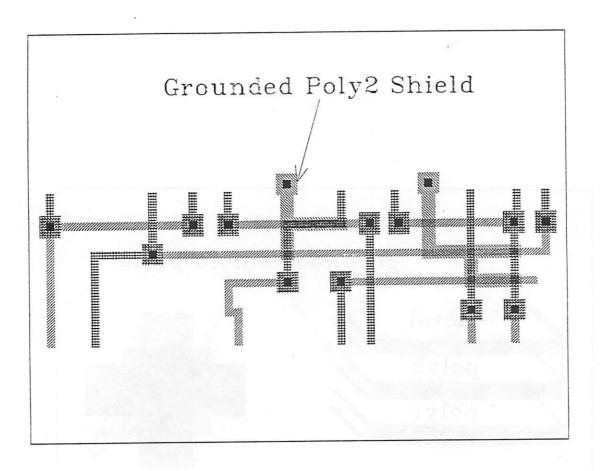

in the x and y directions for each capacitor block are evaluated in such a way to minimize an estimate of the total area of the filter. In the second stage, a symbolic representation for each capacitor block showing the relative positions of unit capacitors belonging to that block is produced. In the third stage a layout for each capacitor block is generated. There are several ordering steps to minimize the maximum density of each channel, as well as to minimize an estimate of the overall wiring length. An optional postrouting step is available to shield the cross-overs between summing nodes of the operational amplifiers and the large signal nets. The generated layout is stored in Oct [5]. In the next two chapters the algorithmic details of this system will be presented.

# Chapter 4

# **Generation of Capacitor Arrays**

### 4.1 Introduction

Design of compact high-accuracy array of capacitors is an error prone and laborious process even for moderate size SC filters. To meet the requirements of the floor planning, we developed algorithms to generate compact arrays of fixed area/perimeter ratio capacitors.

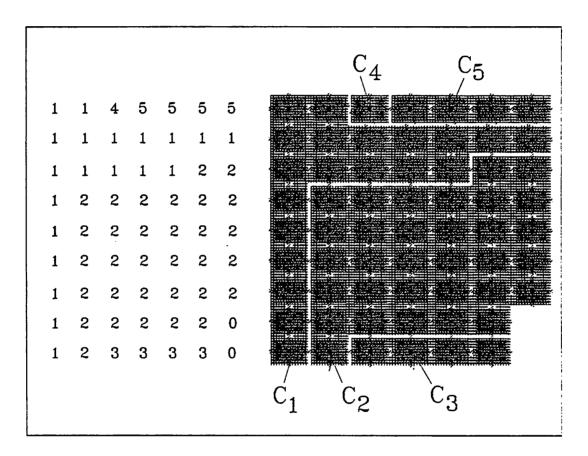

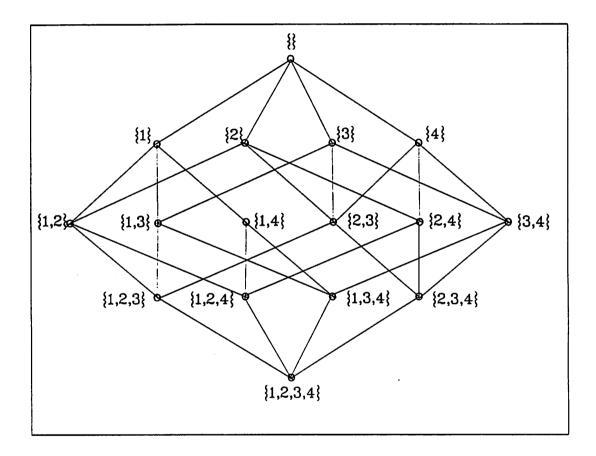

Generation of capacitor arrays is performed in three stages. In the first stage, the dimensions of each capacitor block and the shape of its unit capacitors are evaluated to minimize the overall area of the filter. In the second stage, for each capacitor block, a symbolic matrix showing the relative positions of unit capacitors of each capacitor in the block is generated. In the third stage, a spacer program converts the symbolic matrix generated for each block into a layout for the given design rules and evaluated unit capacitor dimensions. This method is general enough to be used in almost any other floor-planning style for SC filters or other applications requiring highly ratio-accurate capacitor blocks with flexible aspect ratios.

In Section 4.2, the algorithms for evaluating the optimum capacitor block dimensions are presented and then analyzed. Section 4.3 deals with the algorithms developed for symbolic matrix generation. In Section 4.4, the steps involved in converting the symbolic information into mask layout are studied. A solution to generating area/perimeter constant geometries for fractional capacitors is presented in the final section.

### 4.2 Evaluation of Block Dimensions

#### 4.2.1 Problem Formulation

A capacitor block i can be perceived as an  $n_{y_i} \times n_{x_i}$  matrix of interconnected unit-capacitors. For each capacitor block i,  $n_{x_i}$  and  $n_{y_i}$  should be large enough for the capacitor block to accommodate all of the unitcapacitors of all its capacitors. Since in our layout strategy, each capacitor is required to have at least one unit-capacitor either on top or at the bottom of its capacitor block, the minimum number of columns required for capacitor block i is  $\max(N_{tc_i}, N_{bc_i})$ , where  $N_{tc_i}$  and  $N_{bc_i}$  are the number of capacitors with connections on top and the number of capacitors with connections at the bottom of block *i*, respectively. As long as the above restrictions are satisfied. one is free to choose the number of rows and columns of each capacitor block. Another degree of freedom is the ability to choose the aspect ratio of the unitcapacitor for each capacitor block. As it has been discussed in Section 3.2. the aspect ratio of a fixed-area rectangular unit-capacitor affects only the capacitor ratio-accuracy. The aspect ratio can therefore take on a range of values. as long as the given capacitor ratio accuracy is maintained. Our goal is to minimize the area of the filter defined by its bounding box (Figure 4.1) by taking advantage of the degrees of freedom described above. To formulate the problem, the following definitions are required:

$N_b$  = number of capacitor blocks.

$w_{uc_i}$  = unit capacitor width for block *i*.

$l_{uc_i}$  = unit capacitor length for block *i*.

$n_{x_i}$  = number of unit capacitors in the x direction for block i,

Figure 4.1: A geometric example for Problem 4.1. The bounding box of the filter is shown in dashed lines. A capacitor block has been expanded to show more detail.

$n_{y_i}$  = number of unit capacitors in the y direction for block i,

$N_{tc_i}$  = number of capacitors with connections on top of block i,

$N_{bc_i}$  = number of capacitors with connections at the bottom of block *i*.

$N_{uc_i}$  = total number of unit capacitors for block i,

$A_{u_i}$  = area of unit capacitor for block *i*,

$S_{uc}$  = spacing between two adjacent unit capacitors.

$W_{min}$  = minimum allowable unit capacitor width,

$L_{min}$  = minimum allowable unit capacitor length.

W = the larger of the widths of op-amp array and switch array,

- H =sum of the height of the switch array, the height of the op-amp array and estimate of the heights of the two channels,

- $S_{caps}$  = sum of the separations of capacitor blocks required for route through channels.

Given these definitions, the height of the capacitor array, which is the height of the tallest capacitor block, can be written as:

$$h_{carray} = \max_{i} (n_{y_i} \ (l_{uc_i} + S_{uc})). \tag{4.1}$$

and its width can be written as:

$$w_{carray} = S_{caps} + \sum_{i=1}^{N_b} n_{x_i} (w_{uc_i} + S_{uc}).$$

(4.2)

The relation between  $n_{x_i}$  and  $n_{y_i}$ , and also between  $w_{uc_i}$  and  $l_{uc_i}$  are given by:

$$n_{y_i} = \left[\frac{N_{uc_i}}{n_{x_i}}\right] \qquad i = 1, \dots, N_b, \tag{4.3}$$

$$l_{uc_i} = \frac{A_{u_i}}{w_{uc_i}}$$

$i = 1, \dots, N_b.$  (4.4)

Now we can formulate the following constrained optimization problem:

Problem 4.1 (Find-Dimensions) Minimize:

$$(H + h_{carray})\max(W.w_{carray})$$

(4.5)

subject to:

$$W_{min} \le w_{uc_i} \le \frac{A_{u_i}}{L_{min}} \qquad \qquad i = 1, \dots, N_b.$$

$$(4.6)$$

$$\max(N_{tc_i}, N_{bc_i}) \le n_{x_i} \le N_{uc_i} \qquad i = 1, \dots, N_b.$$

$$(4.7)$$

In the equations above, the technology-dependent parameters  $L_{min}$ and  $W_{min}$  set the bounds on permissible unit capacitor aspect ratios. The space of the above problem is  $2N_b$  dimensional. A vector in the solution space is:

$$\vec{x} = (n_{x_1}, \ldots, n_{x_{N_b}}, w_{uc_1}, \ldots, w_{uc_{N_b}})^T.$$

Since the  $n_{x_i}$ 's and  $n_{y_i}$ 's can take on integer values only, the above problem cannot be solved via optimization algorithms which assume the continuity of the function to be optimized. Although integer programming techniques can be used, due to the intrinsic complexity of these algorithms, it would take too much time to find an optimum solution. Thus, I will present a heuristic algorithm that is not guaranteed to find an optimum solution, but finds an excellent ones in a fairly large set of test problems.

#### 4.2.2 Algorithmic Solution

I start by presenting an efficient algorithm for finding the solution of the problem above for the case where the variables accept a continuous range of values. Then the only change in the problem formulation is the relation between  $n_{x_i}$  and  $n_{y_i}$  as shown below:

$$n_{y_i} = \frac{N_{uc_i}}{n_{x_i}}$$

$i = 1, \dots, N_b.$  (4.8)

Here, I present a gradient-free algorithm based on some properties of this continuous optimization problem. These properties will be presented in the form of theorems and lemmas. Lemma 4.1 states that if the upper bound on the value of  $w_{carray}$  is less than W, then the problem has a trivial solution. Moreover, if this upper bound is greater than W, then according to Theorem 4.1, the optimal width of the capacitor array will also be greater than W. These properties will enable us to solve the problem by systematically solving a system of  $N_b$  disjoint two dimensional optimization problems. A similar method will then be introduced which finds very good solutions for the original form of Problem 4.1.

Now, I present the properties of the continuous optimization problem. In the following, assume  $\bar{x}^0 \doteq (n_{x_1}^0, \dots, n_{x_{N_b}}^0, w_{uc_1}^0, \dots, w_{uc_{N_b}}^0)^T$  solves Problem 4.1.

Lemma 4.1 If

$$\sum_{i=1}^{N_b} N_{uc_i} \left( \frac{A_{u_i}}{L_{min}} + S_{uc} \right) \le W - S_{caps}$$

(4.9)

the, for  $i = 1, ..., N_b$ ,

$$n_{x_i}^0 = N_{uc_i}, \quad w_{uc_i}^0 = \frac{A_{u_i}}{L_{min}}.$$

(4.10)

**Proof:** As a result of the condition of Equation 4.9, the objective becomes the minimization of  $h_{carray}$ , which is at its minimum when  $n_{x_i}$  and  $w_{uc_i}$  assume their maximum values.

The following lemma is required in the proof of Theorem 4.1:

Lemma 4.2 The height of the capacitor array is bounded below by:

$$h_{carray} \ge L_{min} + S_{uc}, \tag{4.11}$$

with the equality satisfied if and only if. for  $i = 1, \ldots, N_b$ .

$$n_{x_i} = N_{uc_i}, \quad w_{uc_i} = \frac{A_{u_i}}{L_{min}}.$$

(4.12)

The proof is clear from the definition of  $h_{carray}$ .

#### Theorem 4.1 If

$$\sum_{i=1}^{N_b} N_{uc_i} \left( \frac{A_{u_i}}{L_{min}} + S_{uc} \right) \ge W - S_{caps}.$$

(4.13)