## Copyright © 1988, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# HIGH PERFORMANCE PROGRAMMABLE DSP ARCHITECTURES

by

Mordechay Toma Ilovich

Memorandum No. UCB/ERL M88/31

20 May 1988

# HIGH PERFORMANCE PROGRAMMABLE DSP ARCHITECTURES

by

Mordechay Toma Ilovich

Memorandum No. UCB/ERL M88/31

20 May 1988

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## HIGH PERFORMANCE PROGRAMMABLE DSP ARCHITECTURES

by

Mordechay Toma Ilovich

Memorandum No. UCB/ERL M88/31 20 May 1988

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## High Performance Programmable DSP architectures

### Mordechay Toma Ilovich

#### **ABSTRACT**

The large increase in the complexity of computations and the processing speed requirements of digital signal processing applications require us to implement high-throughput processing elements (PEs) which can also be used to implement high performance multiprocessing systems.

In this thesis we propose and explore many of the design aspects of a new PE architecture that is suitable for inclusion in multiprocessing systems. It incorporates on the same chip a processing unit (PU) and an autonomous interprocessor communication unit (AIO). Concurrently with the PU that executes the task's computations, the AIO handles and controls the data transfer between the PEs. The AIO operates as 1) an interface between the PU and the network and 2) an intermediate network switch to transfer data between PEs. To avoid network congestion and to achieve a high throughput, the use of virtual-cut-through (VCT) switching and an acknowledgement handshaking protocol is proposed. Four I/O links enables the PE to be embedded in any network with a topology consistent with this number of links, and provides the capability to expand to large multiprocessing configurations. The proposed PE might be build as catalog parts for building multiprocessor signal processing systems. Alternatively, the basic AIO unit might be designed as a macrocell to be incorporated into ASIC (Application Specific IC) implementations. Each AIO can be coupled with a different PU design to yield heterogeneous multiprocessor systems. Further, the communication configuration of the AIO can be parameterized in the macrocell and configured to suit each potential application.

Although DSPs that possess special signal processing features are fabricated in small feature size technologies, their throughput is limited by clock skew problems, limiting their usefulness for some real time applications. To overcome this clock skewing problem, an asynchronous processor architecture is proposed. In an asynchronous processor, no clock is required since the functional blocks are built of asynchronous circuits that communicate through asynchronous interconnection handshake blocks. In the asynchronous processor, the execution time of each instruction is data and instruction dependent, and therefore the "average" throughput will also increase.

When clock skewing is insignificant but the throughput of a synchronous processor is limited because of a large variation in instruction execution time due to data dependency, we propose a GSLA (Globally Synchronous Locally Asynchronous) architecture. This architecture incorporates a clock with a variable duty-cycle. The functional blocks signal the control unit upon the completion of their task and the control unit varies the clock's duty cycle to start a new task. The design principles developed in this thesis should be useful for the development of many general-purpose and special-purpose multiprocessor architectures in the future.

David G. Messerschmitt

avid Mersenchuld

Chairman of committee

#### **ACKNOWLEDGEMENT**

I would like to express my appreciation to my advisor Prof. D.G. Messerschmitt for his guidance, help and support throughout my study. Special thanks and appreciation to Prof. J. Walrand who advised and helped me all the time and was a member of my committee. I wish also to extend my appreciation to Prof. C. Stone, a member of my committee, Prof. R. Katz, a member of my committee, and to Prof. E.A. Lee for some interesting discussions.

Many thanks to my fellow graduate students, T. Meng, K.K. Parhi, V.K. Madisetti and W.H. Ho for the interesting discussions. Special thanks to my friend T.M. Chen for reading and commenting my draft and for our interesting discussions.

This dissertation is dedicated with all my love to my wife Hana and our children Yaron, Yuval and Yoav. Their love, help, encouragement, support, persistence and understanding were indispensable. Their role in my studies are as great as my own.

I also like to thank my parents Mr. and Mrs. Ilovich, my parents in law Mr. and Mrs. Melinarzevitz, my brother Mr. E. Ilovich and his family and our close friend Dr. B. Landkof and his family for their overseas help and encouragement.

This research was supported by grants from NSF and SRC.

### **Table of Contents**

| Abstract                               | 1  |

|----------------------------------------|----|

| Acknowledgement                        | i  |

| Table of Contents                      | ii |

| CHAPTER 1: Introduction                | 1  |

| CHAPTER 2: Multiprocessing DSP         | 5  |

| 2.1 Introduction                       | 5  |

| 2.2 Multiprocessor interconnection     | 8  |

| 2.2.1 Butterfly Parallel Processor     | 8  |

| 2.2.2 Cm* multi-microprocessor         | 9  |

| 2.2.3 The Connection Machine           | 10 |

| 2.2.4 Transputer                       | 11 |

| 2.2.5 NCUBE                            | 11 |

| 2.2.6 Summary                          | 12 |

| 2.3 Proposed Processing Element (PE)   | 12 |

| 2.3.1 Design approach                  | 12 |

| 2.3.2 Data transfer between PEs        | 19 |

| 2.4 Summary of PE's properties         | 23 |

| Reference                              | 24 |

| CHAPTER 3: Communication and protocols | 29 |

| 3.1 Introduction                       | 29 |

| 3.2 Data transfer techniques        | 31 |

|-------------------------------------|----|

| 3.2.1 Communication modes           | 31 |

| 3.2.2 Data transfer techniques      | 31 |

| 3.2.3 Clock synchronization         | 36 |

| 3.2.4 Virtual-cut-through switching | 39 |

| 3.2.5 Data broadcast                | 47 |

| 3.2.6 Design choice                 | 50 |

| 3.3 Interconnection protocols       | 51 |

| 3.3.1 Introduction                  | 51 |

| 3.3.2 PE-PE communication           | 52 |

| 3.3.2.1 Data transfer principles    | 52 |

| 3.3.2.2 Data transfer protocol      | 52 |

| 3.3.3 AIO-PU communication          | 58 |

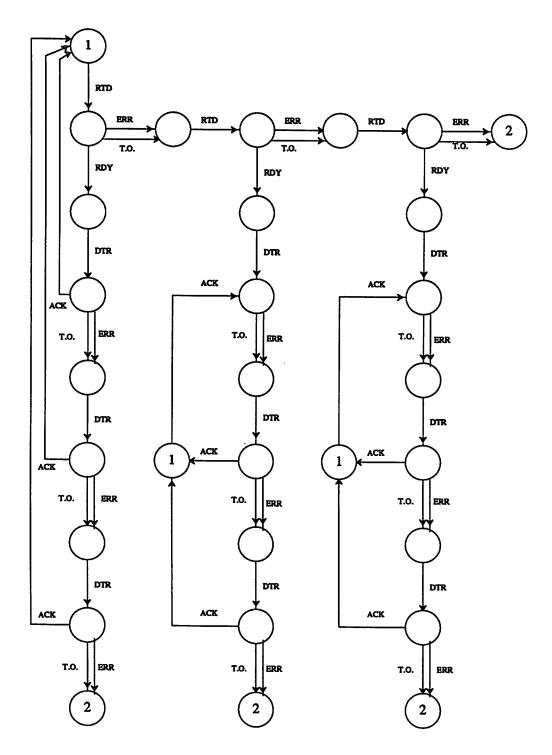

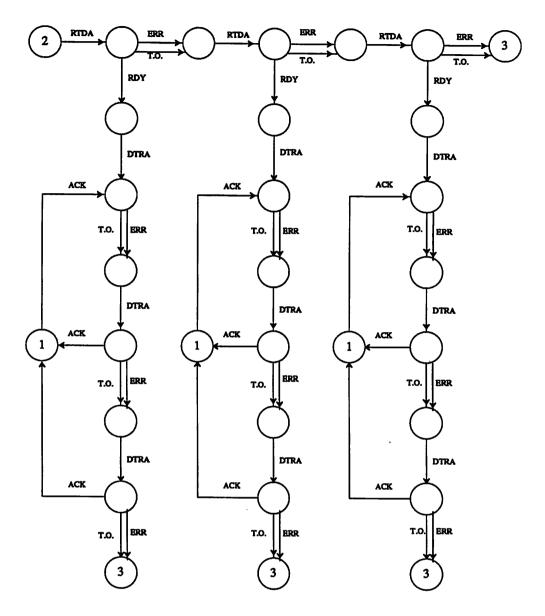

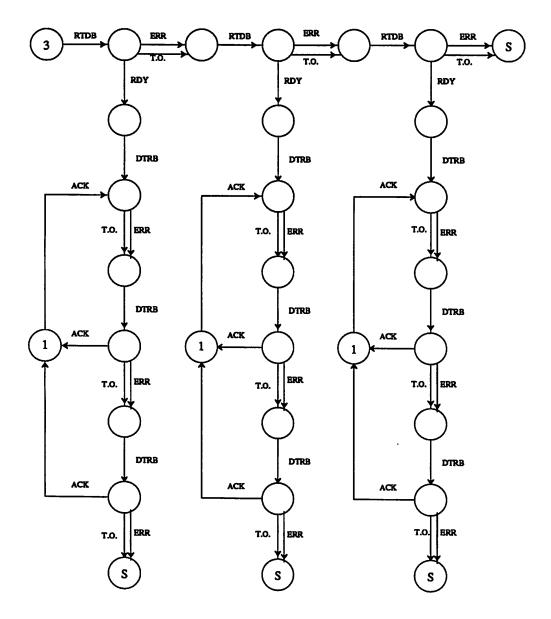

| 3.3.4 Protocol verification         | 60 |

| 3.3.5 Fault tolerance               | 66 |

| 3.3.6 Flow control                  | 68 |

| 3.4 Protocol formats                | 68 |

| 3.4.1 Message formats               | 69 |

| 3.4.2 Short header                  | 75 |

| 3.5 I/O configurations              | 76 |

| 3.5.1 Number of I/O links           | 76 |

| 3.5.2 I/O configurations            | 77 |

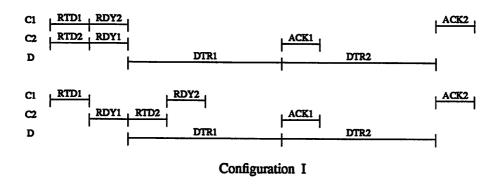

| 3.5.3 Configuration I               | 77 |

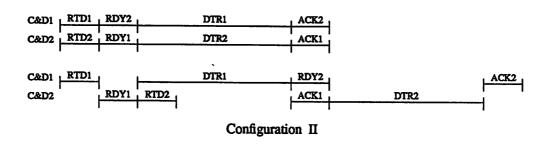

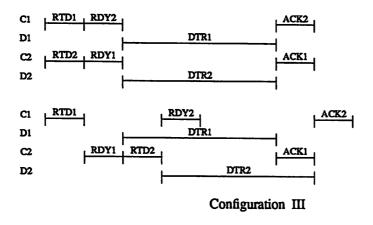

| 3.5.4 Configuration II              | 82 |

| 3.5.5 Configuration III                            | 85  |

|----------------------------------------------------|-----|

| 3.5.6 Summary of I/O link configurations           | 87  |

| Reference                                          | 88  |

| CHAPTER 4: Hardware implementation and performance | 91  |

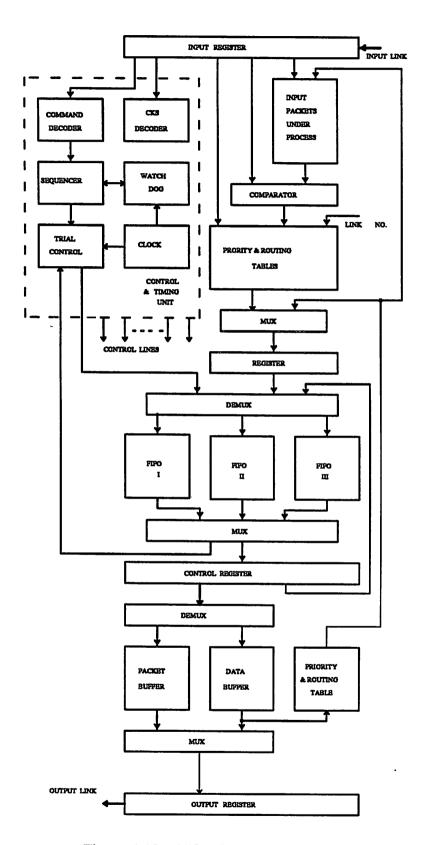

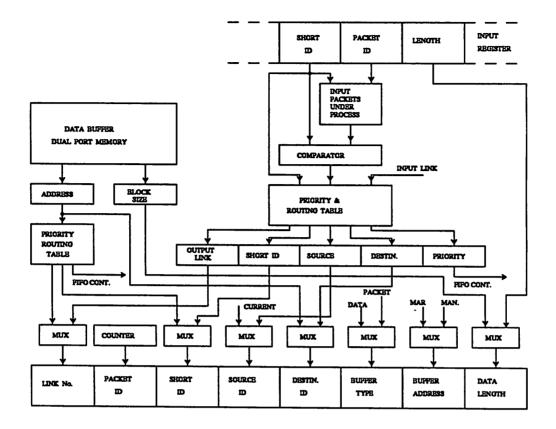

| 4.1 General description                            | 91  |

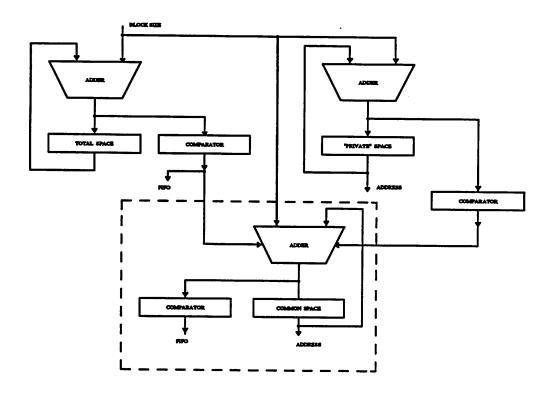

| 4.2 PE's buffers                                   | 96  |

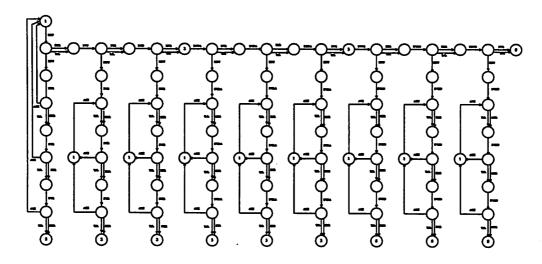

| 4.2.1 Buffer implementation                        | 96  |

| 4.2.2 Buffer size analysis                         | 100 |

| 4.3 Buffer control & bookkeeping                   | 105 |

| 4.4 Communication control                          | 110 |

| 4.4.1 Input packets under process (IPUP)           | 113 |

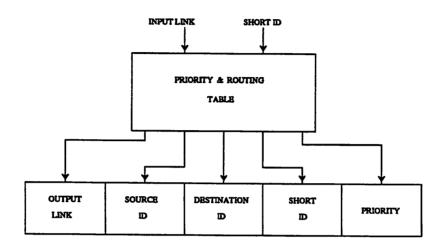

| 4.4.2 Priority & routing tables                    | 113 |

| 4.4.3 FIFOs                                        | 115 |

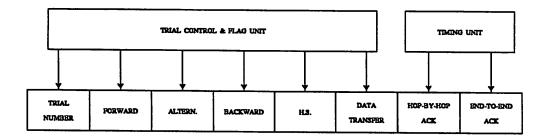

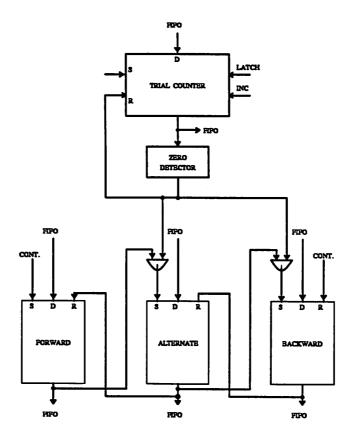

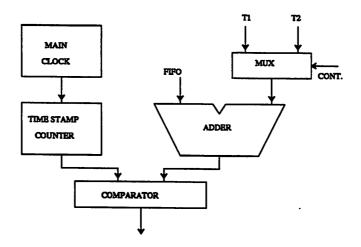

| 4.4.4 Control and timing unit                      | 118 |

| 4.5 ASIC properties                                | 122 |

| 4.6 I/O link's utilization                         | 123 |

| 4.7 PE's performance                               | 125 |

| 4.7.1 Multiprocessor performance                   | 125 |

| 4.7.2 Motorola 56000                               | 128 |

| 4.7.3 Transputer                                   | 134 |

| 4.7.4 Proposed PE                                  | 135 |

| 4.7.5 Performance comparison                       | 137 |

| 4.8 PE's properties - summary                      | 138 |

| Reference                                          | 139 |

| CHAPTER 5: Asynchronous Processor's Concepts & Analysis   | 141 |

|-----------------------------------------------------------|-----|

| 5.1 Introduction                                          | 141 |

| 5.2 Asynchronous design approach                          | 142 |

| 5.3 Data path cycle time comparison                       | 147 |

| 5.3.1 Introduction                                        | 147 |

| 5.3.2 Data path timing model                              | 147 |

| 5.3.3 Synchronous & asynchronous cycle time models        | 149 |

| 5.3.4 Worst case cycle time analysis                      | 154 |

| 5.3.5 Average cycle time analysis                         | 157 |

| 5.4 Conclusions                                           | 163 |

| Reference                                                 | 164 |

| CHAPTER 6: Asynchronous Processor Architectures           | 167 |

| 6.1 Asynchronous pipeline architecture                    | 167 |

| 6.1.1 Introduction                                        | 167 |

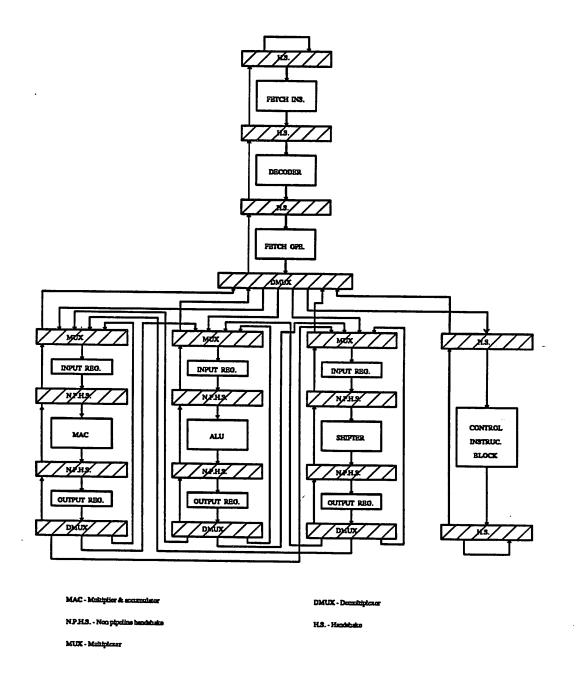

| 6.1.2 Design approach & principles                        | 168 |

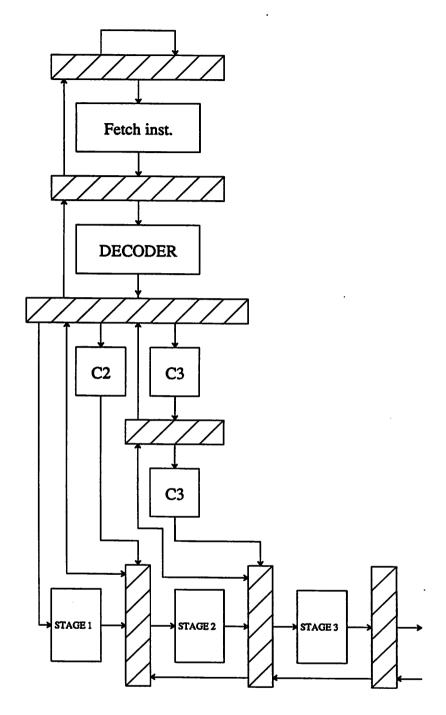

| 6.1.2.1 Fetch instruction                                 | 174 |

| 6.1.2.2 Decoder                                           | 176 |

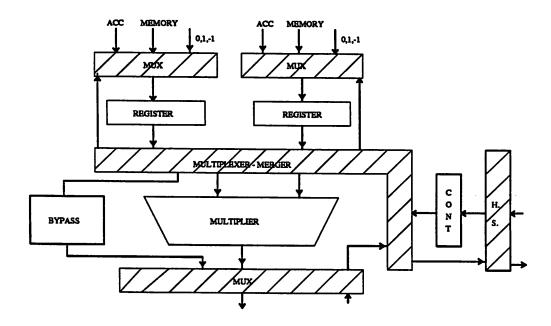

| 6.1.2.3 Multiplier                                        | 184 |

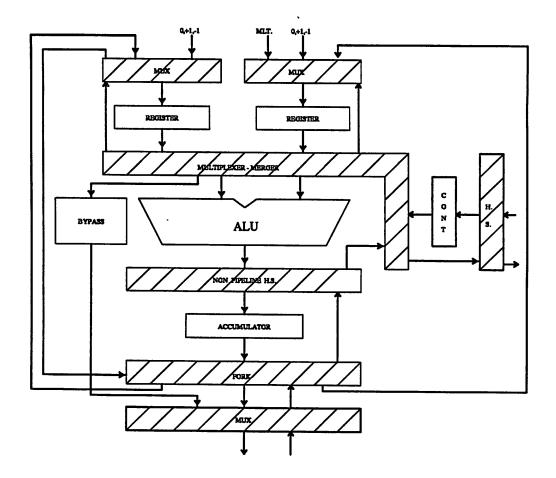

| 6.1.2.4 ALU                                               | 185 |

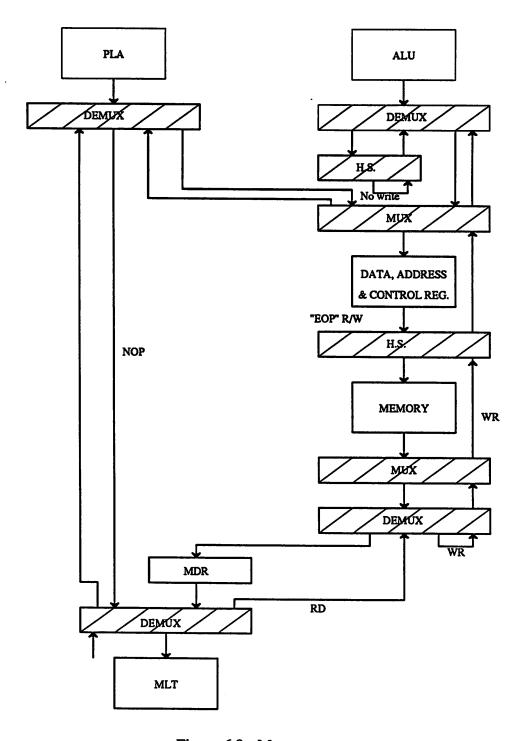

| 6.1.2.5 Data memory access                                | 186 |

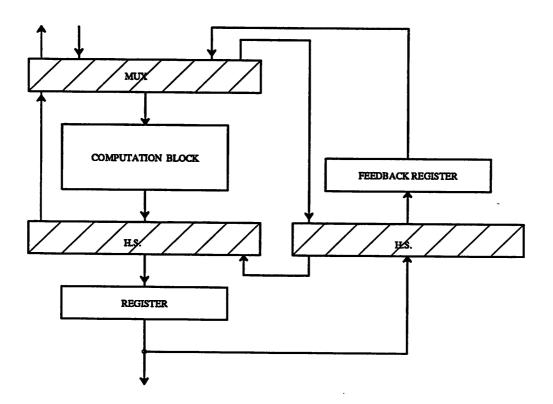

| 6.1.2.6 Feedback                                          | 189 |

| 6.1.2.7 "ASIC" - Application specific integrated circuits |     |

|                                                           | 190 |

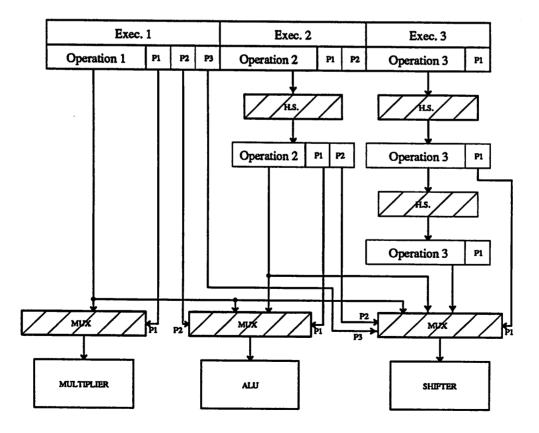

| 6.2 "Hybrid" pipeline architecture                        | 191 |

| 6.2.1 Introduction                                                  | 191 |

|---------------------------------------------------------------------|-----|

| 6.2.2 Methods of operation                                          | 192 |

| 6.2.2.1 "Hybrid" - "RISC" type architecture                         | 193 |

| 6.2.2.2 "Hybrid" - modified pipeline architecture                   | 195 |

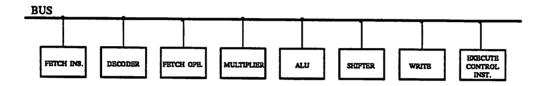

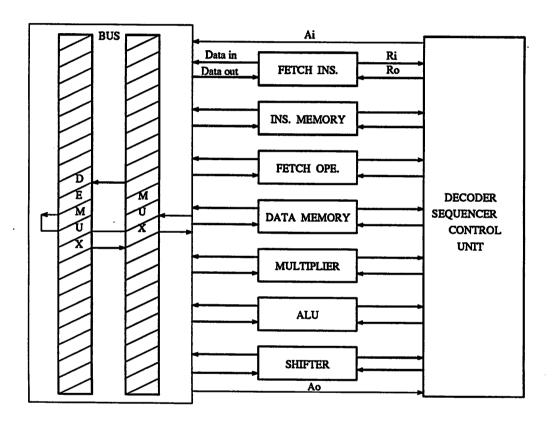

| 6.3 Common bus asynchronous architecture                            | 206 |

| 6.3.1 Introduction                                                  | 206 |

| 6.3.2 Asynchronous common-bus design approach                       | 208 |

| 6.3.3 Asynchronous common-bus implementation                        | 209 |

| 6.3.3.1 "NOFT" design approach                                      | 210 |

| 6.3.3.2 Bypass design approach                                      | 211 |

| 6.3.3.3 Results                                                     | 215 |

| Reference                                                           | 216 |

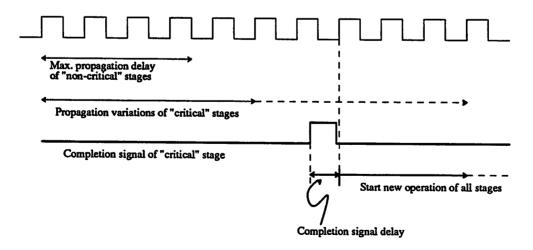

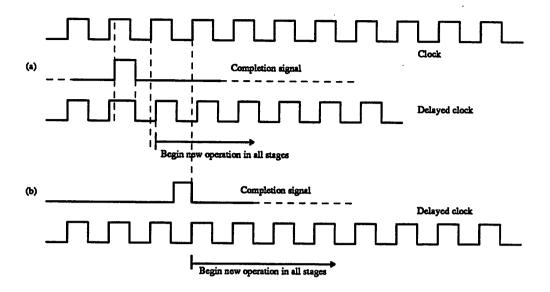

| CHAPTER 7: GSLA - Globally Synchronous Locally Asynchronous Proces- |     |

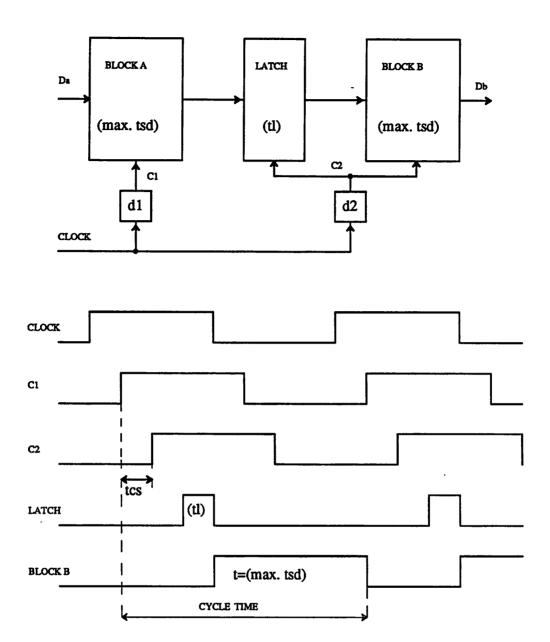

| sor                                                                 | 217 |

| 7.1 Introduction                                                    | 217 |

| 7.2 Clock skew delay's reduction methods                            | 218 |

| 7.3 GSLA implementation                                             | 219 |

| 7.4 GSLA timing analysis                                            | 222 |

| 7.5 Conclusions                                                     | 226 |

| CHAPTER 8: Conclusions                                              | 227 |

| 8.1 Multiprocessing PE                                              | 227 |

| 8.2 Asynchronous PE                                                 | 228 |

| 8.3 Further research                                                | 230 |

### **CHAPTER 1**

### Introduction

#### 1. Introduction

Digital signal processing algorithms are used in a large variety of applications, including image processing, speech processing, sonar and radar systems, biomedical and geophysical (seismic) systems, artificial intelligence, and weather prediction. These applications involve a a large amount of data and computations and require fast computation and high throughput (computation rate).

Most signal processing algorithms are repetitive and allow a high degree of parallelism. These algorithms include complex computations such as transform techniques, convolution/correlation filtering and matrix operations. Transform type techniques include DFT (discrete fourier transform), FFT (fast fourier transform), discrete cosine transform, Karhunen-Loeve transform, Walsh-Hadamard transform, and so on. Filtering types include FIR, IIR, 1-D and 2-D convolution and correlation, 1-D and 2-D interpolation and resampling, linear phase filters: low-pass high-pass and band-pass, Wiener and Kalman filtering, adaptive filtering, window filtering (rectangular, Gaussian, Hamming), differential filtering (gradient, Laplacian), etc.. Matrix operations include matrix multiplication, matrix triangularization (QR decomposition), matrix inversion, singular value decomposition (SVD), eigenvalue computation, solution of Toeplitz linear systems, etc..

The large increase in the complexity of computations, processing speed requirements and the volume of data handled in these applications makes it important to Chapter 1 - 2 -

implement architectures that will increase the computation rate of real-time digital signal processing. The availability of low-cost, high-density, high-speed very large scale integration (VLSI) devices and the emerging of computer-aided design (CAD) facilities enable us to design fast processing elements and high performance multiprocessing systems. This dissertation's main objective is to propose new architectures for processing elements that increase the throughput of a single DSP (digital signal processor) and allow highly concurrent processing systems. The dissertation contains two themes. The first theme investigates and describes an architecture of a processing element which increases the throughput of a multiprocessing systems. The second theme investigates and describes various asynchronous processor architectures which overcome clock skewing problems.

The large degree of parallelism inherent in digital signal processing algorithms and the large amount of data and computations involved in them, suggests the partitioning of computations onto a large number of processing elements. Such multiprocessing architectures typically waste computation time on interprocessor communication, which limits the speedup and the throughput obtained by N processors operating concurrently and transferring data among themselves.

To overcome the communication latencies and the wasted computational time, a processing element (PE) which incorporates on the same chip a processing unit (PU) and an autonomous interprocessor communication unit (AIO) is proposed. Concurrently with the PU that executes the task's computations, the AIO handles and controls the data transfer between the PEs. The AIO operates as 1) an interface between the PU and the network and 2) an intermediate network switch to transfer data between PEs. Operating as an intermediate network switch enables the PE to be embedded in any multiprocessing configuration.

Chapter two describes different existing multiprocessing systems, the proposed

**Chapter 1** - 3 -

PE, and its operation. Chapter three describes the techniques and modes of PE-PE communication, the interconnection protocols and the different I/O configurations. Chapter four has a detailed description of the hardware implementation, including a multiprocessor performance analysis and a performance comparison between the proposed PE and existing DSPs.

Current DSPs possess special features which make them very effective for digital signal processing. Among them are:

- multiplier which can also multiply and accumulate in one cycle.

- ALU with pre- and post-shifting capabilities useful for scaling operands and results.

- address computation unit which allow to pipelining of address calculations

with data path operations.

- A Harvard architecture, which means separate memories for data, program and coefficients, and facilitates parallel prefetching of data and instructions.

- multiple buses to increase the bandwidth of data/instruction transfers.

Although the existing DSPs, fabricated in a small feature size technologies (0.8-2 micron), possess these special features, their throughput is limited by clock skewing problems and they are not adequate to be embedded effectively in a multiprocessing system implementation.

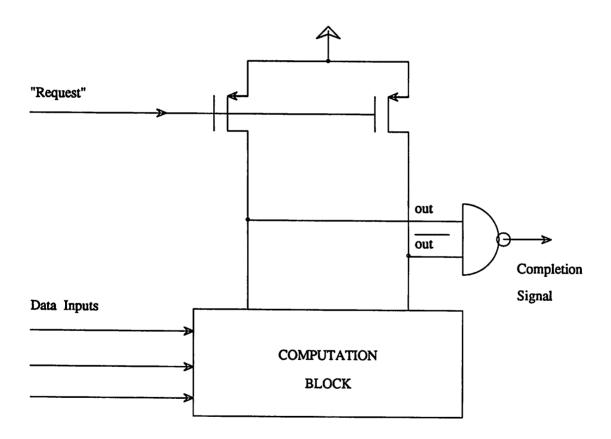

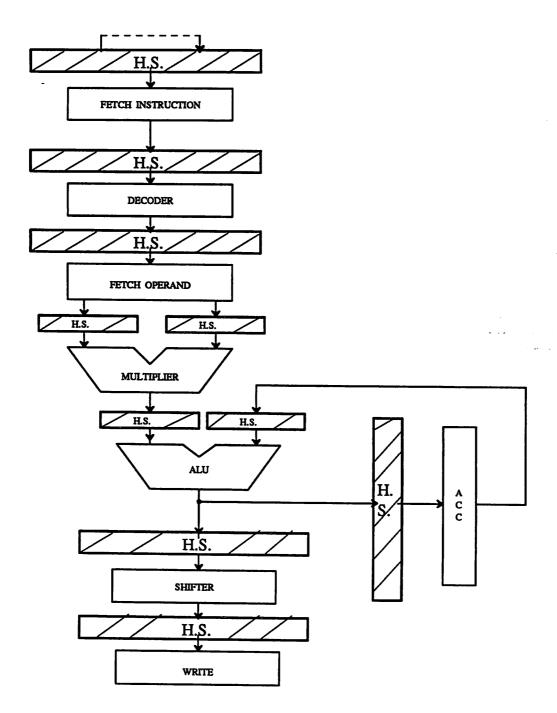

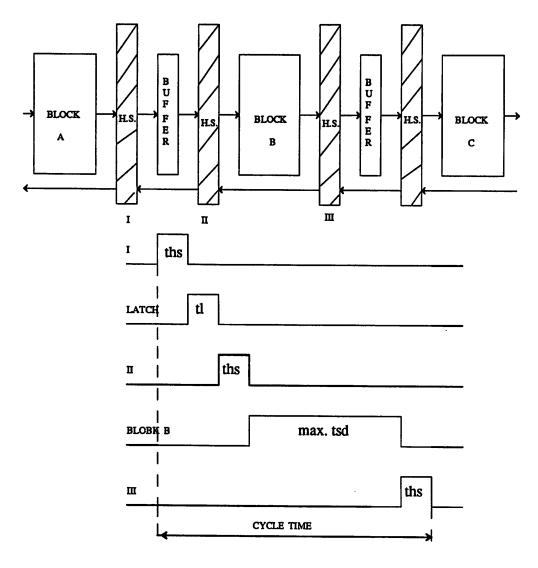

To overcome the clock skewing problem an asynchronous processor architecture is proposed. In designing and implementing an asynchronous processor architecture, no clock is required since the functional blocks are built of asynchronous circuits that communicate through interconnection handshaking blocks. The communication is done by handshaking at the completion of each task. Such an synchronous design eliminates limitations on the throughput imposed by use of a clock, the throughput should therefore increase as the logic speed increases. In the asynchronous processor, the execution

Chapter 1 - 4 -

time of the circuit implementation is data and instruction dependent, and therefore the "average" throughput of an asynchronous processor will also increase.

Chapter five introduces the design of an asynchronous processor. A timing analysis is performed to obtain the conditions on handshaking and clock skew delays such that the asynchronous architecture yields a higher throughput. Chapter six proposes different asynchronous architectures and their implementation.

If and when the clock skewing problems due to IC design and fabrication are solved, the major advantage of the asynchronous architecture diminishes. However, the large variation in the execution time due to data dependency still exists. To overcome this problem in the synchronous processor implementation, a new architecture named GSLA (Globally Synchronous Locally Asynchronous) is proposed in chapter seven. This architecture incorporates a clock with a duty-cycle that can be varied by the control unit. Functional blocks, which due to data dependency have a large execution time variation, signal the control unit upon completion of their task. The completion signals allow the control unit to vary the clock's duty cycle, thus allowing the initiation of a new task.

The last chapter (chapter eight) has conclusions and suggestions for further work and research.

### **CHAPTER 2**

### **Multiprocessing DSP**

#### 2.1. Introduction

Algorithms and programs for real-time signal processing (e.g., tracking radar, sonar systems, image processing and multi-sensor navigation systems), artificial intelligence, weather prediction, biomedical and geophysical applications [1] inherently have a large degree of parallelism. They usually involve a large amount of data and computations (e.g., matrix manipulations - multiplications, inverse, correlations and convolutions) and require fast computation and high throughput (high computation rate). One way to implement this class of algorithms is with a multiprocessor architecture [2, 3, 4, 5, 6, 7, 8]. But multiprocessor architectures have computation latencies which limit the maximum speedup and throughput obtained by N processors operating concurrently with data transfer between them. The speedup and the throughput are limited by:

- 1) Idle time due to imperfect processor load balancing.

- 2) Communication latencies:

- Waiting time caused by long routes and contention for links data has to pass along too many links from the source processor to the destination processor.

- Time required to handle and control the data transfer.

- Processor's computation time wasted on interprocessor communication.

Effective exploitation of the algorithmic parallelism, as well as short paths for data

Chapter 2

transfer are essential to achieve a large computational speed-up. Effective use of multiprocessor system depends upon intelligent schedulers and compilers which either partition the algorithm according to the number of PEs and their interconnection topology, or partition the algorithm and determine the number of the PEs and their interconnection topology [9, 10]. Partitioning the algorithm into many tasks and assigning them to different processors should attempt to:

- Minimize the number of the interprocessor data transfer communications.

- Keep the communications localized (short routes).

- Reduce the delays of data transfer between the PEs.

- Improve the processors load balance to reduce the idle times of the processors.

In general, the scheduling problem is NP complete; the scheduling algorithms therefore use heuristics which do not necessarily yield an optimal partitioning with respect to localization and minimal interprocessor communication. Even more, depending on the algorithm, sometimes optimal partitioning may not be good enough, therefore, the interprocessor communication hardware and protocols are vital for achieving a high computing throughput.

An independent interprocessor communication unit designed to handle and control the data transfer between processors, in parallel and concurrently with the computations, relieves the processor from wasting time on interprocessor communication and reduces the time required for data transfers.

Depending on the algorithm and the number of processors, there are two ways to implement the data transfer interconnections between the processors of a multiprocessor system. One implementation is the shared memory used in the CM\*[11, 12] and in the BBN [13, 14], and the other implementation is the packet switching used in the connection machine[15] and in the NCUBE[16]. The shared memory interconnections are

Chapter 2

composed of either a large common memory or a set of local memories of the processors. Each sample of data is accessed by translating a virtual address to a physical address. Data is transferred to and from the shared memory in one of the following ways:

- Closely coupled through interface controllers.

- Multiple buses or networks (hierarchical clusters).

- Circuit switching for direct data transfer.

- Intermediate circuits for store and forward.

- DMA channels.

In the packet network interconnection, a single byte or data packet is transferred among the processors in one of the following ways:

- Bidirectional buses.

- Shared interface routers.

- DMA channels.

- Hand-shaking.

Interconnection networks which reduce the communication delays and are well suited for general purpose and parallel processing applications [12, 11, 17, 18, 19, 20, 15, 21, 22, 23, 24, 16, 25, 26, 27] have been investigated by several researchers. Studies have shown that for multiprocessor systems containing more than 50 processors, the shared memory interconnection has long delays due to bus contention while the network interconnection which is simpler to implement, reduces communication delays compared to the shared memory and has a good tradeoff between topology and performance of the system. Bus and ring interconnection topologies are cheap to implement but have a limited bandwidth. Mesh and cross-bar interconnection topologies have a high bandwidth but are expensive to implement. The packet network Chapter 2

interconnection combines the advantages of both. It is a closely coupled store-and-forward network that route messages in the form of packets with information about the source, destination and the size of the message. Information (packets) passes through intermediate switches to the destination [28, 29, 30, 31].

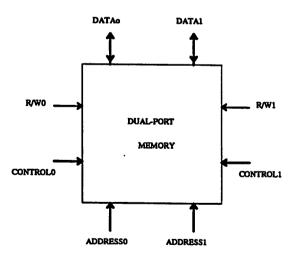

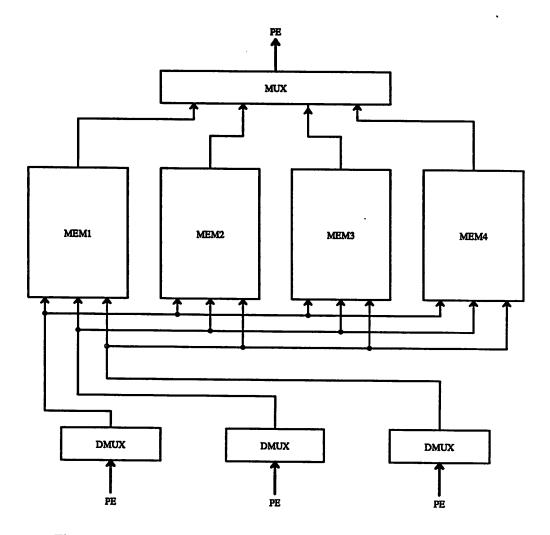

The following chapters describe a way to design a Digital Signal Processor (PE), suitable for multiprocessor systems, which incorporates a Processing Unit (PU) and an autonomous interprocessor communication unit (AIO) on the same chip. The processing unit performs the task's computations while the autonomous interprocessor communication unit (AIO) handles the switching circuit and the data transfer between two PEs. Both units operate concurrently and thus eliminate the waste of processing time for handling and controlling data transfer. Data transfer between the PEs is executed through I/O links that have a high rate data transfer capability ( $\approx$  10-20 Mbits/sec) at the cost of some hardware and software overhead. Data transfer between the PU and the AIO is through dual port memory which can be accessed concurrently by the PU and the AIO, thus preventing any interference between the two units.

### 2.2. <u>Multiprocessor interconnection - background</u>

Many multiprocessor systems like the Cm\*[12, 11], The Connection Machine[15], BBN[14], NCUBE[32, 16], Intel iPSC[32] and the Transputer[33, 34, 35, 36] have different interprocessor communication methods for data transfer and protocols.

Here are a few examples of how interprocessor communication is handled in multiprocessor systems:

#### 2.2.1. Butterfly Parallel Processor

The Butterfly Parallel Processor is an MIMD machine composed of processors with memory and a high performance switch interconnecting the processors. The memory of all the Processor Nodes forms the shared memory which is tightly coupled

**Chapter 2** - 9 -

and can be accessed by each Processor Node. The Processor Node consist of a microprocessor for computations, a Processor Node Controller (PNC) for transmitting and receiving messages, a memory, an I/O bus and an interface to the interconnection switch.

The PNC initiates all messages transmitted over the switch and processes all messages received from the switch. Using memory management, it translates the virtual memory address used by the computing microprocessor into a physical memory address. Thus, the memory of all Processor Nodes appears as a single large global memory to the user. The PNC also provides efficient communication and synchronization between tasks by executing queuing operations in a way similar to the switch operation of a packet switching network.

### 2.2.2. Cm\* multi-microprocessor

The Cm\* is a multiprocessor system with a shared memory. The shared memory is not separated from the PEs. Each PE and its local memory are closely coupled; a network of buses give every PE an access to each non-local memory. The system uses hierarchical packet switching structure. An address and/or a data from a PE is always latched into a switching node of the hierarchical buses structure, and the buses are allocated only for the time interval it takes to transfer the address or the data. The architecture of the system combines several PEs into a "cluster" which provides a shared address mapping and routing processor for handling the intercluster communication. The routing of a PE's reference to target memory is transparent to the user and is performed by special levels of addressing mapping mechanisms and buses. The sender will always receive back an acknowledgement or "Return" message containing the data. Addressing within a cluster is translated by one level of mapping mechanism while addressing between clusters is translated by two levels of mapping mechanism. An intercluster message consist of one to eight words. The sender message consists of the

Chapter 2 - 10 -

following information: source ID, destination ID, control instruction, address of the data and the data (1-8 words). The returned message consists of destination ID, control instruction and the data. Reading/writing data from/to the non-local target memory is done through DMA by the routing processor. For concurrent operation, the routing processors have queues to store messages and to interface between their hierarchical levels.

### 2.2.3. The Connection Machine

The Connection Machine architecture provides a very large number of PEs (processor/memory units) connected by a programmable switching packet communication network, that can connect all PEs in any arbitrary pattern. The key component is a VLSI chip which contains 16 PEs and a router unit of the packet switch communication network. The PEs on the chip are connected in an array of 4 × 4. The router is responsible for routing messages between chips and delivering them to the destination specified by the address. The router communicates with the routers of other chips through an hypercube topology of bidirectional lines. The router can transmit new messages into the network, forward messages between chips and receive and deliver messages to the appropriate PE. The PEs on the chip communicate directly with their four neighbors without the interference of the router. The communication with the router is done by handshaking on the FCFS (first come first serve) basis. A PE initiates a message by sending a packet to its router consisting of an address followed by a "1" followed by the data followed by the parity check. The router accepts messages only if its buffers are not full. This information is then transmitted back to the PE via the router acknowledge flag. The messages will be transferred from the router by FIFO policy, i.e., the message which is at the node the longest time will have highest priority for transmission. When the message reaches its final chip, the local router will deliver it to the appropriate PE by writting it into its memory and notifying the PE that there is a new valid data.

### 2.2.4. Transputer

The transputer is a 32 bit microcomputer with on-chip RAM memory and four standard communication links. Communication between different transputers is point-to-point synchronized and unbuffered. Data transfer is executed only if both transputers are ready. Each link comprises two unidirectional signal lines that carry data and control information. A message is transmitted as a sequence of single bytes. Each link controller has a data transfer overhead that consists of accepting a pointer to the memory, number of bytes to be transferred and the link identity. Data fetch at the sender and data store at the receiver is done by DMA. The data transfer on the link is independent of the processor. The sending transputer initiates transfer by transmitting a byte of data on the output line. The sender then waits for acknowledgement, which is sent through the input line and which signifies that the receiver is able to receive another byte. No other data will be sent before the arrival of an acknowledgement. Each data packet is 11 bits long including 2 bits of header, 8 bit of data, and one END bit. Acknowledgement packets consist of two bits.

### 2.2.5. <u>NCUBE</u>

The NCUBE computer is a multiprocessor that incorporates 2<sup>N</sup> PEs interconnected as an N-dimensional binary hypercube. Each PE has its own local memory, and N direct communication links with its neighbors. Communication with other PEs is performed via asynchronous DMA operations over N pairs of bidirectional lines. Two registers are associated with each link. One is the address register for the message buffer location in the memory and the other is a count register indicating the number of bytes left to send or receive. There is also a "ready" flag and an "interrupt enable" flag for each link. A data transfer is initiated by the processor after checking its flags and setting the appropriate registers. A message consists of a file of data with four associated fields of control information: source, destination, length of data file (up to 64).

Chapter 2 - 12 -

Kbytes) and type of data. Some hypercube systems transfer the whole message at once while others (e.g. Intel's iPSC) partition it into smaller packets that are transmitted sequentially. A new message or packet will be transferred only after the receipt of an "acknowledgement" of previous packet from the receiver. After initiation the processor continues with other operations while the link controller completes the transfer operation via DMA. When the link controller is ready for a new operation (after finishing execution of the previous operation) it will set the appropriate flags and will notify the processor by an interrupt.

### 2.2.6. **Summary**

The aboved survey shows that there are lots of alternatives to transfer data between the PEs. All the alternatives are dedicated for increasing the performance of the particular multiprocessor system. Shared memory used for data transfer between the PEs is not a single large memory but consists of the PE's local memories. Access to the local memories require a network and switches as in Cm\* and BBN. The Connection-Machine uses a complicated programmable switching network for data transfer, while the NCUBE and the transputer use their I/O link as part of the interconnection network. Even though these multiprocessor systems use packet switching, DMA channels and complicated special purpose switches, data transfer in these systems require the processor to lose some computation time and/or memory access time.

### 2.3. Proposed Processing Element (PE)

### 2.3.1. Design approach

In a multiprocessor system which incorporates a large number of processors (on the order of fifty or more), transferring data through a network interconnection is simpler and more economical to implement than through a shared memory interconnection. Chapter 2 - 13 -

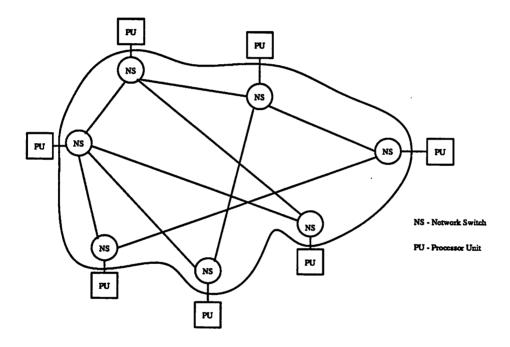

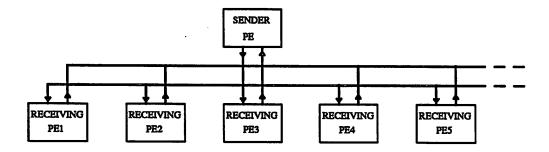

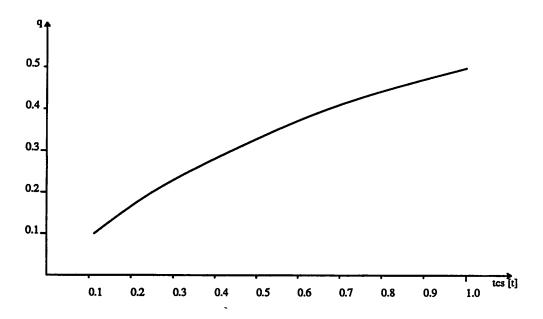

As was mentioned before, the speedup obtained by N processors, depicted in figure 2.1 which operate concurrently in a multiprocessing system and transfer data between them through any network topology is limited by:

- 1) Idle time due to imperfect processor load balancing.

- 2) Waiting time caused by communication latencies in the links and in forwarding data.

- 3) Processor time dedicated to process data messages and to forward them.

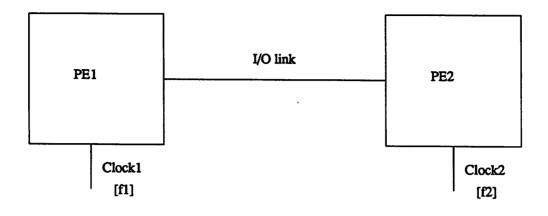

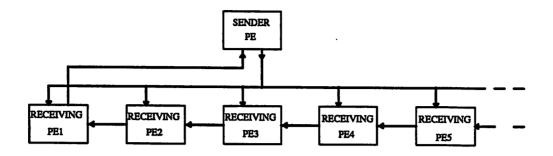

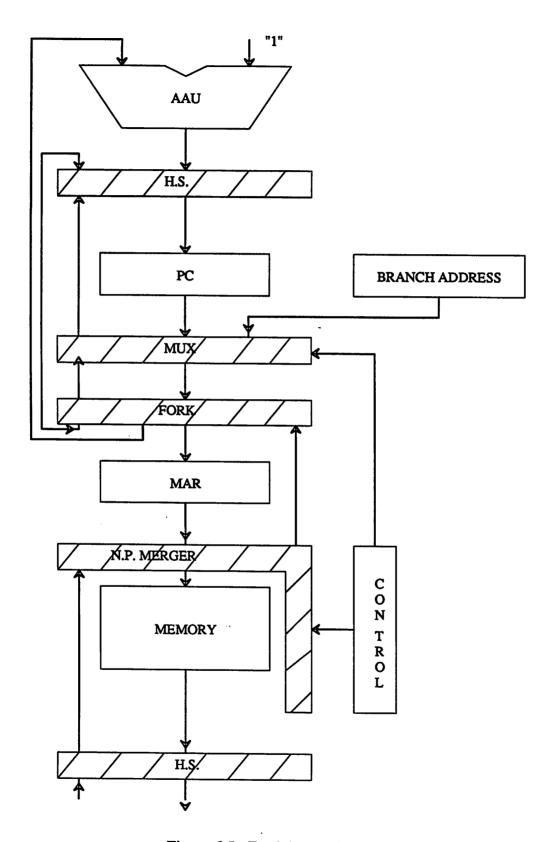

Figure 2.1 - Multiprocessor system

Appropriate processor load balancing with minimal data transfers has to be solved by the scheduler, which partitions the algorithm into tasks and assigns them to different processors so that the transfers are localized and their number minimized. But since the known methods of scheduling do not necessarily yield an optimal partitioning with respect to localization and minimal interprocessor communication, the interprocessor communication hardware and protocols are vital for reducing: 1) The waiting time caused by communication latencies, 2) The processor's time wasted on data transfer

Chapter 2 - 14 -

and communication.

Therefore, the hardware of a multiprocessing system that achieves a computation speedup and a higher throughput must have the following features:

- Minimum processor involvement in controlling and handling interprocessor communication, and thus increasing the processor time dedicated to computations.

- Fast and independent interprocessor data transfer which does not interfere with the task computations and is transparent to the user (separation of processing and communication).

Figure 2.2 depicts a multiprocessing system designed with processing elements that have the above features.

Figure 2.2 - Multiprocessor system with proposed PE

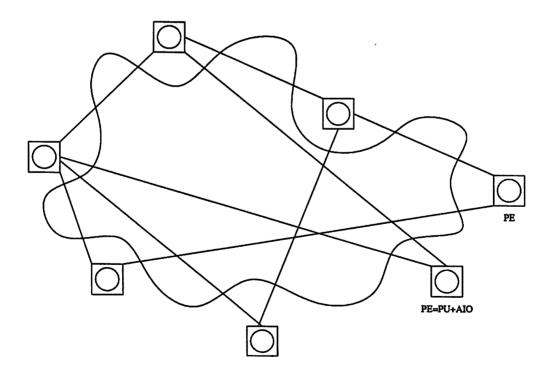

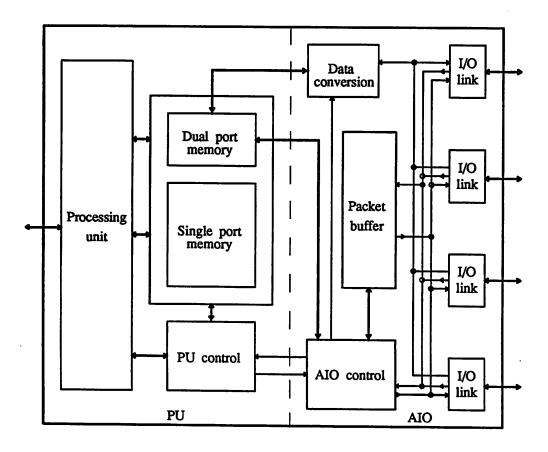

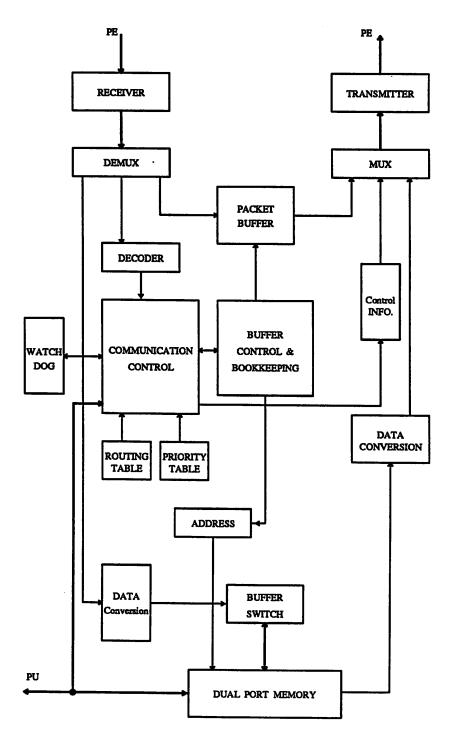

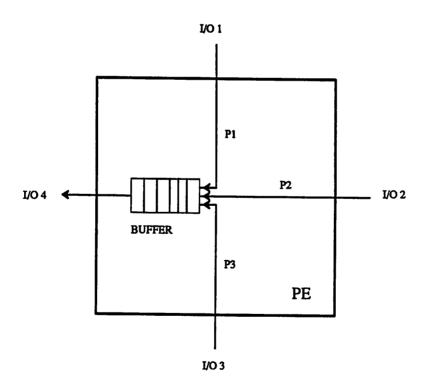

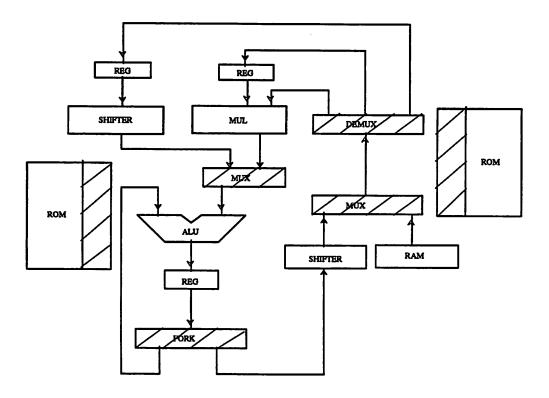

The Processing Element (PE) used in the multiprocessor system of figure 2.2 is depicted in figure 2.3. It incorporates two separate units: the digital signal processing

Chapter 2 - 15 -

unit denoted PU (Processing Unit) and the interprocessor communication unit denoted AIO (Autonomous I/O).

Figure 2.3 - Proposed PE

The processing unit (PU) and the communication unit (AIO) operate independently and concurrently in a way that the data transfer inside the PE between the PU and the AIO and outside the PE between the PEs is transparent to the user. The PU executes the computational part of the task, while the AIO operates either as an autonomous interface for data transfer between the PU and the network or as a network switching node for data transfer between PEs. Handling all the data transfer from the source to the destination by the AIO releases the PU to execute only the computational part of the task. The PE incorporates four pairs of unidirectional I/O links controlled by the AIO which can be used as input and output ports, thus enabling the PE to be embedded in different interconnect topologies of multiprocessor system. When two PEs

Chapter 2 - 16 -

require a higher communication BW it is possible to connect them with up to four interconnection links. In such case the AIO will automatically transfer the packet through

any free link between the two. When two of the links are input links and two are output

links the PE through the AIO control can execute the switch functions in any interconnection network topology such as delta, banyan, cross-bar, mesh, torus, omega, multibus, 4-cube (N-cube) etc. [37, 38, 39, 40, 41]. When in addition the processing power is

necessary, the PE could be part of a systolic array processor or of a N-Cube multiprocessing configuration.

The interconnection between the PEs through the I/O links can be done in several ways: half duplex, full duplex or hand-shake. Data transfer can be serial through one line or parallel through many lines, and thus depending on the application, the data bus can be parametrized during the chip fabrication.

Modularity, parametrizibility and expansibility of the PU and the AIO, dedicated PU implementation according to the application, simple interface between the PU and the AIO and the use of similar protocols for different communication configuration, are the major properties that makes the proposed PE suitable as a macro-cell for many ASICs (Application Specific IC).

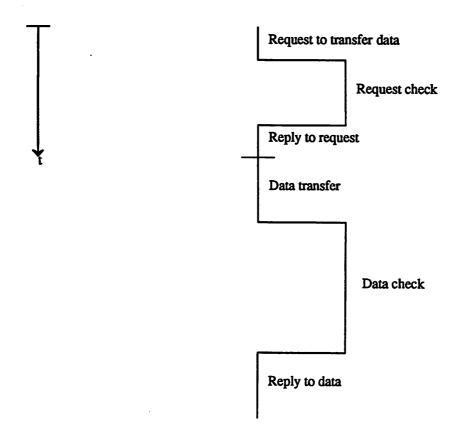

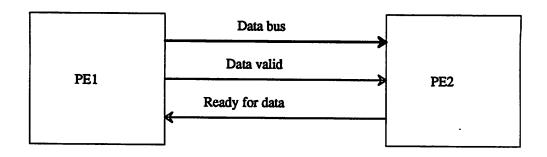

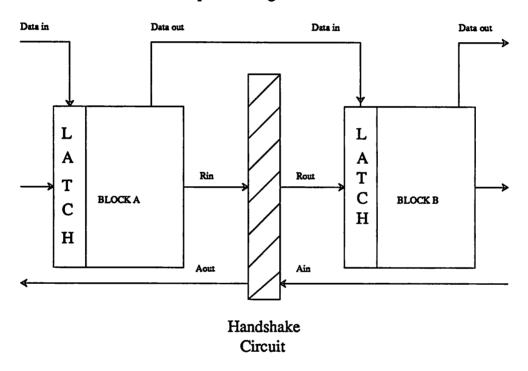

The proposed communication between the PEs is established by a bidirectional handshake protocol illustrated in figure 2.4.

When a source PE must transfer data to another PE, its AIO unit will initiate by handshaking a connection with the AIO of the adjacent PE (intermediate node's PE or destination's PE). The initiation is done by formating a control message according to the protocol and sending it through the communication link. When the AIO of the receiving PE is ready to receive the data, it will signal back and the source will send the data packet. Upon completion of the transfer, the receiver's AIO returns another control message signalling the success/failure of the data transfer. A control message which is

Chapter 2 - 17 -

Figure 2.4 - Handshake communication

much smaller than a data packet contains the following fields: synchronization bits, control instruction, source ID, destination ID, length of data, error detection code and end of message (END). Error detection code like parity words or CRC might not be necessary when the data packets are relatively short (about 2Kbits), and the PEs are close to one another in a free EMI (Electro-Magnetic-Interference) environment.

Speeding up the data transfer can be achieved by using virtual-cut-through (VCT) switching, which is a combination of circuit switching and store-and-forward packet switching. The AIO of each intermediate switching network node checks by handshaking, according to the destination's ID, whether the next node in the path toward the destination is free to receive the data. If the next node (toward the destination) is free, the data is forwarded before it has been received and stored completely in the buffers. This switching scheme requires extra processing power from the AIO as will be described

Chapter 2 - 18 -

later.

Each packet of data from the source to the destination is routed in a minimal number of hops through specific nodes predetermined and assigned by the scheduler [The scheduler may have as an input a given network topology or may output a preferred one].

Storing the data in the packet buffer is necessary for retransmission in case it arrives at the next PE with errors or is lost (according to a fault tolerance policy explained later).

When there are many packets to handle, the AIO will provide preferential service according to priority tables based upon the algorithm's partition and the tasks assigned to each PE by the scheduler.

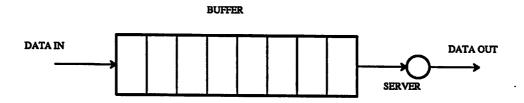

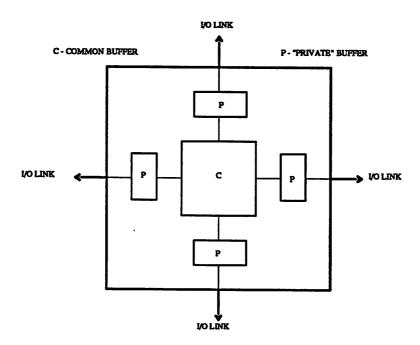

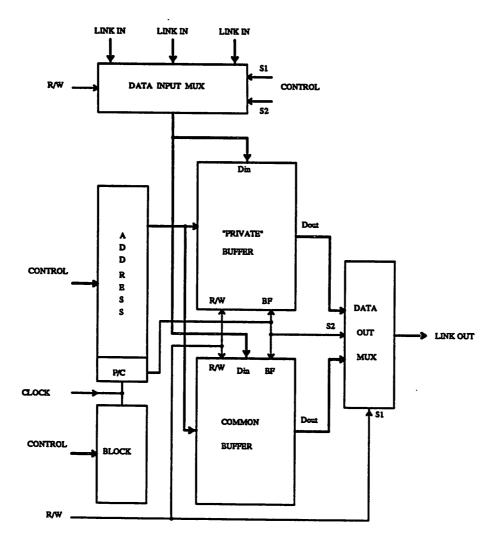

Two types of buffers are incorporated in the processing element. One buffer is the data buffer for interfacing data transfer between the PU and the network when the PE is a source or destination of the data and the AIO operates as an interface between the PU and the network. The other buffer is the packet buffer for data transfer between PEs when the AIO operates as switching node of the network. The data buffer is implemented by a dual port memory, which may be accessed by the PU and the AIO concurrently, thus enabling both units to operate independently without any interference. This dual port memory is in the addressing space of the PU and therefore it is accessed by the PU like any other data in the memory. The other part of the memory which is accessed only by the PU is a regular single port memory. The packet buffer is accessed only by the AIO. This buffer is a temporary storage for data transfer between the PEs. An acknowledgement from the next PE enables the AIO to reuse the storage for new data transfer. The buffer can be implemented by shift registers or single port memories (as will be described later).

Data received by the AIO of the destination PE is stored in predetermined loca-

Chapter 2 - 19 -

tions of the dual port memory buffers. Upon successful reception, the AIO will interrupt the PU to notify, through flags/semaphores, that valid data has arrived. When the PE operates as a switching node of the network, received data is stored temporarily in the packet buffers of the output link through which it must be forwarded to the next PE.

### 2.3.2. Data transfer between PEs

Communication latencies of data transfer are due to: 1) long routes, 2) time to handle message transfers, and 3) waiting time because of the FCFS (firsts-come first-serve) policy that handles and transfers messages in the arrival order and not according to their priority defined by the scheduler.

To decrease these latencies the data transfer procedure is based upon:

- 1) handshaking protocols.

- 2) priority of service.

- 3) routing in minimum number of hops through a virtual- cut-through switching network.

Priority of service and the routes for transferring data in a minimal number of hops are determined by the scheduler during the compilation and the partition of the program.

A handshaking procedure decreases the communication latencies because:

- Data is transferred only when it can be handled by the receiving PE, i.e., there is enough buffer space and data has the priority to be handled, thus freeing the link for transferring the necessary data.

- Saving time in forwarding data to the next PE when the receiving PE operates as a network node by using virtual-cut-through (VCT) switching technique. The receiving PE replies to the sender and at the same time checks whether the next PE is ready to receive the data. If the next PE is ready the

Chapter 2 - 20 -

receiving PE operates in VCT mode.

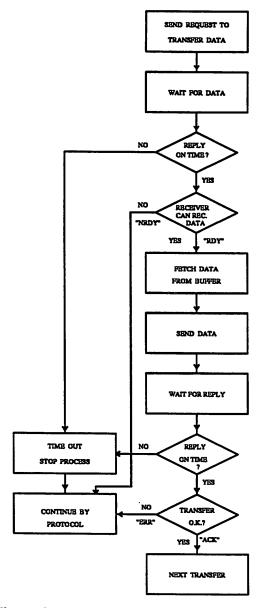

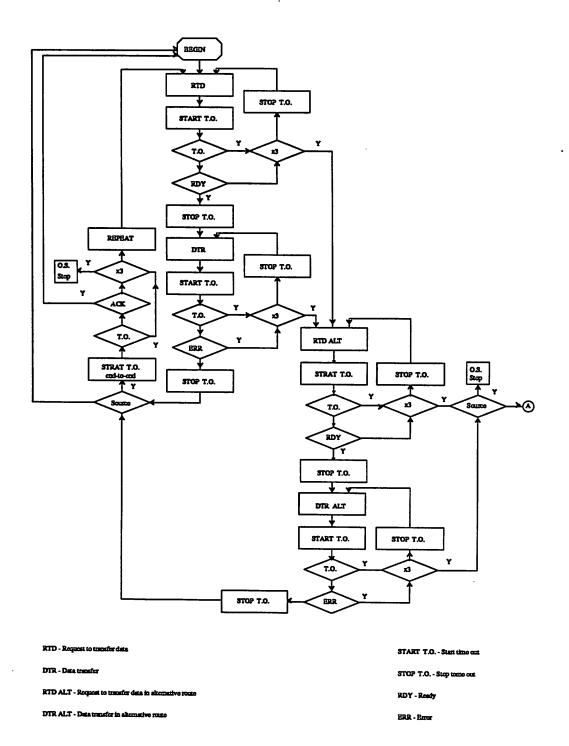

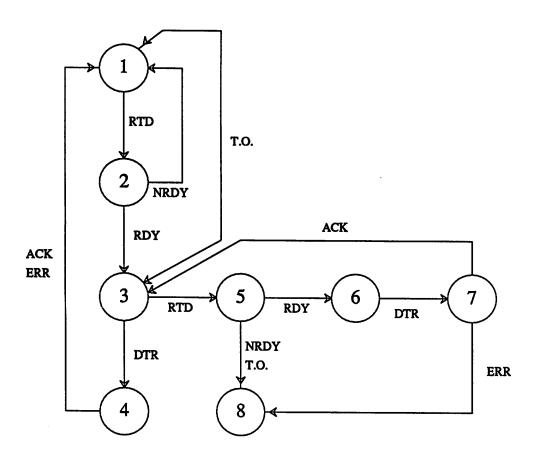

Figure 2.5 depicts the underlying operations executed by a PE in transmitting data according to a data transfer protocol based upon handshaking procedures.

Figure 2.5 - Transmitting PE's operations

The handshaking procedure for data transfer between PEs is always initiated by the sender PE which requests a data transfer and waits for a reply from the receiving PE. If the reply does not arrive during a predetermined time interval or the receiving - 21 -

PE is not ready to receive the data, the sender PE repeats the request or tries to transfer another message according to the detailed protocol described later. If the receiving PE is ready to receive data, the sender PE fetches data from the buffer, sends it and waits for an acknowledgement. When an acknowledgement is not returned during a time interval or the receiving PE replies that errors were detected in the transferred data, the sender PE retransmits the data or continues according to the protocol described later. When a response from the receiving PE verifies that the data has been received without errors, the sender PE can start a new data transfer.

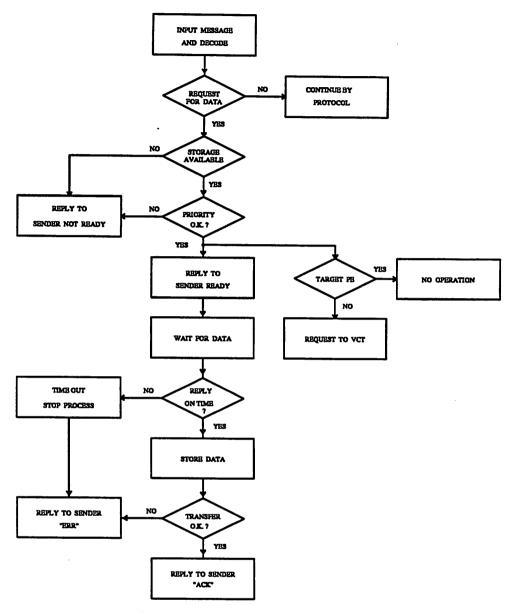

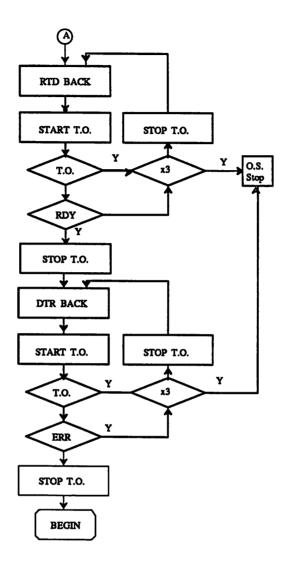

Figure 2.6 depicts the underlying operations of a receiving PE during a data transfer.

Upon receiving a request to transfer data, the receiving PE (next PE) checks whether it has: 1) enough buffer space available to store the data, and 2) the priority to handle data for a specific destination and whether to receive it if multiple messages arrive from different I/O links. If the data to a specific destination has the priority to be handled and there is enough buffer space available, the AIO of the receiving PE replies back to the AIO of the sender PE that it is ready to receive the data. If the receiving PE does not have the priority to handle the data and/or its buffers are full, its AIO will notify the sender that it is not ready to receive the data.

When the receiving PE notifies the sender PE that it is ready to receive data it sets a time-out watch-dog and waits for the data arrival.

In case the receiving PE is not the final destination of the message, i.e., operates as a network switching node that forwards data to the next PE, the receiving PE initiates the handshaking procedure with the next PE at the same time as it replies to the sender PE that it is ready to receive the data.

The receiving PE operates in one of two modes. If the data can be forwarded to the next PE, the receiving PE operates in a virtual-cut-through mode, i.e., it forwards

Figure 2.6 - Receiving PE's operations

data before it has been received and stored entirely. If the data cannot be forwarded to the next PE, the receiving PE operates in the usual store-and-forward mode. In both modes, because of the fault tolerance policy, the received data is always stored in the packet buffers. At the end of the data transfer the receiving PE replies to the sender PE with an acknowledgement (ACK) if no errors have been detected in the data, or with an ERR if errors have been detected. If the data has not arrived during the time interval of the watch-dog it replies to the sender PE with an error message.

Chapter 2 - 23 -

As was mentioned before, data of higher priority will be handled first. Failing to establish an interprocessor connection between two adjacent PEs or to transfer data between them results in later attempts (up to two more attempts) to try the transfer. Trying to overcome failures in the system, if an interconnection link malfunctions or a data transfer fails, the sender PE will try an alternative route and if that also fails it will return the message back to its sender. Any attempt that results in three failures will result in notification to an operating system or to a human operator. A full detailed description of the protocol is described later in chapter 3.

Acknowledgements are used to avoid unnecessary repetitions of data transfers. There are two types of acknowledgements: hop-by-hop and end-to-end. Hop by hop acknowledgement is part of the handshaking procedure between PEs connected by an I/O link. This acknowledgement is to notify the sender PE, connected through an I/O link, that data has been received without errors. Upon receiving a hop-by-hop acknowledgement, the sender PE operates differently if it is a source PE or a switching network node PE. If the sender PE is an intermediate network switching node, it discards the packet after forwarding it in order to use the buffers for another data transfer. If the sender is the source PE of the data it cannot discard it until an end-to-end acknowledgement arrives. An end-to-end acknowledgement is a message from the destination PE to the source PE notifying that the data have been received without errors. Upon receiving this acknowledgement, the source PE discards the data and frees this buffer space for other data. End-to-end acknowledgement is also timed out by another watch-dog dedicated to this purpose (detailed explanation and implementation appear in chapters 3 and 4).

### 2.4. Summary of PE's properties

The proposed PE has the following properties:

Chapter 2 - 24 -

- 1) Separate units for computation (PU) and for communication (AIO).

- 2) Independent and concurrent computation and communication.

- 3) Fast data transfer by employing virtual-cut-through switching and minimum number of hops.

- 4) Variable interconnection band-width between processing elements.

- 5) Macro-cell for "ASIC" implementation:

- Modular and parametrizable.

- PU is adjustable to the application.

- Processor interconnection configuration is adjustable to the application.

- 6) Independent of network topology PE can be embedded in any network topology.

- 7) Simple interface between the PU and the AIO.

- 8) Different buffers for data transfer between the PU and the AIO and for data transfer between the PEs.

### References

- 1. J.L. Baer, "A survey of some theoretical aspects of multiprocessing," *Computing Surveys*, pp. 31-80, March 1973.

- 2. Hockney and Jesshope, in *Parallel Computers*, Adam Hilger, 1981.

- 3. D.J. Kuck, "A survey of parallel machine organization and programming," *Computing Surveys*, pp. 29-59, March 1977.

- 4. P.H. Enslow, "Multiprocessor organization- A survey," *Computing Surveys*, vol. 9, no. 1, pp. 103-129, Mrach 1977.

- 5. Y.Parker, in Multi-microprocessor sytems, Academic Press, 1983.

- 6. H.H. Mashburn, "The C.mmp/Hydra project: An architectural overview," in Comuter structures: Principles and Examples, pp. 350-370, International student

edition.

- 7. L. Snyder, "Introduction to the configurable highly parallel computer," Computer, pp. 47-56, January 1982.

- 8. S.Y. Kung, S.C. Lo, S.N. Jean, and J.N. Hwang, "Wavefront array processors-Concept to implementation," *Computer*, pp. 18-32, July 1987.

- 9. M.C. Chen, "A design methodology for synthesizing parallel algorithms and architectures," *Journal of parallel processing and distributed computing*, pp. 461-491, 1986.

- 10. M. Thaler, C. Loeffler, and G.S. Moschytz, "Programming, analysis and synthesis of parallel signal processing," *Inst. for signal and information processing*, p. 4, 1987.

- 11. R.J. Swan, S.H. Fuller, and D.P. Siewiorek, "Cm\* A modular multiprocessor," AFIPS conference proceedings, pp. 637-644, 1979.

- 12. R.J. Swan, A. Bechtolsheim, K.W. Lai, and J.K. Ousterhout, "The implementation of the Cm\* multi-microprocessor," *AFIPS conference proceedings*, pp. 645-655, 1979.

- B. Lin and P.S. Tzeng, "Benchmarking multiprocessors: A performance analysis of the BBN Butterfly and the Sequent Balance 8000," ERL-EECS Depart. UCB, p. 30, Berkeley, California, May 1986.

- 14. BBN Laboratories Inc., "BUTTERFLY parallel processor overview," BBN report no. 6148, March, 1986.

- 15. W.D. Hillis, "The Connection Machine," in *Ph.D Dissertation*, MIT, Cambridge, Massachusetts, June, 1985.

- 16. J.P. Hayes, T.N. Mudge, Q.F. Stout, S. Colley, and J. Palmer, "Architecture of a Hypercube Supercomputer," *International conference of parallel processing*, pp.

- 653-660, 1986.

- 17. M.A. Franklin, D.F. Wann, and W.J. Thomas, "Pin limitation and partitioning of VLSI interconnection networks," *IEEE tarns. on computers*, vol. C-31, no. 11, pp. 1109-1116, November 1982.

- 18. H.J.Siegel, R.J. McMillen, and P.T. Mueller, "A survey of interconnection methods for parallel processing systems," *AFIPS conference proceedings*, pp. 529-542, 1979.

- 19. H.J. Siegel and R.J. McMillen, "The multistage cube: A versatile interconnection network," *Computer*, pp. 65-76, December 1981.

- 20. K.M. Nichols, "Traffic-Specific interconnection topologies for multiprocessors," in *Ph.D. thesis, Department of EECS, University of California*, Bekeley, 1984.

- 21. C.D. Thompson, "Generalized connection metworks for parallel processor interconnection," *IEEE Transactions on Computers*, vol. C-27, no. 12, pp. 1119-1125, December 1978.

- 22. T.Y. Feng, "A survey of interconnection networks," *Computer*, pp. 12-27, December 1981.

- 23. G.H. Barnes and S.F. Lundstrom, "Design and validation of a connection network for many-processor multiprocessor systems," *Computer*, pp. 31-41, December 1981.

- 24. L.M. Chen and J. Skalansky, "A parallel multiprocessor architecture for image processing," *Proceedings of ,the internatinal conference of parallel processing*, pp. 185-192, 1984.

- 25. C.H. Sequin, "Message switching for multi-microprocessors," proceedings COMPCON spring 80, pp. 131-137, february 1980.

- 26. T.N. Mudge, J.P. Hayes, G.D. Buzzard, and D.C. Winsor, "Analysis of multiple-

Chapter 2 - 27 -

- bus interconnection networks," *Journal of parallel and distributed computing*, vol. 3, pp. 328-343, 1986.

- 27. W. Stallings, in *Data and computer communications*, Macmillan publishing company, New York, 1985.

- 28. A.S. Tanenbaum, in *Computer networks*, Prentice-Hall, Inc., Englewood Cliffs, N.J., 1981.

- 29. L. Kleinrock, "Principles and lessons in packet communications," *Proceedings of the IEEE*, vol. 66, no. 11, pp. 1320-1329, November 1978.

- 30. L.G. Roberts, "The evolution of packet switching," *Proceedings of the IEEE*, vol. 66, no. 11, pp. 1307-1313, November 1978.

- 31. D.M. Dias and J.R. Jump, "Packet switching interconnection networks for modular systems," *Computer*, pp. 43-53, December 1981.

- 32. G.B. Doshi and E.V. Munson, "Benchmarking the Cubes," *UCB project report*, Spring 1987.

- 33. C. Whitby-Strevens, Whitefriars, and L. Mead, "The trasputer," *International symp. on computer architecture*, pp. 292-300, 1985.

- 34. I. Barron, P. Cavill, and D. May, "Transputer does 5 or more MIPS even when not used in parallel," *Electronics*, pp. 109-115, November 17, 1983.

- 35. INMOS, in IMS T414 Product Data, Colorado Springs, December 1986.

- 36. INMOS, in IMS T800 Product Data, Colorado Springs, February 1987.

- 37. A. Gottlieb and J.T. Schwartz, "Networks and algorithms for very large scale parallel computation," *Computer*, pp. 27-36, January 1982.

- 38. B.W. Arden and R. Ginosar, "A multi-microcomputer interconnector," *Proceedings of the international conference of parallel processing*, pp. 353-355, 1984.

Chapter 2 - 28 -

39. M.R. Samatham and D.K. Pradhan, "A multiprocessor network suitable for single chip vlsi implementation," *Proceeding of the international conference of parallel processing*, pp. 328-337, 1984.

- 40. K.M. Kavi, E.W. Banios, and B.D. Shriver, "Message repository facility: An architectural model for interprocess communication," *Proceedings of the international conference on parallel processing*, pp. 271-278, 1984.

- 41. D.A. Reed and D.C. Grunwald, "The performance of multicomputer interconnection networks," *Computer*, pp. 63-73, June 1987.

## **CHAPTER 3**

# Communication and protocols

### 3.1. Introduction

Our interest is in multiprocessor systems containing a large number of PEs which are connected through any arbitrary network. In such systems, the communication methods and the protocol used for data transfer between the PEs are vital to achieve a high throughput. This chapter describes different design alternatives of PE-PE communication and the baseline design choices made for implementing a multiprocessor network systems with the proposed PE. Depending on the application the PE can incorporate different I/O link configurations and/or processing units. Therefore, a particular data transfer mode or technique sometimes is chosen because it has a clear advantage and sometimes is chosen arbitrarily depending on the application, scheduling etc..

Section 3.2 begins with a tutorial of data transfer modes (simplex, half-duplex, full-duplex) and data transfer techniques (handshake, synchronous, asynchronous). A multiprocessing systems containing a large number of PEs, where each PE is limited with the number of its I/O links implies that on the average a certain number of hops is required for data transfer between the PEs. For simple and reliable data transfer in any arbitrary multiprocessor system configuration a synchronous data transfer technique is chosen. To synchronize the clocks of the PEs involved in the data transfer three clock synchronization methods are described. The choice of one of them is arbitrary and depends upon the EMI environment. Fast data transfer with a minimum delay is necessary to obtain a high throughput. Store-and-forward switching and virtual-cut-through

Chapter 3

(VCT) switching in which an intermediate node of the network forwards data to the next one before it has been received entirely, are compared and analyzed. The comparison and the analysis show clearly that the VCT is faster and therefore this method is chosen. Broadcasting data in a multiprocessing system which transfers data by handshaking is difficult to implement. Three methods of data broadcasting are described. Choosing any one of them is arbitrary and depends upon the network configuration and the application.

The type and the formats of exchanging messages between the PEs are very important for correct, complete and simple interaction among them. Section 3.3 describes the chosen protocol and its advantages. To decrease communication latencies a VCT switching mode and an acknowledgement handshaking protocol is chosen. Flow control in the network is obtained by executing the data transfer only if the next PE in the predetermined route can receive it. To avoid network congestion and to detect errors in data transfers an hop-by-hop and end-to-end acknowledgement policy is chosen. Searching analysis is used to verify that the chosen protocol is free of deadlocks, unspecified receptions, non executable interactions and ambiguities.

The message formats described in section 3.4 are based upon the basic format of synchronous data transfer technique described in section 3.2 and upon the chosen protocol described in section 3.3. To increase the message transfer rate some ways of decreasing the message header's overhead are described. Short ID for identifying the source and the destination PEs is one example and the error detection code is another one.

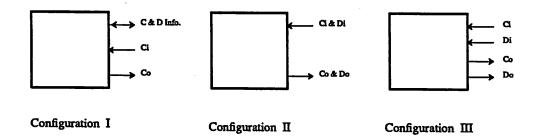

Section 3.5 includes the reasons for choosing four I/O links and a description of three different I/O configurations. The I/O configurations are parametrizable and adaptable to different data transfer techniques, system applications and architecture implementations. The protocols designed in section 3.3 are adjusted to the I/O configuration

Chapter 3 - 31 -

and implementation.

## 3.2. Data transfer techniques

Computer architecture and communication books[1, 2, 3, 4, 5, 6] describe the basic common ways of communication and data transfer techniques between computers themselves and between computers and I/O devices. The next two paragraphs introduce and explain briefly these communication modes and data transfer techniques.

## 3.2.1. Communication modes

The communication between two processing elements connected through I/O links can be done in one of the following modes: simplex, half duplex, or full duplex.

A simplex link transfers information in one direction only. This mode is seldom used in data communications because the receiver cannot communicate with the transmitter to indicate the occurrence of errors.

Half-duplex transmission system is one that is capable of transmitting in both directions but the data can be transmitted in only one direction at a time. In this mode a pair of wires (signal and ground) is required for proper operation.

Full-duplex transmission can send and receive data in both directions simultaneously. This can be achieved by a four-wire link, where a different pair of wires is dedicated to transmission in each direction. A common wire used by both processors reduces the number of the required wires to three. Alternatively, a two-wire circuit can support full-duplex communication if the frequency spectrum is subdivided into two nonoverlapping frequency bands, one for transmit channel and the other for receive channel.

## 3.2.2. <u>Data transfer techniques</u>

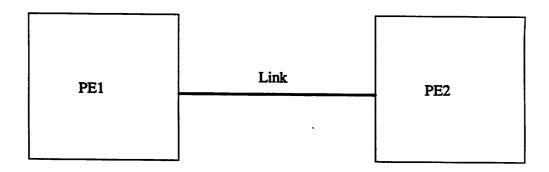

In each of the communication modes data transfer between the processing elements can be done in one of the following methods: handshaking, synchronous or Chapter 3

Figure 3.1 - I/O link

asynchronous.

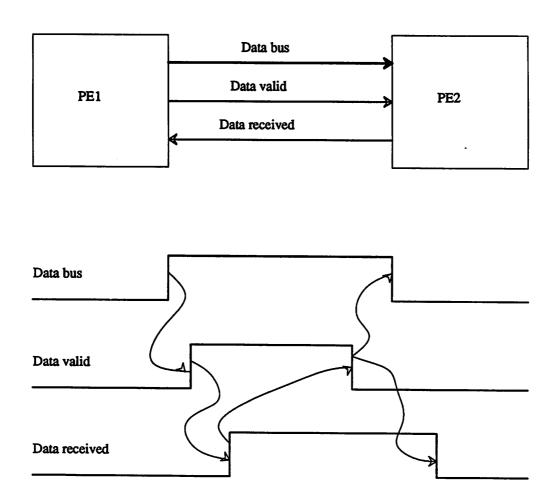

## Handshaking data transfer technique

The basic two-wire handshaking method depicted in figures 3.2 and 3.3, incorporates two control wires and one data bus (contains any number of lines). One control line is in the same direction as the data flow in the bus from source PE to destination PE. This line informs the destination PE whether there is valid data on the bus. The other control line is in the direction from destination PE to source PE and informs the source PE whether it can accept a new sample of data. The control sequence during the transfer depends on the unit that initiates the transfer.

Figure 3.2 shows the data transfer procedure when it is initiated by the source PE. The source initiates the transfer by placing a sample of data on the data bus and activating the "data valid" signal. "Data received" signal is activated by the destination after it has received the data. This signal deactivates the "data valid" signal which deactivates the "data received" signal and sets the data bus to be idle and ready for a new sample of data.

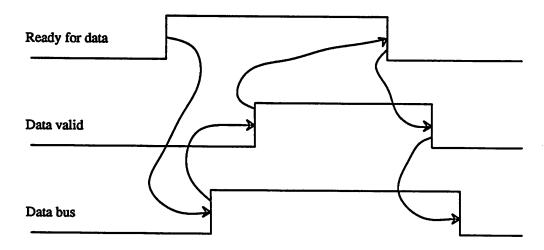

Figure 3.3 shows the data transfer procedure when it is initiated by the destination PE. The destination initiates the transfer by activating the "ready for data" signal. Detecting this signal the source places the data on the data bus and activates the "data valid" signal. After the destination has received the data it deactivates its "ready for

Figure 3.2 - Handshaking initiated by the source

data" signal which deactivates the "valid data" signal and sets the data bus to be idle and ready for a new sample of data.

## Asynchronous data transfer technique

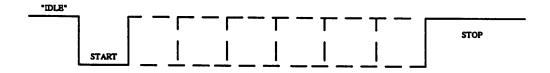

The serial asynchronous data transfer technique employs special bits inserted at the beginning and the end of the data. In this technique, each character (word) depicted in figure 3.4 consists of three parts: a start bit, the data bits, and the stop bits.

The receiver knows the transfer rate and the number of information bits to expect. When there is no data transmitted the link is idle in the "1" state. The receiver detects the "start" bit when the link goes from "1" to "0" and synchronizes the time intervals for receiving the data. After they have been transferred one or two "stop" bits always in the

Figure 3.3 - Handshaking initiated by the destination

Figure 3.4 - Asynchronous data transfer

"1" state are added and the link goes to the idle state.

The asynchronous data transfer technique has the following properties:

- Larger overhead in message protocols. Each transfer of an eight bit character has an overhead of 3 bits (start and stop bits).

- Synchronization at the beginning of each character transfer.

Chapter 3 - 35 -

- More complicated hardware.

- No timing problems between the transmitter and the receiver.

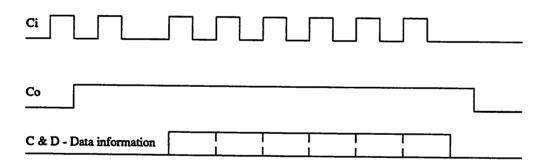

## Synchronous data transfer

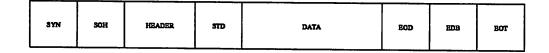

The serial synchronous data transfer technique transmits blocks of data without "start" and "stop" bits. To prevent timing drifts between the transmitter and the receiver, their clocks are synchronized through synchronization information (control bits) embedded in the message. Each block of data begins and ends with control information as depicted in figure 3.5.

Figure 3.5 - Synchronous data transfer

The control information at the beginning of the message is the *preamble* which contains the following data:

- SYN Establishes and maintains synchronization on the link.

- SOH Start of header beginning of message.

- Header Information about the source, destination, block size, message's ID

etc..

- STD Start of data text.

The control information at the end of the message is the *postamble* which contains the following data:

- EOD End of data text.

- EDB Error detection bits.

- EOT End of message.

Chapter 3 - 36 -

The receiver detects the SYN bits and synchronizes its clock to read the message properly. The preamble and the postamble control bits, which have a unique bit pattern, provide the receiver with information about the data and enable the receiver to check its correctness. To distinguish between data and control bits, bit stuffing is necessary in the data information whenever it contains the same bit patterns as the control bits.

The synchronous data transfer technique has the following properties:

- Less overhead in transfer of large data blocks.

- Simpler to implement and requires less complicated hardware.

- Requires synchronization information.

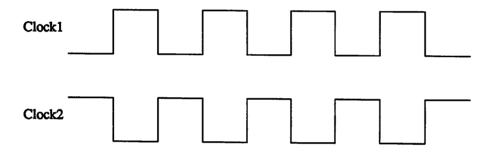

## 3.2.3. Clock synchronization

In the asynchronous data transfer technique the clocks of the processors are very close. In this mode the phase between the clocks is synchronized by the start bit. Therefore, the following question must be asked: What is the allowable drift between the clocks of the transmitter and the receiver? To answer this question it is required to check how many bits is it possible to transfer until the clocks have a phase delay of 180 degrees.

Assume there is a drift of  $\Delta$  f between the clock frequency  $f_1$  of  $PE_1$  and the clock frequency  $f_2$  of  $PE_2$  which is measured by x in [ppm] (parts per million), i.e.,  $\Delta$  f =  $f_1$  -  $f_2$ , or  $f_2$ = $f_1(1+x10^{-6})$ .

The difference in the cycle time  $\Delta T$  is given by:

$$\Delta T = \frac{1}{f_1} - \frac{1}{f_2} = \frac{1}{f_1} - \frac{1}{f_1(1+x\,10^{-6})} = \frac{x\,10^{-6}}{(1+x\,10^{-6})f_1}$$

And the number of bits to be transferred without a clock synchronization error is:

$$n = \frac{\frac{T}{2}}{\Delta T} = \frac{\frac{1}{2}f_1}{\frac{x \cdot 10^{-6}}{(1+x \cdot 10^{-6})f_1}} = \frac{1+x \cdot 10^{-6}}{2x \cdot 10^{-6}}$$

Chapter 3 - 37 -

Figure 3.6 - Clock synchronization

## **Examples**

For x=100 [ppm] = 0.0001 =>

$$n = \frac{1.0001}{0.0002} = 5000$$

[bits]

For x=500 [ppm] = 0.0005 =>  $n = \frac{1.0005}{0.001} = 1000$  [bits]

For x=1000 [ppm] = 0.001 =>  $n = \frac{1.001}{0.002} = 500$  [bits]

As might be expected, these examples illustrate that more bits can be transferred without an error when the drift between the clocks is smaller.

In the synchronous data transfer technique, the clocks of the processor involved in the data transfer have to be synchronized. The "SYN" control bits enable the receiver to synchronize its clock to the transmitter clock, thus enabling the transfer of a large block of data. There are many ways to synchronize the two clocks: PLL (phased lock loop), Chapter 3

bit synchronizer and high frequency shift register.

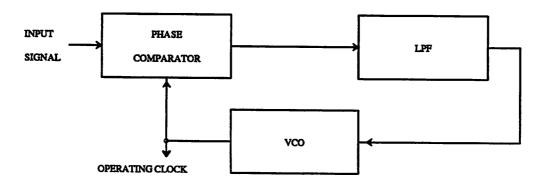

The PLL (phased lock loop) depicted in figure 3.7 is a feedback loop comprised of three basic blocks: a phase comparator, low pass filter and voltage controlled oscillator (VCO).

Figure 3.7 - Phased Lock Loop system

The phase comparator compares the phase and the frequency of the input signal with the VCO frequency and generates an error voltage. The error voltage is fed back to the VCO which synchronizes and locks its frequency to the input signal. Once it is locked, the VCO's frequency is the same as the input frequency except for a phase difference.

The bit synchronizer is a free running oscillator which constantly detects transitions in the input signal and synchronizes its frequency to them. Synchronization takes place after detecting a fixed number of transitions. This circuit also contains a PLL and is very efficient for low signal-to-noise (S/N) ratio signals.

A high frequency shift register is a circuit that samples and latches the input signal with a high frequency input clock (more than ten times the operating clock frequency) into a shift register and checks the number of "1"'s and the number of "0"'s during each operating clock cycle. When a transition occurs in the input signal and there is a difference in the number of "1" and "0", it is a synchronization error. This error is fed back to a VCO for correcting and synchronizing the receiver's clock.

Chapter 3 - 39 -

If the input clocks to the PEs are crystal oscillators with high frequency and their operating frequencies are sufficiently close, the use of shift registers for synchronization is adequate. If the input frequency is not much higher than the operating frequency, the PLL system is required. The bit synchronizer is required only in very noisy environments or in systems with low input data frequency.

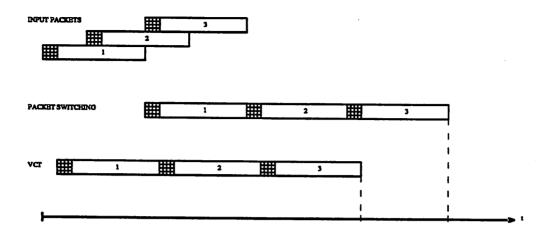

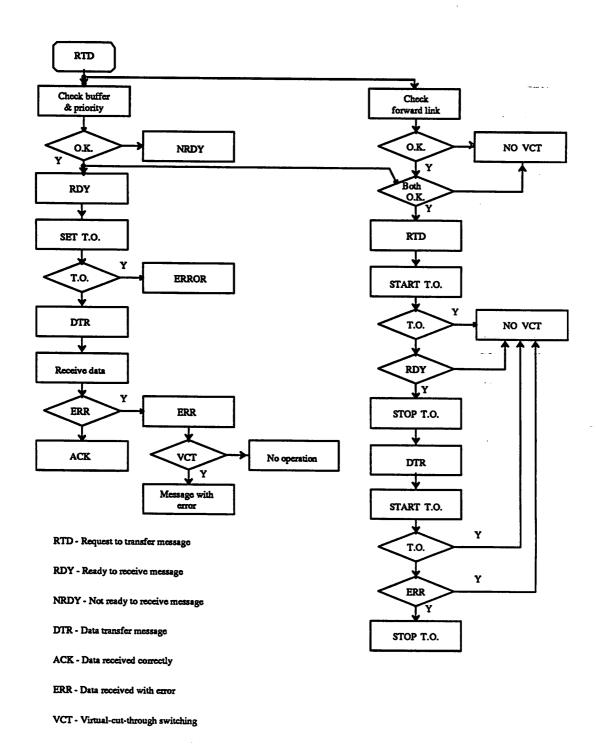

## 3.2.4. <u>Virtual - cut - through switching</u>

In chapter 2 and in section 3.1 it was mentioned that it is possible to enhance the data transfer between the source and the destination if the AIO forwards the message to the next node in the path before it has been received completely. In principle this switching system operates as a combination of circuit switching and store-and-forward packet switching. When a control message arrives to a network switching node the AIO decodes the address, looks up in tables for the next link to be used for forwarding the message (preassigned path) and checks if buffer space is available and if the forwarding link is free. If the forwarding link is free, while reponding to the sender PE that it is ready to receive a packet, the AIO tries to establish a connection with the next PE by forwarding the control message to it. If the connection is granted the AIO will begin to forward the data message to next node before it has been received completely. If the connection is not granted the message is not transferred. In both cases, due to fault tolerance and acknowledgement policy the data is always buffered like in any packet switching system.

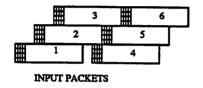

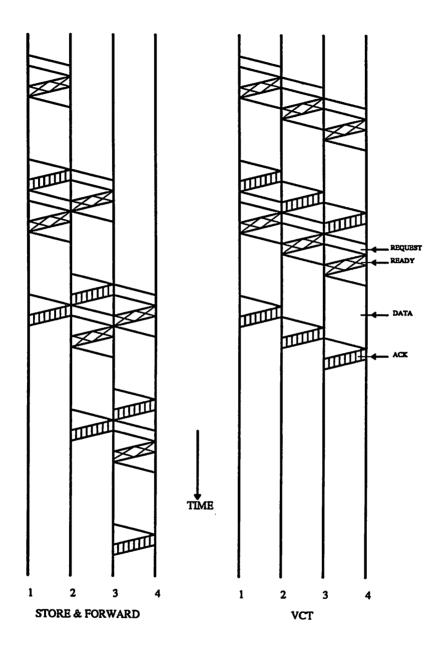

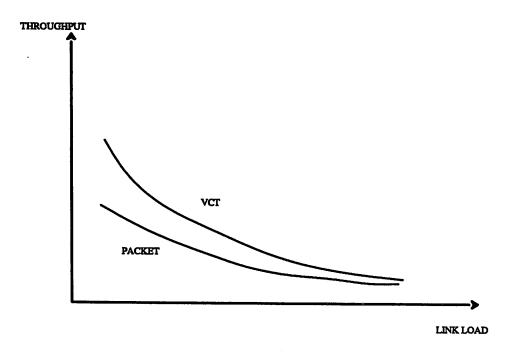

Figures 3.8a and 3.8b depict the delay procured in transferring fixed size data packets between two network nodes of a packet switching system and a virtual-cut-through switching system. The packets arrival rates depicted in figure 3.8b is higher than the rate depicted in figure 3.8a.

In both cases, whether the packet arrival rate is high or low, the network node of a virtual-cut-through network transfers all the packets with a smaller delay equal to the

Figure 3.8a - Transfer delay - low rate fixed size packet arrival

Figure 3.8b - Transfer delay - high rate fixed size packet arrival time required to transfer the data of one packet.

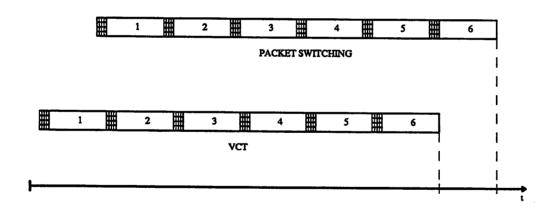

Figure 3.9 depicts the delays in transferring different sized data packets with different arrival rates in both switching systems.

As before, the virtual-cut-through switching system yields a smaller transfer delay equal to the time required to transfer the data of the largest size packet.

Figure 3.9 - Transfer delays - variable sized packets

If there are no transfer errors and the links are free to transfer data ("best case"), the decrease in the delay to transfer packets between two nodes of of the virtual-cut-through switching system increases linearly with the number of network nodes that the packets of an information message have to pass from the source PE to the destination PE. Figure 3.10 depicts the difference in the time that it takes for a message, consisting of three packets, to travel from the source PE, through two network nodes up to the destination PE.

It is possible to compare the "best case" throughput and the network delay of the virtual-cut-through switching system and the store-and-forward packet switching system for packets of the same length.

### Denoting

- \* T time required to transfer packet of data.

- \* t time required to transfer the message header.

Figure 3.10 - Transfer delays between source and destination

- \* n number of packets in a message.

- \* m number hops between source and destination.

- \* T+t time required to transfer data packet and a header.

## Packet switching

Throughput=

$$\frac{T}{T+t}$$

$$Delay=(n+m-1)T+(n+m-1)t$$

### Virtual cut through switching

Throughput=

$$\frac{T}{T+t}$$

Delay=

$$nT+(n+m-1)t$$

This comparison shows that in the "best case", when there are no errors in data transfer and no queueing delays (each PE is always ready to receive and forward messages), transferring a message of n packets through a virtual-cut-through switching system has a smaller delay (higher throughput) when routing the message from the source PE to the destination PE requires more hops (m is large). The decrease in the average delay of the "best case" is (m-1)T.

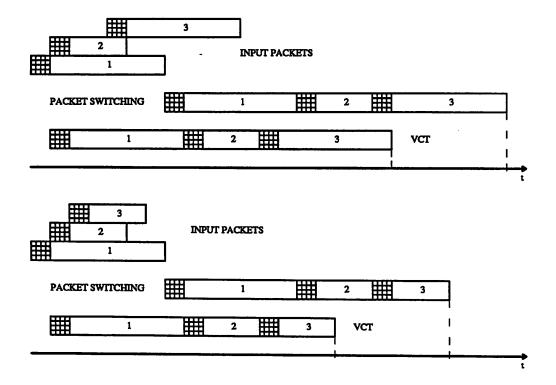

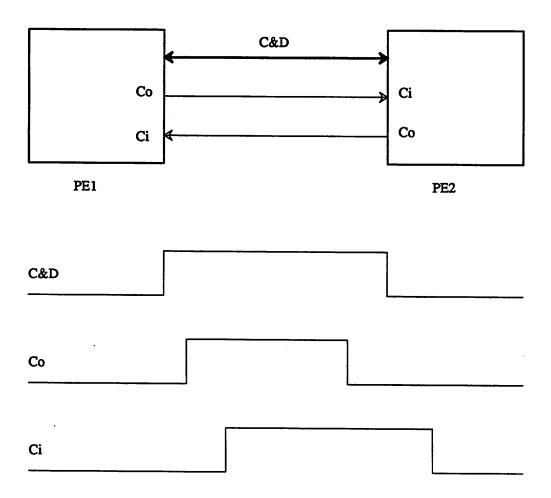

Using the proposed handshaking protocol described in section 3.3 enables the receiving PE to establish a connection with the next PE while replying to the sender PE

Chapter 3 - 43 -

that it is ready to receive the data. Therefore, less data is stored before it is started to be forwarded and the delay time is smaller. Figure 3.11 depicts this property.

Figure 3.11 - Handshaking data transfer

Kermani and Kleinrock in[7] and Hammond and O'Reilly in[6] analyzed the virtual cut through switching system by using M/M/1 queueing theory models and the following assumptions:

Chapter 3 - 44 -

- Poisson distribution of message arrival.

- Exponentially distribution of message length.

- Infinite buffer size.

- Deterministic routing.

- Balanced network utilization.

- Negligible propagation delay.

- No errors due to noise.

They showed that the average delay to send a message through a balanced network is:

Averagedelay =

$$\frac{(n+m-1)}{(1-\rho)}(T+t)-(m-1)(1-\rho)T$$

(3.1)

Where:

- n number of packets of the message

- m average number of hops

- T time to transfer data of a packet

- t time to transfer header of a packet

- ρ utilization of each link (equal to all links)

The first term of the average delay is due to average packet switching delay while the second term is the improvement of the average delay due to the virtual-cut-through feature. This result agrees with the result shown before but it also takes into account the probability  $(1-\rho)$  that the outgoing link is free. In a noisy environment, the probability that the outgoing link is free has to be multiplied by  $(1-P_e)$ , where  $P_e$  is the probability that an error occurred.

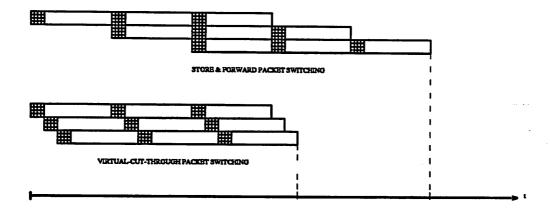

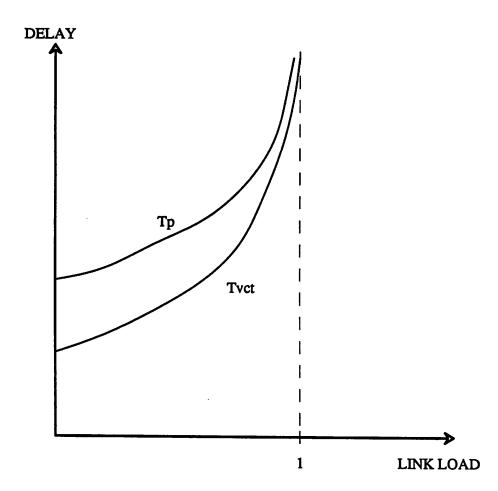

The result above implies the following conclusions (relative to the packet switching):

1) When the average number of hops increases, the average number of forwarding

messages without buffering also increases, which means that the average delay decreases.

- 2) More localized data transfer between adjacent PEs and less data transfer between non adjacent PEs yields more messages transfer without buffering.

- 3) VCT switching systems have smaller average network delay than store-andforward packet switching.

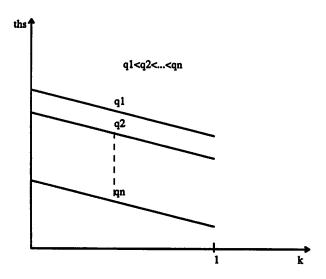

Figure 3.12 - Delay vs. link load

4) For the same network delay, the virtual cut through switching system can transfer more packets than the packet switching system and the difference is greater when the network is lightly loaded.

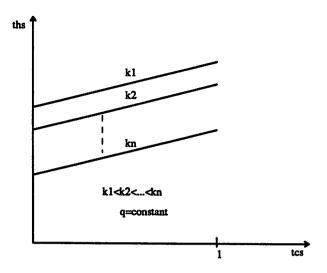

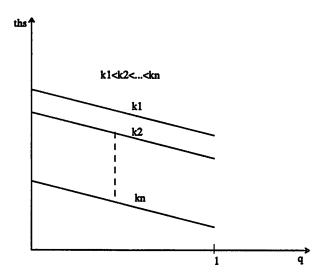

Figure 3.13 - Throughput vs. link load

- 5) VCT switching systems require less buffer storage than packet switching store and forward systems.

- 6) VCT decreases the buffer size required in each node.

- 7) VCT implementation is more complicated and requires more processing power.

As will be explained here the assumptions made earlier in the section for the virtual-cut-through network analysis match the requirements of a multiprocessor system derived in chapter 2.

- Finite buffer size has small effect on the calculated average delay as was shown in [7].

- Deterministic routing which is used for transferring messages in a minimum number of hops is also one of the analysis assumptions.

- Balanced network utilization and PE load, as well as minimizing data transfer imposed on the scheduler (which partitions the algorithm and assigns the tasks to different PEs) are essential for obtaining a large reduction in the average data

Chapter 3 - 47 -

transfer delays.

• Low utilization of the links is equivalent to the demand of localized data transfer between the PEs imposed on the scheduler. Minimizing the number of hops reduces the advantage of the VCT (since the reduction in the average delay of the data transfer is relative to the number of hops) but localizes the data transfers.

The protocol's characteristics and properties required to implement the processing element (PE), described later in this chapter (3.4.1) and in chapter 4, also correspond to these assumptions.

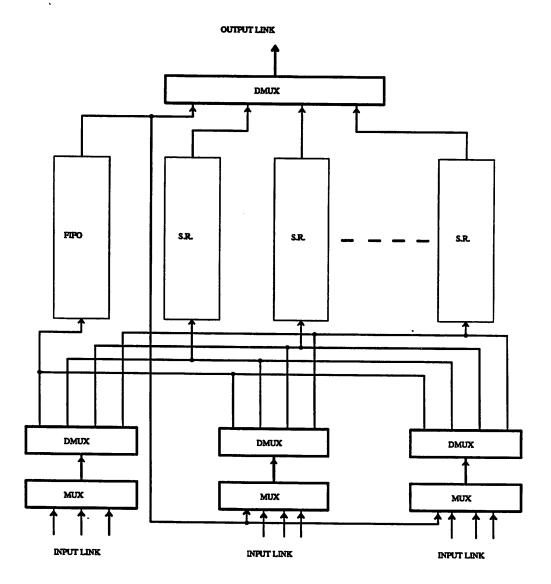

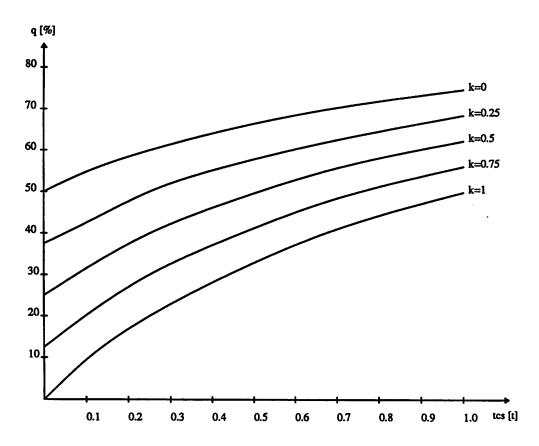

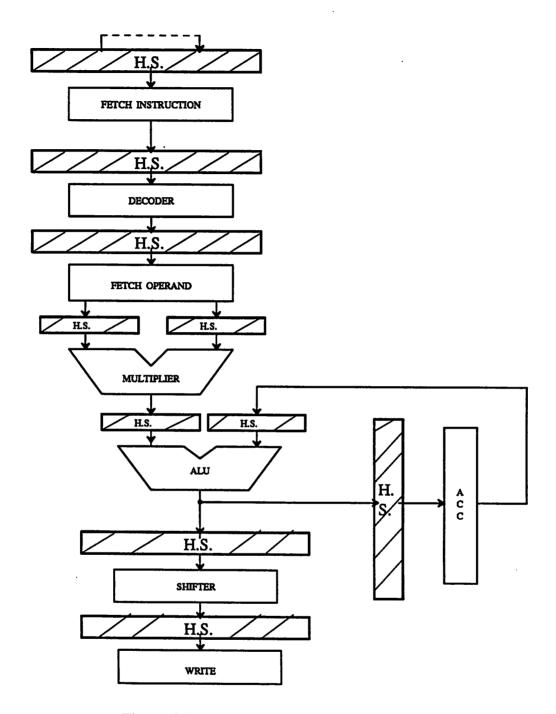

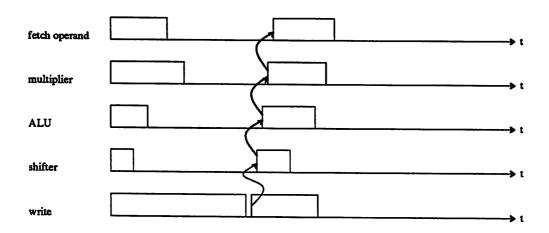

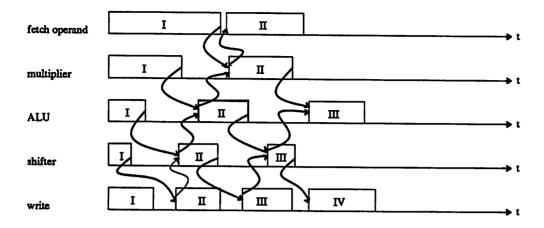

### 3.2.5. Data broadcast