## Copyright © 1987, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

MOS PROCESSES IN THE MICROFABRICATION LABORATORY

by

Katalin Voros and Ping K. Ko

Memorandum No. UCB/ERL M87/12 10 March 1987

#### MOS PROCESSES IN THE MICROFABRICATION LABORATORY

by

Katalin Voros and Ping K. Ko

Memorandum No. UCB/ERL M87/12 10 March 1987

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

#### MOS PROCESSES IN THE MICROFABRICATION LABORATORY

by

Katalin Voros and Ping K. Ko

Memorandum No. UCB/ERL M87/12 10 March 1987

**ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# MOS Processes in the Microfabrication Laboratory

Katalin Voros Ping K. Ko

#### Abstract

This report describes the "standard" MOS processes in the Microfabrication Laboratory of the University of California, Berkeley. These processes are available as options for students doing research in silicon circuit design or fabrication technology. Test devices are described and test results are shown in the appendices.

## MOS Processes in the Microfabrication Laboratory

#### Table of Contents

| Introduction                                   |        |

|------------------------------------------------|--------|

| NMOS Process                                   |        |

| N-Well CMOS Process                            | 2      |

| P-Well CMOS Process                            | 2      |

| Equipment                                      | 3      |

| Documentation                                  | •••••5 |

| Staff                                          |        |

| Summary and Proposals for Further Projects     | 6      |

| Acknowledgements                               |        |

| References                                     |        |

| Appendix I - NMOS Process                      | I-0    |

| Process Run Sheet                              | I-1    |

| Mask and Implant Descriptions                  | I-5    |

| Test Chip Design Listing                       | I-7    |

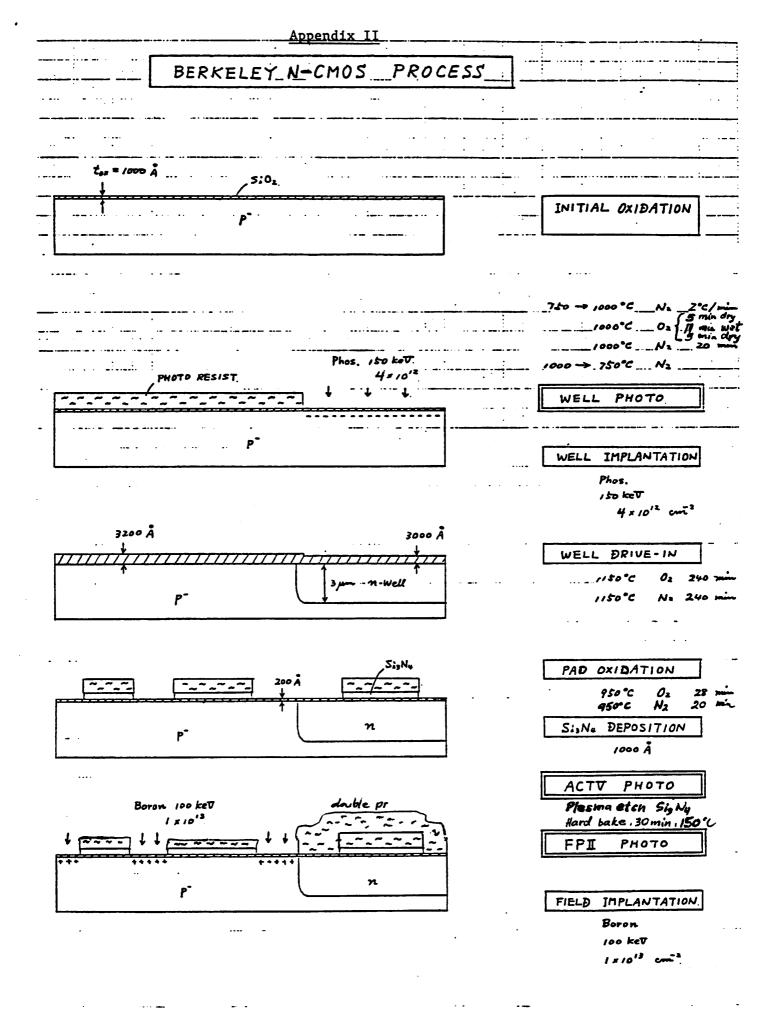

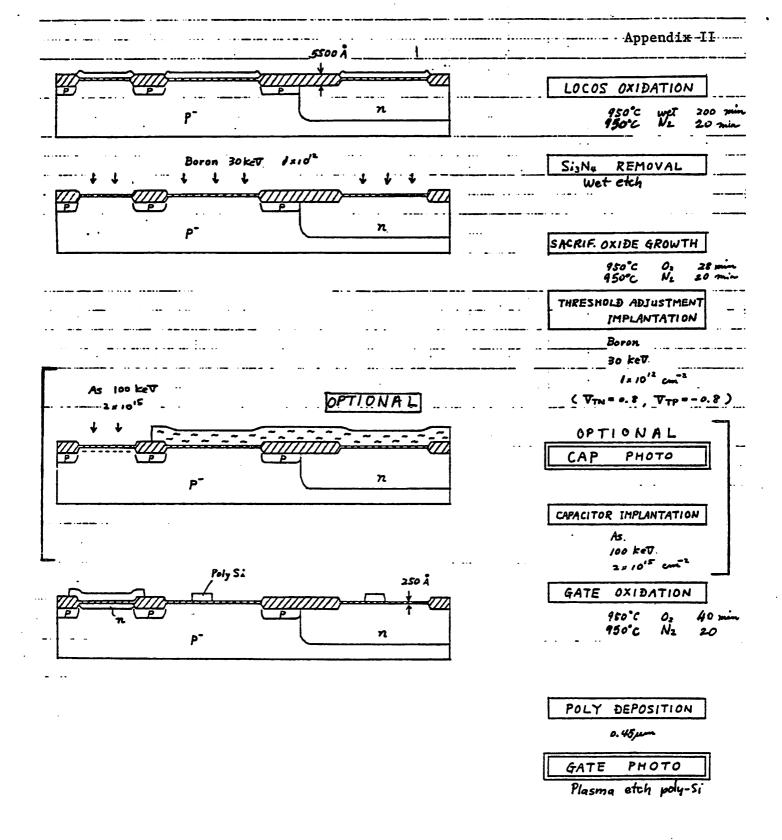

| Appendix II - N-Well CMOS Process              | II-O   |

| Process Run Sheet                              | II-1   |

| Mask and Implant Description                   | II-6   |

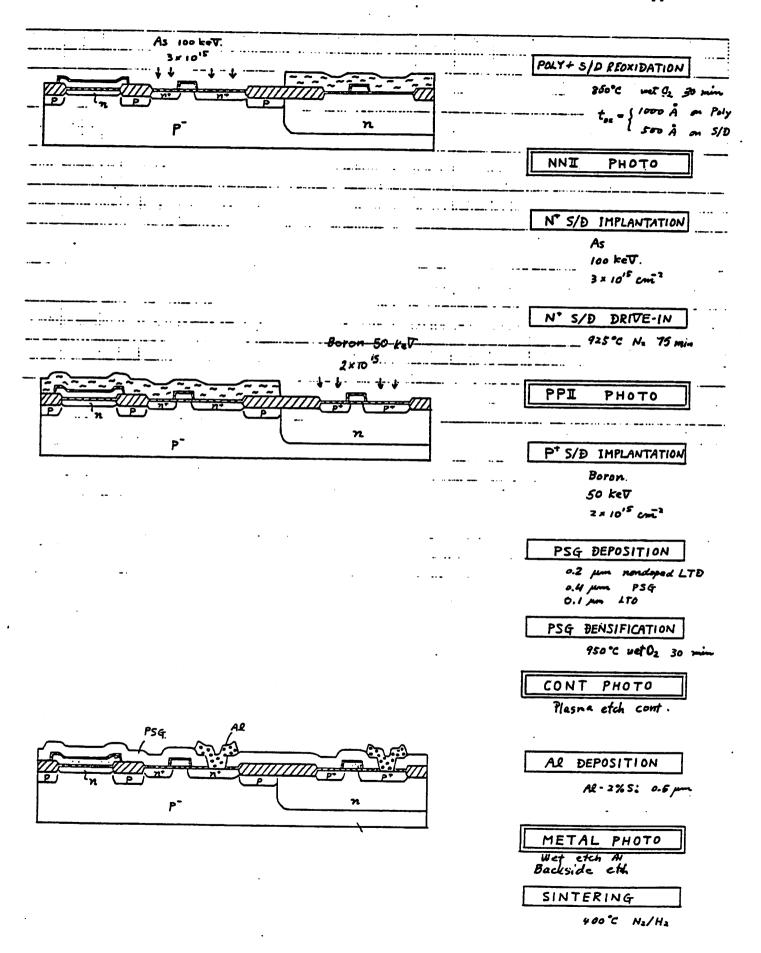

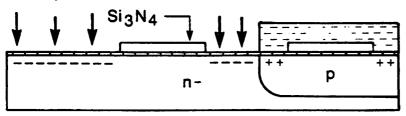

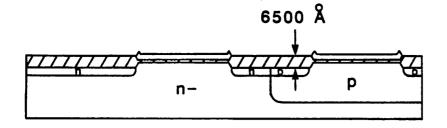

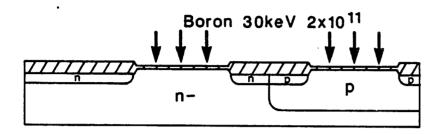

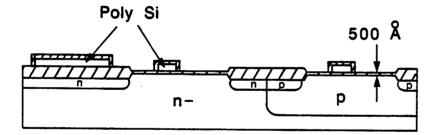

| Process Run Graphic                            | II-7   |

| Appendix III - P-Well CMOS Process             |        |

| Process Run Sheet                              | III-1  |

| Mask List                                      | III-7  |

| Ion Implants                                   | III-8  |

| Process Run Graphic                            | III-9  |

| Appendix IV - P-Well CMOS Double Metal Process | IV-0   |

| Process Run Sheet                              | IV-1   |

| Appendix V - Process Modules                   |        |

| Process Information Storage                    | V-0    |

| Standard 100mm Berkeley VLSI Process Modules   | V-1    |

| Hotpotato Menu System                          |        |

| Hotpotato File for Information Storage         |        |

# MOS Processes in the Microfabrication Laboratory

#### Introduction

During the past two years a strong effort has been made to stabilize and characterize operations in the Microfabrication Laboratory and to develop silicon MOS processes which can be applied to the fabrication of integrated circuits. Maintaining "standard" or "staff" processes has several advantages, the most important being that it provides stability and continuity in an educational laboratory where students come and go, where each project is different and new students need to identify a starting point from which they can carry on their projects. Another important factor is the capability to provide circuit designers with a choice of processes which can be used to design new circuits and to fabricate chips for those who cannot spend the time or are not interested in doing it themselves. Yet, the designer is close to processing, can follow it in detail, and can help make processing decisions: thus, the lab is still providing valuable experience for the student.

The Microlab staff currently maintains a  $2\mu$ m NMOS process, a  $2\mu$ m N-Well CMOS process. a  $3\mu$ m P-Well CMOS process with double poly-silicon and a  $2\mu$ m P-Well CMOS process with double metal ( $5\mu$ m first metal pitch). Complete process descriptions are included in the appendices.

#### **NMOS Process**

The 6-mask NMOS process includes LOCOS isolation, 200Å of gate oxide, buried contacts to provide an extra layer of interconnections and an optional thin poly-silicon layer under the aluminum to prevent spiking.

The test chip, designed by Dr. P. Li, includes the usual process and device test structures and a 512 x 8 bit RAM, which was a FIFO test chip for image processing circuitry designed by P. Ruetz. Listings of devices and transistor test results are shown in Appendix I.

#### N-Well CMOS Process

The first CMOS process in the new Microfabrication Laboratory was developed during a two-semester graduate course given by Professors Oldham and Neureuther with Dr. Yosi Shacham-Diamand.<sup>2, 3</sup> This was an N-Well process which was modified and established as the staff process during 1985.

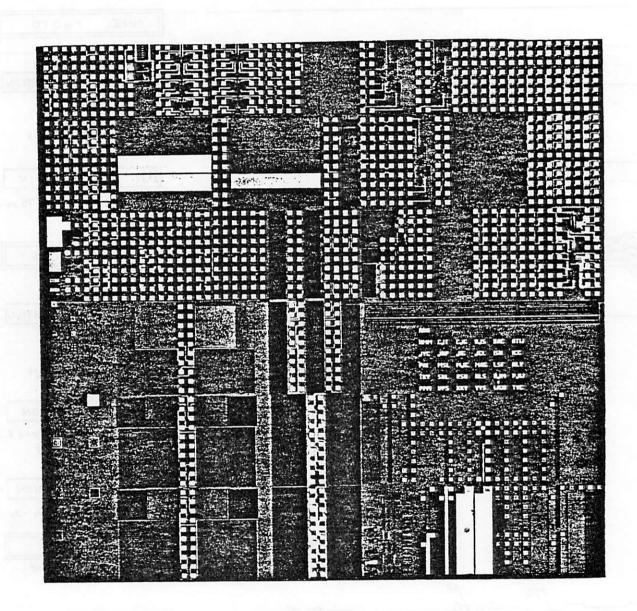

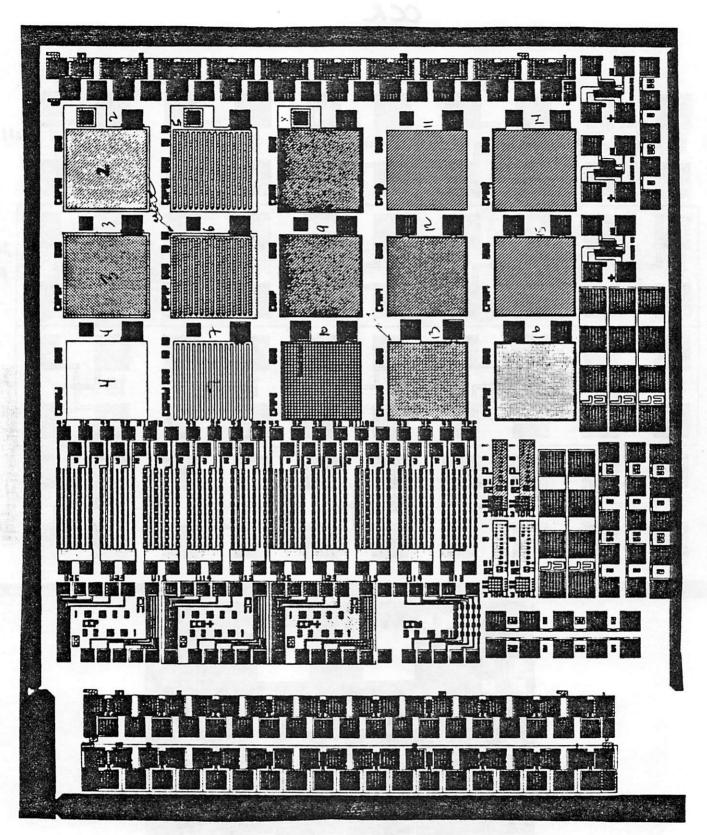

The test chip was designed by the students in the course EECS 290N and the mask set, made during the course EECS 290O, was used for the staff CMOS 1 and 2 runs. Some features of the current N-Well CMOS process are: LOCOS isolation; 250A of gate oxide; self-aligned field implant with double resist photolithography; blanket threshold-adjust implant; single polysilicon; PSG reflow; single metal. Process flow sheets and device results are shown in Appendix II. Device descriptions can be found in References 2 and 3.

#### P-Well CMOS Processes

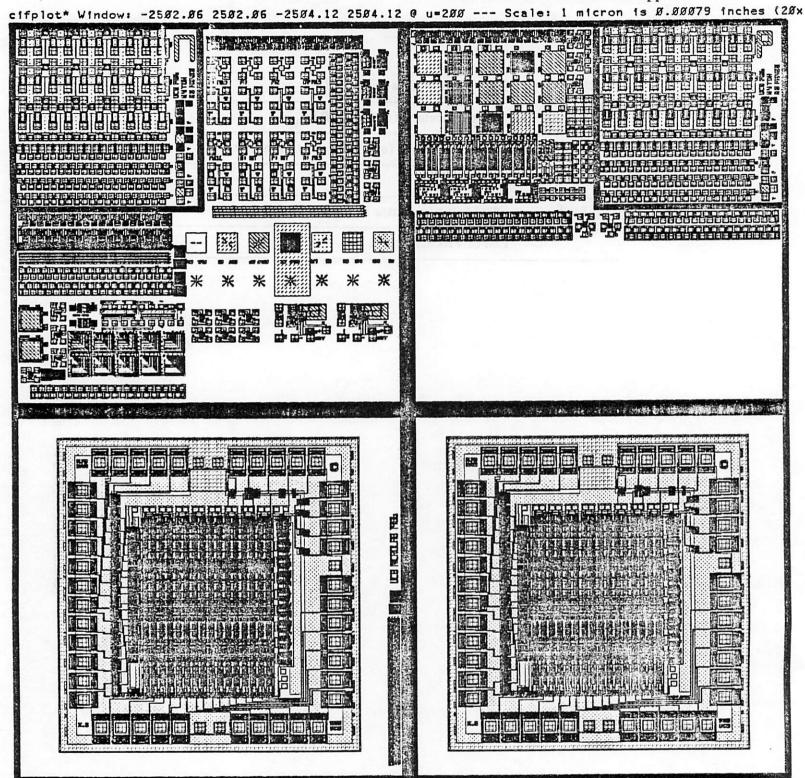

A. A p-well CMOS process was developed during 1986 using a test chip designed by K. Y. Toh<sup>4</sup> and a switched capacitor filter circuit by C. K. Wang.<sup>5</sup> 3 micron MOSIS<sup>6</sup> design rules were applied to ensure compatibility with MOSIS processes. The Wang chip, which tested successfully after MOSIS fabrication, served as a control for our first p-well run (CMOS3). The next two lots (CMOS4 and 5) were of a composite chip consisting of four different circuits designed by students and the Toh test chip as a drop-in in four locations.

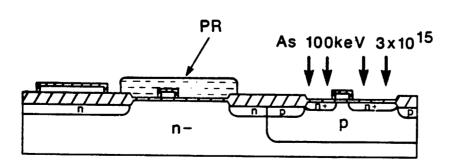

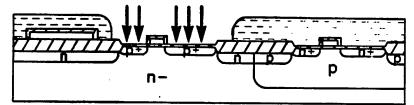

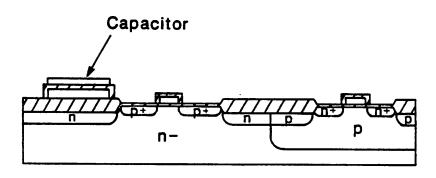

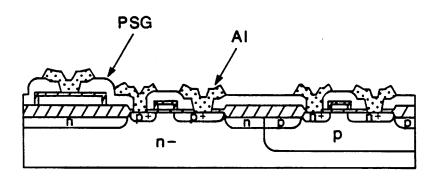

The p-well CMOS process has 500A of gate oxide: two polysilicon layers, the second layer containing only the capacitor top plates, no interconnects. The punchthrough implant is a blanket phosphorus implant which is done before the well implant. A self-aligned p- field implant adjusts doping concentrations in the well (outside of active areas): the reversal of the well mask and the nitride layer are used to protect well and p- active areas during field implant outside of the well.

Process flow sheets, device descriptions and transistor test results are shown in Appendix III.

B. Another variation of the p-well CMOS process was applied to the CMOS6 run. For this lot Pei-in Pai, with the help of Kim Chan, developed a double-metal process which has a composite of spin-on glass/plasma deposited silicon dioxide as the intermetallic dielectric. The rest of the process is basically the same as described in Section A, except that it has only one polysilicon layer. Pertinent information is listed in Appendix IV.

#### Equipment

The Microlab is a complete facility for fabricating integrated circuits. beginning with design, mask making, processing all the way through assembly and testing. Test chip design and layout is done using UCB's KIC graphics editor for integrated circuits. CIF files are transferred into MANN files and loaded on magnetic tape for the GCA MANN 3600 optical pattern generator. The mask shop includes a GCA 3600 pattern generator, two APT automatic mask developers, (one for emulsion and one for chrome), capable of handling 2.5°, 3° and 5° plates; an Ultratech mask copier and a 10:1 mask reduction camera. Students normally make their own mask; staff will also accept tapes and will make masks for a charge for those who are not frequent users of the lab or need only a limited number of masks.

The VLSI area of the lab is equipped to process  $4^n$  silicon wafers. Photolithography is done on an Eaton cassette-to-cassette wafer track, a GCA 6400 10X wafer stepper, and an MTI Omnichuck developer. Hard baking is done in a VWR convection oven. Resist removal is accomplished by acetone rinsing on the MTI Omnichuck or by plasma ashing in a Technics parallel plate etcher. The process is capable of printing 1  $\mu$ m lines and spaces routinely and 0.75  $\mu$ m lines with some extra effort.

For furnace operations the lab has Tylan's Tytan II furnace system with a Tycom 9900 automatic controller. Of the sixteen furnace tubes, four are used for low pressure chemical vapor deposition of silicon nitride, polycrystalline silicon and phosphosilicate glass, or low temperature oxide. Polysilicon is in-situ doped with phosphine to obtain a resistivity of  $7x10^{-4}\Omega$ -cm after anneal. Wet oxidation is done with the addition of steam from a dropper-type steam generator. No chlorine is added during dry oxidations. Standard tubes are TCA cleaned for at least 4 hours

prior to processing. A set of standard programs, with time/temperature/dopant options, written and tested by students in conjunction with staff, is available for all users. If anything out of the ordinary is needed, students may write their own programs after discussing it with the process engineer.

Standard wafer cleaning before furnace operations consists of "piranha" cleaning (mixture of sulfuric acid and hydrogen peroxide) at 120°C for 10 minutes, twice; the second time it is done in the restricted "clean" sink. Cassettes and spin-dryers are also dedicated to "dirty" and "clean" sinks. Wet etching is done in the "dirty" sinks.

For dry etching the Microlab has a LAM plasma etcher dedicated to polysilicon etching  $(CCl_4/He/O_2)$  and a Technics plasma etcher for silicon nitride etching  $(SF_6/He)$  and silicon dioxide etching  $(CHF_3/O_2)$ . Dry etching of silicon dioxide is the weak point in the process currently and upgrading the equipment as well as the process is being investigated.

Metallization is done by sputtering Al/2% Si in a DC magnetron sputterer. A Technics plasma enhanced chemical vapor deposition (PECVD) system is used to deposit passivation glass. Wafers can be diced with a Tempress diamond saw and chips packaged with the aid of a Westbond Ultrasonic wire bonder.

Analytical equipment includes a Nanospec, an ellipsometer and a Tencor profilometer for thin film measurements; a manual and an automatic (Prometrix) four-point probe station and a Tencor Sonogage for resistivity measurements; a C-V test set-up with heated chuck and a manual probe station with curve-tracer for in-process electrical testing. A Vickers image shearing microscope, a Nanoline and a Cwikscan electron microscope by Nanometrics are used for linewidth measurements and visual inspection.

Electrical testing in wafer form is done in the Device Characterization Laboratory which is equipped with several probe stations with HP4145 Semiconductor Parameter Analyzers, HP4280 Capacitance Meter/C-V Plotters and associated instruments and computers to allow for detailed testing and data analysis. An electroglass automatic wafer tester with an HP computer is currently being programmed to provide another option for data collection.

#### Documentation

Operations in the Microlab are controlled by the Berkeley Laboratory Information System (BLIS) which was developed by C. Williams as part of Professor Hodges' Computer-Integrated Manufacturing (CIM) project.<sup>10</sup> The user interface and command interpreter software, called the Wand, has provisions for keeping records such as processing data, equipment operating manuals, etc., along with a host of other capabilities. Thus, all pertinent information is kept on the Wand, which is accessible to all users.

The manual on the Wand contains operating instructions for all equipment in the lab; chemical safety data; process modules for 4" silicon wafer processing (see Appendix V) and standard MOS process outlines as shown in Appendices I-IV. Students use their lab computer accounts to maintain their own records. There is a joint account called "cmos" for the processing staff (in addition to their own) to record all information pertaining to staff projects. To facilitate uniform data entry, a shell script called the "hotpotato", similar to that used in the 290NO classes has been written by L. Lim. Each lot will have a new file and after a step has been completed, processing information is entered along with observations, measurements, etc. The "hotpotato" format and the shellscript listing is included in Appendix V.

#### Staff

The Microlab, which also provides a facility for III-V compounds and cryoelectronic device research along with silicon work, is supported by 12 full-time employees consisting of 5 maintenance technicians, a junior engineer responsible for facilities, with a development engineer as supervisor, a senior process engineer, who is also the lab manager with 3 processing assistants/associates, and an administrative assistant with part-time student help for office support. The Microlab is a separate cost center within ERL; with its own accounting, purchasing and billing. The processing assistants/associates carry out the work involved with the staff projects, provide operational maintenance and act as advisors/helpers to students who require it. A part-time student operates the ion implanter and another one provides software support.

The Faculty-in-charge, who is a professor chosen by the Director of ERL, acts as liaison between faculty and staff. He also plays an active role in overseeing the budget and in purchasing new equipment. His most important function, however, is to be the technical advisor for the staff's development work and to help to establish short and long term goals for the lab.

#### Summary and Proposals for Further Projects

This report is a simplified overview of the staff activities during the past two years in the Microfabrication Laboratory. It should answer several often heard questions: What processes is the staff working on? What standard processes are available for designers? How is such a facility operated?

Now that the standard processes are in place and the lab is operating in a steady state, more or less, further development work can be started. Due to limited resources, the staff cannot take on independent research contracts; projects are determined by need, requests from faculty or students suggesting joint projects, volunteering to do part of the work.

There are several possibilities for investigation. The most obvious approach would be to apply independently developed process steps, such as metal lift-off, 11 and contrast enhancement lithography, 12 boron diffusion from planar sources, 13 or those that are being developed, such as silicide application to the existing processes. With the recent acquisition of a 3-target sputtering system further exploration of multi-level metallization is within our reach. Bringing all the improvements together the design rules for the current processes could be scaled down. Developing a bipolar and/or bi-cmos process in the lab could also be a challenging goal and would expand our design capabilities considerably.

#### Acknowledgements

This development effort could not have been done without the dedicated work of the Microlab staff. They are: Don Rogers, now retired, former manager; Robert Hamilton and his maintenance group, Brad Bingham, Dick Chan, Phil Guillory, Steve Hoagland, Robert Norman, James Parrish; the processing group, Kim Chan, Marilyn Kushner, Robin Wallach; Rosemary Spivey in

the office, and the student helpers who worked part-time for the Microlab. Tom Booth. Thomas Coleman, Ron Johnson, Lyndon Lim, Martin Lim, Dave Mudie, Tom Muller, Gyula Nagy, and Joe Salazar.

Several graduate students were also instrumental in the successful implementation of the standard processes. They are: Chuck Dennison, Pei-Lin Pai, K. Y. Toh, Christopher Williams, Albert Wu and Konrad Young.

Finally, many thanks are due to the professors who built and supported the Microlab from the beginning and are continuously encouraging and appreciating the work being done there.

#### References

- 1. Peter Alexander Ruetz, "Architectures and Design Techniques for Real-Time Image Processing ICs," Memorandum No. UCB/ERL M86/37. Electronics Research Laboratory, University of California, Berkeley (May 1986).

- 2. W. G. Oldham et al., "Berkeley CMOS Process Test Patterns," Memorandum No UCB/ERL M84/26, Electronics Research Laboratory, University of California, Berkeley (March/June 1984).

- 3. W. G. Oldham et al., "Berkeley CMOS Process, a User's Guide," Memorandum No. UCB/ERL M84/84, Electronics Research Laboratory, University of California, Berkeley (October 1984).

- 4. Kai-Yap Toh, "Wide-Band, Low-Noise, Matched Impedance Amplifiers in Submicron MOS Technology," Memorandum No. UCB/ERL M86/78, Electronics Research Laboratory, University of California, Berkeley (September 1986).

- 5. Chorn-Kuang Wang, Rinaldo Castello, Paul R. Gray, "A Scalable High-Performance Switched-Capacitor Filter," *IEEE Transactions of Circuits and Systems* CAS-33(2) p. 167 (February 1986).

- 6. George Lewicki, "3 Micron CMOS P-Well Design Rules," Version 1.1. University of Southern California, Los Angeles (April 1985).

- 7. P. L. Pai, A. Chetly, R. Roat, N. Cox, C. Ting, "Material Characteristics of Spin-On Glasses for Interlayer Dielectric Applications," *Journal of the Electrochemical Society*, p. to be published (1987).

- 8. G. Billingsley and K. Keller, "KIC: A Graphics Editor for Integrated Circuits," Memorandum No. UCB/ERL M83/62, Electronics Research Laboratory, University of California, Berkeley (October 1983).

- 9. Katalin Voros, Pantas Sutardja, William G. Oldham, "A 10:1 photomask reduction camera," Proceedings of the Society of Photo-Optical Instrumentation Engineers 633 Optical Microlithography V p. 292 (March 1986).

- D. A. Hodges, C. Williams, T. Muller, L. A. Rowe, "Information Systems for Manufacturing," Unpublished Report. Electronics Research Laboratory, University of California, Berkeley (1986).

- 11.

P. L. Pai, W. G. Oldham, Metallization Approaches Using Lift-Off and Spin-On Glass, Submitted to the Symposium on VLSI Technology (1987).

- 12.

W. G. Oldham. "The Use of Contrast Enhancement Layers to Improve the Effective Contrast of Positive Photoresist," *IEEE Transactions on Electronic Devices* 2 p. 247 (February 1987).

- 13.

R. Alley, P. K. Ko, K. Voros, "Characterization of the BORON+ Planar Dopant Source Moisture Enhanced Process," Memorandum No. UCB/ERL M85/75, Electronics Research Laboratory, University of California, Berkeley (September, 1986).

## Appendix I

### **NMOS Process**

#### Microlab NMOS Process Version 1.1 (July, 1985)

| 0.0 <b>S</b> t | arting Wafers: 18-22 ohm-cm, P-type, <100>                                                                |

|----------------|-----------------------------------------------------------------------------------------------------------|

| 1.0 Bu         | ffer Oxide Growth: Target t <sub>ox</sub> = 400Å                                                          |

| 1.1            | TCA clean oxidation tube.                                                                                 |

| 1.2            | Standard clean wafers:piranha for 10 minutes 1:25 HF dip until hydrophobic                                |

| 1.3            | Dry Oxidation: 95 minutes dry O <sub>2</sub> 10 minutes N <sub>2</sub> anneal (ramp down)                 |

| 2.0 N          | itride Deposition: Target t <sub>nit</sub> = 1500Å                                                        |

| 2.1            | Standard clean wafers.                                                                                    |

| 2.2            | Deposit 1500Å of Si <sub>3</sub> N <sub>4</sub> : 25 minutes at 800°C.                                    |

| 3.0 A          | ctive Area Definition: Mask NACT                                                                          |

| 3.1            | Standard clean wafers.                                                                                    |

| 3.2            | HMDS: 1 minute Spin photoresist on Eaton: Kodak 820, 4600 RPM, 25 seconds soft bake at 120°C, 45 seconds  |

| 3.3            | Expose: GCA 6200 10x Wafer Stepper                                                                        |

| 3.4            | Develop: on MTI Omnichuck, Kodak 932:H <sub>2</sub> O=1:1, 60 seconds Inspect for alignment and exposure. |

| 3.6            | Descum: Technics-c. O <sub>2</sub> plasma. 300 mtorr. 50 Watts. 1 minutes                                 |

| 3.7            | Hard Bake: 20 minutes at 120°C in air                                                                     |

| 4.0 N          | itride Etch: Technics C, SF <sub>6</sub> :He, 35 Watts.                                                   |

| 5.0 <b>F</b>   | eld Ion Implantation                                                                                      |

| 5.1            | Boron (B <sup>11</sup> ), 100 KeV, 6 x 10 <sup>12</sup> /cm <sup>2</sup> , angle of incidence: 7°         |

| 5.2<br>C       | Resist strip: plasma ash resist in Technics-c: 2, 300 Watts, 7 minutes. Piranha clean in sink 8.          |

| 6.0 L          | ocos Oxidation: Target t <sub>ox</sub> = 7500Å                                                            |

| 6.1            | TCA clean wet oxidation tube.                                                                             |

| 6.2            | Standard clean wafers. 1:25 HF dip. 30 seconds.                                                           |

|                |                                                                                                           |

| 6.3 Wet Oxidation at 950°C: 5 min dry O <sub>2</sub> 5 hrs 30 min wet O <sub>2</sub> 20 min N <sub>2</sub> anneal t <sub>ox</sub> =                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.0 Nitride Removal                                                                                                                                                                                                                                                 |

| 7.1 Oxide dip: 1:25 HF, 2 minutes.                                                                                                                                                                                                                                  |

| 7.2 Hot phosphoric acid etch (155°C) for approx. 30 minutes (Do not dip off pad oxide.)                                                                                                                                                                             |

| 8.0 Depletion Photo: Mask DEPI Normal exp. time and focus. Inspect, descum, hard bake.                                                                                                                                                                              |

| 9.0 Depletion Implant                                                                                                                                                                                                                                               |

| 9.1 As, 200 KeV. Split lot into 3 for doses as follows:  a) 2.0 x 10 <sup>12</sup> /cm <sup>2</sup> b) 2.5 x 10 <sup>12</sup> /cm <sup>2</sup> c) 3.0 x 10 <sup>12</sup> /cm <sup>2</sup>                                                                           |

| 9.2 Remove resist and piranha clean wafers.                                                                                                                                                                                                                         |

| 9.3 Strip off pad oxide in 1/10 HF until back side is clear.  Do a 10 second overetch.                                                                                                                                                                              |

| 10.0 Gate Oxidation: Target t <sub>ox</sub> = 200Å                                                                                                                                                                                                                  |

| 10.1 Standard clean wafers, 1:25 HF dip for 30 seconds                                                                                                                                                                                                              |

| 10.2 TCA clean gate oxidation tube.                                                                                                                                                                                                                                 |

| 10.3 Dry oxidation at 950°C: 40 min dry O <sub>2</sub> 20 min N <sub>2</sub> anneal (no ramp down) t <sub>ox</sub> =                                                                                                                                                |

| 11.0 Thin Polysilicon: t <sub>poly</sub> = 500Å                                                                                                                                                                                                                     |

| 11.1 Immediately after gate oxide deposit 500Å of poly-Si                                                                                                                                                                                                           |

| 12.0 Threshold Adjust Implant Blanket implant. B <sup>11</sup> , 50KeV (Each group from depl. impl. will receive 3 different doses a) 4.0 x 10 <sup>11</sup> /cm <sup>2</sup> b) 6.0 x 10 <sup>11</sup> /cm <sup>2</sup> c) 8.0 x 10 <sup>11</sup> /cm <sup>2</sup> |

| 13.0 Buried Contact Photo: Mask BCON Increase exposure by 10%.                                                                                                                                                                                                      |

| 13.1 Standard clean.                                                                                                                                                                                                                                                |

| 13.2 Dehydrate wafers at 750°C for 5 minutes.                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------|

| 13.3 HMDS, spin, expose, develop, inspect, descum, hard bake.                                                               |

| 14.0 Thin Poly-Si Etch Etch rate ~ 100Å/second. Etch 10 seconds+ 2 seconds overetch.                                        |

| 15.0 Oxide Etch                                                                                                             |

| 15.1 Etch in 5:1 BHF for 45 seconds Wet wafers before etching.                                                              |

| 15.2 Remove resist, piranha clean in sink 8.                                                                                |

| 16.0 Gate Poly-Si Deposition: target t = 4500Å                                                                              |

| 16.1 Standard clean, 1:25 HF dip. 30 seconds (or until dewets). *It is crucial that there be no oxide left in the contacts. |

| 16.2 Deposit gate poly-Si: 4500Å                                                                                            |

| 17.0 Gate Definition Photo: Mask NPLY                                                                                       |

| 17.1 HMDS, spin, expose, develop, inspect, descum, hardbake.                                                                |

| 18.0 Polysilicon Etch                                                                                                       |

| 18.1 Plasma etch poly-Si in LAM.                                                                                            |

| 18.2 Remove photoresist. Piranha clean for 5 minutes                                                                        |

| 19.0 Source/Drain Implant: As, 180 KeV, 5 x 10 <sup>15</sup> /cm <sup>2</sup>                                               |

| 20.0 Reoxidation and Activation                                                                                             |

| 20.1 TCA clean oxidation tube.                                                                                              |

| 20.2 Standard clean, 1:25 HF dip, 30 seconds.                                                                               |

| 20.3 Reoxidize gate and S/D areas 950°C: 30 minutes dry O <sub>2</sub> 20 minutes N <sub>2</sub> anneal                     |

| 21.0 <b>PSG Deposition</b> : Target t <sub>PSG</sub> = 8000Å<br>Deposit 8000Å PSG.                                          |

| 22.0 Densification<br>950°C. 30 minutes wet O <sub>2</sub>                                                                  |

| 23.0 Contact Photo: Mask CONT Increase exposure time by 25%. Immersion develop.                                             |

| 23.2 Do an etch-bake-etch sequence.                                                                                         |

| 23.2 Plasma strip photoresist. Piranha clean. 1:25 HF dip. 30 seconds                                                       |

| OPTIONAL: 24.0 Polysilicon Deposition                                                                |

|------------------------------------------------------------------------------------------------------|

| 24.1 Deposit thin poly-Si: 500Å                                                                      |

| 24.1 Anneal: Anneal at 900°C, 30 min N <sub>2</sub> .                                                |

| 25.0 Metallization: Target t <sub>Al</sub> = 0.7 micron. Sputter on Al/2% Si.                        |

| 26.0 Metal Photo: Mask METL                                                                          |

| 26.1 HMDS, spin, expose, develop, inspect, descum, hard bake. Reduce exposure time by 20%            |

| 26.2 Wet etch aluminum.                                                                              |

| OPTIONAL: 27.0 Polysilicon Etch: Wet etch for 15 seconds.                                            |

| 28.0 Backside Etch                                                                                   |

| 28.1 Spin protective photoresist on front side twice, with hard bake after each coat of photoresist. |

| 28.3 Etch oxide in 5:1 buffered HF until down to poly-Si.                                            |

| 28.4 Wet etch poly-Si on back (gate poly-Si thickness).                                              |

| 28.5 Etch in 5:1 BHF until back clears.                                                              |

| 28.6 Strip front side photoresist in acetone or plasma O <sub>2</sub> . No piranha!                  |

| 30.0 Sintering: Sinter in forming gas for 20 minutes, 400°C.                                         |

| End of Process                                                                                       |

Original Process: Ping K. Ko Modified by Ping Li (2/7/85) and K. Voros (7/19/85)

#### Microlab NMOS Process

#### Mask Descriptions:

1. Active Area: NACT (cf-emulsion)

2. Depletion Implant: DEPI (df-chrome)

3. Buried Contact: BCON (df-chrome)

3. Buried Contact: BCON (df-chrome)4. Gate Definition: NPLY (cf-emulsion)

5. Contact: CONT (df-chrome)

6. Metal: METL (cf-emulsion)

#### Ion Implantations:

1. Field Implant: Boron (B<sup>11</sup>), 100 KeV, 6.0 x 10<sup>12</sup>/cm<sup>2</sup>

2. Depletion Implant: Arsenic (As<sup>+</sup>), 200 KeV, 2.5 x 10<sup>12</sup>/cm<sup>2</sup>

3. Threshold Implant: (Blanket) Boron (B<sup>11</sup>), 50 KeV, 6.0 x 10<sup>11</sup>/cm<sup>2</sup>

4. Source/Drain Implant: Arsenic (As<sup>+</sup>), 180 KeV. 5.0 x 10<sup>15</sup>/cm<sup>2</sup>

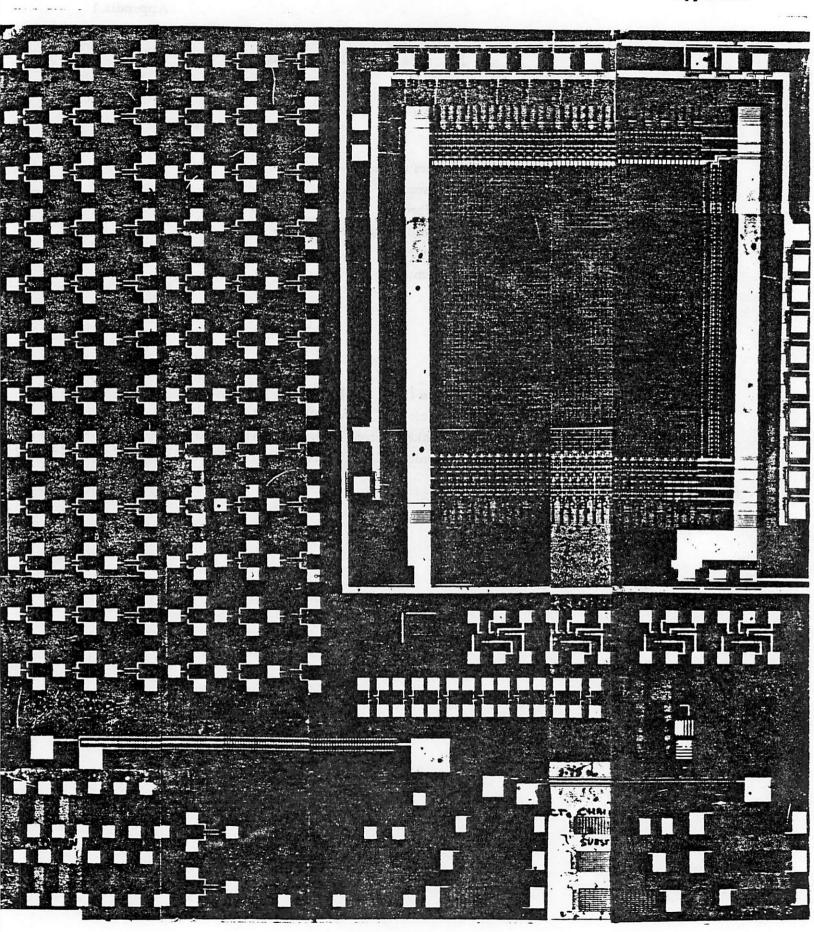

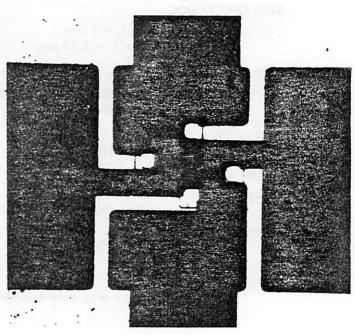

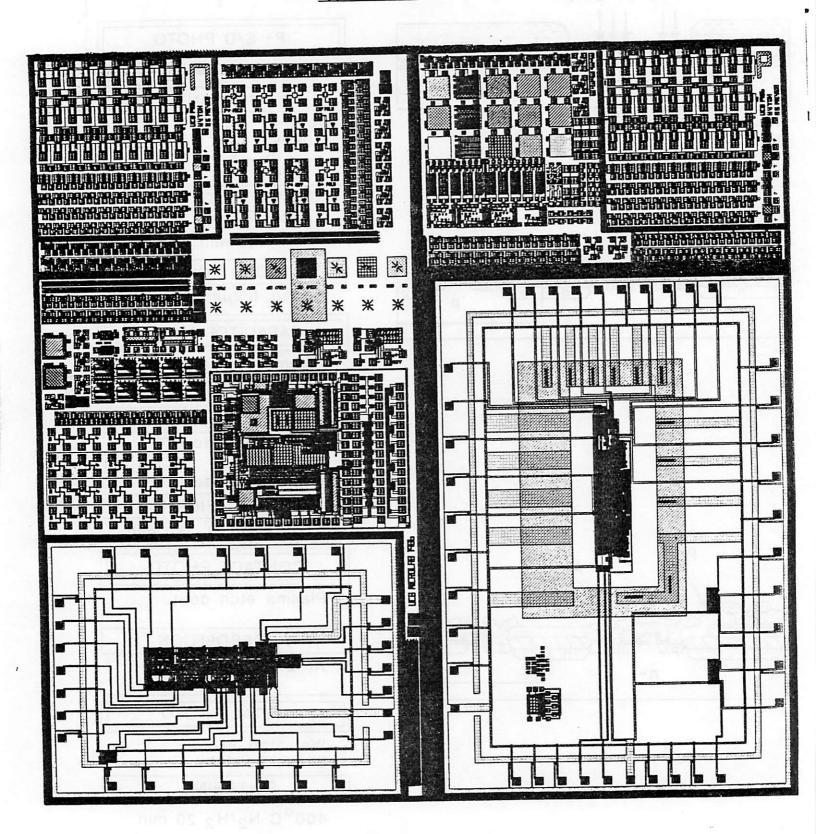

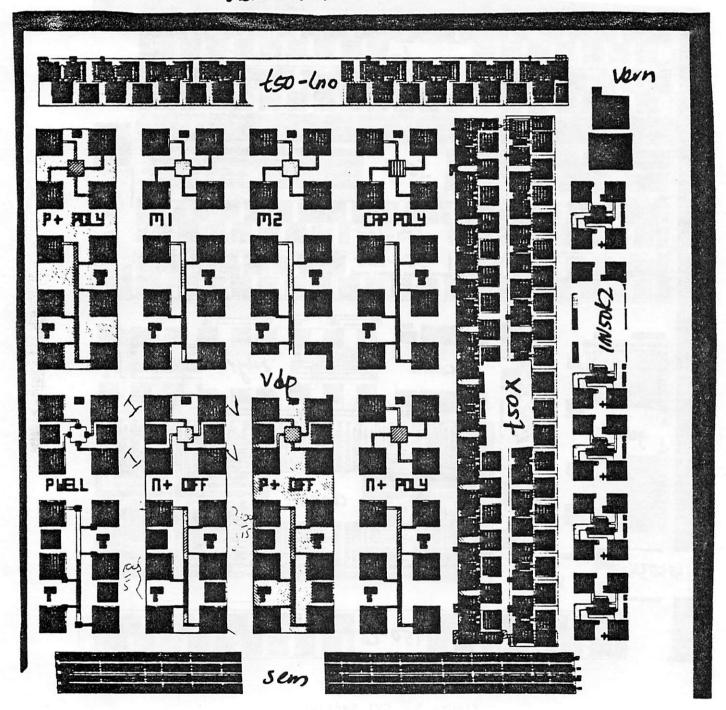

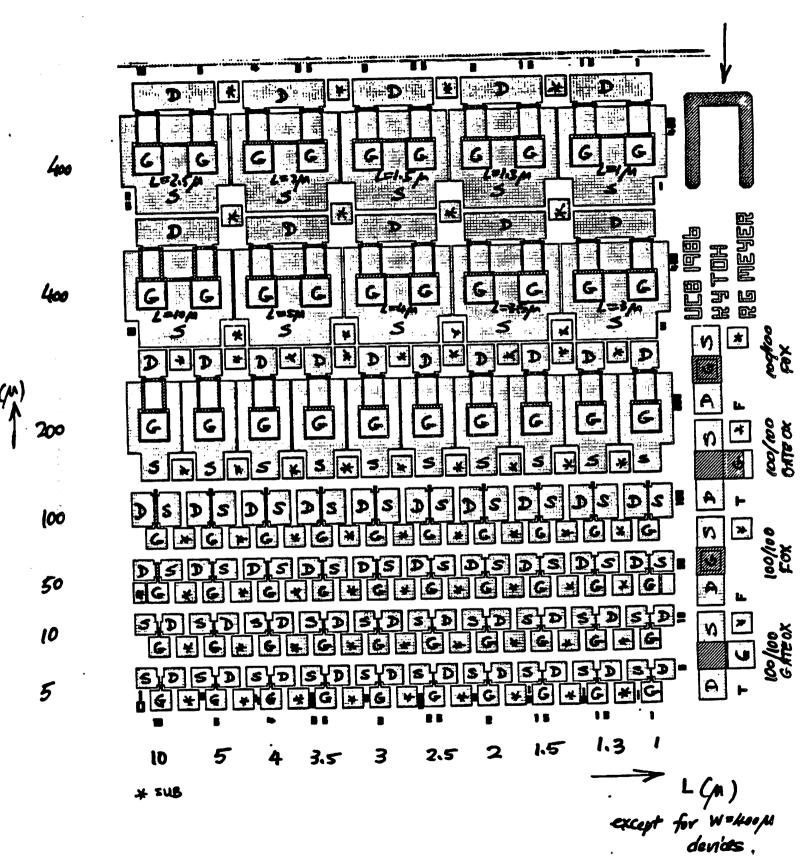

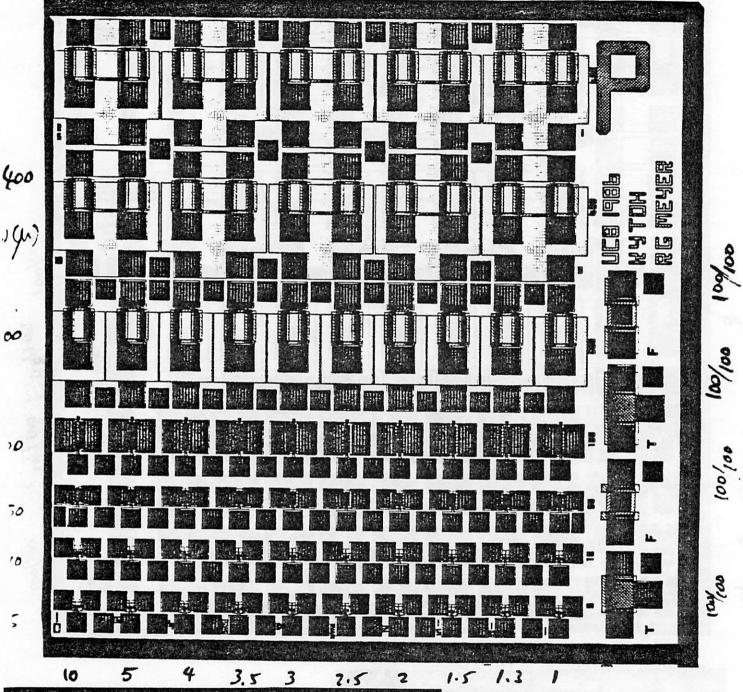

Figure 1. Berkeley NMOS Test Chip

#### NMOS Test Chip Device Listing

Test Transistors: (starting from upper left-hand corner)

3 columns of depletion mode NMOS transistors:  $W = 10, 50, 100 \mu m$

3 columns of enhancement mode NMOS transistors:  $W = 10, 50, 100 \mu m$

Each column has varying gate lengths starting from the top:

$L = 0.75, 1.0, 1.25, 1.5, 1.75, 2.0, 2.5, 3.0, 4.0, 5.0, 6.0, 10.0 \mu m$

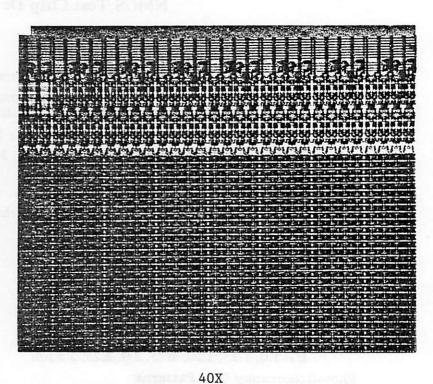

FIFO Test Circuit:

512 x 8 bit RAM (see Reference 1).

$L = 3 \mu m$ , contacts:  $2 \mu m \times 2 \mu m$ , metal pitch:  $9.0 \mu m$

Alignment Verniers:

$0.1 \mu m$  steps.  $\pm 1 \mu m$  total

Amplifiers:

4 differential pairs:

$L_1 = 8 \mu m$  on all  $L_2 = 8 \mu m$  on all

7 Inverters:

$L = 1.0, 1.25, 1.50, 1.75, 2.0, 2.25, 2.5 \mu m$

Photolithography Test Patterns:

contact holes to substrate and to poly-silicon:  $2 \times 2$ ,  $2.5 \times 2.5$ ,  $3 \times 3$ ,  $4 \times 4$ ,  $5 \times 5 \mu m$ ; elbows and line space test patterns

Ring Oscillators:

(left) 200 stage,  $L=2 \mu m$ (right) 200 stage,  $L=1.75 \mu m$

Resistors: (from left)

2 columns poly-silicon, 2 columns depletion implant, 2 columns substrate:

5  $\mu$ m lines; 323  $\square$  total.

2 Field Transistors:

$W = 100 \mu m$ ,  $L = 10 and 7 \mu m$

Diode: substrate/n+

2 Capacitors:

depletion implant gate oxide/poly, field oxide/poly, 430  $\mu$ m x 250  $\mu$ m

Large Transistor:

$L = 200 \ \mu m$ ,  $W = 350 \ \mu m$

Contact Chains:

$2 \times 2 \mu m$  contacts: 3 to poly-silicon, 3 to substrate, 3 buried contacts

Designed by P. Li (January 1985)

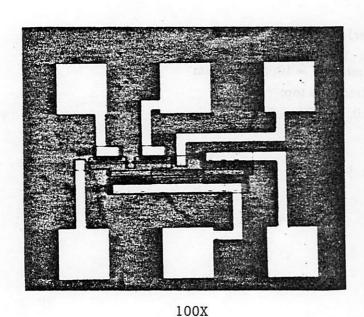

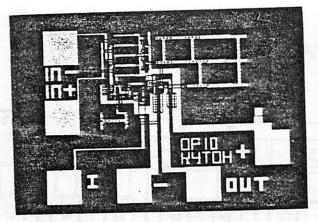

Differential Amplifier

Section of FIFO Test Circuit

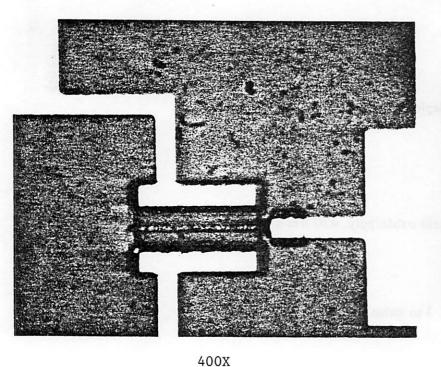

NMOST

400X

Inverter

Variable1:

VD -Ch1

Linear sweep

Start .0000V

Stop 8.0000V

Step .2000V

Variable2: VG -Ch4 Start .0000V Stop 7.0000V Step 1.0000V

Constants:

VS -Ch2 .0000V

VSUB -Ch3 .0000V

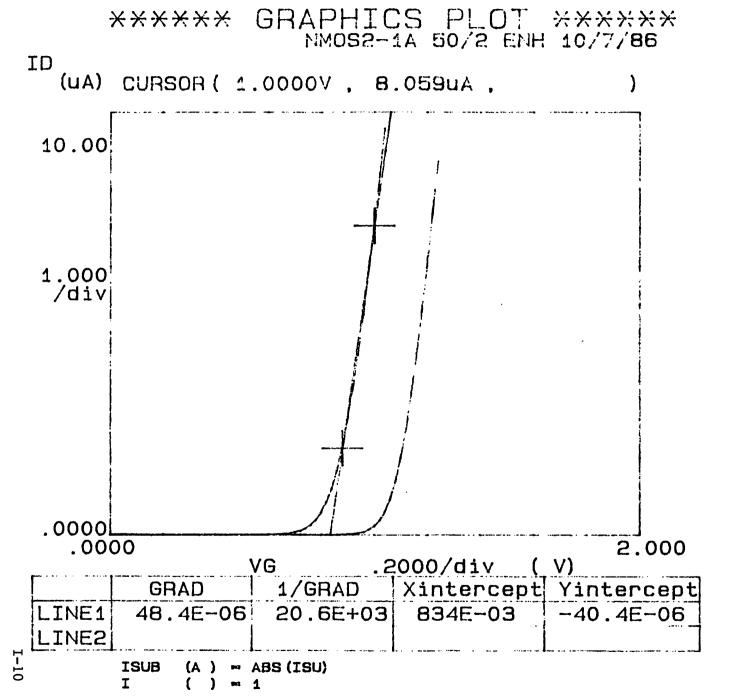

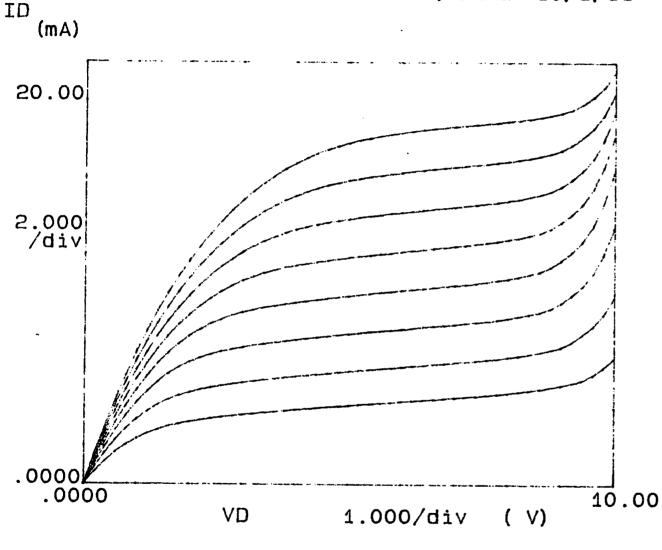

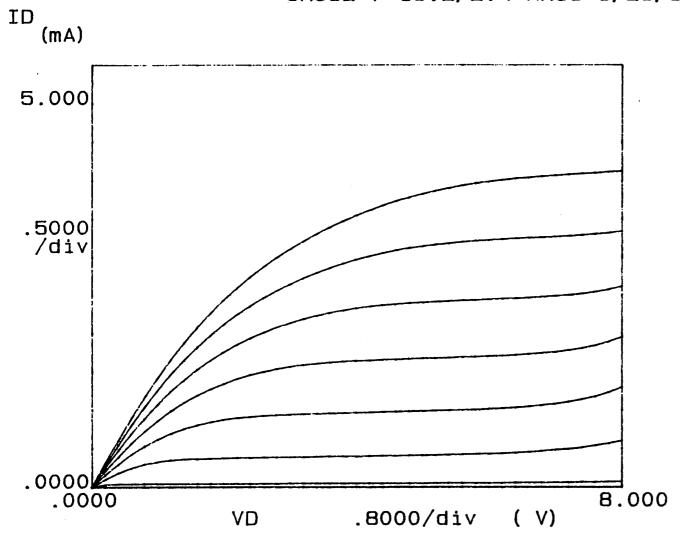

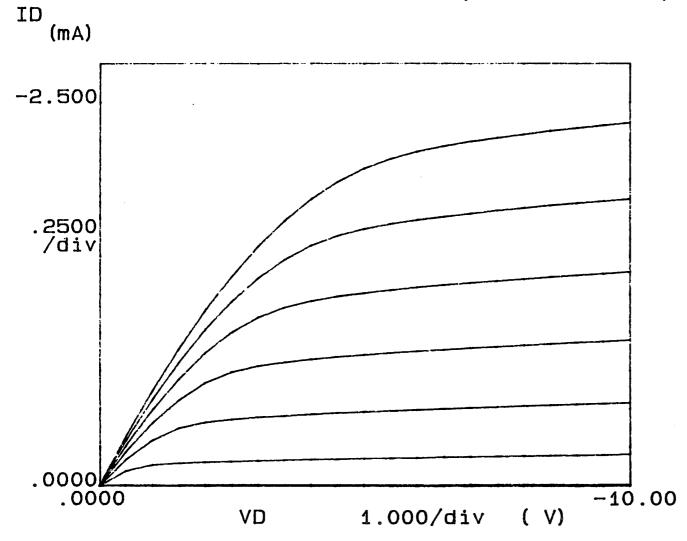

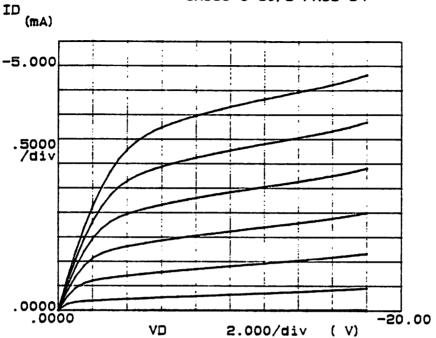

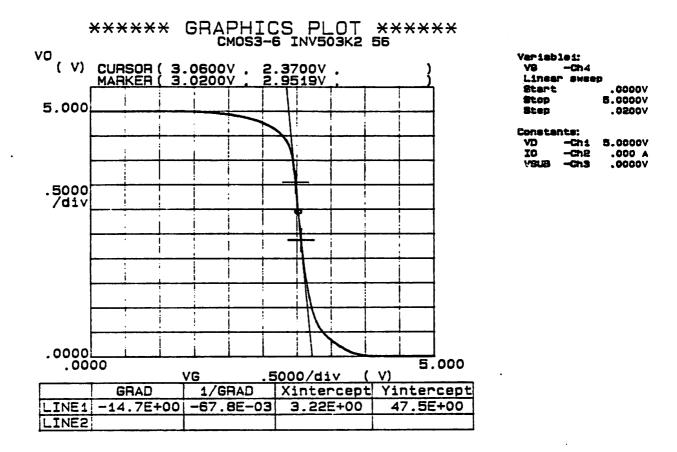

Figure 3a. NMOS2-1A W=50um; L=2um

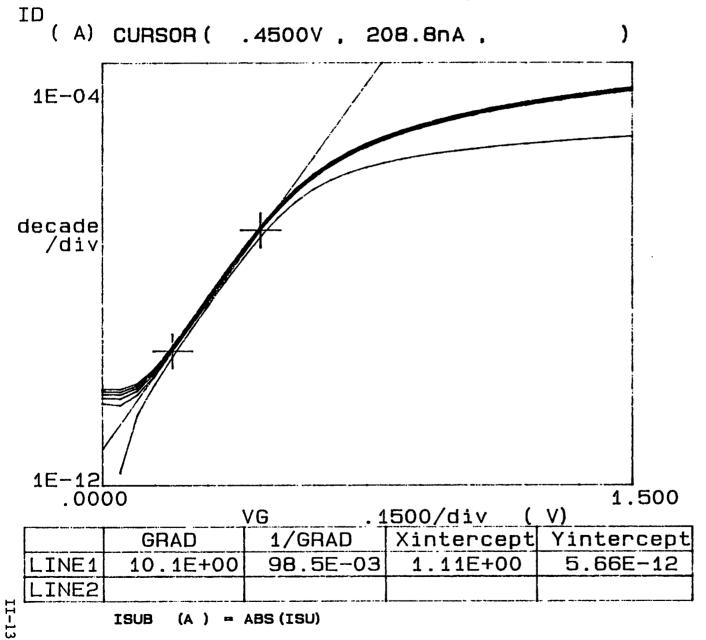

Variable1: VG -Ch4 Linear sweep Start .0000V Stop 2.0000V Step .0200V Variable2: YSUB -Ch3 Start .0000V Stop -1.0000V Step ~1.0000V Constants: VD -Ch1 .0500V -Ch2 .0000V VS

-Vs1

.0000V

V1

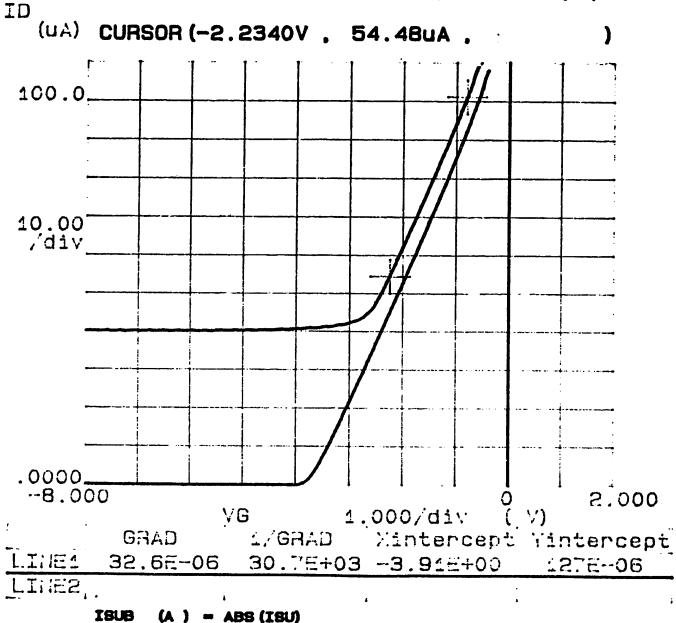

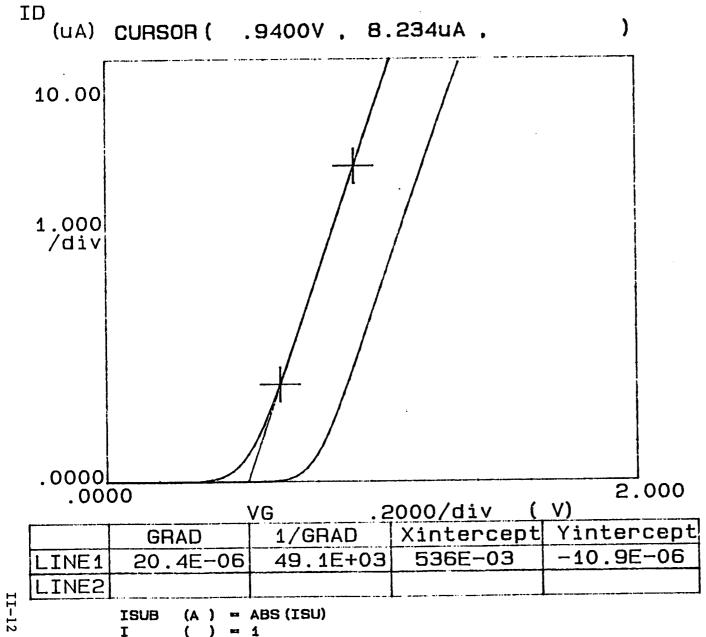

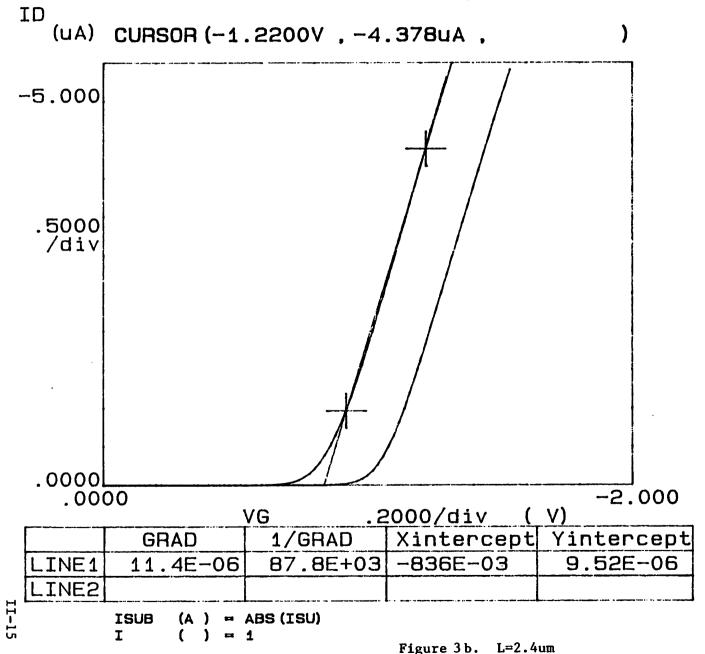

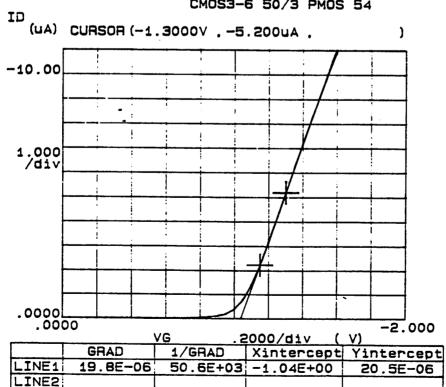

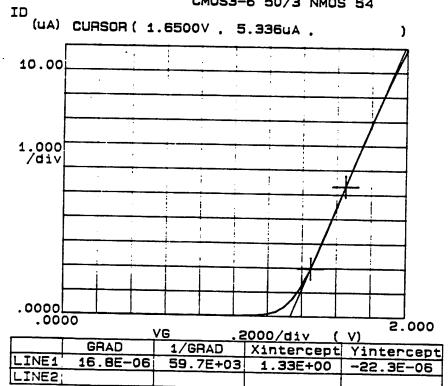

Figure 3b. L=2um Enhancement Mode Device V<sub>+</sub>= 0.83 V

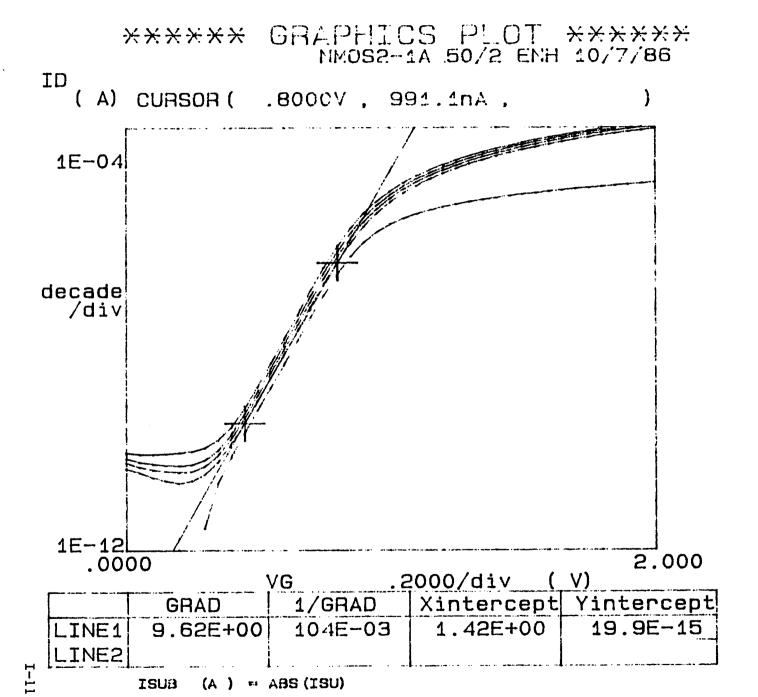

Variable1:

Start

Stop

Step

VD Start

Stop

Step

VS

Variable2:

Constants:

VSUB -Ch3

-Ch4

-Ch1

-Ch2

.0000V

.0500V

.0500V

5.0490V

1.0000V

.0000V

.0000V

Linear sweep

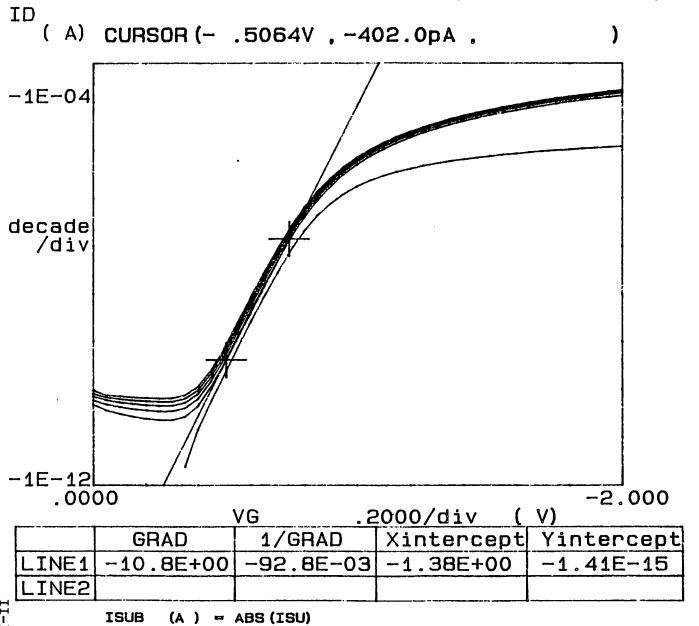

Figure 3c. Subthreshold Current Characteristics of 2um Enhancement Mode Device

Figure 3d. L=1.25um Enhancement Mode Device

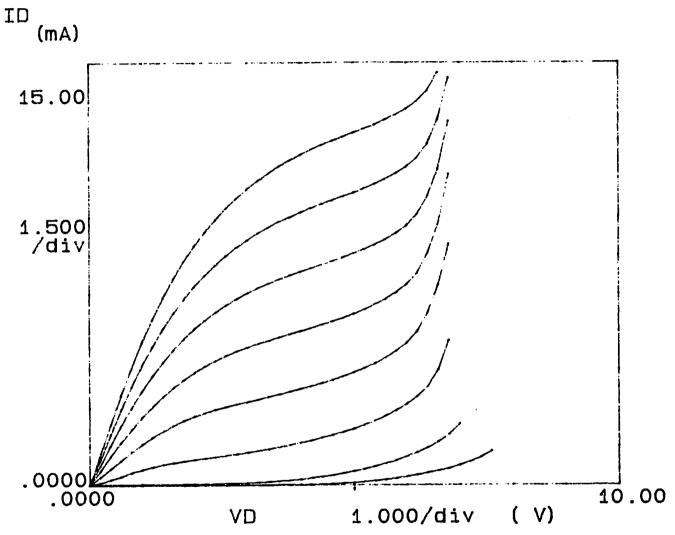

Variable1: VD -Ch1 Linear sweep Start .0000V 10.000V Stop .2000V Step Variable2: VG -Ch4 Start .0000V Stop 7.0000V 1.0000V Step Constants: -Ch2 .0000V VS

-Ch3

.0000V

VSU8

ROUT  $(\Omega) = \Delta VD/\Delta ID$ GD  $(/\Omega) = \Delta ID/\Delta VD$

Variable1: VD -Ch1 Linear sweep

Start .0000V Stop 10.000V Step . 5000A

Variable2: ٧G -Ch4

Start .0000V Stop 7.0000V Step 1.0000V

Constants:

VS -ch2 .0000V VSUB -Ch3 .00007

Figure 4a. NMOS2-1A L=2um Depletion Mode Device

Threshold Implant:  $4 \times 10^{11}/\text{cm}^2$

Depletion Implant:  $2 \times 10^{12}/\text{cm}^2$

ROUT

9D

- AVD/AID

$(/\Omega) = \Delta ID/\Delta VD$

Variable1:

VB -Ch4

Linear sweep

Start -8.0000V

Stop 2.0000V

Step .0500V

Variable2: VSUB -Ch3 Start .0000V Stop -1.0000V Step -1.0000V

VD -Ch1 .0500V V8 -Ch2 .0000V V1 -Vs1 .0000V

Appendix

1

# Appendix II N-Well CMOS Process

Microlab CMOS Process

Modified 290NO process: Version 1.2 (Feb. 5, 1986)

3 um, N-well, single poly-Si, single metal

| 1.0 Starti          | ng Wafers: 18-22 ohm-cm, p-type, <100>                                                                                                                                                      |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0 Initia          | l Oxidation: target = 1000Å                                                                                                                                                                 |

| 2.1 TO              | CA clean furnace tube.                                                                                                                                                                      |

|                     | andard clean wafers: piranha clean for 10 minutes. 10/1 HF dip, spin-dry. lude one p-type control: WELL.                                                                                    |

|                     | et oxidation at 1000°C:  5 minutes dry O <sub>2</sub> 11 minutes wet O <sub>2</sub> 5 minutes dry O <sub>2</sub> 20 minutes dry N <sub>2</sub> asured t <sub>ox</sub> on WELL cont.         |

| •.•                 | Photo: Mask-WELL Il wafers are not included in the photoresist steps.                                                                                                                       |

| 3.1 Sp              | oin resist on Eaton: Kodak 820, 4600 RPM, 25 seconds, soft bake at 120°C, 45 seconds                                                                                                        |

| 3.2 Ex              | rpose: GCA 6200-10X wafer stepper                                                                                                                                                           |

| 3.3 D               | evelop in MTI-Omnichuck: Kodak 932/H2O=1:1, 60 seconds                                                                                                                                      |

| 3.4 D               | escum in TechnicsC: O <sub>2</sub> plasma, 50 W, 1 minute                                                                                                                                   |

| 3.5 H               | ard bake in oven: 120°C, 20 minutes in air.                                                                                                                                                 |

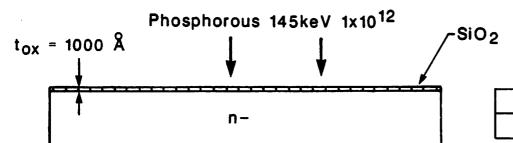

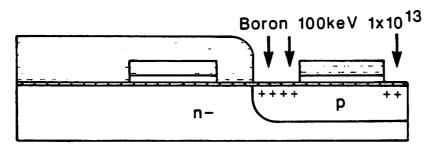

| 4.0 Well<br>(Resist | Implant: phosphorus. $4x10^{12}/cm^2$ , 150 KeV is left on wafers.) Include WELL control (no resist).                                                                                       |

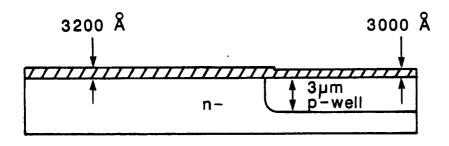

| 5.0 Well            | Drive-In: target $x_j = 3$ um, $t_{ox} = 3000$ Å                                                                                                                                            |

| 5.1 To              | CA clean furnace tube.                                                                                                                                                                      |

| 5.2 E               | tch pattern into oxide in 5/1 BHF. Include WELL control.                                                                                                                                    |

| 5.3 R               | emove resist and piranha clean wafers.                                                                                                                                                      |

| 5.4 St              | andard clean wafers, include WELL control.                                                                                                                                                  |

| a)                  | ry oxidation and drive at 1150°C:  4 hrs dry O <sub>2</sub> 4 hrs dry N <sub>2</sub> Measured t <sub>ox</sub> = on WELL control  Scribe chip off of WELL control; measured x <sub>j</sub> = |

|                                | TOTAL TOTAL CONTRACTOR AND ADMINISTRACTOR AND ADMINISTRACTOR AND ADMINISTRACTOR A |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1<br>                        | TCA clean furnace tube.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                | Remove all oxide in 5/1 BHF until wafers dewet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | Include WELL control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.3                            | Standard clean wafers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.4                            | Dry oxidation at 950°C:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                | 28 minutes dry O <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                | 20 minutes dry N <sub>2</sub> anneal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                | a) Measured t <sub>ox</sub> on WELL control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                | b) Strip oxide off of WELL control in BHF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

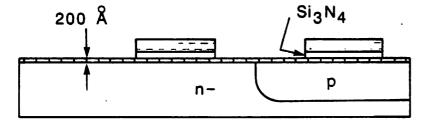

| 6.5                            | Deposit 1000Å of Si-nitride immediately:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                | Dep.time = 22 minutes temp.= 800°C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                | a) Include WELL control. Measured t <sub>nit</sub> =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                | b) Save WELL control for Step 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0 Ac                           | ctive Area Photo: Mask-ACTV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                | n, expose, develop, descum, hard bake.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                | and de Barke TechnicaC alegae etchan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |