## Copyright © 1986, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

ARCHITECTURES AND DESIGN TECHNIQUES FOR REAL-TIME IMAGE PROCESSING ICS

by

Peter Alexander Ruetz

Memorandum No. UCB/ERL M86/37 2 May 1986

# ARCHITECTURES AND DESIGN TECHNIQUES FOR REAL-TIME IMAGE PROCESSING ICS

by

Peter Alexander Ruetz

Memorandum No. UCB/ERL M86/37

2 May 1986

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

## Architectures and Design Techniques for Real-Time Image-Processing ICs

Ph.D.

Peter Alexander Ruetz

E.E.C.S.

#### **Abstract**

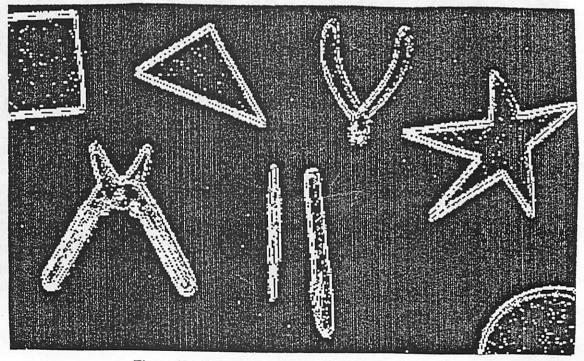

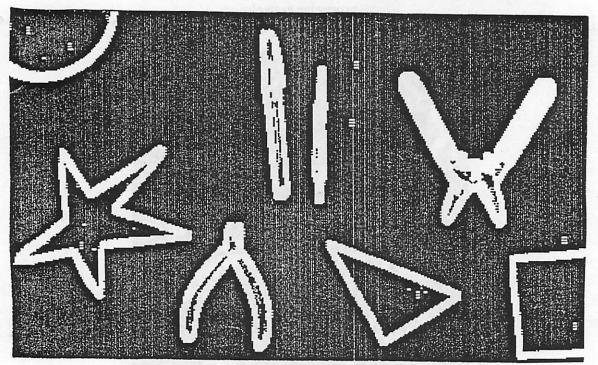

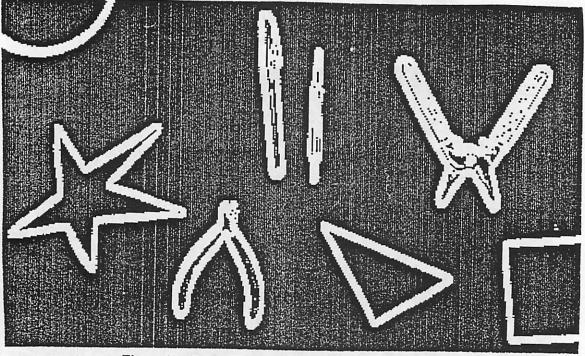

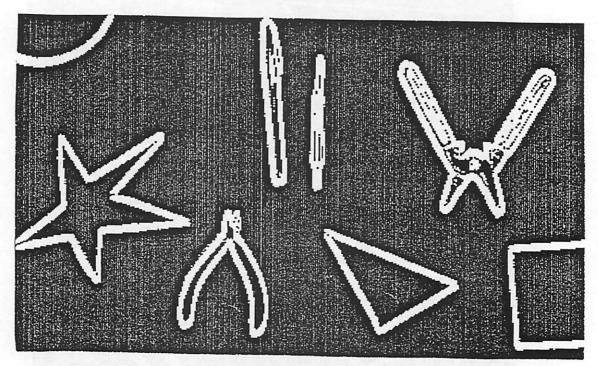

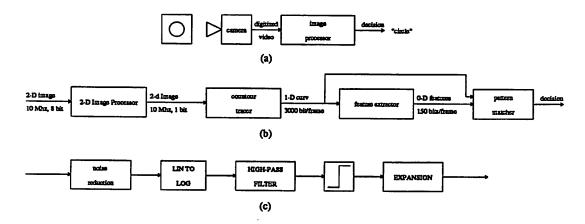

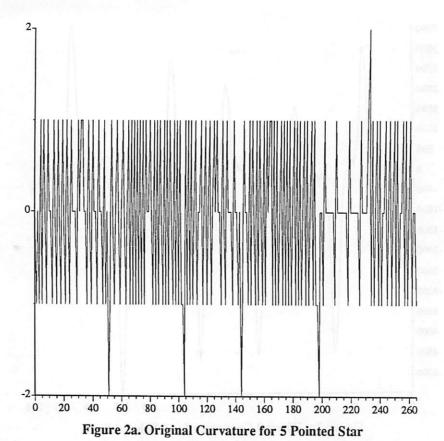

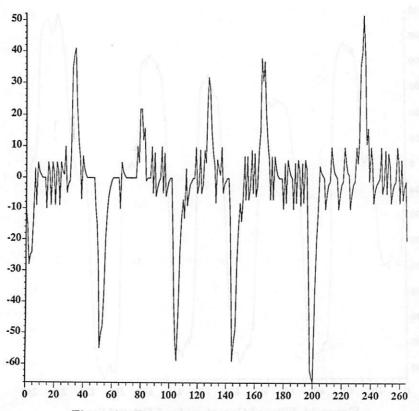

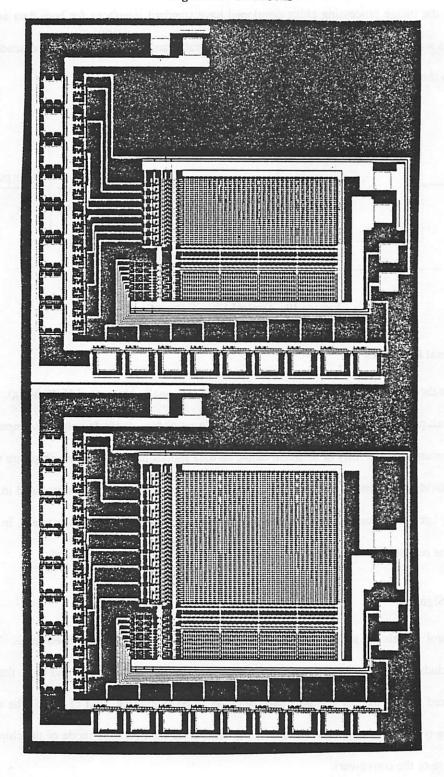

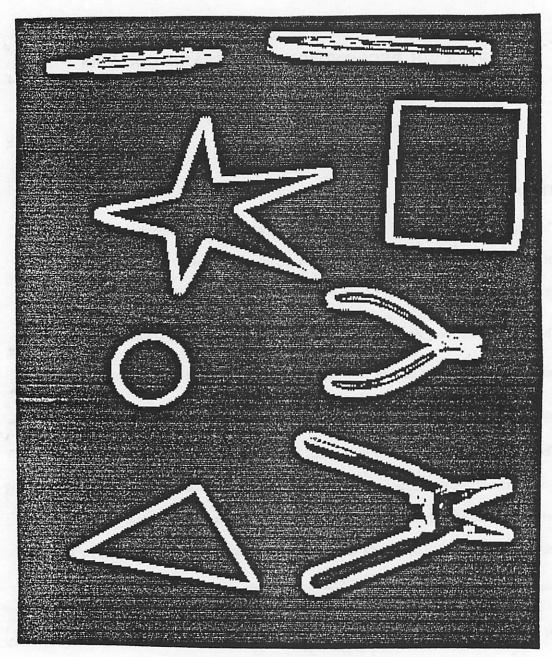

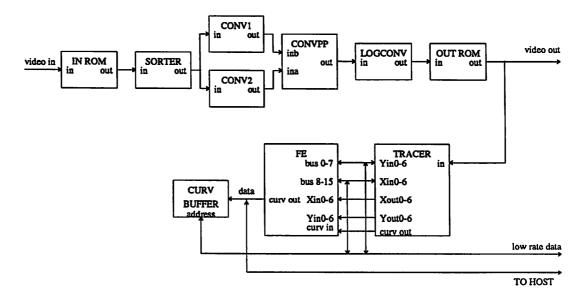

A set of 8 chips, which perform real-time image processing tasks, was designed and fabricated with a 4 $\mu$  NMOS technology. The chips include: a 3x3 linear convolver, a 3x3 sorting filter, a 7x7 logical convolver, a contour tracer, a feature extractor, a look-up-table ROM, and two post processors for the linear convolver. All chips were designed using architectures that are dedicated to the particular image processing task to be performed. The image processing circuits operate on 10 MHz video data (512 x 512 pixel images). The design time for the chips was kept to 1.5 man years by re-using hardware and, in addition, utilizing and developing some appropriate CAD tools. ROM generators and a data-path generator were developed to reduce the circuit design time. An image recognition system was built with these custom chips that can recognize two-dimensional objects that are characterized by their closed outer contours. The complete system is controlled by a SUN work station and operates at rates up to 15  $\frac{frames}{Sec}$ . The recognition system achieved a 97% recognition rate for 8 objects over a wide range of orientation and size variations and a 100% recognition rate without size variations.

Committee Chairman

## **Table of Contents**

| Acknowledgements                                           |

|------------------------------------------------------------|

| CHAPTER 1 INTRODUCTION                                     |

| 1.1 Applications                                           |

| 1.2 Computational Requirements                             |

| 1.3 Goals                                                  |

| 1.4 References                                             |

| CHAPTER 2 IMAGE PROCESSING REVIEW                          |

| 2.1 Introduction                                           |

| 2.2 Segmentation                                           |

| 2.3 Contrast Enhancement                                   |

| 2.4 Filtering                                              |

| 2.5 Noise Rejection                                        |

| 2.6 Edge Extraction                                        |

| 2.7 Edge Enhancement                                       |

| 2.8 Binary Transformations                                 |

| 2.9 References                                             |

| CHAPTER 3 IMAGE RECOGNITION TECHNIQUES                     |

| 3.1 Introduction                                           |

| 3.2 Raw Data to be Utilized                                |

| 3.3 The System                                             |

| 3.4 Recognition Features                                   |

| 3.5 References                                             |

| CHAPTER 4 HARDWARE CHOICES                                 |

| 4.1 Introduction4                                          |

| 4.2 Major Issues                                           |

| 4.3 Comparisons of Image Processor Performance             |

| 4.4 Dedicated Architectures for Space Efficient Processors |

| 4.5 References                                             |

| CHAPTER 5 DESIGN TECHNIQUES FOR FAST CIRCUIT DEVELOPMENT   |

| 5.1 Introduction                                           |

| 5.2 The Hardware Hierarchy                                 |

| 5.3 CAD Issues                                             |

| 5.4 Module Generation                                      |

| 5.5 Data-Path Generation                                   |

| 5.6 References                                             |

| CHAPTER 6 CIRCUITS                                         |

| 6.1 Introduction                                           |

| ······ ····· ···· ···· ·                                   |

| 6.2 Commonly Used Circuits                                       | 92  |

|------------------------------------------------------------------|-----|

| 6.3 Data-Path Cells                                              | 94  |

| 6.4 Central Storage Cells                                        | 102 |

| 6.5 References                                                   | 113 |

| CHAPTER 7 THE IMAGE PROCESSING ICs                               | 114 |

| 7.1 Introduction                                                 | 114 |

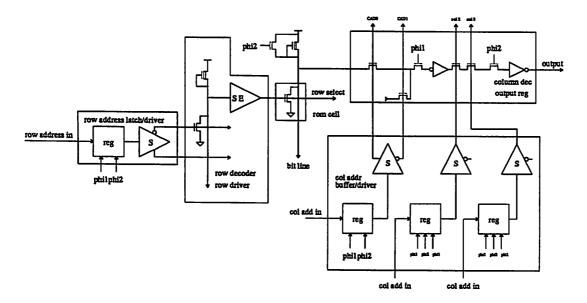

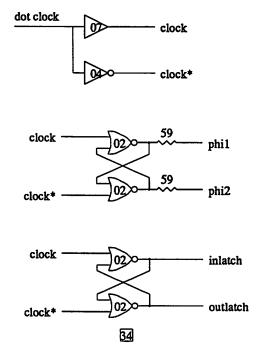

| 7.2 Image Processor Interfaces                                   | 126 |

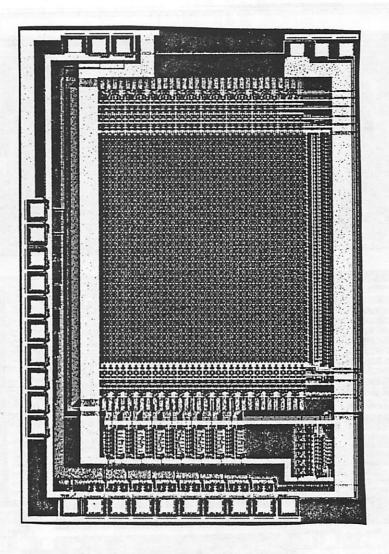

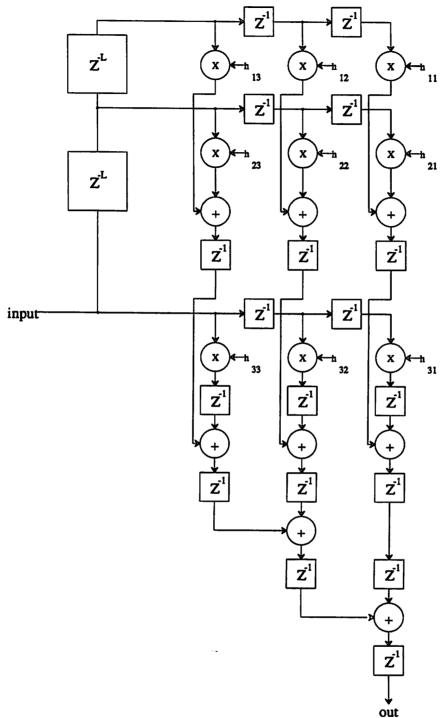

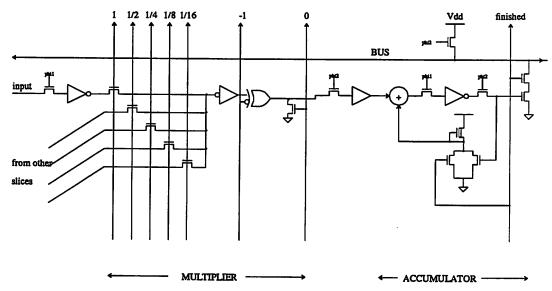

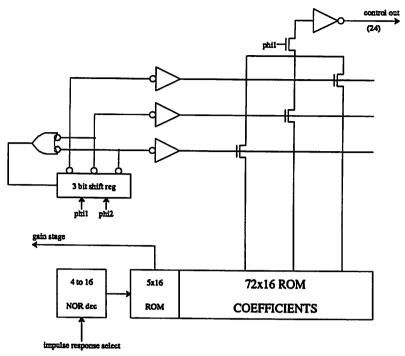

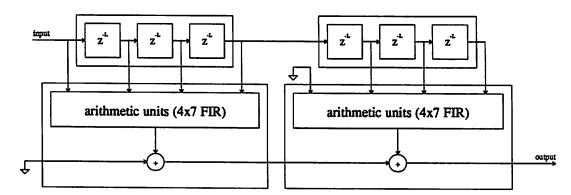

| 7.3 A Single Chip 3x3 Convolver                                  | 129 |

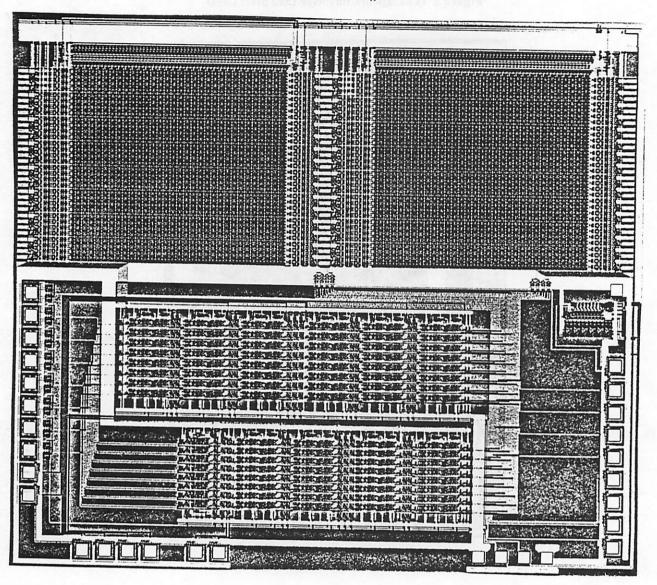

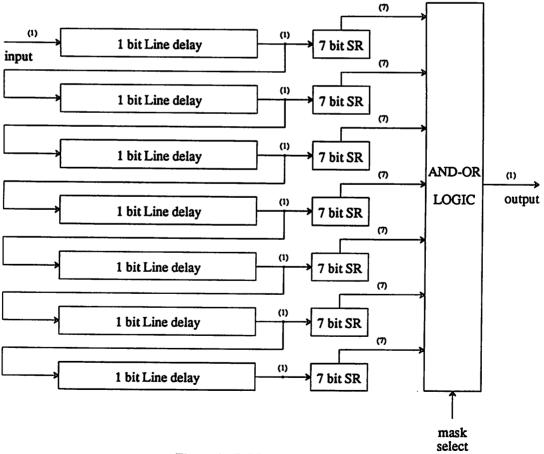

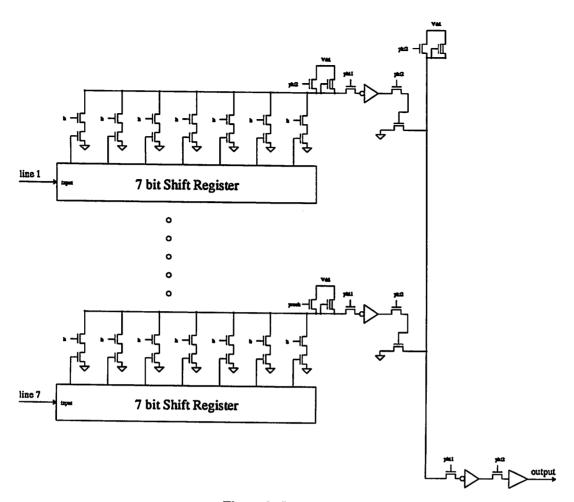

| 7.4 A 7x7 Logical Convolver                                      | 142 |

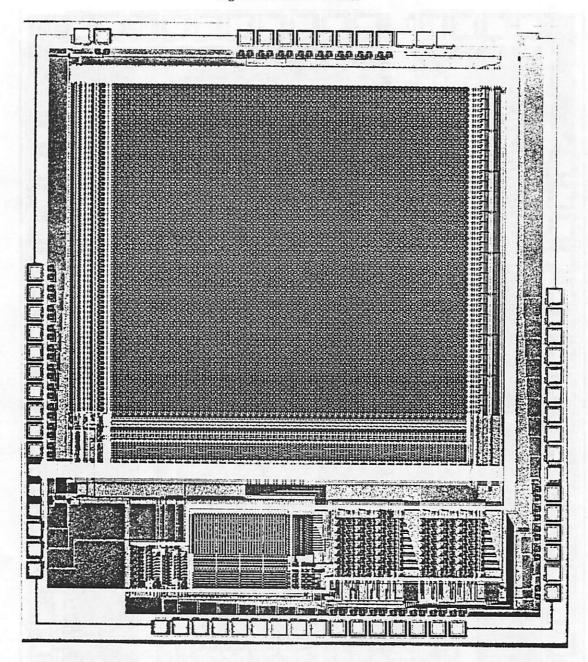

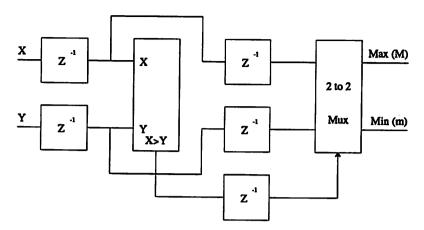

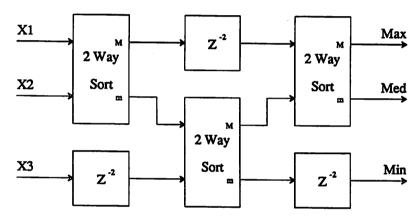

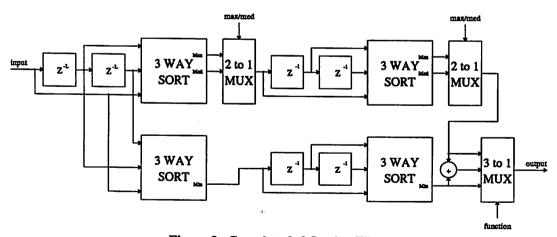

| 7.5 A 3x3 Non-Linear Filter Based on Sorting                     | 148 |

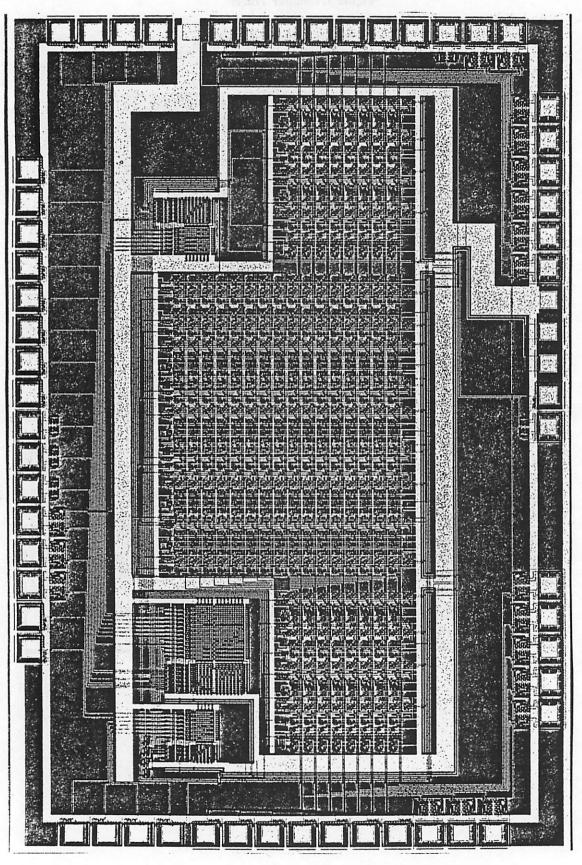

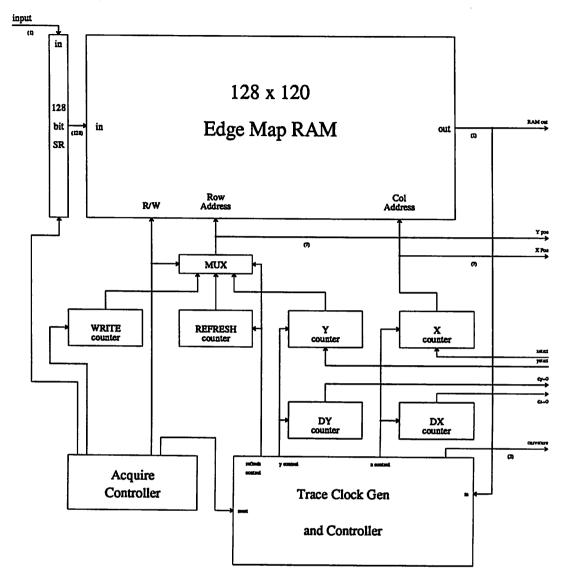

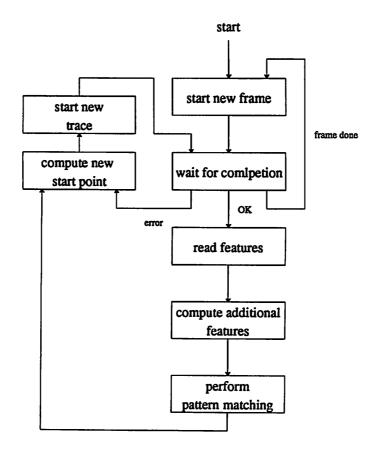

| 7.6 An Image Contour Tracing Chip                                | 154 |

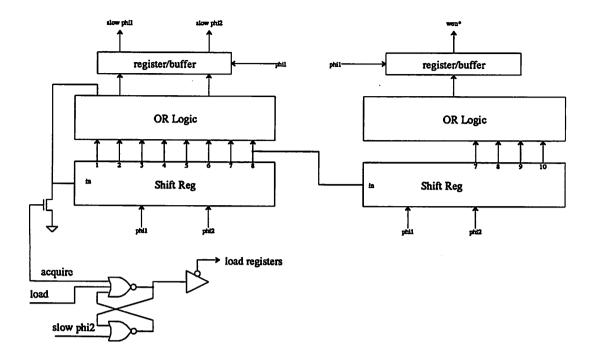

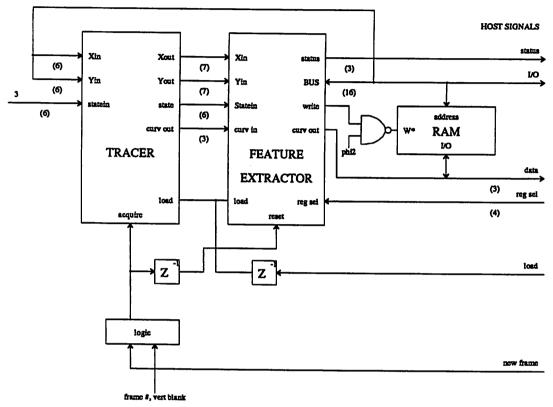

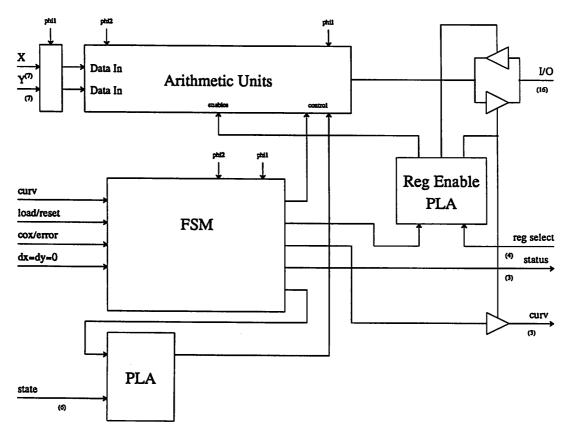

| 7.7 A Feature Extractor for the Image Contour Tracer             | 163 |

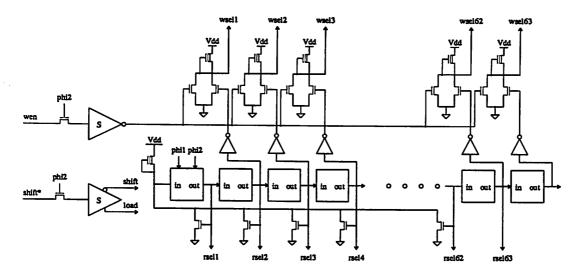

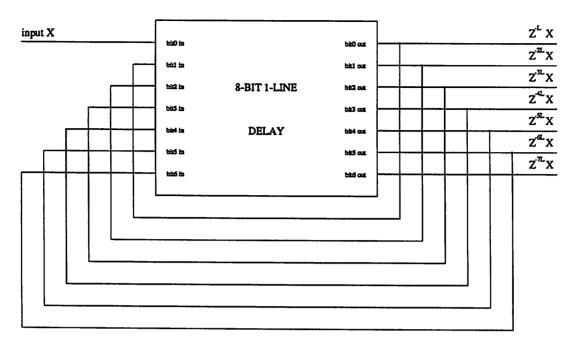

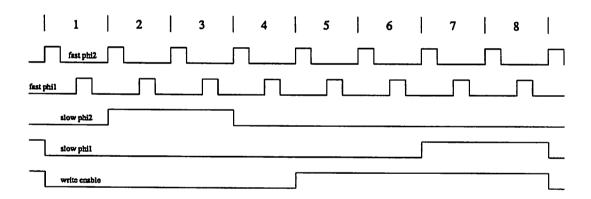

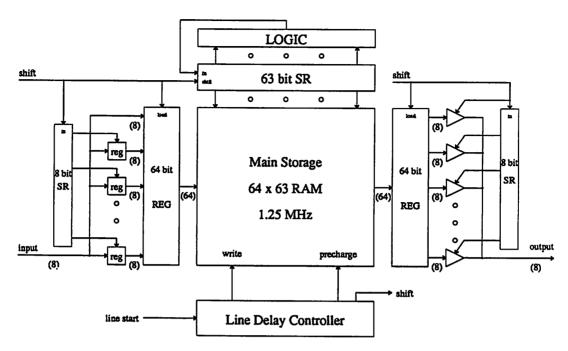

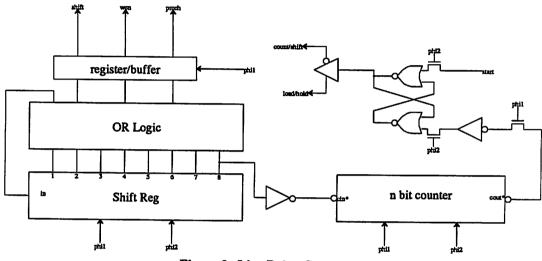

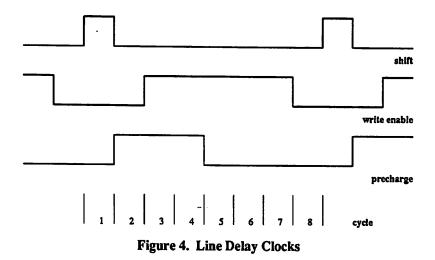

| 7.8 The Line Delay                                               | 173 |

| CHAPTER 8 RECOGNITION RESULTS AND ANALYSIS                       | 181 |

| 8.1 Introduction                                                 | 181 |

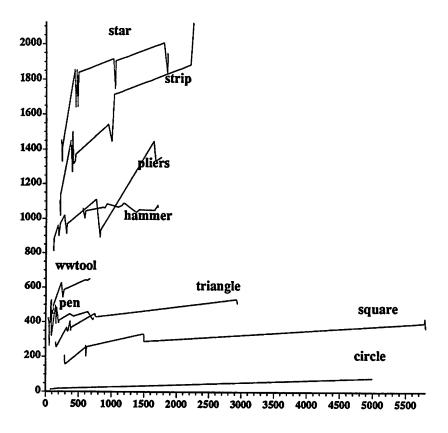

| 8.2 The Features                                                 | 183 |

| 8.3 Recognizer Operation                                         | 195 |

| 8.4 Recognition Results                                          | 197 |

| 8.5 More Constrained Recognition                                 | 198 |

| 8.6 Improving Recognition Accuracy                               | 203 |

| 8.7 Other Recognition Techniques                                 | 204 |

| 8.8 Conclusions                                                  | 208 |

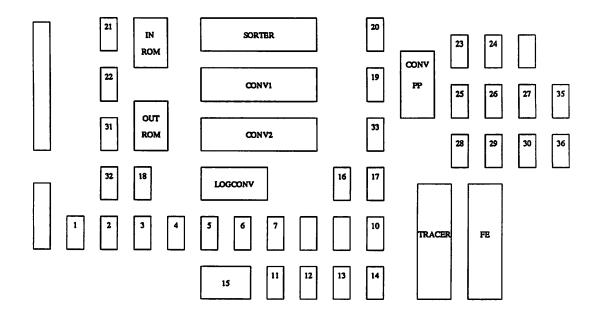

| APPENDIX A THE RECOGNITION BOARD                                 | 209 |

| A.1 Descriptions of Chip Signals                                 | 209 |

| A.2 Board Layout                                                 | 214 |

| APPENDIX B A COMPARISON OF STORAGE CELLS FOR DIGITAL SIGNAL PRO- | 217 |

| CESSING                                                          | 226 |

| B.1 Introduction                                                 | 226 |

| B.2 General Tradeoffs                                            | 226 |

| B.3 Distributed Storage                                          | 226 |

| B.4 Centralized Storage                                          | 227 |

| B.5 Making Choices                                               | 232 |

| B.6 Design Considerations                                        | 236 |

| APPENDIX C NMOS CIRCUIT LAYOUT GUIDELINES                        | 237 |

| C.1 Introduction                                                 | 237 |

| C.2 Transistors                                                  | 237 |

| C.3 Interconnect                                                 | 239 |

| C.4 General Chip Layout                                          | 241 |

| C.5 Sensitivity                                                  | 241 |

| APPENDIX D CAD INPUT DESCRIPTIONS                                | 243 |

|                                                                  | 264 |

|                                                                  | 264 |

| E.2 Input and Output Formats                                     | 267 |

| APPENDIX F IMAGE PROCESSING PROGRAMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| a tikky v vet a tit many kontik kontik kilikanij kenakanij o kala tik kontik kontik in tit mata kontik.<br>Ti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ness from the constraint of the first ness that the second of the constraint of the  |

| en e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| al en la classica de alberto la esta pera particular de por la central de la fille de la compaña de la compaña<br>La compaña de la compaña d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| nte participarent instrumentario de la compositario de la casa de l<br>La casa de la casa de l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| i proposition de la company de la company<br>La companya de la co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| un de la companya de<br>La companya de la co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| on white program is the program of the companies of the second section of the companies of the companies of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| g normy i the granuary of the result of sevent that it is a subject to the contract of the con |

| en e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| order alternation to the conditional graditions, the affect of the constant of the constant of the constant of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| paratitation is a complete consistent with all the terms of the constraint of the constraint of the constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Later work his beautiful asked by the activity on the Army let in the activity of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| m···;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| page of the control o |

#### Acknowledgements

My research advisor, Professor Robert Brodersen, provided me with excellent high level guidance.

The advice he gave always seemed to be slightly ahead of its time. His technical and personal skills made it a pleasure to work with him.

I would like to acknowledge the value of the help and advice given by Robert Kavaler, also known as the roving consultant of Cory Hall. His knowledge of UNIX, the C programming language and his interest in just about everything made my research progress more rapidly.

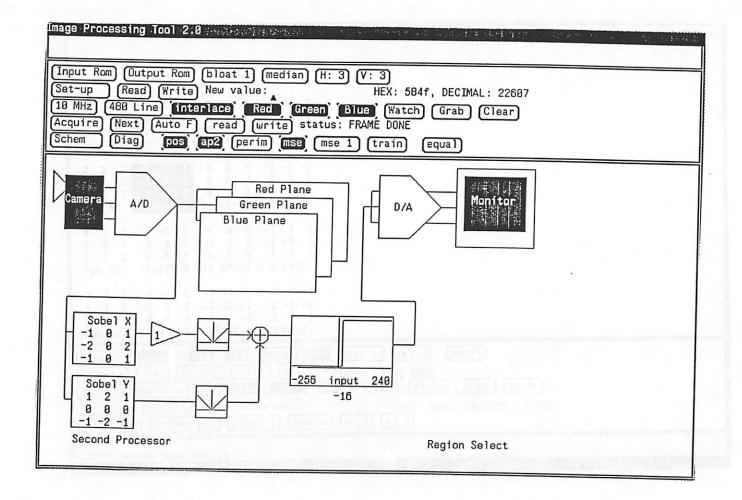

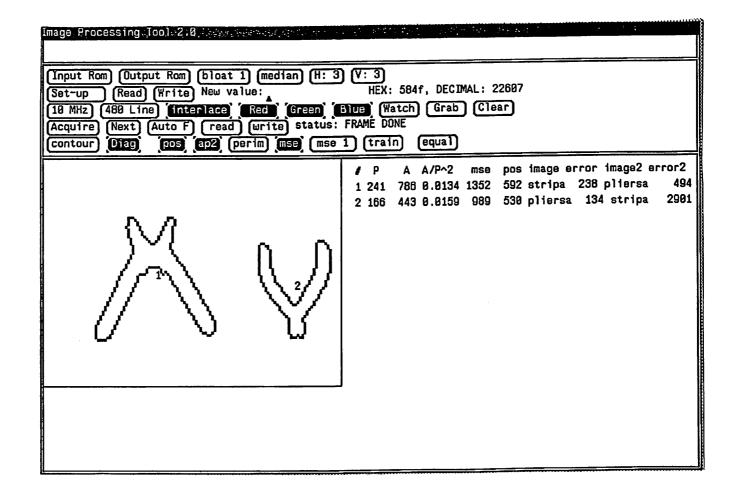

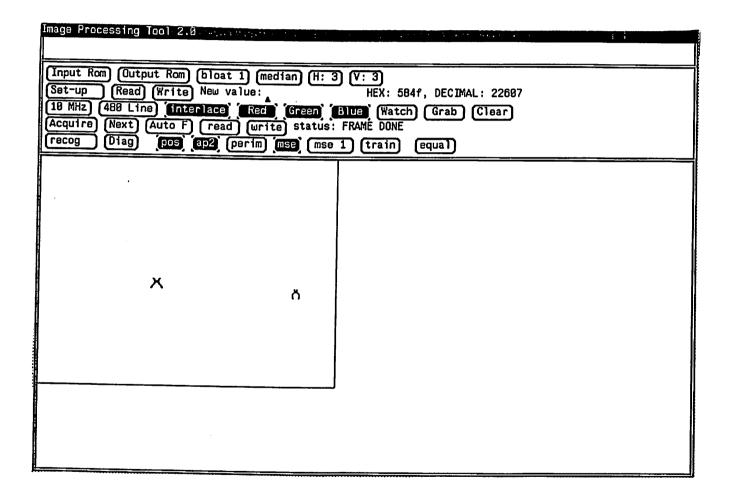

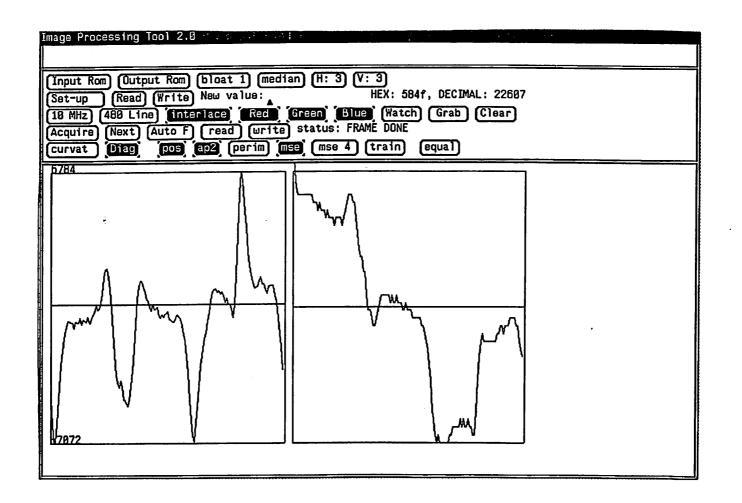

The core graphics routines in "ittool" were developed by Brian Richards. This program made it possible to give good demonstrations in addition to providing a controller for the general development system.

This research was sponsored in part by DARPA and the General Electric Company. IBM partially supported me for three years as an IBM fellow.

The MOSIS group deserves a great deal of credit for providing a reliable and fast NMOS foundry service. They were also very helpful and cordial in trying to resolve any problems that arose.

Finally, my thanks go to my wife, Susan, who read many sections of this and tried to correct my numerous writing errors.

#### CHAPTER I INTRODUCTION

Although work in image processing has been progressing for some time, it is beginning to accelerate with the advent of new image processors. These new processors attack the problems of I/O and computational bottlenecks that have long been associated with image processing. Hopefully, high performance, compact processors will make new image processing algorithms and systems feasible that were considered beyond the realm of possibility only a few years ago.

#### 1.1 APPLICATIONS

There is a wide range of applications of image processing. Some broad classifications are image enhancement, restoration, coding, recognition and characterization. The goal in each of these applications is to convert an image either to a modified image (enhancement and restoration) or to some other representation that requires fewer bits of information (coding, recognition and characterization).

Image enhancement is the subjective improvement of an image for the human visual system. The goal is to allow a person to more easily see some particular feature or features of an image without regard for image fidelity. In fact, techniques are often used which purposefully and drastically alter an image. Medical X-rays are enhanced [1,2] to allow physicians to more easily locate tumors, broken bones or other conditions affecting the patient's health. Image enhancement is also used to help bring out details in or remove noise from images taken in outer space [3]. In these cases, where each image comes at considerable cost, it is desirable to extract as much information as possible.

Image restoration is concerned with restoring an image to its original state after the image has been degraded. In this case it is desired to maintain high image fidelity. One common example of image restoration is the correction of blurred images. The image blur could be caused by camera or subject motion [4], a turbulent atmosphere [5] or diffraction limited optics [6]. Unlike image enhancement algorithms

which tend to be ad hoc, image restoration algorithms are usually based upon more rigorous theory.

Coding of images is used to reduce the bandwidth required to transmit an image via satellite, telephone line or other medium. In addition, mapping satellites generate an enormous amount of data that must be stored. By reducing the transmission or storage requirements for the images, the cost of the image transmission and storage system is reduced. There are two broad classes of coders, those which produce and exact representation of the original image and those which do not. Usually, if some distortion in the final image is tolerable, the total number of the bits required to represent the image can be significantly reduced.

In an industrial environment, characterization of images is quite important. To ensure that manufactured items are of suitable quality, some kind of inspection must be performed. Normally, this is performed by a person who tends to be good at intuitive reasoning but has a more difficult time performing quantitative measurements or tedious tasks. In order to save on labor costs or to improve the reliability of performing tedious inspection tasks, the inspection may be performed with an image processing system. Automated inspection has been employed to verify the quality of thin film disk heads [7], to check that the placement of IC dies within a package is within specifications, and to inspect of various automotive parts [8].

Inspection deals with the characterization of a known object, while recognition deals with the determination of the identity of an unknown object. Recognition could be used to help a robot sort parts on a conveyer belt or to locate a part in order to perform some action upon it. With more advanced recognizers, robots could pick up articles around the house and put them away or look for an electrical outlet to recharge its batteries. In this field, the applications are virtually limitless for a robust 3-D natural scene recognizer.

#### 1.2 COMPUTATIONAL REQUIREMENTS

There are many applications for image processing, but the computation requirements are quite severe. Images typically have a much higher data rate than speech or audio signals and hence special techniques must be employed to handle the I/O and computational bottlenecks.

A typical broadcast quality video image is sampled at a rate on the order of 10-20 MHz. This sampling rate will yield an image that is approximately 512 pixels on a side with a 30 Hz frame rate. It is important to note that the spatial and temporal resolutions both contribute to the high data rates. An image with large spatial resolution, 1K x 1K pixels, but very low temporal resolution, 1 frame/Sec, would only have to be sampled at a 1 MHz rate.

Audio band signals can be sampled at a much lower rate because audio signals are band limited to 20 KHz. For telephony applications, sample rates of 8 KHz are common while for digital audio a sample rate of 44 KHz is typically used. In contrast to video signals which are inherently three-dimensional functions (the dimensions are time, X, Y), audio signals are only one-dimensional functions of time) and therefore there is no notion of a frame rate for audio.

The ratio of data rate to circuit clock rate is quite different for audio and video processing. For a standard MOS process, 10-20 MHz clock rates are feasible. Of course, the actual clock rate depends on the details of the processing technology, the type of signal processing that must be performed, the circuit design techniques and the circuit architecture. Assuming that the use of a 10 MHz circuit, the ratio,  $R = \frac{F_{clk}}{F_{sample}}$ , is 227-1250 for audio signals but only 1 for video signals. R indicates how many times each piece of hardware can be used per sample to perform different operations in the algorithm. In the audio case, each piece of hardware can be used to perform hundreds of operations per sample, while in the video case, each piece of hardware can perform only one operation per sample. If R is large, a single standard architecture can be micro-coded to perform a wide variety of tasks. However, as R approaches 1, parallel architectures must be used, with one physical piece of hardware being used for each operation in the algorithm. To keep the processing elements and storage elements fully utilized, the processing elements have to be connected in a custom configuration.

#### 1.3 GOALS

Several major goals guided this work. It was desired to produce high performance image processors that could perform many of the basic image processing functions that are needed in different applications. In addition, the decision was made to design all of the processors to operate in real-time. This

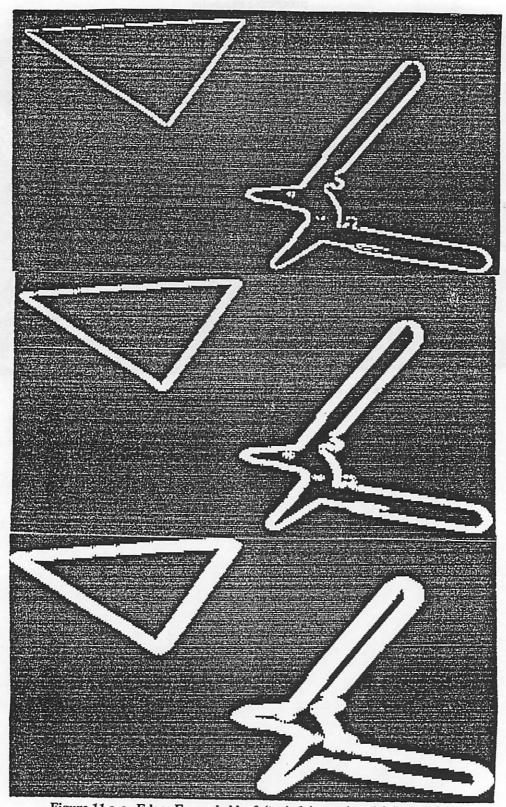

makes it possible to utilize all available data and hence achieve the highest possible throughput. In addition, by operating in real-time, the need for external frame buffers, which add to system complexity, cost and size is avoided. To demonstrate the ability of the chip set to perform some complete task, a goal was set to design and build an image recognition system. To make the problem feasible, the recognition goal was restricted to recognizing 2-dimensional objects that are characterized by their closed contours. Finally, there was a desire to keep the project development time to a minimum. The set of chips had to be designed, fabricated and assembled into a working recognition system in the time allotted for the Ph.D. degree.

Development of a real-time image processing system requires the merging of many fields. The designer or designers must have knowledge regarding the algorithms to be implemented, architectures and circuit design. To quickly develop custom circuits, some knowledge of CAD techniques is invaluable. Tradeoffs must be made between efforts in each of the fields. The designer must know how to choose new algorithms or modify existing algorithms to make the implementation easier. In addition, tradeoffs must be made between the circuit design effort and the CAD software effort. Essentially, if small compromises can be made in one area that result in a major savings of effort in another area, the designer will be successful.

Chapter 2 covers some basic image processing tasks, most of which were implemented on a chip. The functions implemented include 3x3 linear convolution, a 3x3 sorting filter operations, 7x7 logical convolution, contour tracing, feature extraction and point-wise non-linearities. These functions are common tasks that are mentioned often in the literature and these functions appeared to be sufficient to solve the recognition problem. In chapter 3, some basic recognition techniques are discussed. Some analysis is performed to determine the ideal performance that can be expected from these systems. A comparison of the performance, size and complexity of various types of hardware is made in chapter 4. In chapter 5, the techniques used to achieve a fast development time is covered. These include the use of hardware hierarchically and the appropriate use of CAD tools. The basic circuits used in many of the chips are covered in chapter 6. In chapter 7, the architectures and other details of the chips are discussed. Finally, in chapter 8, the performance of the recognizer is covered and some analysis is carried out to determine

the causes of recognition errors and ways in which the system could be improved. In the appendixes, details of the recognition board are covered (appendix A), some storage design techniques are discussed (appendix B) and the CAD input descriptions used in the chips are documented (appendix D).

#### 1.4 REFERENCES

- [1] Hall, E. L., et al., "A Survey of Preprocessing and Feature Extraction Techniques for Radiographic Images," *IEEE Trans. Computers*, vol. C-20, no. 9, pp. 1032-1044.

- [2] Andrews, H. C., et al., "Image Processing by Digital Computer," *IEEE Spectrum*, vol. 9, no. 7, pp. 20-32.

- [3] Nathan, R., "Picture Enhancement for the Moon, Mars and Man," Pictorial Pattern Recognition, G.C. Cheng, Ed., Thompson, Wash. D. C., 1968, pp. 239-266.

- [4] Slepian, D., "Restoration of Photographs Blurred by Image Motion," *Bell Syst. Tech. J.*, vol. XLVI, no. 10, 1967, pp. 2353-2362.

- [5] Horner, J. L., "Optical Restoration of Images Blurred by Atmospheric Turbulence Using Optimum Filter Theory," Applied Opt., vol. 9, no. 1, Jan. 1970, pp. 167-171.

- [6] Frieden, B. R., "Band-Unlimited Reconstruction of Optical Objects and Spectra," J. Opt. Soc. Am., vol. 57, no. 8, Aug. 1967, pp. 1013-1019.

- [7] Petkovic, D., et al., "An Experimental System for Disk Head Inspection," *IBM Research Report*, Dec. 1985.

- [8] Baird, M. L., "Computer Vision Techniques for Locating and Determining Orientation of Circular Gear Banks," GM Research Report CS-244, Aug. 1978.

## CHAPTER II IMAGE PROCESSING REVIEW

#### 2.1 INTRODUCTION

As discussed previously there are many applications for image processing. To implement an image processing system one must choose particular algorithms to perform various low level tasks such as noise rejection, edge enhancement, edge extraction, contrast enhancement and binary image transformations. Usually there are many different ways to perform each task. There are global and local techniques, linear and non-linear techniques and memory-less techniques.

To build a real-time image recognition system, image processing algorithms must be emphasized that are simple enough to implement quickly and efficiently in silicon. Further, it is important to choose algorithms that produce good results for machine decision making and not necessarily for subjective human viewing.

#### 2.2 SEGMENTATION

There are two primary ways to segment an image into the foreground, or objects of interest, and the background. In the first technique, it is assumed that the background and foreground can be separated by using absolute gray-level information. In the second technique, it is assumed that there is a local discontinuity in gray values at the interface between the foreground and background.

#### 2.2.1 Gray-Level Thresholding

In the first technique, it is assumed that objects in the foreground and background have sufficiently different gray levels so that the gray-level image can simply be thresholded. Pixels with gray values above the threshold (or below it) are considered to be in the foreground and pixels with gray values below the threshold (or above it) are assumed to be part of the background. If the image environment is

sufficiently well controlled, the threshold can be determined once and then left at this one particular value.

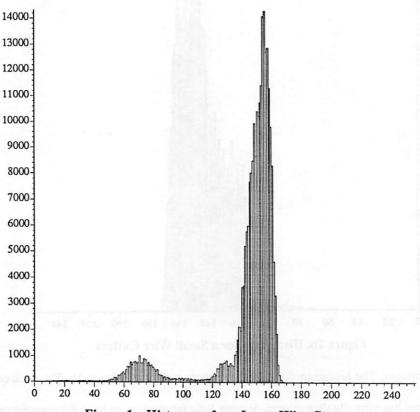

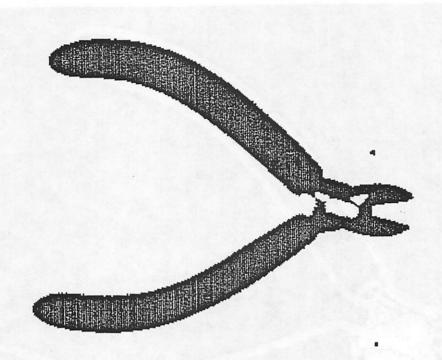

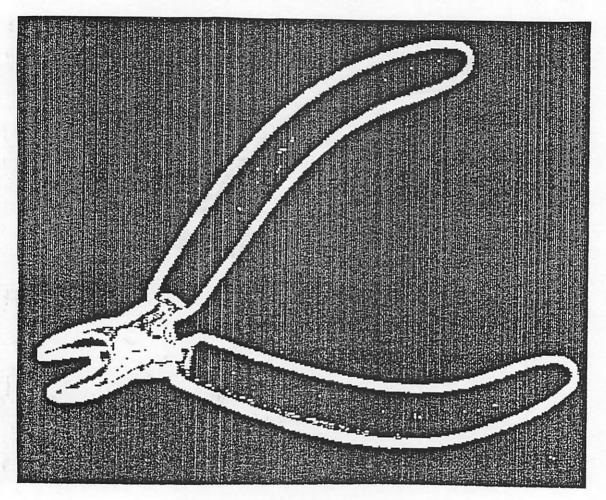

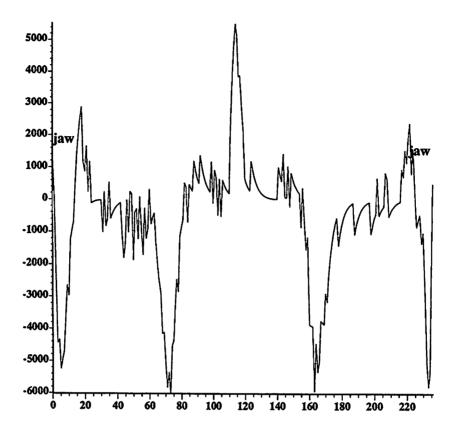

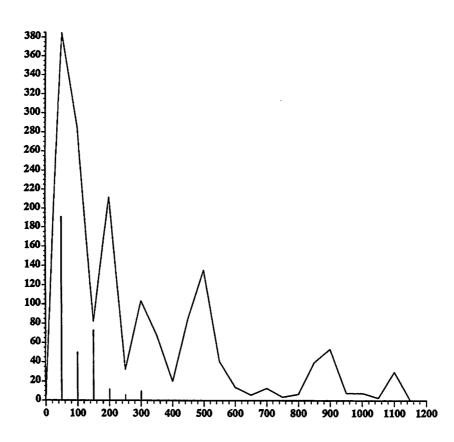

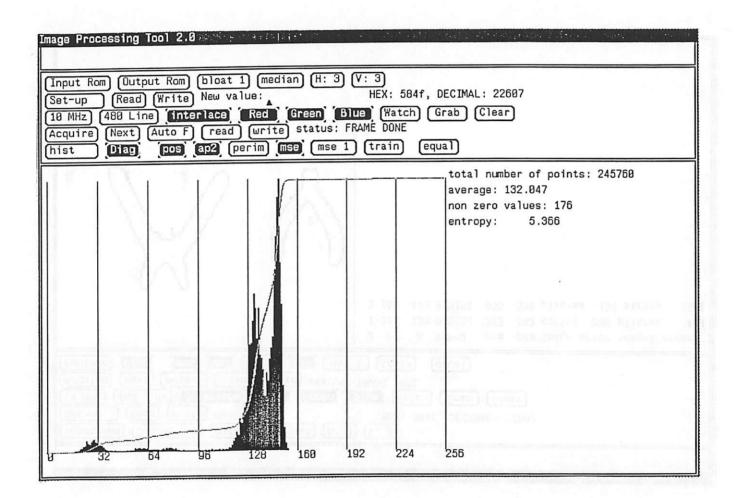

Figure 1a. Histogram for a Large Wire Cutters

For changing environments, the threshold is usually determined adaptively, using information from the image histogram [1,2]. If the background and foreground do have very distinct gray values, the histogram will have two distinct peaks in it; one corresponding to the background and one corresponding to the foreground.

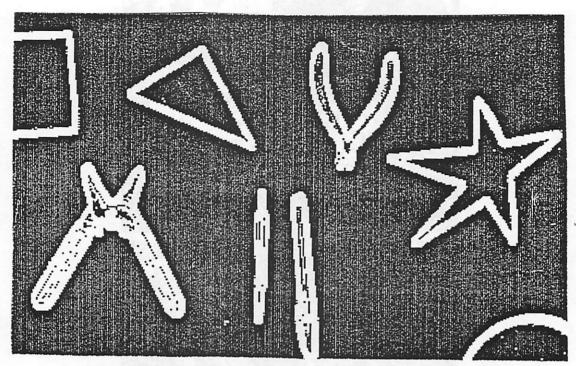

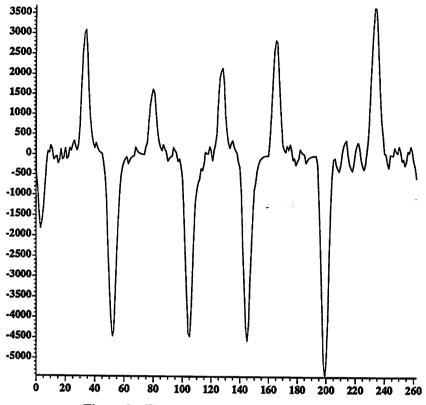

Deficiencies in this technique begin to show up when the foreground and background gray levels overlap or when the foreground objects become small. An example of this is shown in figure 1a, the histogram for a pair of wire cutters. The two peaks can be clearly seen. The large peak at gray levels near 150 corresponds to the background, while the peak at gray levels near 70 corresponds to the foreground. The threshold was chosen to be half way between the two peaks and the resulting segmented image is shown in figure 6. This approach seems to have been fairly successful, except that a small piece of the cutters near the jaws was falsely classified as background. A greater problem arises in dealing with very

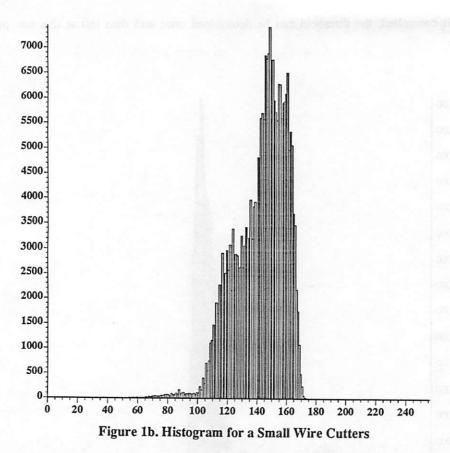

small foreground images. The histogram for a smaller cutters is shown in figure 1b. The peak corresponding to the foreground has virtually disappeared, leaving little information to base the segmentation on.

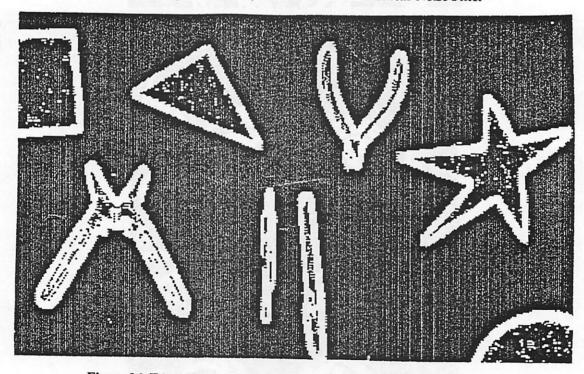

#### 2.2.2 Edge Extraction

Another common approach to image segmentation is involves finding "edges" in the image and assuming that the foreground and background are separated by these edges. These techniques will be discussed in greater detail later. The two cases examined above were also segmented with an edge extractor and the results are shown in figures 7a and 7b. The edge extractor generated a well defined boundary for both cases and hence has better size invariance, but the edge extractor also produced edges inside the object. For systems in which only the outer boundary information is utilized, this is not a problem. However, it may be undesirable in some systems.

#### 2.3 CONTRAST ENHANCEMENT

Contrast enhancement [3] refers to the point-wise manipulation of grey levels to "improve" the

contrast of an image. This could be used to bring out details in medical X-Rays or to make an automated image recognition system less dependent on illumination variations. Because the operations are memory-less and the data is commonly only 8 bits, a simple way to provide an arbitrary grey level transformation is with a look-up table. This can be implemented in a RAM, ROM or PLA depending upon the nature of the problem.

If the image illumination is poor or variable, the grey levels of an image may span only a few bits and provide little contrast. Transforming the image by spreading these few bits into the entire range of available bits will subjectively improve the visibility of the image. The transfer characteristic can be chosen by a human operator or adaptively, using a technique know as histogram equalization [4,5] or modification. In this technique the histogram of an image, the relative probabilities of each grey level occurrence, is used to create a transfer characteristic to modify the original image. The output image has some desired histogram shape, usually flat, that utilizes the entire available range of grey levels. The idea can be demonstrated by assuming that the input (X) and output (Y) have continuous cumulative probability distributions,  $F_X$  and  $F_Y$  respectively.

If Y is computed from X by:

$$Y = F_X(X)$$

Then:

$$F_Y(y) = Pr[Y < y]$$

$$= Pr[F_X(X) < F_X(x)]$$

$$= Pr[X < x]$$

$$= F_X(x)$$

$$= F_X(F_X^{-1}(y))$$

so Y has a uniform probability density.

To summarize, the histogram equalized image is formed by modifying an image by a transfer characteristic that is equal to its cumulative probability distribution. If a non-uniform density is desired, another look-up table can be used to generate an arbitrary output image density.

All of this assumed that the probability densities are continuous. In reality, the densities are discrete which often results in fewer grey levels in the output image. This effect is most pronounced

when the histogram of the input image has strong peaks. Since it is not possible to map pixels with the same grey level to different output grey levels, the large peaks will exist in the output histogram but will be spaced out to make the average height of the histogram a constant. This technique can not add information which did not exist (i.e. more quantization values). For human viewing, the reduction in the number of grey levels in the image may not be a problem (if the number of grey levels is reduced too much contouring of the image becomes obvious) and the resulting image will often be seen as improved. However, problems occur when edges are extracted from the equalized image because pixels that originally were very close in grey value near the peak of the histogram become much farther apart in the output image. Therefore differences in grey level that were caused by low level noise will be amplified and result in false edges.

The problem can be illustrated by assuming that the input and output images have continuous gray levels. The common method of edge detection is to find spatial gradients. If the spatial gradient is large, the point is called an edge point. So, if  $Y = F_X(X)$  and the edge extraction filter is a first derivative in the "s" spatial direction, then:

$$y_{edge} = \frac{dy}{ds} = \frac{dF_X(x)}{ds} = \frac{dF_X(x)}{dx} \frac{dx}{ds} = f_X(x)x_{edge}$$

Therefore, differentiating the histogram equalized image is equivalent to weighting the derivative of the original image by the pdf. It can now be clearly seen that even if  $x_{edge}$  is small and possibly non zero only because of noise,  $y_{edge}$  can be large and a false edge will be found.

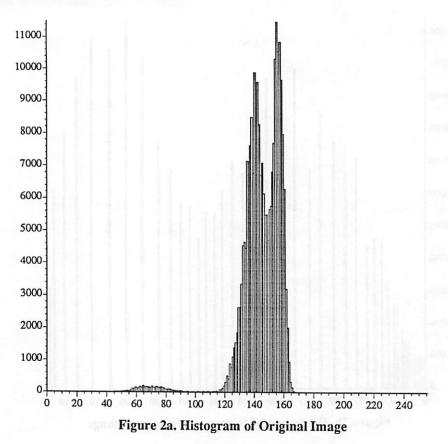

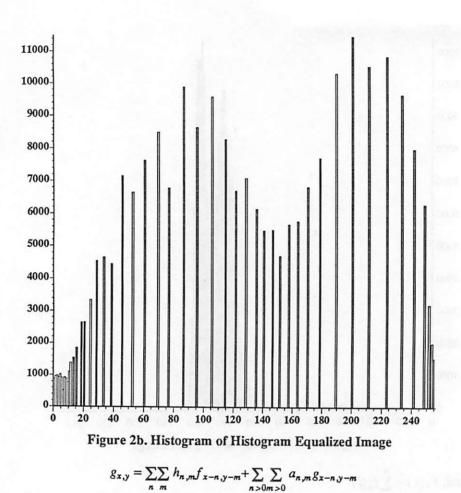

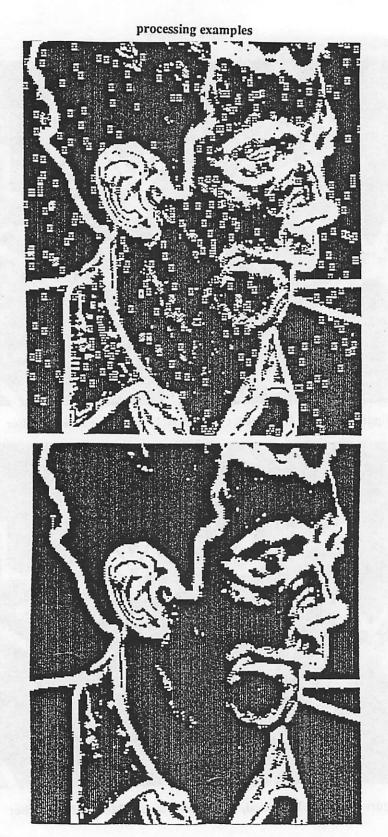

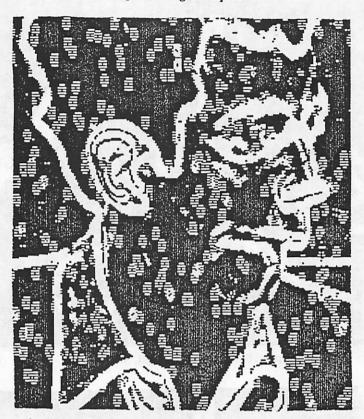

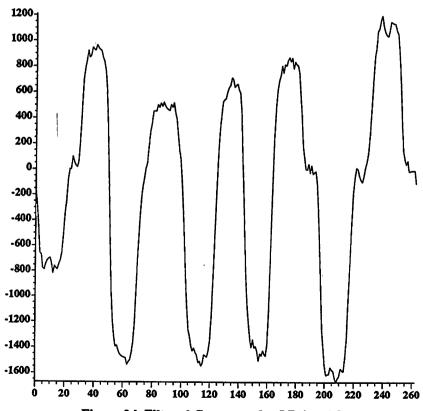

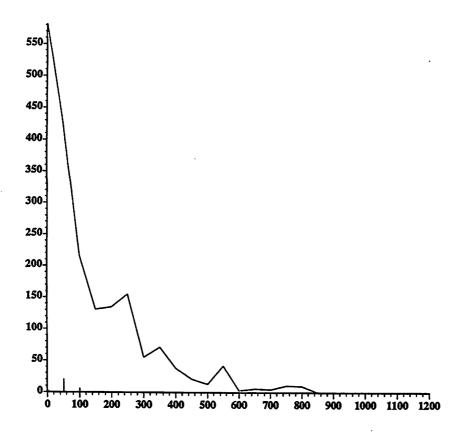

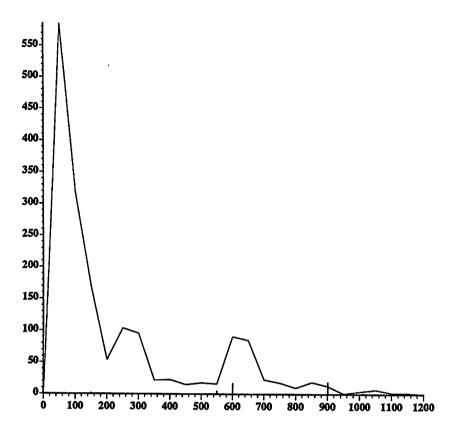

The problems with false edges can be seen in figures 2 and 8. Figure 8a shows the original edge map image and the histogram of the grey level image is shown in figure 2a. Notice that there is a strong peak in the histogram that corresponds to the nearly uniform background. The histogram of the equalized image is shown in figure 2b and the corresponding edge map in 8b. The pixel values from the peak of the original histogram (128-160 grey values) were spread over almost the entire range (40-255). The result of this can be seen in the edge map. The background is full of false edges due to to gain introduced by the equalization.

Histogram equalization can be performed with a few simple operations. First  $f_x(x)$  must be computed by counting the number of pixels that have grey level x.  $F_x(x)$  is then computed by performing the

discrete integral:  $F_x(x) = \sum_{i=0}^{x} f_x(i)$

Another technique is to simply normalize the image by a linear to logarithmic transformation. This is the basis of homomorphic processing [6] and has advantages by reducing the sensitivity of future processing to the image illumination. This technique also introduces gain for small grey values and, therefore, also has some of the same problems as histogram modification. In fact, the logarithmic conversion is similar to histogram equalization when the the image has a histogram that is peaked for small grey values (they are identical if the image has a probability density  $f_X(x) = \frac{1}{x}$ ).

#### 2.4 FILTERING

The noise rejection, edge extraction and edge enhancement algorithms are all based upon linear or non-linear filters. The linear filters can be FIR (finite impulse response) or IIR (infinite impulse response, or recursive). The difference functions for the FIR and IIR filters are:

$$g_{x,y} = \sum_{n} \sum_{m} h_{n,m} f_{x-n,y-m}$$

The FIR filters are commonly used for several reasons. First, FIR filters can be easily pipelined to reduce the required performance of the circuits. Although IIR filters can be pipelined, pipelining requires a significant increase in complexity. Also, since good image models typically do not exist, ad hoc filtering techniques tend to be used that can be implemented with short FIR filters. FIR filters with short impulse responses (3x3 or shorter) have been commonly discussed[7]. Template matching [20] can be performed with an FIR filter where the filter impulse response is the template. These are popular because the short impulse responses can be implemented with less hardware and hence at a lower cost while larger impulse response filters can be made from a cascade of 3x3 impulse response filters. As higher density circuits become possible, the impulse response length will likely increase.

In addition, it is very common for the impulse responses coefficients to be only powers of two [8,12,14,15]. Again, this reduces the cost of the circuit by making it possible to use a small multiplier. For very short impulse response lengths, it is usually not necessary to have higher precision coefficients

(see low-pass filter example later) because careful tailoring of the frequency response is not possible.

The frequency response of the FIR filter can be found by taking the Fourier transform of  $h_{n,m}$ :

$$H(\omega_{x}, \omega_{y}) = \sum_{n = m} h_{n,m} e^{-j(n\omega_{n} + m\omega_{y})}$$

$$H_{X}(\omega) = H(\omega_{X}, 0) = \sum_{n = m} h_{n} e^{-jn\omega_{n}} \qquad \text{where} \quad h_{n} = \sum_{m = m} h_{n,m}$$

$$H_{X}(\omega) = h_{0} + 2\sum_{n > 0} h_{n} \cos(n\omega) \qquad \text{if } h_{n} = h_{-n}$$

$$H_{X}(\omega) = h_{0} + 2j\sum_{n > 0} h_{n} \sin(n\omega) \qquad \text{if } h_{n} = -h_{-n}$$

#### 2.5 NOISE REJECTION

Noise rejection is a common image processing task. Often, the point of view is taken that in a controlled environment, a sufficiently high SNR can be obtained so that noise rejection processors will not be needed. This is true for the human visual system which is insensitive to most kinds of noise. However, in systems which employ local operators to extract edges (i.e. high-pass filters), even seemingly imperceptible noise can produce an output that is comparable with the "true edges".

There are two broad categories for low-pass filters for noise rejection: linear and non-linear.

#### 2.5.1 Linear Low-Pass Filters

Some examples of 3x3 FIR low-pass filter impulse responses [8] (neglecting the gain factor required for unity DC gain) are shown in table 1.

| 1       | 1 | 1 | 1 | 2 | 1 | 1   | 1 | 1 |

|---------|---|---|---|---|---|-----|---|---|

| 1       | 1 | 1 | 2 | 4 | 2 | 1   | 2 | 1 |

| 1       | 1 | 1 | 1 | 2 | 1 | 1   | 1 | 1 |

| (a) (b) |   |   |   |   |   | (c) |   |   |

Table 1. Impulse responses for linear FIR low-pass filters

Note: filters (a) and (b) are separable and can be represented as by impulse responses in the vertical and horizontal dimensions as shown in table 2.

|   |     |   | 1   |   |     |   | 1   |

|---|-----|---|-----|---|-----|---|-----|

| 1 | 1   | 1 | 1   | 1 | 2   | 1 | 2   |

|   |     |   | 1   |   |     |   | 1   |

|   | (a) |   | (a) |   | (b) |   | (b) |

Table 2. Corresponding Vertical and Horizontal Impulse responses for filters 1a and 1b

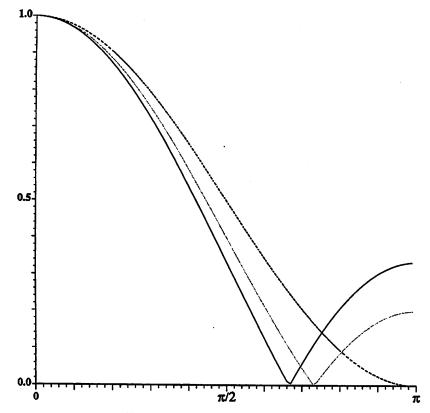

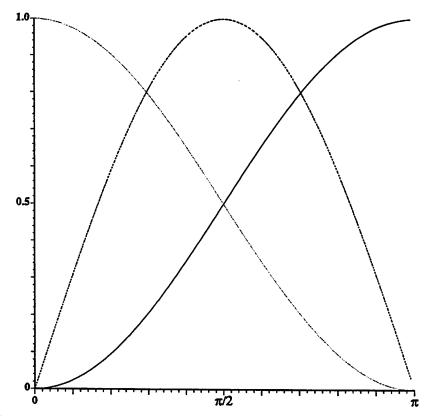

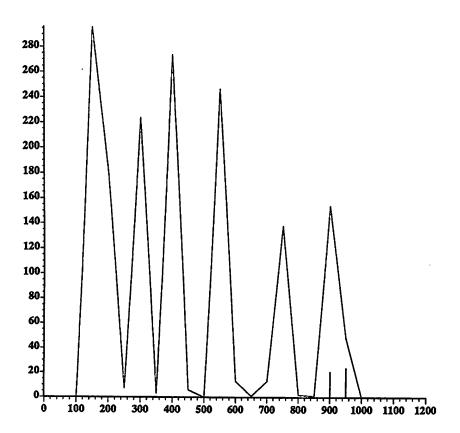

Figure 3.  $|H_X(\omega)| = |H_Y(\omega)|$  for filter a (solid), filter c (dotted) and filter b (dashed) in table 1.

Visually, these filters appear to do very little. A slight blurring of the image can be seen which does not appear to be significant. However, if the low-pass filtering is performed before high-pass filtering and thresholding for edge extraction, an improvement in the resulting edge map can be seen (fewer edges caused by noise).

All of the filters perform similarly. The reason for this is that the shape of the frequency responses for each filter is very similar (see figure 3 for a plot of the one dimensional frequency responses). The filters in table 1 have the following impulse responses (for  $\omega_Y = 0$ ):

$$H_X(\omega) = \frac{1+2\cos(\omega)}{3}$$

$$H_X(\omega) = \frac{1+1\cos(\omega)}{2}$$

$$H_X(\omega) = \frac{2+3\cos(\omega)}{5}$$

With such a short impulse response significant attenuation occurs only at fairly high spatial frequencies  $(>\frac{\omega_s}{4})$ . Even though the coefficients of the filters are coarsely quantized to powers of two, the frequency responses are virtually identical. This indicates that more precision in the coefficients is not a necessity to a shaper roll off. A longer filter impulse response would be needed to produce a narrower filter.

#### 2.5.2 Non-Linear Low-Pass Filters

If linear filters are used for noise rejection preceding high-pass filtering for edge extraction, the edges will be blurred along with the noise. If the filters are not carefully tailored to the power spectrums of the noise and the image (as is not the case in 3x3 operators) the low-pass filter will simply make it "harder" to find the edges. To combat this problem, non-linear filters are often used for noise removal. The most common non-linear filter for noise removal is the median filter, which takes the median of a neighborhood as its output. Another technique rejects "out of bounds" pixels. Both of these filters tend to perform well on noise that has a probability density with long tails (pulse type noise) while the linear filter performs well on Gaussian noise.

The "out of bounds" filter [9] is based upon a linear filter. To determine if a pixel is "out of bounds", it is compared to the average of the 8 pixels around it. If the difference is larger than a predetermined threshold, the pixel is replaced by the local average. With this technique, pixels are only changed when detected to be "bad". If the threshold is chosen properly, obvious errors (pulses) will be removed but edges will be well preserved. The problem is that the threshold must be determined and the optimum value depends upon the image and noise characteristics. If the threshold is too high, noise will not be rejected properly. A threshold that is too low will cause the filter to become linear with the disadvantages described earlier. With a human operating in the loop, it can be chosen subjectively. Otherwise, it must be chosen a priori or an algorithm must be developed to adaptively choose the threshold.