Copyright © 1986, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## COMPUTER-AIDED DESIGN FOR VLSI CIRCUITS

by

A. R. Newton and A. L. Sangiovanni-Vincentelli

Memorandum No. UCB/ERL M86/16

26 February 1986

## COMPUTER-AIDED DESIGN FOR VLSI CIRCUITS

by

A. R. Newton and A. L. Sangiovanni-Vincentelli

Memorandum No. UCB/ERL M86/16

26 February 1986

# ELECTRONICS RESEARCH LABORATORY

THE RACE

College of Engineering University of California, Berkeley 94720

# Computer-Aided Design for VLSI Circuits

A. R. Newton and A. L. Sangiovanni-Vincentelli Department of Electrical Engineering and Computer Sciences University of California, Berkeley, 94720

#### 1. INTRODUCTION

Computer aids have been used for both the design and verification of electronic systems for many years prior to the introduction of commercial Integrated Circuits (ICs) in the early 1960s. Such tools have found their way into virtually every aspect of the design of such systems, from IC process technology to the design of complex computer architectures. However, it is the IC and the complex electronic systems the IC has made possible that have made computer aids an indispensable part of the design of an electronic circuit or system. Not only are computer aids necessary for both the design and verification of integrated circuits today but, as the semiconductor processing technologies mature, computer aids will soon also provide key proprietary advantages as semiconductor and system design houses vie for the promising Application-Specific IC (ASIC) market of the next decade. We believe that the pivotal technologies in future IC CAD systems include tools for IC synthesis, such as placement and routing, combinational and sequential logic synthesis tools, and architectural design aids, design system management tools. including the management of design versions and alternatives in a distributed computing environment, data dependency management, and efficient and flexible interfaces to new tools, verification tools, including physical and electrical rules checking, simulation, and formal verification techniques. In many cases, the new verification tools will take advantage of new multiprocessing hardware to improve their performance or use the evolving heuristic programming technologies, such as rule-based expert systems, to improve flexibility and to encourage the evolution of the tool. In the following sections, the state of each of these areas is reviewed and key areas are noted.

In the remainder of this paper, the CAD tools and techniques used to support the most common design styles are reviewed. Nowadays, the field of CAD for IC design is very broad and it is not possible to cover all aspects of IC/CAD in a single paper. For that reason, the paper is focussed on the techniques critical to both custom and ASIC design.

3

the directions of present research and development for these areas, and future trends. In the following section, some basic cad and design style concepts are introduced and the CAD requirements for ASIC development are explored from a design and marketing point of view. Each of these requirements is then reviewed in the following sections in the context of design management systems, verification tools, and synthesis tools. While the area of testing also involves extensive use of CAD and is also a key technology for IC design, it is dealt with in detail in another paper in this issue and is, therefore, not reviewed here. With the recent rapid increase in compute power per dollar we have seen at the engineer's desk, the next few years promise spectacular progress in all of these areas.

#### 2. DESIGN METHODS AND CAD

#### 2.1. Introduction

The use of a particular class of circuit structures is referred to as a design method, or design style, and while the development of new algorithms and techniques for CAD contunues, a significant contribution to the design of VLSI circuits will continue to come from the development of new circuit design methods. However, while the implementation of a design method does not require the use of computer aids per se, the most successful design methods will be those designed to take maximum advantage of the computer in both the circuit design and verification phases. The design method must provide the structure necessary to use both human and computer resources effectively. For VLSI, this structure also provides the reduction in design complexity necessary to reduce design time and to ensure that the circuit function can be verified and the resulting circuit can be tested. In describing the variety of computer-aids used for IC design, a distinction is made between those techniques used for design, or synthesis, of the IC and those techniques used for its

## Newton & Sangiovanni

verification. In both of these categories, a further distinction is made between techniques relating to the *physical*, or topological, aspects of the design process, such as the generation and verification of mask layout data or the placement of components in a circuit, and *functional* considerations, such as logic description, synthesis, simulation, and test-pattern generation.

Computer aids for design, or synthesis, at both the functional and physical levels, are primarily concerned with the use of *optimization* to improve performance and cost. These design tasks may be formulated as combinatorial optimization problems for operations such as cell placement, routing, logic minimization, and logic state assignment, or as parametric optimization problems for operations such as design at the electrical level. These optimization problems are often too complex to solve directly. Therefore, *partitioning* is often used to reduce the problem to a set of simpler sub-problems. The solutions of these subproblems are later combined in a separate step. Both the partitioning task and the solution of each sub-problem generally involves the use of heuristics to reduce the complexity further.

Design methods can be classified in four categories: programmable arrays, standardcell. macro-cell. and procedural design. A VLSI circuit may consist of one large building block or it may consist of a number of building blocks combined either manually or by a computer program.

A programmable array is a one- or two-dimensional array of repeated cells which can be customized by adding or deleting geometry from specific mask layers. Since a number of processing steps are completed prior to customization, the locations of components on those layers are independent of a particular circuit implementation. Examples of programmable arrays include the Gate-Array[??]. Weinberger Array[??], Storage-Logic Array(SLAJ??], Programmable Logic Array (PLAJ??], and Read-Only Memory (ROM). The gate-array (also referred to as master-slice, or uncommitted logic array) is by far the most common programmable array designed by computer. It is also the case that the computer aids for gate-array design are the most advanced and the most mature. In this approach, a two-dimensional array of replicated transistors is fabricated to a point just prior to the interconnection levels. A particular circuit function is then implemented by customizing the connections within each local group of transistors, to define its characteristics as a basic cell, and by customizing the interconnections between cells in the array to define the overall circuit. Generally a two-level interconnection scheme is used for signals and, in some approaches, a third, more coarsely defined layer of interconnections is provided for power and ground connections. The interconnections are implemented on a rectilinear grid in the *channels* between the cells. In many cases, channels are also provided which run over the cells themselves and in some arrays, wider channels are provided in the center of the array to alleviate the congestion often found in that area if particular routing strategies are employed.

Gate-arrays are used in many technologies. in particular bipolar and CMOS, and arrays containing many thousands of gates have been used[56.57]. In the SLA approach, each "gate" consists of a storage element (flip-flop) and a small, uncommitted PLA. This design method has considerable potential for VLSI but effective design-aids for the synthesis of logic functions in SLA form are not yet available.

PLAs may also be used to implement building blocks directly, with storage elements in the feedback path to implement sequential logic in the classical Moore or Mealy style[??]. The PLA consists of a number of transistor arrays which implement logic AND and OR operations. In MOS technology, NOR arrays are used[60]. A conventional PLA consists of two arrays of cells: an input, or look-up, plane followed by an output plane. A *f olded* PLA may use additional planes, since rows and/or columns in the structure may be shared by more than one circuit variable, as described later. The standard cell (or polycell) approach refers to a design method where a library of custom-designed cells is used to implement a logic function. These cells are generally of the complexity of simple logic gates or flip-flops and may be restricted to constant height and/or width to aid packing and ease of power distribution. Nowadays, however, state-of-the-art standard cell systems permit cells of different height and width to be included in the same design. This results in non-uniform routing channels between adjacent rows and requires a more sophisticated channel routing capability if the silicon area is to be used to its maximum efficiency. Unlike the programmable array approach, standard cell layout involves the customization of all mask layers. This additional freedom permits variable width channels to be used. While most standard cell systems only permit inter-cell wiring in the channels between rows of cells or through cells via predetermined "feed-through" cells, some systems permit over-cell routing if additional levels of interconnect are available. Standard cell systems are also used extensively in a variety of technologies including bipolar and CMOS[??].

It is often relatively inefficient to implement all classes of logic functions in a single design approach. For example, a standard cell approach is inefficient for memory circuits such as RAM and stack. In the *macro-cell*, or building block, method, large circuit blocks, customized to a certain type of logic function, are available in a circuit library. These blocks are of irregular size and shape and may allow functional customization via interconnect, such as a PLA or ROM macro[??], or they can be parameterized with respect to topology as well[??]. With the parameterized cell, the number of inputs and outputs may be parameters of the cell. In some systems macro cells may also be embedded in gate-array or standard-cell designs. The macrocell floorplan style is evolving as the floorplan of choice for large. ASIC designs.

All of the design methods described above may be classified as *data driven*. That is, a description of the required logic function, in the form of equations or an interconnection

6

list, is used as input to a software system which interprets the data and generates the final design. Techniques have been developed over the last few years which can be classified as *procedure*, or program, driven[??]. These *procedural design* approaches, as well as their advantages and limitations as implemented today, are described below. Most of the 'silicon compiler' companies of today, including Silcon Compilers Inc., Seattle Silicon Technology, and SDL, support macrocell-based floorplans, with procedurally-based *module generators* as described in detail later.

### 2.2. The Relationship Between CAD and Design

Since the first CAD tools were applied to the IC design process, designers have complained that CAD lags design. There are those who feel that such a situation is inevitable since, once a designer finds a problem for the CAD engineer to tackle, it takes some time for a the appropriate CAD tool to be written, debugged, and documented. By that time, the designer has "moved on" to new designs and, with them, new problems for CAD. In the early days, designers were able to "work around" problems with the CAD tools at their disposal. Today, however, the job just can't be done without CAD.

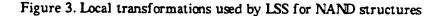

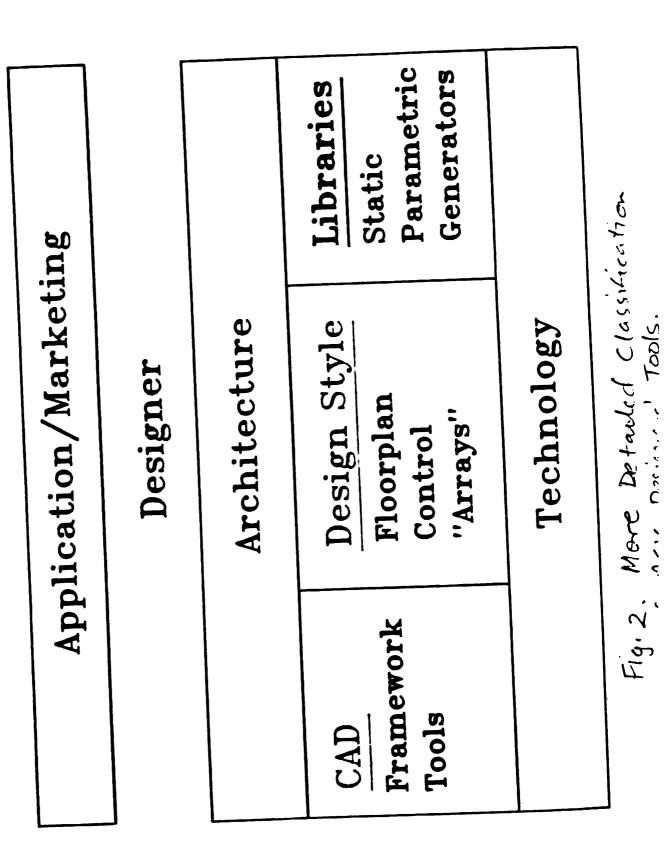

For an ASIC design environment, a simplified designer's view of the role of CAD is illustrated in Fig. 1. The designer, driven by the marketing need for a circuit that meets a particular cost, performance, and functional specification, works with system, logic, and circuit architectures to create a chip design. In that process, the CAD tools are used to evaluate tradeoffs and alternative designs, to construct specific circuit components, and to assemble and interconnect the components to form the final chip patterns. Once the IC mask patterns have been assembled, CAD tools are used to check the final layout and prepare it for the automated manufacture of masks. As the competition for designs increases, driven by the increasing number of companies in the ASIC business and by the high capital cost of a modern IC processing facility, there is increasing demand for designers to be able to differentiate their IC product from that of their competitors. Higher performance, lower cost, more features, or a faster time to market are all major factors which differentiate IC products in the ASIC marketplace. In the past, different companies have been able to provide such product differentiation through their IC fabrication technologies the ability to pack more transistors on a given chip or to provide a higher switching speed per gate drove the designs and their advantage in the marketplace. However, the silicon planar process technology is maturing rapidly — significant gains in performance and density are becoming increasingly expensive and many companies are resorting to "joint ventures," often with former competitors in the United States, Europe, or Asia, to maintain their position in IC process technologies. Because of this decrease in the relative competitive advantage obtained from process technology, semiconductor companies and "silicon foundries" must emphasize other aspects of the design process if they are to compete effectively for the ASIC market. The two avenues available are in architecture — hiring better designers and system architects than their competitors, which is often difficult and is certainly expensive — and in CAD.

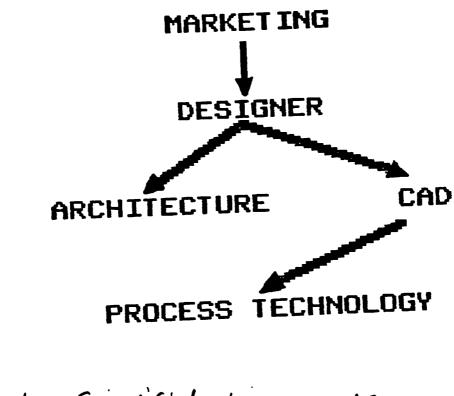

Unfortunately, the perspective shown in Fig. 1 is simplistic and incomplete. As illustrated in Fig. 2, the design task involves three major components: CAD programs, support for specific design styles, and support for component libraries. A lack of CAD support in any of these areas may result in a significant reduction in the competitiveness of the designers' final product. On the other hand, a significant proprietary advantage in any or all of these areas will maintain a companies' position as a force in the marketplace.

The CAD tools area may be subdivided further into three areas: tools for circuit design, or synthesis, tools for circuit verification, and tools for design data management and for the managing the flow of the design process. This last category of tools is of particular importance for it provides the foundation on which the CAD system is build. If the design f ramework is inflexible and cannot adapt to new tools, new design styles, and

changes in process technology, then the design system will soon become obsolete. It is also important in maintaining a competitive advantage in the design process since an *open* framework, which support the addition of locally-developed as well as commercial tools, can be used to provide a proprietary difference between one system and a competitor's system. For that reason, this important area is reviewed in detail in the following section.

As mentioned earlier, since design verification has received a great deal of attention in the past, most of the techniques and tools are relatively mature. The major research issues in the verification area concern improving the performance of the tools for large designs without sacrificing reliability of the results. The use of special-purpose hardware and new computer architectures are playing a major role here. In addition, new algorithms are being developed which exploit the properties of large circuits, such as the repetitive use of circuit structures. Many of the new techniques, while novel and requiring large engineering investments to achieve their potential, are relatively easy to duplicate and therefore cannot provide the foundation for a proprietary technology.

On the other hand, with a few notable exceptions, design synthesis systems for ASIC designs are far less mature and large gains in circuit efficiency and design time are still to be had. In addition, many of the state-of-the-art synthesis techniques involve far more "inspiration" than "perspiration" and, as a result, can form the basis of a proprietary and differentiating technology for ASIC design. Techniques for efficient synthesis (system design, register-level design, logic design, placement, routing, and array compilation) will provide a major focus for both University research and Industrial competition over the coming years and, for that reason, they are reviewed in detail in this paper.

The second important area for differentiation is that of CAD support for design styles. In particular, CAD support for floorplan style (gate-array, standard cell, macrocell, etc.) and support for the design of so-called "random" logic — that portion of a design that cannot be cast into a straightforward and efficient regular layout style, such as RAM.

1

ROM, or datapath. Since designers are finding improved circuit design styles and layout styles continuously, it is essential that a CAD system be able to support a variety of design styles and adapt easily to new development in these areas.

Finally, all ASIC systems require a library of primitive components, whether they be individual transistors, logic gates, or entire subsystems. These library cells may be invariant designs, such as the traditional standard cell or gate array building blocks, the may be parameterized cells, such as those in the libraries offered by the "silicon compiler companies", or they may be sophisticated, module-generator-based libraries, where different cell topologies are generated on the fly as a function of the user's input description.

If a designer is to compete in the competitive ASIC marketplace of tomorrow, he must be able to customize his CAD design environment in all three of these areas.

## 3. THE CAD FRAMEWORK

#### 3.1. Design Data Management

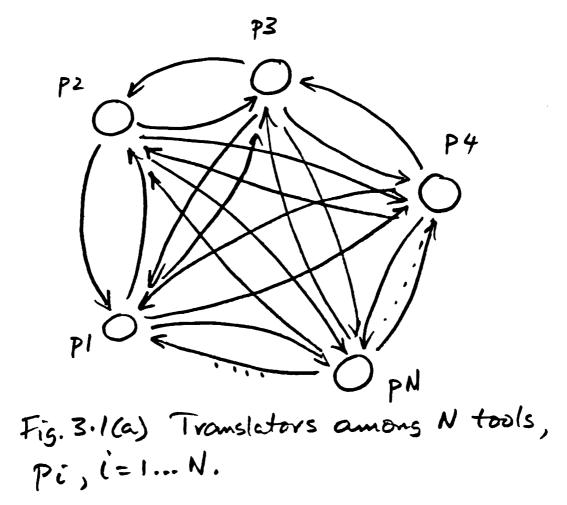

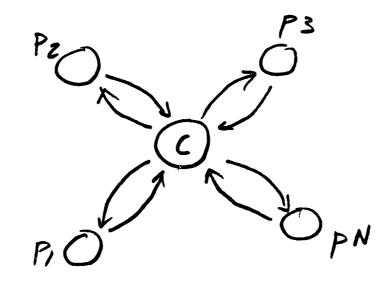

In the 1960's, data-base management was not an issue for IC design — the entire data-base often consisted of a box of punched cards and a hand-drawn roll of mylar that the designer carried with him. In the early and mid 1970's, as circuit complexity increased, proprietary and tool-dependent data formats were developed to represent particular classes of design data, such as mask layout data(e.g. [xymask][stream]) and transistor or gate-level netlist descriptions(e.g. [tegas][spice]). Since most CAD programs were developed independent of one another and had their own input formats, coupling them together to form an integrated system for IC design involved writing translators to and from each program. In the worst case, for N programs, (N - 1)N translators would be needed, as illustrated in Figure 3.1(a). However, the CAD tools were evolving and their input formats were changing along with them. As a result, it was often necessary to

keep a family of translators for each program, with each translator corresponding to a different version of the input data format. Maintaining such a family of translators soon became a CAD manager's nightmare! The number of translators can be reduced to a worst-case of 2N by choosing a common, central format and translating to and from that format, as shown in Figure 3.1(b). A number of *def acto* standard formats evolved in the late 1970's to meet the need for a common format and different companies standardized internally on one format for each class of data. In the mid and late 1970's, a number of public-domain standard formats were adopted and the most successful examples are the CIF (Caltech Intermediate Form Xm&c] for mask-level layout descriptions and SDL (Stanford Design Language[sdi] for gate-level netlist descriptions. While such formats provide a consistent way of *storing* the design data, there is no support for *managing* the data — Which copy is the latest version? Has the layout been changed since the schematic diagram was updated? If I change this cell, which cells that use it will be affected? It is the ability to answer such queries that differentiates a true data management system from a simple data repository.

In parallel with this work, a number of companies developed conventional database systems for managing their IC design data. Often these companies were the large computer or system houses who had experience with the use of database management techniques for discrete digital system design. These record-oriented database management systems (DBMS) were developed to manage IC parts inventories, part location on standard printed circuit (PC) boards, and the connections among IC pins necessary to implement the logic schematic. These lists of connections, used to guide wire-wrap or stitch-weld machines, are generally referred to as *netlists*. While these companies found that the application of conventional relational, network, or hierarchical database management techniques was effective for structured, semi-custom design styles like gate-array and standard-cell, these approaches were not successful for custom design styles or in situations where the underlying process technology and design style was evolving rapidly[4.5]

#### Newton & Sangiovanni

١

However, the same rapid increases in complexity that makes the use of conventional database management techniques difficult has made the need for a unified data management system critical, especially for full-custom or structured-custom design styles. No longer is the entire design process the responsibility of a small, tight-knit group but rather teams of system designers, logic designers, circuit designers, and layout technicians must all work together and share the vast amount of data representing an modern IC-based system.

The representations of IC design data, such as mask layout, schematic diagrams, documentation, simulator input and output, are quite diverse and new representations are being developed continuously. This evolution requires a flexible data management system which can adapt readily to new design methods. The use of conventional database management technology in this area has met with limited success[4.5]. The major limitations here are related to problems specific to engineering applications, while todays data base technology has often evolved from the business area. While specific differences between the needs of the business world and the needs of IC designers can be used to illustrate the problems here, simply solving these problems may not be sufficient. Rather, a completely different approach to the problem is necessary. These systems also exhibit low efficiency compared with the special-purpose solutions that have often been developed in-house. The requirements of a data management system for custom design include: access methods for storing and retrieving geometrical data. multiple versions and design alternatives, back-out of nested transactions, support for workstation and network-based transactions, procedural attachment, and near-optimal performance with relatively cheap hardware.

An analogy can be used to explain where conventional database management fails for custom IC design. Many researchers have noted a strong similarity between the custom IC design process and writing computer programs — mask layout is akin to a binary

DRAFT

image. symbolic layout is analogous to assembly code, and gates or modules are compared with lines of code in a high-level language. The sorts or operations the programmer performs on code, the IC designer would like to be able to perform on the IC design data. In fact, it is from such an analogy that the terms *silicon compiler* and *silicon assembler* evolved. Taking the analogy a step further, it is worth noting that programmers do not store their code in conventional DMBS systems. Rather, they have used conventional file systems (nowadays, often organized hierarchically) with tools to aid management of their code, including source-code control systems (e.g. [SCCS]) and dependency management tools (e.g. [make]). In fact, these tools add to the programming environment many of the capabilities provided by modern database management systems. Over the past few years, a number of IC design data management systems have been developed based on this model [squid] and have been used effectively for custom IC design.

In recent years, the notion of procedural circuit design[14-16] and the rule-based expert system technology have emerged as key components in the design process. These techniques, coupled with the ever-moving boundary between entire systems, printedcircuit boards, and chips, have broadened the requirements for an integrated design system. What is needed to support this work is a flexible design and programming environment that allows a variety of approaches to design to coexist and permits system-level, logic-level, and circuit-level designers, as well as CAD algorithm developers to work together in a single, unified environment. The keys to such a system are common levels of abstraction and standard interfaces among them, as well as a powerful set of synthesis and verification tools which form the basis on which further research is carried out. Each *object* in such a system may be described by *data*, such as its mask layout, by a local *procedure*, such as a parameterized cell, by generic synthesis tools, such as a channel router or a placement program, or by a combination of all of these techniques. As software systems continue to grow in size and complexity, programmers have turned to *object-oriented* approaches to code development and support (eg[flavors]smallTalk]loops]). The next generation of workstations, with an order of magnitude increase in performance at the desktop for comparable price to workstations of today, will be a key factor in making such approaches practical and affordable outside the research laboratory. In an analogous way, IC designers are beginning to develop and use *procedural* descriptions of design components, akin to the objects in many of these languages. In addition, the database management community is directing its attention to the management of object-based descriptions of systems. From an IC design point of view, these three technologies will converge in the next generation of data management and programming systems for IC design. The interfaces to these systems will be indistinguishable from that of an object-oriented, message-based programming environment.

Unfortunately, it is unlikely that a standard, object-based data management interface will be developed in the near future. There is still considerable research required to fully understand the issues involved before a suitable standard can be developed. In addition, competitive market pressures will continue to keep such interfaces proprietary. However, there is a need to move data from one design system to another. The design data represents the "life blood" of an IC design company. If a particular design tool does not function correctly under certain conditions, or a workstation or mainframe computer fails, the problem can generally be overcome and work can proceed. However, if the design data were to be lost in the middle of a large design project, the cost could be astronomical. Not only would the investment in design effort be lost to that point but such a situation would also cost valuable time and a market window might be missed. This is one reason why most IC design companies have resisted trusting all of their data management tasks to a single vendor, particularly if it is not possible to archive all of the data in a nonproprietary format. In addition, once a company has committed their data to a particular vendor's system, they are "locked in" to that vendor unless there is a way of migrating

14

the data to another system.

Another need for data transfer arises in situations where more than one design system or design site is involved. For ASIC design, schematic capture and simulation may take place on a low-cost, customer operated workstation, while the actual silicon implementation of the design occurs at the ASIC vendor's plant.

To meet these and other needs, standard, textual interchange formats are being developed for IC design data. In some cases the definition has focussed on the data necessary to support a particular design style. For example, the EDIF(Electronic Design Interchange Format)[edif], has been developed by a broad base of semiconductor manufacturers. CAD workstation vendors, and system houses to address the needs of ASIC-based system development. In other cases, a broader charter is being attempted, such as the efforts to standardize hardware description languages and behavioral descriptions of systems. The VHDL(VHSIC Hardware Description Language)[vhd1] and HSL-FX[hslfx] activities are the most active in this area today.

In summary, we believe that true open access to design data is an essential first step in the development of a data management framework. Such access must occur at two levels — an object-oriented, programming interface to all data in the database, and a nonproprietary, standard textual format which reflects as much of the semantic content of such systems as is practical.

## 3.2. Representations of the Design

Throughout the IC design process. a variety of different representations or views of the design are used. These representations may reflect a particular level of abstraction. such as the functional specification of the circuit or its mask layout, or they may reflect the view required for a certain application, such as the information required for simulation. The choice of appropriate representations for each level of the design process is a key factor in determining the effectiveness of computer aids since it is via these representations that both the structure of the design as well as specific information relating to a particular design level are expressed. The design process then involves transformations between these representations, both for design and verification. In this section a brief review and classification of the most common representations is presented. This classification is used in the later sections to relate different design aids.

While the particular set of representations used in a design depends on the particular design approach being used, the major categories may be defined as shown in Figure 3.2. These representations fall into three major categories behavioral, schematic, and physical. At the behavioral or algorithmic level, functional intent of the design is described independent of a particular implementation. In most cases, programming languages such as concurrent Pascal[99] or Modula 2[modula] have been used to represent the design at this level, as well as providing a simulation capability. Languages specifically designed for this task have also been developed[114,116-117].

Once a functional implementation strategy has been determined, a schematic view may be generated. At its most abstract level, this schematic view consists of a *chip plan*, illustrating the loose physical placement of the major components and busses. Depending on the complexity of the system, this description may be classified as a Processor, Memory, Switch(PMS)-level description[pms] which describes a system as an interconnection of processors, memory modules, peripherals, and switching networks, or a Register Transfer Level(RTL) or microinstruction-level description, defining the functional relationships between the major components of the design. A separate representation that is used for programmable systems is an Instruction Level description that describes the instructions of the machine.

As the implementation is refined further, logic gate level and finally transistor level schematics may be generated. While the nature of the information contained at each level is different, each more detailed view may be considered a different level of "zooming in" on the implementation. With each new level of refinement more information concerned with the detailed physical and functional implementation of the circuit is included in the description. The final transformation consists of the generation of detailed, mask-level geometries from a device-level schematic view.

The transition between functional and schematic descriptions, and between schematic and mask layout, may involve the use of additional views. The two most common approaches to transforming a behavioral description to a structural, or schematic, representation are the extraction of *control-flow* and/or *data-flow* information. The two approaches differ in the way they derive sequencing information from the behavioral description of the system. Over the past few years, a number of control-flow-based languages and data-flow-based languages have been developed or adapted to meet these needs, as described in more detail later. While CAD tools are available to help perform this transformation for restricted underlying hardware architectures, it remains an area where human creativity generally outperforms the CAD tools.

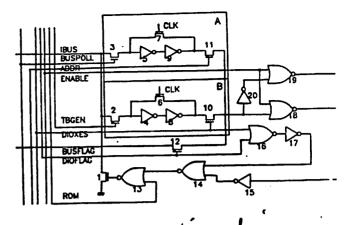

Symbolic layout forms a bridge between a schematic view of the circuit and its mask-level layout. A symbolic layout contains explicit connectivity information as well as the relative placement of circuit components, such as transistors, to form a basic circuit cell, cells to form a building-block, and building-blocks to describe the entire circuit. At the transistor level, one particular form of symbolic layout is called a *stick diagram* since interconnections are represented by their centerlines and hence resemble sticks. In Figure 3.3, a schematic diagram, its symbolic layout, and the corresponding mask-level figures are shown to illustrate the bridging role. One of the key advantages of a symbolic layout is its ability to maintain explicit electrical connectivity information through to the mask level descriptions. Not only can symbolic layout be used to aid the verification of the circuit, but by separating layout-sensitive cells and interconnections, computer programs can

be used to optimize the area utilization of the circuit by modifying only the noncritical interconnections. This process is called *compaction*, or *spacing*, and is described later.

Once an appropriate set of representations for a particular design method has been determined, important that an integrated set of computer aids, coupled with a unified approach to data management, be provided to the IC designer[118].

At each level of the design process described above, these descriptions must permit the structure of the design to be expressed in such a manner that it can be exploited by the design aids. In particular, *regularity* and *hierarchy* must be exploited. For example, regularity in the form of one- or two-dimensional arrays of similar, e.g. RAM, or iterated, e.g. ROM components can reduce the design time since only a small number of basic circuit types need be designed by hand. The verification time is reduced also since only one example of each possible spatial combination of this small number of cells need be verified to certify the entire array. Hierarchy can aid the verification process in a similar manner. The components of a circuit block, such as the logic gates used to implement an arithmetic-logic unit, need only be checked in detail once. When the composition of these cells is checked, only the relationships *between* the cells need be verified. A detailed check of the internals of the cells is not necessary. If these cells are used a number of times, this process can provide substantial savings in computer time. Circuit structure can also be exploited in other areas, such as simulation, circuit synthesis, and testing, as described in the remaining sections of the paper.

## 3.3. User Interface

Since early CAD tools were developed in isolation and often for batch, punched-card environments, diverse card-image-oriented data entry and card-image or line-printeroriented data output formats evolved. For mask artwork entry, a digitizing table and puck were in common use until only a few years ago. These systems have been displaced by interactive graphics-entry stations [calma]applicon][cv] and significant improvements in layout productivity were reported using these systems. However, since these systems were very expensive costing over \$130,000 per station, they were only used by experts trained for fast layout entry and were kept busy around the clock. Noone would think of using one of these stations to write a memo and only occasionally are they used for entering a schematic diagram. Separate, low-cost entry stations were used for these tasks.

Over the past five years, the advent of low-cost, high-resolution bit-mapped graphics, terminals and workstations has altered the economics of user interface dramatically. Low-cost artwork entry systems[kic][caesar][magic] and schematic entry systems have evolved to compete with the more expensive systems and it has become cost-effective to have such capability at each engineer's desk. In the more advanced CAD environments, general-purpose computing functions such as computer mail and networked file systems are also integrated with the CAD interfaces. In most cases, the user interface is similar to that developed at Xerox PARC in the early 1970's[parc] and as embodied in the Apple Macintosh and Lisa families of personal computers — separate windows for each application, pop-up or pull-down menu-based command selection, and bit-mapped graphics interfaces to most tools. In the most recently announced systems, the command syntax is also common for all tools from schematic editing and mask layout to testing and report preparation. A typical screen from such a system is shown in Figure 3.4.

However, from a framework point of view, it important that the user interface be exposed to the CAD developer for the addition of new tools. Ideally, in a consistent object-oriented environment, the user-interface (windows, menus, menu selections, etc.) would be treated as objects in the same environment as the data management system. With the exception of some experimental, in-house systems, there are no systems available today that provide such a uniform interface for the tool builder or CAD system developer.

## 4. VERIFICATION

#### 4.1. Introduction

To shorten the design cycle and to decrease design costs, it is crucial to eliminate as many errors as possible before manufacturing an integrated circuit. Verification compares the design at a certain level of the hierarchy, e.g. circuit, logic or structural level, with a set of specifications identifying possible inconsistencies between specifications and design.

Verification tools have been the first CAD tools to be developed and are probably the most used tools for the production of integrated circuits. There are several different kinds of verification tools. We classify them as *structural verification* tools, *simulation* tools, *performance verification* tools, and *logic verification* tools.

Structural verification is the task of verifying that the *structure* of a design — the arrangement of mask-layout shapes, the connections among those shapes or among the components of a design — satisfy a particular set of rules. For structural verification, the behavior of the components of the design is not considered, only there spatial relationships and connectivity.

Simulation has replaced bread-boarding for the functional verification of integrated circuits since the late 1960's. Components of the design and their interconnections are represented by mathematical models of different complexity according to the level of accuracy desired and to the representation available for the design at a particular stage of the design process. Then, input patterns are presented to the mathematical models and the corresponding outputs are obtained by solving sets of equations. These equations can be verv complex, such as partial differential equations for process simulation, or rather simple, such as Boolean equations for register transfer level simulation. The outputs are then compared to the expected outputs.

While simulation has been used successfully for the verification of large circuits, it cannot guarantee that certain timing specifications are met for all possible input combinations unless all such combinations are tried - an often impractical proposition. Performance verification techniques aim at the determination of the critical delays in a circuit independent of the input patterns.

Logic verification tools are also input pattern independent and verify that two design descriptions at gate or structural level and functional level are formally equivalent. In general, these techniques are much more expensive than simulation but their use increases the level of confidence in the design and are therefore more and more important as the complexity of IC design grows.

## 4.2. Structural Verification

Structural verification is subdivided into three areas: layout-rule checking(LRC), where mask geometries are verified to check if they satisfy a set of spacing, sizing and enclosure rules, electrical rule checking(ERC), where the circuit schematic is verified to find electrical errors due to wrong connections of the devices, and connectivity verification systems(CVS), where a netlist description extracted from the layout is compared against the netlist description extracted from an alternate description, such as the schematic diagram.

For custom and structured custom design styles, structural verification has made possible a substantial reduction in the design time needed to obtain functionally correct circuits[lattin]. However, structural verification alone cannot provide a guarantee that the design meets necessary performance specifications.

For design styles where the circuit is constructed automatically from precharacterized and verified cells using computer programs, such as the standard cell and gate-array design styles, or where large areas of the chip are constructed automatically using module generators, these techniques are used more as a final verification of the output of the CAD synthesis tools than as an active part of the iterative design process itself. For example, a design rule checker may be invoked after an automatic place-and-route system and the following symbolic spacing system have completed a layout, to verify that all the interconnections are properly spaced and that all the components of the design have been placed so that the design rules are satisfied. In our own experience with synthesis tools, we have found that a verification step after the synthesis step often detects

obscure bugs that would have been very difficult to find otherwise. In addition, in systems where the user is permitted to modify the output of the synthesis system (for engineering changes, or "green wires", or to improve the quality of the final output), a verification step is not only useful but essential.

## 4.2.1. Mask-Level Layout Verification

In some design methods, such as full custom or structured custom, the mask geometries corresponding to the devices are entered manually by the designer. *Physical layout rules* or *design rules* specify the the legal or illegal relationships among the polygons used in the IC mask-making and fabrication process to implement the final circuit. These rules account for necessary electrical separation of different components and signals as well as for imperfections in the mask preparation and manufacturing processes. If a designer enters the geometries of the masks such that they satisfy all layout rules, such as minimum spacing minimum size, and minimum enclosure constraints, then the distortions occurring in the translation from the original drawings to the actual geometries in silicon should not reduce the yield of the design significantly.

Industrial rule-sets can be very complex, especially when the shapes of geometries are not restricted. In addition, electrical considerations may add to the complexity of the rules. For example, capacitive coupling between lines requires that long, parallel lines be spaced more conservatively than short parallel runs. For high-performance circuits, as the sizes of components continues to decrease, the importance of parasitic effects such as capacitance, resistance, and inductance is increasing and adding complexity to the electrical aspects of the rules.

In the early days of ICs. layout rules were verified by hand-checking the Mylar masks or the layout plots obtained after digitizing the design. When the number of circuit components was small, this procedure was feasible, but as the size of IC designs increased the time required for manual checking increased, along with the probability of missing an error. In the mid-1970's, computer programs for automatically checking layout rules began to find widespread use[ROS74[MITC74]YAM74]. It is necessary that all the violations be reported by a Layout-Rule Check (LRC) program; missing even a single a rule may affect significantly the yield and the performance of a circuit. Often, the types of rules required to check a new technology are more advanced than the rule-specification language can handle. For example, if the rule involves specific edges of a figure while the rule-language only permits specification in terms of entire figures, the user must either omit the rule, and run a risk of a missed error, or specify a more conservative rule in terms of figures, in which case the LRC program will probably report many "false errors" - situations the rule specifies as being in error which are actually not errors - as well as any real errors that may occur. In addition, LRC programs must be flexible enough to deal with different technologies (e.g. NMOS, CMOS, bipolar) and with different processes.

Because of the size of IC designs today, a complete layout rule check requires that millions of polygons must be inspected with several rules each. The running time of a batch LRC program is often of the order of days on a super minicomputer or mainframe. While early algorithms used for checking layout rules often showed  $O(N^{1.5})$  performance, where N is the number of figures on the layer being checked, over the past decade researchers (e.g.[BA176][BEN80]) have been able to reduce the expected run time to

## 23

almost linear in the number of mask shapes. Once the analysis has been performed, the errors have been reported, and the false errors have been discounted, the true errors must be corrected. Fixing such layout rule violations is an expensive process in a batch checking environment because a layout rule check must be performed every time the layout is modified to verify that no new errors have been introduced.

LRC programs have been developed in house by large merchant and captive semiconductor companies such as INTEL[WAG75]. AT&T Bell Laboratories[MITC74]. Hitachi[??] and IBM[??]. and by vendors such as Calma, NCA. Phoenix Data Systems. Metheus, ECAD and SDA Systems. These programs can verify complex design with complicated layout rules. Some offer the users a language with which new layout rules can be added rather easily[SCH85]. Over the past few years, in conjunction with VLSI design courses[MEA81]. several Universities have developed LRC programs which are based on the Mead and Conway simplified *lambda-based* rules. Because the design styles used often require *Manhattan* geometries (layouts comprised of rectangles only, with their edges aligned with the X and Y axes, akin to the organization of streets in down-town Manhattan) only and do not consider conditional rules, these programs are relatively simple and very fast.

A number of new approaches to LRC have emerged from this activity and have found application in industrial products as well. For example, the concept of *hierarchical* [LAN83] and *incremental* [KIC80][CAE80][MCC83][OUS85] LRC have been explored over the past few years and have been implemented in industrial systems[SCH85] In incremental approaches, a background process checks the layout rules in the vicinity of each figure as it is added to the layout. Since manual layout is a slow process relative to the computing speed of a modern workstation, this is an effective way of using machine cycles that might otherwise have been wasted. It also permits errors to be corrected and re-checked in a tight, local loop so that the number of expensive, batch-mode checks can be reduced or even eliminated completely. interactively. However, incremental LRC

....

must be applied so that temporary LRC violations consciously introduced by the designer as an intermediate state are not continuously reported, disturbing the editing session. This problem is handled using one of several techniques. One approach is to maintain a file of layout rule violations, constantly updated in the background, that can be graphically displayed at the user's request. Another is to verify geometries only at the user's request, avoiding checks on regions which are not completed by the designer[KIC83][CAE83].

Hierarchical LRC takes advantage of the fact that cells are often used more than once in a large design. Once the insides of a cell have been checked, the cell is marked as "done" and then for each use, or instance, of the cell only the local context of the cell need be checked. In fact, it is not the *hierarchical* property of the design that really accounts for the savings but rather the *repetition* of identical cells or collections of figures. As ICs increase in size, the complexity of the design is often managed by increasing the *regularity*[LAT79] or repetition of cells in the circuit so that tools which exploit this fact often show large performance gains. In a modern, symbolic design system, where cells are often parameterized and many different variations can be created form the same master cell, or where a spacing system may adjust each cell differently to meet external constraints such as cell pitch, the advantage of hierarchical LRC is quickly lost[SHA85].

The techniques used by LRC systems can be classified into three categories: regionoperation-based, raster-based, and corner-based. An excellent review of these techniques can be found in [ARN85].

A large number of LRC systems use variations of the region-operation approach. In this approach, layout rules are expressed as a sequence of selection operations, isolating regions to which the rules apply, followed by a check. More complicated rules may require dozens of operations. Boolean operations such as AND, OR, AND-NOT, and sizing operations such as GROW and SHRINK, are implemented to identify the regions and to perform the checks. Most of these LRC systems represent the regions in terms of their

#### 25

edges and the operations are usually specified in terms of edges. Scan-line algorithms are generally used to process effectively massive number of edges [BEN LAU]

Raster-based approaches represent the design in terms of a raster grid, where each of the raster pixels is labeled with the mask layers present in that location. The amount of data required by this approach is obviously very large, much larger than in the previous approach. However, some savings can be achieved by using hierarchical storage schemes where contiguous regions containing the same type of pixel are treated as a single data object[??]. The verification can then be carried out with very simple algorithms. Because of the uniform representation of the data that is provided by this approach, the raster representation supports the use of special-purpose hardware in a straight-forward way. Several hardware accelerators for raster-based LRC have been proposed but no one has been used in production at this time. While this approach is certainly interesting, much work remains to make it practical.

The corner-based approach uses pattern-directed rule application [ARN82]. In this respect, it can be considered as an implementation of a rule-based expert system. Patterns at each corner of the geometries determine which rules to apply and which tolerances are to be checked. Present implementations of corner-based LRC, such as Lyra and Leo [ARN85], are limited to Manhattan or 45 degree angles and cannot handle wide-region operations needed to check conditional rules without some extensions. A rule-based approach has also been applied successfully using an edge-based representation in the Magic system[TAY84].

## 4.2.3. Extraction and Electrical Rule Checking

Once the mask patterns satisfy the physical layout rules, it is necessary to verify that they will actually implement a working circuit. The first step in this process is to recreate a netlist description of the circuit from the mask pattern data. This process is called *extraction*. Since the only information present in the mask layout data is the relative placement of shapes on different mask layers mask-level operations must be performed to recognize individual components, such as transistors, capacitors, and nets. For example, in an NMOS technology, a transistor may be formed where figures on the layers poly and diffusion overlap one another. So a rule for recognizing a transistor might be expressed as:

#### (define transistor (and poly diffusion)))

where a transistor is defined as that region where the logical and (intersection) of figures on the poly layer and the diffusion is not empty. Of course, in real systems the rules are significantly more complicated with many exception conditions. Since the types of operations necessary to recognize components from the layout are very similar to those used for checking the layout rules, it is not surprising that in most cases a LRC program forms the basis of an extraction program. The extraction program also determines parameter values for simulation, such as the sizes of the transistors extracted as well as related parasitic capacitance values. Depending on the design styles supported by the implementors of the extraction tool, the program may only extract gross components such as transistors. lumped parasitic resistance, and parasitic capacitance from interconnect to ground[FIT83], or it may perform a very detailed extraction including interlayer and inter-figure parasitic capacitance calculations [gummel] and even solve two-dimensional field equations where necessary[mitClue].

Like LRC, extraction can take many hours of computer time to perform if and accurate analysis of an entire chip is required. In addition, if coupling capacitances between parallel lines are extracted and RC-networks are used to represent interconnections, the amount of output data generated can be massive. While many of the industriallydeveloped extractors are used to obtain detailed parasitic information, those in general use in University design systems tend to favor speed rather than detailed analysis. In the most common University design styles for VLSI circuits, the layout rules and electrical requirements are constrained to reduce the likelihood of parasitic components altering the function of the circuit. Recently, the concepts of hierarchical and incremental extraction has been developed which makes it possible to verify modifications to design interactively without sacrificing the level of verification that is needed in quality IC designs [SC085].

The extracted netlist provides the basis for a number of additional checks. In particular, connectivity verification, as described in the next section, and electrical rules checking. Electrical rules checking programs evolved from simple implementations that searched the extracted netlist for ridiculously large or small transistors or direct shortcircuits among the power supply lines, clock lines, and the ground line to programs which check for more complex relationships. Such rules include searching a local area of a circuit to be sure transistors related to one another in an electrical sense all have the correct sizes to ensure correct circuit operation. In general, however, new rules were added to these programs by adding additional "hard-wired" procedures or data structures. Recently, a new breed of electrical rule checking programs has evolved based on the use of rule-based expert systems[critter][dialog][rubicc][cv]. Here, the rule-based system is used as a convenient way of expressing the required relationships among components and signals. The fast pattern matching facility of such systems is then used to recognize specific arrangements of components and apply the rules to those arrangements. The rule-based approach provides a convenient programming environment for adding additional, and higher-level. checks.

## 4.2.4. Connectivity Verification

If a transistor-level netlist description of a circuit is available, either from manually-generated simulator input data or from a schematic entry system, the pattern of interconnections among those components and the pattern of interconnections obtained from the extracted netlist can be compared. This process is called *connectivity verification* and connectivity verification systems (CVS) have been used over the past decade to improve dramatically the probability of functionally-correct silicon on the first fabrication run.

Connectivity verification was first used at the board level, for comparing a logic schematic input with a placed and routed board-level implementation of the circuit[apples].

In general, the comparison involves a one-to-one correspondence between the circuit elements. such as transistors, and the nets in the two circuits. not a functional equivalence. Each circuit is represented by a graph, where the nodes in the graph represent either the circuit elements[wombat] or the nets[gemini], and the nets or circuit elements, respectively, are represented by the arcs in the graph. In some cases, both the circuit elements and the nets are represented by nodes in the graph and the arcs simply represent the connections between them. The problem of determining that the two graphs are the same is equivalent to the graph isomorphism problem, a well known combinatorial optimization problem. The worst-case complexity of graph isomorphism is not known. No algorithm has been found with running time bounded by a polynomial in the size of the input, i.e., number of nodes and edges of the graph, but it has no been proven that this problem belongs to the class of NP-complete problems. However, good heuristics are available which can quickly detect if two graphs are isomorphic in most of the cases. If they are not isomorphic, the programs can then isolate the subgraphs that differ in the two netlists. This information is then provided th the user who tries to locate and correct the error.

There are two basic algorithms in use today for comparing two circuits signature calculation (using element signatures as in the Wombat program [14,15] or using node signatures as in the Gemini program [16]). and path tracing. Several approaches have been described in the literature and most LRC/ERC vendors and large IC companies have developed a connectivity verifier.

In the signature calculation approach, signatures are calculated for each element or node in both circuits. A signature is a combination of information about the element or node and its neighbors. The signature can be thought of as a hashing function. All unique signatures in each circuit are compared and any elements or nodes with the same signatures between circuits are marked as the same. This process is repeated until all elements are marked or no more unique signatures can be generated. The information gained on each iteration is fed back into the signature calculations. Almost all connectivity verifiers can handle the straight-forward problem very efficiently with fast, heuristic algorithms. However, most of the time in these programs is spent handling the special cases.

There are many special cases that can degrade the performance of the basic algorithms. Two such cases are *terminal permutability* and *parallel paths*. For some elements, the terminals are logically and/or electrically equivalent and are allowed to permute. The inputs to the basic logic gates (NAND, NOR, etc.) and the source and drain of MOSFETS are examples of such situations. In handling terminal permutability, many connectivity verifiers assume that they will be working with MOSFETS and "hard-wire" the fact that sources and drains can permute; others allow the user to specify how terminals on arbitrary elements can permute, but some do this very inefficiently and others do not always work.

31

Identical or nearly-identical parallel paths (as in bit-slice circuits and RAMs) also present a problem to current connectivity verifiers. If the paths are identical, the algorithms currently used can not distinguish between the paths and may not be able to handle them. In that case, the program may make a random binding of two elements from the possible candidates and proceed. If it discovers later that the choice was erroneous, it must undo the binding and choose another one. Also, if two paths have only small differences (as in ROMs), since only local effects are taken into account, connectivity verifiers also may not be able to distinguish between them.

\*\* CV \*\*

## 4.3. Simulation

## 4.3.1. Introduction

For circuits made from discrete components. *bread-boards* (prototype boards with discrete components) were used extensively to check the functional correctness of the design as well as its performance. However, this approach does not work well for integrated designs since the parasitics on the bread-board are quite different from those on the IC and the thermal and electrical characteristics, as well as component matching properties of the discrete components are also quite different from their IC counterparts. For this reason, electrical circuit simulation was one of the first CAD tools to be developed for IC design and has completely replaced bread-boarding for analog and digital cell design. For large digital designs, breadboards are still used for software development.

Many different forms of simulation can be used for the verification of large digital integrated circuit designs at the various stages of the design process. They may be classified as *Behavioral* (also called algorithmic or functional) simulators. *Register Transf er Level (RTL)* simulators. *Gate Level Logic* simulators. *timing* simulators. *circuit* simulators. *device* simulators. and *process* simulators. Behavioral simulators [51] are used at the initial design phase to verify the algorithms of the digital system to be implemented. Not even a general structure of the design implementation is necessary at this stage. Behavioral simulation might be used to verify the communication protocols in a multiprocessor design, for example.

Once the algorithms have been verified, a potential implementation structure is chosen. For example, a microprocessor, some memory, and a special-purpose input-output module may be chosen to implement the handshaking protocol mentioned above. An RTL simulator can be used to verify the design at this level. Only crude timing models may be available, since the exact circuit parasitics and other implementation details are not yet known. Useful information relating to congestion and hardware/firmware tradeoffs can be obtained from this level of analysis. A variety of RTL languages and associated simulators have been described in the literature [29].

Depending on the design methodology and certain technology issues, a gate-level design may be undertaken, where each of the RTL modules is further partitioned into low-level logic building blocks, or gates. A logic simulator may then be used to verify the design at this level. Sophisticated delay models may be introduced and testability analyses performed.

From the gate level, transistors and associated interconnections are generated to implement the design as an integrated circuit. Accurate electrical analysis can be performed for small parts of this design using a circuit analysis program [1][54] or larger blocks may be analyzed in less detail using a timing simulator [9-10][13]. Once the integrated circuit layout is complete, accurate circuit parameters, such as parasitic capacitance values and transistor characteristics, may be extracted and used at the electrical level. These analyses may then be used to improve the delay models at both the gate and RTL levels to verify the circuit design using accurate timing data.

Device simulators are used to verify whether the device characteristics corresponding to a particular sequence of processing steps are close to a ideal device characteristics.

Finally, the design of a new process or the tuning of an exiting process is aided by process simulators, where the control parameters of the process, such as furnace temperature and initial impurity doping densities, are the input variables and physical information such as impurity profiles are the outputs of the simulator.

A number of simulators have been developed recently which span a range of these levels in the simulation hierarchy. These simulators are called *mixed level* simulators [40-42] and allow different parts of a circuit to be described at different levels of abstraction. Not only does this approach permit a smooth transition between different levels of simulation (since the same simulator and associated input processor is used) but it allows the designer to take advantage of the time and memory savings available from higherlevel descriptions of parts of the circuit.

Excellent tools, either developed in house by IC manufacturer or by tool vendors, are available at all levels of the hierarchy. The parameters often used to judge the quality of a simulation tool are accuracy, speed, and flexibility. By flexibility, we mean the range of analyses supported by the program (time-domain transient, small-signal frequency-domain analysis, timing verification, fault simulation, etc.) and the range and quality of the component models it provides (both N and P channel MOSFETS, bipolar transistors, bidirectional switches, built-in registers, etc.). Because of the increasing size of IC designs, even the fastest simulators are not able to perform simulation as extensively as desired by today's designers. For this reason, several hardware accelerators have been developed for simulation and new algorithms are being explored to exploit multi-processor architectures (see the window in page for a detailed discussion of the use of multi-processors for simulation).

# 4.3.2. Process and Device Simulation

The electrical characteristics of IC devices depend very strongly on the manufacturing process. This process continues to become more complex and more sophisticated and it is often difficult to relate specific processing steps with the overall device characteristics obtained after manufacture. Process engineers are responsible for the design of an IC manufacturing process. They must define a sequence of processing steps, including masking and pattern exposure, implantation, oxidation, and etching, and they must specify and control parameters for each of these steps, including time, temperatures, and implant dosage. Their goal is to design a process which can produce reliably devices with welldefined electrical properties in a manufacturing environment.

The design of the manufacturing process could be carried out by trial and error, monitoring the electrical characteristics of test devices as the parameters of the process are varied. However, not only is such a process time-consuming and expensive, but with the high cost of today's IC manufacturing lines, it is important to design and test the process before it is actually implemented. In addition, while a process is being implemented, it is important that circuit designers have accurate device models so that they can develop their first circuits in parallel with the process development phase. Process simulation is used as a convenient tool in the design and refinement of processing sequences.

Process simulation has been a very active area of research for the past few years and has become an indispensable tool for industry. A key aspect of process simulation is process modeling. An excellent review of this field can be found in [DUT81].

Two approaches have been followed to model accurately the processing of IC devices: the analytical approach and the numerical approach. The trade-offs involved in the selection of one of the approaches are accuracy and compute time. In particular, analytical solutions can be given under simplifying assumptions or from a functional fit from measured data. Hence, these approaches tend to be valid only over a limited range of processing conditions and useful for tuning an existing process more than for a complete design of a new process. On the other hand, the complexity of computation is small and information such as impurity profiles, can be obtained at the expense of function evaluations which do not involve the solution of complicated nonlinear equations. At the other end of the spectrum, numerical techniques can be used to obtain the necessary information by solving set of nonlinear partial differential equations describing the processing steps in detail. As such they can be very accurate, but these computational techniques are time consuming since they involve a double discretization process: in both space and time. FABRICS[STR], developed at Carnegie-Mellon University, is an example of process simulator using analytical models while SUPREM[DUT], developed at Stanford, is an example of a process simulator using the numerical approach. While the process simulators developed at Stanford focus on the oxidation, implantation, and diffusion steps, SAMPLE[NEU], developed at Berkeley, models the photolithographic and etching aspects of the manufacturing process. Simulators currently used in industry are based on numerical techniques. IBM and AT&T Bell Labs have been technical leaders in this field.

In general, IC fabrication processes are affected by random disturbances, such crystal imperfections and dust, which affect greatly the yield of IC circuits. Over the past few years, techniques for designing processes, devices and circuits to maximize yield have become a necessity to provide economically sound products. Unfortunately, accurate numerical techniques such as the ones used by SUPREM cannot be used to predict yield if a statistical characterization of a process is sought since today's computers are not power-ful enough. However, programs like FABRICS can be used to provide a statistical characterization can be generated from processing step information in this type of program.

The ultimate goal of process design is the production of devices with given electrical characteristics. However, process simulation produces as output impurity profiles. The

DRAFT

35

necessary next step is to map this physical information onto device parameters that describe the electrical behavior of the devices resulting from the process. This step is accomplished by programs called *device simulators*. Approaches to device simulation are similar, from a mathematical point of view, to the ones used in process simulation. Numerical techniques involving the solution of partial differential equations, such as Poisson's Equation and the Continuity Equation, are used by programs such as SEDAN developed at Stanford[DUT] and MINIMOS developed at the University of Vienna[SEL]. Analytical techniques are used by FABRICSII[NAS84], a combined process and device simulator, to obtain device parameters for a variety of technologies and transistor models which are used in circuit simulators such as SPICE2[NAG75].

Recently, attention has been devoted to the use of special-purpose hardware to reduce the cost of numerical process and device simulation. In the past, only onedimensional effects were modeled by these tools. Recently, two dimensional process and device simulation has been possible. Three-dimensional effects are now been addressed to represent the processing steps in their full complexity. Japanese companies, in particular, are devoting significant resources to this problem.

For the analytical approach to process and device simulation, more attention is being paid to the development of accurate analytical formulae and of optimization techniques which can be used to design a manufacturing process to reduce the time needed to obtain a satisfactory design.

36

## 4.3.2. Circuit Simulation and Modeling

As mentioned earlier, circuit simulation was one of the earliest tools applied to the design and verification of ICs[??], since 'bread-boards' prototypes of these circuits could not adequately represent the parasitic or thermal effects necessary for prediction of circuit performance. When accurate circuit models are available, circuit simulators provide precise electrical information, such as frequency response, time-domain waveforms, and sensitivity information, about the circuit under analysis. The majority of circuit simulators currently in use contain models for a wide range of active devices, including bipolar junction transistors, MOSFETs, JFETs, MESFETs, and diodes, and hence are largely independent of technology. For this reason, these programs must employ general algorithms for the solution of the set of coupled, nonlinear, ordinary differential equations which describe the integrated circuit and hence cannot exploit the special characteristics of a particular technology.

The most used general purpose circuit simulator is SPICE, developed at the University of California. Berkeley. This program has been adapted for use in many IC design companies, e.g. ADVICE used at AT&T Bell Labs, TI-SPICE used at Texas Instruments. SLICE developed at Harris. The program ASTAP has also been widely used. ASTAP is based on different algorithms than SPICE and has additional capabilities such as userdefined models and statistical analysis. In addition, commercial versions of SPICE, SCEP-TRE, and the ASPEC program are used in industry.

Without models whose accuracy is well matched to the expected accuracy of a simulation, the results of the simulation may not reflect the performance of the circuit under analysis. Recent work on modeling for MOS circuit simulation[??] has focussed on the development of both analytic[??] and semi-empirical[??] models for MOS transistors which predict the characteristics of the devices accurately without requiring large amounts of computer time. With increasingly small geometries on ICs, signal delays and signal degradation caused by interconnect can dominate circuit operation. For this reason, explicit models for interconnect are necessary for accurate simulation and interconnect modelling has returned as an active area of research[??]. The parameters of such models may be provided by the designer interactively or by design programs directly, as described in Section 42.2.

Since circuit simulators have been with us for almost twenty years, and because the problems they attempt to solve are very well understood, the core algorithms used in a modern circuit simulator are generally quite robust. However, as a consequence of their long history, most circuit simulators are batch-oriented programs and the input to the program consists of a textual description of the transistors and their interconnections. Nowa-days, using a CAD workstation, an interactive graphics editor is often used to capture the schematic diagram and provide simulator input.

Circuit simulation techniques can provide accurate waveform analysis for circuits of building-block complexity. However, as circuit size increases the time and memory requirements of a circuit simulation become prohibitive. On an IBM 370/168 computer, the average cost of a SPICE[16] analysis is 6ms/device/clock/timepoint. For a 10,000 device circuit, with 3 clocks and for an analysis of 10us at 1ns steps, the computation time would be in excess of 20 computer days! Nevertheless, the success of circuit simulation in design evaluation has been such that designers wish to continue to simulate large circuits at the level of accuracy provided by this type of program.

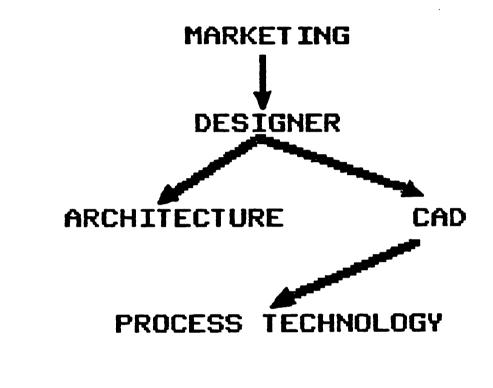

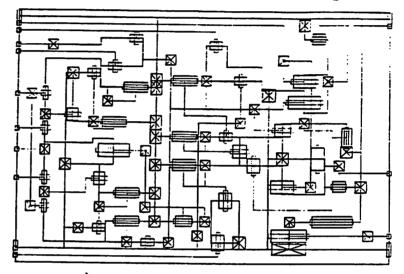

By applying node tearing techniques[82.83] to the interface between cells in the circuit. inactive cells can be bypassed during the equation solution phase. However, these techniques alone provided less than an order of magnitude speed improvement. This is not sufficient improvement in performance to permit cost effective device-level analysis of VLSI circuits. If simulation algorithms are tailored to specific technologies or applications substantial speed improvements can be achieved. Many components of digital MOS or  $I^2L$  circuits can be considered unilateral in nature. This characteristic, as well as the facts that these families are saturating and hence accumulated voltage errors are lost at the extremes of signal swing, and that large digital circuits are relatively inactive at the gate level, are exploited in *timing simulation*. Timing simulators[84-86] can improve simulation speed by up to two orders of magnitude while maintaining acceptable waveform accuracy. These savings are achieved by using node decoupling techniques in conjunction with simplified table look-up models for nonlinear devices.