# Copyright © 1985, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# A HIGH-SPEED, HIGH-PRECISION COMPARATOR DESIGN FOR A 10-BIT, 15MHZ, A/D CONVERTER

by

Toru Baji

Memorandum No. UCB/ERL M85/86

7 August 1985

# Dedication

This manuscript is dedicated to my wife Yoko for her patience and support during this work, and to my daughter Marie for her encouragement with her pretty smile during my hard work days.

A HIGH-SPEED, HIGH-PRECISION COMPARATOR DESIGN FOR A 10-BIT 15 MHZ A/D CONVERTER

Toru Baji

Central Research Lab., Hitachi Ltd.

**ABSTRACT**

This research effort has been directed towards the basic design of a high speed and high precision CMOS comparators. These comparator design techniques are going to be used in the 10 bit 15 MHz A/D converter. [1]

The multi-stage fully differential amplifier and a regenerative latch are used as the basic configuration. Various candidates for the fully differential amplifier have been designed and compared. The fully differential amplifier with the DC gain of 10 and the gain band-width of 2.500 Mrad/sec has been chosen.

The author has joined in this project, when he was visiting ERL, University of California as a visiting industrial fellow from August 1984 to August 1985.

## **ACKNOWLEDGEMENTS**

The author wishes to express his sincere appreciation to Professor David A. Hodges for his kind advice and support throughout the project, and to Joey Doernberg for his great ideas and fruitful discussions.

In addition, the author wishes to thank Jeremy Tzeng for his kind introduction to the UNIX system and its application programs, and for the kind advice for the every day life in this country.

The author express his gratitude to C. K. Wang. Steve Lewis, and many other members of the A/D group for their kind assistance and discussions about the project.

The author also expresses his gratitudes to Dr. Ohba, Dr. Kubo and Dr. Takeda of the Central Research Lab., Hitachi Ltd. and Dr. Obayashi, Dr. Asano and Dr. Yamada of Hitachi America Ltd., for their encouragement and support during my stay in this university.

# Table of Contents

| CHAPTER I INTRODUCTION                                         |    |

|----------------------------------------------------------------|----|

| CHAPTER II TWO STEP PARALLEL A/D CONVERSION                    | 4  |

| 2.1 Basic Configuration and Algorithm                          | 4  |

| 2.2 Fully Differential Configuration                           | 9  |

| CHAPTER III COMPARATOR DESIGN                                  | 12 |

| 3.1 Introduction                                               | 12 |

| 3.2 High Speed Latch Design                                    | 14 |

| 3.3 Offset Cancellation of the Multi-Stage Amplifier           | 17 |

| 3.4 Transition Speed of the Multi-Stage Amplifier              | 19 |

| 3.5 Reset Speed and Stabilization                              | 24 |

| 3.6 Fully Differential Amplifier Configurations                | 27 |

| 3.7 Simulation of the Comparator                               | 35 |

| CHAPTER IV CONCLUSION                                          | 38 |

| Appendix A Transient Response of the Latch                     | 39 |

| Appendix B Process Parameter Tolerance of the Latch            | 42 |

| Appendix C Transient Response of the Multi Stage Preamplifier  | 46 |

| Appendix D Characteristics of Fully Differential Amplifiers    | 51 |

| Appendix E Optimum Design of the Fully Differential Amplifiers | 73 |

| Appendix F Reset Speed and Stabilization                       | 85 |

| REFERENCES                                                     | 88 |

## CHAPTER 1. INTRODUCTION

Recently, the conventional video signal processing in the analog form has been replaced by digital signal processing, improving the performance, the reliability and in some cases even the production cost. This replacement has taken place first in the TV studios, where intensive and high quality signal processing is required, no matter how expensive the cost of the equipments will be.

Thanks to the development in the VLSI technology, digital video signal processing becomes affordable even for home used video equipment. Now, several manufacturers provides high quality and multi-function digital TV sets. [2] [3] The sampling rate and quantization bits required in this application are 4  $f_{sc}$  ( 14.32 MHz ) and 8 bits respectively. The signal bandwidth of a video signal is 4.2 MHz, so 3  $f_{sc}$  will be enough to prevent aliasing. But, for the color signal processing ( especially for the PAL ), it is convenient to use 4  $f_{sc}$ . Considering only the random quantization noise, a signal to noise ratio ( SNR ) of 48 dB can be achieved with the 8 bit resolution. This is high enough for the commercial TV video signal. Many Analog to Digital Converters ( ADC ) which satisfy these specifications, have been reported and manufactured, both in bipolar and CMOS processes. [4] [5] For high resolution TVs, a sampling rate as high as 100 MHz will be required. [10]

The next step in the digital video signal processing will be the introduction of digital video tape recorders (Digital VTR) and digital TV cameras. [6] [7] In the 3-CCD Digital TV camera [7], an analog gain adjust circuit, a limiter and an analog white balance circuit is installed between the CCD solid-state imagers and the ADCs. There is a feedback loop to the limiter to keep the black level constant. All these circuits are used to quantize the input signal effectively in 8 bits. The SNR of this camera is 52 dB for the random noise. For high quality studio cameras, an SNR above 60 dB is required. This means that a quantization of more than 10 bit is required. Even for the home used TV cameras, 10 bit resolution will be desirable. It will make possible to remove all the analog circuits between the image sensor and the ADC.

The quantization of the video signal which experiences many signal processings. requires more bits than 8. Such applications are the digital TV cameras, the digital studio equipment[8] and the Medical Electronic (ME) equipment, such as digital radiography. In a digital studio, many pieces of equipment will be connected in tandem. Each signal process will experience a rounding of the digital signal, degrading its quality.

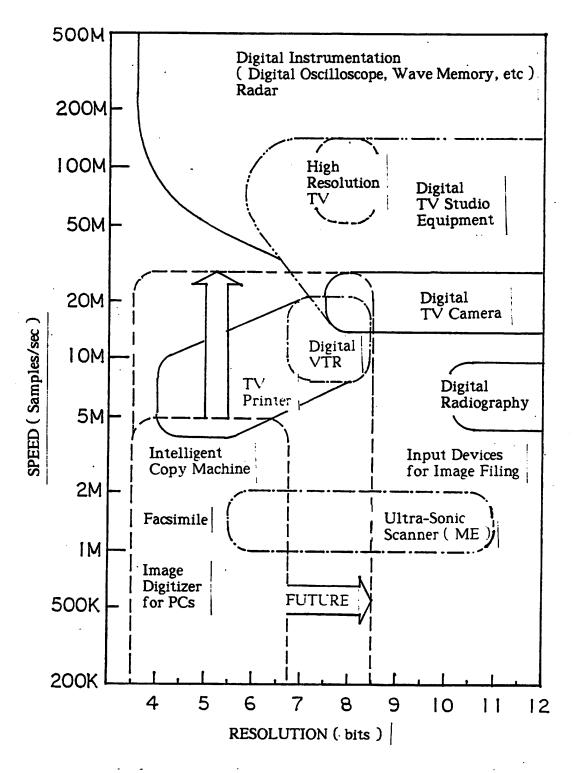

There are many other applications for the high speed, high resolution ADCs. Fig.1-1 shows some application fields, depending on the speed and the resolution of the ADCs. [10]

For now, only one monolithic video frequency 10-bit ADC has been reported using a bipolar technology.[9] It can quantize the input signal with a sampling rate of 20 MHz. The drawback of this device is its size ( 40,000 Transistors, 9.2 mm x 9.8 mm ) and its large power consumption ( 2.0 W ). Moreover, to compensate the reference voltage deviation, it has 8 drivers to drive the reference resistor string, and requires laser trimming.

To realize this circuit in CMOS technology, we have to expand the circuitry of an 8 bit CMOS ADC, 4 times. Beside this expansion, one more amplification stage must be added in the comparator to get the sufficient resolution, and much attention should be paid to the precision of the resistor string and to the charge feed-through problem. A rough estimation from an 8 bit CMOS ADC [5] implies that the size and power consumption of a 10 bit video frequency CMOS ADC will be 21.6 mm x 16.0 mm and 1.2 W respectively.

Taking these problems into account, J. Doernberg has developed a novel algorithm for a high speed, high resolution ADC [1]. Basically, it is a two step ADC. However, it utilizes a parallel binary-weighted capacitor- arrays to quantize the signal. This requires neither sample and hold circuit nor subtractor circuit, which are the most critical analog parts in the conventional two step ADCs.

The most difficult component to design in this ADC is the high speed, high resolution comparator. Because of the two step conversion, it must be operated with the speed much faster than twice of the conventional flash type ADC. Moreover, it has to maintain the 10 bit resolution at that speed.

We have developed a multi-stage fully differential comparator to satisfy those requirements. Here in this paper, the basic analysis and design of the comparator has been discussed in detail.

Fig. 1-1 Application Fields for the High Speed

High Resolution ADC

# CHAPTER 2 TWO STEP PARALLEL A/D CONVERSION

## 2.1 Basic Configuration and Algorithm

As mentioned in the previous section, the parallel conversion technique can perform the A/D conversion in a single clock cycle. However, it requires  $2^N$  comparators and a precisely fabricated, and sometimes trimmed resistor string. For example, to implement a 10-bit, 20 MHz ADC, 1024 high resolution ( $\approx 1$  mV sensitivity) and high speed ( $\approx 50$  nS settling) comparators will be required.

Recently, a 10-bit, 20 MHz ADC fabricated in an ECL process has been reported.[9] However, its chip size is large,  $10 \times 10 \text{ } mm^2$ , and its power dissipation is 2.08 watts. Moreover, it contains eight operational amplifiers (op. amps) to bias the resistor string. This is used for the temperature drift compensation of the bipolar transistor's input bias current in the comparators.

These factors will make it difficult to fabricate this ADC with a high yield rate, and consequently a reasonably low price.

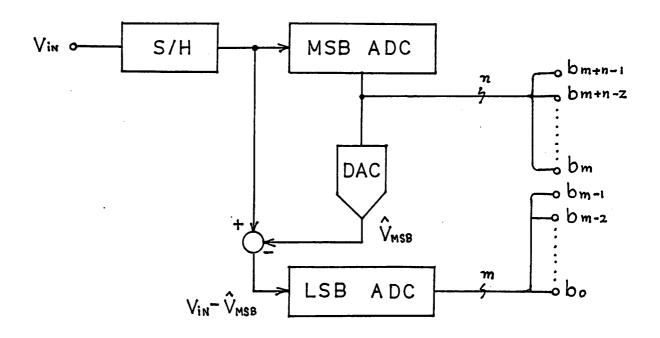

As a solution to these problems, two or multi-step parallel conversion [11] [12] techniques have been proposed. One of the most frequently used technique is shown in Fig. 2.1-1. It executes the m-bit MSBs conversion in the first step, then subtracts the quantized MSBs signal  $\hat{V}_{MSB}$  from the sampled and held input signal  $V_{in}$ , and executes the LSBs conversion as the second step. The disadvantages of this technique is the requirements for high speed settling and precise circuits for the S/H and subtractor. It is difficult to design those circuits with the settling time of less than 20 ns within the error of 0.05% (0.5 LSB resolution in 10 bits).

A promising two-step parallel conversion technique has been proposed by Joey Doernberg. [1] Instead of using a resistor string with  $2^N$  taps as the reference voltage, it has multiple capacitor arrays connected in  $2^N$  different bit patterns. What is important in

this technique is that the S/H and subtract functions are merged in these capacitor arrays. Neither an external S/H circuit nor a subtractor are required.

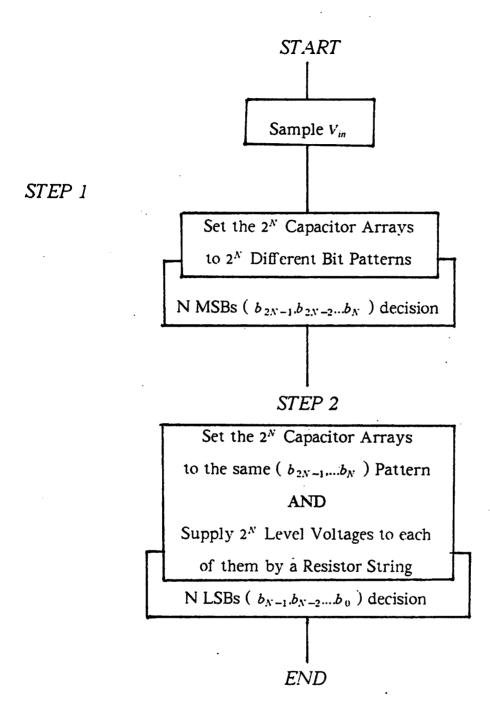

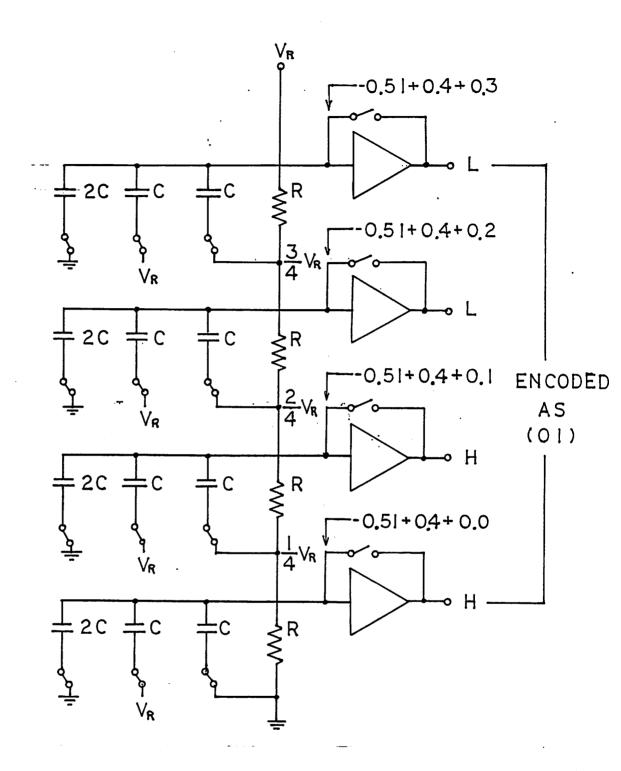

An example of the operation of 4-bit, two-step parallel ADC is shown in Fig. 2.1-3 to 4, and its algorithm in Fig. 2.1-2.

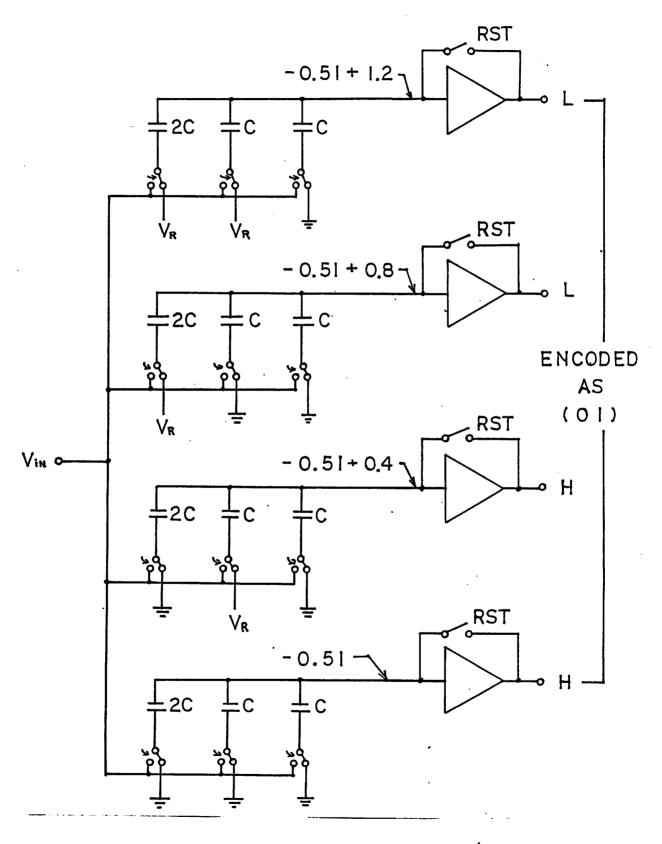

As shown in Fig. 2.1-3, the 4-bit ADC consists of 4 capacitor arrays, each of them containing 3 binary-weighted capacitors. For an N-bit ADC, these numbers will be  $2^{\frac{N}{2}}$  and N/2+1 respectively. Each array has a comparator, and that is shown in the figure as an ideal amplifier with a gain of  $-\infty$ . The bottom plate switches of the capacitors are connected to the input, Vref or GND.

At the start, those switches are connected to the input voltage Vin. At the same time the reset switch around the comparator is closed, in order to set the voltage of the top plates of the capacitors to virtual GND for the ideal case, or to the offset voltage of the comparator generally. In this way, the input signal is sampled on the capacitors. Then all the switches are reconnected to the opposite side. Here the rightmost capacitors are connected to GND, while the other two are connected in 4 different bit patterns. From top to bottom, (11), (10), (01), (00), where we assign 0 for GND, and 1 for Vref. This is the first step of the conversion. If we assume the input voltage of 0.51V (  $(0101)+\Delta$ ), for the reference voltage Vref of 1.6V, then the input voltage of the comparators will take the value as shown in Fig.2.1-3. Here  $\Delta$  is a signal less than 1 LSB, and in the case above,  $0.51=0.5+0.1=\frac{(0101)_2}{(10000)_2}1.6+0.1$ . The outputs from the top to the bottom are ( LLHH ). In this way, the input signal has been measured to be between 0.4V and 0.8V for the 1.6V reference ( full scale ). Therefore, the encoded binary output should be ( b3.b2 ) = ( 0.1 ).

In Fig. 2.1-4, the second step ( the LSBs conversion), is shown. Here, the left two capacitors of all arrays are connected to Vref or GND, depending on the ( b3,b2 ) MSBs data acquired in the first step.

In this example of Vin=0.51V, the 2C's are connected to GND, and C to Vref, taking into account that  $(b3,b2) = (01) \rightarrow (GND,Vref)$ . Simultaneously, the rightmost capacitors are connected to a resistor string, picking up equally spaced voltages. The operations described above shows *THE ESSENCE* of this technique. The functions that are essential for the two step A/D has been accomplished as follows:

1) S/H: Holding the input data on the capacitors all through the two steps.

2) Subtraction: Subtract the quantized MSBs output from the input signal by setting the bit patterns of all arrays to that of the MSBs data.

The input for each comparator is shown in the Fig. 2.1-4, for the input signal of 0.51V. Then the output of the comparators will be (LLHH) from the top to the bottom. And the encoded binary data is (b1,b0) = (01). The full 4-bit data will be  $(0101)_2 = 5$ . and this means the quantized value of 0.5V for the Vref of 1.6V. Details of this operation will be discussed in the section 2.2.

The following are the calculations of some basic design parameters.

The 4-bit ADC consists of 4 capacitor arrays, each of them containing 3 capacitors. (

2C. C and C ) For a N-bit ADC, the number of capacitor arrays will be  $2^{\frac{N}{2}}$ , and the number of the capacitors in each array will be N/2+1. If we define the minimum size capacitor as the unit capacitor, the number of unit capacitors to realize an N-bit ADC will be;

$$N_{CU} = 2^{\frac{N}{2}} \left( \sum_{k=1}^{\frac{N}{2}} 2^{k-1} + 1 \right) = 2^{N}$$

(2.1-1)

For a 4 bit ADC ( N=4 ), this number is 16. For 10 bits this will be 1024. Using a unit capacitor of 8 x 8  $\mu m^2$ , ( 0.05pF capacitor with Tox = 30 nm, and some area margin ) the area will be 65,536  $\mu m^2$ .

The area occupied by the switches of the capacitor array is also an important factor to be considered. To equalize the time constants for each capacitor switch pair, the width of those switches must be also scaled, depending on the size of the capacitances. The minimum size MOS switch will be used with the minimum size capacitor. And its size should be doubled, every time the accompanying capacitor is doubled. The detailed circuit will be shown in Chapter 3. Here we will only count the area of those control switches in units of a unit size MOS transistor. Each capacitor is connected to 4 switches of the same size, except the one that is connected to the resistor string. This rightmost capacitor is connected to 3 switches. So the number of unit size transistors used in the N-bit ADC will be:

$$N_{swu} = 2^{\frac{N}{2}} \left( 4 \sum_{k=1}^{\frac{N}{2}} 2^{k-1} + 3 \right) = 2^{\frac{N}{2}} \left( 2^{(\frac{N}{2}+2)} - 1 \right)$$

(2.1-2)

For a 4 bit ADC, that number is 60. For a 10-bit ADC that will be 4064. If a unit MOS switch of W=5 microns and L=2 microns (Ron = 16 Kohm under Vgs=0.5V, Uexp = 0.4 and KP = 61  $\mu$ A/V<sup>2</sup>) is used, the area of that unit MOS switch can be estimated as 75  $\mu$ m<sup>2</sup>. Then the total area occupied by these switches will be 304,800  $\mu$ m<sup>2</sup>, which is about five times larger than the area occupied by the capacitor arrays. If folded layout is used for the wide MOS switches, this area will be reduced as far as 50% of the size above. If a fully differential configuration is used, this number will be doubled. However, with this technique, it will be possible to reduce the chip area by a large amount, compared to a parallel ADC (flash) discussed in chapter 1.

Because a large number of capacitors are used in this ADC, attention must be taken to the input capacitance Cin. It consists of the the capacitors in the capacitor arrays and the junction capacitors of the MOS switches used there. If we assume that the junction capacitance of the unit MOS switch (including both drain and source) is:

$$C_{iu} = \xi C_{u}$$

Then the input capacitance can be calculated as follows:

$$C_{in} = N_{cw} (1 + \xi) C_{ii} = 2^{N} (1 + \xi) C_{ii}$$

(2.1-3)

For a junction area of 5 microns x 13 microns and Cj of 5 x  $10^{-4}$  F/m<sup>2</sup>, we get  $\xi = 0.65$  for Cu of 0.05 pF. For an ADC of N=10 bit. Cin is calculated to be 84.5 pF.

The acquisition time for the sample and hold can be considered as the time required to charge the capacitor arrays within the desired precision of 0.5 LSB. Let's consider the worst case of sampling a full scale signal of N bits. Because of the scaling of the MOS switches mentioned above, the RC time constant for the charging is the product of the unit capacitance and the Ron of the unit MOS switch. Then the acquisition time to reach the 0.5 LSB precision can be calculated as follows:

$$T_{aq} = C_u R_{onu} \ln(\frac{0.5}{1024}) = 7.62 C_u R_{onu}$$

(2.1-4)

For Cu = 0.05pF and  $Ronu = 16 k\Omega$  this value will be 6ns. But in actual design, the resistance of the signal lines, the maximum current available from the comparator and other factors must also be considered.

Fig. 2.1-1 Two Step Parallel ADC using S/H and Subtractor

Fig. 2.1-2 Two Step Parallel ADC Algorithm

Fig. 2.1-3 MSBs A/D Conversion in the Two Step Parallel ADC (Vref = 1.6V, Vin = 0.51V)

Fig. 2.1-4 LSBs A/D Conversion in the Two Step Parallel ADC (Vref = 1.6V, Vin = 0.51V)

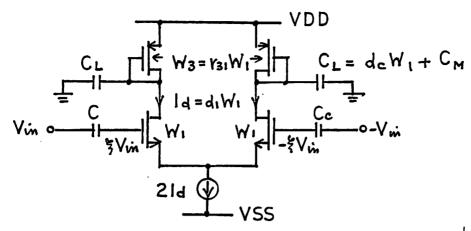

## 2.2 Fully Differential Configuration

In the previous section, the basic circuit configuration of the ADC has been described.

Here, the fully differential version of the same architecture will be discussed.

The advantages of the fully differential configuration is in the increase of the immunity against various common mode noise, and in the doubling of the signal swing. These factors are important in the realization of a high speed high resolution ADC.

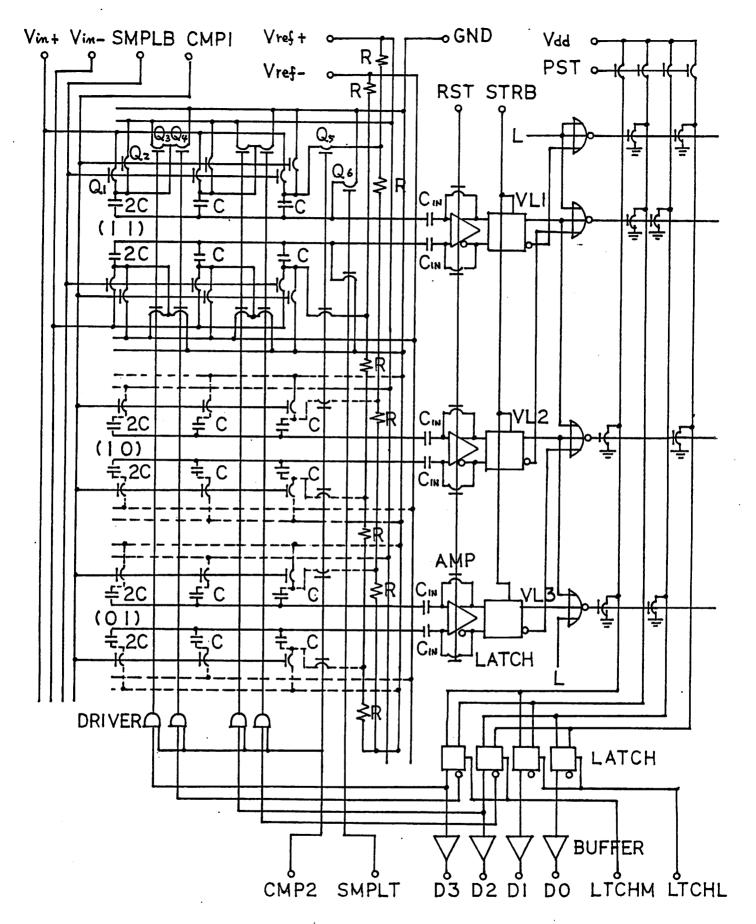

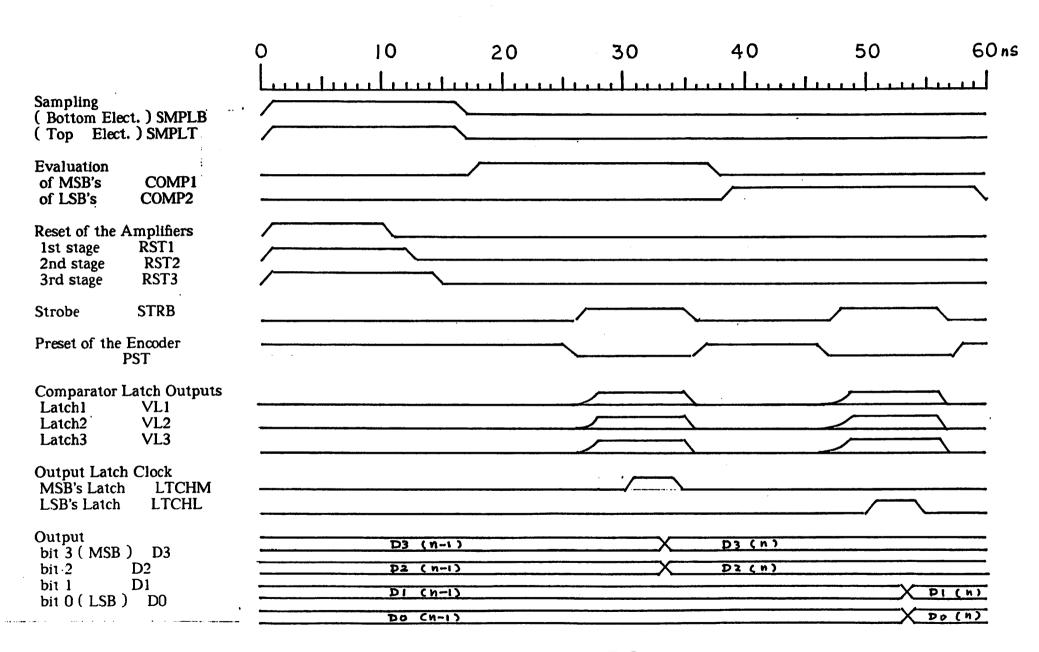

Fig. 2.2-1 shows the basic circuit using a 4 bit model. Fig. 2.2-2 shows the timing chart for its operation. The input signal is supplied in a differential mode at  $V_{in+}$  and  $V_{in-}$  If the input signal is supplied from a single ended device, a precise single to differential mode converter is required. The low input impedance is essential in this ADC. Consequently, a precise transformer will be the best device for this conversion.

In the following part, the A/D Conversion process will be explained. First, the sampling control signals SMPLB and SMPLT are set in their high level (H). Q1 and Q6 turns on, and the input signal is sampled in each capacitor. At the same time, the reset control signal RST is set H, and this closes the loop of the amplifier, sampling its offset voltage in the input capacitor  $C_{in}$ . In the actual case, multi-stage amplifiers are used, in order to achieve a high gain and high speed. (Sec 3.4) Three reset pulses RST1, RST2 and RST3 are shown in the figure. They are opened in that order to sample the feed-through charge from the transistors closing the loop. (Sec 3.3)

After the reset of the amplifiers. (15 ns in Fig. 2.2-2) the sampling switches are open at the same time. Then at 17 ns, the evaluation begins when COMP1 is turned H. There, the capacitors in the array are connected either to ground or  $V_{ref}$ , depending on the code of the comparator. For example, the code of the uppermost comparator is  $(11)_2 = 3$ . In this case, both 2C and C are connected to the  $V_{ref}$ .

During the evaluation period, the small difference between the input signal and the reference is amplified to a sufficient value to turn the latch in the desired direction. This

voltage depends on the device parameter variation of the latch, and is in the order of 100 mV. (Sec 3.2) The time required to achieve this value from the smallest signal of 1 mV is around 10 nS, when three stage amplifier each of the gain-band width of 1,200 Mrad/sec is used. (Sec 3.4) When a sufficient amplification is attained, the strobe STRB is turned H and the output of the comparator is latched.

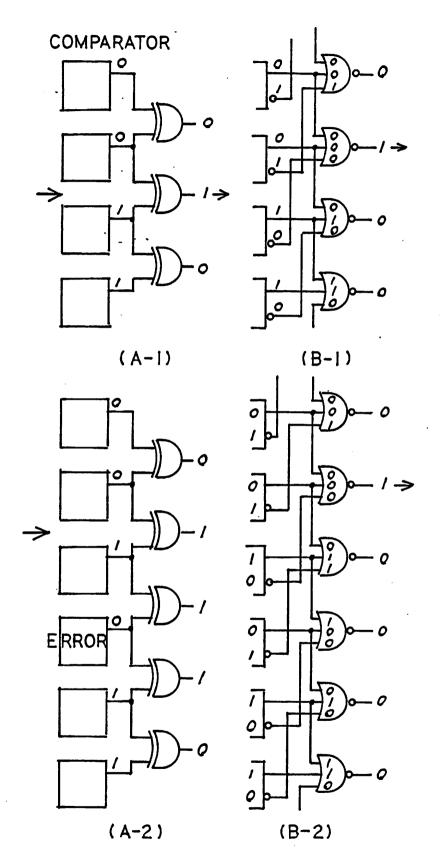

The encoder consists of three input NOR gates and a NOR form complementary 2 bit encoder. The three input NOR gates are used to decode the signal level from the outputs of the comparators. Fig. 2.2-3 shows two possible circuits for the signal level decoder. Here, the circuits in Fig.(A) are using exclusive OR (EXOR) for the decoding. In figures (A-1) and (B-1), the operation without error are shown. Only one of the EXOR or the NOR becomes 1, and that shows the place where the output of the latches turn from 1 to 0. Fig. (A-2) and (B-2) show the decoding process with the existence of an error output from the 4th comparator. In the circuit using EXOR, three gates shows the output of 1, resulting in a error after the NOR form decoder. On the other hand, the decoder using NOR indicates only one position without error. This circuit has such a redundancy that it detects only the first change from 0 to 1 in the comparator's output. However, if the error comes in the third comparator in Fig. (B-2), the decoder will indicate a wrong position. But, this does not make a fatal result. This NOR decoder is now widely used in the flash type ADCs.

For a 4 bit ADC, this NOR gate must drive 2 gates, and for 10 bit ADC, 5 gates, which is not a large load. The delay time here can be designed to be less than 1 ns.

In the NOR form 2 bit decoder, 2 transistors are connected in parallel to the vertical signal line. For the 10 bit ADC, this becomes to 16 transistors in parallel. The load capacitance here is the junction capacitances of the 16 NMOS transistors in parallel, the junction capacitance of the PMOS pull-up transistor and the gate capacitance of the output latch. Again this load is not so large and a delay time less than 2 ns can be achieved in this stage.

The output latch for the MSB signals are also used in the feed-back loop of the ADC to hold the MSB data. It must operate as quick as possible, so that output buffers are required to make its capacitive load small.

The most critical part in the MSB data feed-back path is the driving of the bottom switches for the LSB evaluation. (Q3, Q4 and so on) For a 10 bit ADC 64 bottom switches are connected in the vertical control line. If a unit transistor of W=10  $\mu m$  and L=2  $\mu m$  is considered, the scaled transistor Q3 or Q4 will have the width W of 160  $\mu m$ . This results in the load capacitance of 30 pF. In order to design the delay time within 5 ns. a large size driver with the W of around 150  $\mu m$  will be required for the driver of the most-significant-bit capacitor's bottom switch. Also to drive this large size transistor, a series of inverters scaled by the factor of 1/e will be required.

Taking all these factors into consideration, the delay of this feed-back path could be estimated to be less than 10 ns.

After the MSB data are reproduced in the capacitor array, and the 32 level reference voltages ( 4 level in this figure ) are supplied through Q5, the LSB evaluation starts. After a sufficient amplification can be attained as before, STRB is turned H and the signal is latched.

The LSB data is decoded to a binary code by the same decoder used for MSB.

From this rough estimation, one cycle of conversion can be estimated to be 60 ns at least. In the following section, a SPICE of the full comparator circuit has been performed. It doesn't include the logics, but it shows that a 10 bit resolution can be achieved with the cycle time of 60 ns. There, 10 ns of logic delay has been assumed.

In the actual case, the change of the input signal during the evaluation must be considered. For a numerical example, the 2.5 V full swing signal of 5 MHz has the maximum rate of change of 79 mV / ns. The ADC must sample and hold this signal. The techniques used to solve this problem will be discussed in detail by J. Doernberg [1].

Fig. 2.2-1 Fully Differential Configuration of the A/D Converter ( 4 bit Model )

Fig. 2.2-2 Timing Chart of the A/D Converter

Fig. 2.2-3 Function of the Signal Level Decoder

#### CHAPTER 3 COMPARATOR DESIGN

#### 3.1 Introduction

The most critical part for the designing of a high-speed high-precision ADC is the comparator. This is true especially for the two step ADC, where the comparator must operate in twice the speed of a conventional flash type ADC.

CMOS amplifiers inherently suffers from a large offset voltage. On the other hand, their input impedance is so high that it is easy to sample these offset voltages in capacitances. However, the problem of feed-through charge injection from the loop-closing switches arises. To solve this problem, a special sequence for the loop-closing switch operation is used. This is reviewed in Sec. 3.3. Moreover, the advantage of a fully differential configuration to prevent amplifier's saturation by these feed-through charge has also been discussed.

The reset speed is equally important as the signal evaluation speed. Sometimes it takes as much time as in the evaluation. The speed and stabilization during the reset operation is discussed in Sec.3.4.

For a high-speed high-precision comparator, the utilization of a multi-stage amplifier configuration is essential. Basic analysis and SPICE simulations of this multi-stage configuration are reported in Sec.3.5.

The amplifier to be used in this configuration should have a much higher gain bandwidth than the conventional CMOS amplifiers. Some new approach for the design of these amplifiers has been discussed in Sec.3.6.

A regenerative latch is required to amplify the small signal to a logic level and then hold it. The speed of a latch depends not only to the transient response speed, but also to its sensitivity, or the minimum input signal required to amplify the input signal in the correct direction. Sec. 3.2 explains these points in detail.

In the last section of this chapter, a SPICE simulation of a full circuit of the comparator has been performed. This simulation has been accomplished in an early stage, before the optimization of the amplifiers described in Sec. 3.6. Therefore, an early version of a fully differential amplifier has been used. However, it demonstrated the feasibility of this ADC architecture and the 3 stage amplifier with one latch configuration.

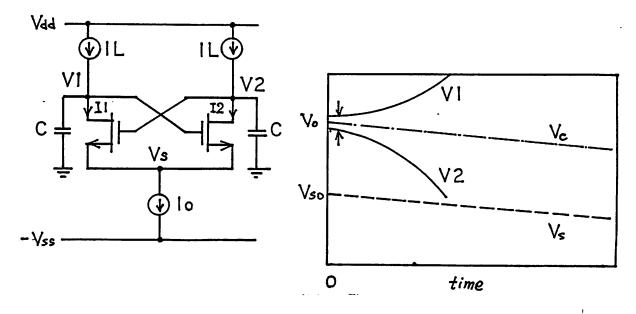

# 3.2 High Speed Latch Design

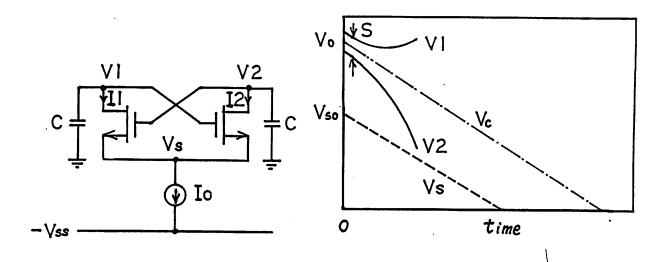

The speed of a latch can be determined by two factors. One is the transient speed. and the other is the sensitivity or the minimum input signal required to amplify the signal in the desired direction.

When a latch with a cross-coupled common-source transistor couple is considered, the transient response is an exponential one. The input signal is amplified rapidly by its positive-feedback mechanism. This is explained in detail in the appendix A. The time constant there can be calculated as  $C_L/g_m$ , where  $C_L$  is the load capacitance and  $g_m$  is the trans-conductance of the driver transistor.

Even with the high speed transient response, the overall speed of the latch depends also on its sensitivity. If the sensitivity is low, much time should be spend at the amplification in the previous stages to acquire a sufficient amplitude of the signal. The sensitivity of the latch is analyzed in detail in appendix B.

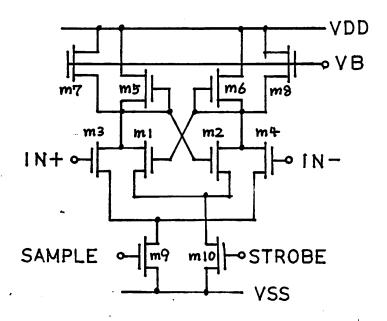

Fig. 3.2-1 shows the basic circuit of the latch used in the SPICE simulation of the full size comparator. (Sec 3.7) Here, the last stage of the multi-stage amplifier m3 and m4 is merged with the cross-coupled transistor latch m1 and m2. The load transistors m5 to m8 are used in common. The selection between the amplifier and the latch is performed by two transistors m9 and m10. By this configuration, the signal from the amplifier is directly coupled to the latch, making the transient speed fast. The drawback of this circuit is that the amplifier cannot be reset independently. However, the offset in the last stage result in a small equivalent input offset, divided by the gain of the previous stages. (Sec 3.3) In the actual circuit, more switch transistors are required for the proper operation. These are explained in Sec. 3.7.

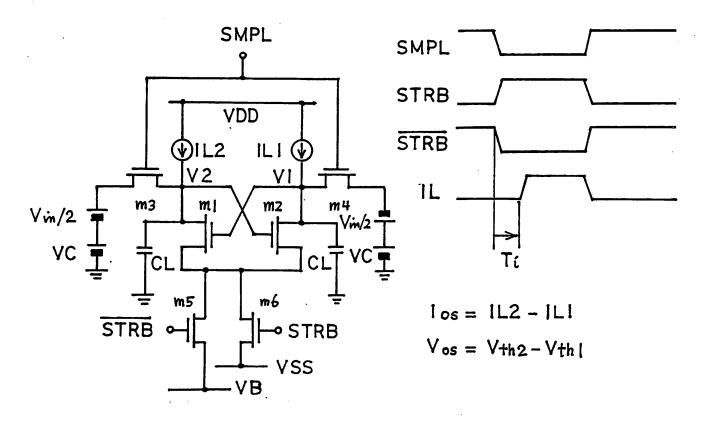

A basic SPICE simulation has been performed for the design of the latch. Fig. 3.2-2 shows the circuit used there. Here, the differential input signal  $V_{in}$  is sampled directly to the drains of m1 and m2 through the transistors m3 and m4. During the sampling period,

the sources of m1 and m2 are connected to some bias voltage  $V_B$  to cut off these transistors. After the sampling is finished, the strobe pulse STRB is turned high and after a certain delay time of  $T_i$ , the current sources IL1 and IL2 become active. The difference in the threshold of the transistor pair m1,m2 and the difference in the current of the sources IL are described by offsets  $V_{os}$  and  $I_{os}$  respectively.

The load current is 100  $\mu A$  , the load capacitance  $C_L$  is 0.1 pF and the dimensions of the driver transistors m1 and m2 are W/L = 27  $\mu m$  / 2  $\mu m$ .

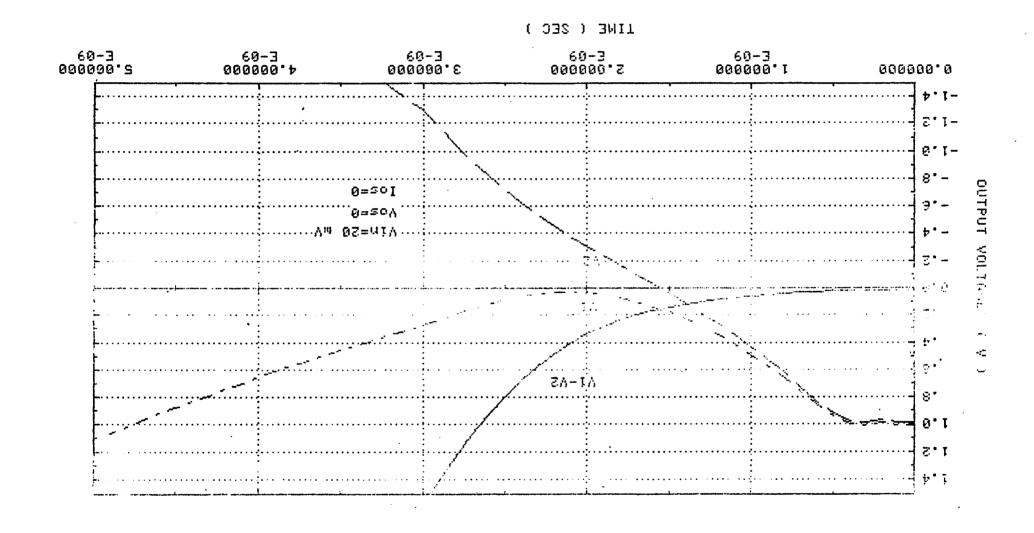

Fig. 3.2-3-1 shows the simulation result when no offset exists. The node voltages V1 and V2 falls due to the difference between the current IL1+IL2 and the current flowing m6. The differential output V1-V2 increases exponentially as calculated in appendix A. The time constant in the simulation result is 0.5 ns. The time constant estimated from  $C_L/g_m = 0.1 \text{ pF}/285 \,\mu\text{A}/V$  is 0.35 ns.

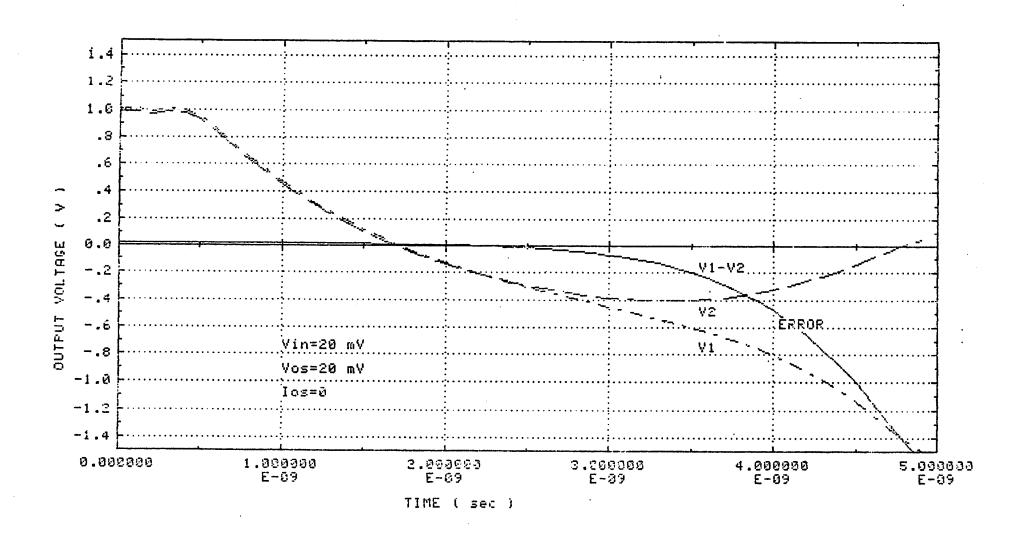

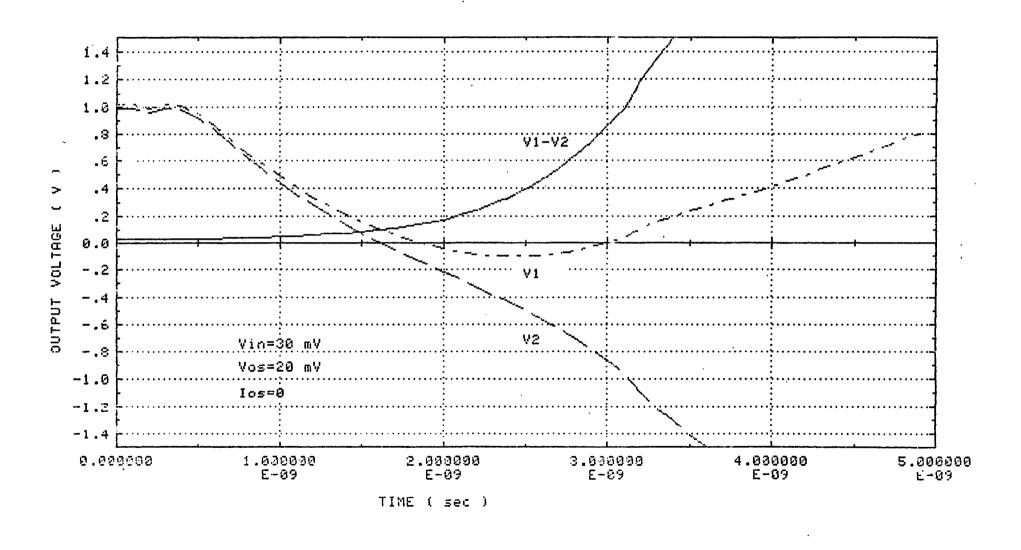

Fig. 3.2-3-3 shows the simulation result with an offset of  $V_{os} = 20$  mV. It is clear from appendix B. Eq. (B-18) that the minimum input voltage to amplify the signal in the desired direction is just  $V_{os} = 20$  mV. In this simulation, the input voltage is in its critical value of 20 mV, and the signal has been amplified in the wrong direction.

In Fig. 3.2-3-3, the offset voltage is still assumed to be 20 mV. However, the input signal is increased to 30 mV, and the signal is amplified in the correct direction.

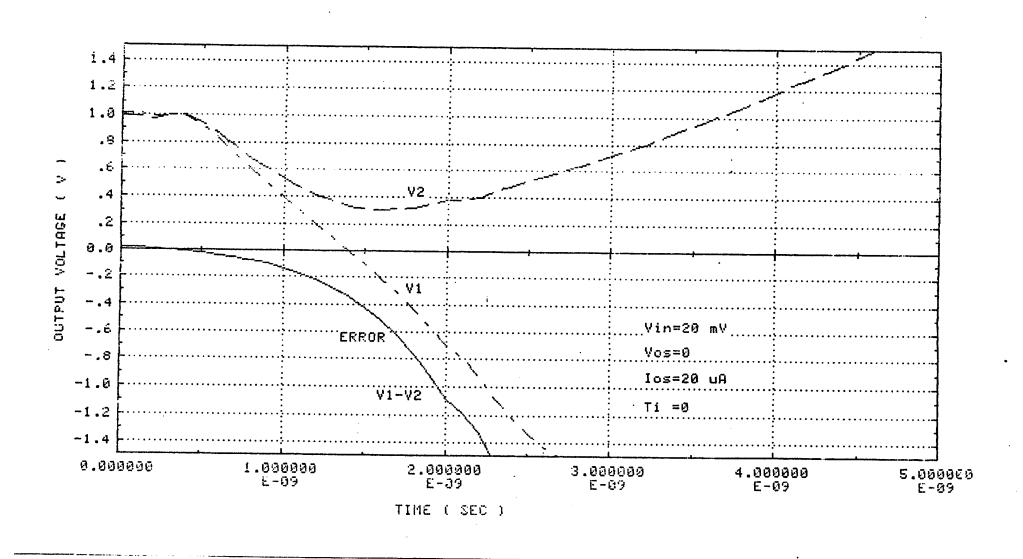

Fig. 3.2-3-4 shows the simulation under the offset current  $I_{os}=20~\mu A$  and the input signal of 20 mV. From appendix B Eq. (B-18), the sensitivity of the latch can be estimated as:

$$\frac{I_{os}}{\alpha C_L (V_{s0} - VC + V_{th})}$$

Here,  $\alpha$  is the rate of voltage change in the source of m1 and m2.  $V_{s\,0}$  is the initial voltage of that source, VC is the common mode voltage at the input, and  $V_{th}$  is the threshold voltage of the driver transistors m1 and m2. This value can be calculated to be 260 mV, under the condition of  $\alpha = 334$  mV/ns,  $V_{s\,0} = 2.5$  V,  $V_{th} = 0.8$ , VC=1.0 V and  $C_L = 0.1$ pF.

This is a relatively large value.

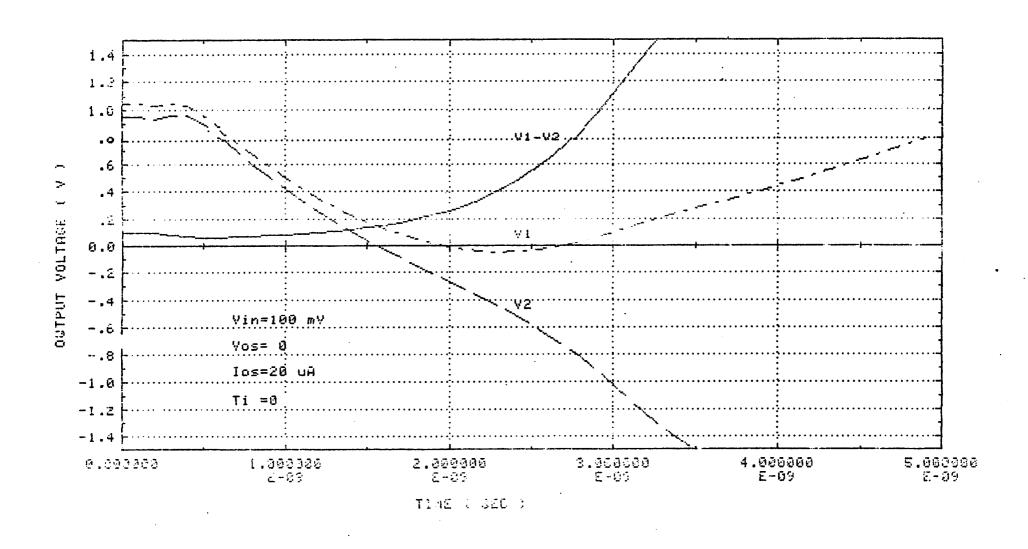

Fig. 3.2-3-5 is the simulation result of the latch with the same current offset  $I_{os}$  as before, but with the input voltage of 100 mV. Here, the signal has been amplified in the correct direction. The critical sensitivity seems to be less than the value of 260 mV calculated above.

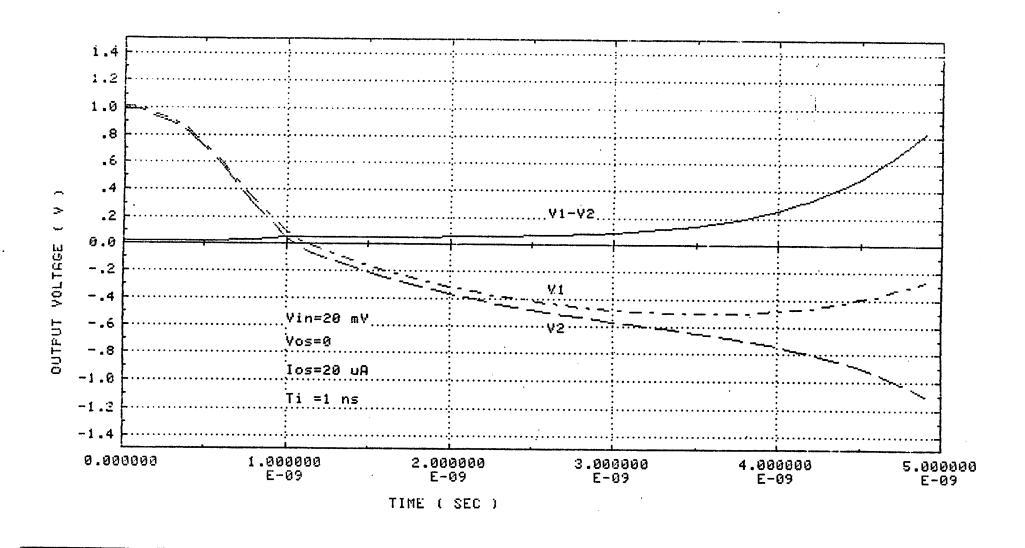

As shown in the appendix B, this poor sensitivity due to the offset  $I_{os}$ , can be improved by supplying the current with a certain delay  $T_i$  after the strobe. During this delay, the latch can amplify the signal to a sufficient value, without experiencing the current offset. This is shown in Fig. 3.2-3-6. Here, the load current is activated 1 ns after the strobe signal. The signal is amplified sufficiently before the current sources are activated, and the signal is amplified in the correct direction. This technique is also used in the DRAM sensing amplifiers.

As the conclusion of this section, the speed of a latch is determined not only by the transient response, but also by the sensitivity of the latch. Fqually attention should be paid to the matching of the current sources and driver transistors, as well as its current amount and device size.

Fig.3.2-1 Basic Circuit Configuration

Fig.3.2-2 Circuit used for a Basic Simulation

Fig.3.2-3-2 Simulation Result (2)

Fig.3.2-3-3 Simulation Result (3)

Fig.3.2-3-4 Simulation Result (4)

Fig.3.2-3-5 Simulation Result (5)

Fig.3.2-3-6 Simulation Result (6)

## 3.3 Offset Cancellation of the Multi-Stage Amplifier

The offset voltage of a MOS amplifier is much larger than that of the bipolar amplifiers. Even with the well controlled fabrication process, the mismatch of the threshold voltage between two adjacent transistor is larger than 10 mV. This value is about 10 times larger than the  $\frac{1}{2}$  LSB voltage of 1 mV. ( Here, a 10 bit ADC with the reference voltage of 2.048 V has been assumed. )

On the other hand, the MOS transistors have a very high input impedance which make the holding of a signal very easy. By utilizing this property, the offset voltage can be stored on a coupling capacitor which is connected between the multi-stage amplifiers. Moreover as described below, the feed-through charge can also be stored in these capacitors by a proper sequence of the reset switches.

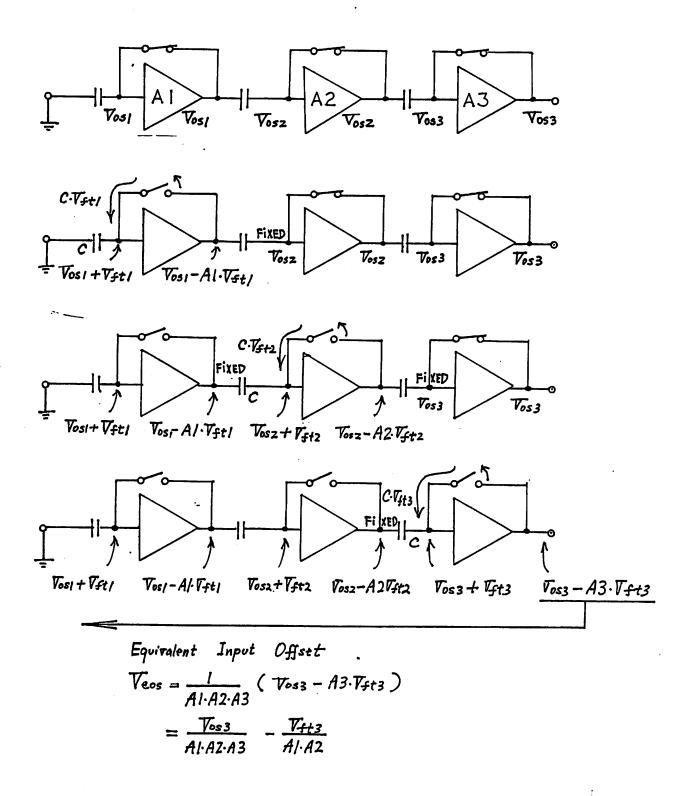

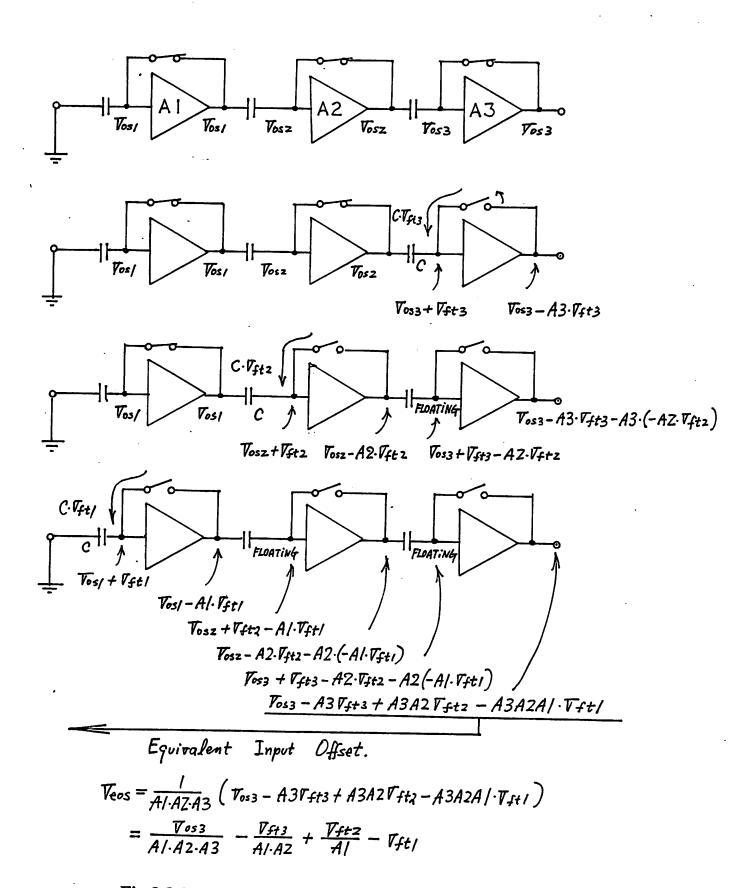

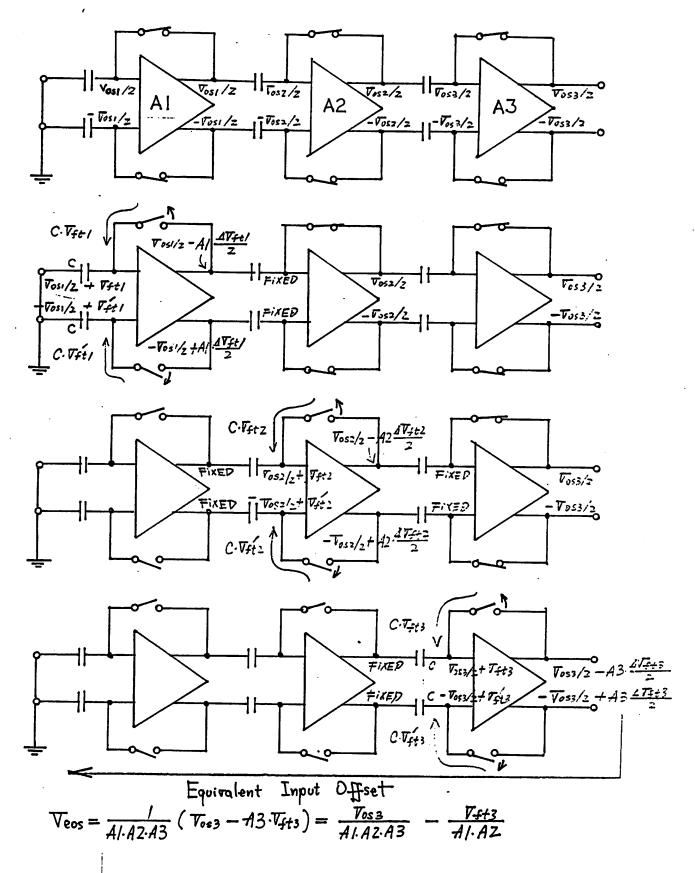

Fig.3.3-1 shows a multi-stage amplifier of three stages and its reset switch operation sequence. There are many orders in the sequence to open these switches after the reset has been accomplished. (3!=6 ways) Here, the two extreme cases has been examined.

In this figure, the switches are opened from the top (left) to the last (right). When all those switches are closed, the offset voltage  $V_{osi}$  appears in the output and input terminal of each amplifier. When the leftmost switch is opened, the feed-through charge  $CV_{fil}$  is stored at the input node. At the same time,  $V_{fil}$  is amplified by the first amplifier and that voltage is stored on the coupling capacitor connected in the output of the first amplifier. This is capable, because the second amplifier is in a closed-loop state, and consequently its input node voltage is fixed to its offset voltage  $V_{os}$ .

In this order, the second and third switches are opened. On the last stage, the output appears to be;

$$V_{os3} - A 3V_{ti3}$$

This offset is referred at the input equivalent offset voltage  $V_{cos}$  as:

$$V_{eos} = \frac{V_{os3}}{A 1A 2A 3} - \frac{V_{ft3}}{A 1A 2}$$

If the gain of the amplifiers is sufficiently large, the input offset voltage can be suppressed within  $\frac{1}{2}$  LSB. As a numerical example, suppose that the offset voltage  $V_{os}$  is 10 mV, the feed-through voltage  $V_{ft}$  is 0.354 V (switch size W/L= 5  $\mu m$  / 2  $\mu m$ ,  $C_{ox}$  = 1.4 fF/ $\mu m^2$ , control voltage swing 5 V and C= 0.2 pF) and the gain is A1=A2=A3=10.

From the equation above,  $V_{eos}$  is -0.77 mV, which is less than  $\frac{1}{2}$  LSB.

The drawback of this single-ended circuit is the saturation of the amplifier by the large feed-through voltage. For example, the output voltage of the last stage is -1.75 V, which is large enough to saturate the last stage. As described in the following, this problem can be solved by using a fully-differential configuration.

Fig.3.3-2 shows the offset voltage when the switches are opened in the order of right, middle and left. This is the other extreme case. Once the switch in A3 is opened, its input node becomes floating and the amplifier is active. Under this condition, the feed-through voltages from the previous stages are amplified. This results in a large offset voltage as shown in the figure.

Fig. 3.3-3 shows the offset sampling for a fully-differential configuration. The equivalent input offset voltage  $V_{eos}$  has the same value with the non-differential configuration. However, the advantage of this configuration is in the small feed-through voltage amplification. As shown in the figure, only the difference of the feed-through voltage  $\Delta V_{fi}$  is amplified. If the dimension of the switches is matched within 10 %, the output swing due to the feed-through amplification can be reduced to 10 % of the previous value. With the same parameters used above, the output voltage due to the feed-through  $A \, 3\Delta V_{fi} \, 3$  can be reduced to 177 mV. This value is small enough to prevent saturation.

Fig.3.3-1 Sampling of the Offset and Feed-through Voltage in a Single-Ended Multi-Stage Amplifier ( Correct Sequence )

Fig.3.3-2 Sampling of the Offset and Feed-through Voltage in a Single-Ended Multi-Stage Amplifier (Wrong Sequence)

Fig.3.3-3 Sampling of the Offset and Feed-through Voltage in a Fully-Differential Multi-Stage Amplifier

# 3.4 Transient Response of the Multi-stage Amplifier

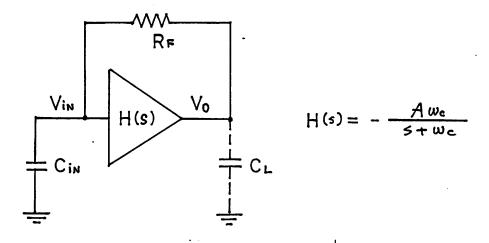

In this section, the design of the optimum number of stages N for the multi-stage preamplifier will be discussed. For the first order approximation, a single pole amplifier will be used in the following analysis. This is a reasonable assumption for the single differential amplifier followed by a source follower, which are going to be used in this comparator design. If we assume the DC gain and cut off frequency of such an amplifier to be Ao and  $\omega_c$ , respectively, its transfer characteristic will be:

$$A(\omega) = \frac{A_0}{1 + j\frac{\omega}{\omega}}$$

(3.4-1)

The step response for the amplifier above can be easily calculated to be:

$$V_{out}(t) = A_0 V_{in} (1 - e^{-\omega_c t})$$

(3.4-2)

Here. Vin is the amplitude of the input step. The acquisition time required to get the output to Vreq is:

$$T_{acq} = \frac{1}{\omega_{c}} ln \left( \frac{1}{1 - \frac{V_{req}}{A_{o}V}} \right)$$

(3.4-3)

If the product of the DC gain Ao and the input voltage Vin is much larger than the required output swing Vreq, the equation above will be simplified as:

$$T_{acq} \approx \frac{1}{\omega_c} ln \left( 1 + \frac{V_{req}}{V_{iu} A_0} \right) \approx \frac{1}{\omega_c} \frac{V_{req}}{V_{in} A_0} = \frac{V_{req}}{V_{in}} \frac{1}{GBW}$$

(3.4-4)

The acquisition time is inversely proportional to the Gain Bandwidth, GBW = Ao  $\omega_c$ .

Analogous to the single stage response, the response for the N stage preamplifier may be considered as follows. The GBW for the multi stage preamplifier can be calculated as in the Appendix C, and its value is

$$GBW = \sqrt{2^{N} - 1} \omega_{c} A_{0}^{N}$$

(3.4-5)

Next. some numerical examples are shown. Under the conditions of  $\omega_c$  = 333Mrad, Ao=10 and Vreq/Vin=1000, Tacq is 0.723nS for N=4 and 0.0783nS for N=5. SPICE calculations have been performed for the same parameters, and the results are Tacq=7.0nS for N=4 and 5.25nS for N=5. The failure of the calculation above has come from the neglection of the phase shift for the multi-stage preamplifier. The phase shift at  $\omega$  is not

$$\Phi = -Tan^{-1}(\frac{\omega}{\omega_m}) = -Tan^{-1}(\frac{\omega}{\omega_m})$$

(3.4-6)

like a single pole amplifier, but

$$\Phi = -NTan^{-1}(\frac{\omega}{\omega_c}) \tag{3.4-7}$$

In this way, the phase shift increases proportionally to the number of stages N, and this makes the delay much greater than that estimated by Eq. (3.4-3) to (3.4-5).

The SPICE calculation can give us the correct answer, but it is insufficient if an intuitional search for the optimum number of stages N is required. In the following, a very simple analytical equation for the acquisition time Tacq will be presented. It coincides with the results of SPICE with a relatively small error, and moreover it can explain the dependence of Tacq on  $\omega_c$ ,  $A_0$  and N more clearly.

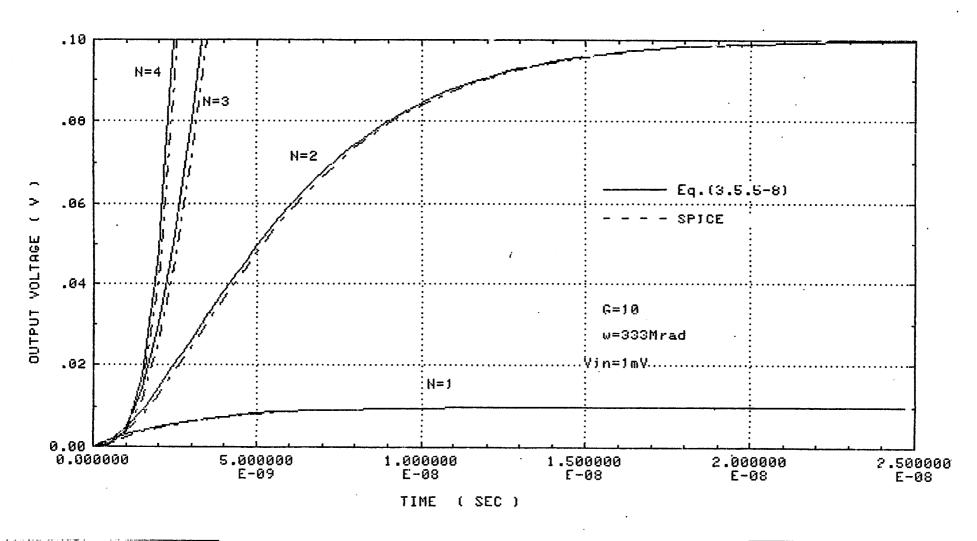

The accurate calculation for the transient response of the multi stage preamplifier has been performed in Appendix C. Here, the solution is repeated.

$$V_{out}(t) = A_0^N V_{in} \left\{ 1 - e^{-\omega_c t} \sum_{k=0}^{N-1} \frac{(\omega_c t)^k}{k!} \right\}$$

(3.4-8)

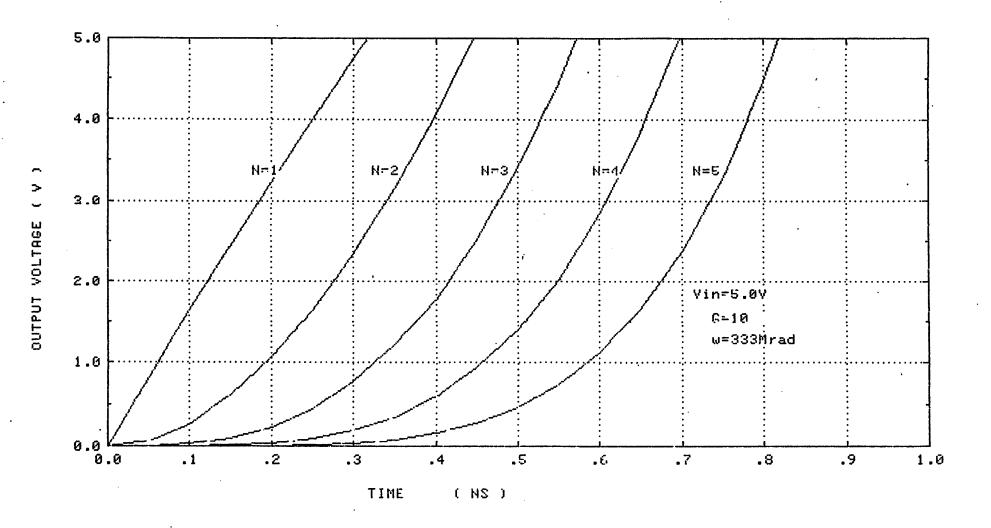

Fig. 3.4-1 shows the transient response for a series of multi-stage amplifiers, calculated from Eq. (3.4-8) and from SPICE. The curves calculated from the equation above coincide well with those calculated by SPICE with a small error.

Fig. 3.4-2 shows the transient response calculated from Eq. (3.4-8), but with the output voltage range equal to the input voltage of 5V. This is the situation experienced in a multi stage inverters (logic). Here, the greater the number of stages that are used, the greater the delay will be. This is different from the result above, where the input signal has to be amplified to a much higher value than the input.

Substituting Tacq for t and Vreq for Vout(t), in Eq.(3.4-8), and then solving for Tacq, we'll get:

$$T_{acq} = -\frac{1}{\omega_c} ln \left( 1 - \frac{V_{req}}{A_0^N V_{in}} \right) + \frac{1}{\omega_c} ln \left( \sum_{k=0}^{N-1} \frac{(\omega_c T_{acq})^k}{k!} \right) \quad . \tag{3.4-9}$$

The first term in the right hand side is analogous to the right hand side of Eq. (3.4-3). The second term is added to that as the effect of the phase shift in the multi stage preamplifier. In order to make the dependence of  $T_{acq}$  on the GBW and Vreq/Vin much clearer, the following assumptions have been made.

$$V_{req} << A_0^N V_{in}$$

$\omega_c T_{acq} << 1$

Those mean sufficient gain and short acquisition time compared to  $\frac{1}{\omega_c}$ . Then Eq. (3.4-9) can be approximated as follows (Appendix E);

$$T_{acq} = \frac{1}{\omega_{c}} \left( \frac{6V_{req}}{A_{0}^{N}V_{in}} \right)^{\frac{1}{3}}$$

(3.4-10)

From the equation above, it is much more effective to increase the gain Ao, rather than the cutoff frequency  $\omega_c$ , in order to achieve a high speed acquisition. The difference is of the exponent factor of N/3-1. But in the actual implementation, the number of stages is

3 or 4. So there is not so much difference. Another interesting point is the dependence of  $T_{acq}$  on Vreq/Vin. It is proportional to the 1/3 power of Vreq/Vin and not to the value itself. This means that there is no significant acquisition time increase to get a high resolution ( high Vreq/Vin ) comparator. For example, the 1/10000 resolution can be achieved by only 10 times longer acquisition time compared to that of an 1/10 resolution.

Another approximation for  $T_{acq}$  has been reported. [13] That is reviewed in Appendix C and repeated here.

$$T_{acq} = \frac{1}{GBW} \left( \frac{V_{req} N!}{V_{in}} \right)^{\frac{1}{N}}$$

(3.4-11)

In spite of its extreme approximation, it can explain the dependence of  $T_{acq}$  on Vreq/Vin or GBW from a qualitative point of view.

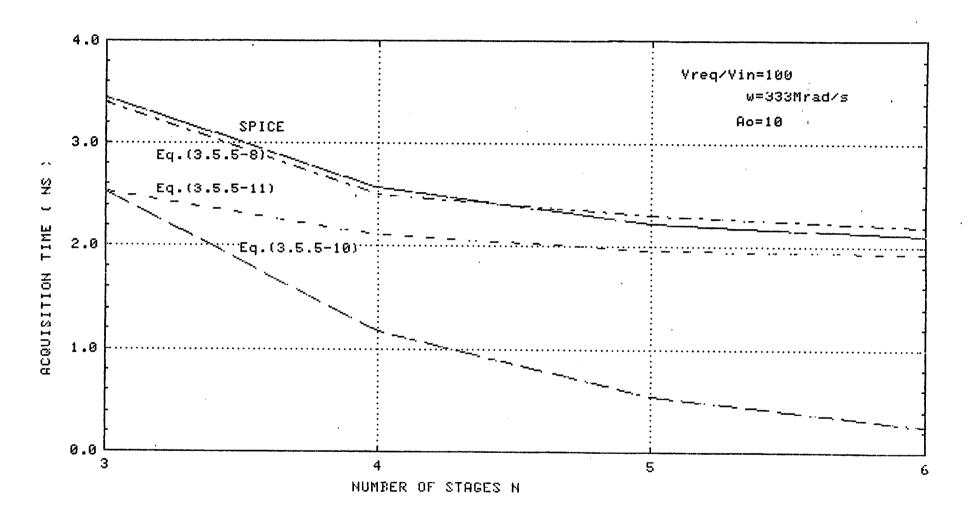

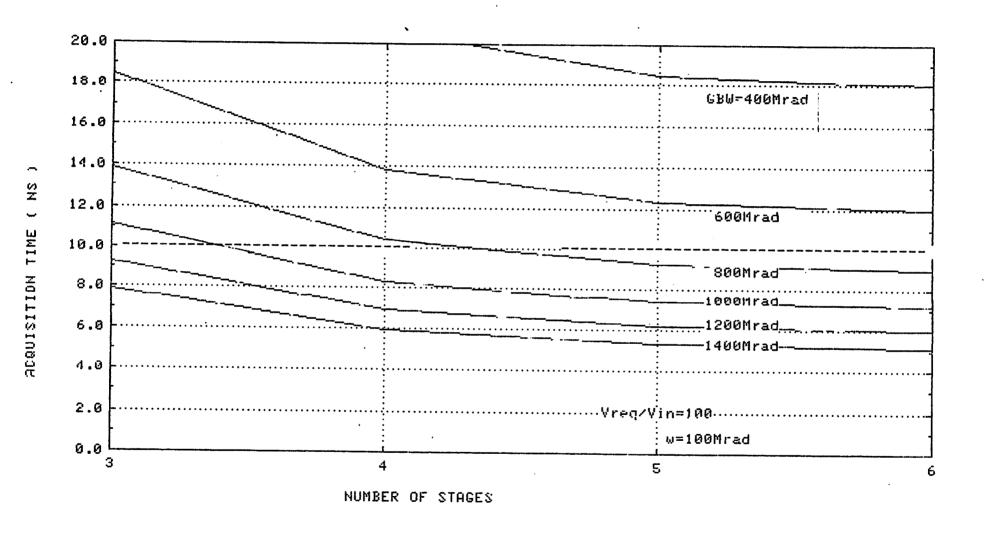

Fig. 3.4-3 shows the plot of Tacq vs N calculated from Eq. (3.4-11), the accurate analytical Eq. (3.4-8), its approximated form of Eq. (3.4-10) and SPICE simulation. The accurate analytical equation coincides well with the SPICE simulation. Eq.(3.4-11) shows relatively small error compared to Eq (3.4-10). The following data are calculated by Eq. (3.4-8). However, Eq. (3.4-10) or Eq.(3.4-11) can help to make clear the relations between  $T_{acq}$  and Vreq/Vin or GBW. They will be discussed in the following.

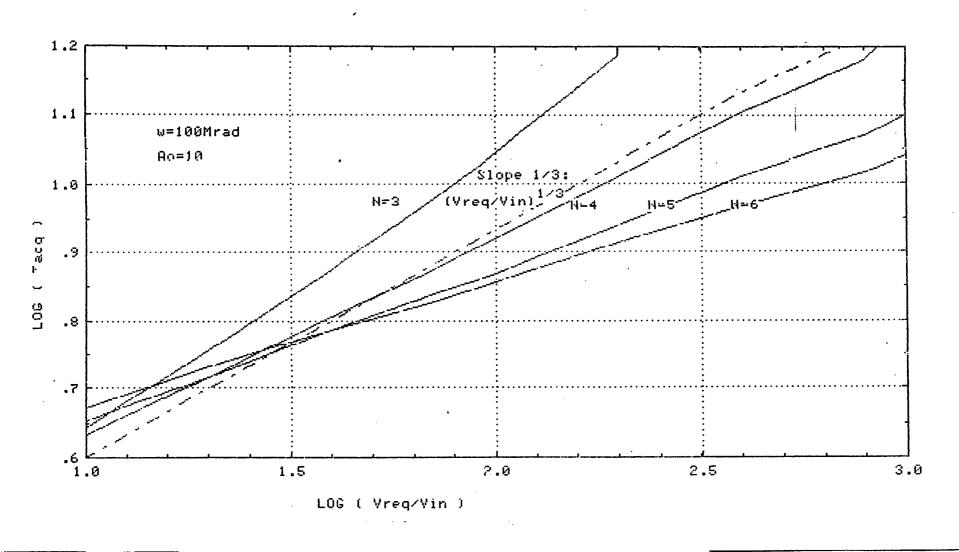

Fig. 3.4-4 is a log-log plot of  $T_{acq}$  vs Vreq/Vin. It will be seen that  $T_{acq}$  is not directly proportional to Vreq/Vin. but rather proportional to its 1/N power, as in Eq.(3.4-11). The slope decreases slightly as the number of stages N increases.

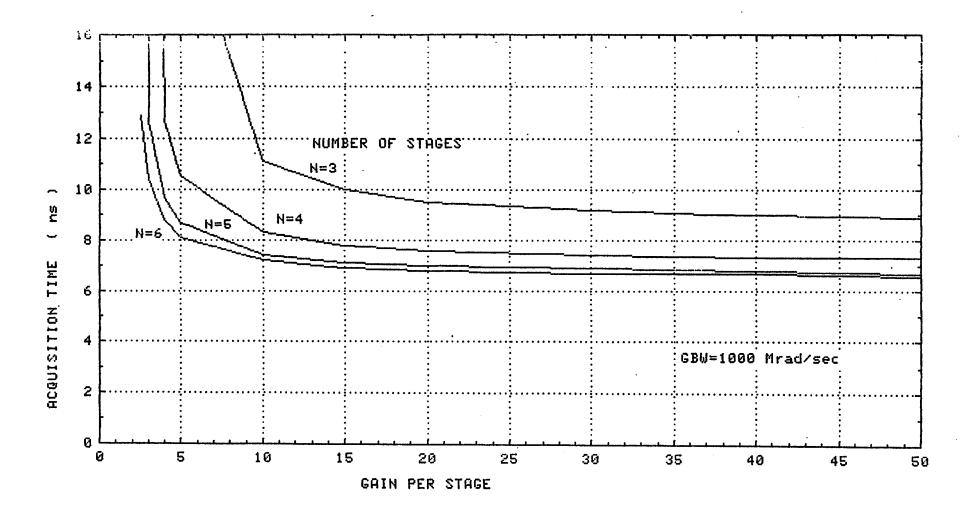

Fig. 3.4-5 shows the dependence of  $T_{acq}$  on gain Ao, under the condition of a constant GBW of 1000Mrad. Here the value of Vreq/Vin=100. For N larger than 4, and gain larger than 10.  $T_{acq}$  is almost independent to the gain change. It is interesting that GBW solely can predict the response. This could be explained by Eq.(3.4-11), but not by Eq.(3.4-10). For large N, higher order terms should be included in the approximation.

When the gain  $A_0$  is less than  $(Vacq/Vin)^{1/N}$ , it is impossible to acquire the value of

Vacq. Before that critical value, Tacq begins to rise, when the gain becomes relatively small. This is explained by Eq.(3.4-10). For N=6, Tacq will be inversely proportional to the gain.

The dependence of  $T_{acq}$  on the number of stages N is shown in Fig. 3.4-6. Here, Vreq/Vin=100 is assumed. The curve begins to saturate above N=3. Considering the space and power required in the multi stage comparator, it will be better not to use more than 3 stages. This will be discussed in the summary section of this chapter.

As described in the previous sections, the acquisition time should be required to be less than 10 nS. To realize this with 3 stage preamplifier, a GBW of more than 1200Mrad will be required. Here, the concept of GBW, and not of  $\omega_c$  and Ao separately, is applicable, due to the result from Fig.3.4-5.

For the design of the comparator, a simple equation explaining all the characteristics mentioned above, should be used. From the previous discussion, the best way will be to use Eq.(3.4-11), with a correction coefficient  $\alpha$ .

$$T_{acq} = \frac{\alpha}{GBW} \left(\frac{V_{req} N!}{V_{in}}\right)^{\frac{1}{N}}$$

(3.4-12)

Here the value of  $\alpha$  is approximately 1.1 to 1.4, depending to the number of stages N.

Fig.3.4-1 Transient Response of a Multi-Stage Amplifier

( Vreq/Vin=100, GBW=3330 Mrad/s )

Fig.3.4-2 Transient Response of a Multi Stage Inverter

( Vreq/Vin=1.0, GBW=3330Mrad )

Fig.3.4-3 Acquisition Time versus Number of Stages

Fig.3.4-4 log-log Plot of Acquisition Time versus Vreq/Vin

Fig.3.4-5 Acquisition Time versus Gain Ao under a constant GBW

Vreg / Tin = 100

Fig.3.4-6 Acquisition Time versus Number of stages for various GBW.

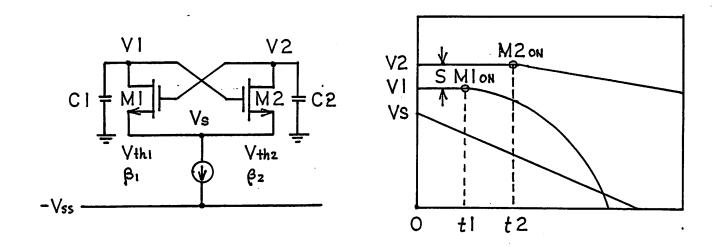

## 3.5 Reset Speed and Stabilization

For a high speed comparator, the reset speed is equally important as the evaluation speed. In the actual case the same amount of time or more is spent for the reset.

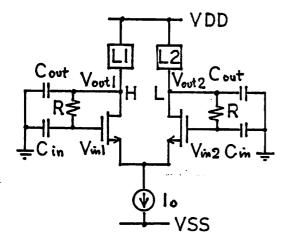

Fig.3.5-1 (A) shows the basic circuit of the amplifier with a closed loop. L1 and L2 are the loads expressed in a general form. R is the resistance of the switch closing the loop,  $C_{out}$  and  $C_{in}$  are the output and input capacitances respectively.

From appendix D and F, it is clear that the reset process can be divided in two distinct phases. In the first phase, the reset speed is determined by the RC constant, where R is the resistance of the loop-closing switch and C is the series capacitance of  $C_{out}$  and  $C_{in}$ . (Fig. 3.5-1 (B)) During this phase, the input and output voltages approach each other.

If the time constant of the amplifier, the inverse of the cut-off frequency, is much smaller than the RC time constant, this time constant of the amplifier will determine the overall decay. This is explained in appendix F.

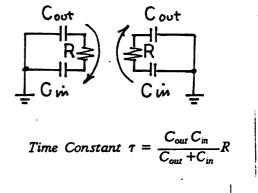

After  $V_{in}$  and  $V_{out}$  approach to the same value, the circuit enters to the second phase. (Fig. 3.5-1 (C)) Here, the parallel capacitor  $C_{in} + C_{out}$  is charged or discharged through two conductances  $g_m$  and  $G_L$ .  $G_L$  is the conductance of the load and  $g_m$  is the conductance of the diode connected driver transistor.

If a current source load is used here,  $G_L$  is small, and it will take more time for the comparator to be reset when compared to the diode-connected MOS load. (Sec 3.6) However, a certain gain is required in each amplifier, so that  $G_L$  of the diode load cannot be made too large. In both case,  $g_m$  will dominate the time constant.

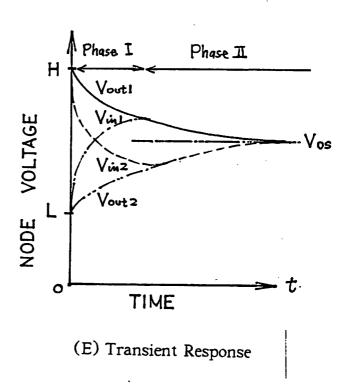

Fig. 3.5.1-(E) shows the modeled transient response during the reset.

Some SPICE simulations are performed to verify this characteristic. The amplifiers used here are: (1) Fully-differential amplifier with diode and current source loads, and (2) Fully-differential- cascode amplifier with diode and current source loads. These circuits

are described in detail in Sec. 3.6.

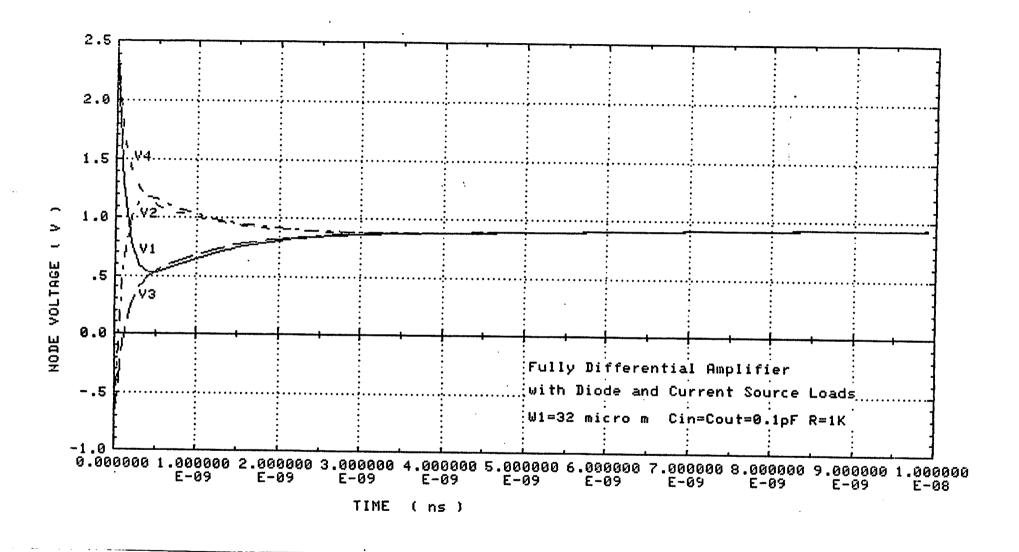

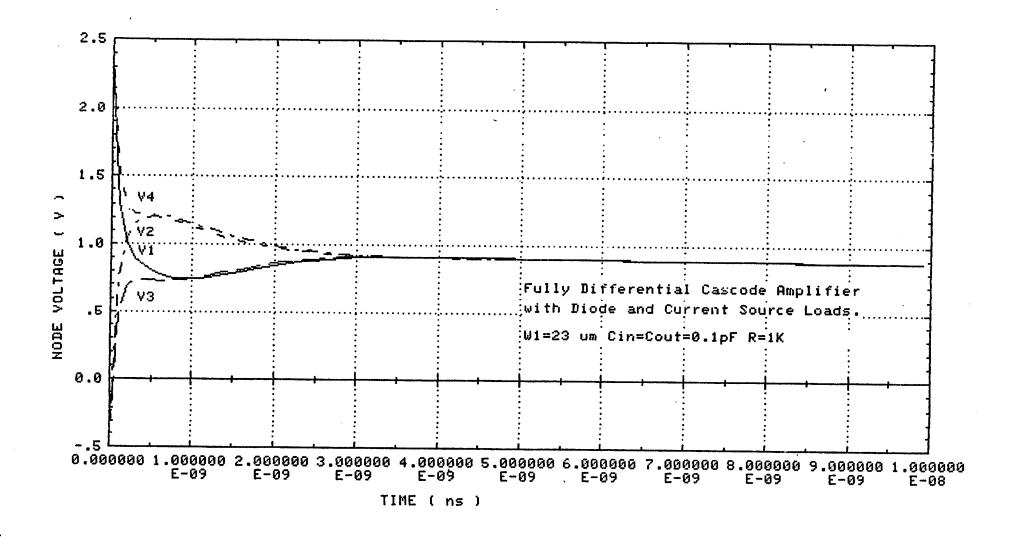

Fig. 3.5-2 is the results of the transient response simulations for the reset of those fully-differential amplifiers.

In Fig.3.5-2 (1), a resistance of R=1 k  $\Omega$  is used, so that the RC time costant can be calculated as 1k\*0.1pF/2 = 0.05 ns. The time constant extracted from the simulation is 0.1 ns. The time constant calculated for the second phase is

$$\frac{C_{in} + C_{out}}{g_{in}} = \frac{0.2pF}{270\mu A/V} = 0.74ns$$

That value extracted from the simulation is 0.65 ns.

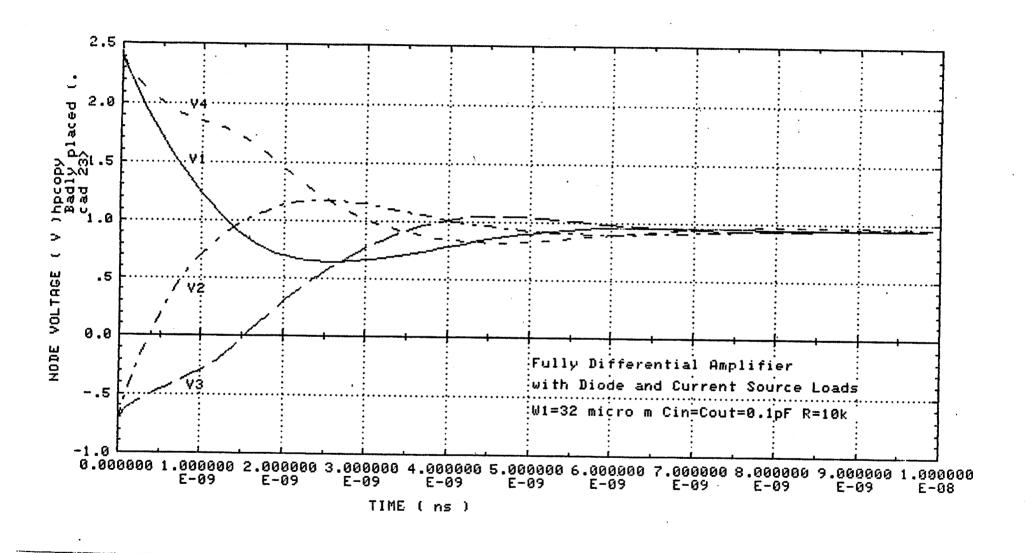

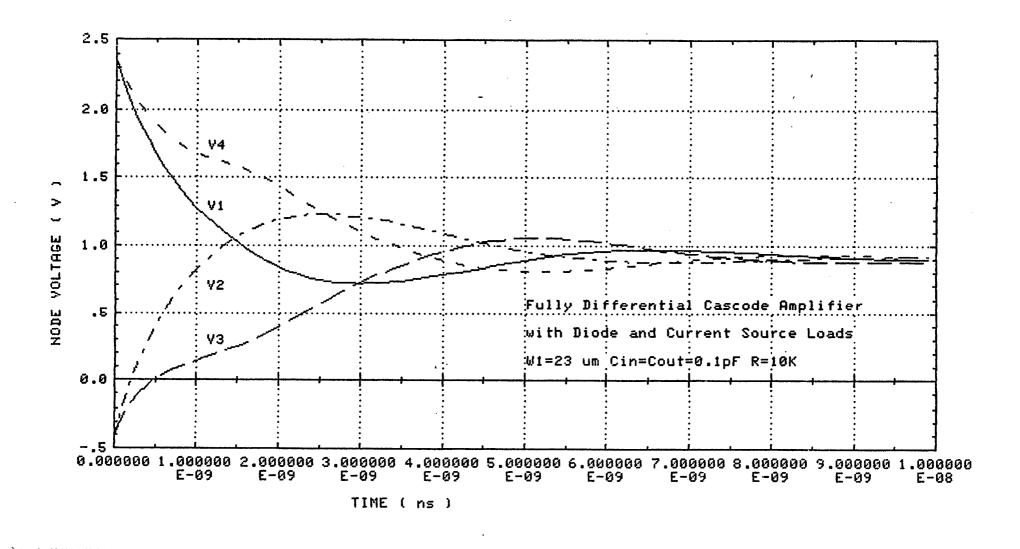

Fig. 3.5-2 (2) shows the simulation result for the same circuit and parameters, except the resistance R=10 k  $\Omega$ . The time constant during the first phase is 0.5 ns from calculation and 0.9 ns from simulation.

Here, the transient response shows some oscillation. This is caused by the second pole introduced by the RC circuit in the closed loop. From the criteria for preventing oscillation (Appendix F Eq. (F-12)), the gain-band width of the amplifier A  $\omega_c$  must satisfy the following relation:

$$A \omega_{\rm c} \leqslant \frac{1}{4RC_{in}}$$

Here, the gain-band width is 2200 Mrad/sec and  $\frac{1}{4RC_{in}}$  is 250 Mrad/sec. To avoid any oscillation, R must be less than 1.14 k  $\Omega$ . However, the size for this switch is about W/L =  $25\mu m/2\mu m$ . This value is so large that a large amount of the feed-through charge will be induced into the amplifier, causing saturation. Even with a fully-differential configuration, this problem is fatal.

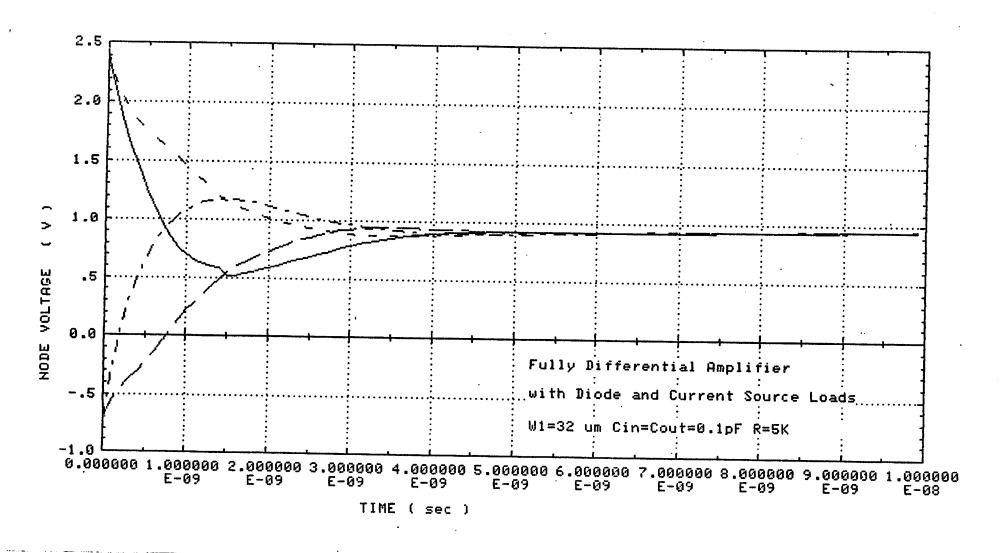

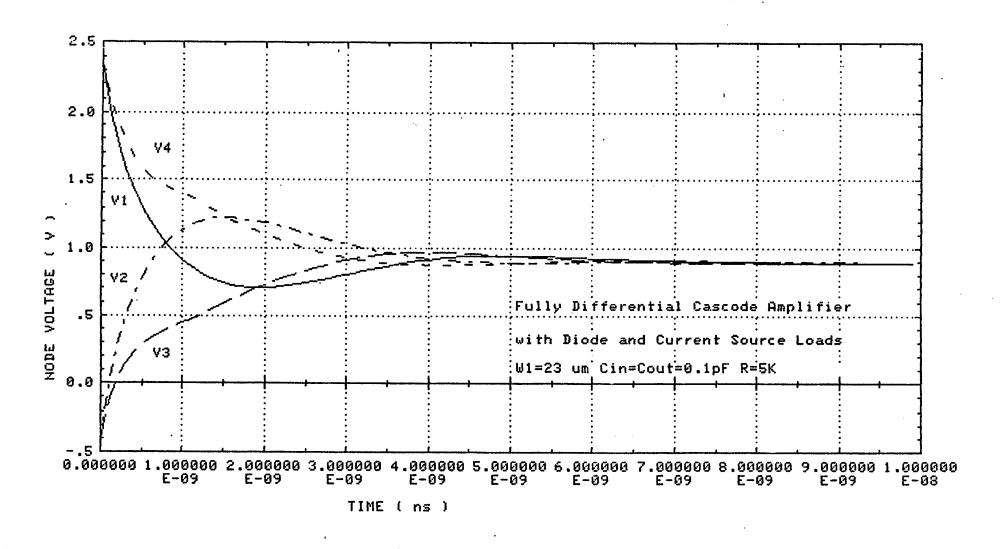

Fig. 3.5-2 (3) is the transient response of the reset for  $R=5~k~\Omega$  It takes about 10 ns to settle to its final value, but the transistor size of W/L= 13  $\mu m/2~\mu m$  is acceptable.

Fig. 3.5-3 (1) to (3) are the transient simulations for the cascode amplifier. (Appendix E. Sec 3.6) The basic characteristics are the same to the previous simulations, except

the tendency of oscillation. The reason for that is the existence of the non-dominant pole in the cascode amplifier. In order to achieve a high speed reset, attention must be paid to this pole.

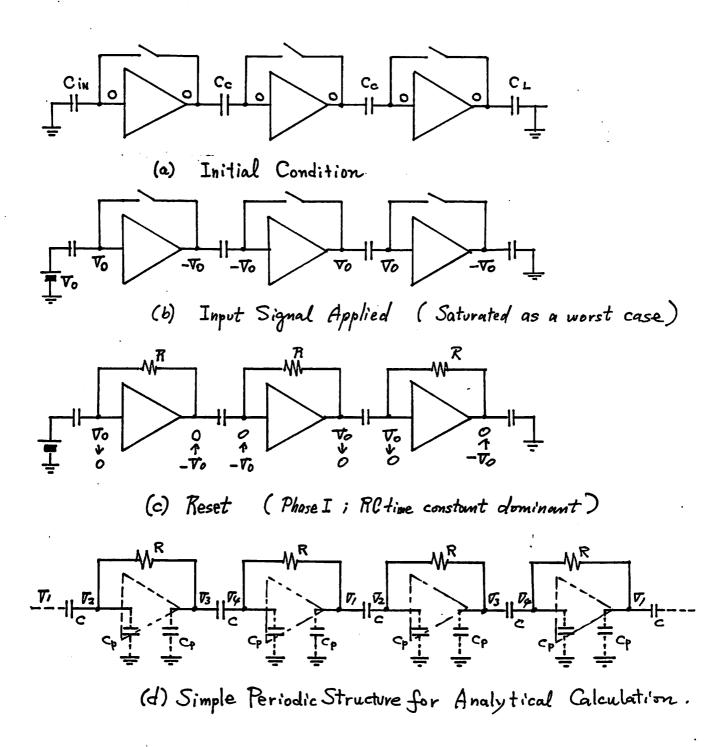

Next, the reset speed of a multi-stage comparator will be discussed. Fig. 3.5-4 shows the basic circuit to be considered. To make the analysis easier, the initial condition of  $V_{os}$  =0 V has been assumed. (Fig.3.5-4(A)) This means that all nodes are set to 0 V after reset.

As a worst case, a large input voltage  $V_0$  is supplied, and all of the amplifiers are saturated. The outputs are set either to  $V_0$  or  $-V_0$ . (Fig.3.5-4(B))

Next, the loop-closing switches are turned on to reset the comparator. (Fig. 3.5-4(C)) All node voltages move towards their initial value of 0 V. To make the calculation easier, a simple periodic structure, or a regular structure has been assumed. (Fig. 3.5-4(D)) Here, the number of stages are infinitely expanded in both sides, and consequently the node voltages can be repeated periodically.

Fig. 3.5-6 shows the solution for this regular structure. The time constant calculated for the first phase is  $C_p R/2$ , where  $C_p/2$  is the series capacitance of the two  $C_p$  connected in the input and output of the amplifier. There is no effect of the coupling capacitance C. This result can be understood intuitively, if we notice that there is no change in the charge stored on the coupling capacitances. (Fig. 3.5-4(C) and (D))

(A) General Closed-Loop Circuit

(B) Phase I of the Reset

Fig.3.5-1 Transient Response of the Reset Operation

Fig.3.5-2 (1) Transient Response during the Reset of a Fully Differential Amplifier (1)

2

Fig.3.5-2 (2) Transient Response during the Reset of a Fully Differential Amplifier (2)

Fig.3.5-2 (3) Transient Response during the Reset of a Fully Differential Amplifier (3)

Fig.3.5-3 (1) Transient Response during the Reset

of a Fully Differential Cascode Amplifier (1)

Fig.3.5-3 (2) Transient Response during the Reset of a Fully Differential Cascode Amplifier (2)

Fig.3.5-3 (3) Transient Response during the Reset

of a Fully Differential Cascode Amplifier (3)

Fig.3.5-4 Reset of a Multi-Stage Comparator

Regular Structure

$$V_1(o) = V_o$$

$$V_3(0) = -V_0$$

$$V_4(0) = -V_0$$

# \* Equation to be solved

$$\begin{pmatrix}

s(C+C_p)R+1 & -sCR & O & -1 \\

-sCR & s(C+C_p)R+1 & -1 & O \\

O & -1 & s(C+C_p)R+1 & -sCR \\

-1 & O & -sCR & s(C+C_p)R+1

\end{pmatrix}

\begin{vmatrix}

V_1 \\

V_2 \\

V_3 \\

V_4

\end{vmatrix} = C_pRV_0 \begin{vmatrix}

1 \\

-1 \\

-1

\end{vmatrix}$$

\* Solution

$$V_1(s) = V_0/(s + 2/C_PR)$$

$U_1(t) = V_0 e^{-\frac{t}{C_PR/2}}$

Fig.3.5-6 Solution for the Regular Structure

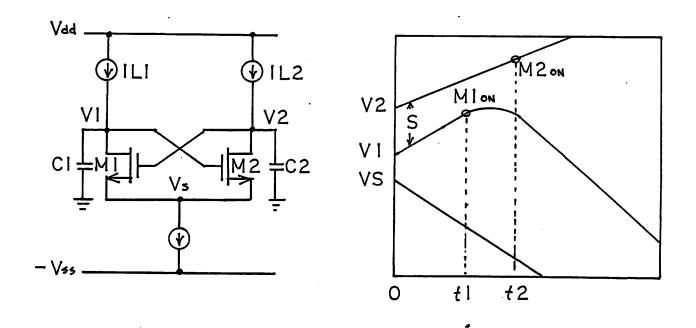

# 3.6 Characteristics of Fully-Differential Amplifiers

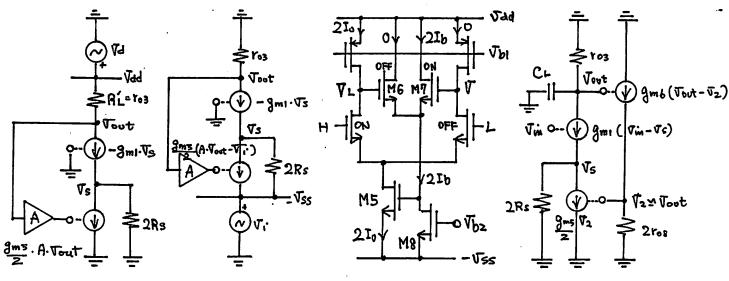

#### 3.6-1 Reset Sequence

The optimum amplifier configuration depends on the operation sequence of the comparator. There are basically two kinds of sequence to be considered, based on the number of reset operations used in one A/D conversion cycle.

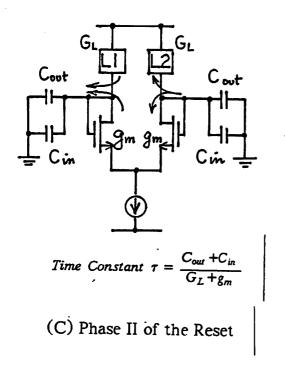

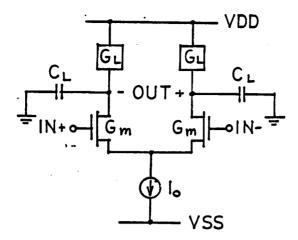

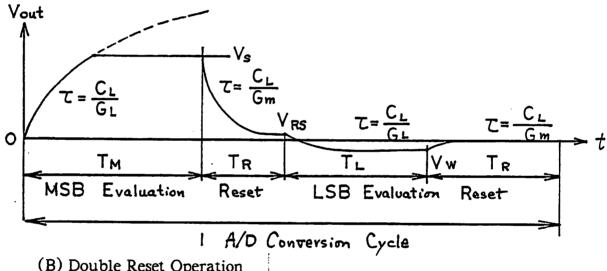

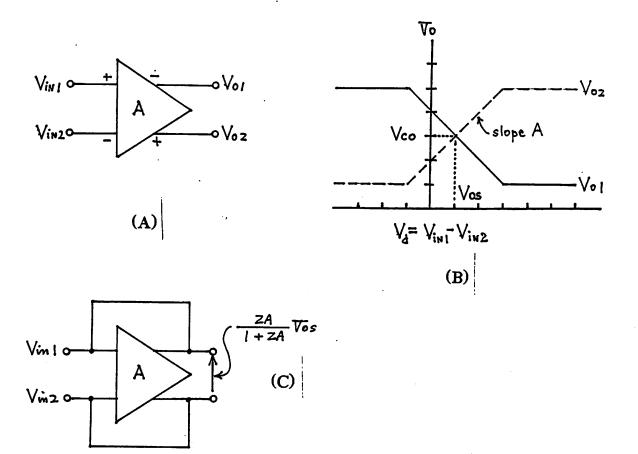

Fig. 3.6-1 shows those two sequences. (A) is the basic circuit of the fully-differential amplifier to be considered here. Here,  $G_L$ ,  $G_m$  and  $C_L$  are the conductance of the load, the transconductance of the driver and the load capacitance respectively.

Fig. 3.6-1 (B) shows the transient of the output voltage in the double reset operation. Here, the amplifiers are reset after each MSB and LSB evaluation. The time constant of the transient during the evaluation is  $C_L/G_L$ . From the calculation in Sec. 3.5, it is clear that the time constant during the reset interval is  $C_L/(G_L+G_m)\approx C_L/G_m$ . Here, small RC constant for the closed loop ( small resistance of the loop-closing switch ) has also been assumed.

Let's consider the worst case (the most time consuming case), that is the 1 LSB evaluation in the opposite direction after a saturation of the amplifier during the MSB evaluation.

The residual output voltage  $V_{RS}$  after the first reset is:

$$V_{RS} = V_S e^{-\frac{T_R}{C_L/G_m}} (3.6-1)$$

Here.  $V_S$  is the output voltage of the amplifier in a saturation, and  $T_R$  is the reset time. With this voltage as an initial condition, the final voltage  $V_W$  after the LSB evaluation is:

$$V_{W} = V_{RS}e^{-\frac{T_{L}}{C_{L}/G_{L}}} - AV_{LSB}(1 - e^{\frac{-T_{L}}{C_{L}/G_{L}}})$$

(3.6-2)

Here.  $T_L$ , A and  $V_{LSB}$  are the LSB evaluation time, the gain of the amplifier and the input signal of 1 LSB respectively.

To acquire the correct answer, this value should be negative. Therefore, the following restriction for the conductance of the load device can be derived.

$$G_L \geqslant \frac{C_L}{T_L} \ln(1 + \frac{V_{RS}}{AV_{LSB}})$$

As a numerical example:

$V_{LSB} = 1 \text{ mV}$

A = 10

$C_L = 0.1 \text{ pF}$

$T_L = 10 \text{ nS}$

$G_m = 200 \ \mu A / V$

$T_M = 10 \text{ ns}$

$V_S = 1 \text{ V}$

$T_R = 5 \text{ ns}$

$V_{RS}$  can be calculated to be 45  $\mu V$ , and  $G_L \geqslant$ 45 nA/V, which is a small value. From this estimation, it is clear that not only the MOS load connected in a diode configuration but also a current source load with low  $G_L$  is possible to use in this double reset operation. This means that an amplifier with high gain of  $G_m/G_L$  is able to be used. However, the speed of a multi-stage amplifier depends basically on the gain-band width GBW of the amplifier. (Sec 3.4) so that there is no advantage to use a high gain amplifier with current source loads, which require a common-mode feedback to maintain the CMRR and to stabilize the DC output level.

The drawback of this double reset operation is the complexity of the control. As is shown in Sec. 3.3, the loop-closing switches of the amplifiers must be opened in a certain delayed sequence to sample the feed-through charge. In order to satisfy this sequence, a total time of 8 ns will be required for a reset time of 5 ns. This is a large time consuming portion for a high speed ADC.

Another possible reset sequence is the single reset operation. This is shown in Fig. 3.6-1 (C) In this operation, the reset is performed only after the LSB evaluation. Here,

much attention should be paid to the relatively large time constant of  $C_L/G_L$  during the LSB evaluation.

Let's assume the worst case, that is the 1 LSB evaluation in the opposite direction after the saturation of the amplifier during the MSB evaluation. The final output voltage after the LSB evaluation period  $T_L$  is:

$$V_{w} = V_{S} e^{\frac{-T_{L}}{C_{L} / G_{L}}} - A V_{LSB} (1 - e^{-\frac{T_{L}}{C_{L} / G_{L}}})$$

(3.6-3)

Again, to acquire the correct answer, this voltage should be negative. The conductance of the load should satisfy the following condition:

$$G_L \ge \frac{C_L}{T_L} \ln(1 + \frac{V_S}{AV_{LSB}}) \tag{3.6-4}$$

Using the same numbers as the previous numerical example, we get the result of  $G_L \ge 46\mu A/V$ . This large value cannot be realized by a current source load. Beside this condition, a certain gain  $G_m/G_L$  is required for the amplification of small signals. These conditions are satisfied with the multi-stage configuration, and in some cases, a high speed low gain amplifier at the head of that multi-stage amplifier. Also, a MOS diode clamp may be used in the head amplifier to reduce the  $V_S$ .

The considerations so far was dealing with a single stage. This concept can also be expanded for the multi-stage amplifier.

In this report, fully-differential amplifiers with MOS loads connected in a diode configuration will be discussed. These amplifiers have a high band-width of  $G_L$  /  $C_L$  and low gain of  $G_m$  /  $G_L$ .

The discussions and SPICE simulations in this report are based on the single reset operation. The upcoming report by J. Doernberg [4] will discuss also the double reset operation.

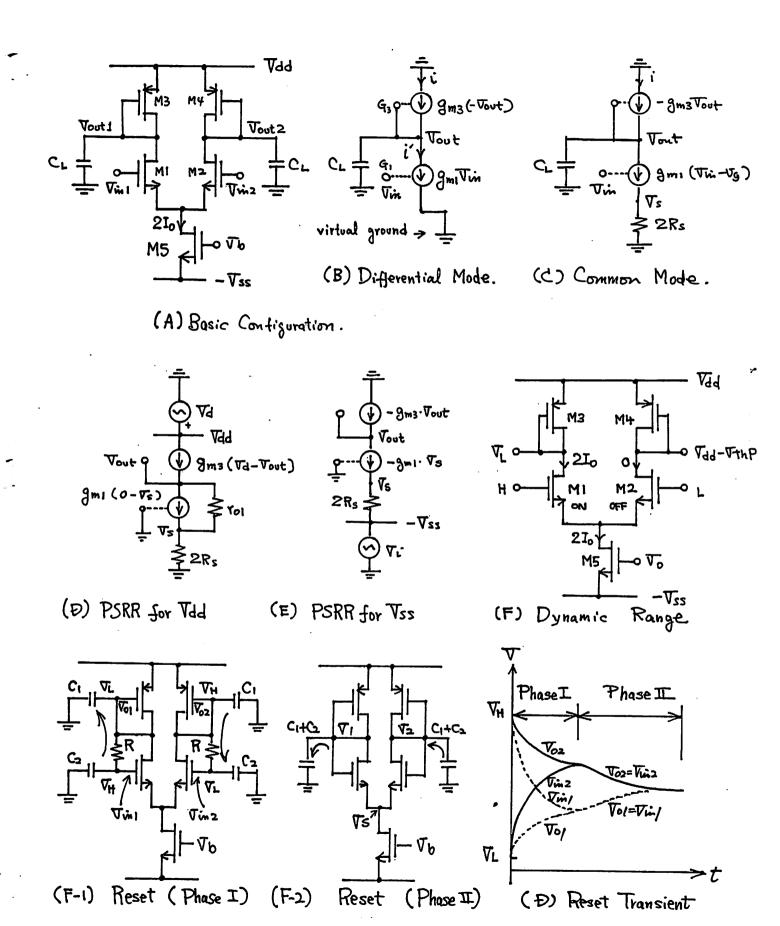

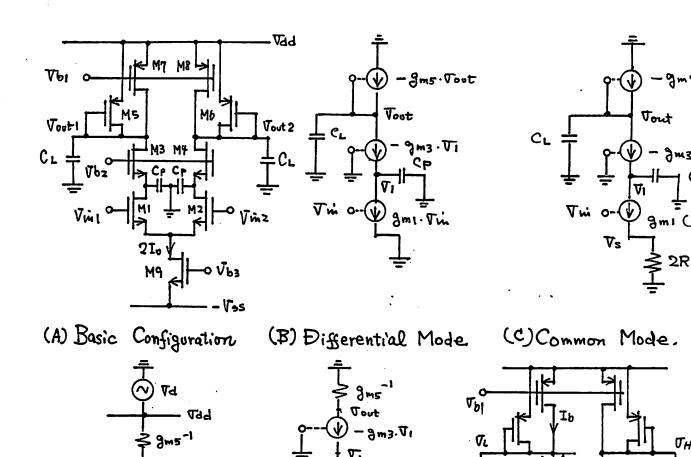

#### 3.6-2 Characteristics of Fully-Differential Amplifiers.

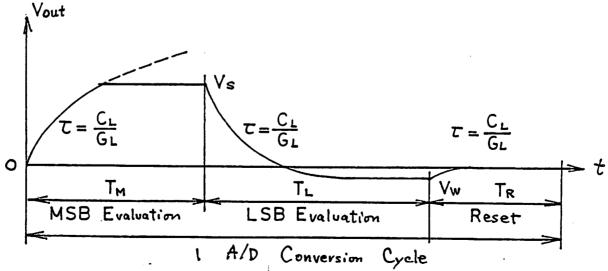

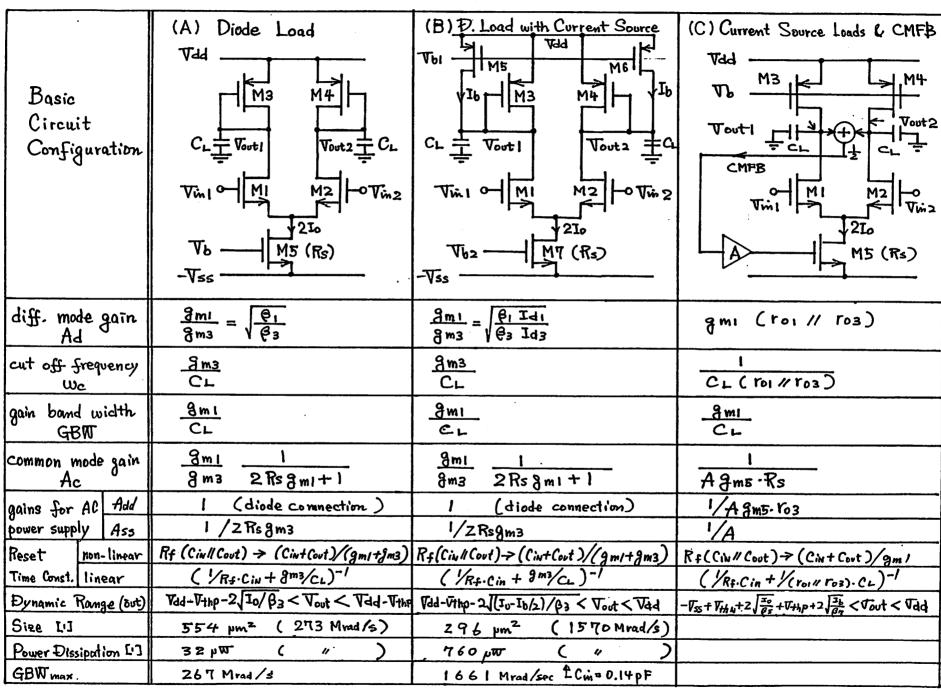

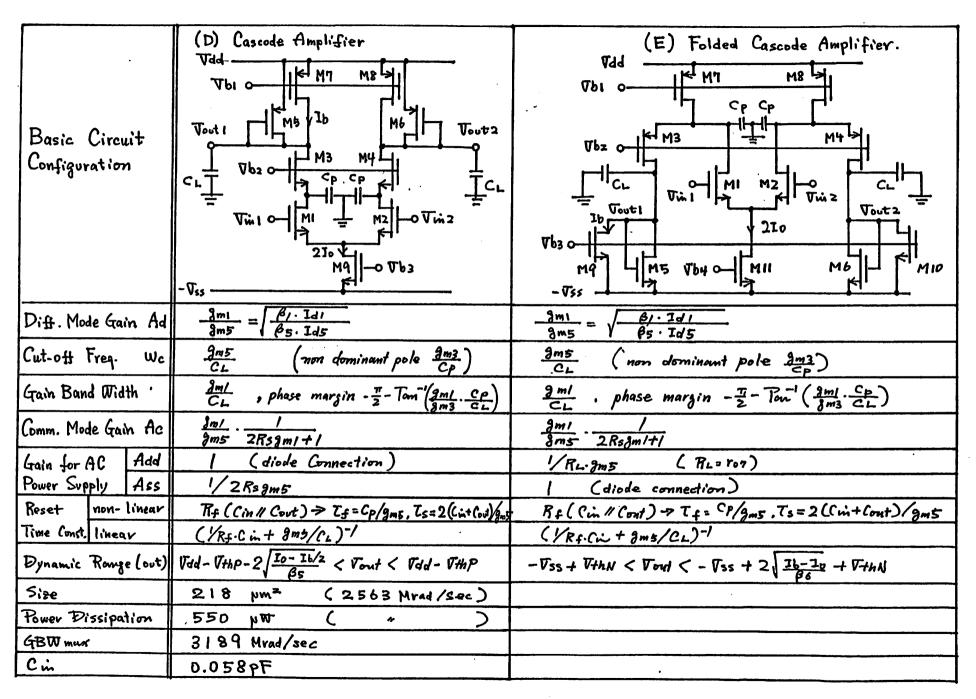

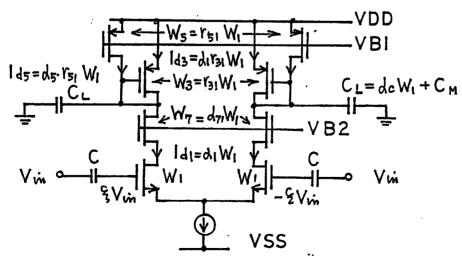

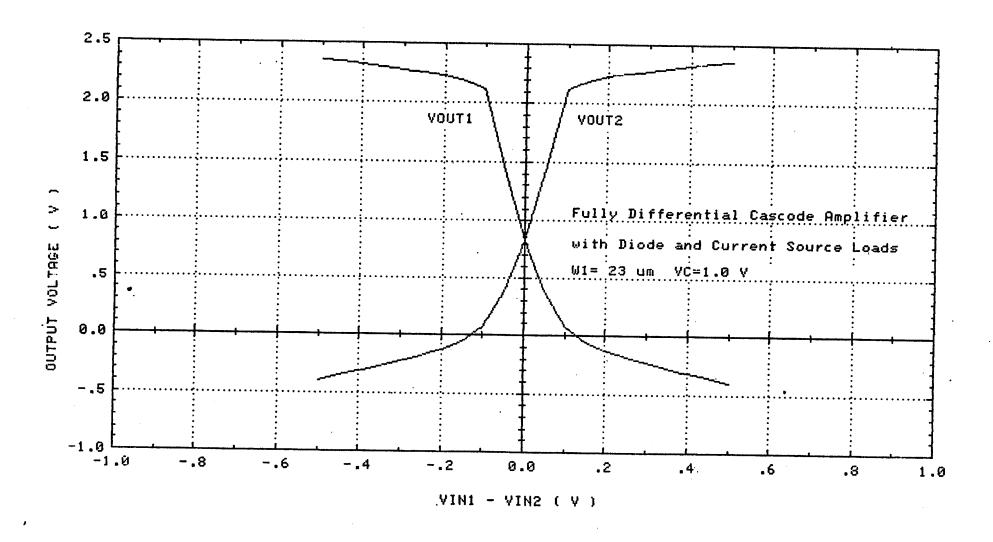

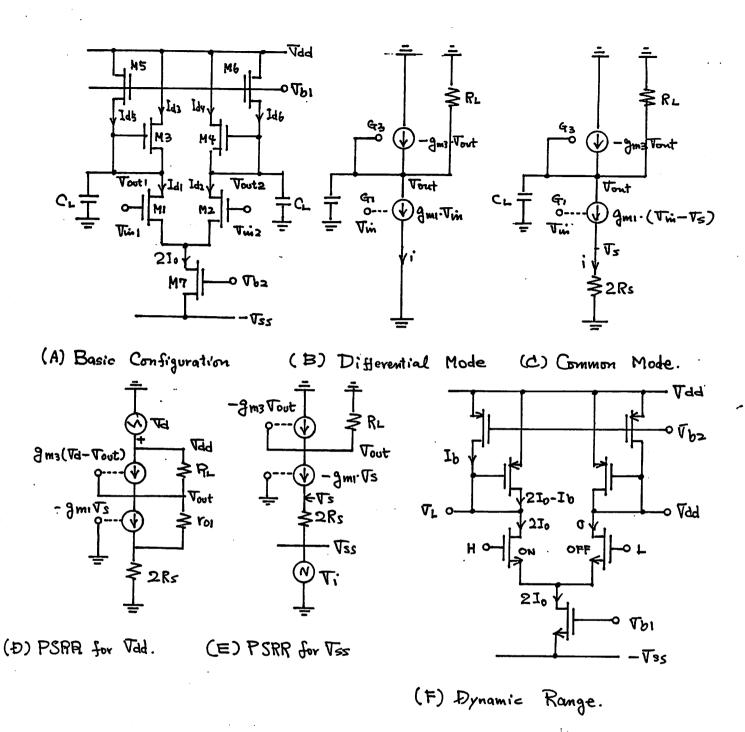

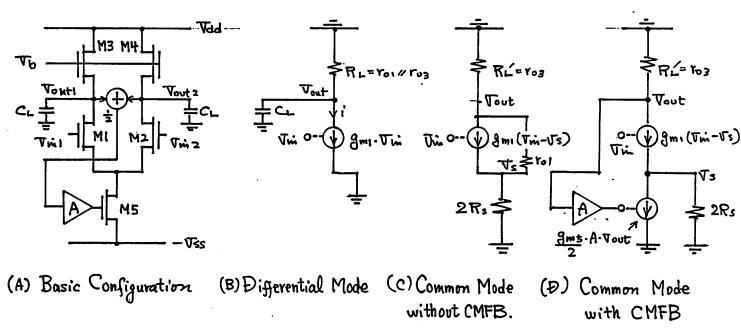

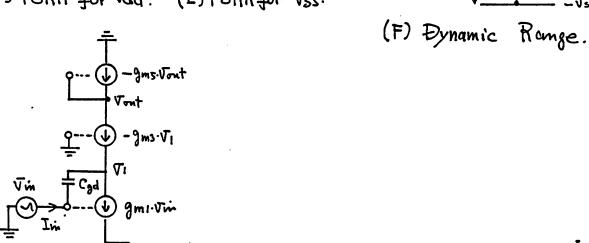

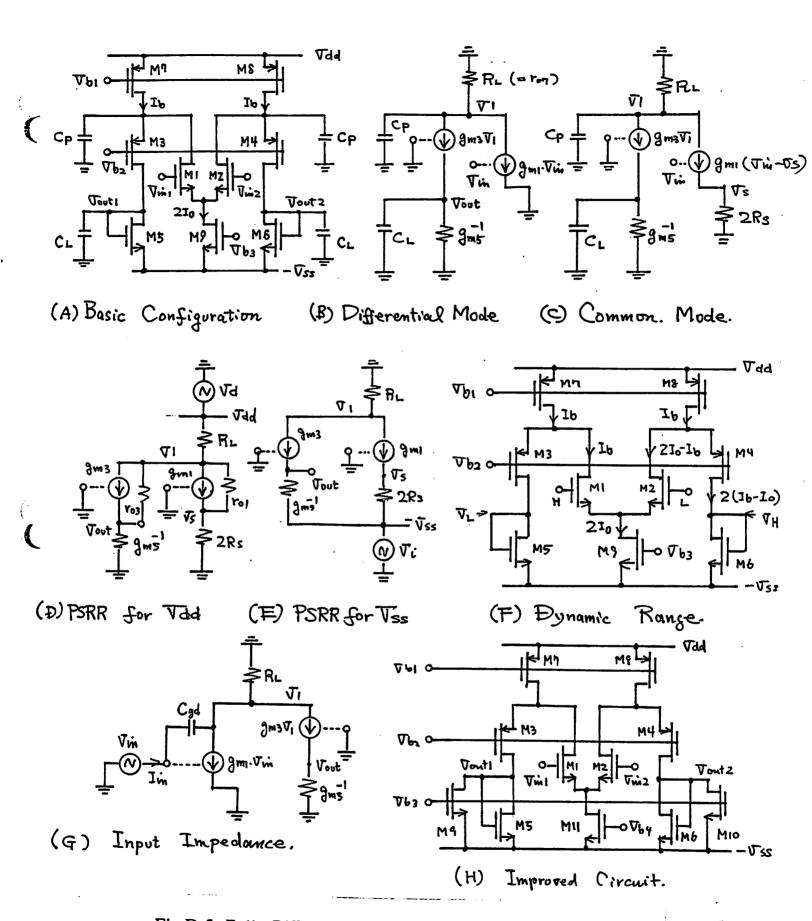

Fig. 3.6-2 shows various differential amplifiers examined here. Every circuit has a diode connected MOS loads, except (C) which has a current source load and a common-mode feedback (CMFB) circuit. The details of the calculations are explained in appendix D. Here, only the essential characteristics of each amplifier will be reviewed.

Fig.(A) is the simplest circuit using MOS loads M3 and M4 connected in a diode configuration. ( diode load ) The drawback of this circuit is that the gain is determined only by the square of the dimension ratio of the driver to the load device. For a 3 stage amplifier used in a 10 bit ADC, at least the gain of 10 is required for each stage. To realize this, the W1/W3 ratio of 100, or the (W1L3)/(W3L1) ratio of 100 will be required. This makes the device size large.

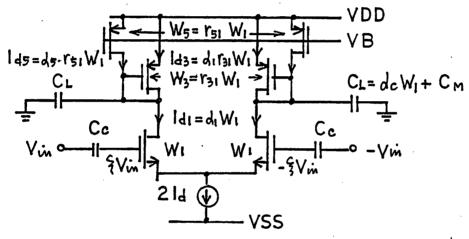

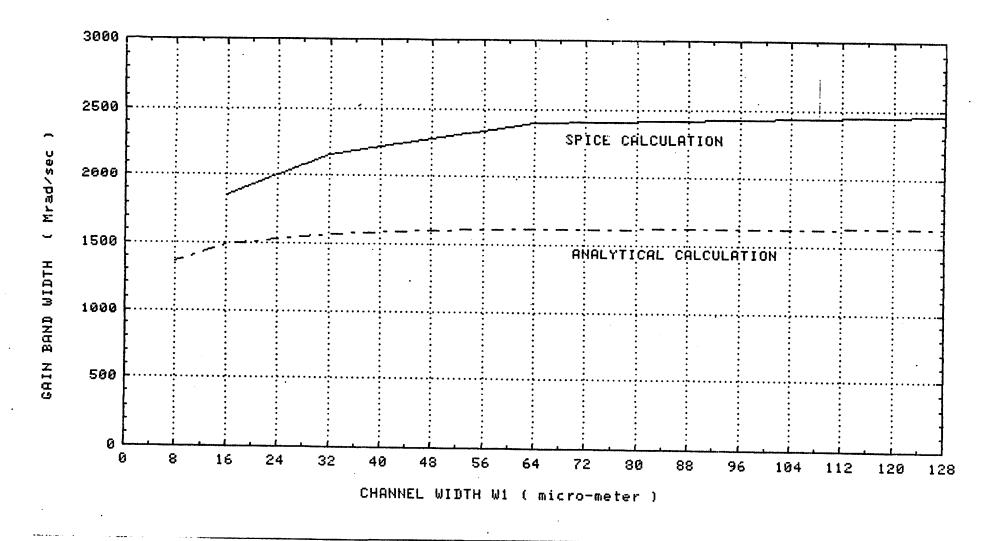

Fig.(B) is the improved circuit proposed by J. Doernberg. Two current sources M5 and M6 are added to the previous circuit. These current sources supply extra current to the driver transistors M1 and M2. The desired gain can be attained by the ratio W1/W3 and the current ratio Id1/Id3. This circuit shows enough GBW of 1570 Mrad/sec and reasonable size of  $296 \ \mu m^2$ , which is around half of the previous circuit. A detail design of this amplifier is reported in appendix E.

Fig. (C) is the only circuit examined here that uses current source loads. In order to get a high CMRR ratio. a CMFB circuit is used. Here the CMFB circuit is expressed by a general form, which consists of an adder to extract the common mode voltage from the output and an amplifier. Usually a common-source differential amplifier is used here as a source follower. The gain of this CMFB circuit is close to unity. There are many other way to implement this type of amplifiers, but they are not discussed here.

This circuit shows a high gain of  $g_{m1}(r_{o1}//r_{o3})$  , but its cut off frequency  $1/C_L(r_{o1}//r_{o2})$  is relatively low. It is difficult to use this circuit in the single reset operation.

Fig.(D) is an improved version of (B). The problem in the previous circuit was the relatively large Miller capacitance. Coupling capacitance  $C_c$  is used between each amplifier

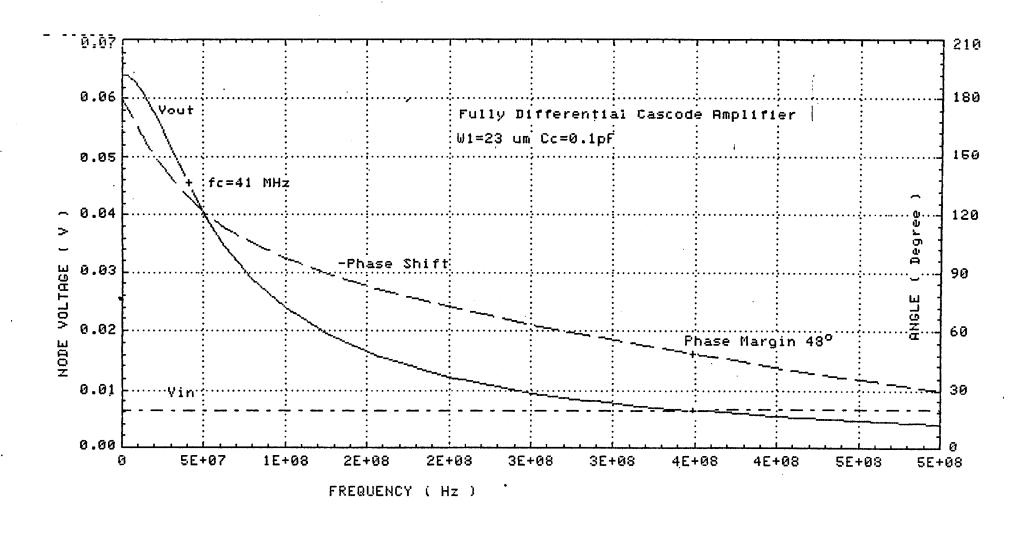

stage, and the output voltage from the previous stage is attenuated by the ratio of  $C_c/(C_c+C_{in})$ , where  $C_{in}$  is the input capacitance of the amplifier containing the Miller capacitance. With that Miller capacitance, the input capacitance is almost doubled, resulting in a large attenuation. Moreover, this large capacitance results in a large load capacitance for its previous stage, degrading its GBW. In the circuit of Fig.(D), cascode transistors M3 and M4 are added to suppress the voltage change in the drain of M1 and M2, and consequently to reduce the Miller capacitance. This suppression depends on the dimension ratio of the cascode transistor and the driver transistor. By this configuration, a very high GBW of 2,500 Mrad/sec has been achieved. The optimum design of this circuit will discussed in Sec. 3.6-3.

Here, a non-dominant pole is induced by the parasitic capacitance  $C_p$  at the node between the cascode transistor and the driver transistor. This degrades the stabilization during the reset operation. Details are discussed in appendix D.

Fig.(E) shows the folded version of the previous circuit. Using this configuration, the output swing can be increased. However, even with the previous circuit, an output swing of 3.0 V can be achieved for a 5 V power supply, which is sufficient for our application.

Fig.(F) shows another method to solve the problem of large load capacitance due to the Miller effect of the next stage. Source followers M7 and M8 are added, so that the load capacitance can be reduced to a relatively small value of  $C_p$ . The drawback of this problem is the large power consumption. To maintain the unity gain of the source follower over the GBW of the differential circuit, the transconductance of M7 and M8 must be the same to that of M1 and M2. This results in doubling the power consumption if the same transistor dimension is used.

This circuit has been used in the simulation of the full comparator. (Sec. 3.7) The power consumption for a comparator with three amplifiers of this type and a latch is 20.2 mW. resulting in a large power consumption of 646.4 mW for the 10 bit ADC.

Fig.(G) shows a class AB amplifier. This circuit is very attractive for its high drivability in the class B operation. The drawback of this circuit is the large input capacitance of around 0.4 pF. In this amplifier, the input signal must drive two complementary transistors, and this doubles the input capacitance.

#### 3.6-3 Optimum Design of the Fully-Differential Amplifier

#### (1) Amplifier with Diode Loads

Three circuits are chosen from the previous section and studied in detail. The first one is the fully-differential amplifier with diode loads. As shown in Fig. 3.6-3 (A), all the dimension of the transistors and the current flowing the current sources are scaled with respect to the width W1 of the driver transistor. Here, the conditions for the optimum design is the output voltage  $V_0$  in the reset state, the DC gain G and the attenuation rate  $\xi$  due to the coupling capacitance between amplifiers. Details of this calculation are described in appendix E. As the final result, the gain bandwidth GBW can be expressed with respect to W1 as:

$$GBW = \frac{\alpha_{\rm g} W \, 1}{\alpha_{\rm c} W \, 1 + C_M} \tag{3.6-5}$$

Here,  $\alpha_g$  and  $\alpha_c$  are the coefficients that show the linear dependence of the transconductance and load capacitance on W1 respectively.

The gain bandwidth increases asymptotically to a maximum value of  $GBW_{max} = \alpha_g / \alpha_c$ .

Under the conditions of G=20.  $\xi$  = 0.5 and  $V_0$  = 1 V, the maximum value of  $GBW_{max}$  = 267 Mrad/sec can be achieved. This is a relatively small value. To attain 90% of this value, a channel width W1 of more than 21  $\mu m$  is required.

#### (2) Amplifier with Diode and Current Source Loads

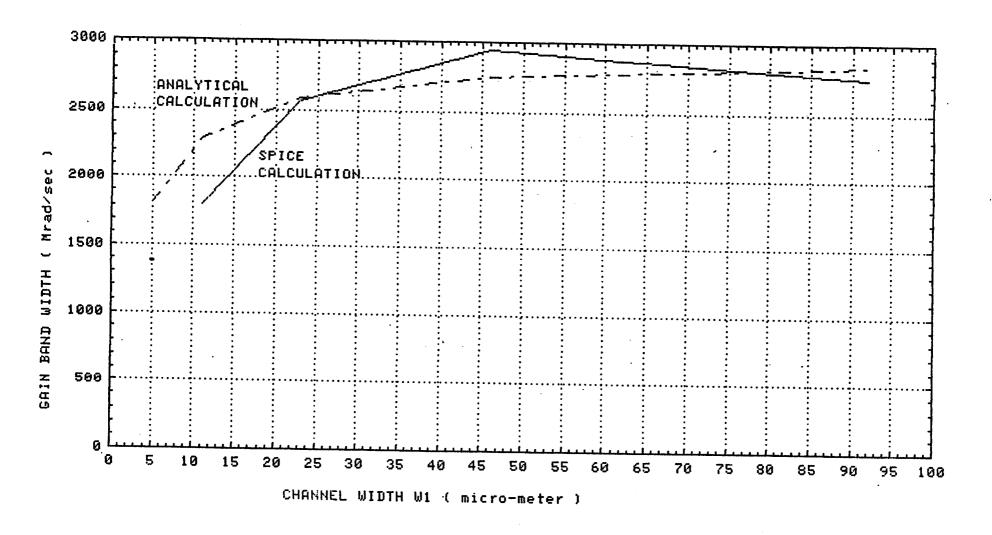

The circuit is shown in Fig. 3.6-3 (B). Under the same condition described before, the GBW can be expressed in the same form as in the Eq. (3.6-5). The dependence of the GBW on W1 has been calculated and simulated. This result is shown in Fig. 3.6-4. Here, the GBW increases asymtotically to its maximum value in both cases. However, the maximum value differs each other, the maximum value from the analytical calculation is 1660 Mrad/sec, while that value from simulation is 2500 Mrad/sec. In the analytical calculation, a channel width of more than  $16 \ \mu m$  is required to achieve a 90% GBW of the maximum GBW.

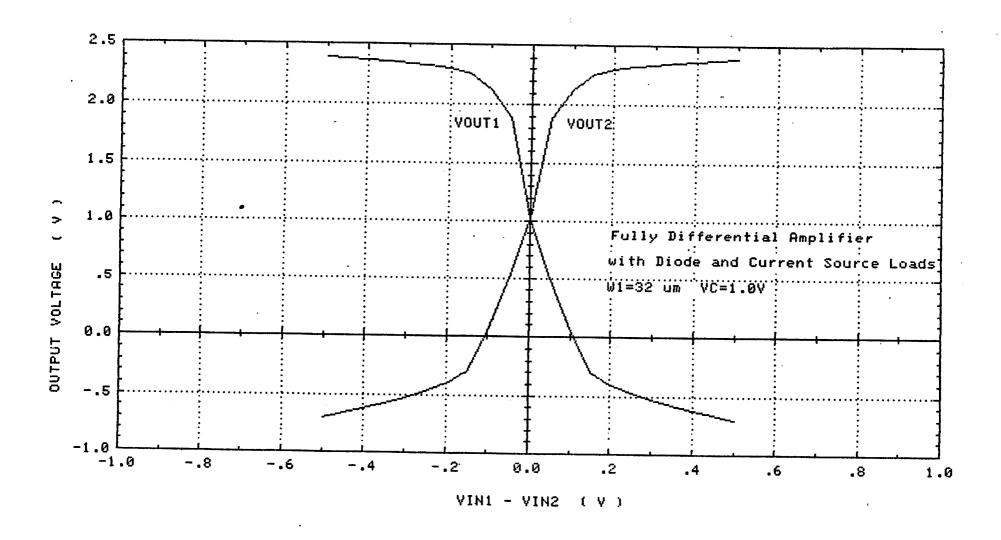

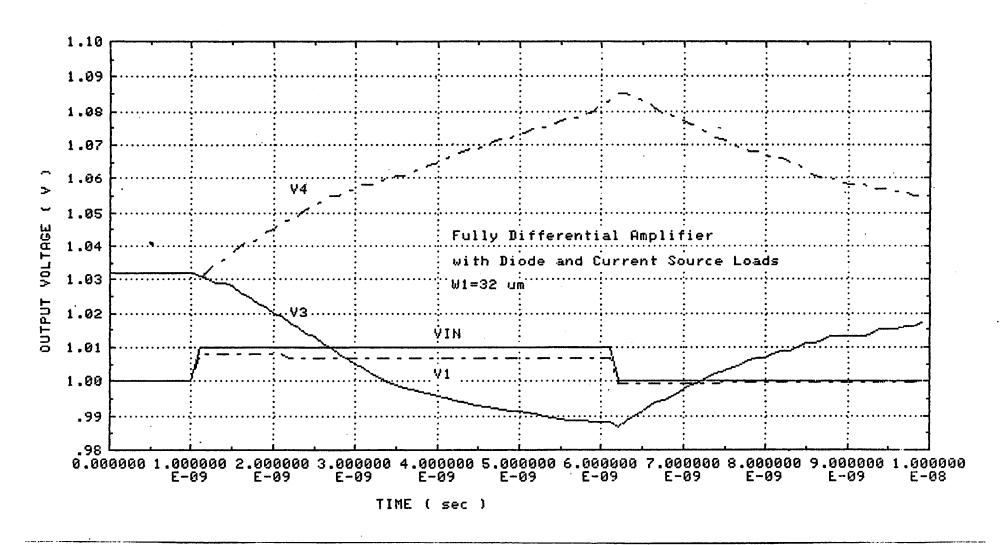

Here, some characteristics for an amplifier of W1 = 32  $\mu m$  has been simulated. Fig. 3.6-5 shows the DC transfer curve. The output swing is around 3.0 V which is a value large enough for our application. The cross point of the two outputs, which is the point set after the reset, is 1.0 V which is just the expected value for the calculation.

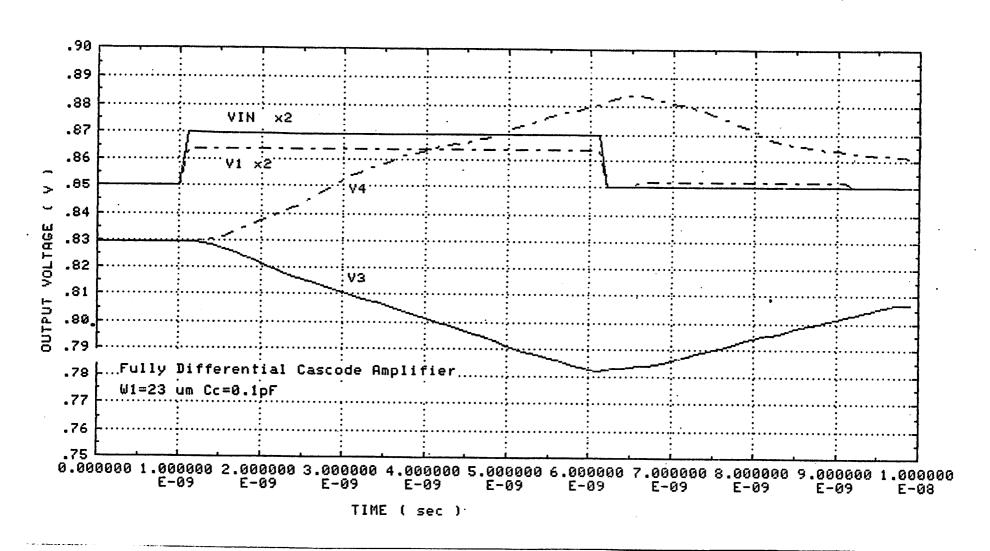

Fig. 3.6-6 is the transient response for the input voltage of 10 mV. Due to the Miller effect in the input capacitance, the input signal is attenuated to about 70% of its value. ( V1 ) The response for this short time period is almost linear with the slew-rate of 9 mV/sec, which is well predicted by Eq.( 3.4-2). If the cut off frequency and time product  $\omega_c t$  is much smaller than unity, the equation above can be approximated as:

$$V_{out}(t) = GBW V_{in} t$$

From this equation the slew-rate can be approximated as 1600 Mrad/sec x 7 mV  $\approx$  11 mV/sec.

#### (3) Cascode Amplifier with Diode and Current Source Loads

This circuit is shown in Fig. 3.6-3 (C). Under the same condition described before, the GBW can be expressed in the same form as in the Eq. (3.6-5). The dependence of the GBW on W1 has been calculated and simulated. This result is shown in Fig. 3.6-7. Here, the GBW increases asymtotically to its maximum value for the analytical calculation. However, GBW has a maximum peak for the SPICE simulation. The maximum value from

(A) General Circuit Configuration of a Differential Amplifier

(B) Double Reset Operation

(C) Single Reset Operation

Fig.3.6-1 Reset Operation

<sup>[1]</sup> Size and Power for an Optimum Design (GBWZ 0.9GBWmax, Geffective=10. Wmin=2 pm. Vout level considered at Vdm=0)

Fig.3.6-2 Basic Characteristics of Fully Differential Amplifiers (1)

Fig.3.6-2 Basic Characteristics of Fully Differential Amplifiers (2)

Fig.3.6-2 Basic Characteristics of Fully Differential Amplifiers (3)

(A) Amplifier with MOS loads in Diode Connection

(B) Amplifier with Diode and Current Source Loads

(C) Cascode Amplifier with Diode and Current Source Loads

Fig.3.6-3 Optimum Design of the Differential Amplifiers

Fig.3.6-4 Gain Bandwidth Dependence on W1

Fig.3.6-5 DC Transfer Characteristics

Fig.3.6-6 Transient Response of the Amplifier

with Diode and Current Source Loads ( Vin = 10 mV )

Fig.3.6-7 Gain Bandwidth Dependence on W1 for a Cascode

Differential Amplifier with Diode and Current Source Loads

Fig.3.6-8 DC Transfer Characteristics of the Cascode

Differential Amplifier with Diode and Current Source Loads

Fig.3.6-9 Transient Response of a Single-Stage Cascode Amplifier

with Diode and Current Source Loads ( Vin = 10 mV )

Fig.3.6-10 Amplitude and Phase Characteristics of a Cascode

Differential Amplifier.

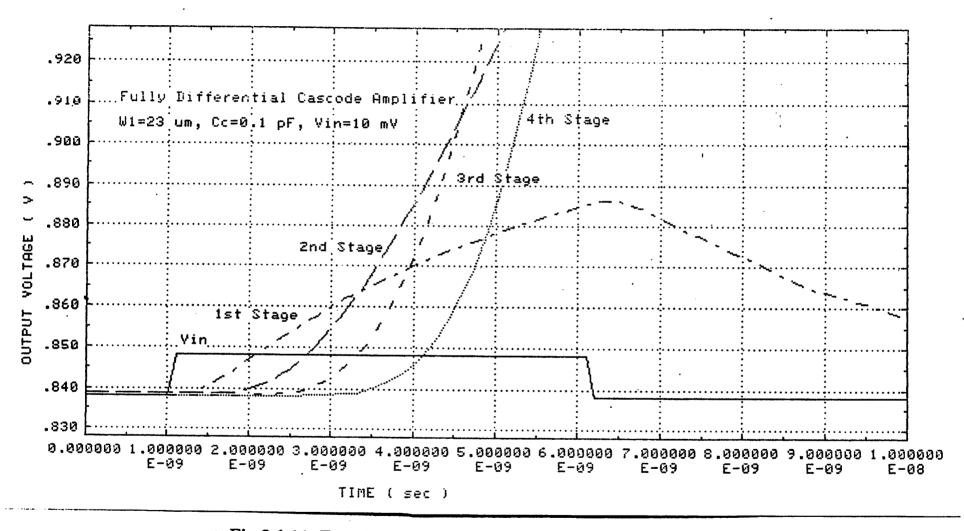

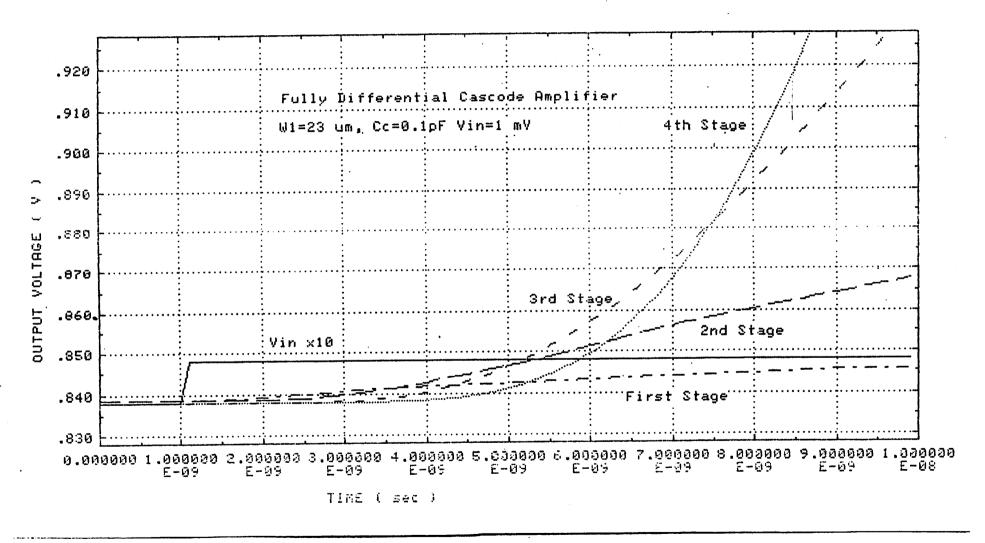

Fig.3.6-11 Transient Response of a Multi-Stage Cascode Amplifier

with Diode and Current Source Loads ( Vin = 10 mV )

Fig.3.6-12 Transient Response of a Multi-Stage Cascode Amplifier

with Diode and Current Source Loads ( Vin = 1 mV )

ı

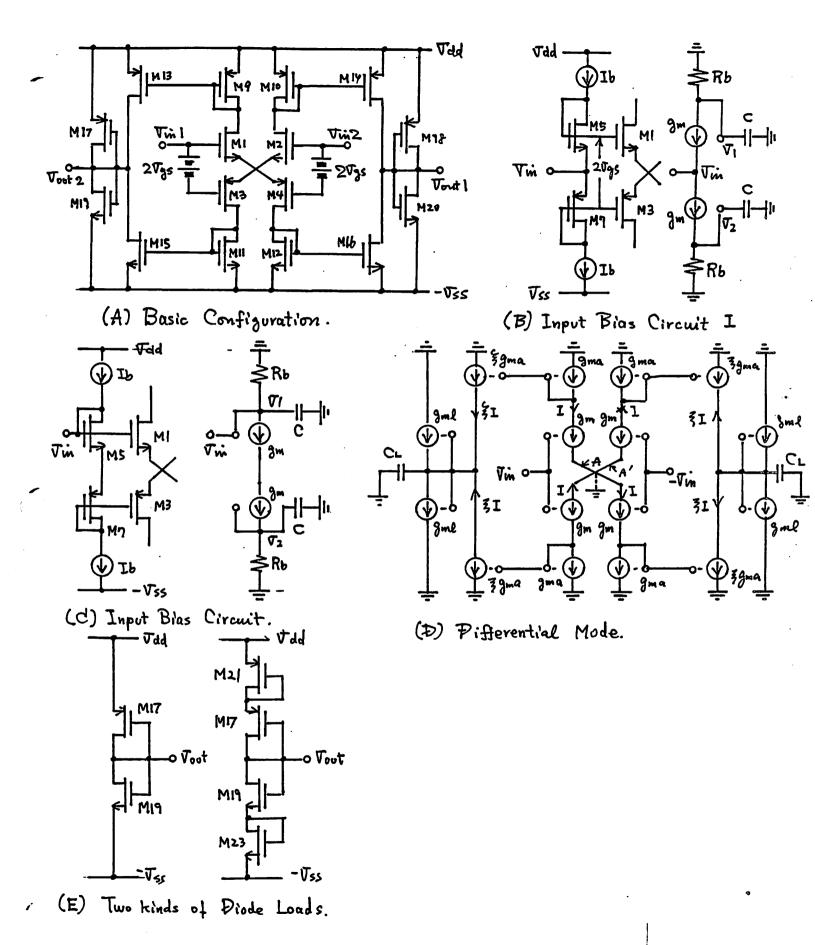

### 3.7 Simulation of the Comparator

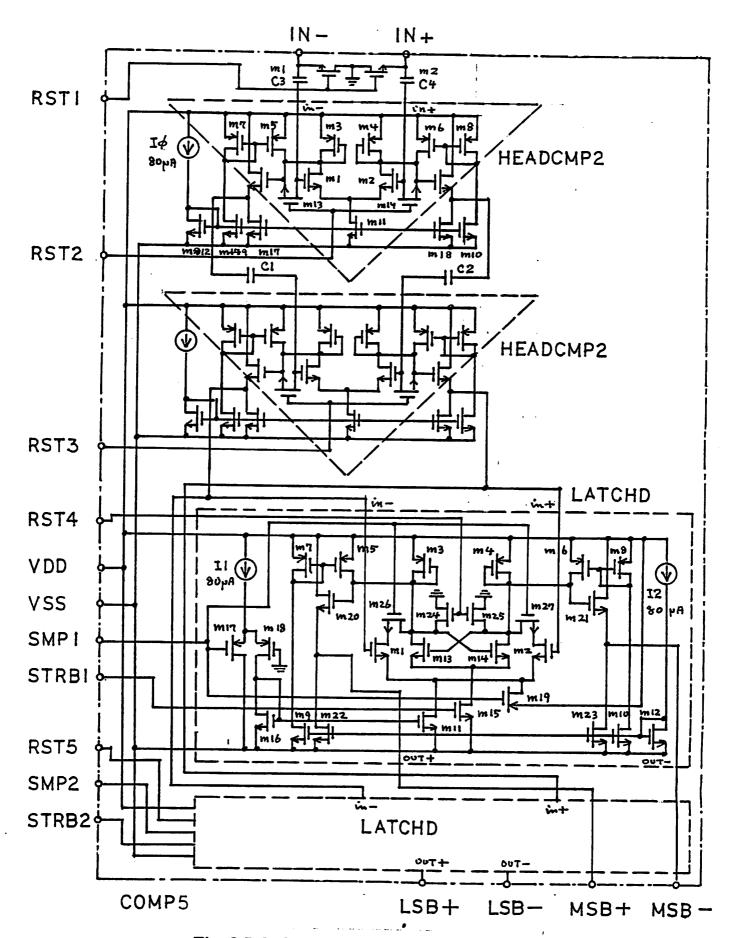

A SPICE simulation of the full size comparator has been performed in the early stage of this project, for the purpose to check the feasibility of the architecture. The optimization of the amplifier used in the comparator has finished after this simulation. The amplifier used in this simulation is not the cascode type, but the diode and current source load type with a source follower buffer. Consequently, the speed is not as fast as the final version which will be reported in the upcoming paper. [1] However, even with this circuit the 10 bit, 15 MHz ADC can be realized, and the result of this simulation has encouraged us to proceed to the next step.

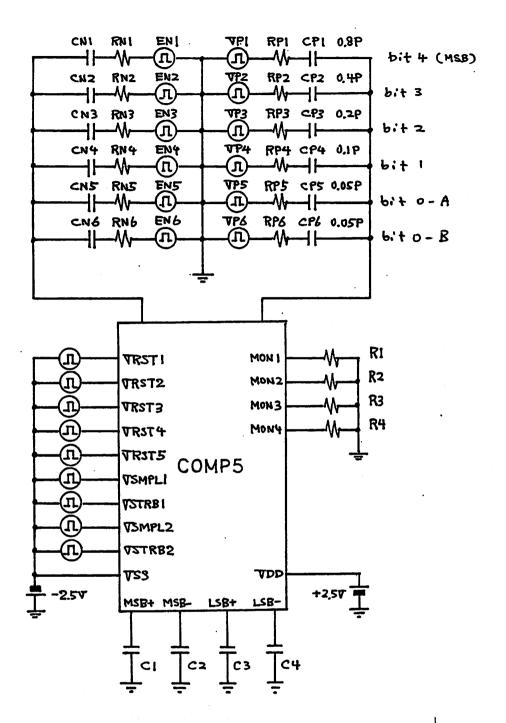

Fig. 3.7-1 shows the full circuit used in the simulation. The binary weighted capacitor array has been modeled as a pulse generator, a resistor and a capacitor connected in series. The pulse generator simulates the input signal or the reference voltage appearing in the bottom plate of the capacitors. The resistor is the on resistance of the bottom plate switches and is scaled, depending on the size of the capacitors. The minimum size resistor and capacitor have the value of 8 k  $\Omega$  and 0.05 pF respectively. COMP5 is the comparator sub-circuit including the multi-stage amplifier and latch.

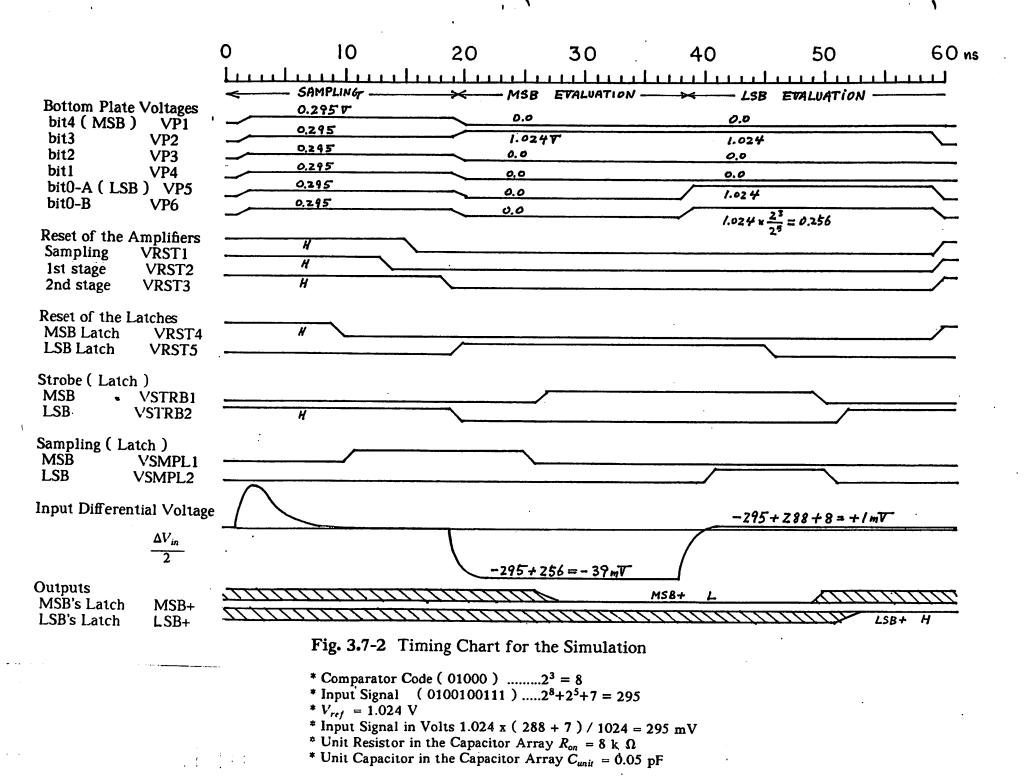

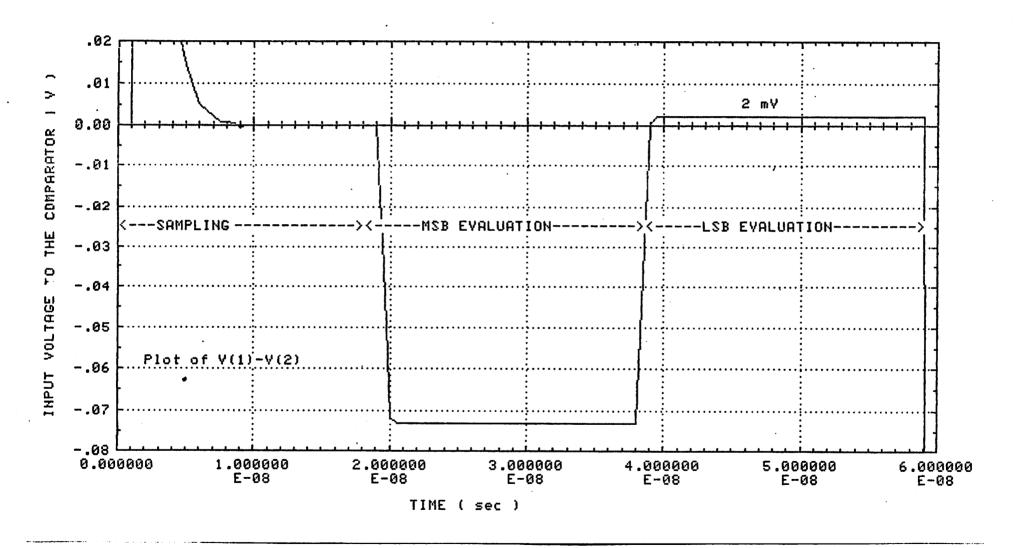

Fig.3.7-2 is the timing chart used in this simulation. The code of the comparator used here is assumed to be  $(01000)_2 = 2^3 = 8$ , and the input signal is  $(0100100111)_2 = 2^8 + 2^5 + 7 = 295$ . The reference voltage  $V_{ref}$  is 1.024 V, so that the input voltage is 295 mV.

From 0 to 20 ns. This input voltage is applied to the capacitors through the pulse generators VP1 to VP6. Then for the MSB evaluation period, the reference voltage is supplied only to the bit3 capacitor. This corresponds to the code (01000) of this comparator. The five most significant bits of the input data are (01001), and is larger than the comparator code. Then low level output L appears in the output MSB+. (From the sense that the input is larger than the reference, it might be better to set the output MSB+ to high

level H. ) A 5 bit data of (01001) is supposed to be attained from the decoder, and this code is fed back to the capacitor array, turning its bottom plate voltage as 0.0, 1.024, 0.0, 0.0, 1.024 from the MSB to the LSB capacitors. A reference voltage of 256 mV, corresponding to the code (01000) is supplied to the bit0-B capacitor. Here, the five least significant bits of the input is (00111), which is smaller than the comparator code (01000). The output of H appears at LSB+ in this case.

Fig. 3.7-3 shows the comparator subcircuit COMP5. It consists of four subcircuits. Two of them are the fully differential amplifier HEADAMP2, and the other two are the differential amplifier merged with the latch. Transistors m1 and m2 are the sampling switches for the top electrode of the capacitor arrays.

HEADCMP2 is a fully differential amplifier with diode connected loads m3 and m4, and current sources m5 and m6. The number of transistors is 12.

LATCHD is the latch subcircuit with a differential amplifier. The driver transistors m13 and m14 of the latch share the same loads m3 to m6 with the driver transistors m1 and m2 of the amplifier. By this configuration, the smooth transfer of signals from the multi-stage amplifier to the latch can be realized. Transistors m26 and m27 are used to disconnect the amplifier drivers from the latch. These switches are essential to prevent the interference from the amplifier to the latch. (The node voltages of the source of m1 and m2 are pulled high during the latch operation. However it takes time to cut off m1 and m2, and they interfere the latch operation.)

Current source 11 and the differential amplifier composed by m16 to m18 are used to switch the amplifier and adjust its current.

Here in this comparator, two latches are used. One for the MSB evaluation and the other for the LSB evaluation. The purpose of this dual latch structure is to feed-back the MSB data to the capacitor array as soon as possible, without using any extra latch to hold the MSB data.

Fig. 3.7-4 shows the program list of this simulation. SPICE Version 2G.1 is used here. Fig. 3.7-5 shows the node voltage as the result of the initial DC calculation, and the power dissipation. As was described in the previous section, the amplifier with source follower buffers consume more power than the other configurations. The total power dissipation here is 20.2 mW. Using 32 comparators will results in the power consumption of 646.4 mW, which is a relatively large value.

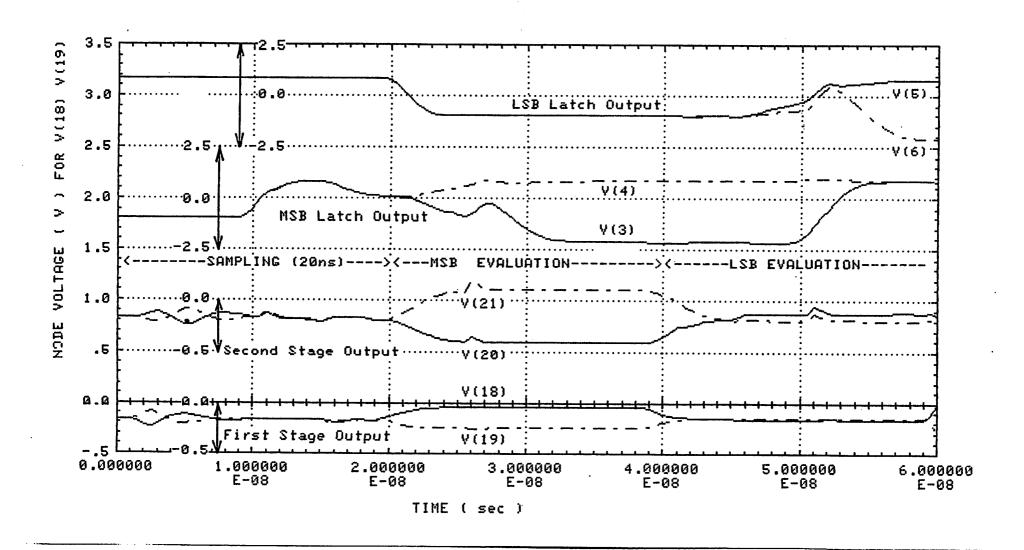

The result of the simulation is shown in Fig. 3.7-6. Here the MSB data can be evaluated at 30 ns from the sampling of the signal, and the LSB data can be acquired at 57 ns. The LSB data can be held by the latch during the next sampling and MSB evaluation cycle, so that a sampling cycle time of 60 ns is feasible.

The input voltage of the comparator is shown in Fig. 3.7-7. Here, no offset voltage is assumed in the comparator. During the sampling period, the input voltage jumps high and then saturates to zero. (less than a half LSB of 1 mV in the simulation) Then for the MSB evaluation there is a differential input of -74 mV. (Ideally it should be -78 mV.) And for the LSB evaluation the differential input is +2 mV as estimated in Fig. 3.7-2.

Fig. 3.7-1 Full Size Comparator Simulation

- \* Comparator Code ( 01000 ) ....... $2^3 = 8$

- \* Input Signal (0100100111) ..... $2^8 + 2^5 + 7 = 295$

- \*  $V_{ref} = 1.024 \text{ V}$

- \* Input Signal in Volts  $1.024 \times (288 + 7) / 1024 = 295 \text{ mV}$

- \* Unit Resistor in the Capacitor Array  $R_{on} = 8 \text{ k } \Omega$

- \* Unit Capacitor in the Capacitor Array  $C_{unit} = 0.05 \text{ pF}$

Fig. 3.7-3 Comparator Sub-Circuit COMP

```

U/ 1U/ UU ------ 17.7/.74 ---

3F1UE 40.0

FULL SIZE COMPARATOR COMP4 TEST

TEMPERATURE =

27.000 DEG C

INPUT LISTING

*3 APRIL 1985

*3 STAGE OF HIGH SPEED AMP

* COMP CODE 01000

INPUT

'01001 00111 ( 0.295V)

1.024V

VREF

CUNIT

0.05PF

BKOHM

RUNIT

ICYCLE 60NS ( 16.7MHZ ) , 4 APRIL

INCREASE THE POWER OF THE SOURCE FOLLOWER. 4 APR

INCREASE THE BW OF HEADAMP BY THE FACTOR OF 2 ( M3.4 )

ADD M2 (BIG SW) IN COMP4 AND KEEP VRST2 H FOR T=0, 29 APRIL

ADD CAPACITORS AT THE FRONT OF THE COMPARATORS, 2 MAY

CHANGE THE CONVERSION CONDITION IN .OPTIONS, 3 MAY

0.1P

C2

0.1P

Č3

0.1P

5

0

C4

6

0.1P

R1 18

0

1 T

R2

19

0

1 T

R3 20

1 T

R4 21

0

1 T

CP1 22

0.8P

CP2 23

0.4P

CP3 24

0.2P

CP4 25

0.1P

CP5

26

0.05P

CP6 27 1

0.05P

CN1

0.8P

0.4P

CN2

35

0.2P

CN3 36 2

CN4

37

0.1P

CN5 38 2

0.05P

CN6

39 2

0.05P

RP1

28 22 0.5K

RP2

29 23 1K

RP3 30 24 2K

31 25 4K

RP4

RP5

26 8K

32

RP6

33 27 8K

RN1

40 34 0.5K

41

35 1K

RN2

RN3

36 2K

42

RN4 43 37 4K

38 8K

RN5 44

RN6 45 39 8K

7 0

DC

2.5

VDD

vss

8 0

DC

VRST1

8

PULSE(5 0 15N 1N 1N 53N &0N)

PULSE(5 01345N 1N 1N 49N 70N)

PULSE(5 0 18N 1N 1N 40N 60N)

PULSE(5 0 9N 1N 1N 49N 60N)

VRST2 10

8

VRST3 11

8

VRST4 12

PULSE(0 5 19N 1N 1N 25N 60N)

PULSE(0 5 10N 1N 1N 14N 60N)

PULSE(0 5 26N 1N 1N 22N 60N)

VRST5 13

8

VSMPL1 14

8

VSTRB1 15

VSMPL2 16

PULSE(0 5 40N 1N 1N

8

9N 60N)

VSTRB2 17

79N 5 80N 0)

PWL(0 0 51N 0 52N 5

VP1

28

PULSE(0 0.295 1N 1N 1N 17N 70N)

VP2

PWL(0 0 1N 0 2N 0.295 19N 0.295 20N 1.024 59N 1.024 60N 0)

29

0

EP3

30

0

28

EP4

31

0

VP5

PWL(0 0 1N 0 2N 0.295 19N 0.295 20N 0 38N 0 39N 1.024 59N 1.024

32

0

60N 0)

PWL(0 0 1N 0 2N 0.295 19N 0.295 20N 0 38N 0 39N 0.256 59N 0.256

VP6

33

0

```

Fig. 3.7-4-1 Simulation Program List (1)

60N 0)

```

EN1

EN2

41

a

29

0

EN3

42

0

30

0

EN4

31

-1

EN5

44

A

32

0

-1

EN6

45

.0

33

2 3 4 5 6 7 8 9 10

CKT COMP4 1 2 3

11 12 13 14 15 16 17 18 19 20 21 COMP4

4 5 6 7 8 9 10 11

SUBCKT COMP4 1 2

MSB- LSB+ LSB- VDD VSS RST1 RST2 RST3 RST4 RST5

IN+ IN- MSB+

17

*SMP1 STRB1 SMP2 STRB2 MON1 MON2 MON3 MON4

18 22

19 23

0.1P

C2

0.1P

C3

24

0.1P

25

0.1P

M1

0

8

NMOS

W=40U

L=2U

AD=260P AS=260P PD=53U PS=53U

W=40U

NMOS

L=2U

AD=260P AS=260P PD=53U PS=53U

24 25 18 19 7

22 23 20 21 7

A

10

HEADCMP2

8

11

HEADCMP2

20 21 4

14 15

7

8 12 LATCHD

7

20 21 6

16 17

8 13 LATCHD

ENDS COMP4

•HEADCMP2 SUBCIRCUIT

*3 APRIL 1985

*HEADCMP WITH SOURCE FOLLOWER

.SUBCKT HEADCMP2

2 12

1

IN+ IN- OUT- OUT+ VDD VSS RST

10 DC 80U

RS

10 1MEG

9

M 1

NMOS W=27U AD=175.5P AS=175.5P PD=40U

NMOS W=27U AD=175.5P AS=175.5P

PD=40U

PS=40U

AS=78P

M3

8

PD=23U

PMOS W=12U AD=78P

PS=23U

M4

8

8

PMOS W=12U AD=78P

AS=78P

PD=23U

PS=23U

М5

8

PMOS W=24U .AD=156P

AS=156P

PD=37U

PS=37U

PMOS W=24U AD=156P

8

PD=37U

AS=156P

PS=37U

M7

6

8

PMOS W=24U AD=156P

AS=156P

PD=37U

м8

PMOS

₩=24U AD=156P

AS=156P

PD=37U

PS=37U

М9

6

10

Q

NMOS

W=16U AD=104P

AS=104P

PD=29U

M10

7 10

9

NMOS W=16U AD=104P

AS=104P

PD=29U

3 10

9

NMOS

W=36U AD=234P

AS=234P

PD=49U

PS=49U

10 10 9

NMOS W=8U

AD=52P

AS=52P

PD=21U

4 11

NMOS W=8U

AD=52P

AS=52P

PD=21U

5 11

AD=52P

AS=52P

M14

2

NMOS

W=8U

PD=21U

PS=21U

4 12

5 13

NMOS W=24U AD=156P