Copyright © 1985, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# A SYSTEM FOR TESTING CUSTOM DESIGNED VLSI

by

J. Dinur

Memorandum No. UCB/ERL M85/57

15 July 1985

5.5 Condum Res. UCity 1 21, RP5757

16 July Level

YARP ANDRALE IN RADIESE 2011/01-FD 115

isi aga of Toprogering Santa, Bhrkela, Ita (Christia, Bhrkelan Stilo

# A SYSTEM FOR TESTING CUSTOM DESIGNED VLSI

4

by

J. Dinur

# Memorandum No. UCB/ERL M85/57

15 July 1985

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

# A System For Testing Custom Designed VLSI

Julian Dinur

Department of Electrical Engineering and Computer Science Electrical Engineering Division University of California Berkeley California 94720

## ABSTRACT

This manual contains a general description of a system for testing custom designed VLSI chips. The manual also explains how to use the system and the main steps of testing a VLSI chip. The system was built at U. C. Berkeley, E.E. Department.

May 24, 1985

This research was funded by the Defense Advanced Research Projects Agency, contract number: N00039-85-C-0107.

# Table of Contents

· \_

.

:

| 1. INTRODUCTION                                                      | 1  |

|----------------------------------------------------------------------|----|

| 2. OPERATION MODES                                                   | 2  |

| 2.1. The test mode                                                   | 2  |

| 2.2. The debug mode                                                  | 2  |

| 3. HARDWARE                                                          | 3  |

| 3.1. General description                                             | 3  |

| 3.2. The GPP board                                                   | 4  |

| 3.3. The DSP chips tester board                                      | 8  |

| 3.4. The RAM chips tester board                                      | 8  |

| 4. FIRMWARE                                                          | 11 |

| 5. SOFTWARE                                                          | 12 |

| 5.1. The most useful commands :                                      | 12 |

| 6. THE MAIN STEPS OF TESTING A CHIP                                  | 13 |

| 7. RECOMMENDED DESIGN RULES FOR TESTABILITY                          | 15 |

| 8. APPENDIX A - Procedures                                           | 16 |

| 9. APPENDIX B - An example of a program in assembly language         | 18 |

| 10. APPENDIX C - An example of a program in C                        | 20 |

| 11. APPENDIX D - The I/O addresses for the special purpose board     | 21 |

| 12. APPENDIX E - I/O Drivers                                         | 22 |

| 13. APPENDIX F - The communication protocol over the serial channels |    |

|                                                                      | 24 |

| 14. APPENDIX G - The dumpdata.c program                              | 25 |

| 15. APPENDIX H - SCHEMATICS                                          | 26 |

| 15.1. GPP Board - I/O Part                                           | 26 |

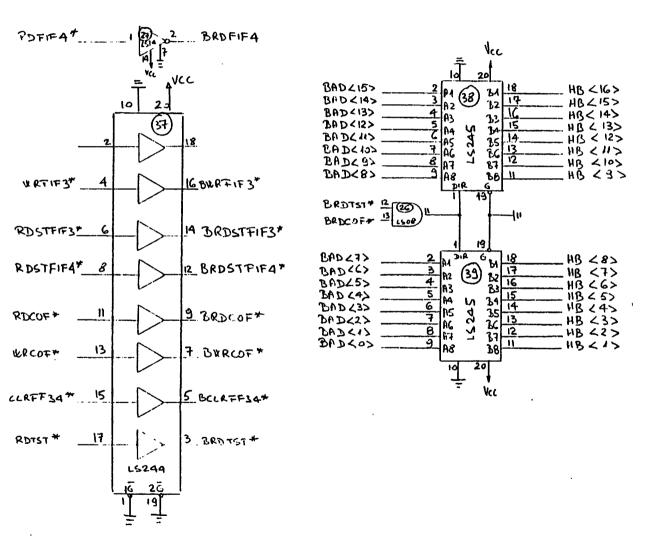

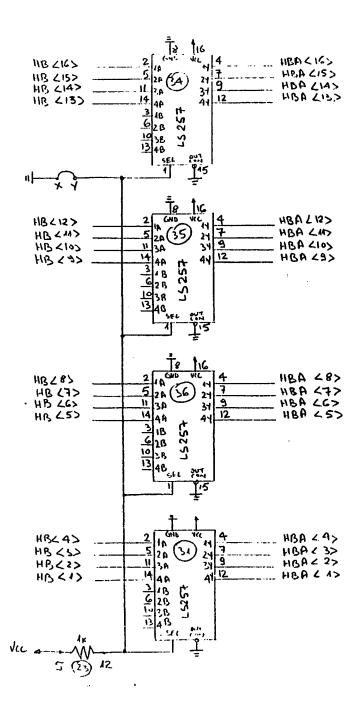

| 15.2. DSP Chips Tester Board                                         | 32 |

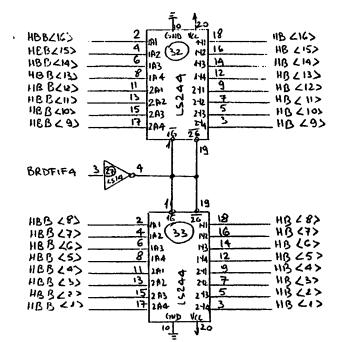

| 15.3. RAM Chips Tester Board                                         | 41 |

# A System For Testing Custom Designed VLSI

Julian Dinur

Department of Electrical Engineering and Computer Science Electrical Engineering Division University of California Berkeley California 94720

#### 1. INTRODUCTION

An inexpensive and very efficient system for functionally testing custom designed VLSI chips has been designed and built. The system, currently used at U.C. Berkeley in the EECS Department, is very efficient for testing digital signal processor (DSP) and RAM chips.

The tester is connected to a host computer which down-loads a testing program and an input data file. During the program execution, the system stores the results in an output data file. After the execution of the program, the system up-loads the output file to the host computer for examination.

The system has two operation modes : a test mode and a debug mode.

In the test mode, the stored output results are the regular data outputs from the tested chip. In the debug mode, the stored output results are the contents of the output bus from the tested chip, after each input clock.

### 2. OPERATION MODES

#### 2.1. The test mode

In this operation mode, the regular output results from the tested chip are stored in the tester memory. The results are then up-loaded to a file in the host computer for examination. The resultant file is compared with a pre-prepared file which contains the expected results.

In the case the two compared files are identical, the assumption is that the chip works properly. (To verify this assumption, the process is repeated for many different input files).

In the case the two compared files are different, further investigation is needed to find out what is wrong in the chip. This can be done by using the debug mode.

#### 2.2. The debug mode

In this operation mode, the stored results in the tester memory are the contents of the output bus from the tested chip, after each input clock cycle. The results are up-loaded to a file in the host computer for examination. As in the test mode, the resultant file is compared with a pre-prepared file which contains the expected results. In this case an incorrect result can indicate which unit in the tested chip does not work properly, or which command is not executed as expected.

A farther investigation of the chip's design then needs to be performed, in order to pinpoint flaws and allow for any necessary design corrections.

#### 3. HARDWARE

#### **3.1.** General description

The VLSI tester consists of 2 boards : a general purpose processor (GPP) board and a special purpose board. All the boards are built on Multibus compatible cards.

The GPP board is built around a 16-bit microprocessor and its main roles are:

a. Store the test program loaded from the host computer.

b. Run the test program in conjunction with the special purpose board and store the results.

c. Up-load the results to the host computer.

The general purpose board contains the interface between the GPP and the device under test (DUT). Two special purpose boards have been built : a board for the digital signal processor (DSP) type chips and a board for the RAM type chips.

The main roles of the board for testing DSP chips are :

a. Store the input data file sent by the GPP board and enable the DUT to read the input data at its own rate.

b. Store the output results from the DUT and enable the GPP to read this file at its own rate.

c. Enable data write/reads directly to/from the DUT.

The main roles of the board for testing RAM chips are :

a. Store the RAM address sent from the GPP.

b. Store the input data sent from the GPP and write it into the RAM.

c. Store the output data from the RAM and to enable the GPP to read it.

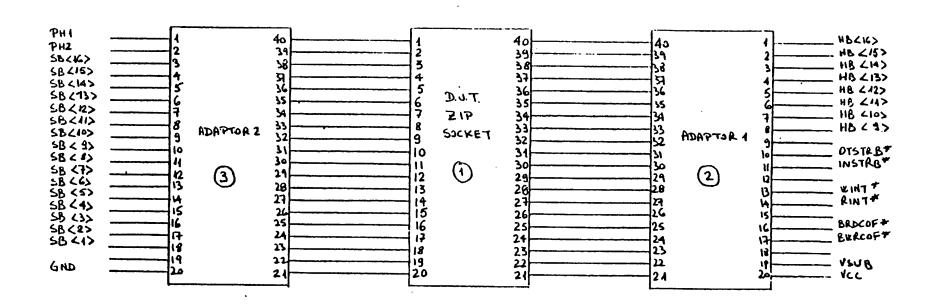

In order to enable the testing of chips with different pinout, a special adaptor has to be prepared and placed on the special purpose board.

### 3.2. The GPP board

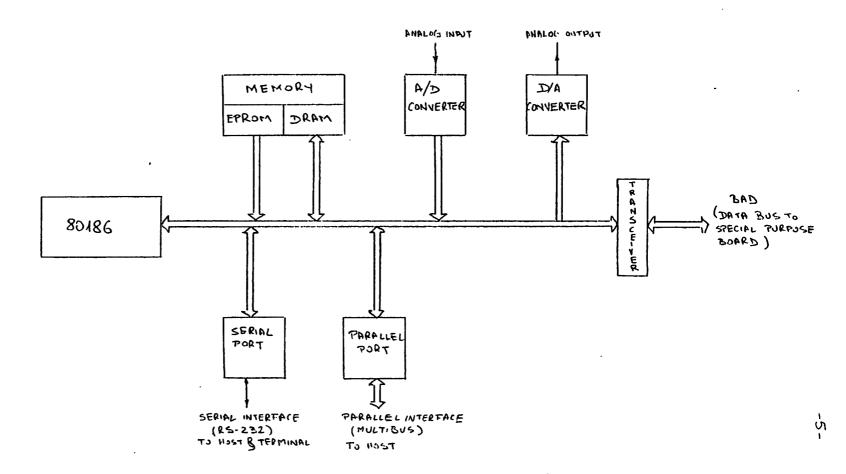

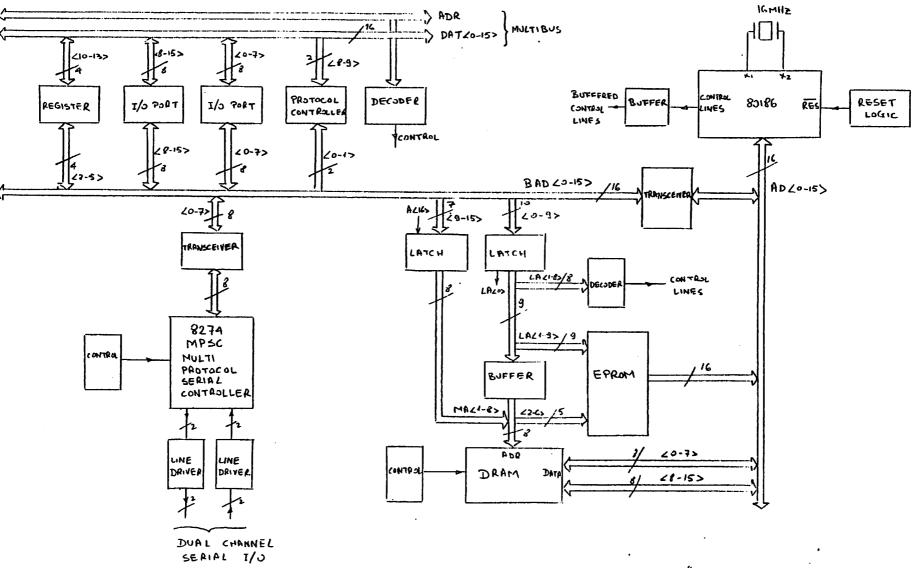

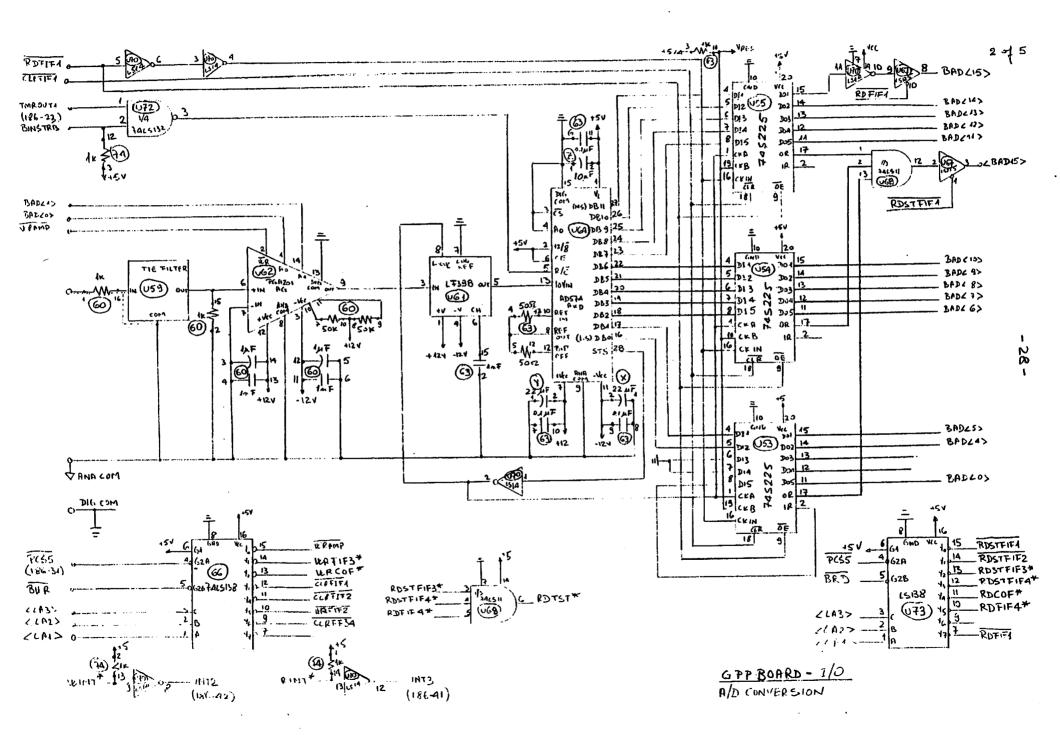

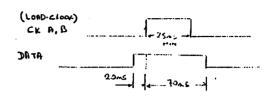

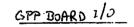

The GPP is based on the Intel 80186 microprocessor and contains the following functional blocks (please see fig. 1 - fig.3):

a. EPROM (2 k \* 16 bits) - stores the firmware which enables the GPP to communicate with a host computer (VAX, for example) through the serial or parallel ports.

b. DRAM (64 k \* 16 bits) - stores the test program, the input data file and the output testing results.

c. Two serial I/O ports - enable the serial communication between the GPP and a host computer through the RS-232 protocol.

d. Parallel interface - supports the communication with a host computer through the Multibus based protocol.

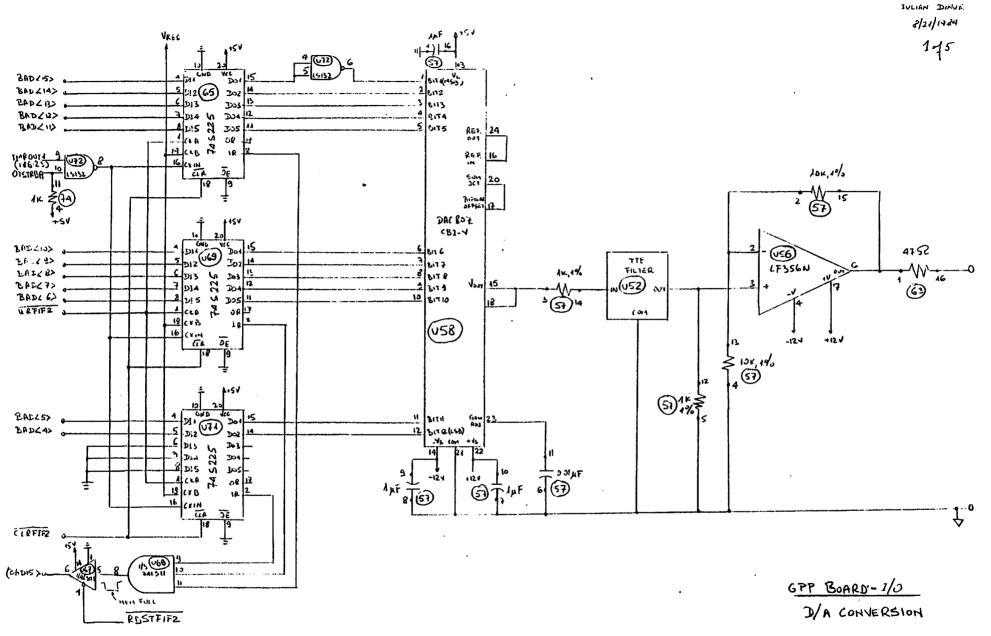

e. A/D converter - enables the GPP to read samples from the analog input at a rate up to 25 kwords (12 bits) per second.

f. D/A converter - enables the GPP to send data to the analog output at a rate up to 200 kwords (12 bits) per second.

The GPP board is based on the SPUDS board (for details on the SPUDS board, please see the report "SPUDS" by William Baringer, Memorandum No. UCB/ERL M84/4, January, 1984).

# FIGURE 1 : GPP BOARD - GENERAL BLOCK DIAGRAM

-

J. DINUR

FIGURE 2: GPP BOARD . DIGITAL SECTION (SPUDS") DETAILED BLOCK DIAGRAM J. DINUR

-6-

FIGURE 3: GPP BOARD - ANALOG SECTION DETAILED BLOCK DIAGRAM JULIAN DINUR

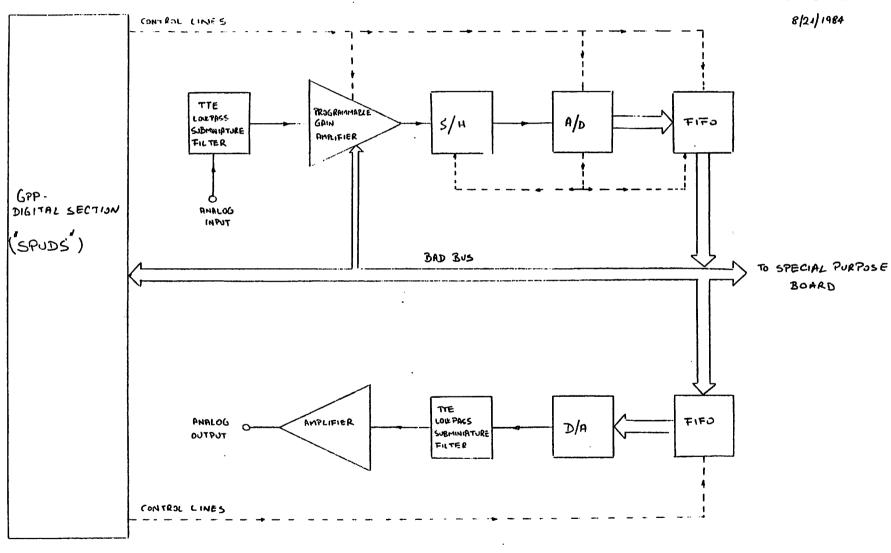

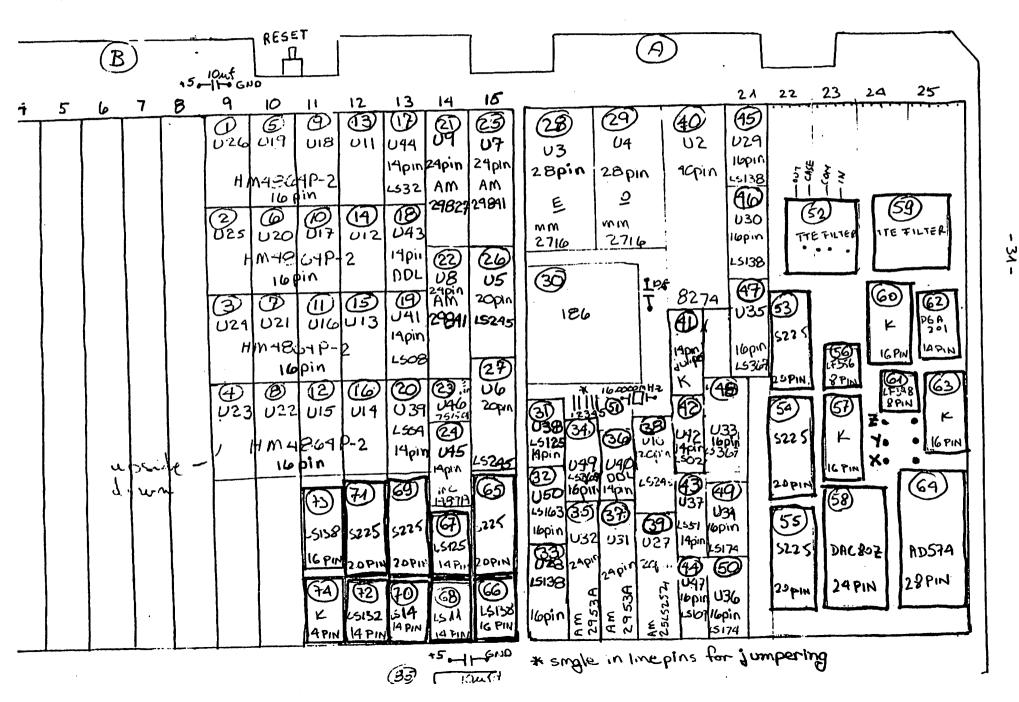

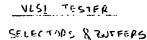

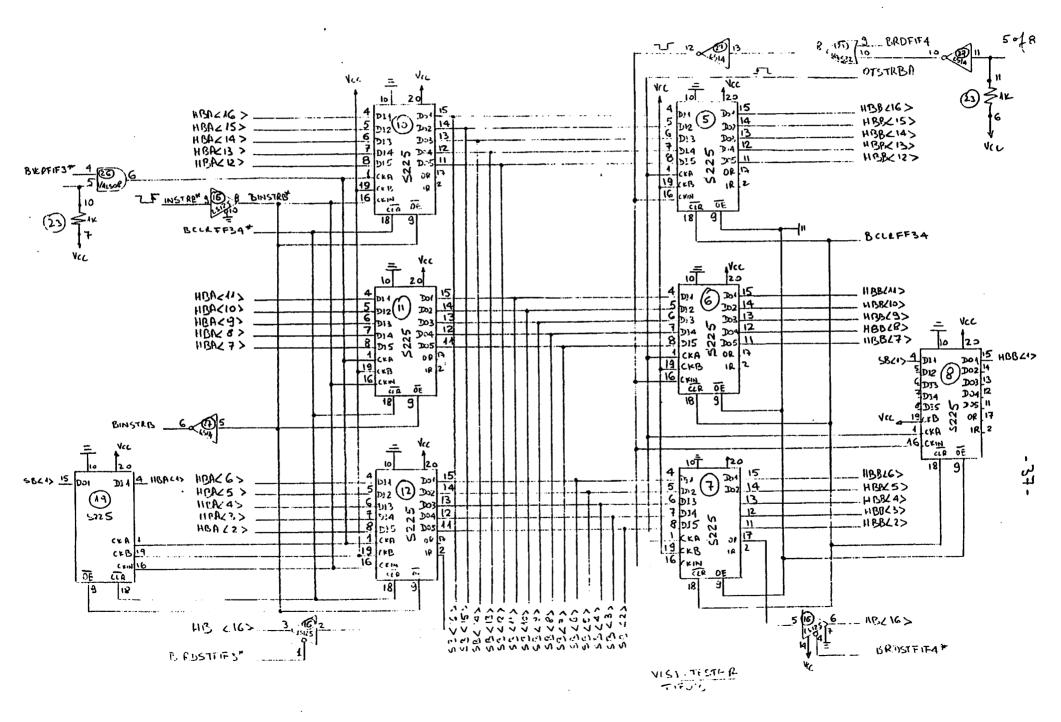

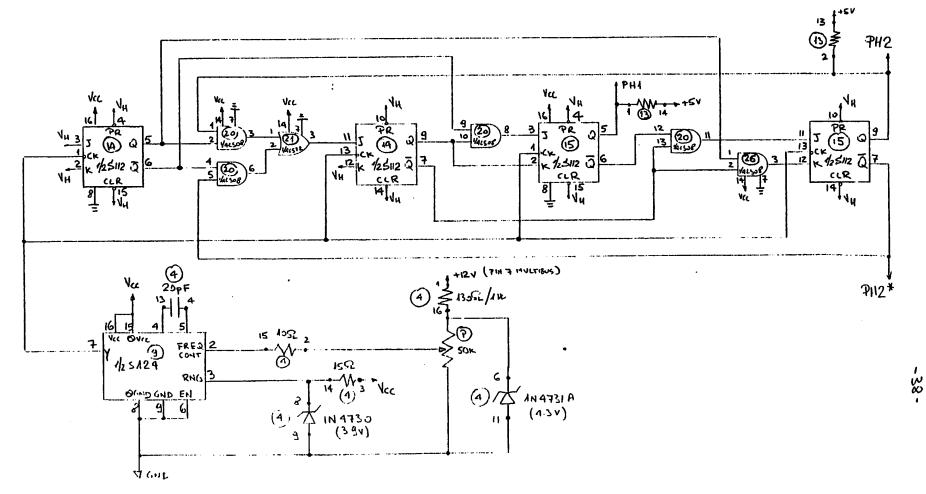

#### 3.3. The DSP chips tester board

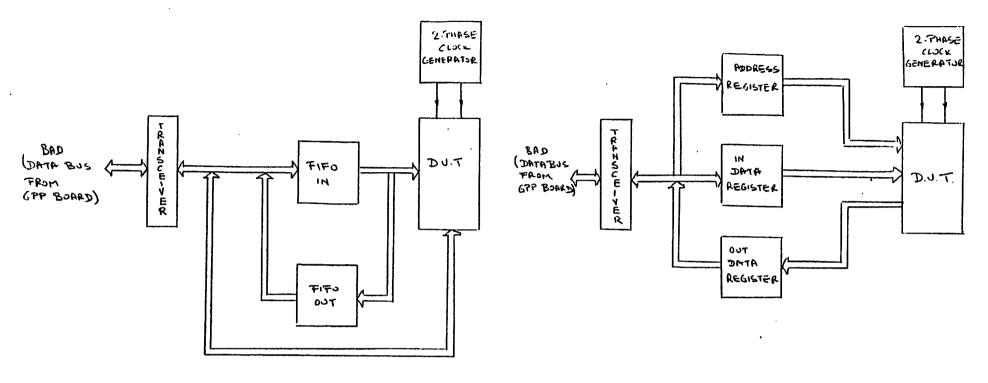

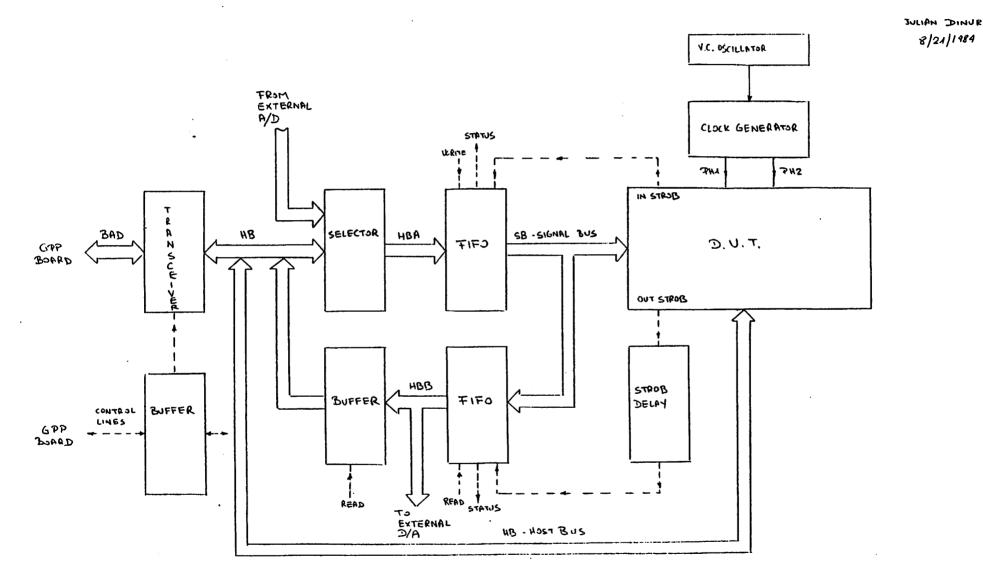

This board consists of the following functional blocks (please see fig. 4 - fig.5):

a. FIFO input memory - stores up to 16 words of 16 bits each of input data sent from the GPP to the DUT.

b. FIFO output memory - stores up to 16 words of 16 bits each of output data sent from the DUT to the GPP.

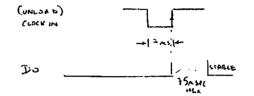

c. Clock generator - generates 2-phase non overlapping clocks (1/4 duty cycle).

Due to the small number of words in the FIFO, the minimum time between consecutive input data to the DUT is about 5 useconds. (A new faster board with a larger memory is under development).

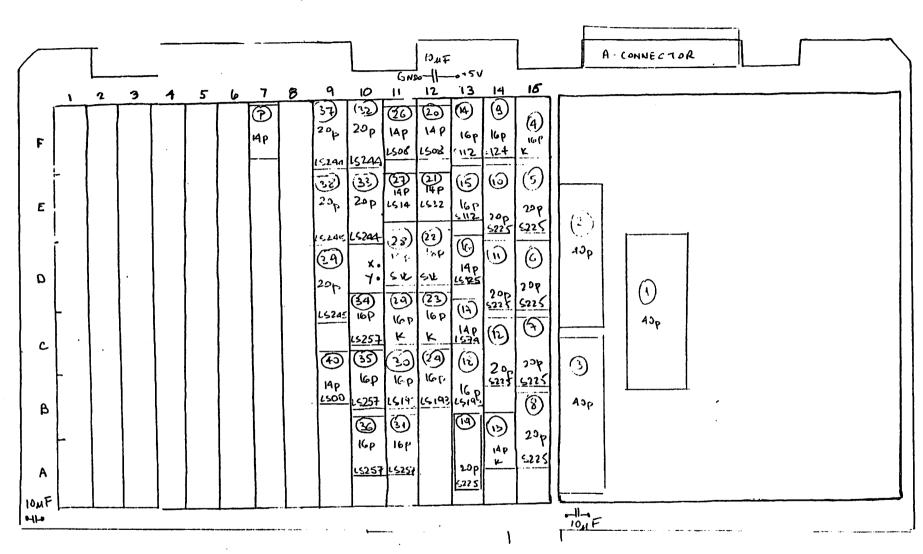

### 3.4. The RAM chips tester board

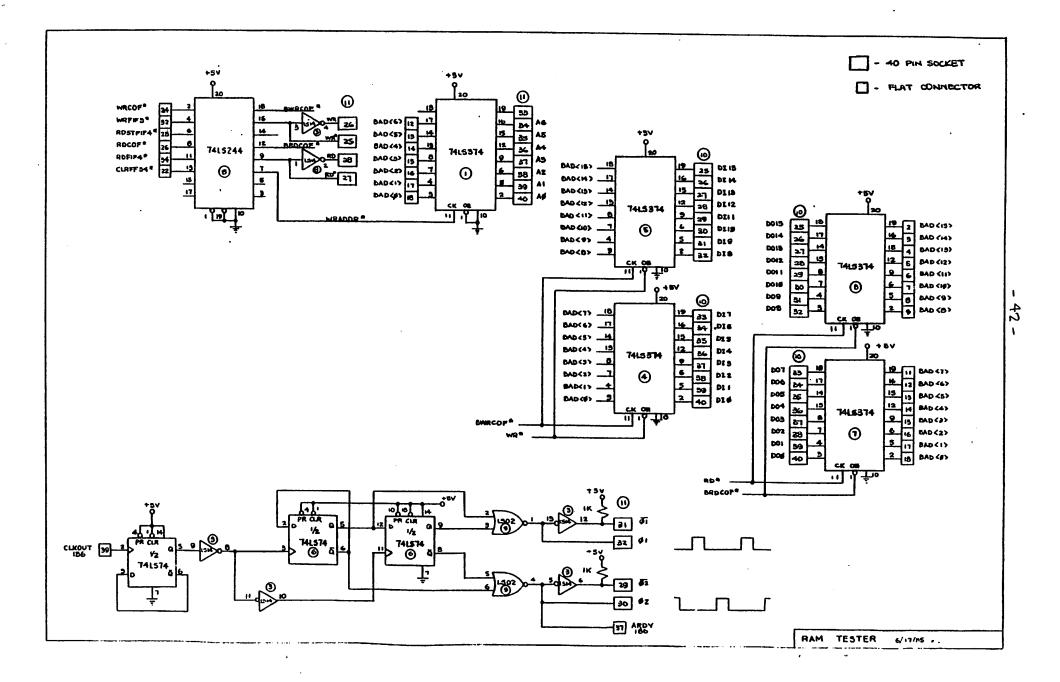

This board contains the following functional blocks (please see fig. 2):

a. Address register - stores up to 8 bits of address sent from the GPP.

b. Input data register - stores up to 16 bits of input data sent from the GPP to the DUT.

c. Output data register - stores up to 24 bits of output data sent from the DUT to the GPP.

d. Clock generator - generates 2-phase non overlapping clocks (3/8 duty cycle).

Because the GPP board sees this board as a mapped I/O device, the RAM addresses have to be sent first and then stored on the tester board. After that (about 1 usecond later), the data can be written or read from the RAM. (A new faster board is under development).

•

<u>A.</u>

. .

•

B.

FIGURE 4 : SPECIAL PURPUSE BOARD - GENERAL BLOCK DIAGRAM

A : FOR DSP CHIPS B .: FOR RAM CHIPS 10-

•

10

TIGURE 5 : STECIAL PURPOSE BOARD FOR DSI' CHIPS. DETAILED BLOCK DIAGRAM

The firmware in the EPROM on the GPP board was written so that a terminal may be connected to serial channel B and the host computer to serial channel A. The GPP board then acts in a "terminal emulator" mode where characters received from the host are passed on to the terminal's screen. However, if a certain string of control characters is received from the host computer, the code is not sent to the terminal, but stored in the DRAM on the GPP board. At the end of the transfer of the user's program, another set of control characters is sent as an end-of-text indicator, and program execution of the 80186 commences at the beginning of the new program in DRAM.

A typical program loaded into DRAM could allow control of the tester via the terminal, and send data back to the terminal for examination. Data may also be sent to the host computer for storing and further processing.

#### 5. SOFTWARE

The test programs can be written in C and/or Intel 80186 assembly language.

The C programmer can use a large amount of pre-defined procedures (please, see appendix A) and an 8086 cross compiler.

#### 5.1. The most useful commands

A program in assembly language should have the suffix .a86. For example:

prog.a86

The assembler a86 will produce the file prog.b :

#### a86 prog.a86

The C cross assembler will produce the executable file xx.com ( xx is an arbitrarily name ):

#### cc86 -1 -o xx prog.b

To assemble a C program, p.c, and an assembly program, prog.b, the following command should be used :

#### cc86 -1 -o xx p.c prog.b

To load the executable file in tester's memory, one should use the command:

#### pdploader xx.com /usr/local/86ldr

If using the C program presented in appendix c, the output results will be stored in the file "results" in the host computer, in the user's directory. To read this file on the terminal, the following command can be used :

#### dumpdata < results

dumpdata.c is a C dump program (please see appendix G). The user can modify this program in order to get a different output format.

### 6. THE MAIN STEPS OF TESTING A CHIP

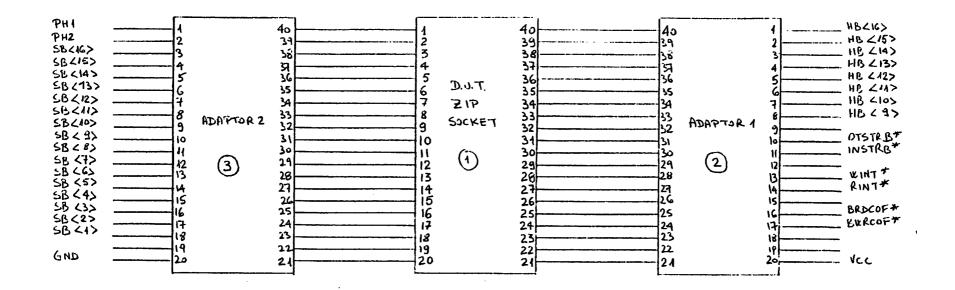

a. Prepare the adaptor for the specific chip pinout (a special form has been prepared for this purpose, please see figure 6).

b. Prepare the software (the assembly language program and/or the C program with the input data file).

c. Begin to test in the "test mode" : load the testing program and examine the output result file.

d. In the case the the results are incorrect, the chip can be tested in the "debug mode". To do that a small hardware modification is needed and the software has to be updated.

e. The use of an oscilloscope and a logic analayzer for testing the waveforms and the timing of the chip's signals is strongly recommended.

À

.

# FIGURE 6: DSP (HIPS TESTER ROFRD: ZIP SOCKET

1

AND ADAPTORS

•

### 7. RECOMMENDED DESIGN RULES FOR TESTABILITY

a. Use only "active low" external signals.

b. Use only uninverted input clock.

c. Use built-in firmware for testing.

d. Use a reset pin to reset the chip. All internal flip flops and latches should be reset or set to known states :

- Counters

- Stack pointers

- Internal data busses

- Tristate output pads.

e. Being able to preset portions of a circuit can be very useful. The preset value can be hardwired into the circuit or programmed from the outside. The intent of presettability is to allow a portion of the circuit to be easily placed into a known state other than the reset state to activate a function to be tested.

### 8. APPENDIX A - Procedures

The procedures were prepared by Robert Kavaler. They are on ucboz in : ~kavaler/85/cc86mit/lib186.

#### sys/

```

DmaSetup.a86

DmaSetup((long) source, (long) dest, count, control,

channel (FFC0/FFD0))

MemFill.a86

MemFill(Physical_Address, count, data0, data1, ...)

Refresh.c

Refresh()

int.a86

splow()

/* enable interrupts */

sp high() /* disable interrupts */

splx(splhigh_return) /* return the old set-up for interrupts */

SetInt(type, raddr)

io.a86

IoIn(port)

/* write data to port */

IoOut(port, data) /* read data from port */

ios.a86

IoInsb(port, address, len)

IoInsw(port, address, len)

IoOutsb(port, address, len)

IoOutsw(port, address, len)

lblt.c

lblt(to, from, len) /* long block transfer by DMA */

mem.a86

MemIn(Physical_Address) /* read words */

MemOut(Physical_Address, data) /* write words */

misc.a86 GetDS()

GetCS()

physaddr.aE6 physaddr(addr)

sbrk.c

sbrk(incr)

sys.c

ttyio.c

/* serial communication with the TTY */

_rcn_out(c) /* data : c - character */

_rcn_ob() /* status */

_rcn_in() /* status */

<u>rcn_ib()</u> /* data */

/* serial communication with the host computer */

vaxio.c

_rvx_out(c)

<u>_rvx_ob()</u>

<u>_rvx_in()</u>

<u>_rvx_i</u>b()

```

#### opsys/

```

dispatch.a86 Dispatch()

PromImm - from assembly language routines only, use jmp

menu.c

menu()

object.c CreatObjects(length, number)

GetObject(Objects)

LinkObject(Objects, object)

UnlinkObject(Objects, object)

Lock(x)

plock.c

Unlock(x)

pmalloc.c

pmalloc(num)

pfree(p)

process.c

ProcStart(Processes)

ProcKill(Processes)

procinit.a86 InitDone()

```

792

ptime.c TimeStamp() creatq(msize, nmessages) queue.c resetq(q) getq(q) igetq(q) getlq(q, b) putq(q)iputq(q) putlq(q, b) killq() shell(prompt, commands)

shell.c

. . . . . . . . . .

- -- --

/\* for Multibus communication \*/ messages/

MesgInit.c MesgInit() MesgOut(data, length) MesgOut.c MesgQIn.c MesgIn(p) MesgFlush() NewMgInQ(type, q) MesgQOut.c MesgQOut(p) SendObject(Objects, obj, len) SendQueue(q, len)

multibus/ - low level stuff gen/ - standard C library - \*printf, and getline (my own creation, used by shell) stdic/

Standard I/O is difficult to explain, just follow these rules. Before any input/output use one of the following calls:

#include <stdio.h> extern SIOSYSTEM sio\_oconsole; if using RS 232 ports sio\_new(&sio\_oconsole)

-or-

#include <stdio.h> extern SIOSYSTEM sio\_multibus; if using SUN "mbhost" program sio\_new(&sio\_multibus)

835

#### 9. APPENDIX B - An example of a program in assembly language

```

.data

a program to test the cmos ram (cram)

a contains 18 bytes

.comm

_a,18

_b,12

b contains 12 bytes

.comm

.comm

_c,18

_addra,2

.comm

_addrb,2

.comm

.text

_first is the name of the program

.globl

_first

_addra

.globl

address of input data

.globl

addrb

address of output data

first:

pusha

push all registers on stack

MAXDAT=3

the max no. of blocks (3 words each)

in input file

mov bx,*1

mov_addra,#_a

mov_addrb,#_b

mov cx,#MAXDAT

init1:

mov si,#_a

mov di,#_b

mov dx,#0x028E

debug pulse

outw

read data from (80186)memory

11:

mov ax.(si)

dx,#0x028C |write data to addr. reg.

mov

outw

prepare for next addr.

add si,*2

read data from (80186)memory

mov ax,(si)

mov dx, #0x0284

write data to data reg.

outw

mov dx,#0x0282

write to cram

outw

add si,*2

11

repeat for each cram addr.

loop

```

```

833

```

- 19 -

```

mov cx, #MAXDAT

```

```

12: mov ax,(si)

read data from memory

mov dx,#0x028C

write data to addr. reg

outw

ł

add si,*2

1

|.

mov dx,#0x028A

inw

read data from cram

1

mov dx,#0x0286

|read M.S.Part of data from cram

4 m.s.b.

inw

and ax,#0x000F

clear non-relevant bits

mov (di),ax

store data in memory

add di,*2

1

mov dx,#0x0288

read L.S.Part of data from cram

16 l.s.b.

inw

mov (di),ax

store data in memory

add di,*2

loop 12

repeat for each addr. in cram

jmp init1

start from the beginning

dec bx

jnz init1

popa

restore all registers

ret

.even

.data

<u>a</u>:

7

.word

.word

0

.word

10

256

.word

.word

63

32767

.word

.word

7

10

.word

63

.word

_<u>c</u>:

.word

0,0,0,0,0,0,0,0,0

_b:

0,0,0,0,0,0

.word

```

#### 10. APPENDIX C - An example of a program in C

This C program should be assembled with a program in assembly language in orde to enable the up-loading of the output file from the tester memory.

```

#define SIO sio_oconsole

#include <stdio.h>

#include <sys.h>

#define LENGTH 48

extern first();

extern int *addra;

extern int *addrb;

main()

Į

splhigh();

/* disable interrupt */

first();

/* call the assembly program */

splow();

/* enable interrupt */

initialize();

/* init. the tty */

printf("start up-loading\n ");

r_write("results",addra,LENGTH);

/* up-load the output file */

/* "results" : the file name in te host */

/* addra : the starting address in the DRAM on GPP board */

/* LENGTH : the number of bytes in the file */

printf("end up-loading\n ");

3

initialize()

Σ

extern SIOSYSTEM SIO;

sio_new(&SIO);

vaxrawmode();

3

vaxrawmode()

/* the following code initializes the serial */

/* controller on the tester board for writing */

/* to the host computer

٤

IoOut(VAXCSR, 0x05);

IoOut(VAXCSR, 0x68);

IoOut(VAXCSR, 0x03);

IoOut(VAXCSR, 0xC1);

IoOut(VAXCSR, 0x04);

IoOut(VAXCSR, 0x4E);

3

```

832

## 11. APPENDIX D - The I/O addresses for the special purpose board

adrtest1.a86 .globl \_main \_main: loop: mov dx,#0x0280 in read status FIFO 1 (A/D) out |set amp. gain add dx,\*2 read status FIFO 2 (D/A) in write data to FIFO 3 (host to D.U.T.) out add dx,\*2 read status FIFO 3 (host to D.U.T.) in write coef. to D.U.T. out add dx,\*2 read status FIFO 4 (D.U.T. to host) in clear FIFO 1 (A/D) out dx,\*2 add read coef. from D.U.T. in clear FIFO 2 (D/A) out add dx, \*2 in read data from FIFO 4 (D.U.T. to host) out write data to FIFO 2 (D/A)dx,\*2 add N.D in out N.D add dx,\*2 in read data from FIFO 1 (A/D) out N.D nop;nop;nop jmp loop

#### 12. APPENDIX E - I/O Drivers

## UNIX 4.2BSD I/O driver for GPP board

#### Hardware:

There are three distinct ports on the GPP board: CSR, DATA, and RESET. A read from the RESET port will reset the GPP board and jump to the on-board PROM. This is considered a hard-reset. The CSR and DATA ports are both readable and writable, but they have a different meaning if read or written. Thus code like:

#### CSR = ENABLE;

will not do the obvious thing. Instead a variable is kept in memory that contains what is in the CSR and was last written. The data port is designed so that strings of characters will not have their bytes reversed, while strings of shorts will end up with reversed bytes. This is because of the byte ordering incompatibility between the SUN and 186. In addition, the CSR port is active low on the SUN side, so every read and write to the SUN CSR should be complemented to get active high signals. All of these concerns are handled correctly by the driver.

#### UNIX driver:

The driver implements 4 system calls: open, read, write, and ioctl. Open just checks that its arguments are legal. The read and write system calls receive and send "messages" to the GPP board through the MULTIBUS. Message lengths must be even (in bytes). A message consists of any number of data words followed by a unique word (called a header). The header word is distinguished from data through the use of the CSR port. From the UNIX program point of view a message is just a variable length data stream that is sent to the GPP board. The driver handles all handshaking and header generation. The CSR bits are defined as follows:

### /\* description of CSR bits \*/

| /            |            | /           |

|--------------|------------|-------------|

| #define      | SP_OUTEN   | 0x000100    |

| #define      | SP_OUTRDY  | 0x000100    |

| #define      | SP_INEN    | 0x000200    |

| "<br>#define | SP_INRDY   | 0x000200    |

| "<br>#define | SP_PROGMAS | SK 0x003C00 |

/\* message bits \*/ #define SP\_MGMASKTYPE 0x000C00 #define SP\_MGTYPEH 0x000400 #define SP\_MGTYPEM 0x000800

> TYPEM is the CSR bits for messages, TYPEH is the CSR bits for headers. All headers also have a data word associated with them. Thus there are 65536 distinct headers, only 2 are currently

used, 0 and 1. Most headers are 0, but the down-load PROM on the GPP board recognizes a header of 1 to mean start the loading the incoming message into RAM, and execute from there. To change the header that is sent out at the end of a message one uses the SP\_CHHEADER ioctl call:

# int i;

i = (header); ioctl(sp\_fn, SP\_CHHEADER, &i);

Additional ioctl calls are:

SP\_RESET - read the RESET port, returning control to the spuds PROM.

SP\_FLUSH - called to reset the driver if read or write terminates early (i.e. from a kill signal).

SP\_{RD,WR}{DATA,CSR} - read/write the DATA/CSR registers directly. These calls should never be used except to debug things. CSR bits come out active high.

The read system call should be used as:

actual\_message\_size = read(sp\_fn, buf, MAX\_MESSAGE\_SIZE); only one process should execute this command since one never knows what messages will be received.

The write system call can be used by any process. Serialization of the calls is perform by the driver. The write system call is:

errcode = write(sp\_fn, outmessage, outmessage\_length); the value returned should always be outmessage\_length or an error occured.

# 13. APPENDIX F - The communication protocol over the serial channels

#include <stdio.h>

#include <host.h>

# /\*

## To READ or WRITE UNIX files over serial lines

The following protocol is used on the client end:

```

in read() or write()

```

- send a SYNC FILE\_RD (or FILE\_WR)

- send the file name

- send a SYNC END\_OF\_MESSAGE

```

in r_read() or r_write()

```

```

- wait for the client to respond with SYNC FILE_RD (or FILE_WR)

(if we receive SYNC ERROR, there is a problem reading

```

or writing the file)

IN READ

- read in characters from the host until a SYNC END\_OF\_MESSAGE is received

IN WRITE

- send BLOCK\_SZ characters to the host

- send a SYNC EOB

- repeat until all the desired samples have been transmitted

- send a SYNC END\_OF\_MESSAGE

# /\* SHELL ESCAPE

works similarly to the read/write functions.

- 1) client sends SYNC COMMAND\_MODE

- 2) client sends command

- 3) client sends END\_OF\_MESSAGE

- 4) client goes into "terminal mode" which it stays in until it gets a SYNC END\_OF\_MESSAGE from the pdp

- 5) host executes the command taking stdin from the client which it now treats as a standard terminal (it has temporarily discontinued raw mode)

- 6) host transmits SYNC END\_OF\_MESSAGE when the forked of command has finished

- 7) client sends END\_OF\_MESSAGE to acknowledge

\*/

### 14. APPENDIX G - The dumpdata c program

This program is used to dump the output data results stored in a ASCII file, by the testing program, to a terminal.

```

#include <stdio.h>

```

```

main(argc, argv)

char *argv[];

int argc;

٤

printblock(10, 8); /* dump the input data file */

while(1) {

printblock(36, 8); /* dump the output results */

}

}

getshort(fp)

FILE *fp;

٤

int c1, c2;

c1 = getchar(fp);

c2 = getchar(fp);

if(c2 == EOF) {

printf("0);

exit(0);

ł

return (int) (short) ((c1\&0xFF)+((c2\&0xFF)<<8));

}

printblock(blocksize, linesize)

int blocksize, linesize;

Į

int i, col;

col=0;

for(i=0; i<blocksize; i++) {</pre>

if(col++ >= linesize) {

col=1;

printf("0);

3

printf("%8d", getshort(stdin));

ł

printf("0);

}

```

# 15. APPENDIX H - SCHEMATICS

15.1. GPP Board - I/O Part

.

| SPUD GND   | 0                                     |              |              |

|------------|---------------------------------------|--------------|--------------|

| BADZISS    |                                       | 2            |              |

| ZADZ14>    | 3                                     | · -0         |              |

| BADC13>    | · · · · · · · · · · · · · · · · · · · | 4            |              |

| BADKIZS    | <u> </u>                              | U            |              |

| -          | -                                     | 6            |              |

| BADKUS     | 7                                     | 0            |              |

| BADLIOS    | 3                                     | 2            |              |

| BADC9>     |                                       | ð            |              |

| BAD< 82    | 9<br>0                                | 10           |              |

| spud gnd   |                                       | Ō            |              |

| BAD<7>     |                                       | 12           |              |

| BAD 26>    |                                       | Ö            |              |

| BAD<5>     | 3                                     |              |              |

| BAD<4>     |                                       | 14           |              |

| BADER      |                                       | 0            |              |

| RAN        | 0                                     | 16           |              |

|            | 0                                     | ()           |              |

|            |                                       | 18           |              |

| PHD TO>    | 0                                     | ·0           |              |

| 2105 CIVID | 0                                     | 20           |              |

| RDTST *    |                                       | 0            |              |

| SRID GND   | 0                                     |              |              |

| CLRFF34*   |                                       | Q            |              |

| SFUD GND   | 23                                    |              |              |

| WRCOF *    | -                                     | 24           |              |

| SPUD GND   | 15                                    | -0           |              |

| RDCOF*     | 0                                     | 26           |              |

| -          |                                       | ····· 0      |              |

| SPUD GND   | 0                                     | 28           |              |

| KD51+1+4   |                                       | 0            |              |

| 2400 6140  | 0                                     | 30           |              |

| RDSTFIF3*  |                                       | 0            |              |

| SPUD GND   |                                       | 32           |              |

| KR7173*    |                                       |              |              |

| SFUL GND   |                                       |              |              |

| RDFIF4*    |                                       | 34<br>0      |              |

| SPUD GND   | 35                                    |              |              |

|            |                                       | م <u>ک</u> د |              |

|            | ੋਸੋ                                   | Ú            |              |

|            | U                                     | <b>58</b>    |              |

|            | ઝ                                     | 0            |              |

|            | 0                                     | 40           |              |

|            | A.                                    | 0            |              |

|            | 4i<br>O                               | <b>6</b> 3   |              |

|            |                                       | 42           | _TESTER GND  |

|            | 43                                    |              | OTSTRBA      |

|            |                                       | 44           | _TESTER GND  |

|            | 45                                    |              | BINSTRB      |

|            | <i>c</i>                              | 46           | TESTER OND   |

|            | 47                                    | · · · · · ·  | WINT*        |

|            | V                                     | 41           | TESTER OND   |

|            | 49                                    | ()           | KINT+        |

|            | ()                                    | 50           | TESTER GND   |

|            |                                       | Q            | . INDIER UND |

•

SPUTSE NEST TE STOR PIN DESIGNATION FOR EQ. PIN RIBBON CARLE CONNECTOR (A)

.

•

-29-

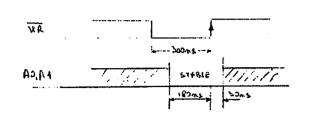

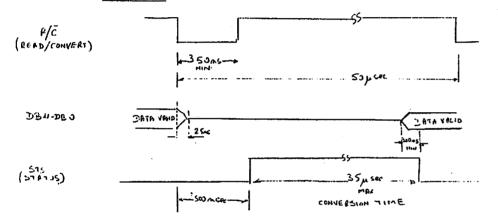

3. 7 5

AD574 AKD

PGA 2DAAG

TIMING DIAGRAMS

1 20

1

GPP BOARD - LAYOUT

FOR WIRE WRAPPING .

Front View

- 32 -

# 15.2. DSP Chips Tester Board

VLSI TESTER LAYOUT (FOR DEP (11175) FRONT VIEW

......

. .

1

К

2 - 1 8

.

۱.

.

VISI TESTER

.

,

t ω ՄI ۱

3-18

4 0 7 8

- 36-

v **\***

NES: TESTER CLOCK GUNERATOR

6 0 8

. .

8 - 1 8

- 40-

| SPUD GND             | - 4    | <b>1</b>           |              |

|----------------------|--------|--------------------|--------------|

| BADL 15>             |        | · 2                |              |

| BA2214>              |        | 3                  |              |

| BAUL13>              | · ·    | 9 4<br>⊴- 0        |              |

| ZEDLIZZ              |        | 5                  |              |

| BADKHS               |        | ·····              |              |

| BADLIOS              |        | 7                  |              |

| BADCON               |        | n<br>x0            |              |

| CBDC82               |        | ,                  |              |

| SPUD GND             |        | 0 10               |              |

| BADATS               |        |                    |              |

| BAD 26>              |        | Ň                  |              |

| BAD(5)               |        | 2                  |              |

| BADZAS               |        | 14                 |              |

| BAD <3>              |        | i <del>5</del> 0   |              |

| BAD <2>              |        |                    |              |

| BAD < 12             |        | 7                  |              |

| BAD 203              |        | 0 <sub>18</sub>    |              |

| SPUD GND             |        | व ∵−0              |              |

|                      | (      | 0 20               |              |

| BRD TST*             | 3      | LI0                |              |

| SRUD GHD<br>CLR FF34 | *      | 0 22               |              |

|                      |        | <u>ъ</u> о.,       |              |

| SPUD GND             |        |                    |              |

| WRCOF .              |        | 5-0                |              |

| SPUD GND<br>RDCOF*   |        | <sup>()</sup> 26   |              |

|                      |        | цт <sup></sup> О   |              |

| SPUD GND             |        | 0 28               |              |

| RDSTFIF4"            |        | ·O                 |              |

| SPUD GND             |        | ດັ່ງລ              |              |

| RDSTFIF3*            |        | <u>ii</u> ·0       |              |

| SPJD GND             |        | ñ                  |              |

| KEFIF3*              |        | -                  |              |

| STUD GND             |        | <u>}</u>           |              |

| rdfif4*              |        | <b>^</b>           |              |

| spud GND             |        | 5 1                |              |

|                      | ;      | vi <sup>10</sup> R |              |

|                      |        | 6 SB               |              |

|                      | 3      | а <sup>0</sup>     |              |

|                      |        | 0 40               |              |

|                      |        | 4 0                |              |

|                      |        | "<br>41            |              |

|                      |        | ( <del></del>      | TESTER GND   |

| ·                    | •      | 43                 | DTSTRBA      |

|                      |        | 44 <sup>1</sup> /4 | TESTER GND   |

|                      |        | 1                  | BINSTAB      |

|                      |        | , <u>7</u> ,       | TESTER GND   |

|                      | 4      | ·····              | WINT *       |

|                      |        | <u> </u>           | TESIFE CHID  |

|                      | ,<br>, | 50                 |              |

|                      |        | · · · · · ·        | _ TESTER END |

|                      |        |                    |              |

.

SPUBLINESTER PIN DESIGNATION FOR 50- PIN HIBBON CABLE CONNECTOR. (A)

٤

- 41 -

# 15.3. RAM Chips Tester Board

~