# Copyright © 1985, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# AUTOMATED SYNTHESIS OF MULTI-LEVEL COMBINATIONAL LOGIC IN CMOS TECHNOLOGY

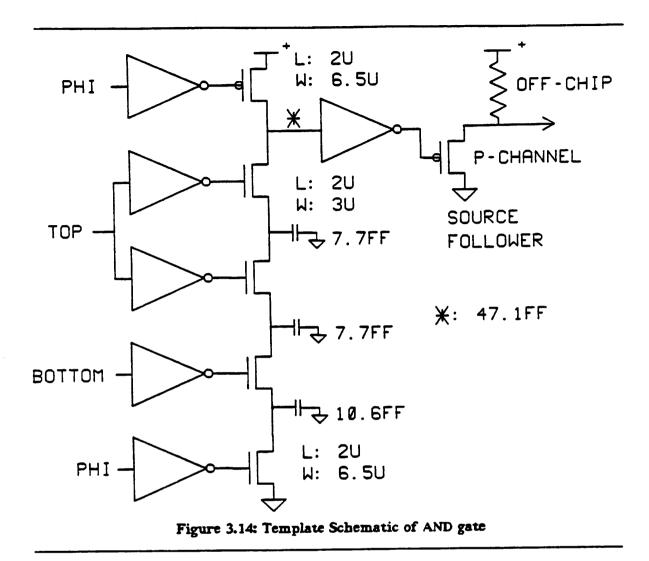

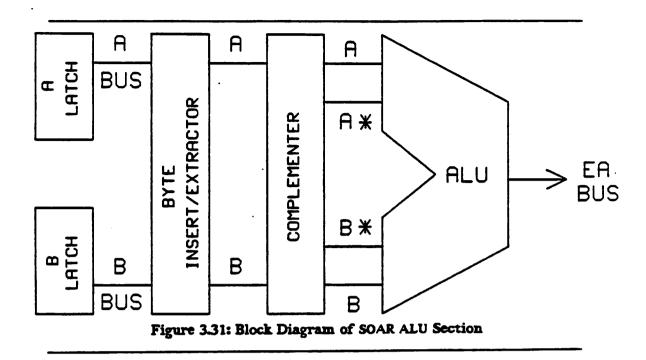

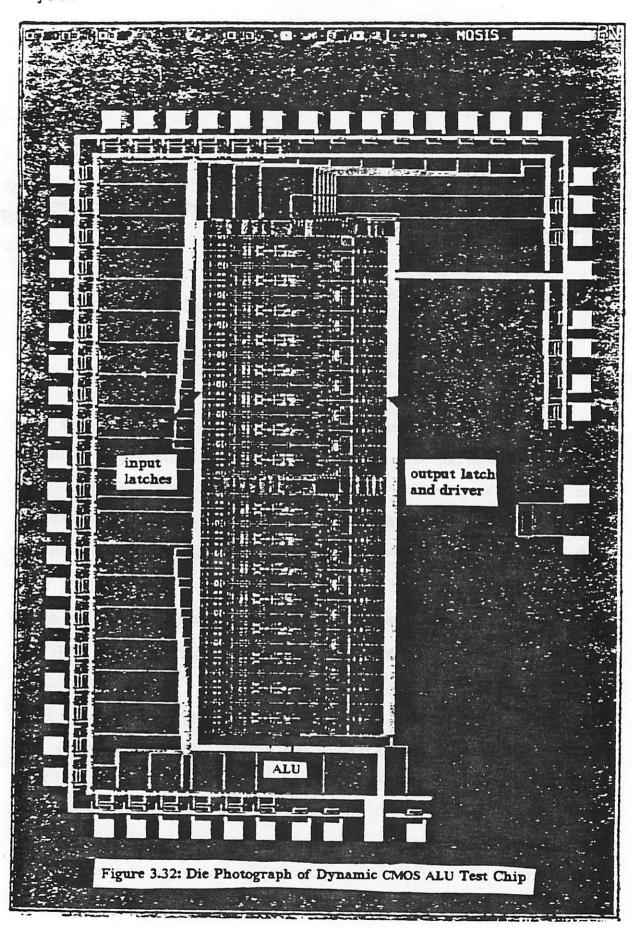

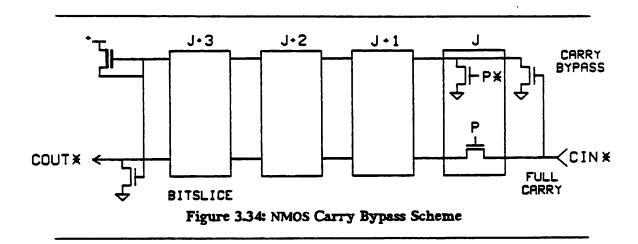

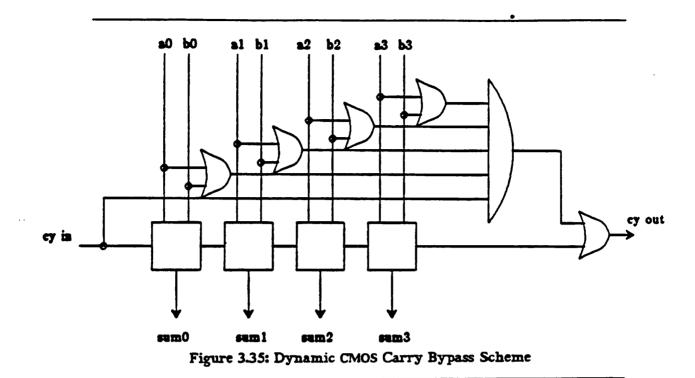

bу

M. E. Hofmann

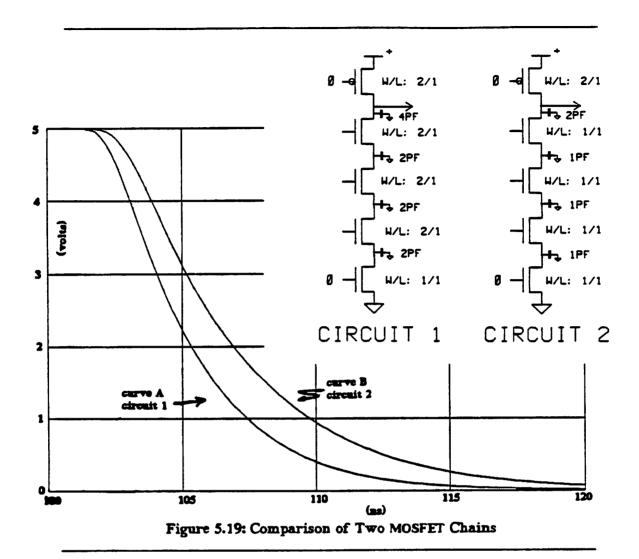

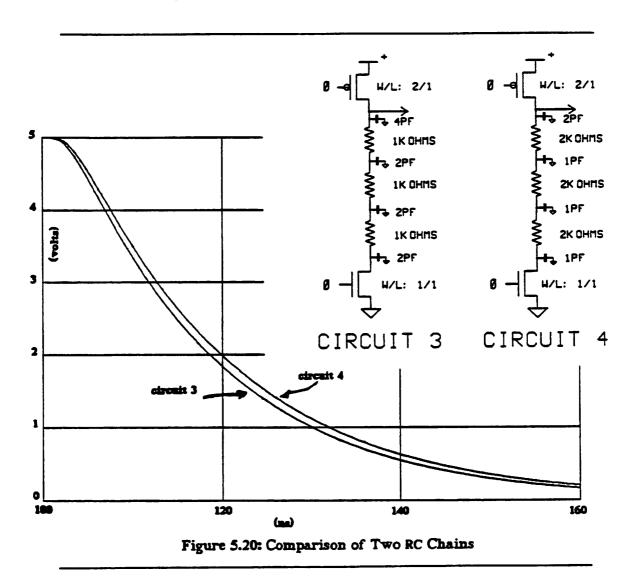

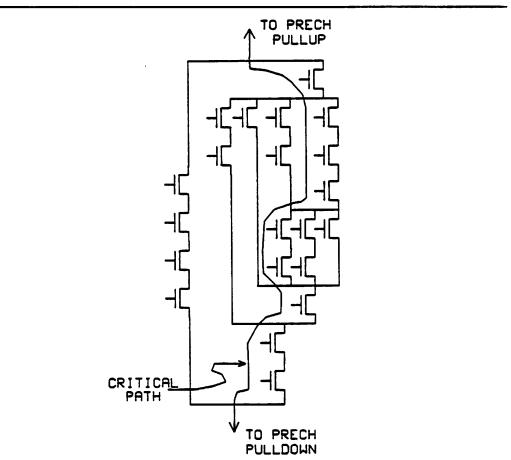

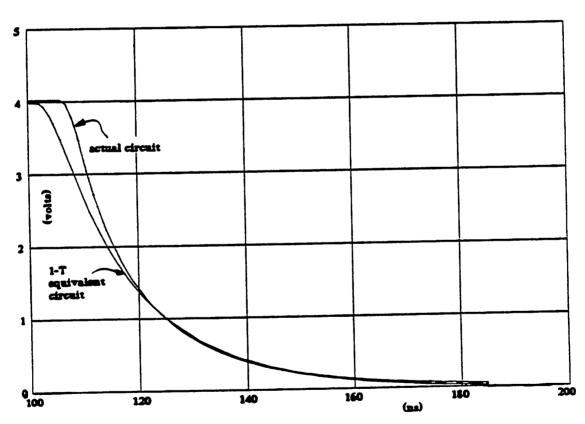

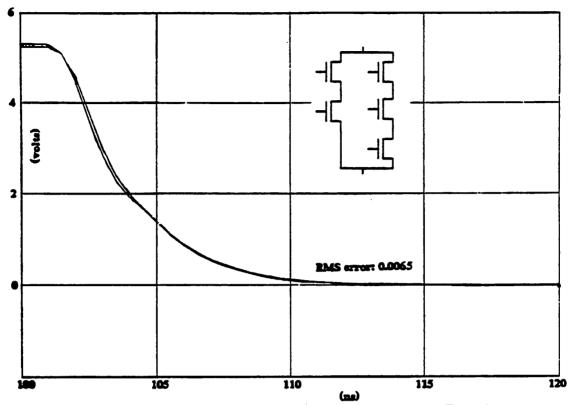

Memorandum No. UCB/ERL M85/53 1 July 1985

# AUTOMATED SYNTHESIS OF MULTI-LEVEL COMBINATIONAL LOGIC IN CMOS TECHNOLOGY

by

M. E. Hofmann

Memorandum No. UCB/ERL M85/53 1 July 1985

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

# AUTOMATED SYNTHESIS OF MULTI-LEVEL COMBINATIONAL LOGIC IN CMOS TECHNOLOGY

bу

M. E. Hofmann

Memorandum No. UCB/ERL M85/53 1 July 1985

**ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### ACKNOWLEDGMENTS

Professor Richard Newton, my research advisor, provided the inspiration for this work. I wish to acknowledge his contribution first.

Over the course of the research described in this thesis I have had the opportunity to work with and ask the help of many people. They are not too numerous to mention. I want to thank Rick Spickelmier, Tom Quarles, and Peter Moore for general advice, programming help, and those things which "only take five minutes".

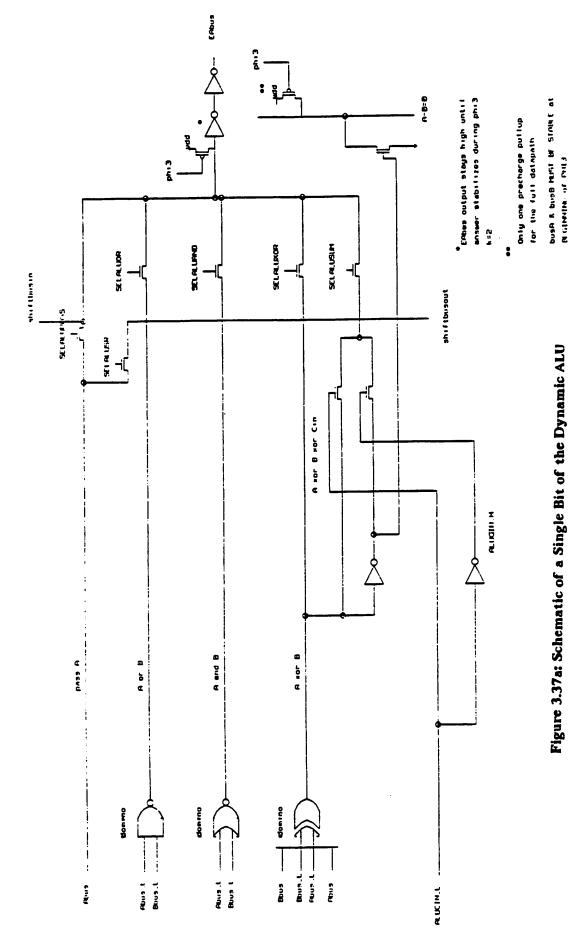

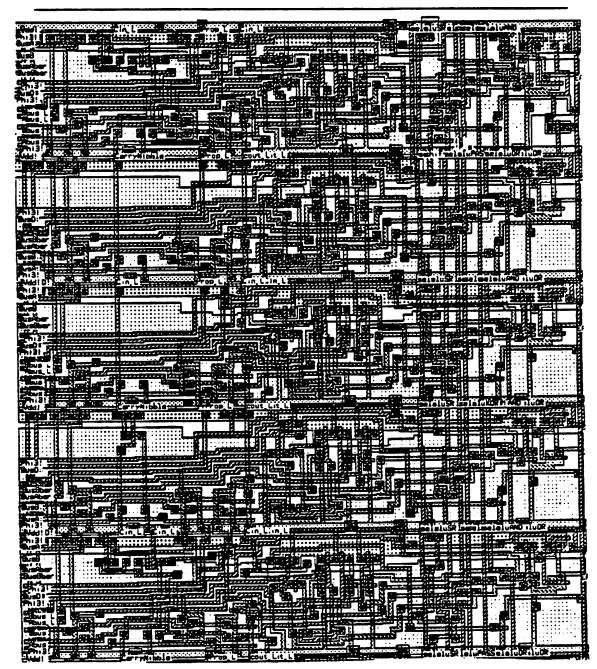

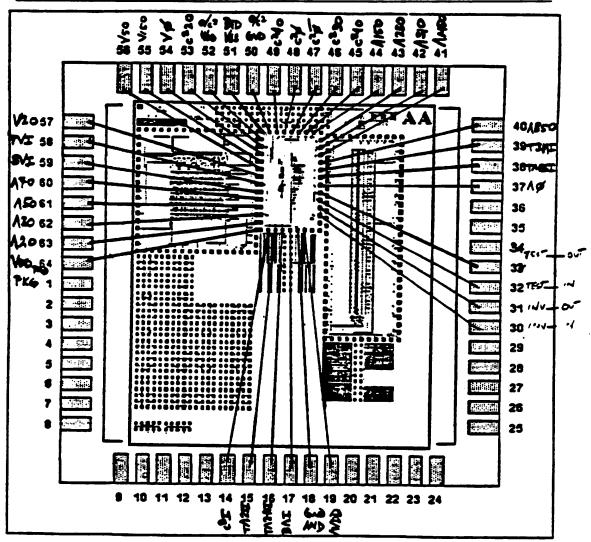

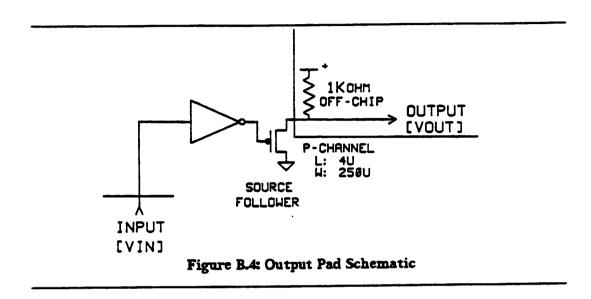

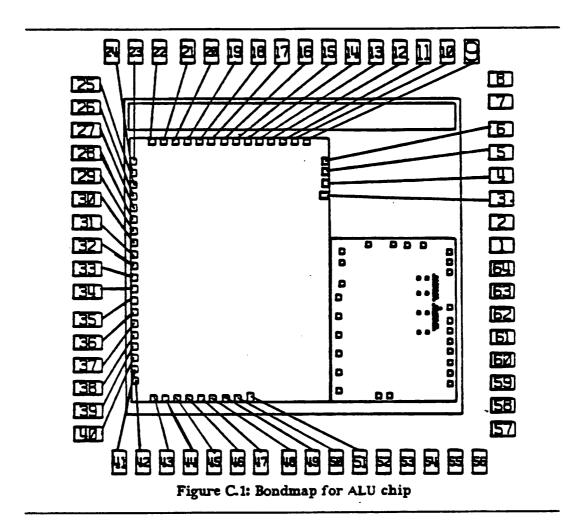

Several discussions with Professor Hugo DeMan provided useful insight into the design of NORA CMOS circuits. For work on specific problems I want to acknowledge several people: Peter Moore spent many hours on the ALU design and hacked the logiclevel simulator to handle CMOS gates. (I also thank Peter for his uncanny ability to prove mathematical theorems in the time it takes him to go from a seated position to the blackboard.) Richard Rudell contributed to my knowledge of Boolean minimization problems and quickly added new features to the ESPRESSO program that helped in the evaluation of various minimization strategies. Ron Gyurcsik wrote a program to do least-squares fits and one to aid in MOSFET threshold voltage calculations. Ron also helped in the formulation of the charge redistribution equations. In the design of the ALU chip I wish to thank Dave Wallace for design of the input latches. John Zapisek for design of the destination logic, and B.K. Bose for design of the input and output pads. Thanks to their diligence the chip worked on first silicon. On the dynamic CMOS test chip I want to thank Joan Pendleton for work on the DRC rules file and for the design of the input and output pads. Chuck Kring contributed many hours in lab helping me benchmark this chip and Kok Chang ran a multitude of SPICE2 simulations.

The dynamic CMOS test chip was fabricated at XEROX PARC. Ben Pugh and Bridget Scamporrino at XEROX provided wafer processing details and test parameters. Their assistance in chip fabrication is gratefully acknowledged. Partial funding by Tektronix. Inc..

Digital Equipment Corporation, and DARPA under grant N00039-83-C-0107 is also acknowledged.

I want to thank Jeff Burns in his editorial capacity for reading numerous drafts of this thesis. I would like to thank Jeff Burns, Ron Gyurcsik. Ken Keller, Grace Mah, Karti Mayaram. Tom Laidig, Deirdre Ryan, and Chris Marino for being regular guys. They are a credit to this universe and I think they are really swell. If it weren't for people like these life would be far less entertaining.

I want to thank my parents, Garda and Peter. They provided support and encouragement and gave me good advice when I wasn't in the most optimistic of moods. More than anyone else, they provided me with a reason and a goal for undertaking this project.

Finally. I would like to thank myself. I'm glad now that I stuck with it, though on the whole, if I had it to do over again, I think I'd rather move up to the Yukon and shoot moose. In finishing this work it seems only fitting and proper to quote the immortal philosopher and observer of goings-on. F. Flintstone: "Yabba-Dabba-DOO!"

# AUTOMATED SYNTHESIS OF MULTI-LEVEL COMBINATIONAL LOGIC IN CMOS TECHNOLOGY

#### Mark Eric Hofmann

Ph.D.

Department of Electrical Engineering and Computer Science

Sponsors: Tektronix. Inc.,

Digital Equipment Corporation

Richard Newton

Committee Chairman

#### **ABSTRACT**

A framework for the synthesis of combinational logic functions in a dynamic CMOS technology is presented. The input to the package of programs, which may be run as a pipeline, is a set of Boolean equations. The synthesis package generates mask-level geometries as output. Circuit optimizations for both speed and area have been developed. This approach compares favorably with other automated synthesis systems, such as PLA-based methods, in terms of circuit delay and layout area.

Different technologies and design styles for the implementation of combinational logic have been studied. Static and dynamic circuits have been characterized and extensively simulated. Two experimental chips were fabricated to further examine dynamic CMOS circuits. One of the test chips, a 32-bit ALU, is being used as part of a VLSI RISC microprocessor. The test measurements show that many dynamic circuits will have charge redistribution problems unless precautions are taken in design. Algorithms have been developed which partition complex circuits so that charge redistribution problems are avoided.

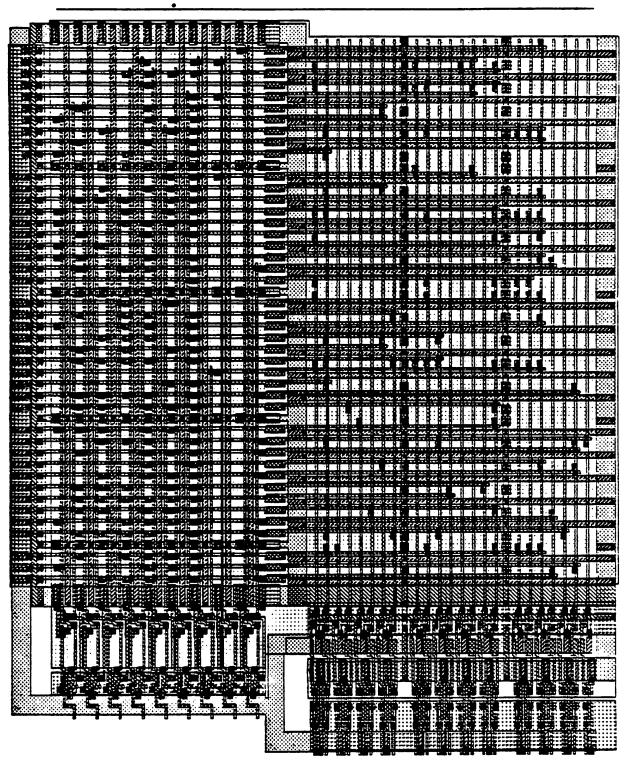

The regular structure generated by the pipeline is an extension of Weinberger arrays. The use of the *Domino* design style allows the construction of complex gates. Rather than perform a two level expansion on the Boolean equations, the framework maintains a multi-level expression hierarchy. This hierarchy is implemented in a multi-level matrix which can be topologically compacted. The algorithms for compaction presented in this dissertation allow simple-column and multiple-row folding with external constraints. The folded connectivity matrix is translated to the mask level by a context-based tiler. The tiler reads from a tile library and is process independent.

## Table of Contents

| Chapter 1: Introduction and Review of Previous Work                  | 1  |

|----------------------------------------------------------------------|----|

| 1.1 Need for Automation of Combinational Logic                       | 1  |

| 1.2 Goals of Current Research                                        | 2  |

| 1.3 Organization of this Dissertation                                | 3  |

| 1.4 Comparison with Previous Work                                    | 5  |

| 1.5 PLA Design                                                       | 15 |

| 1.6 Summary of Results                                               | 17 |

| Chapter 2: Comparison of Static and Dynamic CMOS Circuits            | 19 |

| 2.1 Design of Static CMOS Logic                                      | 19 |

| 2.2 Design of Dynamic CMOS Logic                                     | 23 |

| 2.3 Dynamic CMOS Design Using NORA                                   | 31 |

| 2.4 Special Design Considerations in Dynamic CMOS                    | 41 |

| 2.5 Conclusions                                                      | 46 |

| Chapter 3: Simulation and Measurement of Static and Dynamic Circuits | 47 |

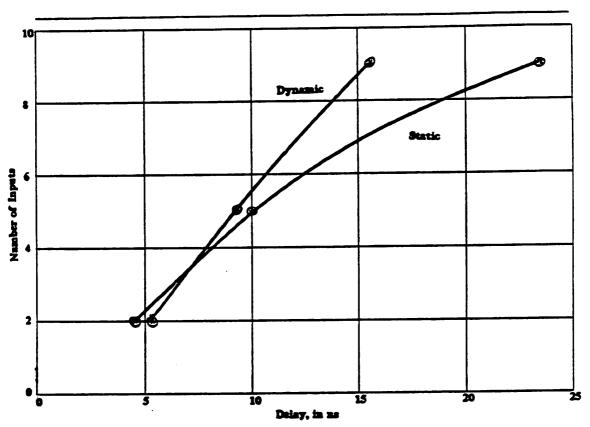

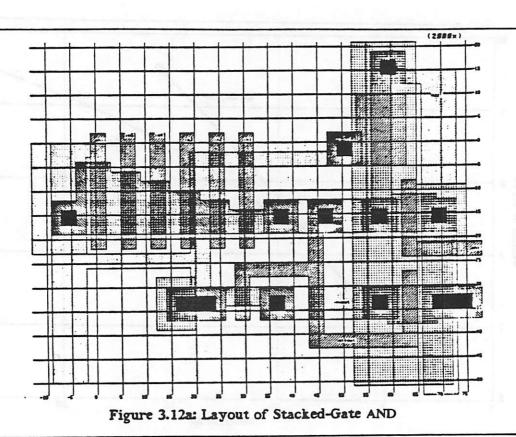

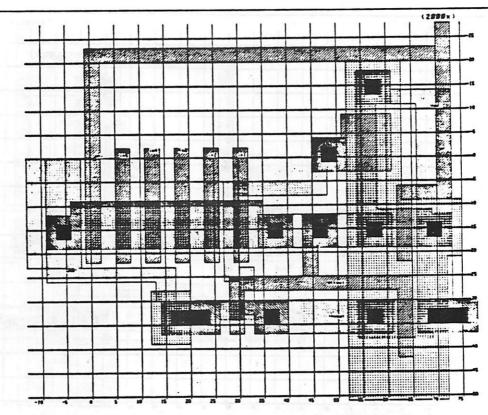

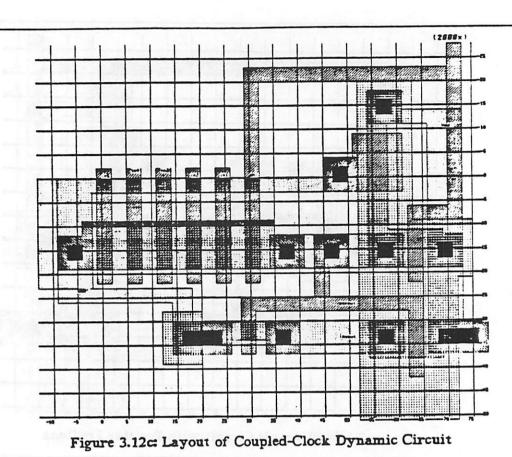

| 3.1 Range of Circuits Simulated                                      | 47 |

| 3.2 Rationale for Choice of Benchmark Circuit                        | 48 |

| 3.3 Simulation Technique                                             | 48 |

| 3.4 Standard Static CMOS Benchmark                                   | 49 |

| 3.5 Dynamic CMOS Benchmark                                           | 51 |

| 3.6 Simulation of Dynamic Circuits with Charge Redistribution        | 55 |

| 3.7 Comparison of Optimized Dynamic Circuits                         | 59 |

| 3.8 Delay and Charge Redistribution Measurements from a Test Chip | 63             |

|-------------------------------------------------------------------|----------------|

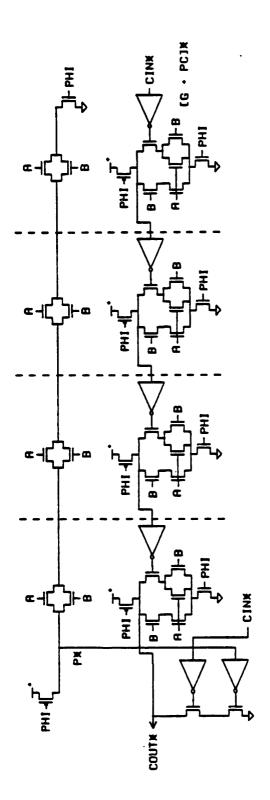

| 3.9 Measurements of a 32-bit Dynamic Domino ALU                   | 80             |

| 3.10 Summary                                                      | 98             |

| Chapter 4: The MAMBO Synthesis Package                            | <b>9</b> 9     |

| 4.1 Overview of the MAMBO Pipeline                                | <del>9</del> 9 |

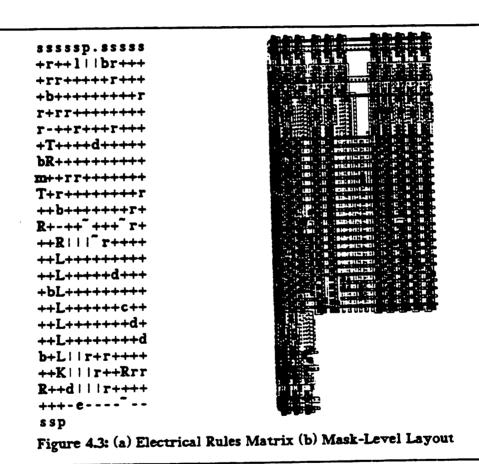

| 4.2 Representation of Boolean Expressions— MGMG                   | 105            |

| 4.3 Transformation into Target Technology— MGMG                   | 109            |

| 4.4 Alternate Transformation into Target Technology               | 116            |

| 4.5 Summary                                                       | 116            |

| Chapter 5: Delay Optimization and Partitioning of Dynamic Meshes  | 118            |

| 5.1 Partitioning of Transformed Gates— MOSMESH                    | 118            |

| 5.2 The Charge Sharing Criterion in MOSMESH                       | 119            |

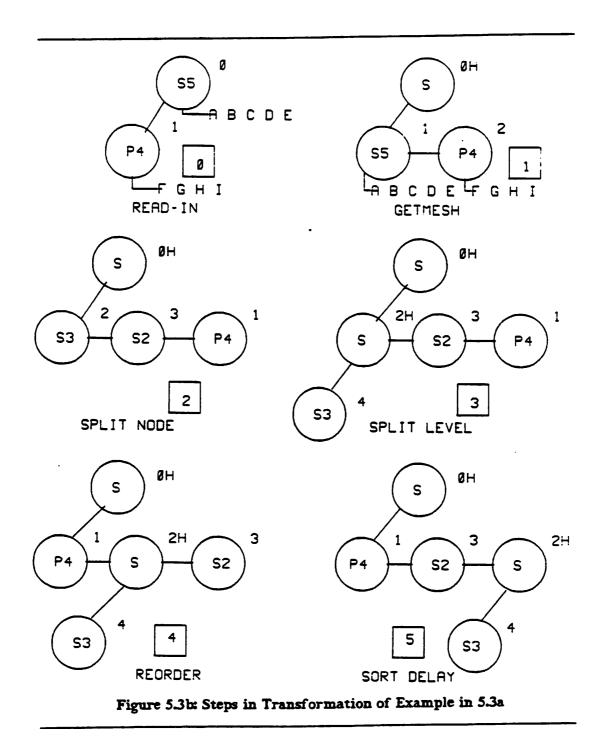

| 5.3 Data Structure for Gate Partitioning                          | 119            |

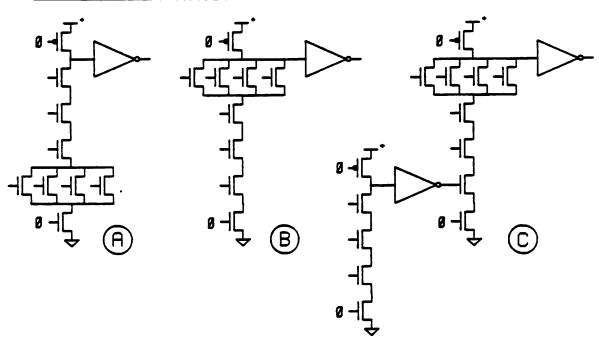

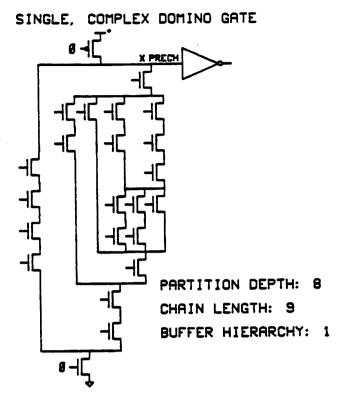

| 5.4 The Partitioning Algorithm                                    | 123            |

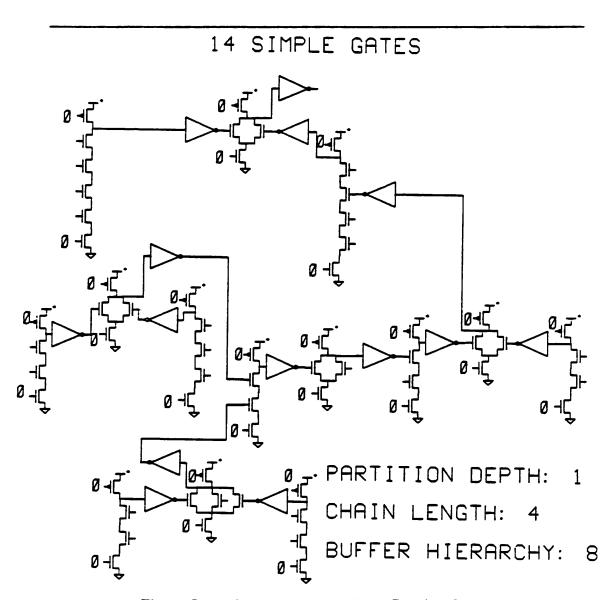

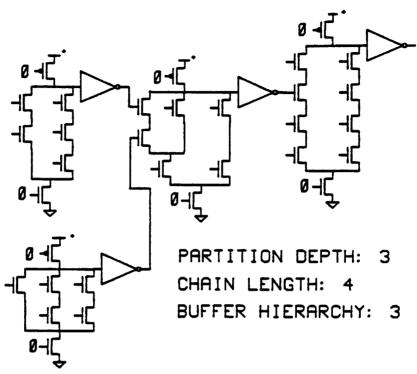

| 5.5 An Example of MOSMESH Partitioning                            | 132            |

| 5.6 Calculation of Signal Delay in a Partitioned Mesh—MKTBL       | 142            |

| 5.7 A Simple MOS Model for an Arbitrary Mesh                      | 146            |

| 5.8 Elimination of Redundant Clusters— MIMIC                      | 161            |

| 5.9 Summary                                                       | 167            |

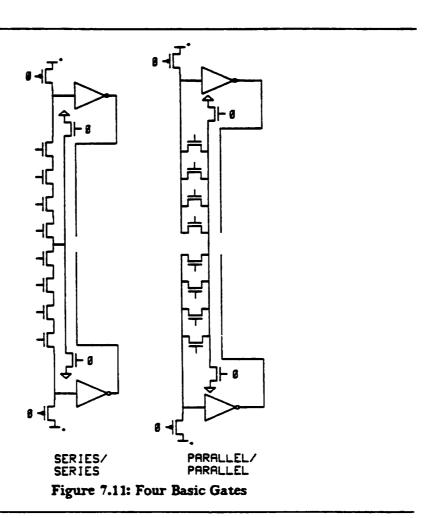

| Chapter 6: Compaction and Layout of Domino Matrix Structures      | 168            |

| 6.1 Conversion of Partitioned Circuit to Matrix Structure— MKMAT  | 168            |

| 6.2 Algorithms for Topological Compaction— TWIST                  | 179            |

| 6.3 Examples of Row and Column Folding                            | 196            |

| 6.4 Summary                                                       | 204            |

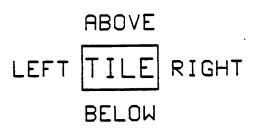

| Chapter 7: Physical Design: Comparison of Layout Tiling Methods | 205 |

|-----------------------------------------------------------------|-----|

| 7.1 Distinction Between Routed and Tiled Methods                | 205 |

| 7.2 Tiled Methods                                               | 207 |

| 7.3 A Structure for the Layout of Complex Domino Cells          | 213 |

| 7.4 Context-Based Tiling— TINKER                                | 215 |

| 7.5 Mask-Level Layout Generation— TAILOR                        | 221 |

| 7.6 Summary                                                     | 229 |

| Chapter 8: Comparison of Synthesis Methods                      | 230 |

| 8.1 Comparison Criteria for Multi-Level Matrices and PLAs       | 230 |

| 8.2 Area Versus Speed Tradeoff in MAMBO                         | 232 |

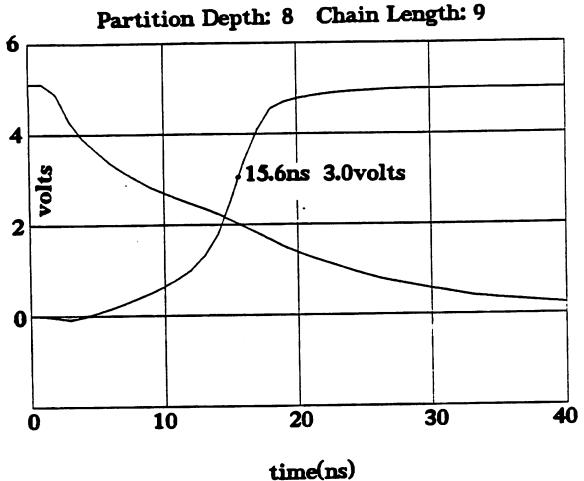

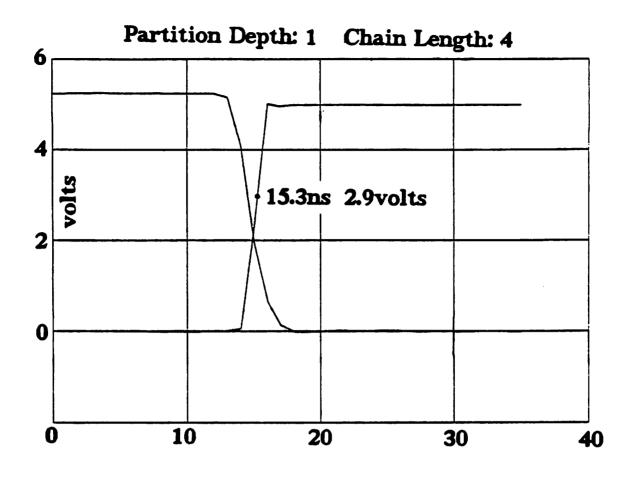

| 8.3 Effect of Series Chain Length on Circuit Speed              | 235 |

| 8.4 Effect of ON-set Versus Literal Count Minimization          | 235 |

| 8.5 Summary                                                     | 237 |

| Chapter 9: Conclusions and Further Work                         | 238 |

| Appendix A: SPICE2 MOS Models                                   | 243 |

| Appendix B: Measurement of the Dynamic CMOS Test Chip           | 245 |

| Appendix C: Evaluation of a 32-bit Dynamic CMOS ALU             | 254 |

| Appendix D: MAMBO Source Listing                                | 268 |

| References                                                      | 269 |

#### CHAPTER 1

#### Introduction and Review of Previous Work

Much of the circuitry in a VLSI design may be cast in a regular, or array-based, form and thus may be generated automatically. However, blocks of complex combinational logic often require hand layout because they are not structured; the time spent on this portion of the design is often the most significant part of the project [latt81]. The aim of the work presented in this dissertation was to explore methods of automating the design of complex logic functions. In addition to reducing the time between circuit conception and circuit fabrication, automated methods of circuit design and layout decrease the possibility of design error, ease the overhead of circuit modification and often lead to efficient testing strategies.

### 1.1. Need for Automation of Combinational Logic

A typical VLSI chip is comprised of a relatively small number of different sections. In almost any VLSI design there will be sections of RAM and ROM. There will likely be a processing section, for example an ALU in a microprocessor architecture. In addition, signal buffering, conditioning circuitry, and control logic are required. In general, a processor may be divided into two broad sections: control and datapath. The control section consists of complex combinational logic and a small amount of storage circuitry. The datapath section includes ROM, RAM, an ALU, and intermediate storage latches. Even in a highly structured chip design, such as the reduced instruction set CMOS SOAR processor [patt81], over 30% of the chip area was used explicitly for control purposes [mari85]. On the other hand the combinational part of the control logic contributes only 10% of the total device count. The disparity in these figures reflects the patently irregular nature of combinational logic.

\*\*Irregular\*\* in this sense means that the pieces of combinational logic do not fit together well.

and a substantial amount of routing is required to connect them.

So-called random or arbitrary combinational logic used in a custom design has a replication factor close to one. Replication factor is defined as the number of times the same cell is used or placed in the design. The replication factor of the datapath is typically skewed by on-chip ROM or RAM. For SOAR the RAM replication factor is over 2300. SOAR is a 32-bit bitslice machine, and therefore, even excluding RAM, the replication factor is over 32 since storage latches and buffers are used several times in each bitslice. For the control logic of the SOAR chip common latch, buffer, and inverter library cells were used wherever possible. Still, almost all of the control logic is implemented using 14 PLAs. Even though this logic may make up only a small part of the total device count, it represents a significant amount of chip area and often the majority of distinct, designed cells. A major portion of the design time is expended in layout of this logic.

#### 1.2. Goals of Current Research

The goal of this research was to create a framework to study the automatic generation, optimization, and layout of arbitrary, multi-level combinational logic. As explained in Section 1.4, the input to the package presented in this dissertation is an optimized, multi-level combinational logic description. The logic function may have been hand-optimized or optimized automatically [bray84b] [rude85] for logic compactness. The goal of the work described here is to optimize the function for both speed and area, taking into account electrical considerations. Since the process-critical parts of the package read from technology files, changes in processing parameters, within the given design style and technology, can be easily accounted for. The actual layout generation is performed by a design-rule-independent tiling program which means that the program does not have to be modified as design rules change.

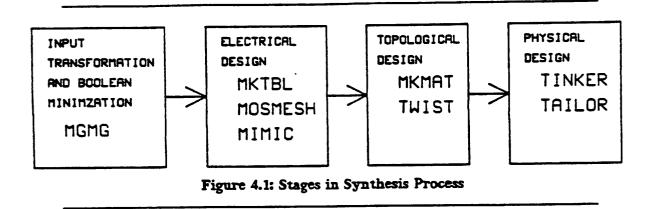

The synthesis framework has been implemented as a pipeline of CAD programs that allows a circuit designer to specify combinational logic at a high level and produce an efficient circuit realization at the mask level. A pipeline of programs is a set of programs

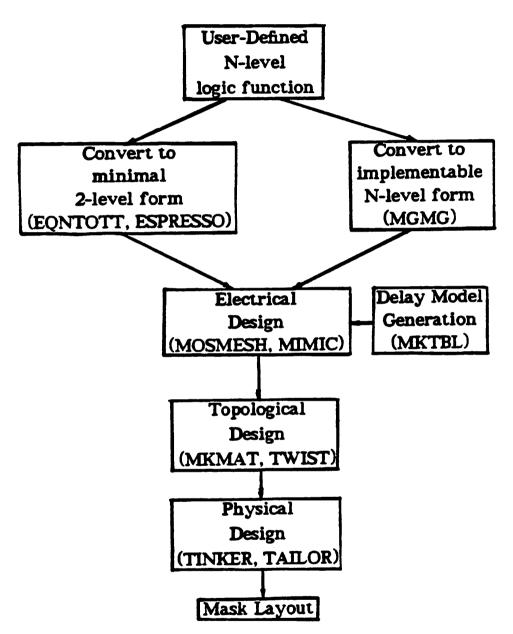

that may be used either separately or as a package. If used as a complete package, the output of one program drives the next without need for user intervention. A program or package of programs that generates a particular type of cell automatically is called a module generator [newt81]. In Figure 1.1 the stages in the implemented pipeline, known as MAMBO, are shown. The names of the associated tools in the pipeline are given in parentheses.

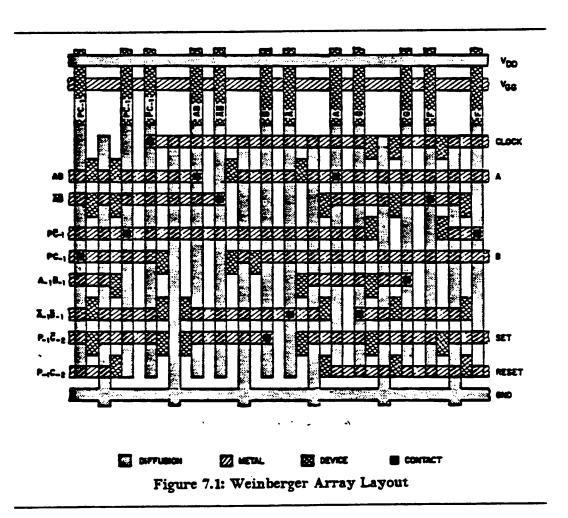

In the pipeline implementation a technology, electrical design style, and layout method must be chosen. Large-scale digital designs are typically implemented in a MOS technology because of its superior packing density. For this project the CMOS technology has been chosen because it is possible to design low power, dense circuits in CMOS. The choice of design style is an implementation-level decision. The relevant design parameters are the speed of a basic gate, area consumption, and ease of automated layout, topological optimization, and Boolean minimization. After extensive simulation, a mixed static and dynamic, clocked design style was chosen. The term layout method applies to the geometric level of design. The layout method used in this project is a generalization of Weinberger arrays. It has the advantage of guaranteeing a regular, structured layout.

#### 1.3. Organization of this Dissertation

This dissertation has nine chapters. The remainder of the introduction provides a review of previous work in the area of automated synthesis of combinational logic modules. Contrasts between static and dynamic CMOS design styles are drawn in Chapter 2. The advantages and deficiencies of each style, along with their best application areas, are described. Detailed results of simulations of static and dynamic circuits in a specific CMOS process are presented in Chapter 3. Results from a test chip constructed to examine problems with dynamic circuits are also described. Chapter 3 concludes with results from a 32-bit ALU test chip designed in the Domino style. In Chapter 4 an overview of the stages in the MAMBO synthesis system is presented. The objective and constraints at each synthesis step are stated and the initial parsing and logic optimization phases are described

# MAMBO Pipeline

Figure 1.1: Stages in the MAMBO Automated Logic Synthesis System

in detail. In Chapter 5 the tradeoffs involved in partitioning large, dynamic, combinational circuits are explained. Circuits may be partitioned according to several criteria to result in reduced delay and greater ease of layout. In Chapter 6 algorithms for the area

optimization of matrix structures are explored. The current structure is contrasted with previous work on folded, tiled PLA structures. Chapter 7 contains an overview of layout tiling methods and a comparison between tiled and routed methods. The separation of electrical and geometrical rules is examined. A comparison of layouts and delays of several PLAs from the SOAR chip with multi-level dynamic implementations is presented in Chapter 8. Conclusions and directions for further work are presented in Chapter 9.

#### 1.4. Comparison with Previous Work

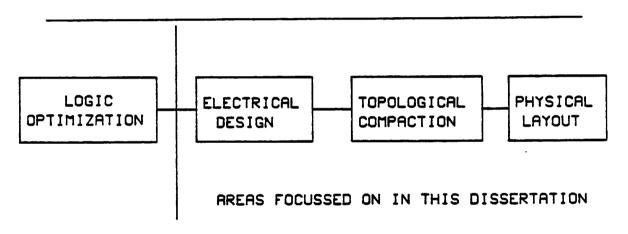

The combinational logic synthesis problem can be broken up into four parts as shown in Figure 1.2.

Figure 1.2: The Four Steps in Logic Synthesis

The first step, logic optimization, is a multi-faceted problem. The goal of logic optimization is to reduce circuit complexity in some manner so that the optimized circuit requires less chip area. The front-end program in the MAMBO pipeline, MGMG, will perform simple logic optimization if requested, however it is assumed that the logic expressions input to the MAMBO package are already in a logically optimized form. Two methods of logic optimization are reviewed here. The first method reduces circuit complexity by partitioning the function. The methods of functional and hierarchical partitioning are described. The second method is logic optimization by multi-level Boolean minimization.

#### 1.4.1. Logic Optimization by Circuit Partitioning

A circuit may be partitioned according to the function it performs. That is, if the designer knows something in particular about the function he wishes to implement he may be able to use this to advantage in circuit generation. An example circuit where such techniques are useful is the exclusive-or (XOR) function. In an n-input XOR the function has the value 1 if and only if an odd number of inputs are 1. The following example is taken from [flei75]. A calculation is carried out on the number of bits it would take to represent an XOR function on 16 inputs, using different decoding schemes. For the case of one decoder with 16 inputs the XOR maps into a single column with  $2^{16}$  bits. This represents the completely decoded case, where each bit (a 1 or a 0) indicates the function output. This could be mapped into a single circuit. The other extreme is to employ 16 1-bit decoders. Each decoder produces two outputs, the input variable and its inversion. Now there are just two possible cases per decoder times 16 decoders or  $2^1 \times 2^4 = 2^5 = 32$  bits per column. However  $2^{15}$  columns are required, since there are  $2^{15}$  ways of representing two variables across 16 inputs. This case, which could be implemented by partitioning a single PLA into 16 smaller arrays, is clearly the worst case.

There are intermediate solutions and these are tabulated in Figure 1.3.

| Number      |             |                      |

|-------------|-------------|----------------------|

| of decoders | per decoder | number of bits       |

| 1           | 16          | $2^{16} = 65.536$    |

| 2           | 8           | $2^{10} = 1024$      |

| 4           | 4           | $2^9 = 512$          |

| 8           | 2           | $2^{12} = 4096$      |

| 16          | 1           | $2^{20} = 1.048.576$ |

Figure 1.3: Total number of bits to implement XOR

The best case turns out to be four 4-input decoders. This situation could be realized by four small PLA circuits. In this example, the output of each decoder produces  $2^4 = 16$  lines. Since four decoders are used this is a total of  $4 \times 2^4$  or 64 bits per column. Since each decoder deals with only four inputs there are just  $2^3$  minterms per PLA. Thus the total bit count across all columns of all PLAs is just  $4 \times 2^4 \times 2^3$  or 512 bits overall.

In this presentation the routing between the component circuits has been neglected.

This can represent a significant portion of the circuit area. An example circuit which illustrates the interconnection routing problem is presented at the end of this section.

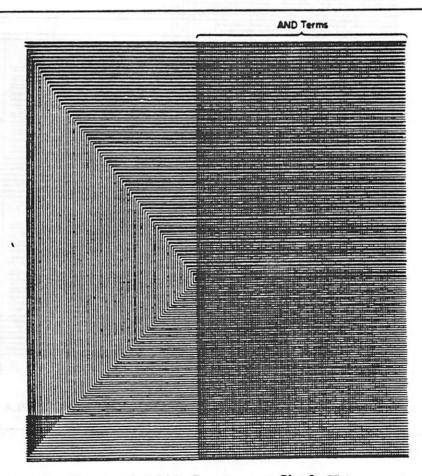

Another partitioning method to reduce total cell area is to implement a hierarchy of cells. This approach does best when the functions are complex and heavily interdependent. This method is similar in effect to the approach employed by the current work, where a multi-level form of the input Boolean expressions is retained. The following example is taken from [ayre79]. Here the designer wishes to implement a 16-bit counter. It can be implemented as single circuit in two-level logic. A schematic representation of a single PLA implementation is shown in Figure 1.4. PLA area is 32,000 units.

Figure 1.4: 16-bit Counter as a Single PLA

However, by introducing additional logic stages, so that the circuit is now AND-OR-AND-OR, the overall area of the counter can be reduced. The total area for the two-deep implementation is 11,500 units.

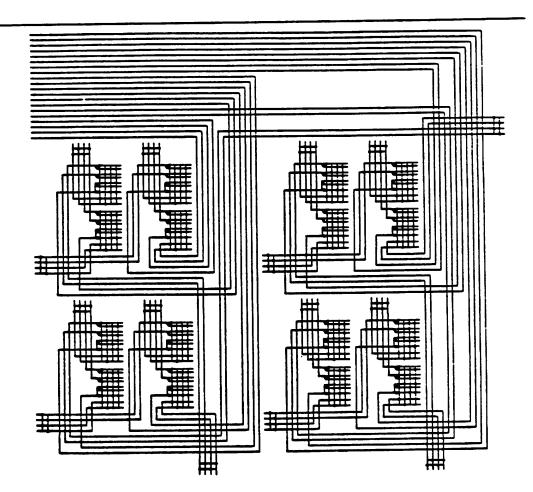

The decomposition can be continued until the minimum branching factor of two is reached. In this case, if each bit of the 16-bit counter is handled by a single PLA, a five-level representation can be obtained. A schematic representation of such an implementation is presented in Figure 1.5. Total area of the circuit is 7,000 units.

Figure 1.5: 16-bit Counter as Five Levels of PLA

Because total cell area has been reduced significantly, the speed of the counter, although not reported, would increase, other factors remaining equal. It is not clear from [ayre79] whether or not the additional routing area for the PLA interconnections was taken

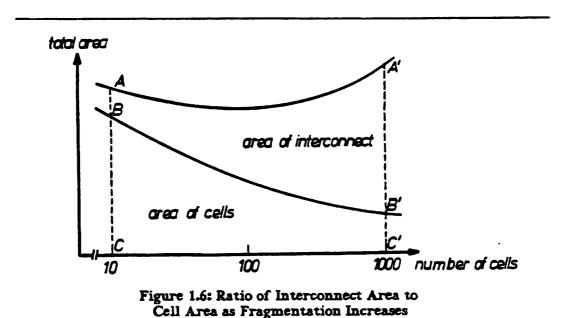

into account. It would appear from the diagrams that routing area has been factored into the area calculation. In general, as circuit function is broken up into more and more levels of logic, the ratio of routing area to cell area increases. The total area may, in fact, increase in absolute terms. The amount of space dedicated to routing in the last two examples appears significantly greater than the amount of space occupied by the PLA module area. The curve shown in Figure 1.6, from [sans81], shows that as the area of individual cells, for example PLAs, decreases in size and complexity proportionally more area is taken up by interconnect.

### 1.4.1.1. Example Interconnection Problem in Partitioning

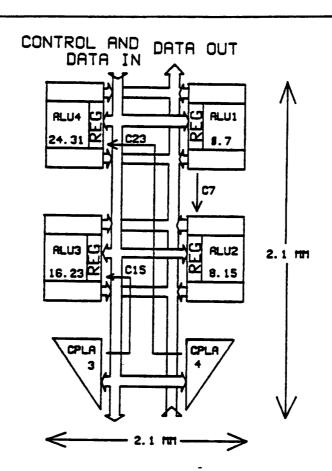

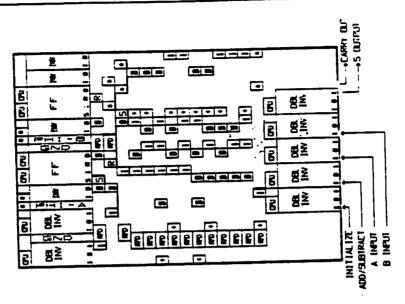

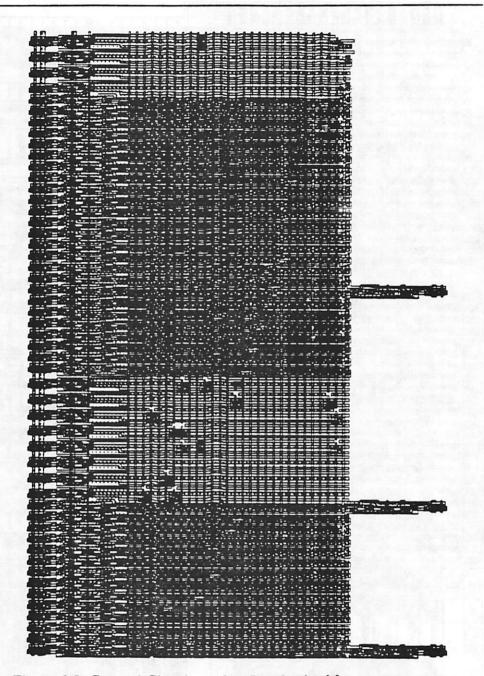

When a larger block is partitioned by either of the two methods just presented interblock routing becomes an issue. Layout schemes which route by block abutment, therefore, can result in a substantial area savings. A partitioned 32-bit ALU implemented as six PLAs has been compared with a bitslice approach [sout82]. Four 8-bit PLAs, based on the highly optimized, compact design presented in [schm80] form the core of the NMOS

In the extreme, total chip area may increase even though there are fewer device placements.

design. Two other carry-lookahead PLAs are employed for speed. The floorplan of the .

32-bit ALU-PLA layout is shown in Figure 1.7.

Figure 1.7: Floorplan of Partitioned ALU-PLA

The bitslice approach was based on a single cell per bit design. Carry generation was accomplished by a Manchester-type carry chain which is able to bypass 4-bit sections of the ALU for fast carry propagation.

Both designs were fabricated in a single layer metal, polysilicide process. A comparison of the two designs is shown in Figure 1.8.

| Attribute        | PLA                | Bitslice    |

|------------------|--------------------|-------------|

| Worst-case Speed | 22ns               | 35ns        |

| Power            | 200mW              | 125mW       |

| Total Area       | 4.2mm <sup>2</sup> | $1.0mm^{2}$ |

| Routing Area     | 1.8mm <sup>2</sup> | -           |

Figure 1.8: Comparison of PLA and Bitslice Techniques

A significant portion of the PLA design. 1.8mm<sup>2</sup>, or 43%, is taken up in routing area. This is because it is very difficult, if not impossible, to generate partitioned PLAs that route by abutment. Presumably the bitslice design takes up less space not only because the slices connect by abutment, but also because they are more regular in structure. The speed advantage of the PLA is due largely to the full carry-lookahead: the tiling approach itself does not compromise circuit speed. The comparison indicates that a layout scheme which routes by abutment gives a more compact result. This result is especially important in multi-level circuits where the amount of intercell routing is large.

#### 1.4.2. Logic Optimization by Boolean Minimization

Rather than apply special knowledge about a circuit to minimize its area. direct multi-level Boolean minimization can be employed to reduce device count and hence circuit area. Several algorithms have been published [bray82] [risc82] [bray84b] which deal with fast, heuristic methods for both decomposition and factorization of Boolean expressions. Decomposition is a technique for discovering common subexpressions in a system of (two or more) Boolean expressions. Factorization is a similar technique, used to rearrange a single expression. Brayton and McMullen [bray82] outline an algorithm which simplifies a set of functions until they are "relatively prime" by successive substitution of new variables for common subexpressions.

Before examining the process of decomposition, it is useful to define some terms. Two expressions are said to be relatively kernel free if they have no kernels in common. A kernel of an expression is a cube free primary divisor. A cube is a set c of literals such that if Boolean variable x is an element of c,  $\bar{x}$  is not in c. A literal is a Boolean variable

or its negation. An expression is said to be cube free if the only cube evenly dividing the expression is 1. Function g divides function f evenly if (f/g)g = f. The product and division operators are defined for f orthogonal to g. Functions f and g are said to be orthogonal if none of the literals of f are in g. The primary divisors of an expression f are those cubes g which divide g, i.e. g and g are example. If g is a primary divisor of g divides g and g are for g and g are those sample and g are g are g and g are g are g and g are g and g are g are g and g are g and g are g are g and g are g and g are g are g and g are g are g are g and g are g are g and g are g are g are g and g are g are g are g are g and g are g are g and g are g are g are g are g are g are g and g are g and g are g

Decomposition is applicable to sets of Boolean expressions, while factorization applies to single functions. It is the decomposition methods that are useful for matrix optimization. Decomposition is a two step process. First, common subexpressions, consisting of two or more cubes, are extracted from of a set of functions until the expressions are relatively kernel free. At this point expressions can, at most, share a single cube. In the second step, these are located and extracted also. The result is that the only common divisors are single literals; all global commonality has been discovered.

Brayton and McMullen call the first step distillation and the second step condensation. Both steps involve simplification of an expression by extracting a common subexpression; each step is repeated until no common subexpression can be found among any pair of expressions.

Both steps require a selection heuristic. In distillation the object is to find a pair of kernels K, K' such that at least 2 cubes are common, for K, K' not in the same function. In the condense algorithm a pair of cubes c, c' must be found such that at least 2 literals are common, for c, c' not in the same function. The effectiveness of these steps depends on the selection heuristic. Rather than search for all kernels, one can define the *level* for a kernel and then restrict the search to all kernels at a given level. The level of a kernel is recursively defined. Level 0 kernels are all kernels in which no literal appears twice. Kernels  $K^{n+1}(f)$  are those kernels, not including f itself, which are kernels of  $K^n(f)$ . By this definition the complete kernel set, K(f), is the union of all levels n of  $K^n(f)$ .

The table in Figure 1.9, from [bray82], shows an example of 0- and 1-level partial kernel decomposition.

| Decomposition<br>Level | Transistor<br>Count |

|------------------------|---------------------|

| None                   | 2750                |

| 0-Level                | 1928                |

| 1-Level                | 1786                |

Figure 1.9: Example of Boolean Decomposition

Partial decomposition is supplemented by an additional collapsing step after the condensation algorithm. This extra step is useful because some kernel terms may not have multiple instances, in other words they appear only once in the set of Boolean functions. In this case back substitution into the kernel list allows the discovery of complex subexpressions and reduces the number of separate subexpressions. As a practical consideration the complement of the extracted kernel is also computed: it may form part of the subexpression as well.

The result of using the above approach is a smaller number of gates and perhaps a decrease in the total number of Boolean variables. Gate reduction comes from elimination of duplicate function implementation. The number of Boolean variables in a set of logic expressions is the sum of input, output, and intermediate variables. The number of input and output variables remains fixed. The number of intermediate variables will be reduced if it is possible to collapse subexpressions. The logic-optimized circuit is thus both smaller and denser than the original circuit.

#### 1.4.3. Implementation of Logic-Optimized Circuits

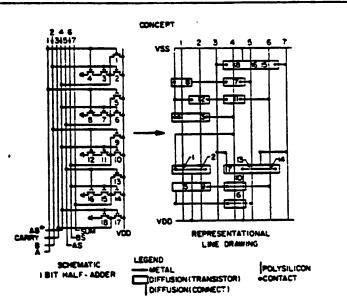

After logic optimization, the combinational circuit proceeds through the stages of electrical, topological and physical design— the topics of this dissertation. Combinational logic may be realized in many different ways. The structured forms of layout include Weinberger arrays [wein67], storage/logic arrays or SLAs [pati79], and gate matrices [lope81]. These methods are termed tiled methods because connection between cells is by

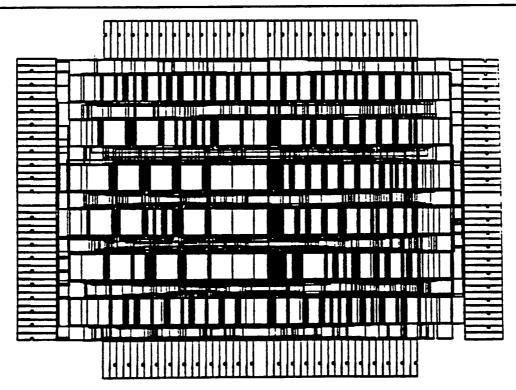

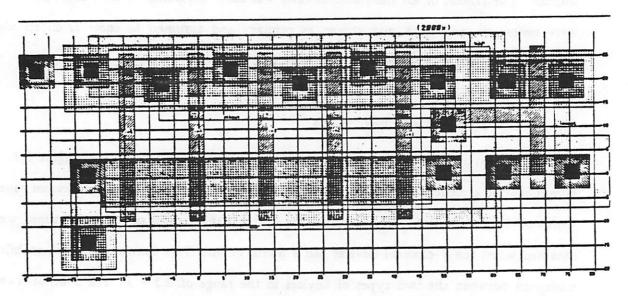

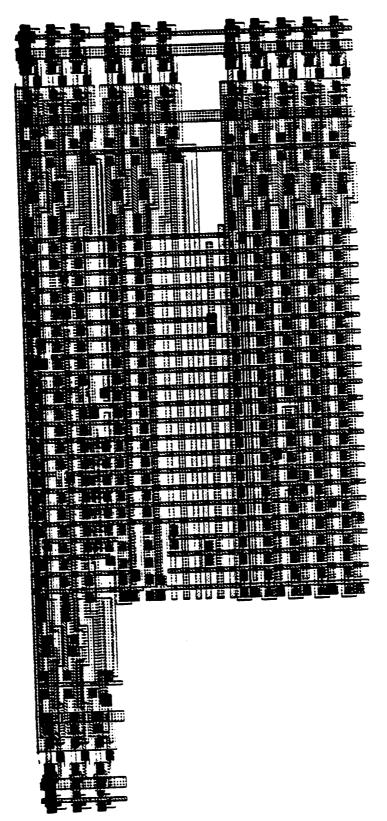

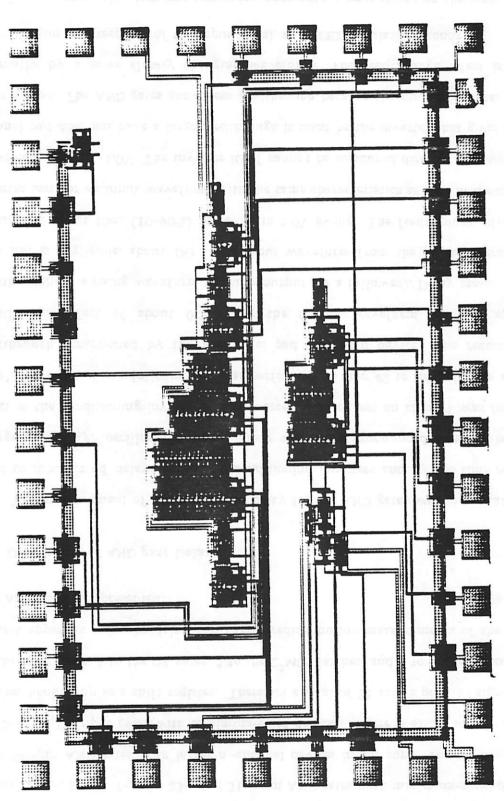

abutment, just like tiling a floor. In comparison, there are routed schemes where interconnection between blocks of logic is performed by a router. Hand layout or the layout of partitioned PLAs are examples of routed approaches. Another common technique for implementing combinational logic is the "standard cell" approach. [souk81]. In a standard cell system simple functions are performed by each of many different cells. The cell collection makes up a library. Each cell in the library has the same height but a variable width. The height constraint allows for the construction of rectangular routing channels to interconnect cells. The cells are selected from the library on the basis of their function and are placed in rows, perhaps by an automated placement program, based on the number and position of their inputs and outputs. The cells are then routed automatically. A typical standard cell layout is shown in Figure 1.10 [dunl83].

Figure 1.10: Automated Standard Cell Layout

<sup>&</sup>lt;sup>1</sup>Recently standard cell systems have been developed which permit both variable height and variable width cells.

Other tools that work from high-level circuit descriptions are the MACPITTS program [sout83] and work on silicon compilation at IBM [bray84a]. The MACPITTS program generates Weinberger arrays for the control structures and is an example of a tiled method. The IBM approach is based on a form of Dynamic CMOS logic known as differential cascode voltage switched logic (DCVS). In this routed method, compact function cells are constructed and an automated program performs the cell interconnection.

#### 1.5. PLA Design

The most successful structured approach to date is based on a two-level circuit representation. It is possible to represent any combinational circuit in two-level form (i.e. product-of-sums, sum-of-products) [nag175]. The classical implementation of such a representation is the *Programmable Logic Array* or (*PLA*) [carr72]. Because research into PLA generation and optimization is well advanced it is reviewed in detail here. PLAs are often the approach of choice for combinational logic design because they are easy to machine generate and, for small circuits, give good speed due to their two-level nature. In practice, however, PLAs which implement functions of many input and output variables (e.g., 20 to 100) tend to be slow. This is a direct result of their large size. Such PLAs are large because they provide the possibility for every input term, or its complement, to take part in every product term and, therefore, to influence every output. These PLAs often have a correspondingly large number of product terms which adds to the worst-case circuit delay. Large PLAs have high source capacitances on product term lines. Unless special precautions are taken, there will also be large IR drops on input and output signal paths [mah84].

#### 1.5.1. PLA Compaction by Folding

Not long after the first PLA generation programs were introduced [glas80] [hofm80] [land82] it was recognized that PLA density could be increased by topologically rearranging the input and output blocks or *planes* of the PLA. Functionally the PLA remains

unchanged, however some of the unused placement sites have been discarded. This topological rearrangement is called *folding*. Folding compacts the PLA by taking advantage of the fact that though all inputs may contribute to a given product term, and all product terms may contribute to a given output, it is very rare that such fully connected terms exist. Therefore, in what is known as *simple* folding two inputs can share the space formerly occupied by a single input. This can be done likewise for output and product terms. In *multiple* folding more than two input, output, or product terms are collapsed into the space of a single term.

Early work on PLA folding theory and implementation was carried out by [hach82] and by [hofm80]. In [luby82] the optimal PLA folding problem was shown to be NP-complete. Therefore, heuristics are employed to generate fast, near-optimal compaction. Several early folding heuristics were shown to be near-optimal only for certain classes of PLAs and an exhaustive search algorithm using branch-and-bound techniques was found useful on small (e.g < 20 inputs/outputs) or dense PLAs [hofm80]. The program runtime proved prohibitive for large, sparse structures.

While many of the early folding programs provided significant area reduction they often did so at the expense of increased external routing.<sup>2</sup> Specifically, the designer had no control over the placement of input and output signals. This meant that while the area of the core planes of the PLA was reduced the overall area of the PLA, with the interconnection routing taken into account, might actually have been worse. More recent work by De Micheli [demi84] [demi82] addresses the folding problem with input and output constraints in detail. De Micheli presents a set of heuristics for both constrained and unconstrained multiple folding. Running in a constrained mode, area reductions appear to be about 20% less (referenced to original area at 100%) than their unconstrained compacted counterparts [demi84]. This work represents the current state-of-the-art in PLA compaction.

<sup>&</sup>lt;sup>2</sup>The BLAM program [hofm80] was able to reduce a large UC Berkeley RISC I processor control PLA by 40%. The compacted version of the PLA was not used because input signal routing from the surrounding circuitry to the PLA was difficult using the layout techniques available at that time.

#### 1.5.2. PLA Compaction by Block-Partitioning

Partitioning a circuit into independent pieces, that is subcircuits which have distinct inputs and outputs, will reduce circuit area. Partitioning a PLA in this manner is in effect performing block diagonalization on the original PLA. For example, in the case of an AND plane with n inputs and m product terms, the unpartitioned plane occupies  $O(n \times m)$  area. In the partitioning limit, if each input contacts only a single product term, the AND planes of the m fully partitioned PLAs total O(n) in area. This type of block-partitioning is employed by the SMILE program described in [demi83].

#### 1.5.3. Deficiencies of PLA Compaction Approaches

While folding and partitioning produce area-efficient circuits, which is one of the key parameters in the assessment of module generators, such programs only indirectly address the problem of circuit delay. The fan-in of the PLA planes may be reduced by compaction and this may indirectly decrease the critical path delay, but no delay optimization is provided by folding or partitioning itself. The work in this dissertation recognizes that timing analysis and delay optimization are crucial points in high-performance circuit design. In contrast to the PLA-based combinational logic systems, the work presented here takes as its primary goal the optimization of critical path delay. Topological compaction is performed after delay optimization and care is taken not to degrade circuit performance.

#### 1.6. Summary of Results

The target specification of this research was to build a tool that produces delayoptimized circuits which are also compact in layout area. This goal has been met. Typical

worst-case circuit speeds, as a result of delay optimization, are around a factor of two faster than comparable optimized PLA implementations of the same logic function. Of the

examples tested, circuit speedups ranged from 1.2 to 2.5 times a PLA with the greater

speedups seen on the more complex circuits. The tradeoff with speed is circuit area. The

straightforward automated tiling scheme used in MAMBO produced structures typically

twice the size of comparable PLAs, though the range was from 1.5 times for large PLAs to 5 times for small circuits. For particular circuits MAMBO designs are both faster and smaller than comparable PLA implementations. These results show that the optimized multi-level approach yields circuits with a speed advantage at a cost in area. The designer may tune the synthesized circuit for the most favorable area-speed tradeoff. The multi-level approach is most effective for complex combinational circuits where it yields circuits more than twice as fast as comparable PLAs with a only a small increase in circuit area. Detailed comparisons of combinational logic synthesized using the MAMBO pipeline appear in Chapter 8.

#### CHAPTER 2

## Comparison of Static and Dynamic CMOS Circuits

#### 2.1. Design of Static CMOS Logic

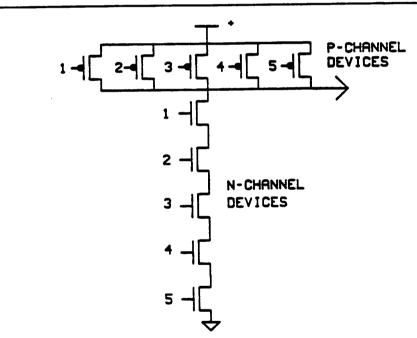

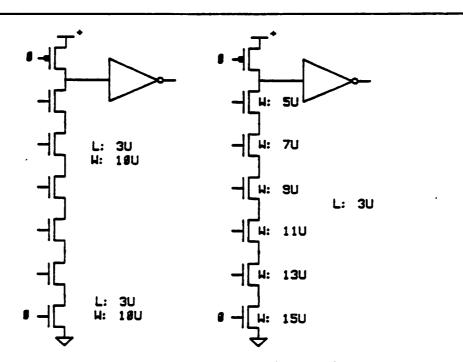

To provide active pullup and pulldown of logic signals in static CMOS design, the circuit function is duplicated by n- and p-channel devices. The two groups of devices are logic duals of one another. The example circuit of Figure 2.1 realizes the NAND function of five inputs.

Figure 2.1: Static CMOS NAND Function of 5 Inputs

A conducting path is opened between GND and the output node when all five inputs are asserted high. By contrast, a path between  $V_{DD}$  and the output node exists when any one of the p-channel devices is asserted low. Each input signal drives two gates, an n-channel and a p-channel device.

#### 2.1.1. Ratioing N- and P-Devices

For the NAND gate, at least one input signal must be low to drive the output node high. To drive the output low, all input signals must be high. Since both states are driven, it is important that the rise and fall times be approximately equal if overall circuit performance is to be optimized. It is standard practice to ratio the FETs to obtain this goal. There are two factors which exert first-order effects on gate delay. For particular values of  $V_{GS}$  and  $V_{DS}$ , the MOSFET current is directly proportional to K, a transconductance parameter, where

$$K_n = \frac{W_n}{L_n} \mu_n C_{o_1} \tag{2.1a}$$

and

$$K_p = \frac{W_p}{L_p} \mu_p C_{ox} \tag{2.1b}$$

for the n-channel and the p-channel devices, respectively. Here it is assumed that the thickness of gate oxide is the same for both devices thus  $C_{\rm ox}$ , the gate oxide capacitance per unit area, is identical for both devices. W and L represent the width and length of the MOSFET active area, respectively. The surface mobility of electrons in the p-type substrate,  $\mu_n$ , is typically two to three times higher than the surface mobility of holes in the n-type substrate,  $\mu_p$ . The exact ratio depends on a variety of factors, including substrate doping, and therefore depends on whether an n-well, p-well, or twin-tub technology is used. The second factor is the effective  $\frac{W}{L}$  ratio of "on" devices between  $V_{\rm out}$  and  $V_{DD}$  or between  $V_{\rm out}$  and GND. By varying W and L of the series and parallel connected devices in Figure 2.1, both of these factors can be overcome. In the SPICE2 [nage75] simulations that follow it is assumed that  $\mu_n=2.5\mu_p$ .

#### 2.1.2. Fanout Loading Calculations

Since static CMOS gates consist of functions duplicated in p- and n-logic, each input signal must drive both an n- and a p-device. The first-order input gate capacitance of

§ 2.1.2

such a static circuit is given by:

$$C_{in} = C_{ox} \left( W_n L_n + W_p L_p \right) \tag{2.2}$$

For an inverter, the p-channel device contributes about twice as much gate capacitance as the n-device. Therefore, a single inverter load in static CMOS is equivalent to approximately three inverter loads in NMOS technology and, in general, dynamic CMOS circuits show a smaller input capacitance than their static CMOS counterparts [pret85].

#### 2.1.3. Design of NAND and NOR in Static CMOS

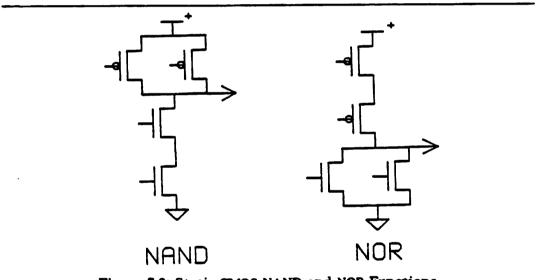

The logic functions NAND and NOR are realized more simply than AND and OR in static CMOS. This is because the unimplanted n-device turns on when  $V_{GS}$  is large positive, hence when the gate is high and the source is grounded. The p-device turns on when  $V_{GS}$  is large negative, hence when the source is tied to  $V_{DD}$  and the gate is low. That is, for both device types, when the input voltage increases the output voltage decreases. This contributes the basic inverting component. A positive logic NAND is fashioned by placing n-devices in series and p-devices in parallel. A positive logic NOR is built by placing the p-devices in series and the n-devices in parallel.

In practice, there is a bias toward building static CMOS gates in NAND form. The two factors which affect device sizing, series chain length and mobility differences, tend to cancel in the design of a NAND gate. For the NOR case the two factors are multiplicative, resulting in a large disparity in p- and n-device sizes, especially for high fan-in gates. The large p-devices add capacitance to the output node and consume circuit area. It is for this reason that some circuits, for example the gate matrix designs in the BELLMAC chip. [kang83a] have been built using only NAND gates.

#### 2.1.4. Worst-Case Delays for Static NAND Gates

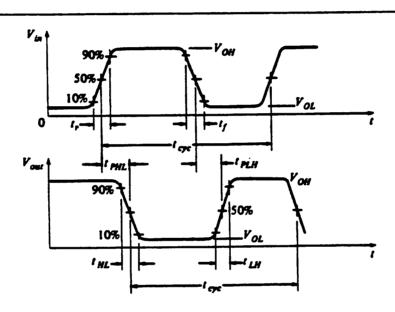

For a NAND configuration the worst-case delay time is  $T_{PHL}$ , the amount of time it takes the output to go from high to low. This definition is illustrated in Figure 2.2 (from [hodg83]). The delay time is given by:

$$T_{PHL} = \frac{C_T (V_{OH} - V_{OL})}{2I_{D(avg)}} \tag{2.3}$$

where the total capacitance is given by:

$C_I = N_O C_G + N_I C_{GDp} + N_I C_{GDn} + (N_I - 1) C_{GSn} + K_{eq} [N_I C_{DBp} + (2N_I - 1) C_{DBn}]$  (2.4) In Equation 2.4  $N_O$  represents the gate famout.  $I_D$  is inversely proportional to  $N_I$ , the number of inputs:

$$I_D = \frac{K/2(V_{GS} - V_t)^2}{N_t} \tag{2.5}$$

K is the process-dependent transconductance parameter.

Figure 2.2: Delay Time Calculation for Static NAND

### 2.1.5. Relative Placement of Gate Input Signals

Consider a high fan-in NAND gate. The speed at which the gate makes the  $1 \rightarrow 0$  transition depends on the speed at which all the n-devices react. By placing the fastest switching FET closest to the output node, the output voltage will begin to fall and the gate will begin to make the transition, even before the more distant transistors have fully turned on. It is important that the designer take advantage of this information in circuit layout. This concern applies only to the n-devices since the p-devices are in parallel:

hence there is no "closest" transistor to the output node.

#### 2.1.6. Static CMOS Speed

Pullup and pulldown times for best and worst case SPICE2 simulations for a 5-input AND gate (NAND with inverted output) are tabulated in Figure 2.3. In the worst-case analysis a single input was switched, in the best-case simulation all inputs were switched in parallel. The sizes of n- and p-channel devices were adjusted to achieve roughly equal rise and fall times in the worst case. As with other simulations described here, the circuits were laid out and all parasitic capacitances were extracted and accounted for in the simulations. The SPICE2 models used for simulation appear in Appendix A.

| 5-Input AND | $L_p/W_p$ | $L_n / W_n$ | risetime (ns ) | falltime (ns ) |

|-------------|-----------|-------------|----------------|----------------|

| Best case   | 3/6       | 3/10        | 7.3            | 2.9            |

| Worst case  | 3/6       | 3/10        | 9.8            | 10.0           |

Figure 2.3: Delay Times for 5-Input Static CMOS AND Gate

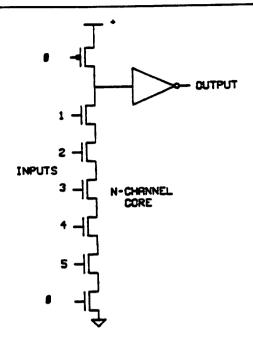

#### 2.2. Design of Dynamic CMOS Logic

The design of dynamic circuits in CMOS offers considerably more layout flexibility than static methods. Dynamic methods rely on charge storage for correct operation. The most commonly employed dynamic methods use two-phase clocking (one clock). In the initial or precharge phase, output nodes are precharged to either logic high or low. In the second phase, called the evaluate phase, output nodes either remain stable or are allowed to make a single, unidirectional transition. With this latter constraint circuit "glitches" are avoided. This is important in charge transfer circuits, because once a node is improperly discharged it cannot return its valid state until the next precharge.

Dynamic circuits offer an advantage over static designs: fewer devices are needed in most cases since circuit function is not duplicated. Removal of the dual network makes design-for-testability easier [gonc83]. The logic used to realize the function, called the core, may be of either n- or p-devices. In the examples that follow n-cores are most

often used.

Dynamic circuit design also has several disadvantages. Some of these drawbacks are summarized:

- The electrical design of dynamic circuits is unquestionably more difficult than in the static case.

- The circuits must be simulated to determine the necessary precharge time.

- Dynamic circuits potentially suffer from a charge redistribution problem on the output node.

- It is especially important to consider the ordering of "internal" versus "external" signals to address this charge problem.

- Certain dynamic design styles are not logically complete.

- Dynamic circuits utilizing two different clocks can have circuit races if not carefully designed.

In the following sections each of these topics is considered with regard to the two most commonly used dynamic design techniques.

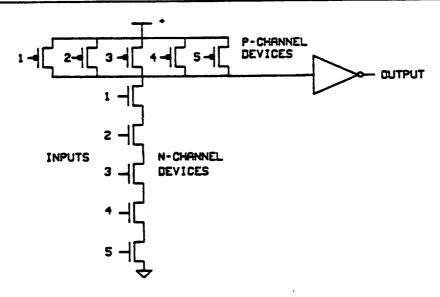

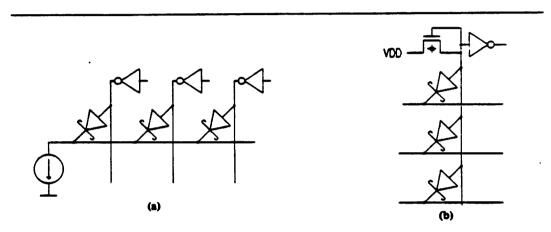

#### 2.2.1. Dynamic CMOS with Domino Logic

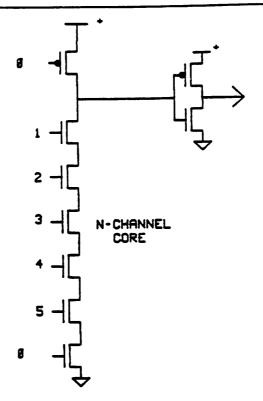

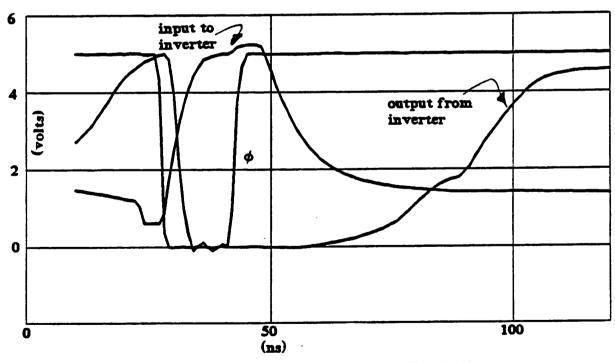

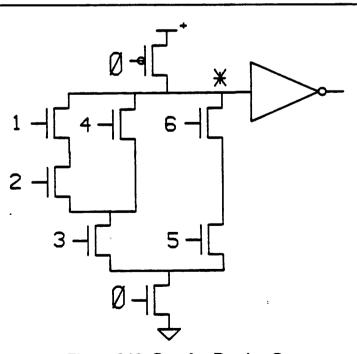

The most basic dynamic design is a style termed *Domino* after Krambeck, et. al. [kram82]. This style involves the use of a single clock, denoted by  $\phi$ . This clock controls a p-channel and an n-channel device; the former between circuit logic output and  $V_{DD}$ , the latter between the circuit logic and GND, as shown in Figure 2.4. In addition, a static inverter is required at the output of the gate. The Domino representation of a 5-input AND circuit is shown in Figure 2.4.

Figure 2.4: CMOS Domino 5-input AND circuit

While a standard (static) gate requires 2k devices to realize such a function, where k is the number of inputs, a Domino gate requires k+4 transistors. The core is composed of k devices: two additional transistors are gated by the clock, and two devices are required for the static output inverter.

The Domino gate works in the following way: During the precharge phase  $\phi$  is held low. The p-channel pullup device charges the Domino core output node high and the core is isolated from GND. At the end of precharge the core node is at  $V_{DD}$ . In the evaluate phase  $\phi$ -goes high which connects the core to GND and isolates the core output from  $V_{DD}$ . If, during evaluate, inputs to the core devices are asserted such that a path is created between the output node and GND, then the output node makes a single  $1 \to 0$  transition. Otherwise, the output node remains in its precharged (high) state.

This process is then repeated with the next precharge phase. The term "Domino" comes about from the analogy of setting up a line of dominoes (precharging) and then letting the first domino make a transition. This may cause a further transition which may, in turn, cause a succeeding transition and so forth— much like the effect of toppling a chain of dominoes.

#### 2.2.2. Device Sizing in Dynamic CMOS

Dynamic logic is ratioless, which is to say that pullup and pulldown devices are not sized depending on the amount of current they draw, or their relative mobility. The static circuits just examined were ratioed in order to compensate for series stacking and for mobility variations so rise and fall times were about equal. In precharged logic only a single state transition is possible. To save circuit area, minimum devices can be used: to gain speed, wide devices can be employed in the core. The sizing of n-channel and p-channel devices are essentially independent tasks.

#### 2.2.3. Static Inverter Requirement

The need for the static inverter is explained fully in the original paper on Domino logic. Briefly, the inverter is required because the precharge state brings the (n -core) output node high. If there is no inverter, a logic high will turn on the following n-channel device. At the beginning of evaluate, therefore, the n-core of a succeeding gate will be active and may be falsely discharged. This occurs because a momentary connection exists between the output of the driven gate and GND. Once this node is discharged it cannot be recharged until the next precharge phase. To prevent this, all input gates are required to be off at the beginning of the evaluate phase. It is therefore necessary to add an inverter in between precharged (high) nodes and driven n-channel (active high) devices.

### 2.2.4. Distinction Between External and Internal Signals

It is important in a dynamic design style. like Domino. to draw the distinction between an *internal* and an *external* signal. An internal signal is one which comes from a previous Domino gate. An external signal comes from a static source such as a latch. Internal signals must be "off" at the beginning of the evaluate phase. An external signal, however, is expected to be *stable* at the beginning of the evaluate phase— whether it is on or off. That is, internal signals are stable and off during precharge and may make a single transition during evaluation. External signals are expected to stabilize before the end of precharge and remain in their final state during evaluation. Thus, another consideration in the calculation of the precharge interval is the length of time it takes external signals to stabilize.

In dynamic circuits relative signal placement is also important. Since external signals must be stable before the beginning of evaluation, they are placed closest to the output node. The internal signals come next and their placement depends on the order in which they switch. Note that if a series external signal is "off" during evaluation the state of any internal signals does not matter, since the external signal blocks any output node transition.

## 2.2.5. The Charge Redistribution Problem in Dynamic Circuits

It has already been pointed out that in dynamic circuits care must be taken to avoid improper discharge of a precharged node. Charge may also be lost from the output node due to the phenomenon of charge redistribution. This problem is most evident in circuits with a high fan-in of largely internal signals. Figure 2.5 illustrates the problem.

Figure 2.5: The Charge Redistribution Problem

Assume all signals are internal. If, during evaluation, the two devices closest to the output node turn on but the third device remains off, the output node should remain high. However, when the internally driven FETs turn on, charge stored on the output node capacitance flows into the source/drain capacitances of the n-devices. The output charge is thus split across several nodes. If the collective source/drain capacitances are of the same order as the gate capacitance of the static inverter, the charge lost from the precharged node may cause the voltage there to drop and the static inverter to make a false transition.

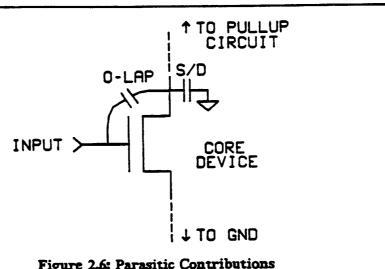

The charge redistribution problem can be quantified and a simple criterion for the onset of charge redistribution is now defined. This criterion is used by the MOSMESH program, described in Chapter 4, to determine the presence of a charge redistribution problem. The precharged capacitance (prech) lies on the node designated by an asterisk in Figure 2.5. All other capacitances represent parasitics (para). A charge redistribution (CR) problem is defined to exist if:

$$\frac{prech + (head) \times para}{prech + (head + middle) \times para} < \frac{V_{TH}}{V_{DD}}$$

(2.6)

where:

head: number of drain nodes from the core devices which touch the prech node

middle: number of source/drain nodes from the core devices which are not head and which do not touch the grounded pulldown device gated by the clock

$V_{TH}$ : the switching threshold of the output buffer/inverter

$V_{DD}$ : positive power supply rail

The buffer capacitances which contribute to the prech capacitance are:

$$W \times L_p \times C_{OXp} + W \times L_n \times C_{OXn} +$$

(gate capacitance)

$$C_{GDOp} \times W_p + C_{GSOp} \times W_p +$$

(s/d overlap cap)

$$C_{GDOn} \times W_n + C_{GSOn} \times W_n +$$

(s/d overlap cap)

$$C_{GBOn} \times L_n + C_{GBOp} \times L_p$$

(gate/bulk overlap cap)

The pullup device also contributes to the prech capacitance:

$$C_{J_F} \times Area_{pullup} + C_{JSW_P} \times Perimeter_{pullup} +$$

(bulk capacitance)

$C_{GDO_P} \times W_{pullup}$  (overlap cap)

The parasitic contributions come from two sources: from junction capacitances of the source and drain to the substrate and from source/drain overlap capacitances. Note that the parasitic capacitances contributed by the head devices add to the prech capacitance. The capacitances given below are per source or drain region per device.

$$C_{Jn} \times Area_{core} + C_{JSWn} \times Perimeter_{core} +$$

(core bulk cap)

$C_{GSOn} \times W_{core}$  (s/d overlap cap)

A breakdown of the parasitic contributions is shown in Figure 2.6.

Figure 2.6: Parasitic Contributions

There are two solutions to the CR problem, both involve keeping the ratio of output node capacitance to parasitic input capacitance large. The first method is to make the static inverter larger. This has the advantage that the circuit can now drive a large fanout. Adding capacitance slows the switching time, however. Small circuit area, one of the advantages of dynamic designs, is also compromised. The second approach is to decrease the size of the core devices. If these devices are of minimum size, however, they represent a higher resistance and thus cause the gate to switch more slowly. Thus, without significantly modifying the circuit, the only solution to the redistribution problem requires slowing down the circuit. This is a drawback which both Domino style circuits and NORA circuits, described in Section 2.3, suffer.

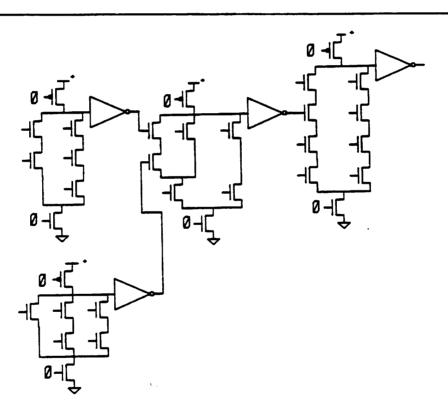

#### 2.2.6. Domino Circuits Are Not Logically Complete

The addition to the dynamic circuit of the interstage inverter means that Domino gates are either AND or OR in function. Neither configuration can produce an inversion and hence the Domino family is not logically complete by itself. This drawback can be overcome by moving the inversions to the last Domino stage. The last stage has no restrictions on its output, assuming it drives standard static CMOS logic. This moving of inversions, also called *bubble pushing*, can be accomplished by expression-tree transformation. The software tool MGMG, described in Chapter 4, can transform an arbitrarily deep expression tree to AND—OR form.

# 2.2.7. OR Gates Preferred in Dynamic CMOS

In contrast to static CMOS, where device ratioing for mobility plays a role, the practical gate for implementing dynamic circuits is the OR function (n -core). Since the single p-device is only active in precharge, it is not affected by the n-core devices (which are only active in evaluate). It is preferable to arrange the n-devices in parallel to reduce the resistance path between output node and GND. Parallel n-devices give the OR function. By creating the same device configuration with a p-core in place of the n-channel devices, the AND function is constructed. Typically, Domino design is n-core only.

The pure n-core OR function and the pure p-core AND function have the additional advantage over their counterparts of being immune to the charge redistribution problem. This is because of the single device between output node and clocked device; there are no internal nodes for redistribution.

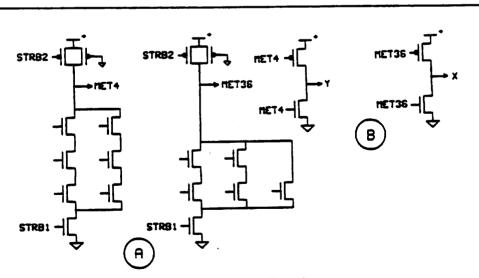

# 2.3. Dynamic CMOS Design Using NORA

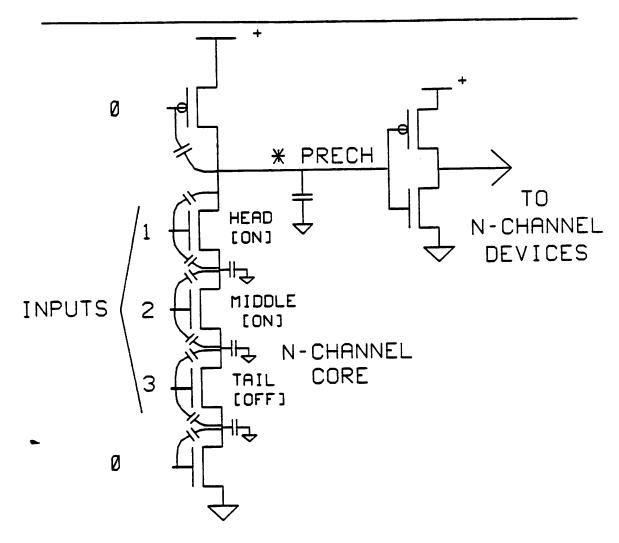

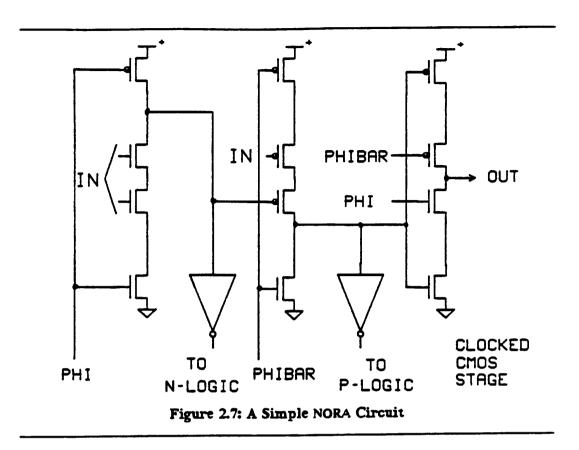

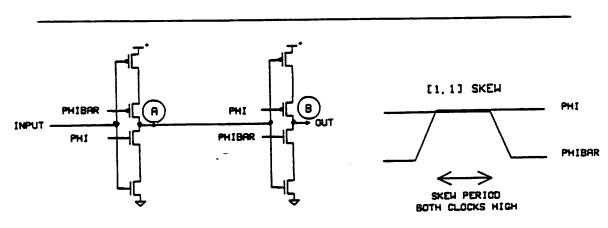

A style of dynamic CMOS design which utilizes both n- and p-core gates in an alternating pattern has been described by Goncalves and DeMan [gonc83]. This style is more complicated than the Domino approach, which it is based on. NORA logic uses two clocks, commonly denoted by  $\phi$  and  $\overline{\phi}$ . The name NORA comes from NO RAce logic. A NORA circuit is shown in Figure 2.7.

The first gate in this figure resembles a Domino gate except that the interstage inverter is not used. NORA obviates the need for such inverters by requiring a p-core gate follow an n-core one. Alternatively, an inverter could be used to connect two n-core gates in succession in which case NORA reduces to the Domino style. By eliminating the need for an interstage inverter, both n- and p-core gates can be built realizing the NAND and NOR functions. Since negations can also be realized it would appear at first glance that NORA designs are logically complete. This is not the case. As a result of the construction rules to preserve the racefree properties of NORA, explained below, the designer realizes no greater design flexibility from NORA circuits than from standard Domino designs. However, because the static inverter is not required, the overhead for a NORA circuit is reduced: NORA gates require only k+2 devices to implement a k-input, single-output function.

Like Domino logic, NORA utilizes a precharge and an evaluate phase. Unlike Domino, two clock phases are employed. This allows pipelining of interconnecting stages but also

introduces the potential problem of circuit races due to skewed clocks. In Domino logic circuit races are not possible since all gates are controlled from the same clock. There is a problem of clock distribution about a large circuit, a problem common to all dynamic designs.

# 2.3.1. The C<sup>2</sup>MOS latch in NORA logic

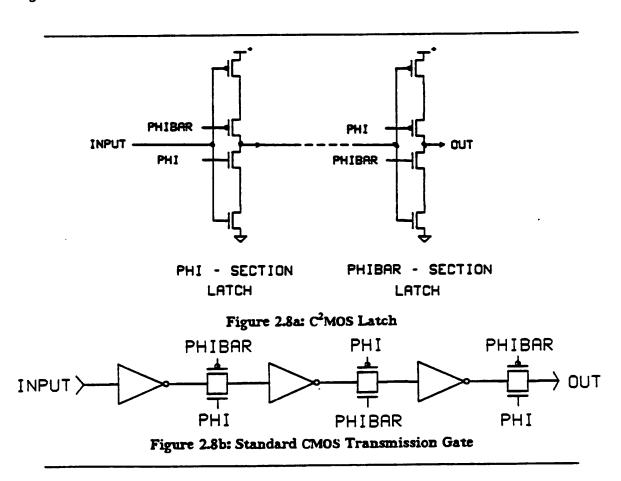

By employing a C<sup>2</sup>MOS (clocked CMOS) latch between pipelined circuit stages one can guarantee that races are avoided. This latch was first proposed and analyzed in [suzu73]. Figure 2.8a shows the latch in its most common configuration.

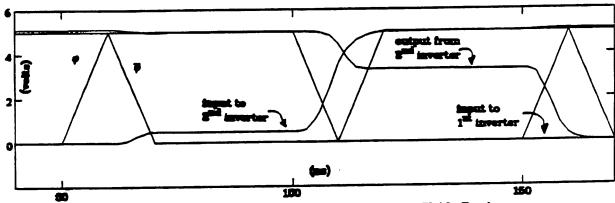

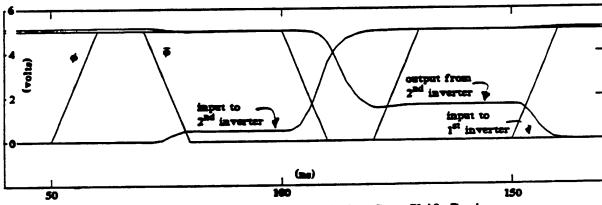

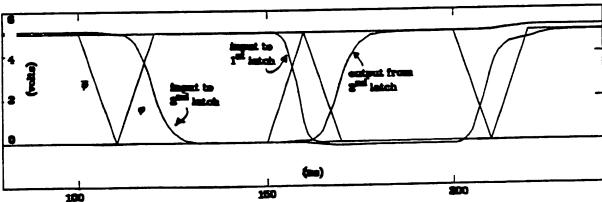

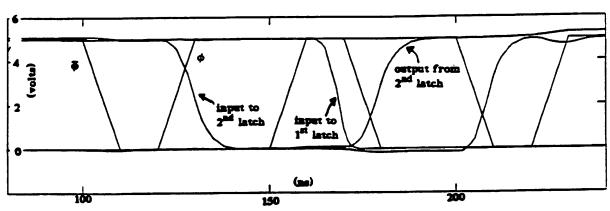

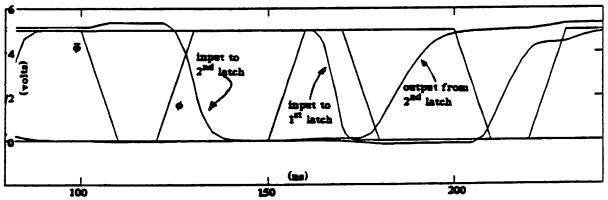

This latch, which uses four transistors, is used in place of the CMOS transmission gate, shown in Figure 2.8b. In Figure 2.9 SPICE2 simulation waveforms are shown for a shift register using first a pair of simple pass gates and then a pair of C<sup>2</sup>MOS latches. It can be

seen that the former configuration is sensitive to clock skew. As skew is increased logic • levels are compromised. This occurs because in the skew period the transfer gate is neither on nor off, therefore logic levels are undefined. The skew period is that interval when  $\phi$  and  $\overline{\phi}$  are both 1 or both 0. By comparison, the clocked latch is always in a defined state. Note that the clocked CMOS latch inverts its input data.

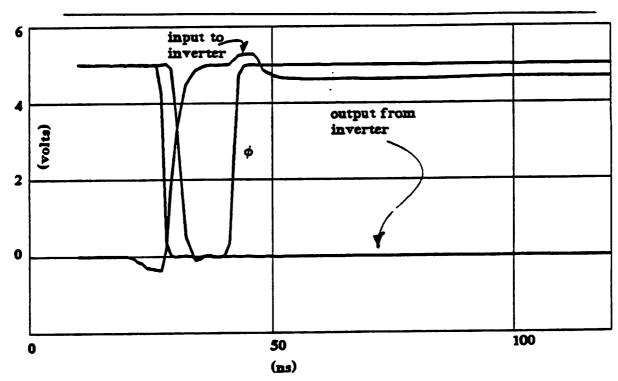

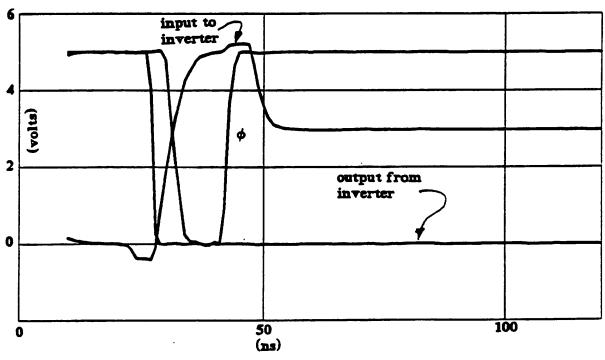

Figure 2.9a: 10ns Skew in Transmission Gate Shift Register

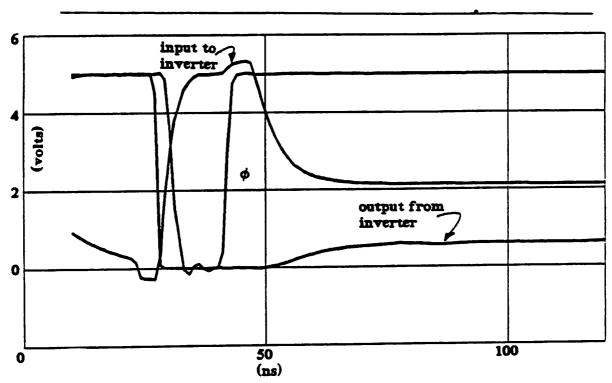

Figure 2.9b: 20ns Skew in Transmission Gate Shift Register

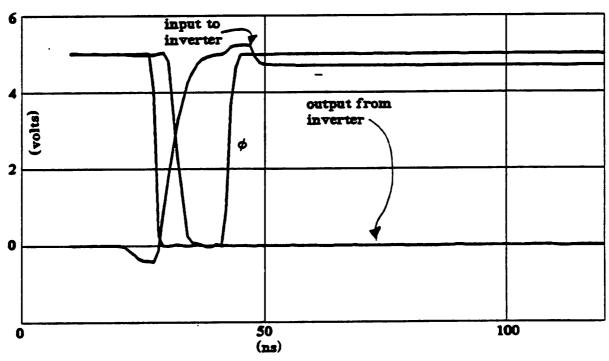

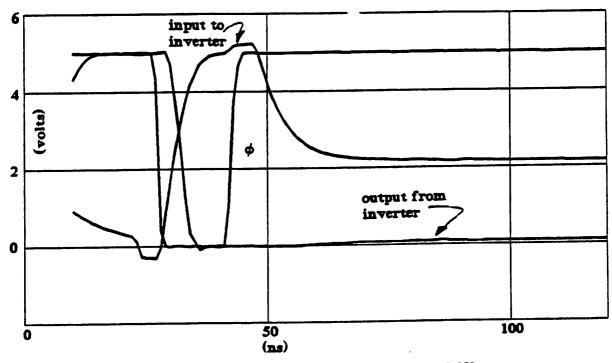

Figure 2.9c: 10ns Skew in C<sup>2</sup>MOS Shift Register

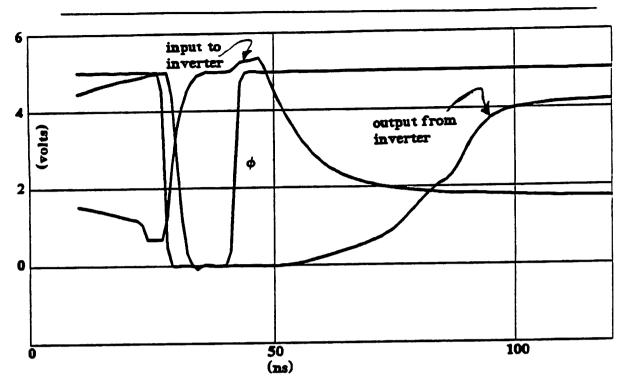

Figure 2.9d: 20ns Skew in C2MOS Shift Register

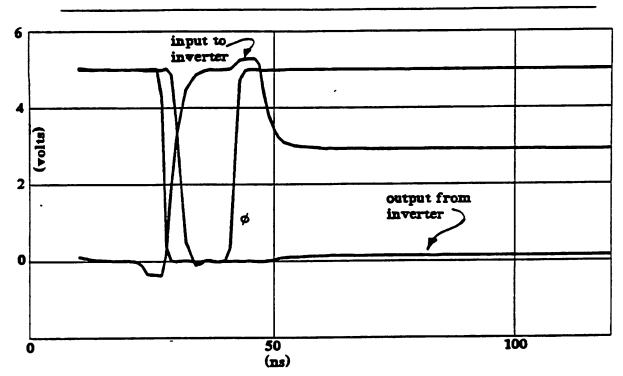

Figure 2.9e: 30ns Skew in C<sup>2</sup>MOS Shift Register

The operation of the clocked CMOS latch is shown in Figure 2.10.

Figure 2.10: Operation of C<sup>2</sup>MOS Latch

If a 0 is shifted into the first latch, then it is only possible for node B to take a  $1 \to 0$  transition if node A makes the  $0 \to 1$  transition and  $\overline{\phi} = 0$  and  $\overline{\phi} = 1$ .  $\overline{\phi}$  must equal 0 in

order for node A to make the transition high, but it must be 1 so that node B can make the transition low. Since  $\Phi$  can only be either on or off such a skew problem cannot affect the latched signals. This example of skew is called (1,1) skew because it is analogous to the pass gate example with both  $\Phi$  and  $\Phi$  high. A similar potential race condition exists in the case where  $\Phi$  and  $\Phi$  are both low. This is called (0,0) skew. Again, the operation of the  $C^2$ MOS latch is immune to these skew conditions.

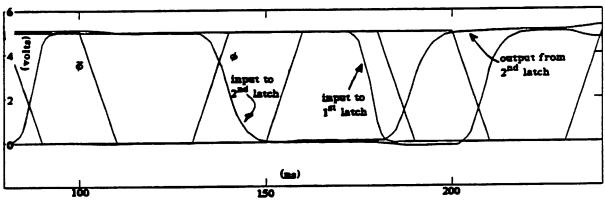

Unfortunately, it is still possible to have skewed-clock-induced races in  $C^2MOS$  circuits. If the  $V_r$ 's of the complementary devices are mismatched then there exists a voltage range,  $V_r$ , where the n-device is beginning to turn on and the p-device is not yet off, and vice versa. Notice in Figure 2.10 that  $\phi$  drives an n-channel device in the first latch, but a p-channel device in the second latch. This insures that the latches work on opposite phases. However, it also means that the conditions  $\phi = 0$  and  $\phi = 1$  are not mutually exclusive. It is still possible to have clocked feedthrough between latches. The SPICE2 simulation result given in Figure 2.11 shows this effect when  $V_{tp}$  is -2.0V and  $V_{tn}$  is +0.5V. The  $C^2MOS$  latch is immune to clock skew but is still sensitive to  $V_r$  mismatches.

Figure 2.11: 20ns Skew in C<sup>2</sup>MOS Shift Register with V. Mismatch

#### 2.3.2. Pipelining NORA stages

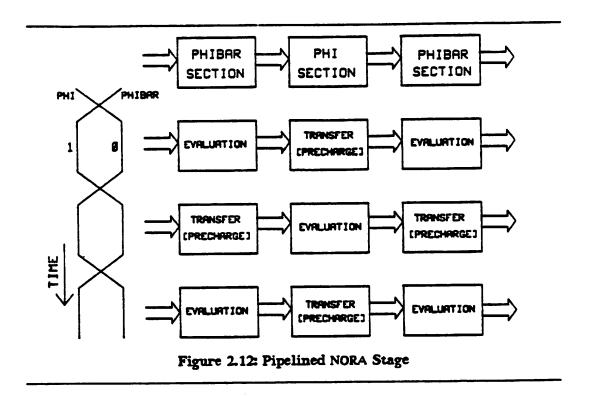

In the NORA style stages are coupled via the clocked CMOS latches. Each stage, which may be composed of an arbitrary number of n- and p-core gates, is clocked by  $\phi$  and  $\overline{\phi}$  signals.  $\phi$  sections are interleaved with  $\overline{\phi}$  sections to create a continuous pipeline. A  $\phi$

section is in precharge when  $\phi = 0$  and  $\overline{\phi} = 1$ . A  $\overline{\phi}$  section precharges under the opposite conditions. This allows the stages to be connected as shown in Figure 2.12 [gonc83].

By using this technique, a result becomes available at the end of each evaluation phase, thus at the end of each clock cycle. It is assumed that the  $\phi$  and  $\overline{\phi}$  sections are of roughly equal complexity and, therefore, precharge and evaluate times will equal each other. In NORA, half the clock cycle is spent in precharge and half in evaluation. Domino logic, which is not pipelined, does not require an even split between precharge and evaluation phases. It is important in speed comparisons with static logic to factor in the precharge or setup time of dynamic circuits.

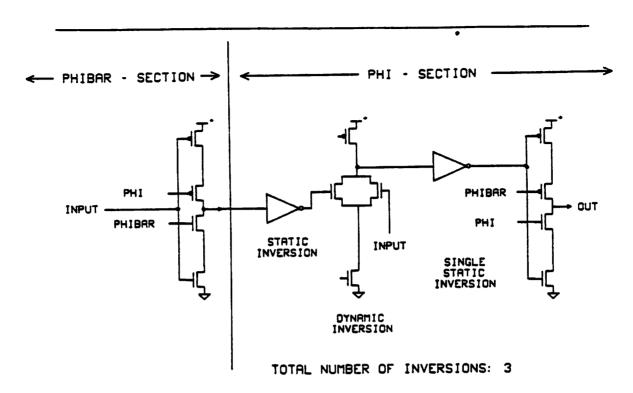

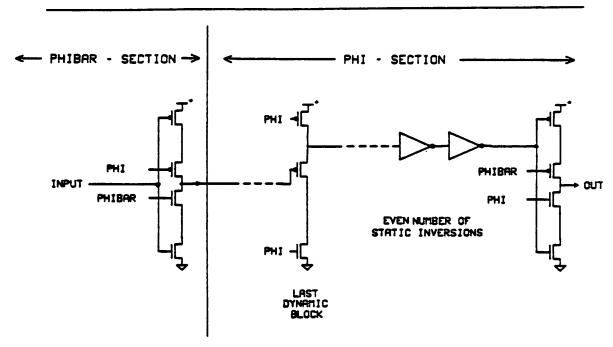

# 2.3.3. Construction Rules to Preserve Racefree Properties

In order to preserve the "racefree" properties of NORA conferred by the C<sup>2</sup>MOS latch a number of construction rules must be observed. As summarized by Goncalves and DeMan [gonc83] the rules are:

- (1) There is an even number of static inversions between the last dynamic stage of a section  $(\phi \text{ or } \overline{\phi})$  and the C<sup>2</sup>MOS output latch. (Precharge racefree.)

- (2) There is at least one dynamic block placed in such a way that there is an even number of inversions between this dynamic block and the C<sup>2</sup>MOS input latch. (Evaluation racefree.)

The total number of (dynamic and static) inversions between the input and output C<sup>2</sup>MOS latches is even. (Evaluation racefree.)

. These constraints are in addition to the requirement of a static inverter to eliminate the Domino internal delay problem.

The intent of these rules is to insure that within each  $(\phi \text{ or } \overline{\phi})$  section the data signal is controlled by only one clock; it is independent of the opposite phase clock. The data signal must be immune from races in both precharge and evaluation phases. For the precharge phase consider the converse of the first rule; assume a single (static) inversion between the last precharged node and the output latch. For the n-core device in a  $\phi$  section shown in Figure 2.12 the precharge node goes high in precharge as a result of a  $\phi$ -controlled precharge FET. The output of the static inverter goes low and information on the latch output could be lost if the p-channel clocked FET, controlled by  $\overline{\phi}$ , was clocked late with respect to the  $\phi$ -controlled precharge. This configuration depends on both clocks. Without the inversion (an even number of inversions) the input to the latch goes high. Now for the latched information to be lost the  $\phi$ -controlled n-channel device would have to turn on. But both the precharge device and the controlling latch device are gated by the same clock. This clock is low in  $\phi$ -section precharge by definition and therefore latched information is preserved.

When the clock is high, the  $\phi$ -section is in evaluation. Consider the converse of the second evaluation racefree constraint; assume that between the output latch from a  $\overline{\phi}$  section and the output latch from the next  $\phi$  section there is a single static inversion. This configuration is shown in Figure 2.13.

Figure 2.13: φ—section with Single Static Inversion (Contradiction of NORA rule 2.)

In  $\phi$ -evaluation,  $\phi$  goes high: if the output from the inverter is also high then information on the output latch may change because the n-channel clocked device gated by  $\phi$  is on. But if the inverter output is high, the input must be low. The logic 0 was the result of the n-channel clocked device of the previous ( $\overline{\phi}$  section) latch being on. This device is gated by  $\overline{\phi}$ . Again, if skew exists between the two clock phases, latched information may be lost. With an even number of interstage inversions it is only possible for one latch to be "on", allowing its output to reflect changes at its input. Because the  $\phi$  and  $\overline{\phi}$  latches are active on opposite phases, the same clock that activates the  $\phi$  latch deactivates the  $\overline{\phi}$  latch. The racefree properties are preserved because data transfer depends only on a single clock.

The first evaluation racefree rule guarantees that the racefree properties are preserved by assuring that a dynamic block is gated by the same clock that gates the input C<sup>2</sup>MOS latch, as illustrated in Figure 2.14.

Figure 2.14: Precharge Racefree Rule: Even number of static inversions between last dynamic stage and output latch.

If this dynamic block is the last dynamic block of the section then it must be followed by an even number of (static) inversions- as required by the precharge constraint. If the dynamic block is not the last block then it is followed by an even or odd number of dynamic blocks. If there are an odd number more blocks, then the total number of inversions is even, which is the second evaluation racefree rule. If the number of succeeding dynamic blocks is even, then there must be an even number of inversions between this logic block and the C<sup>2</sup>MOS output latch. This again assures that data signals depend only on a single clock.

It is often possible to change a circuit which violates these constraints into one which obeys the rules. Three possibilities are suggested [gonc83]:

- 1) A static inversion can be converted into a dynamic one.

- 2) A static inversion can be converted to a C<sup>2</sup>MOS latch.

- 3) The static inverter can be placed after the  $C^2MOS$  latch.

#### 2.4. Special Design Considerations in Dynamic CMOS

In this section three aspects of CMOS design particular to dynamic logic are examined. First, inverter buffer sizing is considered with regard to noise margin, delay, and charge redistribution. Second, the effect of an added static pullup to the precharge node is described. Finally, a stacking scheme is examined which can often speed up a high fan-in series gate. Such circuits are typically slow and, therefore, speedup is especially important.

## 2.4.1. Noise Margins in the CMOS Inverter

A static inverter is employed to connect stages in Domino and NORA logic. The noise margin of this inverter is of particular importance in the design of dynamic circuits. The high and low noise margins used in this analysis are defined as:

$$NM_{L} = V_{IL} - V_{OL} \tag{2.7a}$$

and

$$NM_H = V_{OH} - V_{IH} \tag{2.7b}$$

respectively. Following a standard text, for example [hodg83], the points  $V_{IH}$  and  $V_{IL}$  on the voltage transfer curve are defined by  $dV_{out}$  /  $dV_{in} = -1$ . By solving for this derivative and using the result in the appropriate drain equation the noise margin parameters can be obtained.

The drain current of a device in saturation is given by

$$I_D = \frac{k}{2} (V_{GS} - V_t)^2 \tag{2.8a}$$

where  $V_{DS} \geqslant V_{GS} - V_i$ . The drain current in the linear region is

$$I_{D} = \frac{k}{2} [2(V_{GS} - V_{t})V_{DS} - V_{DS}^{2}]$$

(2.8b)

where  $V_{GS} \ge V_t$  and  $V_{DS} \le V_{GS} - V_t$ . To find  $V_{IH}$  and  $V_{OL}$ , assume the *n*-channel device is in the linear region and the *p*-channel device is in saturation. Thus  $I_{DN(lin)} = I_{DP(sar)}$  or

$$\frac{K_n}{2} [2(V_{IH} - V_{in})V_{OL} - V_{OL}^2] = \frac{K_p}{2} (V_{DD} - V_{IH} - V_{ip})^2$$

(2.9)

In this equation and those that follow the absolute value of  $V_{tp}$  is used.  $K_n$  is  $kW_n / L_n$  and  $K_p$  is  $kW_p / L_p$ . Solving this equation for  $V_{IH}$  yields

$$V_{IH} = \frac{\pm [2K_{p}(V_{DD}) - K_{n}(V_{OL})(2K_{p}(V_{tp} + V_{tn})) + (K_{n} - K_{p})V_{OL}]^{1/2}}{K_{p}} + K_{p}(V_{tp}) - K_{n}(V_{OL}) - K_{p}(V_{DD}) - K_{p}(V_{DD})$$

$$(2.10)$$

Solving the  $dV_{out}/dV_{in}$  equation for a slope of -1 yields

$$V_{lH} = \frac{2V_{OL} + V_{ln} + (K_p / K_n)(V_{DD} - V_{lp})}{1 + (K_p / K_n)}$$

(2.11)

By equating these two expressions and iterating, a solution can found simultaneously for  $V_{IH}$  and  $V_{OL}$  Results for various pullup/pulldown ratios are given in Figure 2.15 for the worst-case SPICE2 model. It can be seen that the NMOS device is, in fact, in the linear region while the PMOS device is saturated.

To find  $V_{IL}$  and  $V_{OH}$  assume the n-channel device is in saturation and the p-channel device is in the linear region. Thus  $I_{DP(lin)} = I_{DN(sat)}$  or

$$\frac{K_p}{2}[2(V_{DD}-V_{IL})(V_{DD}-V_{OH})-(V_{DD}-V_{OH})^2] = \frac{K_n}{2}(V_{IL}-V_{In})^2$$

(2.12)

Solving this equation for  $V_{IL}$  yields:

$$V_{IL} = \frac{\pm [(V_{OH} - V_{DD})(2K_n V_{tn} + (K_p - K_n)V_{OH} - (K_p + K_n)V_{DD})]^{1/2}}{K_n}$$

$$\frac{-K_n V_{tn} - K_p (V_{OH} + V_{DD})}{K}$$

(2.13)

Solving the  $dV_{out}$  /  $dV_{in}$  equation for a slope of -1 yields:

$$V_{IL} = \frac{2V_{OH} - V_{DD} - V_{tp} + (K_n / K_p)V_{tn}}{1 + (K_n / K_p)}$$

(2.14)

By equating these expressions and solving as before, values for  $V_{IL}$  and  $V_{OH}$  are obtained. Results for various pullup/pulldown ratios are given in Figure 2.15. It can be seen that the NMOS device is in saturation while the PMOS device is in the linear region of operation.

A factor related to noise margin is the  $V_{in}=V_{out}$  point, sometimes called  $V_{IH}$  or the logic threshold voltage. This point occurs between  $V_{IL}$  and  $V_{IH}$ , when both devices are in saturation, thus  $I_{DN(soff)}=I_{DP(soff)}$  or

$$\frac{K_n}{2}(V_m - V_{tn})^2 = \frac{K_p}{2}(V_{DD} - V_m - V_{tp})^2$$

(2.15)

$V_{TH}$  values are summarized in Figure 2.15.

| Noise Margins for Selected Device Ratios (in volts) |             |      |          |                 |                 |      |      |          |

|-----------------------------------------------------|-------------|------|----------|-----------------|-----------------|------|------|----------|

| $L_n / W_n$                                         | $L_p / W_p$ | VOL  | $V_{IL}$ | V <sub>IH</sub> | V <sub>OH</sub> | NML  | NMH  | $V_{IH}$ |

| 3/4                                                 | 3/24        | 0.38 | 2.96     | 3.55            | 4.25            | 2.58 | 0.70 | 2.93     |

| 3/4                                                 | 3/10        | 0.50 | 2.05     | 2.99            | 4.56            | 1.55 | 1.57 | 2.50     |

| 3/4                                                 | 3/8         | 0.52 | 1.84     | 2.85            | 4.62            | 1.32 | 1.77 | 2.39     |

| 3/16                                                | 3/24        | 0.53 | 1.58     | 2.66            | 4.70            | 1.05 | 2.04 | 2.25     |

| 3/14                                                | 3/12        | 0.53 | 1.12     | 2.31            | 4.85            | 0.59 | 2.54 | 1.98     |

Figure 2.15: Noise Margins versus Device Ratios

## 2.4.1.1. Effects of Device Ratioing on Noise Margin

For the static CMOS inverter case it is preferable to have symmetric noise margins and to place  $V_{TH}$  midway between  $V_{OL}$  and  $V_{OH}$ . For the SPICE2 parameters used in the simulations in this report, where  $\mu_n$  is 2.5 times  $\mu_p$ , it can be seen that ratioing devices to cancel mobility differences also gives symmetric noise margins and a good  $V_{TH}$ . This is shown in the second line of Figure 2.15. This device ratio also guarantees approximately equal rise and fall times. It is the ratio of pullup to pulldown, not their absolute size, that determines noise margin.

In dynamic design there is the additional constraint of signal degradation due to leakage and charge redistribution. Also, precharged dynamic gates are unidirectional in nature, making either a  $0 \rightarrow 1$  or  $1 \rightarrow 0$  transition. Therefore best performance is obtained when noise margins are not equal.

Unfortunately, these additional constraints argue for opposing constructions. Consider an n-core dynamic circuit, precharged high. The accompanying buffer-inverter (if used) has its output driven low. The important transition is  $0 \rightarrow 1$  at the output. To