# Copyright © 1985, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# TIMING RECOVERY IN DIGITAL SUBSCRIBER LOOPS

bу

C-P. Tzeng

Memorandum No. UCB/ERL M85/29

22 April 1985

# TIMING RECOVERY IN DIGITAL SUBSCRIBER LOOPS

bу

C.-P. J. Tzeng

Memorandum No. UCB/ERL M85/29

22 April 1985

**ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### TIMING RECOVERY IN DIGITAL SUBSCRIBER LOOPS

### Chin-Pyng Jeremy Tzeng

Ph.D.

Department of Electrical Engineering and Computer Sciences

Sponsors:

Committee Chairman

Advanced Micro Devices, Fairchild Semiconductor, Harris Corp., National Semiconductor, and Racal-Vadic, with a matching grants from the University of California's MICRO (Microelectronics and Computer Research Opportunities) program.

#### **ABSTRACT**

Timing recovery is a critical function that must be provided to synchronize a digital subscriber loop communication link. Low-cost electronics for digital subscriber loop systems will be achieved with VLSI technology. Sampled-data techniques are the most practical means of obtaining the necessary signal processing functions in VLSI form.

This thesis reports on studies of two sampled-data timing recovery techniques, the wave difference method, and the baudrate sampling technique. The major goal is the integrated circuit implementation of these techniques. The design issues concerning interrelated problems of echo cancellation, equalization, and timing recovery are addressed. The roles played by the line code and pulse shape in timing recovery are reported. The impact of these timing recovery methods on the implementation of the echo canceller and on the performance of the digital subscriber loop system is also presented.

Computer simulations indicate that the performance of both timing recovery approaches is satisfactory. Experimental results for the baudrate sampling technique agree well with the simulation results. A fully-integrated digital subscriber loop transceiver is concluded to be feasible.

I like to express my deepest thanks to Professors David A. Hodges and David G. Messerschmitt for their guidance and support throughout the course of my research work. I am also grateful to Dr. Oscar Agazzi, who pioneered the work on digital subscriber loops at Berkeley, for his technical assistance.

I thank Professor Robert W. Brodersen for letting me use the silicon compiler developed in his group to build an experimental chip, and Jan Rabaey for helping me coding the silicon compiler. It is unfortunate that the chip is still undergoing testing and thus it is not mentioned in this thesis. The help from Peter Ruetz on designing the digital VCO chip. Ho-Ping Tseng on preparing the figures, and the valuable discussions with my colleagues, Graham Brand and Nan-Sheng Lin, and many other graduate students here at Berkeley have been very useful.

I also wish to thank Peter O'Riordan and Peter Winship for constructing the experimental breadboard systems. Without the cables provided by Pacific Telephone, the experiment would not have been complete.

This work was supported by Advanced Micro Devices, Fairchild Semiconductor. Harris Corp., National Semiconductor, and Racal Vadic, with a matching grant from the University of California's MICRO program.

# TABLE OF CONTENTS

| Chapt | ter 1 - Introduction                                            | 1  |

|-------|-----------------------------------------------------------------|----|

| -     | Digital Subscriber Loops                                        | 1  |

|       | 1.1.1 Comparison Between TCM and Echo Cancellation Systems      | 6  |

| 1.2   | Line Coding and Pulse Shaping                                   | 8  |

|       | 1.2.1 Digital Line Coding                                       | 9  |

|       | 1.2.2 Pulse Shaping                                             | 12 |

|       | 1.2.3 Combining Line Coding and Pulse Shaping                   | 13 |

| 1.3   | Echo Cancellation                                               | 14 |

|       | 1.3.1 Echo Canceller Structures                                 | 15 |

|       | 1.3.2 Fully Analog Approach                                     | 16 |

|       | 1.3.3 Implementation Alternatives for the Fully Analog Approach | 17 |

|       | 1.3.4 Other Transversal Filter Structures                       | 23 |

| 1.4   | Summary                                                         | 26 |

| Chapt | er 2 - System Design                                            | 28 |

| 2.1   | Design Parameters and Techniques                                | 28 |

|       | 2.1.1 Error Rate Objectives                                     | 28 |

|       | 2.1.2 Echo Cancellation                                         | 29 |

|       | 2.1.2.1 Interpolation Echo Cancellers                           | 32 |

|       | 2.1.3 Echo Cancellation Requirement                             | 34 |

|       | 2.1.4 Equalization                                              | 34 |

|       | 2.1.5 Timing Recovery                                           | 35 |

|       | 2.1.6 Synchronization in Subscriber and Central Office Sets     | 35 |

| 2.2   | System Description                                              | 36 |

|       | 2.2.1 Scramble and Descrambler                                  | 38 |

|       | 2.2.2 Line Coder                                                | 39 |

|       | 2.2.3 Transmit and Receive Filters                              | 40 |

|       | 2.2.4 Equalizer                                                 | 42 |

|       | 2.2.5 Echo Canceller                                            | 42 |

|       | 2.2.6 Detector                                                  | 42 |

|       | 2.2.7 Timing Recovery                                           | 43 |

|       | 2.2.7.1 Timing Function Generator                               | 44 |

|       | 2.2.7.2 Loop Filter and VCO                                     | 44 |

| -     | er 3 - Timing Recovery                                          | 46 |

| 3.1   | Conventional Timing Recovery Methods                            | 47 |

|       | Optimum Timing Phase                                            | 51 |

| 3.3   | On the Timing Phase Recovered by the Spectral Line Method       | 53 |

|       | 3.3.1 The Importance of Timing Phase                            | 55 |

|            | 3.3.2 Timing Phase Recovered by the Spectral Line Method  |

|------------|-----------------------------------------------------------|

|            | 3.3.3 Prefiltering                                        |

|            | 3.3.4 Summary                                             |

| 3.4        | Timing Recovery in DSL                                    |

|            | 3.4.1 Practical Considerations                            |

|            | 3.4.1.1 Echo Canceller                                    |

|            | 3.4.1.2 Line Impairments                                  |

|            | 3.4.1.3 Equalization Techniques                           |

|            | 3.4.2 Objectives of Timing Recovery                       |

|            | 3.4.3 Summary                                             |

| Chap       | ter 4 - Phase-Locked Loops                                |

| _          | Timing Jitter Effect on Performance of Echo Canceller     |

|            | Residual Error in Echo Canceller due to Timing Jitter     |

|            | PLL                                                       |

|            | 4.3.1 Analog PLL                                          |

|            | 4.3.2 DPLL                                                |

| 4.4        | Voltage Controlled Oscillator (VCO)                       |

|            | 4.4.1 Analog VCO                                          |

|            | 4.4.1.1 Multivibrator Analog VCO                          |

|            | 4.4.1.2 Crystal VCO (VCXO)                                |

|            | 4.4.2 Digital VCO (DVCO)                                  |

| Chant      | ter 5 - Equalization                                      |

|            | Performance Bounds                                        |

| J.1        | 5.1.1 Matched-Filter Bound in an Ideal Channel            |

|            | 5.1.2 Matched-Filter Bound in a Nonideal Channel          |

|            |                                                           |

|            | 5.1.3 Optimum Linear PAM Receiver                         |

| 5 2        | 5.1.4 Optimum PAM Receiver with DFE                       |

|            |                                                           |

|            | Linear Transversal Filter                                 |

|            | Decision Feedback Equalizer (DFE)                         |

|            | Summary                                                   |

|            | ter 6 - Wave Difference Method (WDM)                      |

| 0.1        | Analysis of the Wave Difference Timing Recovery Technique |

|            | 6.1.1 The Wave Difference Method                          |

|            | 6.1.2 WDM Frequency Detector                              |

| <i>-</i> - | 6.1.3 Comparison of the WDM with the Spectral Line Method |

|            | Performance of the WDM                                    |

| _          | An Example of Timing Recovery Design                      |

| 6.4        | 9                                                         |

|            | Equalization                                              |

|            | Summary                                                   |

|            | er 7 - Baudrate Sampling Technique (BST)                  |

| 7.1        | Line Coding and Pulse Shaping                             |

|            | 7.1.1 Line Coding                                         |

| 7.1.2 Pulse-shaping                                                              | 157 |

|----------------------------------------------------------------------------------|-----|

| - 7.1.2.1 Pulse-shaping by digital coding                                        | 158 |

| 7.1.2.2 Pulse-shaping by analog filtering                                        | 159 |

| 7.2 Timing Function                                                              | 161 |

| 7.3 Timing Jitter Analysis                                                       | 168 |

| 7.3.1 Timing Jitter Model                                                        | 168 |

| 7.3.2 Jitter Spectrum                                                            | 170 |

| 7.4 Equalization/Data Detection                                                  | 173 |

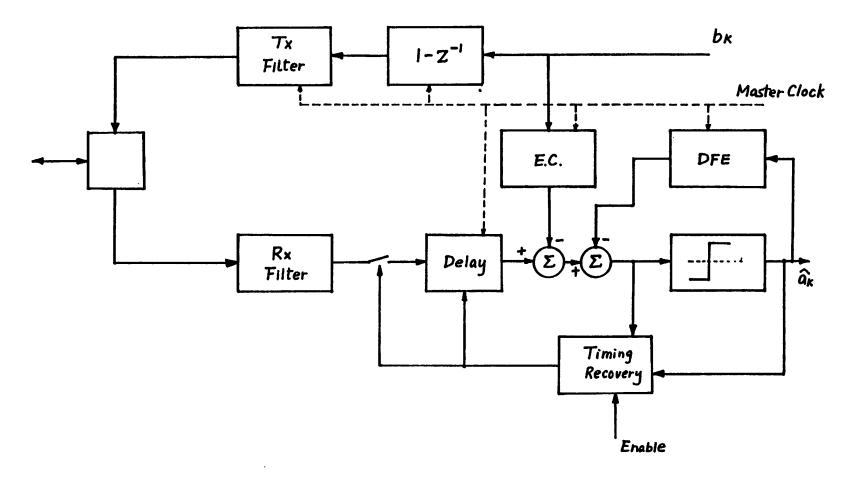

| 7.5 Subscriber End Transceiver                                                   | 175 |

| 7.6 Central Office End Transceiver                                               | 176 |

| 7.7 Integrated Circuit Implementation                                            | 177 |

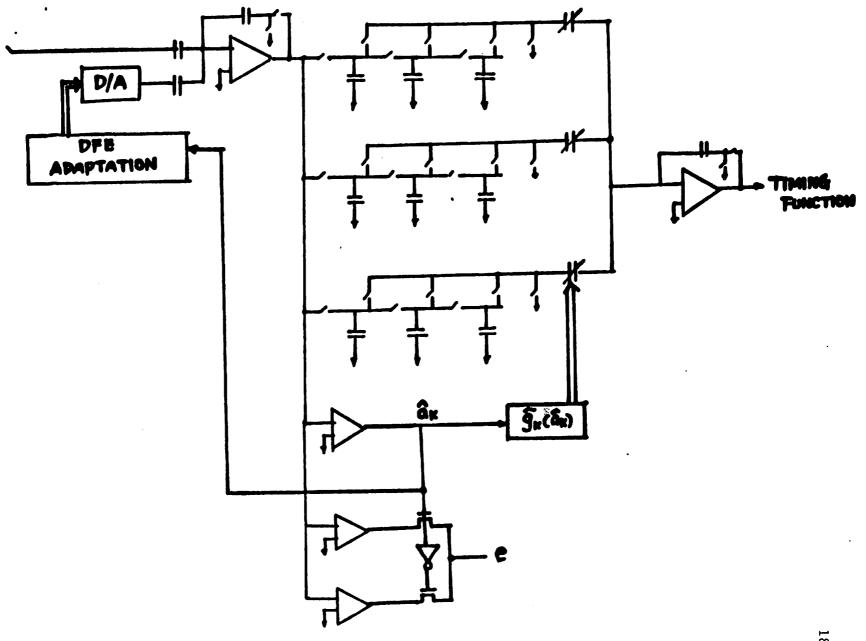

| 7.7.1 Digital Timing Recovery and DFE                                            | 178 |

| 7.7.2 Analog Timing Recovery and Digital DFE Adaptation with Analog Cancellation | 179 |

| 7.7.3 Fully Analog DFE and Timing Recovery                                       | 181 |

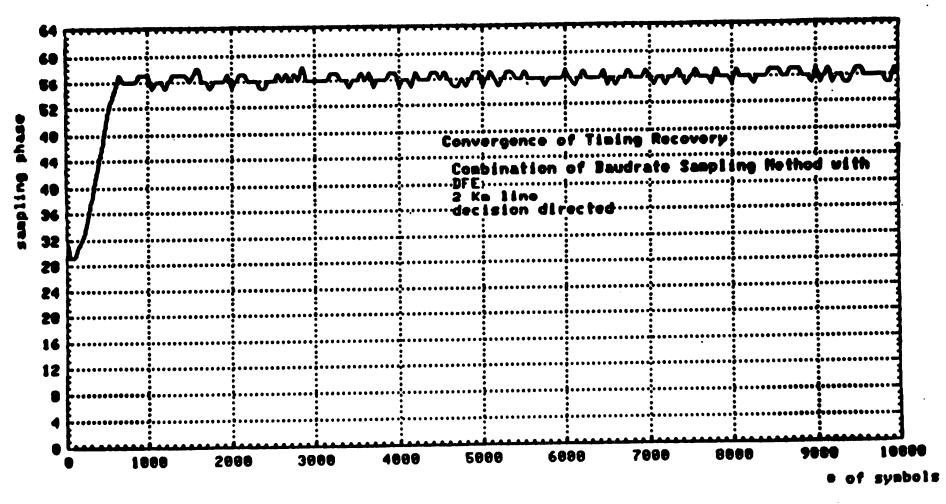

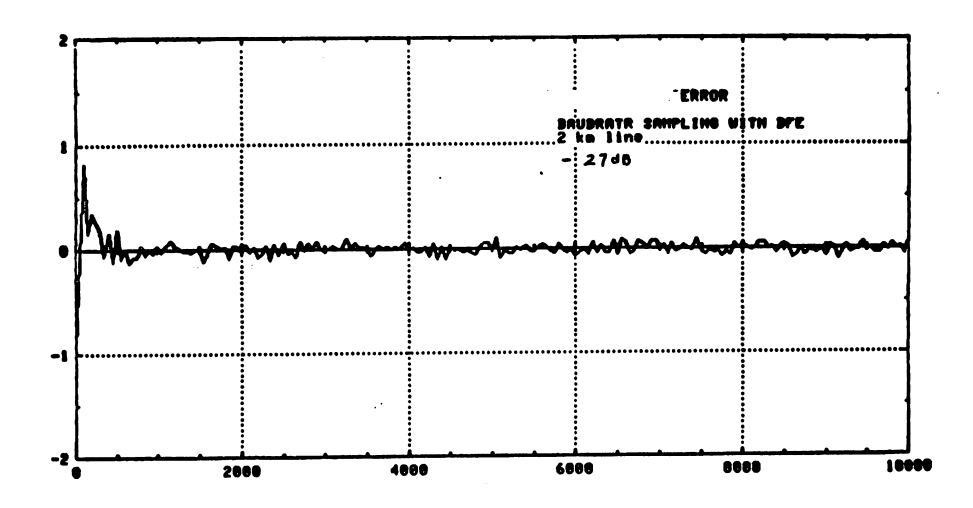

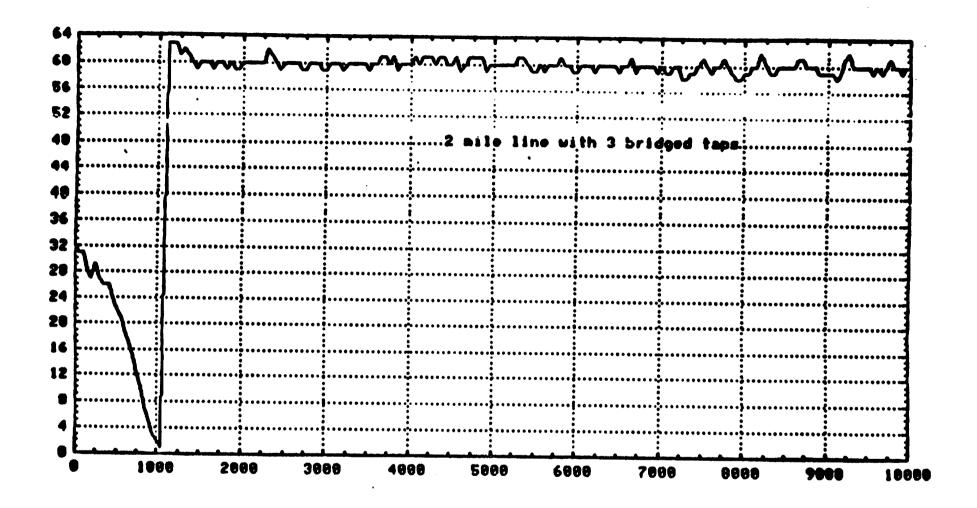

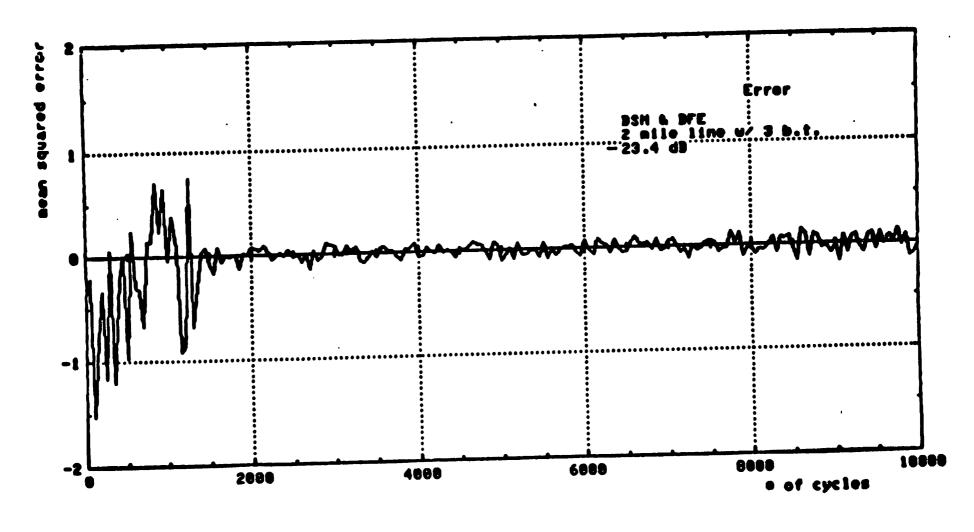

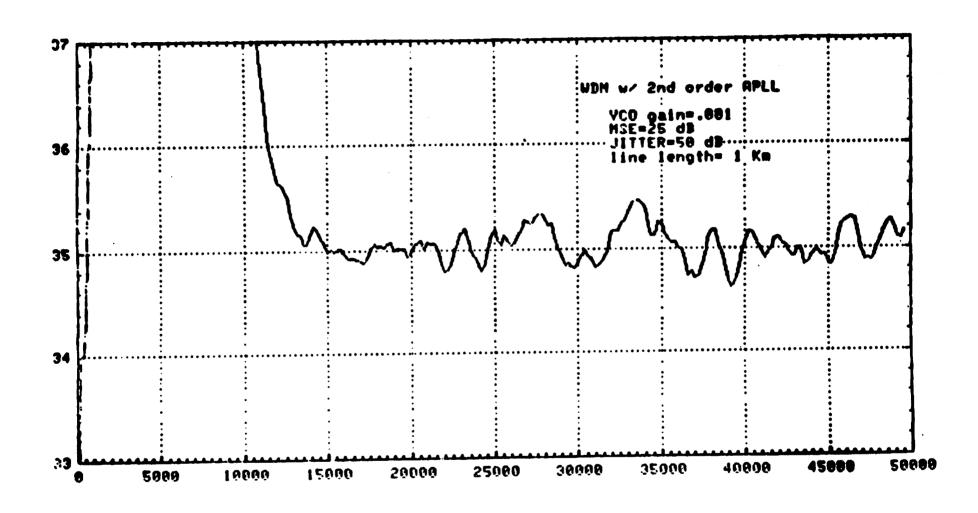

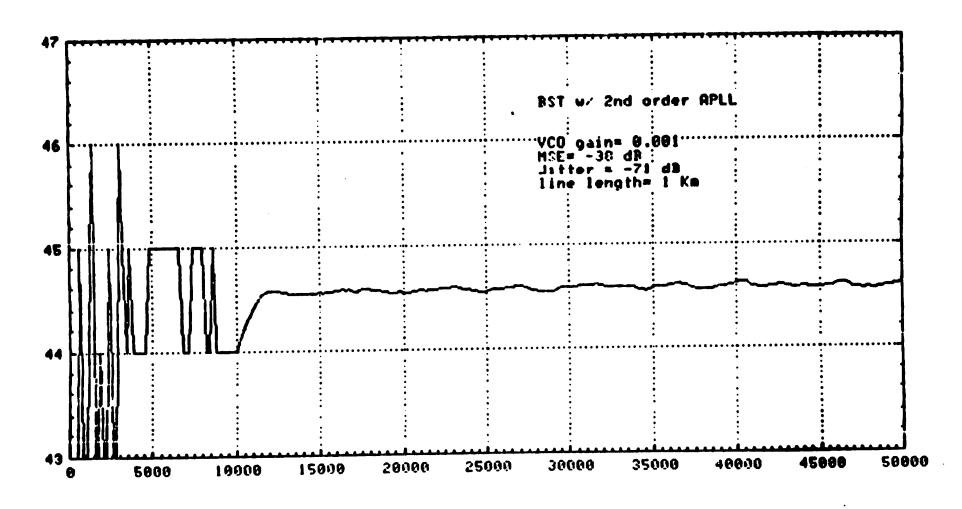

| 7.8 Simulation Results                                                           | 181 |

| 7.9 Experimental Results                                                         | 189 |

| 7.10 Summary                                                                     | 191 |

| Chapter 8 - Conclusions                                                          | 192 |

| 8.1 Comparison of WDM and BST                                                    | 192 |

| 8.2 Computer Simulation of Echo Canceller Alternatives                           | 194 |

| 8.3 2-stage echo canceller                                                       | 199 |

.

•

## CHAPTER 1

#### Introduction

Evolving plans for the Integrated Services Digital Network (ISDN) will be introduced into use over the coming years. At present, public-switched telephone networks (PSTN's) are generally becoming more digital in nature, with the increasing use of 64 kb/s Pulse Code Modulation (PCM) switching and transmission. This trend will gradually lead to a multi-service ISDN in which end-to-end digital connectivity exists and through which a multiplicity of services (voice and non-voice) are accessible by the customer.

An ISDN can be regarded as a general-purpose digital network capable of supporting a wide range of services (such as voice, data, text, and image) using a small set of standard multipurpose user-network interfaces. The activities in setting standards on various aspects of ISDN's to prepare an orderly evolution into ISDN have been actively taken up by the International Telegraph and Telephone Consultative Committee (CCITT).

#### 1.1. Digital Subscriber Loops

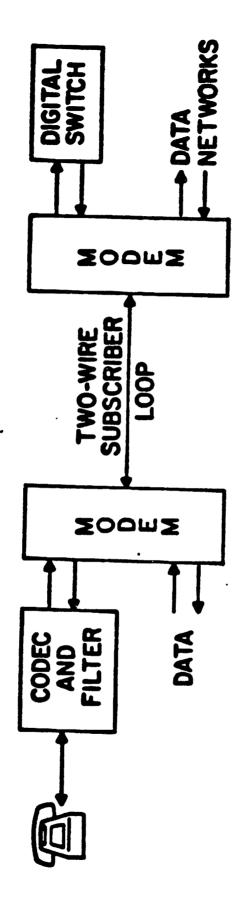

The digital subscriber loop (DSL) is an important element of the ISDN. Integrated voice and data services will be provided to the customer over a common facility based upon existing twisted-pair cables. The data rate under consideration for the digital subscriber loop is 144 Kb/s, which includes provision for two voice/data channels at 64 Kb/s each plus a data channel at 16 Kb/s. As shown in Figure 1.1, representing a typical application of DSL, voice transmission requires a codec and filter to perform the analog-to-digital and digital-to-analog conversions on the customer premises, together with a modem for transmitting the full-duplex data stream over the two-wire

Figure 1.1. A typical application of DSL, where 2 voice channels, 64 kb/s each and 1 data channel at 16 kb/s can be transmitted simultaneously in full-duplex fashion.

subscriber loop. The central office end of the loop has another full-duplex modem, with connections to the digital central office switch for voice or circuit-switched data transmission, and to data networks for packet-switched data transport capability. Throughout this thesis, the term "DSL modem", representing a combination of modulator and demodulator, will be used interchangeably with the term "DSL transceiver", representing a combination of transmitter and receiver.

Full-duplex transmission on a single pair of wires requires a means of separating the signals in the two transmission directions. Two competing methods for the baseband full-duplex data modems are time-compression multiplex (TCM), also known as the burst mode or ping-pong technique, and the echo-cancellation (or hybrid mode) technique.

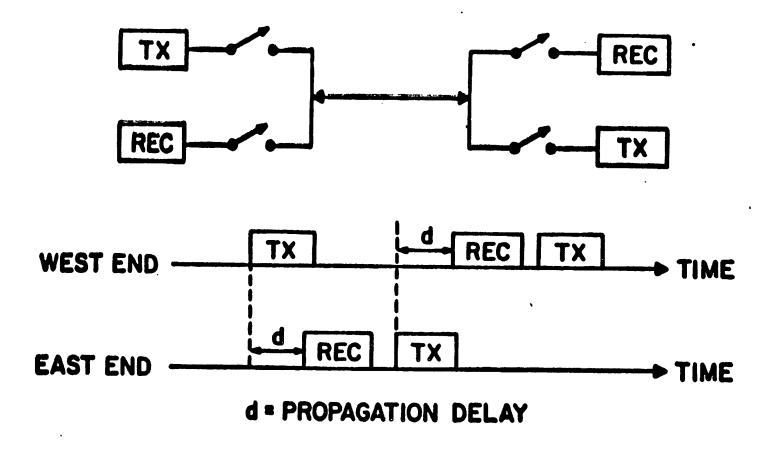

A TCM system divides the common medium in time, transmitting first in one direction and then in the other. The two ends transmit bursts alternately, as shown in Fig. 1.2. A guard time is necessary between the bursts to ascertain that the residual reflections from the burst will not be detrimental to the reception of far-end data. These reflections die down rapidly after the end of the bursts but lingering effects prevail due to mismatch and bridged tap effects. The required line data rate is, therefore, more than twice the data bit rate in each direction.

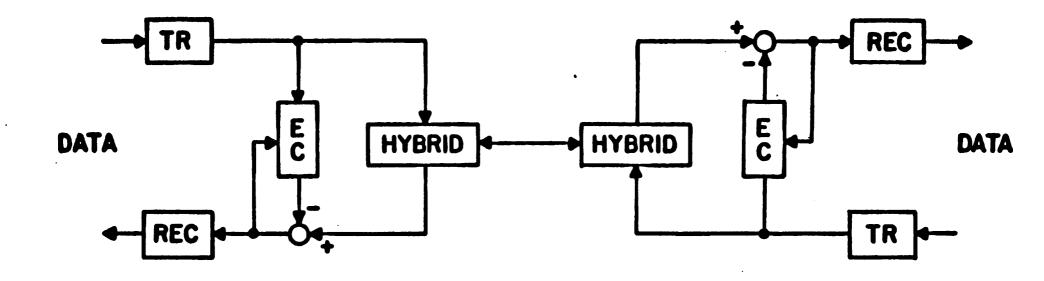

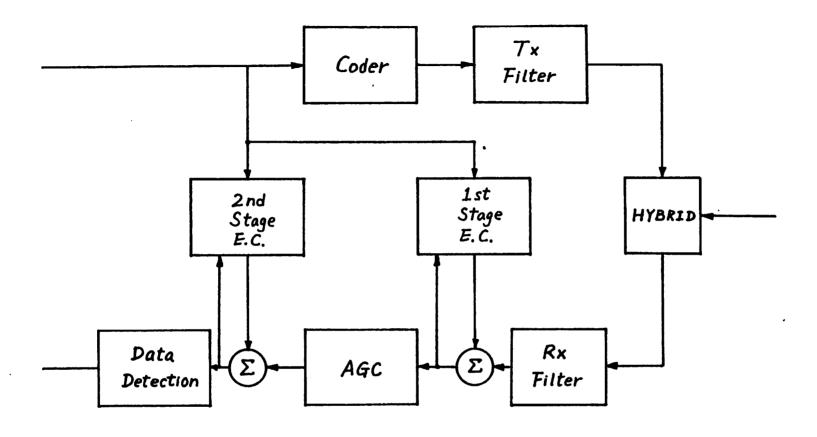

The alternative echo-cancellation mode system is shown in Figure 1.3. Both transmitters operate continuously. The signal received from the far end is corrupted by a large component of near-end signal, resulting from near-end hybrid unbalance, reflection from the far-end hybrid, or reflection from possible bridged taps. A self-adapting echo canceler, one in each modem, synthesizes a replica of the echo using the transmitting data. This replica is subtracted from the total received signal. Then only the desired far-end signal enters each receiver. The major advantage associated with this method is that the line rate is equal to the data bit rate (assuming binary data

Figure 1.2. A time compression multiplexing (TCM) mode DSL system, where time is divided into slots for two sides to transmit one burst at a time.

Figure 1.3. A block diagram of an echo cancellation DSL system, also called hybrid mode system. An echo canceller is used to separate the two-way signals on the same pair of wires.

transmission). Overall, the echo canceller and subtracter must reduce the unwanted signal by 50-60 dB. This is a challenging requirement.

There has been considerable work on techniques for and realization of the echo canceler for DSL systems [1-6]. Large scale integration of the echo canceller for hybrid-mode modems has been shown to be quite feasible [1]. Any nonlinearity introduced by asymmetry of the transmitted pulse, A-D or D-A conversions, and nonlinear transformers, etc. can also be compensated with a nonlinear echo cancellation technique [2].

This thesis focuses on the timing recovery in DSL. The detailed consideration and requirements of the timing recovery in DSL are described in Chapter 3. The emphasis is on the timing recovery techniques that are suitable for integrated circuit realization. Sampled-data techniques are the most practical means of obtaining the necessary signal processing functions in VLSI form. The necessary signal processing functions include transmit and receive filtering, line coding, echo cancellation, equalization, and data detection. The two sampled-data timing recovery methods, the wave difference method and the baudrate sampling technique, to be described in later chapters, are applicable to both the burst mode and the echo cancellation systems. They also apply to a variety of line codes.

#### 1.1.1. Comparison Between TCM and Echo Cancellation Systems

The echo cancellation DSL system is more complex in implementation due to the presence of the echo cancellation and the stringent requirements associated with the echo canceller. However, the following points also contribute to the performance comparison of the two.

1) Line attenuation. The line rate in a TCM system is greater than twice the line rate of a echo-canceller system with the same data line because of the need for a guard time

and the time-domain multiplexing in the burst-mode system. The line attenuation is thus higher in the burst-mode system.

- 2) penetration range. Since the maximum transmitted level is limited by compatibility with other services, and the minimum received level is limited by impulse noise and/or crosstalk from other services, the maximum range of penetration is lower for burst-mode than for echo-cancellation.

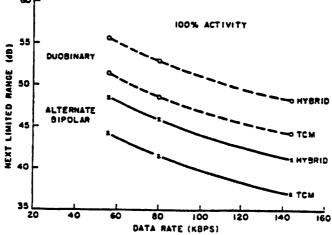

- 3) crosstalk limitation. Reference [7] gives results of very detailed analysis of crosstalk and impulse noise limitations for both systems. Fig. 1.4, reproduced from that reference, shows that the range of an echo-cancellation system is typically about 7dB larger than for burst-mode system. It is also deduced from this reference that the crosstalk may be the most crucial limiting factor in terms of the range and data rate of a DSL system.

#### 1.2. Line Coding and Pulse Shaping

Line coding techniques have been extensively studied since the emergence of local networks and the ongoing evolution of the public telecommunication network to digital service. Line coding, also referred to as digital line coding or digital signaling, is usually used in broadband communication systems where the bandwidth of the channel is much wider than the spectrum of the signals. Examples are baseband local networks, including low bit rate data transmission on twisted-pairs and Ethernet on coaxial cables, and short loop digital PBX connections for terminals, hosts, and digital phones. In such systems, the transmission media cause little distortion of the pulse due to their wide bandwidth, and digital waveforms can be transmitted and received with little or no distortion.

However, in transmission systems where the channel bandwidth is limited, digital transmission with analog forms are more reliable. In such cases, pulse shaping filtering

Figure 1.4. Range of TCM and echo cancellation (hybrid mode) systems, as limited by the far end cross talk (FEXT) and the near end cross talk (NEXT). Reproduced from reference [7].

provides the analog formation. Nyquist waveforms with limited spectrum and zero intersymbol interference at the symbol intervals are typical examples of shaped pulses. The filtering involved is generally low pass filtering. In addition to limiting the spectrum of the pulses, it can also filter out the high frequency noise picked up along the transmission channel. The filtering, if placed at the transmitter, limits the high frequency components of the pulses which can interfere with the other transmission systems. If placed at the receiver, it can eliminate the out of band noise which could come from other transmission systems. A split form of filtering, half at the transmitter and the complex conjugate at the receiver can also provide matched filtering for optimizing the signal to noise ratio.

A proper combination of digital line coding technique with a pulse shaping function can preserve the advantages of the two, and is the preferred system configuration.

#### 1.2.1. Digital Line Coding

A digital signal is a sequence of discrete, discontinuous voltage pulses. Each pulse is a "symbol". The repetition rate of these pulses is called the symbol rate, or more commonly, the baud rate. The two important characteristics of a digital signal to be determined at the receiving end are the timing information and the data sequence. The associated properties which affect the determination of timing and data at the receiving end are spectrum bandwidth, error-detection capability, signal synchronization capability, and immunity to the channel impairments.

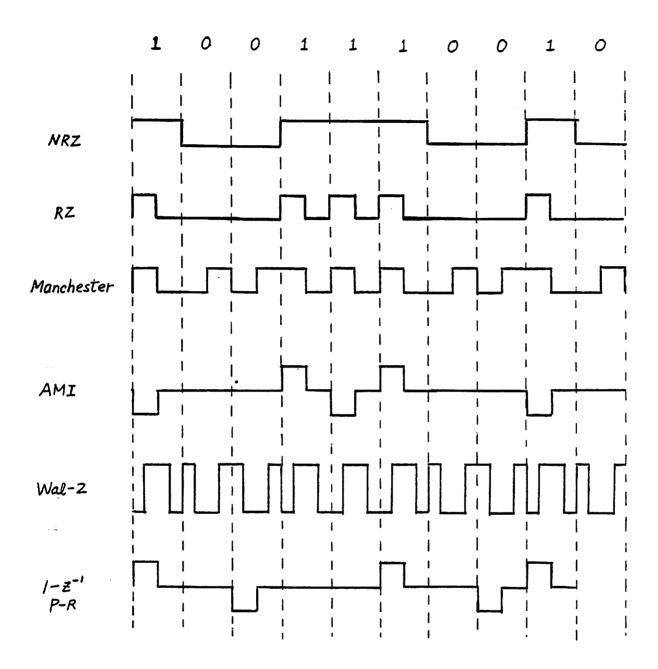

The line coding schemes which are of interest to us fall into the following categories: Non-Return-to-Zero (NRZ), Return-to-Zero (RZ), Biphase (or Manchester), Bipolar (or AMI), Partial-Response (PR), and Wal-2 code. NRZ and RZ codes, because of it binary nature, are also classified as binary coding. Each category has its own variations. The details of these line codes are illustrated in Fig. 1.5. Some aspects of these line codes will be discussed in the following.

Figure 1.5. Summary of various line codes.

Even in broadband transmission, the bandwidth of the spectrum of the signal is desired to be as low as possible. Bandwidth is an expensive asset, because noise and interference increase with the bandwidth required for the signal. The elimination of the DC component in the signal spectrum is also an important factor if AC coupling is to be used. NRZ is the simplest code, it also efficiently uses the bandwidth. The main limitations of the NRZ are the presence of the DC component and the lack of synchronization capability. RZ is basically the same as NRZ except it takes more bandwidth. Bipolar code is a nonlinear-processed version of NRZ by ensuring alternate positive and negative going pulses to remove the DC component. Note the 3 level property of the bipolar coding and the correlation between the various levels. Manchester and Wal-2 codes are DC free and require more bandwidth. Various partial-response codes have different properties. Generally, they require less bandwidth and 3 level transmission. Some PR codes also have no DC component.

Manchester code uses more bandwidth to ensure a predictable transition in the middle of each interval. The receiver can use this information for timing recovery and error detection. However, if the channel introduces substantial pulse distortion, the property will be lost.

For the same dynamic range, the codes with 3 levels lose some signal-to-noise ratio if the noise level is constant. This results because the distance between any two adjacent levels in a 3-level transmission is only half that of the 2-level transmission if the total dynamic range is fixed. Considering the bandwidth, the less bandwidth a code takes, the more immune to noise it is.

Although digital line coding is more frequently used in the broadband case where equalization is generally not necessary, some codes provide advantages with respect to equalization. This property becomes more important as the line coding is used with subsequent pulse shaping for a channel with limited bandwidth. Intersymbol interfer-

ence caused by the dispersion of pulses is one of the major obstacles to error-free transmission. Pulses normally experience trailing type dispersion (postcursor) in most channels, and the dispersion is a major source of *intersymbol interference (ISI)*. If a symbol has equal positive and negative pulses, the trailing tails tend to cancel and the resulting effective channel impulse response is shorter, and the ISI is also reduced. This property will be referred to as "self-equalizing", and will be exploited more later. Manchester and Wal-2 codes have this property, as do some forms of partial-response.

Some of the characteristics mentioned above change if the pulsing shaping follows the line coder. For example, the signal spectrum will be the overall spectrum of the line code and the filtering.

The convolutional coding, or trellis coding, inserts redundancy into the data sequence. In conjunction with maximum likelihood detection, which can easily be realized with a Viterbi decoder, trellis coding offers superior performance to uncoded signals in a noisy environment [54].

If adaptive filtering is used, whether in the equalization or in the echo cancellation, the convergence characteristic is a function of the signal spectrum and the correlation within the data sequence. It will be shown later that AMI coding, although it removes the DC component, is inferior to binary or partial-response coding in convergence speed.

#### 1.2.2. Pulse Shaping

Overlapping of pulses may cause intersymbol interference. Nonoverlapping requires that a pulse be confined to one time interval. A signal limited in time requires infinite bandwidth. However, symbols can overlap and yet still be free of intersymbol interference, because in a sampled-data system intersymbol interference is only defined at certain time instants. Decisions in data communication are made in discrete time. It turns out that pulses satisfying Nyquist criterion have zero crossing at multiples of

certain time intervals and have limited bandwidth. Nyquist pulses have been widely used in data communication due to these properties. If the timing can be properly recovered and if there is no distortion in transmission, data can be received without intersymbol interference. In the presence of channel distortion, some means of equalization must be used.

Special pulse shapes can be designed such that the precursor intersymbol interference is zero. The interference before the main pulse is referred to as precursor intersymbol interference. And that trailing the main pulse is called postcursor intersymbol interference.

#### 1.2.3. Combining Line Coding and Pulse Shaping

By combining the digital line coding with proper pulse shaping, we can fully utilize the existing knowledge on line coding developed for broadband system for systems with less bandwidth. In fact, there is no clear boundary between the two, either conceptually or in implementation. Line coding, if linear, can be viewed as passing a sequence of binary weighted delta functions through a filter with the impulse response equal to the pulse shape. Similarly, nonlinear filtering applies to nonlinear line coding. However, an artificial boundary is useful from the implementation point of view. Line coding can normally be implemented in digital circuitry. On the other hand, pulse shaping, normally an analog operation, is considerably more complicated. Although digital filters can be used to perform the equivalent analog filtering function, this is generally not advantageous. Still in some cases, it is difficult to distinguish the two when they are combined together. The location of the function also plays a role. If the operation is done before the transmit filter, where the signal is in digital form, it can be viewed as precoding. If however, the same function is placed at the receiver, where the signal is in analog form, it is more reasonably viewed as equalization. Later in the application in the digital subscriber loops, we will exploit different forms of line coding

and pulse shaping, both at the transmitter and in the receiver.

#### 1.3. Echo Cancellation

The echo canceller is one of the most critical components in the echo cancellation method digital subscriber loops. Although it is not the focus of this thesis, it deserves special attention, because it affects the requirements of the timing recovery. A practical system requires the echo canceller to achieve a 50-60 dB echo cancellation. In other words, the average power of the residual echo after the echo canceller must be at least 50-60 dB lower in magnitude compared to the echo power before cancellation. This stringent requirement places constraints on the nonlinearity allowed in the echo channel or in data conversions. It also limits the allowable jitter of the clock used to sample the received signal. Note that this clock is also used in the transmitter in synchronous fashion as required in the digital subscriber loops. The actual constraints on the nonlinearity depend on the the method of implementation. A 60 dB echo cancellation requires that the timing jitter be limited to  $\frac{1}{1000}$  of a data period. This condition basically prohibits the use of digital phase-locked loops (DPLL) unless some interpolation technique is used [8].

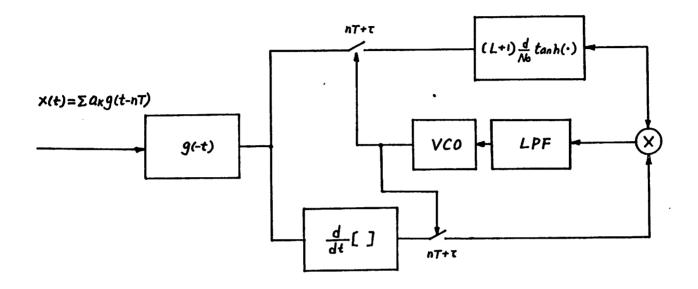

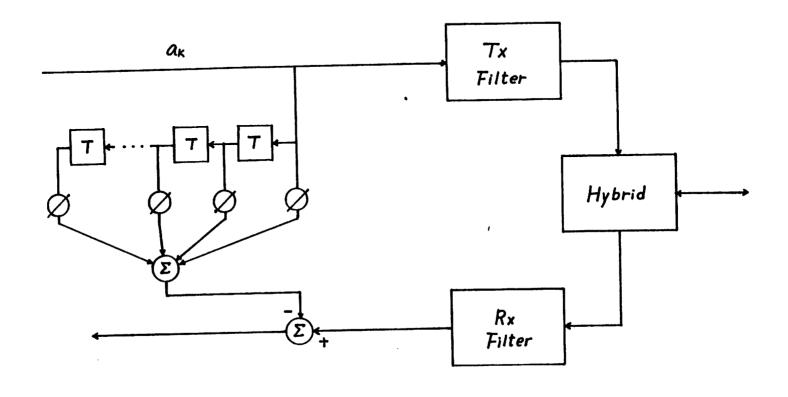

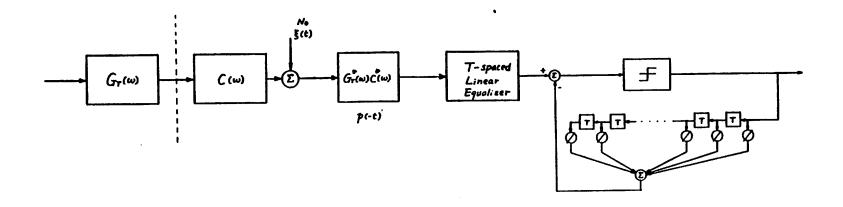

The complexity of the echo canceller, no matter how it is implemented, depends heavily on the subsequent processing. Data detection, post-equalization, and timing recovery must all be performed after the echo cancellation. Data detector together with a T-spaced transversal filter type linear equalizer operates at the baudrate, and as a consequence, can work with a baudrate operated echo canceller. Most timing recovery techniques require at least two samples per baud to retrieve the timing information from the data signal. As a result, the echo canceller must be operated at twice the baudrate to provide those samples to the timing recovery block. The complexity of the echo canceller increases linearly with the sampling rate. The conversion speed of the data conversion circuits, if any, must also be speeded up accordingly.

#### 1.3.1. Echo Canceller Structures

The echo canceller uses the digital data from the transmit section to reproduce the echo by synthesizing the echo path using adaptation algorithms. The replica of the echo will then be subtracted from the received signal in the receiver section to complete the echo cancellation function. There are many adaptive filter structures and adaptation algorithms to choose from. Two structures being considered for I.C. realization are the transversal filter structure and the look-up table structure. In the look-up table structure, the adaptation is normally done in the digital domain. The echo replica is stored in a memory, usually a RAM, to be addressed by the transmit data sequence. The addressed data, the replica of the echo, are read out, subtracted from the received signal, and then updated before being written back into the same location. The actual cancellation may take place in either analog or digital domain. A digital-to-analog converter is used to convert the memory readout into analog voltage for analog cancellation. Likewise, an analog-to-digital converter is used in the digital approach to convert the received signal into digital form for digital subtraction. For the digital subscriber loop application, where the data rate is in the range of 144 kbps, A-to-D converters with the required linearity are not yet feasible in VLSI technology. Analog subtraction is, therefore, the dominant approach in the look-up table structure.

There are more varieties of transversal filter structure. It is reasonable to pursue digital means for adaptation and filtering because the echo canceller is driven by digital data. Nevertheless, these functions can also be done easily in the analog domain. With the options of analog or digital subtraction, analog or digital adaptation, and analog or digital filtering, there are 4 combinations considered as candidates for VLSI integration [1,9]. The fully analog implementation performs all the required functions in analog domain without any data conversion. This solves the problem of nonlinearity in the data conversion. In view of currently known analog capability in CMOS technology, it

should be an attractive approach for VLSI realization. It was however determined not feasible because of the small step size required which in turn calls for large capacitor ratios in the switched-capacitor circuitry[9]. The problems associated with the large capacitor ratios are severe enough to rule out this approach. The small step size came about because there were no ways to cancel the far-end signal from the error terms used for adaptation [9]. The situation changes as the baudrate sampling technique, described in full detail in Chapter 7, is successfully developed.

#### 1.3.2. Fully Analog Approach

Two recent developments provided methods to cancel the far-end signal from the error terms. The adaptive reference echo cancellation (AREC) uses a reference former to reproduce the far-end signal to be subtracted from the error term [10]. The reference former, being a transversal filter with the received data as input, can be operated in a time-interleaved fashion to reform the far-end signal at sampling rates higher than data rate. The inevitable delay in the feedback was shown to be no problem if the step size is small.

The other new development is a new technique to recover the timing with sampling rate equal to the data rate, and is thus termed the baudrate sampling technique throughout this thesis. Employing a specific pulse shaping method, this timing recovery technique resolves a timing phase with nearly no precursor intersymbol interference. The far-end signal can then be reproduced using past decisions in an adaptive decision feedback equalizer (DFE) with no delay. A structure with a combination of echo canceller and DFE was proposed before. [11]. It has never been reduced to practice, however, for to two reasons. First, any precursor intersymbol interference of the far-end signal cannot be effectively eliminated. Secondly, no previously known method to recover timing using baudrate sampling was proven reliable. The baudrate sampling timing recovery technique, which will be discussed in much more detail in Chapter 7.

brought new life to the combined structure of echo canceller and DFE. This is a better approach than AREC because in addition to offering cancellation of far-end signal with no delay, it allows a simpler echo canceller. More importantly, the capability to eliminate the far-end signal completely and to recover timing at the baudrate allows a much larger step size for the same degree of echo cancellation. Therefore, the fully analog combination of echo canceller and DFE becomes a viable approach.

The all-analog approach eliminates the need for data conversions. This provides the advantages of eliminating an important source of nonlinearity and its simplicity leads to a small area in VLSI implementation. Other nonlinearities in the echo path (including the hybrid or transmitted asymmetry of pulses can be removed with the nonlinear echo cancellation technique developed by O.Agazzi [2].

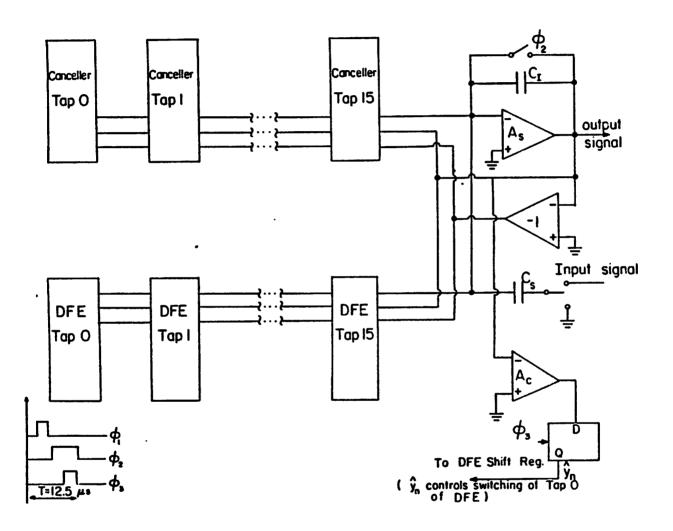

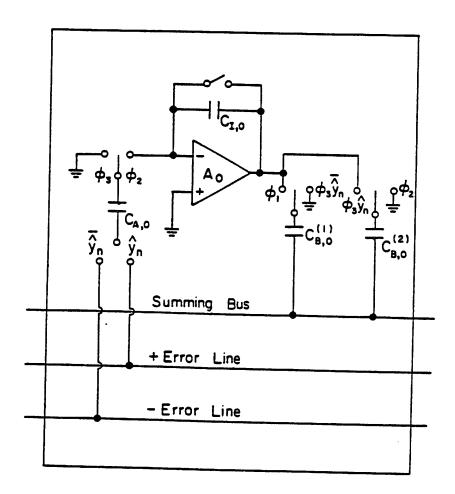

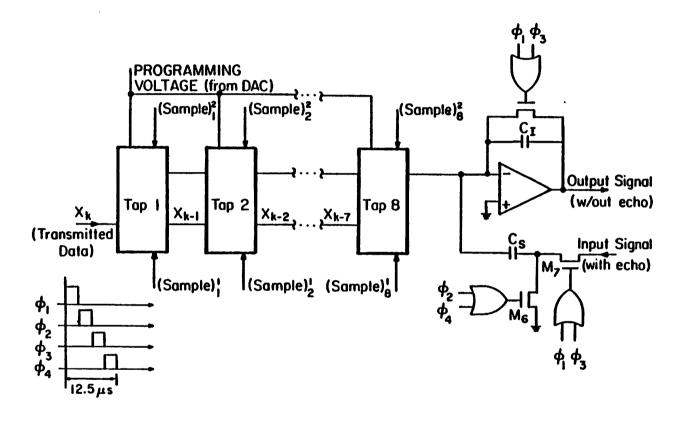

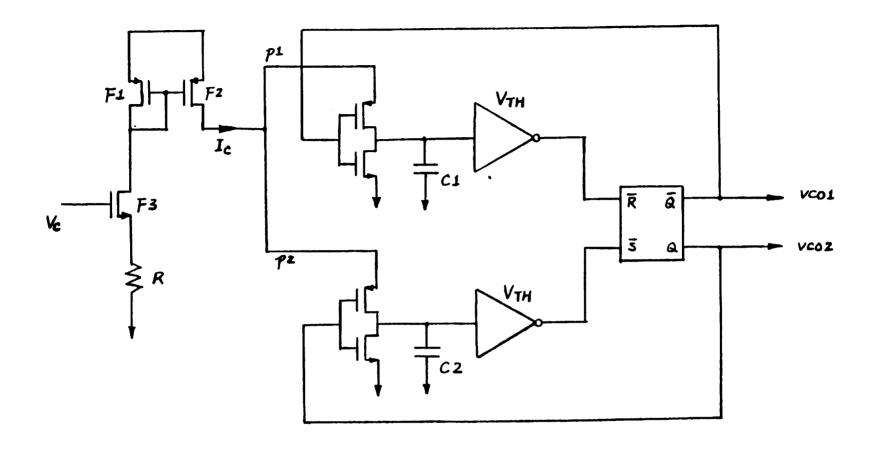

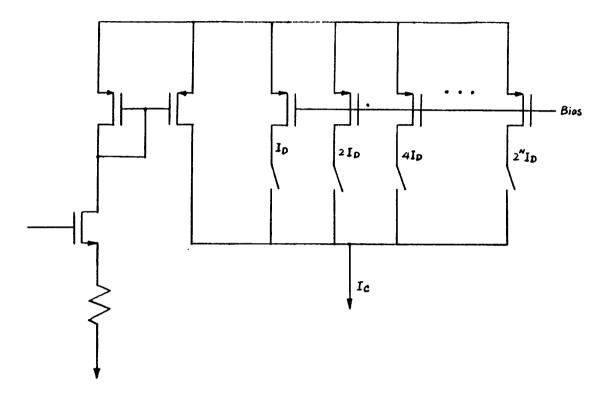

## 1.3.3. Implementation Alternatives for the Fully Analog Approach

A straightforward implementation of the all analog echo canceller was described in great detail in [9]. Figures 1.6-1.8, reproduced from [9], illustrate in block diagram form the all analog approach of the combined echo canceller and DFE in Fig. 1.6, the details of the echo canceller taps in Fig. 1.7, and DFE taps in Fig. 1.8. The combination of echo cancellation and DFE together with the baudrate sampling timing recovery make possible both a larger step size, and in turn, the switched capacitor approach which is shown in these figures. Experiment showed that a step size of 0.3 is sufficient. A step size of 0.5 was also shown to perform well in a computer simulation.

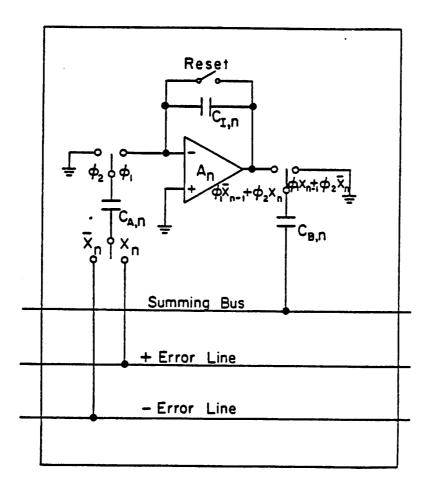

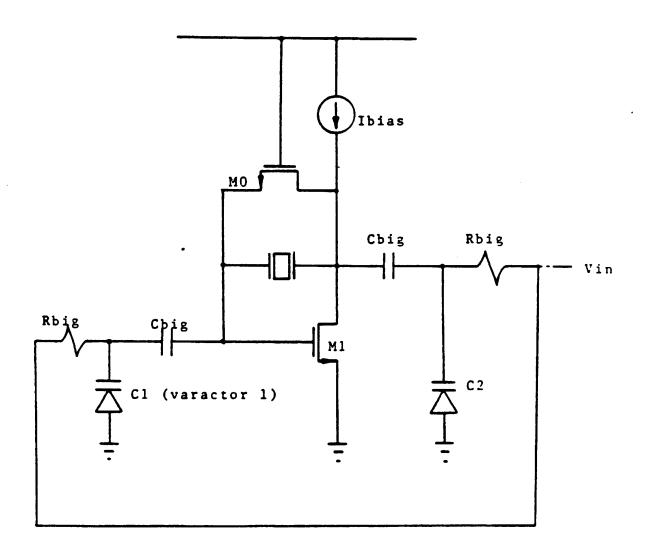

A more exotic implementation alternative is to use capacitors to store the tap coefficients and source followers to buffer the storage from the summing circuitry, rather than using a sample-and-hold amplifier for each tap coefficient. This results in a great saving of area and components. This structure was used in [9] in the analog-digital echo canceller to implement the transversal filter. The block diagram and the circuit schematic of the taps are shown in Figs. 1.9 and 1.10 respectively.

Figure 1.6. A simplified circuit schematic of a fully analog implementation of the combination of echo canceller and decision feedback equalizer (DFE). Details of the taps are in Figs. 1.7 and 1.8.

Figure 1.7. Detail of an echo canceller tap as used in Fig. 1.6.

Figure 1.8. Detail of a DFE tap as used in Fig. 1.6.

Figure 1.9. Circuit schematic of an analog implementation of a transversal filter echo canceller, the correction term for the tap updating comes from a digital update logic via a DAC. The taps are shown in Fig. 1.10.

Figure 1.10. Circuit schematic of an echo canceller tap, using a capacitor for tap coefficient storage and a source follower as an output buffer for summation.

In the analog-digital echo canceller, the adaptation was performed with digital circuits in digital domain and then converted via a D-to-A for analog transversal filter. Here we propose to replace the adaptation and D-to-A circuits with a single echo canceller tap described in last section and shown in Fig. 1.7. The analog filter design as shown in Figs. 1.9 and 1.10 had been fabricated and proven experimentally to be satisfactory[9]. Note that the adaptation is updated periodically rather than continuously. The speed of convergence is slower, but the final resolution is not affected.

A unique feature offered by both these analog implementations is that the true stochastic-gradient algorithm can be employed for tap adaptation, whereas in most other approaches, the sign algorithm is more commonly used for implementation reasons. The benefit from this feature is small residual error and faster convergence.

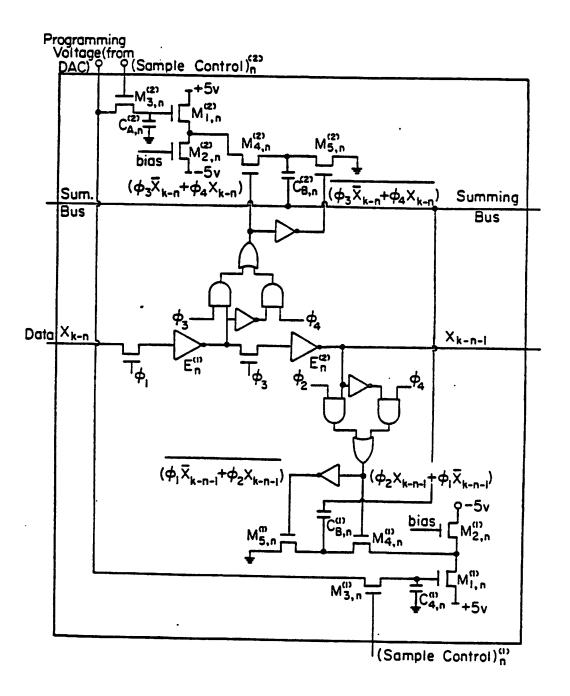

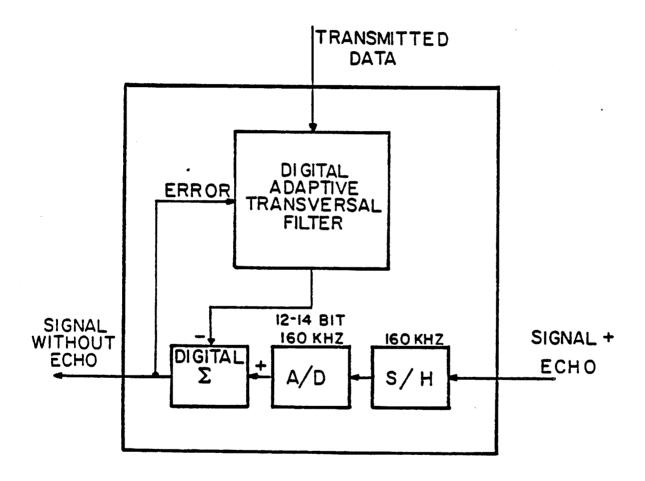

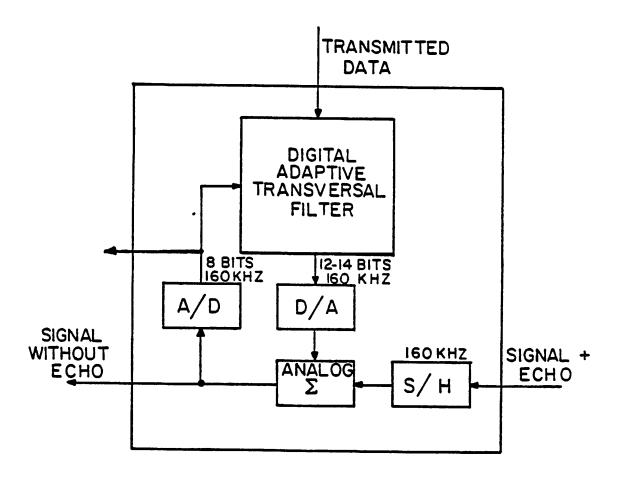

#### 1.3.4. Other Transversal Filter Structures

Other implementation alternatives have been studied extensively elsewhere [9]. They are shown in Figs. 1.11-1.13, again reproduced from [9]. The operating rate of these echo cancellers was originally at twice the data rate. With the new baudrate sampling technique, the number of taps can be reduced by a factor of 2, and the required speed of the data conversions is also reduced by the same factor.

#### 1.4. Summary

In this chapter, the integrated services digital network (ISDN), the two possible implementations of digital subscriber loop systems, the comparison of the two, and the limiting factors were introduced. Line coding and pulse shaping, which are important design issues of the system, also have considerable impact on the equalization and timing recovery. There is a need to understand the complexity of implementation for the echo canceller, which affects and is affected by the timing recovery design. A description of the components in a DSL transceiver is in Chapter 2. The detailed description

Figure 1.11. Digital echo canceller, where the incoming signal is digitized, and all the signal processing and cancellation is done in digital domain.

Figure 1.12. Digital transversal filter with analog cancellation. D/A is used to convert the echo replica to analog domain for cancellation, A/D is used to convert the echo-free signal for adaptation, and possibly further signal processing. e.g., equalization and timing recovery.

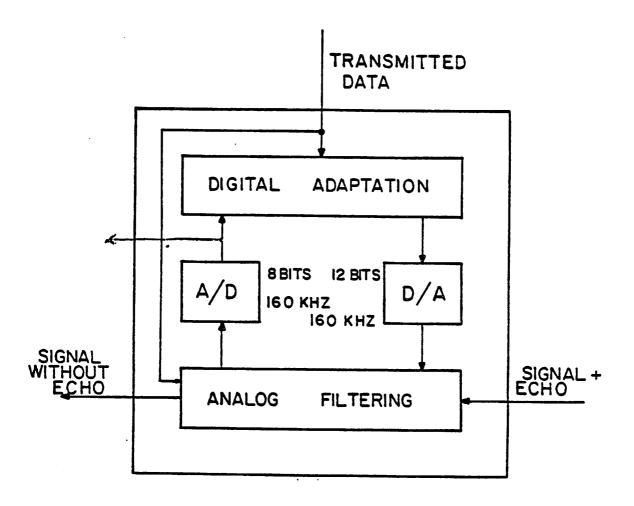

Figure 1.13. Analog/digital echo canceller, transversal filter is in analog domain with digital adaptation.

and requirements of the timing recovery is provided in Chapter 3, where the interrelated design issues of the timing recovery, the echo canceller, and the equalization will also be addressed. The two most promising timing recovery methods will be described in Chapters 6 and 7, following the chapters on the phase-locked loops and equalization.

#### CHAPTER 2

## System Design

In Section 2.1, the analysis of several system parameters will be summarized, so will be certain important building blocks. A description of the components involved in a full-duplex modem will be considered in Section 2.2. This chapter draws heavily on Chapter 2 of the thesis by Agazzi [9].

#### 2.1. Design Parameters and Techniques

Basic techniques like echo cancellation, equalization and timing recovery will be introduced in this section. The specifications associated with these functions will also be given.

#### 2.1.1. Error Rate Objectives

The error rate, which can be translated to the signal-to-noise ratio requirement, for a given communications system depends on the statistical distribution of the disturbance. The main sources of disturbance in the context of a digital subscriber loop (DSL) are echo, crosstalk, and impulse noise. Thermal noise, on the other hand, can be ignored because it is much smaller than the other sources mentioned. The crosstalk noise can be adequately modelled by a Gaussian distribution when the number of crosstalk interferers is large. The residual echo error after echo cancellation is random and bounded. Its distribution has been modelled as "approximately Gaussian" [12] and as "uniform" [9] by different people. In either case, if the variance of the crosstalk noise is much higher than that of the residual echo noise, the composite noise distribution will be dominated by that of the crosstalk noise, and vice versa. Impulse noise is generally characterized in terms of the number of events per unit time, instead of its

statistical distribution. It is much more difficult to deal with, and so it will not be considered. Generally speaking, a signal-to-noise ratio of 20 dB gives us enough margin for a comfortable error rate.

#### 2.1.2. Echo Cancellation

The two basic structures considered for echo canceller were introduced in Chapter 1, they are the transversal structure and the look-up table or memory structure. In this section, we will present the adaptation algorithm and the associated parameters that governs the convergence speed and the residual error [6].

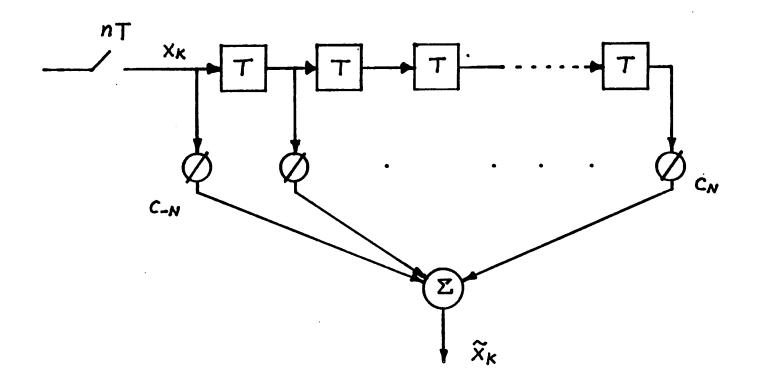

Although other algorithms have been proposed in the literature [13,14], the least mean square (LMS) algorithm has gained widespread acceptance in adaptive transversal filter because of its simplicity and efficiency. A small variation of the LMS algorithms leads to the stochastic gradient algorithm, where a simple iterative update equation can be formulated. For a transversal filter echo canceller which covers N band intervals, the N coefficients  $c_i(k)$  are iteratively updated according to

$$c_i(k+1) = c_i(k) + \alpha r(k) a(k-i)$$

(2.1)

where r(k) is the control signal at time kT,  $\alpha$  is the *step size*, and a(k-i) is the data symbol being transmitted from the local transmitter at time (k-i)T. The output of the transversal filter, the echo replica, is given by

$$\hat{e}(k) = \sum_{i=0}^{N-1} a(k-i)c_i(k)$$

(2.2)

and is subtracted from the received signal s(k) to yield the control signal  $r(k) = s(k) - \hat{e}(k)$ . If s(k) = e(k) + u(k), where e(k) is the echo signal and is linearly dependent on the local data a(k), and u(k) is the far-end signal independent of a(k), the adaptive filter will continuously try to minimize the root-mean square (rms) value of the residual error  $e(k) = e(k) - \hat{e}(k)$ . Note that in general the control

signal r(k) used for adaptation includes both the residual error  $\epsilon(k)$  and the far-end signal u(k), where u(k) can be comparable or small relative to the echo signal e(k) depending on the length and attenuation of the channel. The residual error  $\epsilon(k)$  is the driving force in the adaptation, and the far-end signal u(k) is a disturbing signal in the control loop. The performance of the adaptive filter is represented by its convergence characteristics, in which the rate  $R^2(k) = P(\hat{e}-e)/P(u)$  is given as a function of the time index k. Here  $P(\hat{e}-e)$  is the (short-time) average power of  $e(k)-\hat{e}(k)$  and P(u) is the average power of u(k) [6]. The convergence can be adequately characterized by only two parameters,  $\delta$  and  $\nu_{20}$ , where

$$\delta = \lim_{k \to \infty} R^2(k) \tag{2.3}$$

and

$$\nu_{20} = 1/\log(R(k)/R(k+1)), \quad R^2(k) \gg \delta$$

(2.4)

The parameter  $\delta$  characterizes the converged state and  $\nu_{20}$  is a measure for the initial speed of convergence for large values of  $R^2(0)$ . Here  $\nu_{20}$  represents the number of iterations required for 20 dB reduction of R(k). In practical circumstances it will always hold that  $KN \ll 1$ , and then

$$\delta \approx \alpha N / 2 \tag{2.5}$$

and

$$\nu_{20} \approx 2.30/\alpha \tag{2.6}$$

It should be clear from Eqs. (2.5) and (2.6) that the choice of  $\alpha$  allows a tradeoff between initial speed of convergence and final value. Note that this tradeoff can be expressed independent of  $\alpha$  as

$$\delta \cdot \nu_{20} \approx 1.15N \tag{2.7}$$

It is also clear from Eq. (2.1) that there are N updates to be performed per iteration,

and each update requires one multiplication. The number of taps is equal to N.

In the look-up table structure, the combination of N near-end data symbols is used as the address for a random access memory (RAM). The contents of the RAM at this address is the echo replica  $\hat{e}^k[a(k),a(k-1),...,a(k-N+1)]$ , corresponding to the combination of data symbols a(k),a(k-1),...,a(k-N+1) at time t=kT. If a certain address is read at time t=kT, its content is used firstly for echo subtraction, and subsequently updated with a correction term, while all the other contents remain unchanged. For the stochastic gradient algorithm, the updating is formulated as

$$\hat{e}^{k+1}[a(k),a(k-1),...,a(k-N+1)] = \hat{e}^{k}[a(k),a(k-1),...,a(k-N+1)] + \alpha r(k)$$

(2.8)

where  $r(k) = s(k) - \hat{e}(k)$  as before. The parameters  $\nu_{20}$  and  $\delta$  corresponding to this method are given by

$$\delta = \alpha/2 \tag{2.9}$$

and

$$\nu_{20} \approx 2.30 \cdot 2^N / \alpha \tag{2.10}$$

which yields

$$\delta \cdot \nu_{20} \approx 1.15 \cdot 2^N \,. \tag{2.11}$$

Note that there is only one update per iteration, and only one multiplication is needed. However, the size of the memory grows exponentially with N. For binary data, the memory size is  $2^N$ .

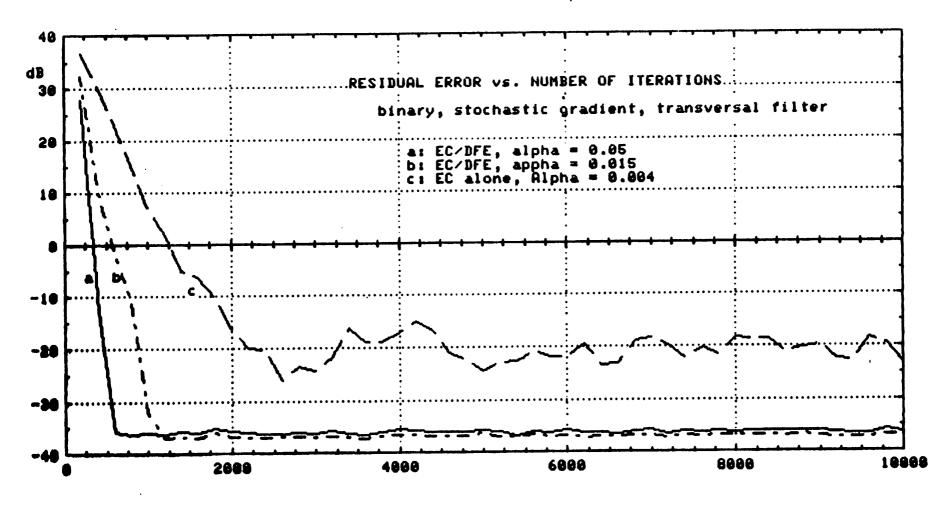

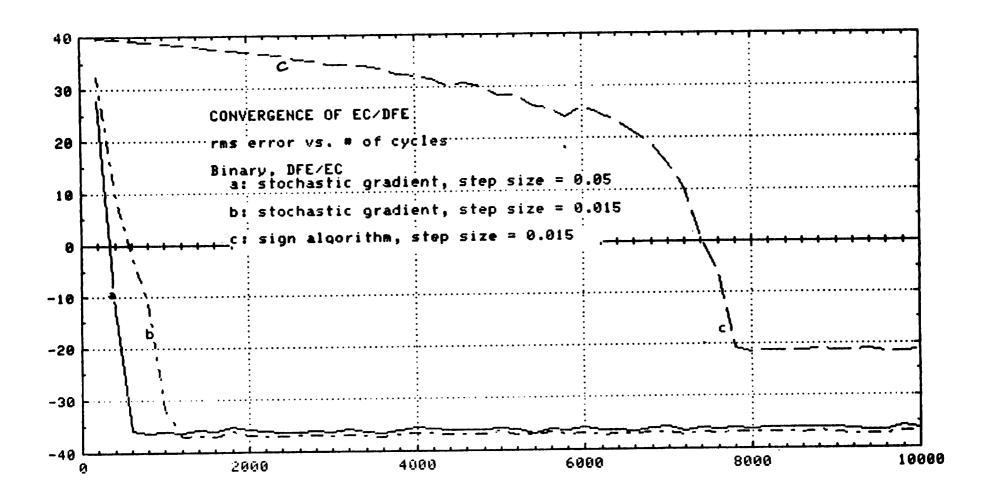

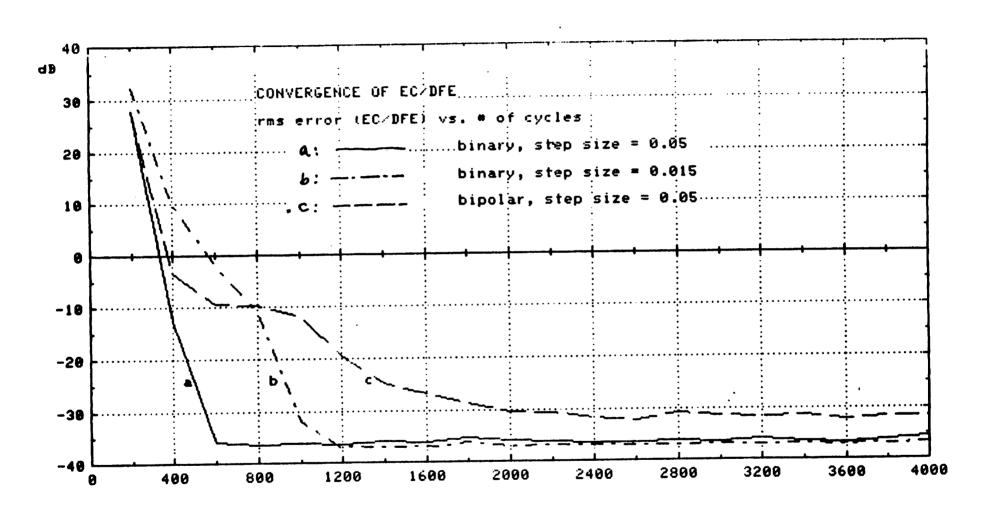

For 20 dB echo cancellation, where  $\delta = 0.01$ , and assuming N = 5,  $\alpha = 0.004$  and  $\nu_{20} = 600$  for the transversal filter case, and  $\alpha = 0.02$  and  $\nu = 3700$  for the look-up table. The small values of the step size  $\alpha$  comes from the distubing components in the control term due to the far-end signal.

There may be variations as to the updating methods, e.g., sign algorithm vs. stochastic algorithm; level of transmission, e.g., binary vs. ternary; and inclusion or exclusion of far-end signal in the control term. Some simulation results comparing those alternatives will be covered in Chapter 8.

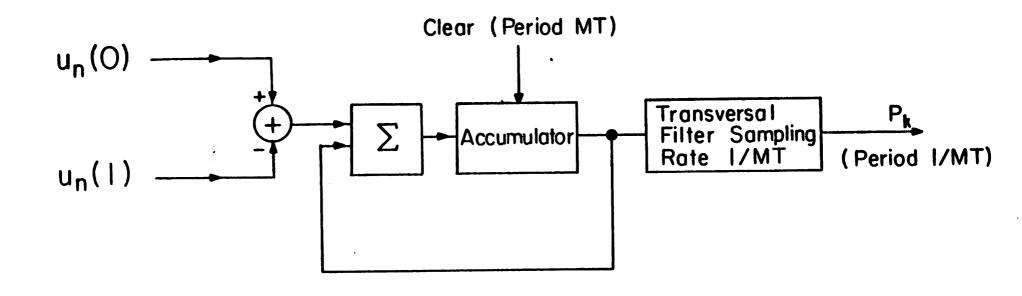

## 2.1.2.1. Interpolation Echo Cancellers

The echo canceller described in last Section normally puts out one echo-free sample per baud, which is generally sufficient for equalization and data detection. Timing recovery, another function that must be implemented in a DSL transceiver, needs echo-free signal to obtain a clock that is in lock to the far-end transmitter. More than one sample per baud may be required to perform timing recovery if a frequency domain approach is used, such as the spectral line method [20,24,26,30]. In order to preserve the spectrum of the received signal without aliasing distortion, the sampling rate must be at least twice the bandwidth of the signal. Typically the spectrum of the data signal extends beyond  $\frac{1}{2}f_b$ , often as high as  $f_b$ , where  $f_b$  is the data rate.

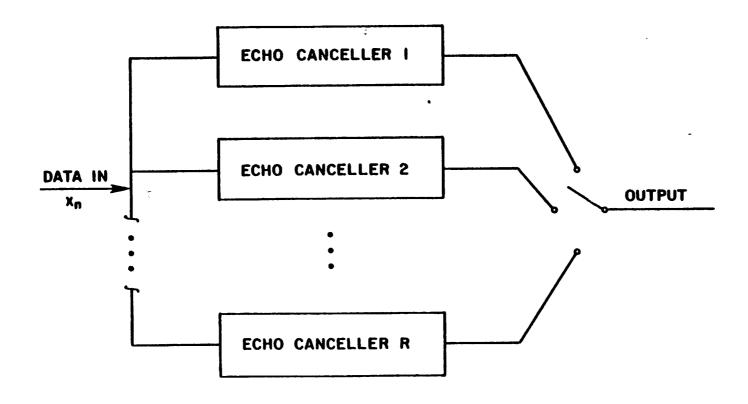

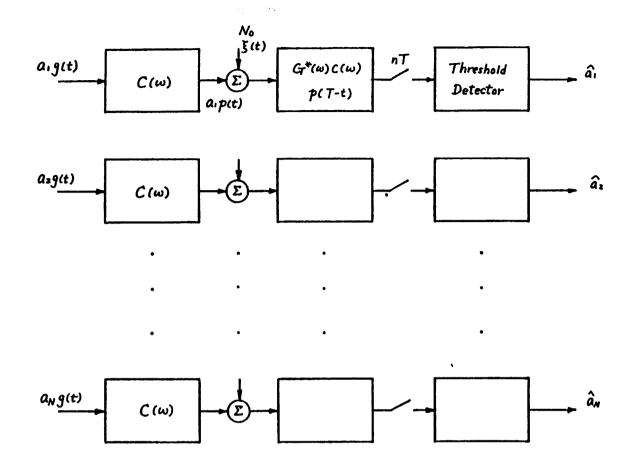

In the transversal filter echo canceller, an oversampling factor of R can be implemented with RN taps. Unavoidable hardware complexity is involved if a transversal filter with RN taps is used. However, because the input is a data sequence at a rate of  $f_b$ , a time-interleaved structure as shown in Fig. 2.1 can be used instead. This structure consists of R N-tap subfilters, each sampling at rate  $f_b$ , with a phase difference  $\frac{T}{R}$ , where T is the baud interval. At the output the samples of the R filters are then combined sequentially again with a phase difference of  $\frac{T}{R}$ . The total number of taps is still RN, and the number of updates also grows to RN per iteration. The convergence time remains the same as a baudrate sampling transversal filter because each subfilter operates independently of one another.

Figure 2.1. Time interleaved echo canceller with R subfilters.

In the look-up table approach, R independent memory blocks, each is assigned to a specific phase, can be used to accomplish an interpolating echo canceller. The memory size is  $R \cdot 2^N$ , and the number of updates also grows to R per iteration.

# 2.1.3. Echo Cancellation Requirement

The performance measure of an echo canceller is defined as the ratio of the input to the output rms echo ratio. When measure in dB, it is expressed as

$$E_{c} = 20 \log_{10} \left[ \frac{rms \ in \, put \ echo \ power}{rms \ out \, put \ echo \ power} \right]$$

(2.12)

If a transhybrid loss of 10 dB and a line attenuation of 45 dB are assumed, a 20 dB signal-to-echo ratio requires an echo cancellation of 55 dB.

#### 2.1.4. Equalization

3 ...

The pulse-shaping filters, including transmit and receive filters, of a data transmission system are generally designed either assuming a flat frequency response in the channel, or a particular compromise response, which is chosen to approximate as closely as possible the response most likely to be encountered in practice. However the actual line response will generally depart from the one used in the design, because the system is required to operate with various line configurations. The distortion will generate intersymbol interference (ISI).

Equalizers are linear or nonlinear networks designed to correct ISI arising from the nonideality of the channel. They may be manually adjustable or automatic, depending on how their impulse responses are tailored to the desired responses. Chapter 5 is dedicated to the equalization techniques that are considered as candidates or that are related to the application of DSL.

#### 2.1.5. Timing Recovery

The receiver is required to synchronize to the far-end receiver in a data transmission system to ensure the correct detection of far-end data. It is necessary to sample the incoming data signal at either the maximum eye opening for direct data detection, or at instants appropriate for the equalizer used. The transmitter is also required to be synchronized to the received signal in order to ensure that the signal switch with which the transceiver located at the central office interfaces, transmits and receives data at the same rate.

#### 2.1.6. Synchronization in Subscriber and Central Office Sets

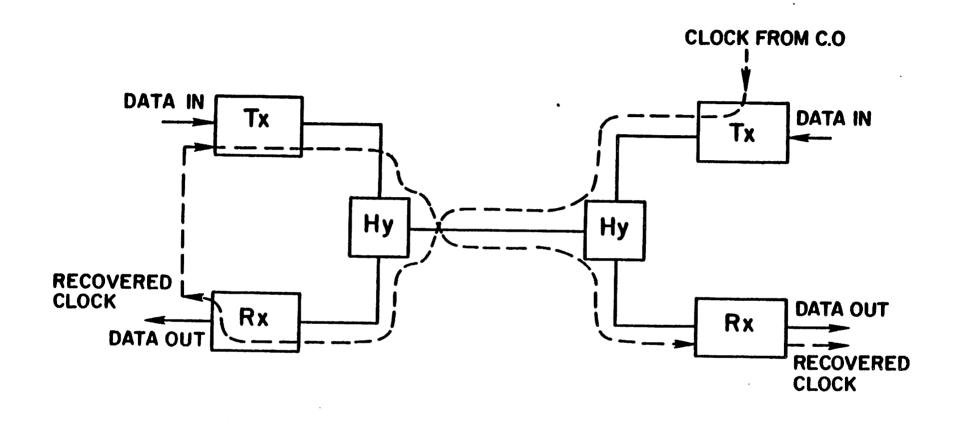

The central office transmitter receives its clock from the switch. The receiver at the subscriber end synchronizes to the received signal and thus is also slaved to the switched clock. The transmitter of the subscriber transceiver is then synchronized to the received clock to ensure that the central office transceiver transmits and receives at the same rate, except at the beginning of the transmission when the echo canceller and the timing recovery of the subscriber transceiver have not yet converged. The central office receiver then adjust its clock phase which is used to sample its received signal using its own timing recovery circuitry. Note that although the frequency at the central office is always correct for the received signal, the correct sampling phase depends on the round-trip delay of the line, and consequently it must be determined from the received signal. Overall, the timing information follows an open loop: from the central office transmitter to the subscriber receiver, from here to the subscriber transmitter, and finally back to the central office receiver, as shown in Fig. 2.2.

#### 2.2. System Description

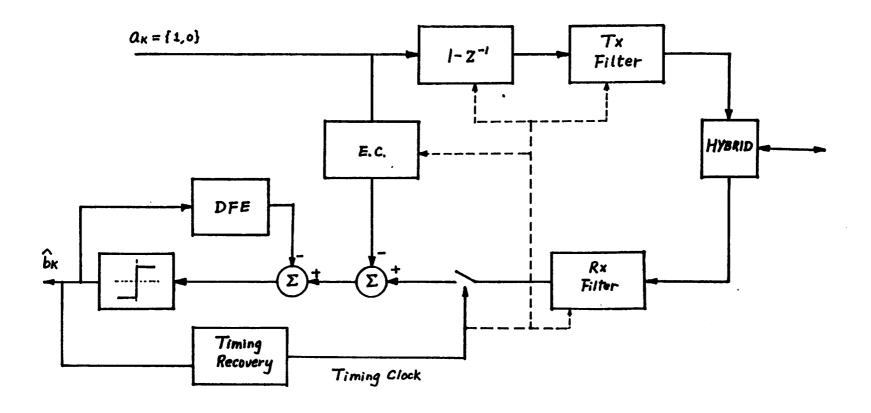

In this section, all the functions to be implemented in a DSL transceiver equipped with the baudrate sampling technique timing recovery as mentioned in Chapter 7 are

Figure 2.2. Timing information flow in the digital subscriber loop. Timing originates at the central office, is recovered at the subscriber receiver and used by the subscriber transmitter. The central office receiver must lock onto the subscriber transmitter because the correct sampling phase depends on the round-trip delay.

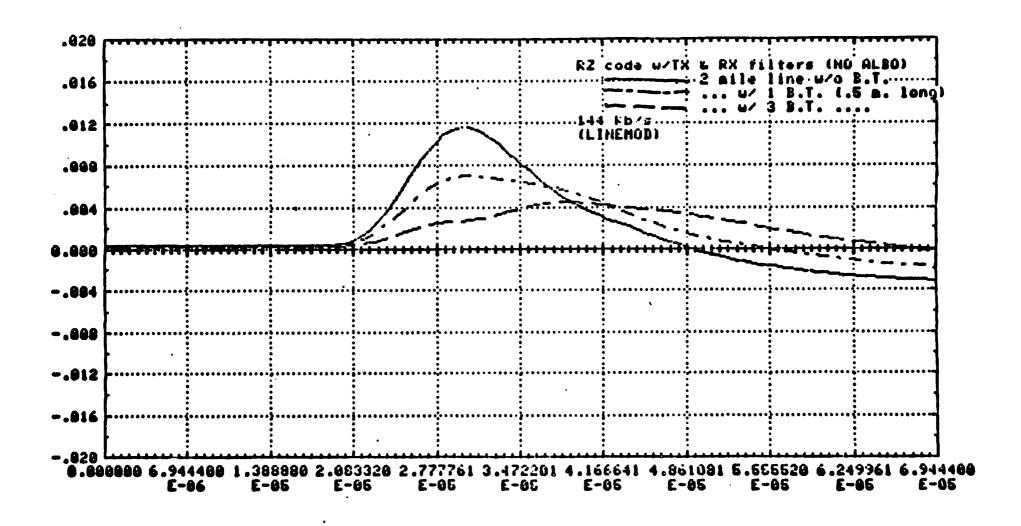

described. The experimental breadboard implementations cover all the functions required but the echo canceller, the details on the breadboard design can be found in references. [15,16] All the functions except the echo canceller are applicable to both the time compression multiplexing (TCM) and the echo-cancellation systems. Since the echo-cancellation mode system has much more restricted requirements on the sampling rate and the timing jitter, the implementation will be focused on this system. Fig. 1.3 in Section 1.1 shows a block diagram of a full-duplex echo-cancellation system under consideration. Two baseband DSL transceivers communicate at 160 kb/s on a single pair of twisted-pair wires. One of them is located at the central office, the other at the subscriber end. Typically, a transhybrid loss of  $10 \ dB$  is expected of the hybrid, that can be either a hybrid transformer or an electronic balance circuit. Line attenuation of  $45-50 \ dB$  is measured at half the data rate for a 5km subscriber loop. An echo cancellation of  $55-60 \ dB$  is thus required for  $20 \ dB$  signal-to-echo ratio.

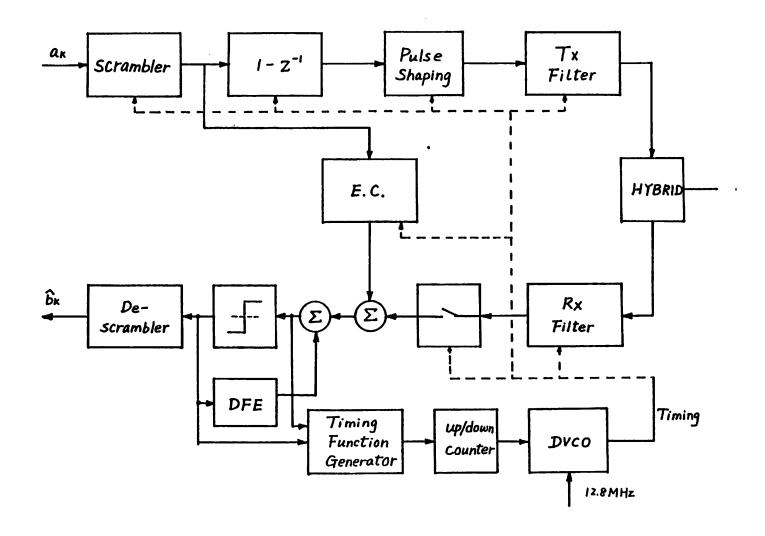

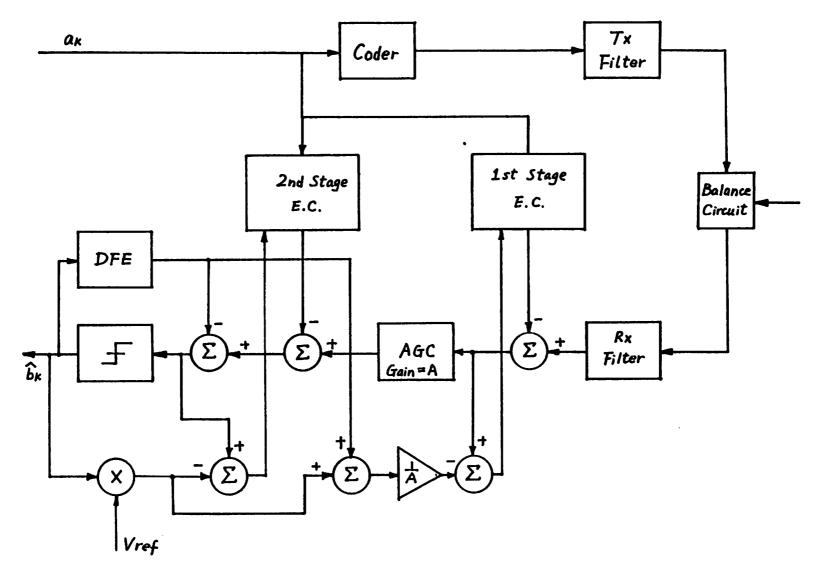

The system configuration which was chosen for breadboard implementation, also considered as the preferred configuration for VLSI implementation, is shown in detail in Fig. 2.3. They are described in more detail in the following subsections.

#### 2.2.1. Scramble and Descrambler

The scrambler randomize the data sequence to ensure a pseudo-random sequence even during idle or repetitive data patterns [17]. A random data sequence is required for the convergence of the echo canceller and the equalizer, to avoid discrete spectral components in the signal spectrum, as well as to aid timing recovery in the receiver. The scrambler chosen is recommended by CCITT and performs a modulo 2 division by the polynomial  $1+x^3+x^{20}$  [18], where x is the input to the scrambler and assumes values of 1 and 0. When a constant binary value is placed at the input of the scrambler, a period sequence with period  $2^{20}-1$  is generated. For all practical purposes, this can be considered as random because the period is very long.

Figure 2.3. Detailed block diagram of the DSL transceiver.

The scrambler, which is self-synchronizing, performs a modulo 2 multiplication by the same polynomial.

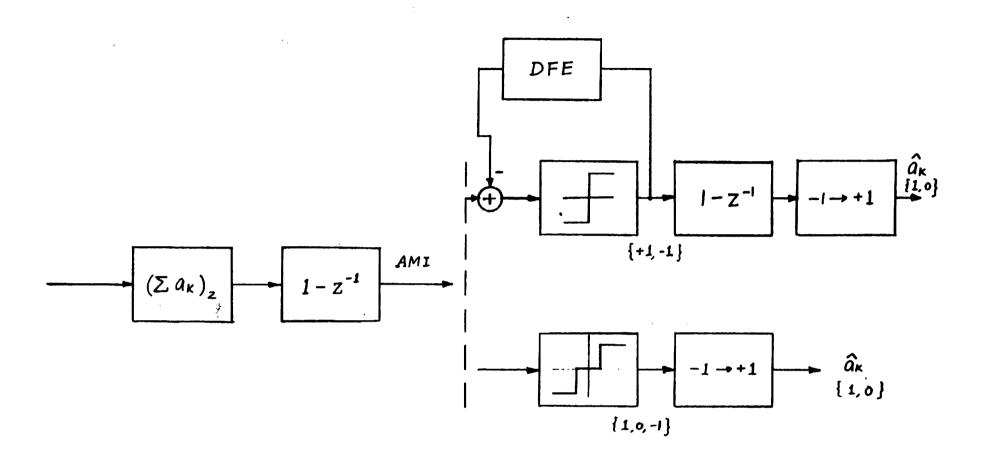

#### 2.2.2. Line Coder

A line coder at the transmitter converts the data sequence into another sequence according to a set of special rules. It is normally done in digital domain, although it may also serve the purpose of pulse shaping if the sampling rate is higher than the data rate. The code chosen for the experiment and proposed for DSL application is the  $1-z^{-1}$  partial response. Other partial-response codes with similar property, such as the modified duobinary can also be used, although they don't ensure alternate mark inversion. The  $1-z^{-1}$  partial response is a 3-level code, however, because it is generated from a 2-level code through a linear process, it can be treated as a 2-level code going through a channel with an impulse response equal to  $1-z^{-1}$ . It is desired to avoid 3-level code in the echo canceller, because of not only the additional hardware complexity, but also a slower adaptation speed. The fact that this 3-level code can essentially be treated as a 2-level code presents a great advantage.

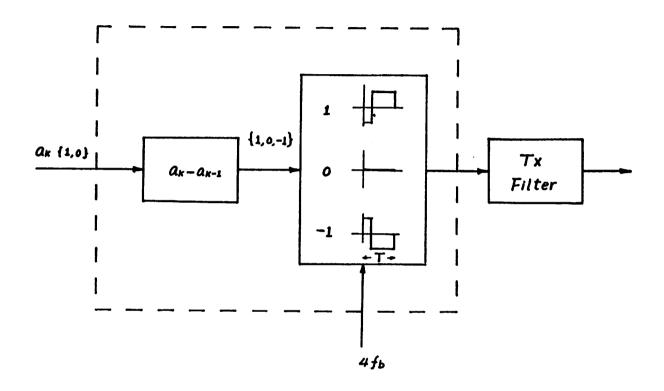

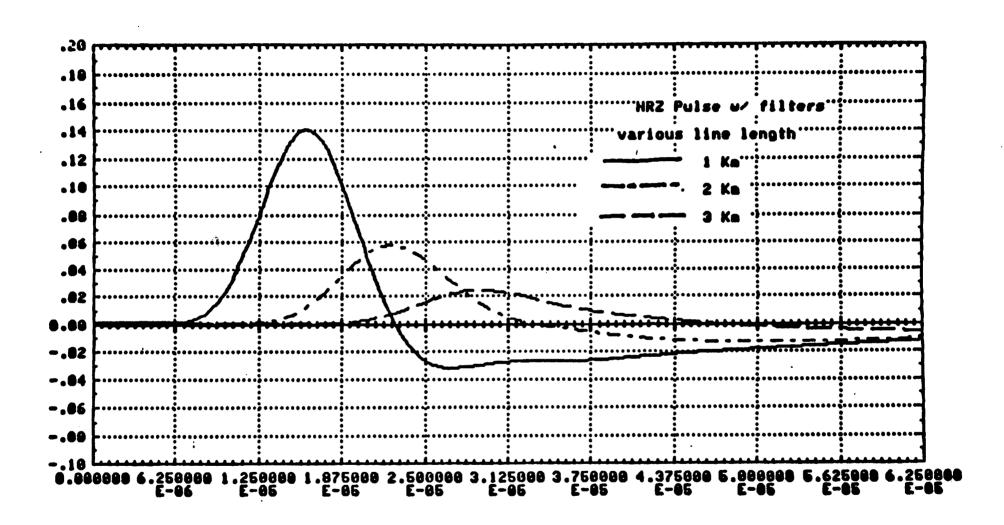

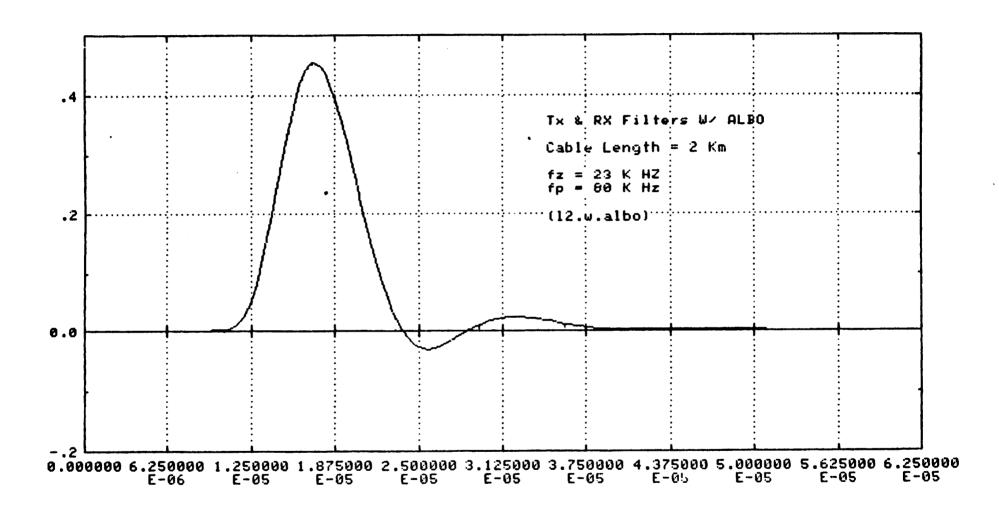

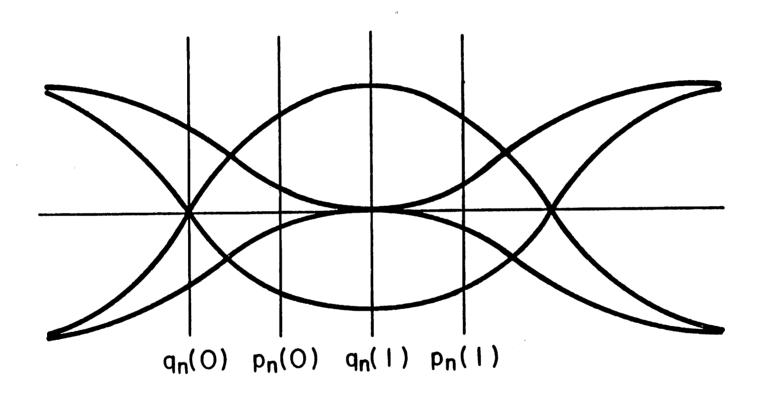

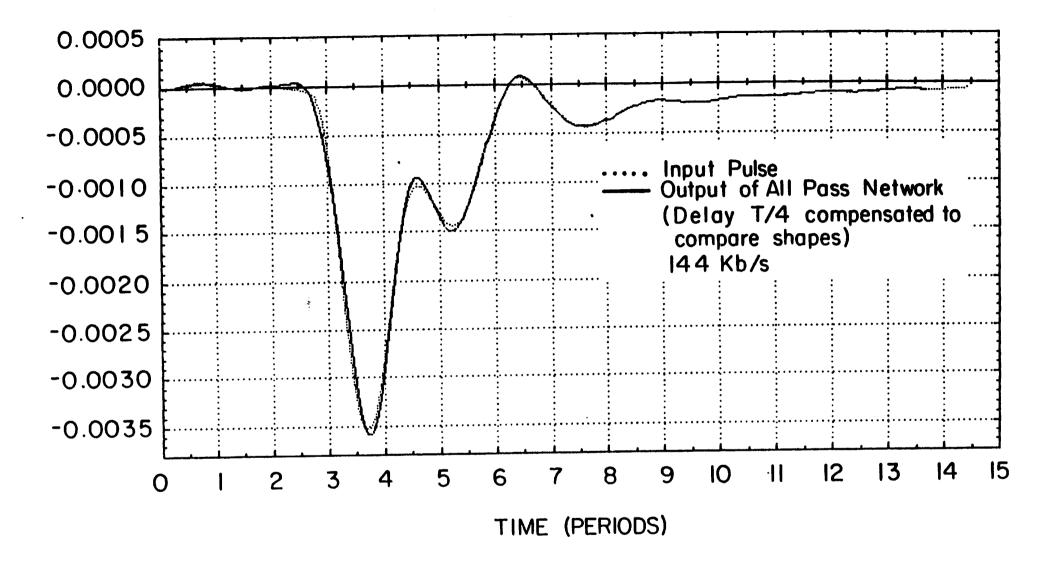

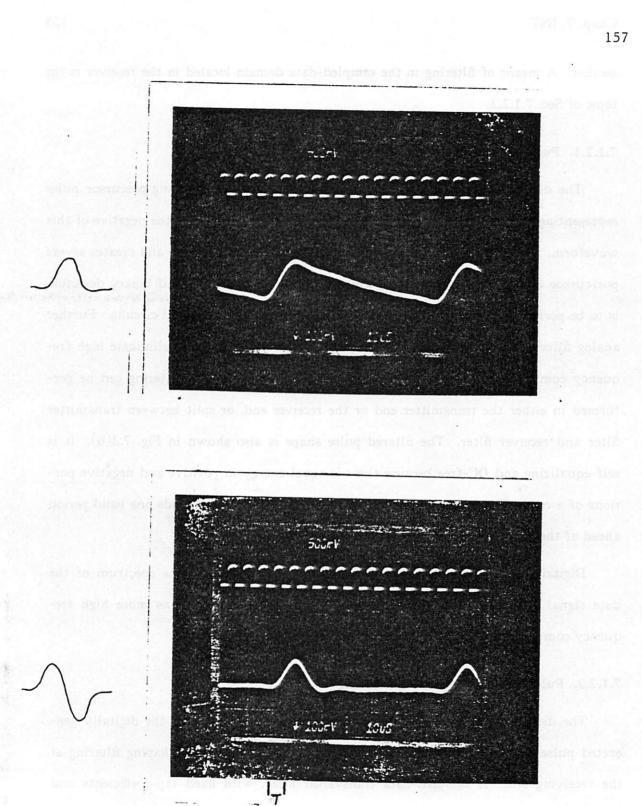

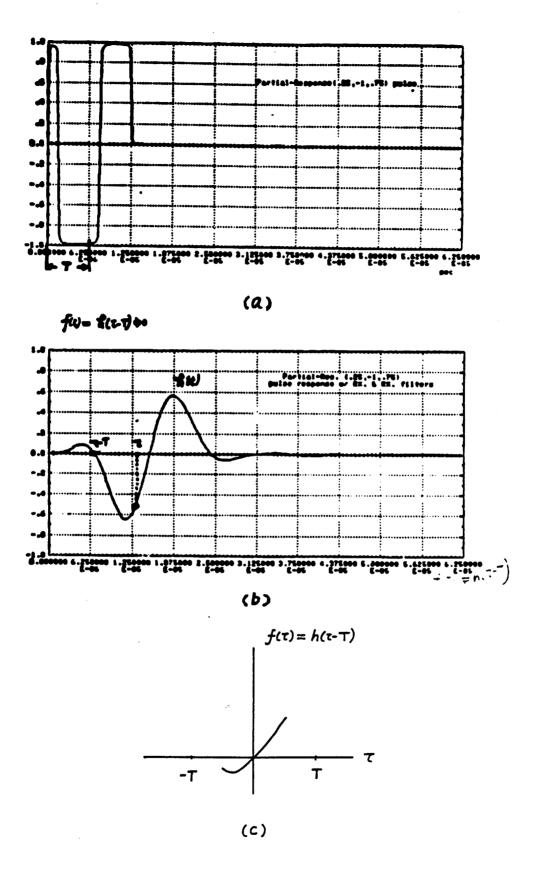

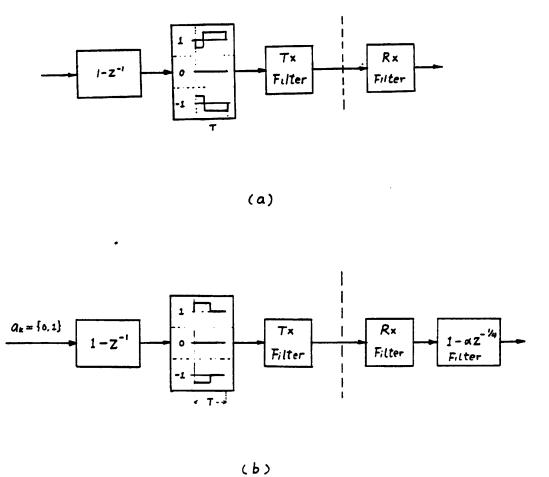

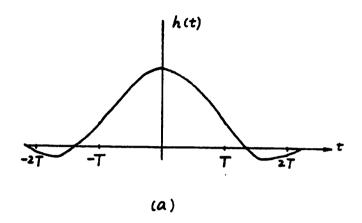

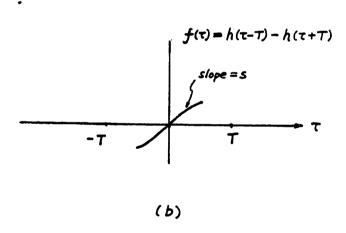

A pulse shaping function is also accomplished by the line coder by sampling the line coder at  $4f_b$ , where  $f_b$  is the data rate. The shaped pulse has a zero crossing at the first precursor, provides a simple target point for timing recovery. The line coder as used in the experimental setup is shown in Fig. 2.4. It should be noted that this pulse shaping function can be performed at the receiver using analog filtering techniques alternatively.

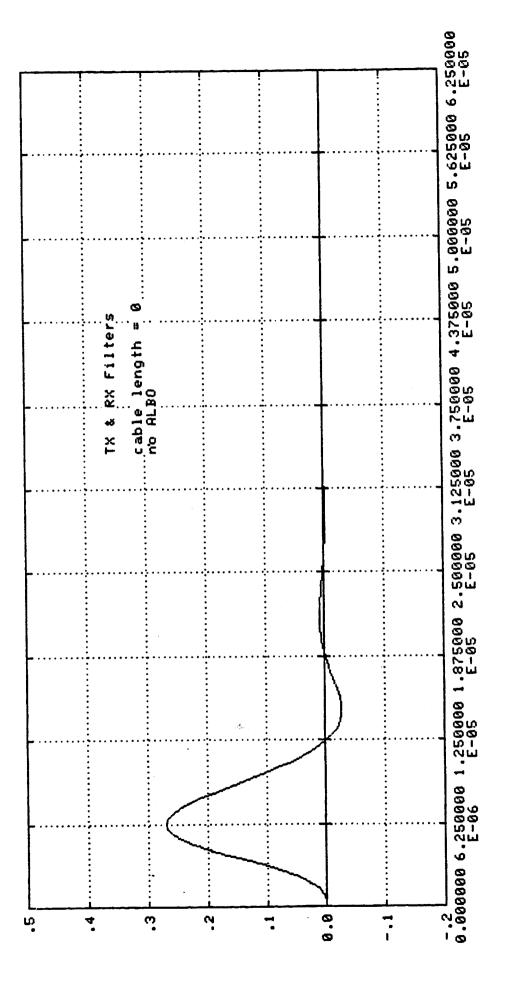

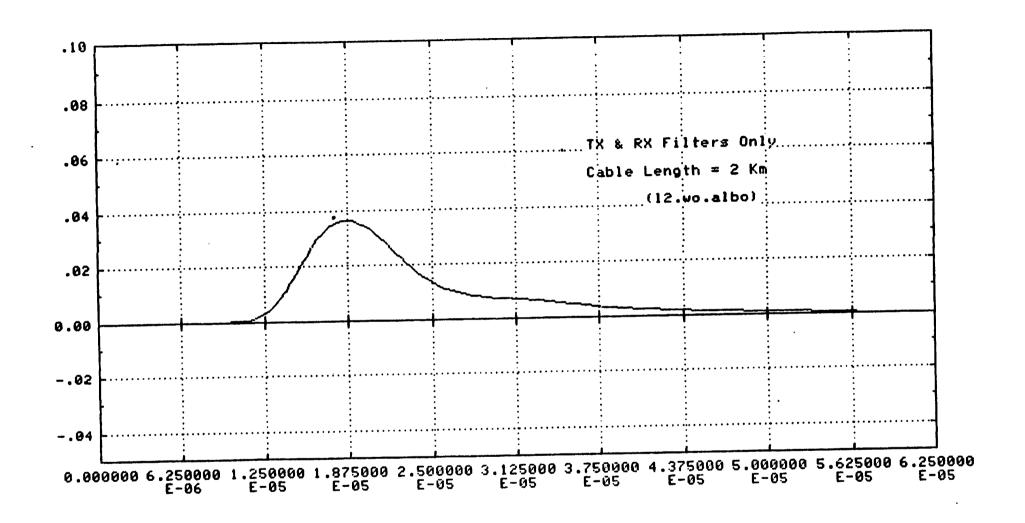

# 2.2.3. Transmit and Receive Filters

Minimal intersymbol interference filters [19] are used for the transmit and receive filters.

Figure 2.4. The digital line coder that performs both the  $1-z^{-1}$  partial response coding and the pulse shaping.

The alternative approach of using minimal ISI matched filters was also considered. It offers the best protection against white Gaussian noise in the ideal channel, however, with significant increase in complexity. The small improvement in nonideal channel may not justify the excessive complexity required by a matched filter.

Furthermore, the duration of the impulse response must be kept low to reduce the number of taps required by the echo canceller and the equalizer. This requirements applies also to the *effective channel impulse response*, which is the composite impulse response including the effect of line coder, transmit and receiver filters, and the channel characteristics. The self-equalization property of the  $1-z^{-1}$  partial response helps to reduce the length of the effective channel impulse response.

The transmit filter has a low-pass property to avoid the unnecessary crosstalk and radio frequency interference (RFI), which increases with frequency. The nonlinearity which may appear in the filtering must be kept at a minimum. The symmetry of the pulses must meet the same requirement.[9] The receiver filter must also have a low-pass property to reject the out-of-band noise from the channel. The pole location for the transmit filter is:

$$p = -8.168 + j 0.0$$

and the pole locations of the receive filter are:

$$p1 = -1.313 + j 2.97$$

$$p2 = -1.313 - j 2.97$$

$$p3 = -2.141 + j 1.154$$

$$p4 = -2.141 - i 1.154$$

These values are in radian frequency and are normalized to the data rate.

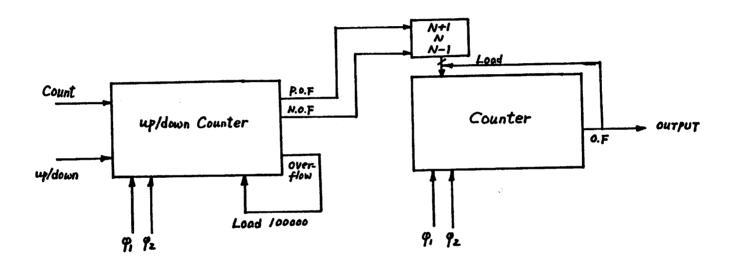

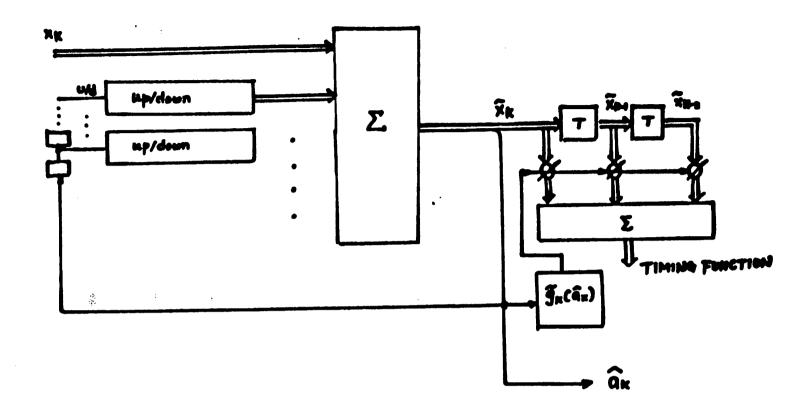

## 2.2.4. Equalizer

No  $\sqrt{f}$  equalizer was used in the experiment setup because a self-equalizing line code was used. A digital decision feedback equalizer (DFE) is used to mitigate the effect of ISI caused by the partial-response portion of the pulse and that caused by the bridged taps. The required number of taps was found to be 8 from extensive computer simulation. The relatively large number was simply due to the severe ISI caused by multiple bridged taps. The number can be reduced if more restricted line configurations were used. The taps weights of the DFE were stores in a bank of up-down counters, each has 12 bits and can be incremented or decremented by one least significant bit (LSB) per update. In other words, sign algorithm was used for adaptation. However, only 8 bits were converted to analog form for cancellation.

## 2.2.5. Echo Canceller

The echo canceller was not included in the experiment setup, because the feasibility had been illustrated and a large number of variations is available for implementation. The effect of residual echo on the timing recovery and equalization was tested by injecting an attenuated echo from a local transmitter. The degree of attenuation was adjustable. The alternatives and design issues of the echo canceller were presented in Sections 1.3 and 2.1.2.

## 2.2.6. Detector

Since a DFE was used to remove the partial-response portion of the pulses, the 3-level pulses were detected using a 2-level detector as 2-level codes. The threshold of the 2-level detector is well defined at the center of the signal and independent of the line attenuation. The detector can start making correct decisions even before the AGC converges. It offers a great improvement in the start-up convergence.

## 2.2.7. Timing Recovery

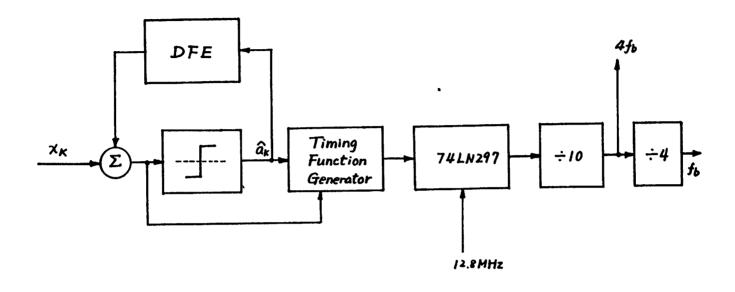

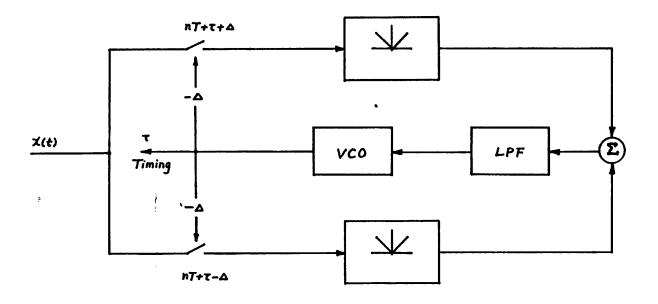

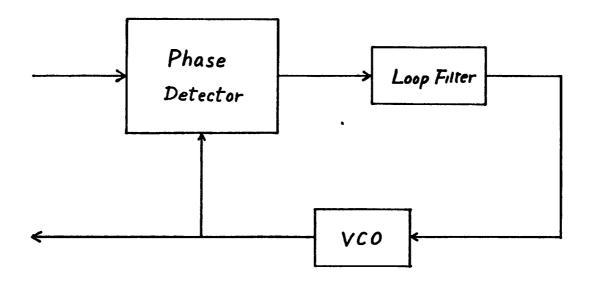

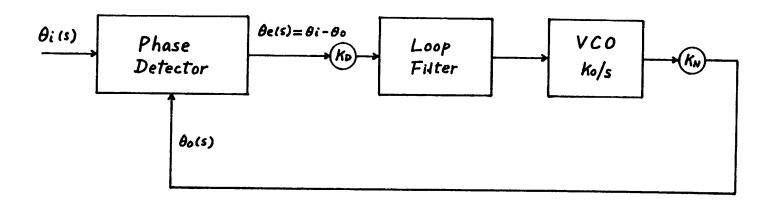

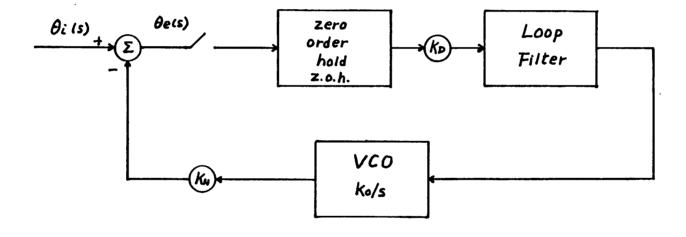

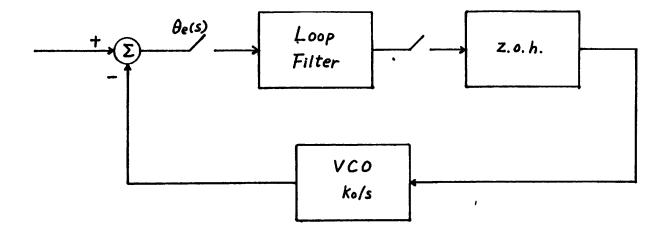

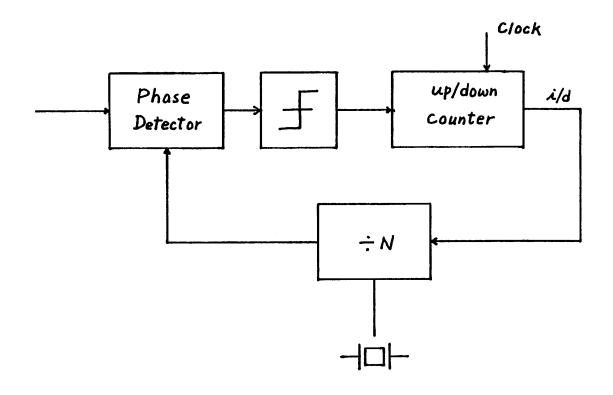

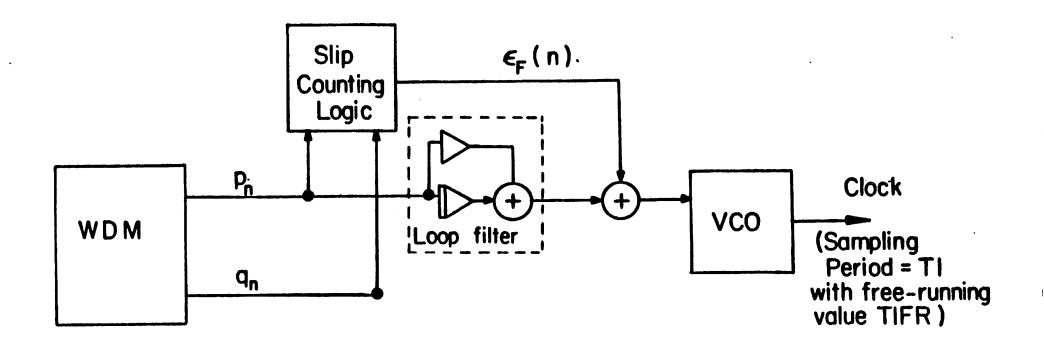

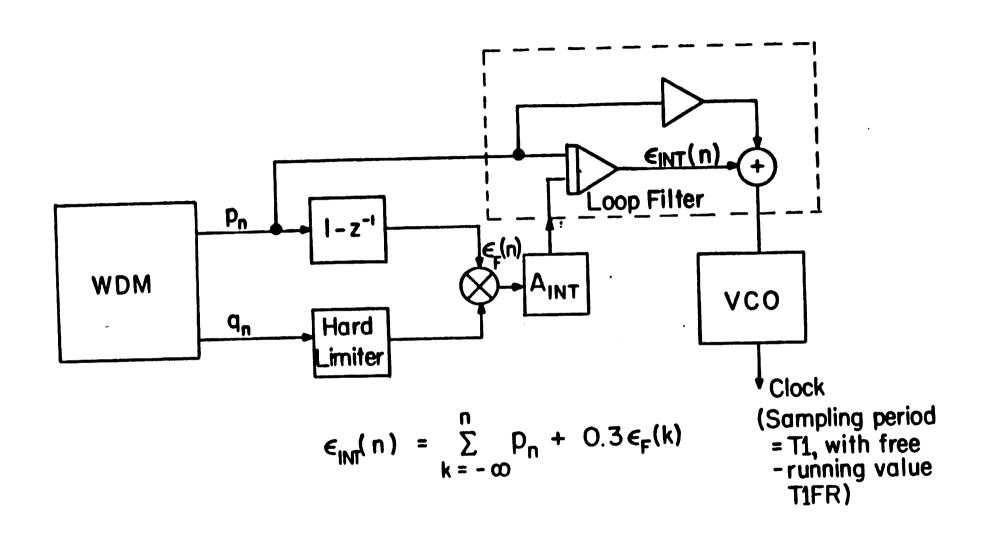

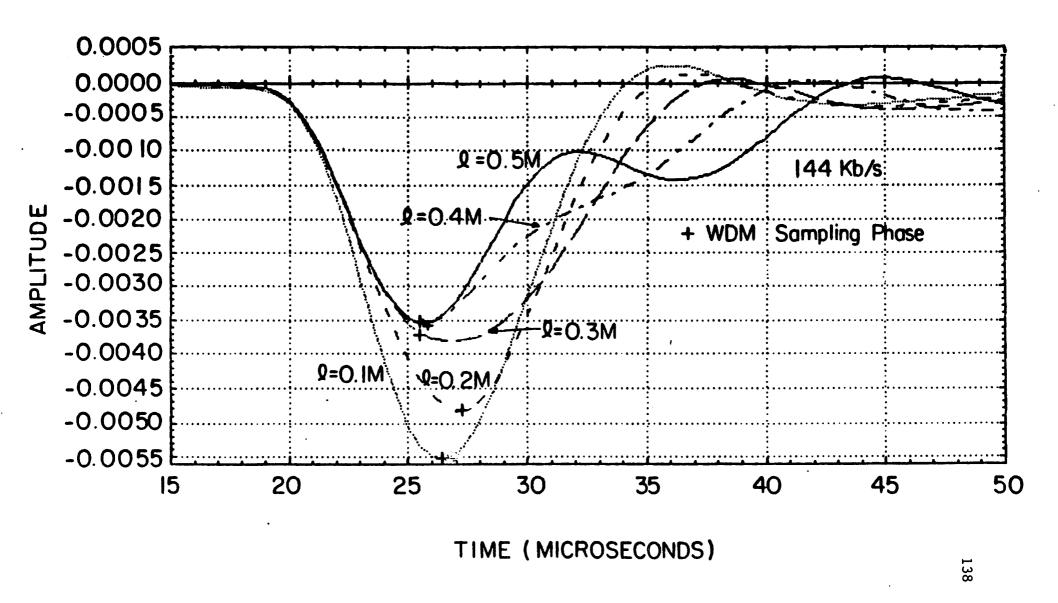

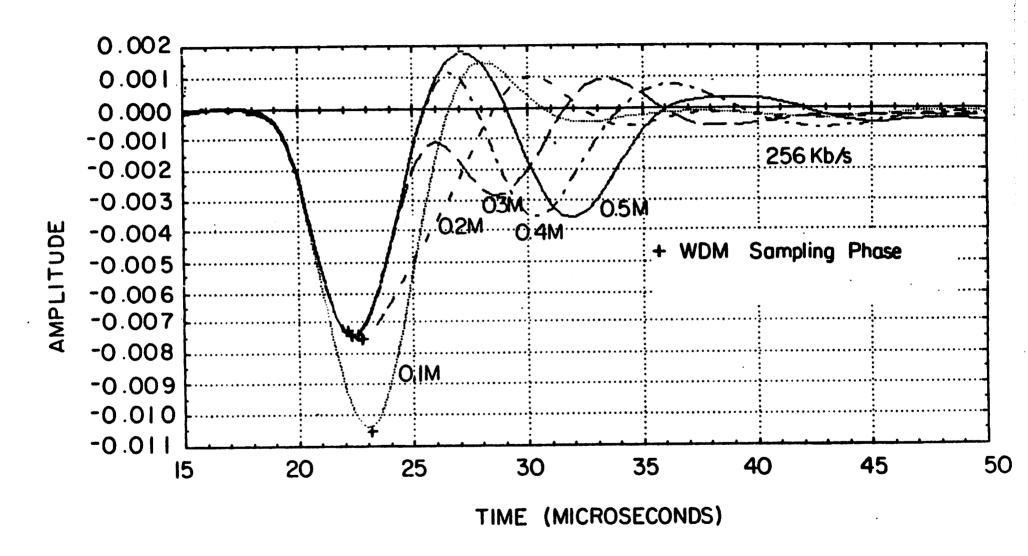

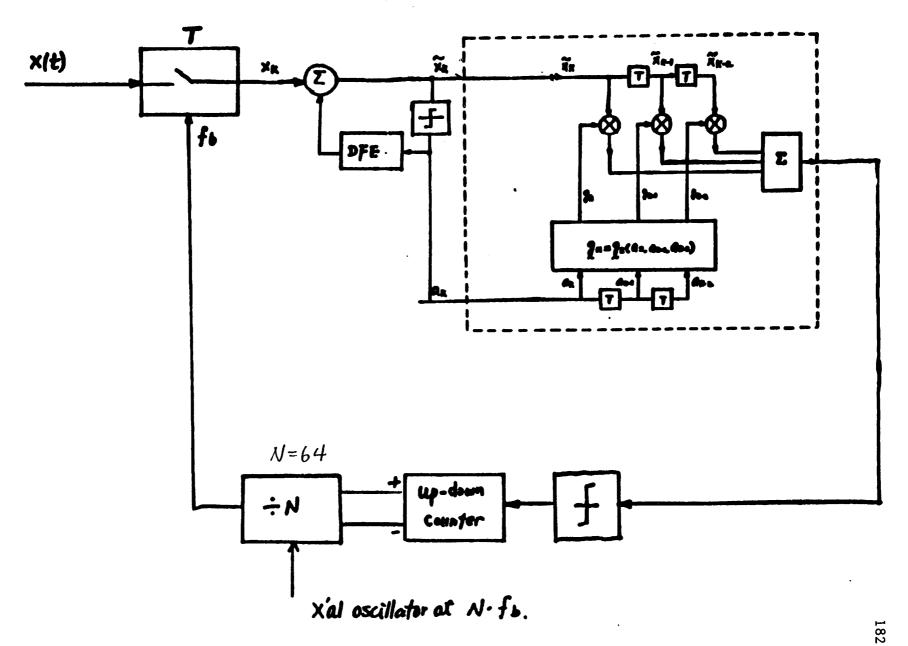

In the experimental system, the baudrate sampling technique was used for timing recovery. The details of this timing recovery technique is in Chapter 7. A block diagram of the timing recovery is shown in Fig. 2.5, where 3 basic blocks are shown, namely, the timing function generator, loop filter, and the voltage controlled oscillator (VCO). It must be noted that the input to the timing recovery is the equalized signal, where the ISI has been removed by DFE. These three blocks constitute a phase-locked loop (PLL), where the timing function generator serves the purpose of a phase detector in a PLL.

# 2.2.7.1. Timing Function Generator

Two versions of the timing function generator were built, corresponding to the digital and the analog approaches described in Chapter 7. The digital approach assumes that the echo canceller outputs a digital signal and the DFE cancellation is also performed in digital domain. A precision of 8 bits was assumed. The analog implementation was built to simulate the switched-capacitor realization of the analog timing function generator. Because of the fundamental difference between integrated circuits and off-the-shell analog components, multiplications were achieved with MDAC's.

## 2.2.7.2. Loop Filter and VCO

Two versions of loop filter and VCO were also built in the breadboard form. In the digital approach, an off-the-shelf part, the SN74LS297 digital phase-locked filter, was used for the loop filter. A divided-by-40 counter also used off-the-shelf TTL parts. The timing jitter in this configuration could be as high as  $\frac{1}{40}T$ . This value can cause performance degradation in the echo cancellation unless interpolation technique is used.

Figure 2.5. Block diagram of the timing recovery used in the experiment setup.

An analog version of the loop filter and VCO was also constructed. The VCO part used was the SN74LS124. The acquisition time was long and timing jitter high as expected because of the large VCO gain and the low precision of the free running frequency.

The most promising and reasonable implementation would be a *crystal VCO* (VCXO), which although not implemented in the experiment setup, has been successful used before in a similar application [9].

## CHAPTER 3

# Timing Recovery

A hierarchy of synchronization problems needs to be considered in digital data communication. Carrier synchronization, which is required only in the passband system, concerns the regeneration of both the frequency and the phase of the carrier. Bit synchronization, or timing recovery, is concerned with synchronizing the receiver clock with the baseband data-symbol sequence, whether it is a demodulated passband signal in the carrier system or a baseband signal originally [20]. Again, timing recovery, also referred to as symbol synchronization, involves both the frequency and phase. Word, frame, and packet synchronization, involving a specially designed message format, belong to another level in hierarchy, which is not considered here. An accompanying pilot tone transmitted along with the data signal is another means to provide timing information to the receiver, which will not be discussed here either. In other words, self-timing, where the timing frequency and phase are derived from the information-bearing signal without any pilot tone, is the one of interest to us.

The recovered timing clock, in the simplest situation, is used to sample the data signal for decision. A small timing jitter, which is the fluctuation in sampling instants deviated from a uniformly time-spaced clock, is allowable. The recovered timing is also used to retransmit data if the timing recovery is in a repeater. Timing jitter can accumulate along the repeater chain. If a sampled-data transversal filter is used for equalization, the recovery timing clock may also be used to clock this filter. In a synchronous system, where the *local transmitter* clock is slaved to the recovered timing in the transceiver, the recovered timing may be the only clock in the transceiver. In the latter three cases, the jitter specification is much more restrictive.

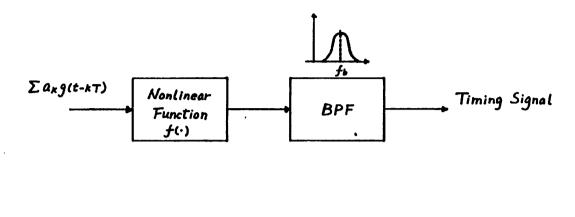

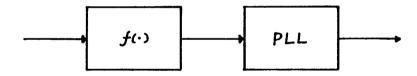

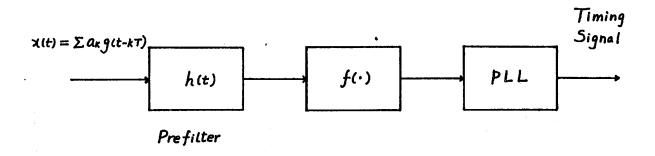

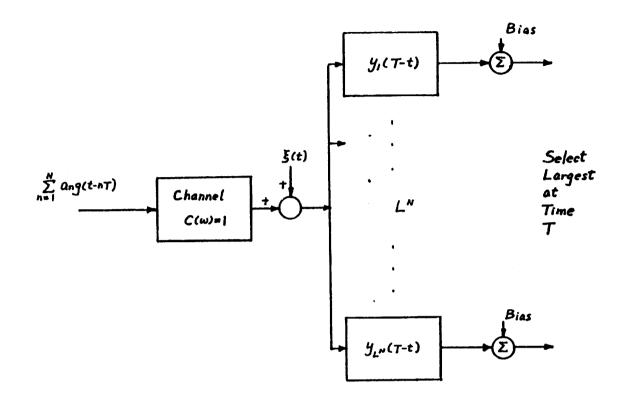

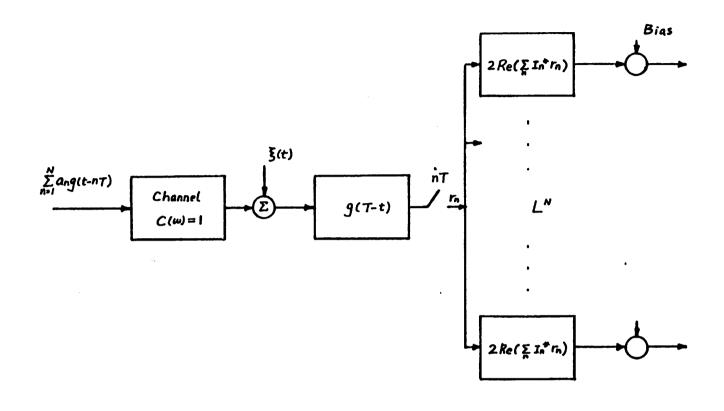

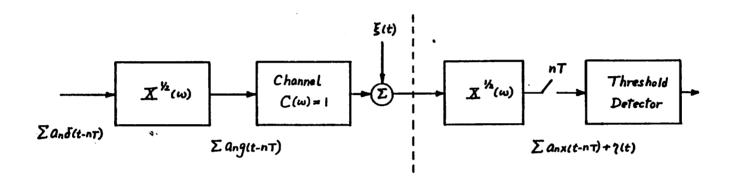

# 3.1. Conventional Timing Recovery Methods

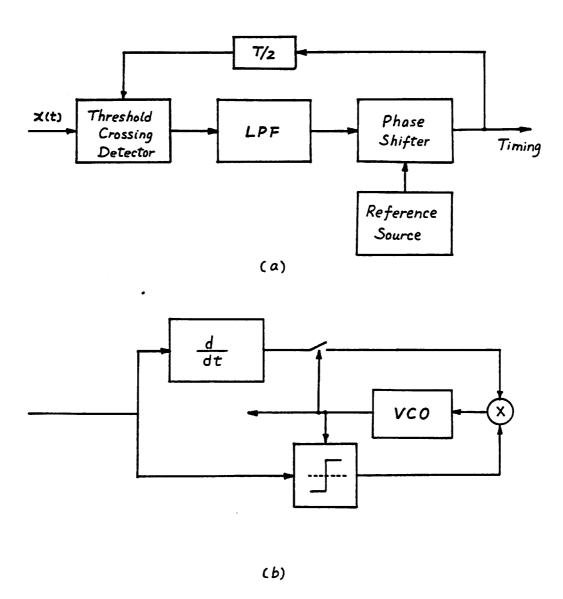

Since the classic paper on the statistics of regenerative digital transmission in 1958 by W. R. Bennett [21], the timing recovery technique has received considerable attention. A survey of literature on timing recovery shows that a variety of methods has been studied or developed. The spectral line method, most commonly realized and analyzed in the square-loop configuration, is the most straightforward approach [20,24,26,30]. In the spectral line method, the data signal is passed through a nonlinear device before being processed by a narrow bandpass filter or its equivalent, a phaselocked loop (PLL), as shown in Fig. 3.1. It can easily be shown that the expected value of the nonlinearly processed signal has a periodic term with the frequency equal to the data rate. It is often stated that a spectral line component is created at the data rate in the spectrum although the signal is cyclo-stationary and on which the power spectrum is not defined. The discrete spectral line component is then extracted with a narrow bandpass filter. The phase and the magnitude of this periodic signal in relation to the data signal depend on the nonlinear function and the pulse shape. However, because of the complexity involved with nonlinearity, square-law nonlinear process is the only one tractable. More details about the timing phase obtained by the spectral line method will be covered in Section 3.3.

The threshold crossing and the sampled-derivative methods were analyzed in [22]. The block diagrams of these two methods are shown in Fig. 3.2. In the threshold crossing method, an error pulse with amplitude equal to the difference between the time of the zero crossing and the time of the nearest sampling pulse is generated each time the signal crosses zero. In the sampled-derivative method, the error signal is the sampled value of the derivative of the data signal multiplied by the polarity of the signal at that time. Note both methods have inherent nonlinear functions in the error signal generation. It is shown in [22] that although the timing jitter performances are very

Figure 3.1. The conventional spectral line method for timing recovery, where  $f_b$  is the data rate, and is equal to  $\frac{1}{T}$ .

Figure 3.2. Threshold crossing method (a) and sample-derivative method [22].

similar, the timing phases recovered by the two methods are different if the pulse is not symmetrical. The phase recovered by the threshold crossing method is the time instant,  $\tau$ , such that  $f(\tau-T/2)=f(\tau+T/2)$ , and that recovered by the sampled-derivative method is the peak of f(t), where f(t) is the effective channel impulse response representing a symbol, and T is the time interval between pulses. The maximum eye opening as observed in the eye diagram is not necessary at either of the two timing phases recovered by these two methods. However, if the impulse response is symmetrical around its peak, the two phases coincide at the maximum eye opening.

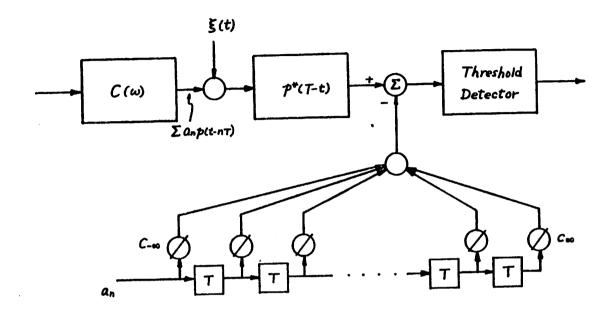

In [23], another method, namely the early-late gate method was analyzed. The block diagram of the early-late gate method is shown in Fig. 3.3. The optimum timing phase in the sense of maximum likelihood is also derived. An important result of the study showed that both the sampled-derivative and the early-late gate methods are good approximation of the implementation of the maximum likelihood strategy. Note again that a nonlinear operation, the full-wave rectification, is included in the early-late gate implementation.

The timing recovery methods described in this section are either continuous-time or sampled-data with sampling period much less than the data interval. Timing recovery techniques with lower sampling rates are the preferred approach as we will see after taking practical considerations into account.

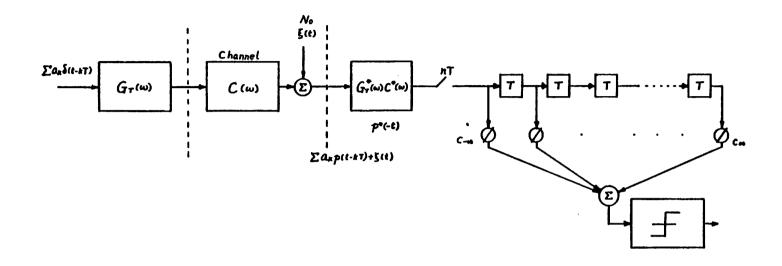

#### 3.2. Optimum Timing Phase

The implementation of the maximum likelihood strategy is shown in Fig. 3.4., where a matched filter is inserted in the front end to generate an effective channel impulse response which is symmetrical around its center. The optimum timing phase in this configuration is apparently the center of symmetry for maximum likelihood detection. It is also obvious that all the timing recovery methods mentioned in last section converge to this timing phase if there is a filter matched to whatever the channel

Figure 3.3. Early-late gate method [23]. The two sampling phases are either advanced by  $\delta$  or retarded by  $\delta$  with respect to the desired phase.

Figure 3.4. Implementation of maximum likelihood strategy [23].

characteristics happen to be. Because a matched filter is difficult to implement, more realistic data transmission systems use lowpass filters instead. What is then the optimum timing phase? It has been assumed in some studies [12,23] that the desired sampling timing is that instant when the unequalized impulse response is a maximum. It was later shown by Lyon [24] that such a timing phase can result in a spectral null if a T-spaced transversal filter is used for equalization. In general, the best sampling phase depends on the subsequent equalization scheme. For instance, if no equalizer is used other than a slicing device for data decision, the phase with maximum eye opening in the eye diagram is the best sampling instant. It has also been shown that the timing at the peak of a periodic alternating data sequence is the optimum phase for a T-spaced transversal equalizer[25]. Since the timing phase plays an important role in equalization, it is useful to find out exactly what timing phase is recovered. In next section, a technique to locate the recovered timing phase in the spectral line method is described.

# 3.3. On the Timing Phase Recovered by the Spectral Line Method

Let's consider the timing recovery in a baseband data transmission. The input signal assumes the form

$$x(t) = \sum_{k=-\infty}^{\infty} a_k \ g(t-kT)$$

(3.1)

where  $\{a_k\}$  is the data message sequence and g(t) is the signaling pulse, sometimes also referred to as the *impulse response* of the effective channel, which includes the pulse shaping filter, transmit and receive filters, and the transmission medium. T is the symbol interval, and is equal to  $\frac{1}{f_b}$ , where  $f_b$  is the data rate (baud-rate). In a binary data system,  $a_k$  can only assume the values +1 and -1.

A nonlinear operation  $f(\cdot)$  is performed on x(t) and results in signal y(t)

$$y(t) = f(x(t))$$

(3.2)

A discrete line at the data rate is generated in the signal spectrum of y(t) after the non-linear operation  $f(\cdot)$  is performed on the input signal x(t). This frequency component is separated from the residual continuous spectral components by using a narrow bandpass filter or its equivalent, a phase-locked loop.

This technique is widely used in the passband systems where the baseband spectrum is relatively narrow compared to the carrier frequency and the channel has a relatively flat spectrum around the carrier frequency. The spectral line method can resolve satisfactory timing phase under the condition that g(t) is symmetrical about the peak. In most systems, Nyquist pulses are used for g(t) to minimize the intersymbol interference. Nyquist pulses are symmetrical around the peak, and therefore, spectral line method recovers the phase at the peak of the pulses.

However, problems occur for high baudrate transmissions. In high speed passband modems, where symbol rate can be 2400 baud / sec or higher, the channel spectrum is not flat any more. In high speed baseband systems, where the baseband spectrum occupies the whole channel spectrum, the channel could cause large distortion of the pulse shape. The recovered timing phase for an asymmetrical pulse using the spectral line method is no longer at the peak. The recovered timing phase under such conditions is the topic of this section.

Because of the difficulties in dealing with the nonlinearity, only the square-law nonlinearity has been analyzed [26]. The analysis was done not only for the recovered timing phase but also to compare the timing jitter generated by the continuous spectrum. The jitter analysis turned out to be pessimistic because of the fact that the signal is cyclostationary. However, the power and the phase of the *timing tone* are still valid.

Assuming that G(f) is band limited to  $\frac{1}{T}$ , the magnitude and phase of the timing tone generated by the square-law nonlinearity is

$$A_1 = \int_{-\infty}^{\infty} G\left(\frac{1}{T} - f\right)G(f)df \tag{3.3}$$

where G(f) is the Fourier transform of g(t).

It is obvious from Eq.(3.3) that the recovered timing phase for a symmetrical g(t) is at the center of symmetry. Since G(f) is real for a symmetrical g(t), so is  $A_1$  real, and the phase is zero. The phase for an arbitrary g(t) can also be calculated from Eq.(3.3).

#### 3.3.1. The Importance of Timing Phase

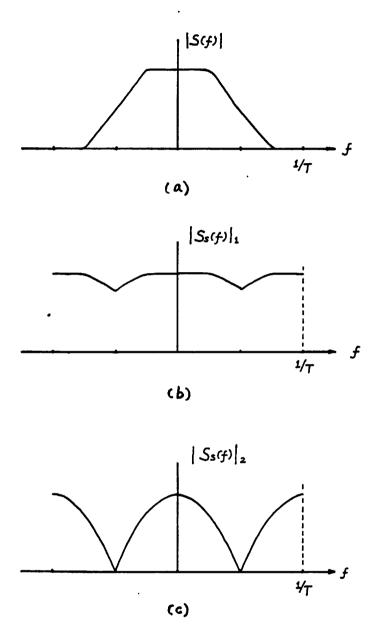

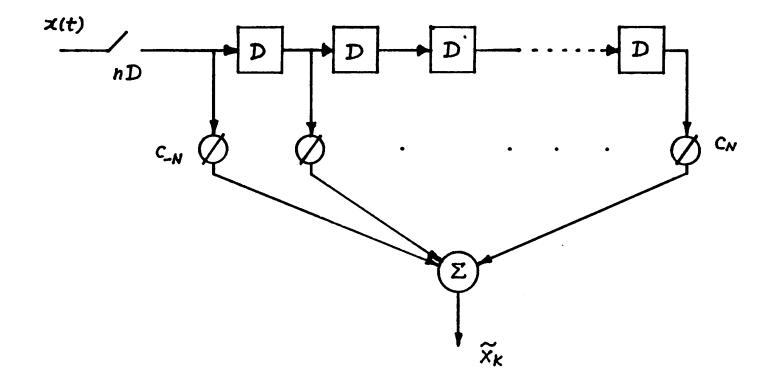

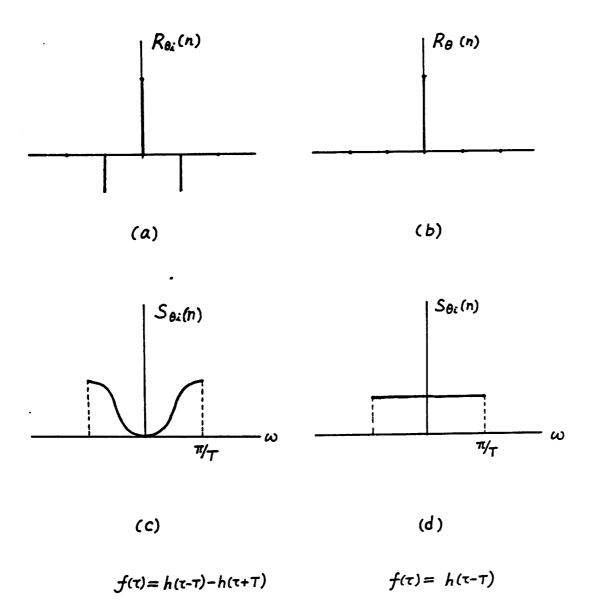

If Nyquist pulses are received, such as in the case of narrow baseband transmission and flat channel spectrum, the optimum sampling time is at the center of symmetry, which is also the peak of the pulse. If the recovered timing is used for clocking the equalizer as well as for the detection, the definition of the optimum timing phase depends on the following equalization scheme. A commonly used equalizer is the transversal filter type linear equalizer. As shown if Figure 3.5, a tapped delay line transversal filter with spacing T ( $T = \frac{1}{f_b}$ ) takes samples  $\{x_k\}$  from the received signal x(t) and performs filtering function on  $\{x_k\}$ . The tap coefficients are usually adaptive and are updated to minimize the mean squared detection error. Because  $x_k$ 's are sampled from x(t) at rate  $\frac{1}{T}$ , the power spectrum of  $\{x_k\}$  is periodic with period  $\frac{1}{T}$ . The relationship between the power spectra of x(t) and that of  $\{x_k\}$ , denoted by S(f) and  $S_s(f)$  respectively, are shown in Figures 3.6, the spectra shown in Figures 3.6(b) and 3.6(c) are called the folded spectra and are functions of sampling phase. Normally, S(f) and  $S_s(f)$  are complex.

The effect of the transversal filter is to generate a compensating transfer function proportional to  $\frac{1}{S_s(f)}$  and the output will have a flat folded spectrum identical to the folded spectrum of a baseband PAM signal with Nyquist pulses. A major drawback of

Figure 3.5. Structure of a tapped delay line transversal filter with spacing T.

Figure 3.6. (a). Magnitude of the power spectrum of a PAM data signal. (b). Magnitude of the power spectrum of a sampled PAM data signal, sampling at phase 1. (b). Magnitude of the power spectrum of a sampled PAM data signal, sampling at phase 2.

this equalizer is that for a power spectrum  $S_s(f)$  with nulls at some frequencies, the transfer function of the equalizer will have a very large gain at these frequencies, and consequently, enhance the noise. As noted above, the shape of  $S_s(f)$  depends on the sampling phase, and therefore, the timing recovery phase becomes important in this application.

Lyon [24] has shown that for normal telephone channel, where the frequency response decreases with frequency and where phase is a nonlinear function of frequency, a sampling phase at the peak of the pulse can create a null at the band-edge, at  $f = \frac{1}{2T}$ . Obviously, if the linear equalizer is to be used, sampling at the peak is not optimum. Lyon has proposed to select a sampling phase which maximizes the band-edge component. It is interesting to note that if the pulse is symmetrical, the phase which maximizes the band edge component is also at the center of symmetry.

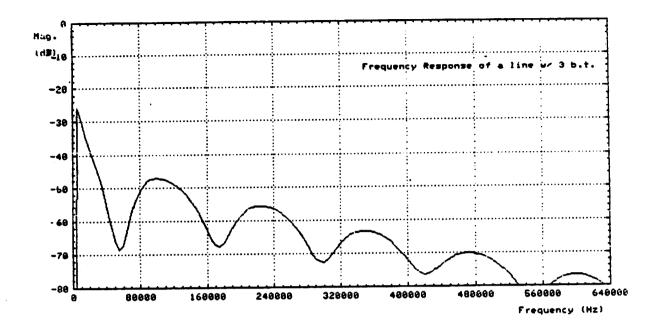

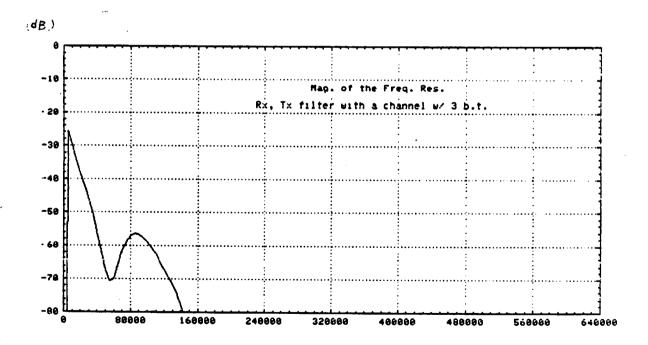

Bridged taps, which are open-ended wire pairs attached to the main subscriber loops, can alter the characteristics of the transmission channel dramatically. Figure 3.7 shows the frequency response of a subscriber loop with three bridged taps intact. There are periodical valleys in the frequency response. In this case, nulls can exist within the band and make it more difficult to define the optimum timing phase.

The validity of the spectral line method for timing recovery can be evaluated if the timing function phase recovered by this method for any arbitrary non-linear function can be determined analytically. Next section we will present two approaches to calculating the timing phase obtained by the spectral line method.

## 3.3.2. Timing Phase Recovered by the Spectral Line Method

A brute force approach to calculating the timing phase recovered by the spectral line method is to generate a large number of random data symbols and the corresponding baseband pulse amplitude modulation (PAM) signal x(t) and also the corresponding nonlinearly processed signal y(t). Then periodically average y(t) for

Figure 3.7. (a). Frequency response of a twisted pair with 3 bridged taps intact. (b). Composite frequency response of the transmit filter, channel as shown in (a), and the receive filter.

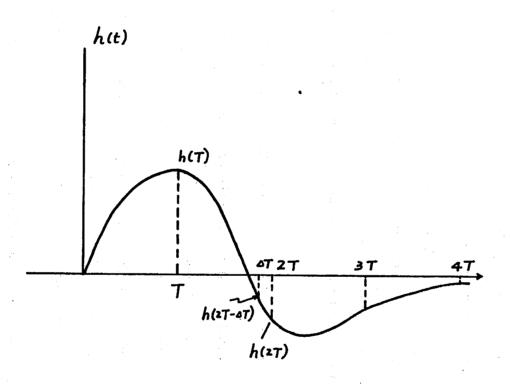

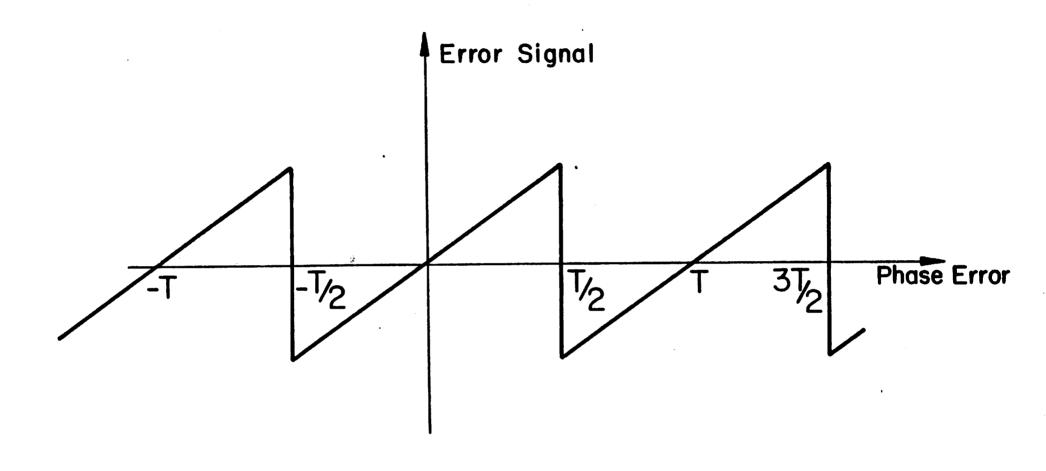

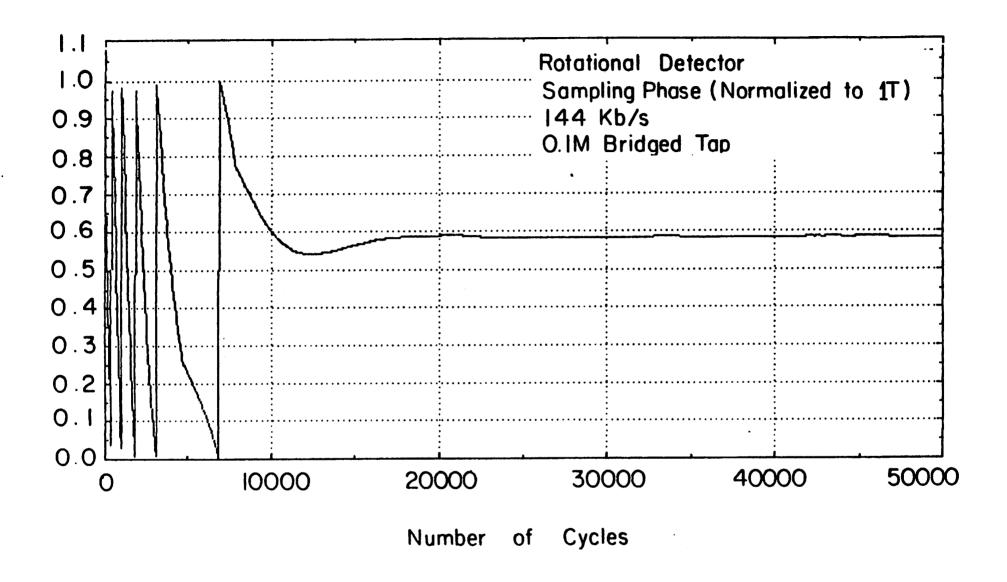

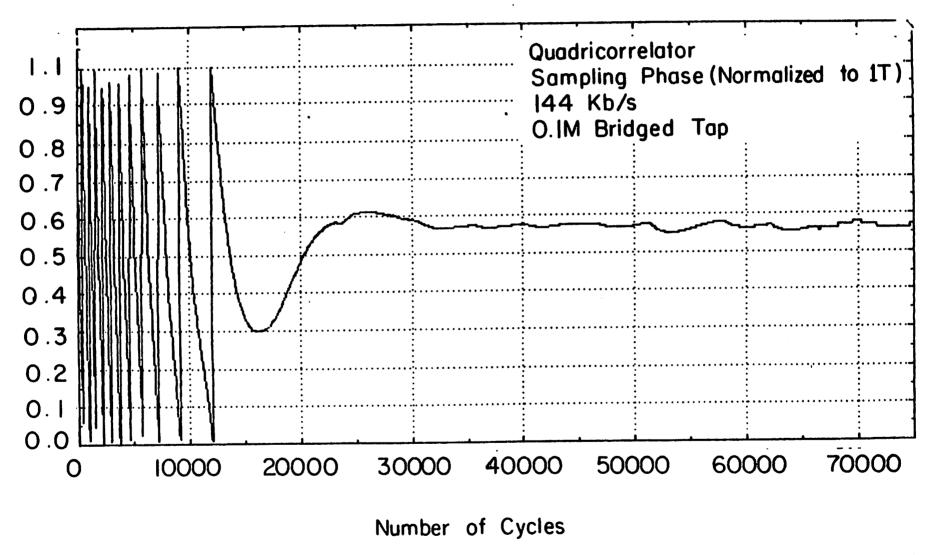

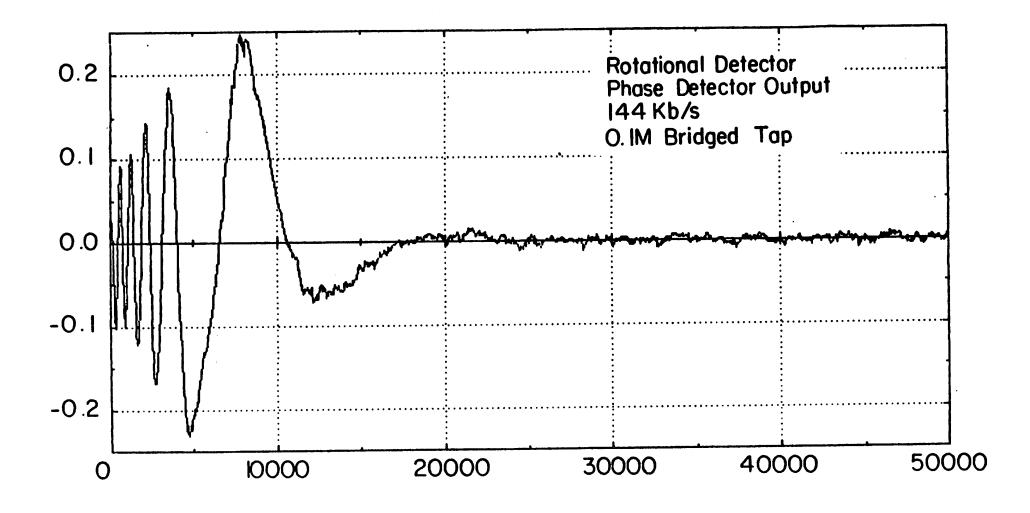

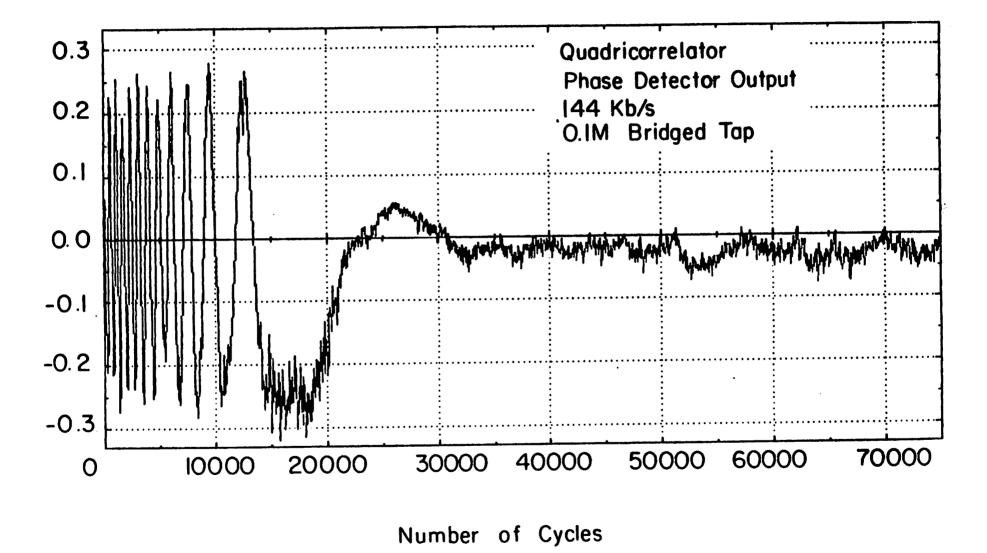

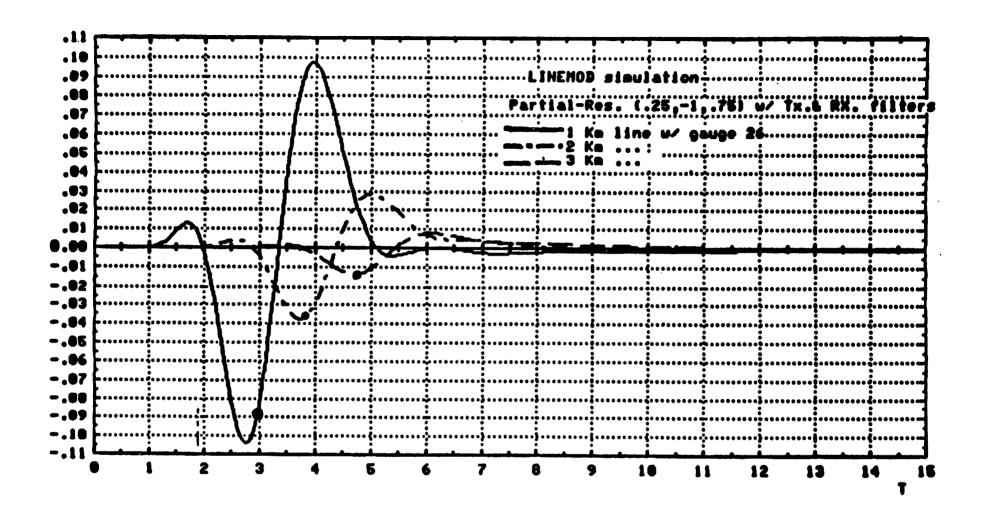

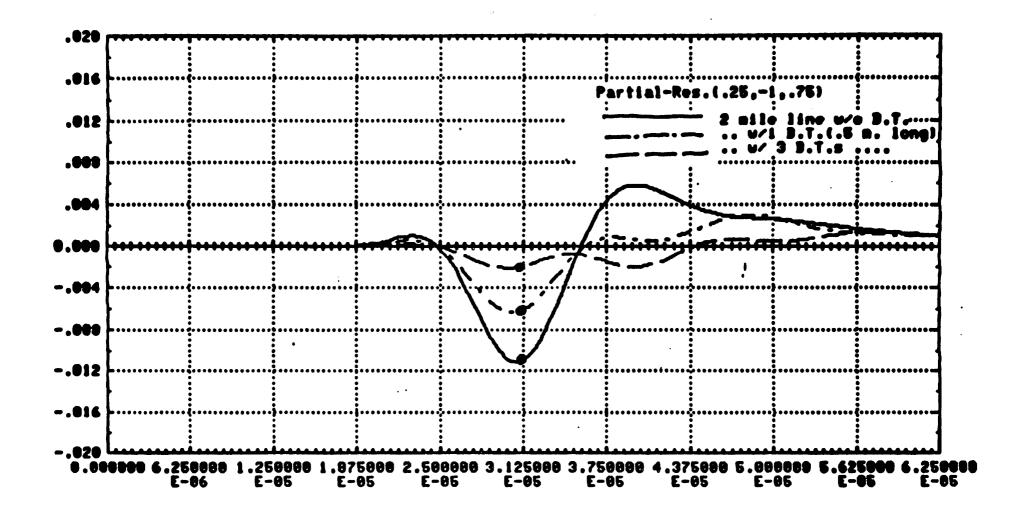

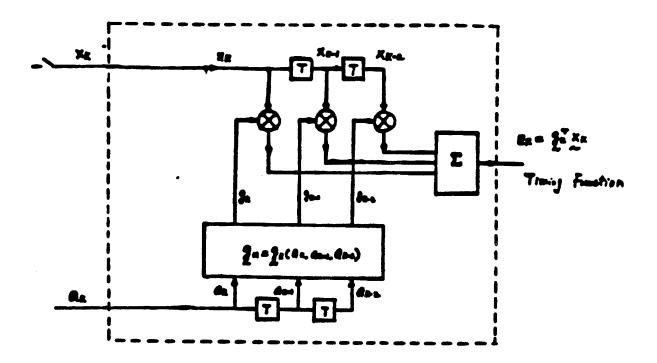

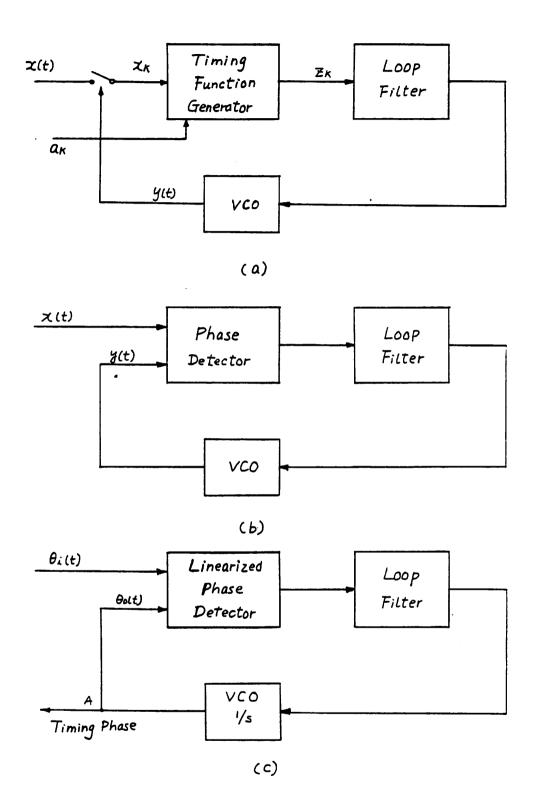

0 < t < T with period T. A Fourier series expansion can then be operated upon this averaged signal and the phase of the Fourier component at frequency  $f = f_b$  is the recovered phase.