### Copyright © 1985, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# M85/11 287 Pages

AUTOMATIC GENERATION OF SIGNAL PROCESSING INTEGRATED CIRCUITS

by

Stephen P. Pope

Memorandum No. UCB/ERL M85/11 22 February 1985

## AUTOMATIC GENERATION OF SIGNAL PROCESSING INTEGRATED CIRCUITS

by

Stephen P. Pope

Memorandum No. UCB/ERL M85/11 22 February 1985

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

#### Automatic Generation of Signal Processing Integrated Circuits

Ph.D.

Stephen P. Pope

E.E.C.S.

#### Chairman of Committee

A system for the automated design of signal processing integrated circuits is described in this thesis. The system is based on a library of circuit cells, and a software package which can configure the cells into complete integrated circuits. The architecture of the cell library is optimized for low and medium bandwidth digital signal processing applications. Circuits designed with the system use a multiprocessor architecture.

Input to the system is a design file written in a specialized programming language. Software emulation from the design file is used to verify performance. A two-pass silicon compiler is used to translate the design file into a mask-level description of an integrated circuit.

A major goal of the project is to make the system usable by those with little or no formal training in integrated circuits. A second goal is to reduce the time and cost associated with performing an integrated circuit design, while still producing designs which are reasonably efficient in their use of the technology.

Development of the system was guided by basic research on appropriate architectures and circuit constructs for signal processors. As part of this research an integrated circuit was designed which performs speech analysis and synthesis. This vocoder circuit is intended for use in low-bit-rate digital speech transmission systems.

This thesis is dedicated to my wife. Kathleen.

This thesis is decidated to my wife, retired.

ting the second of the second

•

entropies de la companya de la comp La companya de la co

and the state of t

#### Acknowledgements

The list of those who influenced this research is quite long, and it is only possible to mention a few individuals here. Among the contributors to the LPC Vocoder design, Ron Fellman. Thomas Glad and Bjorn Solberg played major roles. Jan Rabaey and Peter Reutz made large contributions to the silicon compiler work. I would also like to extend my thanks to Prof. Richard Newton and his students, without whose work on CAD tools little of this research would have been possible.

Most of all I would like to thank Prof. Robert Brodersen for his extensive support and management of this project.

#### Table of Contents

| 1. Signal Processor Design                                   | 1  |

|--------------------------------------------------------------|----|

| 1.1 Dedicated Signal Processors                              | 1  |

| 1.2 Processing of Sampled Signals                            | 3  |

| 1.3 Architectural Alternatives for Digital Signal Processing | 6  |

| 1.4 Design Methods for Digital Integrated Circuits           | 9  |

|                                                              |    |

| 2. A Single-Chip LPC Vocoder                                 | 12 |

| 2.1 Introduction                                             | 12 |

| 2.2 Processor Architecture                                   | 16 |

| 2.3 Processor Implementation                                 | 21 |

| 2.4 Adaptive Lattice Analyzer                                | 24 |

| 2.4.1 Lattice LPC Algorithm                                  | 24 |

| 2.4.2. Lattice Analyzer Implementation                       | 30 |

| 2.5 Pitch Tracker                                            | 31 |

| 2.5.1 Pitch Tracker Algorithm                                | 31 |

| 2.5.2 Pitch Tracker Implementation                           | 37 |

| 2.6 Speech synthesizer                                       | 41 |

| 2.7 The Vocoder IC                                           | 45 |

| 2.8 Conclusions                                              | 49 |

|                                                              |    |

| 3. The Macrocell Approach to Signal Processor Design         | 51 |

| 3.1 Introduction                                             | 51 |

| 3.2 Processor Architecture                                   | 54 |

| 3.3 Control Sequencer                                        | 58 |

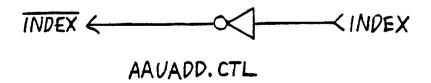

| 3.4 Address Arithmetic Unit                                  | 63 |

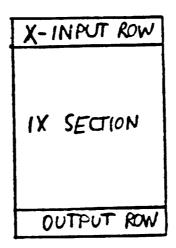

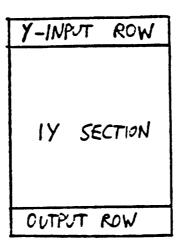

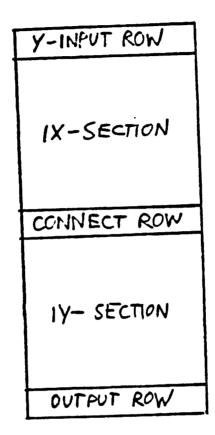

| 3.5 Processor Data Path                                      | 67 |

| 3.5.1 Data Path Organization                    | 67  |

|-------------------------------------------------|-----|

| 3.5.2 Arithmetic Unit                           | 70  |

| 3.5.3 Multiply and Divide Operations            | 72  |

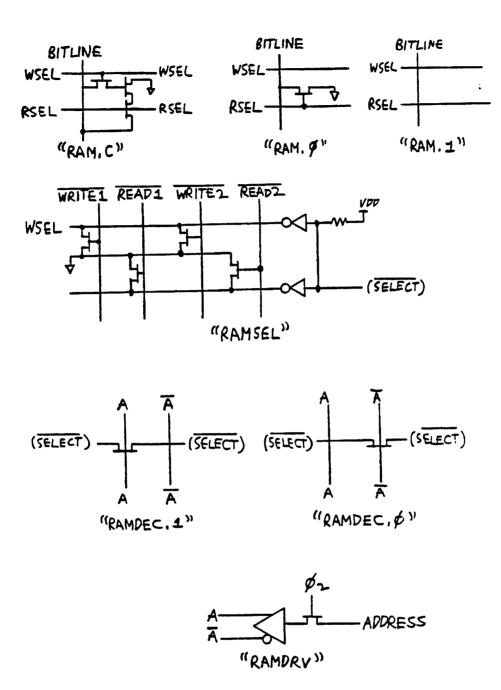

| 3.5.4 Data Memory                               | 76  |

| 3.6 Finite State Machine                        | 77  |

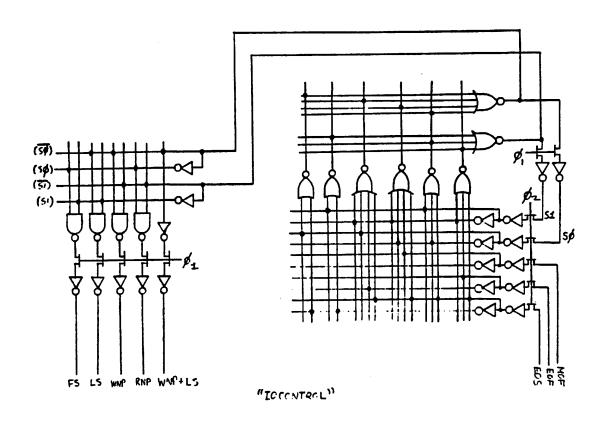

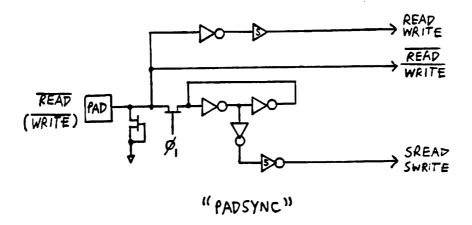

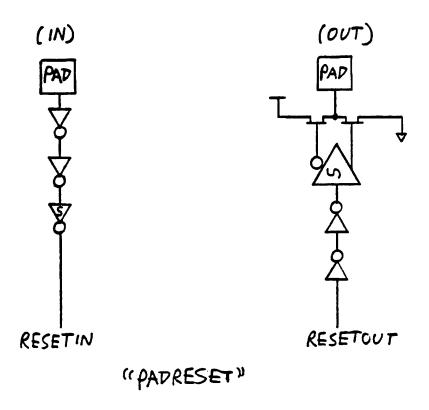

| 3.7 Input-Output and Communications             | 80  |

| 3.7.1 Off-Chip I/O                              | 80  |

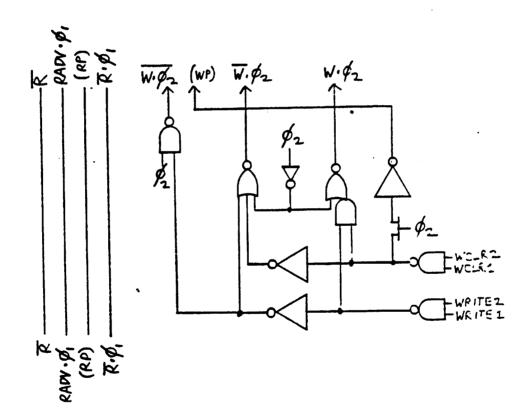

| 3.7.2 Interprocessor Communication              | 84  |

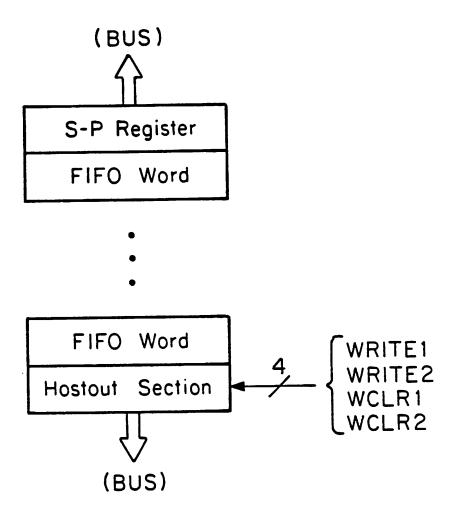

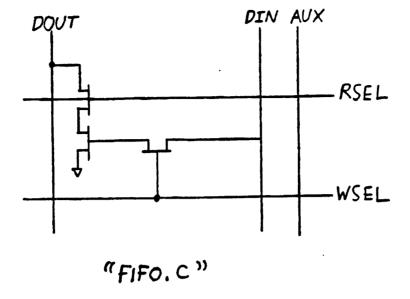

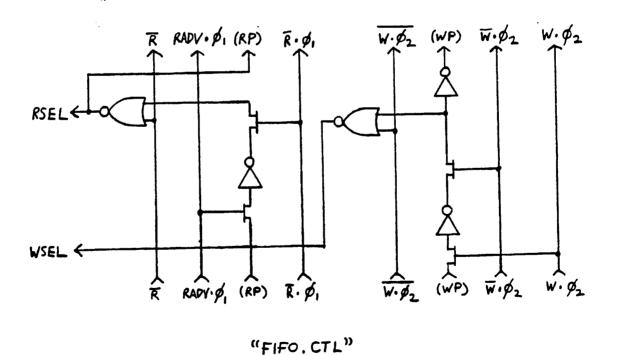

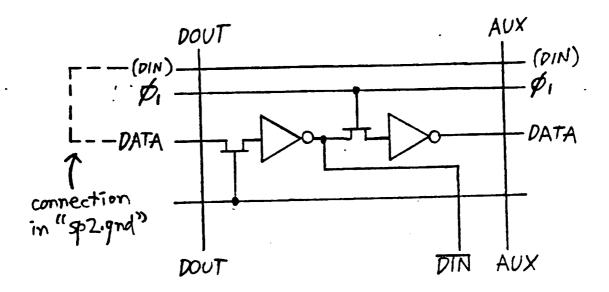

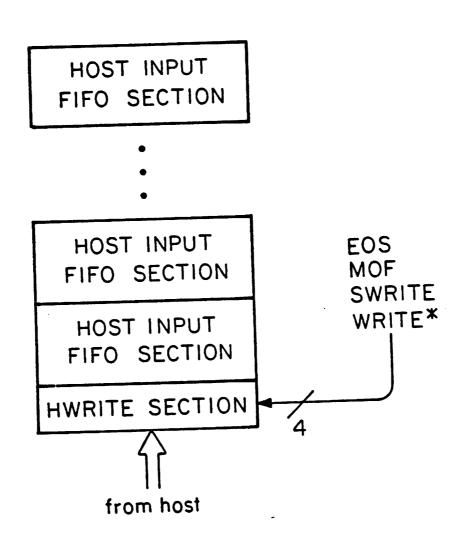

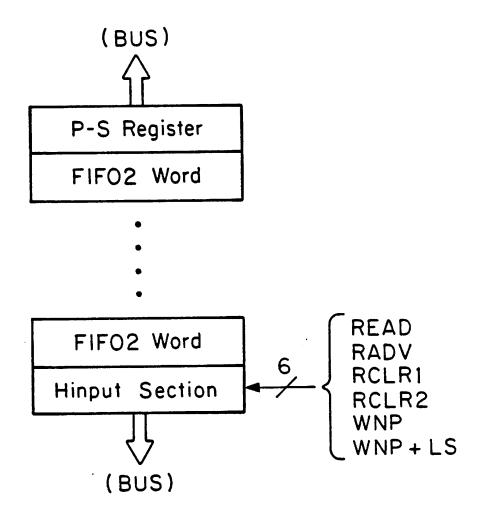

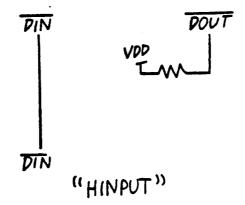

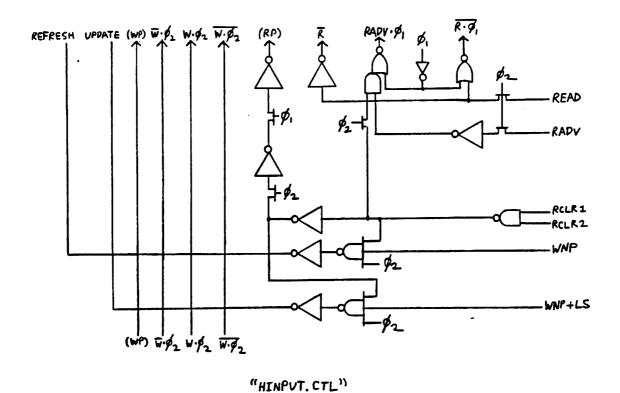

| 3.7.3 Host Interface                            | 86  |

| 3.8 Cell Library                                | 92  |

| 3.8.1 Characteristics of Library Cells          | 92  |

| 3.8.2 Technology Parameters for Macrocells      | 94  |

| 4. Software Package for Macrocell Design System | 97  |

| 4.1 Design File and Front-End Software          | 97  |

| 4.1.1 The Design File                           | 97  |

| 4.1.2 The Emulator \$104                        |     |

| 4.1.3 Silicon Compiler First Pass               | 105 |

| 4.2 Intermediate File and Macrocell Assembly    | 106 |

| 4.3 Placement and Interconnect                  | 108 |

| 4.3.1 Outline of Placement and Routing Strategy | 109 |

| 4.3.2 Processor Floorplan                       | 110 |

| 4.3.3 Technology Specification                  | 114 |

| 4.3.4 Channel Router                            | 115 |

| 4.4 Software Package Summary                    | 121 |

| 5 Case Histories and Conclusions                | 123 |

| 5.1 Digital Audio Equalizer        | 123 |

|------------------------------------|-----|

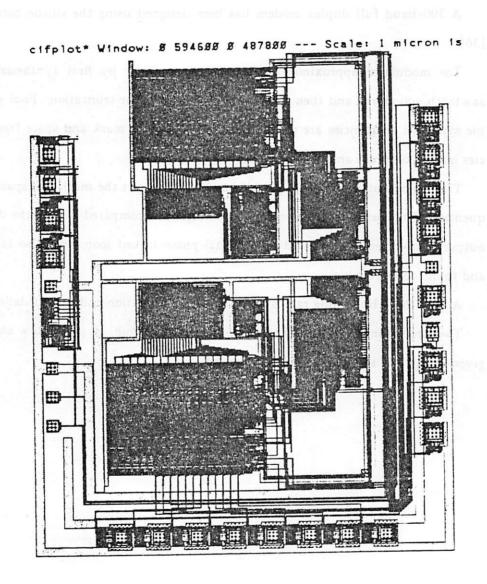

| 5.2 LPC Vocoder                    | 128 |

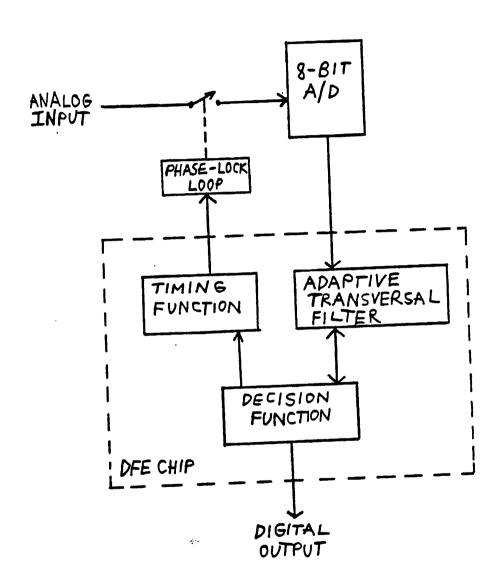

| 5.3 Decision Feedback Equalizer    | 131 |

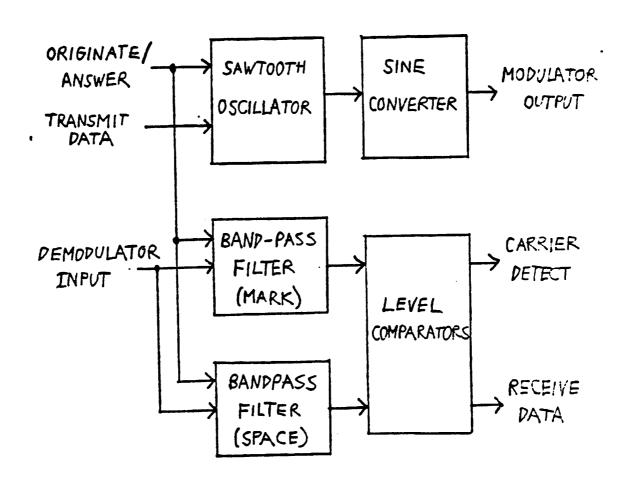

| 5.4 300-Baud Modem                 | 134 |

| 5.5 Conclusions                    | 137 |

| Appendices                         | 139 |

| A. LPC Vocoder Documentation       | 139 |

| B. NMOS Cell Library Documentation | 153 |

| C. Design File Description         | 227 |

| D. Design File Examples            | 255 |

| E. Companion Tape                  | 268 |

| References                         | 269 |

#### Chapter 1 - Digital Signal Processors

#### 1.1 Dedicated Signal Processors

The ability to design complex, large-scale integrated (LSI) circuits has not kept up with the technological advances that allow such devices to be fabricated. This situation has led to an increasing use of computer automation in integrated circuit design, and a decreasing emphasis on minimization of circuit area. This dissertation is concerned with design methods specifically intended for digital signal processing applications. The goal of such methods is the ability to implement economically important circuit functions with reasonable circuit density, while keeping the design time short.

Despite numerous predictions over the past decade that digital signal processing LSI circuits would soon have a huge impact on large segments of the industry. such an effect has not yet materialized. To better understand why this is so, it is necessary to consider how signal processing functions differ from other applications.

A signal is a representation of a time-varying physical quantity. Common examples of signals are sounds, vibrations, and electromagnetic waves. A signal processor is a device or system which conditions, analyzes, synthesizes, or otherwise modifies or creates signals.

Signal processors may be subdivided into general purpose signal processors and dedicated signal processors. A general-purpose signal processor is one that may, through reconfiguration or reprogramming, perform a variety of fundamentally different algorithms. This dissertation is concerned with dedicated signal processors — ones that perform a single algorithm. There might be a few variables or parameters that may be modified, but such a system, once created, is pretty much devoted to a single task. Also, the systems studied here are those which work with sampled and digitized (quantized) signals. Digital signal processors such as

these have a number of advantages over their analog counterparts: reproducibility. control over dynamic range and other performance aspects, and the ability to be programmed to perform complex tasks.

From an abstract point of view, virtually any computation would satisfy the above definition of signal processing. After all, the inputs and outputs of any computing system can be viewed as time sequences. From a practical point of view, signal processors are distinguished by the following two properties:

- (1) Because signals result from ongoing, real-world physical processes, certain types of processing tend to recur in different signal-processing situations. Filtering, modulation, correlation and convolution are all classical signal processing functions.

- (2) The signals involved are processed in *real time*. This means that the rate of processing is sufficient to keep up with incoming and outgoing signals. Thus processing could proceed indefinitely without loss of continuity.

Central to the research described here is the utilization of integrated circuit (IC) technology in the implementation of signal processing systems. There are two aspects in which the use of this technology is significant. First is the potential for dramatic cost savings that arises when custom integrated circuits are designed into a system. Second is the fact that conventional design methods and system architectures are no longer suitable as the level of integration becomes very high.

The remaining sections of this chapter cover background material regarding digital signal processing systems, their architectures, and techniques for their implementation using IC technology.

Chapter 2 discusses the design of an integrated circuit which implements a

low-bit-rate speech analysis/synthesis system. This LPC Vocoder integrated circuit represents a fairly complex and sophisticated signal processing system which uses a variety of processing techniques in its implementation. The LPC Vocoder IC was designed in a full custom fashion — the goal of the project was to create as efficient a vocoder implementation as possible, without solving the more general problem of implementing other, similar applications. The vocoder IC was fabricated and tested, with test results presented in Chapter 2.

Chapters 3, 4 and 5 represent a broadening of scope of the research. The premise is that similar implementation techniques can be applied to different signal processing applications with good results. To take advantage of this generality, a design system was created which allows the rapid generation of digital signal IC's. The IC's produced with this system are assembled from the cell library described in Chapter 3. Chapter 4 describes a software package which automates much of the design process. In Chapter 5 the results of this approach are presented.

#### 1.2 Processing of Sampled Signals

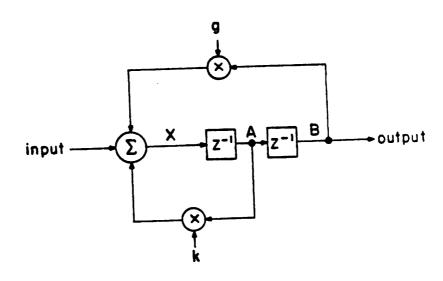

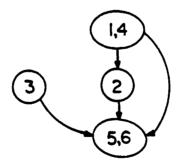

Signal processing algorithms are often presented by means of a signal flow diagram. Fig 1.1 is a signal flow diagram for a second-order filter section. Note that the primitive operations involved are multiplication, addition, and delays. All linear filters, however complex, are composed of these same operations.

The filter section may be implemented by repeatedly executing the following sequence of operations. The period of repetition is one sample interval. The quantities A and B represent the state (memory) of the filter, while X is a temporary variable. ":=" is the assignment operator.

$$X := input + kA + gB$$

out put  $:= B$

$B := A$

$A := X$

In order for this abstract program to operate properly, the timing of the system must be such that each time the program is repeated the values "input" and "output" refer to new input and output samples respectively. The four-instruction program is executed from top to bottom without branching, and repeats each sample.

Fig.1.1 Flow diagram for a second-order filter

The example above is very simple; however, it suggests that all linear digital filters (and possibly other signal processing functions as well) may be implemented with by a processor with the following properties:

- (1) A simple instruction set

- (2) A program which is executed once per sample

- (3) A lack of branches in the program flow

The research described in this dissertation demonstrates that this simple model serves as a basis for the design of reasonably powerful signal processors.

It should be noted that some system functions do not conform to the above model. Consider the Fast Fourier Transform [1], for example. In this case a block of input data (say 128 samples) is processed as a unit, resulting in an algorithm that is difficult to express by a program that repeats at the sample rate. Thus property (2) above would preclude efficient implementation of a Fast Fourier Transformer using the the approach described above.

Many signal processing algorithms make use of a frame. A frame is an interval many samples in length. The concept of a frame is significant because many interesting attributes of a signal, such as second moments and spectral characteristics, vary much less rapidly than the signal waveform itself. This being the case, it is possible to represent the desired attribute as being constant over an interval of considerably greater duration than the sample interval. This sort of data reduction is known as signal analysis and is widely used. The inverse operation, wherein a sampled-data signal is created from lower bandwidth data, is termed signal synthesis.

A typical signal processing system might consist of a front-end in which sample-rate processing is performed, an intermediate level in which frame-rate

processing is performed, and additional levels in which processing occurs at increasingly slower data rates. For those levels with a sufficiently slow data rate, conventional computer hardware may be programmed to economically perform the operations required. Other levels may require special-purpose hardware to meet performance goals.

The cell library of Chapter 3 allows a frame rate to be defined and used for the purpose of off-chip I/O. Semi-custom chips designed using the cell library can then serve as special-purpose front-end processors. I/O processing differs qualitatively from the other sorts of processing in a typical system, justifying separate hardware. Also motivating this focus is the perception that the I/O processing is often the major obstacle to a successful hardware realization.

#### 1.3 Architectural Alternatives for Digital Signal Processing

Early digital signal processors were assembled from small- and medium-scale integrated circuits. Since this approach led to rather bulky systems, a considerable degree of specialization is evident in these early designs. Typical examples would be special purpose Fast Fourier Transform (FFT) machines [2], and a computer hard-wired to perform a speech pitch detection algorithm [3]. A considerable emphasis was often placed on fast array multipliers. In fact, much of the research on multiplier implementations was done by those pursuing signal processing applications [4]. Because of the throughput requirements and real-time constraints, pipeline architectures were popular as well.

As the 1980's approached, single-chip digital signal processors started to become available. A few of these were dedicated circuits intended for special applications. An early example would be a speech synthesis chip developed by Texas Instruments for use in a toy known as the "Speak-and-Spell" [5]. Of more

interest to signal processing researchers was the availability of general purpose. programmable DSP chips such as those of N.E.C. [6]. Bell Laboratories [7]. and Texas Instruments [8]. Architecturally, these circuits all followed a standard formula. The instruction set resembles that of a conventional microprocessor. Hardware organization is also conventional, with some pipelining added and a parallel multiplier attached.

Despite heavy promotion, these general purpose processors have failed thus far to achieve widespread use. One probable reason for this is that the general-purpose architecture is seldom a good match for any given application. Such a circuit offers a fixed combination of resources (program memory, data memory, arithmetic capacity) which can not be tailored to suit the designer's needs. The inclusion of a large parallel multiplier results in an expensive part in each case. Although there is a definite need for multiply-accumulate operations in a typical signal processor, it is difficult to make efficient use of the parallel multiplier when programming the circuit to perform a complex system function.

Because of the problems described above, a number of researchers have worked on the problem of designing semi-custom digital signal processing IC's [9-11]. The goal of this work is to combine the cost-effectiveness of a full custom design (such as the vocoder chip of Chapter 2) with the short design times possible using general purpose hardware. The underlying assumption of such work is that similar applications can be efficiently implemented using different configurations of the same hardware.

Semi-custom design approaches have a target architecture to which individual designs must conform. There are several types of target architectures which have been proposed. Three general categories may be identified: (1) processors built around a parallel array multiplier: (2) bit serial processors: and (3) bit-parallel processors without parallel array multipliers.

The parallel multiplier approach is often regarded as the best signal processing solution. This is only partially true. Parallel multipliers by necessity must be constructed with a fixed precision, e.g. a 16 by 16 multiplier. They are therefore best suited for algorithms which make heavy use of multiplies, all of which require about the same precision. Unfortunately, precision requirements in signal processing algorithms vary considerably. Many multiplies require only a low precision coefficient, such as a power of two. The parallel multiplier is in these cases underutilized. Also, there is the architectural problem of getting data to and from the parallel multiplier without bottlenecks occurring. The cost, in terms of busses and registers, is high. In summary, a parallel multiplier is a high cost, high throughput hardware item that fails to see good utilization in actual practice.

The second option, bit serial designs [12], are the opposite end of the architectural spectrum. In an effort to maximally utilize the logic elements of the circuit, bit-level pipelining is used. High clock rates are needed to reap the full advantage of this approach, creating a particularly difficult low-level design problem. An advantage is that bit-serial functional units can be combined in a modular fashion, a plus if the target system is a dedicated processor. One drawback of this approach is that a number of low level functions (such as division) are not compatible with the LSB-first bit-serial format. Due to the hard-wired nature of the systems, control and decision-making functions are not easily implemented. Also, a system-wide wordlength is generally established for all data, in an effort to avoid intractable timing problems. This is a disadvantage, since all data must be represented by words of the same precision.

The third option, bit-parallel processors without parallel multipliers, is the one used for the designs described in this dissertation. An arithmetic unit which can complement, shift and accumulate bit-parallel data is used. This unit may be microprogrammed to multiply signal data by either bit-serial or signed-digit

coefficients. (Signed-digit representation provides a low-cost method for fixed coefficient multiplies, as discussed in Section 3.5.) Because the arithmetic element is relatively compact, several such processing units may be included on a single IC. Thus the advantage of modularity exhibited by the bit-serial approach is retained here. This results in a better match between algorithm and hardware organization than is possible in designs using large parallel multipliers.

The bit-parallel processors are microprogrammed, resulting in a versatility lacking in hard-wired approaches. Although fully hard-wired architectures might be more efficient in the abstract, programmability is a virtual necessity in a complex system. Control, decision-making and input-output functions are all more readily implemented in a programmable environment.

#### 1.4 Design Methods for Digital Integrated Circuits

Numerous approaches, systems and methodologies have been proposed or are in use for integrated circuit design. One reason for this is that, viewed in the abstract, integrated circuit design is a large process with a high level of complexity and many degrees of freedom. Many methodologies seek to constrain the design problem, to make it less complex while still achieving performance goals.

IC designs are ultimately specified at the geometric level on a number of mask layers. In a full-custom design, the designer has complete control over these low-level geometries. Standard cell and gate-array design methods involve specifying the design at a logical level, and creating the mask geometries from a predefined set of primitive elements. Thus standard-cell and gate-array approaches constrain the design problem to make it more tractable.

As a general rule, the more constrained the design problem is made, the more easily a design may be produced. However, this design can not be optimized to the

same extent as a full custom design.

Many IC design systems are intended to fill a certain market need. For example, a standard-cell system might be intended to produce circuits which are replacements for systems designed from a standard logic family (for example, the 74-series TTL family). Such systems have the severe drawback that the designer is using logic designs and architectures appropriate for one technology (TTL-MSI) while producing a circuit in a different technology (MOS-LSI).

In addition to the degree of customization, a distinction may be drawn between graphical and procedural methods of specifying IC layouts. In the graphical approach, the designer specifies the mask geometries directly, usually with the aid of a computerized graphics editor. In the procedural approach, the specification is at a higher, functional level; software is used to translate the higher-level specification to the mask level.

The LPC vocoder circuit described in Chapter 2 was designed with purely graphical methods. This approach resulted in a high degree of customization, and many opportunities to optimize the design. Since no procedural methods were employed, the design time was high, and the overall approach would not have been suitable for applications with much greater complexity. Architecturally, however, the methods used in the vocoder IC are applicable to even larger, more complex designs. This conclusion is the motivation for the macrocell-based design system described in Chapters 3, 4 and 5.

The term *macrocell* has been assigned various meanings in the past. It is now generally agreed that a macrocell is a large block of circuitry containing perhaps several thousand transistors. The approach used in assembling the macorcells is to tile (array) smaller rectangular cells in two dimensions. The tiling process is sufficiently flexible that the macrocells can be customized for specific tasks.

One premise of the macrocell technique is that a target application range has

been identified. This dissertation is concerned solely with digital signal processors. Typical applications would be speech processing, telecommunications and digital audio. However, the macrocell approach may be applied to any group of applications. The more narrow the application range, the more the macrocell-based designs will resemble full-custom designs in terms of architectural efficiency.

Since MOS processes evolve rather rapidly, a desirable property of an IC design system is that it can be applied to a number of different processes. Macrocell based systems can be designed such that only the underlying cell library is technology-dependent.

In summary, the macrocell approach has the following advantages:

- (1) Large blocks of circuitry are generated by procedural methods.

- (2) The underlying cell library is designed by graphical methods.

- (3) Architectures can resemble those of full-custom designs.

- (4) The design system may be ported to different technologies.

#### Chapter 2 - A Single-Chip LPC Vocoder

#### 2.1. Introduction

A number of applications benefit from the fact that, with sufficient processing, speech may be analyzed, encoded at a low data rate, and then resynthesized. For example, the available bandwidth of a telephone line or microwave channel may be better utilized if data compression methods are employed. In "voice mail" networks, where spoken messages are stored electronically and subsequently forwarded to their destination, data reduction reduces the storage cost.

In many applications, digital encoding of speech is needed to allow the use of encryption algorithms (for security) or error-correction techniques (to compensate for a noisy channel). Often, the available bandwidth is that of a voice-grade analog channel — a few kilohertz. In situations such as these, it is necessary to digitally encode speech at a low enough data rate that the digital data may be transmitted in the available bandwidth.

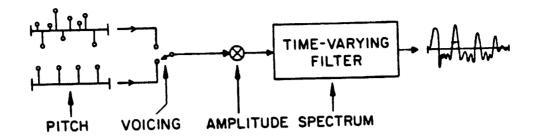

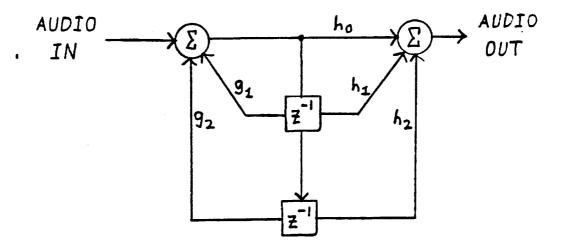

Low-bit-rate coding systems, where the transmission rate is 2400 bits/second or lower, cannot attempt to reproduce the speech waveform itself. Instead, a set of slowly-varying parameters is extracted from the speech. Synthetic speech may be generated from these parameters. A vocoder is a system of this sort based on a model for speech synthesis similar to that shown in Fig.2.1.

This model, roughly analogous to the human vocal tract, consists of an excitation source driving a time-varying filter. The excitation source is described by three parameters: voicing, pitch, and amplitude. The voicing parameter represents a binary decision between a voiced, vowel-like sound and an unvoiced sibilant. The pitch represents the fundamental period of a voiced sound.

The excitation signal presented to the filter has a flat overall spectrum. The

Fig.2.1 Vocoder speech model

Fig.2.2 Target system for the vocoder I.C.

Fig.2.3 Multiprocessor organization

filter is programmed to impart the desired time-varying spectral shape to the signal. Since a representation of this spectrum is part of the parameter set, vocoders must perform some form of spectral analysis as part of their processing. Accurate preservation of the spectral shape of the speech signal is important in maintaining intelligibility.

Because of the importance of spectral representation, vocoders are often classified according to the spectral analysis methods used. Channel vocoders use either filter-bank or transform techniques to represent the energy in different parts of the spectrum. This report describes an LPC vocoder circuit using linear predictive coding (LPC) to represent the spectrum.

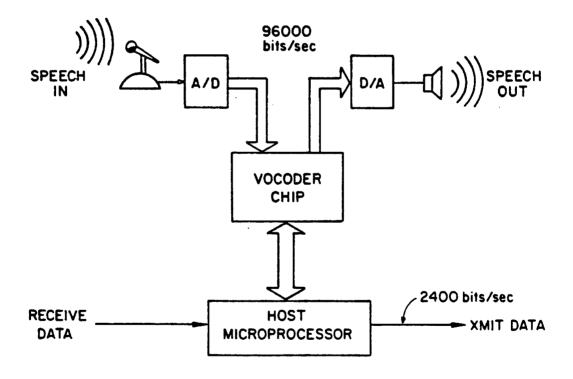

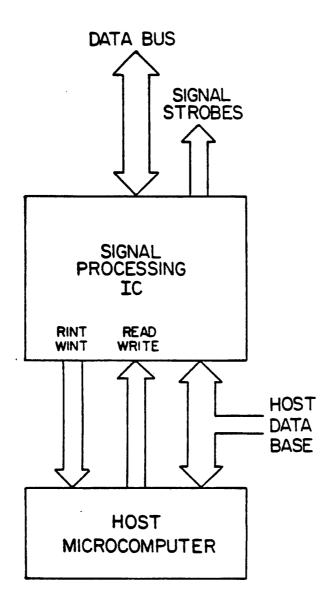

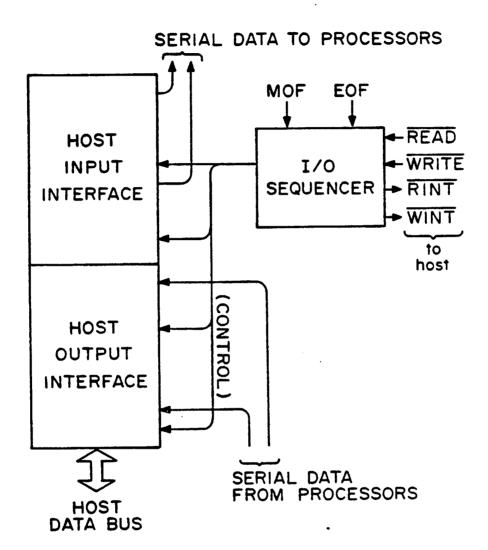

Fig. 2.2 shows how the vocoder circuit would be used in a typical application. Digitized speech (from an A/D converter) is used as input to the device. The input speech is analyzed and the resulting parameters are transferred off-chip to a host microcomputer. The host formats the data for transmission (typically at 2400 bits/second). Simultaneously, an incoming data stream is transferred to the vocoder circuit, where it is used to generate a synthetic speech signal. The vocoder thus operates in full-duplex mode, allowing two-way low-bit-rate speech transmission.

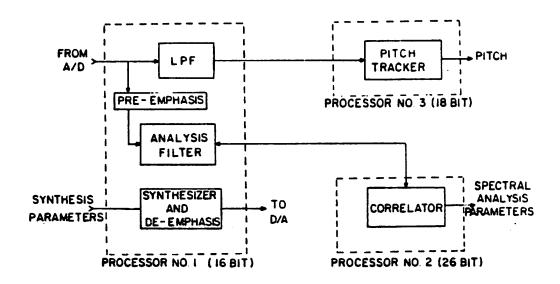

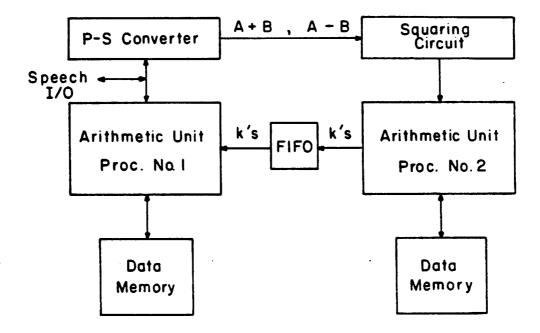

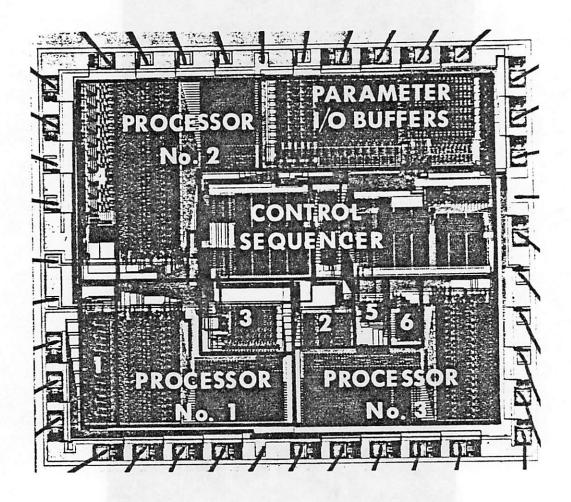

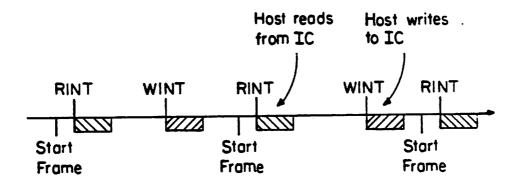

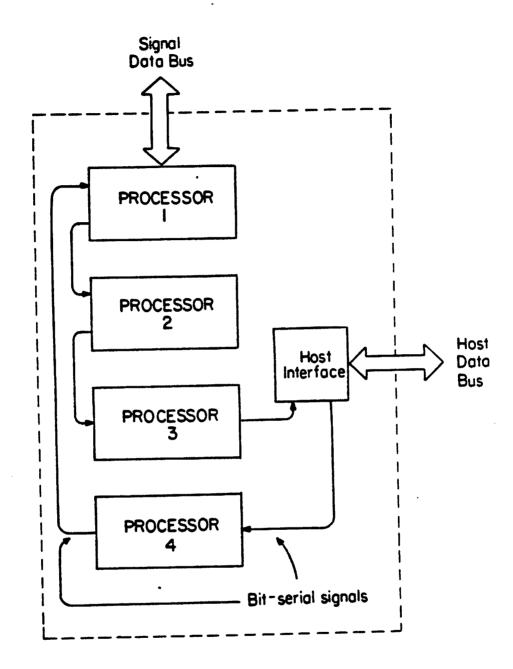

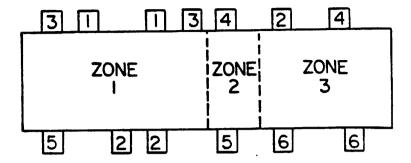

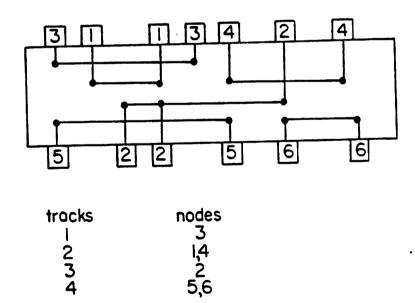

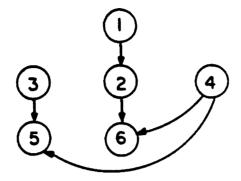

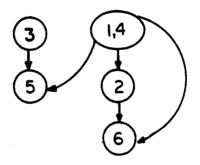

To handle the complexity needed for a complete LPC vocoder algorithm, a monolithic multiprocessor approach was used. Three processors are included on the single I.C. Each processor performs a specific part of the vocoder algorithm, as shown in Fig.2.3.

Processor No. 1 performs most of the linear filtering of the speech signals that is required. Included are lattice filters for both spectral analysis and synthesis: pre-emphasis and de-emphasis networks; and a low-pass-filter whose output is used for speech pitch detection.

Processor No. 2 computes correlation values from signals in the analysis lattice

filter. These correlation values are used for spectral estimation as described in Section 2.4.

Processor No. 3 extracts pitch and voicing information from the input speech.

The algorithm is partitioned so that each processor is fairly self-contained. Communication among the processors is performed over a small number of bit-serial data lines. This avoids the need for large parallel busses between processors. The use of multiple, dedicated processors and bit-serial communication contributes to the area efficiency of the circuit.

#### 2.2 Processor Architecture

Vocoder algorithms require a fairly diverse set of operations in their realization. Because of this a microprogrammed approach was used in the vocoder IC. Each processor contains a read/write memory and a simple arithmetic unit which, under control of a microsequencer, is programmed to perform the operations required. Among the operations used are multiply-accumulate, division, absolute value (rectification), and comparison. These operations may be combined to create complex functions such as filtering, correlation, and pitch extraction.

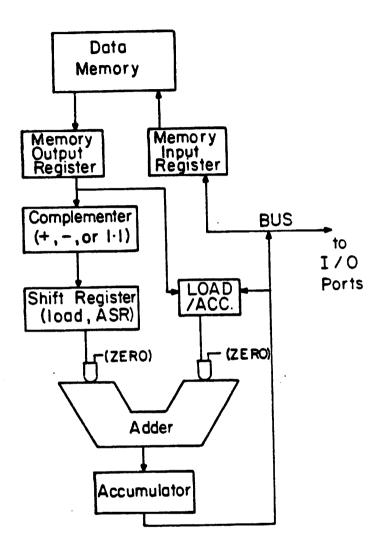

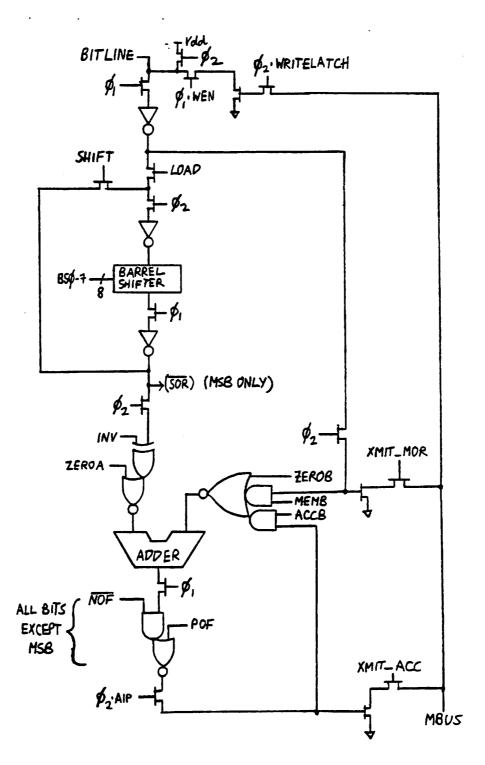

Multiply-accumulate operations are a common feature of signal processing algorithms. Examples are the programmable lattice filters used in both the spectral analysis and speech synthesis portions of the vocoder. The multiply-accumulate operations are implemented by programming the arithmetic unit shown in Fig.2.4. This involves multiplying signal data which is internal to the processor's readwrite memory by externally available coefficients. The sample delays are implemented by providing the appropriate address sequence to the memory.

Data in the read-write memory and the arithmetic unit are represented as parallel two's complement words. The word length is optimized for each of the

Fig. 2.4 Arithmetic unit block diagram

three processors. Processor No.1, used for linear filtering of the speech signal, has a 16-bit word.

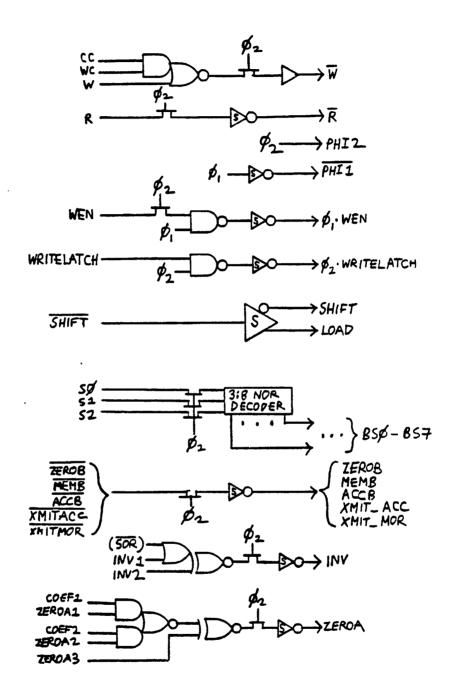

The arithmetic unit contains three pipeline registers (MOR, SR, and ACC) and a transparent latch (MIR). Pipelining allows concurrent memory access, invert/shift, and accumulate operations, resulting in good throughput for a relatively compact circuit. Operation is best understood by the action of microinstructions on the contents of these registers.

The memory output register (MOR) is loaded each cycle with the result of a memory access. The accessed data is available the following cycle. There are no control options.

The shift register (SR) may be either loaded or shifted right arithmetically. When loading the shift register, the MOR is used as input, and may be optionally complemented. Options include true, complement, or absolute-value data; and complementing by the sign bit of an externally available coefficient bit. The following symbolic microinstructions describe these actions:

sr := sr/2

sr := mor

sr := -mor

sr := |mor|

sr := mor.coef

A number of different options are available as input for the accumulator. The B-inputs of the adder may be set equal to zero. ACC, or MOR. The A-inputs may be set equal to zero. SR, or the contents of SR gated with a bit from an external coefficient. These options are described by the following microinstructions:

acc := 0

acc := mor

acc := acc

acc := sr

acc := sr + mor

acc := sr + acc

acc := coef\*sr

acc := coef\*sr + mor

acc := coef\*sr + acc

The memory input register (MIR) is a transparent latch which has as input either ACC or an external signal from the I/O bus. (The external signal may be bit-serial data originating from one of the other two processors on the chip which has been converted to bit-parallel form.) The MIR may be loaded or held under program control. When loaded, the new data is available the same cycle. Loading is indicated by the "load enable" microinstruction:

load\_en

The purpose of the MIR is to hold temporarily a value which needs to be stored in the read/write memory. By holding such a value until the next free memory cycle, memory access conflicts are avoided.

Microinstructions are also used to address and control the read/write memory. All told, a horizontal control word of approximately 24 bits is used for controlling each processor.

In much of the processing needed for the vocoder algorithm, the most prevalent operations are multiply-accumulates by a variable coefficient. To allow this, the coefficient is made available in a bit-serial, sign-magnitude, MSB-first format. The multiply is performed by first complementing the data with the sign bit of the coefficient, then accumulating a sequence of right-shifted partial products which are gated with the magnitude bits of the coefficient.

The following microcode fragment performs a multiply-accumulate. The coefficient is eight bits. The data is first read into MOR, then microinstructions are executed as shown below. Because of the pipelining, microinstructions controlling SR and ACC are given on the same line and occur on the same cycle.

At the end of this sequence, MIR contains the result of the multiply added to the prior contents of ACC. The "single-accumulator" architecture allows the same accumulator register to be used for summing partial products and accumulating the results of a series of multiplies. This parallel-serial approach to multiplication results in a low-cost implementation of the multiplies required for the lattice filters used in the vocoder.

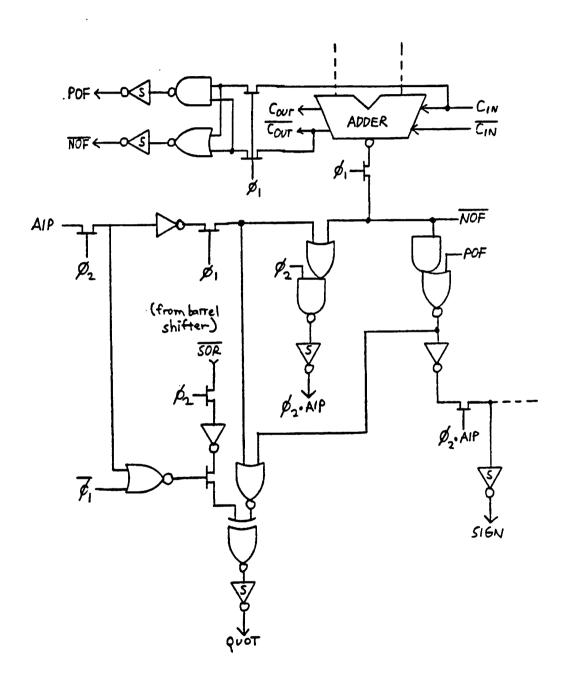

The adder element of the arithmetic unit employs saturation logic, which limits the result of an addition to the maximum positive or negative value upon positive or negative overflow respectively. Among other advantages, this rules out the possibility of large-amplitude limit cycles in recursive filters.

The processor arithmetic unit described above is based on a single accumulator, performing multiply/ accumulate operations by a microprogrammed. "shift and add" method. The small circuit area occupied by this arithmetic unit is a key feature allowing multiple processors and high throughput in the vocoder IC.

#### 2.3 Processor Implementation

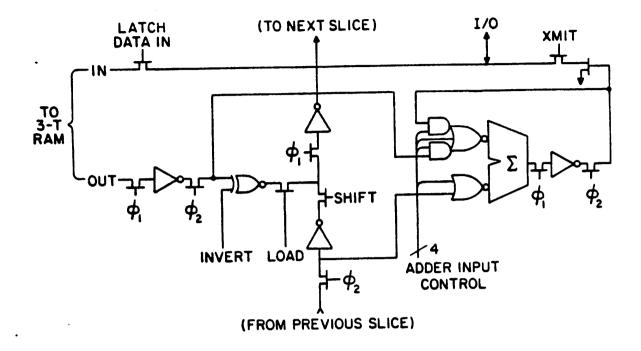

In order to easily implement processor arithmetic units with different word lengths, a bit-slice organization for the arithmetic unit was used. Due to the fact that the arithmetic unit bit-slice is replicated many times in the three processors that comprise the vocoder circuit, considerable effort was spent making this element compact and high-performance. The schematic for a single bit-slice is shown in Fig.2.5. (This schematic is slightly simplified; part of the memory interface, and the adder saturation logic, are not shown.)

Each bit-slice contains 65 transistors and occupies an area of about 100 sq. mils. This small size makes possible the inclusion of multiple processors in the vocoder I.C. By way of contrast, a single 16 x 16 array multiplier (often thought of as an essential element of a digital signal processor) would exceed in area all three of the arithmetic units on the vocoder circuit.

Fig. 2.5 Arithmetic unit bit-slice schematic

Fig. 2.6 Adder schematic

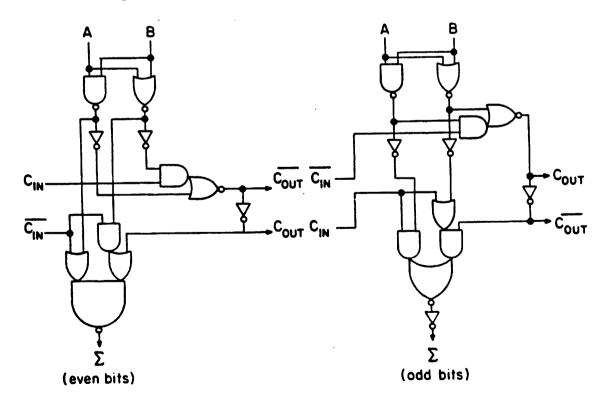

Because of the bit-slice organization, the adder circuit used in the arithmetic unit is a ripple-carry design. Separate circuits were designed for the odd-numbered and even-numbered bit slices, as shown in Fig.2.6. Layout and circuit design were carefully optimized to minimize nodal capacitances along the carry chain. Since carry outputs are used in the sum generation logic, each carry output feeds a minimum-size inverter which isolates this logic from unnecessarily loading the carry chain.

The use of separate odd and even adder circuits, alternating between positive and negative logic, provides a single level of gate delay for each bit in the carry chain. Add times under 200 nsec, for 26 bits were typically measured. The performance of the adder is well-matched to other critical paths in the vocoder circuit, such as RAM and ROM access times, and does not by itself limit the computation rate.

The processor data memory uses the three transistor cell, chosen because of its relative insensitivity to process parameters and supply voltage variation. As is the case with word lengths, the number of words in the data memory of each processor is chosen to match that processor's function. The data memory is laid out on a more narrow pitch than the arithmetic unit bit-slice, with the memory bit-lines routed to the bit-slice array.

Additional flexibility is provided by allowing some of the memory locations to be programmed with read-only constants. This is needed in the implementation of the pitch tracker algorithm discussed in Section 2.5. In this algorithm, it is necessary to compare signals to constant thresholds. Note that the approach of directly including constants in the data path makes inclusion of a gateway between control and data paths unnecessary.

Each processor contains a small amount of control circuitry along one edge of the bit-slice array. This circuitry buffers the control signals that the microsequencer sends to the processor, and allows external coefficients to be multiplexed into the control path as discussed in Section 2.2. Circuitry is also included that allows for long division operations in a manner similar to the parallel-serial multiply operations discussed above.

#### 2.4 Adaptive Lattice Analyzer

#### 2.4.1 Lattice LPC Algorithm

Preservation of spectral information is essential to any speech coding technique. One approach to spectral analysis models the speech samples as a random process whose second-order statistics are stationary over short time intervals. This leads to the LPC (linear predictive coding) method [13], so named because it involves predicting the value of an incoming sample as a linear combination of previous samples. The number of previous samples used in the linear combination is referred to as the order of the analysis. For speech coding, a tenth-order LPC analysis is often used [14].

The spectral information that results from an LPC analysis can be represented in one of several equivalent forms: predictor coefficients, normalized autocorrelation values, log area ratios, and reflection coefficients [15]. Each of these forms may be translated into any of the others, so each is a possible choice as part of the parameter set for a vocoder. The reflection coefficients (also known as partial correlation values) have the following practical advantages:

- (1) The spectrum is relatively insensitive to quantization errors of the reflection coefficients.

- (2) The reflection coefficients may be computed by an adaptive filter structure

known as the adaptive lattice analyzer, described below.

(3) The reflection coefficients may be used to program an all-pole filter (described in Section 2.6) which is used for resynthesizing vocoded speech.

A typical speech coding format is the 2400 bit/second LPC-10 format, which transmits a set of ten reflection coefficients every 22.5 milliseconds [16]. Thus it is convenient to use an LPC analysis method that yields these reflection coefficients directly, rather than first computing one of the other equivalent LPC parameter sets and converting to reflection coefficients.

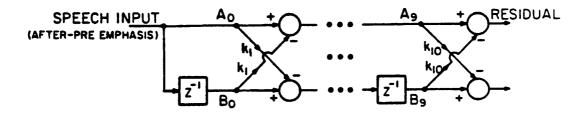

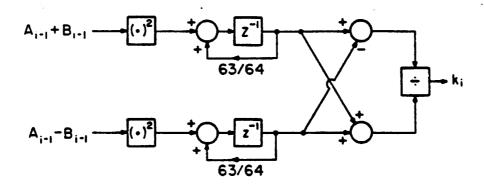

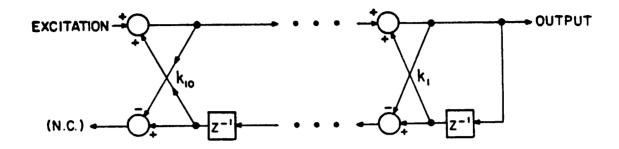

The adaptive lattice analyzer contains two parts: an all-zero programmable lattice filter (Fig.2.7) and a correlator (Fig.2.8). The lattice filter contains ten identical stages, each of which has two inputs  $A_{i-1}$  and  $B_{i-1}$ . These inputs are fed to the correlator, which computes  $k_i$  as the normalized cross-correlation of  $A_{i-1}$  and  $B_{i-1}$ . For stationary input signals,  $A_{i-1}$  and  $B_{i-1}$  have the same energy

$$EA_{i-1}^2 = EB_{i-1}^2$$

(where E is the expected value operator). Burg [17] first proposed using the average of these two energies for computing the normalized cross correlation

$$k_i = \frac{2EA_{i-1}B_{i-1}}{EA_{i-1}^2 + EB_{i-1}^2}$$

The  $k_i$  are limited to values between -1 and +1. The vocoder IC computes the  $k_i$  to a precision of eight bits. This exceeds the precision requirements for commonly used 2400 bit/second transmission formats.

The outputs of the correlator are the  $k_i$ 's, which are then used to program the lattice filter. Each  $k_i$  is recomputed every sample interval, allowing the lattice analyzer to adapt continuously to the changing statistics of the input signal.

The correlation (Fig.2.8) uses a single pole low-pass filter to approximate the expected value operator. Kang [18] claims a small performance improvement if a two-pole filter is used here.

The output  $A_{10}$  of the tenth-order lattice analyzer is known as the residual. and can be thought of as the input signal filtered so as to remove most of the correlation between samples. In the frequency domain, this means the residual will have a spectrum that is close to flat. The spectral information that has been removed is contained in the  $k_i$ .

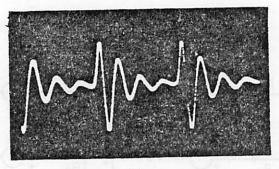

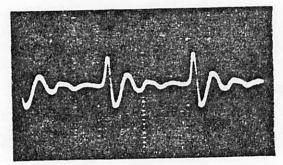

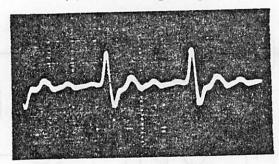

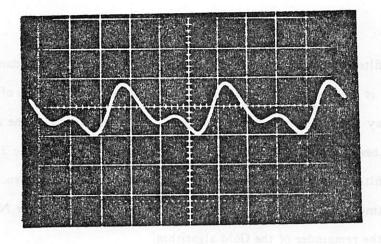

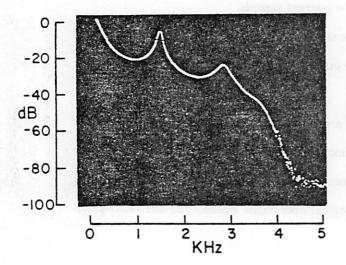

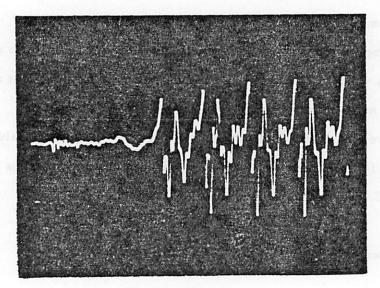

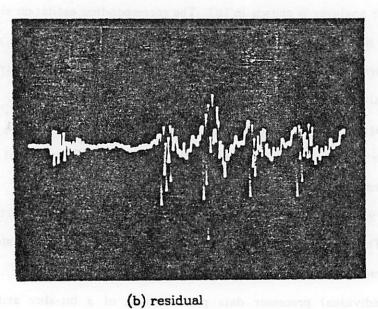

This effect is illustrated in Fig.2.9. These photographs were obtained by applying a periodic input signal to the input of the vocoder IC's lattice analyzer, and monitoring the signal  $A_i$  at different stages in the filter. These signals appear on the data bus of Processor No. 1 and were strobed into a D/A converter to obtain the data. The input signal to the lattice analyzer has a periodicity of 200 Hz, and exhibits a strong resonance at about 1 kHz. This resonance is apparent from the ringing in the time response. As the signal travels through the lattice this resonance becomes less pronounced. The residual output of the final stage resembles an impulse train, which has a flat overall spectral shape. The fine structure of the spectrum is preserved in the residual. In this illustration, the spectral fine structure is characterized by a concentration of spectral energy at harmonics of the 200 Hz fundamental. Although this fine structure is not extracted by the lattice analyzer, in an LPC vocoder some of this information is extracted by performing a pitch analysis (described in Section 2.5).

In the vocoder IC, the lattice analyzer is preceded by a pre-emphasis filter with the transfer function  $1-\frac{15}{16}z^{-1}$ . The pre-emphasis serves to improve the

Fig.2.7 Analysis lattice filter

Fig.2.8 Correlator

(a) Input

(b) Second stage output

(c) Fourth stage output

(d) Tenth stage output (residual)

Fig.2.9 Signals at different points in lattice analyzer

Fig.2.10 Configuration of Processors 1 and 2

distribution of the reflection coefficients.

# 2.4.2 Lattice Analyzer Implementation

Implementation of the lattice analyzer was the dominant issue when studying appropriate architectures for the vocoder IC. The lattice filter itself requires variable-coefficient multiplies, while the correlator requires a squaring operation, fixed-coefficient multiplies, and a two-quadrant division (two-quadrant because the denominator is always positive). Both lattice filter and correlator require single-sample delay operators. The processor structure described in Section 2.2 is characterized by a single-accumulator arithmetic unit and an addressible data memory. This processor may be programmed to perform the multiply-accumulate, divide, and delay operations required. Combined with a look-up table that approximates the squaring operator, this processor becomes a suitable architecture for the lattice analyzer.

The computation for the lattice filter is divided between two processors. Fig. 2.10 shows the data path organization for these two processors. Processor No. 1 implements the pre-emphasis filter and the ten lattice filter stages. Processor No. 1 also implements the ten-stage all-pole lattice synthesis filter described in section 2.6. The microcode for a single stage of each ten-stage filter is contained in a subprogram, which is iterated ten times per sample interval to implement the two filters. The subroutine also computes the values  $A_{i-1}+B_{i-1}$  and  $A_{i-1}-B_{i-1}$ , which are inputs to the squaring look-up table. These two values are transmitted over bit-serial lines to the squaring circuit, which is physically located adjacent to Processor No. 2. Processor No. 1 has a 16 bit wordlength.

The input to the squaring circuit is truncated to 12 bits unsigned, and the 20 most significant bits of the squared output are preserved. This output is used as

input to Processor No. 2, which has a 26 bit wordlength. A longer wordlength is required for Processor No. 2 since squaring a signal doubles its dynamic range.

Processor No. 2 is programmmed with the two single-pole estimation filters and the divide operation. These operations form a subroutine which is iterated ten times per sample interval, computing the ten reflection coefficients  $k_i$ . The  $k_i$  appear as a bit-serial output signal resulting from the long division operation. This bit-serial signal is routed back to Processor No. 1.

The adaptive lattice analyzer requires half the resources of Processor No. 1 and all of Processor No. 2. This amounts to half of the resources of the three-processor vocoder IC being devoted to the important task of spectral analysis.

### 2.5 Pitch Tracker

## 2.5.1 Pitch Tracker Algorithm

In addition to the spectral analysis described in the section above, the speech input of the vocoder must be analyzed for excitation parameters. Referring to the parameter set shown in Fig.2.1, the pitch period and voiced/unvoiced decision are both provided by implementing a pitch tracking algorithm developed by B. Gold [19]. With only minor changes, the algorithm used is referred to in [19] as the "second modification" of the original Gold Pitch Tracker.

In contrast with the algorithms for lattice analysis and synthesiser, the pitch tracker requires a variety of non-linear and decision-making operations. These include peak detection. Boolean arithmetic, comparing signals to constant thresholds, incrementing and resetting counters, and selecting the maximum among a set of signals.

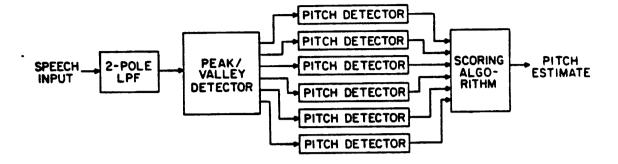

This algorithm is shown diagramatically in Fig.2.11. The input speech is first

Fig.2.11 Gold Pitch Tracker algorithm

Fig. 2.12 Six signals formed after peak-valley detection

(c) Pitch Period Counter

Fig.2.13 Signals from one of the six pitch detectors

low-pass filtered to a bandwidth of a few hundred Hertz. The fundamental pitch frequency is assumed to lie within this band. However, harmonics of the fundamental may also pass through the low-pass filter. The intent of the algorithm is to reject these harmonics and extract the fundamental period. The 2-pole linear low-pass filter is implemented by a short section of microcode in Processor No. 1. The resulting signal is then sent over a bit-serial line to Processor No. 3, which performs the remainder of the Gold algorithm.

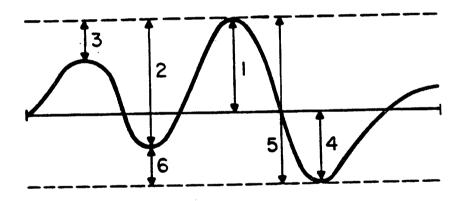

First, peaks and valleys in the low-pass filtered speech are detected. Values for the amplitudes of the most recent peak and previous valley are maintained. Six new signals are formed, each being a different combinations of the current input sample (CS), the amplitudes of the previous peak (LP), and the amplitude of the previous valley (LP). With proper interpretation, these six signals correspond to the six quantities indicated in Fig.2.12:

| signal | computed as | examined at   | interpreted as                                                        |

|--------|-------------|---------------|-----------------------------------------------------------------------|

| 1      | cs          | input peaks   | magnitude of peaks                                                    |

| 2      | (CS-LV)/2   | input peaks   | difference in magnitude<br>between peaks and the<br>preceding valleys |

| 3      | (CS-LP)/2   | input peaks   | difference in magnitude between adjacent peaks                        |

| 4      | -cs         | input valleys | magnitude of valleys                                                  |

| 5      | (LP-CS)/2   | input valleys | difference in magnitude<br>between valleys and the<br>preceding peaks |

| 6      | (LV-CS)/2   | input valleys | difference in magnitude between adjacent valleys                      |

(The values of these signals are ignored except at input peaks and valleys as shown above.)

The six signals are sent to six identical pitch detectors. These pitch detectors each form a estimate of the time interval (period) between major peaks in their inputs. A basic premise of the Gold algorithm is that of parallel processing: each individual pitch detector forms a pitch period estimate which is not in itself reliable. However, by combining the six estimate a reliable pitch estimate is obtained.

Each pitch detector functions by timing the interval between major peaks in its signal. To accomplish this, a means of rejecting minor, insignificant peaks is required. The decision as to whether the input is at a major input peak is based on three criteria:

- (1) The peak detector input must be at a peak or valley as given in the above table.

- (2) After a major peak is detected, a blanking interval of three milliseconds (24 samples) duration is entered during which all peaks are rejected.

- (3) Following the blanking interval, an exponentially-decaying threshold signal is computed. This threshold is initialized with the amplitude of the previously detected peak, and decays with a time constant of five milliseconds. Minor peaks which fail to exceed this threshold are ignored.

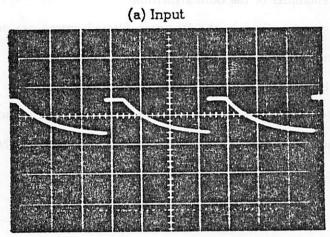

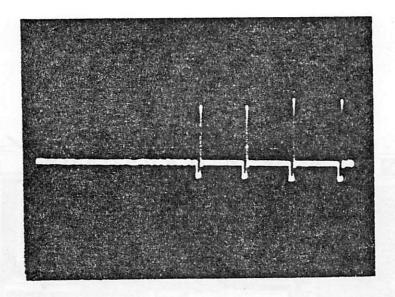

- Fig.2.13 illustrates the function of one of the six pitch detectors. These photographs were obtained by strobing various signals appearing on the data bus of Processor No.3. into a D/A converter. The top photo (a) is the input to the pitch detector. In this example there is a strong second harmonic which the pitch detector succeeds in rejecting. Photo (b) shows the threshold signal, with the blanking interval and exponential decay in evidence. The sawtooth waveform of the bottom photo (c) is the value of the pitch period counter. This counter is sampled prior to being reset to give a pitch period estimate.

In this way six estimates of the pitch are obtained. Each estimate is regarded as a candidate for possibly being the actual pitch period. A scoring algorithm is used to select one of the six as the best estimate. Each candidate is given a score

ranging from one to eighteen by performing a "window comparison" between the candidate and each of the following eighteen values:

The six current pitch estimates (i.e., the candidates themselves):

The previous pitch estimates from each of the six detectors:

The sum of the current and previous estimates for each detector.

(The rationale for including the sum of consecutive estimates from a pitch detector is that a pitch detector often locks on to the second harmonic rather than the fundamental. In this case the sum of two consecutive estimates is the period of the fundamental.)

If none of the estimates has a score greater than a fixed threshold the input speech is determined to be unvoiced and no pitch estimate is outputted.

## 2.5.2 Pitch Tracker Implementation

The pitch tracker microprogram is organized into a main program followed by six iterations of a subprogram. The entire microprogram repeats each sample interval. each input sample. The main program performs the peak/valley detection and part of the scoring algorithm. The subprogram implements the pitch detectors and most of the scoring computation.

The main program performs the following functions:

- (1) Maintains the variables LP and LV (last peak and valley)

- (2) Forms the six pitch detector input signals

- (3) Decides if one of the six pitch estimates (the "current candidate") has the highest score so far. The current candidate may change from sample to sample.

Fig.2.14 Processor No. 3 with FSM attached

(4) Every six samples, makes a pitch/voicing decision and transmits either the winning pitch estimate, or zero if unvoiced.

Each subprogram iteration performs the following functions for one of the six pitch detectors:

- (1) Implements the pitch detector by maintaining the threshold level, the pitch period counter, and values for the current and previous pitch estimate.

- (2) Adds the pitch detector's contribution to the score of the current candidate.

By computing the score for one candidate each sample, the pitch tracker makes a new pitch determination every six samples. Note that decimation is involved here. One could compute all six scores every sample interval, selecting a new value for the pitch estimate each time. However, a vocoder system does not require pitch estimates this frequently. Thus one can reduce the computational requirements by decimating to a lower sample rate for the scoring computation.

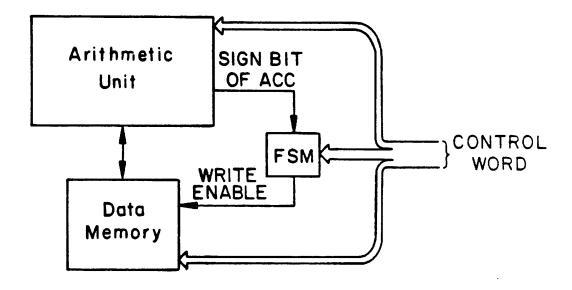

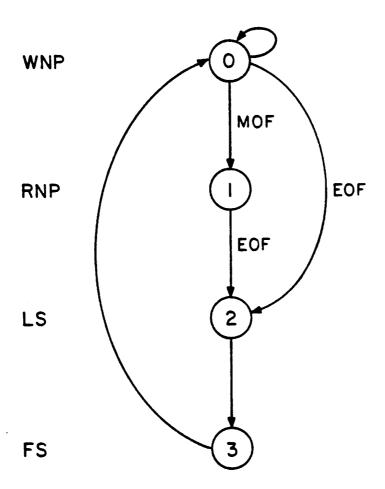

Implementing the algorithm above using the arithmetic processor that has been described requires additional hardware to support the decision-making and conditional operations required. This is in contrast to the spectral analysis and synthesis parts of the vocoder algorithm, which involve little or no conditional logic. To support the need for decision-making capability, two hardware features were included in Processor No. 3: a small finite-state machine (FSM), and a special conditional write operation. Fig.2.14 shows how this FSM is attached to the data and control paths for Processor No. 3.

The FSM is customized to perform the exact logical operations that are needed in the pitch detection algorithm. The FSM has three bits of state:

| CC   | Condition Code                           |

|------|------------------------------------------|

| SLP  | The slope of the input signal            |

| LSLP | The value of SLP for the previous sample |

The CC (condition code) bit must be true for a conditional write (WC) instruction to effect a write cycle.

The inputs to the FSM are control signals from the microsequencer and the sign bit of the accumulator. (In the following, SIGN is true if the accumulator is non-negative.) These seven microinstructions were used to modify the state of the FSM:

| instruction | action                                          |

|-------------|-------------------------------------------------|

| SET         | CC := SIGN                                      |

| AND-        | CC := CC and (not SIGN)                         |

| SSL         | LSLP := SLP; SLP := SIGN                        |

| SIP         | CC := LSLP and (not SLP)                        |

| SIV         | CC := SLP and (not LSLP)                        |

| SPV         | even subroutine iterations: functions as SIP    |

|             | odd subroutine iterations: functions as SIV     |

| VPE         | "valid pitch estimate" (true every six samples) |

The FSM instructions are executed concurrently with the data path instructions (described in section 2.2.) for Processor No. 3.

The SET and AND- instructions allow comparisons to be made. The SSL instruction is executed once per sample, after loading CS-LS into the accumulator. This sets the boolean variables SLP and LSLP to indicate the slope of the input

signal the slope of the input at the current and previous sample instant respectively. SLP and LSLP can then be decoded to indicate whether the input is at a peak or valley. This allows implementation of the SIP. SIV and SPV instructions for the FSM.

The conditional write instruction assigns the MIR to a variable in data memory only if CC is set true. The following example shows how this is used to maintain the variable LP, which holds the amplitude of the most recent input peak. The following sequence of instructions maintains the value of LP.

R CS : read current sample from data memory

acc:=mor SIP load\_en : MIR = current sample

: CC is true only if at a peak

WC LP : store current sample in LP only if at peak

In summary, the use of a FSM and a conditional write instruction replaces the role of logical instructions and conditional branches in a conventional computer architecture. The FSM attached to Processor No. 3 is quite small (only eighteen product terms), but can perform the logical operations needed for the Gold pitch tracker algorithm.

## 2.6 Speech Synthesizer

The speech synthesizer function of the vocoder IC is performed using a system resembling the vocoder model for speech production. Fig.2.1. The excitation source has amplitude and pitch/voicing parameters as inputs, with its output driving a synthesis filter. The filter is programmed with a set of ten reflection coefficients.

MEASURED RESPONSE

COMPUTER SIMULATION

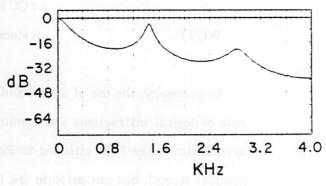

Fig. 2.16 Predicted and measured response of synthesis filter

Fig.2.15 Lattice synthesis filter

Fig.2.17 Voiced excitation waveform

Compared to the spectral and pitch/voicing analysis, the speech synthesis functions of the vocoder IC require relatively little hardware. About half of the resources of Processor No. 1 are devoted to implementing the lattice synthesis filter. Fig.2.15., and a de-emphasis network with the following response:

$$\frac{1}{1-\frac{3}{4}z^{-1}}$$

In addition, a small amount of specially-designed circuitry serves as the excitation source. Alternatively, an external excitation source may be used, allowing application of the vocoder IC in a base-band or voice excited vocoder [20].

The predicted and measured response of the lattice synthesis filter when programmed with a fixed set of reflection coefficients is shown in Fig.2.16. The reflection coefficients used were:

$$k_1 = 0.391$$

$$k_2 = -0.586$$

$$k_3 = 0.703$$

(all other k's are zero)

The measured response exhibits a rolloff due to anti-alias filtering in the test fixture. Taking this into account, the agreement between the predicted and measured responses is very close.

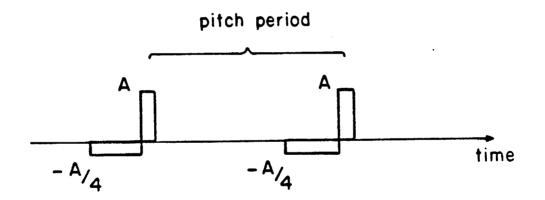

A number of different waveforms can be used for the unvoiced and voiced excitation waveforms. The voiced waveform used in the vocoder IC consists of a unit impulse train (whose period is the pitch period) convolved with the function shown in Fig.2.17. This function imparts a high-pass response to the otherwise

flat spectrum of the impulse train.

Each sample of the unvoiced excitation waveform has a magnitude of A/4, but with a sign which is the output of a pseudo/random generator. This results in a white (but not Gaussian) unvoiced excitation.

The unvoiced waveform has no D.C. component (i.e., average value of zero). The reason for using a high-pass waveform for the voiced excitation is to avoid an audible D.C. level shift on voiced/unvoiced transitions.

#### 2.7 The Vocoder IC

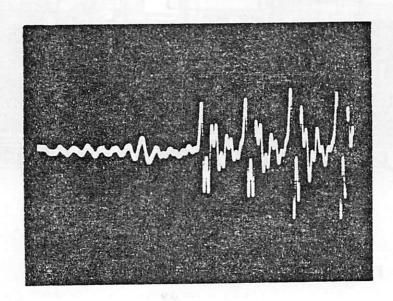

Fig.2.18 shows a complete analysis/synthesis sequence as performed by the vocoder IC. The input to the analyzer is shown in (a). This is a speech fragment of approximately 45 milliseconds in length. The residual output of the vocoder IC's lattice analyzer is shown in (b). The corresponding excitation signal (from a computer simulation) is shown in (c). The IC's lattice synthesizer, when excited by this signal and programmed with the reflection coefficients computed by the lattice analyzer, produced the synthetic speech signal shown in (d). Total length of the fragment is 44 milliseconds, divided into four frames of 11 milliseconds each. One set of pitch, voicing, energy, and reflection coefficient values was transmitted each frame.

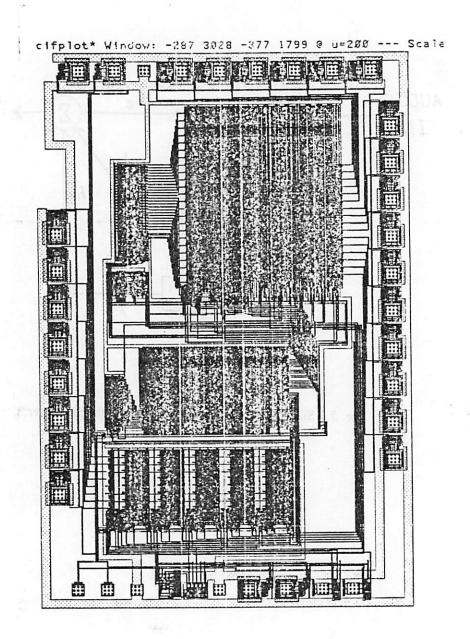

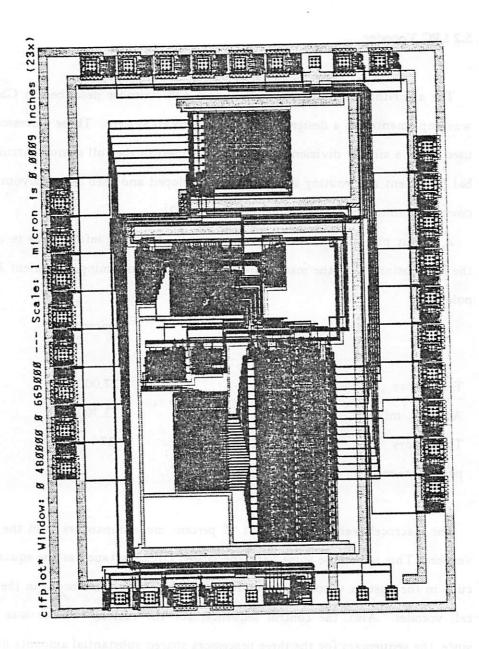

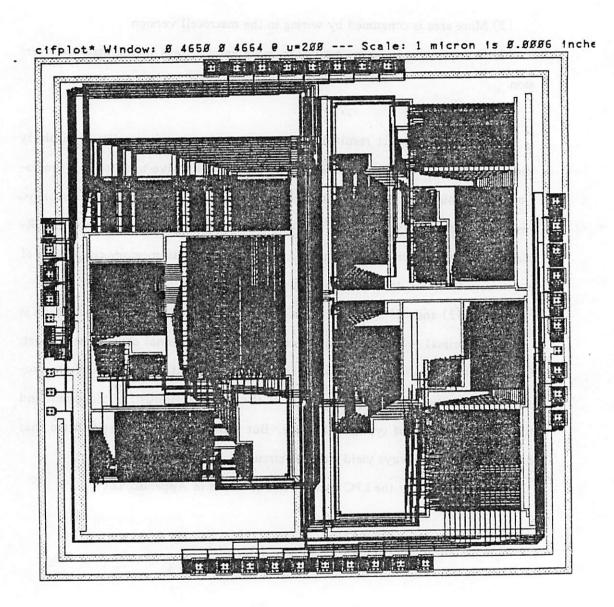

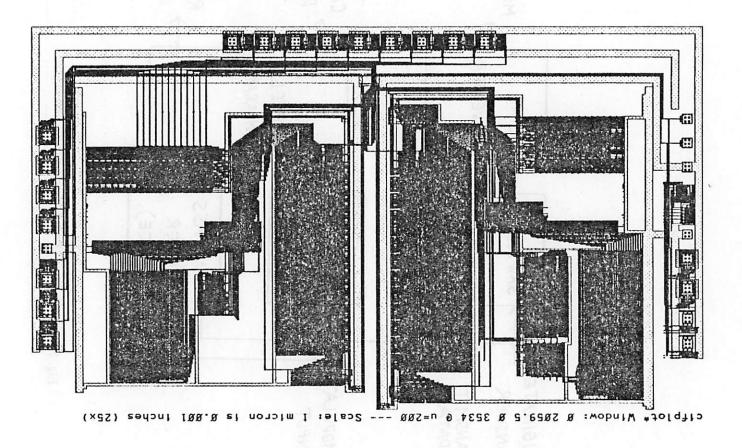

Fig.2.19 shows a die photograph of the IC, with major functional blocks labeled. The three processors, the control sequencer, and parameter storage buffers consume most of the area.

The individual processor data paths consist of a bit-slice arithmetic unit attached to a data memory. The pitch of the data memory is narrower than that of the arithmetic unit: thus in Fig.2.19 the processor data paths are L-shaped. Groups of wires connecting the data memories to their arithmetic units are visible

(a) speech input

Fig.2.18 Analysis-synthesis sequence

(c) excitation

(d) synthetic speech output

Fig. 2.19 Die photograph of vocoder IC

in the photograph. Besides these, most wires in the vocoder circuit connect control sequencer outputs to the various processing elements.

The control sequencer contains two read-only memories (ROM's) and two program counters. Timing and control signals for all circuits are generated here. The two ROM's contain a total of 6 kbit of microcode.

In addition to the major blocks which are labeled in Fig.2.19. the following smaller circuits are identified by number:

- (1) excitation source for synthesizer

- (2) address indexing unit for Processor No. 1

- (3) FIFO buffer for reflection coefficients

- (4) look-up table for squaring operator

- (5) address indexing unit for Processor No. 3

- (6) FSM for Processor No. 3

The circuit is fabricated in a 4u NMOS process, containing 23.000 transistors on a 0.265° x 0.225° die. The circuit requires a two-phase, 2.88 MHz clock and dissipates 600 mW.

## 2.8 Conclusions

The design of any integrated circuit involves decisions on a number of issues.

The LPC vocoder IC presented an interesting design problem due to the high

computation rate, the real-time constraint, and the fact that the algorithm as well as the architecture could be adapted to suit the technology. Held in balance by this design were performance, area efficiency and magnitude of design effort.

Quite a bit of efficiency was gained by recognizing that adaptive algorithms for spectral and pitch analysis were well suited to a fully integrated approach. These algorithms avoid the large amount of storage required by "block" algorithms, which typically require buffering a large number of input samples. Also, the fact that most of the algorithms used consisted of repetitions of identical stages (i.e., lattice filter stages or pitch detector channels) reduces the complexity of the control sequencer.

The most important aspect of a design such as this is the data path architecture. The single-accumulator architecture used in the three arithmetic units resulted in a compact and effective circuit. By operating three of these arithmetic units in parallel high computational throughput is obtained. It should be noted that a parallel array multiplier circuit would occupy more circuit area than all three arithmetic units combined. This suggests that array multipliers, which are often found in signal processing IC's, are not always the best architectural choice.

# Chapter 3 - The Macrocell Approach to Digital Signal Processor Design

#### 3.1 Introduction

Custom circuit design and production has never accounted for more than a small fraction of the IC industry. The vast majority of the digital integrated circuits designed and manufactured are high-volume parts such as memories, microprocessors, and standard logic families. Industrial production facilities are geared towards the manufacture of these high-volume components. Market conditions tend to favor the production of high volume components, with little incentive for the design and manufacture of more specialized circuits.

Still there are reasons to believe that dedicated signal processing I.C.'s will eventually play a more important role. One is the huge potential market represented by the telecommunications industry. Another is the slow but steady progress being made in the field of computer-aided design (CAD) of integrated circuits.

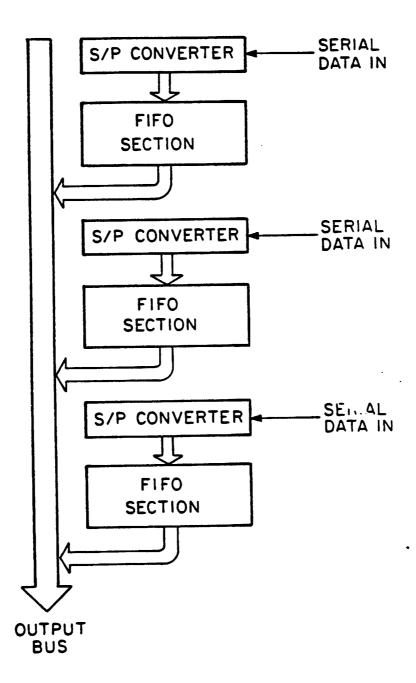

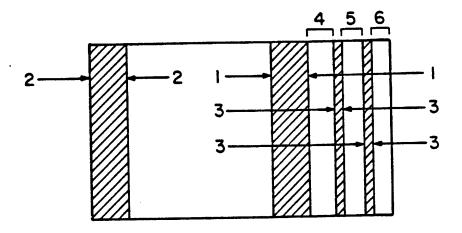

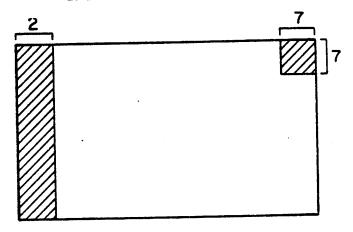

Several competing approaches exist for custom and semi-custom integrated circuit design. Gate arrays and standard-cell designs allow a short design cycle, but a premium is paid in terms of efficiency. The approach taken here is the use of large, parameterized blocks of circuitry called macrocells. These macrocells differ from standard-cells in that they are large (ranging from several hundred to several thousand transistors). Also, standard-cell designs consist of regular rows of cells separated by wiring channels. Macrocells are assembled from a cell library by forming a two-dimensional array of cells. This leads to macrocells which are themselves very dense. A major consideration in macrocell-based designs is the proper placement and interconnection of these large blocks.

Of primary importance is the ability to configure the macrocells for a

Fig. 3.1 Macrocell design system software

particular application, resulting in a more efficient design. A number of parameters and options may be specified for the macrocells described here. These include data path widths: programming and sizing of control memory, data memory and programmed logic arrays (PLA's); and configuration of the interprocessor communication network. Thus a macrocell is not a fixed block of circuitry, but a class of circuit blocks configured according to explicit rules from the underlying cell library.

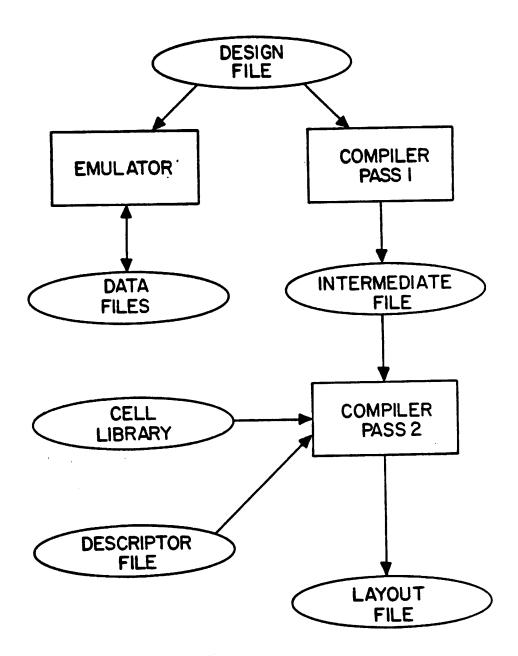

Design systems based on standard cells or gate arrays involve considerable supporting software for simulation and layout generation. A similar approach is taken here. The software system consists of an *emulator* and a two-pass *silicon* compiler. The emulator and compiler accept as input a design file, which is a text file prepared by the designer. This software system is diagrammed in Fig.3.1.

The design file has a very readable format. Each IC contains several processors operating concurrently. The designer specifies hardware parameters and symbolic microinstructions for each processor. Local constants and variables are declared. Interprocessor and off-chip communications are specified by declaring global variables which are external to the individual processors.

The emulator allows verification of circuit performance prior to fabrication. A full set of debugging commands is available, such as tracing, breakpoints, single-step, and setting or displaying variables. A non-interactive mode allows long simulation runs to be performed.

The first pass of the compiler extracts hardware parameters from the design file. Symbolic microcode is assembled into binary. The resulting hardware description is input to the second pass, which accesses the cell library and assembles the macrocells. Placement and interconnect routines follow. The system is intended to generate automatically a mask-level description of the I.C.

The term silicon compiler has been generously applied to specialized IC design

systems which generate circuit layouts automatically [21]. In fact, any layout-generating software which does not fit into some other category (graphics editor. router, etc.) is likely to be called a silicon compiler. The system described here satisfies this definition.

A major goal in the design of the software package was process independence. Integrated circuit fabrication processes evolve rapidly. Also, it is dificult for a designer who does not control a captive fabrication facility to ensure continued availability of a given process. For these reasons, a macrocell design system should function for any fabrication process that might become available. This goal was achieved by introducing a small number of parameters which characterize the process for the purposes of the software package. The software may then be used with any process by redesigning the cell library in the new process.

By limiting the focus of the design system to a family of signal processing functions, efficient and specialized architectures may be employed. The range of applications includes: speech processing (vocoders, sub-band and waveform coders, speech recognition), telecommunications (modems, line equalizers, echo cancellers), and digital audio (mixing, equalization, reverberation and other effects). It is estimated that several dozen commercially valuable dedicated IC's will be designed with this system.

The remainder of this chapter discusses the architecture and hardware organization used in the macrocell system. Chapter 4 describes the design file and the software system. In Chapter 5, example designs using the macrocell system are presented. Details of the cell library and design file format are presented in Appendices B and C respectively. Design file examples are given in Appendix D.

## 3.2 Processor Architecture

The LPC Vocoder circuit described in chapter 2 is essentially the prototype architecture for the macrocell based designs considered here. This architecture is characterized by the following:

- (1) Multiple processors on a single IC.

- (2) A bit-parallel, single accumulator processor architecture.

- (3) Microprogramming of dedicated signal processing functions.

- (4) Use of a finite state machine for decision-making.

- (5) Bit-serial communications among the processors.

Study of algorithms within the target range indicated that the same general architecture, with suitable parameterization, can perform the algorithms efficiently.

For convenience, discussion of the architecture is divided into several sections. This section is an overview of the individual processor architecture. Sections 3.3 through 3.6 describe components of the processor in greater detail. Section 3.7 describes the multiprocessor and 1/O aspects.

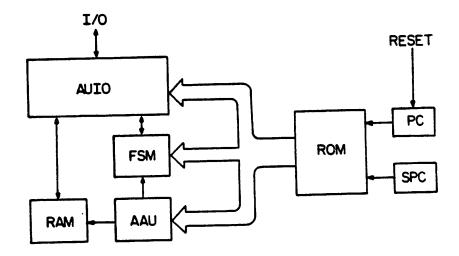

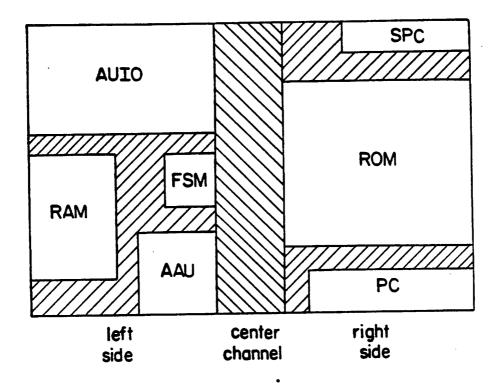

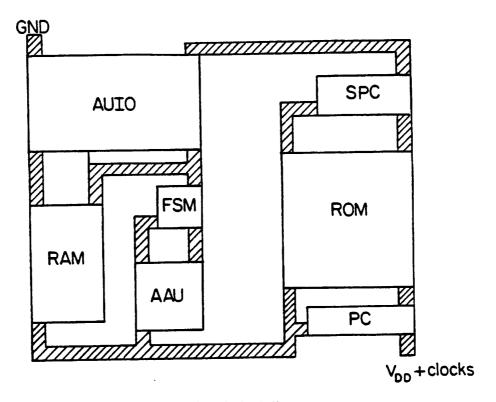

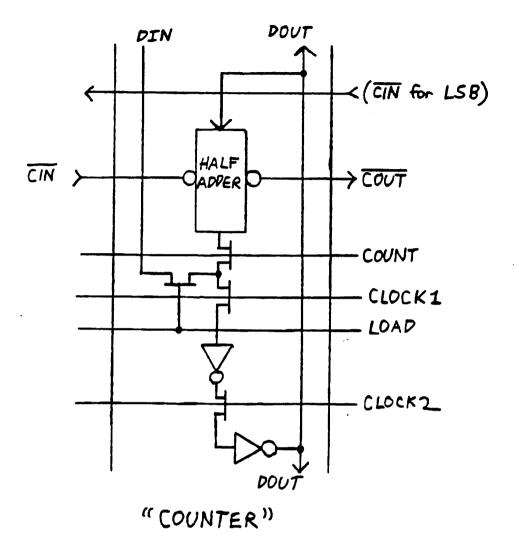

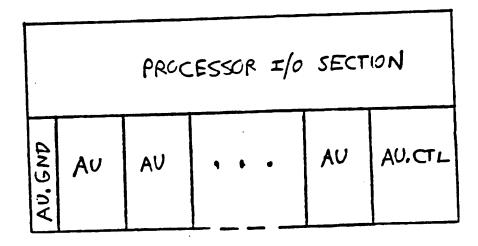

Each processor is organized into the following macrocells:

PC (program counter)

ROM (microcode read-only memory)

SPC (subprogram counter — optional)

AAU (address arithmetic unit — optional)

FSM (finite state machine — optional)

AUIO (arithmetic unit with I/O circuits)

RAM (processor data memory)

A fully configured processor is diagrammed in Fig.3.2.

Fig. 3.2 Macrocells forming a fully configured processor

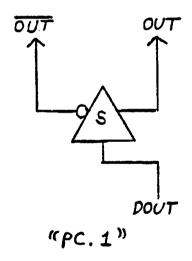

The processor executes its microprogram (stored in ROM) once per sample interval. The microprogram consist of a "main program" optionally followed by a fixed number of "subprogram" iterations. The SPC macrocell is included only if the subprogram is used. Except for this iteration pattern, there are no branches (conditional or unconditional) in the program execution. The PC, ROM and optional SPC macrocells are collectively known as the control sequencer and are described in Section 3.3.

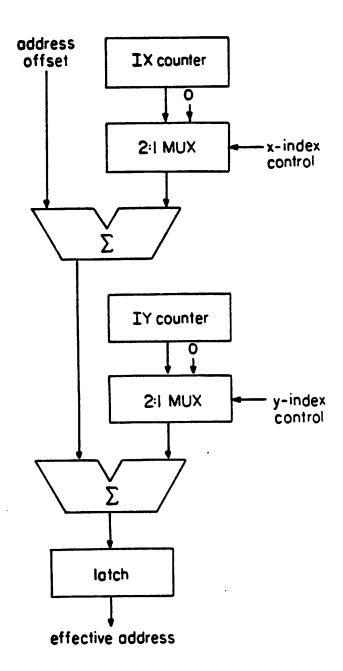

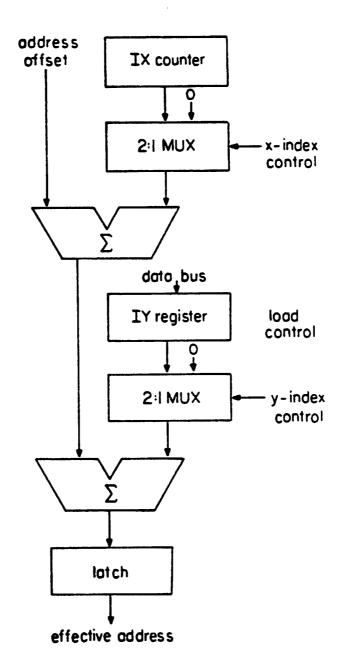

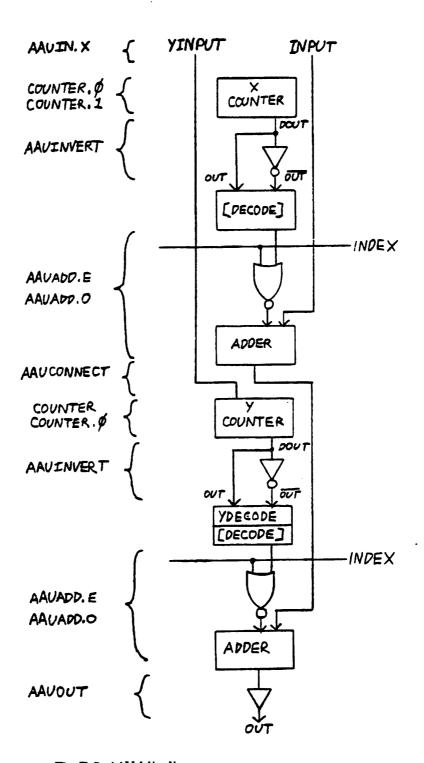

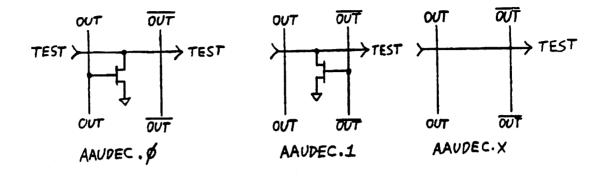

The output of the control sequencer is a sequence of control words. The control word can be subdivided into a number of fields. One of these is the address offset field. It is this field that is used as input to the AAU macrocell. The AAU modifies the address offset to produce the effective address for the processor data memory (RAM macrocell). In some simple cases, no modification is required and the AAU macrocell is not included. In these cases the address offset field of the control word serves directly as the effective address. The AAU macrocell is described in Section 3.4.

Viewed together, the ROM, PC, SPC and AAU present a stream of horizontal control and address words to the AUIO, RAM, and (optional) FSM macrocells.

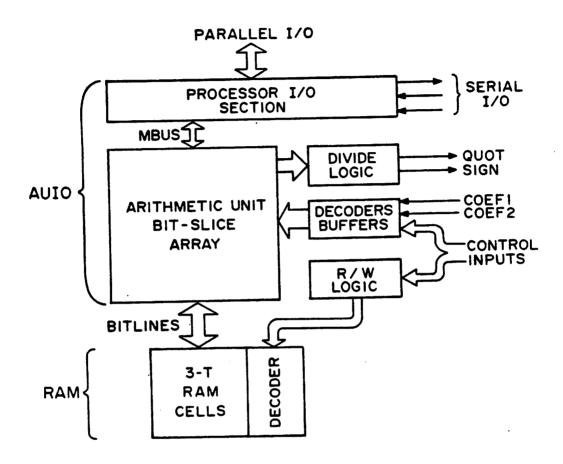

The AUIO macrocell consists of an arithmetic unit and an I/O interface. The arithmetic unit together with the RAM (data memory) macrocell form the signal data path. This is where all operations on signals are performed. This data path may be microcoded to perform fixed coefficient multiplies, variable coefficient multiplies, add, subtract and accumulate operations, division, and comparisons. In addition, the data memory allows delay operations, introduction of constants and table-lookup. The arithmetic unit and data memory are described in Section 3.5.

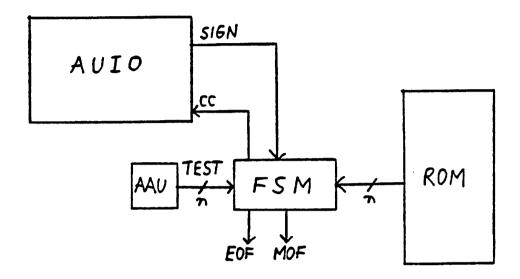

The final component of the processor assembly is the optional finite-state machine (FSM). This is where logical operations, conditional operations and decision-making are performed. The FSM accepts Boolean inputs from two

sources: a comparison in the arithmetic unit; and tests on index registers internal to the AAU. The FSM operates on these inputs and its own internal state. FSM operations are controlled by a field of the control word. Outputs from the FSM are used for two purposes: to control write cycles in the RAM macrocell: and to initiate I/O to an off-chip host (see Section 3.7). The FSM is described in Section 3.6.

The processor assembly executes its microprogram once per sample interval. Since primitive operations such as multiplies must be microcoded, it follows that the sample rate must be substantially slower than the processor's clock rate. Otherwise, there would not be time for a significant amount of processing during the sample interval. On the other hand, if the ratio of clock rate to sample rate becomes very large, the architecture exhibits an imbalance wherein the control ROM consumes nearly all of the silicon area, and the data path only a small fraction. This situation is aggravated since the horizontal control words are not densely encoded. Based on the relatively sizes of the library cells, the processor architecture is most efficient if the ratio of clock rate to sample rate is between 50 and 1000. This corresponds to a sample rate range of 5 kHz to 100 kHz, since the cell library is designed to operate at a maximum 5 MHz clock rate.

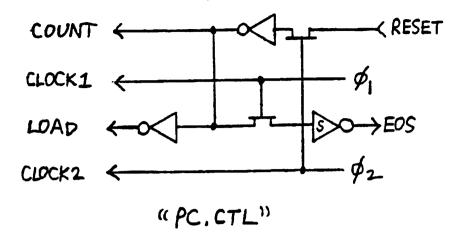

### 3.3 Control Sequencer

An important aspect of the macrocell design system is the fact that the individual processors are microprogrammed to perform dedicated tasks. In fact, most of the design file input to the software system consists of microcode. The control sequencers are programmed with this microcode, and therefore control all timing and data-path operations for their processors. In addition, timing strobes generated by the control sequencers can exit the processor assembly to be used for control of interprocessor or off-chip communications.

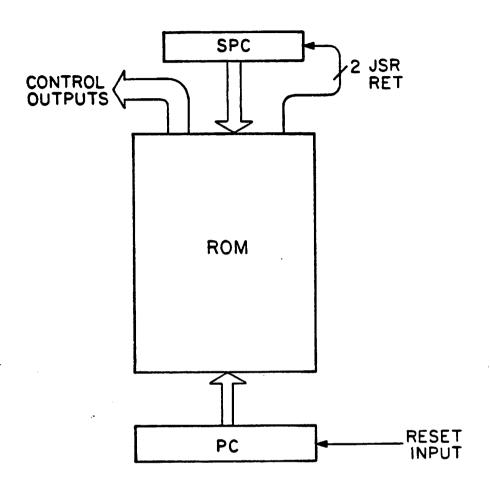

Fig.3.3 Control sequencer

The control sequencer consists of the ROM macrocell, the PC (program counter) macrocell, and the SPC (subprogram counter) macrocell. The subprogram is optional; if there is no subprogram, the SPC is not included. The outputs of the ROM are known as the control word. The control word is very horizontal: it contains many non-overlapping fields, each of which has an independent function. Rarely are two different functions assigned to the same bit of the control word.

The AUIO macrocell has many control inputs, accounting for perhaps half of the control word. Therefore, provisions are made for defaulting unused signals in this field to ground or Vdd, reducing the typical ROM width.

A few control signals are used to clear and increment the two program counters, PC and SPC. It is required that the various processors on a chip be synchronized, i.e., each processor begins its microprogram on the same clock cycle at the beginning of each sample interval. In order to allow this, one processor is designated as the master processor for timing purposes. Contained in the control word for the master processor is a signal named RESET. This signal is asserted at the end of each sample interval, and serves to reset the PC (program counter) macrocells for all processors on the chip. There are no inputs to the control sequencer aside from this reset input.

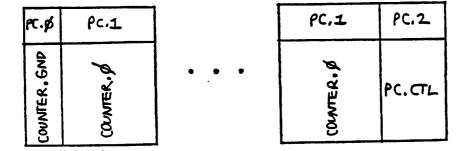

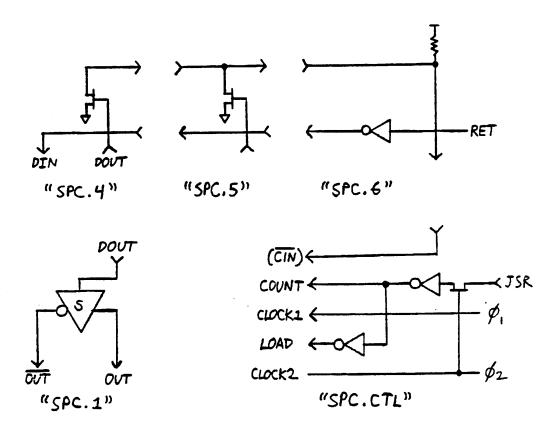

There are two possible configurations for the control sequencer: with or without a SPC. The following discussion applies to the case where there is a SPC. The hardware is diagrammed in Fig.3.3.

The SPC macrocell requires two timing signals JSR and RET as control inputs. The JSR signal is asserted at the end of the main program, and at the end of each subprogram iteration. The RET signal is asserted concurrently with the final JSR at the end of the final subprogram iteration. When JSR and RET occur simultaneously, the SPC is cleared and remains cleared until the next JSR. When JSR is

asserted but RET is inactive. SPC is loaded with a one and commences counting. Thus, SPC equals zero during the main program and counts from one to an upper limit during each subprogram iteration.

Note that the end of the final iteration of the subprogram need not be coincident with the end of the sample interval. The reason for this is that the total execution times for different processor's microprograms will in general be unequal. Therefore, there may be an idle interval following the end of the microprogram lasting until the end of the sample.

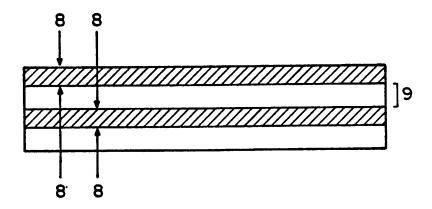

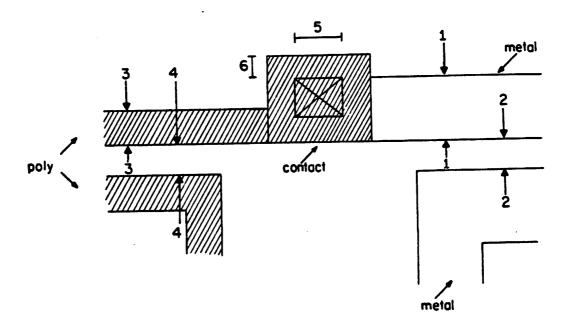

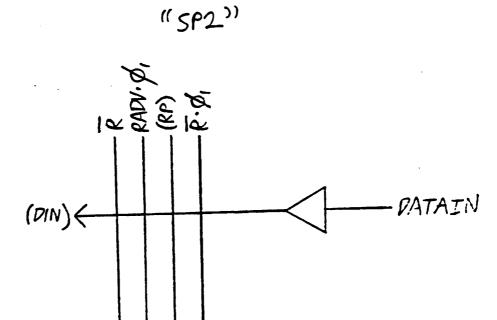

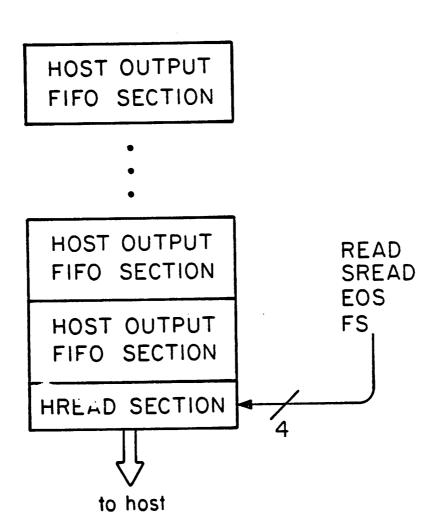

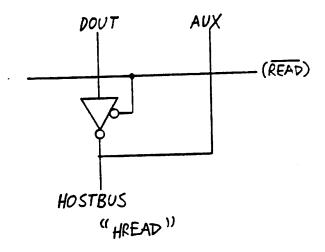

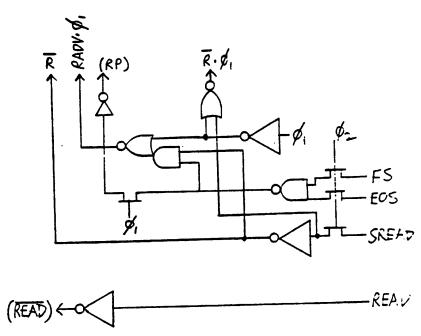

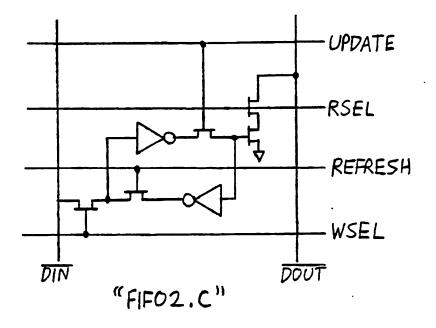

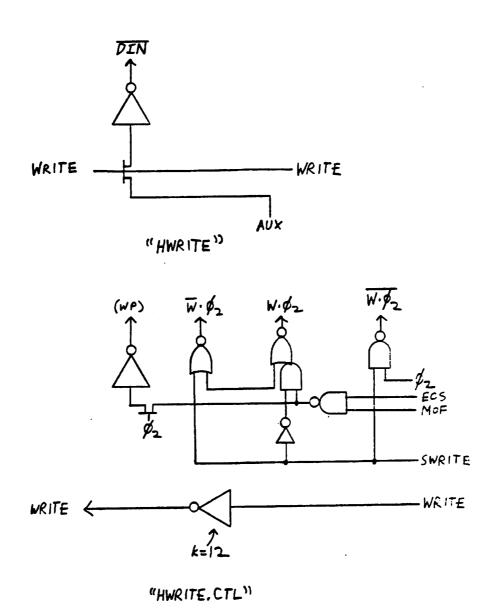

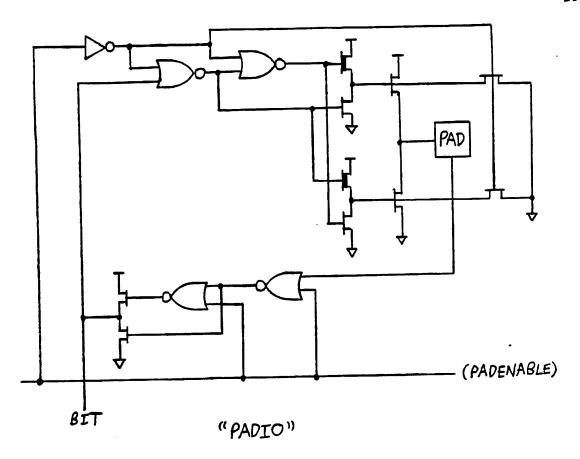

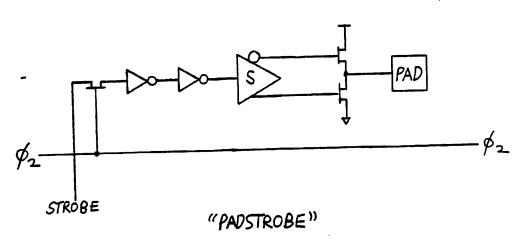

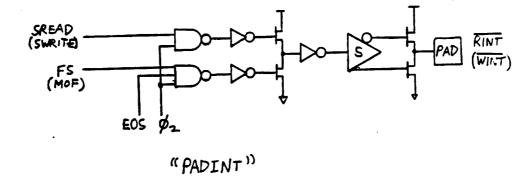

Also note that the subroutine iterations are not explicitly counted. The subroutine iterates the desired number of times only because the RET signal is asserted on the proper cycle.