## Compiling Communication-Minimizing Query Plans

Eric Love

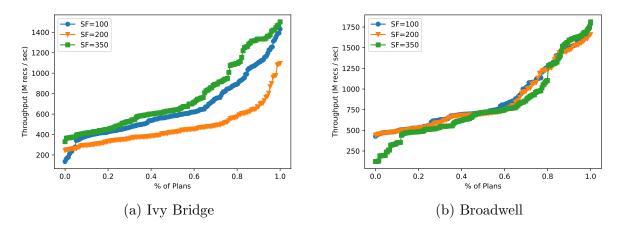

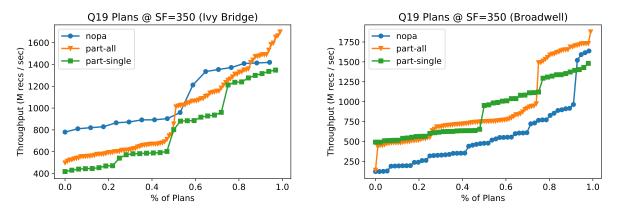

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2019-181 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2019/EECS-2019-181.html

December 20, 2019

Copyright © 2019, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

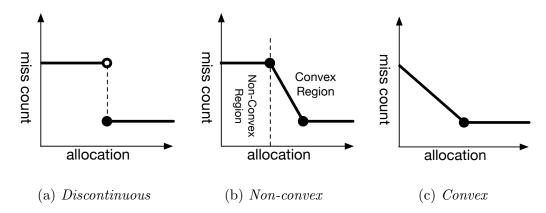

## Acknowledgement

The information, data, or work presented herein was funded in part by the Advanced Research Projects Agency-Energy (ARPA-E), U.S. Department of Energy, under Award Number DE-AR0000849. Research was partially funded by ADEPT Lab industrial sponsors and affiliates Intel, Apple, Futurewei, Google, and Seagate. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof. Compiling Communication-Minimizing Query Plans

by

Eric J Love

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Krste Asanović, Chair Assistant Professor Jonathan Ragan-Kelley Assistant Professor Zachary Pardos

Fall 2019

The dissertation of Eric J Love, titled Compiling Communication-Minimizing Query Plans, is approved:

| Chair | <br>Date |  |

|-------|----------|--|

|       | <br>Date |  |

|       | <br>Date |  |

University of California, Berkeley

Compiling Communication-Minimizing Query Plans

Copyright 2019 by Eric J Love

#### Abstract

#### Compiling Communication-Minimizing Query Plans

by

#### Eric J Love

#### Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Krste Asanović, Chair

Because of the low arithmetic intensity of relational database operators, the performance of in-memory column stores ought to be bound by main-memory bandwidth, and in practice, highly-optimized operator implementations already achieve close to their peak theoretical performance. By itself, this would imply that hardware acceleration for analytics would be of limited utility, but I show that the emergence of full-query compilation presents new opportunities to reduce memory traffic and trade computation for communication, meaning that database-oriented processors may yet be worth designing.

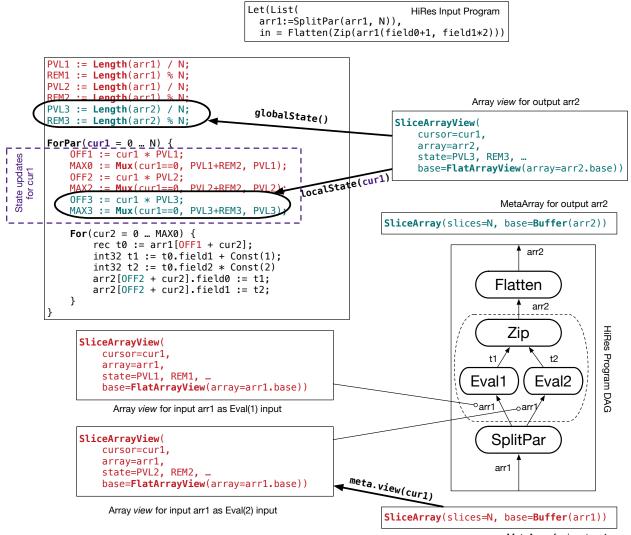

Moreover, the communication costs of queries on a given processor and memory hierarchy are determined by factors below the level of abstraction expressed in traditional query plans, such as how operators are (or are not) fused together, how execution is parallelized and cache-blocked, and how intermediate results are arranged in memory. I present a Scala-embedded programming language called Ressort that exposes these machine-level aspects of query compilation, and which emits parallel C++/OpenMP code as its target to express a greater range of algorithmic variants for each query than would be easy to study by hand.

# Contents

### Contents

| <ul> <li>1 Introduction &amp; Background <ol> <li>History &amp; Related Work</li> <li>Databases &amp; Database Machines of Tomorrow</li> <li>Methodology</li> <li>Methodology</li> <li>Methodology</li> </ol> </li> <li>2 Machine-Level Query Optimization <ol> <li>Introduction</li> <li>Machine-Level Planing</li> <li>Dimensions of Machine-Level Planing</li> <li>A Case Study: TPC-H Query 19</li> </ol> </li> </ul> | 1         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <ul> <li>1.2 Databases &amp; Database Machines of Tomorrow</li></ul>                                                                                                                                                                                                                                                                                                                                                      |           |

| <ul> <li>1.3 Methodology</li></ul>                                                                                                                                                                                                                                                                                                                                                                                        |           |

| 1.4 Contributions of this Thesis                                                                                                                                                                                                                                                                                                                                                                                          | 6         |

| <ul> <li>2 Machine-Level Query Optimization</li> <li>2.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                           | 10        |

| <ul> <li>2.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                       | 11        |

| <ul> <li>2.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                       | 12        |

| <ul><li>2.2 Dimensions of Machine-Level Planing</li></ul>                                                                                                                                                                                                                                                                                                                                                                 | 12        |

| 2.3 Plan Derivation by Transformation                                                                                                                                                                                                                                                                                                                                                                                     |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

| 3 HiRes: A Language for MLP                                                                                                                                                                                                                                                                                                                                                                                               | 33        |

| 3.1 HiRes Operators & Syntax                                                                                                                                                                                                                                                                                                                                                                                              |           |

| 3.2 HiRes Type System                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                         |           |

| 3.4 HiRes Case Studies                                                                                                                                                                                                                                                                                                                                                                                                    | 59        |

| 4 Operator Fusion: Constraints & Algorithms                                                                                                                                                                                                                                                                                                                                                                               | <b>62</b> |

| 4.1 Introduction $\ldots$                                                                                                                                                                                                                                                                                                                |           |

| 4.2 The Shared Clique Formation Algorithm                                                                                                                                                                                                                                                                                                                                                                                 | 63        |

| 4.3 Inner and Outer Loop Fusion Particulars                                                                                                                                                                                                                                                                                                                                                                               | 75        |

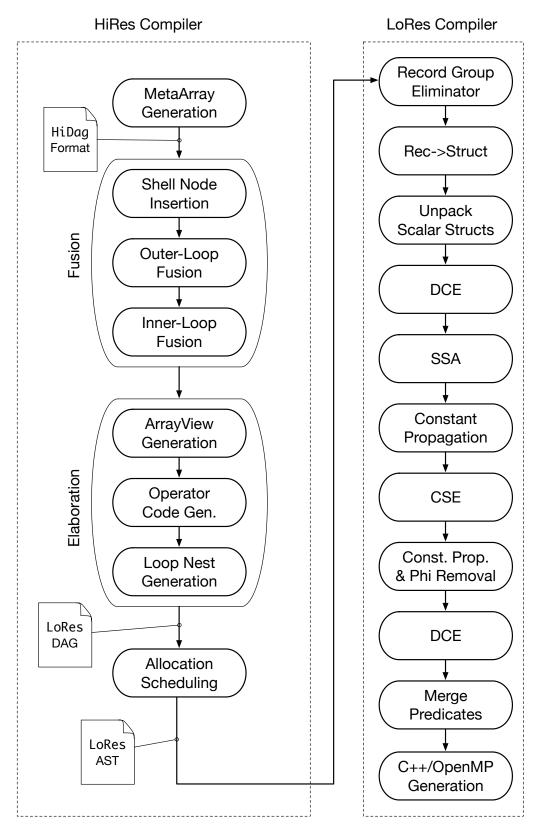

| 5 Ressort Compiler Architecture & Implementation                                                                                                                                                                                                                                                                                                                                                                          | 81        |

| 5.1 HiRes Compilation Pipeline                                                                                                                                                                                                                                                                                                                                                                                            | 82        |

| 5.2 LoRes Compilation Pipeline                                                                                                                                                                                                                                                                                                                                                                                            | 91        |

| 6 Evaluation                                                                                                                                                                                                                                                                                                                                                                                                              | 103       |

| 6.1 Experimental Platform                                                                                                                                                                                                                                                                                                                                                                                                 | 103       |

| 6.2 "TPC-H"-Like Queries                                                                                                                                                                                                                                                                                                                                                                                                  |           |

i

ii

| 7 | Con | nmunication-Aware Query Cost Models             | 109 |

|---|-----|-------------------------------------------------|-----|

|   | 7.1 | Original Model of Manegold, Boncz, and Pirk     | 109 |

|   | 7.2 | Extensions for Communication Bounds             | 112 |

|   | 7.3 | A Manegold-Based Roofline Model                 | 121 |

|   | 7.4 | Summary & Limitations                           | 122 |

|   | 7.5 | Case Study: TPC-H Query 19                      | 123 |

|   |     | Proof of NP-Hardness of Single-Phase Allocation |     |

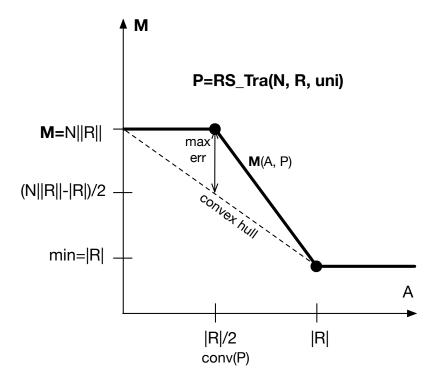

|   | 7.7 | 2x Error Bound on Convex Hull Allocation        | 128 |

| 8 | Con | clusions & Future Work                          | 130 |

|   | 8.1 | Summary                                         | 130 |

|   | 8.2 | Principal Findings & Recommendations            | 131 |

|   | 8.3 | Limitations & Future Work                       | 131 |

|   | 8.4 | A Methodological Plea                           | 132 |

#### Acknowledgments

The greatest reward by far of graduate school has been getting to know the friends and colleagues I met along the way, and this thesis would not have been possible without their support, encouragement, patience, and advice. I will remain forever grateful to more individuals than could be named here, but I would like to give special thanks to a few:

- I want to express my gratitude to my advisor, Krste Asanović, who generously supported my forays into research outside the more traditional realms of computer architecture and hardware design, as well as my other committee members Jonathan Ragan-Kelley and Zachary Pardos, who were kind enough to review this dissertation.

- While a post-doc at UC Berkeley, Lisa Wu Wills was a mentor to me and advocate of this work. I am happy to see her advise many other graduate students now as faculty at Duke University.

- I am lucky to have met an exceptional generation of senior students when I arrived in Berkeley. Scott Beamer and Chris Celio were two of the first people to welcome me, and our friendship has only grown through three successive labs, numerous RTL refactoring sessions, and more than a healthy number of session ales. Practically everything I know about micro-architecture I learned from discussions with my former and future colleague Andrew Waterman-more likely than not in our local watering hole, Beta Lounge, whose own contribution to this thesis is incalculable.

- Upon entering the PhD program together, Martin Maas and I shared a desk, a research project (PHANTOM), and many fond memories. My subsequent desk-mate, Orianna DeMasi, is an inspirational human and inexhaustible source of encouragement. I am grateful for my continued friendship with her and our friends Albert Magyar and Nathan Pemberton, without whom this thesis would not have been possible.

- The UCB-BAR research group has been an overwhelmingly fun workplace, and I am fortunate to have had such outstanding colleagues there, among them Adam Izraelevitz, Albert Ou, Alon Amid, Colin Schmidt, David Biancolin, David Bruns-Smith, Henry Cook, Howie Mao, Jack Koenig, Palmer Dabbelt, Sagar Karandikar, Sarah Bird, and Yunsup Lee. While it is sad to say goodbye, am excited to continue working alongside some of them at SiFive.

- Of course, some of the most important people in our lives may sit, not next to us, but thousands of miles away, and I do not know how I would navigate life without the daily virtual presence of Rose Nissen, my best friend since high school and an indefatigable force. And though the end of college has put a whole continent between us, Dylan Morris and Kavita Mistry have been consistent companions throughout the tribulations of grad school.

- I would not be here without a lifetime of encouragement from my parents, Jack and Susan, to whom I owe everything, and who, in reading this, will be elated to see that I have finished. Neither would I have completed a computer science PhD without the mentorship of Yiorgos Makris, who encouraged me as an undergraduate to pursue research and gave me my first opportunities.

- Lastly, I would like to thank the sponsors of the ADEPT Lab, whose generous funding made this work possible. The information, data, or work presented herein was funded in part by the Advanced Research Projects Agency-Energy (ARPA-E), U.S. Department of Energy, under Award Number DE-AR0000849. Research was partially funded by ADEPT Lab industrial sponsors and affiliates Intel, Apple, Futurewei, Google, and Seagate. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

## Chapter 1

## Introduction & Background

This thesis takes a step towards demarcating the performance limits to the performance of database analytics queries on the hardware of today and of the next decade. Such workloads, whether known as *decision support* queries, *data warehouse* queries, or *online analytics processing (OLAP)*, do largely what is summarized by the SQL in Figure 1.1, the 6th query from the TPC-H [70] benchmark suite (Q06). They scan large arrays of data, compute various quantities derived from them, filter them based on those results, and tabulate some final answer. Other queries may be more complicated, and incorporate relational joins, but this basic pattern constitutes the bulk of the "work" done in analytics processing.

```

select

sum(l_extendedprice * l_discount) as revenue

from

lineitem

where

l_shipdate >= date '1994-01-01'

and l_shipdate < date '1995-01-01'

and l_discount between 0.06 - 0.01 and 0.06 + 0.01

and l_quantity < 24</pre>

```

Listing 1.1: TPC-H Query 06 in SQL Form

While they may seem computationally simple, significant complexity lurks wherever their peak performance is sought. And the throughput of queries similar to Q06 has been important enough to motivate the design of custom hardware for their acceleration since at least a century and a half ago. The principal concern of this thesis is how to approach the design of database hardware for the next decade. However, we do not advance any particular architecture or accelerator blueprint, and instead argue that the first step towards any such effort should be to consider the widest possible space of semantically equivalent algorithms (query plans) that might be employed to implement the range of queries likely to be processed by the new hypothetical machine, and only then to propose hardware with the "best" of these algorithmic mappings in mind, rather than optimizing (micro-)architectures for whatever implementation strategy happened to have superior performance on platforms that exist right now. The notion of optimality in this case turns out to be minimal data movement, as Setion 1.2 later argues.

Consequently, we propose a language and compile framework that widens the space of hardware-conscious plan choices that query processors can consider, and attempt to predict how much future hardware could improve its results.

## 1.1 History & Related Work

Before contemplating the contemporary obstacles to OLAP optimization, though, it is instructive to review some characteristic examples from the last hundred years of attempts to execute analytics queries at ever-greater speeds. At each stage, what changes is the physical constraints of the underlying hardware.

### A Century and a Half of Hardware-Driven Analytics

#### In the 19th Century

Already in 1888, Herman Hollerith's tabulation machine [69] was enlisted to analyze the results of the upcoming American census of 1890. Though it lacked any Turing-complete processor, it accelerated aggregation "queries" by advancing mechanical dials one step at a time in response to electrical signals formed where metal springs passed through holes punched in a paper card to indicate the presence or absence of demographic characteristics. It also facilitated group-by aggregations using a "sorting drawer" into particular slots of which operators were instructed to insert cards based on some combination of their attributes. Moreover, this specific machine was selected for use in the Census because it excelled in an already-standardized query benchmark contest, comprising the tabulation of prior census results for some districts of St. Louis, M.O. Thus, even without the benefit of general-purpose computers, a purely application-specific accelerator approach to query processing prefigured today's landscape of database hardware proposals in both its approach and its metrics.

#### In the 20th Century

Nearly one century after Hollerith's pioneering efforts, hardware support for analytics processing was deemed of sufficient importance to merit a special issue of the IEEE Transactions on Computers [30] in 1979. In an era of mainframes, tape drives, and relatively expensive magnetic disks, "the database machine (DBM) [was] the result of an atchitectural approach which [...] distributes processing power closer to the devices on which data are stored." Four decades ago, then, the idea emerged of processing near data as a way to eliminate the CPU as a central bottleneck to the processing of data at the aggregate bandwidths supplied by storage devices; today, proposals for intelligent SSD controllers echo this idea.

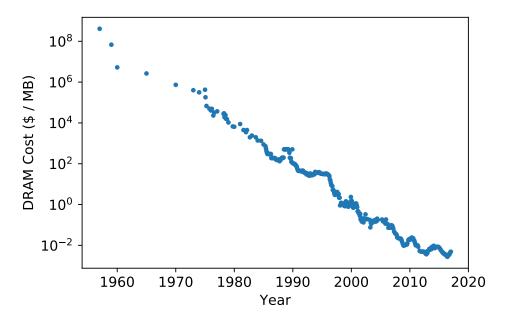

Figure 1.1: The Cost of DRAM Over Time (Data from McCallum [21])

A decade later, the Gamma Database Machine project by DeWitt et al. at the University of Wisconsin witnessed the dawn of the main memory era, in which multiple megabytes of DRAM were inexpensive enough to provision for a single compute node, as Figure 1.1 shows. In their proposal, dozens of Intel processors interconnected with a custom network could perfom parallel joins by partitioning hash tables into chunks small enough to fit (sometimes) in the 8MB of DRAM attached to each processr. Their software also compiled some selection predicates to executable code, foreshadowing the age of query compilation in which SQL interpretation overhead was an obstacle.

#### In the 21st Century

By the turn of this century, the cost of DRAM had dropped to mere dollars per megabyte, making gigabytes available per processor, and fitting entire tables into main memory. The resulting reduction in disk seeks and increase in scan bandwidth quickly made CPU power a key performance barrier in a growing number of analytics workloads. This led to the emergence of *column stores*, which packed all rows of a single attribute together in continuous extents of memory. This enabled the application of a relational operator to whole *columns* of records at a time, whereas under previous execution models, records would have been processed individually, and any control or interpretive overhead for each operator was incurred repeatedly. For example, in the so-called "Volcano" model (after the project of the same name by Graefe [16]), each operator instantiated in a query plan is an object supplying a **next()** method that downstream operators can call to obtain one tuple at a time, and

which itself would call its own inputs' **next()** methods, incurring whatever function call overhead this entailed many times per record. By contrast, C-Store [66] (later Vertica [28]) and MonetDB [7] (later Vectorwise [76]) were early prominent examples of column stores that upended this paradigm.

The transition from record-at-a-time to operator-at-a-time query processing also facilitated the exploitation of instruction- and data-level parallelism inside the processor, becuase each operator now consisted of a single tight loop over records that could be unrolled either dynamically by superscalar pipelines or statically by compilers, and in some cases this even meant that vectorized instructions could then be emitted. This, in turn, led to a proliferation of papers explaining how best to hand-optimize common relational operators for emerging multi-core [26, 5, 3] and multi-socket [29, 59] systems, as well as SIMD instruction set extensions [57, 71, 51, 48].

Even column-at-a-time execution suffers from the requirement that each operator's result be written out fully to memory, before being read back again by the next operator that consumes it. One way around this problem, implemented by Vectorwise, was to switch from column-at-a-time processing to *block-at-a-time* processing, where each block would be small enough to fit in cache. In this way, dependent operators would pass data to each other through cache, at least, rather than memory, while still amortizing control overhead across each block.

Eventually this too proved inadequate, as the highest-performance database architectures sought to bypass the memory system entirely and pass data between operators through registers. This required query *compilation*, and several projects emerged to turn SQL into executables, most notably HyPer [25] by Kemper and Neumann, which used the LLVM [31] compiler backend to generate machine code. HyPer was eventually commercialized as Tableau [67] and since then several other academic query compilers have appeared, focusing either on how to structure such compilers [60, 68], or how to tune code-generation parameters [9].

At the same time, need arose for standard benchmarks for analytics. The Transaction Processing Council, which had for nearly a decade supplied the industry standard benchmark for transaction processing performance, devised the "H" suite of about two dozen non-transactional queries [70]–such as that shown in Listing 1.1. This has animated much of the research into both hardware- and software-based analytics support ever since, and this dissertation makes use of it as well, though without following all of its requirements (see Section 1.3 below).

#### **Database Machines Today**

More recently, growing demand for OLAP performance and even lower costs per byte of DRAM have inspired processor manufacturers to design analytics-tailored hardware. Intel collaborated with SAP to offer database-oriented servers capable of addressing up to 12TB of memory from eight sockets [20], while Oracle's SPARC M7 [43] supports 16TB, and includes instruction set extensions designed specifically to support analytics by accelerating scans, filtering, joins, and compression.

Aside from the instruction-level acceleration offered by Oracle, these offerings mostly resemble traditional, general-purpose server platforms with board-level support for larger memory capacities (i.e. custom buffer chips to access more DIMMs and more threads per socket). However, as Moore's Law [41] appears to reach its end, and the number of transistors that can be packed on a single chip at optimal cost no longer doubles every eighteen months, more application-specific kinds of acceleration will have to replace raw core counts as the main driver of higher query throughput.

Accordingly, academics have investigated alternative architectures and micro-archtectures. The most general-purpose of these add, like the SPARC M7, assistance for various aspects of query processing. Hayes et al. proposed extensions to vector instruction sets to ease the cache pressure that results from vectorizing radix partitioning and joins [17, 18]. In "Meet the Walkers" [27], Kocberber et al. offloaded the serial indirect loads (pointer chasing) of hash-table builds and probes to dedicated functional units that live outside of the processor's pipeline, allowing many more memory operations in flight than an out-of-order core could sustain. At the more application-specific end, Kara et al. proposed an FPGA-based partitioning accelerator [23], while Wu et al. presented a dataflow architecture for accelerating entire queries on FPGAs with networks of operator-specific accelerators [74]. Finally, Oracle's Database Processing Unit (DPU) was published at MICRO'17 [1], and combined ensembles of 160 small, in-order cores per chip with a 76GB/s memory interface to perform hash partitioning and other relational operations at line rate.

The efficacy of these proposals has been judged both by way of the TPC-H benchmark suite, and by others that emerged to address some of its limitations. Leis et al. proposed a Join Order Benchmark (JOB) [33] to increase the number of joins in sample queries up to eight or more, unlike the two or three typical of TPC-H, and further proposed the use of real-world datasets from IMDB instead of the synthetic relations with uniform random values specified by TPC-H, as these would be more reflective of the queries today's users seek to run in practice. In order to facilitate research into database hardware, Shao et al. proposed DBmbench [61], a suite of microbenchmarks that better represent analytics query execution with small datasets than would TPC-H scaled to an equivalent size, which would result in e.g. smaller hash tables and therefore different micro-architectural characteristics. The work that follows neither makes use of the Join Order Benchmark nor DBmbench, but does contemplate new standards for evaluating query performance in the future.

## **1.2** Databases & Database Machines of Tomorrow

In light of the foregoing decades' worth of query acceleration research, it is reasonable to ask what a database machine of the next decade might look like, and how one might go about designing it. The downward trend of Figure 1.1 suggests that the cost of DRAM will only continue to shrink. Meanwhile, the improving performance of emerging non-volatile memory (NVM) technologies, like Intel's Optane DC Persistent Memory Modules (PMMs) [19], will put terabytes of data within a few hundred nanoseconds of processors, which database researchers are beginning to exploit [4, 53]. What sort of system architecture would best be poised, ten years hence, to make use of this abundance?

#### Limits to Query Processing Performance

The answer may depend on one further trend in future memory systems: the relatively stable *bandwidths* that electrical interconnects can supply between processors and off-chip memory, which already are scaling more slowly than transistor densities. Memory capacities continue to rise through the terabyte range, growing numbers of DIMMs to support them should supply higher aggregate bandwidths even if single DRAM bank cycle times stay fixed. However, individual chips are limited in the amount of data they can transmit per unit time via the pins affixed to their packages, whose size does not scale downwards with transistors, and whose cost remains high relative to other parts of the chip. This limit has remained within 100-200GB/s per socket over the past few years for the highest-end server parts (such as the Intel and Oracle DBMs in Section 1.1), and in general, over the past decade, the ratio of arithmetic capacity to bandwidth wall likely lies ahead.

#### Arithmetic Intensity of Analytics Queries

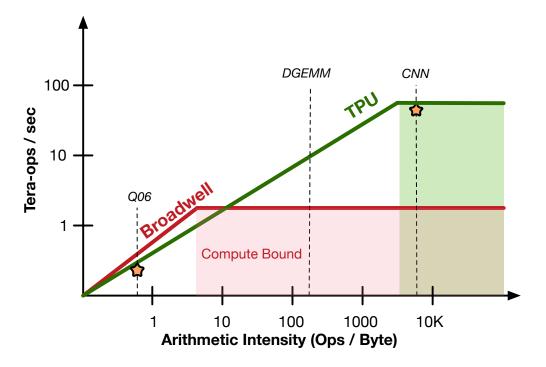

TPC-H Q06 query hints at why this bandwidth wall represents a crucial impediment to analytics performance. Its simplicity makes it very easy to calculate how much data a (naïve) plan for that query must move between processor and memory: assuming the four attributes accessed are each encoded as 32-bit values (two single-precision floating point numbers and two integer-valued dates), then 16 bytes must be scanned per record, for which 7 operations (5 comparisons, one multiply and one add) must be performed, yielding an *arithmetic intensity* of 0.44 ops/byte. In Figure 1.2, a *roofline model* [72] plots the performance limits of different machines as a function of a workload's arithmetic intensity. Q06 lies *far* to the left, bandwidth-bound side, regardless of whether one considers the roofline for an Intel Xeon E5-2667 (Broadwell) server part or Google's custom Tensor Processing Unit (TPU) [22] (chosen to show two ends of the machine roofline spectrum). <sup>1</sup>

The latter, whose crossover point at which workloads can start to become compute-bound lies beyond 1000 (floating point) ops/byte, is shown to emphasize one point: that hardware acceleration tends to succeed only when arithmetic intensities are orders of magnitude higher than that of Q06. Moreover, since empirical measurements of this particular query's performance later on (Chapter 6) show that existing machines already achieve close to 50% of the roofline's indicated peak, no amount of custom acceleration hardware could accelerate that query plan more than 2x unless more bandwidth can be supplied.

<sup>&</sup>lt;sup>1</sup>The Oracle DPU [1] would be a more natural comparison here, but we could ascertain from their publication how much arithmetic bandwidth each DPU die supplies.

Figure 1.2: Approximate Roofline Model of Intel Broadwell and Google TPU

#### Towards the Bandwidth Wall

Q06 may have been a particularly egregious example, since it consisted of an entirely scanbased query, but a similar analysis can be extended to more complex analytics operations as well. Joins, for example, ought to entail more significant data re-use. Using a more elaborate analysis than the above (see Chapter 7), we have estimated the communication costs-and therefore peak throughput-of the high-performance hash-join implementation presented by Schuh et al. [59]. Relative to the specifications of the machine reported in their evaluation, their measurements already appear to be approaching 40% of the bandwidth-defined peak, for at least some problem sizes. Similar analysis for other operators-especially using the AVX256 vectorization results of Polychroniou et al. [48]-gives even higher fractions of the theoretical machine peak. From this we might extrapolate that the next few years of research, combined with the increasing prevalence of "SQL-in-Silicon" [43] instruction extensions, will propel relational operator implementations in high-performance query execution engines ever closer to their communication-determined limits.

#### Implications of the Bandwidth Wall

These trends suggest that designers of tomorrow's DBMs should focus less on hardware extensions to accelerate individual relational operators and more on customizing the compute and memory systems to help queries *move less data*; secondly, they should concentrate on the

possibilities for reducing memory traffic that arise when *full query compilation is employed*, and more inter-operator optimization is possible.

#### Hardware-Assisted Communication Reduction

Within the former category, designers may consider at the coarsest level of granularity whether a database-focused processor might for example benefit more than other workloads from devoting a larger fraction of fixed silicon budgets to cache rather than pipelines, or whether analytics workloads can benefit from technologies like High-Bandwidth Memory (HBM) [36, 47], which places multiple gigabytes of DRAM into the same package as the processor, enabling much higher access bandwidths<sup>2</sup>. The utility of either approach depends on finding temporal locality (data re-use) in query execution, which itself depends critically on choices made during query compilation.

Specialized hardware can also be employed to reduce the amount of data that must be brought into the processor in the first place, for instance by performing filtering operations in memory or SSD controllers [13], as some have explored. Or, designers can consider whether DBMs might best be constructed with a larger number of smaller sockets, supplying greater aggregate bandwidth albeit with a higher likelihood of NUMA effects. We forego such considerations in this study, on the grounds that, eventually, what happens within a single package still matters.

Some queries like Q06 can really only be sped up if accesses to some fields can be avoided, or their size can be reduced. To avoid unnecessary accesses, the column imprints technique of Sidirourgos and Kersten [63] supplies a small secondary index structure to avoid accessing cache lines if their contents can be determined not to contain relevant values. In complex predicates, accesses to unneeded attributes can be pruned in the presence of short-circuit boolean ANDs, as 2 describes, though this can result in steep branch-misprediction penalties on general-purpose processors. Meanwhile, compression techniques that trade additional arithmetic for less data movement are another way to reduce traffic, and they can be made cost-free with hardware support. For queries that use string-valued attributes, dictionary compression can drastically reduce data movement when the domain of an attribute is small. This can be combined with *bit packing*, which places multiple elements of non-byte-sized (e.g. 6- or 11-bit) values contiguously into the same word, requiring unpacking upon access, which Polychroniou and Ross [50] showed how to do in isolation at line rate on Intel architectures using AVX SIMD instructions, but which in the context of more complex compiled queries could likely benefit from hardware support. BitWeaving [34] solves a similar problem with an even more computationally expensive mechanism.

Clearly, compression and avoidance techniques should be assumed in the design of a future DBM, but the more interesting implication of the approaching bandwidth wall is that database hardware should *seek to accelerate algorithms and query plans that minimize*

<sup>&</sup>lt;sup>2</sup>Though not that much higher: the HBM2E parts announced by Samsung [56] in 2019 offer 410GB/s, which does not represent an order of magnitude difference with regard to the highest-end off-chip memory products

*data movement*, rather than those that simply happen to be the fastest already on today's platforms. This might entail tolerating *random* accesses better than general-purpose outof-order cores, as would be necessary to make full use of technologies like HBM [47]. This consequence of the bandwidth constraint is the focus of the rest of this thesis.

#### **Communication-Minimizing Query Plans**

While the arithmetic intensity of individual relational operators is not high relative to that of other workloads, the trend towards dynamic compilation offers new opportunities to treat *entire query plans* as single algorithmic units to be optimized and, conversely, for which to optimize hardware. Not only does compilation make it possible to reduce communication by avoiding the materialization of intermediate results, but it means that the memoryaware optimizations employed by Schuh et al. [59] (and others) to implement individual operators can be codified into re-usable *code generators* that can extend their effects across fused sub-queries while also tailoring them as needed to any combination of input datatypes and formats. Since the consequences of such choices intimately affect a query's interaction with the hardware on which it executes, we call them *machine-level plan* decisions, and discuss them at length in Chapter 2. And since they can significantly alter the query's data movement requirements in particular, we think that the large plan space they engender should be studied intensively by the architects of any future DBM. Furthermore, *those plans, or plan choice strategies, that result in the least communication should be the ones DBMs should be designed to accelerate.*

Secondly, it is possible to analyze these communication requirements for a given memory hierarchy and degree of parallelism without physically measuring the number of bytes transferred on a physical machine. The cache-miss cost model of Manegold, Boncz, and Kersten [38] can be leveraged, in modified form, to estimate the number of cache lines that a query plan-when specified at a sufficiently low level of abstraction-should need to transfer. If the widest possible space of (machine-level) plans for a query is analyzed in this way, then the least communicative of these ought to be considered as an *upper bound* on that query's performance for any system with the same bandwidth and cache capacity. If that plan does not turn out to be the empirically highest-performing on today's systems, then the task of a DBM designer is to remove whatever computational bottleneck prevented it from executing at line rate. At the same time, the results of such study should indicate the answers to questions about the marginal benefit different classes of query can derive from different allocations of cache and compute resources, making it possible to co-design the hardware with query plans.

More generally, it can be hoped that future advances in both hardware and software approaches to query acceleration be judged relative to the bounds set by the bandwidth wall, and made knowable by communication cost models. As expectations about query benchmarks continue to evolve, so too should the methods of interpreting those benchmarks' results, and the ensuing chapters take initial steps towards that goal.

## 1.3 Methodology

A few necessary caveats limit the scope of this study:

- No DB frontend: We cannot compile all the way from SQL directly, as our current prototype lacks a SQL parser, algebrizer, and logical optimizer.

- Limited benchmark set: We do not present results for any complete benchmark suite-neither TPC-H nor TPC-DS nor others-but rely instead on a limited subset of queries for which we could produce plan generators.

- Non-conformance with TPC-H: To the extent that we make use of "TPC-H" queries, we do not adhere to all of the specification requirements. In particular, all string-valued attributes are assumed to be *dictionary-encoded* to the smallest byte-aligned size that can contain them, and consider only queries for which this is possible.

- Oracular cardinality estimation: Any discussion of "optimal" plan choices assumes that query optimizers can predict the selectivity of any predicate, which in practice is not possible.

- Throughput, not latency: Compilation time (both in the Ressort compiler and in C++ compilation) is excluded from any benchmarking on real systems, as the primary focus is on maximizing the rate of processing large datasets

- Lock-free algorithms: While many parallelization strategies for the algorithms under discussion have been devised that rely on either locks or atomic operations, these are deferred to future evaluation in favor of their lock-free alternatives

- **Raw performance**: Even if the bandwidth wall stalled query throughput entirely, custom architectures for analytics could easily increase performance per Watt of the processor, but we do not consider power or energy normalization here. (It should be noted, though, that even a zero-Watt processor could not achieve orders-of-magnitude energy efficiency increases for workloads that saturate memory bandwidth, as the latter subsystem's contribution to overall power footprint is substantial.)

## **1.4** Contributions of this Thesis

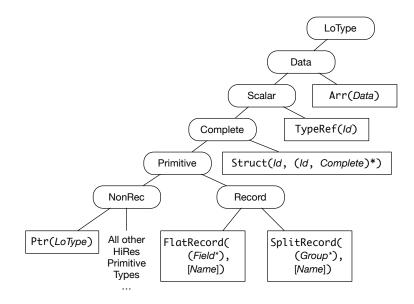

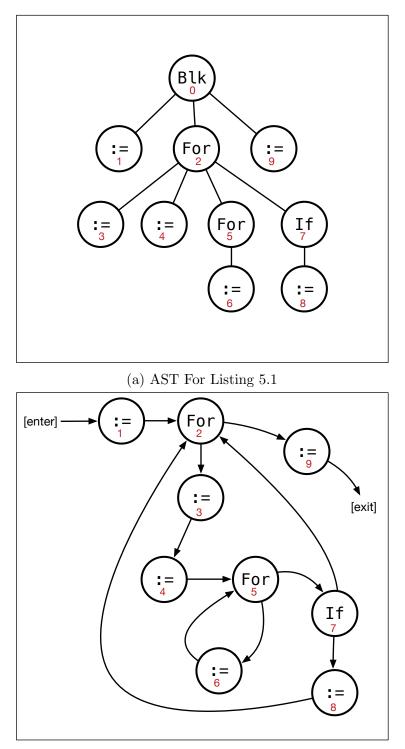

In light of the aims outlined above, the main contributions of this thesis are: (1.) the introduction of the concept of machine-level plans (Chapter 2), which unify all communicationdetermining aspects of fully-compiled queries into a single abstraction, (2.) the design of a statically-typed domain-specific language, HiRes (Chapter 3), for representing machine-level plans, and (3.) a compiler, *Ressort* (Chapter 5), that refines it to C++ code with parallel OpenMP [11] annotations that can be compiled and executed with any existing toolchain. Additionally, Chapter 7 presents a set of refinements to the communication cost model of Manegold, Boncz, and Kersten that expand its predictive capability to future memory systems.

## Chapter 2

## Machine-Level Query Optimization

## 2.1 Introduction

Fully-query compilation, in which SQL programs produce executable binaries, is the state of the art for high-performance, in-memory query processing engines, as it removes any per-record SQL interpretation overhead, allows for the exploitation of instruction- and datalevel parallelism within queries, and permits inter-operator optimizations that would be impossible in any other execution model. Many recent papers have presented advances in the design and architecture of query compilers [25, 9, 60, 68] and intermediate representation formats [46, 44] for query plans, making them an active area of current research. At the same time, the database community has investigated in great depth how to optimize hash joins [26, 3, 59] and other relational operators [49, 51] for the lowest-level of processorspecific parameters such as cache geometries, branch predictors, and vector instruction set extensions. While query compilation frameworks generally acknowledge the importance of these last-level mapping considerations, and set their parameters at a coarse granularity, not all the proposals of these works are fully expressible using the lowest level of query representation such compilers expose. This thesis builds on the rich legacy of research on hardware-tuning relational operators to design a new, more expressive query compiler backend.

More specifically, it introduces the concept of a machine-level plan (MLP) representation, which makes explicit all the memory-resident data structures needed for query execution, along with their layout (e.g. row- or column-ordering for each subset of attributes in a relation), the manner in which they are accessed, and how execution is parallelized. The choices presented by MLP lie below the traditional level of query optimization, where relational algebra may be rewritten to, e.g., change the order of joins or the application of where clauses. Once those choices are fixed by a traditional query optimizer, MLP plans answer questions such as "which attributes in a scan can be skipped based on already-known predicates?", and "when are the results of selection compacted into contiguous extents?" and "which attributes used after a join are packed into a custom hash-table?" and "where if at all in a query should partitioning be inserted to induce parallelism or locality?" Even once these questions are settled, MLP representation exposes yet another plan tradeoff, namely: which buffers must be physically materialized in memory, and which may exist only virtually, in CPU registers? This chapter shows how the both the traditional Volcano (record pull) [16] and data-centric (record push) processing models enforce one particular set of answers to this question, while query semantics permit others that may be more optimal.

The rest of this chapter explains the idea of machine-level plans more thoroughly, describing first the dimensions along which machine-level plans can be varied, how plans can be generated by transformation from a baseline, what the relative costs and benefits of each choice are, and, finally, how such choices can combine across a full plan. Put another way, this chapter codifies the toolbox of optimizations appearing in hand-tuned operator implementations that others have described, and makes them available for full queries and for re-targeting to inputs with arbitrary datatypes and formats. We do not claim to have invented them, but contribute instead a synthesis of these tuning methods, into a generalizable framework. The discussion in this chapter serves to motivate the specific machine-level plan representation presented in Chapter 3.

#### Assumptions

In the presentation that follows, the performance implications of machine-level planing choices are considered relative to two abstract machines. One consists simply of an idealized on-chip storage unit surrounded by idealized compute resources and connected to memory by a channel of fixed and finite bandwidth. It is limited only by the need to move data between on-chip and off-chip memory, and represents a purely bandwidth-bound query processor. Tradeoffs for each plan choice are discussed first relative to this *memory* or *traffic* bound.

The other abstract machine is a server-class, multi-socket, general-purpose multiprocessor representative of the machines typically used for high-performance analytics processing today, and provides context for computational (i.e. not bandwidth-related) bottlenecks that limit the throughput of query plans on hardware that exists today and which was available for evaluation. Tradeoffs for machine-level planing are secondarily discussed relative to platforms with real-world artifacts such as branch predictors and load-store queues, as well as a limited arithmetic bandwidth that requires parallelism to be fully utilized. Units of parallel execution are referred to as "threads" for the sake of convenience, but could represent some other abstraction such as SIMD lanes.

A much broader spectrum of compute devices exists, and many of these have been considered for query processing, from GPUs [52, 57, 75, 8] to FPGAs [73, 74]. We omit explicit discussion of these platforms, as many insights from the compute-bound analysis are more or less translatable. Instead, we turn our attention to the most common query processing machines, and those yet to be built.

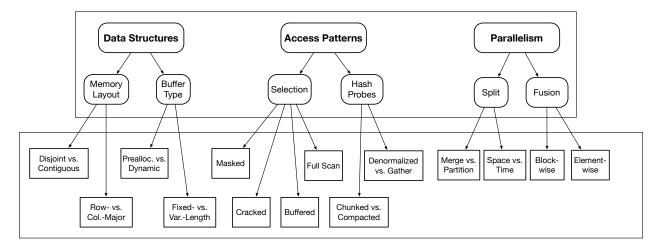

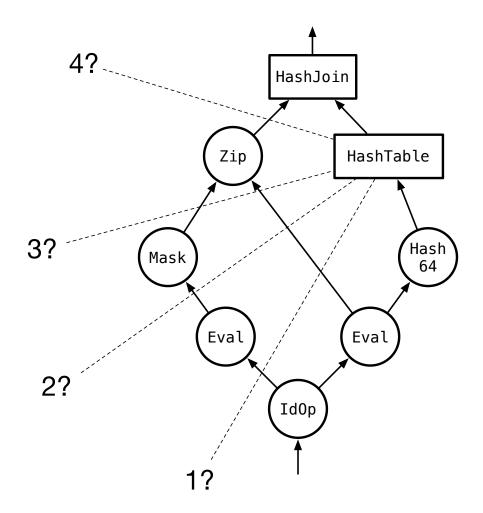

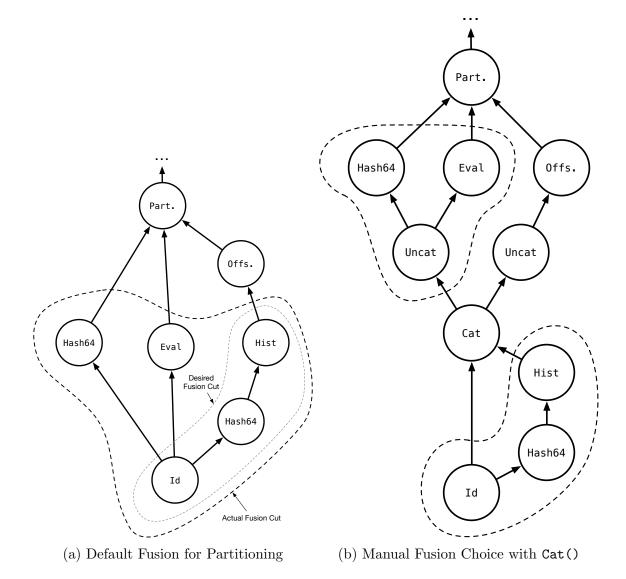

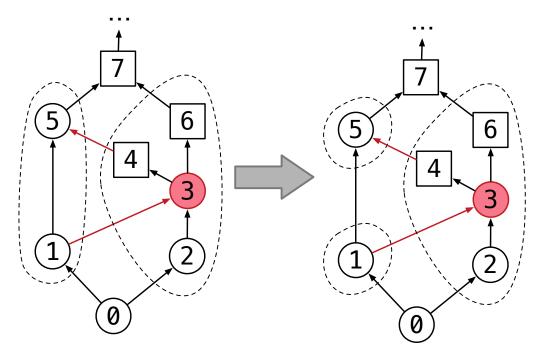

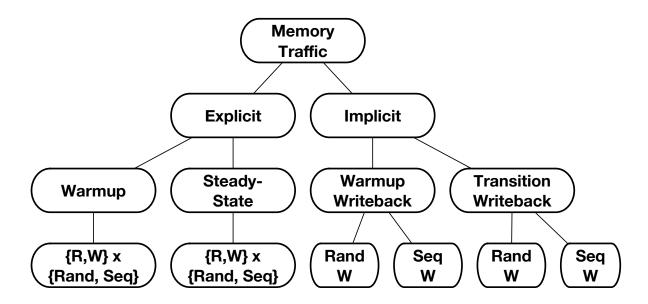

Figure 2.1: Dimensions of Machine-Level Plans

## 2.2 Dimensions of Machine-Level Planing

The upper box of Figure 2.1 shows the three basic "dimensions" along which machine-level planing decisions can be made: *data structures*, *access patterns*, and *parallelism*. These dimensions are not, strictly-speaking, orthogonal, and choice of one may constrain choices of another, but they are a nonetheless a useful decomposition of the ways in which a query's execution maps onto memory hierarchies and computational resources.

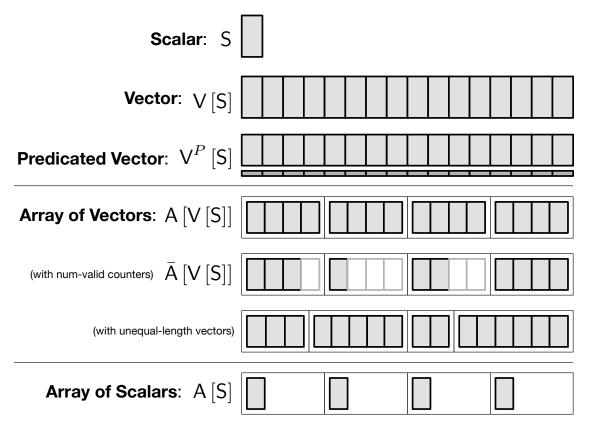

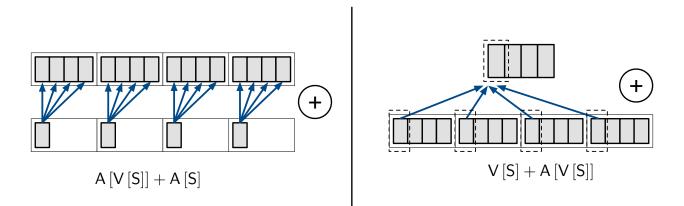

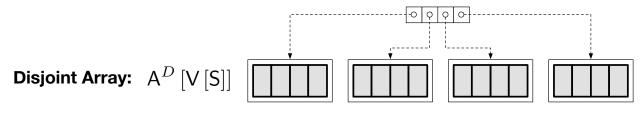

**Data structures**. In the course of execution, various intermediate results will need to be *materialized* by some operators into memory-resident buffers for use by others. Even if a query's original inputs have a fixed structure of independent, dictionary-compressed, perattribute columns, these intermediate products do not need to be arranged the same way, but different memory layouts, such as row- and column-major order, or non-contiguous buffers (e.g. those split among NUMA domains), offer different access performance characteristics. Meanwhile, some buffers may be designed to accommodate an initially-unknown number of elements, while others may require counting their maximum storage requirements before use, but allow easier access afterwards.

Access patterns. Some kinds of operations result in different orders of access to data that is already arranged in memory. For example, selection (filtering) operations can obviate the need to read individual rows of buffers used in subsequent steps, but avoiding such reads may result in additional computation, or require buffering indices of valid rows, and then gathering those that make the cut. Structures that are *probed*, like hash-tables, may start off with linked lists of elements that must be traversed, but can be reshaped to flattened forms after insertion is completed, in order to allow contiguous probes.

**Parallelism**. Individual operators can be parallelized by dividing up their inputs between threads, or partitioning them based on data-dependent key values, and either choice may affect how subsequent operations on their results are parallelized. Two or more operations can be *fused*, interleaving their execution on an element-by-element basis without any intervening materialization, or by interleaving the processing of smaller blocks of the elements processed by each (i.e. the block-at-a-time model implemented by Vectorwise [76] as described in Section 1.1 of the previous chapter. These choices can change communication patterns and cache working-set sizes substantially.

Within each of these categories, the more specific parameters shown in Figure 2.1's lower box can be varied by *transforming* a default, or baseline, plan into more complex ones by a series of procedures that require very different realizations as compilable code. Without presenting a formal representation of query plans at the machine level, the next section reviews these transformational possibilities abstractly, and describes the benefits they may provide in terms of communication and computation efficiency, as well as costs they might entail of the same resources.

## 2.3 Plan Derivation by Transformation

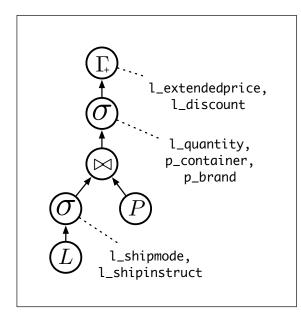

To illustrate the concrete choices made in each of the three machine-level planning dimensions, consider a query such as TPC-H Query 19, whose SQL is shown in Listing ??. In classical query planning, a "logical" optimizer would fix the order in which selections occur before or after a join (in this case realizing that each of the 1\_shipmode and 1\_shipinstruct clauses is identical and can be factored out before the join), resulting in the plan of Figure 2.2a. A "physical" planner would choose to instantiate a hash join, for instance, instead of a nested-loops join.

```

1

select

2

sum(l_extendedprice* (1 - l_discount)) as revenue

3

from

4

lineitem,

5

part

6

where

7

(p_partkey = l_partkey

8

and p_brand = 'Brand#12' and p_container in ('SM CASE', 'SM BOX', 'SM PACK', 'SM

PKG')

9

and l_quantity >= 1 and l_quantity <= 1 + 10 and p_size between 1 and 5

10

and l_shipmode in ('AIR', 'AIR REG') and l_shipinstruct = 'DELIVER IN PERSON')

11

or

12

(p_partkey = l_partkey and p_brand = 'Brand#23'

13

and p_container in ('MED BAG', 'MED BOX', 'MED PKG', 'MED PACK')

14

and l_quantity >= 10 and l_quantity <= 10 + 10 and p_size between 1 and 10

and l_shipmode in ('AIR', 'AIR REG') and l_shipinstruct = 'DELIVER IN PERSON')

15

16

or

17

(p_partkey = 1_partkey and p_brand = 'Brand#34'

18

and p_container in ('LG CASE', 'LG BOX', 'LG PACK', 'LG PKG'

19

and l_quantity >= 20 and l_quantity <= 20 + 10 and p_size between 1 and 15

20

and l_shipmode in ('AIR', 'AIR REG') and l_shipinstruct = 'DELIVER IN PERSON');

```

Listing 2.1: TPC-H Query 19 in SQL Form

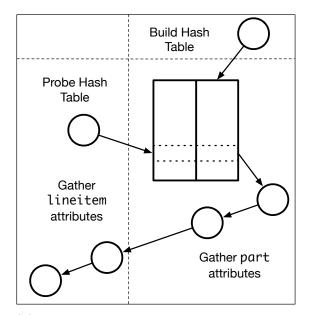

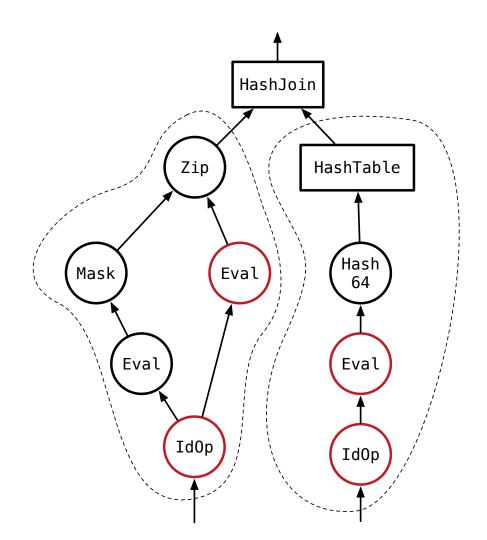

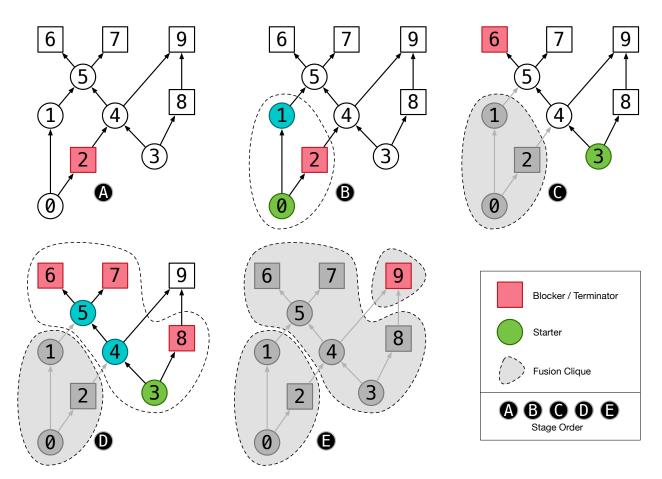

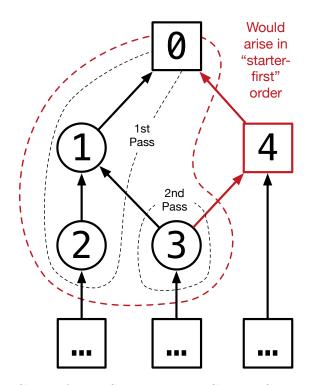

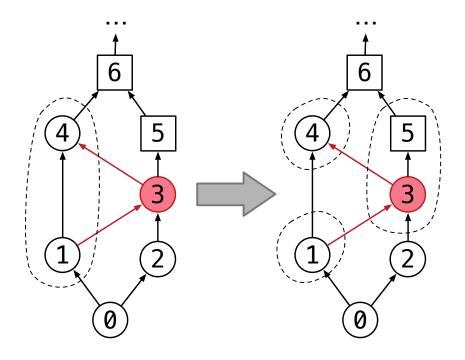

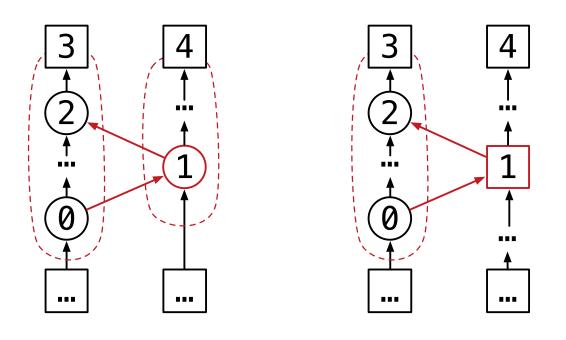

(a) Traditional Query Plan (Semi-Physical) for TPC-H Q19: Scan of lineitem, followed by selection on l\_shipmode and l\_shipinstruct, hash join on l\_partkey, followed by further selection and aggregation (average).

(b) Base Q19 Execution Diagram. Circles represent column scans, and arrows represent the "flow" of a tuple, while boxes represent a hash-table or materialized partition.

Figure 2.2: Two views of a default plan for TPC-H Query 19

Then, a "machine-level" planner would further refine this into something like Figure 2.2b, which depicts a query plan's execution in terms of the flow of a record through space and time, as well as the layout of relevant data structures, rather than as a DAG of relational operators, in order to reveal the plan's machine-level characteristics.

Here, circles represent accesses to one or more attribute columns (scans and gathers) and the computation of any results from them, while arrows represent actions that each record may conditionally *cause*, such a subsequent scan, a hash-table probe, or insertion. Square boxes denote hash-tables, while dotted vertical lines very coarsely separate the two relations (the *build relation* lineitem and *probe relation* part). Horizontal dotted lines divide execution into distinct stages; in Figure 2.2, the "hash-table build" stage must complete before the records of lineitem are joined against its result. Thus, these time divisions correspond–roughly–to separate loops or loop nests in any code that would implement them.

In Figure 2.2b, two relations are joined via a hash-table built from a single key attribute, preceded by and followed by selection based on others, which are *gathered* (via position vectors) from their original columns when needed. The join style is a reasonable default, as many database engines–especially non-compiled ones–will have a ready-made join operator that expects a (hash, row-ID) tuple table format.

This example is fairly representative of many other queries, which differ merely by the addition of further joins, selections, and aggregations. In each of the sections that follow, one machine-level plan *transformation* offers a choice that affects the execution of one of this plan's operators; later, Section 2.4 shows how these choices interact across the entirety of a machine-level plan, and how they can apply recursively.

#### #1: Split-Merge Parallelization

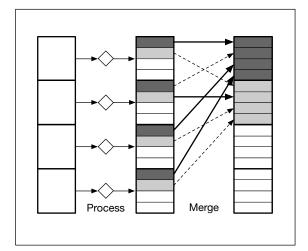

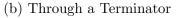

Figure 2.3: Split-Merge Parallelization

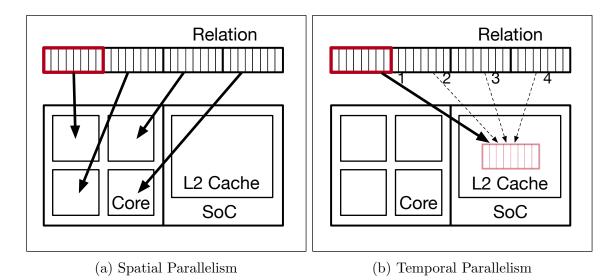

The simplest way to parallelize a query plan is to *split* a relational operator's input records into equal-sized subsets, and apply the operator to those subsets separately. The kind of independence imposed on the resulting subsets can either be *spatial* (Figure 2.4a), or *temporal* (Figure 2.4b). Spatial parallelism applies when each unit of input is assigned to a different processing element, such as a thread, processor, socket, or SIMD lane. Temporal parallelism applies when the units of input are still processed sequentially in time, but the scope of inputs considered at once is limited in order to reduce contention on some resource such as cache. The cache blocking of matrix multiply algorithms is an example from another domain; in relational query optimization, an example would be building independent hashtables for subsets of the total input under the assumption that these will fit better in cache.

**Costs.** Of course, as the latter example highlights, such independence is not free of cost: in the hash-table case, independent aggregations, for example, would later have to be *merged* by aggregating the aggregates themselves. Figure 2.3 depicts this more generally for all kinds of *split-merge* parallelism: if blocks of input are processed separately, any operation that reorders records based on their values will require a subsequent merge–so called because of its resemblance to the eponymous step of mergesort–to stitch the results back together. In the paradigmatic plan of Figure 2.2b, all that follows the initial hash-table build may be split

Figure 2.4: Spatial and Temporal Parallelism

without a merge; splitting the hash-table build would necessitate a merge of the parallel tables.

The impact of the split-merge transformation on performance will generally depend on the relative cost of this merger compared to the benefit of independence. If the data in each block are sufficiently re-used, then splitting may reduce traffic enough to improve performance even without the benefit of parallelism. On the other hand, even parallelism may be of minimal benefit if the merger must be performed serially.

The other possible cost of split-merger is that spatial parallelization sometimes requires data structures to be replicated once per "thread" (if atomic operations are not available or are too slow), thus increasing the size of the working set.

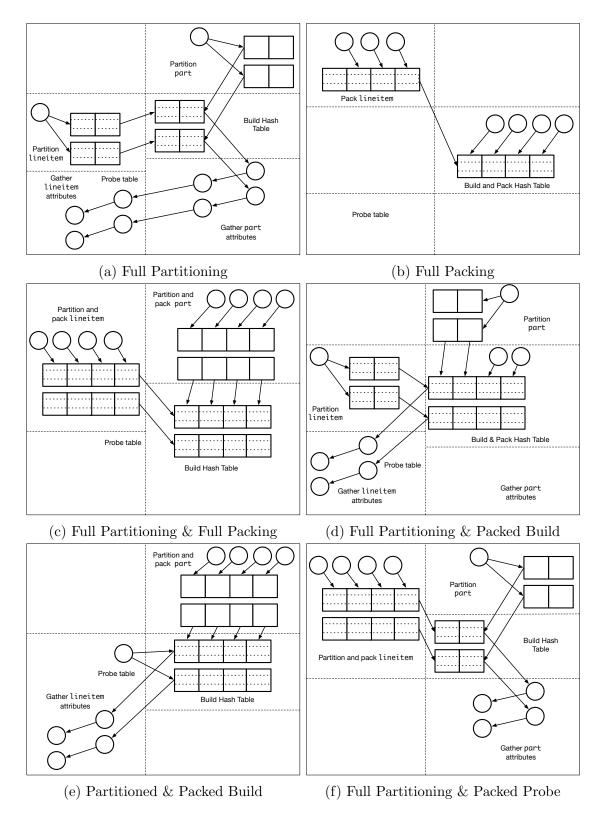

### #2: Partition Parallelism

If split-merger is limited by the (possible) need to perform an expensive, serial merge operation, then its alternative is *partitioning*, which divides inputs among several partitions based on the values of some attribute chosen as the *key*, which is often a hash function of an underlying attribute used as a join or aggregation key. In radix partitioning, a subset of the key's bits are used as the address of each record's output partition, making the partitions independent, because a single key can appear in at most one of them. This value independence makes subsequent merging unnecessary. The parallelism induced by partitioning, like that from splitting, can also be exploited either spatially or temporally.

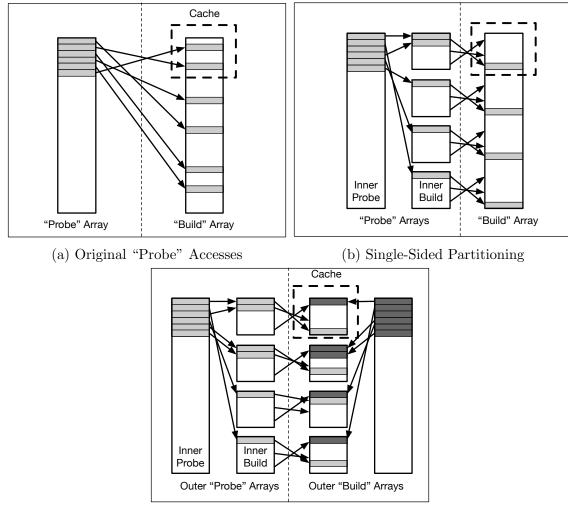

In the recurring example of Figure 2.2b's join, partitioning could apply to either the left (lineitem) side, the right (parts) side, or both. Figure 2.5 shows the consequences of these strategies in terms of memory access patterns. In the original non-partitioned plan, there are two operations that resemble Figure 2.5a: (1.) the initial construction of the hash-table

(c) Double-Sided Partitioning

Figure 2.5: Aggregation, Joins, and Hash Tables with and without Partitioning

of part on key field p\_partkey, and (2.) the join loop, in which that hash-table is probed with records from lineitem using the l\_partkey field as a key. In both cases, the physical array containing the hash-table acts as the *build* array, while data values in the two key fields determine which locations in that array are accessed. This means such accesses are possibly scattered across the length of the build array (depending on the distribution of the keys), generating many cache misses if it array is larger than the cache. This is a performance impediment not only on contemporary general-purpose processors, which can sustain only a limited number of outstanding misses at a time, but also by the more abstract metric of raw communication cost, if the width (in bytes) of the attribute fields accessed is much smaller than the size of a cache line.

Benefits. Partitioning can both reduce the likelihood of such cache misses, and provide

additional parallelism. In Figure 2.5b, records are first distributed to independent buckets based on the addresses in the (outer) build array (i.e. keys) to which they will generate accesses, meaning that those resulting probes (arrows across the vertical dotted line) will be distributed over narrower ranges, hopefully resulting in more reuse of records once they have been brought into the cache. It also means that each of the resulting partitions can be processed in parallel, without atomics or locking, as they are guaranteed to access disjoint locations in memory (which matters in the aggregation or hash-table build case, though not in a join). In the case of a join, *double-sided* partitioning (Figure 2.5c) occurs when the hash-table build is parallelized by partitioning with the same function used to partition the probe relation, yielding in a miniature hash join between each corresponding pair of partitions in the two relations.

**Costs**. Partitioning requires both extra computation, and extra communication: in radix partitioning, the key fields of all input records must be first scanned once while a *histogram* is built to count the number of elements in each resulting partition, so that sufficient space in the output buffer can be allocated for them; then, all input records must be scanned again and scattered to their respective partitions, all while the histogram's counters must be incremented to track the offset at which the next record should be emitted. Thus, the total traffic cost is at least (1.) two full scans of the input keys, (2.) one full scan of input values, and (3.) one full (scattered) write of the output.

However, cache misses from random accesses may also occur: radix-m partitioning has a working set of at least  $2^m$  cache lines-one per partition-since the next record to be output at any point could fall into any one, in the worst case of a uniform key distribution. The histogram, too, is part of the working set, though smaller, as one cache line is likely to hold several counters. In the worst case, a high-fanout partitioning may result in the transfer (read-modify-write) of one cache line per record during histogram-building and *two* during movement, in addition to the two full sequential scans of the input.

On realistic platforms, other non-bandwidth bottlenecks may emerge: cache misses between levels of the on-chip hierarchy may degrade performance of general-purpose pipelines even if no off-chip traffic is incurred, and other real-world constraints like cache conflicts and the reach of translation lookaside buffers (TLBs) may impede execution if the working set's virtual address range exceeds TLB capacity (though there are workarounds for this, such as huge pages, or software write-combining buffers [57] – see Section 3.1).

In order for partitioning to be profitable under a raw communication metric, it must eliminate more cache line transfers in a future join or aggregation than it causes in its own execution. If computation is considered, then any traffic increase must be offset by the resulting parallelism downstream in the query, which often may only be realized by way of partitioning.

#### #3: Attribute Packing & Memory Layout

A classical element of schema design in relational databases is *denormalization*, which eliminates copies of an attribute that is shared between two or more relations, relegating its

storage instead to a single table. For example, in the TPC-H schema, a lineitem of an order pertains to a specific part with qualities, such as price, that are common to all orders in which it might be included. Instead of replicating that price for each lineitem in which the part is referenced, a separate **part** table includes a single copy of it, and so computing the cost of an order requires joining against the **part** table to retrieve it. This has a clear tradeoff: it reduces the amount of storage required for the whole dataset, at the cost of additional joins.

Denormalization has an analogue in machine-level planing. Figure 2.2b illustrates the execution of precisely the join described above. The coarse schematic depicts a hash join using a table with two columns, which naturally correspond to the join key (the part number, encoded as 1\_partkey or p\_partkey in lineitem and part respectively), and a row ID, which points back to each part's original location in the part table. When the join is performed, a matching part for a given partkey has other attributes that can be retrieved by gathering them from the original part table based on their row IDs. However, this need not be so. An alternative join style, such as shown in Figure 2.11b, could instead pack all attributes of the part relation into the hash-table, eliminating the need for any future gather. The same principle applies to partitioning as well, or any other shuffling operation, including sorting: when part of a record is moved based on one attribute, the others can either follow it or remain in place. The choice is not all-or-nothing, either: any subset of possibly-relevant attributes can be packed or not.

**Benefits**. Because hash-table construction (most likely) reorders entries significantly, and randomly, with respect to their original sequence, post-join gather operations will be scattered randomly over the original table, resulting in poor memory locality and a higher number of cache misses, which packing can eliminate. Any matching probe to a packed table can access all relevant attributes at once, in a single cache line, or at least a smaller number of them.

The decision to pack also offers an opportunity to adjust the memory layout of the reordered table. Just as any table can be arranged in row- or column-major order, so too can any packed hash-table. While it may seem counterintuitive to lay out packed hash-table attributes in discontiguous arrays, this can be fruitful when, e.g. the join key is itself rather selective, or one other attribute is used in a selective post-join filter, prior to others: in this case, all attributes accessed after the initial join-filter can be co-located in a single array that forms an effective secondary working set. Of course, such re-shaping of relations need not be incorporated into a hash-table build or partition, and can be applied on its own prior to the execution of any other operation.

**Costs**. In addition to the sequential read traffic required to scan all packed attributes, the addition of columns to a hash-table or partition output increases the size of the working set during its construction and, for hash-tables, all subsequent probes. If that increase exceeds cache capacity, the resulting capacity misses may dwarf any savings from reduced gathers.

```

1

size_t count = 0;

2

for (size_t i = 0; i < N; i++) {</pre>

3

bool a = A[i], b = B[i]; c = C[i];

4

5

6

rec_t d = D[i];

7

bool mask = a && b && c

8

if (mask) out[count++] = d;

9

10 }

```

Listing (2.2) Complex predicate filter

```

size_t count = 0;

for (size_t i = 0; i < N; i++) {

bool a = A[i];

if (a) {

bool b = B[i], c = C[i];

rec_t d = D[i];

bool mask = b && c;

if (mask) out[count++] = d;

}

}

```

Listing (2.3) A "cracked" version of 2.2

Figure 2.6: C Code for Cracked Predicate Application

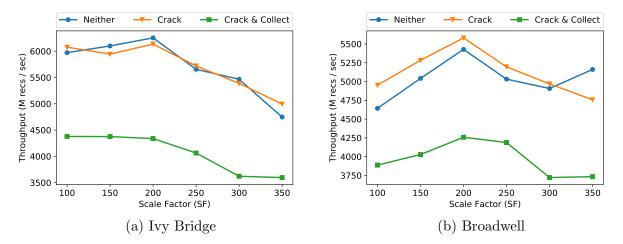

### #4: Predicate Attribute "Cracking" & Access Serialization

Where attribute packing is not useful, its antithesis may well be. If a filter operator's predicate consists of several disjunctive clauses, each of which uses a different attribute, then loading all fields may consume more bandwidth than necessary if initial clauses are highly selective. The canonical filter loop in Listing 2.2 exhibits precisely this excess. To its right, Listing 2.3 wraps accesses to the secondary attributes B[] and C[] (in separate columns) inside an if statement conditioned on the truth value of A[].

The literature [64] has treated this distinction as one between *vectorization* (Listing 2.2) and *compilation* (Listing 2.3), insofar as the word 'vectorization' implies computing the full predicate for a column of records at a time without any intervening branches, while 'compilation' implies the opposite. A more generic term used in this thesis is *cracking*, which emphasizes the splitting up of predicate evaluation (and avoids conflicting meanings of 'vectorization', hereafter reserved for the exploitation of data-parallel architectures).

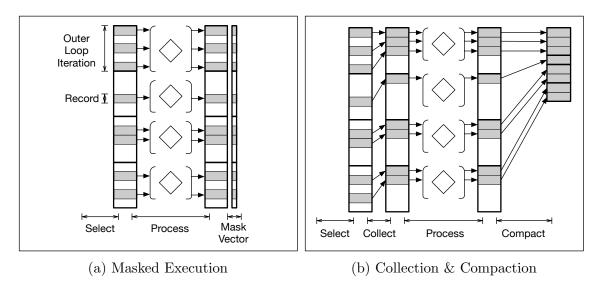

The cracking transformation encompasses not just the serialization of attribute accesses shown in Listing 2.3 but also any changes to memory layout and execution that result from choosing whether or not to coalesce the sparse subset of records that survive a filter after it is applied and before the next materialization occurs. For example, both main loops in Figure 2.6 build a dense array of valid records in their output, but these loops could be split into two, with a vector-valued **mask** output in between, as in Figure 2.7a.

Or, the loop could be split into two *with* coalescing in between ("collect" in Figure 2.7b), producing dense runs of elements of A, which may then be processed without any mask. In this case, "processing" would entail gathering needed elements from B[], C[], and D[] via position values stored during collection. This is intermediate buffering is sometimes necessary in real systems to obtain any benefit from the communication reduction of cracking, as Polychroniou [48] and others have shown. Normally, this buffering would occur on a blockwise basis: by applying temporal splitting in conjunction with cracking, an idealized query plan assembles a block of valid addresses to gather in the next loop that is sufficiently large

to amortize any startup overhead while also small enough not to exhaust cache capacity and so have to spill to memory between iterations of the outer loop.

Figure 2.7: Masking vs. Collecting & Compacting

**Benefits**. Under a pure communication cost metric, cracking is beneficial when the selectivity of each initial predicate is low enough to totally eliminate the need for access to at least some cache lines containing other attributes. Whether this is the case depends on both the selectivity and the size of the attribute(s) being accessed, as Pirk et al. [45] show: if the cache line is larger than the attribute size (e.g. eight 8-byte values in a 64-byte line), then a 50% selectivity will have for example a negligible impact on the number of lines transferred, while an 8% selectivity might cut communication roughly in half. The benefit of coalescing is that fewer cache lines may be needed to contain a materialized output if a denser packing of valid records causes fewer lines to be touched.

Under a cost metric that also considers computational requirements, cracking can eliminate superfluous expression evaluation in addition to suppressing unneeded loads and stores. Meanwhile, coalescing obviates the need to access mask or "valid" bits for each tuple, removing conditional branches.

**Costs**. In terms of memory traffic, cracking should have a worst-case neutral cost when considered in isolation. However, it conflicts with attribute packing, which negates its benefit by putting separate fields in adjacent memory and thus within the spatial footprint of a single line transfer. Coalescing can potentially increase memory traffic if it forces the materialization of intermediate results where none otherwise was needed.

In the real world of general-purpose CPUs, cracking entails additional data-dependent branches, which can dramatically decrease performance when their selectivity nears 50% and their outcomes therefore become unpredictable, causing frequent full or partial pipeline flushes (or other control-flow divergence phenomena on data-parallel processors), as others have reported [64].

#### #5: Dynamic Arrays vs. Pre-Allocation

Common operations such as joins and hash-table builds produce results whose sizes are not statically knowable in advance, or which are divided into partitions or buckets of initial unknown lengths.<sup>1</sup>

Even if a sophisticated query optimizer estimates join cardinality with high accuracy (though likely it will not [33]), this guess may still be exceeded at runtime, requiring dynamic allocation of additional space in necessarily disjoint memory. This discontinuity will affect all consumers of the operator's result, which must traverse all extents of records allocated in the course of execution. Eliminating that discontinuity requires *compacting* all such extents, which can be done at any downstream point in the query plan.

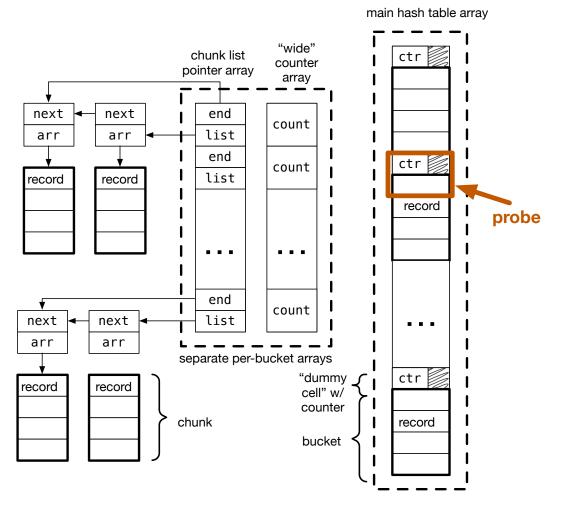

Alternatively, the inputs to operators with dynamically-sized output can be processed in two passes: one to *count* the number of outputs that will be generated (or the sizes of each of its buckets or partitions), and one to perform the operation itself. This is almost universally the case for partitioning, but could be applied to joins as well. Hash tables are a trickier case, as it is impossible to count in advance the number of distinct keys falling into each bucket without actually enumerating them, which requires an allocation of space equal to the number of keys. Still, it is possible to at least tabulate an upper bound on the number of keys that map to each bucket, which will over-provision space in the case that many elements share a key and are aggregated, but at least guarantees that the total size of all buckets combined is no larger than the original input, rather than its square, as would be needed to pre-allocate without such a count.

**Benefits**. Pre-allocation eliminates the need for linked list traversals, unpredictable dynamic allocation, and compaction, and can drastically reduce the need to over-provision hash-table and partition space in the presence of non-uniform key distributions and imperfect hash functions. Under a strict communication metric, choosing to pre-allocate may not have a noticeable salutary effect, but its elimination of irregular branches, serialized memory accesses, and dynamic allocation may significantly reduce computational bottlenecks on real systems.