# **Bio-Inspired Artificial Olfactory System**

Ping-Chen Huang Jan M. Rabaey

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2017-173 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2017/EECS-2017-173.html

December 1, 2017

Copyright © 2017, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Bio-Inspired Artificial Olfactory System

by

Ping-Chen Huang

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Jan Rabaey, Chair Professor Kannan Ramchandran Professor Bruno Olshausen

Fall 2015

# Bio-Inspired Artificial Olfactory System

Copyright 2015 by Ping-Chen Huang

#### Abstract

Bio-Inspired Artificial Olfactory System

by

Ping-Chen Huang

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Jan Rabaey, Chair

The escalating statistical variation of device behaviors in the nano-scale era has led to a search for alternative computational paradigms where randomness can be treated as opportunities rather than nuisance. This will allow computational systems to be built with circuits designed at the nominal case and have better access to the advantages of scaled technologies. Such computational paradigms may emerge as we explore the information processing in the biological sensory systems, which achieve unparalleled performance and energy efficiency with mediocre and unreliable components. Implementations of signal processing tasks such as feature extraction, learning, or recognition can especially benefit from bio-inspired computational models. In this thesis, we present a bio-inspired artificial olfactory system, which consists of an analog feature extraction front end that operates efficiently in the low-precision regime and a spike pattern classifier that exploits the randomness in circuits.

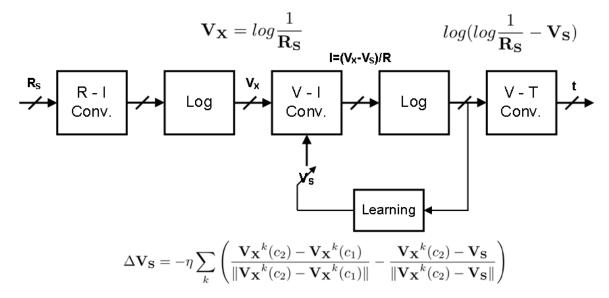

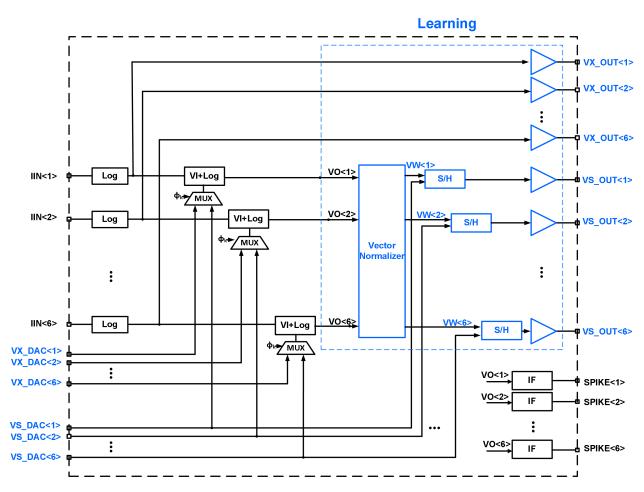

The analog front end implements a novel trainable feature extraction algorithm for metal-oxide gas sensor arrays. The algorithm extracts one composite feature of all analytes and transforms the sensor responses into concentration-invariant spike patterns. This composite feature is extracted by performing the gradient decent algorithm during training. This 6-channel analog frond end consumes 519 nW/channel in the training mode, and 463 nW/channel in the recognition mode.

The spike pattern classifier consists of a transformation of the input spikes into high-dimensional sparse vectors and a cortical memory model. The transformation is based on a random sampling scheme that can be efficiently performed with circuits exhibiting large parametric variations. Moreover, sparse representations allow fast and robust pattern storage and retrieval with associative memories such as the correlation matrix memory. Its realized today that hyper-dimensional computing architectures like this may be a perfect match to the emerging nano-scale devices. We show how this classifier can be densely and efficiently implemented in a 3-D CNFET-RRAM technology.

Dedicated to my parents.

# Contents

| C             | Contents |                                                                              | ii |

|---------------|----------|------------------------------------------------------------------------------|----|

| $\mathbf{Li}$ | st of    | Figures                                                                      | v  |

| Li            | st of    | Tables                                                                       | ix |

| 1             | Intr     | roduction                                                                    | 1  |

|               | 1.1      | The Need for New Computing Models                                            | 1  |

|               |          | 1.1.1 The End of Moore's Law                                                 | 1  |

|               |          | 1.1.2 Emerging Nanotechnologies                                              | 3  |

|               | 1.2      | The Search for New Computing Models                                          | 7  |

|               | 1.3      | The Return of Neuro-Inspired Computing                                       | 8  |

|               |          | 1.3.1 The Recurring Waves of Neuro-Inspired Computing                        | 8  |

|               |          | 1.3.2 Features of Neural Computation                                         | 9  |

|               |          | 1.3.3 Opportunities of Neuro-Inspired Computing                              | 10 |

|               | 1.4      | Research Goal                                                                | 10 |

|               | 1.5      | Thesis Outline                                                               | 10 |

| 2             | Sys      | tem Overview                                                                 | 12 |

|               | 2.1      | The Biological Olfactory Pathway                                             | 12 |

|               |          | 2.1.1 Sensing in the Olfactory Epithelium                                    | 13 |

|               |          | 2.1.2 Signal Integration in the Olfactory Bulb                               | 15 |

|               |          | 2.1.3 Dimensionality Exampsion in the Olfactory Cortex                       | 17 |

|               |          | 2.1.4 Computations in Higher-Level Cortices                                  | 21 |

|               | 2.2      | Architecture Overview                                                        | 21 |

|               | 2.3      | An Information-Theoretic Framework for Joint Architectural and Circuit Level |    |

|               |          | Optimization                                                                 | 23 |

|               |          | 2.3.1 Circuit-Level Comparison                                               | 23 |

|               |          | 2.3.2 Joint Architectural and Circuit Level Optimization                     | 28 |

| 3             | An       | Analog Gas Sensing Front End                                                 | 34 |

|               |          | Metal-Oxide Gas Sensors                                                      | 35 |

|              |            | 3.1.1 Sensing Mechanism                                   |

|--------------|------------|-----------------------------------------------------------|

|              |            | 3.1.2 Sensor Response Characteristics                     |

|              |            | 3.1.3 Arrayed Sensing                                     |

|              | 3.2        | Algorithms                                                |

|              |            | 3.2.1 Feature Extraction                                  |

|              |            | 3.2.2 Learning                                            |

|              | 3.3        | CMOS Implementation                                       |

|              |            | 3.3.1 Architecture Overview                               |

|              |            | 3.3.2 Impelementation of the Feature Extraction Algorithm |

|              |            | 3.3.3 Implementation of the Learning Algorithm            |

|              |            | 3.3.4 System Functionality                                |

|              |            | 3.3.5 Summary                                             |

|              |            |                                                           |

| 4            | Spil       | ke Pattern Classifier in Advanced Nanotechnologies 77     |

|              | 4.1        | Hyper-Dimensional Computing                               |

|              | 4.2        | Spike Pattern Classifier                                  |

|              |            | 4.2.1 Sparse Vector Generator                             |

|              |            | 4.2.2 Correlation Matrix Memory                           |

|              |            | 4.2.3 Behavior Simulation                                 |

|              | 4.3        | Implementation in Advanced Nanotechnologies               |

|              |            | 4.3.1 The Monolithic 3D Integration Platform              |

|              | 4.4        | Sparse Vector Generator in CNFETs and RRAMs               |

|              | 4.5        | Correlation Matrix Memory in RRAMs                        |

|              |            | 4.5.1 The RRAM Model                                      |

|              |            | 4.5.2 Pulsed-Programming of RRAM Resistance               |

|              |            | 4.5.3 The RRAM Prototype                                  |

|              |            |                                                           |

| 5            | Con        | aclusions 100                                             |

|              | 5.1        | Thesis Contributions                                      |

|              | 5.2        | Future Work                                               |

| ٨            | Don        | ver-Precision Models 103                                  |

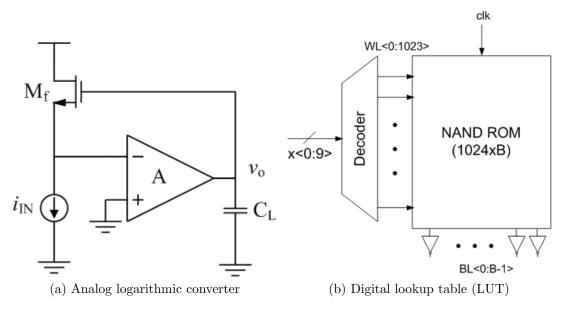

| А            | A.1        | Analog Logarithmic Transform                              |

|              | A.1<br>A.2 | Digital Logarithmic Transform                             |

|              | A.2        | A.2.1 Leakage Power Estimation                            |

|              |            |                                                           |

|              |            | A.2.2 Dynamic Power Estimation                            |

|              | ۸ ၁        | A.2.3 Total Power Consumption                             |

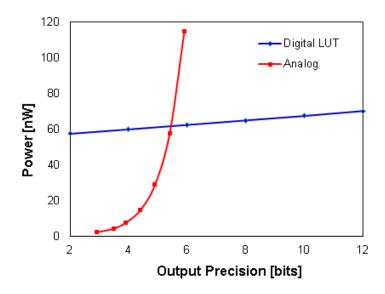

|              | A.3        | Analog VS. Digital                                        |

| $\mathbf{B}$ | Erro       | or Analysis 111                                           |

|              | B.1        | Error Modeling                                            |

|              |            | B.1.1 Errors from the V-I Converters                      |

|    | B.2          | B.1.2 Errors from the Normalizer |  |

|----|--------------|----------------------------------|--|

|    | C.1          | Parameters                       |  |

| Bi | Bibliography |                                  |  |

# List of Figures

| 1.1  | Microprocessor trend over the past 40 years. Adapted from [1]                          | 2  |

|------|----------------------------------------------------------------------------------------|----|

| 1.2  | Scaling trends of gate and interconnect delays. Adapted from [3]                       | 2  |

| 1.3  | Idealized model of the potential barrier separating the source drain potential         |    |

|      | wells, where $w$ is the well width, $a$ is the barrier width, and $E_b$ is the barrier |    |

|      | energy. Adapted from [5].                                                              | 3  |

| 1.4  | Barrier model of charge-based memory. Adapted from [11]                                | 4  |

| 1.5  | Conductive filament in the metal-oxide RRAM. Adapted from [21]                         | 5  |

| 1.6  | Monolithic 3D integration of logic and memory devices. Credit: M. Shulaker             | 6  |

| 1.7  | Traditional and alternative computing paradigms                                        | 7  |

| 2.1  | The olfactory pathway. Adapted from [37]                                               | 13 |

| 2.2  | Structure of the olfactory epithelium. Adapted from [37]                               | 13 |

| 2.3  | Topology of an odor receptor in the membrane. Individual amino acid residues           |    |

|      | are indicated by balls. Red balls indicate residues that vary extensively among        |    |

|      | odor receptors. Adapted from [37]                                                      | 14 |

| 2.4  | Expression zones in the olfactory epithelium. Zones expressing different receptor      |    |

|      | genes are marked in different colors. Adapted from [37]                                | 14 |

| 2.5  | Combinatorial receptor codes for odors. Adapted from [37]                              | 15 |

| 2.6  | Convergence of signals from the OE to the OB. Adapted from [37]                        | 16 |

| 2.7  | Odor coding in the OE and the OB. Adapted from [37]                                    | 16 |

| 2.8  | Stereotyped map in the olfactory cortex. Signals of the same type of olfactory         |    |

|      | receptor (marked with the same color) project to multiple spots in the cortex.         |    |

|      | Adapted from [37]                                                                      | 17 |

| 2.9  | Signals of different receptors converge in the OB and then diverge into the OC.        |    |

|      | Adapted from [37]                                                                      | 18 |

| 2.10 | Two coding strategies in term of autoencoder networks. Adapted from [46]               | 19 |

| 2.11 | Projection pursuit. The left part shows the state space of a two-dimensional data      |    |

|      | set. The right part shows the distribution of the projection onto the axes. When       |    |

|      | the axes are aligned with the data structure, the response shows a high degree of      |    |

|      | kurtosis. Adapted from [40]                                                            | 20 |

| 2.12 | Resulting basis functions of sparse coding. Adapted from [32]                          | 21 |

| 2.13 | System architecture                                                                    | 22 |

| 2.14 | Four types of signal representations                                                | 24 |

|------|-------------------------------------------------------------------------------------|----|

| 2.15 | Different signaling systems as noisy channels                                       | 24 |

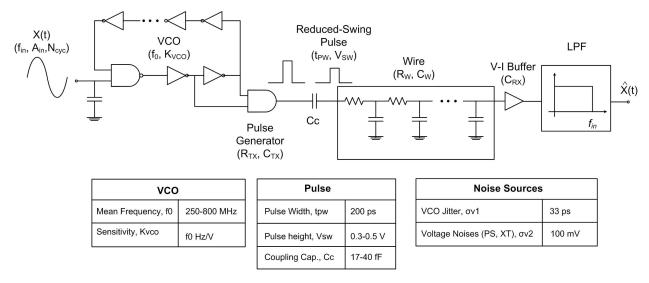

| 2.16 | Modeling of a on-chip digital communication link and the parameters in the          |    |

|      | model. The interconnect parameters are based on UMC's 90nm CMOS Technology.         | 25 |

| 2.17 | Modeling of a pulse-rate modulated communication link and the parameters in         |    |

|      | the model                                                                           | 26 |

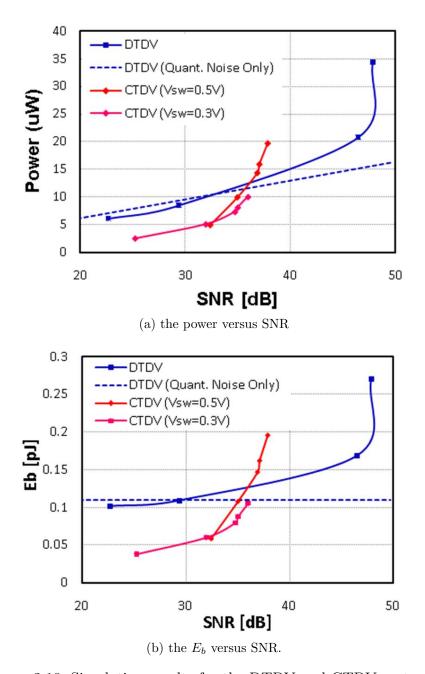

| 2.18 | Simulation results for the DTDV and CTDV systems                                    | 27 |

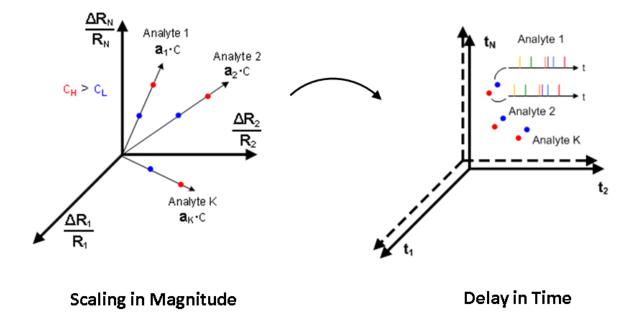

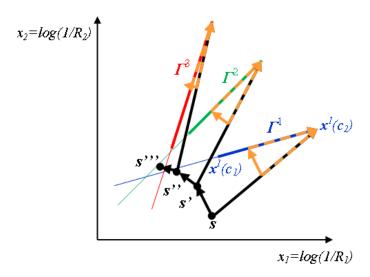

|      | Concentration invariant encoding                                                    | 29 |

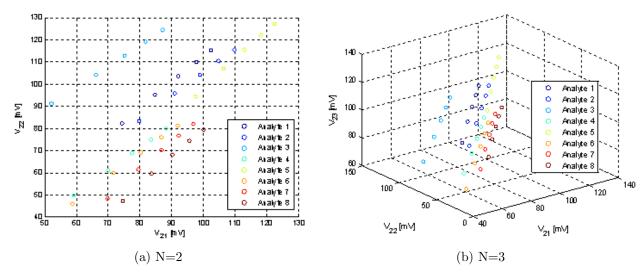

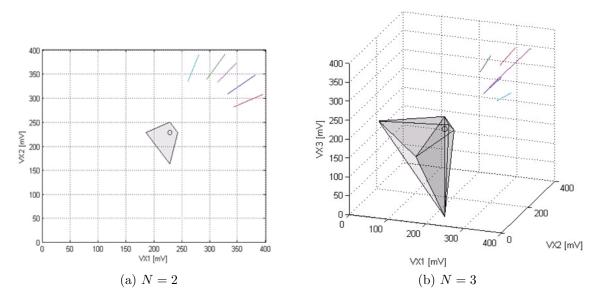

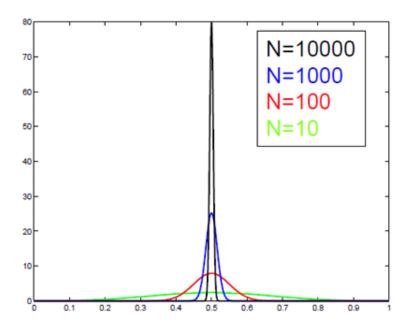

| 2.20 | Analyte responses in the log space with different number of sensors $(N)$           | 30 |

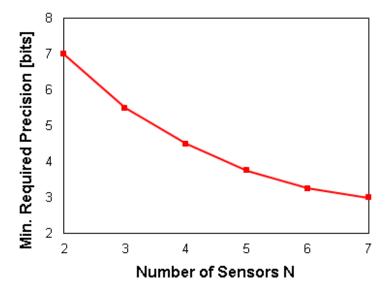

| 2.21 | Minimum required precision per degree of freedom                                    | 30 |

|      |                                                                                     | 31 |

|      |                                                                                     | 31 |

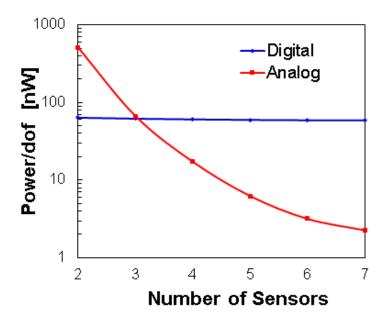

| 2.24 | The required power per degree of freedom $P(N)$                                     | 32 |

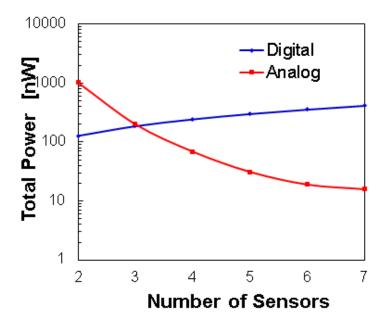

|      | Total power consumption $N \cdot P(N)$                                              | 33 |

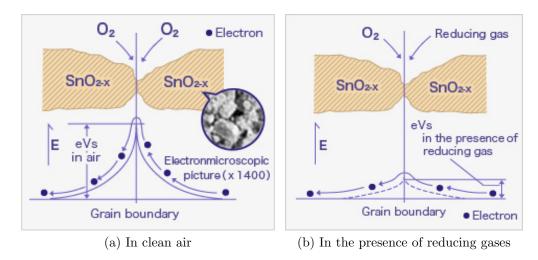

| 3.1  | Potential barriers at the grain boundaries in metal-oxide semiconductors. Credit:   |    |

|      | FIGARO, Inc                                                                         | 35 |

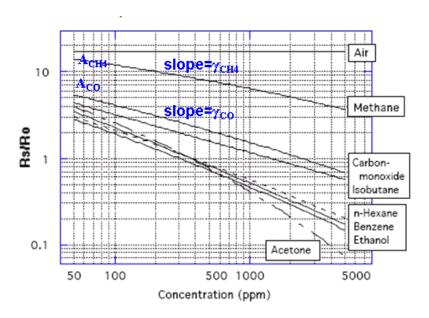

| 3.2  | ,                                                                                   | 36 |

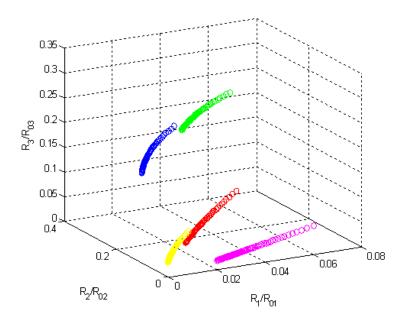

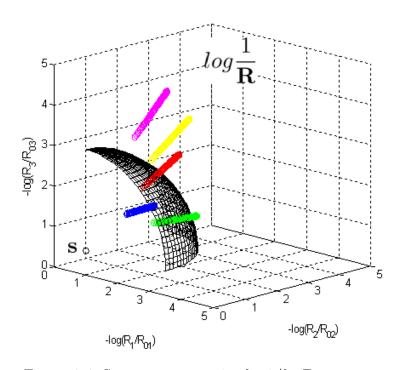

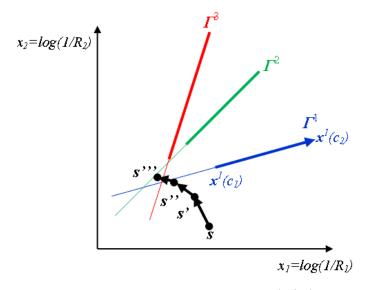

| 3.3  | Response trajectories in the sensor response space                                  | 38 |

| 3.4  | Sensor responses in the $1/log\mathbf{R}$ space                                     | 39 |

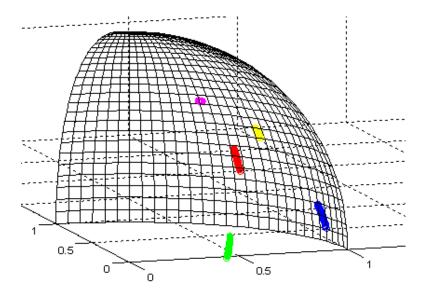

| 3.5  | Projected trajectories on the unit sphere centered at s                             | 36 |

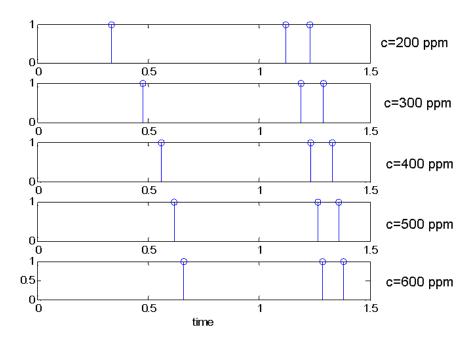

| 3.6  | Analyte responses at different concentrations are transformed to a unique spike     |    |

|      |                                                                                     | 41 |

| 3.7  |                                                                                     | 41 |

| 3.8  |                                                                                     | 43 |

| 3.9  |                                                                                     | 43 |

| 3.10 |                                                                                     | 44 |

| 3.11 |                                                                                     | 45 |

| 3.12 |                                                                                     | 46 |

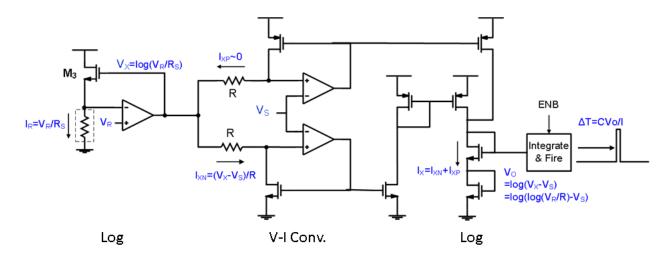

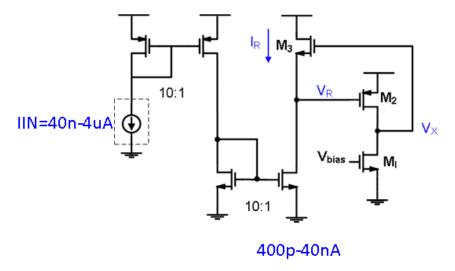

| 3.13 | Schematic of the input logarithmic converter                                        | 46 |

|      | Simulated and measured output voltage versus input current for the input log        |    |

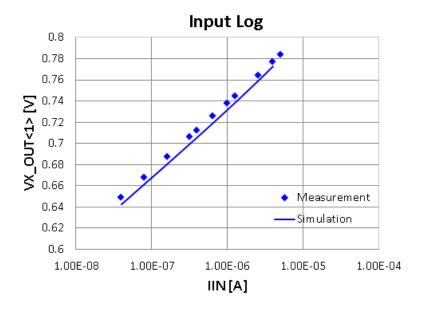

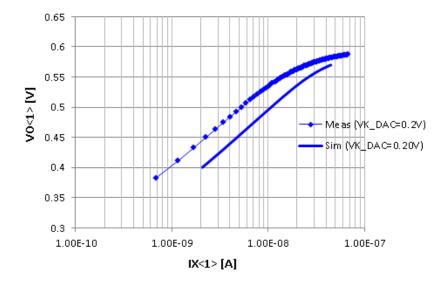

|      |                                                                                     | 48 |

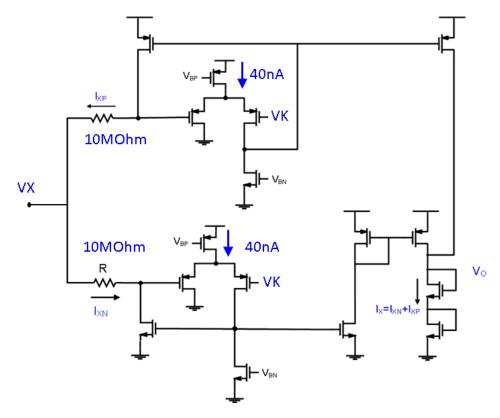

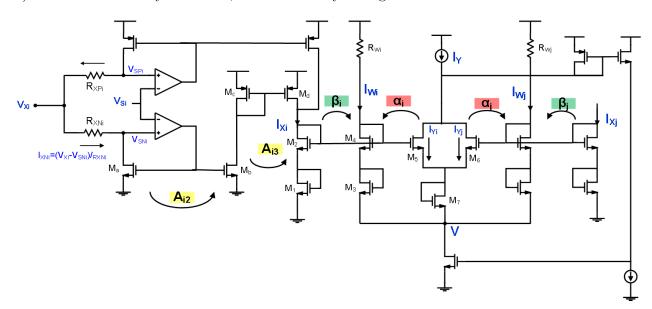

| 3.15 | Schematic of the VI converter and the second log converter                          | 48 |

| 3.16 | Implementation of the pseudo-resistor                                               | 50 |

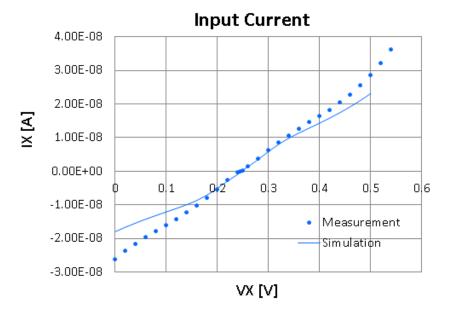

| 3.17 | Input current $I_X = I_{XN} + I_{XP}$ of the V-I converter $(V_K = 0.25 \text{ V})$ | 51 |

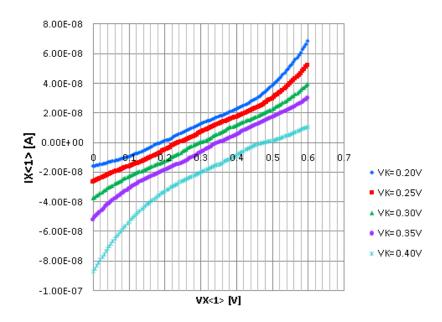

|      | $I_X$ versus $V_X$ at different $V_K$ 's                                            | 51 |

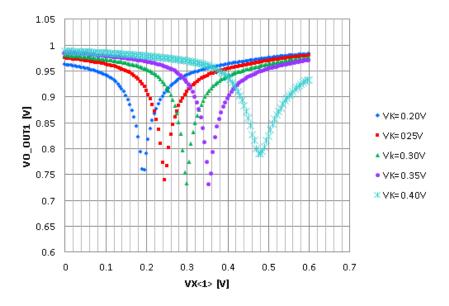

| 3.19 | $V_O$ versus $V_X$ at different $V_K$ 's                                            | 52 |

|      |                                                                                     | 52 |

|      |                                                                                     | 53 |

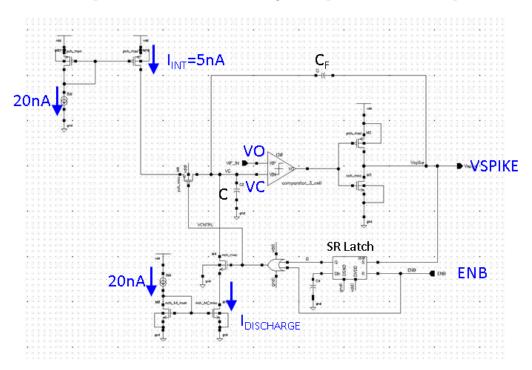

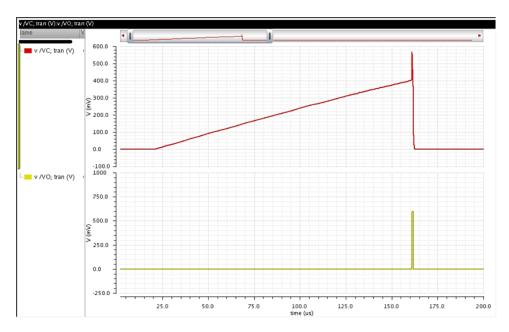

|      | Simulation of $V_C$ and $V_{SPIKE}$                                                 | 54 |

|      |                                                                                     | 55 |

|      | Monte Carlo simulation of the switching delay                                       | 56 |

| 3.25         | Measured output spike in response to the transition of the enable signal (ENB).                                           |

|--------------|---------------------------------------------------------------------------------------------------------------------------|

| 3.26         | System states in Phase I of learning                                                                                      |

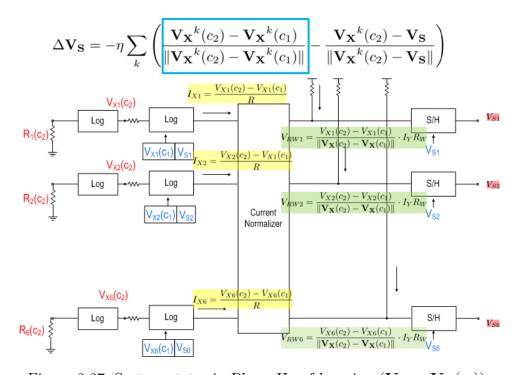

| 3.27         | System states in Phase IIa of learning $(\mathbf{V}_{\mathbf{K}} = \mathbf{V}_{\mathbf{X}}(c_1))$                         |

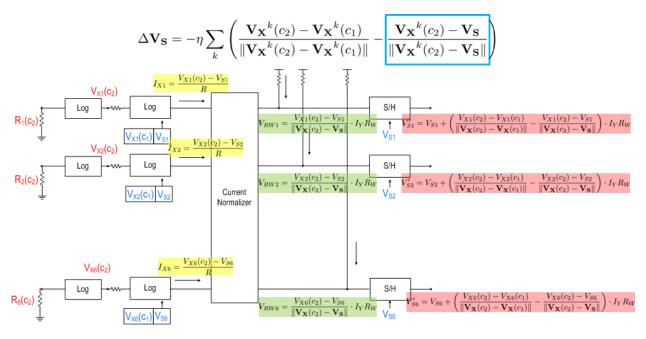

| 3.28         | System states in Phase IIb of learning $(V_K = V_S)$                                                                      |

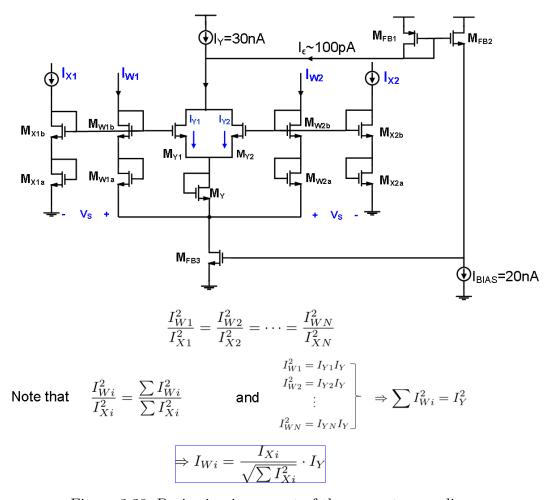

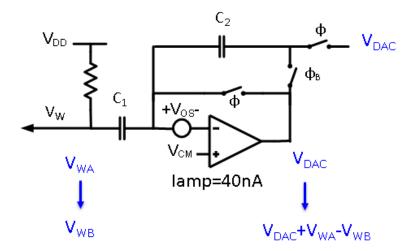

|              | Basic circuit concept of the current normalizer                                                                           |

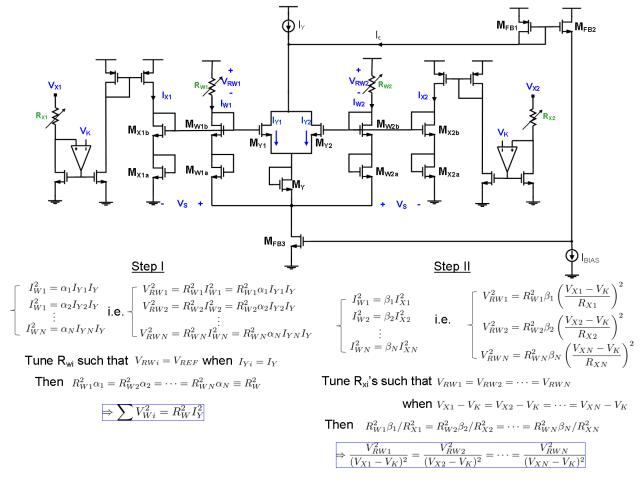

| 3.30         | The calibration procedure of the current normalizer                                                                       |

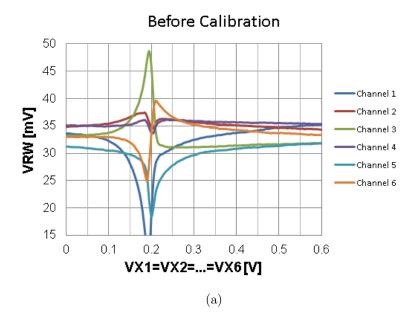

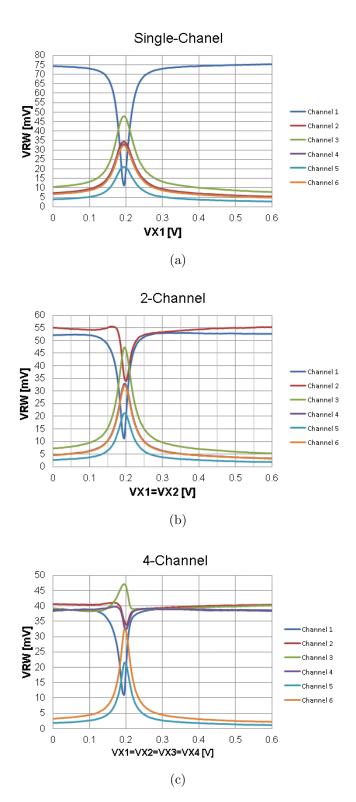

| 3.31         | Outputs voltages (a) before and (b) after calibration when all channels are swept                                         |

|              | from 0 to 0.6V with $V_K$ =0.2V                                                                                           |

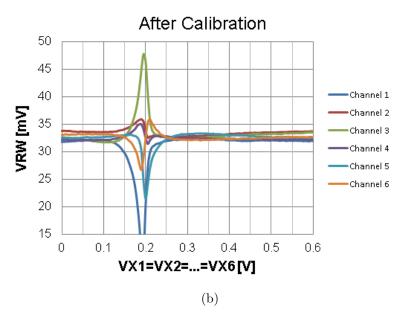

| 3.32         | Output voltages when the normalizer has only (a) 1 channel (b) 2 channels (c) 4                                           |

|              | channels on. The input of the off-channels are connected to $V_K$ =0.2V                                                   |

| 3.33         | Schematic of the sample-and-hold circuit                                                                                  |

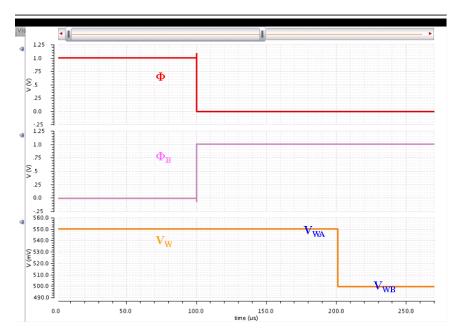

| 3.34         | Timing between the clock signal $\Phi$ and the input signal $V_W$                                                         |

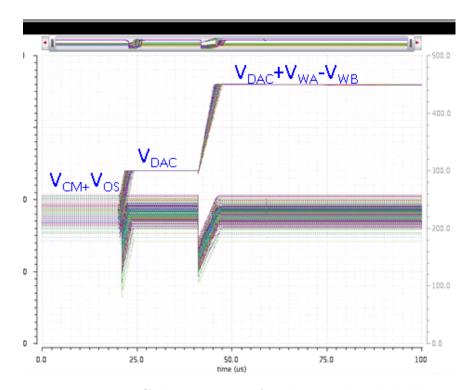

| 3.35         | Monte Carlo simulation for the sample-and-hold circuit                                                                    |

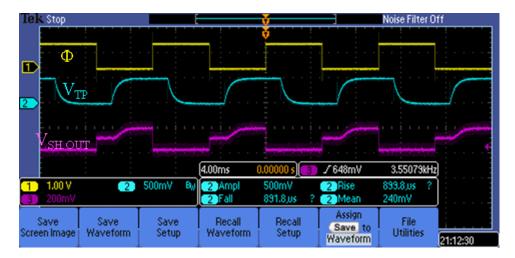

| 3.36         | Measured output of the sampled-and-hold circuit                                                                           |

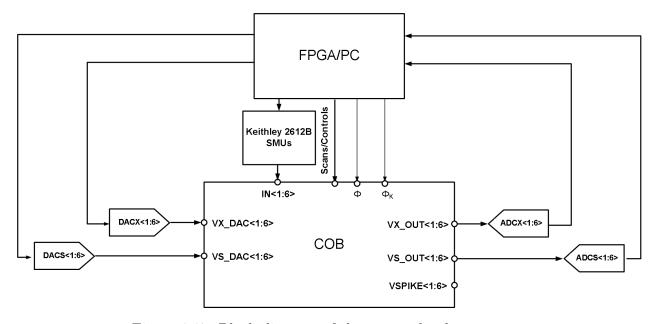

| 3.37         | Block diagram of the system-level test setup                                                                              |

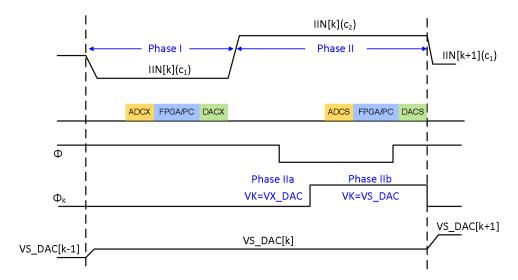

| 3.38         | Timing diagram for one learning trial                                                                                     |

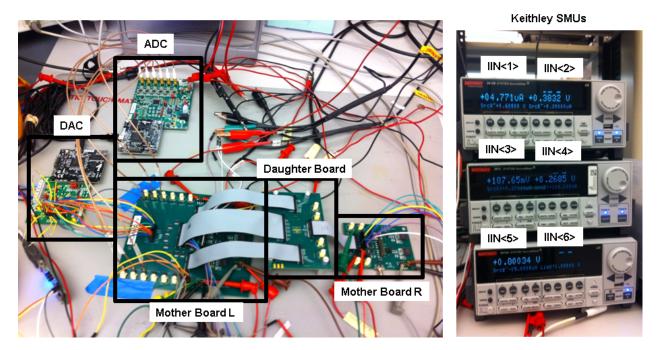

| 3.39         | The testing setup                                                                                                         |

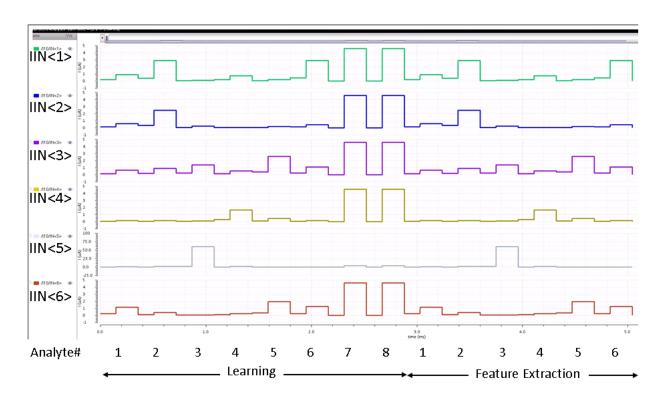

| 3.40         | The input current excitations                                                                                             |

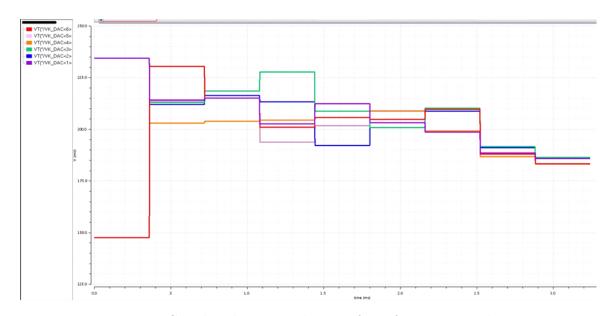

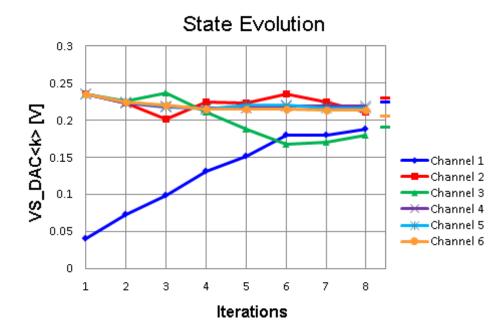

| 3.41         | Simulated state evolution of $V_S$ from an initial state                                                                  |

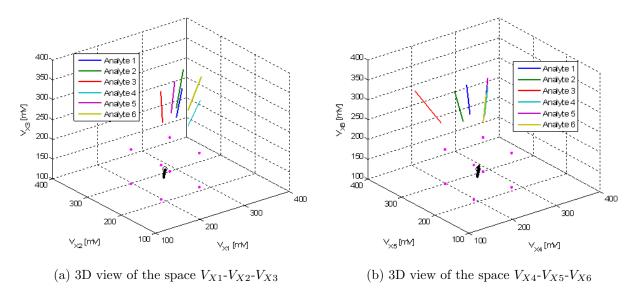

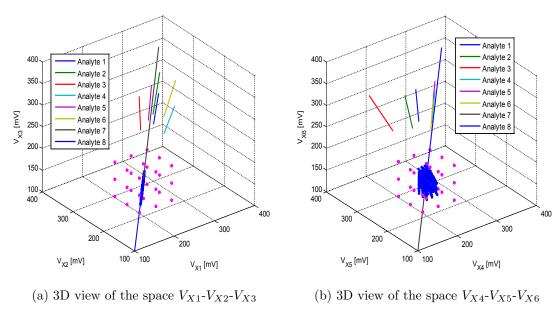

| 3.42         | Simulated final states (in black) from 64 initial states (in megenta) of $V_S$                                            |

| 3.43         | The tolerable range of final states $V_S$ with different number of sensors $N$                                            |

| 3.44         | Simulated worst-case final states (in blue) from 729 initial states (in megenta) of                                       |

|              | $\mathbf{V_S}$ considering device variations                                                                              |

| 3.45         | Measured state evolution from an initial state of $V_S$                                                                   |

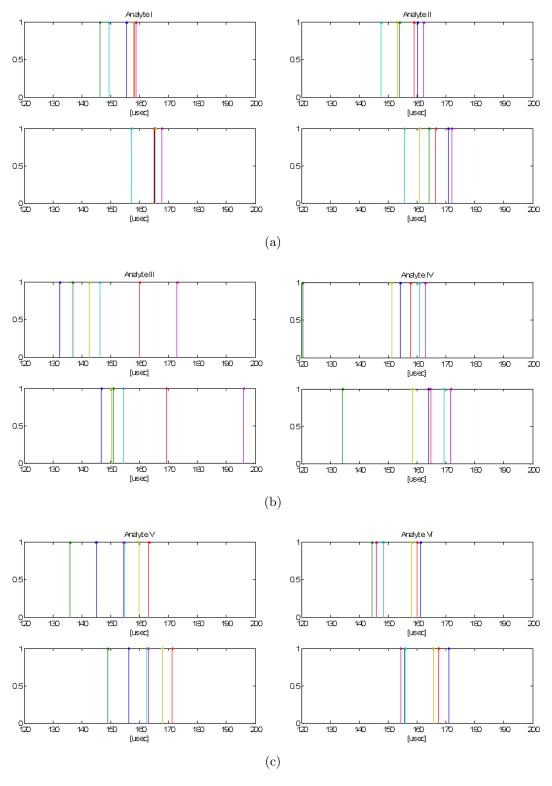

| 3.46         | Measured output spike patterns. Each analyte is presented at a low and a high                                             |

|              | concentration levels                                                                                                      |

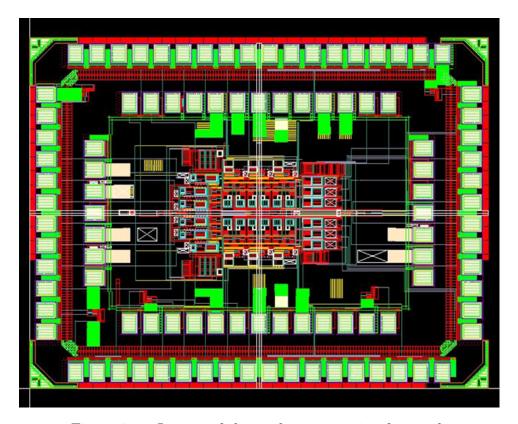

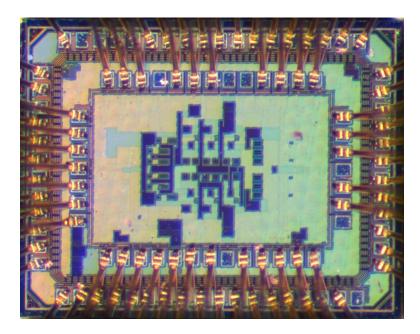

| 3.47         | Die photograph                                                                                                            |

| 4.1          | Normalized distance histogram of binary vectors in N-dimensional spaces                                                   |

| $4.1 \\ 4.2$ | · · · · · · · · · · · · · · · · · · ·                                                                                     |

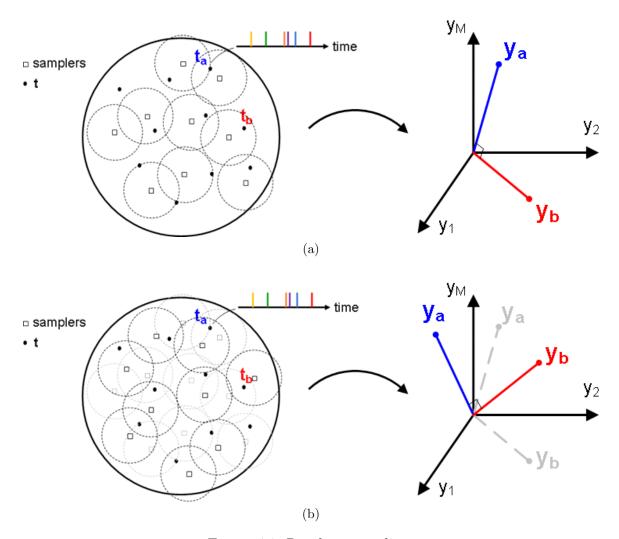

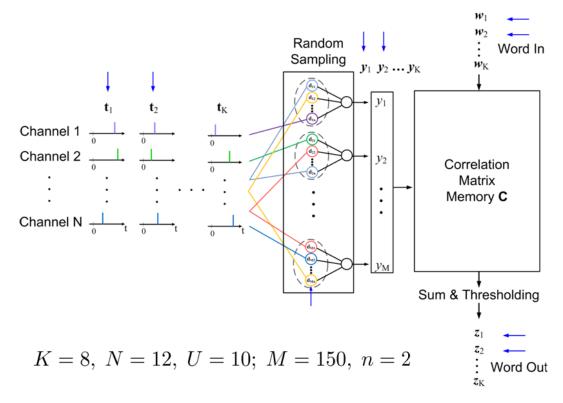

| 4.3          | Random sampling                                                                                                           |

| 4.3<br>4.4   | The coincidence detector outputs 1 when output spikes align                                                               |

| 4.4          | The geometric interpretation of the random spike sub-sampling. In this case,                                              |

| 4.0          | The geometric interpretation of the random spike sub-sampling. In this case, $N=3, M=3, \text{ and } n=2, \ldots, \ldots$ |

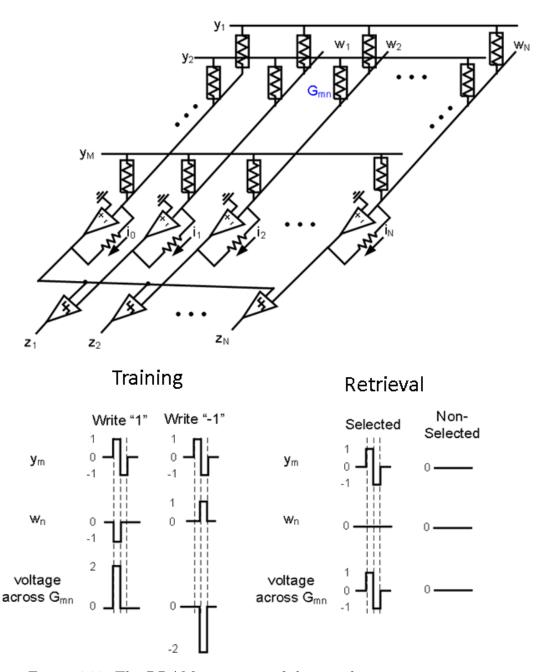

| 4.6          | Structure of the unnormalized correlation matrix memory                                                                   |

| 4.7          | Simulation setup of the spike pattern classifier.                                                                         |

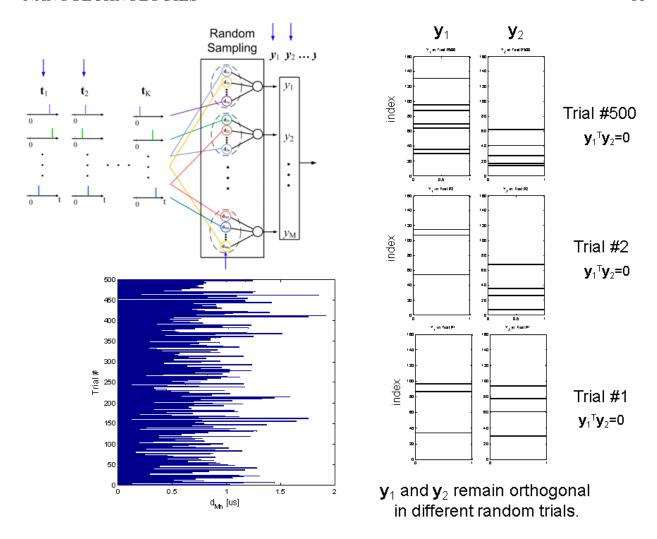

| 4.8          | 'Strobing' the randomized trials                                                                                          |

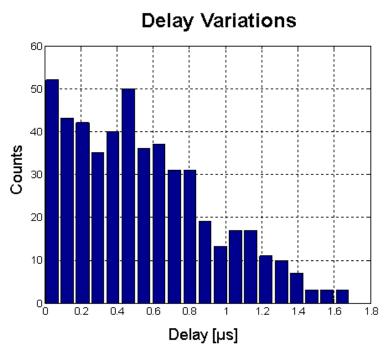

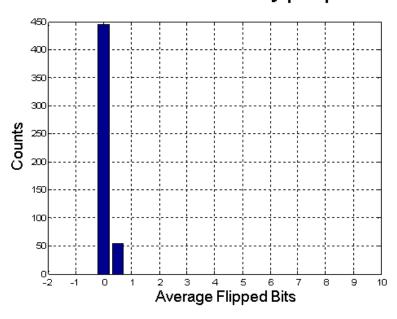

| 4.9          | Simulation results.                                                                                                       |

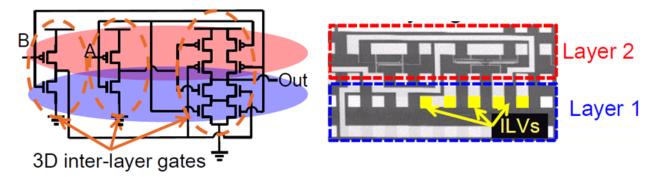

| 4.10         | Monolithic 3D integration of inter-layer and fully-complementary CNFET logic                                              |

| 1.10         | gates. Adapted from [24]                                                                                                  |

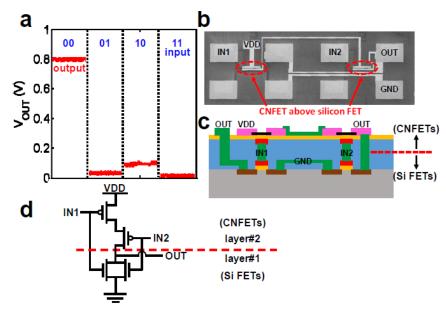

| <u> 4</u> 11 | Monolithic 3D CNFET/silicon FET NOR2 gate. Adapted from [25]                                                              |

| <b>4.11</b>  | mononome ob Ont bij sincon i bi norez gave. Adapted nom [20]                                                              |

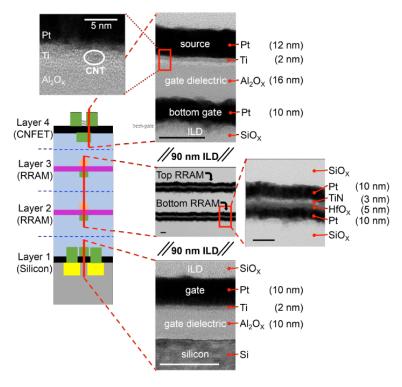

| 4.12                  | Transmission electron microscopy (TEM) images of four vertically stacked layers                                                                                             |     |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                       | in the 3D integration platform. Adapted from [26]                                                                                                                           | 89  |

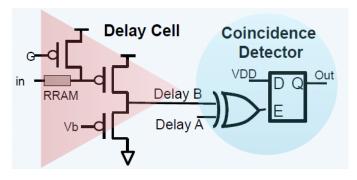

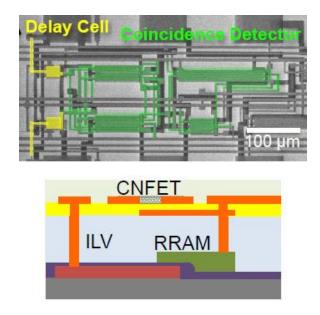

| 4.13                  | Implementation of the delay cell and the coincidence detector. Credit: Tony Wu.                                                                                             | 90  |

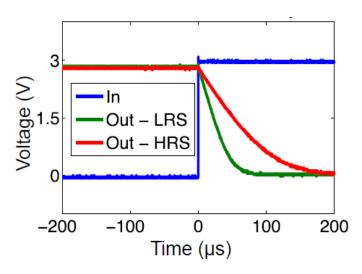

| 4.14                  | Measured output from the CNFET and RRAM delay cell. Credit: Tony Wu                                                                                                         | 91  |

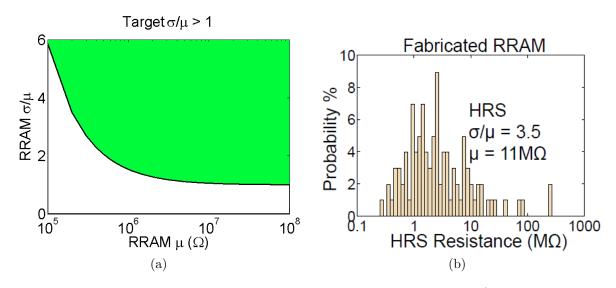

| 4.15                  | Required RRAM variation to achieve a delay variation of $\sigma/\mu > 1$ . Credit: Tony                                                                                     |     |

|                       | Wu                                                                                                                                                                          | 91  |

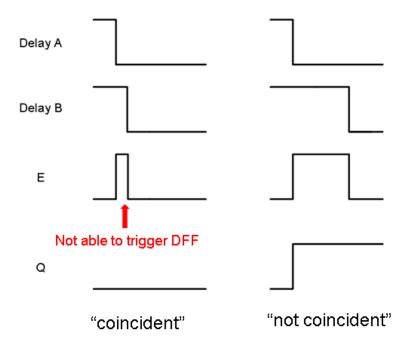

| 4.16                  | Operation of the coincidence detector                                                                                                                                       | 92  |

|                       | Cross-sectional view of the delay cell and the coincidence detector. Credit: Tony                                                                                           |     |

|                       | Wu                                                                                                                                                                          | 92  |

| 4.18                  | The 3D cross-point array architecture with RRAM devices at the junctions.                                                                                                   |     |

|                       | Adapted from [21]                                                                                                                                                           | 93  |

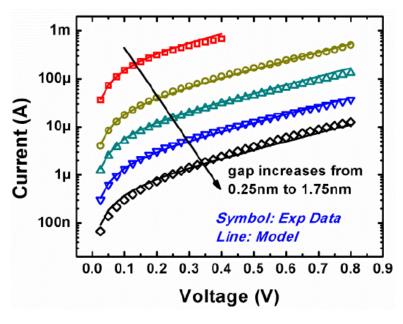

| 4 19                  | I-V fitting of multi-level resistance states by varying the gap tunneling distance.                                                                                         |     |

| 1.10                  | Adapted from [21]                                                                                                                                                           | 94  |

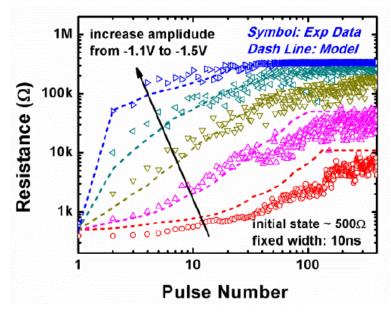

| 4 20                  | Measured and modeled gradual resistance change by varying the pulse amplitudes.                                                                                             | 0 1 |

| 1.20                  | Adapted from [21]                                                                                                                                                           | 94  |

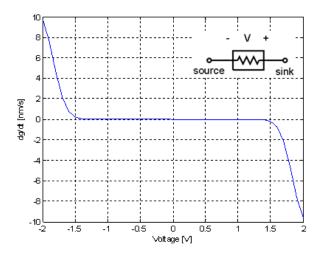

| 4 21                  | The change rate of the tunneling gap $dq/dt$ as a function of the applied voltage                                                                                           | 01  |

| 7.21                  | V between the source and sink terminal, for a gap size $g$ of 1nm                                                                                                           | 95  |

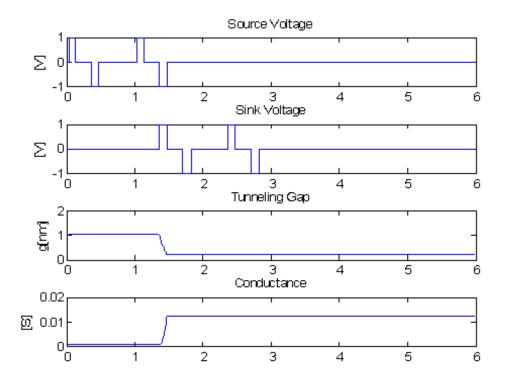

| 1 22                  | Pulsed programming of the RRAM resistance                                                                                                                                   | 96  |

|                       | The RRAM prototype of the correlation matrix memory                                                                                                                         | 97  |

|                       | Comparison of the operations required by the CMM and those performed by the                                                                                                 | 91  |

| 4.24                  | RRAM prototype                                                                                                                                                              | 99  |

|                       | Titte prototype.                                                                                                                                                            | 55  |

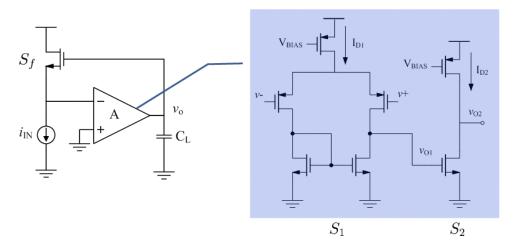

| A.1                   | Schematic of the logarithmic amplifier                                                                                                                                      | 104 |

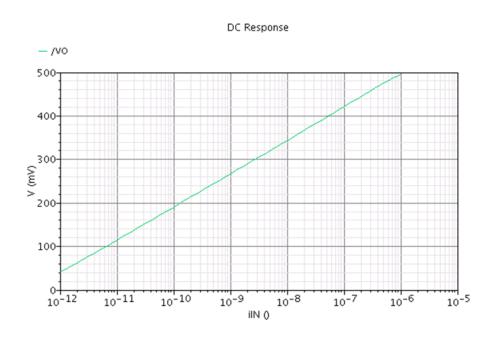

| A.2                   | DC response of the logarithmic amplifier: $V_o$ versus $\log i_{in}$                                                                                                        | 104 |

| A.3                   | Digital look-up table (LUT) for logarithmic transform                                                                                                                       | 106 |

| A.4                   | The worst case configurations for output low (left) and output high (right)                                                                                                 | 107 |

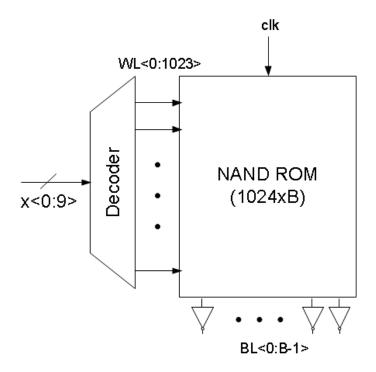

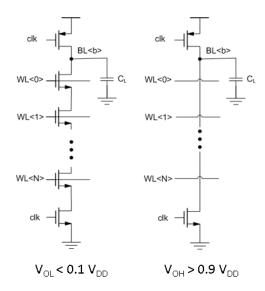

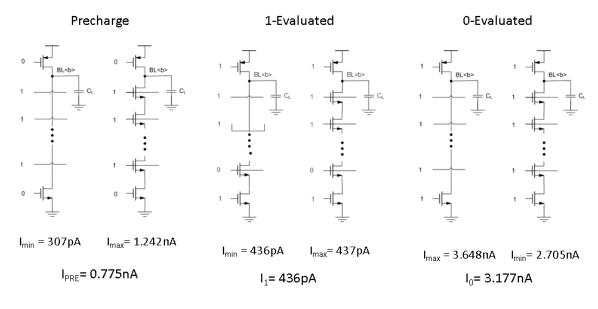

| A.5                   | Leakage estimation for the NAND-ROM                                                                                                                                         | 107 |

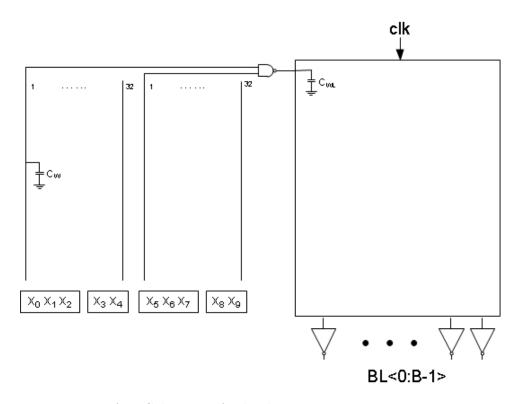

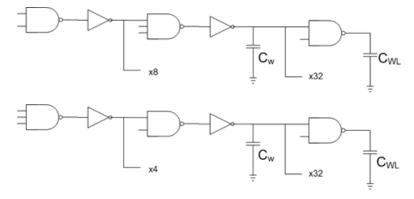

| A.6                   | Schematic for loading capacitance estimation                                                                                                                                | 108 |

| A.7                   | Different branchings in two-input and three-input decoders                                                                                                                  | 108 |

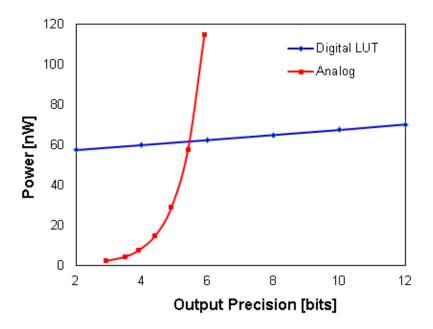

| A.8                   | The power-precision relationship of the analog and digital logarithmic transforms.                                                                                          | 110 |

|                       |                                                                                                                                                                             |     |

| B.1                   | Modeling the errors due to device mismatch for the computation in the learning                                                                                              |     |

|                       | phase                                                                                                                                                                       | 111 |

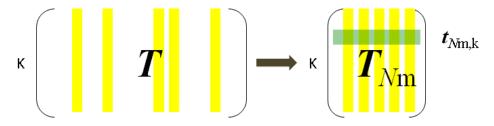

| C.1                   | Extracting columns of T according to the indices in M to form T                                                                                                             | 117 |

| C.1<br>C.2            | Extracting columns of <b>T</b> according to the indices in $N_m$ to form $\mathbf{T}_{N_M}$ The geometric interpretation of the random sampling groups. In this case, $N=3$ | 111 |

| $\bigcirc$ . $\angle$ |                                                                                                                                                                             | 118 |

|                       | and $n = 2$                                                                                                                                                                 | 119 |

# List of Tables

|     | Input referred channel precision at different input currents                    |     |

|-----|---------------------------------------------------------------------------------|-----|

| A.1 | Current consumption, output noise, and output voltage variation at different    |     |

|     | sizing factors                                                                  | 105 |

| A.2 | Simulated analog power and estimated digital power of the logarithmic transform |     |

|     | as functions of output precision                                                | 109 |

### Acknowledgments

Writing the acknoledgement reminds me of the time when I just arrived in Berkeley. Naive as I was, I didn't know what was ahead of me. I wouldn't be able to finish this thesis without the help and support from so many people along this long journey.

First, I would like to thank my research advisor, Prof. Jan Rabaey, for his constant support and guidance. From the time I was in a mist to find a way out, to the time I needed a lot of resources to get things done, he is always there and ready to help. His exceptional vision has shaped this thesis in a direction that I couldn't have imagined in the beginning. What has come out in the end is indeed a wonder to me.

I would also like to thank Prof. Bruno Olshausen, who led me into the field of neural computations. After taking his class, I made a significant progress. His passion has inspired me to dive into many interesting theories. That was the most enjoyable time in my PhD. I also have to thank Prof. Elad Alon and Prof. Kannan Ramchandran for serving in my qualifying/thesis committee.

During the early stage of my research, I worked with Prof. Jajeet Roychowdhury and his student Prateek Bhansali. It was them who brought this research to biologically inspired computations and the olfactory system. I value the time of our weekly genuine brainstorming for alternative computing paradigms. Around the same time, I had chances to work with Prof. David Macii from University of Trento and Prof. Lauri Koskinen from University of Turku. As a junior graduate student, I learned a lot from these two experienced researchers.

I have to thank William Mickelson and Allen Sussman from Prof. Alex Zettl's Lab to conduct gas sensor testings for us in their facilities. These sensors are tested with toxic gases. I couldn't imagine doing these experiments myself. With these measurement results, I was able to build models for gas sensors.

As for my first and last tapeout in Berkeley, it is an epic story. In the early phase, I received a lot of help from Ashkan Borna on block-level designs. Even he left Berkeley, he still spent time to discuss with me some design problems. In the later phase, I owe a lot of thanks to Jun-Chau Chien for unselfishly sharing his circuit design, tapeout, and testing experiences, and for brainstorming with me. I wouldn't be able to tapeout or test the chip successfully without his help. I would also like to thank Siva Thyagarajan for helping me on automating the simulation of large number of initial states. People whom I have consulted regarding the tapeout and testing also include Wen Li, Wenting Zhou, Yida Dhuan, Min-Han Hsieh, Nai-Chung Kuo, Tsung-Te Liu, Namsoeg Kim, Nathan Narevsky, Dan Yeager, and William Biederman. Thanks to Brian Richard for coordinating the tapeout shuttles and setting up the CAD tools. TSMC has kindly donated the silicon area. The working of this chip is largely attributed to their amazingly accurate models. I also thank Silitronics for performing the excellent wire bonding and SMT assembly, Wilson Chang for helping debug the scan chain, and Fred Burghardt for getting every test equipment ready.

In the later stage of my research, I had the chance to work with Prof. Subashih Mitra's and Prof. Philip Wong's groups from Stanford University and Pentti Kanerva from the Redwood

Neuroscience Institute. The sparkles from mixing these two fields contribute to Chapter 4 of this thesis and will be continued in the following years.

This research was funded by Giga-Scale Research Center (GSRC) and later by Systems On Nanoscale Information fabrics (SONIC) Center. Both are parts of SRC STARnet Centers, sponsored by MARCO and DARPA.

I spent most of my graduate student life in the Berkeley Wireless Research Center (BWRC) and received a lot of support from Jan's group, BWRC faculty, and students. Special thanks to the BWRC staffs who had/have been taking take of our computing systems and daily administrative stuffs: Kevin Zimmerman, Bira Coelho, James Dunn, Greg Pearson, Tom Boot, Deirdre McAuliffe-Bauer, Olivia Nolan, Leslie Nishiyama, Sarah Jordan, and Candy Corpus. I also enjoyed the time with some students/researchers who always stayed up late in BWRC together and thank them for walking to my car in the middle of the night: Nai-Chung Kuo, Min-Han Hsieh, Wilson Chang, Bo Zhao, and Angie Wong.

Within the department, I also gained a lot of help from the EECS faculty, students, and staffs. Special thanks to Ruth Gjerde, and Shirley Salanio: other than taking care of the administrative work of our degree program professionally and efficiently, their kindness and patience make international students feel like home.

During my internship in the Kilby Lab of Texas Instrument, my manager Ali Kiaei had provided me a lot of freedom and support to help me finish testing and the thesis. I couldn't ask for a better manager.

Outside of the school, I thank the supports from Heart Chan practitioners. Although I started practicing Heart Chan meditation when I was young, I didn't notice its benefits until I picked it up again few years ago. It has helped cultivate the inner strength, and helped clear my mind to deal with research problems.

Finally, I have to thank my family for bearing me so long. Even during my mother's toughest time, they never asked me to quit and always encouraged me to keep going. No words can express my gratitude and love to them. Thanks to my boyfriend Shih-Yu Yeh, and Shu-Jen Lu. They are my best listeners and always on my side.

Thank you all so much!

# Chapter 1

# Introduction

We are nearing the end of a long, historically unique, and profoundly transformative trend in the device miniaturization of information technology. As devices shrink to molecular dimensions, current practices and assumptions will lead to increasingly inefficient systems. Emerging nano-devices have been actively sought as successors to the silicon CMOS field-effect transistors (FETs). Although they are not immediately ready to replace silicon FETs, some of their unique properties have opened a new door for alternative computing paradigms that could build much more efficient systems. In the first part of this chapter, the motivation to explore new architectures is given. Next, the promise of neuro-inspired computing and its return are discussed. Finally, the research goal is stated and the organization of this dissertation is provided.

# 1.1 The Need for New Computing Models

## 1.1.1 The End of Moore's Law<sup>1</sup>

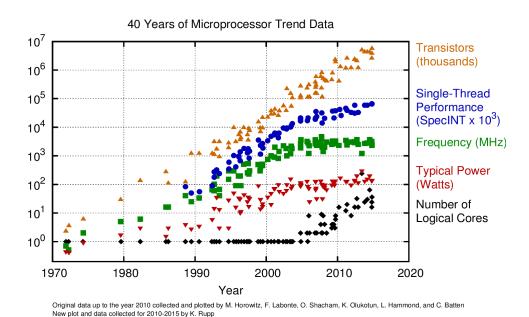

At the end of Moore's Law, we are getting diminishing gains from technology scaling. Figure 1.1 shows the microprocessor trend over the past 40 years [1]. Even if transistor count keeps rising, the clock frequency leveled off a decade ago - the power has reached the limit. Therefore, as the number of cores increases exponentially, the improvement of single-thread performance is only incremental.

What makes technology scaling worse is the increasing variability. As technology scales from 45 nm to 12 nm, the threshold variation increases by almost four times [2]. Although the threshold voltage (and supply voltage) has stopped scaling down, this will still cause severe reliability issues. To ensure reliable operation, the overhead from adding more and more operational margins will soon offset the intrinsic advantage of scaling.

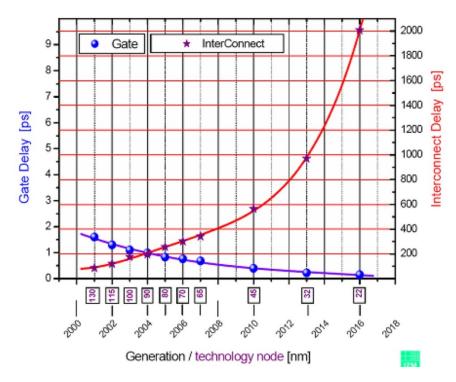

The other problem of scaling the planar CMOS technology is the on-chip interconnect, which has taken up 90% of volume in an IC chip today. Figure 1.2 shows the scaling trends

<sup>&</sup>lt;sup>1</sup>To be more accurate, it's actually Denard's Law that is ending.

Figure 1.1: Microprocessor trend over the past 40 years. Adapted from [1].

Figure 1.2: Scaling trends of gate and interconnect delays. Adapted from [3].

of gate and interconnect delays [3]. The interconnect RC delays are increasing exponentially with scaling. Therefore, interconnect is dominating device power consumption, performance and cost.

Eventually, the semiconductor industry will need a approach to supplement and extend CMOS beyond its fundamental scaling limit.

### 1.1.2 Emerging Nanotechnologies

### Fundamental Scaling Limits of Charge-Based Logic Devices

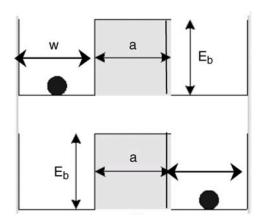

How much further can the present CMOS-based technology be scaled? A theoretical analysis [4], [5] based on a two-well model for the source-gate-drain structure of an FET (Figure 1.3) derived the minimum barrier width  $a_{min}$  and height  $E_{bmin}$  such that a electron is either in the drain or source with 50% probability by thermionic emission or quantum mechanical tunneling. It is shown that  $a_{min}=1.5$  nm and  $E_{bmin}=kTln2$ , where k is the Boltzmann constant, and T is the absolute temperature. An additional constraint requiring minimization of energy dissipated in changing potential well sets  $a_{min}=5$  nm.

Figure 1.3: Idealized model of the potential barrier separating the source drain potential wells, where w is the well width, a is the barrier width, and  $E_b$  is the barrier energy. Adapted from [5].

Since high-volume manufacturing technology for the 16 nm node is currently being ramped to full production, the 5 nm generation may go into manufacturing in 7 years or in 2020. Consequently, scaling of CMOS-based information technology will face fundamental limits within the next 5-7 years or by 2020. This determines a need to have any new technology for extending CMOS in place by that time.

#### **Emerging Logic Devices**

For emerging logic devices, the quantitative assessment and benchmark by ITRS [6] and investigations between 2011-2013 [7] suggest that substantial progress has been made in

demonstrating devices beyond conventional CMOS. Specifically, a bifurcation is observed that some devices appear to hold promise for higher speed operation than CMOS (e.g. Mott FET, carbon nanotube FET (CNFET)), while others might provide a route to lower power consumption (e.g. nanowire FET, negative capacitance ferroelectric). For example, an ideal CNFET inverter at 32-nm can have 13X of improvement in Energy-Delay-Product compared to a 32-nm CMOS inverter [8]. At 22-nm and 16-nm nodes, the advantage over silicon CMOS can improve to 20X [9]. This is due primarily to near ballistic electrical transport in CNTs. However, each emerging device still has challenges to overcome before any of them can be considered as an "heir" to the silicon CMOS FET. In CNFET technology, for example, the challenges remain controlling the percentage of metallic CNTs grown or deposited on substrate, CNT alignment and positioning, getting high density aligned CNTs [10], and the difficulty of addressing individual CNTs with source, drain, and gate contacts within a dense, interconnected circuit [7].

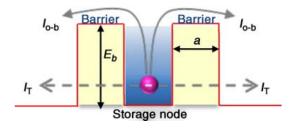

### Fundamental Scaling Limit of Charge-based Memory

Current memory technologies (DRAM, SRAM, and flash) are based on storing electron charges in a storage node. States 0 and 1 are created by the presence or absence of electrons in the charge storage node. A theoretical analysis based on a barrier model (Figure 1.4) [11] shows that the minimum barrier height  $E_{bmin}$  to suppress thermionic emission and the minimum barrier width  $a_{min}$  to suppress tunneling are  $E_{bmin} = 1.42$  eV, and  $a_{min} \approx 5$  nm, for a retention time of 10 years<sup>2</sup>.

Figure 1.4: Barrier model of charge-based memory. Adapted from [11].

However, both DRAM and flash cannot reach this theoretical limit. From the Space-Action metric [12], DRAM achieves optimum performance in the 40-50 nm regime. As the size of the DRAM approaches the scaling limit, the access time will dramatically increase due to the serial resistance of the cell capacitor. Also, there is still no known manufacturable solution for DRAM beyond the 20 nm node [13].

The scalability of flash memory is limited by the gate stack - practical minimum size of a floating gate cell is roughly 10 nm. As of the time of this writing, production NAND

<sup>&</sup>lt;sup>2</sup>This is for non-volatile memories. For smaller retention times, e.g., 50-100 ms, typical for DRAM,  $E_{bmin}$  and  $a_{min}$  can be smaller.

flash has been scaled to a critical dimension of 16 nm [14] and 3D Vertical NAND [15, 16] has entered commercial production. However, endurance and rention have become strongly degraded as flash tunnel oxides become thinner, leading to extensive error correction code (ECC) schemes and substantial redundant storage requirements [17].

In contrast, SRAM scalability has no obvious hard limiting factor to prevent it from reaching the theoretical limit [11]. However, a significant challenge for SRAM scaling is the increasing variability that will result in the failure of the cell. Moreover, minimum cell area cannot be maintained below 45 nm, if the minimum supply voltage and data retention voltage are to be minimized [18].

#### **Emerging Memory Devices**

According to the taxonomy of memory technologies from ITRS [13], emerging memory devices include ferroelectric memory and resistance switching memories (RRAM). Among RRAM, Redox RAM (ReRAM) technologies have advanced rapidly for the past few years. Overall ReRAM assessment is similar or better than existing CMOS-based nonvolatile memories [19]. This is due to its promising scalability, dense integration, and CMOS-compatibility. Some recent breakthroughs in ReRAM significantly enhanced its perceived potential, for example, a 32-Gb multi-layer NAND-scale array demonstration [20].

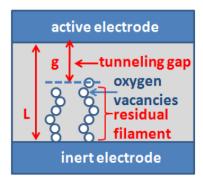

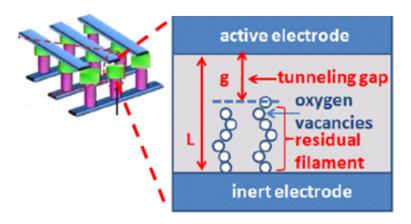

Scalability below 10 nm is predicted for all emerging memories. For ReRAM, it's operation and switching relies on the conductive filament in the metal-oxide, as shown in Figure 1.5 [21]. Since the size of the conductive filament is less than 10 nm, in principle it can scale down to sub-10 nm regime [22]. It's also reasonable to conclude that other emerging memories that rely on filamentary switching will scale to the same dimensions as standard filamentary ReRAM.

Figure 1.5: Conductive filament in the metal-oxide RRAM. Adapted from [21].

Except for ferroelectric memory, all of the emerging memory technologies are two terminal resistance switching devices. This makes them amenable to an efficient crossbar configuration. This is the most dense possible configuration, as each individual device only occupies an area of  $4F^2$  [17], where F is the minimum feature size of the device. The other advantage of

ReRAM is that the fabrication temperature is CMOS back-end-of-the-line (BEOL) process compatible and no special material is required.

Generally, all emerging memories are scored low in the "operational reliability" category [17]. This is due to their variability in switching between the low-resistance state (LRS) and the high-resistance state (HRS) and also the lack of long term reliability.

However, the memresistive behavior [23] exhibited in the emerging memories have enabled efficient implementation of synaptic function that is very difficult to realize by devices in conventional technologies. This has enabled alternative computing paradigms that could be much more efficient than today's von Neumann-based systems.

### The 3D Nano Promises and Challenges

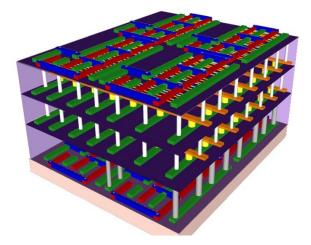

As mentioned previously, on a deeply-scaled CMOS chip, an enormous amount of power and performance compromise are wasted on the interconnects. The greatest barrier holding today's processors from reaching higher computing speeds lies not in transistors but in the communication with memory. However, recent breakthroughs in monolithic 3D integration have demonstrated a visible new path ahead: from 3D integration of CNFET logics [24], 3D integration of CNFETs with silicon CMOS logics [25], to the 3D integration of CNFET/silicon CMOS logic and ReRAM memory [26]. The most important breakthrough is to interweave memory devices with computing devices. Figure 1.6 shows a four-layer prototype built by Stanford researchers. The bottom and top layers are logic transistors. Sandwiched between them are two layers of memory. The use of inter-layer vias (ILVs) to connect between various layer allows massive vertical interconnect density [26], maximizing the benefits of 3D integration. This has vastly reduced the "commuting time" between the processor and the memory, and will make the a chip much faster.

Figure 1.6: Monolithic 3D integration of logic and memory devices. Credit: M. Shulaker.

Although the 3D integration technology offers great density, the large variabilities and error/failure rates of the emerging logic and memory devices pose a great challenge for building a reliable system. Moreover, to reduce energy per operation and to minimize the heat flux, circuits built from such devices essentially must operate in a low signal-to-noise ratio (SNR) regime. A system requiring high SNR operation will simply fail, or will need overly designed circuits with large operational margins to work - this option will no longer be affordable as the system size scales up. Therefore, before device research comes up with solutions for making better and more reliable devices, we may need to seek solutions at the architectural-level: could there be an alternative computing model that can perform reliable computation efficiently with large number of devices exhibiting significant variations and failures? This has therefore led to a search for new computing models.

# 1.2 The Search for New Computing Models

Figure 1.7 illustrates the concept of traditional and alternative computing paradigms. In the traditional platform, the information processing architecture/algorithms presume its underlying computations are executed deterministically and reliably, whereas the devices today exhibit large variations. Therefore, the system level reliability is usually achieved by circuit/logic level reliability. As mentioned above, the cost of make each computing element precise and reliable will soon become unaffordable and offset the intrinsic advantages of scaled technologies. Therefore, the mapping is very inefficient.

In the alternative paradigms, we are looking for architecture/algorithms that expect the statistical natures in the computing elements, so that reliable computation can be achieved without the devices needing to behave precisely and reliably. Hence the circuits do not need to be over-designed and can be designed in the efficient regime. Therefore, the mapping is inherent efficient.

Figure 1.7: Traditional and alternative computing paradigms.

In fact, the natural world represents a gold mine of problem solving algorithms, yet this potential is largely untapped. Collective behaviors that operate without central control to regulate activity and growth are ubiquitous in nature. For example, neurons act collectively

as networks to produce sensations, cognition and motions, while each individual neuron is prone to variations and failure. Many animal groups regulate their movement without a leader, such as bird flocks or fish schools. Social insects live in colonies, which forage, maintain their nests, and reproduce based on simple local cues and interactions. It is shown that three environmental constrains might have shaped the nature's evolution of collective behavior [27]: the patchiness of the resource, the operating costs of maintaining the interaction network that produces collective behavior, and the threat of rupture of the network.

Since a large network of today's nano-devices is very similar to a network of biological organisms, future nano technologies may need to be used in computing paradigms like those in nature, where functions emerge as the collective behavior of the devices interacting locally and does not require each individual to be precise and reliable. Among natural computations, neural computation is one of the most sophisticated and advanced. While it is not considered general purpose, the brain performs functions such as feature extraction, recognition, learning, and decision making very well. Therefore, neuro-inspired computing may lead to cheap and efficient processors for cognitive applications.

# 1.3 The Return of Neuro-Inspired Computing

## 1.3.1 The Recurring Waves of Neuro-Inspired Computing

Speaking of neuro-isnpired computing, it's not a new term. It has seen few times of booms and winters over the past several decades.

The first wave occurred between the 40's and the 60's. It began with McCullogh-Pitts' model (1943), Hebbian learning (1949), and then Frank Rosenblatt's perceptron (1958). Since a single-layer of perceptrons was shown to have severe limitations for solving complex problems in Minskey and Papert's book *Perceptrons* (1969), all the research funds was diverted to the field later called artificial intelligence (AI). Hereafter, virtually no research at all was done in connectionism for 10 years.

The second wave occurred between the 80's and the 90's. In 1982, John Hopfield introduced a form of neural network that can learn and retrieve patterns in a completely new way. Around the same time, David Rumelhard proposed a new method called back-propagation to train multi-layer perceptrons. These two discoveries revived the field of connectionism. During this period, Carver Mead recognized that neuro-inspired computing could be promising for building more efficient computing systems and had promoted neuromorphic systems [28]. However, the technology at that time was not able to make it an attractive alternative. There was no efficient and simple way to implement adaptive function either, making it difficult to build large learning networks.

The third wave is happening right now. It is because we are getting better understanding of some neural functions. Between late 80s and early this century, there have been many important theories developed, such as the Boltzman machine [29] (which later evolved into deep learning), Sparse Distributed Memory (SDM) [30] (later generalized to hyperdimen-

sional computing [31]), and the Sparse Coding [32], etc. Also, the success of deep learning (e.g. Google Brain) has triggered a surge of efforts to build machines that can process data in much the same way the brain does [33]. In addition, the emerging nanotechnologies have enabled some neural functions and architectures that were previously very difficult or impossible to be built. Therefore, if anyone can figure out how the brain makes use of noisy neurons to compute and apply it to the emerging technologies, the information technology could be revolutionized. These are why there is significant investment today in combining the research of computational neuroscience and engineering.

## 1.3.2 Features of Neural Computation

The brain is a wonder of millions of years of evolution. Here are some of the important features of neural computation.

- Brains are the most energy-efficient systems in the world: The human brain performs more than 10<sup>16</sup> FLOPS (floating-point operations per second) with only 20 W of power consumption [34]. This is 2-3 orders of magnitude more efficient than today's most energy-efficient silicon equivalence.

- Robustness in the presence of component defects and variations: For example, human can have complete visual color perception with incomplete deployment of color receptors [35]. Also even though neural responses are highly variable (with Fano factor  $\sigma/\mu \approx 1$  [36]), the neural system can still perform reliable functions.

- Amazing performance with mediocre components: The neural systems do not have precise and excellent neural components. However, the use of collective computation by low to moderate-precision units can actually perform more complex and precise computations. For example, the auditory system can tell difference of time arrival within 10  $\mu$ s with cells having time constant of 1 ms [34]. The olfactory system can discriminate  $10^4$ - $10^5$  of odors with slight differences of chemical structures using olfactory receptors having broad reception ranges [37].

- Seamless interaction of the analog world: Each sensory modality uses specific kind of sensor to sense analog information from the world. The useful information or features are extracted using analog processing. It was point out that the use of physical functions in analog computation is the key to its energy efficiency [28].

- 3D integration of memory and computation: Unlike a digital microprocessor where there is a centralized computing unit and a separate memory unit, the computation and memory are intimately integrated and distributed in the brain. Therefore, there is no 'von Neumann bottleneck' as in a microprocessor. The brain has closely coupled its algorithms with the implementation [38], unlike the standard engineering practices where algorithm design is mostly independent from how it will be implemented. Moreover, the fantastic 3D interconnect technology allows a fan-in and fan-out of 6,000

connections per neuron [34] compared to roughly 6 of a logic gate in the microprocessor. These might also be why the brain has achieved unparallel performances.

### 1.3.3 Opportunities of Neuro-Inspired Computing

Given the features of neural computation and the properties of current and emerging technologies, we can summarize the opportunities of neuro-inspired computing as follows.

- To exploit the properties in neural computing, including robustness to variations/failures and efficient low resolution processing through massively parallel computing, and to ensure efficient operation in the most informative regions of the input statistics through adaptation and feedback.

- To efficiently realize some hard cognitive problems, such as artificial olfaction, vision, classification, detection, and decision making, etc.

- To leverage the opportunity while mitigating the challenges in the emerging nanotechnologies. For example, hyper-dimensional computing paradigm [31] that is very difficult or even impossible in a 2D platform can be efficiently implemented in a 3D logic and memory integration platform while be very robust to device variations and failures.

## 1.4 Research Goal

The research goal of this thesis work is to develop an efficient neuro-inspired implementation for feature extraction and classification. As a demonstration, we have chosen the application to be artificial olfaction. First, it's because gas sensor signals are considered static and easier to deal with, compared with audio and video signals. Second, since so far there are very rare research efforts or commercial products of integrated signal processing front end for gas sensor arrays, we believe we can have good contributions to this field. Third, other than traditional applications in explosive detection, in food or pharmaceutical industry, it is predicted that there is an increasing market of integrated gas sensors in smart phones or handsets for health monitoring (e.g. breath analysis) and environmental monitoring [39]. Therefore, an integrated artificial olfactory system may find its application soon.

## 1.5 Thesis Outline

The thesis is organized as follows.

Chapter 2 provides an overview of the information processing in the sensory pathway, with an emphasis on the olfactory system. Based on the understanding of the biological sensory pathway, the architecture for the artificial olfactory system is proposed, which consists of an analog feature extraction front end and a spike pattern classifier. Finally an information-theoretic framework is developed to evaluate the energy efficiency of signal representations and to systematically optimize a design at both the architectural and circuit level.

Chapter 3 describes the design of the analog gas sensing front end. The analog front end implements a novel trainable feature extraction algorithm for metal-oxide gas sensor arrays. The algorithm extracts one composite feature of all analytes and transforms the sensor responses into concentration-invariant spike patterns. This composite feature is extracted by performing the gradient decent algorithm during training. This 6-channel analog frond end consumes 150nW/channel in the training mode, and 250nW/channel in the recognition mode.

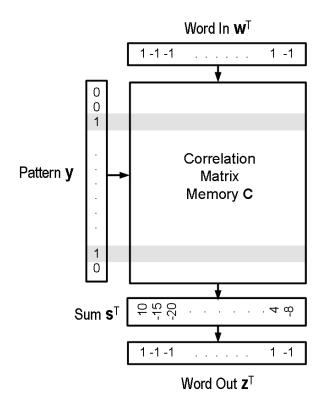

Chapter 4 describes the spike pattern classifier consisting of a sparse transformation of the spike patterns and a cortical memory model. The transformation is based on a random sampling scheme that can be efficiently performed with circuits exhibiting large parametric variations. Moreover, sparse representations allow fast and robust pattern storage and retrieval with associative memories such as the correlation matrix memory. As mentioned in previous sections, hyper-dimensional computing architectures like this may be a perfect match to the emerging nanotechnologies. We show how this classifier can be densely and efficiently implemented in a 3-D CNFET-RRAM technology.

Chapter 5 concludes by summrizing the key contributions and suggesting directions of future research.

# Chapter 2

# System Overview

In this chapter, an overview on the biological olfactory pathway is given, including the sensing mechanism in the olfactory epithelium (OE), the combinatorial coding in the olfactory bulb (OB), and the overcomplete representation in the primary olfactory cortex (OC). Next, a signal processing architecture inspired by the olfactory pathway is proposed for artificial olfaction. Finally, an information-theoretic framework and a joint architectural and circuit level optimization methodology are provided to systematically determine the optimum architecture for efficiency.

# 2.1 The Biological Olfactory Pathway

Probably the oldest sensory system in the nature, the olfactory system concerns the sense of smell. Through the sense of smell, humans and other mammals can perceive a vast number and variety of chemicals in the external world. It is estimated that humans can sense  $10^4$  to  $10^5$  chemicals as distinct odors. Even a slight change in the chemical structure of an odorant can change its perceived odor. How do mammals detect so many different environmental chemicals? And how does the brain translate those chemicals into diverse odor perceptions?

Unlike visual and auditory systems, the mechanisms of mammalian olfaction remained a mystery until early this century. The discovery of the olfactory receptors and the combinatorial coding in the mammalian olfactory system by Richard Axel and Linda Buck was awarded the Nobel Prize in 2004. The first half of this section is primarily from the Nobel Lecture on their discovery [37]. The second half describes the computational principle behind the sparse and overcomplete representations in the primary cortex [32], [40], [41] and how such representation might be subsequently processed.

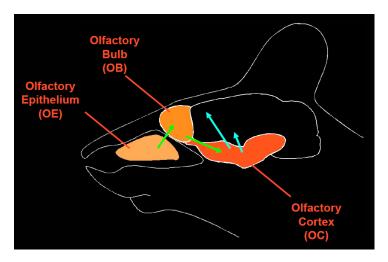

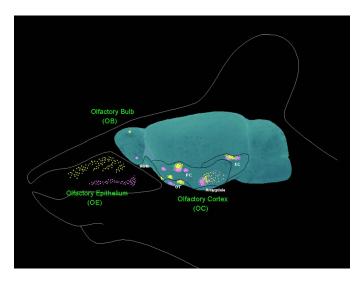

The signal processing in the olfactory system can be roughly divided into three stages, as shown in Figure 2.1. The first stage is in the **olfactory epithelium (OE)**, where odorants are initially detected by millions of olfactory sensory neurons. These neurons then transmit signals to the **olfactory bulb (OB)** of the brain, which then relays those signals to the **olfactory cortex (OC)**. From there, olfactory information is sent to a number of other

brain areas, including higher cortical areas thought to be involved in odor discrimination, and deep limbic areas thought to mediate emotional and physiological effects of odors.

Figure 2.1: The olfactory pathway. Adapted from [37].

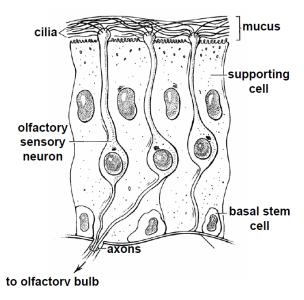

## 2.1.1 Sensing in the Olfactory Epithelium

The olfactory epithelium contains millions of *olfactory sensory neurons*, as shown in Figure 2.2. At the surface of the epithelium, each neuron extends cilia into the nasal lumen, allowing it to be in contact with odorants dissolved in the nasal mucus. Each neuron communicates with the brain via a single axon extending to the olfactory bulb.

Figure 2.2: Structure of the olfactory epithelium. Adapted from [37].

#### Olfactory Receptors

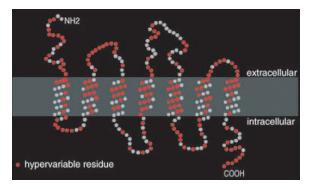

How do these neurons detect odorants? In Axel and Buck's experiments, they discovered a family of G protein-coupled receptors (GPCRs) that are expressed exclusively by olfatory sensory neurons. These receptors, though related, vary extensively in their amino acid sequences. This is how the receptors interact with odorant with different structures. Figure 2.3 shows the structure of one olfactory receptor. Odorants can bind to the extracellular part of the receptor and activate the G protein, which will initiate subsequent messengers and trigger a change of gene expression within the nucleus.

Figure 2.3: Topology of an odor receptor in the membrane. Individual amino acid residues are indicated by balls. Red balls indicate residues that vary extensively among odor receptors. Adapted from [37].

Later studies indicate that humans have about 350 different olfactory receptors and mice have about 1000. Each neuron can express only one olfactory receptor gene, and each receptor gene is expressed in several thousands of neurons. Neurons expressing the same receptor gene are distributed within one zone in the olfactory epithelium, as shown in Figure 2.4.

Figure 2.4: Expression zones in the olfactory epithelium. Zones expressing different receptor genes are marked in different colors. Adapted from [37].

### The Combinatorial Coding

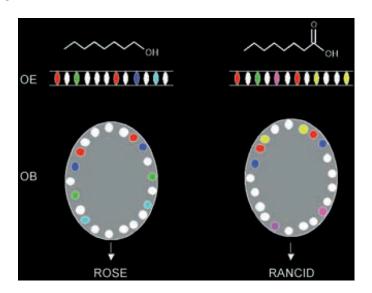

How do olfactory receptors respond to odorants? By examing the responses of different receptors to different odorants, it is concluded that odor receptors are used combinatorially to encode odor identities. As conceptually illustrated in Figure 2.5, each olfactory receptor can detect multiple odorants, and each odorant can activate multiple different receptors. It was shown that such combinatorial code can actually maximize the mutual information [42].

Figure 2.5: Combinatorial receptor codes for odors. Adapted from [37].

## 2.1.2 Signal Integration in the Olfactory Bulb

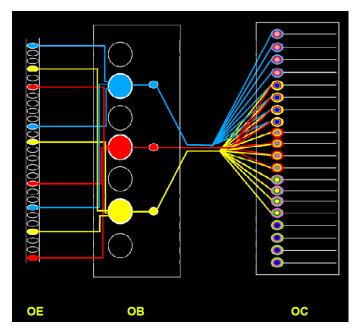

How does the brain translate an odorant's combinatorial receptor code into a perception? Each olfactory sensory neuron in the olfactory epithelium sends a single axon to a spherical structure called glomerulus in the olfactory bulb. Since there are only 2000 glomeruli while there are 10 million olfactory sensory neurons, there is a massive convergence in the olfactory bulb. Axons of thousands of olfactory sensory neurons expressing the same olfactory receptor converge in only 2-4 glomeruli dedicated to the same olfactory receptor, as shown in Figure 3.42. This allows a high degree of signal integration.

This further indicates that sensory information that is broadly organized and interspersed in different zones in the nose is transformed into a stereotyped sensory map in the bulb. Remarkably, this map is virtually identical in different individuals. This bulb map is likely to be important for stimulation of odor memories. Sensory neurons in the epithelium are

short lived and are continuously replaced. However, the bulb map remains constant over time, assuring odorants can elicit distant memories.

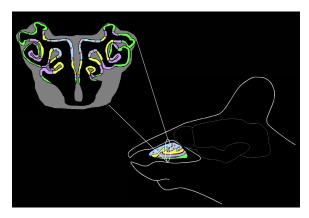

Figure 2.6: Convergence of signals from the OE to the OB. Adapted from [37].

Therefore, in the nose the code for an odor is a dispersed ensemble of neurons, each expressing one olfactory receptor. In the bulb, the code is a specific combination of glomeruli and have a similar spatial arrangement among different individuals. This is illustrated with two examples in Figure 2.7.

Figure 2.7: Odor coding in the OE and the OB. Adapted from [37].

## 2.1.3 Dimensionality Exampsion in the Olfactory Cortex

What happens to this information at higher levels of the brain to ultimately generate odor perceptions?

Mitral cells in the bulb relays the signals from glomeruli to the olfactory cortex. The olfactory cortex is composed of a number of distinct anatomical areas. The largest area is called the piriform cortex (PC). In the 80's, it was shown that a tracer placed in one small region of this cortex would back-label mitral cells in many parts of the bulb [43]. This indicates that the organization of sensory information in the olfactory bulb could not be recapitualted in the cortex. How the information is organized in the olfactory cortex was a mystery.

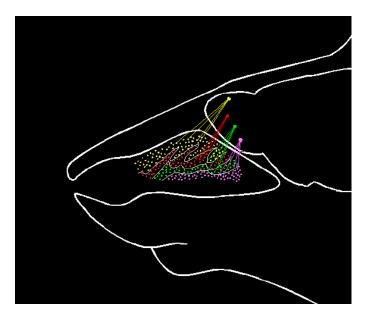

By developing a genetic method to trace neural circuits, Buck's experiments found that signals from one type of receptor in the bulb project to multiple areas in the olfactory cortex, with a divergence ratio about 1:20 to 1:30, as shown in Figure 2.8.

Figure 2.8: Stereotyped map in the olfactory cortex. Signals of the same type of olfactory receptor (marked with the same color) project to multiple spots in the cortex. Adapted from [37].

This map in the cortex is markedly different: Signals from different receptors are spatially segregated in different glomeruli in the OE and OB. In contrast, different receptor signals overlap extensively in the OC and single cortical neuron receives signals from a combination of glomeruli expressing different receptors. Moreover, it was shown that in rat primary olfactory cortex, odor-evoked firing activity is sparse and distributed across the cortical neuron population [44]. Therefore, after the convergence of signals from OE to OB, the combinatorial code in OB is transformed to an overcomplete and sparse representation in the OC. Figure 2.9 illustrates how signals are arranged in these three stages.

Figure 2.9: Signals of different receptors converge in the OB and then diverge into the OC. Adapted from [37].

#### Sparse Coding with Overcomplete Basis Functions

What is the significance of this dimensionality expansion? In fact, such dimensionality expansion also exists in the visual system: from the lateral geniculate nucleus (LGN) to the primary visual cortex (V1) [45]. Therefore, the sparse coding theory for V1 simple cells [32], [40], [41] may provide useful insight here. As will be explained shortly, such dimensionality expansion allows the neurons in the cortex to learn the higher-order structure of the inputs and represent the input with as few active neurons as possible.

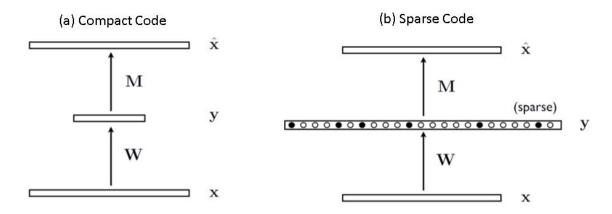

It's postulated that one important goal of sensory coding is to transform the redundancy (statistical dependence) in the input information to more effective representations for later stages of processing [40]. If we consider a code in terms of an autoencoder network, the design of the code is to find the optimized encoder **W** and decoder **M** such that information loss is minimized:

$$\min_{\mathbf{W}, \mathbf{M}} |\mathbf{x} - \hat{\mathbf{x}}|^2, \tag{2.1}$$

where  $\mathbf{x}$  is the input information, and  $\hat{\mathbf{x}}$  is the recovered information.

Figure 2.10 shows two coding strategies under two different constraints [46]. According to the information theory, the best code is the one that can preserve the input information with least number of bits. This is the compact code in Figure 2.10(a), where the constraint is imposed on the number of elements representing the information. This can be achieved by

principle component analysis (PCA) or singular value decomposition (SVD). Since each output element represents a basis function in an orthonormal set, the input data is decorrelated at the output. It has been noted that Hebbian learning can find the principle components under the right conditions [47]. It was also shown that such redundancy reduction strategy is used in the early visual system [48]. However, the limitation is that it considers only the redundancy due to linear pairwise correlations of the input data and is not sufficient to account for the receptive field of neurons found in the cortex. Such representation also has many drawbacks: First, information can easily be lost due to a failure or malfunction of a neuron. Second, every output neuron has high activity for all inputs. Therefore, this code might be suitable in situations where only limited output dimensionality is available.

Figure 2.10: Two coding strategies in term of autoencoder networks. Adapted from [46].

The idea of sparse coding (Figure 2.10(b)) is based the assumption that the sensory system is organized to achieve as complete a representation of the input information as possible with minimum number of active neurons [49]. Not only the proportion but also the actual number of active neurons is reduced. Therefore, the constraint of the sparse code is not on the number of total neurons. Rather, it allows a much greater number of neurons to code, and constrains the number of active neurons.

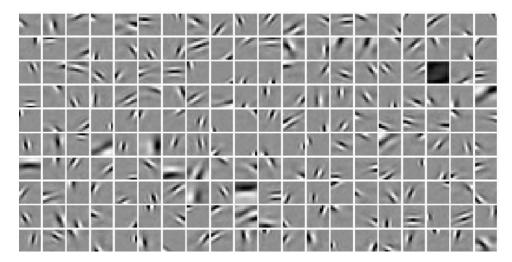

The receptive field of simple cells in mammalian primary visual cortex is characterized as spatially localized, oriented and bandpass, similar to the basis functions in the wavelet transform. Also, the firing of neurons in V1 is sparse and distributed across all neurons. This has led to a conjecture that neurons in the primary visual cortex have adapted themselves to the higher-order structures in the input, such that the response histogram is highly non-Gaussian [40], as shown in Figure 2.11. This is further confirmed by the fact that convolving a Gabor filter with natural images yields highly non-Gaussian responses. And the Gabor function resulting in the highest kurtosis in the response histogram resembles the receptive fields found in V1.

But how do neurons in V1 arrive at such receptive fields from natural images? It was demonstrated that placing only two global objectives is sufficient to account for the principal

Figure 2.11: Projection pursuit. The left part shows the state space of a two-dimensional data set. The right part shows the distribution of the projection onto the axes. When the axes are aligned with the data structure, the response shows a high degree of kurtosis. Adapted from [40].

spatial properties of simple-cell receptive fields: (1) that information to be preserved, and (2) that the representation be sparse [32]. Figure 2.12 shows the resulting basis functions learned from natural images. It can be seen that except for some low-frequency basis functions, most of them are localized, oriented and bandpass.

As for why using an overcomplete basis - i.e. the number of code elements (basis functions) is greater than the effective dimensionality of the input space, it was shown that sparsification with an overcomplete basis will make each unit more selective to stimulus properties [41] and create more diversities of features in the basis. Several theories had proposed that natural images actually lie along a low-dimensional manifold embedded in a N-dimensional hyperspace [50], [51]. Therefore, it is suggested that the advantage of overcomplete coding is that the manifold becomes flattened out in the space defined by overcomplete basis, making it easier for higher cortical areas to learn structures in the data (i.e., the shape of the manifold) [52].

The other reason for overcomplete representations is that the higher-level cortices are hypothesized to compute with high-dimensional vectors [31]. As will be described in Chapter 4, the brain might have leveraged some subtle properties in the hyper-space such that its computation is highly robust to component variations and failures.

Not only in mammalian visual cortex, there are evidences of sparse coding in other sys-

Figure 2.12: Resulting basis functions of sparse coding. Adapted from [32].

tems and species, such as in the mushroom body of locusts [53], auditory cortex in mice [54], hippocampus in rats and primate [55], etc. Although there is no direct evidence for sparse coding in mammalian olfactory cortex, this still provides useful insight for the design of a bio-inspired system.

## 2.1.4 Computations in Higher-Level Cortices

The computations in higher-level areas are still poorly understood. However, several important biologically plausible models have demonstrated alternative computing paradigms intertwining computation and memory, for example, the Hopfield network [56], the Sparse Distributed Memory for the the cerebellum [30], self-organizing maps, and Hierarchical Temporal Memory (HTM) [57], etc.

Recent years, more and more research efforts are devoted to probabilistic models, inference, and recurrent networks, such as Boltzman machines, deep learning, long-short term memory networks, etc. Some of them have been proved powerful in analyzing the big data. We are looking forward to the future advancement in computational neuroscience that may revolutionize the human information technology.

# 2.2 Architecture Overview

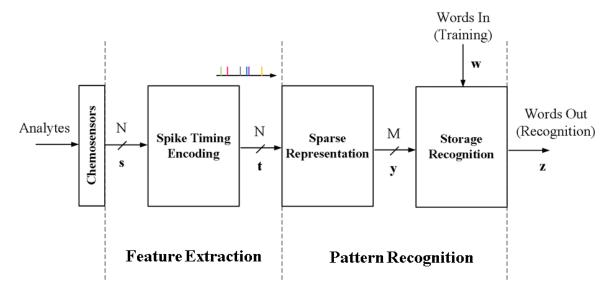

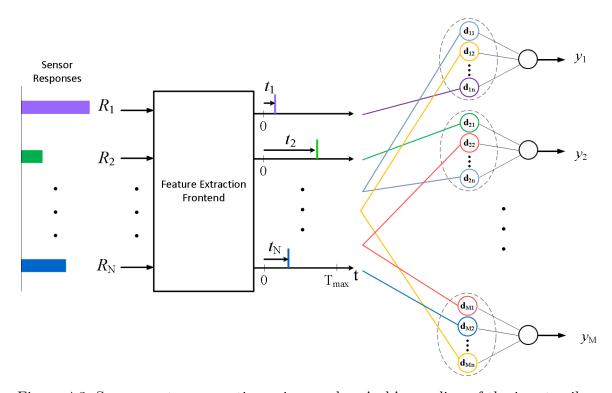

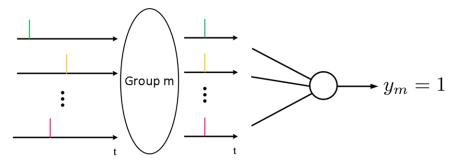

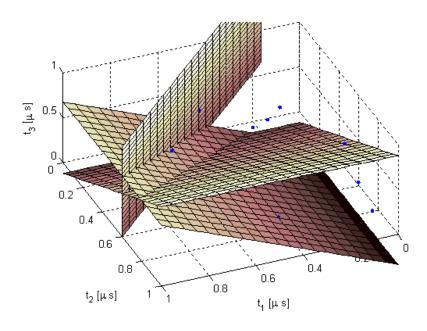

In light of the biological olfactory pathway, an architecture for artificial olfaction is proposed, as shown in Figure 2.13.

The analytes are first sensed by N gas sensors. Because most gas sensors are broadly responsive, an array of different sensor types must be used to produce unique signatures for different analytes. This is similar to the combinatorial coding in the olfactory epithelium and the olfactory bulb. The sensor output vector is denoted by  $\mathbf{s}$  and has a dimension of N.

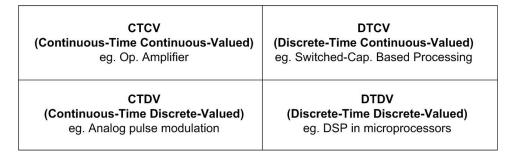

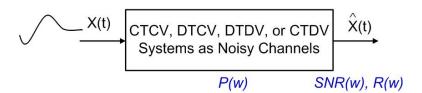

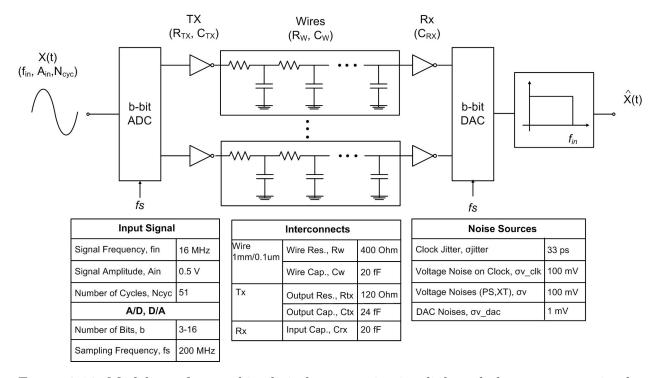

Figure 2.13: System architecture.