# Verification and Synthesis of Clock-Gated Circuits

Yu-Yun Dai

# Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2017-122 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2017/EECS-2017-122.html

June 26, 2017

Copyright © 2017, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Verification and Synthesis of Clock-Gated Circuits

by

Yu-Yun Dai

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering-Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Robert K. Brayton, Chair Professor Sanjit Seshia Professor Alper Atamtürk

Summer 2017

# Verification and Synthesis of Clock-Gated Circuits

Copyright 2017 by Yu-Yun Dai

#### Abstract

#### Verification and Synthesis of Clock-Gated Circuits

by

Yu-Yun Dai

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Robert K. Brayton, Chair

As system complexity and transistor density increase, the power consumed by digital integrated circuits has become a critical constraint for VLSI design and manufacturing. To reduce dynamic power dissipation, clock-gating synthesis techniques are applied to circuits to prune register updates by modifying the next-state functions of the registers. Hence to verify this kind of synthesis, sequential equivalence checking (SEC) of clock-gated circuits is required.

In this thesis, we examine the application of reverse engineering and control logic extraction to assist in the analysis and verification of clock-gated circuits. The proposed methodology also enables sequential clock-gating synthesis to further reduce dynamic power. A secondary focus is on recognizing circuit functionalities with deep learning techniques.

The first part of the work deals with the use of transparent logic to recognize control and data paths of gated-level circuits. We invent abstraction models (dependencies graphs, DGs) of sequential circuits and then explain how they can be used to formulate sufficient conditions for legal clock-gating. It is then demonstrated how to perform efficient sequential equivalence checking (SEC) between a circuit before and after clock-gating synthesis based on DGs. The proposed formulation is extended to allow sequential clock-gating synthesis to be done systematically and automatically.

The second part of the thesis introduces the use of neural networks to recognize circuit properties, which can be used to benefit and improve reverse engineering methods. We invent a representation of gate-level circuits to work with neural networks and build a framework for circuit recognition, including function classification and detection. The proposed framework can also be used to locate high-level constructs in the sea of logic gates. To people who have made me a better person.

# Contents

| Co  | onter                                                       | nts                                                                                                                                                                                                                                                  | ii                                                                                             |

|-----|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Lis | st of                                                       | Figures                                                                                                                                                                                                                                              | iv                                                                                             |

| Lis | st of                                                       | Tables                                                                                                                                                                                                                                               | vii                                                                                            |

| 1   | Intr<br>1.1<br>1.2<br>1.3<br>1.4                            | coduction         Preliminaries         Background         Contributions         Thesis Organization                                                                                                                                                 | 1<br>1<br>3<br>3<br>4                                                                          |

| 2   | Ver:<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5                     | ification with Characteristic Graphs         Characteristic Graphs         Sequential Redundancy and Clock-Gating         Overall Flow         Experimental Results         Summary                                                                  | <b>5</b><br>6<br>9<br>13<br>15<br>17                                                           |

| 3   | <b>Tra</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | nsparent Logic in Hardware Designs         Introduction         Overview         Extending Transparent Logic         Transparency Identification         Practical Challenges         Experimental Results         Summary and Possible Applications | <ol> <li>19</li> <li>20</li> <li>22</li> <li>26</li> <li>31</li> <li>33</li> <li>37</li> </ol> |

| 4   | Dep<br>4.1<br>4.2<br>4.3                                    | Dependency Graphs         Dependency Graph         Construction of Dependency Graph         Summary                                                                                                                                                  | <b>39</b><br>40<br>42<br>45                                                                    |

iii

| 5       | Legal Clock-Gating Conditions5.1Problem Formulation using DGs                                            | <b>47</b><br>47<br>48<br>48<br>55<br>60<br>65<br>68                                                         |

|---------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 6       | Sequential Equivalence Checking of Clock-Gated Circuits6.1Identifying Clock-Gating Conditions            | <b>71</b><br>71<br>73<br>74<br>75<br>77                                                                     |

| 7       | Clock-Gating Synthesis7.1Synthesis with Update Conditions                                                | <b>78</b><br>78<br>79<br>83<br>85<br>85                                                                     |

| 8       | Circuit Recognition with Convolutional Neural Networks8.1Preliminary: Modern Machine Learning Algorithms | <ul> <li>86</li> <li>87</li> <li>91</li> <li>92</li> <li>94</li> <li>95</li> <li>95</li> <li>102</li> </ul> |

| 9<br>Bi | Conclusions and Future Directions                                                                        | 104<br>106                                                                                                  |

| Dl      | unography                                                                                                | 100                                                                                                         |

# List of Figures

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ | Standard representation of a sequential circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\frac{1}{2}$ |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

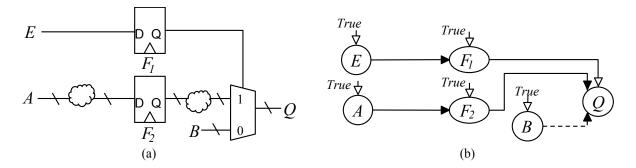

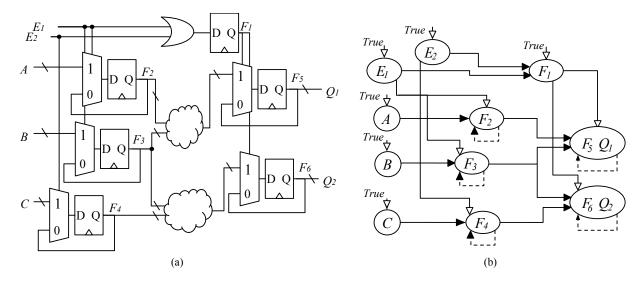

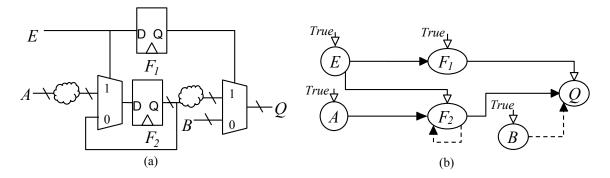

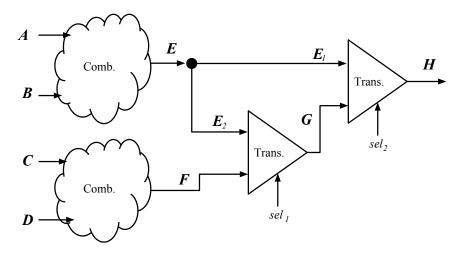

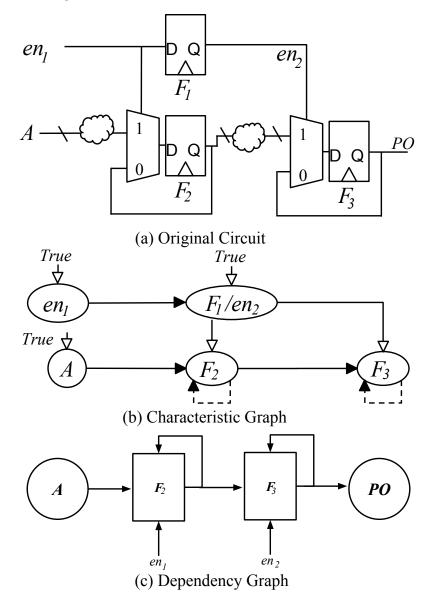

| 2.1                                       | A sequential circuit (a) with its characteristic graph (b). Each circle stands for a group<br>of signals, while <i>selection-edges</i> , <i>on-edges</i> and <i>off-edges</i> are represented respectively<br>by solid lines with white arrows, solid lines with black arrows, and dotted lines with<br>black arrows. $Q$ is switched between $F_2$ and $B$ , where $F_1$ is the selection signal. The<br>selection-edges of the inputs, $E$ , $A$ and $B$ , are connected to $True$ . The selection-edge<br>of $F_1$ is driven by $True$ , because $F_1$ has no off-edge. | 6             |

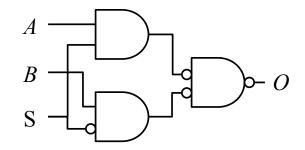

| 2.2                                       | A typical 2-to-1 multiplexer represented as an AIG, where $A$ and $B$ are the two inputs,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

|                                           | S is the selector, and O is the output: $O = SA + S'B$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7             |

| 2.3                                       | A clock-gated sequential circuit (a) with its characteristic graph (b). Each clock-gated FF is represented by a FF feeding back to a MUX controlled by a selection signal. The clock-gated FFs, $F_2$ to $F_6$ , are updated only when their corresponding selection signals, $E_1$ , $E_2$ or $F_1$ is 1; otherwise, they keep the same values as already saved in the                                                                                                                                                                                                    |               |

|                                           | corresponding FFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10            |

| 2.4 $2.5$                                 | The revised circuit for Figure 2.1 with its characteristic graph, where the inputs, outputs and FFs are perfectly mapped to those in the golden design                                                                                                                                                                                                                                                                                                                                                                                                                     | 11            |

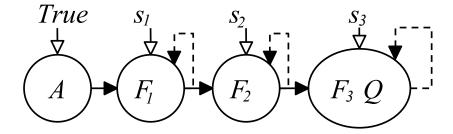

| 2.0                                       | by True. The signals, $s_1$ , $s_2$ and $s_3$ represent the updating conditions for FFs $F_1$ , $F_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |

|                                           | and $F_3$ , respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12            |

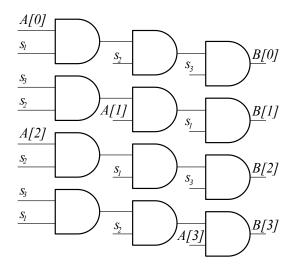

| 3.1                                       | A transparent word can be implemented by composing smaller transparent words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24            |

| 3.2                                       | A longer transparent word may be obtained from smaller transparent words and an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

|                                           | NPN isomorphism class.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25            |

| 3.3                                       | A compound word composed of three depth-one words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29            |

| 3.4                                       | An example containing proceeding words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30            |

| 3.5                                       | An example with disjoint transparent blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31            |

| 3.6                                       | A transparent block which is not the result of compositions of NPN isomorphism classes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33            |

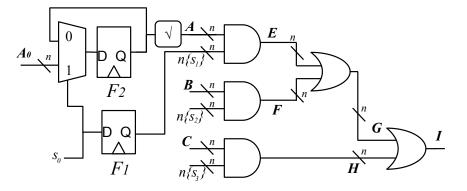

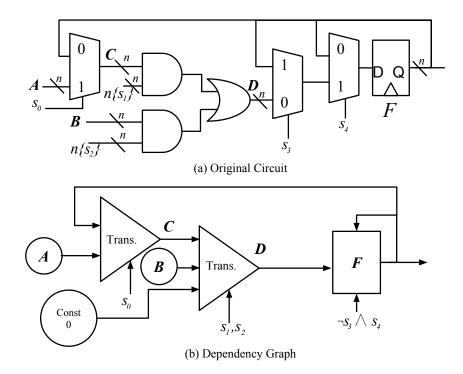

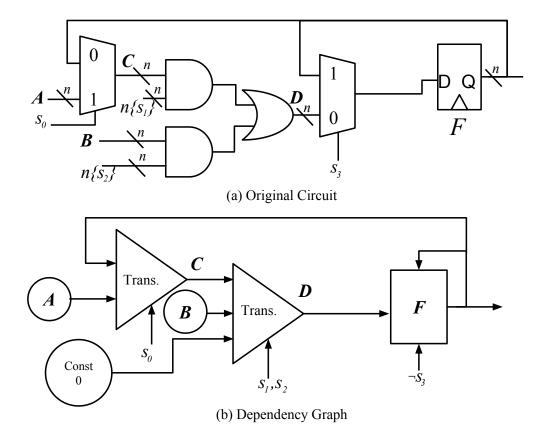

| 4.1                                       | Considering transparent logic in clock-gating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40            |

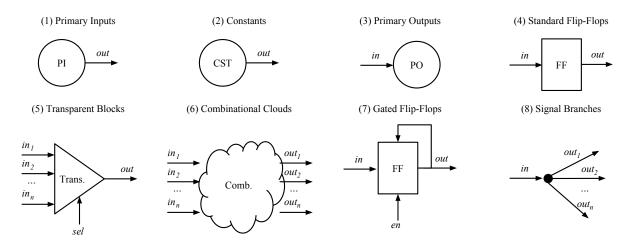

| 4.2                                       | Eight types of vertices used in a dependency graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40            |

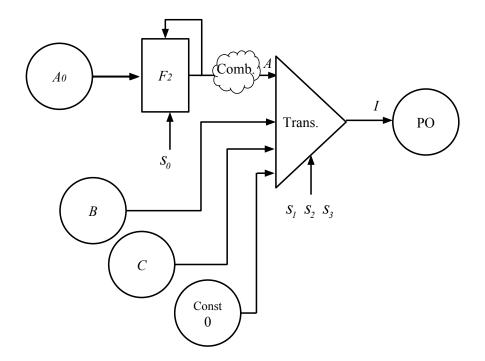

| $\begin{array}{c} 4.3 \\ 4.4 \end{array}$ | Dependency graph for the circuit in Figure 4.1                                                                                                                                                                                                                                                                                         |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

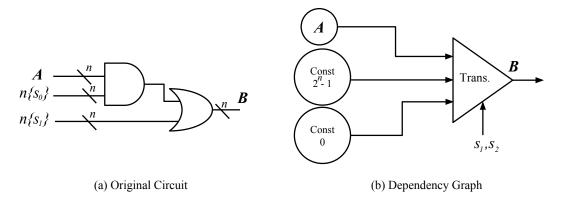

| 4.5                                       | (a) Transparent block with two possible constant outputs. (b) Corresponding depen-<br>dency graph                                                                                                                                                                                                                                      |

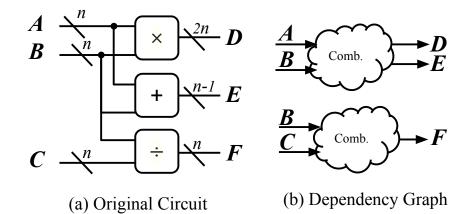

| 4.6                                       | (a) Three arithmetic operators with shared input words. (b) Corresponding DG 4                                                                                                                                                                                                                                                         |

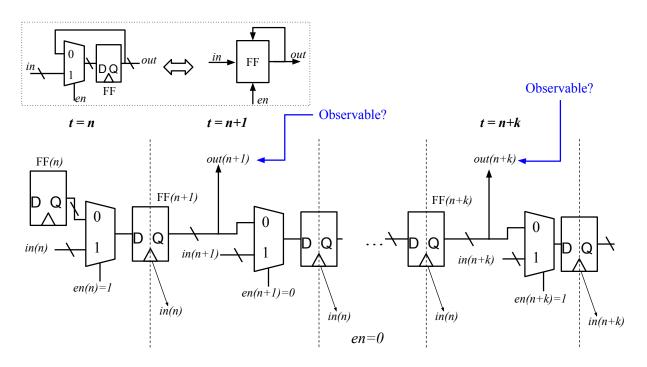

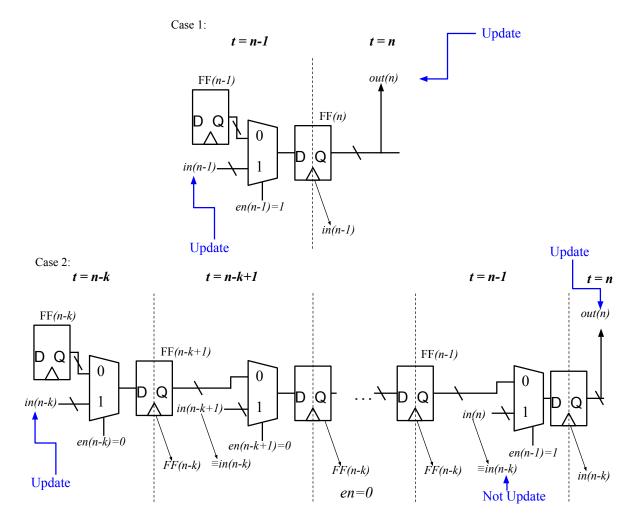

| 5.1                                       | An example to demonstrate the observable condition of the input for a set of gated FFs at the $n^{th}$ time frame, labelled as $in(n)$ . The bottom diagram represents the top diagram unrolled k time frames when $en$ again becomes 1                                                                                                |

| 5.2                                       | Example DG demonstrating an observable condition for the target gated FF 5                                                                                                                                                                                                                                                             |

| 5.3                                       | Three cases when deriving observable conditions for FFs in loops                                                                                                                                                                                                                                                                       |

| 5.4                                       | An example to demonstrate how the ouput of a gated FF can be updated                                                                                                                                                                                                                                                                   |

| 5.5                                       | An example to demonstrate how a satisfiability clock-gating condition can be verified. 5                                                                                                                                                                                                                                               |

| 5.6                                       | Two examples with FFs on sequential loops. The initial states and combinational logic are included                                                                                                                                                                                                                                     |

| 5.7                                       | The formulated property includes more cases for updates than necessary                                                                                                                                                                                                                                                                 |

| 5.8                                       | An example with a sequence of gated FFs before the target FF                                                                                                                                                                                                                                                                           |

| 5.9                                       | DG for all circuits in Figure 5.10                                                                                                                                                                                                                                                                                                     |

| 5.10                                      | Circuit that can be clock-gated by satisfiability or by observable conditions separately. 6                                                                                                                                                                                                                                            |

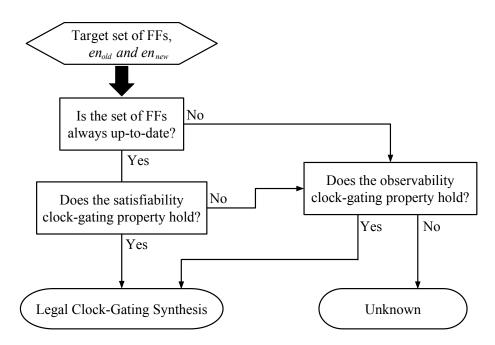

| 5.11                                      | Verification flow for a target set of FFs                                                                                                                                                                                                                                                                                              |

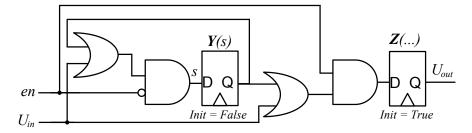

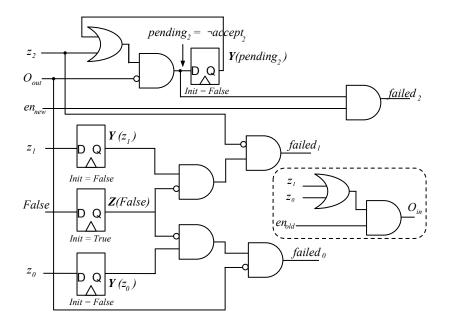

| 5.12                                      | Circuit for $\mathbf{Z}\{[en] \land [\mathbb{U}(in) \lor \mathbf{Y}([\neg en]\mathbf{S}[\mathbb{U}(in) \land \neg en])]\}$ based on old enable <i>en</i> and the                                                                                                                                                                       |

| 5.13                                      | update condition of the input                                                                                                                                                                                                                                                                                                          |

| F 1 4                                     | enable signals and the observable condition of its output                                                                                                                                                                                                                                                                              |

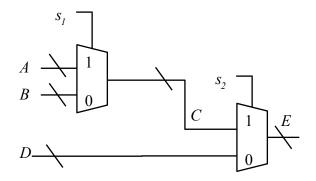

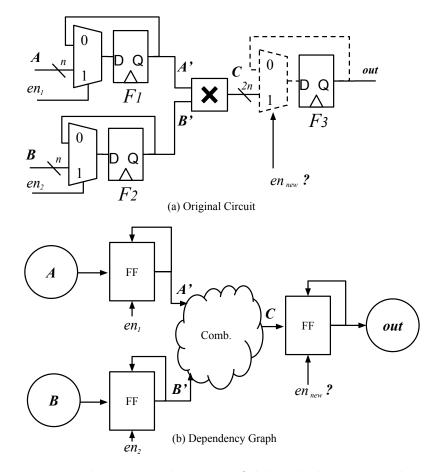

| 5.14                                      | (a) A sequential circuit clock-gated using with both satisfiability and observability. (b) the corresponding characteristic graph, (c) the corresponding dependency graph 6                                                                                                                                                            |

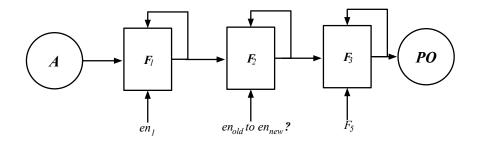

| 6.1                                       | (a) Golden circuit for the one in Figure 4.4. (b) Corresponding dependency graph for the above circuit                                                                                                                                                                                                                                 |

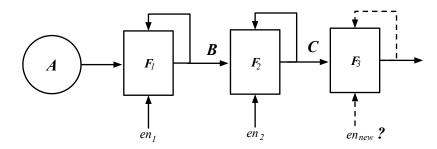

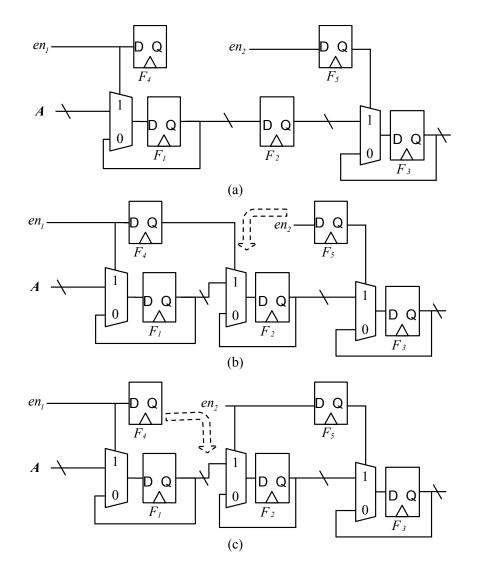

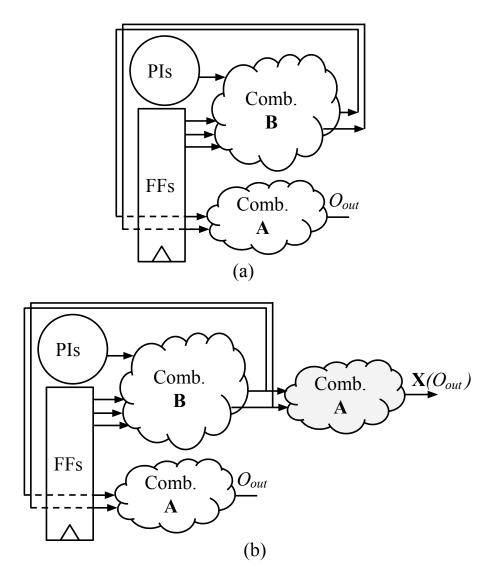

| 7.1                                       | Example for synthesizing $en_{new} = \mathbf{X}(\mathbb{O}(out))$ . In (a), $O_{out}$ has been built as a new signal in the circuit. Then in (b), the combinational circuit $\mathbf{A}$ supporting $O_{out}$ is duplicated and added to the other combinational block $\mathbf{B}$ which supports $\mathbf{A}$ across one time frame. |

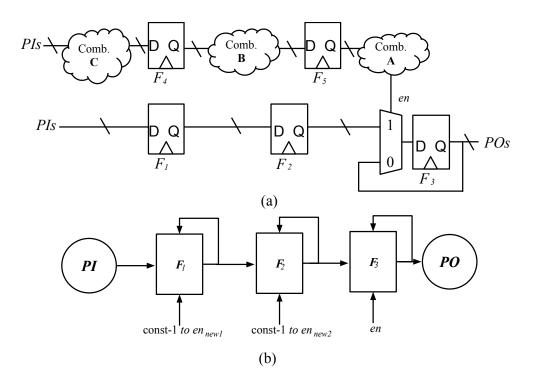

| 7.2                                       | An example for observability clock-gating synthesis. (a) A sequential circuit with two                                                                                                                                                                                                                                                 |

| 1.2                                       | sets of target FFs, $F_1$ and $F_2$ . (b) The corresponding DG                                                                                                                                                                                                                                                                         |

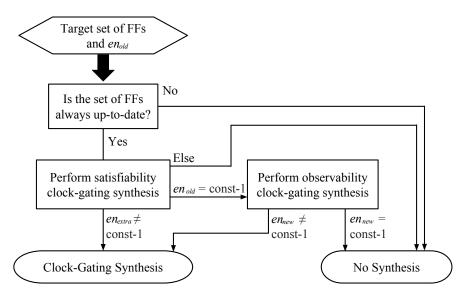

| 7.3                                       | Synthesis flow for a target set of FFs                                                                                                                                                                                                                                                                                                 |

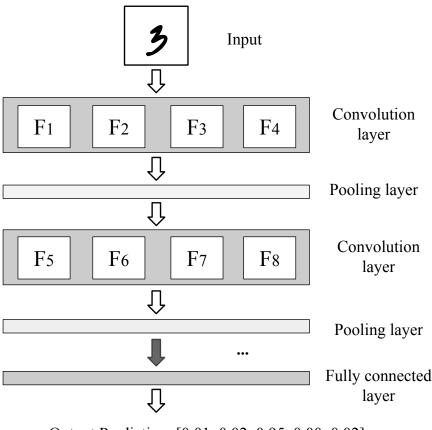

| 8.1                                       | A typical convolution network for image processing. There are five expected outputs (classes), and the input object is most likely to belong to the third class in this case. 8                                                                                                                                                        |

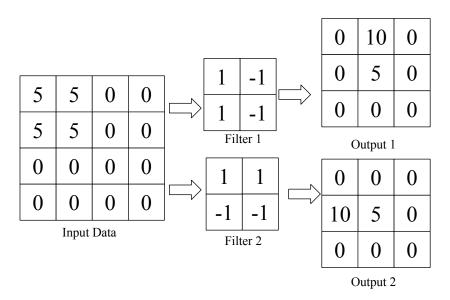

| 8.2                                       | A convolution layer with two $2 \times 2$ filters for image processing                                                                                                                                                                                                                                                                 |

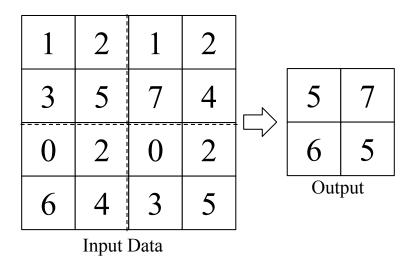

| 8.3                                       | Max-pooling layer for image processing                                                                                                                                                                                                                                                                                                 |

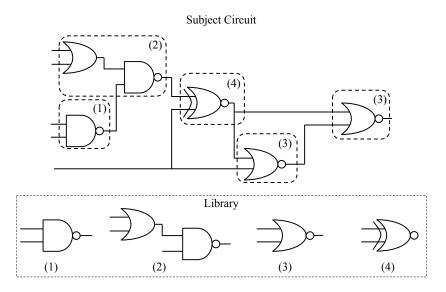

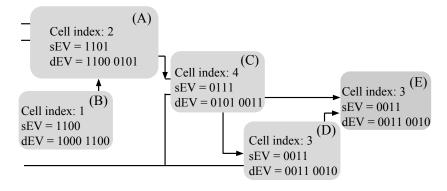

| 8.4                                       | A running example of circuit convolution                                                                                                                                                                                                                                                                                               |

| 8.5 | The subject circuit after technology mapping. The cell index for each node refers to |     |

|-----|--------------------------------------------------------------------------------------|-----|

|     | the corresponding library cell in Figure 8.4.                                        | 93  |

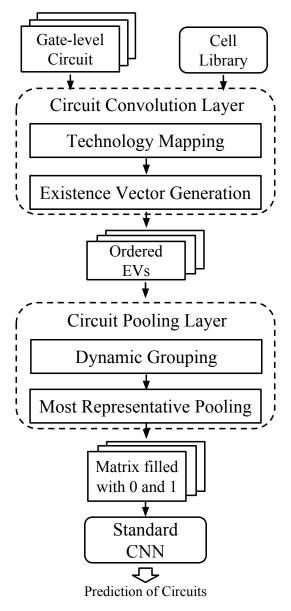

| 8.6 | The proposed framework for circuit classification.                                   | 96  |

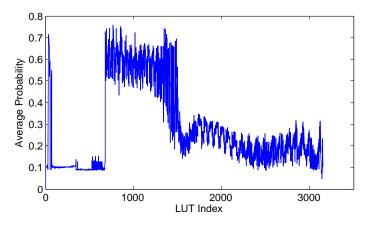

| 8.7 | The average probability (likelihood) versus each LUT for an example circuit, which   |     |

|     | contains one multiplier.                                                             | 102 |

|     |                                                                                      |     |

# List of Tables

| 2.1                 | Comparisons with <i>super_prove</i> and <i>Absec</i> on three OpenCores [33] cases and two synthetic cases.                                                               | 16         |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.2                 | Comparisons with <i>super_prove</i> and <i>Absec</i> on <i>qmult</i> , a design from OpenCores [33], with varying bit-widths.                                             | 16         |

| 3.1                 | Statistics of the selected benchmarks from HWMCC'14 [17].                                                                                                                 | 34         |

| 3.2                 | Experimental results of the structural and functional approaches on ten selected cases from HWMCC'14 [17].                                                                | 35         |

| 3.3                 | Experimental results of the functional approaches on unrolled cases from HWMCC'14 [17].                                                                                   |            |

| $5.1 \\ 5.2$        | Observable condition for the input of each type of vertex                                                                                                                 | $49 \\ 55$ |

| 6.1                 | Comparisons with the CG method on three OpenCores [33] cases, two synthetic cases<br>and three industrial cases.                                                          | 76         |

| 6.2                 | Comparisons with the CG method on <i>qmult</i> , a design from OpenCores [33], with varying bit-widths.                                                                   | 77         |

| 7.1                 | Experimental results of the proposed clock-gating synthesis flow                                                                                                          | 85         |

| $8.1 \\ 8.2 \\ 8.3$ | Sample runtime of converting AIGs into Boolean matrices                                                                                                                   | 97<br>98   |

| 0.0                 | classification. The numbers under <i>Training Number</i> indicate the number of training cases in each class; the total training size is triple of the number.            | 99         |

| 8.4                 | The average and standard deviation of accuracy rates for each setting of operator detection. The value of $n$ indicates the total number of arithmetic operators for each |            |

|                     | case, where at most one is a multiplier. $\ldots$                                                                                                                         | 99         |

#### Acknowledgments

First and foremost, I would like to thank my advisor, Prof. Robert Brayton for all the guidance, help, support and encouragement during my graduate study in Berkeley. He has been a wonderful mentor and living example for me to be a better researcher and human being. Many thanks to Ruth for sharing her observations of Bob and a lot of heartwarming moments. I wish I could become a person like Bob who has been an incredible role model for many people.

It has been my pleasure to work with Dr. Alan Mishchenko during the past four years. Without his ABC framework, my research projects might be significantly delayed. His selfless sharing has provided me plenty of ideas about not only researches on verification and synthesis, but several aspects of life.

My thanks goes to Professor Sanjit Seshia, Professor Alper Atamtürk and Prof. Andreas Kuehlmann for their valuable feedback to my thesis work. Their courses on verification, mathematical programming and logic synthesis have established essential foundations for my research works.

I have enjoyed the interactions with my colleagues in our group, Sayak Ray, Baruch Sterin, Jiang Long and Yen-Sheng Ho. Indeed, I need to express my special thanks to Baruch for all of his generous and patient helps. Also, I thank Tianshi Wang, Karthik Aadithya, Antonio Iannopollo, Baihong Jin, Shromona Ghosh, Pierluigi Nuzzo, Chung-Wei Lin and Ben Zhang from other groups for the many wonderful moments and conversations I have had with them in the DOP center.

Prof. Jajeet Roychowdhury has dramatically changed my graduate study since my first year in Berkeley. His courses on numerical methods, his challenging questions in my first preliminary exam, and his demands for my paper writing and presentation skills have sharpened me a lot. Without his push, I might not be able to proceed forward so quickly.

Working with Prof. Anant Sahai and Michel Maharbiz for the EE16B course has been a unique and unforgettable experience in Berkeley. I have learned a lot from my fellow GSIs and uGSIs, as well as my students. I also thank Prof. Stavros Tripakis for giving me the chance to teach in EE244 as the way I wanted.

I would like to express my special thanks to Kei-Yong Khoo, who was the manager for my internship in Cadence. He introduced the concept of clock-gating to me, which has been the main focus of this thesis. I have had a great time with my mentor Danny Ho and other members from the Conformal team. I would recommend this team to everyone who might want to work on combinational equivalence checking or ECO problems.

The weekly lunches and chats with members in WICSE have been significant entertainments during the four years. I thank Qie Hu, Fanny Yang, Vidya Muthukumar, Mindy Perkins, Regina Eckert, Sandy Huang, Rashmi Vinayak, Cathy Wu, Alice Ye, Penporn Koanantakool and Mangpo Phitchaya Phothilimthana for many marvelous conversations we have had together.

I would like to give a special note of thanks to Shirley Salanio, for her prompt and cheerful help for all concerns or issues I have during my graduate study in the EECS department. I thank my family members, especially my parents, for shaping me to the person who I am. Their influences on all of my characteristics can hardly be reciprocated. I hope I have made them proud.

I want to express my deepest gratitude to my husband, Wei-Hsun (Wish) Lin, for his consistent and unconditional support, even before I applied for the Ph.D. program. We have been the best friend to each other, and I believe we will share more monumental moments in the future.

# Chapter 1

# Introduction

This dissertation is a study of how formal methods and reverse engineering can be used to verify and synthesize digital circuits for minimizing dynamic power consumption. In the course of this study, several new concepts and techniques are introduced to analyze and extract circuit properties to build a framework for verification and synthesis to achieve low power circuit designs.

Before moving to the main part of this work, we begin with some background about sequential clock-gating in Section 1.1, and existing methods for sequential equivalence checking in Section 1.2.

It is assumed throughout that the reader has some familiarity with algorithmic notation, the vocabulary and terminology of digital design, Boolean logic and temporal logic.

# **1.1** Preliminaries

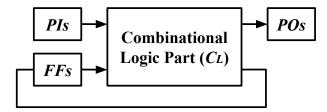

A sequential circuit, as shown in Figure 1.1, consists of a combinational logic part  $(C_L)$ , and sets of primary inputs (PIs), outputs (POs) and memory components (flip-flops, FFs). The combinational part represents a functional mapping from PIs and current states of FFs, to POs and the next state of each FF.

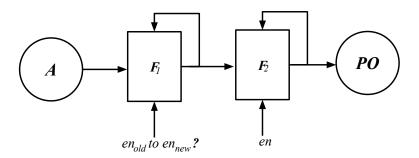

Figure 1.1: Standard representation of a sequential circuit.

In modern VLSI design flows, combinational and sequential synthesis techniques [23] are applied to sequential circuits to minimize chip area, reduce power consumption, optimize

#### CHAPTER 1. INTRODUCTION

the clock period, etc. Combinational synthesis preserves the sequential behavior of FFs to reduce the cost functions, while sequential synthesis provides more flexibility by possibly changing the next state functions and thereby producing further reductions in the power consumption.

To manufacture chips while considering power consumption, static and dynamic power of running the circuits are analyzed. Static power refers generally to the power required to maintain the state of a circuit, while dynamic power refers to power needed during switching activity. In this thesis, we only focus on dynamic power consumption.

To reduce the power consumed for updating FFs, synthesis tools apply satisfiability (forward) and observability (backward) clock-gating [20]. Satisfiability clock-gating is used to disable the clock of a FF when its input data remains unchanged during the current clock period. Thus, a FF need not be updated if the incoming data remains the same as that saved in the register. Observability clock-gating turns off the clocks to FFs when the current values of the FFs input can never be observed at the POs.

Generally, satisfiability and observability clock-gating techniques modify the clocks of FFs by using enabling signals. These are sequentially redundant in that they can be removed without modifying any observed sequential behavior. These redundancies are used to minimize the frequency of updating some of the FFs, hence reducing dynamic power consumption. Therefore, the clock-gated circuit will keep the same sequential properties but with fewer updates of the memory components.

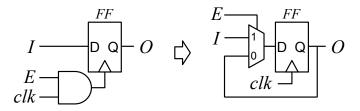

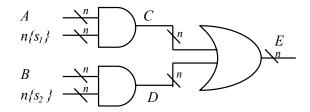

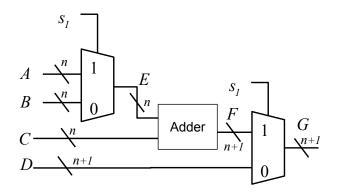

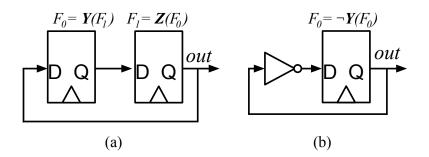

Figure 1.2: An equivalent model for clock-gating a FF.

As shown in Figure 1.2, clock-gating a FF can be modeled with a feedback loop through a multiplexer, where the enable signal, E, controls the switching of O between I and its old value. This allows the modeling of clock-gated circuits to be done with only generic FFs. Notice that in practice, the circuit on the left-hand side of Figure 1.2 can result some latch issues, so in practice, real clock-gating construct can be more complicated; however its modeling is the same as shown in Figure 1.2.

Once synthesis is applied to a circuit, sequential equivalence checking (SEC) is used between the circuits before and after synthesis [24]. As the need for SEC techniques increases, efficient methods become not only more necessary but also enable the use of sequential synthesis in the first place as such synthesis has usually avoided due to verification complexity. The complexity of general SEC is P-SPACE complete, and hence more complex than combinational equivalence checking (CEC), which is only NP-complete.

# 1.2 Background

After synthesis, we need to ensure that the circuits before and after synthesis are sequentially equivalent [2]. SEC for general circuits is typically formulated as a model checking problem on the miter between two sequential circuits (where the PI pairs are merged and the PO pairs are XORed to form the outputs of the miter circuit). Thus, sequential model checking techniques, including induction [42], bounded model checking (BMC) [5] and property-directed reachability (PDR) [14], can be applied to check if the outputs of the two circuits are identical forever. If an output of the miter can ever become 1, meaning this pair of POs are evaluated to distinct values under the same input sequences, sequential equivalence is violated. In this case, model checking can provide an input sequence leading to the violation. Otherwise, the two circuits are proved sequentially equivalent.

Due to the P-SPACE complexity of model checking, applying this to SEC problems may be too hard. Of course, CEC can be tried and if successful, the two circuits are also sequentially equivalent. However, most effective sequential synthesis techniques tend to change the next state functions. For circuits under retiming and resynthesis, when the history of sequential synthesis is kept, the SEC problems can be reduced and solved more easily [21]. Similarly, to verify circuits after clock-gating synthesis, the SEC problem can be reduced to a CEC problem by an existing technique. Savoj at el. [41, 40] proposed a combinational approach to SEC for clock-gating synthesis. This approach aimed at circuits synthesized using satisfiability and observability don't cares (SDC and ODC) [39]. Although it worked well compared to existing methods, this approach has several weaknesses: (1) it cannot conclude non-equivalence, and therefore cannot supply a witness to help understand the reason for this, (2) it requires unrolling and there is no suggested number of timeframes for unrolling, (3) it still has a scalability problem, especially when the combinational logic is extremely complicated.

It is therefore important to develop a systematic approach to verify proposed clockgating conditions on circuits. Additionally, an automatic method is proposed to find further clock-gating conditions for synthesis to reduce dynamic power consumption.

## **1.3** Contributions

In this thesis, we first propose an SEC method to apply to clock-gated circuits, based on the fact that sequential clock-gating synthesis usually only adds extra control logic to disable clocks when applicable. Given a pair of circuits, golden (**G**) and revised (**R**), where **R** is clock-gated from **G**, we build abstraction models, *characteristic graphs*, for both. Then for each candidate of a set of clock-gated FFs, we formulate sufficient conditions for legal clock-gating based on the characteristic graph. Once the sufficient properties are justified and the clock-gating condition is proved legal, the extra control logic is indeed a sequential redundancy for the original circuit. By reducing all proved sequential redundancies on the input circuits, the two circuits become more similar to each other, so the SEC problem gets

easier and hence can be solved usually by existing general SEC engines quickly.

Moreover, to resolve more complicated clock-gating conditions, we should consider more properties of the circuits which are excluded by characteristic graphs. To extract detailed control logic and data dependencies from circuits, we introduce a concept called *transparent logic* to model data flow under control. We also propose a functional approach to identify transparent logic from gate-level circuits. Unlike structure approaches which rely on structure matching, the proposed method can recognize more transparent logic and provide more insights of the target circuit. This concept can be used widely in verification and reverse engineering.

Based on recognized transparent logic, we invent another abstraction model, *dependency* graphs, to describe clock-gating structures and data dependencies for sequential circuits. Those graphs represent the essential information of clock-gating, but bypassing irrelevant combinational logic blocks. Then we formally formulate sufficient properties of legal clock-gating on dependency graphs using temporal logic. Those properties can be represented as circuits and verified by hardware model checkers. Dependency graphs are compatible with the proposed SEC flow that relies on characteristic graphs.

Moreover, the formulation of dependency graphs leads to clock-gating synthesis algorithms. We propose an automatic flow to synthesize enable signals which turn off the clocks of target FFs to reduce the frequency of their updating. This flow can be adopted into a modern VLSI design flow to achieve low power circuits.

To retrieve more high-level information from gate level circuits, we also experiment with deep learning techniques to recognize functionalities (like datapath operators) of circuit blocks. We invent a new representation for circuits to work with machine learning techniques and demonstrate how it can capture essential features for circuit recognition. To the best of our knowledge, this is probably the first work applying neural networks to recognize circuit types.

### 1.4 Thesis Organization

The rest of the thesis is organized as follows. Chapter 2 presents *characteristic graphs* and the usage in verification of clock-gating conditions. Chapter 3 introduces transparent logic and a functional approach to recognize transparent logic in hardware designs. The definition and construction of dependency graphs are stated in Chapter 4, while Chapter 5 shows how to formulate legal clock-gating conditions on dependency graphs. The proposed clock-gating verification and synthesis flows are demonstrated in Chapter 6 and 7, respectively. Chapter 8 explains how to recognize functional blocks with deep learning techniques. Lastly, Chapter 9 concludes this thesis.

# Chapter 2

# Verification with Characteristic Graphs

The methodology introduced in this chapter is based on the observation that some sequential synthesis methods only modify a circuit by introducing control structures that are sequentially redundant [20]. Hence equivalence checking can be based on detecting and proving these redundancies, eliminating them, and then doing SEC between the resulting (simplified) circuit and a *golden model*. We propose such a method that uses an abstraction, characteristic graph (CG), of a circuit to formulate legal clock-gating conditions. We apply them to sequentially clock-gated circuits, and give some experiments comparing the new method against existing techniques.<sup>1</sup>

In the next two chapters we further extend and generalize these ideas with the concepts of dependency graphs (DGs) and transparent paths. DGs address more detailed data dependencies than CGs do. Recognizing transparent logic blocks can decompose larger combinational blocks into smaller sub-circuits and provide more detailed data flow information. The use of DGs complements CGs in that they provide more information, but it takes more time to analyze and build DGs for circuits. However, DGs are able to provide more precise properties for legal clock-gating conditions, which can benefit clock-gating synthesis as well as verification.

This chapter is organized as follows: In Section 2.1, a method for representing some essential features of a clock-gated circuit using a *characteristic graph* is described. Section 2.2 discusses the connection between the CG and sequential redundancy in clock-gated circuits. The overall flow of our SEC method for clock-gated circuits is given in Section 2.3, and Section 2.4 compares the performance of the proposed method with previous works, using several sets of experiments. Section 2.5 summarizes the results and discusses some limitations of the proposed method.

<sup>&</sup>lt;sup>1</sup>The full version of this chapter has been published in Design Automation Conference 2015 [12].

## 2.1 Characteristic Graphs

A characteristic graph (CG) is an abstraction of its corresponding circuit. It is a high-level description, which represents only essential characteristics needed for equivalence.

#### 2.1.1 Characteristic Graph

A characteristic graph  $\mathbf{G} = (\mathbf{V}, \mathbf{E})$  is a directed graph, where a vertex stands for a group of PIs, POs, FFs or internal signals in the corresponding circuit. Each directed edge represents a signal dependency from one group to another. There are three types of edges: *selection-edge*, *on-edge* and *off-edge*. A selection-edge connects exactly one signal to its target group, to indicate the conditional switch of the group dependency. On-edges and off-edges connect the different sets of support groups to the target group if the selection signal is 1 or 0, respectively. The selection-edge of each PI is driven by a constant *True*, which means the value of each input signal is unconditionally updated. A group containing PIs cannot be driven by other groups. Some FFs can be in the same group with POs because those FFs are also combinational ouputs and controlled by the same selector. Hence this type of group can have edges to other vertices. An algorithm is given in Algorithm 2.1 for constructing the CG of a sequential circuit.

Figure 2.1: A sequential circuit (a) with its characteristic graph (b). Each circle stands for a group of signals, while *selection-edges*, *on-edges* and *off-edges* are represented respectively by solid lines with white arrows, solid lines with black arrows, and dotted lines with black arrows. Q is switched between  $F_2$  and B, where  $F_1$  is the selection signal. The selection-edges of the inputs, E, A and B, are connected to *True*. The selection-edge of  $F_1$  is driven by *True*, because  $F_1$  has no off-edge.

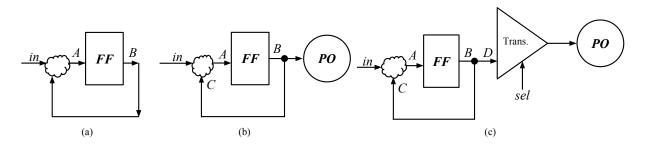

Figure 2.1 depicts a sequential circuit with its corresponding characteristic graph. A line with a white arrow represents a selection-edge, while solid and dotted lines with black arrows are on-edges and off-edges. The circles (vertices) stand for sets of signals in the original circuit, including PIs, E, A and B, the PO, Q, and FFs,  $F_1$  and  $F_2$ . Note that there is no on-edge or off-edge into each PI, and their selection-edges are driven by constant *True*. Thus the value of each PI is not driven by any other signal, and it is updated at every clock tick. For the output, Q, the value of  $F_1$  (selection-edge) determines if its value is driven by B (on-edge) or  $F_2$  (off-edge). Finally,  $F_1$  is only driven by E, so it has no off-edge and its selection is True.

To sum up, a characteristic graph abstracts the data dependency among 'essential' signals, while ignoring combinational logic parts, which are usually irrelevant for proving clockgating equivalence. Although this abstraction is especially motivated by the SEC problem for clock-gated circuits, the idea might be used in similar problems.

#### 2.1.2 Construction of Characteristic Graph

Given a sequential gate-level circuit, the characteristic graph is constructed in three steps: (1) recognize selection signals (2) create vertices (3) build dependencies.

**Recognize selection signals**: When the input circuit is generated from a synthesis tool, in which 2-to-1 multiplexers (MUXes) are supported and explicitly expressed, the selector inputs of these MUXes are easily recognized and designated as selection signals. If the input circuit is an and-inverter-graph (AIG), the instances of a MUX structure shown in Figure 2.2 needs to be identified. The output signal O is controlled by S and conditionally switched between A and B. Therefore, the signal S here is recognized as the selection signal for the group consisting of output O. This structural matching can be performed over the AIG very quickly. However, it is possible that some essential MUX controls could be missed. Also, in this chapter, it is assumed there is at most one MUX in front of each FF, so it is possible that some clock-gating conditions might be overlooked, which would make the final equivalence check harder.

Figure 2.2: A typical 2-to-1 multiplexer represented as an AIG, where A and B are the two inputs, S is the selector, and O is the output: O = SA + S'B.

**Create vertices**: Initially, all POs and FFs are grouped by their common selection signals, while signals without selection conditions are put into individual groups. For example, in Figure 2.1, E, A, B and  $F_1$ ,  $F_2$  are put in individual vertices. Each selection signal occupies an individual vertex. Each signal must be in no more than one vertex.

**Build dependency**: Edges in the CGs represent data dependency in the sequential circuits. Starting with each signal covered by a vertex, we backtrack the original circuit for one time frame to find its set of supports (PIs or FFs), and then connect the vertices

containing those supports with edges to the target signal. If a vertex (a set of signals) is driven by a selection-edge (controlled by a selection signal), we need to find the two groups of supports, which determine the target value when the selection signal is 1 or 0, and then connect through on-edges and off-edges, respectively. After all vertices have been processed, a complete characteristic graph has been constructed.

| Algorithm 2.1 Characteristic Graph Construction                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Require: Cir: a gate-level sequential circuit with the sets of primary inputs PI, primary                                                     |

| outputs $\mathbf{PO}$ and flip-flops $\mathbf{FF}$                                                                                            |

| <b>Ensure:</b> $\mathbf{G} = (\mathbf{V}, \mathbf{E})$ : characteristic graph for <b>Cir</b> , with the sets of vertices, <b>V</b> and edges, |

| $\mathbf{E}$                                                                                                                                  |

| 1: $\mathbf{V} = \emptyset$ and $\mathbf{E} = \emptyset$                                                                                      |

| 2: $\mathbf{S} = recognize(\mathbf{Cir})$ $\triangleright$ S is the set of selection signals                                                  |

| 3: for all $PI_i$ in PI do                                                                                                                    |

| 4: $\mathbf{V} = \mathbf{V} \cup \{PI_i\}$                                                                                                    |

| 5: for all $s_i$ in S do                                                                                                                      |

| 6: $\mathbf{V} = \mathbf{V} \cup \{s_i\}$                                                                                                     |

| 7: $\mathbf{T} = findTarget(\mathbf{Cir}, s_i)$ $\triangleright \mathbf{T}$ is the set of FFs and POs controlled by $s_i$                     |

| 8: $\mathbf{V} = \mathbf{V} \cup \{\mathbf{T}\}$                                                                                              |

| 9: for $ff_i$ in <b>PO</b> or <b>FF</b> not covered by any $v$ in <b>V</b> do                                                                 |

| 10: $\mathbf{V} = \mathbf{V} \cup \{ff_i\}$                                                                                                   |

| 11: for all $v$ in V do                                                                                                                       |

| 12: <b>if</b> $v$ is controlled by selection signal $s$ <b>then</b>                                                                           |

| 13: $connect(v, getVertex(\mathbf{V}, s), selection)$                                                                                         |

| 14: for all $t$ covered by $v$ do                                                                                                             |

| 15: $\mathbf{Sup}_{on} = \mathbf{Sup}_{on} \cup backtrack(\mathbf{Cir}, t, s, on)$                                                            |

| 16: $\mathbf{Sup}_{off} = \mathbf{Sup}_{off} \cup backtrack(\mathbf{Cir}, t, s, off)$                                                         |

| 17: for all each support $sup_{on}$ in $Sup_{on}$ do                                                                                          |

| 18: $\mathbf{E} = \mathbf{E} \cup connect(v, getVertex(\mathbf{V}, sup_{on}), on)$                                                            |

| 19: for all each support $sup_{off}$ in $Sup_{off}$ do                                                                                        |

| 20: $\mathbf{E} = \mathbf{E} \cup connect(v, getVertex(\mathbf{V}, sup_{off}), off)$                                                          |

| 21: else                                                                                                                                      |

| 22: for all $t$ covered by $v$ do                                                                                                             |

| 23: $\mathbf{Sup} = \mathbf{Sup} \cup backtrack(\mathbf{Cir}, t)$                                                                             |

| 24: for all support <i>sup</i> in Sup do                                                                                                      |

| 25: $\mathbf{E} = \mathbf{E} \cup connect(v, getVertex(\mathbf{V}, sup), on)$                                                                 |

Given a sequential circuit, **Cir**, with the sets of primary inputs **PI**, outputs **PO** and flipflops **FF**, the algorithm for constructing the characteristic graph  $\mathbf{G} = (\mathbf{V}, \mathbf{E})$  is shown in Algorithm 2.1. The function  $recognize(\mathbf{Cir})$  at Line 2 is used to detect the MUX structures in **Cir** and collect their set of selection signals **S**. Based on **S**, **PI**, **PO** and **FF**, vertices are created and added into **V** through Line 3 to Line 10. The function  $findTarget(Cir, s_i)$  is used to collect the set of signals, which are controlled by  $s_i$ . From Line 11 to 25, the vertices are connected according to the data dependencies in **Cir**. For the function connect(...) at Line 13, 18, 20 and 25, the first argument is the target vertex, the second is the support vertex, and the third is the edge type. The function  $getVertex(\mathbf{V}, sup)$  returns the vertex which covers sup.

The function backtrack(...) at Lines 15, 16 and 23 goes back one time frame from target t and returns the supports (PIs or FFs) on the boundaries. If the third argument, s, and fourth argument, on or off, are specified, this function will only backtrack the specified input side of each target MUX, and collect the corresponding supports.

Once the characteristic graph is constructed, it is used to detect sequential redundancy candidates.

## 2.2 Sequential Redundancy and Clock-Gating

Given a sequential circuit, sequential redundancy refers to a signal that can be replaced by another signal or a constant value (1 or 0), while preserving sequential equivalence to the given circuit. Thus, the fanouts of such signals can be moved to other existing signals or to constants without changing the observed behavior.

Clock-gating synthesis can be based on either satisfiability or observability of signals. During this, additional control signals are created in a sequential circuit to reduce the frequency of updating the FFs. These extra signals, by definition, must be sequentially redundant in order to preserve sequential equivalence.

In this section, sufficient conditions are proposed for legal satisfiability and observability clock-gating on sequential circuits that result in sequential redundancies. Those sufficient conditions of legal clock-gating are formulated using CGs and then proved on the original circuits. Here we only demonstrate standard examples for this thesis, while the proposed theorems and algorithms, as well as proofs are detailed in [12].

#### 2.2.1 Satisfiability Clock-Gating

Satisfiability clock-gating aims at turning off clocks for FFs when the input data is identical to the value in the previous time frame. One special case is that their support FFs remain at their previous states. Thus, the clock-gating is legal if all target FFs are guaranteed to update their states when their support FFs are updated. Otherwise, if none of the supports are updated, it is immaterial (don't care) if the target FFs are updated. Under proper initial states, the signal for disabling a clock is redundant and can be set to a constant.

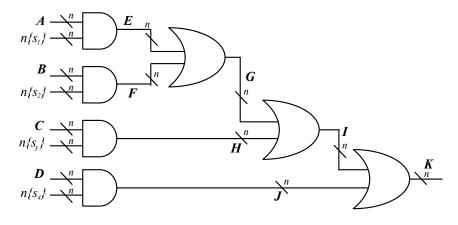

The circuit in Figure 2.3 is an example of satisfiability clock gating:  $F_1$  (initialized as 1) is sequentially redundant because it can be replaced by constant 1, while the behavior observed at the outputs,  $Q_1$  and  $Q_2$ , remains the same. The sequential redundancy,  $F_1$  to

the MUXes in front of  $F_5$  and  $F_6$ , is added to avoid updating  $F_5$  and  $F_6$  when their support FFs ( $F_2$ ,  $F_3$  and  $F_4$ ) remain in the same states.

Figure 2.3: A clock-gated sequential circuit (a) with its characteristic graph (b). Each clock-gated FF is represented by a FF feeding back to a MUX controlled by a selection signal. The clock-gated FFs,  $F_2$  to  $F_6$ , are updated only when their corresponding selection signals,  $E_1$ ,  $E_2$  or  $F_1$  is 1; otherwise, they keep the same values as already saved in the corresponding FFs.

To verify if the clock-gating condition on  $F_5$  and  $F_6$  is legal, i.e. the connection from  $F_1$  to the MUXes is sequentially redundant, a sufficient condition proposed by the CG method (detailed in [12]) is that both the following conditions are satisfied:

- 1. The initial value of  $F_1$  is 1.

- 2. The LTL property

$$\mathbf{G}(E_1 \lor E_2 \Rightarrow \mathbf{X}F_1) \tag{2.1}$$

must hold all the time.

**Proof**: For time frame 0, because the initial state of  $F_1$  is 1, it is safe to replace the selector of each MUX in front of  $F_5$  and  $F_6$  with constant 1. Then, the LTL property in Equation 2.1 guarantees  $F_5$  and  $F_6$  must be updated in the next time frame whenever any support FFs,  $F_2$ ,  $F_3$  or  $F_4$  get updated ( $E_1 = 1$  or  $E_2 = 1$ ) in the current time frame. In other words, if all support FFs are unchanged from the previous clock cycle ( $E_1 = 0$  and  $E_2 = 0$ ), the input value for  $F_5$  or  $F_6$  is the same as the old one, and is immaterial if  $F_5$  or  $F_6$  is updated or not. Thus the selector can be 1 or 0 in those cases. By choosing it to be 1 in those cases as well,  $F_1$  becomes constant 1, i.e.  $F_1$  is stuck-at-1 sequentially redundant. **Q.E.D.**

Note that the above condition is not a necessary condition because even if  $F_2$ ,  $F_3$  or  $F_4$  may change to new states, it might be that the combinational logic actually computes a next

state for  $F_5$  or  $F_6$  which is the same as its current state. In general, such a condition would be difficult to identify and/or expensive to implement, although an easy case would be a multiplier with an argument equal to zero.

The above example demonstrates the legality of a single time frame satisfiability, which can be formulated on the CG entirely. Moreover, given a target control signal  $C_{sat}$ , which is the updating condition of a set of FFs, the CG method can propose sufficient conditions of legal clock gating that go across multi-time frames. Based on the characteristics of the input circuit, there is a natural number N, such that for each k between 1 and N ( $1 \le k \le N$ ), the CG method can propose a corresponding k-time frame sufficient condition for  $C_{sat}$  being stuck-at-1 sequentially redundant. That is, once any of the N conditions can be justified,  $C_{sat}$  is sequentially redundant.

#### 2.2.2 Observability Clock-Gating

Observability clock-gating is used to disable updating FFs when these updates are not observable at the POs. In other words, the differences (updating or not updating) of gated FFs cannot be propagated to any POs before the FFs are updated. Recall the example in Figure 2.1, a set of FFs,  $F_2$ , can be gated by using observability as shown in Figure 2.4. If the connection from E to the MUXes before  $F_2$  can be proved as sequential redundancy, the observability clock-gating applied on  $F_2$  is legal and can be reduced.

Figure 2.4: The revised circuit for Figure 2.1 with its characteristic graph, where the inputs, outputs and FFs are perfectly mapped to those in the golden design.

To verify if the clock-gating condition applied to  $F_2$  is legal, a sufficient condition proposed by the CG method is that the following LTL property

$$\mathbf{G}(\mathbf{X}F_1 \Rightarrow E) \tag{2.2}$$

holds all the time.

**Proof**: The LTL property in Equation 2.2 guarantees  $F_2$  is updated when its target Q depends on the value of  $F_2$  in the next time frame. If E is 0, this property implies that Q is independent of  $F_2$  in the next time frame due to  $F_1 = 0$ . This blocks any new state of

$F_2$  to be observed at any output. Thus the selector of the MUX in front of  $F_2$  can be 0 or 1 in these cases. By choosing it to be 1, the selector is sequentially stuck-at-1 redundant. **Q.E.D.**

Similar to the satisfiability clock-gating cases described in Section 2.2.1, given a target control signal  $C_{obs}$ , which determines if a set of FFs is updated, we can also formulate sufficient conditions for observability clock-gating across multiple time frames, which justify the target signal,  $C_{obs}$ , as sequential stuck-at-1. According to the properties of the input circuit, there is a natural number N, such that the proposed CG method can formulate a corresponding k-time frame condition for each k between 1 and N. If one of the N conditions can be proved,  $C_{obs}$  is sequentially redundant.

#### 2.2.3 Using the Characteristic Graph

A characteristic graph exposes the essential properties of the corresponding circuit, including signal dependency and control signals. It contains information required to formulate properties for the legality of a clock-gated circuit. The on-edges and off-edges of a CG connect the targets and supports across each time frame, while each selection-edge indicates the updating condition for a group of signals. As discussed in Section 2.2.1 and 2.2.2, sufficient conditions for the legality of satisfiability and observability clock-gating can be formulated with LTL properties. Each selection signal associated with a proved condition has its corresponding signal in the original circuit which can be replaced by 1.

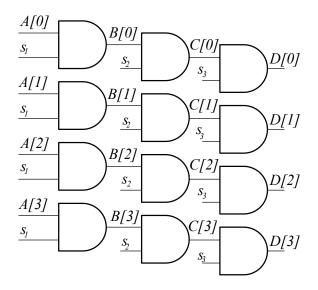

Figure 2.5: A CG with three stages of FFs. The vertex A is a PI, where the selection-edge is driven by *True*. The signals,  $s_1$ ,  $s_2$  and  $s_3$  represent the updating conditions for FFs  $F_1$ ,  $F_2$  and  $F_3$ , respectively.

Consider the CG in Figure 2.5, where  $F_1$ ,  $F_2$  and  $F_3$  are FFs, Q is a PO and  $s_1$ ,  $s_2$  and  $s_3$  are their corresponding control signals. Control signal  $s_1$  only can be from an observability clock-gating case, where a sufficient property for  $s_1$  being sequential stuck-at-1 is  $\mathbf{G}(\mathbf{X}s_2 \Rightarrow s_1)$ . The CG method cannot formulate observability clock-gating conditions across more than one time frame for  $F_1$  because there is a sequential loop due  $F_2$ .

For  $s_2$ , it can be a satisfiability clock-gating case with the property  $\mathbf{G}(s_1 \Rightarrow \mathbf{X}s_2)$  and  $s_2$  is 1 in the first time frame, or else an observability clock-gating case with the property  $\mathbf{G}(\mathbf{X}s_3 \Rightarrow s_1)$ .

$s_3$  can only be a satisfiability clock-gating case, and the sufficient condition requires (1)  $\mathbf{G}(s_2 \Rightarrow \mathbf{X}s_3)$  holds and (2) the initial condition of  $s_3$  is 1. The proposed algorithm terminates when trying to go across  $F_2$ , because its selection-edge is not driven by True.

The sufficient conditions proposed by the CG method can be proved on circuits by general hardware model checkers. As implied by the LTL safety properties, only the fanin cones of those control signals need to be considered by model checking, and hence irrelevant combinational logic will be excluded automatically by state-of-the-art model checking methods. Thus, when model checking the generated properties on the original circuit, the problem size is effectively much less.

There are some limitations on finding sequential redundancy on CGs. Currently each vertex on a CG covers all signals controlled by the same selection signal, so some sequentially redundant points may be missed. For example, if a set of FFs is clock-gated by a satisfiability condition with a control signal, s, while another set of FFs is clock-gated by an observability condition also with s, both cases could be legal but cannot be proved by the current formulation. This issue can be resolved by separating all FF into different vertices, but that may result in duplicate properties to be proved.

### 2.3 Overall Flow

Given two sequential circuits, golden (**G** and clock-gated, **R**), with a mapping correspondence between PIs and POs of the circuits, SEC verifies if the output sequences are identical when the same input sequences are applied. If **R** is known to be a clock-gated version of **G**, instead of applying general SEC methods, the difficulties of SEC can be reduced using the CG approach. Here the overall flow of this method is outlined.

As the use-model, it is assumed that the golden model  $\mathbf{G}$  may be already be clock-gated in the RTL, possibly manually by the designer. Therefore in comparing  $\mathbf{G}$  and  $\mathbf{R}$ , we propose to reduce them both with the CG method and apply the proved redundancies to get  $\mathbf{G}$ ' and  $\mathbf{R}$ ', which will be compared.

Algorithm 2.2 outlines an algorithm to perform SEC between two circuits,  $\mathbf{G}$  and  $\mathbf{R}$ , and report if they are sequentially equivalent( $\mathbf{EQ}$ ) or not( $\mathbf{NON-EQ}$ ).

The function CEC(...) at Line 1 performs general combinational equivalence checking between corresponding signals for each pair and returns a set of unproved pairs. The function charGraph(...) returns the corresponding characteristic graph for the specified circuit.

The loop between Lines 7 and 15 verifies each candidate and revises the corresponding CG according to the proved redundancy one by one. At Line 7, the function *comparison*(...) analyzes these unresolved pairs and proposes a candidate for sequential redundancy by comparing their CGs. The function defineProperty(...) applies the ideas in Section 2.2 for each target signal, and generates the set of corresponding LTL properties (**P**) to be proved. Notice that not only **R** but also **G** can contain sequential redundancies, so from Line 8 to 11, properties are defined for  $C_G$  or  $C_R$ , respectively.

```

Algorithm 2.2 Proposed SEC Flow

Require: G and R: two circuits with mapped PIs, POs and FFs.

Ensure: SEC result: EQ or NON-EQ

1: nonEQ = CEC(G, R)

2: if nonEQ = \emptyset then

return EQ

3:

4: C_G = charGraph(\mathbf{G})

5: C_R = charGraph(\mathbf{R})

6: proved = \emptyset

while candidate = comparison( nonEQ, C_G, C_R) do

7:

if candidate \in \mathbf{G} then

8:

\mathbf{P} = defineProperty(\mathbf{candidate}, C_G)

9:

10:

else

\mathbf{P} = defineProperty(\mathbf{candidate}, C_R)

11:

proof = multiProve(\mathbf{P})

12:

if isLegal(proof) then

13:

14:

revise(candidate, C_G, C_R)

proved = proved \cup candidate

15:

(\mathbf{G'}, \mathbf{R'}) = simplify(\mathbf{proved}, \mathbf{G}, \mathbf{R})

16:

17: return SEC(\mathbf{G'}, \mathbf{R'})

```

The function multiProve(...) at line 12 verifies a circuit with multiple outputs. Given a set of properties  $\mathbf{P}$ ,  $multiProve(\mathbf{P})$  verifies all properties simultaneously, and then returns the resulting set **proof**, which lists both proved and disproved properties. At Line 13,  $isLegal(\mathbf{proof})$  analyzes the result and determines if **candidate** is sequentially redundant using theorems stated in [12]. When any of the sufficient conditions proposed by the theorems is satisfied, the candidate is proved. Due to the possible dependencies among candidates, the corresponding CG should be revised using proved redundancies before the next run. All proved candidates are used to simplify  $\mathbf{G}$  and  $\mathbf{R}$  into  $\mathbf{G}$ ' and  $\mathbf{R}$ ' at once (Line 16).

Finally, we perform  $SEC(\mathbf{G'}, \mathbf{R'})$  to check if  $\mathbf{G'}$  and  $\mathbf{R'}$  are sequentially equivalent. If  $\mathbf{G'}$  and  $\mathbf{R'}$  are proved to be **NON-EQ**,  $SEC(\mathbf{G'}, \mathbf{R'})$  can return a counter-example, which is also valid for  $\mathbf{G}$  and  $\mathbf{R}$ . Therefore, the proposed algorithm can provide counter-examples to users for debugging.

A limitation of the structural approach used is that previous synthesis done on **R** might have destroyed some of the MUX structures in the circuit. Then some MUXes might not be recognized during the CG construction and thus the algorithm might fail to identify all sequentially redundant points. In any case, as much redundancy as possible is identified. The resulting simplification might be enough for SEC to still be able to prove the property.

To show how this algorithm works, consider the circuits in Figure 2.1 and 2.4 as **G** and **R** respectively. At line 1, only the pair for  $F_2$  fails CEC and is added into **nonEQ**. At Line

7, E, the selection signal of  $F_2$ , is a candidate of sequential stuck-at-1 redundancy. Since it can only be observability clock-gating, the corresponding property,  $\mathbf{G}(\mathbf{X}F_1 \Rightarrow E)$ , is created and proved. Then  $\mathbf{R}$  is simplified into  $\mathbf{R}$ ' by replacing the selector of the MUX of  $F_2$  by constant 1, while  $\mathbf{G}$ ' is the same as  $\mathbf{G}$ . Therefore  $\mathbf{G}$ ' and  $\mathbf{R}$ ' become identical to Figure 2.1, and can be proved equivalent by SEC easily. Finally, the algorithm returns that  $\mathbf{G}$  and  $\mathbf{R}$  are sequentially equivalent.

### 2.4 Experimental Results

We compare the CG method against two state-of-the-art methods.

- 1. Model checker *super\_prove* [7]. This is a general purpose gate-level model-checker, which won the single-output track in the Hardware Model Checking Competition 2014 (HWMCC'14) [17].

- 2. *Absec*, a command implemented in ABC [8] which uses the algorithm in [40]. This is specific to checking clock-gated circuits. It unrolls the circuit a determined number of clock cycles and uses CEC to prove the desired result.

The CG method,  $SEC(\mathbf{G}, \mathbf{R})$  is implemented in ABC. The *multiProve*(...) function used is *multi\_prove*, which won the multi-output track in HWMCC'13 [16] (not held since). We also apply *super\_prove* to the final SEC between **G'** and **R'**.

All experiments were performed on a 16-core 2.60GHz Intel(R) Xeon(R) CPU with a 1500 second time limit. The example circuits were clock-gated manually at the RTL, and then synthesized into AIGs to create  $\mathbf{R}$ . Each input for *super\_prove* is a multi-output miter between a golden design ( $\mathbf{G}$ ) and its clock-gated circuit ( $\mathbf{R}$ ). The inputs for *Absec* and the CG method are  $\mathbf{G}$  and  $\mathbf{R}$  are given separately before mitering.

#### 2.4.1 Performance for General Clock-Gated Cases