## Millimeter-Wave/Terahertz Circuits and Systems for Wireless Communication

Siva Viswanathan Thyagarajan

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2016-22 http://www.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-22.html

May 1, 2016

Copyright © 2016, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Millimeter-Wave/Terahertz Circuits and Systems for Wireless Communication

by

Siva Viswanathan Thyagarajan

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Elad Alon Professor Paul K. Wright

Spring 2014

Millimeter-Wave/Terahertz Circuits and Systems for Wireless Communication

Copyright  $\bigodot$  2014

by

Siva Viswanathan Thyagarajan

#### Abstract

Millimeter-Wave/Terahertz Circuits and Systems for Wireless Communication

by

Siva Viswanathan Thyagarajan Doctor of Philosophy in Electrical Engineering and Computer Sciences

> University of California, Berkeley Professor Ali M. Niknejad, Chair

The ubiquitous use of electronic devices has led to an explosive increase in the amount of data transfer across the globe. Several applications such as media sharing, cloud computing, Internet of things (IoT), big-data applications demand high performance interconnects to achieve high data rate communication. The mm-wave/terahertz band offers several gigahertz of spectrum for high data rate communication applications. This thesis explores millimeter-wave/terahertz circuits and terahertz systems for various applications in CMOS technology. Some of them include links for personal area networks, wireless backhauls, chip to chip communication (short-range) links in form factor constrained devices (wireless in a box) and also for long-range high-speed communication (using phased arrays or lenses).

In particular, this research explores the feasibility of millimeter-wave/terahertz systems and also the performance of critical blocks such as power amplifiers. A linear power amplifier is designed in a deeply scaled technology node (28 nm) and the various challenges in the design process are discussed. The performance is validated using measurement results and compared across various technology nodes. Non-linear millimeter-wave switching power amplifiers are also explored due to their high efficiencies and a prototype is fabricated to verify the modeling and simulation results.

The ideas and modeling strategies from the individual blocks are used in the design of mm-wave/terahertz transceivers. Simple modulation schemes such as on-off keying, binary phase shift keying and quadrature phase shift keying are used for transmission of data. Two transceiver prototypes with different transmitter and receiver architectures are fabricated in bulk CMOS technology. The system level considerations and architecture choices are discussed. Theoretical analysis of critical blocks with design choices are explained along with their implementation details. The system level measurements from the two transceivers confirm the feasibility of such links at millimeter-wave/terahertz frequencies. The work from this thesis demonstrates the world's first fully functional link at frequencies greater than 200 GHz in CMOS technology.

To my parents, brother, sister, extended family and mentors

# Contents

| Co       | onten       | ts                                                  | ii           |

|----------|-------------|-----------------------------------------------------|--------------|

| Li       | st of       | Figures                                             | $\mathbf{v}$ |

| Li       | st of       | Tables                                              | xiii         |

| Ac       | cknov       | wledgments                                          | xiv          |

| 1        | Intr        | oduction                                            | 1            |

|          | 1.1         | Communication in the 60 GHz band                    | 2            |

|          | 1.2         | Communication beyond $100 \mathrm{GHz}$             | 4            |

|          | 1.3         | Organization of the dissertation                    | 6            |

| <b>2</b> | <b>A</b> 60 | GHz Wideband Power Amplifier in 28nm CMOS           | 7            |

|          | 2.1         | 28 nm technology : Actives and Passives             | 8            |

|          | 2.2         | Power Amplifier Design                              | 10           |

|          |             | 2.2.1 Power Combiner/Splitter                       | 12           |

|          |             | 2.2.2 Drain-Source Neutralized Cascode Stages       | 15           |

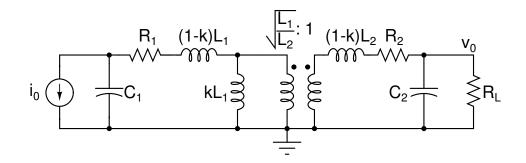

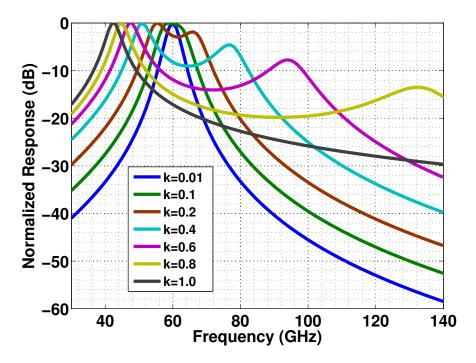

|          |             | 2.2.3 Low Coupling Coefficient Transformer Networks | 19           |

|          |             | 2.2.4 Pre-driver stage                              | 22           |

|          |             | 2.2.5 Sizing of the amplifier stages                | 22           |

|          | 2.3         | Measurement Results                                 | 22           |

|          | 2.4         | Conclusion                                          | 28           |

| 3        | Tera        | ahertz Transceiver : System level considerations    | 30           |

|          | 3.1         | Choice of the carrier frequency                     | 30           |

|          | 3.2 | Challenges in the transmitter and receiver design                            | 31 |

|----------|-----|------------------------------------------------------------------------------|----|

|          | 3.3 | Modulation Schemes                                                           | 32 |

|          |     | 3.3.1 On-off Keying (OOK)                                                    | 33 |

|          |     | 3.3.2 Phase Shift Keying - Binary (BPSK) and Quadrature (QPSK)               | 33 |

|          | 3.4 | Link budget                                                                  | 35 |

|          | 3.5 | Choice of the intermediate frequency $(IF)$                                  | 37 |

|          | 3.6 | Local Oscillator (LO) Phase Noise                                            | 39 |

|          | 3.7 | Other issues                                                                 | 43 |

|          | 3.8 | Conclusion                                                                   | 43 |

| 4        | A 2 | 60 GHz Wireless Transceiver in 65 nm CMOS                                    | 44 |

|          | 4.1 | Transceiver architecture                                                     | 44 |

|          | 4.2 | Millimeter-Wave Inverse Class-D Switching Power Amplifier                    | 46 |

|          |     | 4.2.1 Modeling of active devices                                             | 47 |

|          |     | 4.2.2 Switching Power Amplifier Design                                       | 53 |

|          |     | 4.2.3 Standalone Measurement Results                                         | 57 |

|          |     | 4.2.4 PA design in the sub-terahertz transceiver                             | 60 |

|          | 4.3 | Modulator Design                                                             | 60 |

|          | 4.4 | IF Amplifier Design                                                          | 61 |

|          | 4.5 | Other blocks                                                                 | 72 |

|          | 4.6 | Measurement Results                                                          | 72 |

|          | 4.7 | Conclusion                                                                   | 76 |

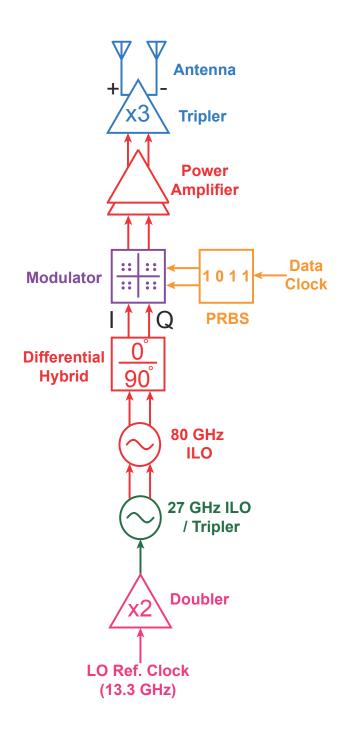

| <b>5</b> | A 2 | 40 GHz QPSK Wireless Transceiver in 65 nm CMOS - Part I                      | 78 |

|          | 5.1 | Transmitter Architecture                                                     | 78 |

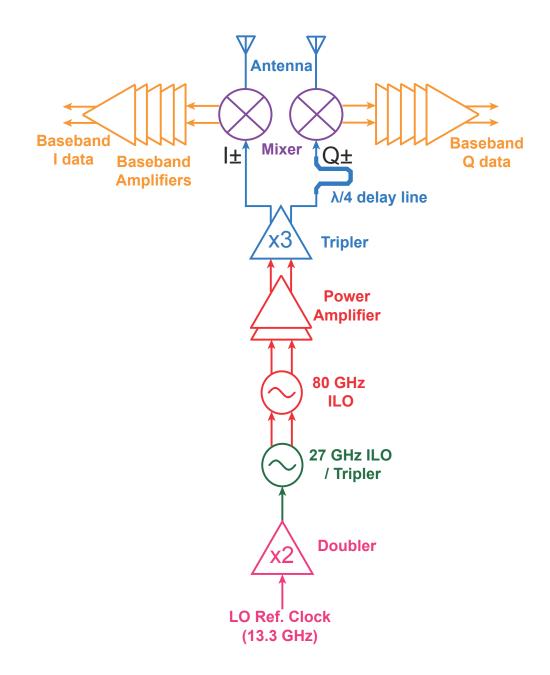

|          | 5.2 | Receiver Architecture                                                        | 80 |

|          | 5.3 | Antenna Design                                                               | 80 |

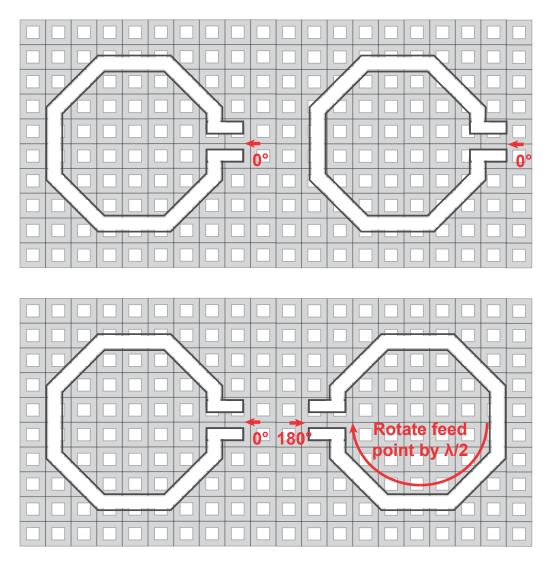

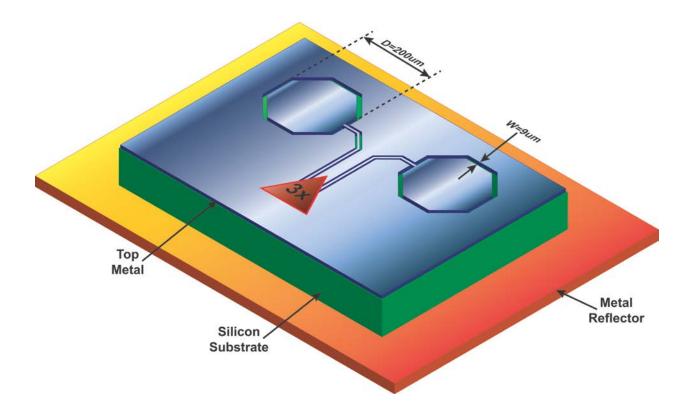

|          |     | 5.3.1 Transmitter Antenna Structure                                          | 82 |

|          |     | 5.3.2 Receiver Antenna Structure                                             | 86 |

|          |     | 5.3.3 Transmitter/Receiver Combined Link                                     | 88 |

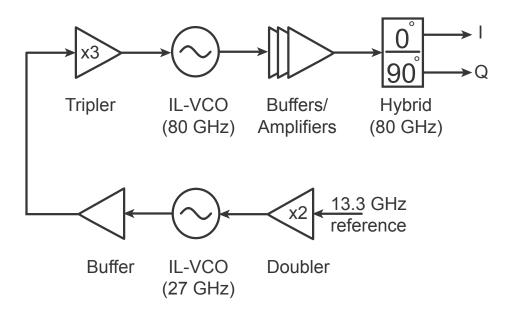

|          | 5.4 | LO Architecture                                                              | 90 |

|          |     | 5.4.1 Comparison of various architectures for $80\mathrm{GHz}$ LO generation | 90 |

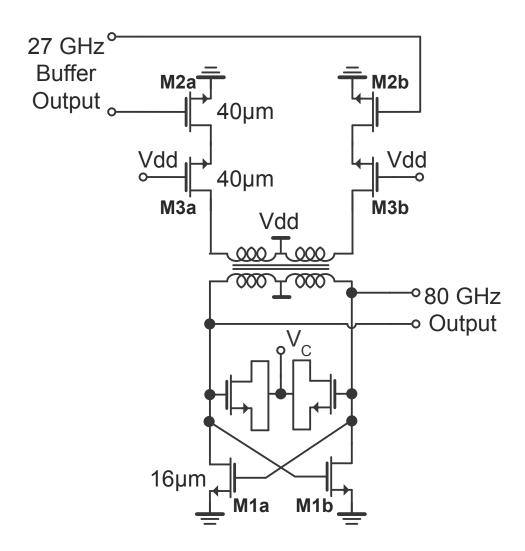

|    |        | 5.4.2           | $80{\rm GHz}$ Injection-locked voltage controlled oscillator | 93  |

|----|--------|-----------------|--------------------------------------------------------------|-----|

|    |        | 5.4.3           | 80 GHz LO chain amplifiers                                   | 97  |

|    |        | 5.4.4           | 27 GHz injection-locked voltage controlled oscillator        | 104 |

|    |        | 5.4.5           | 27 GHz buffer                                                | 105 |

|    |        | 5.4.6           | Hybrid design                                                | 106 |

|    |        | 5.4.7           | Simulation Results of the complete LO Chain                  | 115 |

|    | 5.5    | Concl           | usion                                                        | 117 |

| 6  | A 2    | $40\mathrm{GH}$ | z QPSK Wireless Transceiver in 65 nm CMOS - Part II          | 118 |

|    | 6.1    | Sub-T           | Perahertz Mixer Design                                       | 118 |

|    |        | 6.1.1           | Sub-Terahertz Active Mixer                                   | 119 |

|    |        | 6.1.2           | Sub-Terahertz Passive Mixer                                  | 123 |

|    |        | 6.1.3           | 240 GHz Passive Mixer Design                                 | 129 |

|    |        | 6.1.4           | 240 GHz In-phase/Quadrature Phase Generation                 | 130 |

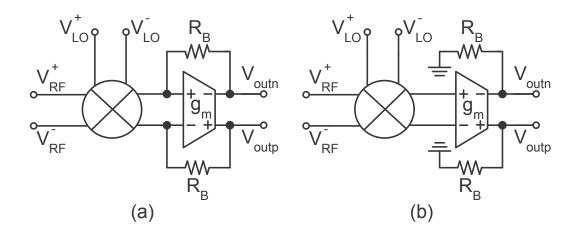

|    | 6.2    | Choice          | e of the baseband amplifier                                  | 131 |

|    | 6.3    | Other           | blocks                                                       | 134 |

|    | 6.4    | Measu           | rement Results                                               | 135 |

|    |        | 6.4.1           | Transmitter Measurements                                     | 135 |

|    |        | 6.4.2           | Transmitter-Receiver Wireless Link Measurements              | 147 |

|    | 6.5    | Concl           | usion                                                        | 159 |

| 7  | Cor    | nclusio         | n                                                            | 162 |

|    | 7.1    | Thesis          | 5 Summary                                                    | 162 |

|    | 7.2    | Future          | e Directions                                                 | 163 |

| Bi | ibliog | graphy          |                                                              | 165 |

# List of Figures

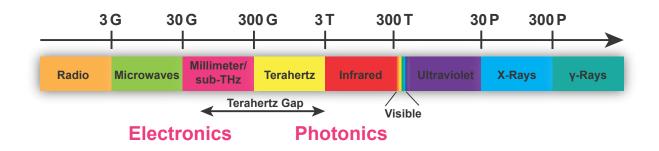

| 1.1  | Electromagnetic spectrum showing the millimeter/terahertz region                                                                                                                                        | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Millimeter-wave/terahertz networks for personal area networks [left] and wire-<br>less backhauls [right]                                                                                                | 3  |

| 1.3  | Futuristic flexible device with wireless interconnects                                                                                                                                                  | 4  |

| 1.4  | Flexible device can be upgraded by attaching two such devices and the chips communicate with each other wirelessly                                                                                      | 5  |

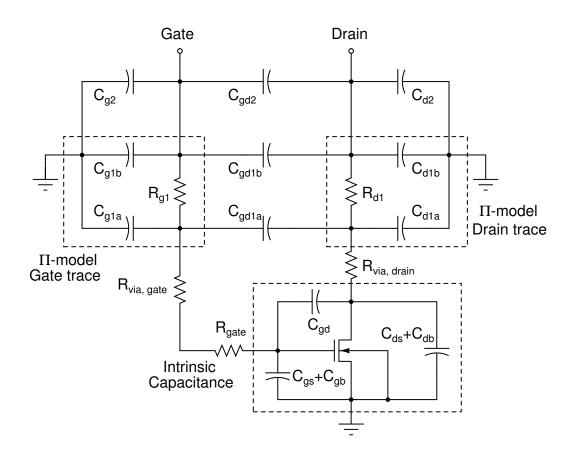

| 2.1  | Model of unit finger of the active device                                                                                                                                                               | 9  |

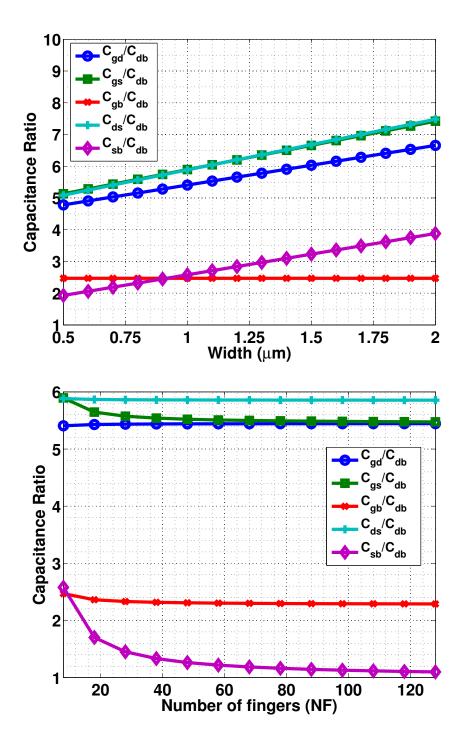

| 2.2  | Wiring capacitance ratio as a function of width (NF=8) and number of fingers $(W=1 \mu m) \dots $ | 11 |

| 2.3  | Transformer passive network with dummy metal layers                                                                                                                                                     | 12 |

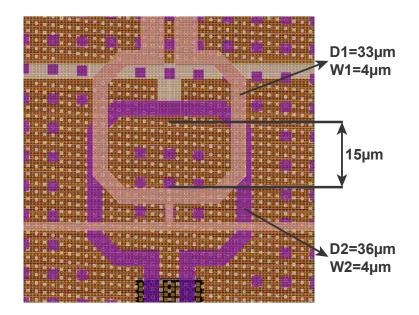

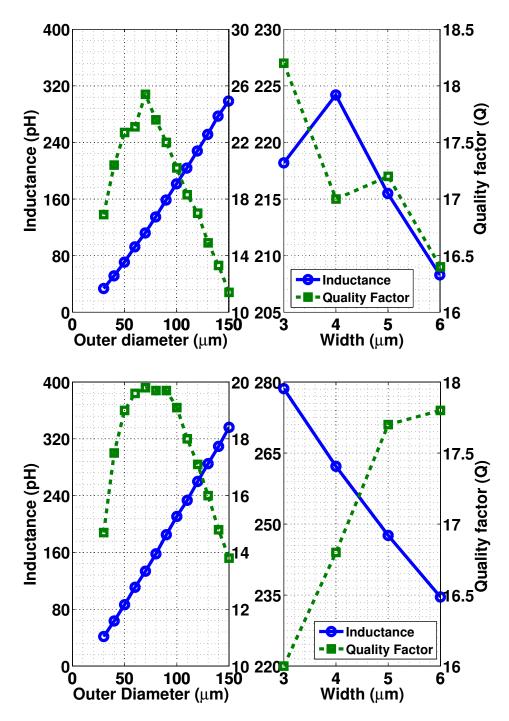

| 2.4  | Simulated spiral inductance and quality factor as a function of outer diameter $(W = 4 \mu\text{m})$ and width $(D_{out} = 120 \mu\text{m})$ for ultra-thick metal [Top] and Alucap [Bottom] layers     | 13 |

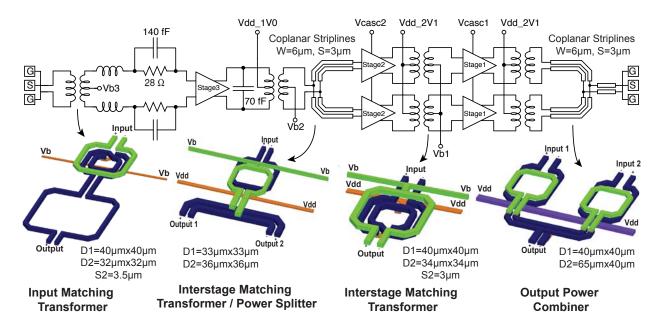

| 2.5  | Circuit diagram of the overall power amplifier with the matching network structures                                                                                                                     | 14 |

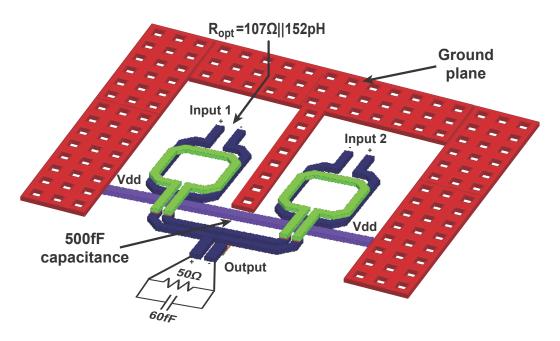

| 2.6  | Transmission line based output power combiner                                                                                                                                                           | 14 |

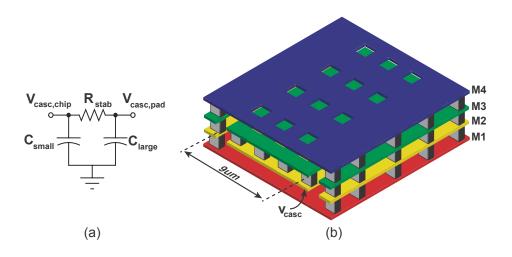

| 2.7  | (a) Conventional cascode gate stabilization network (b) Shielded cascode gate : M2/M3 signal, M1/M4 ground shield                                                                                       | 16 |

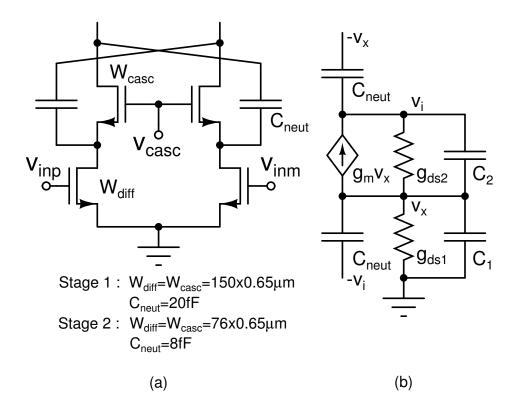

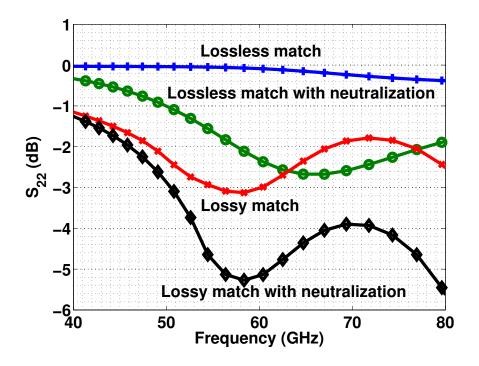

| 2.8  | (a) Circuit diagram of the output and interstage networks (b) Small signal equivalent circuit                                                                                                           | 16 |

| 2.9  | Simulated output reflection coefficient $S_{22}$                                                                                                                                                        | 18 |

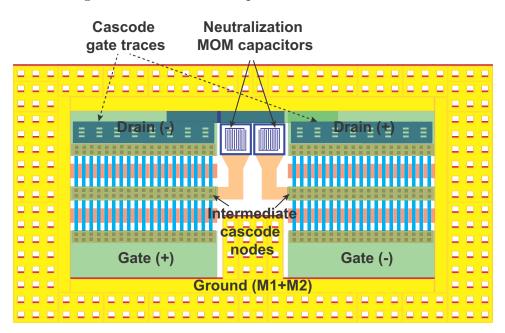

| 2.10 | Layout of the output and interstage devices                                                                                                                                                             | 18 |

| 2.11 | Equivalent model of the transformer matching network $\ldots \ldots \ldots \ldots$                                                                                                                      | 19 |

| 2.12 | Variation of the filter response as a function of the transformer coupling coefficient 'k'                                                                                                              | 19 |

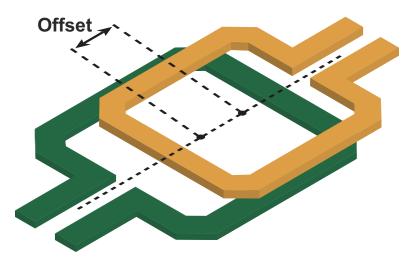

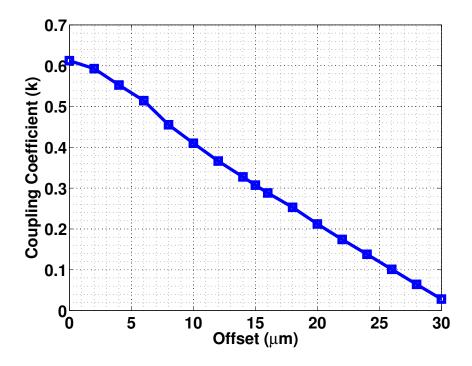

| 2.13 | Transformer implemented using square spirals : Coupling coefficient is varied by changing the offset                                                                                                                                      | 21 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Simulated coupling coefficient of a transformer implemented using square spirals                                                                                                                                                          | 21 |

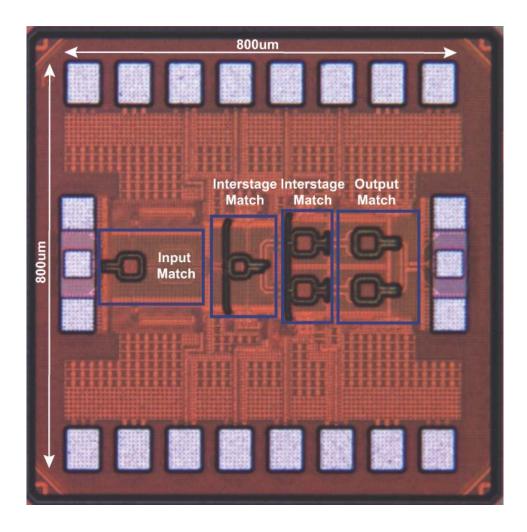

| 2.15 | Chip microphotograph                                                                                                                                                                                                                      | 23 |

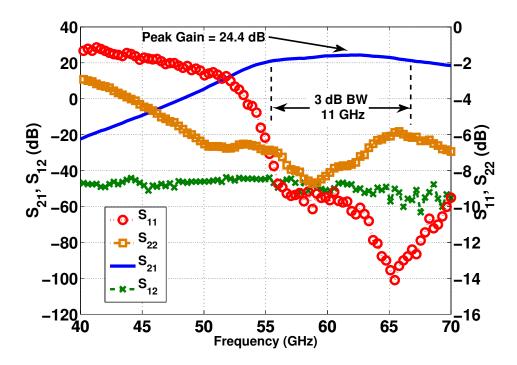

| 2.16 | Measured S-parameters                                                                                                                                                                                                                     | 24 |

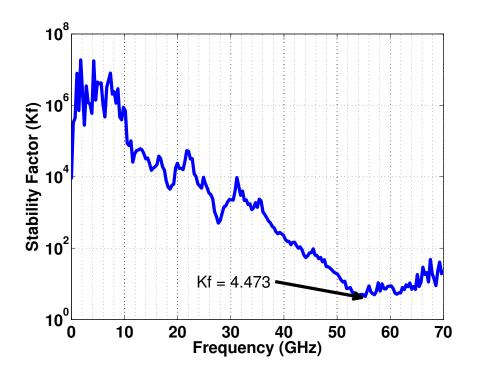

| 2.17 | Measured stability factor as a function of frequency $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                          | 24 |

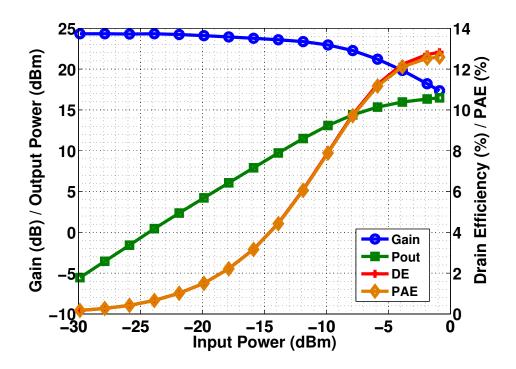

| 2.18 | Measured gain, output power, drain efficiency and power-added efficiency as a function of the input power at 62 GHz                                                                                                                       | 25 |

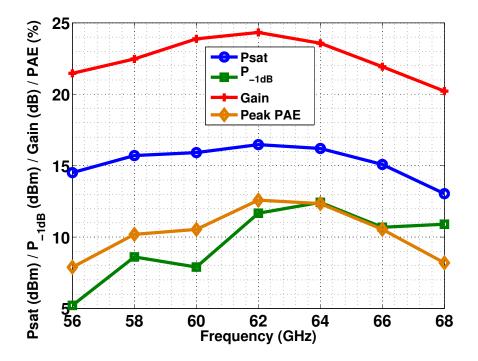

| 2.19 | Measured small signal gain, Psat, $P_{-1dB}$ and power-added efficiency as a function of frequency $\ldots \ldots \ldots$ | 25 |

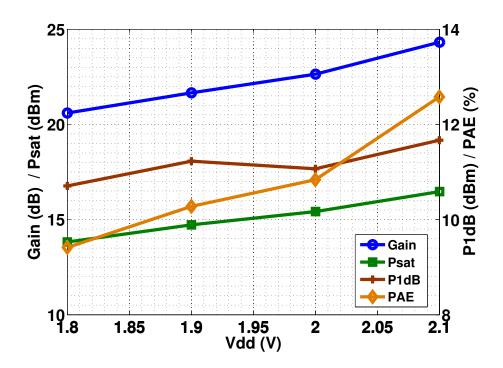

| 2.20 | Measured small signal gain, Psat, $P_{-1dB}$ and power-added efficiency as a function of supply voltage at $62 \text{ GHz}$                                                                                                               | 26 |

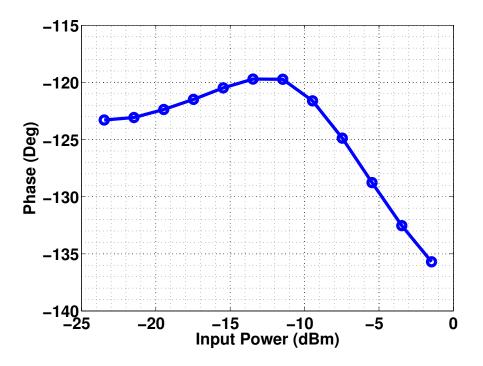

| 2.21 | Measured AM-to-PM distortion at $62\mathrm{GHz}$                                                                                                                                                                                          | 27 |

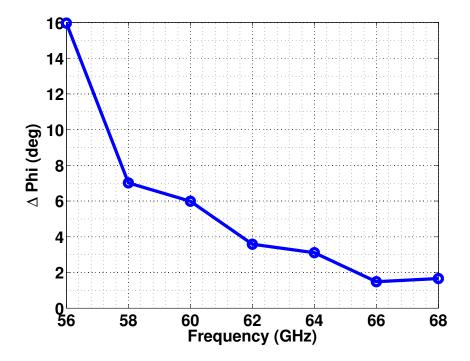

| 2.22 | Measured peak phase overshoot (AM-to-PM) as function of frequency                                                                                                                                                                         | 27 |

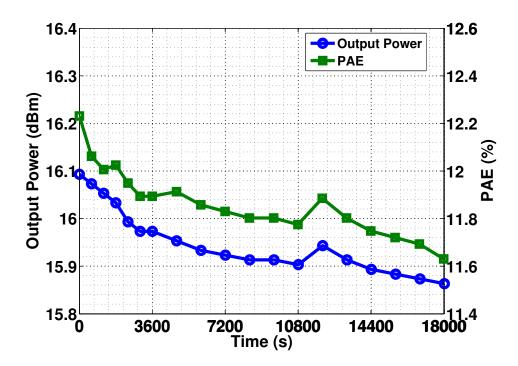

| 2.23 | Measured output power and power-added efficiency due to RF stress                                                                                                                                                                         | 28 |

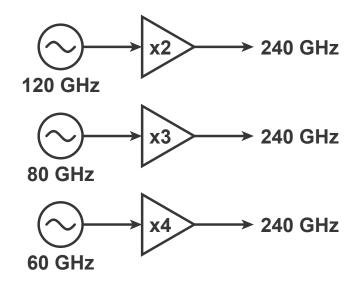

| 3.1  | Harmonic generation techniques to generate a carrier of $240\mathrm{GHz}$                                                                                                                                                                 | 31 |

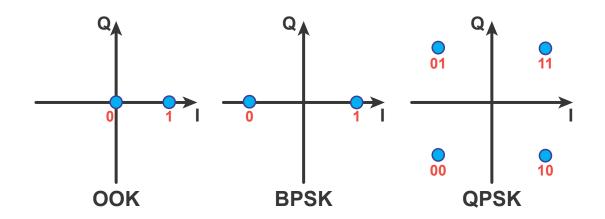

| 3.2  | Constellation diagrams for OOK, BPSK and QPSK modulation schemes $~$                                                                                                                                                                      | 32 |

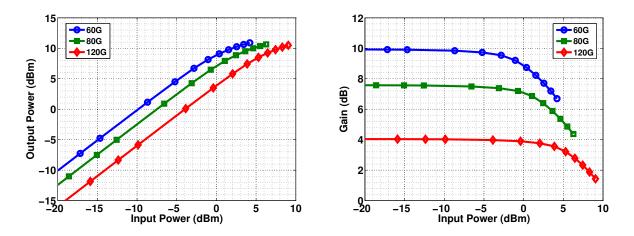

| 3.3  | Simulated output power [left] and gain [right] as a function of input power at $60 \text{ GHz}$ , $80 \text{ GHz}$ and $120 \text{ GHz}$ for a $54 \mu\text{m}$ device $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$          | 37 |

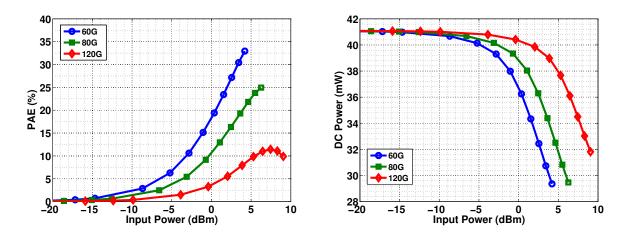

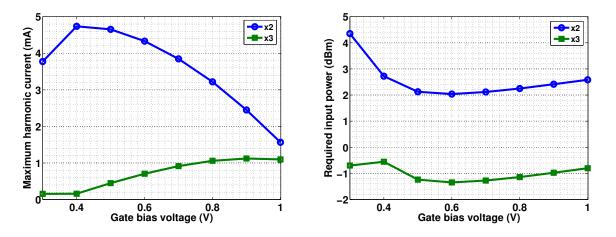

| 3.4  | Simulated power added efficiency [left] and DC power consumption [right] as a function of input power at 60 GHz, 80 GHz and 120 GHz for a 10 $\mu$ m device                                                                               | 38 |

| 3.5  | Maximum harmonic current [left] and the corresponding required input power [right] as a function of the gate bias voltage for a $\times 2$ (doubler) and $\times 3$ (tripler)                                                             | 38 |

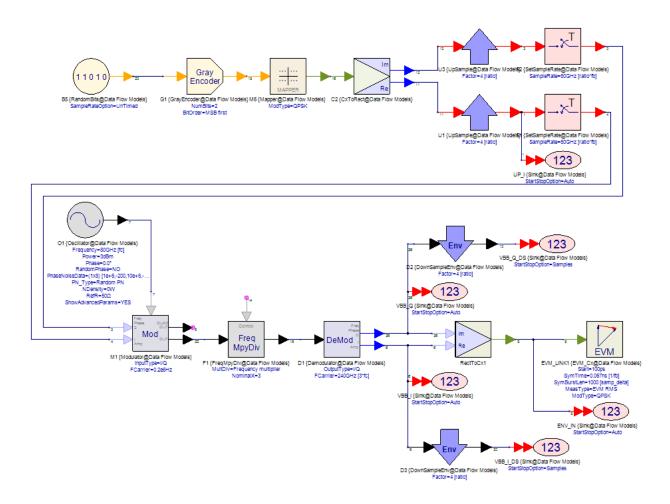

| 3.6  | Block diagram of the transceiver with LO phase noise                                                                                                                                                                                      | 40 |

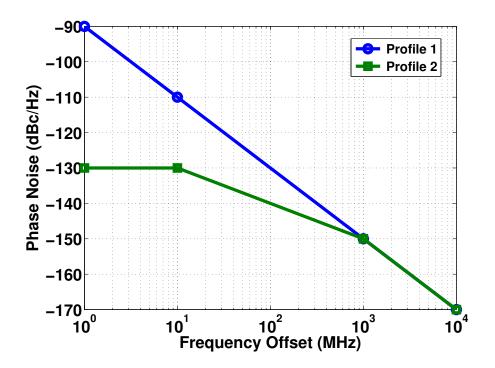

| 3.7  | Phase noise profiles for the 80 GHz oscillator $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                  | 41 |

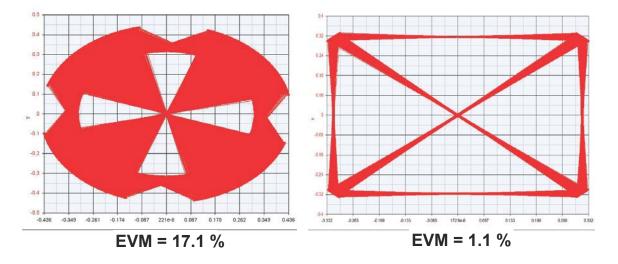

| 3.8  | Simulation constellation diagram and error vector magnitude (QPSK modulation) with the two phase noise profile - profile 1 [left] and profile 2 [right] $$ .                                                                              | 41 |

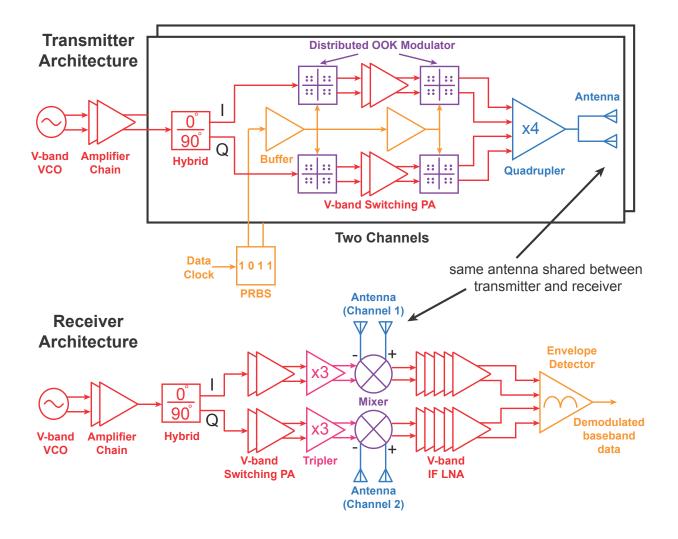

| 4.1  | Block diagram of transceiver architecture                                                                                                                                                                                                 | 45 |

| 4.2  | Inverse class-D amplifier with the switch model                                                                                                                                                                                           | 47 |

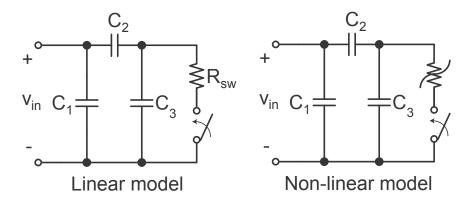

| 4.3  | Linear and non-linear switch models with device parasitics                                                                                                                                                                                | 47 |

| 4.4  | Comparison between linear switch model and BSIM model $\hdots$                                                                                                                                                                            | 48 |

| 4.5  | Comparison between non-linear switch model and BSIM model                                                                                                                                                                                 | 49 |

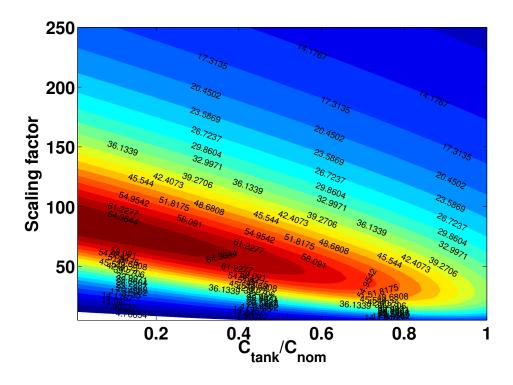

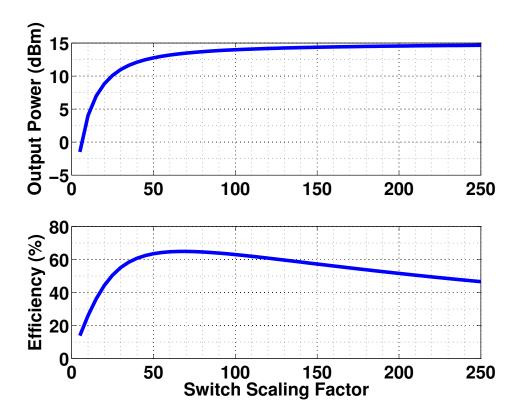

| 4.6  | Drain efficiency contours using ideal output match for $100 \Omega$ load and quality factor of 3        | 50 |

|------|---------------------------------------------------------------------------------------------------------|----|

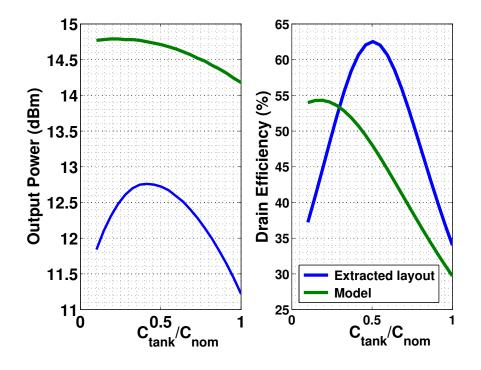

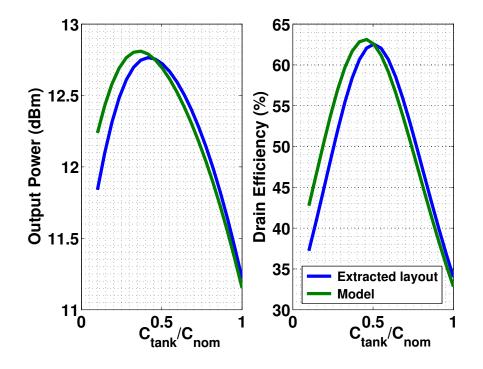

| 4.7  | Output power and drain efficiency with the tank inductance tuned to the switch capacitance              | 51 |

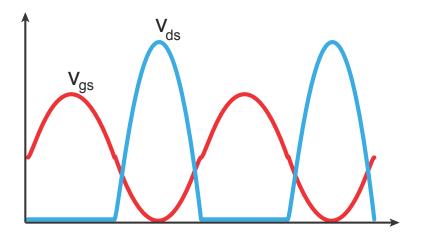

| 4.8  | Inverse class-D waveforms                                                                               | 51 |

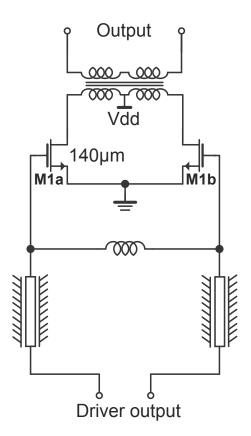

| 4.9  | Schematic of the Inverse class-D power amplifier                                                        | 52 |

| 4.10 | Output transformer matching network                                                                     | 53 |

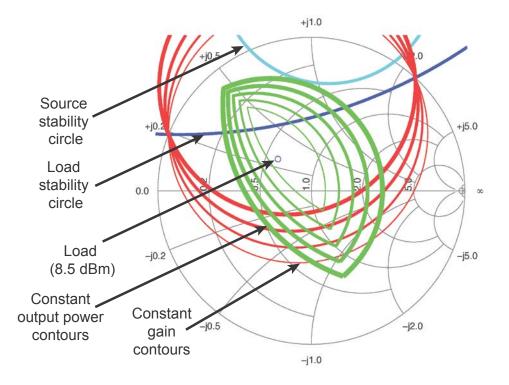

| 4.11 | Driver stage design - output power and gain contours, load stability circle and source stability circle | 54 |

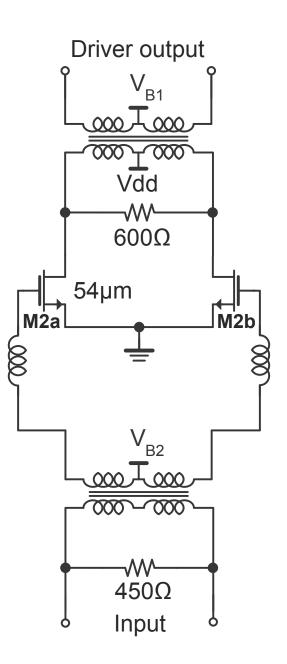

| 4.12 | Schematic of the Inverse class-D power amplifier driver stage                                           | 55 |

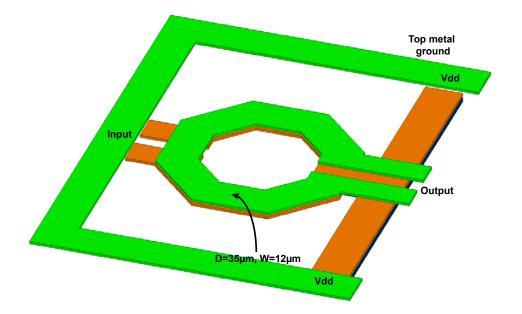

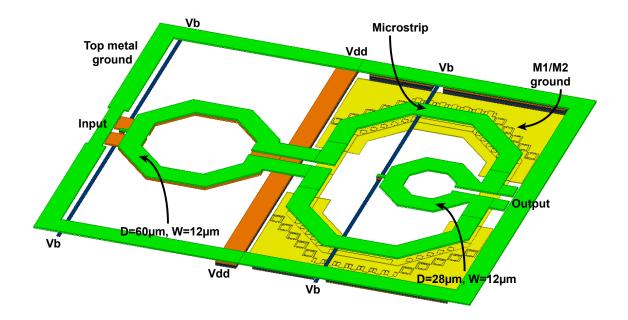

| 4.13 | Interstage inductor, microstrip, transformer based network                                              | 56 |

| 4.14 | Input transformer matching network                                                                      | 56 |

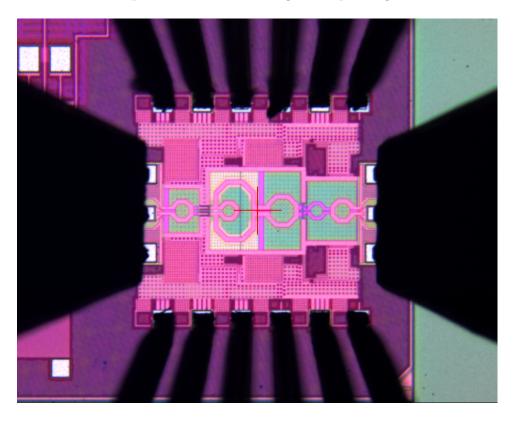

| 4.15 | Chip microphotograph of the switching power amplifier with probe landing .                              | 57 |

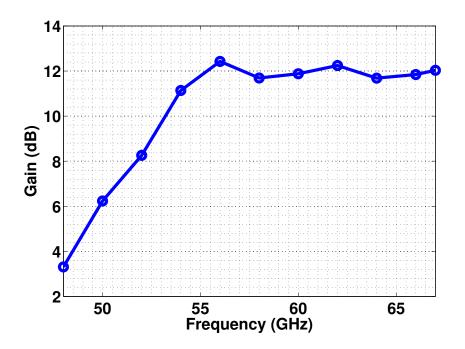

| 4.16 | Measured gain of the switching power amplifier as a function of frequency                               | 58 |

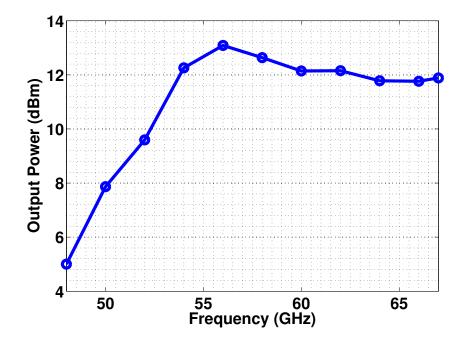

| 4.17 | Measured output power of the switching power amplifier as a function of frequency                       | 58 |

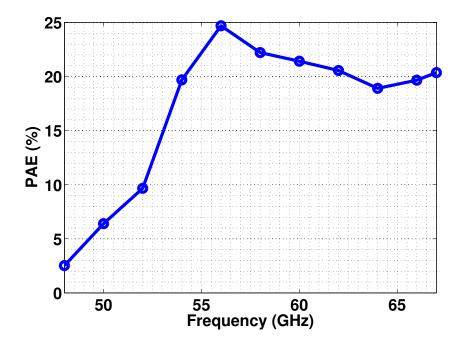

| 4.18 | Measured power added efficiency (PAE) of the switching power amplifier as a function of frequency       | 59 |

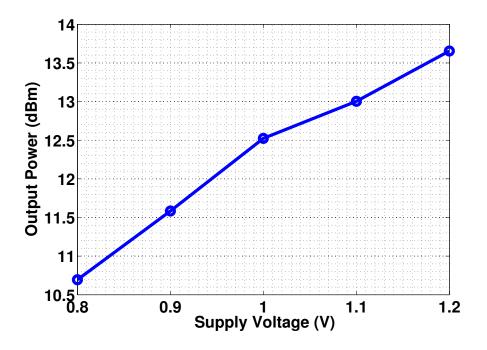

| 4.19 | Measured output power of the switching power amplifier as a function of the supply voltage              | 59 |

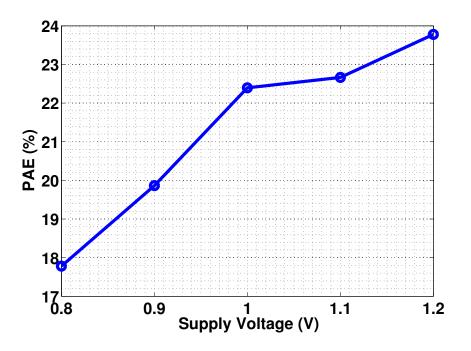

| 4.20 | Measured PAE of the switching power amplifier as a function of the supply voltage                       | 60 |

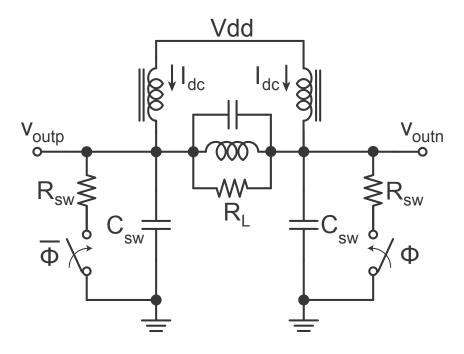

| 4.21 | Schematic of the voltage mode modulator                                                                 | 61 |

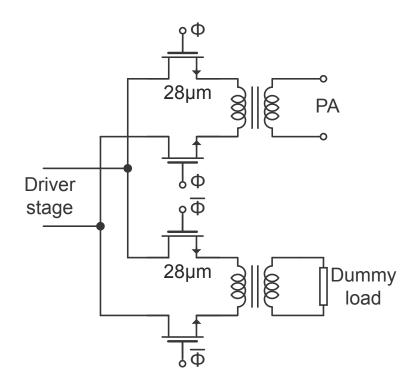

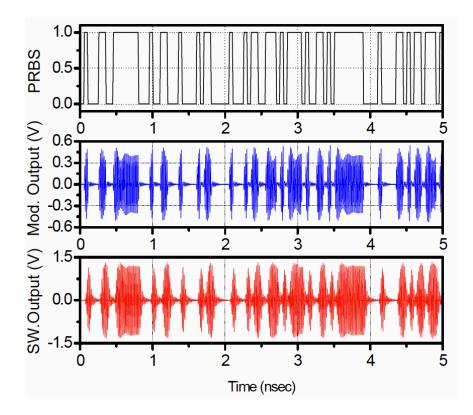

| 4.22 | Simulated modulator output and PA output with PRBS input waveform $\ $ .                                | 62 |

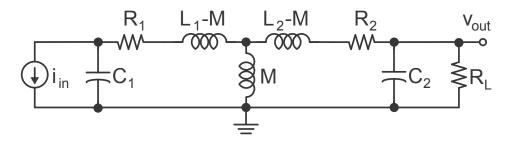

| 4.23 | Transformer equivalent model                                                                            | 63 |

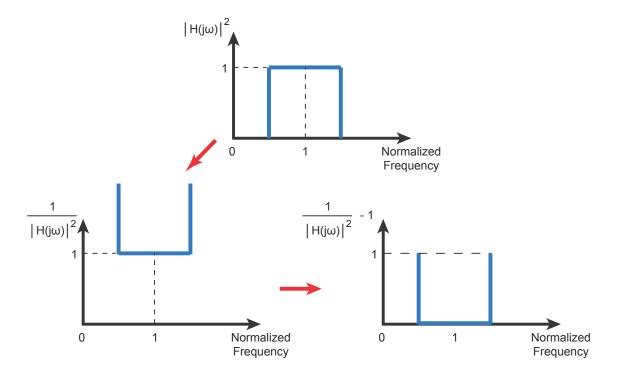

| 4.24 | Procedure to obtain maximally flat bandpass response                                                    | 64 |

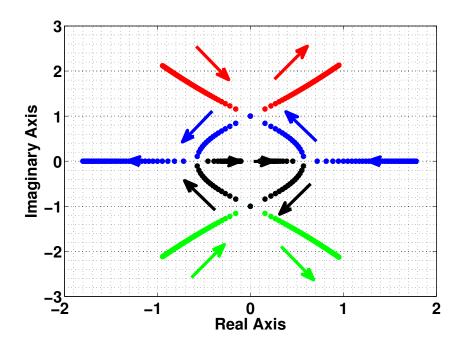

| 4.25 | Root locus plot of the maximally flat transfer function                                                 | 66 |

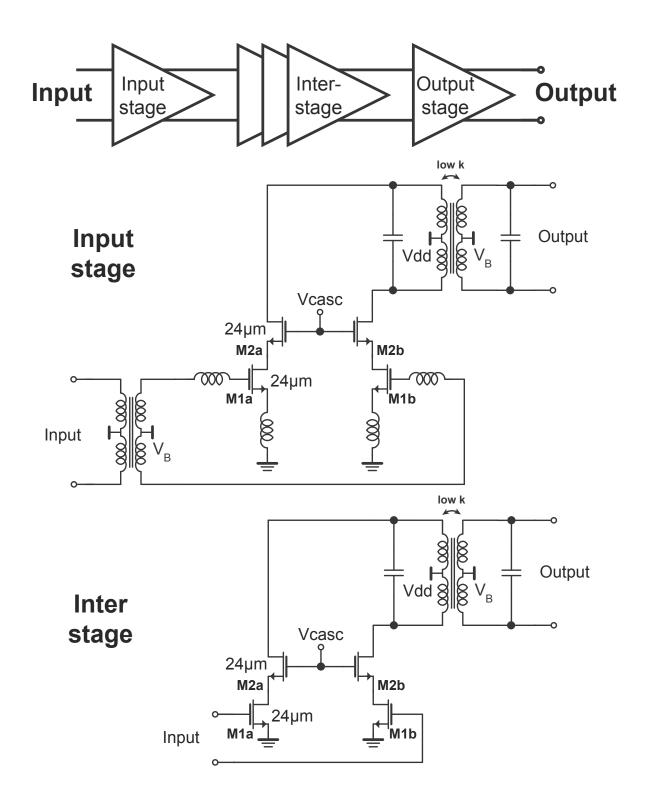

| 4.26 | Schematic of the five stage IF amplifier with the input and interstage networks                         | 67 |

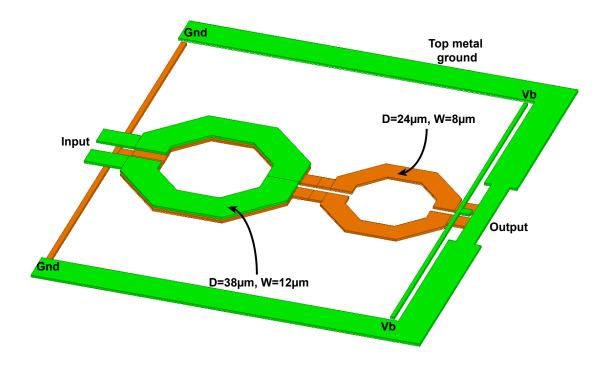

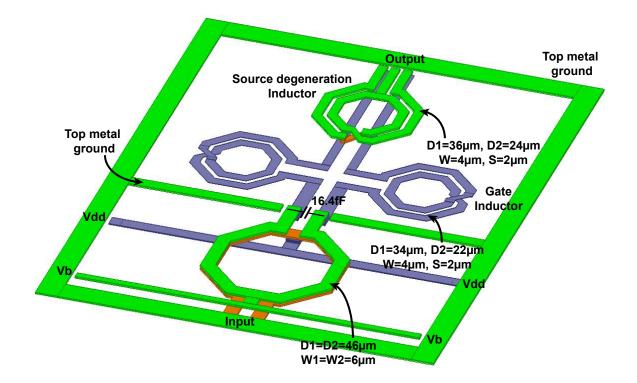

| 4.27 | Layout of the input matching network with degenerating inductors                                        | 68 |

| 4.28 | Layout of the low-k transformer matching network                                                        | 68 |

| 4.29 | Layout of the output transformer matching network                                                       | 69 |

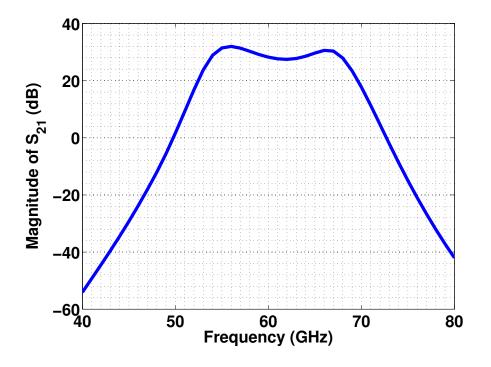

| 4.30 | Simulated gain $(S_{21})$ of the IF amplifier                                                           | 70 |

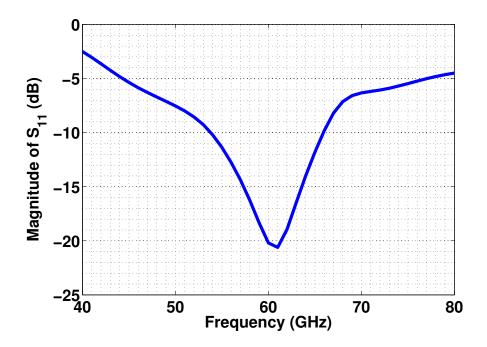

| 4.31 | Simulated gain $(S_{11})$ of the IF amplifier                                                           | 70 |

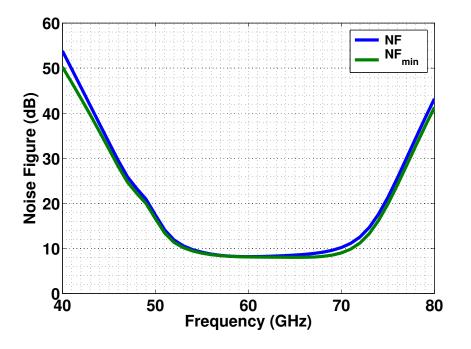

| 4.32 | Simulated noise figure of the IF amplifier                                                              | 71 |

|      |                                                                                                         |    |

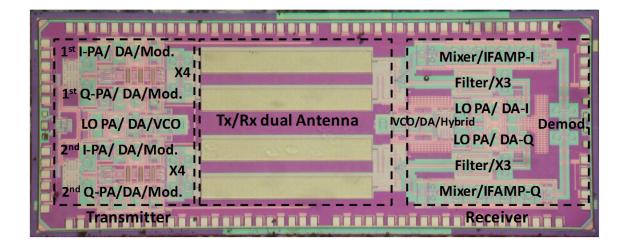

| 4.33 | Chip microphotograph of the transceiver                                                                                  | 73 |

|------|--------------------------------------------------------------------------------------------------------------------------|----|

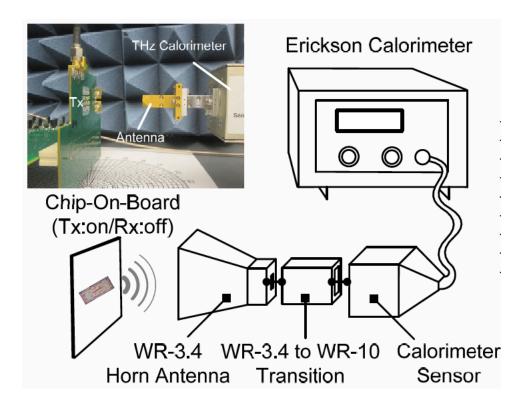

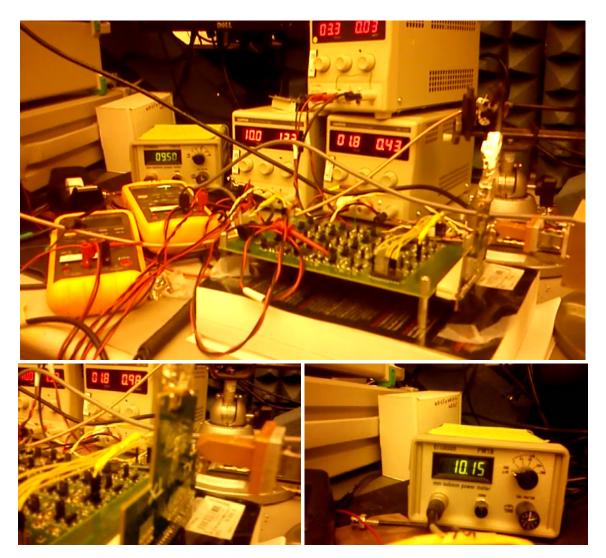

| 4.34 | Equivalent isotropic equivalent power (EIRP) measurement setup using calorimeter                                         | 73 |

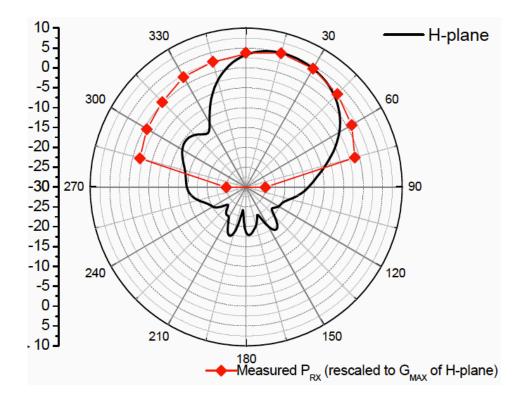

| 4.35 | Measured and simulated antenna pattern                                                                                   | 74 |

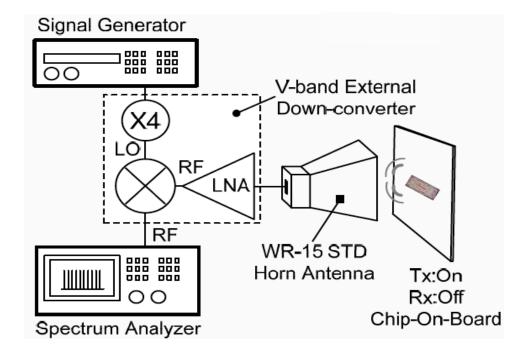

| 4.36 | Transmitter spectrum measurement setup using an external down-converter .                                                | 74 |

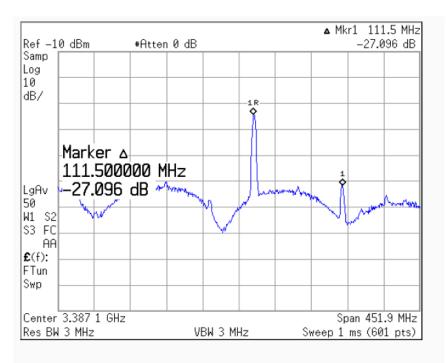

| 4.37 | Down-converted transmitter spectrum for $14 \mathrm{Gbps}$ data $\ldots \ldots \ldots \ldots$                            | 75 |

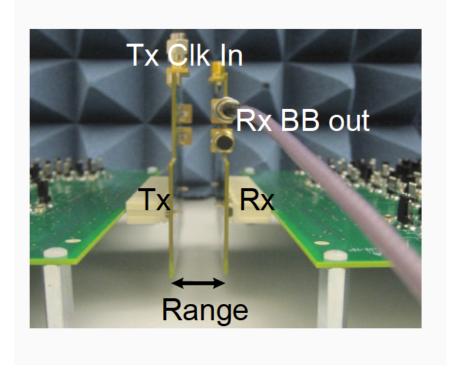

| 4.38 | Link measurement setup                                                                                                   | 75 |

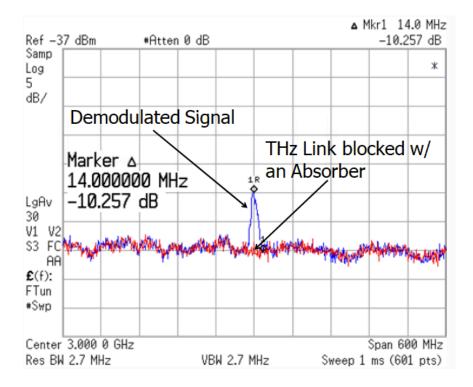

| 4.39 | Link measurement for a continuous wave (CW) signal with and without absorber                                             | 76 |

| 5.1  | Transmitter architecture                                                                                                 | 79 |

| 5.2  | Receiver architecture                                                                                                    | 81 |

| 5.3  | Beam forming with feed point rotation and input phase shift for a slotted loop antenna array                             | 83 |

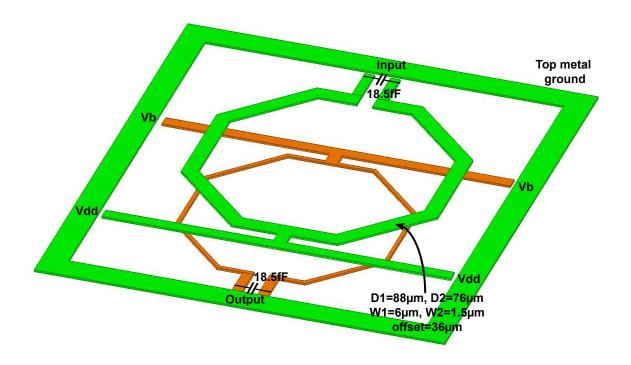

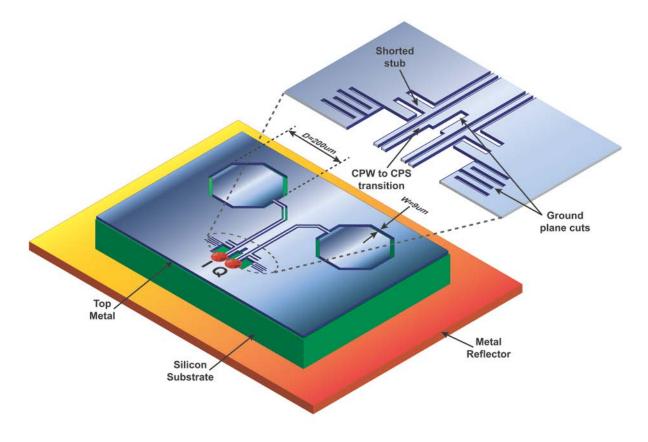

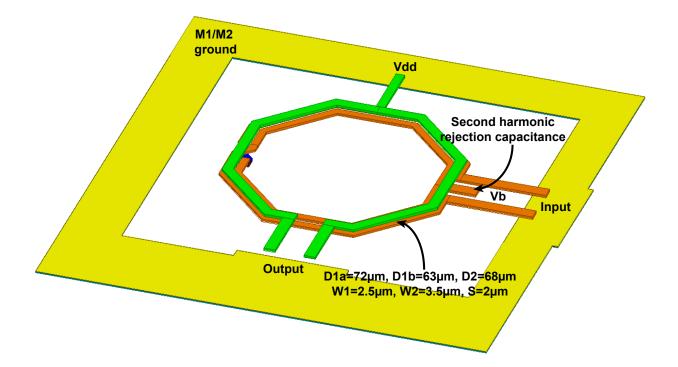

| 5.4  | Structure of transmitter slotted loop antenna                                                                            | 84 |

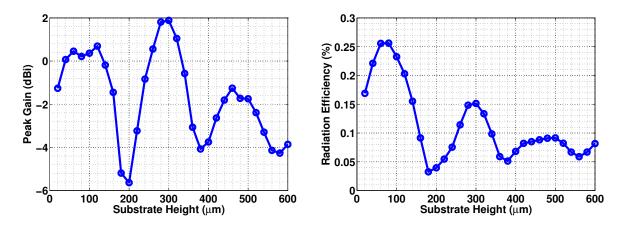

| 5.5  | Simulated peak gain [left] and radiation efficiency [right] as a function of the substrate height                        | 84 |

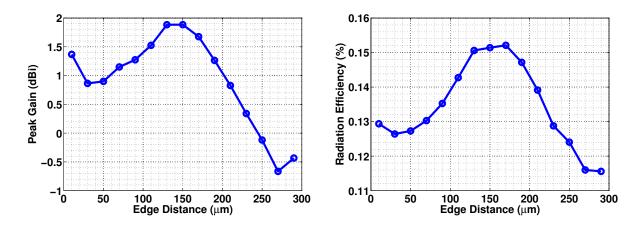

| 5.6  | Simulated peak gain [left] and radiation efficiency [right] as a function of the edge distance                           | 85 |

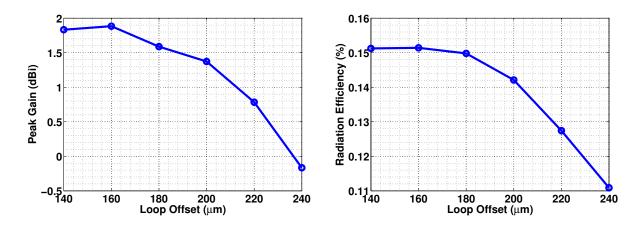

| 5.7  | Simulated peak gain [left] and radiation efficiency [right] as a function of the loop offset from the center of symmetry | 85 |

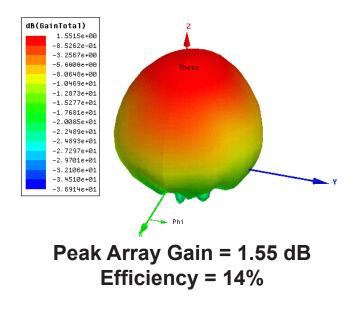

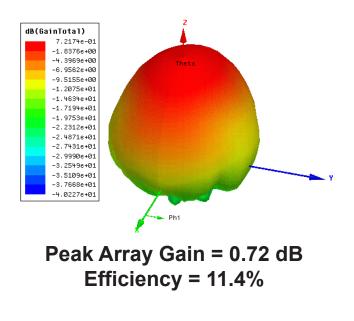

| 5.8  | Simulated gain pattern of the transmitter antenna                                                                        | 86 |

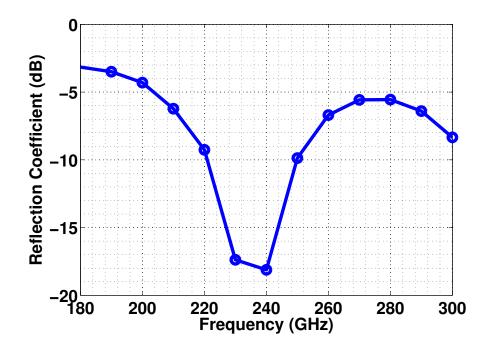

| 5.9  | Simulated input reflection coefficient $(S_{11})$ of the transmitter antenna $\ldots$                                    | 87 |

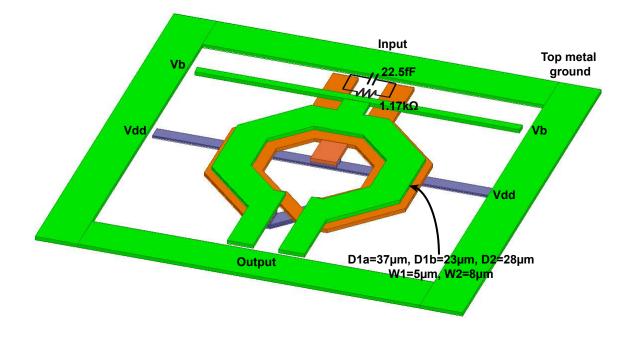

| 5.10 | Structure of the receiver slotted loop antenna                                                                           | 87 |

| 5.11 | Simulated gain pattern of the receiver antenna                                                                           | 88 |

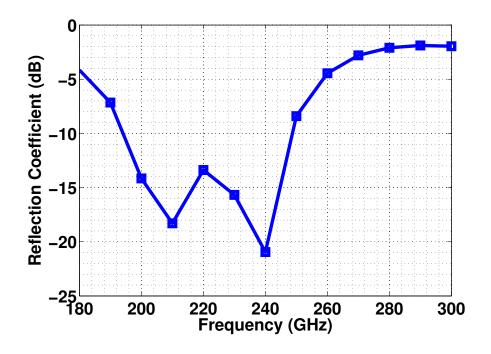

| 5.12 | Simulated input reflection coefficient $(S_{11})$ of the receiver antenna                                                | 89 |

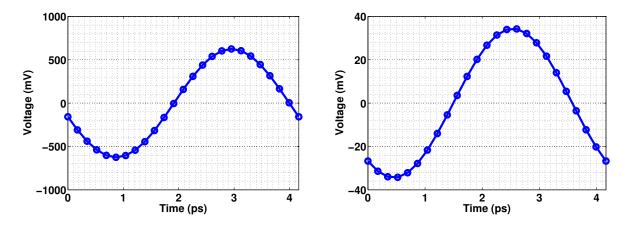

| 5.13 | Antenna-mixer interface - Simulated differential signal [left] and common mode signal [right] at the mixer RF ports      | 89 |

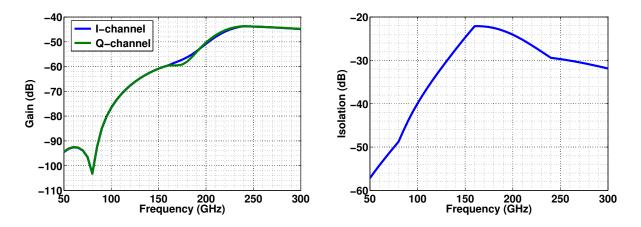

| 5.14 | Antenna-mixer interface - Simulated gain from Tx to Rx [left] and isolation [right] between the Rx antennas              | 90 |

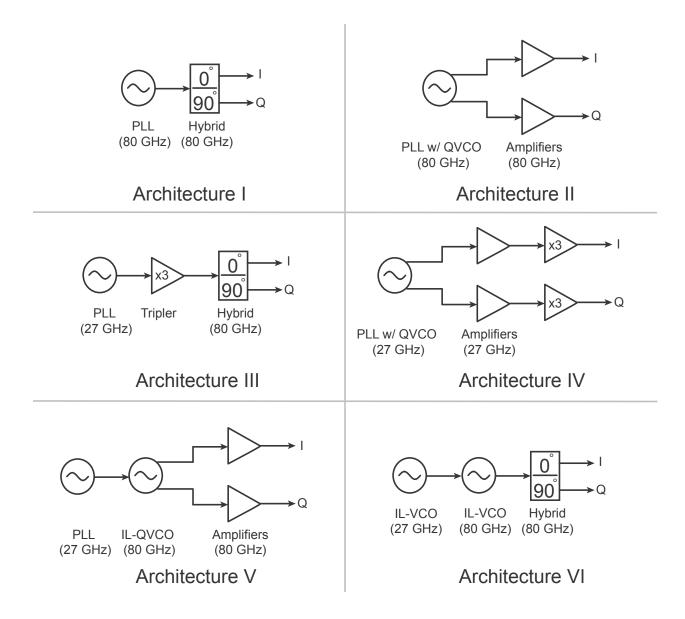

| 5.15 | Choice of different architectures to generate the 80 GHz LO signals $\ldots$ .                                           | 91 |

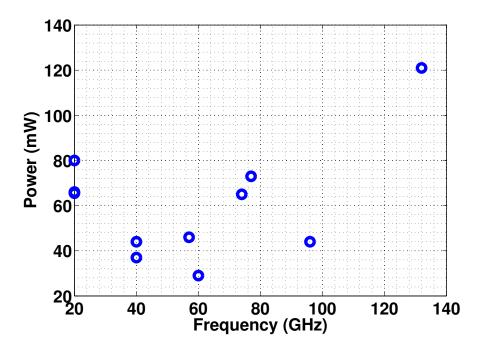

| 5.16 | Power consumption as a function of operating frequency for published PLL designs in literature                           | 92 |

| 5.17 | 80 GHz LO architecture                                                                                                   | 94 |

| 5.18 | Schematic of the 80 GHz Injection-locked oscillator with the injection devices coupled using a transformer               | 95 |

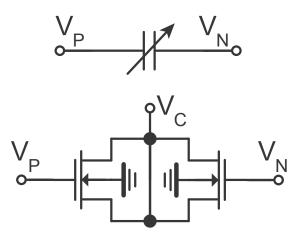

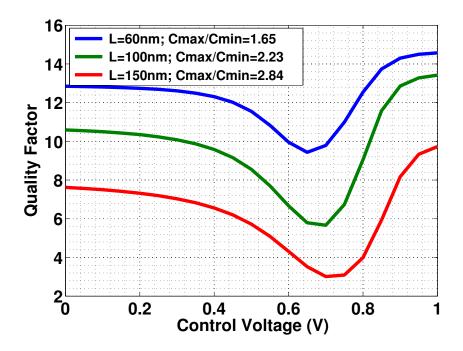

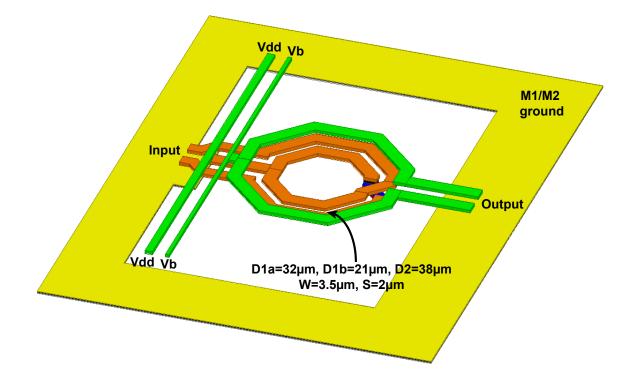

| 5.19 | Schematic of MOS varactors used in the IL-VCO                                                                                                                                                                                                              | 96  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.20 | Variation of varactor quality factor with the tuning voltage at $80\mathrm{GHz}$                                                                                                                                                                           | 96  |

| 5.21 | Transformer matching network between the 80 GHz IL-VCO and the injection device                                                                                                                                                                            | 97  |

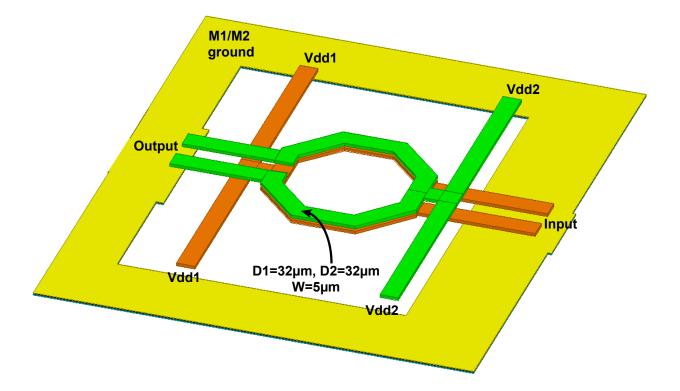

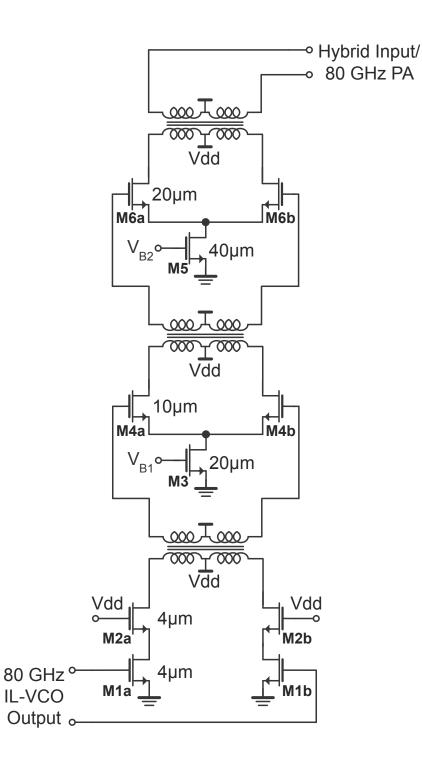

| 5.22 | Schematic of 80 GHz LO buffer chain $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                         | 98  |

| 5.23 | $80\mathrm{GHz}$ LO buffer chain : Buffer 1 - Buffer 2 transformer matching network .                                                                                                                                                                      | 99  |

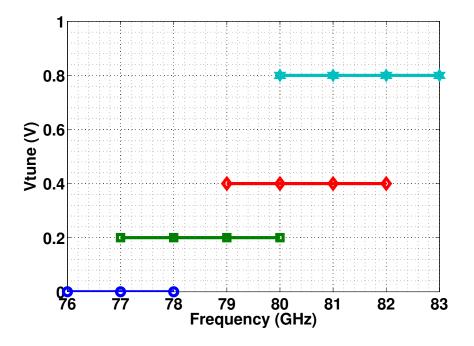

| 5.24 | $80\mathrm{GHz}$ IL-VCO - Lock range as a function of the tuning voltage                                                                                                                                                                                   | 99  |

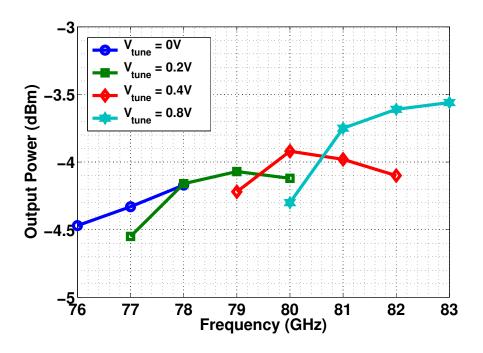

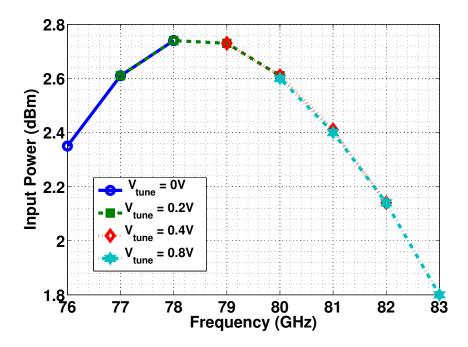

| 5.25 | 80 GHz IL-VCO - Output power with the first buffer as a function of frequency for different tuning voltages under lock                                                                                                                                     | 100 |

| 5.26 | 80 GHz IL-VCO - Input power as a function of frequency for different tuning voltages under lock                                                                                                                                                            | 100 |

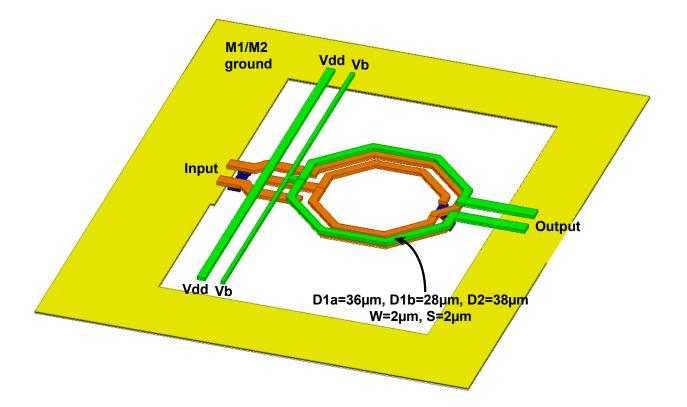

| 5.27 | $80\mathrm{GHz}$ LO buffer chain : Buffer 2 - Buffer 3 transformer matching network .                                                                                                                                                                      | 101 |

| 5.28 | $80\mathrm{GHz}$ LO buffer chain : Buffer 3 - hybrid transformer matching network                                                                                                                                                                          | 101 |

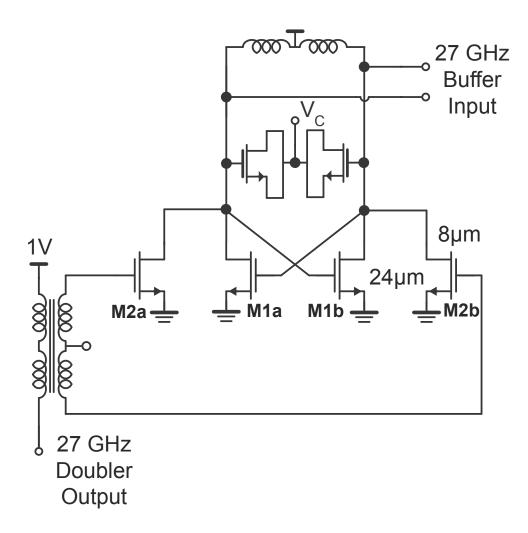

| 5.29 | Schematic of the $27\mathrm{GHz}$ Injection-locked oscillator with the injection devices                                                                                                                                                                   | 102 |

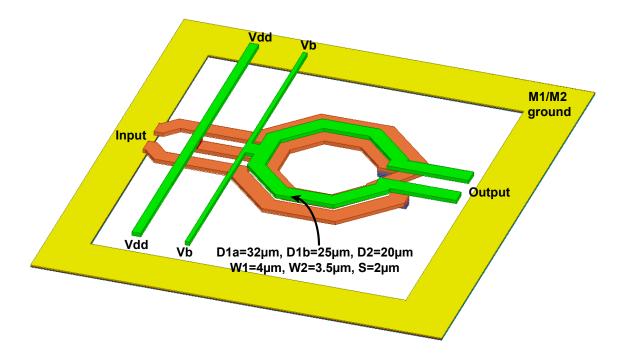

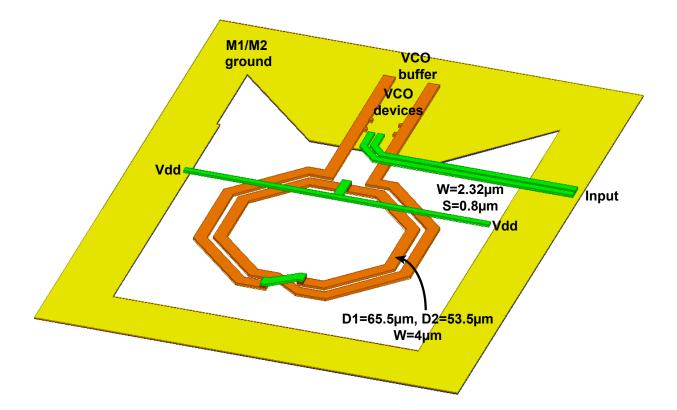

| 5.30 | 27 GHz IL-VCO loop inductor                                                                                                                                                                                                                                | 103 |

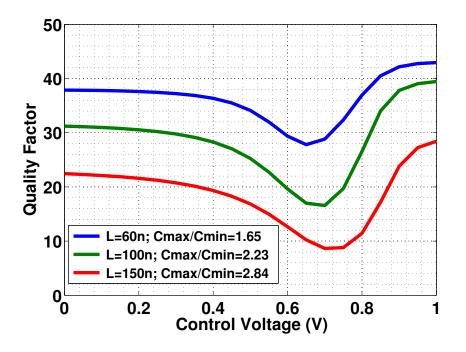

| 5.31 | Variation of varactor quality factor with the tuning voltage at 27 GHz                                                                                                                                                                                     | 103 |

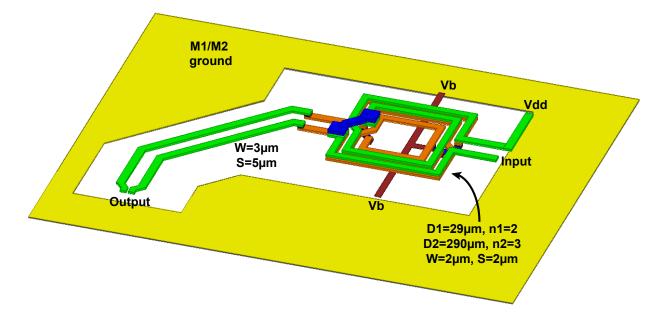

| 5.32 | Transformer matching network between the doubler and the $27\mathrm{GHz}$ IL-VCO                                                                                                                                                                           | 104 |

| 5.33 | Schematic of 27 GHz LO buffer                                                                                                                                                                                                                              | 105 |

| 5.34 | Transformer matching network between the 27 GHz LO buffer and the 80 GHz injection device                                                                                                                                                                  | 106 |

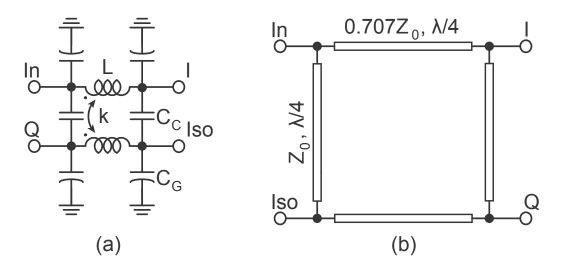

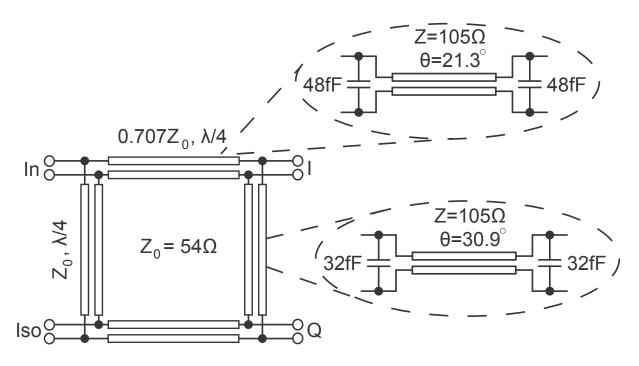

| 5.35 | (a) Transformer-based hybrid (b) Branch-line coupler hybrid $\ldots$                                                                                                                                                                                       | 107 |

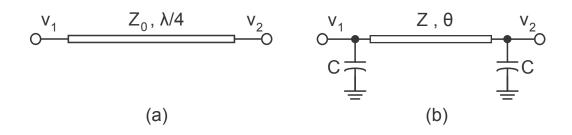

| 5.36 | (a) $\lambda/4$ transmission line (b) Capacitively loaded equivalent $\ldots \ldots \ldots$                                                                                                                                                                | 108 |

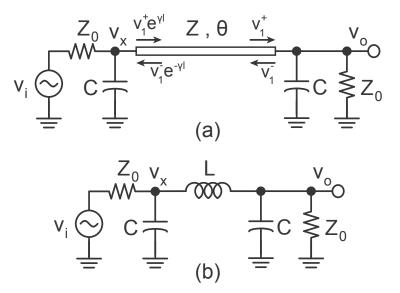

| 5.37 | (a) Transmission line circuit with matched load (b) Transmission line circuit with lumped components                                                                                                                                                       | 108 |

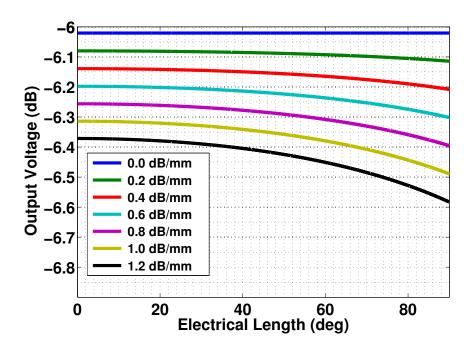

| 5.38 | Variation of the output voltage with line length for different attenuation at 80 GHz                                                                                                                                                                       | 109 |

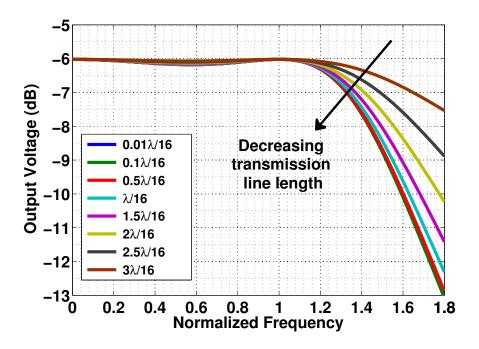

| 5.39 | Variation of the output voltage with frequency for various line lengths                                                                                                                                                                                    | 110 |

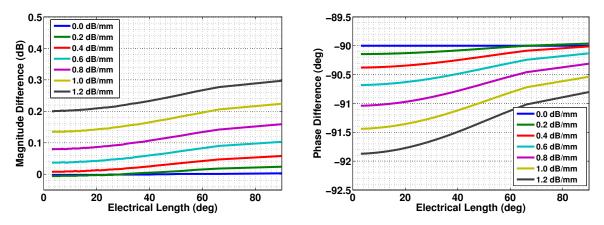

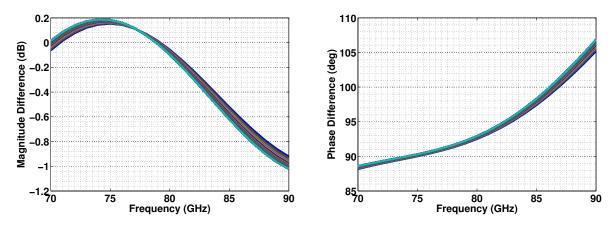

| 5.40 | Simulated I/Q magnitude and phase difference of the hybrid as a function of the transmission line length (with characteristic impedance $Z_0/\sqrt{2}$ ). The transmission line with characteristic impedance $Z_0$ is kept constant at its nominal value. | 111 |

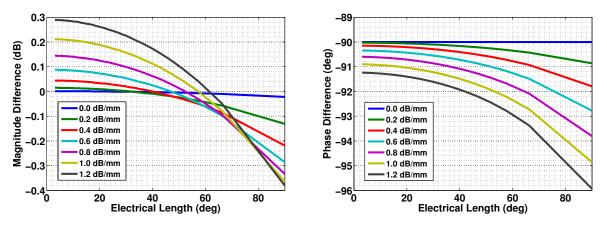

| 5.41 | Simulated I/Q magnitude and phase difference of the hybrid as a function of the transmission line length (with characteristic impedance $Z_0$ ). The transmission line with characteristic impedance $Z_0/\sqrt{2}$ is kept constant at its nominal value. | 111 |

| 5.42 | Simulated I/Q magnitude and phase difference of the hybrid as a function of frequency for different transmission line length (with characteristic impedance $Z_0/\sqrt{2}$ ). The transmission line with characteristic impedance $Z_0$ is kept constant at its nominal value. | 112 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.43 | Simulated I/Q magnitude and phase difference of the hybrid as a function of frequency for different transmission line length (with characteristic impedance $Z_0$ ). The transmission line with characteristic impedance $Z_0/\sqrt{2}$ is kept constant at its nominal value. | 112 |

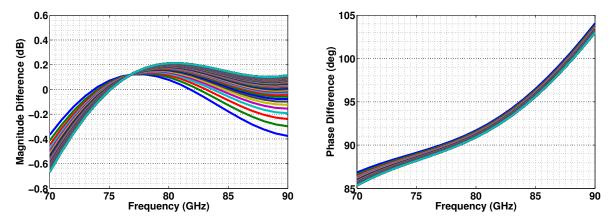

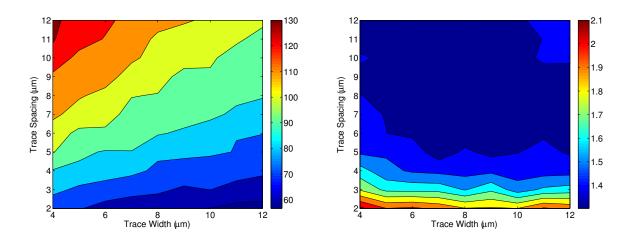

| 5.44 | Simulated characteristic impedance and loss in dB/mm of CPS lines as a function of conductor width and spacing at $80 \mathrm{GHz}$                                                                                                                                            | 113 |

| 5.45 | Schematic of differential hybrid structure                                                                                                                                                                                                                                     | 113 |

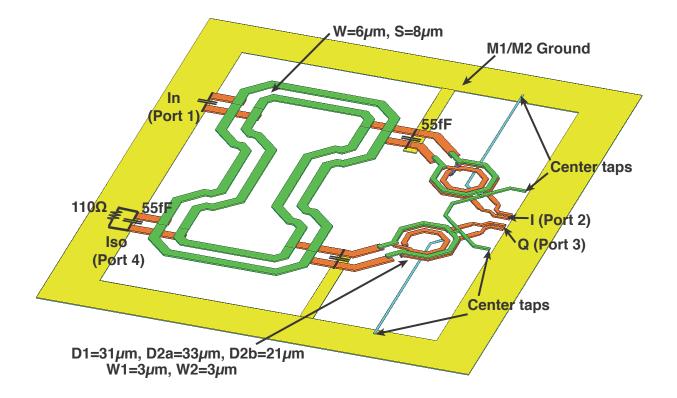

| 5.46 | Layout of differential hybrid structure                                                                                                                                                                                                                                        | 114 |

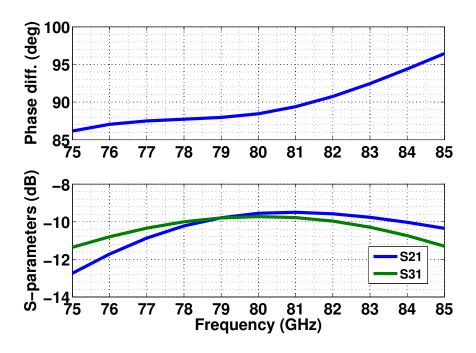

| 5.47 | Simulated phase difference and gain of differential hybrid structure including the input transformer (not shown)                                                                                                                                                               | 115 |

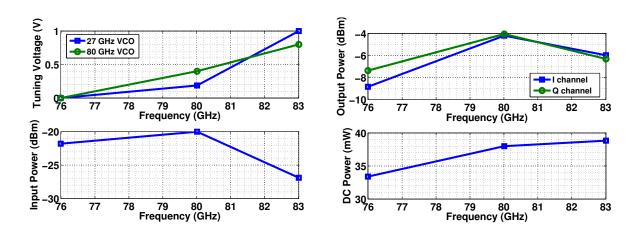

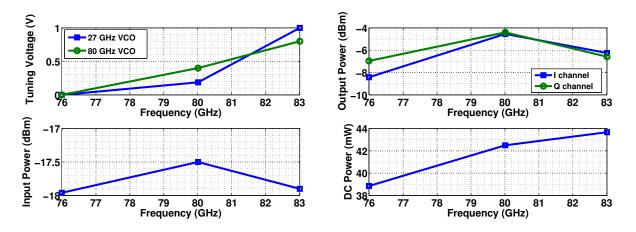

| 5.48 | Tuning voltages, Input Power, Output Power and DC Power consumption as a function of frequency (tt corner)                                                                                                                                                                     | 116 |

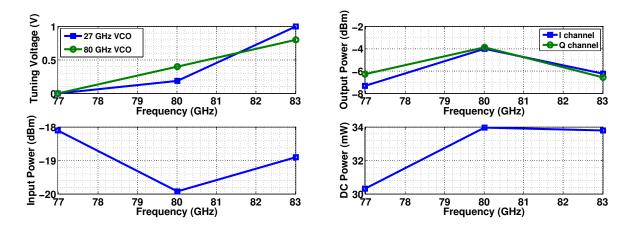

| 5.49 | Tuning voltages, Input Power, Output Power and DC Power consumption as a function of frequency (ss corner)                                                                                                                                                                     | 116 |

| 5.50 | Tuning voltages, Input Power, Output Power and DC Power consumption as a function of frequency (ff corner)                                                                                                                                                                     | 116 |

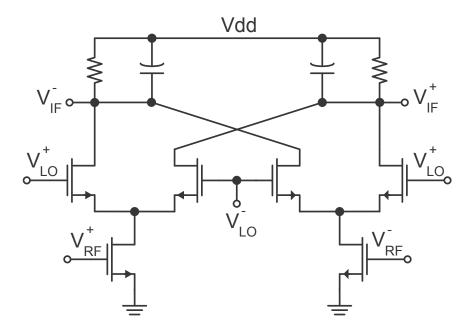

| 6.1  | Schematic of fully balanced active mixer                                                                                                                                                                                                                                       | 119 |

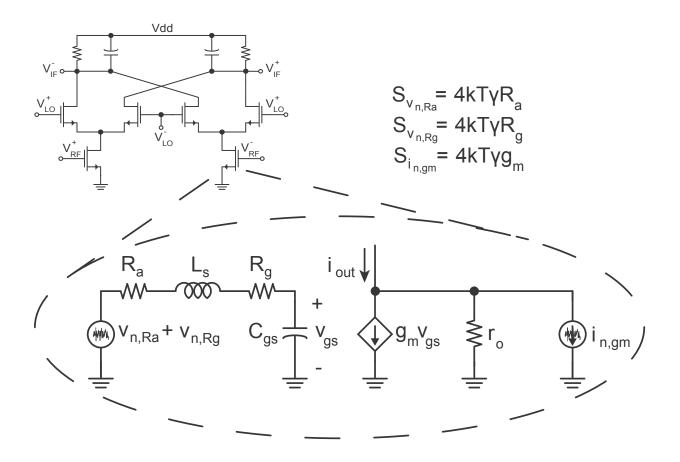

| 6.2  | Noise analysis of fully balanced active mixer                                                                                                                                                                                                                                  | 120 |

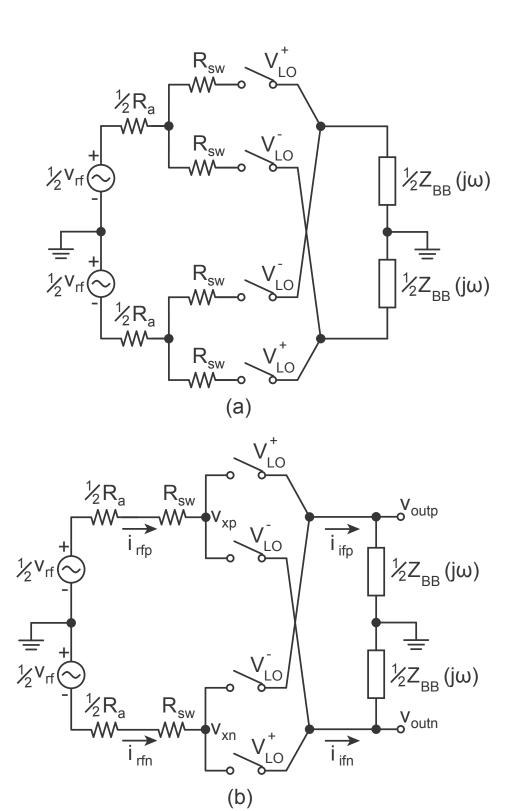

| 6.3  | Schematic of fully balanced passive mixer                                                                                                                                                                                                                                      | 121 |

| 6.4  | Switch model of fully balanced passive mixer                                                                                                                                                                                                                                   | 122 |

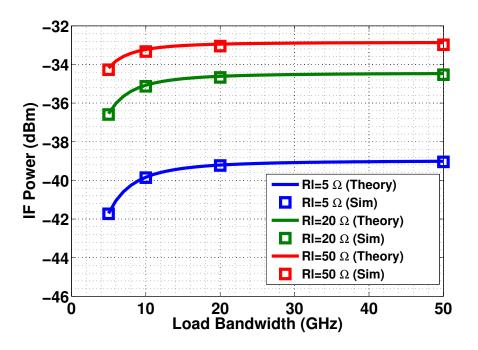

| 6.5  | Variation of IF power as a function of IF bandwidth for the passive mixer using the switch model                                                                                                                                                                               | 125 |

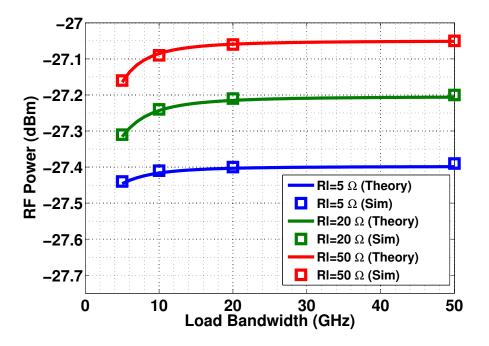

| 6.6  | Variation of IF power as a function of RF bandwidth for the passive mixer using the switch model                                                                                                                                                                               | 126 |

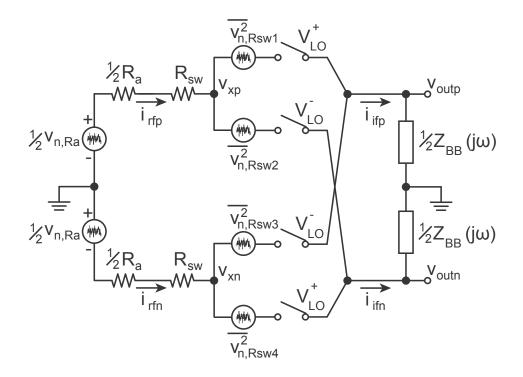

| 6.7  | Noise analysis of fully balanced passive mixer using the switch model $\ldots$ .                                                                                                                                                                                               | 127 |

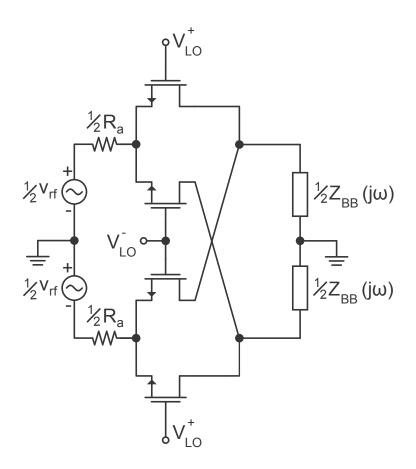

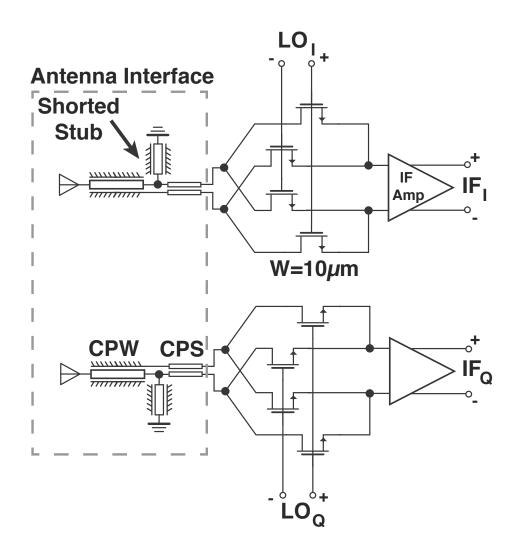

| 6.8  | Schematic of the passive mixer with the antenna interface                                                                                                                                                                                                                      | 130 |

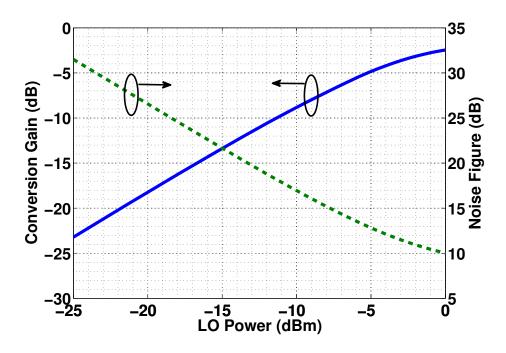

| 6.9  | Simulated voltage conversion gain and noise figure as a function of the LO power                                                                                                                                                                                               | 131 |

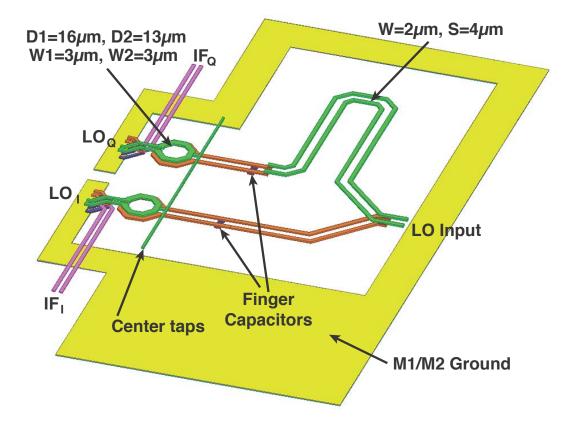

| 6.10 | 240 GHz I/Q generation and mixer LO matching interface $\ldots$                                                                                                                                                                                                                | 132 |

| 6.11 | 240 GHz I/Q generation and mixer LO matching interface $\ldots$                                                                                                                                                                                                                | 134 |

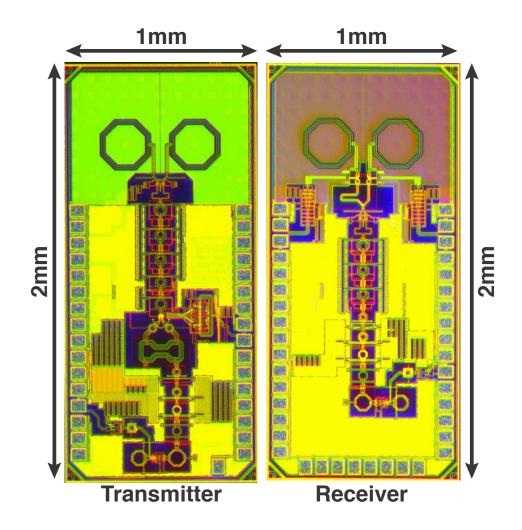

| 6.12 | Chip microphotograph of the transmitter and receiver                                                                                                                                                                                                                           | 136 |

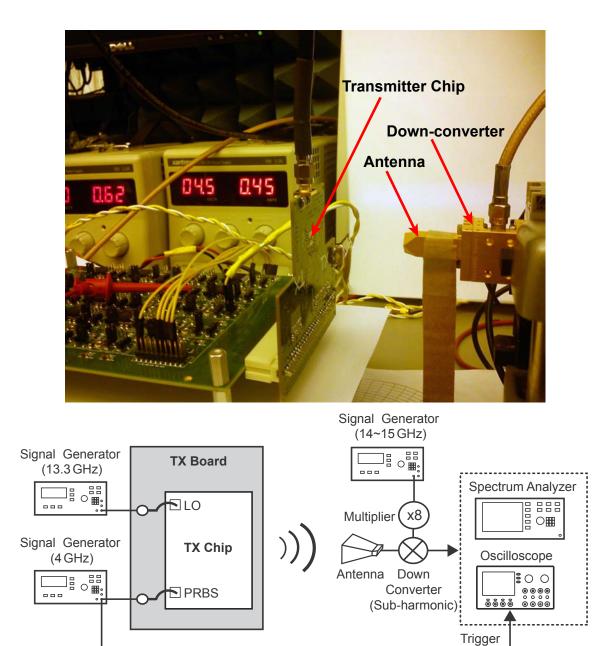

| 6.13 | Transmitter measurement setup $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                    | 137 |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|

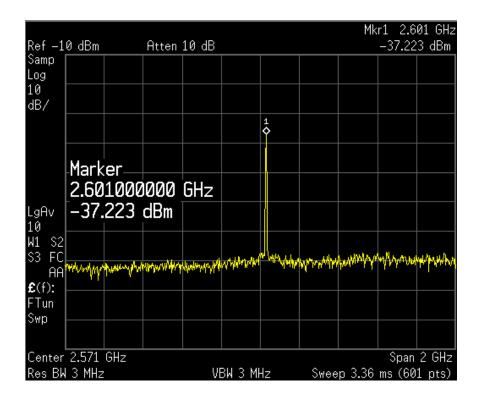

| 6.14 | Transmitter continuous wave (CW) mode measurement $\ldots \ldots \ldots \ldots$                                                 | 138 |

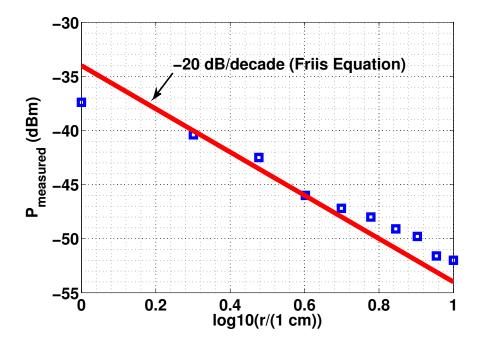

| 6.15 | Variation of transmitter output power with distance                                                                             | 138 |

| 6.16 | Calorimetric measurement of EIRP                                                                                                | 139 |

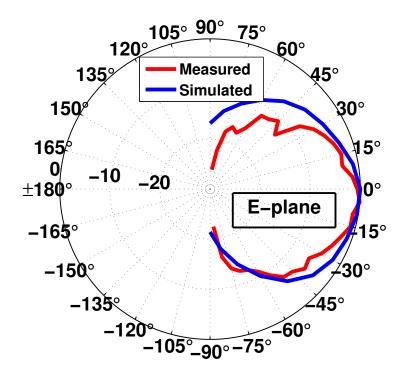

| 6.17 | Measured and simulated antenna pattern in E-plane                                                                               | 140 |

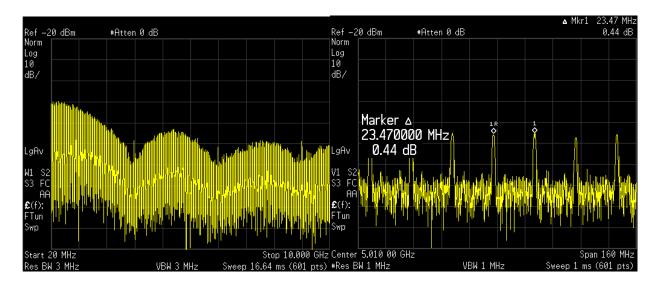

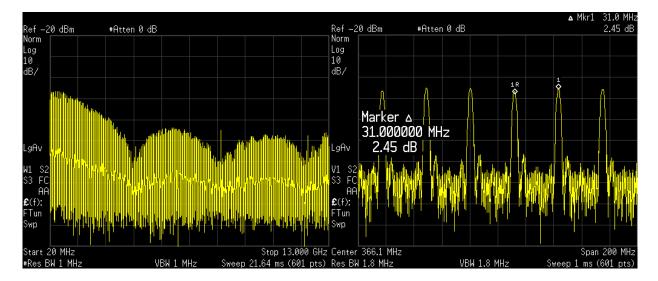

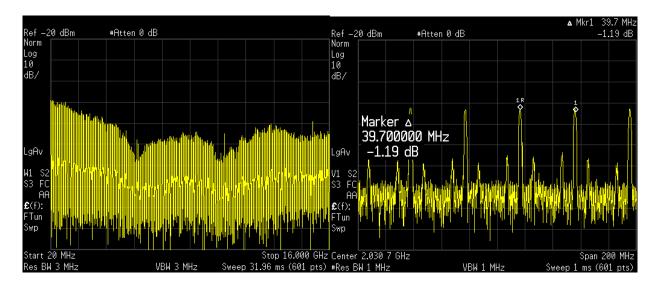

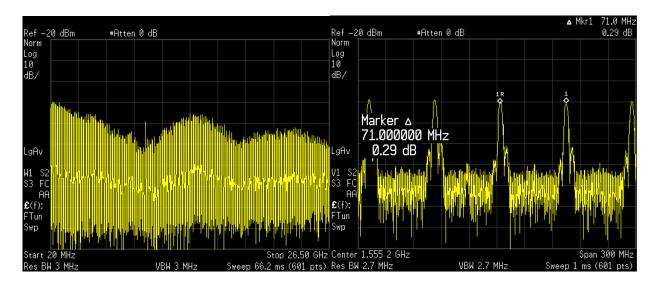

| 6.18 | Measured down-converted transmitter spectrum and beat frequency for 3 Gbps data                                                 | 141 |

| 6.19 | Measured down-converted transmitter spectrum and beat frequency for 4 Gbps data                                                 | 141 |

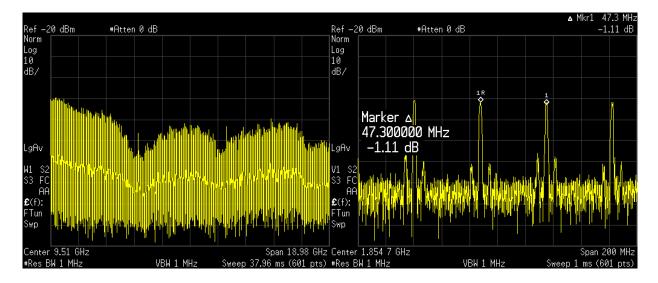

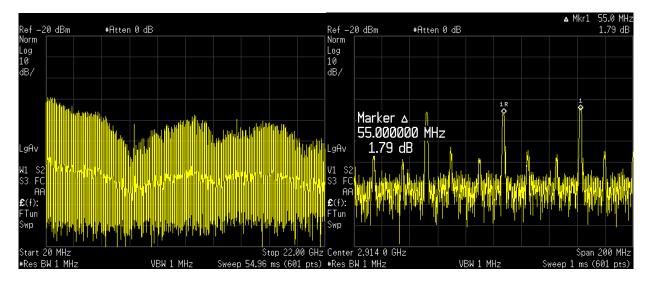

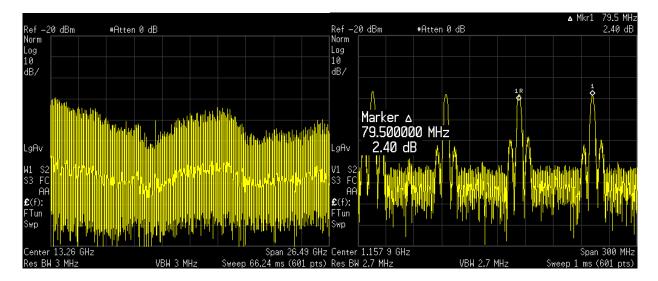

| 6.20 | Measured down-converted transmitter spectrum and beat frequency for 5 Gbps data                                                 | 142 |

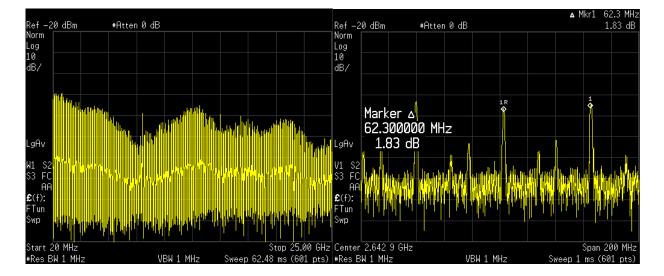

| 6.21 | Measured down-converted transmitter spectrum and beat frequency for 6 Gbps data                                                 | 142 |

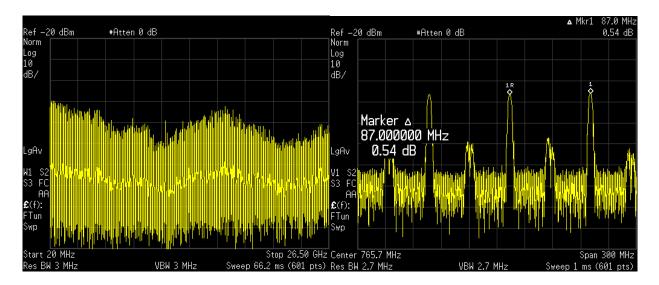

| 6.22 | Measured down-converted transmitter spectrum and beat frequency for 7 Gbps data                                                 | 143 |

| 6.23 | Measured down-converted transmitter spectrum and beat frequency for 8 Gbps data                                                 | 143 |

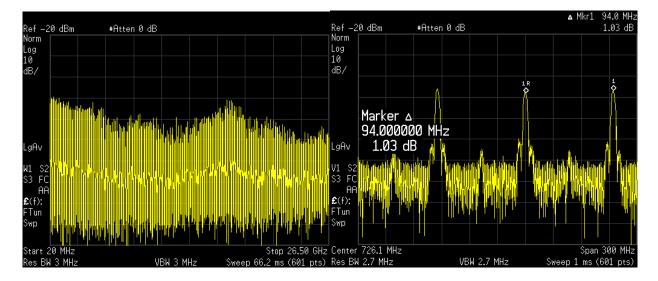

| 6.24 | Measured down-converted transmitter spectrum and beat frequency for 9 Gbps data                                                 | 144 |

| 6.25 | Measured down-converted transmitter spectrum and beat frequency for 10 Gbps data                                                | 144 |

| 6.26 | Measured down-converted transmitter spectrum and beat frequency for 11 Gbps data                                                | 145 |

| 6.27 | Measured down-converted transmitter spectrum and beat frequency for 12 Gbps data                                                | 145 |

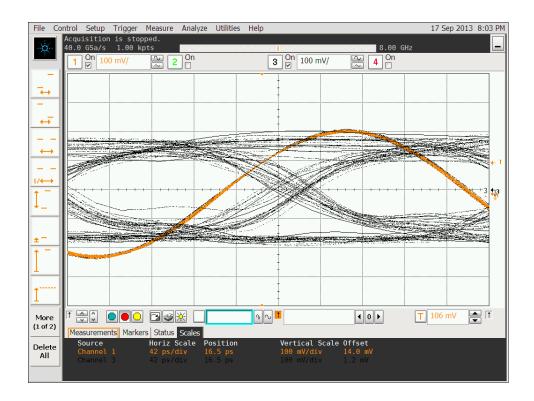

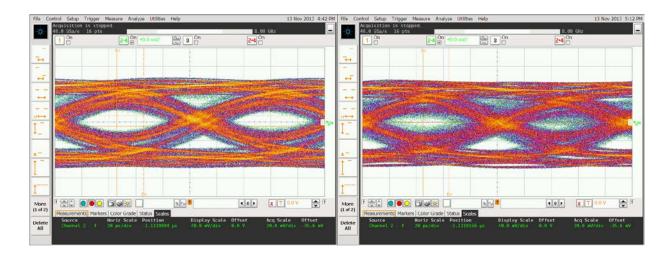

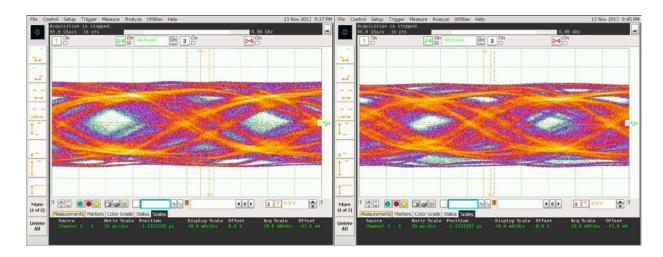

| 6.28 | Measured transmitter eye diagram for 4 Gbps data                                                                                | 146 |

| 6.29 | Measured transmitter eye diagram for 6 Gbps data                                                                                | 146 |

| 6.30 | Measured transmitter eye diagram for 8 Gbps data                                                                                | 147 |

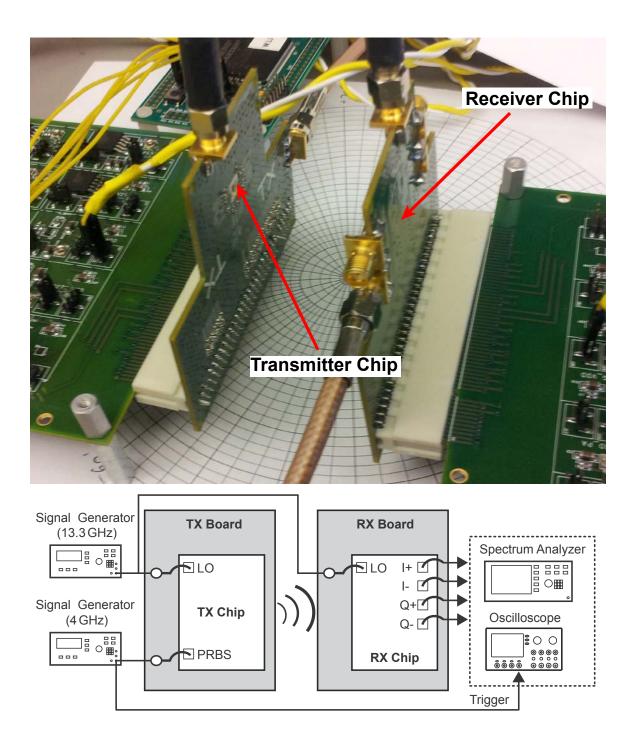

| 6.31 | Receiver measurement setup                                                                                                      | 148 |

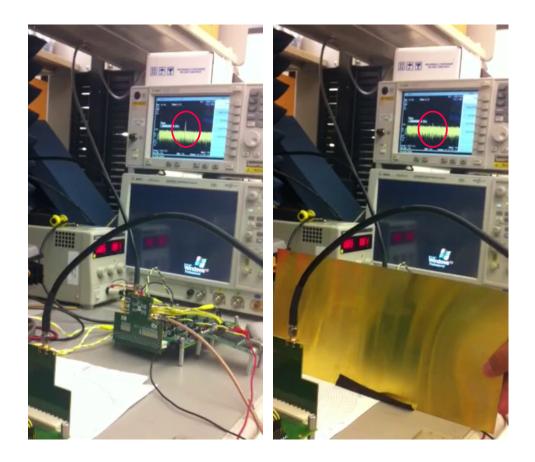

| 6.32 | Link CW mode measurement with and without reflector                                                                             | 149 |

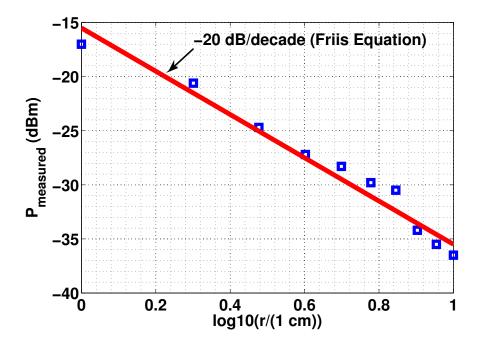

| 6.33 | Variation of measured received output power with distance in CW mode $\$ .                                                      | 149 |

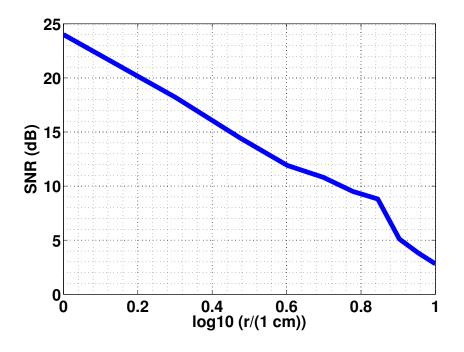

| 6.34 | Variation of measured SNR with distance in CW mode                                                                              | 150 |

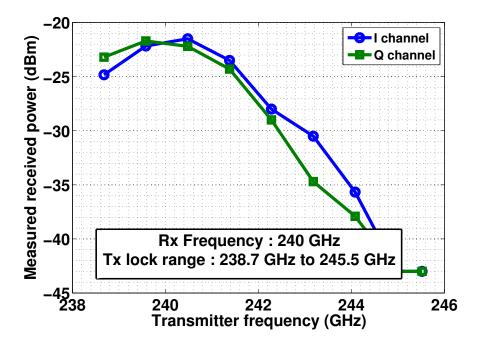

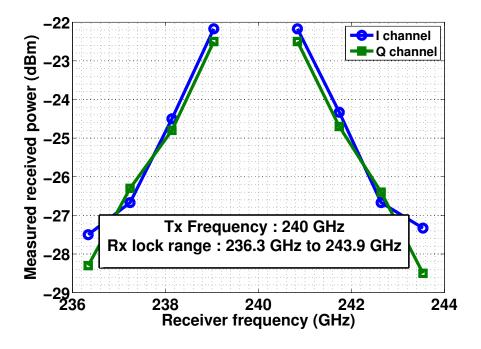

| 6.35 | Measured CW receiver power for I and Q channels with varying transmitter LO frequency. Receiver LO frequency is held at 240 GHz | 151 |

| 6.36 | Measured CW receiver power for I and Q channels with varying receiver LO frequency. Transmitter LO frequency is held at 240 GHz | 151 |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|

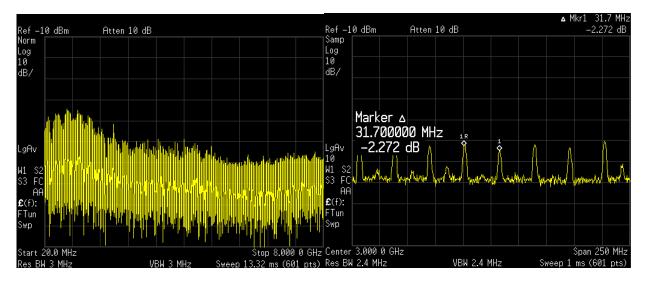

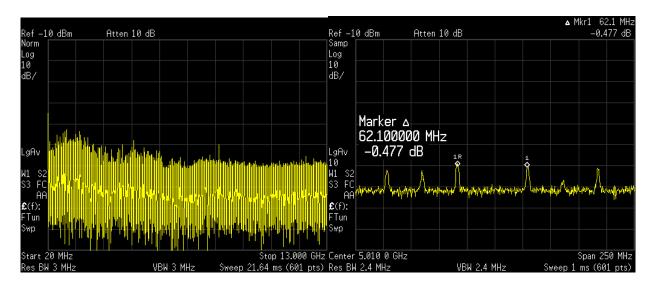

| 6.37 | Measured receiver spectrum and beat frequency for 4 Gbps data $\ldots$                                                          | 152 |

| 6.38 | Measured receiver spectrum and beat frequency for 8 Gbps data $\ . \ . \ .$ .                                                   | 152 |

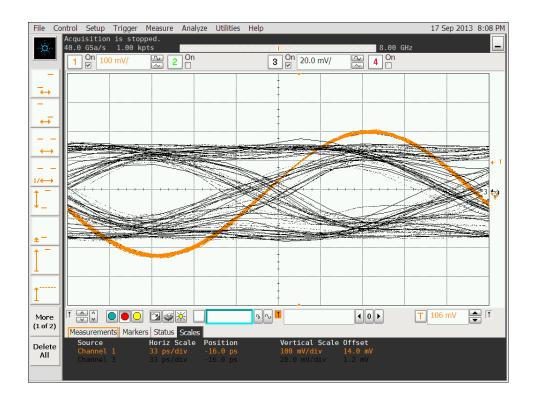

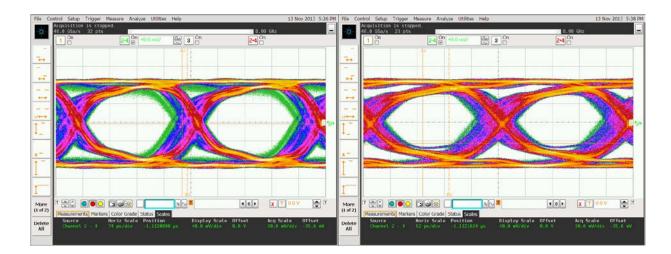

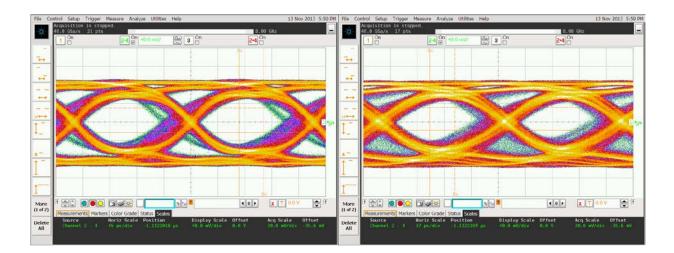

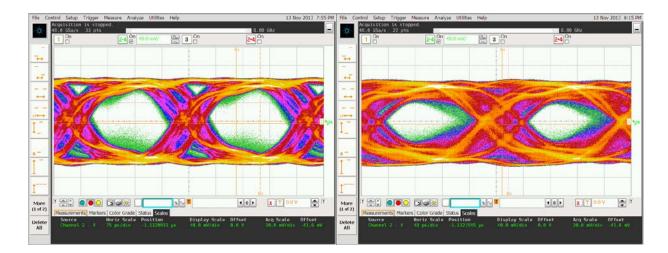

| 6.39 | Measured receiver eye diagram for 3 Gbps [left] and 4 Gbps [right] data in BPSK mode                                            | 153 |

| 6.40 | Measured receiver eye diagram for 5 Gbps [left] and 6 Gbps [right] data in BPSK mode                                            | 153 |

| 6.41 | Measured receiver eye diagram for 7 Gbps [left] and 8 Gbps [right] data in BPSK mode                                            | 154 |

| 6.42 | Measured receiver eye diagram for 9 Gbps [left] and 10 Gbps [right] data in BPSK mode                                           | 154 |

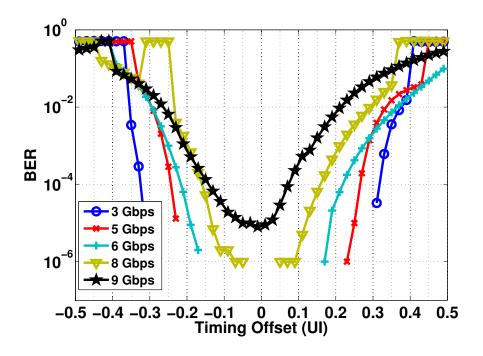

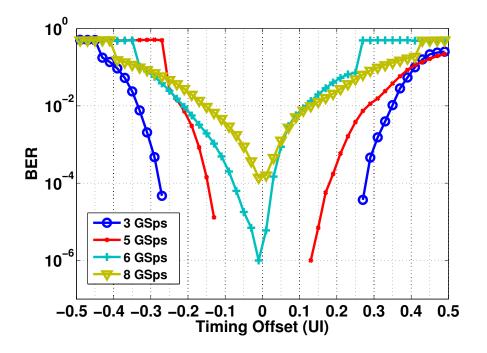

| 6.43 | Measured bit error rate (BER) for BPSK mode $\ldots \ldots \ldots \ldots \ldots \ldots$                                         | 155 |

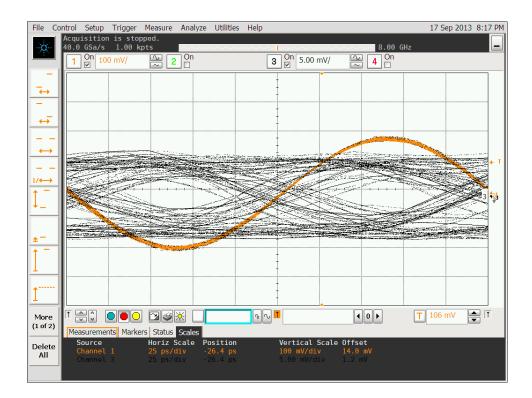

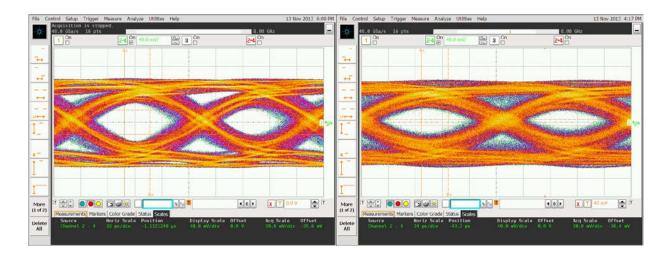

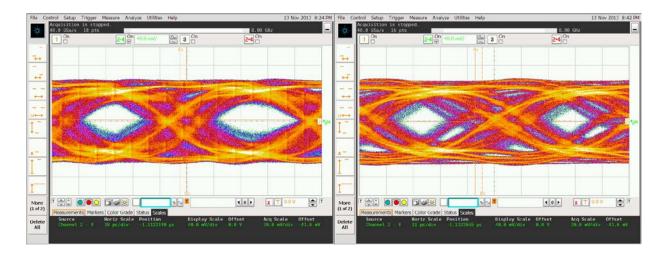

| 6.44 | Measured receiver eye diagram (I-channel) for 3 Gbps [left] and 4 Gbps [right] data in QPSK mode                                | 156 |

| 6.45 | Measured receiver eye diagram (I-channel) for 5 Gbps [left] and 6 Gbps [right] data in QPSK mode                                | 156 |

| 6.46 | Measured receiver eye diagram (I-channel) for 7 Gbps [left] and 8 Gbps [right] data in QPSK mode                                | 157 |

| 6.47 | Measured bit error rate (BER) for QPSK mode                                                                                     | 157 |

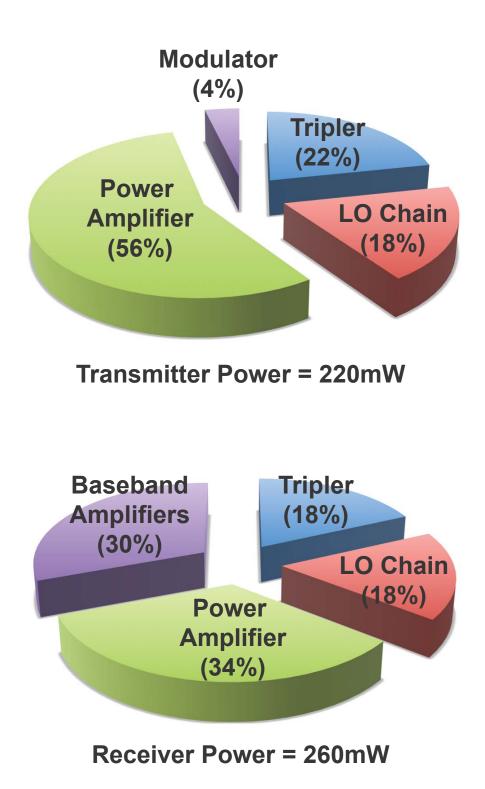

| 6.48 | Power consumption distribution for the transmitter and receiver chips                                                           | 158 |

# List of Tables

| 2.1 | Comparison Table of 60 GHz CMOS Power Amplifiers                                              | 28  |

|-----|-----------------------------------------------------------------------------------------------|-----|

| 3.1 | Wireless link budget for OOK, BPSK and QPSK modulation                                        | 36  |

| 4.1 | Calculated coefficients of the transfer functions for maximally flat response $% f(x)=f(x)$ . | 66  |

| 5.1 | Summary of LO architectures                                                                   | 93  |

| 6.1 | Summary of published sub-terahertz transmitters                                               | 159 |

| 6.2 | Summary of published sub-terahertz receivers                                                  | 160 |

| 6.3 | Summary of published sub-terahertz transceivers                                               | 161 |

#### Acknowledgements

I guess only one person gets the doctorate degree from a PhD dissertation but there is great deal of help and support from a lot of talented people which makes this happen. I have been fortunate to have worked with many of them here at Berkeley and in the industry and a lot of them who have supported me throughout my studies. I would like express my gratitude to them.

Firstly, I would like to thank my advisor Prof. Ali M. Niknejad for his constant support and guidance throughout the last five years. I would describe him as a very calm and composed person who is always there to help his students. I have always turned towards him for his valuable advice on courses, internship, job search and other professional decisions. He is also technically very knowledgeable and I admire his skill in analyzing any problem from a different angle. He sometimes gives a totally different perspective to the problem at hand and an elegant solution emerges. Not only have I had this experience myself but have also heard the same from my fellow graduate students. I would also like to thank Prof. Elad Alon for the valuable discussions and feedback over the many years. I have taken more courses with him than any other professor in Berkeley and the long technical discussions in courses and research have always helped me. I also admire his intent to help students from other groups even if its on a late Friday evening. I would like to thank Prof. Paul K. Wright for being part of my quals and thesis committee and providing valuable feedback on my research and dissertation. I would also like to thank Prof. Robert G. Meyer for being part of my quals and masters committee and providing feedback during the quals examination. I would also like to express my sincere gratitude to my undergraduate professors Prof. Shanthi Pavan and Prof. Nagendra Krishnapura for introducing me to the field of Integrated Circuit Design and teaching those wonderful courses at IIT Madras.

I would like to thank my collaborators Shinwon Kang and Jungdong Park for their support and contributions in the design of the various chips. I am thankful for the great technical discussions and for the positive and negative critiques of my design which made me improve them further. Also, to the eventful night outs during tapeouts which kept me moving forward. I would also like to thank Dr. Dick Plambeck from the Astronomy Department for supporting us with terahertz instruments. I would like to thank Chintan Thakkar, Jiashu Chen and Sriramkumar Venugopalan for their support, advice and interesting technical discussions. I am also grateful to other members of my group namely Cristian Marcu, Amin Arbabian, Debopriyo Chowdhury, Steven Callender, Jun-Chau Chien, Lu Ye, Ashkan Borna, Maryam Tabesh, Juan Yaquian for their support and encouragement. I would also like to thank Yue Lu, Lingkai Kong, Han-Phuc Le, Pramod Murali, Kwangmo Jung, Yida Duan, Charles Wu, William Biederman, Dan Yeager, Katerina Papadopoulou, Sharon Xiao, Ping-Chen Huang, Wen Li, Andrew Townley, Paul Swirhun, Lucas Calderin, Greg Lacaille, Nai-Chung Kuo, Rikky Muller, Mervin John, Michael Lorek, Lingqi Wu, Jaehwa Kwak, Costis Sideris, Krishna Settaluri, Brian Pepin, Turker Beyazoglu, Richard Przybyla, Mitchell Kline, Igor Izyumin.

My thanks to my course professors Prof. Ali M. Niknejad, Prof. Elad Alon, Prof. Borivoje Nikolic, Prof. Clark Nguyen, Prof. Jaijeet Roychowdhury, Prof. Michael Lustig, Prof. Russel Ahn, Prof. Dan-Virgil Voiculescu and Dr. Paul Smith. I would also like to thank Prof. David Allstot and Prof. Bernhard Boser. My thanks to Shirley Salanio for patiently answering my questions and supporting me throughout the PhD program. I would also like to thank Ruth Gjerde, Rebecca Miller, Patrick Hernan, Jennifer Gardner and Tracey Richards. Special thanks to the BWRC staff for their support and tireless efforts in making life easier for us and giving us more time to concentrate on research. I would like to thank Brian Richards, Ubirata Coelho, Olivia Nolan, Leslie Nishiyama, Sarah Jordan, Fred Burghardt, Susan Mellers, Tom Boot, Pierce Chua, Gary Kelson, Deirdre Bauer and Kevin Zimmerman.

My sincere thanks to Intel Corporation for the Intel fellowship 2013-2014 and Electrical Engineering and Computer Sciences department, UC Berkeley for the fellowship during the first year of my graduate studies. I would also like to acknowledge the support of National Science Foundation, UC Discovery, C2S2, SRC, TxAce and TSMC University Shuttle program for chip fabrication. I would like to thank my Intel mentor Dr. Christopher Hull for giving me the opportunity to work in cutting edge technologies and sharing his technical expertize with me. My thanks to my Intel colleagues Yanjie Wang, Stephane Ramon, Glenn Murata, Oleg Korobeynikov and others in Germany and Israel. I would like to express my sincere gratitude to my Texas Instruments mentor Dr. Baher Haroun for giving me the opportunity to work in TI's next generation products and sharing his knowledge and expertise in RF domain. My thanks to my TI colleagues Joonhoi Hur, Lei Ding, Rahmi Hezar, Swaminathan Sankaran and Nirmal Warke.

I would like to thank my friends in Berkeley who made my stay here memorable. Thanks to Vinay Jayakumar, Sriramkumar Venugopalan, Chintan Thakkar, Debanjan Mukherjee, Venkatesan Ekambaram, Pramod Murali, Aditya Medury, Pratik Bhansali , Kartik Ganapathi, Sudeep Kamath and Adarsh Krishnamurthy. Thanks to my other friends Varun Sridharan, Saurabh Saxena, Ankur Roy, Baradwaj Vigraham and Pawan Agarwal for keeping life interesting and listening to my long hours of complaints and jokes.

Lastly but definitely not the least, I would like to express my gratitude to my mom Anandhi and dad Thyagarajan for their endless love, immense sacrifices, constant support and guidance, without which I would not have reached the stage in life that I am in today. My thanks to my brother Krishna for always being there for me. I would like to thank my aunt Shyamala, uncle Sankaranarayanan and brothers Jagan, Aswin and Sriram for their constant encouragement. Thanks to my sisters Bharathi and Nithya for your constant support and great home food during my graduate studies. I would also like to thank my aunt Viji, uncle Swaminathan and cousin Prakash for their constant support. Thanks to my grandfather, grandmother, uncles and aunts for their encouragement and support.

### Chapter 1

# Introduction

The ubiquitous use of various electronic devices ranging from laptops, mobile phones, tablets, etc has tremendously increased the connectivity across the globe. Media sharing such as videos and music, online gaming, video chatting and social networking have led to a dramatic rise in the data transfer between devices. It is predicted [1] that by 2017, there would be 1.4 zettabytes of data being shared across the globe. Around 3.6 billion people would be online and the number of connections would increase from the current 12 billion to 19 billion. There would be a 79% growth in the number of smart phones and 104% in the tablets leading to increased connectivity and data sharing. Such high data rate transfers would require very high throughput, dense chip-to-chip interconnects in high performance computing, cloud computing, laptops and mobile phones. On the wireline front, today's electrical links can deliver close to 25 Gbps of data at energy efficiencies of 2-4 pJ/bit [2][3] and several demonstrations of data rates beyond 30 Gbps have also been shown [4][5]. However, increasing the data rates further results in lower energy efficiency due to the bandwidth limitations of the channel. On the optical domain, data rates close to 20 Gbps have been demonstrated [6]. However, the performance of these links is generally affected by the high laser power and temperature sensitivity of the devices. Today's wireless 4G LTE standards allow data rates of 30 Mbps to peak values of 100 Mbps for mobile smart phones [7]. With the latest 3GPP release in December 2014, these values would increase to a maximum of 1 Gbps. Thus, the increased data transfer in the future requires high bandwidth interconnects for high performance computing, data centers and mobile applications.

The millimeter-wave (sub-terahertz) and terahertz bands offer tremendous potential to achieve this target due to the availability of several gigahertz of spectrum in the band. Fig. 1.1 shows the electromagnetic spectrum. The millimeter-wave/terahertz region is defined from 30 GHz to 3 THz based on the wavelength of the electromagnetic wave. Electronic devices have been mainly operating in the low frequency regime of this spectrum and their performance degrades as one approaches their cut-off frequencies. Today's CMOS technologies have typical cut-off frequencies of ~ 200 GHz. On the other hand, there has been significant

Figure 1.1. Electromagnetic spectrum showing the millimeter/terahertz region

work in the photonics domain at frequencies greater than 3 THz in the infrared region. The photon energy ( $E = h\nu$ , where h is the Planck's constant and  $\nu$  the frequency) starts reducing as one approaches closer to the lower end of the infrared region. Hence, a significant proportion of the electromagnetic spectrum is unexplored starting from 50 GHz to 3 THz and is popularly referred to as the terahertz gap. Recently there has been significant interest in the 60 GHz band for high data rate communication in both outdoor and indoor networks. The millimeter-wave/terahertz band is also becoming popular for imaging applications at 94 GHz, 140 GHz and 220 GHz [8]. Applications in the automotive radar industry in the 77-78 GHz band are gaining interest for blind spot detection to minimize accidents. Terahertz chemical imaging or molecular spectroscopy is another emerging area of application where certain substances can be detected based on their high degree of absorption at these frequencies. This can be used to detect harmful gases such as carbon monoxide (which has response at 230 GHz) or phosphine (which has response at 266 GHz). This work inspects the millimeter-wave/terahertz band for communication applications and discusses various circuits and system designs at these frequencies.

### **1.1** Communication in the 60 GHz band

As described earlier, the 60 GHz band (V-band) is becoming popular for commercial products due to the availability of 7 GHz of unlicensed spectrum from 57 GHz to 64 GHz. This would allow very high data rate communication in applications such as personal area networks (PANs) for media sharing and wireless backhauls as shown in Fig. 1.2. The WiGig standard (IEEE 802.11ad) [9] which is now part of the Wi-Fi alliance allows the whole band to be used in time division duplexing (TDD) mode thereby allowing high data rates. This could be used for streaming high-definition video and transferring files across electronic devices. Today's technology with 802.11ac Wireless LAN standard can support a maximum of 2.5 Gbps with three 160 MHz channels and 256-QAM data rate. In contrast, the 60 GHz band can provide maximum throughputs of up to 10 Gbps at higher energy efficiencies compared to nJ/bit numbers from Wireless-LAN. The V-band could also be used for supporting backhaul networks. With the average backhaul data rate scaling up from 35 Mbits/cell to 1 Gbits/cell in the next five years [7], the millimeter-wave links would handle a significant

Figure 1.2. Millimeter-wave/terahertz networks for personal area networks [left] and wireless backhauls [right]

share of the data transfer. This is made more feasible with the recent Federal Communication Commission (FCC) modifications [7] for the maximum allowed transmission power for outdoor communication applications. The modification allows an equivalent power transmission of up to 82 dBm with an antenna gain of 51 dBi which could easily provide wireless network connectivity over a mile of distance. Additionally, operation at millimeter-wave frequencies allows one to use phased-array antennas that allow robust communication over long distances.

CMOS is usually the preferred technology for these applications due to its low cost and continued scaling that allows transistors to be operated in gigahertz range. However, Moore's law driven by digital circuits is detrimental to the design of high power millimeter systems. There have been several demonstrations of 60 GHz transceivers that achieve very high data rates with reasonable efficiencies. One of the critical blocks that determines the overall system efficiency of a mm-wave transceiver is the power amplifier (PA). The design of the PA is especially challenging due to several issues. The low breakdown voltage of transistors and their reduced supply voltages severely limit the output power of the PA. Several on-chip power combining techniques need to be employed to overcome this issue and this leads to degradation in the overall efficiency. Additionally the PA must be designed to be wideband in nature to account for process variations. In this work, the design of a linear wideband power amplifier has been explored in scaled 28 nm CMOS technology. Switching power amplifier architecture has also been explored as an alternative to linear PAs in constant envelope modulation scheme transmitters. The design of an inverse class-D power amplifier has been discussed with measurement results.

Figure 1.3. Futuristic flexible device with wireless interconnects

### 1.2 Communication beyond 100 GHz

The 60 GHz band offers potential for high speed applications. However, to achieve even higher data rates, this research explores frequencies beyond 100 GHz into the terahertz regime. Todays smart phones and tablets incorporate multiple radios (GPS, Bluetooth, 4G LTE, etc) and signal processing units (multi-standard baseband, graphics and CPU) on a single board. Given the form-factor constraints of such a handheld portable device, the high density of integration of these features has become a serious design challenge. One might be able to achieve smaller interconnect footprints and greater flexibility instead by employing short-range wireless links that could replace or complement wired buses, thereby utilizing the available extra space for other features (like high battery capacity).

An equally important application of directional high-data rate wireless interconnects can be envisioned to serve as wireless backhaul networks in data centers. As described earlier, there is a continued demand for high data rates and by the next decade, data rates for the server I/O and core networking are projected to increase to about 100 Gbps and 1 Tbps respectively [10]. This would be a serious bottleneck for the cloud and would require advance hardware resources, often at a steep cost. Therefore, during intermittent periods of heavy data, wireless links could be deployed to ease congestion. Such links would assist the wired network and provide both bandwidth and flexibility to simultaneously transport huge amounts of data. Such links at 60 GHz are already being deployed in industry data-centers [11][12]. Sub-terahertz wireless interconnects with significantly higher data-rates can be

Figure 1.4. Flexible device can be upgraded by attaching two such devices and the chips communicate with each other wirelessly

achieved by using directional links. Leveraging the well-controlled data center environment can enable the implementation of extremely efficient point-to-point links.

One of the futuristic visions of this work is a device shown in Fig. 1.3. The device is a flexible tablet with a display on it. Here chips are placed in their respective slots and there is only power routing through the flexible device. After being powered on, the chips talk to each other using wireless communication and the whole device can be upgraded on the fly as in Fig. 1.4. As the device is flexible, the wireless interconnect solution is a more feasible option compared to wireline or optical. However, this would only be possible when the chips are low cost and efficient. This work therefore focuses on the design of sub-terahertz systems in CMOS technology due to its low cost and the ability to leverage its digital interface. By operating at these high frequencies, the antennas can be integrated on the die thereby further reduced packaging costs. However, the design at these frequencies is faced with various challenges and requires innovations both at the circuit and system level. The design of these sub-terahertz systems also incorporates ideas from the V-band PA designs described earlier.

### **1.3** Organization of the dissertation

The primary goal of this dissertation is to explore feasibility of millimeter-wave and terahertz circuits and transceiver systems in bulk CMOS technology. The dissertation covers three basic aspects of design. It includes the theoretical analysis and modeling of various critical blocks using simple analytical expressions that allow the designer to understand the design trade-offs and arrive at a more efficient design. Secondly, designs are explored at the individual block levels to verify the modeling approaches and also observe performance trends with technology scaling. Finally, these ideas are incorporated into the design of a complete transceiver operating at sub-terahertz frequencies. In Chapter 2, we discuss the design, implementation and measurement results of a 60 GHz power amplifier in 28 nm CMOS technology. In Chapter 3, we discuss the system level considerations in the design of a complete sub-terahertz system. In Chapter 4, we cover the design of an inverse Class-D switching power amplifier with block level measurement results. This PA is then integrated into the first prototype of a sub-terahertz transceiver operating at 260 GHz. The measurement results of the system are discussed. Chapters 5 and 6 bring out the shortcomings in the first prototype and describe a power efficient sub-terahertz transceiver operating at 240 GHz with measurement results. Concluding remarks are provided in Chapter 7.

### Chapter 2

# A 60 GHz Wideband Power Amplifier in 28 nm CMOS

The 60 GHz band with its 7 GHz of unlicensed spectra is a potential solution for high data-rate communication systems in applications such as personal area networks (PANs) and wireless backhauls. Due to the low cost of CMOS technology and its continued scaling in the last decade, transistors can now be operated at high frequencies. However, Moore's Law driven by digital circuits is detrimental to the design of high power RF and mm-wave systems. There have been several demonstrations of 60 GHz transceivers that achieve very high data rates with reasonable efficiency numbers [13–16]. One of the critical blocks that determines the overall system efficiency of a mm-wave transceiver is the power amplifier (PA) [17][18].

The design of the PA is especially challenging due to several issues. The low breakdown voltage of transistors and their reduced supply voltages severely limit the output power of the PA. Several on-chip power combining techniques need to be employed to overcome this issue and this leads to degradation in the overall efficiency. The IEEE 802.11ad standard defines the multi-gigabit wireless communication at 60 GHz and offers the unlicensed band from 57 to 63 GHz for communication in the United States of America. In order to cover this entire band and account for process variations, the PA must be designed as a wideband system with high efficiency and gain. The PA and all the other transmitter blocks must also be made broadband if the same unit needs to be used across the world to cover the WiGig band from 57 to 66 GHz. The improved transition frequencies of the devices provides a partial benefit in this respect. In addition to the above, the stability of the PA is of major concern. Hence, the design of an efficient, high power, stable, wideband PA in a scaled technology node is challenging.

In this chapter, we discuss the design of a linear wideband PA implemented in 28 nm

bulk CMOS technology [19][20]<sup>1</sup>. Due to increased coupling between the drain and source nodes (due to scaling), stability of the PA is of concern and is addressed using a drain-source neutralization technique. The design also utilizes low-k transformer techniques to achieve a wideband PA with 11 GHz bandwidth. To achieve a high output power of 16.5 dBm, the design uses transmission line based power combining networks. Section 2.1 discusses the 28 nm technology node by qualitatively comparing it with 65 nm and also describes the modeling of active and passive devices in this technology. Section 2.2 explains the drainsource neutralization technique and low-k transformer networks and also discusses the circuit details of the PA. The measurement results are shown in Section 2.3 and concluding remarks are provided in Section 2.4.

### 2.1 28 nm technology : Actives and Passives

Scaling to 28 nm technology node improves the transition frequency  $(f_T)$  of the devices and these typically range around 250 GHz. This serves as an important metric in mmwave applications where the data rates are in the Gbps range. In addition, the blocks must be designed to be broadband in nature as there is no convenient way to compensate for process and temperature variations (such as capacitive tuning at lower frequencies). Another important parameter that determines the maximum achievable gain from an active device is the maximum oscillation frequency  $(f_{max})$ . The  $f_{max}$  can be related to the  $f_T$  [21] as

$$f_{max} = \frac{f_T}{2\sqrt{R_g(g_m C_{gd}/C_{gg}) + (R_g + r_{ch} + R_s)g_{ds}}}$$

(2.1)

where  $R_g$  is the gate resistance,  $g_m$  the transconductance,  $C_{gd}$  the gate-drain capacitance,  $C_{gg}$  the total gate capacitance,  $r_{ch}$  the channel resistance,  $R_s$  the source resistance and  $g_{ds}$ the output conductance of the active device. Due to scaling, the gate resistance of the device degrades (as the thickness reduces) and the ratio  $C_{gd}/C_{gg}$  also increases. Although the  $f_T$  of the technology improves, the benefit gained in  $f_{max}$  due to scaling is marginal. Hence, the achievable  $f_{max}$  of the 28 nm technology node is comparable with that of 65 nm. Thus, the maximum achievable gain  $G_{MAX}$  of the device is around ~11-12 dB per amplification stage if one utilizes a common-source structure. The scaled power supply and low breakdown voltages offered by CMOS technology also severely limit the achievable output power levels and efficiency of PAs. In order to achieve high output power, one has to resort to on-chip power combining techniques where power from several unit PAs are combined using on-chip power.

<sup>&</sup>lt;sup>1</sup>In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of University of California, Berkeley products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html to learn how to obtain a License from RightsLink.

Figure 2.1. Model of unit finger of the active device

The modeling of active devices plays a critical role in determining the overall performance of the PA. The model of the active device capturing the various layout parasitics is shown in Fig. 2.1. Modeling the device at the schematic level with the added parasitics allows one to have a scalable model for design optimization and also reduces the simulation time. The model consists of the intrinsic capacitances  $C_{gd}$ ,  $C_{gs}$ ,  $C_{gb}$ ,  $C_{ds}$  and  $C_{db}$  between Metal 1 -Metal 1, Metal 1 - Gate and Metal 1 - Ground. The gate resistance is then modeled using  $R_{qate}$  whose value is determined from measurement results.  $R_{via,qate}$  and  $R_{via,drain}$  model the finger gate via resistance and finger drain via resistance respectively. This is followed by a  $\Pi$ -model of gate and drain traces  $(C_{q1a}, C_{q1b}, R_{q1}, C_{d1a}, C_{d1b}, R_{d1}, C_{qd1a}, C_{qd1b})$ . Multiple sections can be added for higher accuracy. The final gate and drain buses on the top metal are modeled using  $C_{g2}$ ,  $C_{d2}$  and  $C_{gd2}$ . This unit active device model is replicated NF times, where NF is the number of fingers. Careful layout of the active device minimizes the trace lengths and parasitic inductances due to the vias. Hence, no inductance is added as part of the core model. The capacitances in the core model are estimated using parasitic extraction tools. Fig. 2.2 shows the simulated intrinsic wiring capacitance ratio as a function of number of fingers (NF) ( $W = 1 \,\mu m$ ) and width (NF = 8). In both cases, we observe that the drainto-source capacitance  $(C_{ds})$ , gate-to-drain capacitance  $(C_{gd})$  and gate-to-source capacitance  $(C_{gs})$  are comparable. As the  $C_{ds}$  is a dominant portion of the wiring capacitance, it plays an important role in determining the stability of the amplifier as discussed in the next section. We also observe that the ratio  $C_{gd}/C_{gg}$  is close to 1/2 and this is one of the factors determining the  $f_{max}$  in this technology as discussed above. The same circuit is also used for modeling the cascode device. However, in this case, a diode (representing the p-substrate n-well p-n junction) must be added from the source of the cascode transistor to the ground node to accurately predict the PA performance.

With regard to passive devices, this technology node offers one thick metal layer whose current carrying capacity is comparable to that of the 65 nm node. However, due to the scaling of the metal thickness, the sheet resistance of the lower metal layers is 2-3X worse. The shrink in the lower metal stack moves it closer to the substrate and hence increases the loss contribution due to its conductive nature. The electromigration rules for the lower metal layers are also a factor of 2X worse compared to 65 nm technology node. This requires strapping of the lower metal layers and thus results in higher layout parasitics. Due to the stringent requirements with regard to metal density, passive devices such as inductors/transformers must include dummy metal layers from Metal 1 to the top metal. The layout of a transformer with dummy filling is shown in Fig. 2.3. The dummy fill adds a loss of 0.3-0.4 dB per matching stage due to eddy current losses. Complicated design rules along with the aforementioned issues make mm-wave design in this technology node challenging.

As described before, the active device is simulated using the model in Fig. 2.1 whose parameter values are in turn obtained from RC extraction. The connection traces along with the rest of the passives are simulated using High Frequency Structure Simulator (HFSS). The combiner/splitter transmission lines (to be described later) are implemented using the ultra thick metal layer. The transformers are implemented using vertically coupled spiral inductors on the thick metal and alucap layers. Fig. 2.4 shows the simulated inductance and quality factor of single loop inductors as a function of the outer diameter and width. The simulated quality factor averages around 18 at 60 GHz. Changing the inductor trace width shows no appreciable variation in the quality factor of the inductor (as the loss is dominated by the skin effect at these frequencies). The self-resonant frequency of the single loop inductor varies from 300 GHz to 100 GHz as the diameter is changed from 30  $\mu$ m to 150  $\mu$ m. As the quality factor is a weak function of the trace width, a trace width of less than 6  $\mu$ m is used for all the transformers to obtain a high self resonant frequency, thereby reducing the variation in the inductance values.

### 2.2 Power Amplifier Design

In this section, we describe the design of the power amplifier. The power amplifier comprises of three stages that are cascaded together using transformer networks. Fig. 2.5 shows the complete circuit diagram of the 60 GHz power amplifier. In order to achieve high output power, the design employs two cascode output stages that are combined using transmission line based power combining networks. In order to mitigate the stability issue in this technology node, a drain-source neutralized cascode stage is proposed. The design also uses low-k transformer networks to enhance the bandwidth of the amplifier. A single

Figure 2.2. Wiring capacitance ratio as a function of width (NF=8) and number of fingers (W=1  $\mu m)$

pre-driver stage operating of a 1 V supply voltage drives the intermediate stages. The PA is stabilized for common mode oscillations using resistors at the center taps (Vb1, Vb2, Vb3) of the transformers.

Figure 2.3. Transformer passive network with dummy metal layers

#### 2.2.1 Power Combiner/Splitter