# Next Generation Wireless Receiver Architecture Design in Deep-Sub-Micron CMOS Technology

Chaoying Wu

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2016-181 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-181.html

December 1, 2016

# Copyright © 2016, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

Copyright @ 2014

by

Chaoying Wu

# The Dissertation Committee for Chaoying (Charles) Wu Certifies that this is the approved version of the following dissertation:

# Next Generation Wireless Receiver Architecture Design in Deep-Sub-Micron CMOS Technology

| Committee:                    |

|-------------------------------|

|                               |

| Prof. Borivoje Nikolic, Chair |

|                               |

| Prof. Ali M. Niknejad         |

|                               |

| Prof. David J. Allstot        |

|                               |

| Prof. Paul K. Wright          |

### Next Generation Wireless Receiver Architecture Design in Deep-Sub-Micron CMOS Technology

by

#### Chaoying (Charles) Wu

A dissertation submitted in partial satisfaction of the requirements for the degree of

#### **Doctor of Philosophy**

in

Engineering – Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolic, Chair

Professor Ali M. Niknejad

Professor David J. Allstot

Professor Paul K. Wright

May, 2014

#### Abstract

Next Generation Wireless Receiver Architecture Design in

Deep-Sub-Micron CMOS Technology

by

Chaoying Wu

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

The University of California, Berkeley

Professor Borivoje Nikolic, Chair

Current advances in wireless receiver technologies are primarily driven by the need for cost reduction through (1) integration of a radio, an ADC and a digital processor on a single CMOS die, and (2) the design of low-power multi-standard capable receivers. However, due to the spectrum scarcity, future wireless standards, such as LTE, present a whole new set of challenges for radio system design. For example, LTE's highly fragmented spectrum requires multiple chipsets for support. Due to this cost overhead, there is no global LTE-enabled device available in the market now. Moreover, while carrier aggregation (CA) added to LTE brings unparalleled data rate improvement, it seriously complicates the RF frontend design. Modern commercial LTE solutions include multiple chipsets to support various scenarios of CA, which is not cost effective.

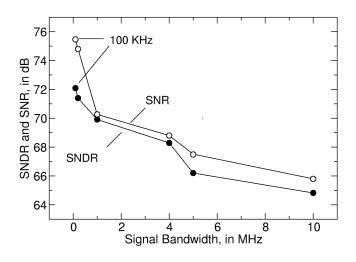

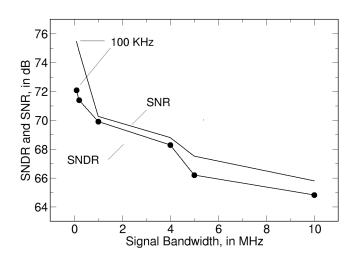

This work focuses on novel receiver architectures that address the design challenges associated with LTE-Advance from two perspectives: (1) a receiver that is capable of wide-frequency range of operation to cover all the LTE bands and (2) a single highly linear RF frontend to support non-contiguous-in-band CA. A novel sigma-delta-based direct-RF-to-digital receiver architecture is introduced in this work as an example of a complete integrated RF-to-digital frontend design capable to cover all the LTE bands. The design is implemented in 65 nm CMOS technology and the SNDR of the receiver exceeds 68 dB for a 4 MHz signal, and is better than 60 dB over the 400 MHz to 4 GHz frequency range. In a different example, we propose a passive-mixer-first receiver system to provide CA support in a cost-effective and power-efficient manner. Mixer-first receiver's superb linearity performance enables the possibility of a single receiver processing the entire LTE RX band, while most of the signal conditioning can be pushed into DSP to enjoy the benefit of process scaling. This design has been demonstrated in a 28 nm bulk CMOS technology, and the overall system achieves <3 dB NF, >15 dBm IIP3 and 35 dB gain with 60 mW of power.

#### Acknowledgements

I have had the honor to work and interact with a group of very intelligent and talented individuals at Berkeley. Without them, my stay in Berkeley would not be as memorable.

First and upmost, I can take this opportunity to express my gratitude to my advisor, Professor Bora Nikolic, for his vision and his dedication to research.

I would like to thank members of my project group, Professor Ali Niknejad for the most insightful discussions, Professor David Allstot for constant encouragement, Professor Elad Alon for always upholding the highest standards.

I have had many lengthy discussions with Christopher Hull and Ken Nishimura during my internships as well as formative stages of my research. My internship experience with Intel and Agilent enriched my knowledge, and widened my view in many perspective. I thank Haideh Khorramabadi, Tom Kwan and David Sobel for many constructive suggestions on research and career. Also, I thank Michael Reiha for his countless effort on teaching me how to properly write a scientific paper. I also appreciate all the helps from Professor Jason Stauth and Professor Seth Sanders.

I was based in BWRC for the most part of my Ph.D. career. I consider it a privilege to be associated with the center. The resource and level of collaboration is unmatched. Senior students and staff laid the foundation that made my research possible. I learned how to use the HFSS emulation platform from Lingkai Kong. I appreciate his effort in listening to me and providing the best solutions. I thank Brian Richards for his supports with my chip design. I was also lucky to have a period of overlap with Jiashu Chen and Jun-Chau Chien, who shared their great depth of design experience. Many thanks go to Yue Lu for always being patient with my questions and helps in emulation and design. Special thanks go to Gary Kelson, Tom Boot, Kevin Zimmerman and other staff members for making BWRC such a pleasant place to work.

The friendship of many peers in Berkeley is perhaps one of the best memories that I will take with me of my graduate studies. I have very much enjoyed being part of DCDG/Bora's group. Zheng Guo, Seng-Oon Toh, Ji-Hoon Park, Dusan Stepanovic, Vinayak Nagpal, Milos Jorgovanovic, Matt Weiner, Sharon Xiao, Katerina Papadopoulou, Jawhwa Kwak and Brian Zimmer have made my stay very memorable. For outside of the group, I appreciate Amin Arbabian's perspective in life, career and in research and most importantly I am thankful for his friendship throughout the years. I thank Siva Thyagarajan for being a loyal friend and for giving me many constructive and critical feedback and support on my research; I have benefited much from our

discussions. I also thank Steven Callender and Shinwon Kang for discussions regarding our common research interests.

Finally, my gratitude goes to my family, who has been a perpetual source of comfort and encouragement. They taught me the values of life, the importance of integrity and work ethics, which I only learn to appreciate gradually over time. They always valued my honest effort, no matter how minuscule. They provided the best cushion to allow me to recover from each setback and become more determined. I dedicate this work to them for their love and support that made it possible.

### **Table of Contents**

| List of Tables                                                       | xi  |

|----------------------------------------------------------------------|-----|

| List of Figures                                                      | xii |

| Chapter 1 Introduction                                               | 1   |

| 1.1 Related Work                                                     | 6   |

| 1.2 Thesis Organization                                              | 8   |

| Chapter 2 Software-Defined Radio Receiver Design                     | 11  |

| 2.1 RF Receiver Design Principles                                    | 11  |

| 2.2 RF Convertor Receiver Design                                     | 14  |

| 2.2.1 Overview on ΔΣ ADC Design                                      | 15  |

| $2.2.2 \Delta\Sigma$ ADC in RF Receivers                             | 19  |

| 2.3 Digital-Assist Receiver Architecture                             | 20  |

| 2.3.1 Passive Mixer-First Receiver Design.                           | 20  |

| 2.4 Understanding the Wireless Standards                             | 21  |

| 2.5 Performance Comparison of Exisiting Designs                      | 31  |

| 2.5.1 Software-Defined Radio Implemenation                           | 35  |

| Chapter 3 ΔΣ Receiver System Architecture                            | 36  |

| 3.1 Introduction                                                     | 36  |

| 3.2 Receiver Architecture                                            | 37  |

| 3.2.1 System Level Design                                            | 37  |

| 3.2.2 Loop Filter Structure                                          | 40  |

| 3.2.3 Jitter Sensitivity                                             | 46  |

| 3.2.4 Current-Mode-Integration Mixing/Sampling                       | 52  |

| 3.3 Summary                                                          | 59  |

| Appendix A Derivation of Multi-Bit RZ and NRZ DAC Jitter Sensitivity | 60  |

| Chapter 4 ΔΣ Receiver Experimental Prototype                         | 63  |

| 4.1 Introduction to System Implementation                            | 63  |

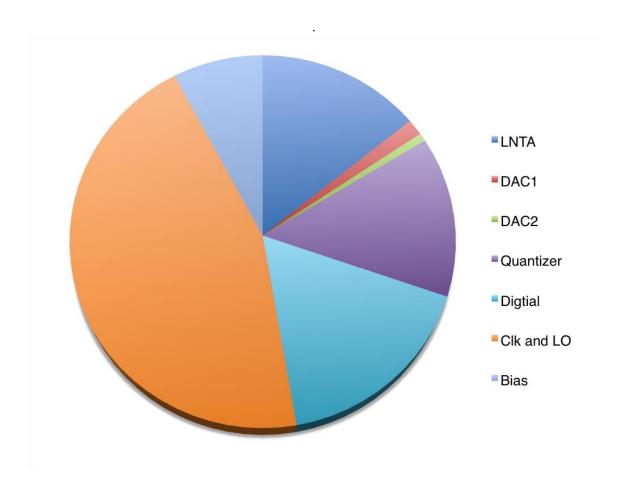

| 4.2 Circuit Design Details                                    | 65  |

|---------------------------------------------------------------|-----|

| 4.2.1 Sub-Channel Design                                      | 65  |

| 4.2.2 Low Noise Transconductance Amplifier                    | 67  |

| 4.2.3 Feedback DAC Designs                                    | 74  |

| 4.2.4 Comparator Design                                       | 77  |

| 4.2.5 LO Generation and Distribution                          | 80  |

| 4.3 Measurement Results                                       | 82  |

| 4.4 Conclusion                                                | 91  |

| Chapter 5 Mixer-First Receiver Design Considerations          | 92  |

| 5.1 Introduction to Passive CMOS Mixer                        | 92  |

| 5.2 Passive-Mixer First Receiver Design                       | 93  |

| 5.3 Baseband Trans-Impedance Amplifier (BB-TIA) Design        | 97  |

| 5.3.1 Noise Analysis for BB-TIA                               | 99  |

| 5.3.2 Analysis for BB-TIA Out-of-Band Linearity               | 102 |

| 5.4 Harmonic Rejection System                                 | 105 |

| 5.4.1 Harmonic Folding and Noise Figure Performance           | 105 |

| 5.4.1 Harmonic Rejection System Design                        | 107 |

| Appendix B Mixer Linearity Analysis                           | 116 |

| Chapter 6 Circuit Prototype for a Mixer-First Receiver Design | 125 |

| 6.1 Introduction                                              | 125 |

| 6.2 System Overview                                           | 125 |

| 6.3 Circuit Design Details                                    | 127 |

| 6.4 Optimizing Noise Figure Performance                       | 133 |

| 6.5 Measurement Results                                       | 136 |

| 6.6 Summary                                                   | 152 |

| Chapter 7 Conclusion                                          | 153 |

| 7.1 Significant Contribution                                  | 154 |

| 7.2 Future Work                                               | 155 |

| Bibliography | <br>158 | 8 |

|--------------|---------|---|

|              |         |   |

### **List of Tables**

| Table 2.1: | RF receiver performance summary                                                        | 32  |

|------------|----------------------------------------------------------------------------------------|-----|

| Table 2.2: | A summary for modern multi-mode multi-radio designs                                    | 34  |

| Table 3.1: | Comparision of P <sub>y</sub> P <sub>yd</sub> on different levels of DACs              | 46  |

| Table 3.2: | SNR comprision between RZ and NRZ DACs with different D                                | AC  |

|            | levels                                                                                 | 47  |

| Table 4.1: | Parasitic capacitor extraction result for different capcaitor layo                     | ut  |

|            | topology                                                                               | 68  |

| Table 4.2: | Performance comparison table                                                           | 87  |

| Table 5.1: | Gain allocation and $G_{\text{m}}$ requirement for different value of $R_{\text{FB}}.$ | 98  |

| Table 5.2: | Filtering Versus out-of-band IIP3                                                      | 100 |

| Table 6.1  | Noise power breakdowns for noise integrated over different                             |     |

|            | bandwidth                                                                              | 120 |

| Table 6.2  | Comparison table with other state-of-art receiver designs                              | 137 |

| Table 6.3  | Comparison table with designs for LTE                                                  | 138 |

# **List of Figures**

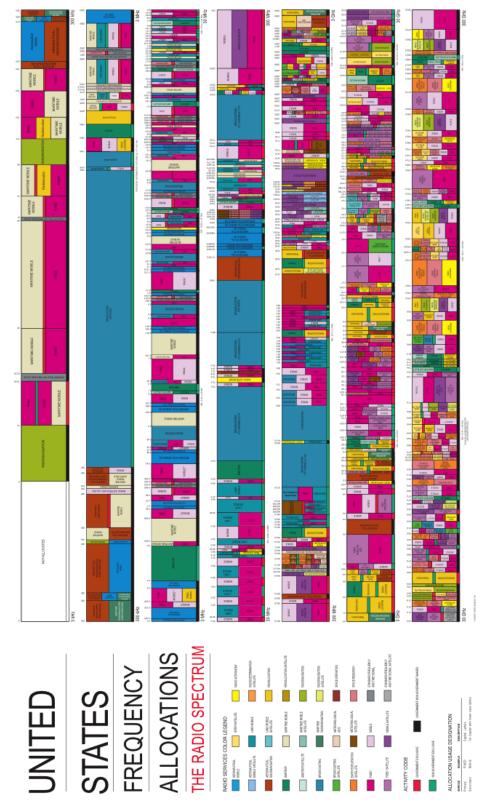

| Fig 1.1:   | Spectrum allocation for United States                                | 2   |

|------------|----------------------------------------------------------------------|-----|

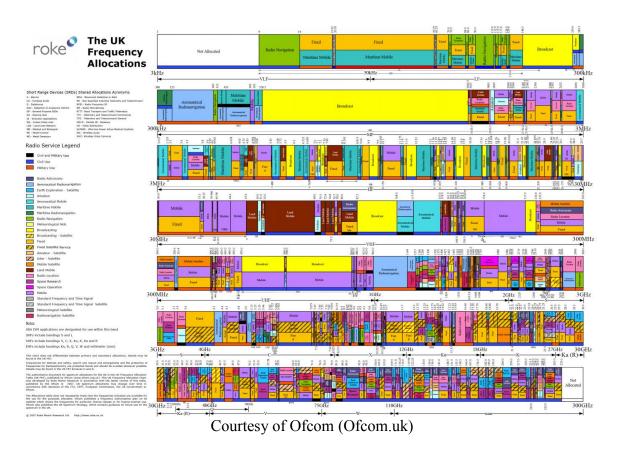

| Fig 1.2:   | The UK frequency allocations                                         | 3   |

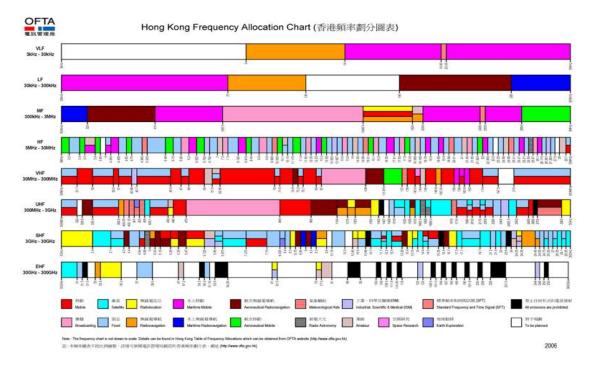

| Fig 1.3:   | Hong Kong frequency allocation chart                                 | 4   |

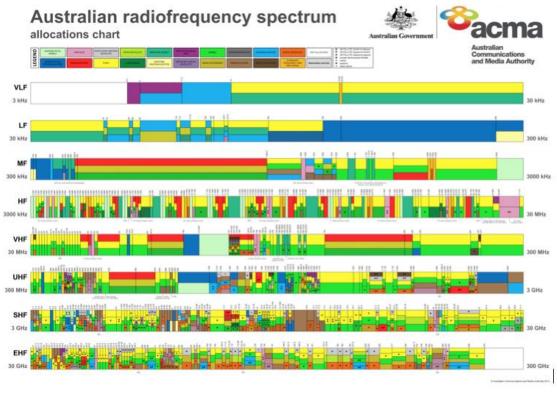

| Fig 1.4:   | Australian frequency allocation chart                                | 4   |

| Fig 2.1:   | The scenario of the near-far problem                                 | 11  |

| Fig 2.2.a: | A blocking mask for GSM                                              | 12  |

| Fig 2.2.b: | A blocking mask for UMTS                                             | 12  |

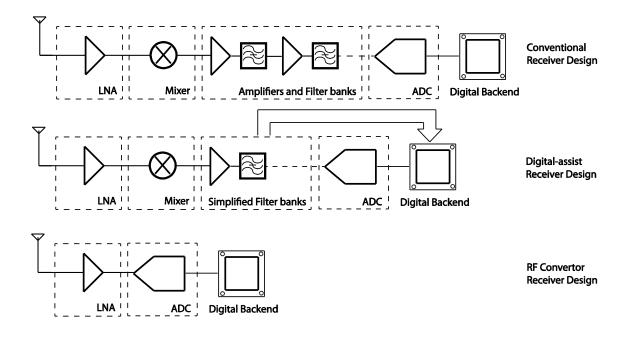

| Fig 2.3:   | Recent evolution of the RF receiver design                           | 14  |

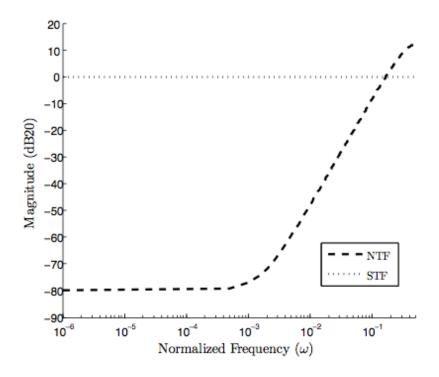

| Fig 2.4:   | A simple $\Delta\Sigma$ modulator                                    | .16 |

| Fig 2.5:   | Signal and noise transfer function of a second-order modulator       | .16 |

| Fig 2.6:   | Evolution of the wireless communication in the past thirty years     | 23  |

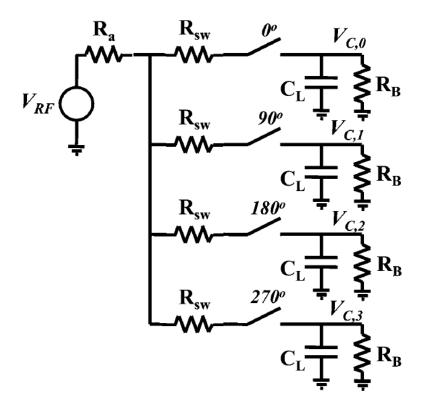

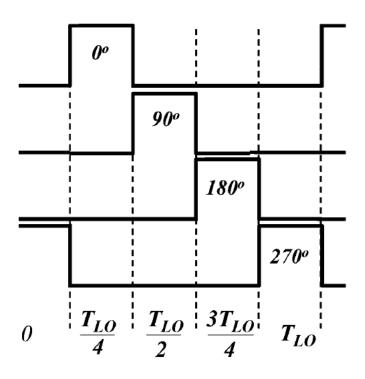

| Fig 2.7:   | Non-overlapping LO waveforms.                                        | 18  |

| Fig 2.8:   | LTE spectrum allocation across the world                             | 24  |

| Fig 2.9:   | Supporting LTE together with other wireless standards                | 24  |

| Fig 2.10:  | Five different models of IPhone 5 for global support                 | 25  |

| Fig 2.11:  | Five sub-carrier carrier aggregation to generate a higher bandwidth. | 26  |

| Fig 2.12:  | LTE carrier aggregation between the licensed and unlicensed bands    | .27 |

| Fig 2.13:  | System requirement for a device supporting LTE CA                    | 27  |

| Fig 2.14:  | Samples of the supported channels from a commercial design           | 28  |

| Fig 2.15:  | Three different scenarios for carrier aggregations                   | 29  |

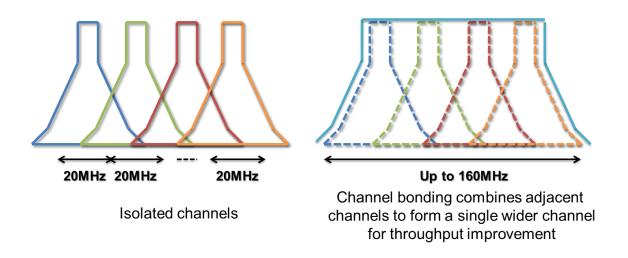

| Fig 2.16:  | Channel bonding for two 20 MHz channels                              | 30  |

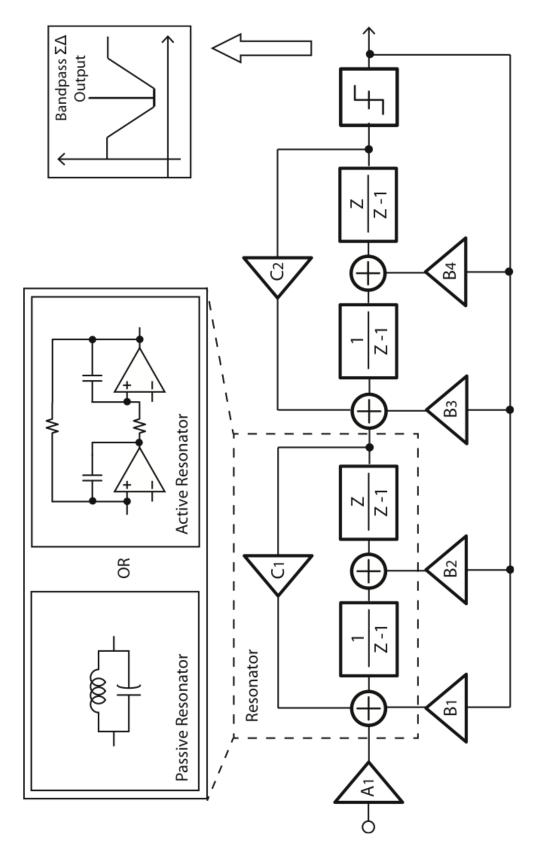

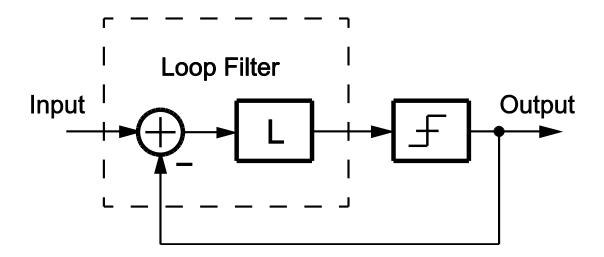

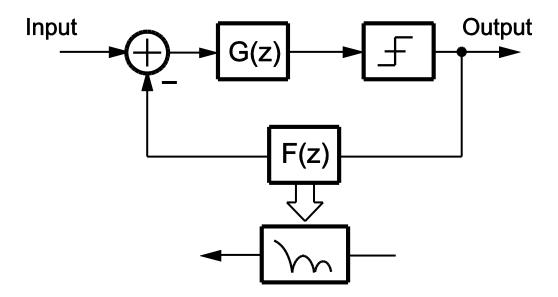

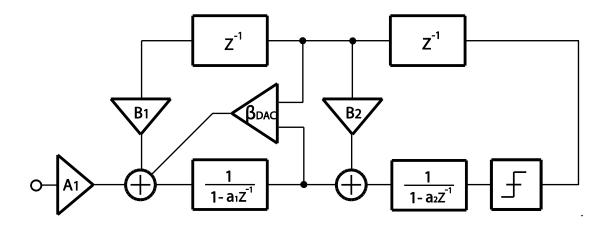

| Fig 3.1:   | Band-pass $\Delta\Sigma$ modulator loop filter in Z transform        | 38  |

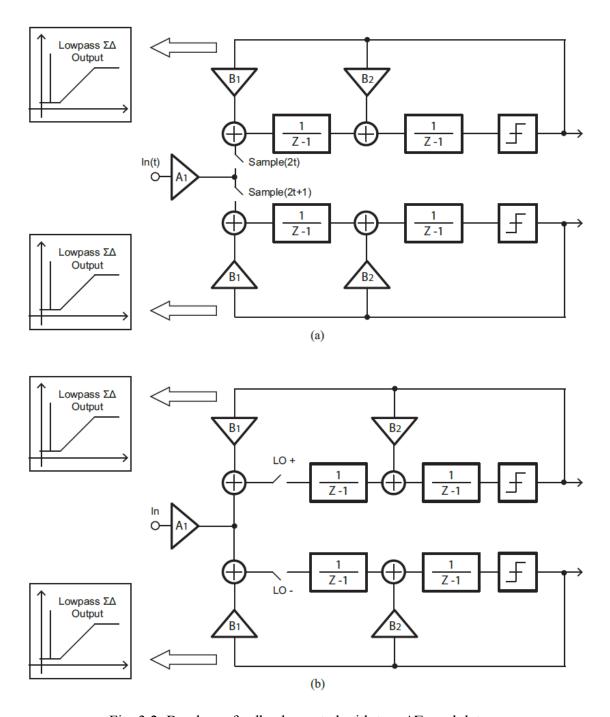

| Fig 3.2:   | Band-pass feedback created with two SD Modulator                     | 39  |

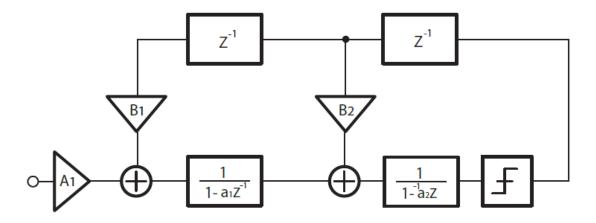

| Fig 3.3:   | A second order CIFB $\Delta\Sigma$ loop filter                       | .40 |

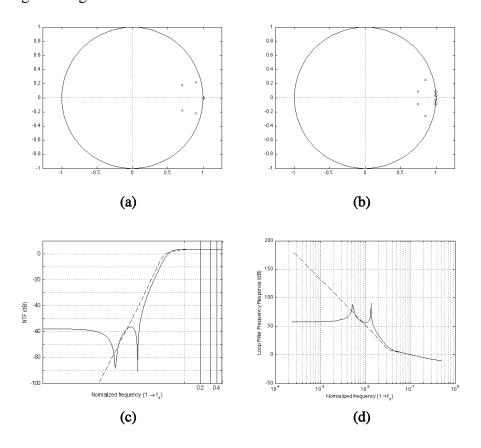

| Fig 3.4:   | Signal and noise transfer functions of a second order modulator      | .41 |

| Fig 3.5:   | Simulation results with complex zeroes                               | .41 |

| Fig 3.6:   | A simplified $\Delta\Sigma$ loop filter                              | .42 |

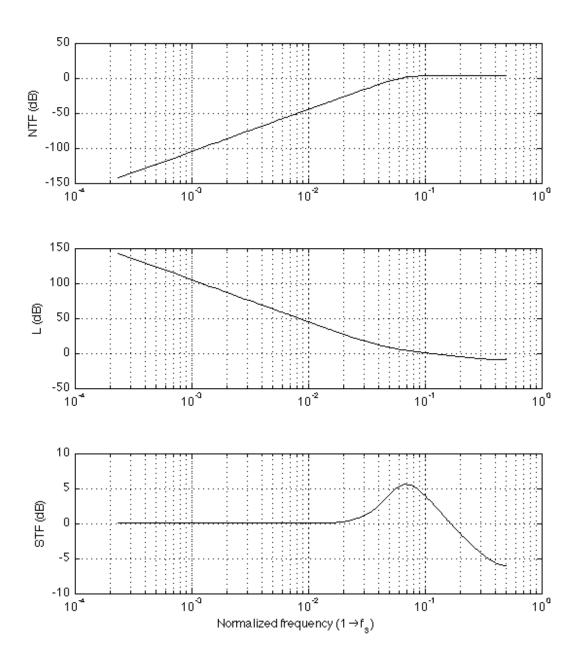

| Fig 3.7:   | Signal transfer function peaking in CIFF architecture                | .44 |

| Fig 3.8:   | A simplified $\Delta\Sigma$ loop model for FIR DAC                   | .45 |

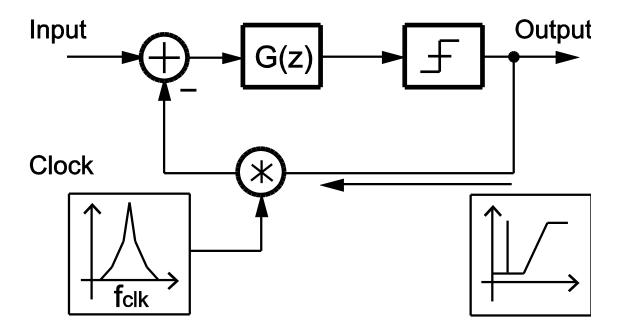

| Fig 3.9:   | A simplified $\Delta\Sigma$ loop model with phase noise              | .46 |

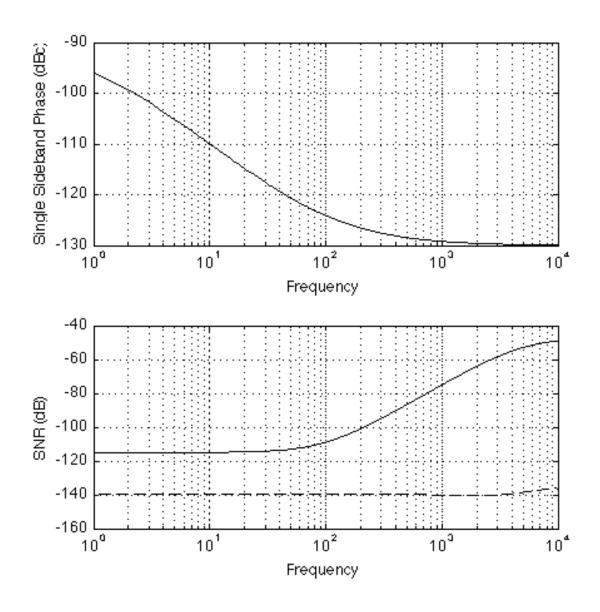

| Fig 3.10: | Simulated output spectrum with phase noise model                        | 47      |

|-----------|-------------------------------------------------------------------------|---------|

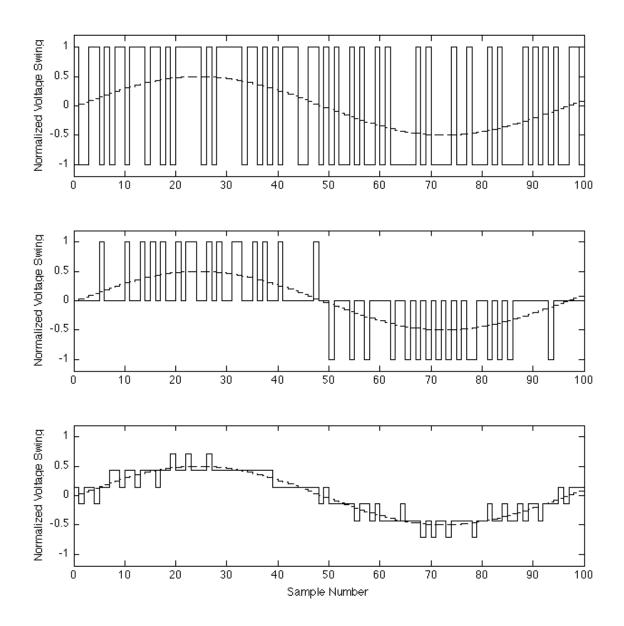

| Fig 3.11: | Time domain output waveform for $\Delta\Sigma$ ADCs with different quan | tizer   |

|           | levels                                                                  | 48      |

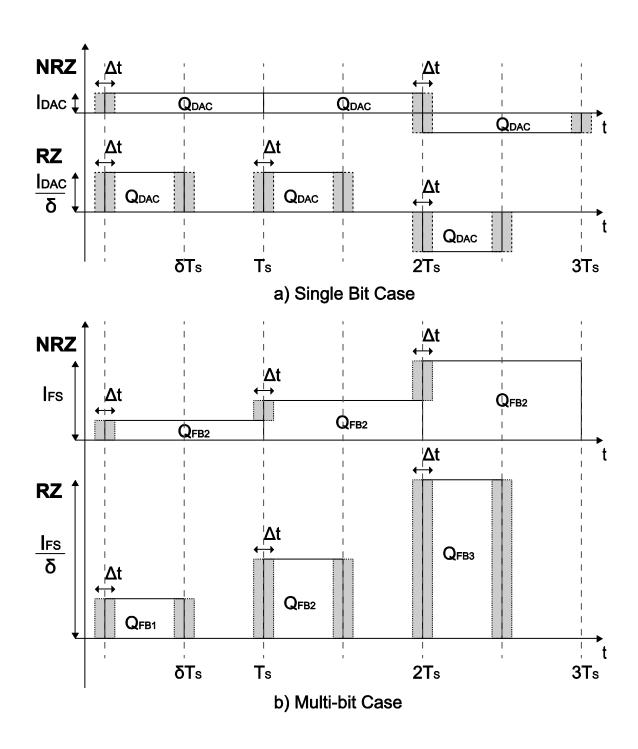

| Fig 3.12: | Comparison of jitter impact on RZ and NRZ DACs                          | 50      |

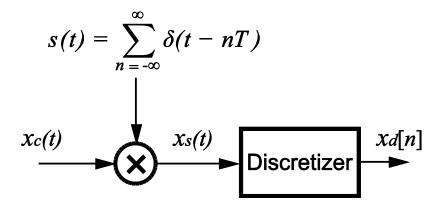

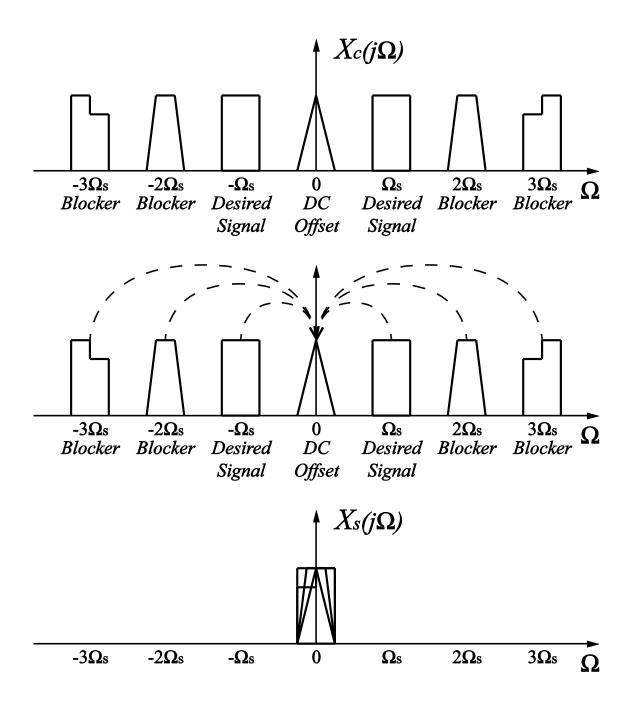

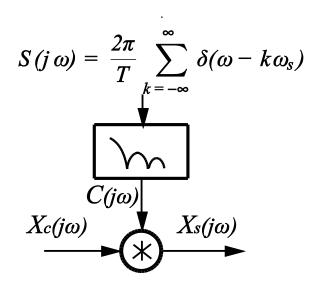

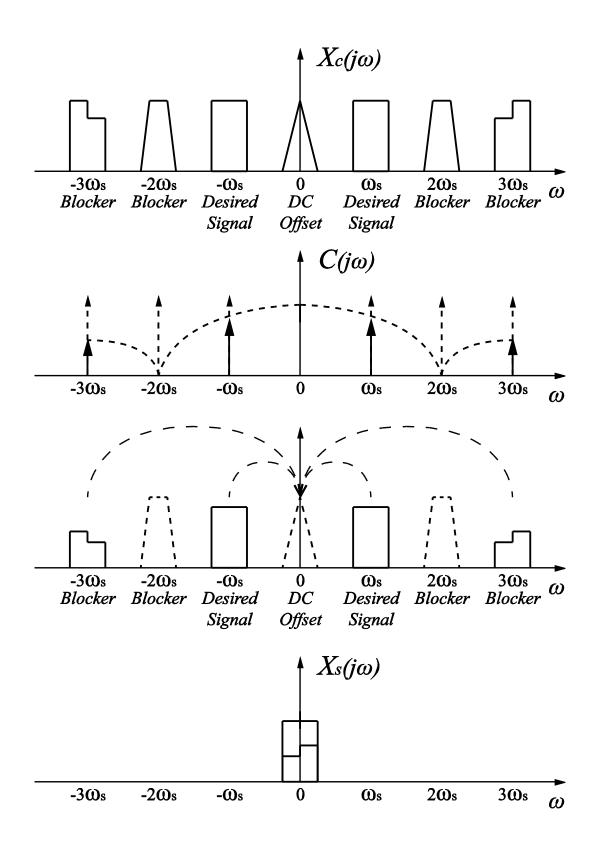

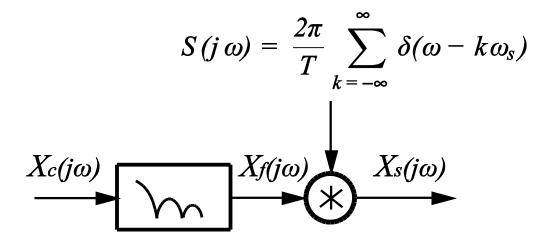

| Fig 3.13: | Equivalent sampling model in time domain                                | 53      |

| Fig 3.14: | Equivalent sampling model in frequency domain                           | 53      |

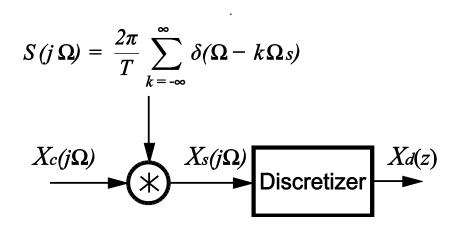

| Fig 3.15: | Effect of frequency domain of using sampling to downconvert RI          | Fsignal |

|           |                                                                         | 54      |

| Fig 3.16: | Equivalent mixing model in time domain                                  | 55      |

| Fig 3.17: | Equivalent mixing model in frequency domain                             | 55      |

| Fig 3.18: | Effect of frequency domain of using mixing to downconvert RF s          | signal  |

|           |                                                                         | 56      |

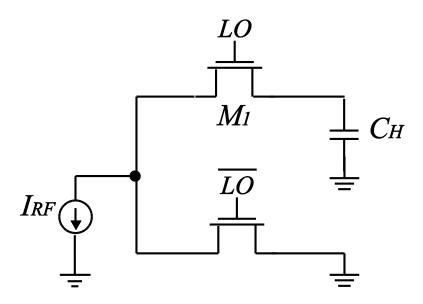

| Fig 3.19: | Current-mode integration sampler with single-ended output               | 57      |

| Fig 3.20: | Equivalent model for CMIS to downconvert RF signal in frequen           | cy      |

|           | domain                                                                  | 58      |

| Fig 4.1:  | Simplified block diagram of the entire receiver                         | 63      |

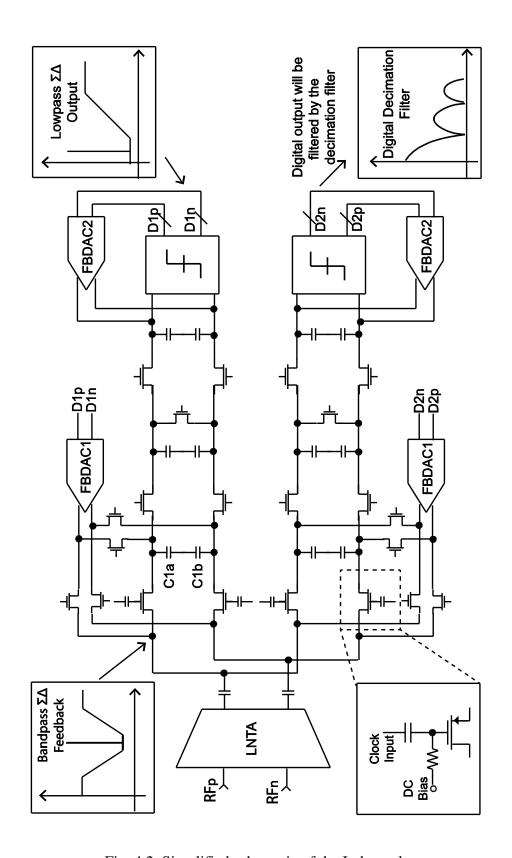

| Fig 4.2:  | Simplified schematic of the I-channel                                   | 65      |

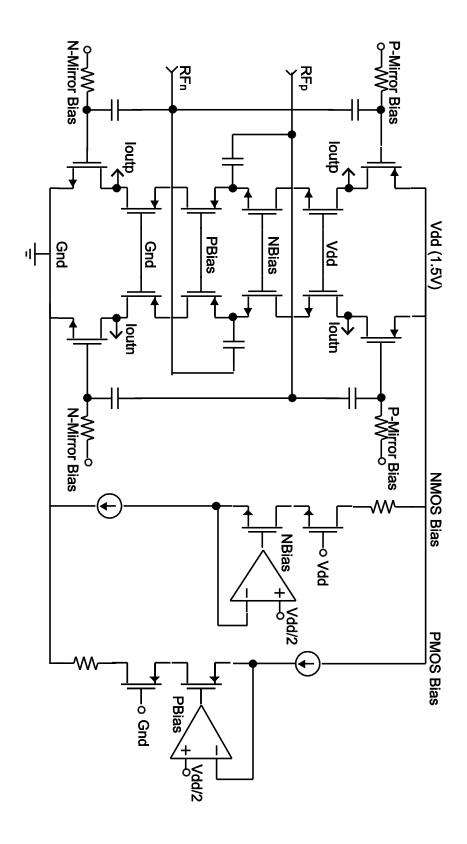

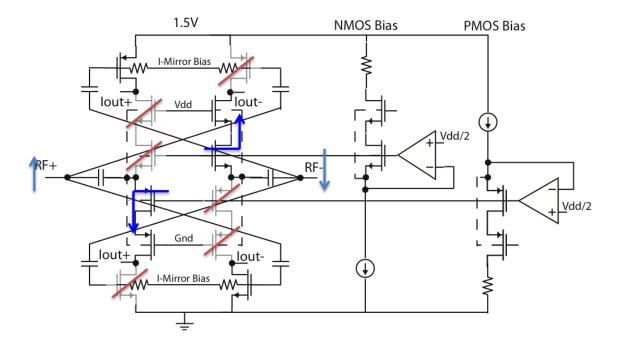

| Fig 4.3:  | Low noise trans-conductance front-end design with bias                  | 67      |

| Fig 4.4:  | Transformer-based output combining network                              | 68      |

| Fig 4.5:  | Noise simulation result of LNTA under different blocker level           | 69      |

| Fig 4.6:  | LNTA linearity simulation results                                       | 70      |

| Fig 4.7:  | Graphical explanation of the LNTA under large blocker transient         | 70      |

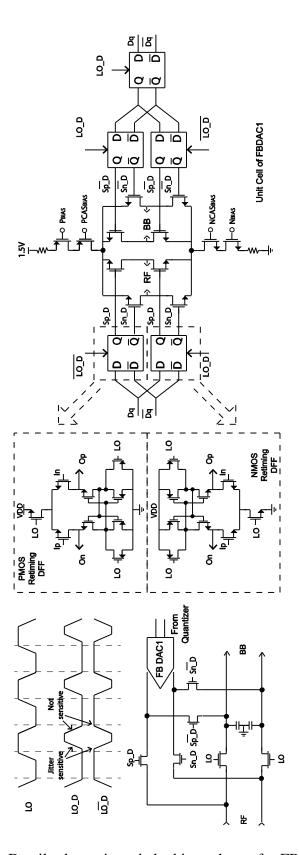

| Fig 4.8:  | Detail schematic and clocking scheme for FB-DAC1                        | 72      |

| Fig 4.9:  | System model including the effects of feedback DAC finite output        | ıt      |

|           | resistance                                                              | 73      |

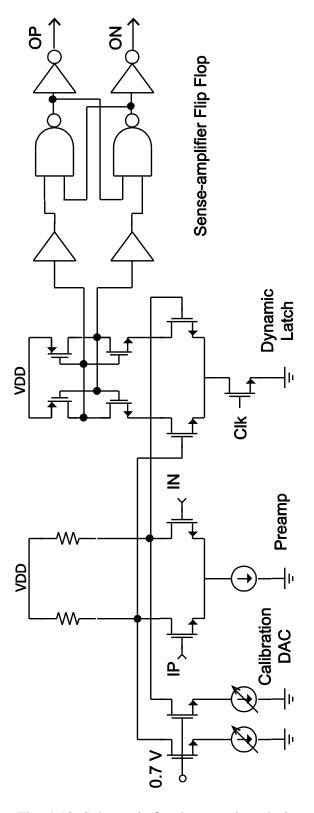

| Fig 4.10: | Schematic for the quantizer design                                      | 75      |

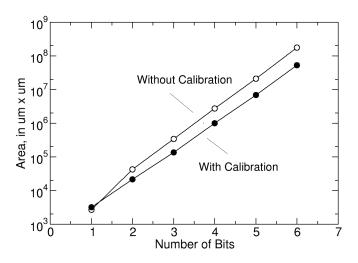

| Fig 4.11: | Quantizer area comparison with and without calibration                  | 76      |

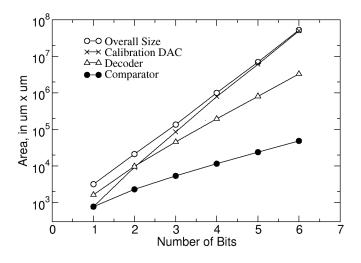

| Fig 4.12: | Quantizer area breakdown with calibration                               | 76      |

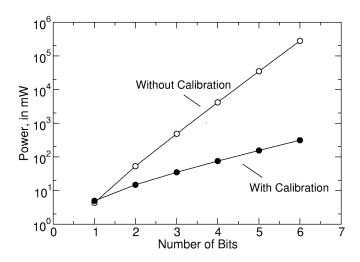

| Fig 4.13: | Quantizer power comparison with and without calibration                 | 77      |

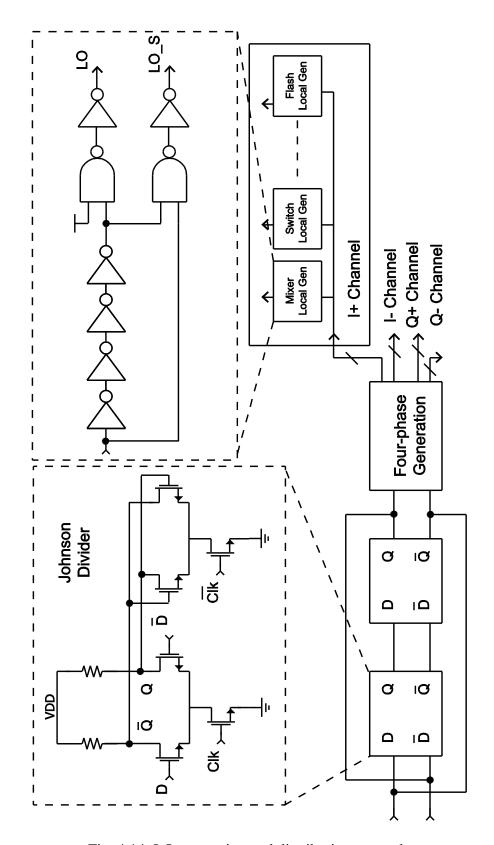

| Fig 4.14: | LO generation and distribution network                                  | 78      |

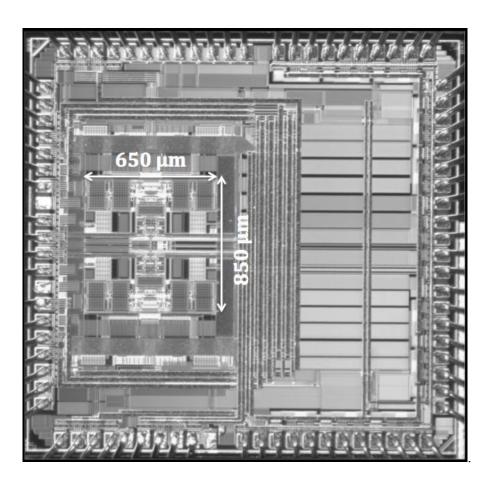

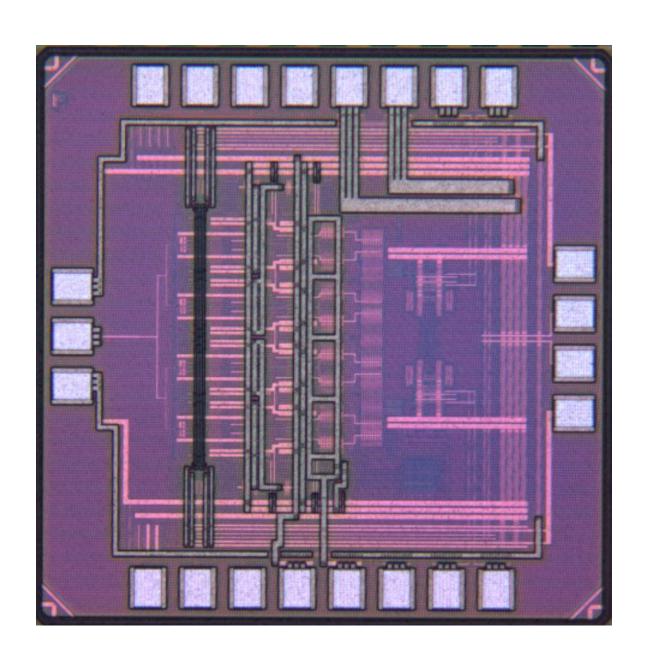

| Fig 4.15: | Chip microphotograph                                                    | 79      |

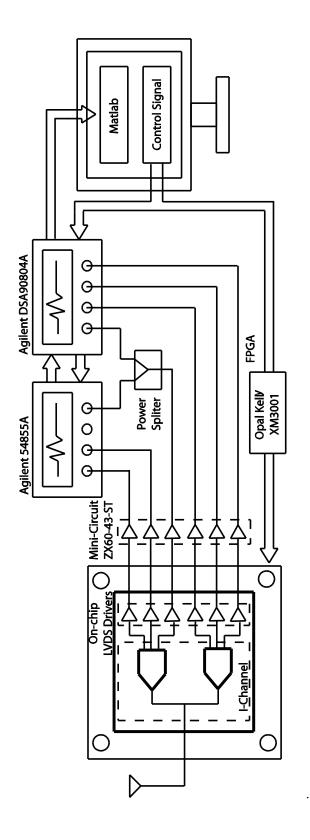

| Fig 4.16: | Measurement setup for data capturing and system control                 | 80      |

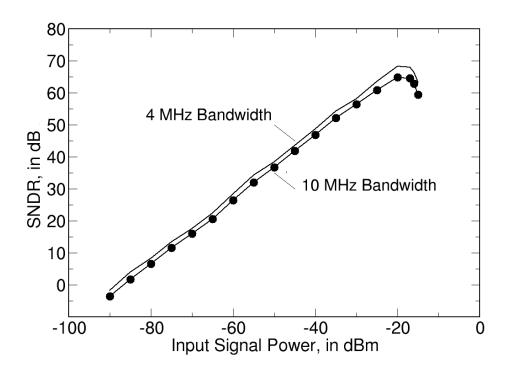

| Fig 4.17: | Measured SNR at 2 GHz carrier frequency                                 | 81      |

| Fig 4.18: | Measured SNR and SNDR at 2 GHz carrier frequency                     | 82       |

|-----------|----------------------------------------------------------------------|----------|

| Fig 4.19: | Output spectrum at 2 GHz center frequency with input signal offse    | t by     |

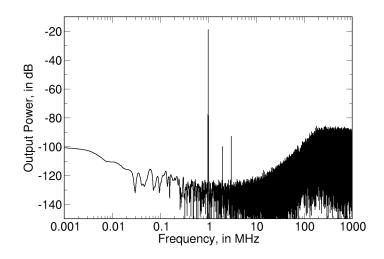

|           | 1MHz                                                                 | 82       |

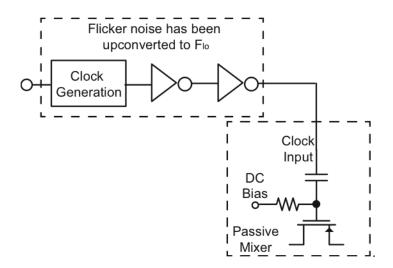

| Fig 4.20: | Flicker noise from LO chain upconversion and downconversion          | 83       |

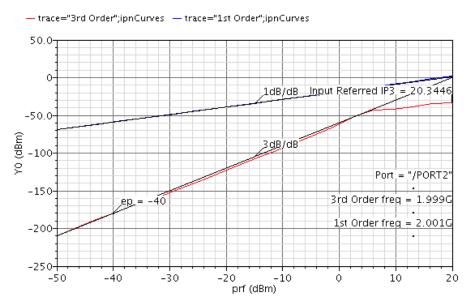

| Fig 4.21: | Two tone tests with 1 MHz tone spacing around 2 GHz center frequency | uency    |

|           |                                                                      | 83       |

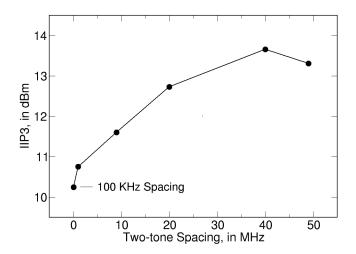

| Fig 4.22: | IIP3 versus two-tone spacing at 2 GHz                                | 84       |

| Fig 4.23: | SNR, SNDR vs. Signal Bandwidth                                       | 84       |

| Fig 4.24: | SNDR versus carrier frequency                                        | 85       |

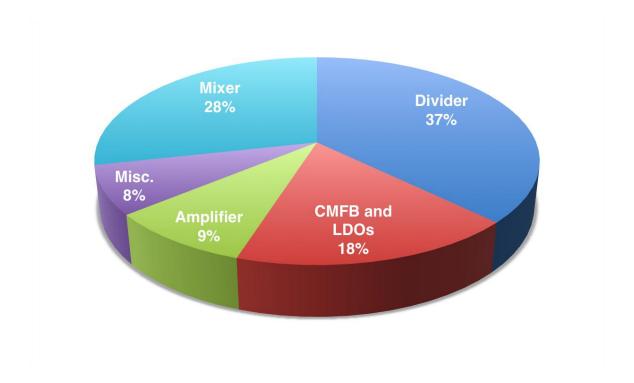

| Fig 4.25: | Power breakdown for the entire receiver system                       | 86       |

| Fig 5.1:  | Simplified circuit model of passive mixer                            | 91       |

| Fig 5.2:  | Non-overlapping LO waveforms                                         | 91       |

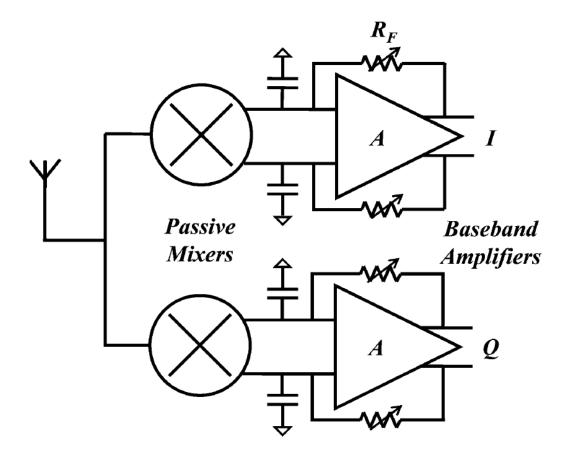

| Fig 5.3:  | Passive Mixer-first receiver with baseband TIA                       | 93       |

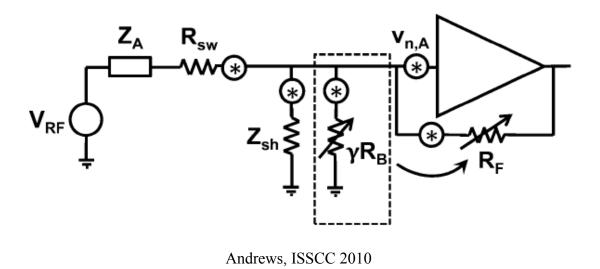

| Fig 5.4:  | Equivalent noise model for mixer-first design                        | 93       |

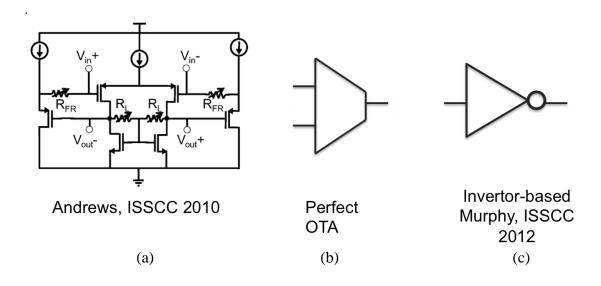

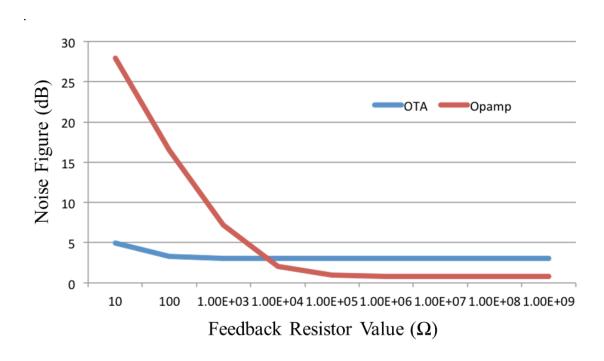

| Fig 5.5:  | Different amplifier structure candidates for BB-TIA design           | 94       |

| Fig 5.6:  | Noise figure (NF) for OTA and Op-amp with different feedback Re      | esistors |

|           |                                                                      | 96       |

| Fig 5.7:  | Noise figure with the second stage amplification stage               | 97       |

| Fig 5.8:  | BB-TIA with CL and CFB                                               | 101      |

| Fig 5.9:  | Input Impedance with CL and CFB.                                     | 101      |

| Fig 5.10: | Harmonic noise folding                                               | 103      |

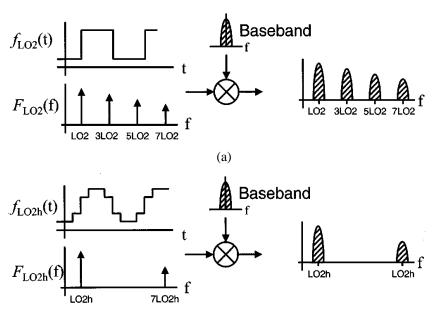

| Fig 5.11: | The idea of harmonic rejection                                       | 104      |

| Fig 5.12: | System level implementation of harmonic rejection                    | 104      |

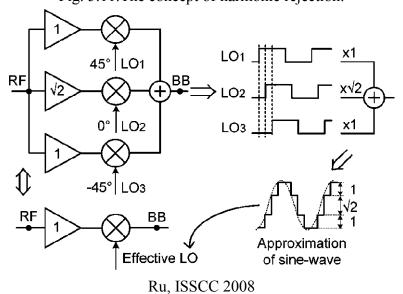

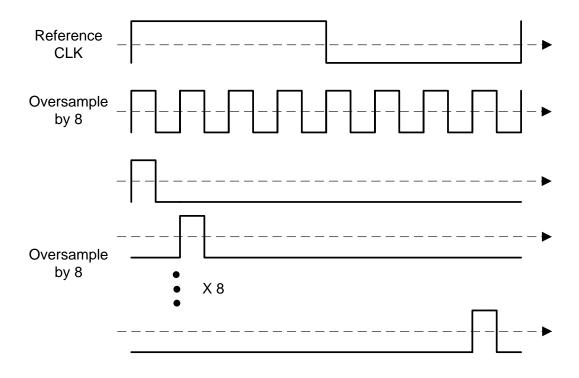

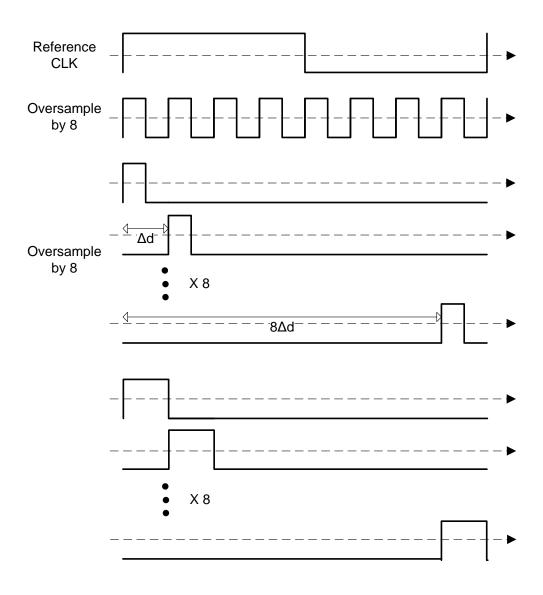

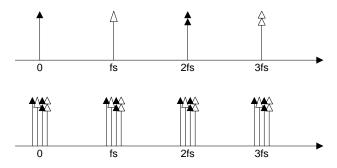

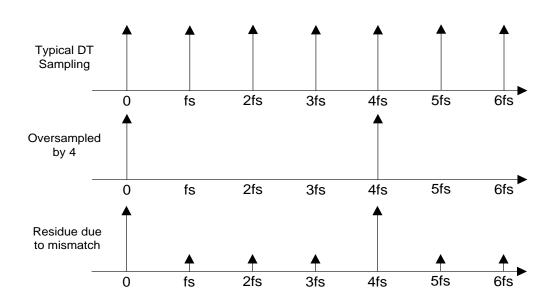

| Fig 5.13: | Oversampling and time domain interleaving sampling                   | 105      |

| Fig 5.14: | Time-domain interleaving sampling with different duty cycle          | 105      |

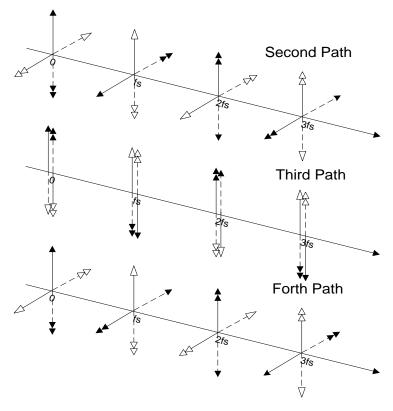

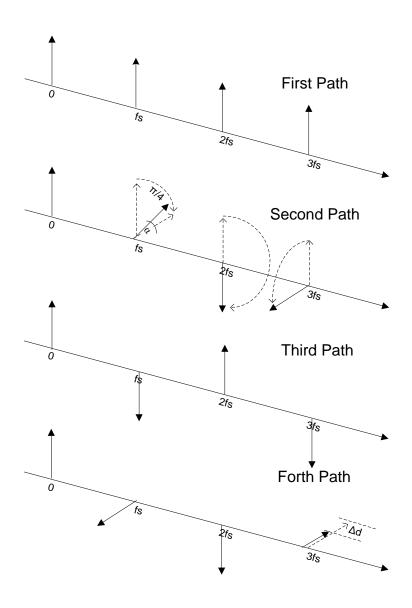

| Fig 5.15: | Aliasing content within one slower sampling path                     | 106      |

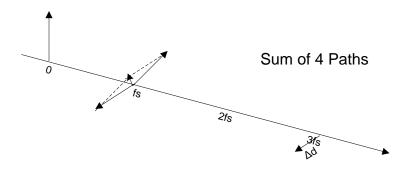

| Fig 5.16: | Aliasing contents in each of the paths                               | 106      |

| Fig 5.17: | Imperfect alignment due to the presence of mismatch                  | 108      |

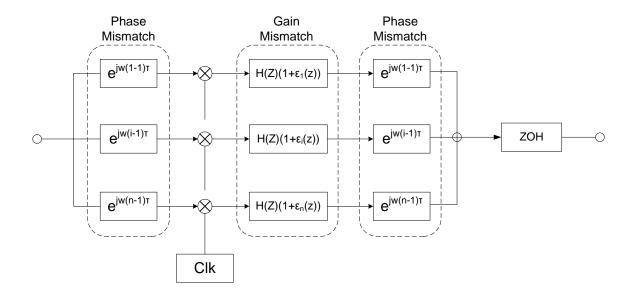

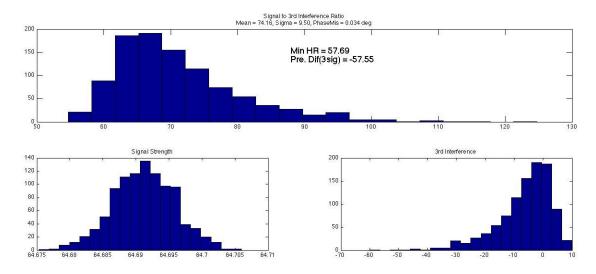

| Fig 5.18: | Incomplete harmonic cancelation due phase and gain mismatch          | 109      |

| Fig 5.19: | Performance limitation due to mismatches                             | 109      |

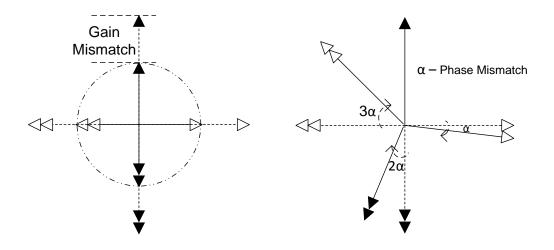

| Fig 5.20: | Behavior model for time-interleave system with phase and gain        |          |

|           | mismatches                                                           | 109      |

| Fig 5.21: | Gain and phase mismatches degrade the HR performance                 | 110      |

| Fig 5.22: | Phase mismatches simulation                                      | 111 |

|-----------|------------------------------------------------------------------|-----|

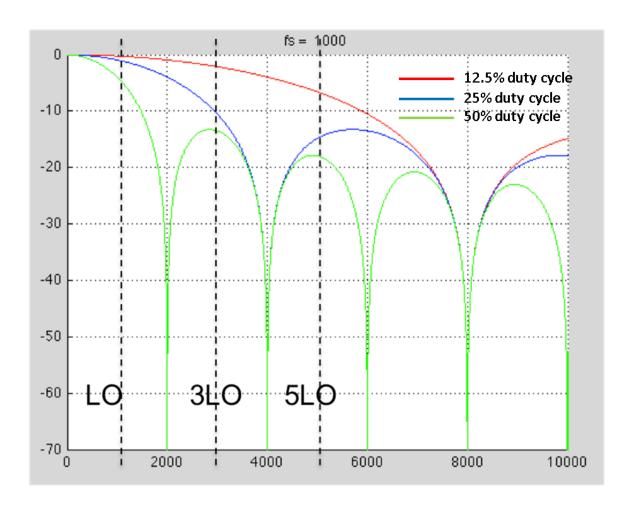

| Fig 5.23: | HR ratio measured with 50%, 25% and 12.5% duty cycle LO          | 111 |

| Fig 5.24: | LO with different duty cycle for harmonic rejection              | 112 |

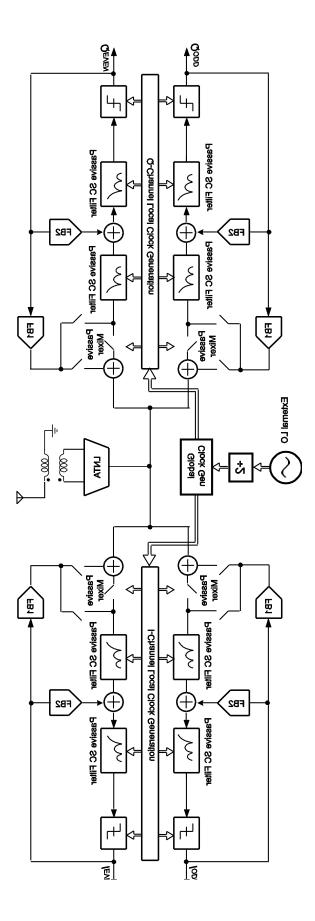

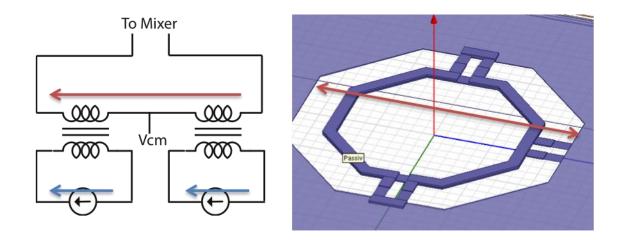

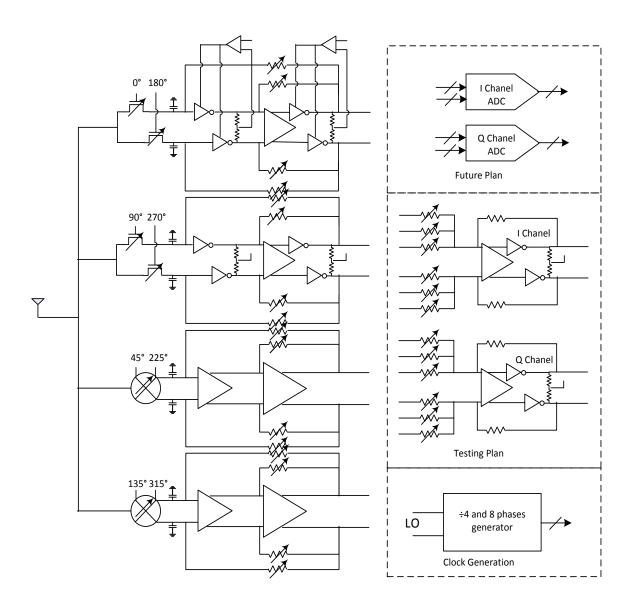

| Fig 6.1:  | Top-level system overview for mixer-first design                 | 114 |

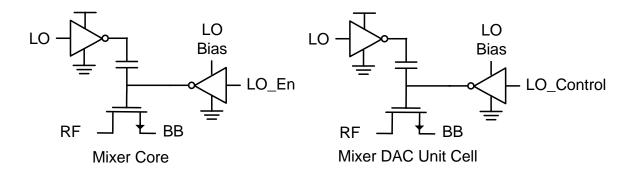

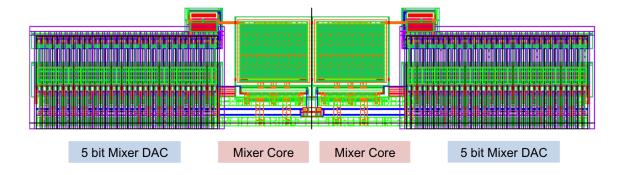

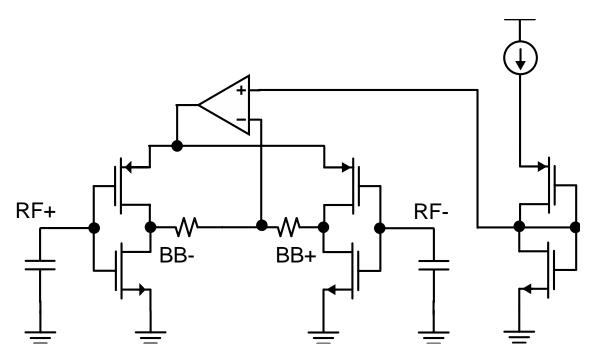

| Fig 6.2:  | Schematic for the mixer core and unit cell in the mixer DAC      | 114 |

| Fig 6.3:  | Layout for the differential mixer cells                          | 115 |

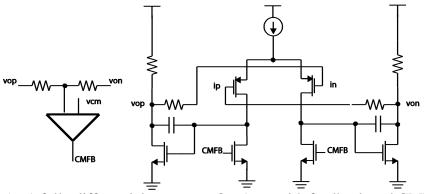

| Fig 6.4:  | Inverter-based amplifier design with CMFB and its bias scheme    | 116 |

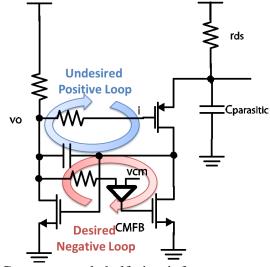

| Fig 6.5:  | Instability of a two-stage amplifier design.                     | 117 |

| Fig 6.6:  | AC-boosting compensation (ACBC) scheme                           | 118 |

| Fig 6.7:  | Detail schematic design for second stage amplifier design        | 118 |

| Fig 6.8:  | Floor planning for the entire system                             | 119 |

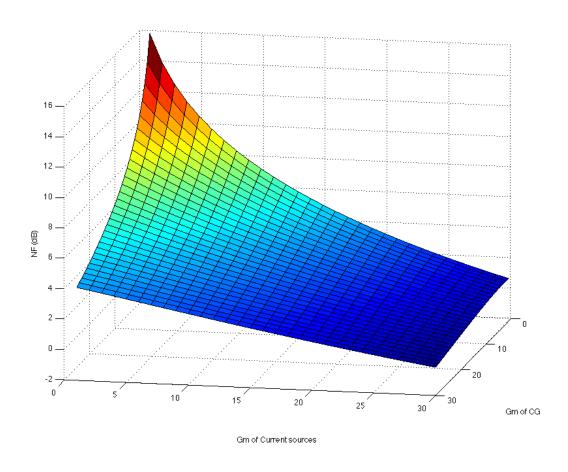

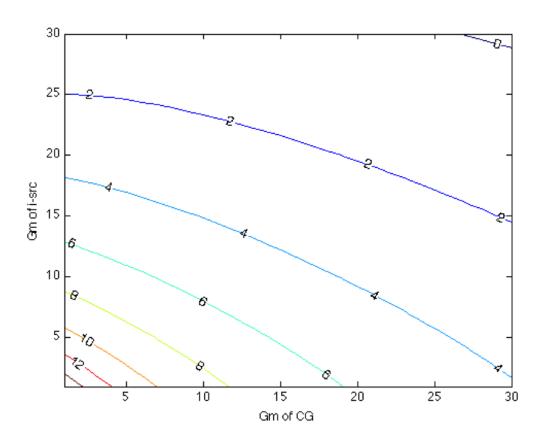

| Fig 6.9:  | Noise power breakdown during large signal transient              | 121 |

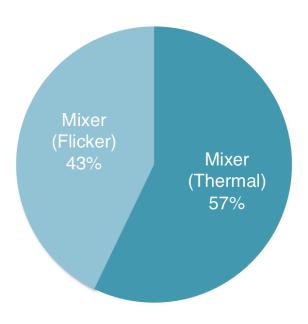

| Fig 6.10: | Mixer noise power break down.                                    | 122 |

| Fig 6.11: | Chip Microphotograph                                             | 123 |

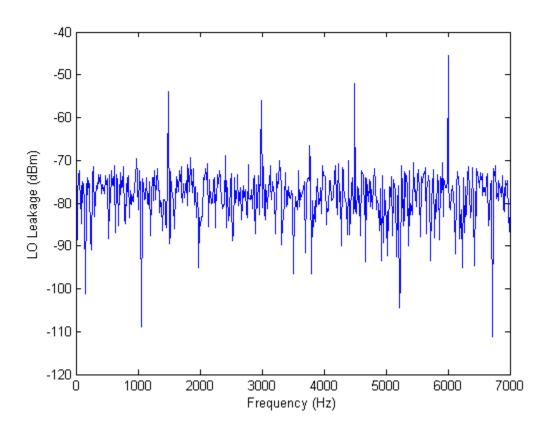

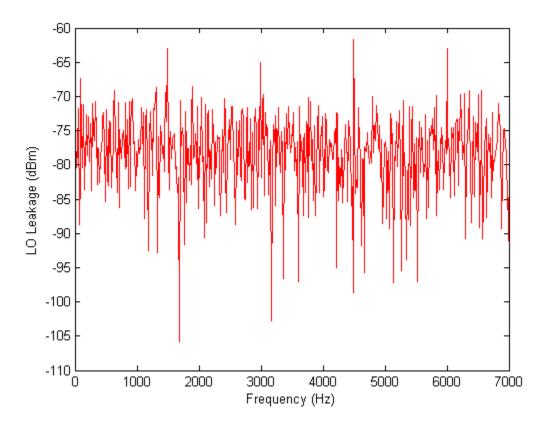

| Fig 6.12: | LO leakage before calibration.                                   | 124 |

| Fig 6.13: | LO leakage after calibration.                                    | 125 |

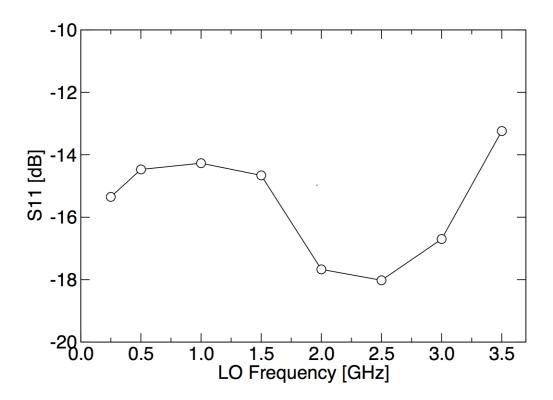

| Fig 6.14: | S11 over wide range of frequencies                               | 126 |

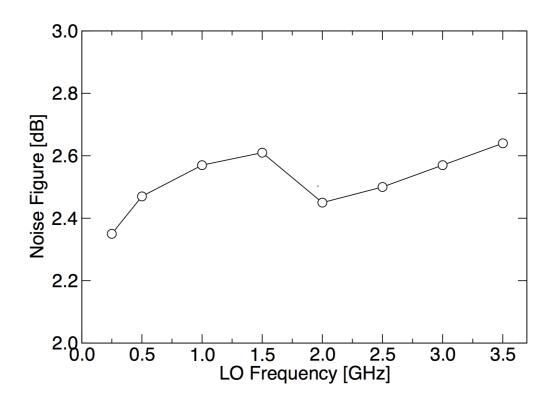

| Fig 6.15: | Measured noise figure performance from 250 MHz to 3.5 GHz        | 127 |

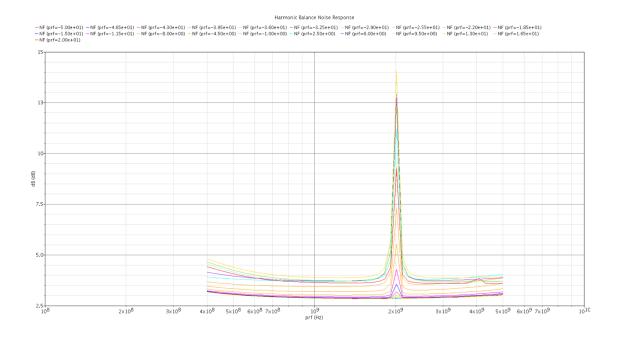

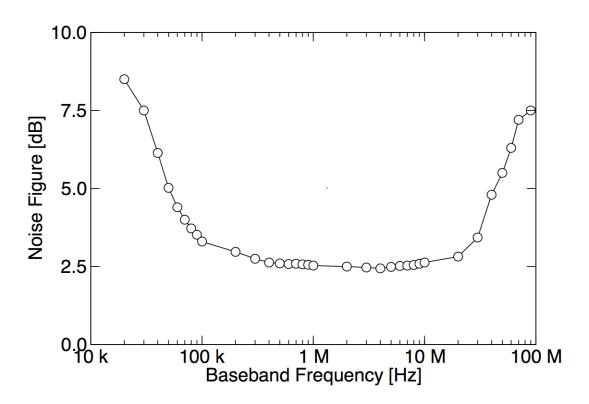

| Fig 6.16: | Measured NF performance with different baseband bandwidth        | 129 |

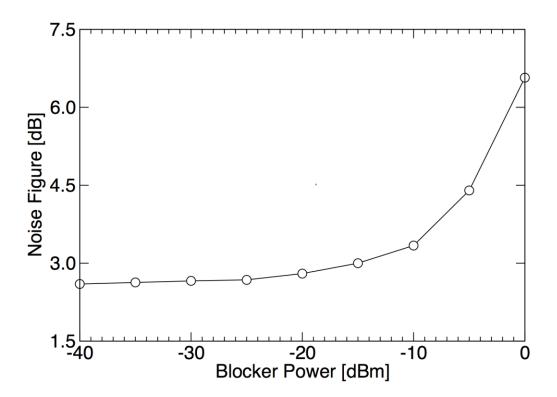

| Fig 6.17: | Noise figure measurement result with various blocker power level | 130 |

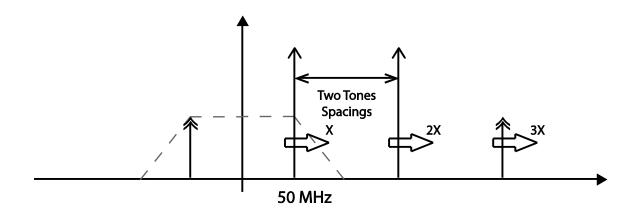

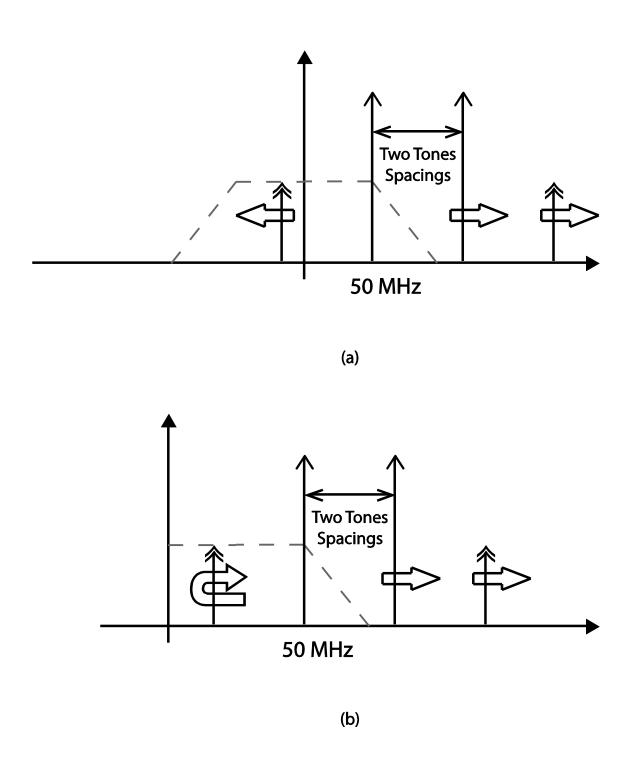

| Fig 6.18: | Test setup for measuring far-out IIP3                            | 131 |

| Fig 6.19: | Test setup for measuring close-in IIP3                           | 132 |

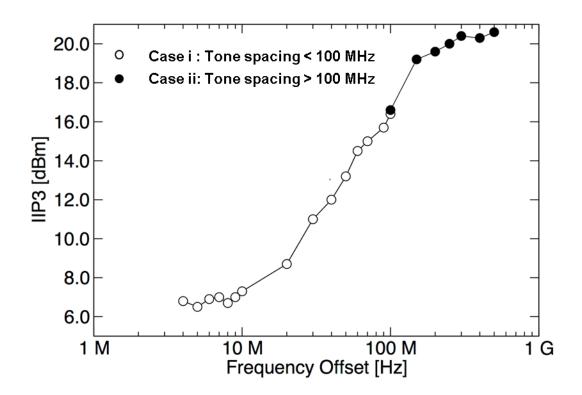

| Fig 6.20: | In-band and out-of-band IIP3 measured                            | 133 |

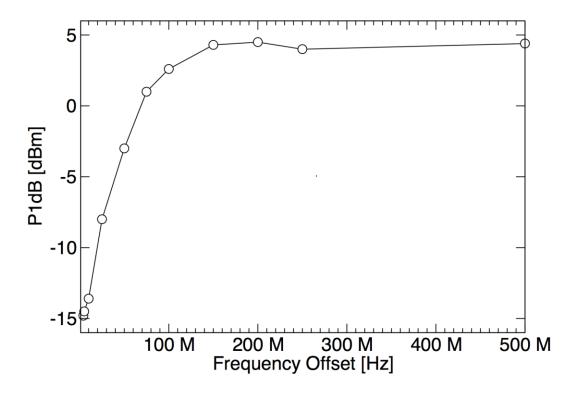

| Fig 6.21: | Measured P1dB for in-band and out-of-band                        | 134 |

| Fig 6.22: | Measured in-band P1dB                                            | 135 |

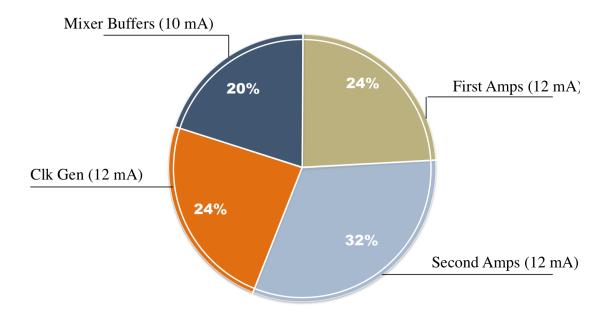

| Fig 6.23: | Power break down for major circuit blocks                        | 136 |

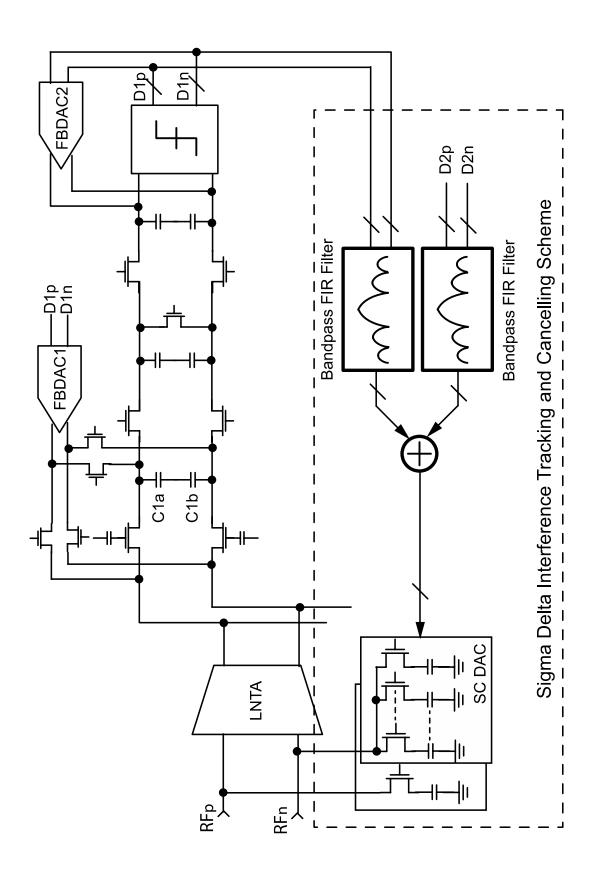

| Fig 7.1:  | Sigma delta receiver with interference cancellation              | 141 |

# Chapter 1

### Introduction

Wireless connectivity has shown its immense significance in the past decade. The continued technology scaling behind the very large system integration (VLSI) has enabled multi-radio system design for mobile applications, which has not been possible in the past century. This highly integrated system on chip (SoC) solution not only allows mobile devices to achieve smaller form factors, but also make the latest wireless technologies more affordable and accessible than they ever were in the past. Coupled with the unending desire for a faster data connection, the wireless connectivity continues to grow, as new wireless standards are introduced to address different needs every year. By now, a wide range of wireless standards exist. Each is highly optimized for power and cost for its own applications, and hence they support different in data rate requirement and cover different range.

It is challenging to support such a multitude of wireless standards with each of them being so drastically different from another. To add to the matter, different countries around the world allocate their spectrum in different ways, and even in the same country, different service providers are operating at different frequency bands. A high-end cellular handset device can support up to a dozen handful of different wireless standards such as GSM, CDMA, UMTS, HSPA, WiFi, Bluetooth as well as LTE, and it is able to operate over more than ten different frequency bands[1]. Up till now, transceiver ICs are often designed with a particular wireless standard in mind, due to the huge difference in system requirement between different standards. To achieve the desired support of the multitude of wireless standards support, multiple chipsets are often required. Given the apparent increase in the design complexity for wireless handset devices and the cost reduction possibility offered by the continuous scaling of the modern CMOS technology, the demand for a single uniform transceiver system which is capable for multi-standard and multi-band operation is highly desired, but not yet available.

Moreover, spectrum scarcity is an increasingly important issue for the decade, and therefore a flexible and dynamic spectrum allocation is preferable. Due to the proliferation of the wireless standards in the past decade, a majority of the commercial bands have been allocated to different standards (Fig. 1.1). As a result, the remaining available frequency bands that can be allocated for future standards are quite limited, while future wireless standards are still striving for a faster data rate and wider bandwidth.

Courtesy of Federal Communication Commission (FCC)

Fig. 1.1 Spectrum allocations for United States.

The story of government spectrum licenses dated back to the 1920s [115], when US official regulators realized that new transmitters might interfere with other system operating in the radio spectrum. The result is that every wireless system required an exclusive license issued by the government to operate; their operations in the radio spectrum are closely monitored and governed by U.S. Federal Communication Commission (FCC). After the introduction of the Advanced Mobile Phone System (AMPS) in 1983 in Chicago, which marked the beginning of the personal wireless application for civilians, it has been a thirty years of prosperity for the commercial wireless communication. However, with virtually all usable radio frequencies issued to different commercial operators and government branches, the inventory of wireless spectrum is running low on the remaining available bands. The irony is that even though wireless spectrum is something we cannot touch, smell, or see, it indeed is becoming one of the most valuable nature resources known to the human kind.

As matter of fact, the spectrum scarcity is a global issue, not just for the United States. As shown in Fig. 1.2, Fig. 1.3 and Fig. 1.4, wireless spectrum is tightly allocated in all major countries and urban areas all over the world. From the look of things, the end is nigh.

Fig. 1.2 The UK frequency allocations

Courtesy of Office of the Communication Authority (ofca.gov.hk) Fig. 1.3 Hong Kong frequency allocation chart

Courtesy of Australian Communications and Media Authority (acma.gov.au) Fig. 1.3 Australian frequency allocation chart

Cognitive radio (CR) is one technology under research that could potentially allow a more efficient use of the existing spectrum. While spectrum is auctioned off at high price, researchers have noticed that most of the licensed frequency bands are being under-utilized for most of the time [2], which suggest there is a potential to improve efficiency of the spectrum usage by sharing it among other systems. The advantage of cognitive radio is its feature of dynamic spectrum access (DSA), which allows different system to look for the unused channels and time-share it.

Regulatory efforts from governments around the world also aim to solve the issue. Cognitive radio is expected to operate in a large portion of the commercial spectrum in the future. As for now, vacant channels have been or plan to be released by governments for different applications. The new devices, known as TV band devices (TVBD) would operate in those frequency bands. Japan, Singapore, the United Kingdom as well the as the United States have been working on to support devices like this. For instance, the European Conference of Postal and Telecommunications Administrations have opened up the 470 to 790 MHz band for TVBD use.

In U.S, the FCC has established the fixed and the portable devices categories for TVBDs. Fixed devices can transmit with a power up to 1 watt, and they may use any of the vacant U.S. TV bands as 2, 5 to 36, and 38 to 51. On the other hand, the portable devices shall operate in TV channels from 21 to 36 and from 38 to 51. The permitted output is 100 mW EIRP, or at a reduced power level of 40 mW when there is an adjacent TV channel.

While research and regulatory efforts aim to solve the issue of the spectrum scarcity, the envisioned implementation of the CR poses a series of serious challenges on the RF transmitter and receiver design. The RF transceiver system needs to be flexible enough to adapt to different frequency band and different standards upon request, which is a huge deviation from the conventional wireless design methodology, where RF transceiver design is highly optimized by one set of application. On the other hand, a faster and more affordable network is always desired, which puts a lot of pressure on the future wireless standard in the absence of the CR. Before CR can be widely deployed, all the future standards would have to struggle between the limited remaining spectrum and the desire for higher data rate.

Long-Term Evolution (LTE) is the latest radio platform technology introduced to the family of the commercial wireless systems. As the result of the increasing global spectrum scarcity, LTE standard is a compromise that consists of total 43 separate bands ranging from 450 MHz all the way up to 3.8GHz. All 43 bands of LTE are separated to fit in the narrow available channels in different geographical regions, and the end result is a highly fragmented spectrum over a wide frequency range, which makes LTE the most difficult standard to provide world-wide support.

Another issue associated with the future wireless system is how to provide a higher throughput with limited bandwidth available. A similar idea as CR has been introduced to the latest wireless technologies, which is known as in-channel spectrum re-

allocation. The recent wireless standards, such as 802.11.ac and LTE all adopted similar schemes. LTE Advanced introduces the idea of carrier aggregation, where multiple inchannel sub-carriers can be allocated for the same user or different users in a wide range of manners, while the 802.11.ac (5G WiFi) includes the idea of channel binding, where the channel bandwidth allocated to a user can be expanded to achieve a much faster data rate when it is possible.

A reconfigurable transceiver is desired because of its ease to cover wide range of wireless standards and frequency bands, in particular it can be a cost-effective solution to support the LTE fragmented spectrum. Moreover, it can be extended to support future dynamic spectrum allocation, such as required by the cognitive radio. The final goal is a single uniform transceiver system, which is sufficiently flexible to support the existing as well as the future standards over a wide-range of frequency bands. The system would ease on the difficulties to support multitude of existing standards as well as open up a path for flexible spectrum allocation scheme for demanded to address the spectrum scarcity issue.

#### 1.1 Related Work

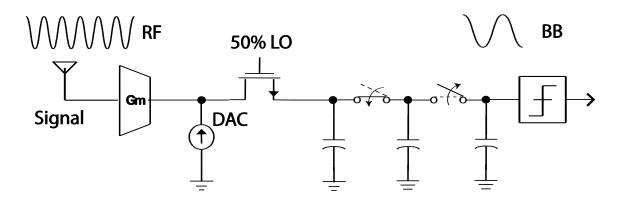

The idea of software-define radio (SDR) is first proposed by Joseph Mitola in 1992 [3]. A software-defined radio is a radio system such that most of its components are implemented by means of software on a general purpose computing device or embedded system. The ideal concept envisions a system which can monitor and transmit over the entire RF spectrum. Since then, there are a few notable examples known as the reconfigurable, or software-defined, RF receivers (SDR) such as references [4][5] [6][7][17][27][30]. All the listed designs adapted the convectional chain of elements design, where the systems begin with an RF amplification stage (LNA), followed by a frequency conversion state (mixer). Then the down-converted signal is filtered by a high-order low-pass filter prior to it reaches the ADC.

Throughout the years, there are a wide range of system implementation proposed to fulfill the grand vision of SDR. In particular, one thing that stands out in the UCLA design [5] is that it contains a low-power discrete-time low-pass filter. This filter makes use of an old and yet well-known concept: the passive switched-capacitor filter, which is popular choice for the baseband filter in RF receiver designs such as [5][7][8] and [9]. The passive switched-capacitor technique has several advantages, such as its precision in the filter cut-off frequency, relaxed requirement on the amplifier settling time as opposed to an active switched-capacitor filter design.

As demonstrated in [10], the passive switched-capacitor filter design can be better combined with the idea of current mode integration sampling mixer. This sampling mixer

provides the necessary down-conversion feature for a RF receiver system, while avoiding the otherwise power-hungry sample-and-hold circuit that is often required for any discrete-time circuit. Since it was first introduced in 2000, the idea of sampling mixer are widely adopted in a few different designs such as [7][8][5][11] and [12].

In this first design, a sampling mixer is used to down-convert the signal from radio-frequency down to base band, and integrated the converted charge on the sampling capacitor. The sample and held signal charge is then digitized by a fast-sampled  $\Delta\Sigma$  ADC. Most of the signal processing are removed from the analog domain and pushed into the digital domain, to take full advantage of the technology scaling.

To be able to support the various existing and future standards, a high-resolution and a high-speed ADC is always preferred for any software-defined radio system [3]. The high-resolution conversion not only can cover the different SNR requirements posed by the different wireless standards, but also ease the interference performance of the frontend circuits. On the other hand, the high-speed feature helps to reduce noise folding and blocker folding down to the band of interest, especially for a sub-sampling receiver system such as [13][14] and [15]. The issue of such an ADC is that its design is not feasible, given the limited power and area budget of a cellular device [16].

As proposed in [17], an alternative is a fast-sample, high-resolution but low-signal-bandwidth  $\Delta\Sigma$  ADC. Even though a high-speed ADC is preferable, wide-band digitizing is not really necessary. As a matter of fact, most of the wireless standards have data concentrated only in a narrow band centered around their carrier frequencies.  $\Delta\Sigma$  ADC is therefore perfect candidate for such an application. It samples the input RF signal at a fast rate, in the case of [17] which would be the RF carrier frequency. This meets the high-speed feature mentioned above. Moreover,  $\Delta\Sigma$  ADC utilizes the large OSR between the data bandwidth and its carrier frequency to produce the desired high resolution conversion within the signal bandwidth, which is essential to cover the SNR requirements for various wireless standards.

Historically, different  $\Delta\Sigma$  ADC based converter designs have been reported in the literature such as [17][18][19][20] and [21]. Some of the reported works have the mixer embedded in the loop design [17][20][21]. However, besides [17], the other two designs can only achieve limited bandwidths such as 40 KHz and 200 KHz, which are clearly not enough to support modern wireless standards. The designs as [18][19] are structured more like a conventional type of  $\Delta\Sigma$  ADC with the exception that a mixer is included ahead of the ADC. As will be discussed later in this work, embedding the mixer inside the  $\Delta\Sigma$  ADC loop filter can effectively improve the overall linearity performance, a better linearity performance is always preferred for SDR sign.

On the other hand, passive-mixers based on CMOS technology can be dated back in early 2000 [57][58]. The recent improvement the CMOS technology really empowers the passive mixer, as it replaces the active mixer designs in industrial system and academia endeavors [59][60]. Compared to the active mixers, passive mixer is known for its bi-directionality. Equivalently speaking, the passive mixer lacks of the reverse

isolation. Bi-directionality makes the analysis for a passive mixer more difficult, so engineering intuition is hard to obtain. Fortunately, recent research efforts such as [59] show an in-depth analysis of the circuit. It has been shown that its two-way frequency translation feature provides passive mixers with a series of benefits over active mixers, therefore, new opportunities together with unique design challenges arise.

Recent research has shown that by utilizing a multiple non-overlapping LO waveforms, the passive mixer designs can be better optimized compared with the use of a more traditional sinusoidal or simple square-wave LO waveforms [58][60][63][64][65]. Each of the clock pulses drives different mixer switch. Together, a series of phase-shifted baseband output can be generated, and they can later be summed with the baseband transimpedance amplifier (TIA) to reconstruct the complete baseband output.

The idea of passive mixer-first design is first proposed by Berkeley Sensor and Actuator Lab in 2004 as a low-power RF frontend for sensor network applications [24]. Limited by the understanding on the passive mixer at the time, the idea was considered too radical and didn't fare too well. Six year after it was first introduced, it has been brought back to the public attention by its original author, Alyosha Molnar and his student Caroline Andrews in ISSCC 2008 [25]. Since then, the idea of the passive mixer-first design has gaining a lot of attention.

### 1.2 Thesis Scope and Organization

This work focuses on the exploration of highly reconfigurable RF receiver designs with the intention to cover multi-band and multi-standard operations. The stress would be on the 0.4-4-GHz frequency-range where most of the commercial wireless communication standards take places.

Flexibility and re-configurability of the RF receiver should be achieved with minimum performance sacrifice as well as maintain the overall design in an economical manners from the silicon area's perspective. Thanks to the continuous technology scaling, digital signal processing (DSP) is getting more powerful and more affordable every day. One of the focuses of this work is to shift part of the signal processing features from the analog domain into the digital world to enjoy the precision and the affordability offered by the DSP core.

Two separate receiver architectures are proposed in this work. The first one is a high performance analog-to-digital converter design aiming at directly digitizing the RF signal and down-convert it to baseband in one step. In this proposed architecture, an analog signal residing at the radio frequency is converted directly into the digital domain using a second order down-converting sigma-delta ( $\Sigma\Delta$ ) modulator. The  $\Sigma\Delta$  ADC architecture is a good fit for such an application since it takes full advantage of the high oversampling ratio (OSR) to provide a wide dynamic range in the frequency band of

interest. Channel selection and bandwidth adjustment is pushed into the digital domain to enjoy the precision and affordability of the DSP offered by the latest CMOS technology scaling. A direct-down-conversion receiver design eliminates problem of with image frequency content folding which is always the issue for superheterodyne design.

A circuit prototype demonstrating the above concept has been designed and measured. The test-chip prototype is able to achieve an SNDR of close to +70 dB across a 4-MHz bandwidth with a programmable center frequency spanning from 400Mhz up to 4GHz. As will be illustrated in this work, the entire design is based on current mode operation, and the tight integration of the  $\Sigma\Delta$  receiver ensures the overall the system to maintain a very good linearity performance. A wideband IIP3 better than +10 dBm is measured in this test-chip prototype.

A second architecture, based on the mixer-first design is proposed in this work, where the first stage of amplification, which is considered as necessary for conventional designs, is removed for better wide-band linearity performance. In this proposed architecture, the RF signal is directly sent to the passive mixers, and it is then down-converted to the baseband directly. A reasonable noise figure can be ensured through careful sizing the passive mixer size as well as optimizing the baseband amplifier's gain. Without the LNA up front, the entire system achieves a better linearity performance over a wide range of frequency both in-band and out-of-band. This is essential to support carrier aggregation introduced in the LTE Advanced.

A passive-mixer-first receiver prototype is designed in 28 nm high-K metal-gate CMOS technology. The frontend 5-bit mixer-DAC provides a wide-band tunable impedance match to suppress the LO leakage. Baseband LNA together with the AC-boosting compensation amplifier provides a 50 MHz baseband bandwidth, which provides support for non-contiguous carrier aggregation for LTE in power efficient manners. The overall design achieves < 3 dB NF, > 15 dBm IIP3 and 35 dB gain with 55 mW power.

Chapter 2 of this dissertation centers on the overview of the issues presented by the upcoming standards. A set of system requirement is derived; a survey of the state-of-art solutions from the conventional receiver design as well as band-pass  $\Delta\Sigma$  ADCs is presented. Finally a few practical performance issues are examined.

Chapter 3 of this dissertation focuses on the system level design of the  $\Delta\Sigma$ . The  $\Delta\Sigma$  based receiver architecture is first introduced. Some of the highlighted analysis from reference [44] is summarized, and new analysis which is essential for performance improvement is also presented.

Chapter 4 of this dissertation discusses the detail implementation of the  $\Delta\Sigma$ -based receiver design. Details of a few core circuit blocks are revealed and explained. A novel class-AB LNTA circuit is presented, along with the pertinent analysis. This chapter concludes with  $\Delta\Sigma$  receiver's measurement results recorded from the test chips.

Chapter 5 of this dissertation addresses the system level trade-off for the mixer-first design. The structure of a mixer-first receiver is first explained, followed all pertinent analysis associated with the design.

Chapter 6 of this dissertation presents implementation detail of the mixer-first design. Detail descriptions of the important circuit blocks are discussed, together with detail analysis for the design. The latter part of this chapter is dedicated to the measurement results from the test chips.

Chapter 7 of this dissertation summarizes the important contribution of this work and suggested potential topics for future improvements and research.

# Chapter 2

## Software-defined Radio Receiver Design

This section starts with an introduction of general design principles of a RF receiver. Derivations of an ADC specification for a receiver are then demonstrated. After that, the basic of  $\Delta\Sigma$  ADC is introduced. Specifications for a reconfigurable receiver are then introduced with the intention to cover some of modern wireless standards. Finally, a survey of state-of-art integrated circuit solutions is presented.

## 2.1 RF Receiver Design Principles

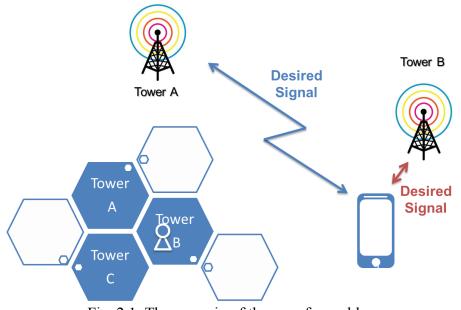

One well-known issue in the wireless receiver community is the near-far problem. The case is depicted in Figure 2.1. It can be described as a device try to receive a weak signal sent by a faraway signal source (system A) in the presence of a strong interference presented by another nearby signal source (system B). Often times, the desired signal and the interference might reside at different frequencies, but they may still be at a close proximity in frequency. As the result, instead of detecting the desired signal, the device might be overwhelmed by the undesired blocker, given the fact that the blocker might be orders of magnitude larger than the desired signal.

The RF receiver has to be able to endure this scenario and maintain the link robustly. In order to do this, a minimum amount of signal to noise ratio (SNR) has to be maintained. The actual required number varies from one standard to another. This minimum SNR does not always need to be positive. For example, some standards such as CDMA can even function properly with a negative SNR down to certain number.

Fig. 2.1. The scenario of the near-far problem

Different from the ADC designers, RF community likes to characterize SNR performance from the noise perspective. The metric used in this case is known as noise figure. Noise measured at the RF receiver has three common sources: 1. the thermal noise; 2. the thermal incident noise due to the antenna and 3. the added noise from the RF receiver circuit. Out of these three noise components, the first two are unavoidable. Therefore, the noise figure is mostly related to the receiver added noise. For the same amount of the SNR desired, a receiver with lower noise figure would be more sensitive to pick up a weaker signal, therefore perform better in the far-near scenario. The minimum signal power level for a particular receiver that ensures correctly demodulation is defined as the receiver sensitivity level.

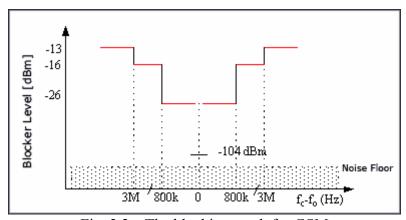

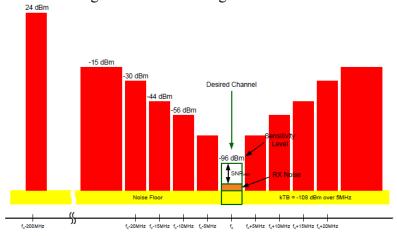

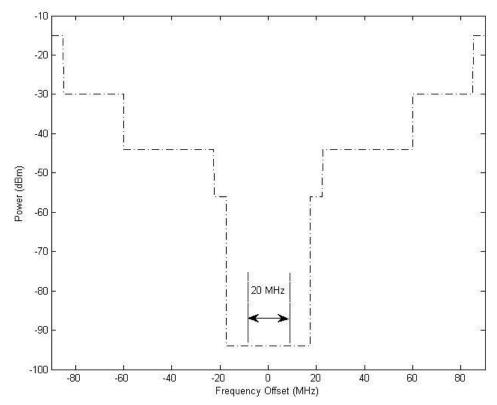

Beside noise figure or sensitivity level which would impact how a receiver to handle the near-far problem, the blocking mask requirement is also important. Two blocking masks for GSM and UMTS are shown in Fig. 2.2.a and b. The masks describe the worst case of near-far problems that should be supported in each of the standards. For the GSM case (Fig 2.2.a), while the signal can be as low as -104 dBm, a blocker which is only 3 MHz away can be at a power level as high as -13 dBm. The difference between the strongest 3 MHz blocker and the desired signal can be as large as 90 dBm. If it is

Fig. 2.2.a The blocking mask for GSM

Fig. 2.2.b The blocking mask for UMTS

translated to a voltage swing, the blocker would be on the order of 10<sup>4</sup> times larger than the desired signal.

Compared Fig. 2.2.a and Fig 2.2.b, it should be apparent that GSM and UMTS are quite different from each other. Not only the required receiver sensitivities differ by  $\sim$  10dBm, but the blocking masks are different too. Therefore, it poses serious challenges to software-define radio system, as it needs to meet the sensitivity and the blocking mask requirement for various standards.

Given this understanding, it helps to explore different strategies in partitioning the analog and the digital components for the optimal implementation of a software-defined radio system. First off, a conventional type of the receiver structure is introduced. Classical receiver design consist a series of amplification stages, filter stages and mixing stages in cascade as shown in Fig. 2.3. For direct-conversion receiver implementation as shown in Figure 2.3, the system has a LNA to provide early amplification which improves the noise figure performance. A down-conversion mixer then translates the signal content from the carrier frequency down to DC or to a low intermediate frequency (IF). Depending on the actual implementation, the filters might occur prior or after the mixing stage to meet the particular blocking mask requirement demanded by the standard. Finally, there is an ADC digitizing the analog signal, and digital output would then be sent to the DSP for demodulation and further processing. As the desired signal travels down this mixed-signal path, it is amplified gradually until it satisfies the minimum SNR requirement demanded by the demodulation process. On the other hand, the blockers or interferences would be attenuated stage after stage so that the components in the receiver chain would not be upset by their presence. As the combine result of these two processes, receiver can handle the near-and-far problem with confidence, and the received signal can demodulated successively even in the minimum signal level.

One major change in direction in the RF receiver design is in the filtering. The channel selection filter, is migrated into the digital domain as shown in figure 2.3 thanks to the technology scaling. Digital assisted design not only helps reduce the silicon area, but also helps achieve a more flexible design. However, the amount of signal processing can be shifted into the digital backend is dictated by the achievable dynamic range and the sampling rate of the ADC. The larger the ADC's dynamic range can be, more signal conditioning can be pushed into the digital domain, and hence the RF frontend is more flexible. From the sampling point of view, if an ADC can sample at faster rate, a less stringent anti-aliasing filter is required. Taking these two points to extreme, it yields to Mitola's vision of the software-defined radio receiver.

Fig. 2.3. Recent evolution of the RF receiver design

To accommodate the vast majority of existing wireless standards as well as the standards that shall be introduced in the next decade, digital-focus design methodology can enable the otherwise fixated RF design with great flexibility. Therefore, this work mostly focuses on the digitally-assisted receiver and the RF convertor architectures.

# 2.2 RF Convertor Receiver Design

At the core of Mitola's vision of SDR, it is a wide-range high-resolution ADC. One might be curious how high a resolution is needed to achieve the software-define radio. In GSM, for example (Fig 2.2.a), if one aims to migrate the all the filtering stage into the digital core, they would need an ADC with at least 102 dB dynamic range (17 bit ENOB) to handle the case where the minimum signal level coexist with 0 dBm out-of-band blocker.

ADC architectures can be categorized into three groups: flash, multi-step and oversampled ADC. Flash ADC can operate at a very high sampling rate, and introduces

the lowest latency among all. However, its resolution is limited and its design is power hungry. Multi-step ADC such as pipeline and SAR digitizes the input signal in a few cycles. They are good fit for applications with medium resolution and medium bandwidth requirement, but they fail to meet the speed and resolution requirements for SDR system. For a Nyquist-rate ADC design, a one-bit resolution improvement requires four times more power, therefore, designing a high-speed Nyquist-rate ADC whose resolution is capable of meeting the near-far requirement is too power hungry to be practical. As the result, Mitola's vision of digitizing at the antenna is not realizable.

To circumvent this fundamental issue, one needs to recognize that the ADC doesn't need to maintain its high dynamic range over the entire half-Nyquist bandwidth. The high dynamic range is needed only within the narrow band where the modulated signal resides. For the rest of the Nyquist bandwidth, the ADC can have a more relaxed dynamic range. The ADC still has to maintain a large full-scale range over a wide range of frequencies to handle the out-of-band blocker. This makes oversampling ADC, in particular  $\Delta\Sigma$  ADC, a potent candidate for software-defined radio application.

### 2.2.1 Overview on $\Delta\Sigma$ ADC Design

$\Delta\Sigma$  ADC is most well-known for its high resolution achieved over a narrow signal bandwidth in a power efficient manner. Moreover, it also ease on the front-end antialiasing filter requirements, hence reduces the overall power consumptions. There are many detail references on  $\Delta\Sigma$  ADC in the literature [22][23]. For completeness of this work, a brief overview of  $\Delta\Sigma$  ADC is included here.

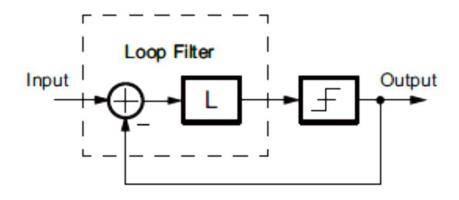

$\Delta\Sigma$  modulator as shown in figure 2.4 features two powerful concepts: oversampling and noise-shaping. Taking advantage of these two concepts,  $\Delta\Sigma$  ADC can achieve a high resolution even with a one-bit quantizer design.

Oversampling helps to increase the in-band SNR of a  $\Delta\Sigma$  ADC by spreading the quantization noise over a wider bandwidth. The signal content outside of the desired bandwidth BW would be cut off by the digital decimation filter. The oversampling ratio (OSR) can be described as the ratio between the Nyquist-rate ( $f_s/2$ ) of the quantizer and the desired signal bandwidth (BW):

Fig. 2.4. A simple  $\Delta\Sigma$  modulator

Fig. 2.5. Signal and noise transfer functions of a second-order modulator

$$OSR = \frac{f_s}{2 \cdot BW} \tag{1}$$

For a quantizer with N-bit resolution, its SNR is (1.76+6.02N) dB. Since the quantization noise is spread over a wider bandwidth, if we assume the quantization noise is white, then the overall in-band SNR with an oversampling ratio can be described as:

$$SNR = 1.76 + 6.02 \cdot N + 10 \cdot \log_{10}(OSR) \tag{2}$$

As OSR is doubled, the overall SNR would increase by 3 dB.

The overall SNR can be further improved by pushing most of the quantization noise out of the band of interest, which is known as the noise shaping. Noise shaping is implemented by enclosing a loop filter inside the  $\Delta\Sigma$  modulator loop as shown in the figure 2.4. This loop filter should have minimum impact on the desired signal, but it highpass filters the in-band quantization noise, and pushes them out of the band as demonstrated in figure 2.5. The actual loop filter implementation varies from design to design, and it can either take the form of a low-pass structure or a band-pass structure. By combining the techniques of oversampling and noise shaping, a much larger SNR improvement can be achieved

Without a loss in generality, assume a low-pass filter is chosen as the  $\Delta\Sigma$  loop filter. The loop filter should have minimum impact on the desired signal, therefore the signal transfer function (STF) is flat in this case. The loop filter's low-frequency gain forces the feedback signal to follow the input signal with high fidelity. The quantization noise content in those frequencies is rejected by the low-frequency gain of the entire loop structure. For short, the large loop gain of the feedback system helps to suppress the in band noise. As the loop gain diminishes at higher frequency, the effect of the noise suppression degrades as well. Therefore the noise transfer function (NTF) rises as the frequency increases, as shown in figure 2.5.

For example, in the case from figure 2.5, a second order low-pass filter is chosen as the  $\Delta\Sigma$  loop filter. The STF and the NTF can be described as:

$$STF = 1 (3)$$

$$NTF = 1 - z^{-2} (4)$$

The STF is truly flat over the entire frequency, and the NTF has a high-pass nature compared to the low-pass loop filter. Given this particular nature of the NTF, the quantization noise is lower at the low frequencies, and hence a higher dynamic range can be assured there. Moreover, NTF has a second order high-pass response, therefore, the out-of-band quantization noise rises with a 40dB-per-decade slope, which is typically described as a second–order noise shaping. In such a way, the  $\Delta\Sigma$  manages to achieve a high resolution in a narrow frequency band, while maintaining a high-sampling frequency which helps to ease the anti-aliasing filter design.

Higher-order  $\Delta\Sigma$  ADC enjoys the benefit of higher order noise shaping, therefore, to achieve the same resolution, lower OSR is required, which helps to reduce the power consumption of the system and simplify the quantizer and feedback DAC design. However, higher-order  $\Delta\Sigma$  ADCs demand higher-order loop filter, which contains more poles and zeroes. Just as every other feedback system, it is much harder to maintain the overall stability when the system becomes more complicated. ADC designers often have to trade off favorably between the orders of the system with a reasonable OSR. In general, most of the commercial  $\Delta\Sigma$  ADC designs refrain to an order less than five, due to the stability and complexity reasons.

As mentioned above,  $\Delta\Sigma$  ADC's output spectrum contains not only the desired signal, but also a wide-frequency of the shaped noise. This suggests its output needs to be filtered and down-sampled before the digital signal processor can demodulate the desired signal efficiently. The digital decimation filter can be implemented in the digital domain without causing too much power consumption. Modern CMOS technology allows for a very power and area-efficient implementation of such digital design. Even better, digital decimation filter can scale with the process, which further reduces its impact on the overall power and area budget.

#### $2.2.2 \Delta\Sigma$ ADC in RF Receivers

As discussed earlier, an ADC that meets the SDR requirements needs to have a high resolution and fast sampling rate at the same time.  $\Delta\Sigma$  ADC offers a unique alternative, compared to other topologies to meet both of these two criteria, while maintaining a reasonable power and cost budget.  $\Delta\Sigma$  ADC is able to avoid the some of the fundamental trade-offs facing by the Nyquist rate ADC designs.

$\Delta\Sigma$  modulator design is promising for RF receiver design is mostly due to its two prominent features: oversampling and noise-shaping. Oversampling raises the Nyquist rate, and hence it eases on the anti-aliasing filter design. For a Nyquist rate ADC design, increasing the sampling-rate is really challenging, since this ADC needs maintain its noise floor over the widened bandwidth. To add to the matter, as the ADC can handle a wider range of input, it is susceptible for the out-of-band interferences, which could be a few times or order of magnitude bigger than the desired signal. Therefore, the required dynamic range and sampling speed requirement makes a Nyquist-ADC design highly impractical.

It is really important to realize that high resolution conversion is not necessary over the entire frequency range, but only for narrow frequency band of interest, where the desired signal resides. For frequencies other than that band of interest, the ADC only needs to tolerate a large input level such as that the large out-of-band blockers are not going to rail out the ADC. Given these two important observations,  $\Delta\Sigma$  ADC truly shines in the SDR application, as it can provide a high dynamic range only over a narrow frequency band, while maintaining a high sampling rate. The narrow-band high-resolution conversion ensures the conversion process of the  $\Delta\Sigma$  ADC is as efficient as possible. Compared to Nyquist-rate designs, where all the signals (both in-band and out-of-band) are still being converted in high resolution, large amount of the power is wasted in converting signals which has little use for demodulation process.  $\Delta\Sigma$  ADC data conversion process is much more energy efficient.

Aliasing is a major issue that plagues any type of the ADC design. However, for RF receiver design, an explicit anti-aliasing filter might not be necessary. First, RF components such as antenna SAW filters, TR switches and duplexers all have limited operational bandwidth.  $\Delta\Sigma$  ADC's sampling rate is often much higher than the narrow band of interest, then, the first aliasing Nyquist zone is quite faraway. Hence, the limited operational bandwidth of various RF components can serve as implicit filtering for aliasing contents. Even better, bondwire has limited operation bandwidth as well, which further helps to suppress the aliasing content. Moreover, as shall be discussed later in this work, other techniques can effectively alleviate the issue of aliasing in an ADC-based RF receiver design. Overall, the removal of an explicit analog anti-aliasing filter not only helps to maintain a better power and area budget of the overall design, but it also enables great flexibility of the design, as the signal bandwidth is no longer explicitly defined in the analog domain. The final signal selection can be pushed into the digital domain, in the

form of the application of digital filters. Combined with a programmable digital system such as FPGA, it allows a possibility of on-the-fly re-programming the digital filters to accommodate the change of signal bandwidths and applications. This feature is very amenable and appealing as a concept for reconfigurable RF receiver.

# 2.3 Digitally-Assisted Receiver Architecture

The beauty of the digitally-assisted Receiver is that a part of the filtering network is shifted into the digital domain. The analog/RF components can be reduced to its minimum to enhance the flexibility and better performance vs. power tradeoff for the overall system. To carry this idea to the extreme, it will very well be an ideal ADC that fits the idea of software-defined radio. Throughout the past decade, technology scaling has been marching into the sub-micrometer region, and it enables devices with sizes 100<sup>th</sup> of micrometers to come into production. At this point of time, realization of devices size even down to single digit nanometer is not that far at all. This improvement in the process shrinking not only makes the digital backend more capable and power efficient than any time before, but also allows many mixed signal blocks, such as ADC, to evolve at the same time. In particular, ADC design for wireless applications has experienced major change in the past decade. In most of the wireless applications, the once dominant Pipeline architecture has become obsolete. Its throne is now claimed by architectures such as  $\Delta\Sigma$  ADC and SAR ADC. SAR ADC architecture scales more naturally with the technology shrinking, while the  $\Delta\Sigma$  ADC draws great benefits from a more capable digital backend enabled by the latest technology improvement. In the literature, SAR ADCs and  $\Delta\Sigma$  ADCs have been reported efficiency that is ten times better than Pipeline ADCs. Because of the more powerful digital core as well as a more capable data convertor, the conventional way of partitioning between the analog/RF domain and digital domain is obsolete, and cannot provide the best performance vs. power tradeoff. In the recent decade, a great amount of research effort has been made in reshaping the boundary between the digital and analog/RF. Many analog/RF components, which used to be deemed as essential or critical for the applications, have been removed from the receiver chain successively. The overall result is a much simpler design with much better power efficiency.

## 2.3.1 Passive Mixer-first Receiver Design

The passive mixer-first receiver design centers on the idea of the passive mixer, which has been reported in 2000 [57][58]. For a fairly long time, active Gilbert mixers have been the mainstay for the integrated receiver system, because of their gain performance. However, they suffer from high flicker noise. Passive mixers, on the other hand, has higher conversion losses but outstanding flicker noise performance [119][120]. Several studies have addressed passive mixer design convers in great detail from the

perspective of noise, dc offset, second-order distortion and third-order distortion[120][121][122][123]. Over the years, it has become the mainstream design for modern commercial integrated receiver systems [59][60].

Also, it has been shown that by utilizing a multiple non-overlapping LO waveforms, the passive mixer designs can be further optimized [58][60][63][64][65]. Recent mixer-first receiver designs have demonstrated that the architecture can achieve excellent noise and linearity performance: reference [25] has shown a sample design with a record-high 25 dBm IIP3, while in [68] a mixer-first system with a 1.9 dB noise figure is reported with the aid of noise cancellation.

### 2.4 Wireless Standards

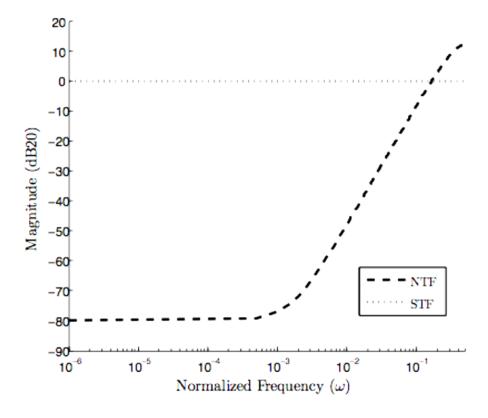

A survey of requirements of a few modern wireless standards is presented in this section in order to shed light on the basic requirements for a reconfigurable RF receiver. Some of the RF signal requirement for different standards can be simplified into a blocker mask and a sensitivity requirement. A short summary between blocker mask requirements from three existing wireless standards is shown in figure 2.6. The blocker mask gives a good understanding about the signal level the receiver needs to tolerate at different frequency offsets. Another requirement is based on the minimum SNR for successful demodulation as well as the sensitivity requirement of a particular wireless standard.

Fig. 2.6.a. Blocker masks for three different wireless standards

Fig. 2.6.b. Blocker masks for LTE with 20 MHz channel bandwidth

The three standards shown figure 2.6 have quite different range of requirements, which is why a reconfigurable RF receiver is so hard to implement. For instance, the GSM standard has the narrowest signal bandwidth of 200 KHz. However, it has some of the toughest blocker mask requirement among the three. In particular, a blocker which is 80 MHz away could be as high as +100 dB larger than the wanted signal. In absolute scale, it means the blocker can be 10<sup>5</sup> times larger than the desired signal. On the other hand, standards like WiMAX have much wider bandwidth to provide a higher throughput. Even though WiMAX mandates 20 MHz signal bandwidth, which is 100 times larger than GSM, its blocker mask requirement is much more relaxed compared to GSM. A reconfigurable RF receiver frontend will have to put up with different requirements demanded by the different standards.

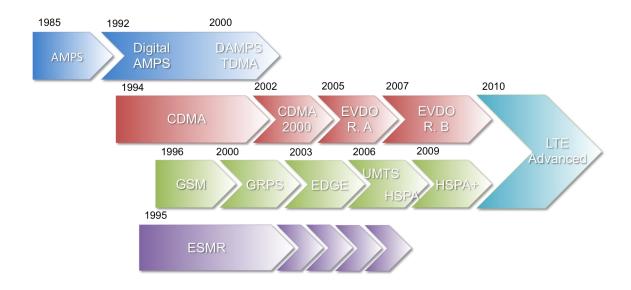

Ever since the introduction of AMPS in 1983 in Chicago, there are more than a dozen different wireless standards introduced in the past thirty years as shown in figure 2.7. With each of them presenting unique requirements on the radio system design, it is impossible and unnecessary to design a flexible radio front-end to address the requirements for every one of them. Instead, this work is only going to focus on to address the needs for LTE Advanced only, since most likely the future wireless standards would face the same challenges that associate with LTE Advanced today.

Fig. 2.7 Evolution of the wireless communication in the past thirty years.

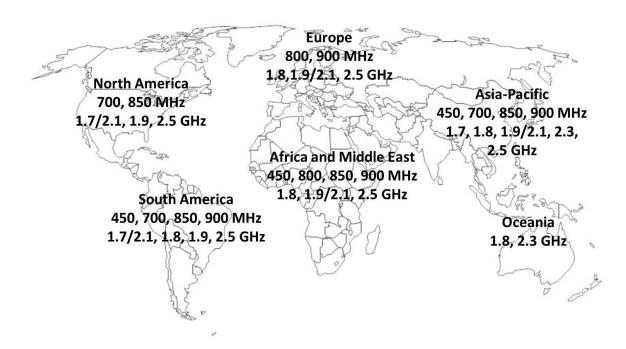

LTE Advanced presented two major challenges to RF receiver design. The first one is its fragmented spectrum. Due to the history of spectrum allocation and political reasons, the availability of spectrum in different countries and regions is fragmented, which has a profound impact on the deployment of LTE internationally. The availability of spectrum for 4G varies widely from country to country and by region with some bands only available in particular countries as shown in figure 2.8. For example, the 700 MHz band, which is popular band in the U.S., is only going to be adopted by a handful of operators outside the America. The 1900 MHz band, on the other hand, would have confined usage only within in the U.S. and Argentina, while the 1500 MHz band would only be limited in Japan.

The spectrum fragmentation is not an issue in the past, since most of the older standards are confined to one or limited bands across the world. For instance, GSM is operating in three bands globally: 900 MH, 1800 MHz (PCS) and 1900 MHz (DCS). Receiver designs that support LTE in different countries requires different hardware inside and outside of the chip, which makes it impossible to achieve an universal design for international LTE support.

Fig. 2.8 LTE spectrum allocation across the world.

Fig. 2.9 Supporting LTE together with other existing wireless standards

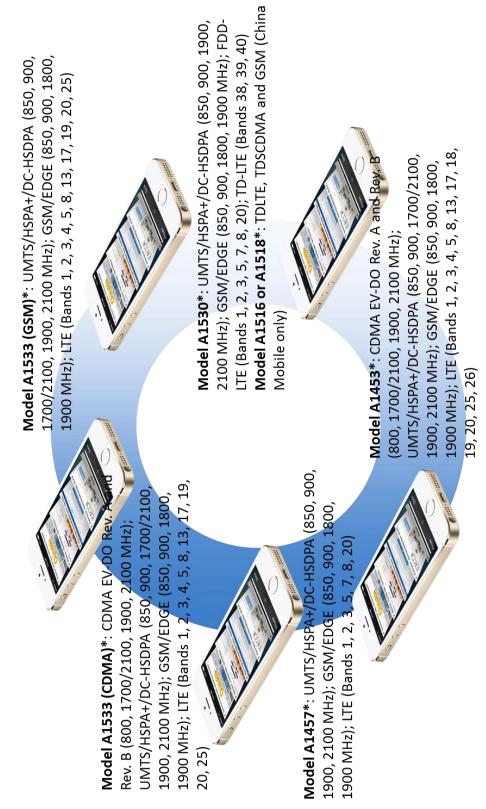

Fig. 2.10 Five different models of IPhone 5 for global support.

The problem gets even worse, when we consider the backward compatibility for legacy wireless standards. Figure 2.9 shows an example of what different wireless standards need to be supported for different part of the world. There are a total of over 40 different RF bands required. As the result, mobile device manufacturers are facing serious challenges in supporting LTE. The highly fragmented spectrum requirement makes it impossible for standardizing devices for a global market. Virtually all countries regulate their radio spectrum in a different way and large portions of the spectrum that could be aggregated for LTE are already in use for other devices or services. Therefore, given the technology limitation, one device for one dedicated region seems to be the cellphone manufactures best strategy so far. For example, the iPhone 5 has five different models to provide the support for different regions and different carriers as shown in figure 2.10. For the reason given above, there are two models dedicated to the U.S. market alone to provide coverage for AT&T and Verizon Wireless.

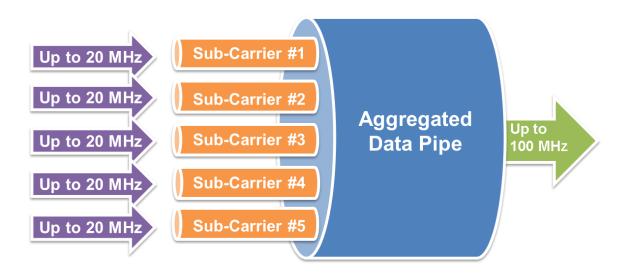

LTE Advanced provides additional improvement in user data rates through carrier aggregation (CA). LTE Advanced can aggregate up to five carriers (up to 100 MHz bandwidth) to a single user and increase capacity for different applications as illustrated in figure 2.11. As a first step, the current LTE Advanced (Cat 4) can support the aggregation of two 10 MHz carriers, which allows a peak 150 Mbps data rate.

Fig. 2.11 Five sub-carrier carrier aggregation to generate a higher bandwidth.

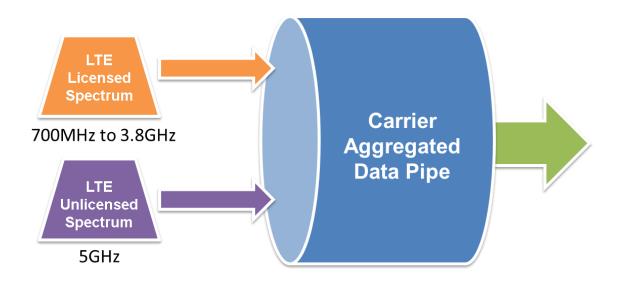

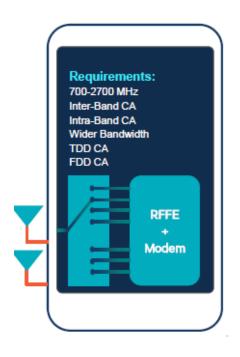

At this time, the 3GPP alliance is aiming on to provide up-to-5 carrier aggregation with up to 100 MHz total bandwidth support to LTE in the future. They also aim to open up an unlicensed spectrum at 5 GHz band for further user data rate improvement, as shown in figure 2.12. Figure 2.13 summarizes the requirement for the modern mobile devices posed by the LTE Advanced, and figure 2.14 lists some of the supported carrier aggregation bands by a modern commercial design.

Fig. 2.12 LTE carrier aggregation between the licensed and unlicensed bands.

Fig. 2.13 System requirement for a device supporting LTE CA.

Fig. 2.14 Samples of the supported LTE CA channels from a commercial design.

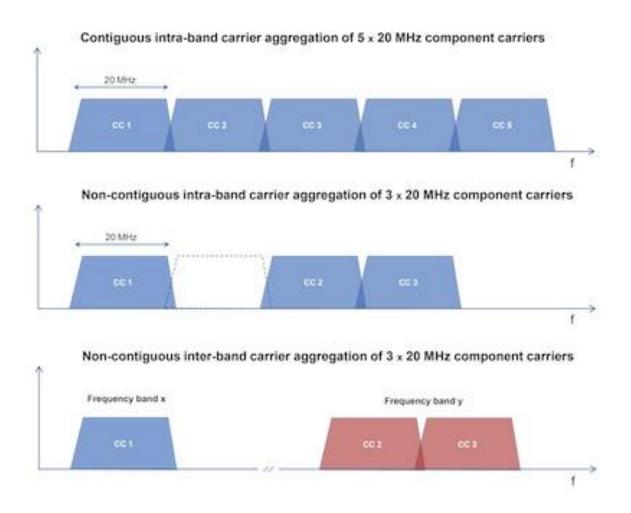

Each aggregated carrier is often referred to as a component carrier (CC). The CC can have bandwidth varies from 1.4, 3, 5, 10, 15 and 20 MHz. Up to five of component carriers can be combined, the maximum resulting bandwidth can be provided is therefore 100 MHz. Carrier aggregation can be used in both the cases of FDD and TDD. As demonstrated in figure 2.14, there are three ways to arrange aggregations. The most straightforward way is to use carriers right next to each other from the same operating frequency spectrum. It is called intra-band contiguous carrier aggregation. However, this might not always be possible since the adjacent carriers might not be the available carrier that can be reallocated. Therefore, LTE-Advanced also requires support for noncontiguous aggregations, which provides the system with wider degree of freedom in combing different component carriers under different operator allocation scenarios. The non-contiguous carrier aggregations can be broken down in two cases: the intra-band non-contiguous case and the inter-band non-contiguous case. The difference between the above two cases are that the allocated component carriers are from the same operating frequency spectrum or from two separate frequency bands as detailed in figure 2.15.

Fig. 2.15 Three different scenarios for carrier aggregations.

In earlier part in this section, we mentioned that there is another modern standard, 802.11.ac (or 5G Wi-Fi), based on a similar idea of the bandwidth reallocation scheme as the LTE Advanced. One example of channel bonding is shown in figure 2.16, where two 20 MHz channels are combined to form a 40 MHz channel to provide faster data throughput. Compared to the case of LTE Advanced, where each of the component carriers maintains its own spectrum mask, the channel bonding eliminates the original channels before combining and takes all the resulted spectrum to form a wider channel. From the spectrum perspective, channel bonding is more efficient, since it removes all physical frequency separation, such as guard bands between adjacent channels. However, it is not as flexible as the carrier aggregation in the LTE Advanced case, since it can only combine nearby channels, while LTE Advanced can even reallocate sub-carriers from different frequency bands for the same users. Also, 802.11.ac poses stringent requirement

on the physical hardware, since the channels can have different spectrum shape with various bandwidth, while LTE Advanced can work with the same physical layer since each component carrier doesn't change its spectrum identity with or without being allocated.

It should not be surprising that the future wireless standards would have to share many of the same design challenges such as LTE Advanced. The struggle between limited spectrum and the never-enough bandwidth demand will get worse as the remaining commercial spectrums become even more scarce over time. A reconfigurable receiver, therefore, would be highly preferable in the future. A reconfigurable frontend not only needs to be able to hop around different bands to support different standards, but more importantly, its flexibility should also be able to support the same standard such as LTE over its fragmented spectrums. In addition, compared to the conventional definition of the reconfigurable frontend, the new generation of SDR receiver also has to be able to reconfigure within the signal bandwidth to provide support for carrier aggregation or channel bonding.

This work is to explore novel architectures for the new generation of SDR receiver designs, which can be reconfigurable inside and outside of the signal bandwidth to address the needs and challenges presented by the future wireless standards.

Fig. 2.16 Channel bonding for two 20 MHz channels.

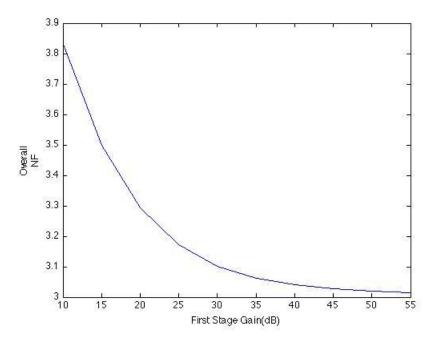

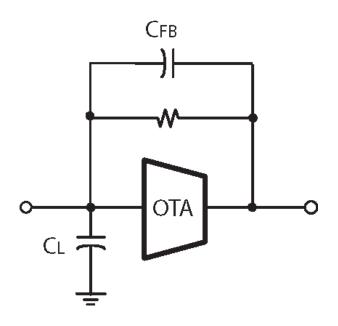

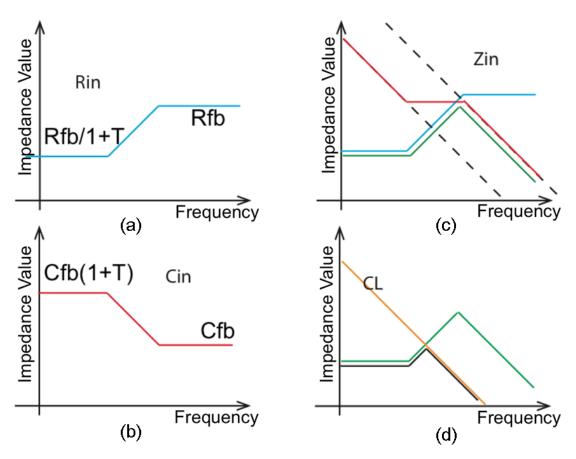

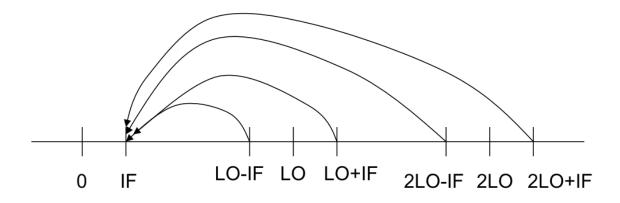

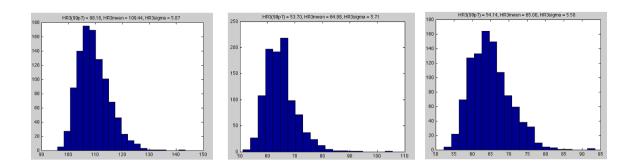

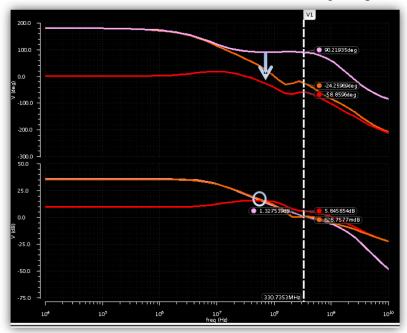

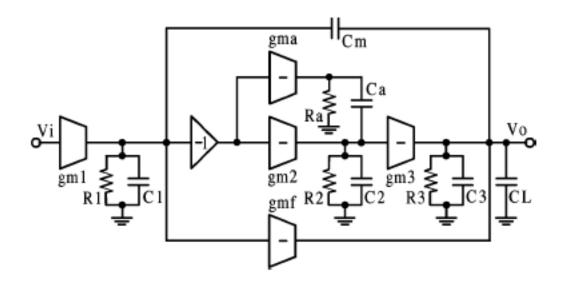

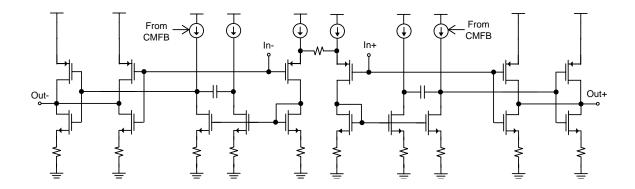

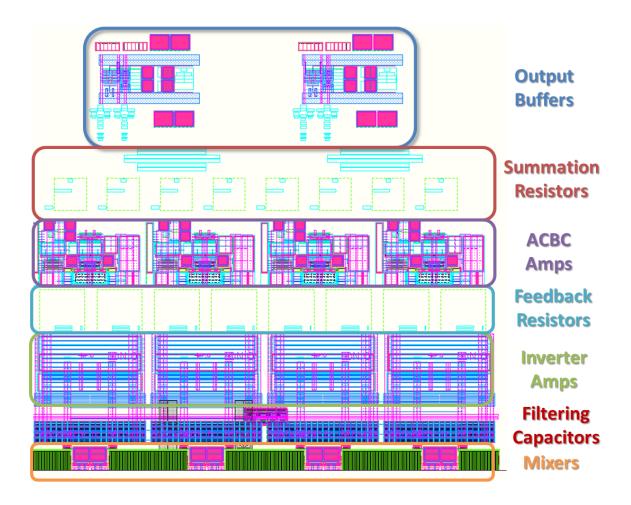

# 2.5 Performance Comparison of Existing Designs