# **Mixed Precision Vector Processors**

Albert Ou Krste Asanović, Ed. Vladimir Stojanovic, Ed.

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2015-265 http://www.eecs.berkeley.edu/Pubs/TechRpts/2015/EECS-2015-265.html

December 19, 2015

Copyright © 2015, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

Acknowledgement

Research is partially funded by DARPA Award Number HR0011-12-2-0016, the Center for Future Architectures Research, a member of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA, and ASPIRE Lab industrial sponsors and affiliates Intel, Google, Nokia, NVIDIA, Oracle, and Samsung. Any opinions, findings, conclusions, or recommendations in this paper are solely those of the authors and do not necessarily reflect the position or the policy of the sponsors.

### **Mixed-Precision Vector Processors**

by

Albert Ji-Hung Ou

A thesis submitted in partial satisfaction of the

requirements for the degree of

Master of Science

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Krste Asanović, Chair Associate Professor Vladimir Stojanović

Fall 2015

### Mixed-Precision Vector Processors

Copyright 2015 by Albert Ji-Hung Ou

# Contents

| C        | ntents                                                | ii           |  |  |  |  |  |

|----------|-------------------------------------------------------|--------------|--|--|--|--|--|

| Li       | t of Figures                                          | iv           |  |  |  |  |  |

| Li       | t of Tables                                           | $\mathbf{v}$ |  |  |  |  |  |

| 1        | Introduction                                          | 2            |  |  |  |  |  |

|          | 1.1 Justification for Mixed Precision                 | 3            |  |  |  |  |  |

|          | 1.2 Justification for Vector Processors               | 4            |  |  |  |  |  |

|          | 1.3 Thesis Organization                               | 5            |  |  |  |  |  |

|          | 1.4 Project History                                   | 6            |  |  |  |  |  |

| <b>2</b> | Related Work                                          | 8            |  |  |  |  |  |

| 3        | Comparison of ISA Approaches                          | 10           |  |  |  |  |  |

|          | 3.1 Subword SIMD                                      | 10           |  |  |  |  |  |

|          | 3.2 Vectors                                           | 13           |  |  |  |  |  |

|          | 3.3 Reduced Precision                                 | 14           |  |  |  |  |  |

|          | 3.4 Mixed Precision                                   | 15           |  |  |  |  |  |

| 4        | Baseline Vector Architecture                          |              |  |  |  |  |  |

|          | 4.1 Programming Model                                 | 17           |  |  |  |  |  |

|          | 4.2 System Architecture                               | 19           |  |  |  |  |  |

|          | 4.3 Microarchitecture                                 | 20           |  |  |  |  |  |

| <b>5</b> | Mixed-Precision Vector Architecture 29                |              |  |  |  |  |  |

|          | 5.1 Programming Model                                 | 29           |  |  |  |  |  |

|          | 5.2 Microarchitecture                                 | 34           |  |  |  |  |  |

| 6        | Evaluation Framework 3                                |              |  |  |  |  |  |

|          | 6.1 Microbenchmarks                                   | 40           |  |  |  |  |  |

|          | 6.2 OpenCL Compiler                                   | 41           |  |  |  |  |  |

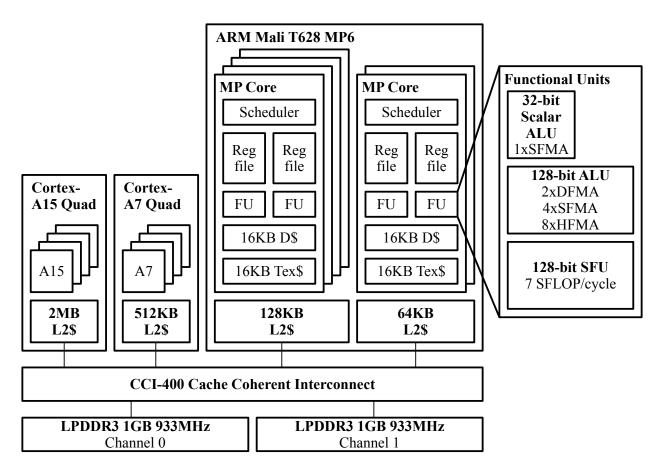

|          | 6.3 Samsung Exynos 5422 and the ARM Mali-T628 MP6 GPU | 42           |  |  |  |  |  |

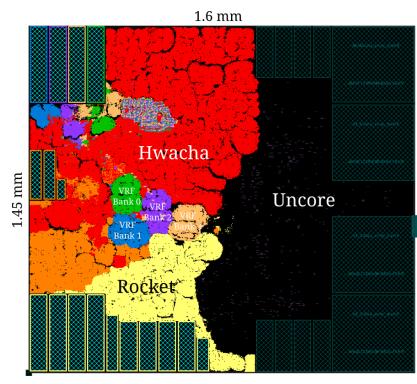

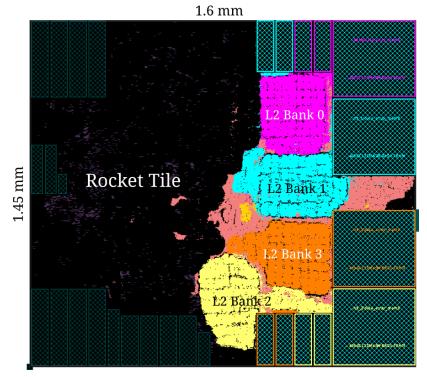

|         | 6.4 RTL Development and VLSI Flow               | 44              |

|---------|-------------------------------------------------|-----------------|

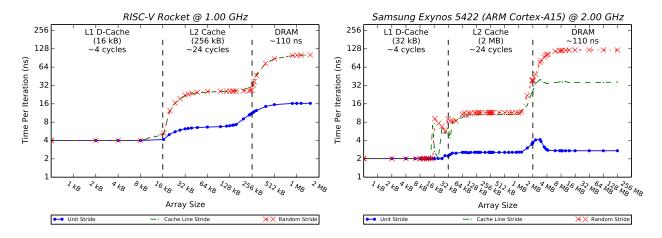

| 7       | <ul> <li>7.1 Memory System Validation</li></ul> | 48              |

|         | 7.3 Performance Comparison                      | 54              |

| 8<br>Bi | Conclusion<br>ibliography                       | $\frac{56}{57}$ |

iii

# List of Figures

| 3.1 | Double-precision SIMD addition                                | 1 |

|-----|---------------------------------------------------------------|---|

| 3.2 | Evolution of SIMD extensions in the x86 ISA 1                 | 2 |

| 3.3 | Double-precision vector addition                              | 3 |

| 3.4 | Single-precision addition                                     | 4 |

| 3.5 | Widening FMA                                                  | 5 |

| 4.1 | Conditional SAXPY kernels written in C                        | 8 |

| 4.2 | Conditional SAXPY kernels mapped to pseudo-assembly           | 8 |

| 4.3 | System architecture provided by the Rocket Chip SoC generator | 9 |

| 4.4 | Block diagram of Hwacha                                       | 1 |

| 4.5 | Block diagram of the Vector Execution Unit                    | 3 |

| 4.6 | Systolic bank execution                                       | 5 |

| 4.7 | Block diagram of the Vector Memory Unit                       | 6 |

| 4.8 | Mapping of elements across a four-lane machine                | 8 |

| 4.9 | Example of redundant memory requests by adjacent lanes        | 8 |

| 5.1 | Simplified logical view of an 8-entry VRF                     | 0 |

| 5.2 | Conditional SAXPY kernels updated for HOV                     | 0 |

| 5.3 | Actual striped mapping to a 2-bank physical VRF               | 5 |

| 5.4 | Hypothetical naive mapping to a 2-bank physical VRF           | 5 |

| 6.1 | Hwacha evaluation framework                                   | 0 |

| 6.2 | Samsung Exynos 5422 block diagram                             | 3 |

| 7.1 | ccbench "caches" memory system benchmark                      | 7 |

| 7.2 | Layout of the single-lane Hwacha design with HOV              | 9 |

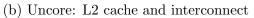

| 7.3 | Area distribution                                             | 0 |

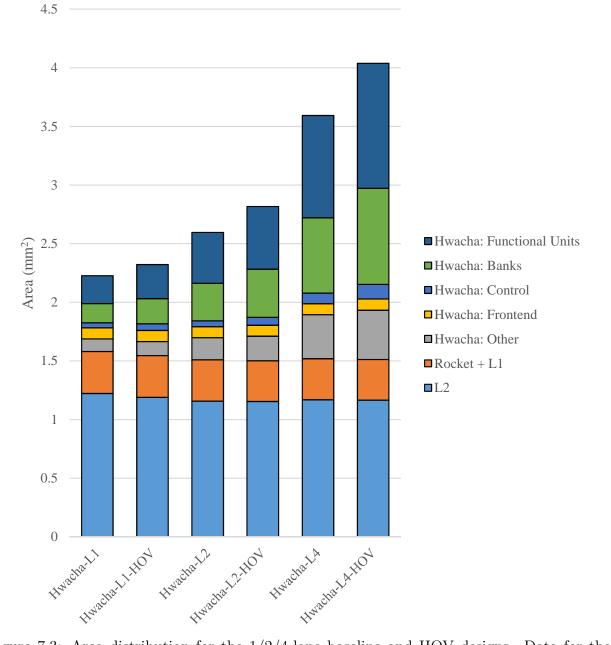

| 7.4 | Preliminary performance results                               | 3 |

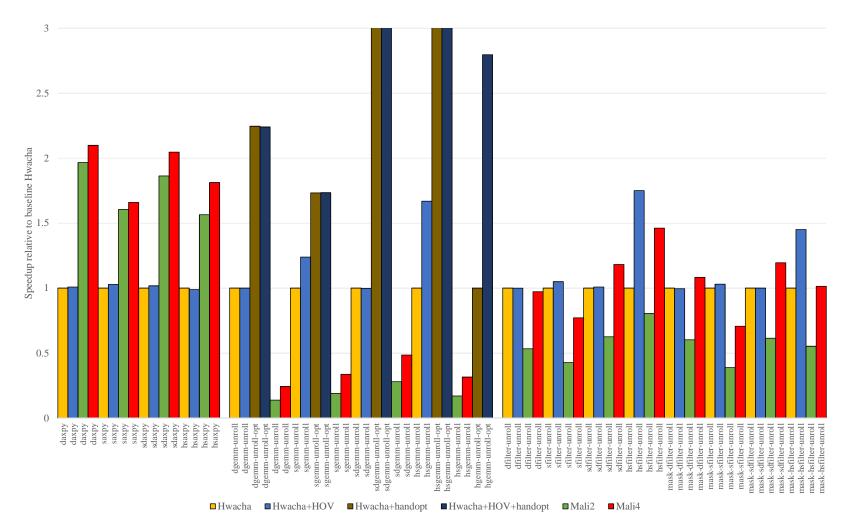

| 7.5 | Preliminary energy results                                    | 5 |

# List of Tables

| 6.1 | Listing of all microbenchmarks            | 41 |

|-----|-------------------------------------------|----|

| 6.2 | Used Rocket Chip SoC generator parameters | 44 |

| 7.1 | VLSI quality of results                   | 48 |

#### Abstract

Mixed-Precision Vector Processors

by

Albert Ji-Hung Ou Master of Science in Computer Science University of California, Berkeley Professor Krste Asanović, Chair

Mixed-precision computation presents opportunities for programmable accelerators to improve performance and energy efficiency while retaining application flexibility. Building on the Hwacha decoupled vector-fetch accelerator, we introduce high-occupancy vector lanes (HOV), a set of mixed-precision hardware optimizations which support dynamic configuration of multiple architectural register widths and high-throughput operations on packed data. We discuss the implications of HOV for the programming model and describe our microarchitectural approach to maximizing register file utilization and datapath parallelism. Using complete VLSI implementations of HOV in a commercial 28 nm process technology, featuring a cache-coherent memory hierarchy with L2 caches and simulated LPDDR3 DRAM modules, we quantify the impact of our HOV enhancements on area, performance, and energy consumption compared to the baseline design, a decoupled vector architecture without mixed-precision support. We observe as much as a 64.3% performance gain and a 61.6%energy reduction over the baseline vector machine on half-precision dense matrix multiplication. We then validate the HOV design against the ARM Mali-T628 MP6 GPU by running a suite of microbenchmarks compiled from the same OpenCL source code using our custom HOV-enabled compiler and the ARM stock compiler.

# Chapter 1

# Introduction

The prominent breakdown of Dennard scaling, amid ongoing difficulties with interconnect scaling, has driven VLSI design into a new regime in which severe power constraints and communication costs prevail. Technology trends have culminated in an evolutionary plateau for conventional superscalar processors, as overly aggressive pipelining, speculation, and out-of-order execution become counterproductive beyond a certain degree of complexity. These challenges have thus prompted a retreat away from maximal sequential performance, a pursuit which heretofore has characterized mainstream computer architecture since its infancy, and has initiated a transition towards *throughput-oriented computing* that instead emphasizes sustained performance per unit energy. These throughput-oriented architectures derive performance from parallelism and efficiency from locality [1], [2].

Fully harnessing the abundant parallelism and locality in emerging applications generally entails some form of hardware specialization, a familiar concept made progressively feasible by the vast transistor budgets afforded by modern CMOS processes. How to balance efficiency with flexibility—and ideally elevate both—is the eternal research question. Mixed-precision optimizations may serve as one answer.

Compared to fixed-function hardware, programmable processors contend with inefficiencies from at least two major sources: overhead of instruction delivery and wasteful power consumption by over-provisioned datapaths. In this work, we propose a dual strategy of seamless mixed-precision computation on a vector architecture to address both aspects.

# 1.1 Justification for Mixed Precision

Relying on prior knowledge within a restricted scope of applications, fixed-function accelerators notably exploit heterogeneous and minimal word sizes in their custom datapaths. Fundamentally, less energy dissipation and higher performance both ensue with fewer bits communicated and computed. In contrast, commodity processors must support a generic assortment of conventional number representations to fulfill a general-purpose role. Thus, the datapath width is often conservatively fixed to the maximum precision and widest dynamic range imposed by any plausible application.

Recently, growing attention is being paid to the impact of limited numerical precision across a variety of application domains relevant to high-throughput processing. It is becoming increasingly common practice in high-performance computing to forgo double-precision floating-point in favor of single precision, owing to the two-fold disparity in peak FLOPS that GPGPUs and SIMD processors customarily manifest. There is cause to be optimistic about the general-purpose viability of reduced-precision computation. In the context of deep learning, for example, the presence of statistical approximation and estimation errors renders high precision largely unnecessary [3]. Moreover, additional noise during training can in fact enhance the performance of a neural network. Workloads that exhibit a natural error resilience at the algorithmic level therefore seem to offer a compelling basis for hardware optimizations capitalizing on precision reduction, while the diversity of applications clearly motivates a programmable solution.

One can imagine a more versatile accelerator capable of programmatically switching its datapath from one reduced-precision mode to another at a time. However, rarely is one global precision optimal or even sufficient throughout all phases of computation. In areas that historically have been the exclusive realm of double-precision floating-point arithmetic, such as scientific computing, there is potential for reformulating existing problems by means of *mixed-precision methods* [4]. These schemes combine the use of different precisions to minimize cost, completing the bulk of the work in lower precision, while also preserving overall accuracy. Iterative refinement techniques, widely applied to linear systems, improve the quality of an approximate solution via gradual updates calculated in extra precision. Similarly, instability in an algorithm may be overcome by selectively resorting to higher precision during more sensitive steps.

The design space of mixed-precision hardware extends from the simple coexistence of variable-width information, such as integer data versus memory addresses, to widening arithmetic operations, such as a *fused multiply-add* (FMA) that sums the product of two *n*-bit values and a 2n-bit value without intermediate rounding.

## **1.2** Justification for Vector Processors

Vector architectures are an exceptional match for the data-level parallelism (DLP) prevalent in throughput computing applications. Compared to instruction-level parallelism (ILP) and thread-level parallelism (TLP), DLP is the most rigid form of machine parallelism but is therefore the most efficient with respect to control overhead.

Each vector instruction concisely expresses an entire set of homogeneous and independent elementary operations, thereby amortizing the cost of instruction fetch, decode, and scheduling. Fewer instructions that encapsulate more work also relaxes bandwidth demands on instruction supply. Whereas managing all possible dependencies among the same number of scalar operations incurs quadratic complexity, the explicit data parallelism reinforces constraints which dramatically simplify the control logic.

From an implementation perspective, the inherent regularity of vector operations promotes extensive modularity and scalability to meet varying performance/power targets. A massively parallel machine may be constructed from a multiplicity of identical and largely self-contained *lanes*, each housing a portion of the vector register file and functional units but together sharing a common scalar and control unit.

Vector data accesses adhere to highly structured and predictable communication patterns. This permits microarchitectural optimizations such as register file banking to reduce port count. Long vectors expose substantial memory-level parallelism to more easily saturate memory bandwidth. In the common case, constant-stride memory operations are particularly conducive to access/execute decoupling and prefetching techniques for hiding latency, since the address stream can be generated separately from other computations.

Vector architectures are readily adaptable to reduced-precision computation. Due to the

intrinsic data independence, a wide datapath can be naturally partitioned to operate on several narrower elements concurrently. For compute-bound workloads, this *subword parallelism* offers an area-efficient mechanism for multiplying arithmetic throughput by an integer factor. The marginal implementation cost principally involves the replication of functional units—crucially, the existing register file ports and interconnection fabric for operand traffic remain unaltered yet enjoy improved utilization.

Reduced precision alleviates memory-bound workloads as well. In general, it is fairly straightforward to increase functional unit bandwidth by instantiating extra ALUs, for their individual area penalties are exceedingly modest as a result of advances in semiconductor device technology, but system-wide memory bandwidth cannot be increased with the same ease. With global communication as a limiting factor, a more compact representation of data realizes more effective use of available bandwidth.

Precision truncation can be regarded as a lossy compression scheme that makes larger problem sizes more economical across all levels of the memory hierarchy. Denser storage of elements directly translates into longer vectors with the same register file capacity. This enables greater register blocking, aiding in-register operand reuse and correspondingly lessening memory pressure. The expanded buffering provided by the vector register file further assists with decoupled execution to better tolerate memory latency. Lastly, a greater concentration of useful data is resident in a cache—if the working set now manages to fit within the L1 or L2 caches where it formerly could not, then a superlinear speedup becomes attainable.

### **1.3** Thesis Organization

Chapter 2 reviews existing architectural techniques for mixed-precision computation and some of their disadvantages. Chapter 3 provides a deeper analysis of subword SIMD and vector architectures, discussing why vector processing serves as a more refined foundation for a mixed-precision programming model. Chapter 4 describes the baseline vector accelerator design, and Chapter 5 elaborates on *high-occupancy vectors* (HOV), the architectural and microarchitectural augmentations to support efficient mixed-precision vector computation. Chapter 6 details the evaluation framework, including RTL development methodology with Chisel and the physical design flow in a commercial 28 nm process technology. Chapter 7 compares complete VLSI implementations of the HOV and baseline designs, first to each other and then against an ARM Mali-T628 MP6 GPU, using a suite of compiled OpenCL and manually optimized assembly microbenchmarks.

## **1.4 Project History**

### Collaboration

This thesis is the result of a collaborative group project. Other people have made direct contributions to the ideas and results included here. The Hwacha vector-fetch accelerator was developed by Yunsup Lee, myself, Colin Schmidt, Sagar Karandikar, Krste Asanović, and others from 2011 through 2015. As the lead architect of Hwacha, Yunsup Lee directed the development and evaluation of the architecture, microarchitecture, RTL, compiler, verification framework, microbenchmarks, and application kernels. I was primarily responsible for the RTL implementation of the Vector Memory Unit and the mixed-precision extensions described in this thesis. Colin Schmidt took the lead on the definition of the Hwacha ISA, RTL implementation of the scalar unit, C++ functional ISA simulator, vector torture test generator, Hwacha extensions to the GNU toolchain port, and the OpenCL compiler and benchmark suite. Sagar Karandikar took the lead on the bar-crawl tool for design-space exploration, VLSI floorplanning, RTL implementation of the Vector Runahead Unit, ARM Mali-T628 MP6 GPU evaluation, and the assembly microbenchmark suite. Palmer Dabbelt took the lead on the physical design flow and post-PAR gate-level simulation in the 28 nm process technology used in this study. Henry Cook took the lead on the RTL implementation of the uncore components, including the L2 cache and the TileLink cache coherence protocol. Howard Mao took the lead on the dual LPDDR3 memory channel support in the testbench and provided critical fixes for the outer memory system. Andrew Waterman took the lead on the definition of the RISC-V ISA, the RISC-V GNU toolchain port, and the RTL implementation of the Rocket core. Andrew also helped to define the Hwacha ISA. John Hauser took the lead on the development of the hardware floating-point units. Many others contributed to the surrounding infrastructure, such as the Rocket Chip SoC generator. Huy Vo, Stephen Twigg, and Quan Nguyen contributed to earlier versions of Hwacha. Finally, Krste Asanović was integral in all aspects of the project.

### **Previous Publications**

This thesis is a direct descendant of the publication "MVP: A Case for Mixed-Precision Vector Processors" [5], presented at the PRISM-2 workshop at ISCA 2014. That paper itself culminated from two graduate-level course projects: CS250 (Fall 2013) and CS252 (Spring 2014), both times undertaken with co-conspirator Quan Nguyen. Whereas all previous work involved retrofitting two earlier incarnations of Hwacha, retroactively designated V2 and V3, this thesis builds on the V4 redesign. V4 represents a complete overhaul of both the ISA and RTL, and unlike its predecessors, it was architected from the very beginning with mixed-precision support as an explicit design objective. The result is an improved mixed-precision implementation with respect to functionality, performance, and ease of integration.

The text has been extensively rewritten to cover additional design rationale, deeper explanation of mechanisms, and other details beyond the scope of the MVP paper. Such material include: in Chapter 3, discussion of vector length control (or lack thereof) and its implications on programming abstractions and, in Chapter 5, sections on portability considerations, polymorphic instructions, and updated microarchitecture.

In addition, this thesis was authored concurrently with a set of UCB technical reports, resulting in some shared content. Chapter 4 appear as expanded passages in the "Hwacha Vector-Fetch Architecture Manual" [6] and the "Hwacha Microarchitecture Manual" [7]. Chapters 6 and 7 are adapted from "Hwacha Preliminary Evaluation Results" [8].

### Funding

Research is partially funded by DARPA Award Number HR0011-12-2-0016, the Center for Future Architectures Research, a member of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA, and ASPIRE Lab industrial sponsors and affiliates Intel, Google, Nokia, NVIDIA, Oracle, and Samsung. Any opinions, findings, conclusions, or recommendations in this paper are solely those of the authors and do not necessarily reflect the position or the policy of the sponsors.

# Chapter 2

# **Related Work**

Subdividing a wide datapath to perform multiple reduced-precision operations in parallel is a classic technique employed by early vector supercomputers, such as the CDC STAR-100 [9]. Asanović [10] and Kozyrakis [11] similarly describe how a vector machine may be viewed as an array of "virtual processors" whose widths are set collectively through a virtual processor width (VPW) control register. However, the element size of an individual vector cannot be configured independently, complicating the intermixture of different types in the same register file: Either VPW must be initialized for the widest datatype in a given block of code, possibly wasting space, or must be appropriately manipulated before each register access, enlarging the instruction footprint.

A related approach is the *subword single-instruction multiple-data* (SIMD) architectural pattern whose earliest instance was perhaps the Lincoln TX-2, which featured separate instructions for treating a full 36-bit machine as four 9-bit parallel machines, among other variations [12]. This style of design has widely endured in multimedia accelerators such as the IBM Cell Broadband Engine [13], and it has witnessed tremendous popular adoption by contemporary general-purpose instruction sets through various forms of packed SIMD extensions, e.g., x86 AVX [14] and ARM NEON [15]. Because vector and subword SIMD architectures are so frequently conflated, chapter 3 aims to elucidate the salient differences between the two—in particular, how subword SIMD's inferior programming abstractions inconvenience a mixed-precision environment.

In what may be considered an inversion of subword packing, an architecture might store

datatypes larger than its nominal bit width by splitting them across multiple adjacent registers. Graphics processing units (GPUs), for example, traditionally possess 32-bit registers; double-precision values occupy aligned register pairs referenced via even-numbered specifiers. This arrangement, while adequate for limited variable-precision support, essentially halves the architectural register set available to an application.

Newer generations of mobile GPUs have acquired native support for half-precision floatingpoint arithmetic (FP16), despite the IEEE 754-2008 standard intending it only as a storage format. It is well known that graphics workloads do not always require the highest fidelity due to limitations in human perception. The NVIDIA Tegra X1, based on the Maxwell architecture, executes FP16 FMAs at "double-rate" throughput, essentially two-wide SIMD operation from the normal FP32 perspective [16]. This development is by no means unique the ARM Midgard, Imagination PowerVR Rogue, and AMD Graphics Core Next Generation 3 (GCN3) families all incorporate FP16 in their rendering pipelines, with implementations sharing varying degrees of resources with the FP32 units.

Classic fixed-point digital signal processors (DSPs) are distinguished by special-purpose features to curtail overflow and rounding errors. These include multiplier-accumulator (MAC) units supporting widening arithmetic, dedicated extended-precision accumulator registers, and supplementary guard bits for saturation. The C54x generation of the famous Texas Instruments TMS320 family serves as a good example with its  $17 \times 17$  multiplier and 40-bit accumulators [17]. However, DSPs characteristically suffer from irregular architectures as a result of ad-hoc evolution, which render them a challenging compiler target and hinder their suitability for a more general-purpose mixed-precision function.

# Chapter 3

# **Comparison of ISA Approaches**

Vectors and subword SIMD are two approaches to instruction set architecture (ISA) design that, to a casual observer, appear outwardly alike: Both leverage data-level parallelism by operating on one-dimensional arrays of quantities and admit microarchitectural optimizations based on subword parallelism. However, a deeper examination reveals significant differences in the ways that mixed-precision computation can be mapped to each architecture. We argue that the advantages of true vector processing revolve around a key innovation in abstraction: flexible hardware vector length control.

## 3.1 Subword SIMD

The term *subword SIMD*, also known as "*short-vector*" *extensions* in the context of a scalar ISA, broadly describes the practice of explicitly packing contiguous subwords of equal size within a single *architectural* register. These are acted upon in parallel by special instructions provided per subword data type.

### **Fixed-width Property**

*Opcodes designate a fixed "vector" length.* In other words, the SIMD width is exposed as part of the ISA. This is the most distinguishing feature of subword SIMD and also its most decisive drawback, as the subsequent discussion will prove.

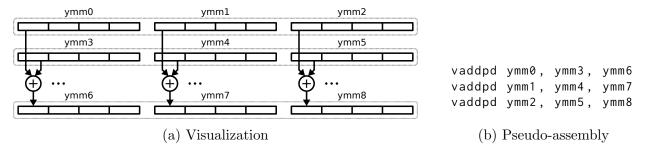

Figure 3.1: Double-precision SIMD addition

Figure 3.1a depicts how four 64-bit subwords may be packed into a single 256-bit SIMD register. Each register may alternatively hold 8 32-bit, 16 16-bit, or 32 8-bit values.

### Short-vector Property

SIMD widths tend to be relatively short. Modern SIMD extensions originated as an ad-hoc retrofit of scalar microarchitectures for a multimedia focus. The reuse of existing scalar register files presented what was then the path of least resistance towards subword parallelism, and it offers some historical basis for the habit of embedding the SIMD width in the ISA as well as for the short length of SIMD "vectors".

Nowadays, a separate register file is normally dedicated to the SIMD unit, decoupling it from the scalar width. Nevertheless, conventional SIMD units remain tightly integrated with the host scalar pipeline. Implementations rely nearly exclusively on *spatial execution*, forcing use of superscalar issue mechanisms to saturate functional units and hide long latencies. Control complexity and power consumption are both adversely impacted, especially if it involves out-of-order scheduling and register renaming.

Moreover, this imposes a practical upper bound on SIMD width—now typically either 128 or 256 bits, fairly modest in relation to the degree of parallelism commonly found in DLP-intensive workloads, which may comprise as much as hundreds of parallel operations. In combination with the inflexible nature of SIMD registers, utilizing the entire register file capacity often entails splitting a longer *application vector* across multiple architectural registers. Doing so inevitably requires more instructions. Figure 3.1b demonstrates such a situation where vectors of twelve elements must be subdivided among three SIMD registers each, resulting in three separate (though independent) vaddpd instructions. These effects all counteract the efficiency gains from DLP.

### **Non-Portability**

SIMD extensions contribute directly to unrestrained instruction set growth. As technology advances, the desire to scale performance across processor generations, along with commercial pressure, begets a natural tendency towards successively wider SIMD implementations. Each transition to a new width involves introducing a complete set of new instructions. The x86 architecture's own cluttered progression from MMX to AVX-512, summarized in Figure 3.2, perfectly illustrates such a trend.

The proliferation of new instructions leads to rapid depletion of opcode encoding space, despite instructions being largely redundant except to distinguish SIMD width. As an example, four versions of packed double-precision floating-point add operations exist in x86: addpd from SSE2 (with opcode 66 ØF 58 /r) and vaddpd from AVX (with prefixes VEX.128, VEX.256, and EVEX.512) [18]. AVX instructions have therefore become as long as 11 bytes.

Worse, applications targeting a particular SIMD width are inherently not portable. Legacy applications cannot automatically benefit from the increased SIMD widths. Code must undergo explicit migration: recompilation at the very least to include the new instructions, but more often a tedious rewrite when intrinsics are used instead of auto-vectorization. Conversely, code compiled for wider SIMD registers fail to execute on older machines with narrower ones. Such incompatibilities necessitate dynamic dispatch to different versions of code at runtime.

$$\stackrel{64\,\text{bit}}{\text{MMX}} \rightarrow \overbrace{\text{SSE} / \text{SSE2} / \text{SSE3} / \text{SSE3} / \text{SSE4}}^{128\,\text{bit}} \rightarrow \overbrace{\text{AVX} / \text{AVX2}}^{256\,\text{bit}} \rightarrow \overbrace{\text{AVX-512}}^{512\,\text{bit}} \rightarrow \stackrel{1024\,\text{bit}}{\text{AVX-512}} \rightarrow ?$$

## 3.2 Vectors

The deficiencies of subword SIMD are not fundamental to data-parallel architectures, rather being artifacts of poor design. In fact, a solution has already existed decades before commodity microprocessors first adopted SIMD extensions, in traditional vector machines descended from the Cray archetype [19].

Vector architectures provide longer, genuine vectors counted in terms of elements instead of bits. The hardware vector length generally ranges from 64 to thousands of elements, an aspect of their supercomputer heritage. Unlike the vast majority of subword SIMD implementations, vector machines incorporate temporal execution to process long vectors over multiple cycles, supplemented by chaining (the vector equivalent of register bypassing) to overlap dependent operations.

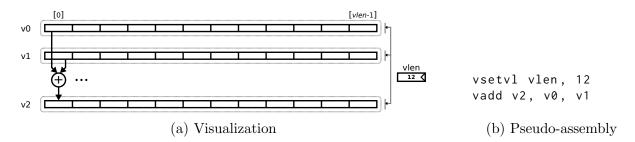

The hardware vector length is dynamically adjustable. A critical architectural feature is the vector length register (VLR), which indicates the number of elements to be processed per vector instruction, up to the maximum hardware vector length (HVL). Software manipulates the VLR by requesting a certain application vector length (AVL) with the vsetvl instruction; hardware responds with the lesser of the AVL and HVL. In Figure 3.3, for example, the VLR is set to 12. Note that only three architectural vector registers are needed here to represent the operands and the result, unlike the SIMD case, producing code that is expressively minimal.

This method of controlling the vector length enables greater scalability while preserving forward and backward compatibility. The VLR informs the program at runtime how to stripmine application vectors of arbitrary length. Essentially, it confers a level of indirection such that software remains oblivious to the HVL: The same code executes correctly and with maximal efficiency on implementations of any HVL. Most importantly, this portability

Figure 3.3: Double-precision vector addition

is achieved without any additional developer effort or ISA changes. (In practice, the ISA may specify a minimum HVL, e.g. 4, to elide stripmining overheads for short vectors.)

## 3.3 Reduced Precision

Now we consider how well the vector and subword SIMD models each accommodate smaller data types, while maintaining the invariant of identical input and output precisions. Our analysis builds upon the previous examples by substituting double precision with single.

With a fixed bit-width, SIMD registers contain a variable number of elements depending on the precision. This burdens the software with a potential fringe case when the application vector length is not a clean multiple of the SIMD width, resulting in partially utilized registers for the tail of the vector. A reduction in precision raises the likelihood of such an occurrence for a given SIMD width.

Simple cases akin to Figure 3.4a might be tolerated by padding the vectors in memory, but others require the insertion of extra fringe code. A compiler generally has two options: either predicate the trailing SIMD instructions based on the element indices or, in the absence of full support for conditional execution, resort to a scalar loop for the remainder.

Conversely, the reduced-precision vector example shown in Figure 3.4b does not deviate conceptually from its predecessor, Figure 3.3. Note that the VLR is agnostic to the precision of the elements and entirely averts all fringe cases for non- $2^n$  problem sizes. The programming model therefore scales more gracefully.

Figure 3.4: Single-precision addition

## 3.4 Mixed Precision

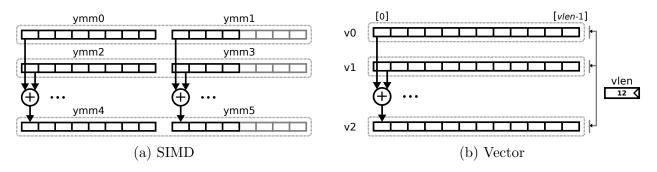

Next, we proceed to the generalized case in which the sources and destinations of an operation may differ in precision. Our analysis concentrates on a hypothetical FMA operation whose output precision is exactly twice that of the input precision, but the same observations also apply if that ratio were reversed.

Figure 3.5a portrays how mixed-precision computation can be quite intricate to convey with subword SIMD. The main difficulty lies in the unequal element counts of the source and destination registers. Consequently, the 8-wide FMA must be decomposed into two separate operations, each reading from either the upper or lower segments of the two sources and then writing to a different destination. Yet SIMD extensions typically provide only instructions that work on the lower end of registers, so extra shuffling to rearrange the operands must precede the upper operation. In the x86 ISA, for example, this might involve a VPERM2F128 instruction ("permute float-point values") to exchange the upper/lower 128 bits of a 256-bit AVX register [18].

A simpler alternative is to store 4 lower-precision operands in a register pair, rather than the maximum of 8 in one, to match the quantity in the destination registers—basically, to restrict the number of elements per register according to the highest precision in order to equalize their lengths. Although tempting, it is still far from ideal, as the inefficient register usage would limit the extent of software pipelining and register blocking.

Contrast that with the vector model shown in Figure 3.5b, which continues to be as

Figure 3.5: Widening FMA. For brevity, the destination register implicitly supplies the addend in this visualization, although in practice it would usually originate from a third source register.

elegant as before. *Hardware vectors always contain the same number of elements regardless of precision*—again, a benefit of the VLR. Therefore merely one instruction suffices per vector, no matter the peculiar combination of input/output precisions.

To summarize the fundamental weakness of SIMD, a static encoding of the SIMD width in the ISA exposes what is essentially a microarchitectural detail—namely, subword packing being software-visible. Vector architectures successfully avoid this by providing indirection through a vector length register.

There remains a question, however, about how exactly the vector register file could leverage subword packing for improved storage density if that aspect is completely invisible to software. Chapter 5 describes how it is possible, by extending the vector ISA with optional configuration hints about register usage, for a microarchitecture to automatically recoup and near-optimally redistribute the space among mixed-precision vectors.

# Chapter 4

# **Baseline Vector Architecture**

Hwacha is a decoupled vector-fetch data-parallel accelerator which serves as the vehicle for our architectural exploration. Its microarchitecture and programming paradigm combines facets of predecessor vector-threaded architectures, such as Maven [20], [21], with concepts from traditional vector machines—in particular, divergence handling mechanisms in software.

## 4.1 Programming Model

The Hwacha accelerator supports a novel programming model, *vector fetch*. It is best explained by contrast with the traditional vector programming model. As an example, we use a conditionalized SAXPY kernel, CSAXPY. Figure 4.1 shows CSAXPY expressed in C as both a vectorizable loop and as a *Single-Program Multiple-Data* (SPMD) kernel. CSAXPY takes as input an array of conditions, a scalar a, and vectors x and y; it computes y += ax for the elements for which the condition is true.

Hwacha builds on traditional vector architectures, with a key difference: The vector operations have been hoisted out of the stripmine loop and placed in their own *vector fetch block*. This allows the scalar control processor to send only a program counter to the vector processor. The control processor is then able to complete the current stripmine iteration faster and continue doing useful work, while the vector processor is independently executing the vector instructions.

Like a traditional vector machine, Hwacha has vector data registers (vv0-255) and vector

```

void csaxpy(size_t n, bool cond[],

1

void csaxpy_spmd(size_t n, bool cond[],

1

\mathbf{2}

\mathbf{2}

float a, float x[], float y[])

float a, float x[], float y[])

3

3

{

{

4

for (size_t i = 0; i < n; ++i)

4

if (tid < n)

if (cond[i])

5

if (cond[tid])

5

6

6

y[i] = a * x[i] + y[i];

y[tid] = a*x[tid]+y[tid];

\overline{7}

\overline{7}

}

}

(b) SPMD

(a) Vectorizable loop

```

Figure 4.1: Conditional SAXPY kernels written in C. The SPMD kernel launch code for (b) is omitted for brevity.

|    |              |                   | 1  | csaxpy_con | trol_thread:         |

|----|--------------|-------------------|----|------------|----------------------|

|    |              |                   | 2  | vsetcfg    | 2, 1                 |

|    |              |                   | 3  | vmcs vs1   |                      |

|    |              |                   | 4  | stripmine: |                      |

|    |              |                   | 5  | vsetvl     |                      |

|    |              |                   | 6  | vmca       |                      |

|    |              |                   | 7  |            | va1, a3              |

|    |              |                   | 8  |            | va2, a4              |

|    |              |                   | 9  | vf         | csaxpy_worker_thread |

| 1  | csaxpy_tvec: |                   | 10 | add        | a1, a1, t0           |

| 2  | stripmine:   |                   | 11 | slli       | t1, t0, 2            |

| 3  | vsetvl       | t0, a0            | 12 | add        | a3, a3, t1           |

| 4  | vlb          | vv0, (a1)         | 13 | add        | a4, a4, t1           |

| 5  | vcmpez       | vp0, vv0          | 14 | sub        | a0, a0, t0           |

| 6  | !vp0 vlw     | vv0, (a3)         | 15 | bnez       | a0, stripmine        |

| 7  | !vp0 vlw     | vv1, (a4)         | 16 | ret        |                      |

| 8  | !vp0 vfma    | vv0, vv0, a2, vv1 | 17 |            |                      |

| 9  | !vp0 vsw     | vv0, (a4)         | 18 | csaxpy_wor | ker_thread:          |

| 10 | add          | a1, a1, t0        | 19 | vlb        | vv0, (va0)           |

| 11 | slli         | t1, t0, 2         | 20 | vcmpe      | z vp0, vv0           |

| 12 | add          | a3, a3, t1        | 21 | !vp0 vlw   | vv0, (va1)           |

| 13 | add          | a4, a4, t1        | 22 | !vp0 vlw   | vv1, (va2)           |

| 14 | sub          | a0, a0, t0        | 23 | !vp0 vfma  | vv0, vv0, vs1, vv1   |

| 15 | bnez         | a0, stripmine     | 24 | !vp0 vsw   | vv0, (va2)           |

| 16 | ret          |                   | 25 | vstop      |                      |

|    |              |                   |    |            |                      |

|    |              |                   |    |            |                      |

(a) Traditional vector

(b) Hwacha

Figure 4.2: Conditional SAXPY kernels mapped to pseudo-assembly. a0 holds variable n, a1 holds pointer cond, a2 holds scalar a, a3 holds pointer x, and a4 holds pointer y.

predicate registers (vp0-15), but it also has two flavors of scalar registers. These are the *shared* registers (vs0-63, with vs0 hardwired to constant 0), which can be read and written within a vector fetch block, and *address* registers (va0-31), which are read-only within a vector fetch block. This distinction supports non-speculative access/execute decoupling, described in Section 4.3.

Figure 4.2b shows the CSAXPY code for Hwacha. The *control thread* (lines 1–16) first

executes the vsetcfg instruction (line 2), which adjusts the maximum hardware vector length taking the register usage into account. vmcs (line 3) moves the value of a scalar register from the control thread to a vs register. The stripmine loop sets the vector length with a vsetvl instruction (line 5), moves the array pointers to the vector unit with vmca instructions (line 6-8), and then executes a vector-fetch (vf) instruction (line 9), which causes the *worker thread* to begin executing the vector fetch block (lines 18–25). The code in the vector fetch block is equivalent to the vector code in Figure 4.2a, with the addition of a vstop instruction to signify the end of the block.

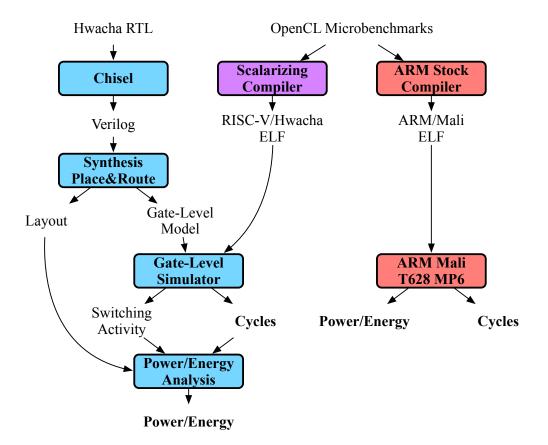

## 4.2 System Architecture

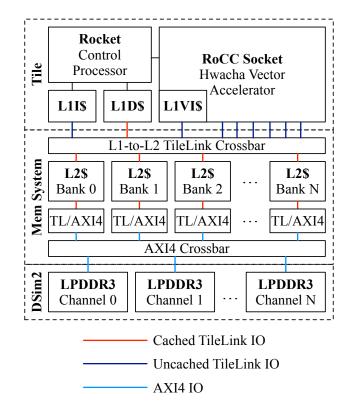

Figure 4.3 illustrates the overall system architecture surrounding Hwacha. The open-source Rocket Chip SoC generator is used to elaborate the design [22]. The generator consists of highly parameterized RTL libraries written in Chisel [23].

Figure 4.3: System architecture provided by the Rocket Chip SoC generator

A tile consists of a Rocket control processor and a Rocket Custom Coprocessor (RoCC) socket. Rocket is a five-stage in-order RISC-V scalar core attached to a private blocking L1 instruction cache and non-blocking L1 data cache. The RoCC socket provides a standardized interface for issuing commands to a custom accelerator, as well as an interface to the memory system. The Hwacha decoupled vector accelerator, along with its blocking vector instruction cache, is designed to fit within the RoCC socket. The control thread and the worker thread of the vector-fetch programming model are mapped to Rocket and Hwacha, respectively.

The shared L2 cache is banked, set-associative, and fully inclusive of the L1. Addresses are interleaved at cache line granularity across banks. The tile and L2 cache banks are connected via an on-chip network that implements the TileLink cache coherence protocol [24].

The refill ports of the L2 cache banks are connected to a bank of cached TileLink IO to AXI4 converters. The AXI4 interfaces are then routed to the appropriate LPDDR3 memory channels through the AXI4 crossbars. The LPDDR3 channels are implemented in the testbench, which simulates the DRAM timing using DRAMSim2 [25].

The memory system parameters such as the cache size, associativity, number of L2 cache banks and memory channels, and cache-coherence protocol are set with a configuration object during elaboration. This configuration object also holds design parameters that are chosen for the Rocket control processor and the Hwacha vector accelerator.

## 4.3 Microarchitecture

The Hwacha vector accelerator combines ideas from access/execute decoupling [26], decoupled vector architectures [27], and cache refill/access decoupling [28], applying them to work within a cache-coherent memory system without risk of deadlock. Extensive decoupling enables the microarchitecture to effectively tolerate long and variable memory latencies with an in-order design.

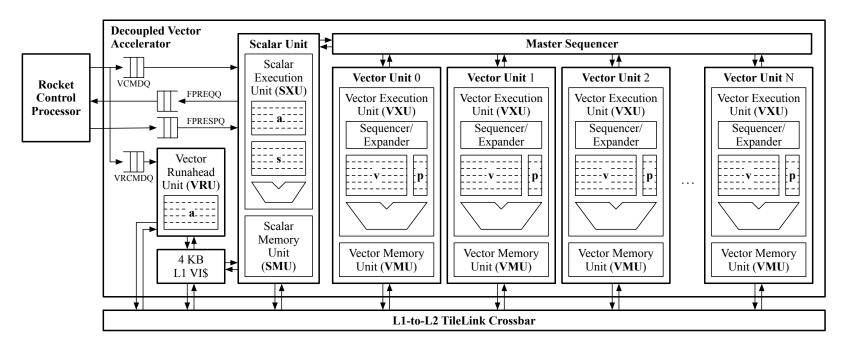

Figure 4.4 presents the high-level anatomy of the vector accelerator. Hwacha is situated as a discrete coprocessor with its own independent frontend. This vector-fetch decoupling relieves the control processor so that it can resolve address calculations for upcoming vector fetch blocks, among other bookkeeping actions, well in advance of the accelerator.

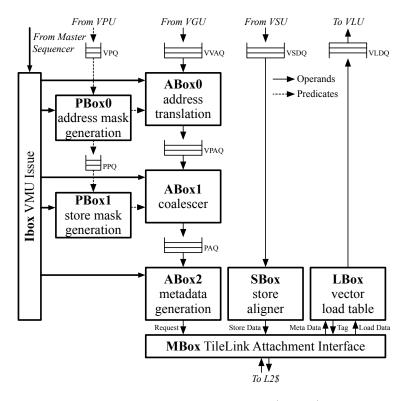

Figure 4.4: Block diagram of Hwacha. VCMDQ = vector command queue, VRCMDQ = vector runahead command queue, FPREQQ = floating-point request queue, FPRESPQ = floating-point response queue.

Hwacha consists of one or more replicated vector lanes assisted by a scalar unit. Internally, the lane is bifurcated into two major components: the *Vector Execution Unit* (VXU), which encompasses the vector data and predicate register files and the functional units, and the *Vector Memory Unit* (VMU), which coordinates data movement between the VXU and the memory system.

Hwacha also features a *Vector Runahead Unit* (VRU) that exploits the inherent regularity of constant-stride vector memory accesses for aggressive yet extremely accurate prefetching. Unlike out-of-order cores with SIMD that rely on reorder buffers and GPUs that rely on multithreading, vector architectures are particularly amenable to prefetching without requiring a large amount of state.

### **RoCC** Frontend and Scalar Unit

Control thread instructions arrive through the Vector Command Queue (VCMDQ). Upon encountering a vf command, the scalar unit begins fetching at the accompanying PC from the 4kB two-way set-associative vector instruction cache (VI\$), continuing until it reaches a vstop in the vector-fetch block.

The scalar unit includes the address and shared register files and possesses a fairly conventional single-issue, in-order, four-stage pipeline. It handles purely scalar computation, loads, and stores, as well as the resolution of consensual branches and reductions resulting from the vector lanes. The FPU is shared with the Rocket control processor via the floating-point request queue (FPREQQ) and floating-point response queue (FPRESPQ). At the decode stage, vector instructions are steered to the lanes along with any scalar operands.

### Vector Execution Unit

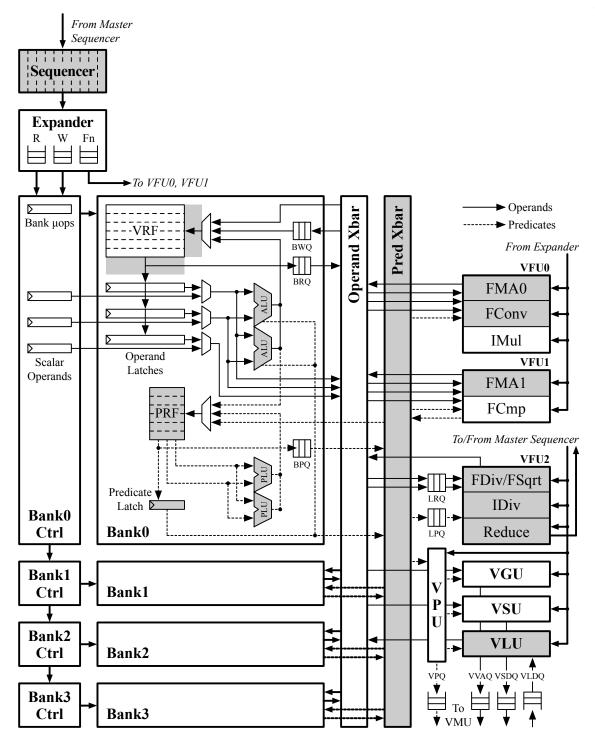

The VXU, depicted in Figure 4.5, is broadly organized around four banks. Each contains a  $256 \times 128b \ 1R/1W \ 8T \ SRAM$  that forms a portion of the vector register file (VRF), alongside a  $256 \times 2b \ 3R/1W$  predicate register file (PRF). Also private to each bank are a local integer arithmetic logic unit (ALU) and predicate logic unit (PLU). A crossbar connects the banks to the long-latency functional units, grouped into clusters whose members share the same operand, predicate, and result lines.

Figure 4.5: Block diagram of the Vector Execution Unit (VXU).

VRF = vector register file, PRF = predicate register file, ALU = arithmetic logic unit, PLU = predicate logic unit, BRQ = bank operand read queue, BWQ = bank operand write queue, BPQ = bank predicate read queue, LRQ = lane operand read queue, LPQ = lane predicate read queue, VFU = vector functional unit, FP = floating-point, FMA = FP fused multiply add unit, FConv = FP conversion unit, FCmp = FP compare unit, FDiv/FSqrt = FP divide/square-root unit, IMul = integer multiply unit, IDiv = integer divide unit, VPU = vector predicate unit, VGU = vector address generation unit, VSU = vector store-data unit, VLU = vector store-data queue, VLDQ = vector load-data queue.

Vector instructions are issued into the sequencer, which monitors the progress of every active operation within that particular lane. The master sequencer, shared among all lanes, holds the common dependency information and other static state. Execution is managed in "strips" that complete eight 64-bit elements worth of work, corresponding to one pass through the banks. The sequencer acts as an out-of-order, albeit non-speculative, issue window: Hazards are continuously examined for each operation; when clear for the next strip, an age-based arbitration scheme determines which ready operation to send to the expander.

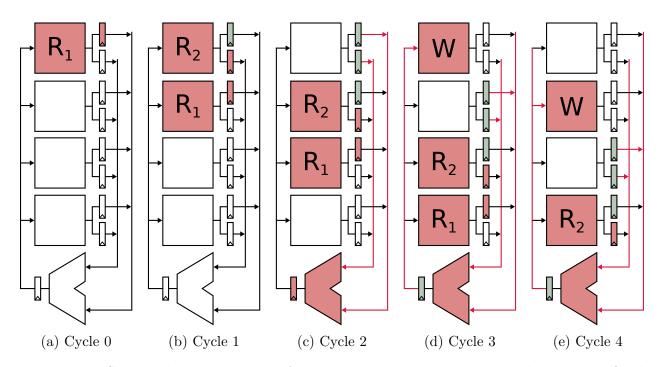

The expander converts a sequencer operation into its constituent micro-ops (µops), lowlevel control signals that directly drive the lane datapath. These are inserted into shift registers with the displacement of read and write µops coinciding exactly with the functional unit latency. The µops iterate through the elements as they sequentially traverse the banks cycle by cycle. As demonstrated by the bank execution example in Figure 4.6, this stallfree systolic schedule sustains n operands per cycle to the shared functional units after an initial n-cycle latency. Variable-latency functional units instead deposit results into per-bank queues (BWQs) for decoupled writes, and the sequencer monitors retirement asynchronously. Vector chaining arises naturally from interleaving µops belonging to different operations.

### Vector Memory Unit

The per-lane VMUs are each equipped with a 128-bit interface to the shared L2 cache. This arrangement delivers high memory bandwidth, albeit with a trade-off of increased latency that is overcome by decoupling the VMU from the rest of the vector unit. Figure 4.7 outlines the organization of the VMU.

As a memory operation is issued to the lane, the VMU command queue is populated with the operation type, vector length, base address, and stride. Address generation for constant-stride accesses proceeds without VXU involvement. For indexed operations such as gathers, scatters, and AMOs, the Vector Generation Unit (VGU) reads offsets from the VRF into the Vector Virtual Address Queue (VVAQ). Virtual addresses are then translated and deposited into the Vector Physical Address Queue (VPAQ), and the progress is reported to the VXU. The departure of requests is regulated by the lane sequencer to facilitate restartable

Figure 4.6: Systolic bank execution of a 2-ary arithmetic operation with a 1-cycle fixed latency. In cycle i, µop  $R_1$  reads the first operand into a buffer at Bank i. In cycle i + 1, µop  $R_2$  reads the second operand into a buffer at Bank i, while  $R_1$  simultaneously reads the first operand into a buffer at Bank i + 1. In cycle i + 2, a crossbar µop (not shown) connects the buffers at Bank i to the two operand lines feeding the shared functional unit at the bottom. In cycle i + 3, µop W commits the finished result to Bank i. Thus, the operand supply is fully pipelined after an initial 1-cycle latency.

exceptions.

The address pipeline is assisted by a separate predicate pipeline. Predicates must be examined to determine whether a page fault is genuine, and are used to derive the store masks. The VMU supports limited density-time skipping given  $2^n$  runs of false predicates [29].

Unit strides represent a very common case for which the VMU is specifically optimized. The initial address generation and translation occur at a page granularity to circumvent predicate latency and accelerate the sequencer check. To more fully utilize the available memory bandwidth, adjacent elements are coalesced into a single request prior to dispatch. The VMU correctly handles edge cases with base addresses not 128-bit-aligned and irregular vector lengths not a multiple of the packing density.

The Vector Store Unit (VSU) multiplexes elements read from the VRF banks into the Vector Store Data Queue (VSDQ). An aligner module following the VSDQ shifts the entries appropriately for scatters and unit-stride stores with non-ideal alignment.

Figure 4.7: Block diagram of the Vector Memory Unit (VMU). Consult Figure 4.5 for VPU, VGU, VSU, VLU, VPQ, VVAQ, VSDQ, VLDQ. VPAQ = vector physical address queue, PPQ = pipe predicate queue, PAQ = pipe address queue.

The Vector Load Unit (VLU) routes data from the Vector Load Data Queue (VLDQ) to their respective banks, using a rotation-based permutation network to handle alignment. As the memory system may arbitrarily order responses, two VLU optimizations become crucial. The first is an opportunistic writeback mechanism that permits the VRF to accept elements out of sequence; this reduces latency and area compared to a reorder buffer. The VLU is also able to simultaneously manage multiple operations to avoid artificial throttling of successive loads by the VMU.

#### Vector Runahead Unit

The Vector Runahead Unit (VRU) takes advantage of the decoupled nature of Hwacha to hide memory latency through prefetching. The VRU consumes a separate Vector Runahead Command Queue (VRCMDQ) ahead of the scalar unit, identifying future vector-fetch targets and maintaining a runahead copy of the address register file. As it populates the vector instruction cache with impending vector-fetch blocks, it decodes and pre-executes unit-strided vector memory operations to refill the L2 cache in anticipation of the actual requests by the vector lanes. Unlike in other machines, these prefetches are in most cases non-speculative. Since the address registers and the vector length cannot be changed by the worker thread, the information provided to the VRU is certain to be accurate.

### Multi-lane Configuration

Hwacha is parameterized to support any  $2^n$  number of identical lanes. Although the master sequencer issues operations to all lanes synchronously, each lane executes entirely decoupled from one another.

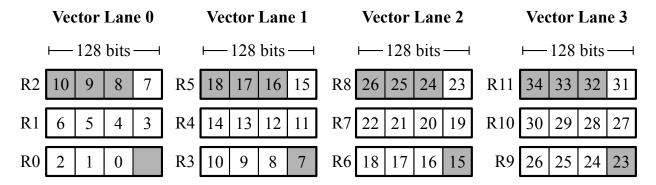

To achieve more uniform load-balancing, elements of a vector are striped across the lanes by a runtime-configurable multiple of the sequencer strip size (the "lane stride"), as shown in Figure 4.8. This also simplifies the base calculation for memory operations of arbitrary constant stride, enabling the VMU to reuse the existing address generation datapath as a short iterative multiplier. The striping does introduce gaps in the unit-stride operations performed by an individual VMU, but the VMU issue unit can readily compensate by decomposing the vector into its contiguous segments, while the rest of the VMU remains oblivious. Unfavorable alignment, however, incurs a modest waste of bandwidth as adjacent lanes request the same cache line at these segment boundaries. Figure 4.9 illustrates an example.

| Vector Lane 0 | Vector Lane 1 | Vector Lane 2 | Vector Lane 3 |

|---------------|---------------|---------------|---------------|

| 0-7           | 8-15          | 16-23         | 24-31         |

| 32-39         | 40-47         | 48-55         | 56-63         |

| 64-71         | 72-79         | 80-87         | 88-95         |

|               |               |               |               |

|               |               |               |               |

|               |               |               |               |

Figure 4.8: Mapping of elements across a four-lane machine

Figure 4.9: Example of redundant memory requests by adjacent lanes. These occur when the base address of a unit-strided vector in memory is not aligned at the memory interface width (128 bits)—in this case, 0x??????4. Each block represents a 128-bit TileLink beat containing four 32-bit elements. Shaded cells indicate portions of a request ignored by each lane. Note that R2 overlaps with R3, R5 with R6, R8 with R9, etc.

## Chapter 5

# **Mixed-Precision Vector Architecture**

We extend the baseline vector architecture with a set of *High-Occupancy Vector* (HOV) enhancements: automatic subword packing for longer vector lengths and higher-throughput execution of reduced-precision operations.

## 5.1 Programming Model

### **Reconfigurable Vector Register File**

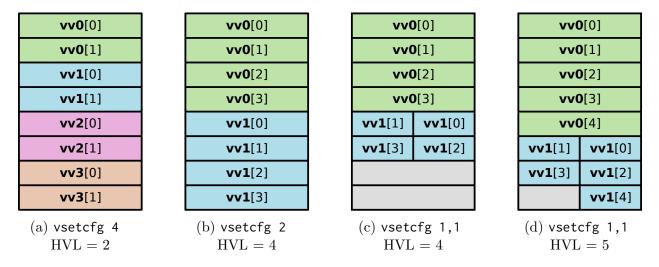

Since there are advantages to both longer vectors and more numerous registers, Hwacha treats the vector register file (VRF) as a fine-grained configurable resource to maximize utilization. From the control thread, the program indicates the number of architectural registers desired for the subsequent vector-fetch blocks through the vsetcfg #vv,#vp instruction. The #vv immediate gives the number of vector data registers from 1 to 256. Similarly, #vp gives the number of vector predicate registers from 0 to 16; if 0, all vector operations execute unconditionally. In response, the vector unit repartitions the physical register file and recalculates the maximum hardware vector length to fill the capacity. Essentially, this provides software with a mechanism to exchange unused architectural registers for longer hardware vectors.

As a simplified demonstration, Figure 5.1a illustrates one possible mapping of four vector registers to an 8-entry VRF, yielding an HVL of 2. Halving the set of vector registers then doubles the HVL to 4, as shown by Figure 5.1b.

Figure 5.1: Simplified logical view of an 8-entry VRF

```

csaxpy_control_thread_hov:

1

2

vsetcfg 0, 2, 0, 1

3

vmcs vs1, a2

4

stripmine:

5

vsetvl

t0, a0

\mathbf{6}

vmca

va0, a1

7

val, a3

vmca

8

va2, a4

vmca

csaxpy_worker_thread

9

vf

10

add

a1, a1, t0

11

t1, t0, 2

slli

12

add

a3, a3, t1

13

a4, a4, t1

add

14

sub

a0, a0, t0

15

bnez

a0, stripmine

16

ret

17

18

csaxpy_worker_thread:

19

vlb

vv0, (va0)

20

vcmpez

vp0, vv0

21

vv0, (va1)

!vp0 vlw

22 !vp0 vlw

vv1, (va2)

23

vv0, vv0, vs1, vv1

!vp0 vfma

24 !vp0 vsw

vv0, (va2)

25

vstop

```

Figure 5.2: Conditional SAXPY kernels updated for HOV. Except for the expanded vsetcfg instruction, highlighted in red, the assembly code is otherwise identical to that of Figure 4.2b.

HOV introduces another dimension of reconfigurability in the VRF: Apart from specifying the number of named vector registers, it also allows for selecting their data type widths from a preset range. The programming model is unaffected except for a singular change to the vsetcfg instruction. #vv is now decomposed into individual subfields #vvd, #vvw and #vvh, denoting the number of requested doubleword (64 bit), word (32 bit), and halfword (16 bit) registers, respectively. Register identifiers are assigned in aggregate by ascending numerical order; higher addresses correspond to decreasing precision. Given vsetcfg 1,2,4,0, for example, the program interacts with vv0 as doublewords; vv1 and vv2 as words; and vv3 through vv6 as halfwords.

From this specification, the hardware automatically determines the appropriate register file mapping, subdivides physical registers as needed into multiple narrower architectural registers, and extends the hardware vector length in proportion to gains in storage density. As is apparent in Figure 5.1c, reduced precision leaves vacant space in the high-order bits of registers. With some rearrangement of elements, of which Figure 5.1d is simply one proposal, contiguous subword packing permits the HVL to be increased by 1.

The developer effort to embrace this optimization is minimal. For many cases, it suffices to modify the vsetcfg instructions alone without rewriting any other code. The CSAXPY kernel, updated for HOV in Figure 5.2, now uses vector registers configured as words instead of doublewords, but it is otherwise identical to the baseline example. For higher-level programming languages, the compiler's register allocator performs most of the work.

Overall, this approach offers a cleaner abstraction than subword SIMD to express mixed precision, particularly in regard to portability. From the perspective of software, architecture register widths are being readjusted instead of packed elements being exposed; the subword packing occurs *implicitly* from the vector register configuration, invisible to the program. An implementation lacking full mixed-precision support may ignore configuration hints and still execute the same code, albeit at reduced efficiency.

#### **Portability Considerations**

It is the responsibility of the architecture to enforce a minimum set of guarantees to ensure consistent program behavior across the range of possible vector machine implementations. Irrespective of the microarchitectural decision to support subword packing for all, none, or a subset of precisions, all operations and trap conditions should be reproducible for the requested vector register file configuration. This concerns, in other words, the ability to execute HOV code with the same result whether or not subword packing is active at the physical level. Portability in this sense can be viewed as matters of both functional correctness and real-world implementation flexibility.

To reason about portability, it is first necessary to distinguish between the size of the data type, as determined by the opcode (the "precision"), and the size of the enclosing container (the register "width").<sup>1</sup> Then the portability issue can be reduced to the problem of determining all legal combinations of precisions and widths for reads and writes. The original baseline configuration, in which all registers are statically constrained to the largest architectural width (64 bits), exemplifies maximal flexibility in the sense that registers are permitted to hold any data of equal or lesser precision. Ideally, in a fully orthogonal model generalized for multiple widths, the default baseline behavior should manifest naturally as the degenerate case, not as an isolated special case.

The desire to impose as few restrictions as possible on the placement of data informs an intuitive maxim: An operation involving a given set of registers is valid if and only if it causes no unrecoverable loss of information. Rules governing the four possible relationships between precision and width follow accordingly:

- 1. Writing higher-precision result to narrower destination: Prohibited on obvious grounds.

- 2. Writing lower-precision result to wider destination: Permitted; must be accompanied by sign extension.

- 3. Reading lower-precision operand from wider source: Permitted; upper bits irrelevant to the operation itself can be safely discarded, which already occurs implicitly inside the functional unit.

- 4. Reading higher-precision operand from narrower destination: Permitted; must be accompanied by sign extension.

$<sup>^{1}</sup>$ In this discussion, the term "register" refers to the individual storage allocated per element, rather than the entire vector, unless otherwise noted.

Most importantly, these enable an implementation to allocate an architecturally narrow register as a physically wider register without requiring it to emulate the former's truncation and sign extension behavior. In other words, the baseline datapath could remain wholly agnostic to the configuration of the architectural register; the only mandatory task is the sign extension of a lower-precision result in Case 2, which is exclusively based on the opcode known *a priori* by the datapath.

The practice of universal sign extension does occasionally leads to some non-intuitive situations. Suppose a VLHU instruction ("vector load halfword unsigned") writes to a vector register configured as halfwords, and those contents are then stored back to memory with a VSD ("vector store doubleword"). From the above specification, one might expect the high-order bits of the doublewords to be sign-extended rather than uniformly cleared. However, if the implementation elects to physically allocate the vector register in doublewords, the store data would happen to consist of zero-extended values instead. The contradiction stems from the fact that the 16-bit load data must be treated as implicitly 17-bit to accurately capture their unsigned nature. Therefore, Case 1 renders invalid any VLHU with a halfword-sized destination; the same applies to VLWU and word-sized destinations.

Case 1 more broadly prescribes that conformant implementations, including the baseline machine if it aims to run HOV code, respect the extended vsetcfg command. Although a microarchitecture may internally assign all requested halfword-sized and word-sized registers to doublewords, it must nonetheless trap on invalid instructions as if those registers were of the intended type.

### **Polymorphic Instruction Sets**

Thus far, it has been assumed that a distinct opcode corresponds to each supported data type (e.g., VFMADD.D, VFMADD.S, VFMADD.H for double/single/half-precision FMAs, respectively). One could imagine *polymorphic instructions* whose input/output precisions are instead determined by the source and destination register specifiers in conjunction with the runtime configuration of the vector register file.

Orthogonality in the instruction set could therefore be achieved without excessive consumption of opcode space or encoding complexity, an increasingly desirable proposition as new mixed-precision operations are added. However, no longer would vector registers be able to hold values of narrower precision than the configured width, which may significantly constrain register reuse by a compiler.

We choose not investigate this concept any further here, as it would involve a drastic overhaul of the vector ISA, and leave it as future work.

### 5.2 Microarchitecture

The microarchitectural extensions for HOV focus on the modules shaded in Figure 4.4, with modifications falling into two broad categories:

- Datapath: parallel functional units and subword compaction/extraction logic

- Control: data hazard checking when chaining vector operations of unequal throughput

### **Register Mapping**

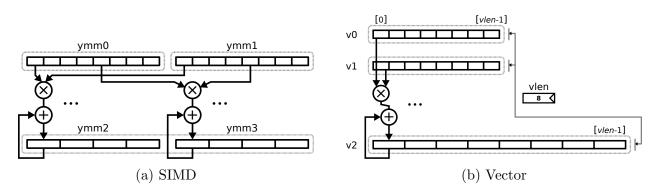

The vector register file banks are segmented into doubleword, word, and halfword regions, with the vector registers interleaved as shown in Figure 5.3. Thus, the starting physical address of a vector register can be straightforwardly calculated by the sum of the architectural register identifier and the associated region offset, and traversing the elements in the vector involves a constant stride equal to the total number of architectural registers of that type.

It is first tempting to assign consecutive element indices to contiguous subwords within a physical entry, but this naive approach soon fails. Consider an operation which reads from both a doubleword register (i.e., vv0) and a word register (i.e., vv2). Should the vector registers be arranged as depicted in Figure 5.4, elements 0 and 1 of vv0 reside in Bank 0 while elements 2 and 3 reside in Bank 1. During each strip, the read µop for vv0 visits Bank 0 for one cycle and then proceeds to Bank 1 in the next, as usual. However, elements 0 to 3 of vv2 are all located in Bank 0. The read µop for vv2 must therefore reserve Bank 0 for two cycles, retrieving a different half of the same entry each time, and then halt before Bank 1. For the following strip, elements 4 to 7, the vv2 µop must begin directly at Bank 1 instead, where it again persists for two cycles.

| Bank 1          |                            |                           |                           | Bank 0                      |                           |                           |                           |  |  |

|-----------------|----------------------------|---------------------------|---------------------------|-----------------------------|---------------------------|---------------------------|---------------------------|--|--|

| vv0[            | <b>vv0</b> [3]             |                           | <b>)</b> [2]              | vv                          | <b>'0</b> [1]             | vv(                       | <b>D</b> [0]              |  |  |

| vv1[            | <b>vv1</b> [3]             |                           | <b>L</b> [2]              | vv                          | <b>1</b> [1]              | vv                        | <b>L</b> [0]              |  |  |

| <b>vv0</b> [7]  |                            | vvC                       | <b>)</b> [6]              | vv                          | <b>'0</b> [5]             | vv                        | <b>D</b> [4]              |  |  |

| <b>vv1</b> [7]  |                            | vvl                       | <b>L</b> [6]              | vv                          | <b>1</b> [5]              | vv                        | <b>1</b> [4]              |  |  |

| <b>vv0</b> [3   | <b>vv0</b> [11]            |                           | [10]                      | vv                          | <b>'0</b> [9]             | vv(                       | <b>D</b> [8]              |  |  |

| <b>vv1</b> []   | 11]                        | vv1                       | [10]                      | vv                          | <b>1</b> [9]              | vv                        | <b>1</b> [8]              |  |  |

| <b>vv0</b> [3   | <b>vv0</b> [15]            |                           | [14]                      | vv                          | <b>0</b> [13]             | <b>vv0</b> [12]           |                           |  |  |

| <b>vv1</b> []   | 15]                        | vv1                       | [14]                      | vv                          | <b>1</b> [13]             | vv0[12]<br>vv1[12]        |                           |  |  |

| <b>vv2</b> [7]  | <b>vv2</b> [6]             | <b>vv2</b> [3]            | <b>vv2</b> [2]            | <br><b>vv2</b> [5]          | <b>vv2</b> [4]            | <b>vv2</b> [1]            | <b>vv2</b> [0]            |  |  |

| <b>vv3</b> [7]  | <b>vv3</b> [6]             | <b>vv3</b> [3]            | <b>vv3</b> [2]            | <b>vv3</b> [5]              | <b>vv3</b> [4]            | <b>vv3</b> [1]            | <b>vv3</b> [0]            |  |  |

| <b>vv4</b> [7]  | <b>vv4</b> [6]             | <b>vv4</b> [3]            | <b>vv4</b> [2]            | <b>vv4</b> [5]              | <b>vv4</b> [4]            | <b>vv4</b> [1]            | <b>vv4</b> [0]            |  |  |

| <b>vv2</b> [15] | <b>vv2</b> [14]            | <b>vv2</b> [11]           | <b>vv2</b> [10]           | <b>vv2</b> [13]             | <b>vv2</b> [12]           | <b>vv2</b> [9]            | <b>vv2</b> [8]            |  |  |

| <b>vv3</b> [15] | <b>vv3</b> [14]            | <b>vv3</b> [11]           | <b>vv3</b> [10]           | <b>vv3</b> [13]             | <b>vv3</b> [12]           | <b>vv3</b> [9]            | <b>vv3</b> [8]            |  |  |

| <b>vv4</b> [15] | <b>vv4</b> [14]            | <b>vv4</b> [11]           | <b>vv4</b> [10]           | <b>vv4</b> [13]             | <b>vv4</b> [12]           | <b>vv4</b> [9]            | <b>vv4</b> [8]            |  |  |

|                 | <b>/v5 vv5</b><br>11] [10] | <b>vv5 vv5</b><br>[7] [6] | <b>vv5 vv5</b><br>[3] [2] | <b>vv5 vv5</b><br>[13] [12] | <b>vv5 vv5</b><br>[9] [8] | <b>vv5 vv5</b><br>[5] [4] | <b>vv5 vv5</b><br>[1] [0] |  |  |

Figure 5.3: Actual striped mapping to a 2-bank physical VRF

| Bank 1                      |                             |                             |                           | Bank 0 |                                 |                           |                           |                           |  |

|-----------------------------|-----------------------------|-----------------------------|---------------------------|--------|---------------------------------|---------------------------|---------------------------|---------------------------|--|

| <b>vv0</b> [3]              |                             | vvC                         | <b>)</b> [2]              |        | vv                              | <b>'0</b> [1]             | vv(                       | <b>0</b> [0]              |  |

| vv                          | <b>1</b> [3]                | vv1                         | L[2]                      |        | vv                              | <b>1</b> [1]              | vv                        | <b>L</b> [0]              |  |

| <b>vv0</b> [7]              |                             | vvC                         | <b>)</b> [6]              |        | vv                              | <b>'0</b> [5]             | vv(                       | <b>D</b> [4]              |  |

| <b>vv1</b> [7]              |                             | vv1                         | L[6]                      |        | vv                              | <b>1</b> [5]              | vv                        | <b>vv1</b> [4]            |  |

| <b>vv0</b> [11]             |                             | vv0                         | [10]                      |        | vv                              | <b>0</b> [9]              | vv(                       | <b>)</b> [8]              |  |

| <b>vv1</b> [11]             |                             | vv1                         | [10]                      |        | <b>vv1</b> [9]                  |                           | <b>vv1</b> [8]            |                           |  |

| <b>vv0</b> [15]             |                             | vv0                         | [14]                      |        | <b>vv0</b> [13] <b>vv0</b> [12] |                           | [12]                      |                           |  |

| <b>vv1</b> [15]             |                             | vv1                         | [14]                      |        | <b>vv1</b> [13] <b>vv1</b> [12] |                           | [12]                      |                           |  |

| <b>vv2</b> [7]              | <b>vv2</b> [6]              | <b>vv2</b> [5]              | <b>vv2</b> [4]            |        | <b>vv2</b> [3]                  | <b>vv2</b> [2]            | <b>vv2</b> [1]            | <b>vv2</b> [0]            |  |

| <b>vv3</b> [7]              | <b>vv3</b> [6]              | <b>vv3</b> [5]              | <b>vv3</b> [4]            |        | <b>vv3</b> [3]                  | <b>vv3</b> [2]            | <b>vv3</b> [1]            | <b>vv3</b> [0]            |  |

| <b>vv4</b> [7]              | <b>vv4</b> [6]              | <b>vv4</b> [5]              | <b>vv4</b> [4]            |        | <b>vv4</b> [3]                  | <b>vv4</b> [2]            | <b>vv4</b> [1]            | <b>vv4</b> [0]            |  |

| <b>vv2</b> [15]             | <b>vv2</b> [14]             | <b>vv2</b> [13]             | <b>vv2</b> [12]           |        | <b>vv2</b> [11]                 | <b>vv2</b> [10]           | <b>vv2</b> [9]            | <b>vv2</b> [8]            |  |

| <b>vv3</b> [15]             | <b>vv3</b> [14]             | <b>vv3</b> [13]             | <b>vv3</b> [12]           |        | <b>vv3</b> [11]                 | <b>vv3</b> [10]           | <b>vv3</b> [9]            | <b>vv3</b> [8]            |  |

| <b>vv4</b> [15]             | <b>vv4</b> [14]             | <b>vv4</b> [13]             | <b>vv4</b> [12]           |        | <b>vv4</b> [11]                 | <b>vv4</b> [10]           | <b>vv4</b> [9]            | <b>vv4</b> [8]            |  |

| <b>vv5 vv5</b><br>[15] [14] | <b>vv5 vv5</b><br>[13] [12] | <b>vv5 vv5</b><br>[11] [10] | <b>vv5 vv5</b><br>[9] [8] |        | <b>vv5 vv5</b><br>[7] [6]       | <b>vv5 vv5</b><br>[5] [4] | <b>vv5 vv5</b><br>[3] [2] | <b>vv5 vv5</b><br>[1] [0] |  |

Figure 5.4: Hypothetical naive mapping to a 2-bank physical VRF

With only one read and write port per bank, the non-uniform pace of µops would lead to myriad bank conflicts. Circumventing these structural hazards would require generating unique schedules for each bank, counter to the systolic execution principle. The control logic would then become quickly intractable. To preserve a regular access schedule, all elements with the same index should reside within the same bank. This inspires the *elementpartitioned* scheme demonstrated by Figure 5.3, which stripes elements such that adjacent slices (pairs of elements) coincide with indices separated by the strip size.

The size of the SRAM arrays remain unchanged. However, the predicate register file is widened to 8 bits so that all predicates associated with a maximally packed SRAM entry of eight halfwords are accessible through a single port in one cycle. The predicate mapping is also striped in the manner above.

#### Maximum Hardware Vector Length

The maximum hardware vector length depends on the number of SRAM entries across all banks and lanes in the machine, as well as the number of architectural registers requested by the program. The extended HVL is calculated with the following formula, implemented as a lookup table in hardware:

$$HVL = \left\lfloor \frac{4r}{4d + 2w + h} \right\rfloor \times n_{\text{slices}} \times n_{\text{banks}} \times n_{\text{lanes}}$$

(5.1)

Variables d, w, and w refer to the desired number of doubleword, word, and halfword vector registers, respectively. For the default configuration, r = 256 (number of SRAM entries per bank),  $n_{\text{slices}} = 2$ , and  $n_{\text{banks}} = 4$ . If subword packing is disabled at design elaboration, the formula reverts to one equivalent to the baseline:

$$HVL = \left\lfloor \frac{r}{d+w+h} \right\rfloor \times n_{\text{slices}} \times n_{\text{banks}} \times n_{\text{lanes}}$$

(5.2)