## Readout Circuits for Frequency-Modulated Gyroscopes

Igor Izyumin

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2015-214 http://www.eecs.berkeley.edu/Pubs/TechRpts/2015/EECS-2015-214.html

December 1, 2015

Copyright © 2015, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### **Readout Circuits for Frequency-Modulated Gyroscopes**

by

Igor Igorevich Izyumin

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Bernhard E. Boser, Chair Professor Elad Alon Professor Dorian Liepmann

Fall 2014

## Readout Circuits for Frequency-Modulated Gyroscopes

Copyright 2014 by Igor Igorevich Izyumin

#### Abstract

#### Readout Circuits for Frequency-Modulated Gyroscopes

by

Igor Igorevich Izyumin

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Bernhard E. Boser, Chair

In recent years, MEMS gyroscopes have become nearly omnipresent. From their origins in automotive stability control systems, these sensors have migrated to a diverse range of applications, including image stabilization in cameras and motion tracking in video games and fitness monitors. A key application for MEMS gyroscopes is pedestrian navigation, which can help provide always-on location in portable devices while minimizing power consumption and infrastructure requirements. While modern smartphones have all of the necessary sensors for inertial navigation, their performance is not sufficient for this application. Consumer-grade MEMS gyroscopes are typically rate-grade devices, and generally have poor bias stability and scale factor accuracy. In addition, their power consumption tends to be too high to enable always-on operation without significantly impacting battery life.

This work describes the first frequency-output MEMS gyroscope to achieve <7 ppm scale factor accuracy and < 6°/hr bias stability with a 3.24 mm<sup>2</sup> transducer. By implementing continuous-time mode reversal in an FM gyro, the rate signal is modulated away from DC, making the system insensitive to the resonant frequency of the transducer. The scale factor is almost entirely ratiometric, depending primarily on the mechanical angular gain factor of the transducer and the accuracy of the timing reference. Scale factor sensitivity to variations in quality factor, electro-mechanical coupling coefficients, and circuit drift is significantly reduced compared to conventional open-loop and force-rebalance operating modes. Low-power frequency-to-digital converters enable a gyroscope with 91 dB of dynamic range and an estimated power consumption below 150  $\mu$ W per axis.

To my family.

## Contents

| Co | ontents                                                                                                                                                                                                                                                         | ii                                                                                                                     |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Li | st of Figures                                                                                                                                                                                                                                                   | iv                                                                                                                     |

| Li | st of Tables                                                                                                                                                                                                                                                    | vi                                                                                                                     |

| 1  | Introduction         1.1       Motivation         1.2       Performance objectives                                                                                                                                                                              | <b>1</b><br>1<br>3                                                                                                     |

| 2  | Frequency-Modulated Gyroscopes2.1Background2.2Quadrature FM operation2.3Lissajous FM operation2.4LFM gyroscope error sources2.5Test setup2.6Sensor model                                                                                                        | 7<br>7<br>8<br>9<br>11<br>14<br>18                                                                                     |

| 3  | Frequency-to-Digital Conversion3.1Introduction3.2Performance requirements3.3FM demodulation methods3.4Comparator design3.5 $\Sigma \Delta FDC$ Architecture3.6Double edge sampling3.7High-level design3.8Circuit implementation3.9Experimental characterization | <ol> <li>19</li> <li>20</li> <li>21</li> <li>27</li> <li>43</li> <li>45</li> <li>47</li> <li>50</li> <li>60</li> </ol> |

| 4  | LFM Signal Processing4.1Background4.2Filtering and resampling                                                                                                                                                                                                   | <b>63</b><br>63<br>63                                                                                                  |

|     | Demodulation reference extraction                |    |

|-----|--------------------------------------------------|----|

| 4.5 | Quadrature extraction       Experimental results | 73 |

|     | 1                                                | 78 |

## Bibliography

5

79

# **List of Figures**

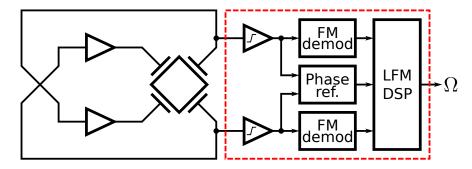

| 2.1  | Lissajous FM gyroscope block diagram.                                                                         | 9  |

|------|---------------------------------------------------------------------------------------------------------------|----|

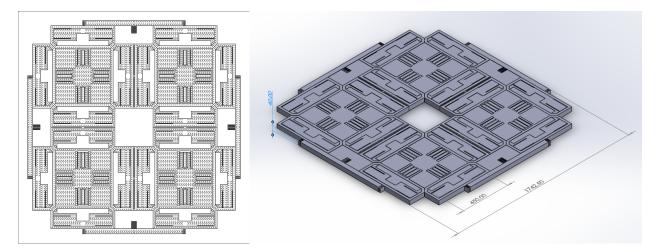

| 2.2  | Layout of quad-mass gyroscope transducer                                                                      | 14 |

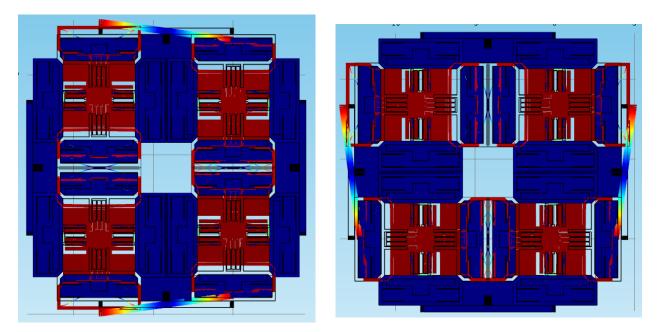

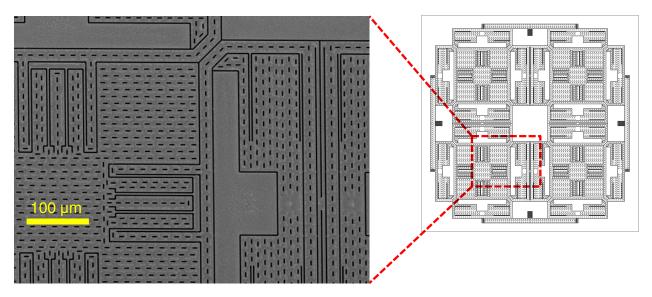

| 2.3  | Desired mode shapes of gyroscope transducer.                                                                  | 15 |

| 2.4  | Scanning electron microscope photograph of fabricated structure                                               | 15 |

| 2.5  | Oscillator differential half-circuit.                                                                         | 16 |

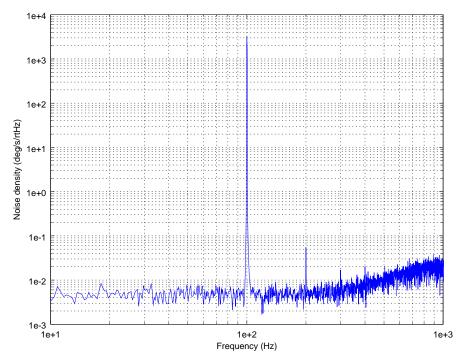

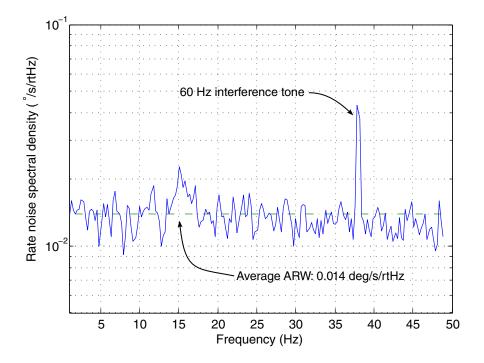

| 2.6  | Measured frequency noise spectral density for single oscillator channel                                       | 16 |

| 3.1  | Arctangent-based FM demodulator                                                                               | 22 |

| 3.2  | FM demodulation by period measurement.                                                                        | 24 |

| 3.3  | Simplified equivalent comparator model.                                                                       | 29 |

| 3.4  | Switching waveforms for comparator model                                                                      | 30 |

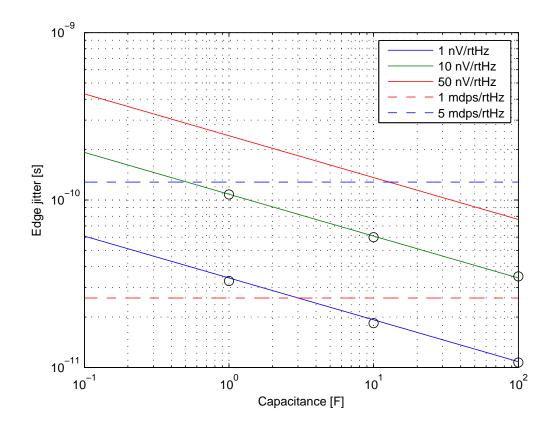

| 3.5  | Calculated and simulated comparator edge jitter vs. C with different levels of                                |    |

|      | input noise.                                                                                                  | 31 |

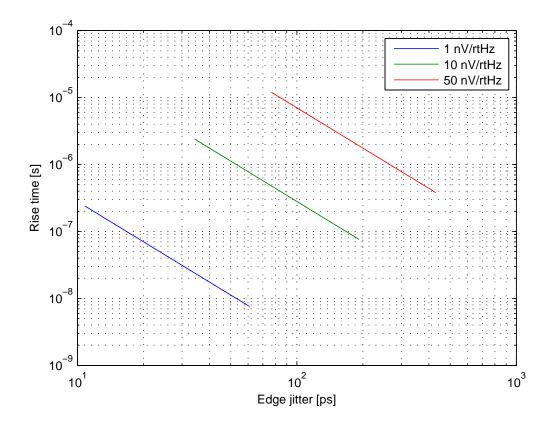

| 3.6  | Calculated comparator rise time vs. edge jitter due to input noise                                            | 32 |

| 3.7  | Example comparator design.                                                                                    | 34 |

| 3.8  | AM to PM conversion in the presence of offset                                                                 | 35 |

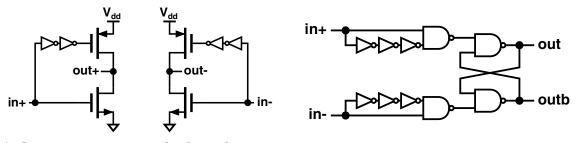

| 3.9  | Comparator implementation.                                                                                    | 40 |

| 3.10 |                                                                                                               | 41 |

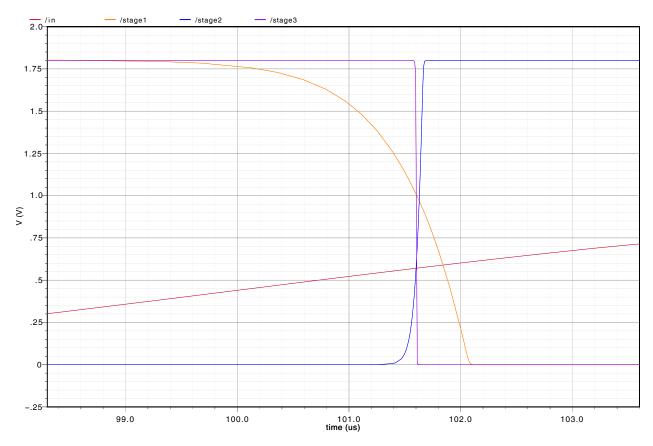

|      | Example comparator switching waveforms                                                                        | 41 |

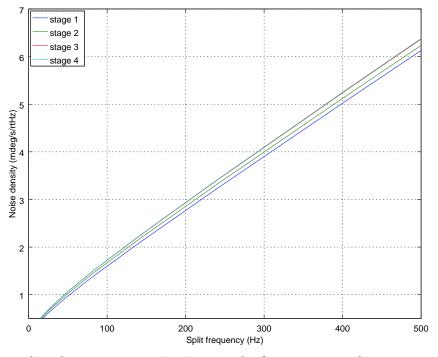

|      | Simulated comparator ARW vs. split frequency at the output of each stage                                      | 42 |

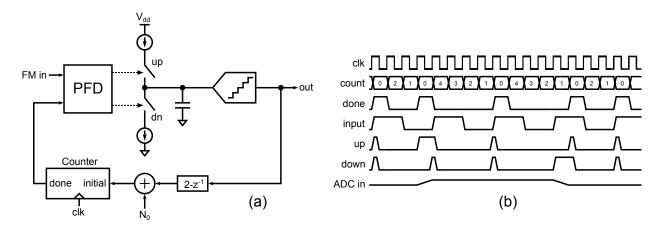

|      | $\Sigma \Delta$ FDC: (a) conceptual block diagram; (b) timing diagram                                         | 43 |

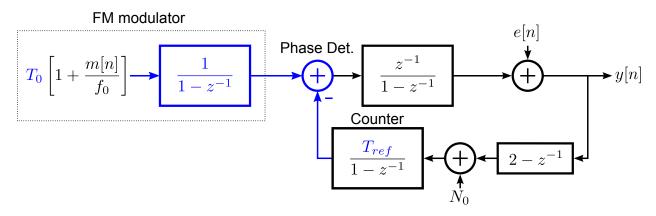

|      | Linearized equivalent model of $\Sigma \Delta FDC$                                                            | 44 |

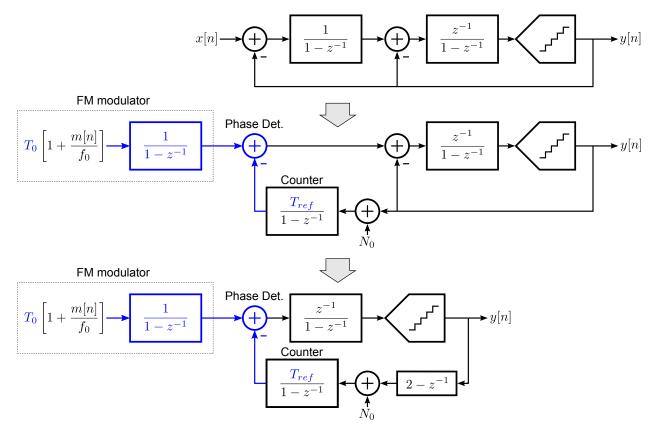

|      | Synthesis of $\Sigma \Delta$ FDC structure from second-order $\Sigma \Delta$ modulator $\ldots \ldots \ldots$ | 45 |

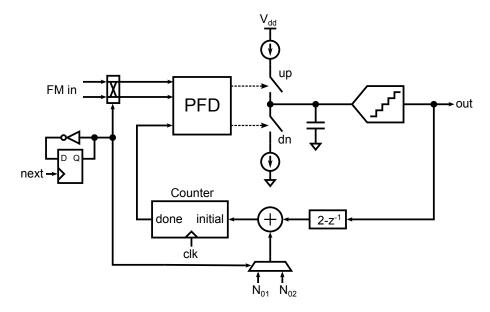

| 3.16 | $\Sigma \Delta FDC$ configuration for double edge sampling                                                    | 46 |

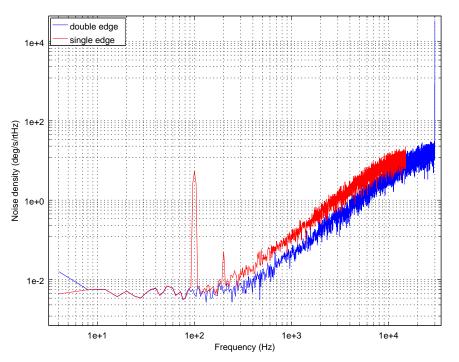

|      | AM rejection via double edge sampling                                                                         | 47 |

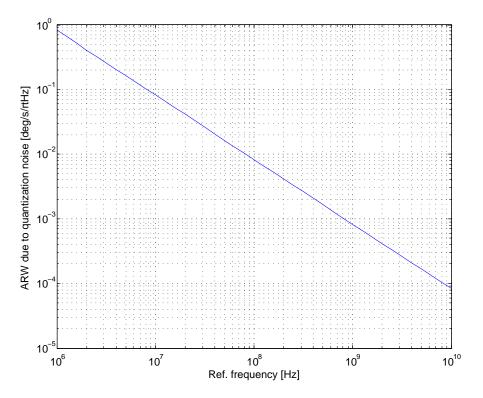

| 3.18 | ARW due to quantization noise as a function of reference clock frequency for                                  |    |

|      | 2nd order loop, $f_{split} = 200$ Hz, $BW = 100$ Hz                                                           | 49 |

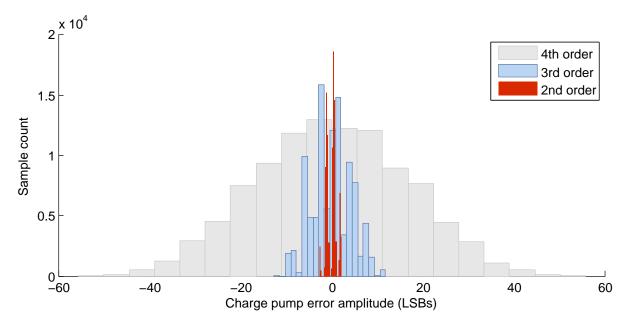

|      | Example fourth-order $\Sigma \Delta$ FDC structure with combined feedback path                                | 50 |

| 3.20 | Simulated phase detector error histogram for 2nd, 3rd, and 4th order loops                                    |    |

|      | with combined feedback.                                                                                       | 51 |

|      | with combined feedback                                                                                        |    |

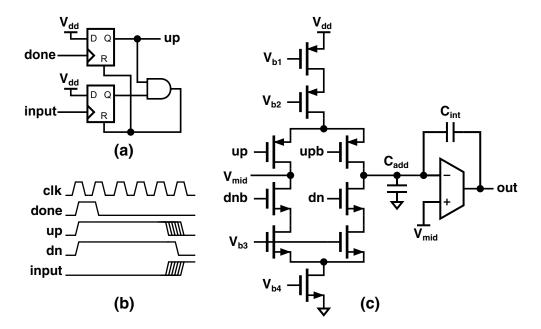

| 3.21 | PFD and charge pump circuits: (a) PFD schematic, (b) timing diagram, (c)               | 50 |

|------|----------------------------------------------------------------------------------------|----|

|      | charge pump and integrator schematic.                                                  | 52 |

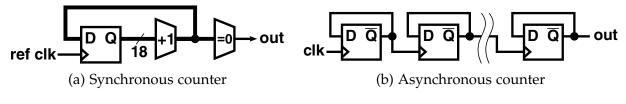

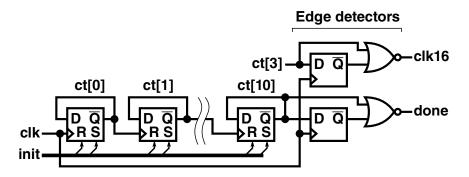

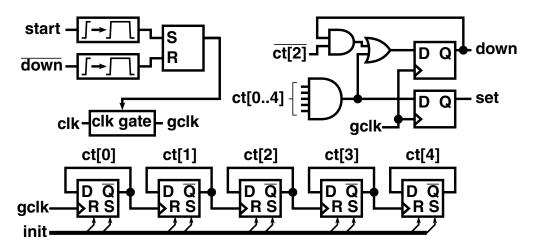

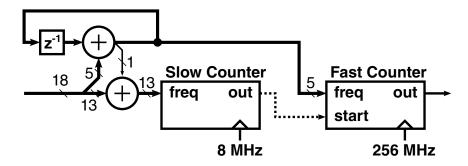

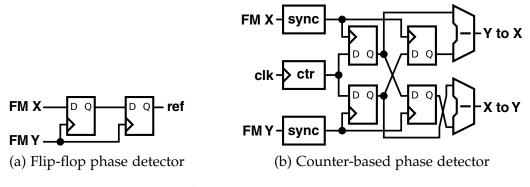

| 3.22 | Counter topologies                                                                     | 53 |

| 3.23 | Slow counter schematic.                                                                | 54 |

|      | Fast counter schematic.                                                                | 55 |

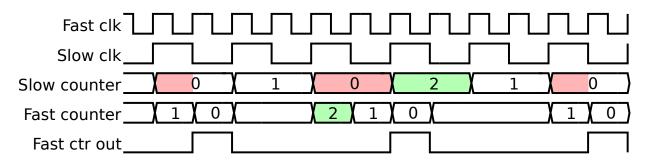

| 3.25 | Dual-stage counter block diagram.                                                      | 56 |

| 3.26 | Dual-stage counter overlap compensation example                                        | 57 |

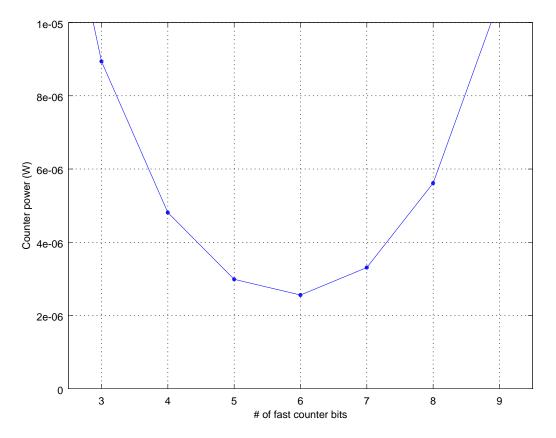

| 3.27 | Total counter dynamic power as a function of the number of fast counter bits.          | 58 |

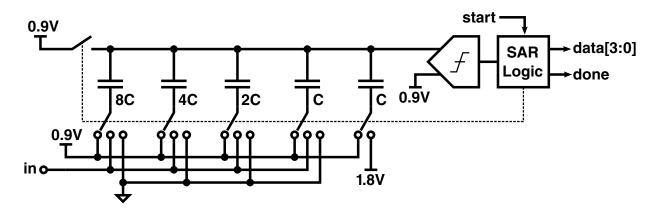

| 3.28 | SAR ADC block diagram.                                                                 | 58 |

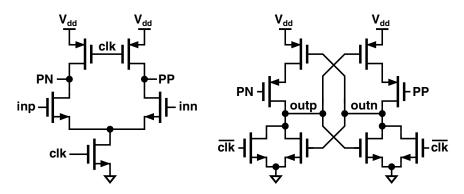

| 3.29 | ADC comparator schematic.                                                              | 60 |

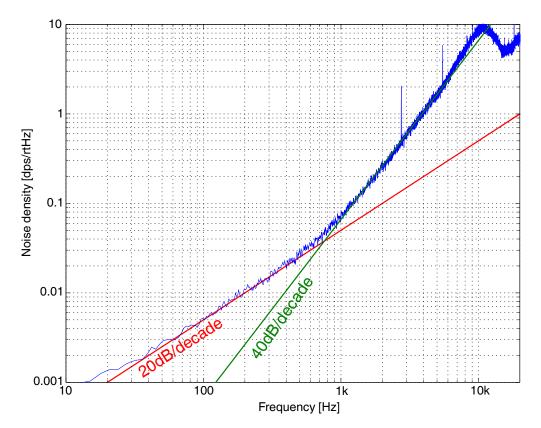

| 3.30 | Measured FDC noise density with 30kHz function generator input                         | 61 |

| 3.31 | Measured FDC power spectrum with 100 Hz sinusoidal frequency modula-                   |    |

|      | tion having 10 Hz deviation amplitude.                                                 | 62 |

| 3.32 | Noise floor with and without applied full-scale modulation                             | 62 |

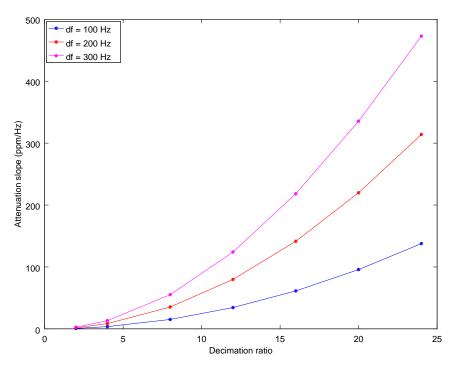

| 4.1  | Split frequency sensitivity as a function of decimation ratio and split fre-           |    |

|      | quency for a 3-stage CIC decimator.                                                    | 65 |

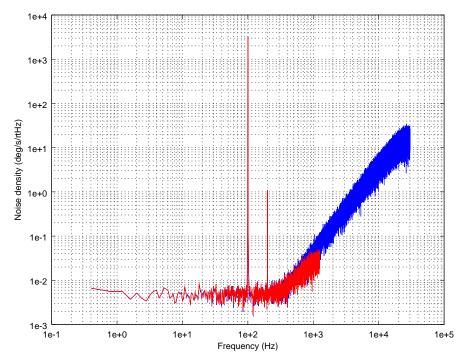

| 4.2  | Power spectral density before and after $24 \times$ , 3-stage CIC decimator with full- |    |

|      | scale modulating signal.                                                               | 66 |

| 4.3  | Power spectral density after resampling                                                | 66 |

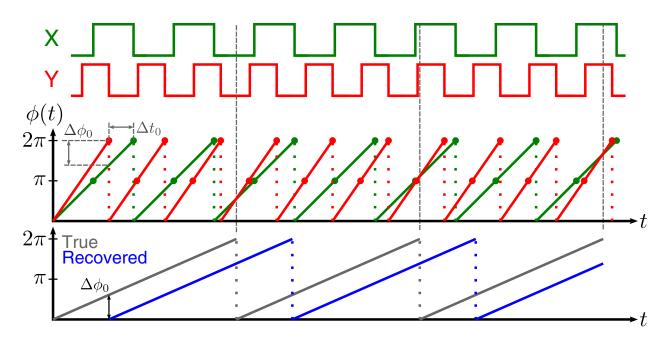

| 4.4  | Reference phase extraction and initial error                                           | 68 |

| 4.5  | Reference phase extraction circuits.                                                   | 68 |

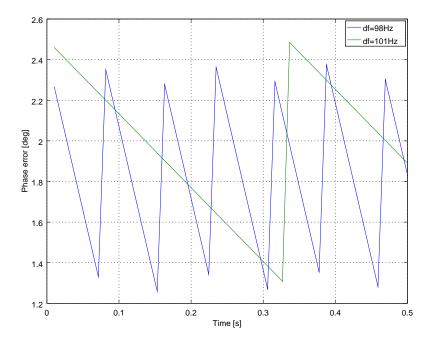

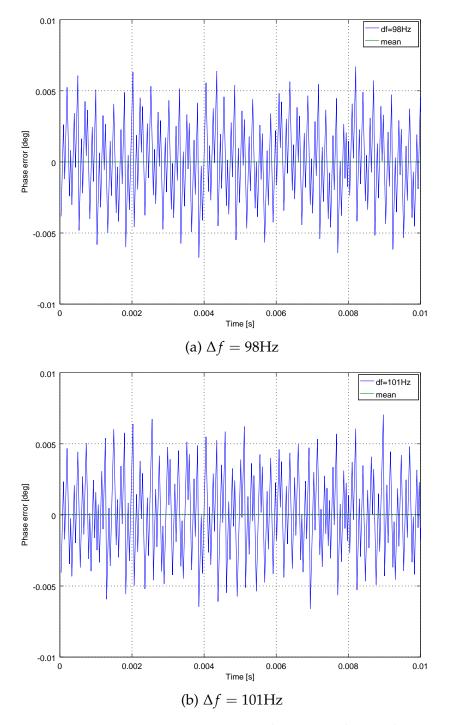

| 4.6  | Simulated phase estimate error as a function of time for the bang-bang phase           |    |

|      | detector phase recovery circuit                                                        | 69 |

| 4.7  | Simulated phase estimate error as a function of time for the counter-based             |    |

|      | phase recovery circuit                                                                 | 70 |

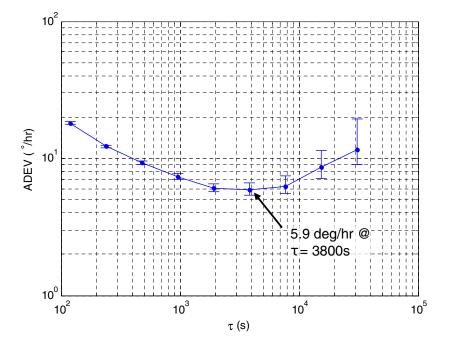

| 4.8  | Bias Allan deviation.                                                                  | 74 |

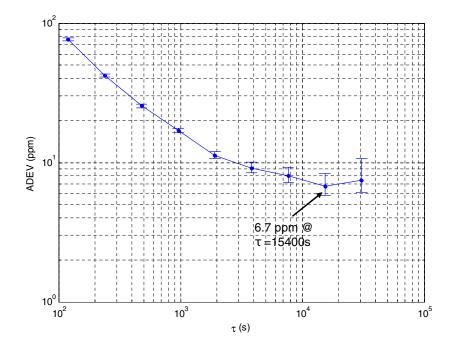

| 4.9  | Scale factor Allan deviation.                                                          | 74 |

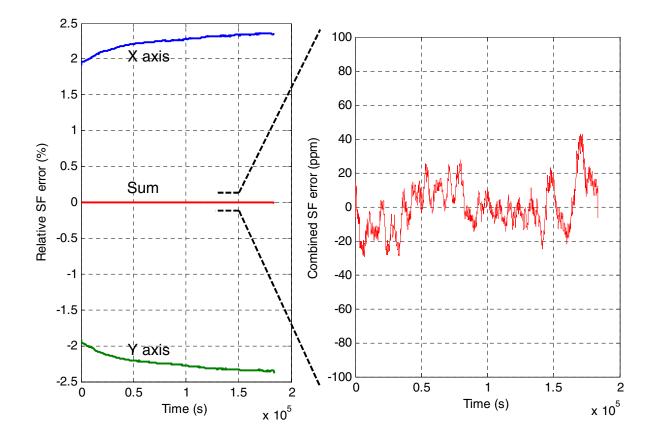

| 4.10 |                                                                                        | 76 |

| 4.11 | Time-domain scale factor measurement                                                   | 77 |

## **List of Tables**

| 1.1 | Comparison of commercially available consumer-grade low-power 3-axis MEMS |    |  |  |

|-----|---------------------------------------------------------------------------|----|--|--|

|     | gyroscopes commonly used in smartphones.                                  | 2  |  |  |

| 1.2 | Comparison of this work to existing products.                             | 4  |  |  |

| 3.1 | Controller state table                                                    | 57 |  |  |

### Acknowledgments

I would like to thank my advisor, Professor Bernhard E. Boser, for his unwavering support, guidance, encouragement, and honest, constructive critical feedback. I would also like to thank my dissertation committee members, Prof. Elad Alon and Prof. Dorian Liepmann, for their time and valuable feedback.

During my time at Berkeley, it was a great privilege to work with such wonderful friends and colleagues as Mitchell Kline, Richard Przybyla, Octavian Florescu, Stefon Shelton, Karl Skucha, Mischa Megens, Simone Gambini, Rikky Muller, Behnam Behroozpour, Burak Eminoglu, Yu-Ching Yeh, Pramod Murali, Hao-Yen Tang, Mekhail Anwar, Efthymios Papageorgiou, Niels Quack, Matthew Spencer, Steven Callender, Milos Jorgovanovic, and many others. They have truly made my graduate school experience both educational and enjoyable.

I would like to acknowledge the staff of the EECS department, BSAC, and Swarm Lab, including Richard Lossing, Kim Ly, Alex Luna, Mila MacBain, Shelley Kim, and Shirley Salanio. They have all been extremely helpful in dealing with administrative matters.

I am forever indebted to my parents, Natalia and the late Igor Sr., and my brother Oleg for their love, countless sacrifices and endless support and encouragement.

I would like to thank TSMC, InvenSense, and the Thomas W. Kenny group at Stanford University for providing integrated circuit and MEMS fabrication. This work was supported in part by the Defense Advanced Research Projects Agency.

## Chapter 1

## Introduction

## 1.1 Motivation

In recent years, MEMS gyroscopes have become nearly omnipresent. From their origins in automotive stability control systems, these sensors have migrated to a diverse range of applications, including image stabilization in cameras and motion tracking in video games and fitness monitors. Every modern smartphone includes a 3-axis gyroscope.

Location data is a key feature enabling many smartphone applications. Location is used for navigation and maps; it can help provide geographically relevant suggestions and targeted advertising; it also provides high-resolution real-time traffic data. Accurate and ubiquitous indoor positioning enables applications such as building automation.

Smartphones use a variety of techniques to obtain position data. The primary location source is the Global Positioning System (GPS). GPS provides accurate and highresolution position data; however, it does not work indoors and has high power consumption due to the required receiver sensitivity. A typical GPS chip consumes 9 mW during operation [1]. Wi-Fi positioning is a lower-power alternative that has the potential to work indoors; however, it has relatively low accuracy. Much work has been done on beacon-based indoor location systems [2]; however, their deployment requires significant capital investment and ongoing maintenance costs, and such systems are therefore unlikely to ever become truly ubiquitous.

An approach that can help provide always-on, high-resolution location data is inertial navigation, also known as dead reckoning. Such a system generally uses a 6-axis inertial measurement unit, consisting of orthogonally mounted accelerometers and gyroscopes that continuously integrate motion data to compute a location estimate. In the general case, inertial navigation requires extremely high-performance, high-cost, macro-scale

|                           | InvenSense                          | Bosch                         | ST                                   |

|---------------------------|-------------------------------------|-------------------------------|--------------------------------------|

|                           | MPU-6050 [3]                        | BMG160 [4]                    | A3G250D [5]                          |

| Angle random walk         | $5 \text{ mdeg/s}/\sqrt{\text{Hz}}$ | 14 mdeg/s/ $\sqrt{\text{Hz}}$ | $30 \text{ mdeg/s}/\sqrt{\text{Hz}}$ |

| Max rate (min. ARW)       | 250 deg/s                           | 125 deg/s                     | 245 deg/s                            |

| ZRO (over temp.)          | $\pm 20 \text{ deg/s}$              | $\pm 1.9$ deg/s               | $\pm 3.8 \text{ deg/s}$              |

| Scale factor (25°C)       | ±3%                                 | $\pm 1\%$                     |                                      |

| Scale factor (over temp.) | $\pm 2\%$                           | $\pm 3.75\%$                  | $\pm 2\%$                            |

| Power                     | 8.6 mW                              | 12 mW                         | 15 mW                                |

Table 1.1: Comparison of commercially available consumer-grade low-power 3-axis MEMS gyroscopes commonly used in smartphones.

sensors to obtain even moderate accuracy. Constraining the problem to pedestrian dead reckoning over relatively short time periods makes it possible to obtain reasonable position accuracy with high-performance MEMS sensors [6]. While the long-term accuracy of dead reckoning is generally poor, such a system could be used to provide continuous location data between periodic GPS or beacon-based location updates, reducing power and improving the user experience.

While modern smartphones have all of the necessary sensors for inertial navigation, their performance is not sufficient for this application. Consumer-grade MEMS gyroscopes are typically rate-grade devices, and generally have poor bias stability and scale factor accuracy. In addition, their power consumption tends to be too high to enable always-on operation without significantly impacting battery life. Table 1.1 shows a comparison between several recent consumer-grade 3-axis MEMS gyroscope units. Bias stability is generally not specified for these parts; the zero rate output (ZRO) and scale factor vary significantly over the operating temperature range. While it is possible to calibrate the ZRO by auto-zeroing when no motion is detected, it is difficult to correct scale factor errors. Scale factor errors can cause significant position errors: for example, a 2% error in the gyroscope scale factor would cause a 3.6° heading error after a single 180° turn. This error, in turn, causes a 6 m position error for every 100 m traveled. Since pedestrian travel in a high-density urban environment may involve a relatively large number of turns, scale factor accuracy is a critical specification.

Frequency-modulated gyroscopes promise to address many of these issues. The foremost advantage of FM operation is the intrinsically accurate scale factor, which does not significantly vary with temperature [7]. Another advantage is the large dynamic range available: while most of the gyros in table 1.1 are restricted to 250 deg/s or less to maintain the specified angle random walk, the FM gyroscope can avoid this trade-off. Finally, virtual mode reversal rejects errors due to cross-axis damping, improving bias stability.

## **1.2** Performance objectives

#### **Bias stability**

Gyroscope performance requirements for an inertial navigation system are difficult to define. The specific navigation system implementation largely determines how gyroscope errors translate into position errors. Nevertheless, it is useful to define a performance metric that quantifies errors introduced by the gyroscope. One such metric is the integrated heading error for a given integration time with zero rate input. This metric ignores scale factor errors, which are input-dependent and which need to be considered separately.

When the gyroscope output is integrated, multiple error sources corrupt the measurement. These error sources can generally be separated by their spectral characteristics into angle random walk (integrated angle error  $\propto \sqrt{t}$ ), bias instability (integrated angle error  $\propto t$ ), and rate random walk (integrated angle error  $\propto t^2$ ). At short integration times, angle random walk (ARW) tends to dominate; the other sources generally dominate for longer integration times.

The most commonly accepted method of characterizing the stability of gyroscopes is the Allan deviation [8]. To compute the Allan deviation for a given time duration  $\tau$ , a long rate measurement is sliced into pieces of length  $\tau$ , and the mean is computed for each such piece. Subsequent values are then differenced; the standard deviation of the resulting differences is the Allan deviation. The Allan deviation thus represents the rms random drift for a given integration time. Multiplying the Allan deviation by the integration time provides an estimate of the rms integrated angle error for a given integration time.

A rough estimate of the required gyroscope accuracy can be obtained by considering the requirements of a pedestrian navigation system. Such systems typically estimate the distance traveled using a step counting approach, and use the gyro to keep track of heading [6]. For this calculation, it will be assumed that the pedestrian is traveling along a straight line at a constant speed, and the speed is accurately known. The maximum integrated angle error  $\Delta \theta$  over the integration time  $\tau$  for a given distance error  $\Delta p$  is then

|                       | InvenSense                          |                               |

|-----------------------|-------------------------------------|-------------------------------|

|                       | MPU-6050 [3]                        | This work                     |

| Angle random walk     | $5 \text{ mdeg/s}/\sqrt{\text{Hz}}$ | 14 mdeg/s/ $\sqrt{\text{Hz}}$ |

| Max rate (min. ARW)   | 250 deg/s                           | > 1000 deg/s (estimated)      |

| Bandwidth             | $\geq$ 250 Hz                       | 50 Hz (estimated)             |

| Bias stability @ 1 hr |                                     | 5.9 deg/hr                    |

| Scale factor accuracy | ±3%                                 | ±10ppm                        |

| Power/axis            | 2.9 mW                              | $< 150 \ \mu W$ (estimated)   |

| Table 1.2: | Comparison | of this | work to | existing | products. |

|------------|------------|---------|---------|----------|-----------|

|            |            |         |         | 0        | 1         |

given by the following expression, where *V* is the average velocity:

ī.

$$\Delta \theta = \frac{1}{\tau} \sin^{-1} \frac{\Delta p}{\tau V} \tag{1.1}$$

If the system goal is to achieve an rms error of 10 m over a 10 minute integration time, and the average walking speed is assumed to be 4 km/h, the maximum allowable Allan deviation is 5.2 deg/hr for  $\tau = 10$  minutes.

#### Scale factor accuracy

Scale factor accuracy is another critical specification for a pedestrian navigation system. Scale factor errors cause a static heading error after every change of direction; such heading errors can result in significant position errors as the pedestrian travels. Because these errors are input-dependent, it is not possible to estimate their magnitude unless some statistics of the input signal are known or assumed.

A rough estimate of the required scale factor accuracy may be obtained by assuming the trip starts with a turn (for example, 180°) and calculating the distance error at the end of the dead reckoning navigation time. In the following equation  $\theta_i$  is the initial turn angle,  $\Delta p$  is the required distance error, V is the velocity, and  $\tau$  is the dead reckoning time.

$$SF = \frac{1}{\theta_i} \sin^{-1} \frac{\Delta p}{\tau V} \tag{1.2}$$

For example, if the walking speed *V* is 4 km/h and the dead reckoning time  $\tau$  is 10 minutes, achieving  $\Delta p = 1$ m distance error after an  $\theta_i = 180^\circ$  initial turn requires scale factor accuracy of 480 ppm or less.

#### Gyroscope bandwidth

Insufficient bandwidth results in a gain error: some energy at higher frequencies is removed by the bandlimiting process. The gyroscope bandwidth should be set to limit the error to some acceptable bound for the fastest possible input signal; in order to do this, the characteristics of the input signal must first be established. In the case of pedestrian navigation, the input signal depends on the biomechanics of the human body. Considerable work exists in this field. In [9], head motion characteristics are measured during various activities, including the measurement of angular rates and accelerations.

A quantitative bandwidth estimate may be obtained by using the measured maximum angular rate and acceleration and assuming some shape for the rate pulse. A convenient pulse shape is a Gaussian pulse, where *T* is the pulse width:

$$\dot{\theta}(t) = \dot{\theta}_{pk} \exp\left[-\pi \left(\frac{t}{T}\right)^2\right]$$

(1.3)

The angular acceleration is then:

$$\ddot{\theta}(t) = \frac{-2\pi\dot{\theta}_{pk}t}{T^2} \exp\left[\frac{-\pi t^2}{T^2}\right]$$

(1.4)

The peak angular acceleration occurs at  $t = \pm T/\sqrt{2\pi}$ ; substituting this into (1.4) and rearranging the resulting expression yields

$$T = \sqrt{\frac{2\pi}{e}} \frac{\dot{\theta}_{pk}}{\ddot{\theta}_{pk}} \tag{1.5}$$

The Fourier transform of (1.3) is

$$\dot{\Theta}(f) = \dot{\theta}_{pk} T \exp[-\pi f^2 T^2]$$

(1.6)

The energy in a given bandwidth is therefore

$$E(B) = \int_{-B}^{B} |\dot{\Theta}(f)|^2 df = \frac{\theta_{pk}^2 T}{\sqrt{2}} \operatorname{erf}(BT\sqrt{2\pi})$$

(1.7)

The gain error as a function of bandwidth is

$$\varepsilon = 1 - \sqrt{\frac{E(B)}{E(\infty)}} = 1 - \sqrt{\operatorname{erf}(BT\sqrt{2\pi})}$$

(1.8)

From [9] we obtain  $\dot{\theta}_{pk} = 1.85 \text{ rad/s}$  and  $\ddot{\theta}_{pk} = 151 \text{ rad/s}^2$  for the activity with the maximum  $\ddot{\theta}_{pk}/\dot{\theta}_{pk}$  ratio, corresponding to the minimum pulse width *T* and thus maximum bandwidth. For a 50 ppm gain error, the estimated minimum bandwidth is 60 Hz.

#### **Power consumption**

Gyroscopes generally have high power consumption. As seen from table 1.1, low-power commercial gyroscopes consume 3 to 5 mW per axis. A typical smartphone is rated for up to 300 hours of standby time with a 9 Wh battery [10], corresponding to an average standby power consumption of about 30 mW. An always-on gyroscope consuming 10 mW would decrease battery life by at least 30%.

A reasonable upper bound for the power consumption of an always-on gyroscope is 2.5% of the total standby power, corresponding to 250  $\mu$ W per axis. As will be shown, frequency-modulated operation can readily achieve this goal.

## Chapter 2

## **Frequency-Modulated Gyroscopes**

### 2.1 Background

MEMS gyroscopes measure angular rate by employing the Coriolis effect in a microfabricated vibratory transducer. The most basic transducer comprises a proof mass, sensing and actuation electrodes, and a spring system that allows the proof mass to move along two independent, orthogonal axes. In the conventional amplitude-modulated operating mode, one of the axes of the transducer is driven at its natural frequency. When angular rate is applied, the direction of vibration is maintained relative to an inertial reference frame. From the rotating reference frame of the gyroscope, this appears as a transfer of vibrational energy from the drive axis to the sense axis, with the magnitude of this effect proportional to the applied angular rate.

The most common readout scheme used with MEMS transducers is the open-loop rate mode. In this scheme, the drive axis oscillation is maintained at a constant amplitude. As the gyroscope is rotated, some of this energy is again transferred to the sense axis, where it is dissipated by the sense axis damper. At the same time, the amplitude control loop replenishes the drive axis energy to maintain a constant amplitude. As a result, the sense axis displacement is proportional to the applied angular rate. This mode has the advantage of being simple to implement, and is commonly used with consumer-grade gyroscopes.

A related mode is force-rebalance (or force-feedback); it is commonly used in higherperformance parts [11]. The force-rebalance mode uses a feedback loop to null out the sense mode oscillation, and measures the force required to do so. This force is proportional to the angular rate. Force-rebalance operation eliminates scale factor dependence on quality factor and frequency split, allowing mode-matched operation and thus reducing power consumption [12]. However, the inherent complexity and the difficulty of ensuring loop stability with the presence of parasitic modes makes this approach relatively unattractive for low-power, inexpensive consumer-grade parts. Furthermore, achieving accurate scale factor still requires precise control of the feedback forces, which is quite difficult.

The design of the transducer structure is generally dictated by the operating mode to be used. Open-loop gyroscopes use a highly-asymmetric transducer, with a relatively large split between the natural frequencies of the drive and sense axes (typically 1-2 kHz). This significantly increases the power consumption of the gyroscope, since the Coriolis force drives the sense axis far from its natural resonance frequency, and the signal is therefore greatly attenuated. However, the transducer has a relatively flat frequency response in this region, and scale factor sensitivity to the frequency split and the quality factor is reduced. Effectively, a large frequency split allows acceptable scale factor stability at the cost of higher power consumption. Frequency-modulated operation allows this trade-off to be completely avoided.

### 2.2 Quadrature FM operation

The most basic FM gyroscope operating mode is known as quadrature FM (QFM) [7,13]. In this mode, both axes are driven by oscillator loops at their natural frequency. A tuning loop adjusts the resonant frequency of one or both axes to ensure a  $90^{\circ}$  phase relationship between their displacements. In the case where the displacements of the two axes are equal, the proof mass orbits in a circle.

In the presence of angular rate, the proof mass continues to orbit undisturbed at its natural frequency (in an inertial frame of reference). However, since the pickoff electrodes are rotating relative to the orbit, the observed frequency shifts by the angular rate with a unity scale factor. In effect, this operating mode is similar to whole-angle readout, where the scale factor is also unity. However, unlike the whole-angle operating mode, the proof mass displacement envelope is rotationally symmetric, obviating the need for a complex controller that must keep track of the proof mass oscillation angle.

In a practical MEMS gyroscope, the scale factor is not quite unity because of the angular gain factor. This factor occurs because some vibrating parts of the gyroscope (such as the springs) are constrained to move along only one mechanical axis, and therefore cannot generate Coriolis force. Because the angular gain factor is set by mass ratios, it is very stable and does not drift significantly over time.

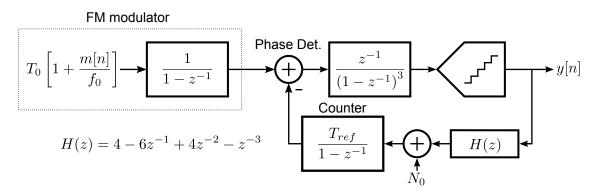

Figure 2.1: Lissajous FM gyroscope block diagram. The red outline shows the readout circuits that will be analyzed in the rest of this work.

One major difficulty with the QFM operating mode is that any drift of the center frequency is directly added to the measured rate output. Because the resonant frequency is typically thousands of times larger than even the full-scale angular rate, even very small frequency shifts result in extremely large rate offsets. While offset drift may be significantly reduced by employing two counter-rotating proof masses (with opposite rate sensitivity), the achievable temperature tracking accuracy is not sufficient to make this approach competitive with AM gyroscopes [13].

### 2.3 Lissajous FM operation

One way to avoid the issue of QFM frequency drift is to periodically reverse the direction of the orbit. This may be done by periodically switching the phase shift between the X and Y oscillations from  $+90^{\circ}$  to  $-90^{\circ}$ , and vice versa. However, the lock time of the tuning loop would severely restrict the gyroscope bandwidth.

Periodic mode reversal may also be accomplished simply by allowing the two gyroscope axes to run at slightly different frequencies; the proof mass now follows a Lissajous curve instead of a circle [7]. This is mathematically equivalent to using a ramp as the setpoint for the QFM tuning loop, where the slope of the ramp is equal to the difference of the axis frequencies. As a result, the rate is modulated by a sinusoid with a frequency equal to the difference between the oscillation frequencies of the two axes. In the case of the ideal gyroscope transducer with no cross-coupling between the two axes, the axis frequencies are given by the following expression, where  $\omega_{ox}$  and  $\omega_{oy}$  are the natural axis frequencies of the X and Y axes,  $v_{xa}$  and  $v_{ya}$  are the velocity amplitudes of each axis,  $\alpha_z$  is the angular gain factor of the transducer,  $\Omega_z$  is the input angular rate, and  $\Delta\phi_{xy}(t)=(\omega_{ox}-\omega_{oy})t.$

$$\dot{\phi_x}(t) = \omega_{ox} - \frac{v_{ya}}{v_{xa}} \alpha_z \Omega_z(t) \sin \Delta \phi_{xy}(t)$$

(2.1)

$$\dot{\phi_y}(t) = \omega_{oy} - \frac{v_{xa}}{v_{ya}} \alpha_z \Omega_z(t) \sin \Delta \phi_{xy}(t)$$

(2.2)

Modulating the rate sensitivity causes the rate signal to move from DC to the frequency of modulation; this is identical to the chopper stabilization technique commonly used in precision amplifiers. As a result, the gyroscope is made insensitive to slow variations in the natural frequency of the transducer, as might result from temperature fluctuations and other drift sources. Furthermore, the scale factor of the gyroscope depends only on the angular gain factor  $\alpha_z$  (a stable, dimensionless parameter set by the transducer geometry) and the velocity amplitude ratios  $v_{xa}/v_{ya}$  and  $v_{ya}/v_{xa}$ . If the demodulated X and Y channel outputs are summed, the sensitivity to velocity amplitude mismatch is greatly reduced due to the reciprocal summation of the two amplitude ratios. Suppose  $v_{ya} = (1 + \varepsilon)v_{xa}$ . The scale factor error is then given by:

$$\frac{\frac{1}{1+\varepsilon} + \frac{1+\varepsilon}{1}}{2} - 1 = \frac{\varepsilon^2}{2(1+\varepsilon)} \approx \frac{\varepsilon^2}{2}$$

(2.3)

The above result illustrates a significant advantage of the LFM gyroscope: the scale factor accuracy is decoupled from the gain accuracy of the circuits. For example, a relatively large mismatch of 0.5% between the X and Y axis velocities results in a scale factor error of only 12 ppm.

LFM operation presents a trade-off between split frequency, bandwidth, and power. Because the rate signal is amplitude-modulated onto a sinusoidal carrier at the split frequency, the gyroscope bandwidth is always less than the split frequency. At the same time, increasing the split frequency requires decreasing the amount of white phase noise for a given resolution spec, increasing power. A somewhat similar trade-off is seen in AM gyroscopes: as the split frequency is increased, usable bandwidth and power also increase. However, unlike the AM gyroscope, LFM operation has excellent scale factor stability even with relatively low split frequencies, allowing power consumption to be significantly reduced if the required bandwidth is relatively small. A disadvantage of LFM operation is the possibility of aliasing in the presence of signal components that exceed the split frequency. For example, a sinusoidal rate input at exactly the split frequency will appear as a DC rate offset at the output of the gyroscope.

## 2.4 LFM gyroscope error sources

In order to start the design of the readout circuits, it is necessary to first understand the error sources that limit the ultimate performance of the LFM gyroscope system.

#### Transducer errors

Numerous errors arise from imperfections in the micromechanical gyroscope transducer. These errors arise from manufacturing imperfections and can also be due to the geometry of the structure. Gyroscope errors can be categorized into errors affecting a single axis, and errors that introduce parasitic coupling between the two axes.

Errors that affect a single axis can affect the effective mass, stiffness, and quality factor. Errors in the effective mass and stiffness affect the resonant frequency of the axis and the gyroscope split. LFM operation depends on these errors being reasonably well-controlled in order to ensure a predictable distribution of split frequencies, but they do not otherwise affect the performance of the gyroscope. Variations in quality factor affect the scale factor of the gyroscope in open-loop AM modes. In the LFM mode, the oscillator circuit cancels the axis losses, and variations in the quality factor do not contribute to scale factor errors.

Most errors in the gyroscope arise from parasitic coupling between the two axes. The parasitic coupling errors are generally classified into cross-stiffness and cross-damping terms. These arise from different mechanical sources. Because they have different phase shifts, they contribute different errors to the gyroscope. When these errors are included, the LFM equations assume the following form, where  $\Omega_c$  terms represent cross-damping and  $\Omega_k$  terms represent cross-stiffness errors [7].

$$\dot{\phi_x}(t) = \omega_{ox} - \frac{v_{ya}}{v_{xa}} (\alpha_z \Omega_z(t) - \Omega_{c,yx}) \sin \Delta \phi_{xy}(t) + \Omega_{k,yx} \frac{v_{ya}}{v_{xa}} \cos \Delta \phi_{xy}(t)$$

(2.4)

$$\dot{\phi_y}(t) = \omega_{oy} - \frac{v_{xa}}{v_{ya}} (\alpha_z \Omega_z(t) + \Omega_{c,xy}) \sin \Delta \phi_{xy}(t) + \Omega_{k,xy} \frac{v_{xa}}{v_{ya}} \cos \Delta \phi_{xy}(t)$$

(2.5)

#### Anisostiffness errors

Anisostiffness, commonly known as quadrature, is an important source of bias instability in gyroscopes. In the most general case, this error source includes any force that is applied to an axis of a gyroscope in proportion to the displacement of the other axis. In the linear model of the gyroscope, anisostiffness refers to the off-diagonal spring terms coupling the two nominally orthogonal axes. Linear errors may be modeled as misalignment of the spring axes relative to the electrodes [7]. In the linear case, the cross-stiffness terms are symmetric.

This error may arise from non-linear sources. One such source is related to spring non-idealities. In the ideal case, gyroscope springs allow motion along only one axis, and do not cause displacement in the perpendicular direction. However, all MEMS flexures require at least some displacement in the orthogonal direction in order to function. While the use of folded flexures and symmetric layout minimizes these effects, any remaining asymmetry (e.g. due to fabrication mismatches) can nevertheless result in motion along the orthogonal direction. This is an entirely nonlinear and non-reciprocal effect, and symmetry of the stiffness matrix is therefore not assured.

The effect of quadrature error in the AM gyroscope is significant motion on the sense axis in phase with the displacement of the drive axis. This motion appears in quadrature with the Coriolis signal, and is nominally rejected by the demodulator. Likewise, in the LFM gyroscope, quadrature error results in a tone at the split frequency that is in quadrature with the rate signal. A large quadrature error uses up dynamic range in the analog front-end, potentially creating linearity issues and/or increasing the noise floor. While quadrature error may be rejected by synchronous demodulation, any phase errors in the demodulator reference can cause it to add to the gyroscope's zero rate output. If the amount of quadrature error or the phase error drifts over time, this can contribute a large bias drift component.

As an example, suppose the gyroscope has  $1000^{\circ}$ /s of quadrature error, and the phase detector is accurate to within 0.1°; both of these values are typical for consumergrade gyroscopes. The zero-rate output is then  $1.75^{\circ}$ /s. If the phase detector error drifts by 1%, the zero-rate output will shift by 63°/hr. Clearly, a large quadrature error makes it very difficult to achieve good bias stability.

#### Anisodamping errors

Anisodamping is an error source that includes any force applied to a gyro axis in proportion to the velocity of the other axis. In the conventional operating mode, it is indistinguishable from applied angular rate. Like anisostiffness, it may be modeled linearly as a misalignment of the damper axes with the electrodes, in which case the cross-damping terms are symmetric ( $\Omega_{c,xy} = \Omega_{c,yx}$ ) and will be cancelled when the FM-demodulated X and Y signals are added together. However, this error source may also arise from nonlinear effects (such as squeeze and slide film damping of an asymmetric structure), in which case it is not necessarily reciprocal and will not be completely cancelled. Maximizing the quality factor of the structure minimizes all damping terms and is the best defense against this error.

#### **Oscillator errors**

The oscillator loops contribute several errors to the LFM gyroscope, including noise, amplitude mismatch, and amplitude ripple.

#### **Oscillator** noise

An excellent analysis of Pierce oscillator noise can be found in [14]. The phase noise of a linear Pierce oscillator is given by:

$$S_{\phi_n^2}(\Delta\omega) = rac{(1+\gamma)kT\omega}{2QE_m\Delta\omega^2}$$

In the above equation,  $\gamma$  is a constant that represents the excess noise contributed by the sustaining circuit (if  $\gamma = 0$ , only the transducer thermal noise is included).  $\omega$  represents the oscillation angular frequency, and  $\Delta \omega$  represents the frequency offset. Q is the quality factor of the transducer, and  $E_m$  is the mechanical energy present in the resonator.

The noise spectrum predicted by the above expression has a  $1/f^2$  shape around the oscillation frequency. The spectrum of the frequency noise is therefore white.

In the presence of transducer or circuit nonlinearity, it is possible for the flicker noise of the oscillator transistors to be upconverted to the oscillation frequency, changing the phase noise shape to a  $1/f^3$  shape near the carrier. After FM demodulation, this error will appear as 1/f frequency noise. In practice, the oscillator should be designed to be sufficiently linear to keep the flicker noise corner far below the LFM split frequency. This is not difficult in the case of high-Q resonators, since only a very small drive signal is needed to sustain oscillation. It is important to note that the corner of the upconverted flicker noise is independent of the flicker noise corner in the baseband, and is determined entirely by the average value of the impulse sensitivity function. In a perfectly linear oscillator, the ISF has no DC component and 1/f upconversion does not occur [14, 15].

#### Amplitude mismatch

As mentioned previously, amplitude mismatch between the X and Y axes can cause a scale factor error. Because of reciprocal summation, the matching requirements are

Figure 2.2: Layout of quad-mass gyroscope transducer.

quite modest: 0.5% matching is sufficient to ensure scale factor stability on the order of 12 ppm. While much better matching is generally possible for monolithic circuit components, the error budget must also include the parasitic capacitances at the sense terminals of the transducer. If these parasitics cannot be accurately matched, a feedback amplifier can be used to neutralize them.

#### Amplitude ripple

In LFM operation, the gyro alternates between QFM (90° phase shift) and whole angle (0° phase shift) operating modes. When the proof mass moves in a straight line, applied angular rate will attempt to transfer energy between the axes, resulting in sinusoidal amplitude variations as the phase shift between the axes varies. This effect is mostly suppressed by the amplitude regulator in the oscillator loop, though some residual amplitude variation will remain. Even in the absence of angular rate, quadrature and cross-damping errors will cause amplitude ripple to be present. The FM demodulator must reject this error source to avoid degrading scale factor and bias stability.

## 2.5 Test setup

### Transducer

A quad-mass architecture [16] was chosen to implement the LFM gyroscope transducer. The layout is shown in fig. 2.2. The quad-mass layout is fully symmetric, thus maximiz-

Figure 2.3: Desired mode shapes of gyroscope transducer.

Figure 2.4: Scanning electron microscope photograph of fabricated structure.

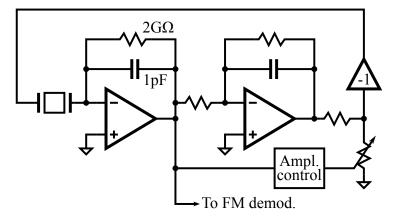

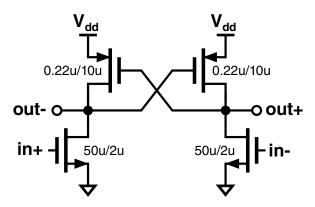

Figure 2.5: Oscillator differential half-circuit.

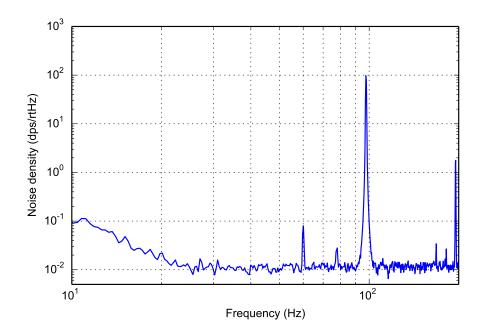

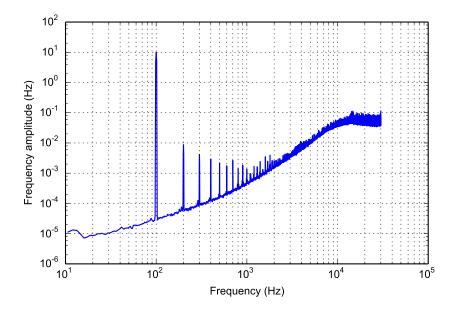

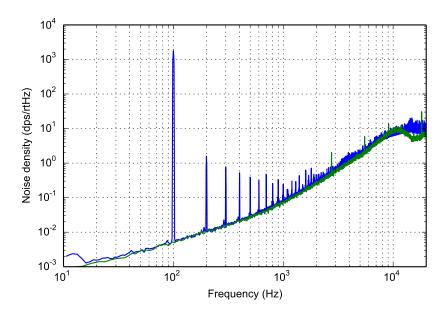

Figure 2.6: Measured frequency noise spectral density for single oscillator channel.

ing quality factor and vibration rejection for both axes. Levers and coupling springs are used to move unwanted modes to higher frequencies. Differential drive and sense electrodes select the desired mode and help reject vibration and other common-mode disturbances. Folded springs are used to connect the proof mass to the frames; the springs are designed to minimize force transfer to the other mode, thus reducing quadrature. The transducer is designed to prevent the transfer of package stress to the springs by using a single anchor point for each frame. This reduces a significant source of drift and helps improve vibration rejection. The transducer was fabricated in the epi-seal HDXI process. An SEM micrograph is shown in fig. 2.4.

#### Sustaining loop

The sustaining loop was implemented as a Pierce oscillator, a low-power and highperformance circuit topology commonly used with crystals [14]. The circuit was implemented using op-amps and discrete components on a printed circuit board. Figure 2.5 shows the schematic of a differential half-circuit of one oscillator channel. The sense port of the MEMS transducer is connected to an active integrator. A very large resistor is used for DC biasing. By maintaining the sense terminal at a virtual ground, the active integrator ensures high linearity and maintains a more accurate phase shift and high CMRR by neutralizing parasitic capacitance at the sense node. The latter advantage is particularly important in the case of a PCB implementation, since the parasitic capacitances are both large and poorly controlled, resulting in significant mismatch between the two differential electrodes.

The output of the first integrator stage is fed to a second active integrator. It is then attenuated by a variable attenuator, inverted, and fed to the gyroscope drive port. An amplitude control loop adjusts the loop gain to maintain a constant envelope at the output of the first integrator. This output is also fed to the frequency demodulator. Figure 2.6 shows the measured noise spectral density for a single oscillator channel. Note that the frequency spectrum is generally white, implying a  $1/f^2$  phase noise shape; this is the expected behavior. The vertical axis is scaled assuming  $\alpha_z = 1$ . The large tone at 100 Hz is the zero-rate output; the tone near 200 Hz is a harmonic of the split frequency, and is likely due to parasitic frequency modulation due to electrode nonlinearity. The tone at 60 Hz is a result of power line interference coupled into the sense node.

#### 2.6 Sensor model

This scope of this work is limited to the design of readout circuits for the LFM gyroscope. The included circuits are delineated in figure 2.1; the transducer and the oscillator are excluded. In order to account for the errors introduced by the excluded components, it is necessary to create a model of the oscillator output.

The following expressions give the time-domain displacement of the X and Y channels in LFM operation. Each signal consists of a cosine with amplitude A and an AM component  $x_{am}(t)$  or  $y_{am}(t)$ . The AM component represents the residual amplitude ripple due to finite amplitude control gain, as well as the AM component of amplitude noise. The argument of each cosine is comprised of a frequency modulation term (the integral), as well as a phase noise term  $\phi_n(t)$ . The arguments of the integrals represent the instantaneous angular frequencies, and are given by equations (2.4) and (2.5).

$$x(t) = [1 + x_{am}(t)]A_x \cos\left[\int_0^t \dot{\phi_x}(\tau) \, d\tau + \phi_{nx}(t)\right]$$

(2.6)

$$y(t) = [1 + y_{am}(t)]A_y \cos\left[\int_0^t \dot{\phi_y}(\tau) \, d\tau + \phi_{ny}(t)\right]$$

(2.7)

Angular rate is extracted by FM demodulating x(t) and y(t) to extract  $\dot{\phi}_x$ ,  $\dot{\phi}_y$  and the phase reference  $\Delta \phi_{xy}$ , and then synchronously demodulating the sine term from  $\dot{\phi}_x$  and  $\dot{\phi}_y$  to extract the angular rate  $\Omega_z$ . The FM demodulator must be designed to reject the AM terms, since they do not contain usable information and can corrupt the FM measurements.

As mentioned previously, the oscillator circuit noise and transducer noise consist of  $1/f^2$  phase noise, which is equivalent to white FM noise. Note that only the tank current has this noise shape, whereas noise taken from the output of the oscillator will have an approximately white spectrum near the frequency of oscillation. For minimum noise, the FM demodulator signal chain should be fed directly from the transducer.

The FM components of the signal consist of the desired LFM tone, as well as crossdamping and quadrature components. For the purposes of error analysis, it will be assumed that the frequency split is 100 Hz, the quadrature offset is 150 deg/s, and the cross-damping offset is 1 deg/s. These values are close to the measured parameters of the test device.

## Chapter 3

## **Frequency-to-Digital Conversion**

### 3.1 Introduction

The frequency demodulator is a key part of any frequency-modulated gyroscope. This block largely determines the resolution, scale factor stability, bias stability, and power consumption of the sensor.

Frequency modulation was first used in early communication systems. Early highpower transmitters could not be keyed on and off, and frequency-shift keying was used to transmit telegraphic signals; the selectivity of the receiver converted the FSK signal to an amplitude-modulated one. Later work employed FM in an attempt to reduce the bandwidth required by an AM transmission by reducing the peak frequency deviation. Carson's analysis of FM [17] showed this to be impossible, and for over a decade FM was considered to be vastly inferior to AM in every respect. Armstrong [18] was the first to recognize the SNR advantages of wideband FM for high-fidelity broadcasting and to develop a practical FM system.

In the process of frequency modulation, a modulating signal m(t) modulates the instantaneous frequency of a sinusoid:

$$x(t) = A\cos\left(\omega_0 t + \int_0^t m(\tau) \, d\tau\right)$$

Note that the amplitude of m(t) has units of frequency. The maximum value of |m(t)| is known as the frequency deviation. In wideband FM, the frequency deviation is larger than the bandwidth of m(t). For example, broadcast FM uses 75 kHz of deviation to modulate an audio signal with a bandwidth of 15 kHz. However, FM gyroscopes are narrowband FM systems: a full-scale 2000 deg/s rate input corresponds to a deviation

of 5.6 Hz, while the bandwidth of the modulating signal is typically at least 50 Hz. In general, the bandwidth of m(t) is much smaller than the center frequency  $\omega_0$ , and the maximum deviation is also assumed to be small compared to  $\omega_0$ .

In general, the amplitude *A* is not constant. For example, any white noise that is added to an FM signal by the processing electronics may be decomposed into an amplitude and a phase noise component. In FM gyroscopes, input rate and quadrature errors cause amplitude ripple, which may not be completely suppressed by the amplitude control loop. These effects can cause significant errors in the demodulator.

## 3.2 **Performance requirements**

The performance specifications for the FM demodulator are driven by the gyroscope performance performance objectives in Table 1.2. In the LFM mode, the amplitude-modulated rate signal is located in the band  $f_{split} \pm BW$ . In order to avoid aliasing, the split frequency must be somewhat larger than the highest-frequency input component; if the input has a bandwidth of 60 Hz, the split frequency should be 100 Hz or more.<sup>1</sup>

The angle random walk is determined by the noise of the oscillator circuit, the comparator (if any), and the FM demodulator (fig. 2.1). If the 10 mdeg/s/ $\sqrt{\text{Hz}}$  budget is split equally between the front-end and the FM demodulator, the in-band noise density at the output of the FM demodulator must be  $10\text{mdeg/s}/\sqrt{\text{Hz}}/(2 \cdot 360^\circ) = 13.9$  $\mu\text{Hz}/\sqrt{\text{Hz}}$ ; for a 60 Hz gyro bandwidth, the integrated in-band rms noise is 152  $\mu\text{Hz}$ . The factor of two in the denominator accounts for the noise allocation between the comparator and the oscillator, and for the two AM sidebands; each of these contribute a factor of  $\sqrt{2}$ .

The maximum angular rate is determined by the input range of the FM demodulator. To accommodate 2000 deg/s, the demodulator must allow an input deviation of  $\pm 5.6$  Hz, plus some additional range to allow for quadrature errors and center frequency drift.

Scale factor accuracy considerations require the FM readout scheme to be ratiometric to an reference clock frequency, either by directly using the reference clock for frequency measurement, or via calibration. As will be shown later, the LFM gyroscope is capable of achieving sub-10 ppm scale factor stability; the FM demodulator must not degrade this.

<sup>&</sup>lt;sup>1</sup>Theoretically, the minimum split frequency is equal to the bandwidth. In practice, some margin must be allowed for frequency drift, filter roll-off, and to prevent aliasing of out-of-band signals.

## 3.3 FM demodulation methods

#### Slope and quadrature detection

The slope detector is the oldest and the simplest approach for FM demodulation. The basic idea is to use a tuned circuit (or a digital filter) to convert frequency variation into amplitude variation. A high-Q resonant circuit is commonly used to maximize the change in amplitude for a given frequency shift.

The quadrature detector is a variation of this concept, and is the most common analog FM demodulator. The FM signal is fed through a resonant network tuned to the center frequency. This produces a nominally  $90^{\circ}$  phase shift, which varies with frequency. The resulting phase-shifted signal is mixed with the original, producing an output approximately proportional to the input frequency deviation. For a given Q, this topology is more linear than the simple slope detector.

These approaches have numerous drawbacks. While they can provide adequate performance for radio receivers using wideband FM, the achievable resolution, scale factor accuracy, and linearity are limited by analog imperfections. Because the achievable filter slope is limited by component quality factors, slope detectors are poorly suited for systems with small frequency deviation, such as gyroscopes. Finally, these circuits are not especially suitable for monolithic integration due to the required high-Q components.

#### Analog phase-locked loops

A phase-locked loop is another option for FM demodulation. An analog PLL uses a feedback loop to keep a voltage-controlled oscillator in a defined phase relationship (generally either 0° or 90°) with the input signal. The VCO control voltage is thus proportional to the frequency deviation from a center frequency. Adjusting the VCO offset and gain allows the PLL to have either high frequency resolution or a wide input frequency range. However, the offset stability, scale factor accuracy, and linearity are set by the VCO voltage-to-frequency characteristic, and are subject to analog errors. In an analog implementation, it is difficult to make these parameters good enough for a gyroscope readout system.

Another disadvantage of the PLL is its limited frequency response. A common "rule of thumb" states that the loop bandwidth of a PLL can be no more than 10% of the input frequency. This implies that for a 30 kHz gyroscope, the maximum bandwidth is on the order of 3 kHz. While this is not a problem in itself, this does imply that the loop has

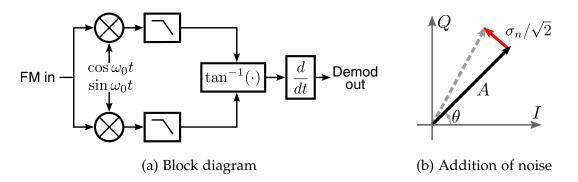

Figure 3.1: Arctangent-based FM demodulator.

significant phase shift even at a typical LFM split frequency of 200 Hz, which changes with component drift, input frequency, and split frequency. This presents difficulties in recovering the phase of the LFM demodulation reference, and can significantly limit achievable quadrature rejection, resulting in poor bias stability.

#### **DSP-based demodulators**

Any of the preceding techniques can be implemented in the digital domain. DSP-based implementations of FM demodulators have significant advantages. They can benefit greatly from the precise timing reference available in most digital systems, eliminating many error sources that limit the performance of analog implementations. A DSP-based PLL is a particularly attractive implementation. The frequency and scale factor accuracy depend only on the accuracy of the reference clock source. Such an architecture is employed in laboratory instruments such as the Zurich Instruments HF2LI lock-in amplifier [19].

To analyze the noise performance of this structure, it is convenient to use the demodulator shown in Figure 3.1a as a model. This is a commonly used structure for DSP-based FM demodulators [20]; it is also quite similar to the front-end of more complicated structures, such as the Costas loop<sup>2</sup> [21]. The FM signal is first quadrature downconverted to either an IF frequency, or to DC. An arctangent function converts the I and Q components to a phase angle, and a derivative operation converts the phase angle to an angular frequency. White noise added to the signal splits equally between amplitude and phase components. Figure 3.1b shows this graphically: the signal is a

<sup>&</sup>lt;sup>2</sup>The Costas loop was originally used to recover a phase reference from a suppressed-carrier AM signal by employing the AM rejection property of this structure.

vector of length *A*, and the added phase noise consists a vector representing a zeromean random variable with standard deviation  $\sigma_n/\sqrt{2}$ . Unlike oscillator phase noise, this added noise is not accumulated and disturbs the phase in a zero-mean fashion.

For a signal with amplitude *A* and white noise density  $\sigma_n$ , the phase disturbance due to noise is (assuming  $\sigma_n \ll A$ ):

$$\sigma_{\theta} = \tan^{-1} \left( \frac{\sigma_n}{\sqrt{2}A} \right) \approx \frac{\sigma_n}{\sqrt{2}A} \tag{3.1}$$

After the derivative operation, the frequency noise density is given by

$$\sigma_f(f) = \frac{\sigma_\theta}{2\pi} 2\pi f = \frac{\sigma_n f}{\sqrt{2}A}$$

(3.2)

Because the FM demodulator effectively differentiates its input, white phase noise at the input of the FM demodulator generates  $f^2$  noise at the output. To determine the required data converter SNR, the total frequency noise power in the signal bandwidth *B* must first be found:

$$P_n(\sigma_n) = \int_{f_c - B}^{f_c + B} \sigma_f(f)^2 \, df = \left[\frac{B^3}{3} + Bf_c^2\right] \frac{\sigma_n^2}{A^2} \tag{3.3}$$

By equating this expression with the desired total frequency noise specification, the required  $\sigma_n$  can be determined:

$$P_n(\sigma_{n,req}) = \sigma_{f,req}^2 B \tag{3.4}$$

$$\sigma_{n,req}^2 = \frac{\sigma_{f,req}^2 A^2}{B^2/3 + f_c^2}$$

(3.5)

The required SNR is then given by the following expression. Note that the bandwidth of interest is twice the gyro bandwidth, since both AM sidebands must be considered.

SNR =

$$10 \log \frac{2A^2}{\sigma_{n,req}^2 2B} = 10 \log \frac{B^2/3 + f_c^2}{\sigma_{f,req}^2 B}$$

(3.6)

To achieve a 5 mdeg/s/ $\sqrt{Hz}$  (13.9  $\mu Hz/\sqrt{Hz}$ ) ARW spec with a gyroscope bandwidth of 60 Hz and a 100 Hz frequency split requires an in-band SNR of 120 dB. It is very difficult to meet such a specification with a sub-1mW power budget. This approach is thus unattractive for low-power, high-resolution gyroscope systems.

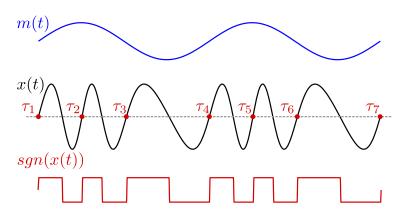

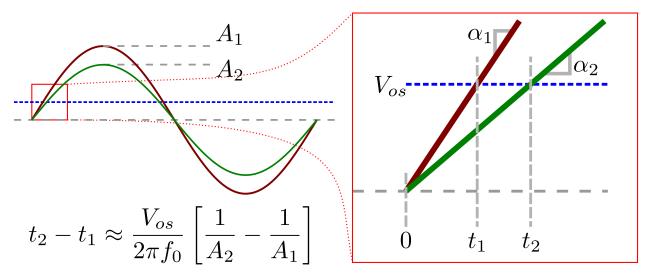

Figure 3.2: FM demodulation by period measurement. The topmost line is the modulating signal; the middle line is the frequency modulated sinusoid. The bottom line shows the signal after the limiter.

#### Period measurement techniques

FM can also be demodulated by directly measuring the period of the incoming signal. In most cases, the signal is first converted to a square wave with a continuous-time comparator (limiter); limiting the signal yields well-defined, fast edges that can be processed by digital circuits. The time interval between edges is then measured; this measurement is typically quantized to some time increment. This quantization noise is first-order shaped.

Consider a frequency-modulated signal x(t) with a modulating signal m(t):

$$x(t) = A\cos\left(2\pi f_0 t + 2\pi \int_0^t m(t) \, dt\right)$$

(3.7)

When x(t) is processed by a comparator, the resulting square wave signal can be equivalently represented as a sequence of time points  $\tau_0, \tau_1 \dots \tau_n$ , where each such point represents a rising edge. This process is shown graphically in figure 3.2. Assuming both the comparator and the signal are free of noise and offsets, each such point  $\tau_i$  can be found from the relation:

$$2\pi f_0 \tau_i + 2\pi \int_0^{\tau_i} m(t) \, dt = 2\pi i \tag{3.8}$$

Note that the left side is simply the argument (i.e. phase) of the cosine in (3.7). The comparator produces a rising edge whenever the phase is equal to multiple of  $2\pi$ .

Assuming that  $|m(t)| \ll f_0$ , that the bandwidth of m(t) is much smaller than  $f_0$ , and

that m(t) has no DC component<sup>3</sup>, equation (3.8) can be approximately solved for  $\tau_i$  to yield the following expression:

$$\tau_i \approx \frac{i}{f_0} + \sum_{k=0}^{i} \frac{m(k/f_0)}{f_0^2}$$

(3.9)

This expression assumes the maximum frequency deviation |m(t)| is small enough that the frequency is approximately constant and the effects of nonuniform sampling can be ignored. In gyroscopes, this is a very good approximation, since a full-scale 2500 deg/s input is only a 230 ppm frequency shift with a 30 kHz transducer.

In order to measure the period, consecutive time points are differenced. In practice, each measured  $\tau_i$  is corrupted by added edge jitter e[i], which comprises quantization noise and various sources of random noise. The resulting expression for the period is thus:

$$\tau_i - \tau_{i-1} = \frac{1}{f_0} \left[ 1 + \frac{m(i/f_0)}{f_0} \right] + e[i] - e[i-1]$$

(3.10)

To recover the original m(t), this expression is multiplied by  $f_0^2$  to transform the period measurement back to a frequency:

$$f_0^2 \cdot (\tau_i - \tau_{i-1}) = f_0 + m(i/f_0) + f_0^2 \cdot (e[i] - e[i-1])$$

(3.11)

The edge jitter undergoes first-order noise shaping (differentiation). This may be understood intuitively by considering that frequency is the derivative of phase; edge jitter is essentially phase noise, so it is differentiated by an FM demodulator.

#### **Frequency counter**

The simplest period measurement architecture is a time-to-digital converter based on a counter. A digital counter fed with a reference clock continuously counts up; the input edge samples the value of the counter, and the previous such sample is subtracted. The resulting value represents the period of the input signal quantized to the period of the reference clock.

Despite its simplicity, this topology has several interesting features. There are no analog errors: the accuracy is set solely by the accuracy of the reference clock. Because of the noise shaping characteristic, a counter is a simple, accurate, and highly precise

<sup>&</sup>lt;sup>3</sup>A DC component of m(t) is simply a static frequency shift, and can be lumped into  $f_0$  without loss of generality.

instrument for frequency measurement when a low sample rate is sufficient. However, achieving high resolution requires extremely high clock speeds.

The FM noise density due to quantization jitter with quantization step  $\Delta$  can be found using (3.11):

$$\sigma_f^2(f) = f_0^4 \frac{\Delta^2}{12(f_0/2)} \left| 1 - e^{-j2\pi f/f_0} \right|^2 = \frac{2}{3} f_0^3 \Delta^2 \sin^2(\pi f/f_0)$$

(3.12)

Achieving 5 mdeg/s/ $\sqrt{\text{Hz}}$  in a 60 Hz bandwidth with a 100 Hz split requires  $\Delta \leq 221 \text{ ps}$ , necessitating a clock frequency of at least 4.53 GHz. Operating at such a high clock frequency requires a large amount of power, likely well over 7 mW in a 0.18  $\mu$ m process [22].

#### Time to digital converters

A time-to-digital converter (TDC) can have higher resolution than a counter for a given reference clock frequency. TDCs are commonly implemented with a delay-locked loop (DLL) architecture. A voltage-controlled delay line is locked to the period of a reference clock. The multiple clock phases are then used to measure the time between two events. The most basic TDC is a thermometer-like design: a number of flip-flops are used to measure the position of a "start" pulse within the delay line. This limits resolution to the delay of a single delay element. Another common TDC architecture is the vernier TDC, which uses two delay lines with a different delay step to achieve a resolution equal to the delay difference. The trade-off is a larger number of stages for a given delay range. Numerous other architectures can also be used, such as gated ring oscillators [23,24].

In order to measure the period of a 30 kHz gyro, a TDC must be combined with a counter to extend its measurement range. This presents a direct tradeoff between counter clock frequency and the required number of elements in the TDC. For example, to meet the previously calculated 221 ps resolution requirement with a 10 MHz counter frequency and a thermometer TDC would require 450 delay elements and associated decoding logic. This would consume significant area. A higher reference clock frequency would reduce the number of delay elements, at the expense of higher counter power.

Another problem is linearity. While the DLL architecture ensures that the total delay of the delay line is always constant, mismatch between individual elements results in nonlinearity. This necessitates complex calibration schemes and generally limits the achievable performance. As a result of these limitations, TDCs tend to have fairly high power consumption – generally on the order of 5 to 50 mW.

### Sigma-delta frequency to digital converters

The sigma-delta frequency-to-digital converter (FDC) takes advantage of the inherent oversampling of the modulating signal present in most FM schemes. For a typical MEMS gyroscope with a resonant frequency of 30 kHz, the sensor bandwidth is generally between 20 Hz and 2 kHz, corresponding to an oversampling ratio between 15 and 1500. Oversampling is commonly used in sigma-delta ADCs to achieve very high resolution with a coarse (often 1-bit) converter. The  $\Sigma\Delta$ FDC realizes the same basic idea in an FM demodulator, by employing noise shaping to improve the resolution of a counter with a relatively low reference clock frequency.

This architecture has numerous advantages over other FM demodulator architectures. The feedback path is entirely digital; therefore, the scale factor accuracy and offset stability of the demodulator depend only on the accuracy of the reference clock. The signal transfer function is simply a delay; unlike a conventional PLL, the signal is not subject to bandwidth limitation and phase distortion. Analog imperfections in the charge pump can affect noise shaping performance, but can not introduce frequency offset or DC gain errors. Noise added by the analog integrator undergoes second-order shaping, and its impact is negligible.

Because of its significant advantages, this is the architecture chosen for this work, and it is fully analyzed in the remainder of this chapter.

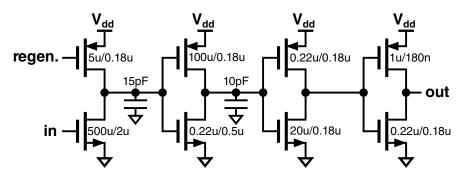

# 3.4 Comparator design

Many FM demodulation methods rely on comparators to convert a sinusoidal FM signal to a square wave. Such comparators are not clocked, and are sometimes referred to as limiters. Limiting an FM signal removes the amplitude modulation components and allows FM signals to be processed by digital logic gates. In a modern CMOS process, digital gates have delays on the order of picoseconds, consume very little power, and have very low phase noise when supplied with fast edges and a clean power supply rail. Even a minimum-size inverter has a negligible noise contribution, provided that the input rise time is sufficiently fast.

The front-end comparator performs the function of an LNA in an RF front-end: it provides sufficient gain to render the noise of any subsequent stages negligible. Without a comparator, significant power must be expended at every stage in the analog chain to maintain a sufficiently high signal-to-noise ratio. For example, the Zurich Instruments HF2LI requires an analog front-end with over 100 dB of dynamic range and a 14-bit, 210

MS/s analog-to-digital converter in order to achieve frequency resolution corresponding to about 0.005 mdeg/s/ $\sqrt{\text{Hz}}$  [19].

A major advantage of comparator-based systems is that the gain is not restricted by the supply voltage. In a linear system, the gain of the front-end amplifiers must be kept low enough to keep the signal swing within the supply voltage rails. This restriction is not present in a comparator-based system. For example, a comparator producing a 30 ps rise time with a 30 kHz signal on a 1.8 V supply generates the same slope as a sinusoidal signal with an amplitude of 318 kV. For a given noise voltage, such a signal is far less susceptible to jitter from subsequent stages than a lower-amplitude one, allowing the use of relatively noisy, low-power, minimum-size logic gates for further processing.

Another advantage of comparators is that they can use dynamic operation to greatly reduce power for a given noise specification. A linear class A amplifier must use a constant bias current to achieve a certain level of noise. A well-designed comparator operates similarly to a class C amplifier, and needs current only during the time it is transitioning. Since comparators generally have a fast transition time, dynamic operation can reduce power by an order of magnitude compared to a linear amplifier designed for the same noise specification.

Unfortunately, comparators also have some disadvantages. A fundamental problem is noise folding. This is easily seen intuitively: a very fast, high-gain comparator only looks at the signal during a very brief time window; as a result, it is sensitive to even very brief noise impulses, which can cause it to transition either before or after the true zero crossing. Another way to understand noise folding is to view the operation of the comparator as a sampling process. The comparator produces sharp edges at the zero crossings of the input. If the rise time is very fast, this waveform can be losslessly represented by a discrete-time sequence of timestamps sampled at a constant phase interval  $\pi$ , if both the rising and the falling edges are considered. If the effects of nonuniform sampling are neglected, the sampling rate is  $2f_0$ , where  $f_0$  is the oscillation frequency of the gyroscope. Thus, any noise components above  $f_s/2 = f_0$  will be folded down into the signal band.

Noise folding is less pronounced in communications systems, where the channel SNR is low and tuned circuits reject out-of-band noise. However, it can be a significant limitation in high-resolution FM systems, and proper measures must be taken to prevent it.

Figure 3.3: Simplified equivalent comparator model.

### **Comparator model**

Analyzing the noise of a comparator is a difficult non-linear problem. The circuit may be analyzed numerically, using a periodic steady-state (PSS) solver, such as SpectreRF. While this is indispensable for final design verification, accurate PSS analysis of a comparator requires an extremely large number of harmonics to be computed. For example, the signals inside a comparator with a 1 ns rise time will contain frequencies up to approximately 400 MHz. With a 30 kHz input signal, over 13,000 harmonics must be computed to obtain an accurate result, making the simulation very slow. Therefore, it is highly desirable to obtain a simple analytical model that can guide the design process in the correct direction and provide intuition.

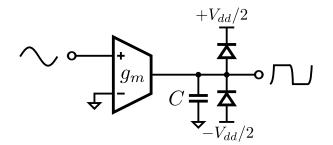

The idealized model of a comparator is shown in Fig. 3.3. The comparator is modeled as a  $g_m$ -C integrator with ideal diodes for voltage limiting. For simplicity, a bipolar supply is defined; the comparator switches at the input zero crossing and has a positive gain. The input in the vicinity of the zero crossing is assumed to be a straight line, which is an accurate approximation for sinusoidal inputs.

It is important to note that the actual comparator circuit is implemented differently. Nearly all comparator topologies operate dynamically: the  $g_m$  device is only active during the time the output is transitioning, and does not consume static current. Because the output slope in a well-designed comparator is generally much higher than the input slope, and the transistor is in saturation during the first half of the transition, the  $g_m$  can be assumed to be roughly constant during the switching event.

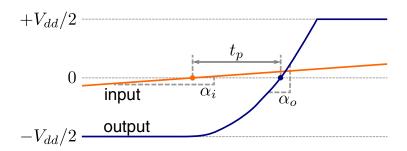

The switching waveforms for this comparator model are shown in Fig. 3.4. The switching behavior starts when the input crosses zero and the comparator begins integrating the input, with the output initially starting at  $-V_{dd}/2$ . The switching process is considered complete when the output crosses zero. It is useful to define a propagation delay  $t_p$  as the time between the input and output zero crossings. The input and output

Figure 3.4: Switching waveforms for comparator model.

slopes at the point of the zero crossing will be denoted by  $\alpha_i$  and  $\alpha_o$ . The comparator gain-bandwidth product is  $\omega_0 = g_m/C$ .

With an input  $x(t) = \alpha_i t$ , the output is:

$$y(t) = \frac{V_{dd}}{2} - \frac{1}{C} \int_0^t g_m x(t) \, dt = -\frac{V_{dd}}{2} + \omega_0 \alpha_i \frac{t^2}{2}.$$

(3.13)

The propagation delay  $t_p$  can be found from the relation y(t) = 0:

$$t_p = \sqrt{\frac{V_{dd}}{\omega_0 \alpha_i}}.$$

(3.14)

By differentiating y(t) at  $t = t_p$ , we obtain  $\alpha_o = \sqrt{\omega_0 \alpha_i V_{dd}}$ . By solving this expression for  $\omega_0$ , we obtain:

$$\omega_0 = \frac{\alpha_o^2}{\alpha_i V_{dd}}.\tag{3.15}$$

The preceding equation allows the required gain-bandwidth product to be found for a given output slope. In further analysis, the comparator is specified using only  $\alpha_i$ ,  $\alpha_o$ , and  $V_{dd}$ , making the analysis easier to relate to simulated or measured behavior.

### Noise analysis

The comparator operates as a periodic integrator. Because of the clipping diodes, the output saturates after the edge transition.<sup>4</sup> Once the output is clipped, its value is independent of the preceding integrator state. Thus, the integrator state is effectively reset after each comparison. From [25], if a source of current noise with spectral density  $S_i(f)$

<sup>&</sup>lt;sup>4</sup>In the actual circuit, clipping occurs when the output approaches the supply rails. Diodes are used to simulate this behavior in an otherwise linear model.