# Room temperature approach to fully transparent, alloxide thin-film transistors

Thomas Rembert Ali Javey, Ed.

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2015-147 http://www.eecs.berkeley.edu/Pubs/TechRpts/2015/EECS-2015-147.html

May 16, 2015

Copyright © 2015, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Low temperature approach to fully transparent, all-oxide, flexible ZnO transistors

by Thomas Rembert

# **Research Project**

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, in partial satisfaction of the requirements for the degree of **Master of Science**, **Plan II**.

Approval for the Report and Comprehensive Examination:

Professor Ali Javey

Research Advisor

5/15/2015

(Date)

\*\*\*\*\*

Professor Vivek Subramanian

Second Reader

5/15/2015

(Date)

### **Table of Contents:**

| Chapter 1 – Introduction and Motivation               | 3  |

|-------------------------------------------------------|----|

| Chapter 2 – Experimental Results                      | 7  |

| 2.1 – Fabrication Process and Cathodic Arc Deposition | 7  |

| 2.2 - ZnO Film Characterization                       | 10 |

| 2.3 – TFT Performance                                 | 13 |

| 2.4 – TFT Bending                                     | 19 |

| 2.5 – NMOS Inverter                                   | 21 |

| Chapter 3 – Conclusion and Future Work                | 24 |

| Acknowledgements                                      | 26 |

| References                                            | 27 |

#### **Chapter 1 – Introduction and Motivation**

The exploration and understanding of electronic material properties and how they can be implemented into a usable form for electronics is the driving force behind developing new types of devices and electronic systems. Within these new types of electronic systems, transparent and flexible electronics represent two emerging fields that have gathered much attention.<sup>1,2</sup> For example, transparent electronics have applications in the area of fully transparent displays. While there are separate research efforts on the development of light-emitting materials needed for displays,<sup>3</sup> there is still a need to develop the underlying electronics to make the system entirely transparent—namely, the pixel-driving transistors and the digital circuits needed for pixel addressing and additional logic. Development of the latter, digital logic circuits, can lead to large scale logic and digital processors that can be integrated into almost any transparent electronic system and maintain full transparency. In the realm of flexible electronics, the focus is on the ability to integrate electronics into existing flexible systems. The application area for this technology quite diverse, ranging from conformal coverage of contoured shapes, such as prosthetic hands, to wearable or implantable health monitoring sensors.<sup>4-7</sup> In order to realize these types of devices, effort must be put into developing mechanically robust electronic materials whose device performance is immune to bending and stretching. Additionally, any fabrication steps involving the flexible substrate material need to be done at a temperature low enough to not damage the substrate, which greatly limits the deposition temperatures for polymer-based substrates. Alternatively, devices can be

fabricated on a rigid substrate then mechanically transferred to a flexible substrate to avoid temperature incompatibility. While each of these areas currently has their own areas of utilization, integrating these two areas of transparent and flexible electronics will lead to even more applications that were previously unable to be realized by the two areas alone. Unfortunately, many of these complex systems cannot be realized without one of the basic building blocks—in this case, the thin-film transistor (TFT).

Original development of the TFT was achieved over thirty years ago using silicon. 8,9 Due to its understood electrical characteristics, deposition, and fabrication processes, silicon-based TFTs using amorphous silicon and polysilicon were first demonstrated.<sup>8,9</sup> However, as our discovery and understanding of new material systems and deposition methods have progressed, the development of TFTs has grown to include alternative thin-film materials, each with their tradeoffs amongst the other material systems. The most widely explored TFT materials after silicon include organic semiconductors and carbon nanotubes (CNTs). Tremendous effort has been put into these material systems, enabling the realization of large-scale flexible circuits for display and sensor applications.<sup>8–15</sup> Organic semiconductors are excellent TFT candidates due to their inherent mechanical flexibility and low deposition temperature. 11,12 Unfortunately, these organic semiconductors are usually extremely air-sensitive, causing rapid device performance degradation. 11 However, organic semiconductors continually prove to be a viable TFT system as advancements have been made in device air stability. 16 CNTs are also an excellent TFT material platform due to their mechanical flexibility, low deposition temperature, and high mobility. 13-15

While CNTs exhibit excellent scaling properties towards large digital circuits in the form of nanotube growth and solution drop-casting, <sup>13,14</sup> these devices are entirely p-type. While much effort has been put into type conversion in CNT systems, <sup>17,18</sup> there is still no reliable method creating n-type CNT devices, and thus CMOS logic, on a large scale. However, despite the challenges in type conversion, CNTs have proven to be an extremely promising material for future digital circuit applications. Additionally, both organic semiconductors and CNTs can be readily dispersed into solutions, which shows promise for ink-jet and roll-to-roll printing of electronic systems. <sup>19–21</sup>

More recently, research efforts have increased in the TFT material of semiconducting metal oxides. The family of semiconducting post-transition metal oxides (ZnO, In<sub>2</sub>O<sub>3</sub>, InZnO, InGaZnO, etc.) offers an additional platform with wide energy band gaps for optical transparency over the full visible range, room temperature deposition (both solution-based and physical vapor deposition techniques) for plastic compatibility, and electrical properties suitable for TFTs for transparent, flexible, and bio-related applications.<sup>7,22–25</sup> However, many existing fabrication techniques for these oxide TFTs, while they are being deposited at room temperature, require higher temperature annealing steps to prime the oxide (i.e., improve crystallinity, improve stoichiometry, or calcination of solutions) for TFT use or to improve the device performance to an acceptable level.<sup>25–29</sup> Unfortunately, the use of higher temperatures for processing and device improvement can severely limit substrate compatibility and present challenges for integration with other components.

In order to retain a wide range of substrate choices without sacrificing device performance, a low temperature approach to fabrication is needed. In this work, we demonstrate fully transparent all-oxide based ZnO TFTs with low operation voltages fabricated using a room temperature plasma deposition method with no post-processing annealing and a maximum device processing temperature of 110 °C.

#### Chapter 2 – Experimental Results

As previously stated, this work consists of transparent all-oxide based ZnO TFTs fabricated on flexible substrates using a room temperature plasma deposition method. With the fabrication techniques and deposition process presented in this report, we seek to propose a new method for low temperature fabrication of flexible oxide-based devices and reaffirm that ZnO is a viable metal oxide material to use for future transparent and flexible electronic systems.

#### 2.1 – Fabrication Process and Cathodic Arc Deposition

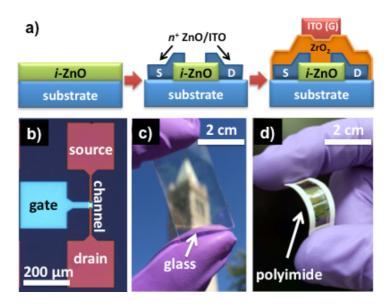

The schematic process flow for the fabrication of top-gated ZnO TFTs is shown in Fig. 1a. ZnO TFTs are fabricated on three different substrates: i) a reference silicon wafer substrate with a 50 nm thick thermal oxide (Fig. 1b), ii) transparent alkali-free borosilicate glass (Fig. 1c), iii) flexible polyimide foil (Fig. 1d).

**Fig. 1: Process Flow and Images of Devices** (a) Process schematics of ZnO TFT fabrication. (b) Optical microscope image of finished device on silicon. (c)

Photograph of finished device array on glass slide. (d) Photograph of finished devices on freestanding polyimide foil bent between fingers.

Substrates are cleaned with acetone and isopropyl alcohol and blown dry with nitrogen. Substrates are then loaded into a cathodic arc vacuum deposition chamber and pumped down to ~5×10<sup>-6</sup> Torr for ZnO deposition. The filtered cathodic arc deposition for zinc oxide has originally been developed for the deposition of transparent conducing oxide films.<sup>30</sup> It has been shown that this deposition technology is similar to pulsed laser deposition (PLD) as it produced a flux of energetic ions. The typical Zn ion energy is 36 eV<sup>31</sup> which leads to atomic scale heat right at the film growth region without imposing a large heat load to the substrate. Additionally, in contrast to magnetron sputtering, negative oxygen ions are not accelerated to very high energies of several 100 eV because the arc operates at low arc voltage (the potential difference between anode and cathode is less than 40 V).

The arc deposition system can be described as follows. Cathodic arc deposition (Fig. 2a) uses a relatively low DC voltage to trigger and sustain a metal arc plasma, where the discharge current of about 100 A is concentrated in non-stationary cathode spots.<sup>32</sup> In contrast to the former work on AZO, here we use a pure (undoped) zinc (99.99%) cathode. It is surrounded by an annular grounded anode body. A permanent ring magnet is placed at the bottom part of the cathode cone: its purpose is to steer the moving arc spots around the cathode, enabling efficient material use and spreading of the heat load on the cathode. The zinc plasma generated at cathode spots streams

away from the cathode into the macroparticle filter coil. The purpose of the coil is to guide the plasma to the substrate, which is not in line-of-sight with the cathode. In doing so, the plasma particles (electrons and ions) are separated from the microscopic but relatively massive zinc droplets, also known as "macroparticles." The coil is made of hollow, water-cooled copper tubing. It operates at a constant current of 400 A, producing a magnetic field of the order of 100 mT (more about plasma guiding and macroparticle removal can be found in Ref. 32. Zn ions react with oxygen to form a ZnO film on the near-room-temperature substrate surface. 30 nm of ZnO is deposited as the active TFT channel material onto the substrates placed 12.5 cm away from the exit of the plasma macroparticle filter coil in a 5 mTorr O<sub>2</sub>/Ar ambient (O<sub>2</sub> 60 sccm, Ar 20 sccm unless otherwise stated).

Photolithography is used to define patterns for the source and drain electrodes via lift-off. Source and drain pads consist of 40 nm thick degenerately doped ZnO deposited at lower O<sub>2</sub> partial pressure partial pressure than the TFT channel ZnO (5 mTorr, O<sub>2</sub> 20 sccm, Ar 20 sccm, room temperature), followed by 30 nm of indium tin oxide (ITO) sputtered in a 7 mTorr Ar ambient also at room temperature. A second photolithography step is performed to define the ZnO channel region of the transistors by etching in hydrochloric acid (HCl 1% for 1 s). In this process, the top ITO film on the source and drain serves as an etch stop barrier for the underlying ZnO, as the etch rate for ITO in HCl is much lower than that of ZnO.<sup>33</sup> A 20 nm thick ZrO<sub>2</sub> top gate oxide is deposited by atomic layer deposition (ALD) at a maximum temperature of 110 °C, and subsequently patterned by photolithography. The same ITO sputtering

and lift-off process is then used to define the top gate contact. Fig. 1b, c, and d show optical images of the devices completed on silicon, alkali-free glass, and free-standing polyimide foils, respectively.

#### 2.2 – ZnO Film Characterization

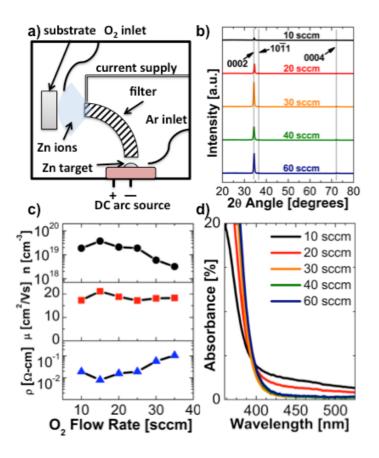

We first explore the material properties of ZnO thin films deposited by cathodic arc. X-ray diffraction spectra (XRD) of the ZnO films as function of  $O_2$  flow rate are shown in Fig. 2b. All films exhibit a polycrystalline hexagonal wurtzite structure and  $\{0002\}$  texture in agreement with literature.<sup>34</sup> The c-axis lattice constant extracted from the 0002 peak at 34.8° is 5.2 Å in good agreement with values for sputtered ZnO films.<sup>35</sup> No peaks corresponding to metallic Zn inclusions are detected. Estimating the grain size from the 0002 peak positions  $2\Theta$  and full-with half-max widths  $\beta$  using the Scherrer equation,  $D(2\Theta) = K \cdot \lambda/\beta \cdot \cos 2\Theta$ , assuming a crystallite shape factor K = 0.9 and substituting  $\lambda = 0.154$  nm for Cu K $\alpha$  radiation, yield grain sizes between  $\sim 17-23$  nm.<sup>36</sup>

Fig. 2: Cathodic Arc Setup and ZnO Film Characterization (a) Schematic of cathodic arc deposition chamber. The permanent magnet is denoted in red. (b) XRD pattern for ZnO film and varying  $O_2$  flow rates. (c) Electron concentration (n), Hall mobility ( $\mu$ ), and resistivity ( $\rho$ ) as a function of  $O_2$  flow rate. (d) Dependence of optical absorption with  $O_2$  flow rate.

For transistor application, it is important to precisely control the conductivity of the ZnO channel to enable gate control. The carrier concentration in the ZnO film can be tuned by adjusting the O<sub>2</sub> flow rate during deposition as the carrier concentration of intrinsic ZnO films directly correlates with the number of oxygen vacancies.<sup>34,37</sup> We choose to keep the Ar flow rate and the total deposition pressure constant (20 sccm and 5 mTorr, respectively) and vary the O<sub>2</sub> flow rate from 10 sccm to 35 sccm

to modulate the electron concentration in the ZnO. As the O<sub>2</sub> flow rate is increased from 15 secm to 35 secm, the electron concentration drops from the mid 10<sup>19</sup> cm<sup>-3</sup> to the low 10<sup>18</sup> cm<sup>-3</sup> (Fig. 2c), while the Hall mobility (second panel in Fig. 2c) essentially remains constant between 17.3-21.2 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, with the highest recorded mobility of 21.1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> being deposited at an O<sub>2</sub> flow rate of 15 secm. For the higher O<sub>2</sub> flow rates above 35 secm, the resistivity of the films (third panel in Fig. 2c) increases too rapidly, rendering Hall mobility determination unreliable. However, the ZnO mobilities reported here appear to be some of the highest Hall mobilities reported for room-temperature-deposited thin film oxides for TFTs reported in literature, showing that cathodic arc deposition is reliable for producing high quality ZnO films.<sup>7,23–25,38,39</sup>

Fig. 2d shows the optical absorption of the ZnO films as a function of wavelength and O<sub>2</sub> flow rate. As the O<sub>2</sub> flow rate increases from 10 to 30 sccm, the sub bandgap absorption at wavelengths longer than 400 nm caused by metallic Zn clusters embedded in the film decreases significantly and the films become more transparent. The absorbance of 30 nm ZnO films in this spectral range drops below 2%. In parallel, the absorption edge at wavelength shorter than 400 nm shifts longer wavelengths for increasing O<sub>2</sub> flow rates due to a reduction of the Burstein-Moss shift with decreasing electron concentration consistent with our Hall measurement results. Absorbance data at 60 sccm O<sub>2</sub>, which is the O<sub>2</sub> flow rate used for the ZnO TFT channel, is practically identical to the data at 40 sccm although film resistivity further increases.

#### 2.3 – TFT Performance

We now focus on ZnO TFT device performance. The TFT device architecture implemented is a top gate structure consisting entirely of transparent oxides. We fabricated the all-oxide fully transparent devices on alkali-free glass substrates. Fig. 3a shows the I<sub>DS</sub>-V<sub>GS</sub> transfer curve of a TFT device on alkali-free glass with channel width and length of 100  $\mu m,$  operated at  $V_{GS}$  =  $\pm 3~V$  and  $V_{DS}$  = 3 V, resulting in an on/off current ratio of  $\sim 10^5$ . The subthreshold slope (SS) is calculated from a linear fit (dotted line) to be SS = 204 mV/dec. The threshold voltage of  $V_t = 0.36 \text{ V}$  was extracted from a linear fit of I<sub>DS</sub> 1/2 vs. V<sub>GS</sub>. The saturation mobility was determined to be  $\mu_{sat} = 4.5 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , calculated using the peak value of the slope of the  $I_{DS}^{1/2}$  vs.  $V_{GS}$  plot under  $V_{DS} = 3$  V saturation operation, assuming a relative permittivity ( $\varepsilon_r$ ) of our ALD ZrO<sub>2</sub> of  $\varepsilon_r$  = 12. Fig. 3b shows the I<sub>DS</sub>-V<sub>DS</sub> characteristic of the device, exhibiting typical square-law behavior and reaching an on-current of almost 40 nA/μm. These values compare well with the best reported oxide low temperature TFTs in literature with SS typically in the range of one hundred to a few hundreds of mV/dec and  $V_t$  less than 1  $V_{\cdot}^{\ 29,40-45}$

Fig. 3: TFT Performance  $I_{DS}$ - $V_{GS}$  and  $I_{DS}$ - $V_{GS}$  curves for W/L = 100  $\mu$ m/100  $\mu$ m device on (a, b) alkali-free glass and (c, d) polyimide. The arrows on the transfer curves indicate the direction of the double sweep measurement.

It should be noted that alkali-free glass is chosen due to impurities in other glasses, such as microscopy slides. We found that charged ions in the glass were causing a threshold voltage shift of our devices, so alkali-free glass was used to avoid this issue. Additionally, the off-current of our devices is comparable to those reported in literature, showing that the room-temperature process is able to produce devices with just as low of an off-current as compared to those with higher temperature processes. In terms of the saturation mobility, our lower values as compared to literature can be associated with interface states between the ZrO<sub>2</sub> gate oxide and ZnO channel overlap

capacitances between the gate and source/drain, which would cause some of the applied gate field to contribute to state filling and source/drain charges rather than channel inversion, as well as contact resistance effects. These effects can be combatted by annealing or plasma treatments for the oxide interfaces and improved alignment during fabrication for the overlap capacitances. Again, seeing that we are avoiding any higher temperature or post-annealing to improve the gate-channel interface, our future work will look into plasma treatment to enhance the ZrO<sub>2</sub>-ZnO interface.

The process was then ported to flexible polyimide foils. Polyimide resin was spun on a temporary silicon handling wafer and cured at 300°C for an hour before device fabrication. Fig. 3c shows the  $I_{DS}$ - $V_{GS}$  transfer curve of the ZnO TFT on polyimide with channel width and length of 100  $\mu$ m operated at  $V_{GS}$  =  $\pm 3$  V, exhibiting an on/off current ratio of almost  $10^5$ , with extracted subthreshold slope, threshold voltage, and saturation mobility of SS = 251 mV/dec,  $V_t$  = 1.2 V, and  $\mu_{sat}$  = 4.8 cm $^2$ V $^1$ s $^1$ , respectively. Fig. 3d shows the  $I_{DS}$ - $V_{DS}$  curves indicating expected square-law behavior with an on-current of again almost 40 nA/ $\mu$ m, thus reaching identical performance characteristics to the device on glass and with those reported in literature.

For each of the  $I_{DS}$ - $V_{GS}$  curves on the two substrates, the increase in off-current at low  $V_{GS}$  operation can be attributed to gate leakage resulting from both the thin 20 nm gate oxide and the source/drain to gate overlap. The value of the subthreshold slope

can also be restricted by trap states in the channel-oxide interface and series resistance effects from our ITO contacts to our ZnO channel. In this study, we choose to avoid higher temperature annealing steps to potentially reduce these effects, and the result is still acceptable TFT performance. The on/off ratio is  $10^5$ , whereas other studies report ratios as high as  $10^{8.40.41}$  This is because the devices are being operated at high operation voltages ( $V_{GS}$  and  $V_{DS} \geq 10$  V). While this on/off ratio is beneficial for display applications, our focus is on scalable TFTs for digital circuits, which would focus more on decreasing power consumption, requiring low voltage operation. Overall, the devices made on glass and polyimide show consistent, transferrable and reproducible behavior, suggesting this method to be a universally applicable technique for creating fully-transparent ZnO TFTs on a variety of substrates. Table I summarizes our results for the ZnO TFT on polyimide and compares this device to other high-performance oxide TFTs reported in literature.

| Material                               | ZnO*            | IGZO <sup>40</sup> | IGZO <sup>41</sup> | IGZO <sup>42</sup> |  |

|----------------------------------------|-----------------|--------------------|--------------------|--------------------|--|

| Dep. Method                            | CAD             | sputtering         | sol-gel            | sputtering         |  |

| On/off ratio                           | 10 <sup>5</sup> | <10 <sup>7</sup>   | 108                | <108               |  |

| V <sub>op</sub> [V]                    | ±3 V            | ±20 V              | ±10 V              | ±3 V               |  |

| SS [mV/dec]                            | 251             | 200                | 95.8               | 60                 |  |

| V <sub>t</sub> [V]                     | 1.2             | 2                  | 2.7                | 0.5                |  |

| μ <sub>sat</sub> [cm <sup>2</sup> /Vs] | 3.1             | 11                 | <10.5              | 10                 |  |

| W/L                                    | 100/100         | 400/100            | 100/10             | 1000/5             |  |

| Max T [°C]                             | 110             | RT                 | 150                | 325                |  |

| Transparent?                           | yes             | yes                | no                 | no                 |  |

| Flexible?                              | yes             | no                 | yes                | no                 |  |

| Material                               | ZnO*            | ZnO <sup>29</sup> | ZnO <sup>43</sup> | ZnO <sup>44</sup> | ZnO <sup>45</sup> |

|----------------------------------------|-----------------|-------------------|-------------------|-------------------|-------------------|

| Dep. Method                            | CAD             | PLD               | sol-gel           | sputtering        | solution          |

| On/off ratio                           | 10 <sup>5</sup> | >104              | 10 <sup>4</sup>   | >104              | >104              |

| Vop [V]                                | ±3 V            | -1 – 4 V          | 0 V – 3V          | ±1.5 V            | -1 V – 3 V        |

| SS [mV/dec]                            | 251             | 250               | ≈300 (est.)       | 180               | 250               |

| V <sub>t</sub> [V]                     | 1.2             | 2                 | 0.7 V             | 0.1               | 0.1               |

| μ <sub>sat</sub> [cm <sup>2</sup> /Vs] | 3.1             | 0.024             | 3.4               | 0.45              | 22.1              |

| W/L                                    | 100/100         | 2000/50           | 1500/100          | 500/50            | N/A               |

| Max T [°C]                             | 110             | 200               | 280               | 200               | 150               |

| Transparent?                           | yes             | yes               | no                | no                | no                |

| Flexible?                              | yes             | no                | yes               | yes               | no                |

Table I Comparison of this work to previous oxide TFTs. The upper portion compares this work to existing IGZO devices, and the lower portion compares this work to existing ZnO devices.  $V_{op}$  and W/L denote the operation voltage and size of the published device, respectively. Max T refers to the maximum temperature used during device processing, excluding substrate preparations.  $V_{op}$  refers to the gate

voltage range in which the device was reported, with the accompanying  $V_{DS}$  voltage being the highest of the reported  $V_{op}$  value. It should be noted that transparency is defined as all components of the transistor, including the gate and source/drain contacts, and the substrate altogether be transparent.

#### 2.4 – TFT Bending

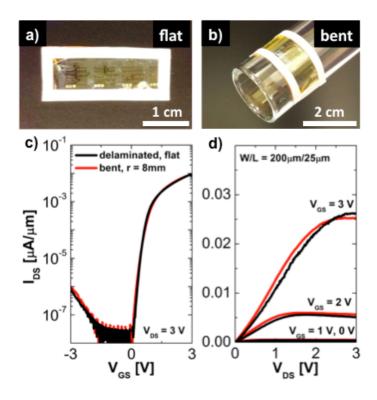

With the focus of these TFTs being on applications in flexible electronics, bending studies are performed to get an idea of the mechanical robustness and its effect on the electrical performance of the device. To remove the polyimide from the handle wafer, the polyimide was cut around the edges and then submerged into DI water for twenty minutes. Putting the sample in water promotes self-delamination of the polymer from the substrate. This process prevents the polyimide from needing to be manually peeled off, which induces strain on the polymer, potentially cracking the fabricated devices. Once the polyimide has delaminated, the polyimide foil is laid flat, and the devices are measured to quantify possible effects from internal strain relaxation during delamination. Bending tests are then performed by wrapping the polyimide around a test tube with  $r=8\,$  mm and measuring the device performance while bent.

Fig. 4 shows the  $I_{DS}$ - $V_{GS}$  and  $I_{DS}$ - $V_{DS}$  curves for the W/L = 200  $\mu$ m/25  $\mu$ m device before peeling off the handle wafer, after peeling off but before bending, and while bent. This device geometry is chosen for its higher output current values.

Fig. 4: Flexible TFT Bending Tests Images of the substrate while (a) flat and (b) bent around a test tube with r=8 mm. (c)  $I_{DS}$ - $V_{GS}$  and (d)  $I_{DS}$ - $V_{DS}$  curves for a device on free-standing polyimide with W/L = 200  $\mu$ m/25  $\mu$ m while flat (black) and bent at r=8 mm (red).

The on-current of the device drops almost one order of magnitude, which may be attributed to defects created in the device during strain relaxation of the polyimide film upon delamination. However, while bent at r=8 mm, there seems to be minimal change in device performance, proving that our ZnO TFT process is not only universally applicable to various substrates but also mechanically robust for flexible electronics.

#### 2.5 – NMOS Inverter

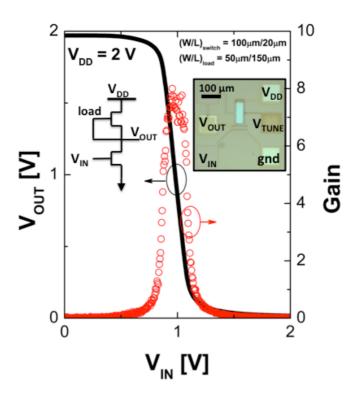

Furthermore, to demonstrate the applicability of this process to integrated logic systems, we have fabricated an inverter gate. Due to these devices being solely NMOS, the inverter was constructed with a depletion-mode transistor load rather than a PMOS device or resistor. Henceforth, the transistor in which the input (V<sub>IN</sub>) is passed is referred to as the "switching transistor," whearas the depletion-mode transistor, whose gate terminal is connected to the inverter output node (V<sub>OUT</sub>), is referred to as the "load transistor." The switching voltage of the inverter only depends on the V<sub>t</sub> of the switching transistor since the load transistor is acting as the resistive load, so the supply voltage to the inverter (V<sub>DD</sub>) was chosen to maximize the inverter noise margin. At an input voltage of  $V_{IN} = 0$  V, the switching transistor is off and has a much greater resistance than the load transistor. Thus, V<sub>OUT</sub> tends toward V<sub>DD</sub>, logic 1. Upon the onset of inversion, the switching transistor changes from the off-state to the on-state. As the switching transistor turns on, the resistance of the switching transistor becomes comparable to and then much less than that of the load transistor, causing V<sub>OUT</sub> to be pulled to ground, logic 0. Fig. 5 shows the transfer characteristics of the inverter at  $V_{DD} = 2 \text{ V}$  as well as an optical image and circuit schematic of the device. The contact pads have been labeled for convenience.

Fig. 5: NMOS Inverter Characteristics Voltage transfer curve ( $V_{OUT}$  vs.  $V_{IN}$ ) and dc gain ( $|\partial V_{OUT}/\partial V_{IN}|$ ) of the all-oxide NMOS inverter on polyimide under an operation voltage  $V_{DD}=2$  V. The switching transistor has a W/L = 100  $\mu$ m/20  $\mu$ m, and the depletion-mode load transistor has a W/L = 50  $\mu$ m/150  $\mu$ m. Inset is a schematic representing the device layout as well as the corresponding optical image of the device with labeled contacts.

It should be noted that the  $V_{TUNE}$  pad is available for  $V_t$  tuning of the load transistor but was not needed and therefore unused in this device. Also plotted is the dc gain of the inverter, defined as  $|\partial V_{OUT}/\partial V_{IN}|$ , which is shown to be ~8. Additionally, the noise margins of the inverter were extracted from the transfer curve by taking the maximum low input voltage  $(V_{LI})$  and the minimum high input voltage  $(V_{HI})$ , corresponding to the input voltages at unity gain, and the corresponding output values of those inputs,

$V_{HO}$  and  $V_{LO}$ , respectively. The high and low input noise margins are then defined as  $NM_H = V_{HO} - V_{HI} \ \text{and} \ NM_L = V_{LO} - V_{LI}, \ \text{respectively}. \ \text{The noise margin values were}$  calculated as  $NM_H = 0.36 V_{DD}$  and  $NM_L = 0.33 V_{DD}$ .

#### **Chapter 3 – Conclusion and Future Work**

In conclusion, we have implemented a cathodic arc deposition technique for room temperature deposition of intrinsic ZnO with electrical and optical quality suitable for transparent transistor applications. Additionally, we have shown this method of ZnO deposition to be usable in the fabrication of all-oxide fully transparent transistors on alkalki-free glass and polyimide with comparable or better electrical performance to alternative TFT platforms and existing oxide TFTs. We performed bending studies to show the mechanical robustness of our device structure to confirm its potential use on flexible substrates. Overall, we have demonstrated a low temperature fabrication process for ZnO TFTs enabling use in both fully transparent and flexible electronic applications.

In future work, we plan to port our process to other flexible plastics, such as PET or PEN. In doing so, we plan to improve device performance by creating better channel-oxide interfaces and decrease series resistance issues, which will help with the gate control of the device and boost device mobility and on/off ratio. Additionally, lower temperature gate oxides via ALD or solution processing will be explored to lower the processing temperature to its lowest limit of 90 °C, as determined by photolithography. Our group has been noted for its development of an e-skin platform based on carbon nanotubes<sup>5,6,14</sup>, which requires uniform TFTs for pixel backplane addressing as well as large-scale digital circuits for on-chip pixel addressing and simple data manipulation. We plan to continue developing our new ZnO platform for

future e-skin applications as an emerging flexible, large-scale circuit systems for backplanes and circuits on various flexible substrates.

## Acknowledgements

This research is supported in part by the Department of Energy Office of Science Graduate Fellowship Program (DOE SCGF), made possible in part by the American Recovery and Reinvestment Act of 2009, administered by ORISE-ORAU under contract no. DE-AC05-06OR23100. Acknowledgements to Joe Wallig for his help with the cathodic arc chamber maintenance should also be extended.

#### References

- (1) Thomas, G. Materials Science: Invisible Circuits. *Nature* **1997**, *389*, 907–908.

- (2) Wager, J. F. Transparent Electronics. *Science* **2003**, *300*, 1245–1246.

- (3) Muller, C. D.; Falcou, A.; Reckefuss, N.; Rojahn, M.; Wiederhirn, V.; Rudati, P.; Frohne, H.; Nuyken, O.; Becker, H.; Meerholz, K. Multi-Colour Organic Light-Emitting Displays by Solution Processing. *Nature* 2003, 421, 829–833.

- (4) Takahashi, T.; Takei, K.; Gillies, A. G.; Fearing, R. S.; Javey, A. Carbon Nanotube Active-Matrix Backplanes for Conformal Electronics and Sensors. *Nano Lett.* 2011, 11, 5408–5413.

- (5) Takei, K.; Takahashi, T.; Ho, J. C.; Ko, H.; Gillies, A. G.; Leu, P. W.; Fearing, R. S.; Javey, A. Nanowire Active-Matrix Circuitry for Low-Voltage Macroscale Artificial Skin. *Nat. Mater.* 2010, 9, 821–826.

- (6) Wang, C.; Hwang, D.; Yu, Z.; Takei, K.; Park, J.; Chen, T.; Ma, B.; Javey, A.

User-Interactive Electronic Skin for Instantaneous Pressure Visualization. *Nat. Mater.* 2013, *12*, 899–904.

- (7) Dagdeviren, C.; Hwang, S.-W.; Su, Y.; Kim, S.; Cheng, H.; Gur, O.; Haney, R.; Omenetto, F. G.; Huang, Y.; Rogers, J. A. Transient, Biocompatible Electronics and Energy Harvesters Based on ZnO. *Small* **2013**, *9*, 3398–3404.

- (8) Le Comber, P. G.; Spear, W. E.; Ghaith, A. Amorphous-Silicon Field-Effect Device and Possible Application. *Electron. Lett.* **1979**, *15*, 179.

- (9) Brody, T. P. The Thin Film transistor—A Late Flowering Bloom. *IEEE Trans*. *Electron Devices* **1984**, *31*, 1614–1628.

- (10) Yang, C.-S.; Smith, L. L.; Arthur, C. B.; Parsons, G. N. Stability of Low-Temperature Amorphous Silicon Thin Film Transistors Formed on Glass and Transparent Plastic Substrates. J. Vac. Sci. Technol. B 2000, 18, 683–689.

- (11) Dimitrakopoulos, C. d.; Malenfant, P. r. l. Organic Thin Film Transistors for Large Area Electronics. *Adv. Mater.* **2002**, *14*, 99–117.

- (12) Klauk, H.; Gundlach, D. J.; Nichols, J. .; Jackson, T. N. Pentacene Organic Thin-Film Transistors for Circuit and Display Applications. *IEEE Trans*. *Electron Devices* **1999**, *46*, 1258–1263.

- (13) Cao, Q.; Kim, H.; Pimparkar, N.; Kulkarni, J. P.; Wang, C.; Shim, M.; Roy, K.; Alam, M. A.; Rogers, J. A. Medium-Scale Carbon Nanotube Thin-Film Integrated Circuits on Flexible Plastic Substrates. *Nature* **2008**, *454*, 495–500.

- (14) Wang, C.; Chien, J.-C.; Takei, K.; Takahashi, T.; Nah, J.; Niknejad, A. M.;

Javey, A. Extremely Bendable, High-Performance Integrated Circuits Using

Semiconducting Carbon Nanotube Networks for Digital, Analog, and

Radio-Frequency Applications. *Nano Lett.* 2012, 12, 1527–1533.

- (15) Lee, C. W.; Weng, C.-H.; Wei, L.; Chen, Y.; Chan-Park, M. B.; Tsai, C.-H.; Leou, K.-C.; Poa, C. H. P.; Wang, J.; Li, L.-J. Toward High-Performance Solution-Processed Carbon Nanotube Network Transistors by Removing Nanotube Bundles. *J. Phys. Chem. C* **2008**, *112*, 12089–12091.

- Głowacki, E. D.; Irimia-Vladu, M.; Kaltenbrunner, M.; Gsiorowski, J.; White,

M. S.; Monkowius, U.; Romanazzi, G.; Suranna, G. P.; Mastrorilli, P.; Sekitani,

T.; et al. Hydrogen-Bonded Semiconducting Pigments for Air-Stable

Field-Effect Transistors. Adv. Mater. 2013, 25, 1563–1569.

- (17) Cheon, J.; Choi, S.; Heo, Y. J.; Lee, S. H.; Lim, J.; Park, Y. J. Fabrication of

-Type CNT Field-Effect Transistor Using Energy Band Engineering Layer

Between CNT and Electrode. *IEEE Electron Device Lett.* 2013, 34, 1436–1438.

- (18) Ha, T.-J.; Chen, K.; Chuang, S.; Yu, K. M.; Kiriya, D.; Javey, A. Highly

Uniform and Stable N-Type Carbon Nanotube Transistors by Using Positively

Charged Silicon Nitride Thin Films. *Nano Lett.* **2014**.

- (19) Subramanian, V.; Chang, P. C.; Lee, J. B.; Molesa, S. E.; Volkman, S. K.

Printed Organic Transistors for Ultra-Low-Cost RFID Applications. *IEEE Trans. Compon. Packag. Technol.* 2005, 28, 742–747.

- (20) Beecher, P.; Servati, P.; Rozhin, A.; Colli, A.; Scardaci, V.; Pisana, S.; Hasan,

T.; Flewitt, A. J.; Robertson, J.; Hsieh, G. W.; et al. Ink-Jet Printing of Carbon

Nanotube Thin Film Transistors. J. Appl. Phys. 2007, 102, 043710.

- (21) Lau, P. H.; Takei, K.; Wang, C.; Ju, Y.; Kim, J.; Yu, Z.; Takahashi, T.; Cho, G.; Javey, A. Fully Printed, High Performance Carbon Nanotube Thin-Film Transistors on Flexible Substrates. *Nano Lett.* 2013, *13*, 3864–3869.

- (22) Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H.

Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors

Using Amorphous Oxide Semiconductors. *Nature* **2004**, *432*, 488–492.

- (23) Carcia, P. F.; McLean, R. S.; Reilly, M. H.; Jr, G. N. Transparent ZnO Thin-Film Transistor Fabricated by Rf Magnetron Sputtering. *Appl. Phys. Lett.* 2003, 82, 1117–1119.

- (24) Fortunato, E. M. C.; Barquinha, P. M. C.; Pimentel, A. C. M. B. G.; Gonçalves, A. M. F.; Marques, A. J. S.; Martins, R. F. P.; Pereira, L. M. N. Wide-Bandgap High-Mobility ZnO Thin-Film Transistors Produced at Room Temperature. *Appl. Phys. Lett.* **2004**, *85*, 2541–2543.

- (25) Masuda, S.; Kitamura, K.; Okumura, Y.; Miyatake, S.; Tabata, H.; Kawai, T.

Transparent Thin Film Transistors Using ZnO as an Active Channel Layer and

Their Electrical Properties. *J. Appl. Phys.* **2003**, *93*, 1624–1630.

- (26) Hoffman, R. L.; Norris, B. J.; Wager, J. F. ZnO-Based Transparent Thin-Film Transistors. *Appl. Phys. Lett.* **2003**, *82*, 733–735.

- (27) Ong, B. S.; Li, C.; Li, Y.; Wu, Y.; Loutfy, R. Stable, Solution-Processed, High-Mobility ZnO Thin-Film Transistors. *J. Am. Chem. Soc.* **2007**, *129*, 2750–2751.

- (28) Bashir, A.; Wöbkenberg, P. H.; Smith, J.; Ball, J. M.; Adamopoulos, G.;

Bradley, D. D. C.; Anthopoulos, T. D. High-Performance Zinc Oxide

Transistors and Circuits Fabricated by Spray Pyrolysis in Ambient Atmosphere.

Adv. Mater. 2009, 21, 2226–2231.

- (29) Kim, I.-D.; Choi, Y.; Tuller, H. L. Low-Voltage ZnO Thin-Film Transistors with High-KBi1.5Zn1.0Nb1.5O7 Gate Insulator for Transparent and Flexible Electronics. *Appl. Phys. Lett.* **2005**, *87*, 043509.

- (30) Mendelsberg, R. J.; Lim, S. H. N.; Zhu, Y. K.; Wallig, J.; Milliron, D. J.;

Anders, A. Achieving High Mobility ZnO: Al at Very High Growth Rates by

Dc Filtered Cathodic Arc Deposition. *J. Phys. Appl. Phys.* **2011**, *44*, 232003.

- (31) Anders, A.; Yushkov, G. Y. Ion Flux from Vacuum Arc Cathode Spots in the Absence and Presence of a Magnetic Field. *J. Appl. Phys.* **2002**, *91*, 4824–4832.

- (32) Anders, A. Cathodic Arcs: From Fractal Spots to Energetic Condensation;

Springer Science & Business Media, 2009.

- (33) Lee, C.-Y.; Chang, C.; Shih, W.-P.; Dai, C.-L. Wet Etching Rates of InGaZnO for the Fabrication of Transparent Thin-Film Transistors on Plastic Substrates. *Thin Solid Films* **2010**, *518*, 3992–3998.

- (34) Wang, Y. G.; Lau, S. P.; Lee, H. W.; Yu, S. F.; Tay, B. K.; Zhang, X. H.; Tse, K. Y.; Hng, H. H. Comprehensive Study of ZnO Films Prepared by Filtered Cathodic Vacuum Arc at Room Temperature. *J. Appl. Phys.* 2003, 94, 1597–1604.

- (35) Detert, D. M.; Lim, S. H. M.; Tom, K.; Luce, A. V.; Anders, A.; Dubon, O. D.; Yu, K. M.; Walukiewicz, W. Crystal Structure and Properties of CdxZn1-xO Alloys across the Full Composition Range. *Appl. Phys. Lett.* **2013**, *102*, 232103.

- (36) Warren, B. E. X-Ray Diffraction; Courier Dover Publications, 1969.

- (37) Özgür, Ü.; Alivov, Y. I.; Liu, C.; Teke, A.; Reshchikov, M. A.; Doğan, S.; Avrutin, V.; Cho, S.-J.; Morkoç, H. A Comprehensive Review of ZnO Materials and Devices. *J. Appl. Phys.* **2005**, *98*, 041301.

- (38) Wang, Y.-L.; Ren, F.; Lim, W.; Norton, D. P.; Pearton, S. J.; Kravchenko, I. I.; Zavada, J. M. Room Temperature Deposited Indium Zinc Oxide Thin Film Transistors. *Appl. Phys. Lett.* **2007**, *90*, 232103.

- (39) Nomura, K.; Takagi, A.; Kamiya, T.; Ohta, H.; Hirano, M.; Hosono, H.

Amorphous Oxide Semiconductors for High-Performance Flexible Thin-Film

Transistors. *Jpn. J. Appl. Phys.* **2006**, *45*, 4303.

- (40) Suresh, A.; Wellenius, P.; Dhawan, A.; Muth, J. Room Temperature Pulsed

Laser Deposited Indium Gallium Zinc Oxide Channel Based Transparent Thin

Film Transistors. *Appl. Phys. Lett.* **2007**, *90*, 123512.

- (41) Kim, Y.-H.; Heo, J.-S.; Kim, T.-H.; Park, S.; Yoon, M.-H.; Kim, J.; Oh, M. S.;

Yi, G.-R.; Noh, Y.-Y.; Park, S. K. Flexible Metal-Oxide Devices Made by

Room-Temperature Photochemical Activation of Sol-Gel Films. *Nature* 2012,

489, 128–132.

- (42) Kim, J. B.; Fuentes-Hernandez, C.; Kippelen, B. High-Performance InGaZnO

Thin-Film Transistors with High-K Amorphous Ba0.5Sr0.5TiO3 Gate Insulator. *Appl. Phys. Lett.* **2008**, *93*, 242111.

- (43) Bong, H.; Lee, W. H.; Lee, D. Y.; Kim, B. J.; Cho, J. H.; Cho, K. High-Mobility Low-Temperature ZnO Transistors with Low-Voltage Operation. *Appl. Phys. Lett.* **2010**, *96*, 192115.

- (44) Xu, X.; Cui, Q.; Jin, Y.; Guo, X. Low-Voltage Zinc Oxide Thin-Film

Transistors with Solution-Processed Channel and Dielectric Layers below

150 °C. Appl. Phys. Lett. 2012, 101, 222114.

- (45) Su, N.-C.; Wang, S.-J.; Huang, C.-C.; Chen, Y.-H.; Huang, H.-Y.; Chiang,

C.-K.; Chin, A. Low-Voltage-Driven Flexible InGaZnO Thin-Film Transistor

With Small Subthreshold Swing. *IEEE Electron Device Lett.* 2010, 31, 680–682.