# Towards an Ultra-Low Energy Computation with Asynchronous Circuits

Tsung-Te Liu

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2014-35 http://www.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-35.html

May 1, 2014

Copyright © 2014, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Towards an Ultra-Low Energy Computation with Asynchronous Circuits

by

Tsung-Te Liu

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Jan M. Rabaey, Chair Professor Elad Alon Professor Paul K. Wright

Spring 2012

### Towards an Ultra-Low Energy Computation with Asynchronous Circuits

Copyright 2012

by

Tsung-Te Liu

#### Abstract

Towards an Ultra-Low Energy Computation with Asynchronous Circuits

by

Tsung-Te Liu

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Jan M. Rabaey, Chair

Emerging biomedical applications would benefit from the availability of digital processors with substantially improved energy-efficiency. One approach to realize ultra-low energy processors is to scale the supply voltage aggressively to near or below the transistor threshold, yet the major increase in delay variability under process, voltage and temperature variations combined with the dominance of leakage power makes robust near- and sub-threshold computations and further voltage scaling extremely challenging.

This research focuses on the design and implementation of robust and energy-efficient computation architectures by employing an asynchronous self-timed design methodology. A statistical framework is first presented to analyze the energy and delay of CMOS digital circuits considering a variety of timing methodologies. The proposed analysis framework combines variability and statistical performance models, which enables designers to efficiently evaluate circuit performance, and determine the optimal timing strategy, pipeline depth and supply voltage in the presence of variability.

Two asynchronous self-timed designs are then implemented. First, a low-energy asynchronous logic topology using sense amplifier-based pass transistor logic (SAPTL) is presented. The SAPTL structure can realize very low energy computation by using low-leakage pass transistor networks at low supply voltages. The introduction of asynchronous operation in SAPTL further improves energy-delay performance without a significant increase in hardware complexity. The proposed self-timed SAPTL architectures provide robust and efficient asynchronous computation using a glitch-free protocol to avoid possible dynamic timing hazards.

Second, an asynchronous neural signal processor is presented to dynamically minimize leakage and to self-adapt to process variations and different operating conditions. The self-timed processor demonstrates robust sub-threshold operation down to 0.25V, while consuming only 460nW in a 65nm CMOS technology, representing a 4.4X reduction in power compared to the state-of-the-art designs. The proposed asynchronous design approach enables CMOS

circuits to fully benefit from continued technology scaling and realize ultra-low voltage operation, without incurring the leakage and variability issues associated with conventional synchronous implementations.

To my beloved family and Chiang-Min

# Contents

| Li | List of Figures List of Tables |        |                                                               | v    |

|----|--------------------------------|--------|---------------------------------------------------------------|------|

| Li |                                |        |                                                               | viii |

| 1  | Intr                           | oducti | ion                                                           | 1    |

|    | 1.1                            | Overv  | iew                                                           | 1    |

|    | 1.2                            | Disser | tation Outline                                                | 1    |

| 2  | Ultı                           | a-Low  | Energy Digital Circuit Design                                 | 3    |

|    | 2.1                            | Oppor  | tunity of Low-Voltage Design                                  | 3    |

|    | 2.2                            | Challe | enge of Low-Voltage Design                                    | 5    |

|    |                                | 2.2.1  | Leakage                                                       | 5    |

|    |                                | 2.2.2  | Variability                                                   | 6    |

|    | 2.3                            | Low-V  | Voltage Design Techniques                                     | 11   |

|    | 2.4                            | Summ   | ary                                                           | 11   |

| 3  | Des                            | ign an | d Analysis of Asynchronous Circuits                           | 13   |

|    | 3.1                            | Oppor  | tunity and Challenge                                          | 13   |

|    | 3.2                            | Model  | ing of CMOS Digital Circuit                                   | 16   |

|    |                                | 3.2.1  | Delay Model                                                   | 16   |

|    |                                | 3.2.2  | Variability Model                                             | 17   |

|    |                                | 3.2.3  | Circuit Delay Variability with Different Logic Depths         | 19   |

|    | 3.3                            | Statis | tical Analysis of Synchronous and Asynchronous Timing Schemes | 19   |

|    |                                | 3.3.1  | Synchronous Approach                                          | 20   |

|    |                                | 3.3.2  | Bundled-Data Self-Timed Approach                              | 21   |

CONTENTS iii

|   |     | 3.3.3 Dual-Rail Self-Timed Approach                   | 23 |

|---|-----|-------------------------------------------------------|----|

|   | 3.4 | Performance Comparison                                | 23 |

|   |     | 3.4.1 Speed Performance                               | 23 |

|   |     | 3.4.2 Energy Performance                              | 27 |

|   | 3.5 | Summary                                               | 28 |

| 4 | Cas | se Study I: Asynchronous SAPTL Design                 | 31 |

|   | 4.1 | SAPTL Architecture                                    | 31 |

|   |     | 4.1.1 Stack and Driver                                | 32 |

|   |     | 4.1.2 Sense Amplifier                                 | 33 |

|   |     | 4.1.3 Synchronous Timing                              | 34 |

|   | 4.2 | Bundled-Data Self-Timed SAPTL Design                  | 34 |

|   |     | 4.2.1 Data Evaluation Cycle                           | 37 |

|   |     | 4.2.2 Data Reset Cycle                                | 38 |

|   |     | 4.2.3 Speed Enhancement                               | 39 |

|   |     | 4.2.4 Glitch Problem                                  | 40 |

|   | 4.3 | Glitch-Free Handshaking Protocol                      | 41 |

|   |     | 4.3.1 Protocol Design                                 | 41 |

|   |     | 4.3.2 Circuit Implementation                          | 43 |

|   | 4.4 | Dual-Rail Self-Timed SAPTL Design                     | 45 |

|   | 4.5 | Test Chip Implementation                              | 46 |

|   | 4.6 | Results                                               | 49 |

|   |     | 4.6.1 Area Comparisons                                | 49 |

|   |     | 4.6.2 Energy-Delay Performance                        | 51 |

|   |     | 4.6.3 Leakage Current Results                         | 52 |

|   | 4.7 | Summary                                               | 53 |

| 5 | Cas | se Study II: Asynchronous Processor Design            | 56 |

|   | 5.1 | Neural Signal Processing for Brain-Machine Interfaces | 56 |

|   | 5.2 | Asynchronous Neural Signal Processor Design           | 58 |

|   | 5.3 | Test Chip Implementation                              | 62 |

|   | 5.4 | Results                                               | 63 |

|   | 5.5 | Summary                                               | 68 |

| C0 | ONTE         | ENTS                     | iv |

|----|--------------|--------------------------|----|

| 6  | Con          | aclusion and Future Work | 70 |

|    | 6.1          | Contributions            | 70 |

|    | 6.2          | Future Work              | 70 |

| Bi | Bibliography |                          |    |

# List of Figures

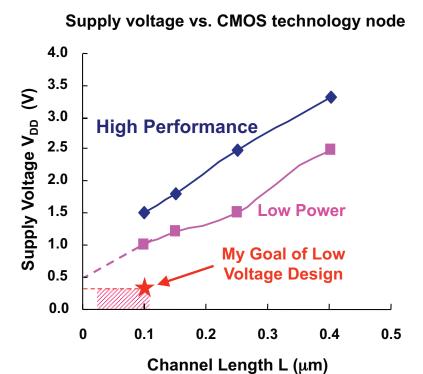

| 2.1  | Supply voltages used in different CMOS technology nodes [ITRS09]                                                                               | 4  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

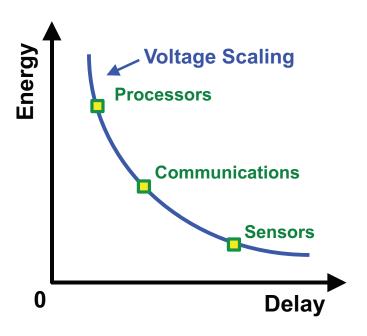

| 2.2  | Energy-delay characteristics of different electronic applications                                                                              | 4  |

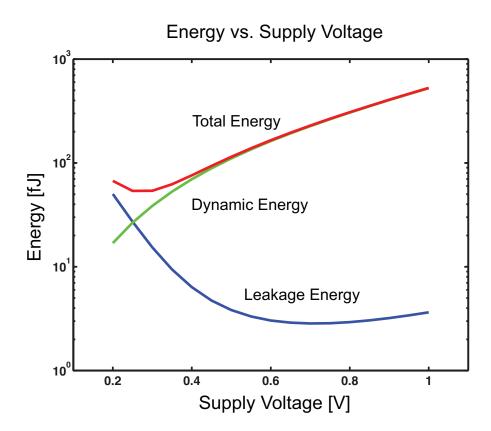

| 2.3  | Energy consumption of an inverter-based ring oscillator as a function of supply voltage                                                        | 7  |

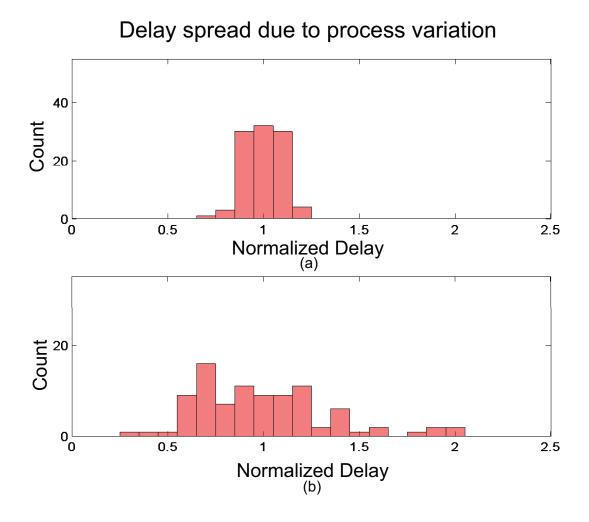

| 2.4  | Delay distribution of a 4FO4 inverter chain under process variations (a) at 1V and (b) at 300mV                                                | 8  |

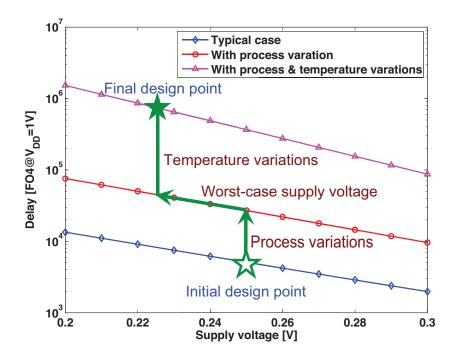

| 2.5  | Delay penalty of the worst-case design methodology under process, voltage and temperature variations                                           | 9  |

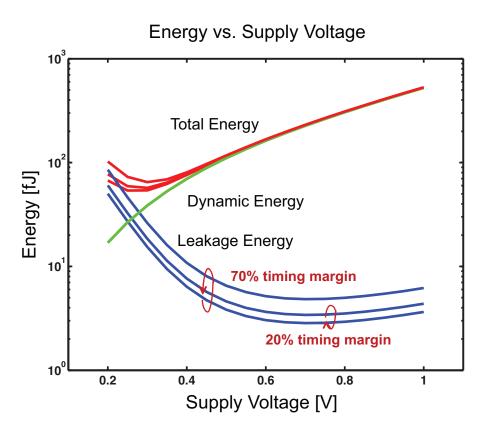

| 2.6  | Leakage and total energy increase as more timing margin is reserved                                                                            | 10 |

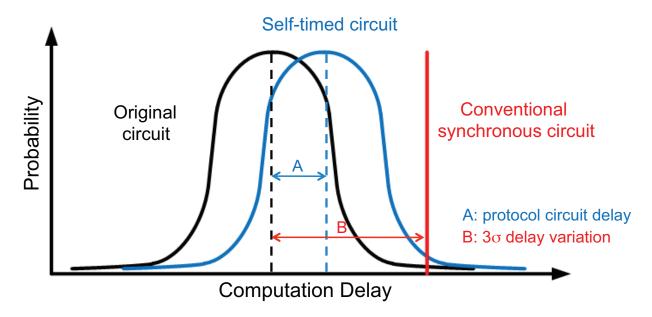

| 3.1  | Performance characteristics of original (black), synchronous (red) and asynchronous (blue) digital circuits                                    | 14 |

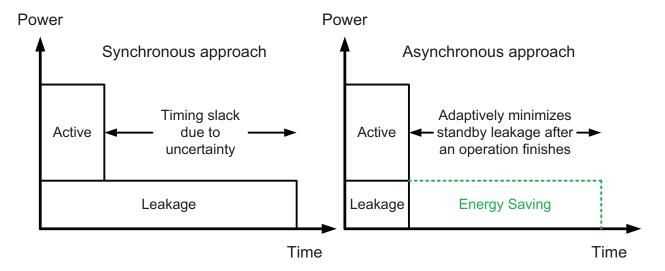

| 3.2  | Power profiles of synchronous and asynchronous systems                                                                                         | 15 |

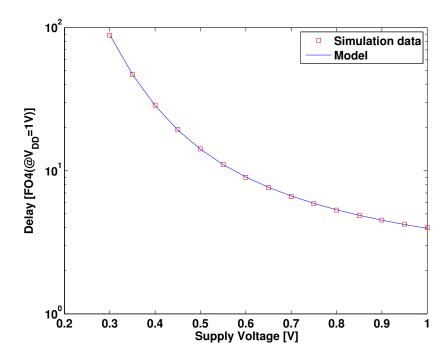

| 3.3  | Simulated and modeled delay of a 4FO4 inverter chain in 65nm CMOS technology                                                                   | 17 |

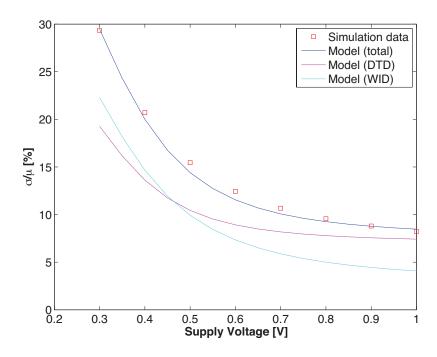

| 3.4  | Simulated and modeled delay variability results                                                                                                | 18 |

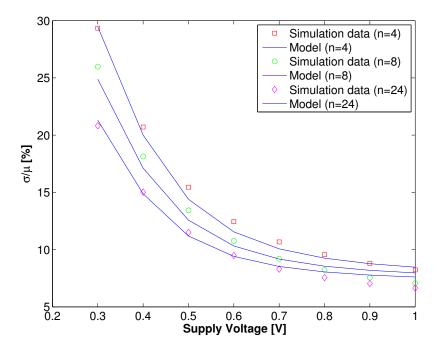

| 3.5  | Simulated and modeled delay variability results for different logic depths                                                                     | 20 |

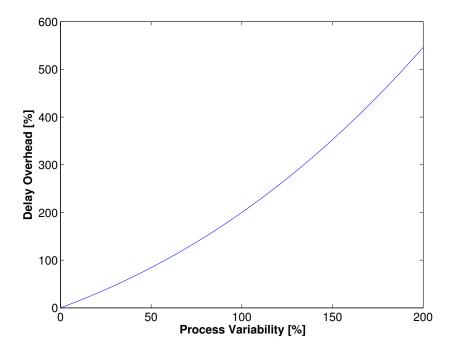

| 3.6  | Delay overhead characteristics of bundled-data self-timed scheme                                                                               | 22 |

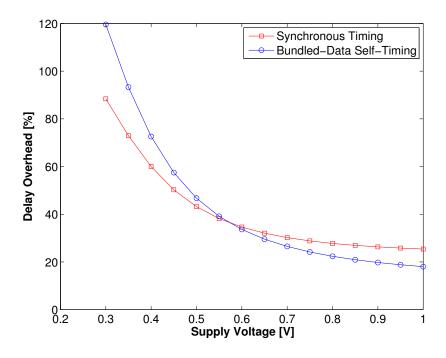

| 3.7  | Delay overhead characteristics of synchronous and bundled-data schemes for a critical path delay of 4FO4                                       | 24 |

| 3.8  | Delay overhead characteristics of synchronous and bundled-data schemes for a critical path delay of 24FO4                                      | 25 |

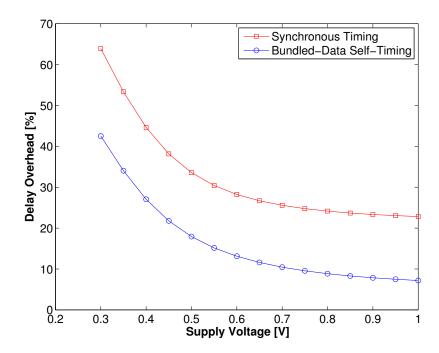

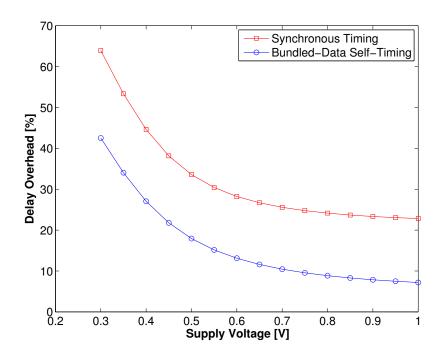

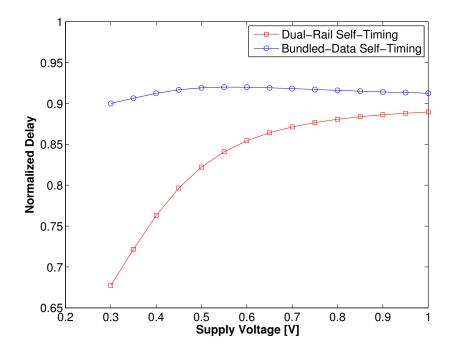

| 3.9  | Speed performances of bundled-data and dual-rail schemes for a critical path delay of 4FO4. The delay is normalized to the synchronous design  | 26 |

| 3.10 | Speed performances of bundled-data and dual-rail schemes for a critical path delay of 24FO4. The delay is normalized to the synchronous design | 27 |

LIST OF FIGURES vi

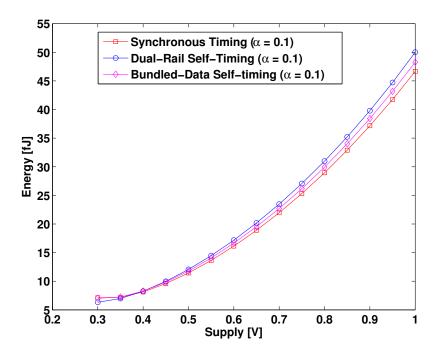

| 3.11 | Energy performances of a 24FO4 inverter chain with different timing schemes for $a=0.1.$                                                                                                                                                                                                                 | 28 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

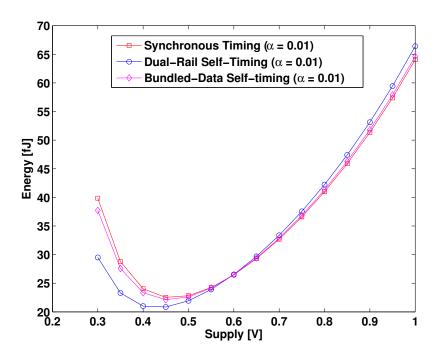

| 3.12 | Energy performances of a 24FO4 inverter chain with different timing schemes for $a=0.01.\ldots\ldots$                                                                                                                                                                                                    | 29 |

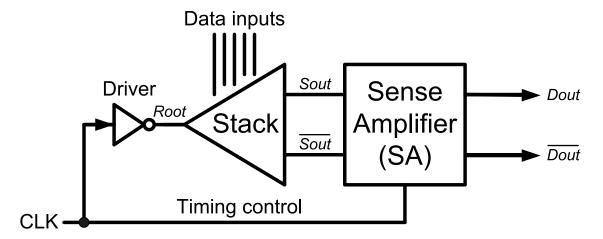

| 4.1  | Architecture of SAPTL module with synchronous timing control                                                                                                                                                                                                                                             | 32 |

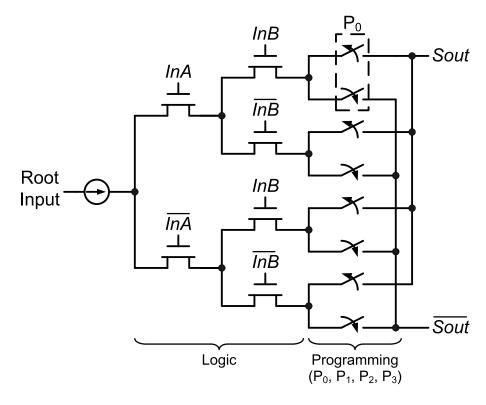

| 4.2  | Schematic of a two-input stack with $N_{stack}=5.$                                                                                                                                                                                                                                                       | 33 |

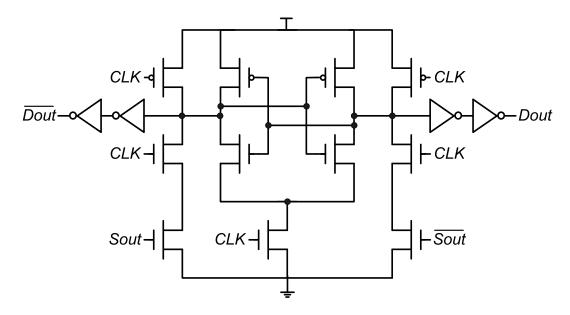

| 4.3  | Sense amplifier circuit                                                                                                                                                                                                                                                                                  | 34 |

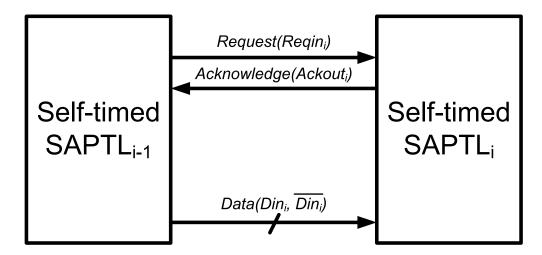

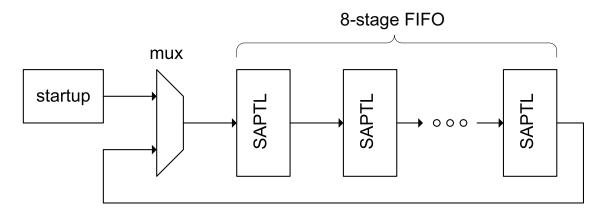

| 4.4  | Communication between two self-timed SAPTL modules                                                                                                                                                                                                                                                       | 35 |

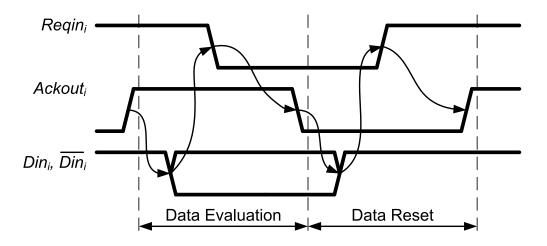

| 4.5  | Two-cycle evaluation-reset operation for the self-timed SAPTL stage $i$ in Fig. 4.4                                                                                                                                                                                                                      | 35 |

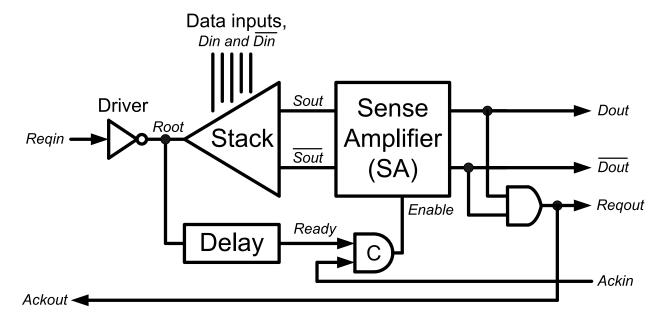

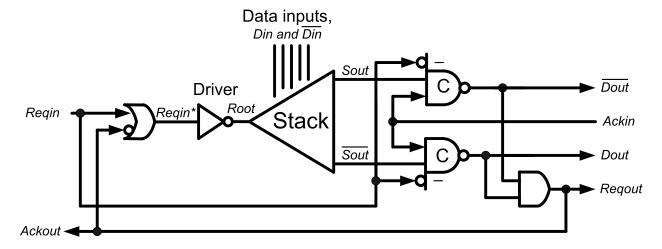

| 4.6  | Architecture of self-timed SAPTL module with bundled-data protocol                                                                                                                                                                                                                                       | 36 |

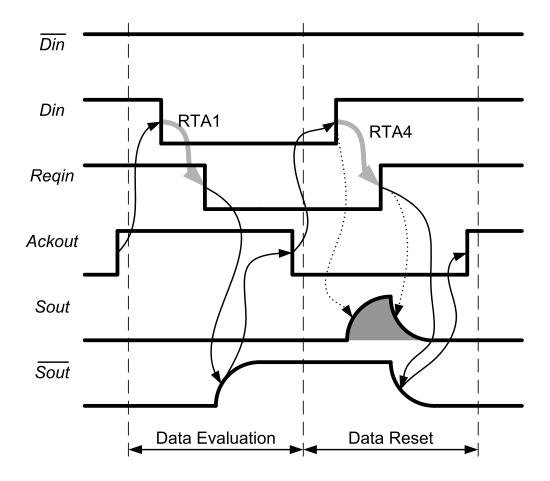

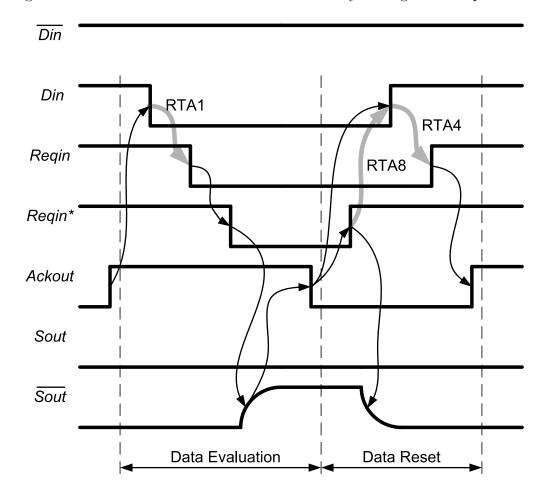

| 4.7  | Timing diagram of self-timed SAPTL                                                                                                                                                                                                                                                                       | 40 |

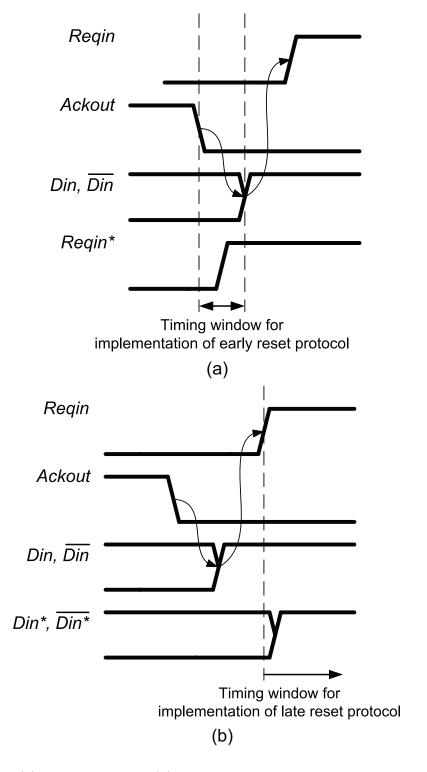

| 4.8  | (a) Early reset and (b) late reset glitch-free handshaking protocol                                                                                                                                                                                                                                      | 42 |

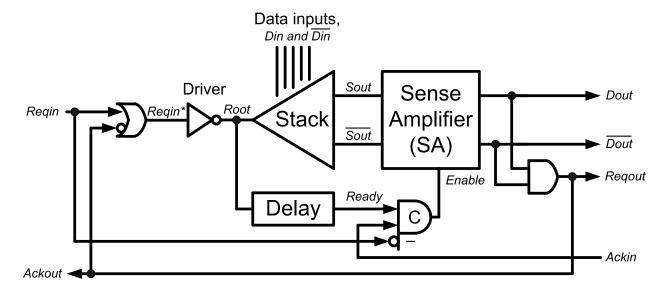

| 4.9  | Self-timed SAPTL structure with early reset glitch-free protocol                                                                                                                                                                                                                                         | 44 |

| 4.10 | Timing diagram of glitch-free self-timed SAPTL                                                                                                                                                                                                                                                           | 44 |

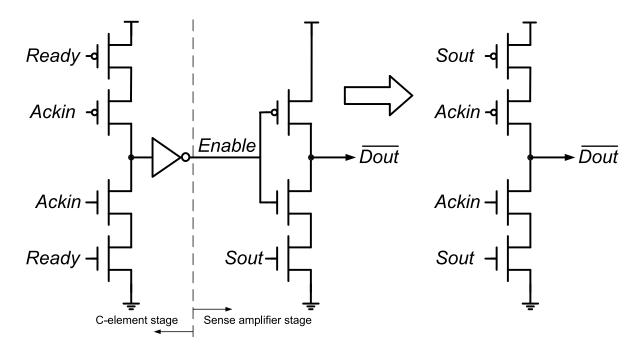

| 4.11 | Logic combination of two-input C-element and sense amplifier circuits                                                                                                                                                                                                                                    | 45 |

| 4.12 | Architecture of glitch-free self-timed SAPTL module with dual-rail protocol.                                                                                                                                                                                                                             | 46 |

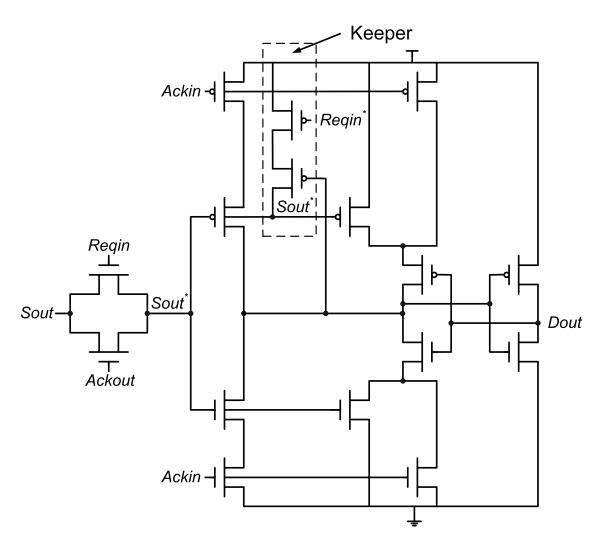

| 4.13 | Two-input C-element circuit with additional decision-making logic for glitch-free self-timed SAPTL                                                                                                                                                                                                       | 47 |

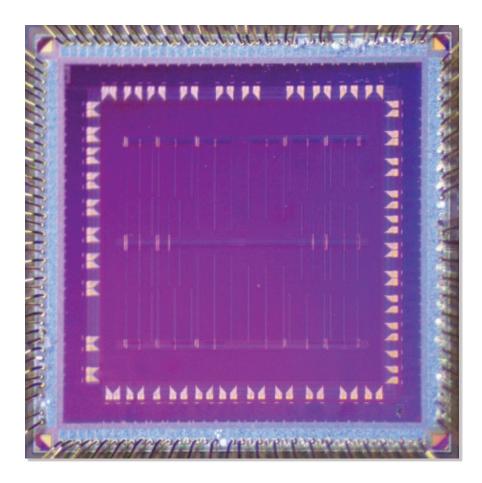

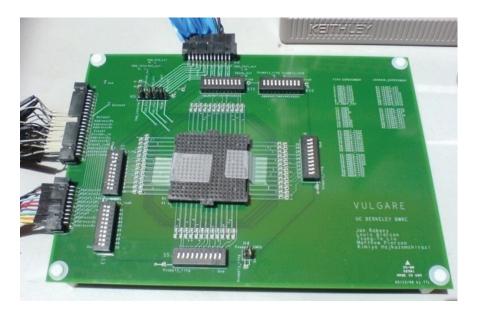

| 4.14 | The self-timed SAPTL test chip                                                                                                                                                                                                                                                                           | 48 |

| 4.15 | The self-timed SAPTL test board                                                                                                                                                                                                                                                                          | 48 |

| 4.16 | Test setup for energy and delay measurements                                                                                                                                                                                                                                                             | 49 |

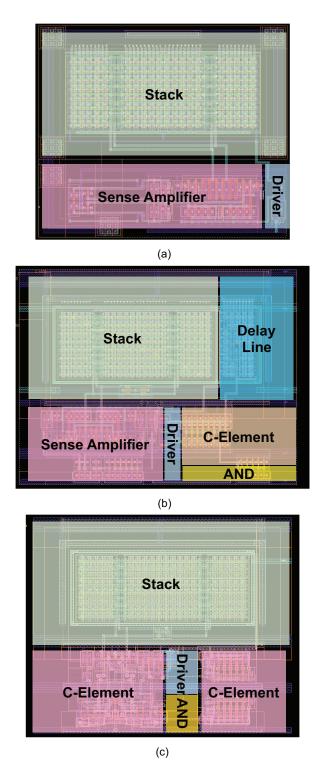

| 4.17 | SAPTL5 layouts in 90nm CMOS technology: (a) The synchronous layout, (b) the bundled-data layout, including the built-in delay line immediately to the right of the stack, and (c) the dual-rail layout. The size of the stack occupies the top half of the figures and is the same for all three layouts | 50 |

| 4 18 | Simulated delay results of the SAPTL5 circuits as a function of supply voltage.                                                                                                                                                                                                                          | 51 |

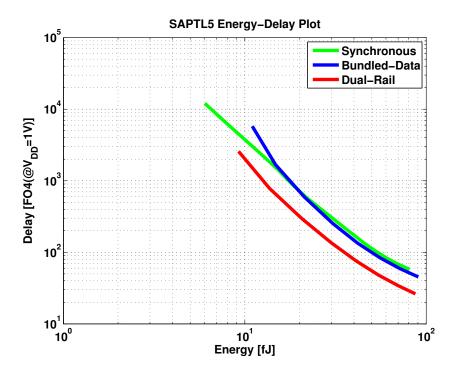

|      | Simulated energy-delay plots of the SAPTL5 circuits for the supply voltage                                                                                                                                                                                                                               | 01 |

| 1.10 | ranging from 300mV to 1 V                                                                                                                                                                                                                                                                                | 52 |

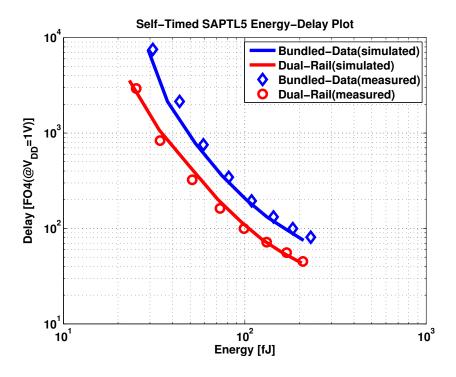

| 4.20 | Measured versus simulated energy-delay plots for the 90nm CMOS self-timed SAPTL5, as the supply voltage is varied from 300 mV to 1 V                                                                                                                                                                     | 53 |

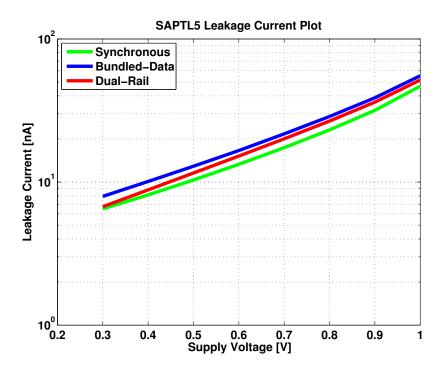

| 4.21 | Simulated leakage current of the SAPTL5 circuits as a function of supply voltage                                                                                                                                                                                                                         | 54 |

LIST OF FIGURES vii

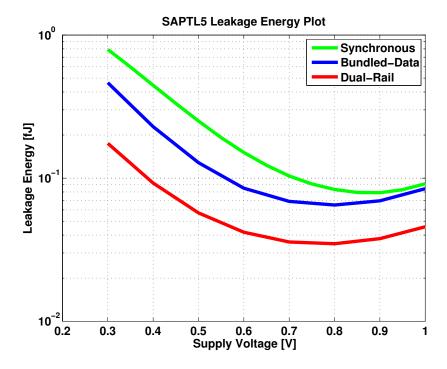

| 4.22 | Simulated leakage energy of the SAPTL5 circuits as a function of supply voltage.                  | 54 |

|------|---------------------------------------------------------------------------------------------------|----|

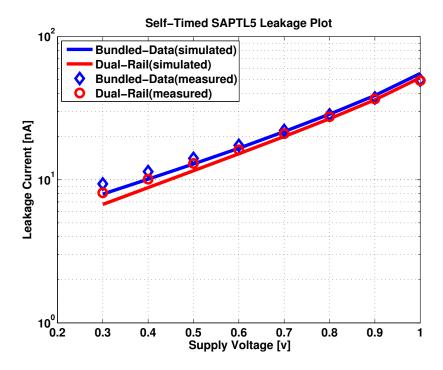

| 4.23 | Measured versus simulated leakage current of the self-timed SAPTL as a function of supply voltage | 55 |

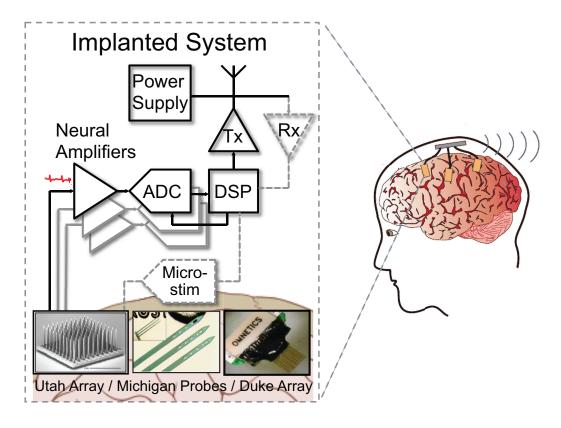

| 5.1  | A generic integrated circuit system for brain-machine interfaces [Muller12]                       | 57 |

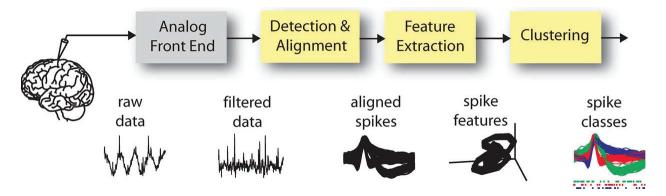

| 5.2  | Spike-sorting process [Karkare11]                                                                 | 58 |

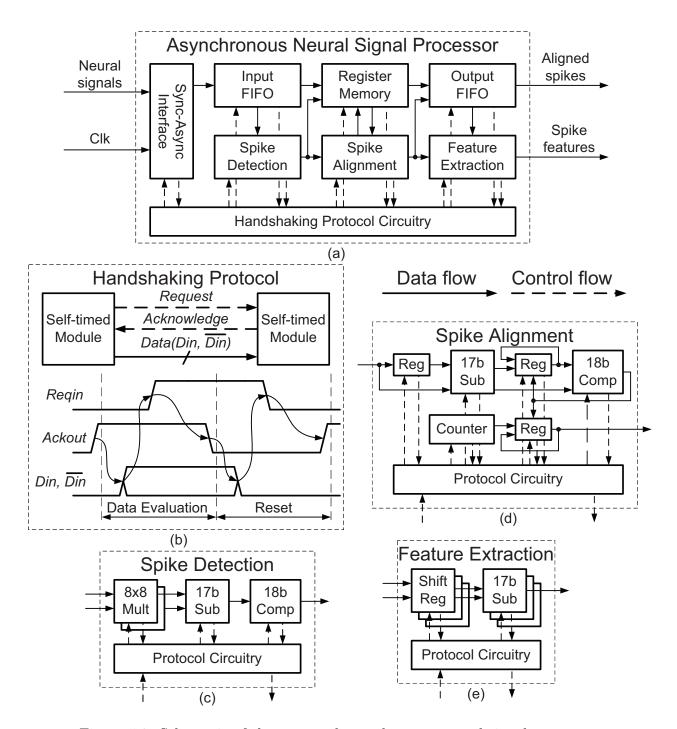

| 5.3  | Schematic of the proposed asynchronous neural signal processor                                    | 59 |

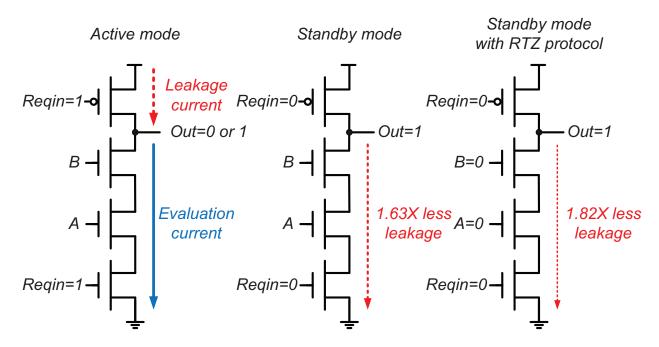

| 5.4  | Leakage characteristics of a dynamic logic gate in different operating modes.                     | 60 |

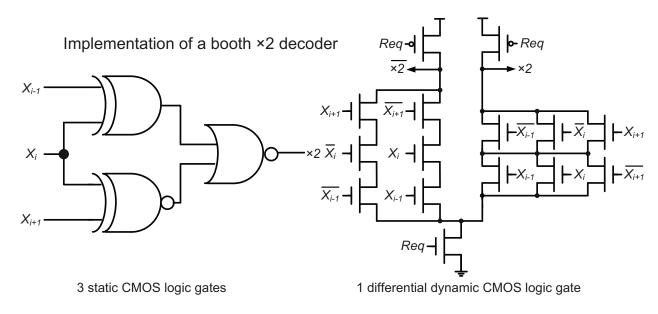

| 5.5  | Circuit implementations of a booth $X2$ decoder using different logic styles                      | 61 |

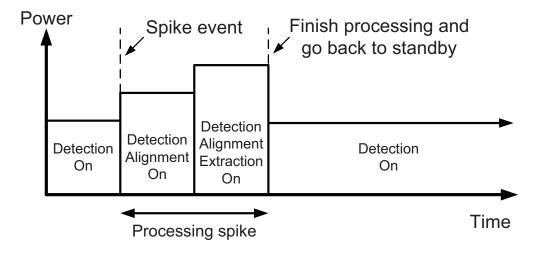

| 5.6  | Power profile of neural signal processor during operation                                         | 61 |

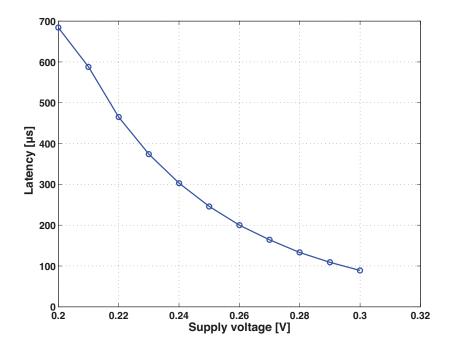

| 5.7  | Processing latency as a function of supply voltage                                                | 62 |

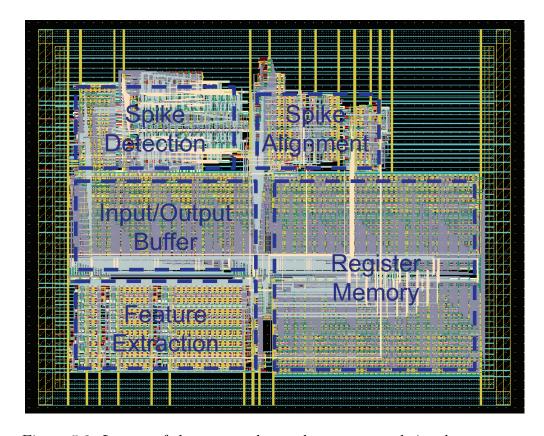

| 5.8  | Layout of the proposed asynchronous neural signal processor                                       | 63 |

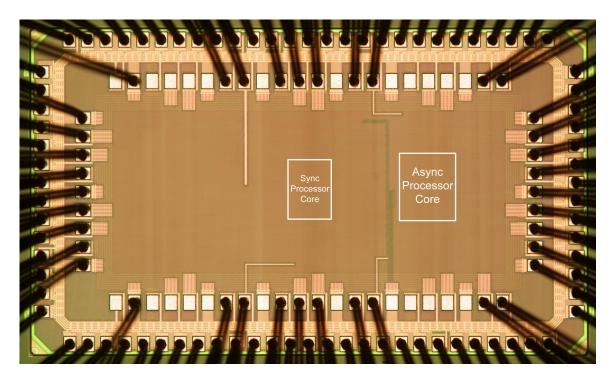

| 5.9  | Die photo of test chip                                                                            | 64 |

| 5.10 | Asynchronous processor test board                                                                 | 64 |

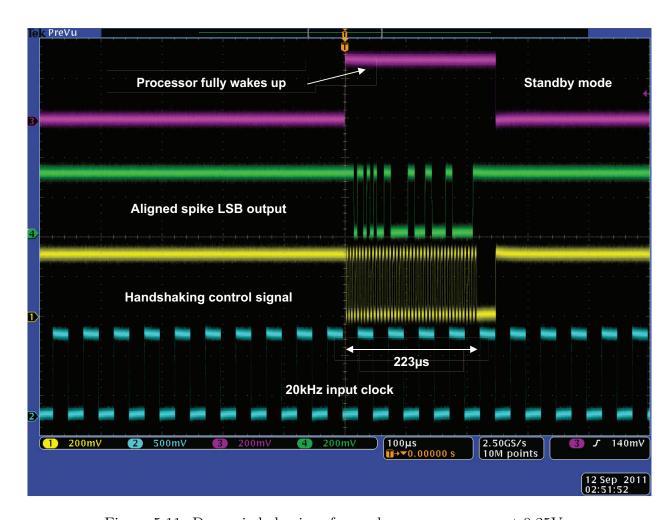

| 5.11 | Dynamic behavior of asynchronous processor at 0.25V                                               | 65 |

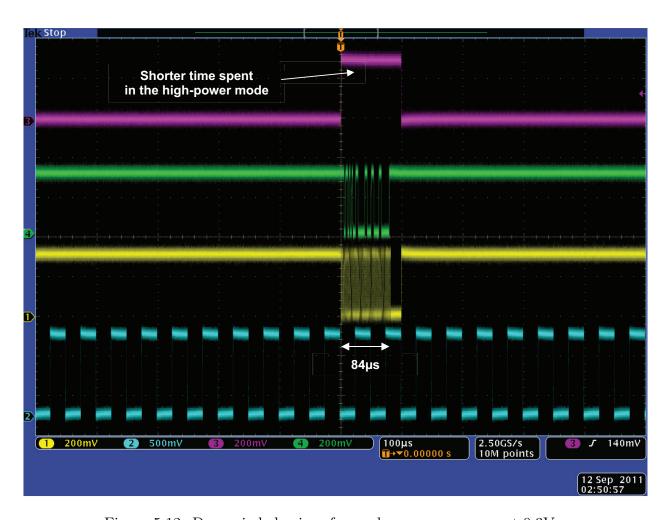

| 5.12 | Dynamic behavior of asynchronous processor at 0.3V                                                | 66 |

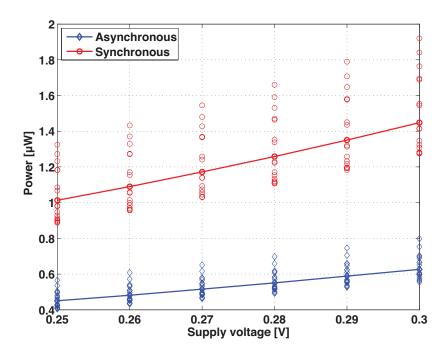

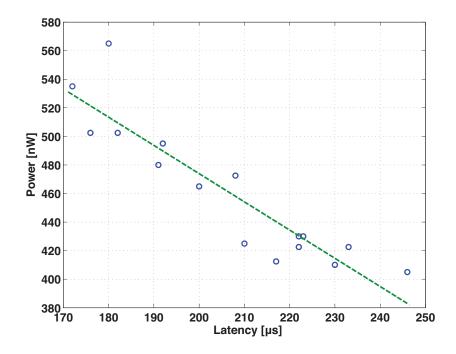

| 5.13 | Measured power consumption results of 16 test chips                                               | 67 |

| 5.14 | Measured power-latency results of 16 asynchronous processors at 0.25V                             | 68 |

# List of Tables

| 3.1 | Speed Performance Analysis Model                                      | 24 |

|-----|-----------------------------------------------------------------------|----|

| 5.1 | Comparison to the state-of-the-art processors and performance summary | 69 |

#### Acknowledgments

The past seven years have been a wonderful and unforgettable journey. A lot of people helped me along the road, and I am extremely grateful to them. Here, I would like to take this opportunity to show my appreciation to some of them.

First, I would like to thank my advisor Professor Jan Rabaey for his guidance and support for my research. With his passion and vision, Jan shows me what is needed to be a researcher. I would also like to thank Professor Elad Alon for his valuable feedback, and Professor John Wawrzynek and Professor Paul Wright for being my qualifying and dissertation committee.

I had a valuable opportunity to work with Marly Roncken and Ivan Sutherland at the time I was looking for my research topic. They led me into this fantabulous asynchronous world and have been inspiring me ever since. They also showed me how to effectively present and deliver a research idea. I really appreciate their encouragement and help with my research work.

I would like to thank Louis Alarcon for being my mentor as well as tapeout partner. He was always the first one I talked to whenever I had a research idea or problem. I would also like to thank everyone at Berkeley Wireless Research Center for the help during my Ph.D. study, especially during the tapeout time. Special thank goes to Jun-Chau Chien for his valuable assistance to my processor tapeout.

Apart from the research life, hanging out with my friends in Berkeley Association of Taiwanese Students has been always enjoyable. I especially want to thank Darsen Lu for being my partner of various activities and the help on all kinds of occasions.

Hsiu-Yu Fan has been an important part of my life during the later stages of my Ph.D. study. I want to thank her for the love and support, especially staying up with me during numerous late-night research works. Her knowledge and philosophy truly enrich my life, and I really treasure her company.

I would like to thank Chiang-Min Cheng for the love, support and understanding. Without her, I would not be able to start this journey at Berkeley, or to accomplish anything near significant. She will be always inside my heart, and be the reason that keeps me fighting for the rest of my life.

Last, but not the least, I would like to thank my family, especially my parents and sister. Their love and unconditional support get me through each challenge, and keep me warm at windy Berkeley. I love them from the bottom of my heart.

# Chapter 1

### Introduction

Researches on energy-efficient circuit and system design have been drawing a lot of attentions from both the industry and the academia since the last decade for the following reasons: First, although the speed of CMOS devices keeps improving due to the efforts on continued technology scaling, further power and energy reduction via technology scaling have become extremely difficult due to issues of leakage and variability [Nowak02]. Second, technology scaling combined with advances in system integration and wireless communication has enabled a new set of electronic devices that used to only exist in science fictions, including ubiquitous sensor swam and miniature medical devices [Rabaey08]. However, these emerging devices can only work on an extremely stringent energy budget. As a result, in order to accommodate the demands from these application and future technology scaling, it is essential to develop alternate devices and novel circuit architectures for ultra-low energy computation.

#### 1.1 Overview

This work presents the design and implementation of robust and energy-efficient computation architectures by employing an asynchronous self-timed design methodology. A statistical analysis framework is first presented to evaluate the energy and delay of CMOS circuits considering a variety of timing methodologies in the presence of variability. Two asynchronous self-timed designs are then implemented. First, a low-energy asynchronous circuit topology using sense amplifier-based pass transistor logic is presented. Second, an ultra-low power asynchronous neural signal processor for brain-machine interface applications is presented.

#### 1.2 Dissertation Outline

Chapter 2 provides an overview of ultra-low energy digital circuit design in the context of voltage scaling. Leakage and variability issues associated with voltage and technology scaling

are discussed. Various circuit techniques for ultra-low voltage operation are also summarized in this chapter.

In chapter 3 an asynchronous self-timed design methodology is introduced as an attractive alternative for the realization of robust and energy-efficient computation. Both the advantage and challenge of design of an asynchronous system are discussed. The energy and delay of synchronous and asynchronous circuits in the presence of process variability are evaluated within a statistical analysis framework.

Chapter 4 presents an asynchronous circuit topology using the sense amplifier-based pass transistor logic (SAPTL). The bundled-data and the dual-rail self-timed protocols are employed to realize asynchronous self-timed SAPTLs, respectively. Low-energy handshaking protocol design and circuit implementation are presented. Results of simulation and measurement on various self-timed SAPTL circuits are compared in 90nm CMOS technology.

Chapter 5 presents an asynchronous neural signal processor for brain-machine interface applications. The background and motivation of on-line neural signal processing are first introduced. Design methodology and circuit implementation of an ultra-low power asynchronous neural signal processor are then presented. Results of measurement on both synchronous and asynchronous designs from a 65nm test chip are compared with the state-of-the-art processors.

Chapter 6 summarizes and concludes this research. Future research directions are also suggested.

### Chapter 2

# Ultra-Low Energy Digital Circuit Design

Voltage scaling has been demonstrated as the most powerful way of reducing digital computation power and energy [Chandrasakan92]. However, as the supply is scaled near or below the device threshold, dramatic increases in leakage and variability severely limit the minimum power and energy that can be achieved. The research goal of this work is therefore to develop circuit techniques and design methodology addressing these two issues, and thus further minimizing power and energy consumption of digital circuits.

In this chapter, an overview of ultra-low energy digital circuit design via aggressive voltage scaling is presented. Section 2.1 first introduces the background and principle of voltage scaling. Leakage and variability, two major challenges of low-voltage operation, are then discussed in section 2.2. Section 2.3 presents and compares the state-of-the-art system and circuit design techniques for low-voltage operation. Section 2.4 concludes this chapter.

### 2.1 Opportunity of Low-Voltage Design

Historically, technology scaling is usually accompanied by voltage scaling. Fig. 2.1 shows the supply voltages used in different CMOS technology nodes for both high-performance and low-power applications [ITRS09]. For long-channel CMOS device, ideally, both transistor density and speed can be increased from technology scaling while still keeping the total power density constant, if the device threshold and supply voltage are also scaled by the same ratio [Dennard74]. However, for short-channel devices in deep-submicron CMOS technology, voltage scaling has been slowing down for the recent CMOS technology nodes due to leakage and variation issues. This results in dramatic increase in power density [Nowak02]. To address this problem, on the one hand, researchers have been looking for "new device" that has better performance characteristics to extend CMOS technology scaling. On the other hand, developing "new circuit" architectures that exhibit lower leakage and better reliability is essential in order to take the full advantage of technology scaling.

Figure 2.1: Supply voltages used in different CMOS technology nodes [ITRS09].

Figure 2.2: Energy-delay characteristics of different electronic applications.

On the application side, emerging sensor applications such as miniature medical devices have drawn huge attention in recent years. These applications have the potential to completely change people's life [Rabaey08]. Since these sensor devices have a very small form factor, they usually operate with a tiny battery, or even rely only on the energy scavenged directly from the environment. As a result, the energy budget of the entire device is severely limited, but the speed performance requirement is usually much relaxed compared to the high-end processors, as shown in Fig. 2.2. As a result, minimizing the energy consumption while meeting the application-specific constraint is the most important design issue for these ultralow energy applications.

If the ultimate design goal is to minimize digital energy and power, and circuit leakage can be neglected, digital circuits should operate at a supply voltage below the nominal supply to reduce dynamic power and energy consumption [Chandrasakan92]. The dynamic power  $P_{dynamic}$  and energy  $E_{dynamic}$  of a CMOS gate can be expressed as [Rabaey03]:

$$P_{dynamic} = \alpha C_{switch} V_{DD}^2 f \tag{2.1}$$

$$E_{dynamic} = \alpha C_{switch} V_{DD}^2 \tag{2.2}$$

where  $\alpha$  is the activity factor,  $C_{switch}$  is the switched capacitance, and f is the operating frequency. Eqs. 2.1 and 2.2 show that voltage scaling has a dramatic impact on dynamic energy and power consumption due to its quadratic dependency. This characteristic is therefore very attractive to these emerging sensor applications that demand for extremely low energy consumption.

While Eq. 2.2 suggests that supply voltage should be lowered as much as possible to minimize the dynamic energy, the total energy consumption, however, may actually increase at low supply voltages due to circuit leakage and variability. Unfortunately, as CMOS technology continues to scale, these two issues become even severe, which significantly limits the energy reduction that can be realized from voltage scaling. In the next section, leakage and variability, two main challenges of low-voltage design, are discussed.

#### 2.2 Challenge of Low-Voltage Design

#### 2.2.1 Leakage

For portable devices, leakage plays a crucial role since it determines the standby power and thus the standby time. At low supply voltages, the dominant leakage source is the weak inversion, or sub-threshold conduction current between source and drain even if the gate voltage is smaller than the threshold voltage [Chandrakasan01]. This off-state leakage current can be expressed as [Taur98]:

$$I_{leak} = \mu_{eff} C_{ox} \frac{W}{L_{eff}} (m-1) V_T^2 e^{\frac{-V_{TH}}{mV_T}} \left( 1 - e^{-\frac{V_{DD}}{V_T}} \right)$$

(2.3)

where

$$m = \left(1 + \frac{C_d}{C_{ox}}\right),\tag{2.4}$$

$C_{ox}$  is the gate-oxide capacitance per unit area,  $C_d$  is the depletion region per unit area, W is the transistor width,  $L_{eff}$  is the effective channel length, and  $V_T = \frac{kT}{q}$ . Note that the sub-threshold leakage current also reduces as supply voltage is lowered due to the effect of drain induced barrier lowering (DIBL).

The power and energy per operation of a CMOS gate,  $P_{total}$  and  $E_{total}$ , including both active and leakage components can thus be expressed as

$$P_{leak} = V_{DD}I_{leak} \tag{2.5}$$

$$E_{leak} = V_{DD}I_{leak}T_{delay} (2.6)$$

$$P_{total} = P_{dynamic} + P_{leak} = \alpha C_{switch} V_{DD}^2 f + V_{DD} I_{leak}$$

(2.7)

$$E_{total} = E_{dynamic} + E_{leak} = \alpha C_{switch} V_{DD}^2 + V_{DD} I_{leak} T_{delay}$$

(2.8)

where  $T_{delay}$  is the computation delay of a CMOS gate. Eqs. 2.5 and 2.6 show that by scaling down supply voltage, both leakage power and total power consumption can be reduced. However, when the supply voltage approaches the threshold voltage, leakage energy and total energy consumption actually start to increase. This is because the computation delay increases exponentially when the supply voltage is scaled below the threshold voltage, which offsets the leakage power reduction from voltage scaling. In general, because of the exponential increase in delay, the minimum energy point of CMOS digital system exists in sub-threshold or near-threshold regions [Wang05].

To estimate the energy consumption characteristics of low-activity sensor circuit, the energy consumption of a 423-stage fanout-of-four (423FO4) inverter-based ring oscillator for different supply voltages is simulated in 90nm CMOS technology, as shown in Fig. 2.3. The minimum energy point of this ring oscillator circuit is around 300mV. Below it, further voltage scaling is useless because the leakage energy dominates the total energy consumption.

#### 2.2.2 Variability

The second issue of low-voltage digital computation is variability. Process variations continue to increase dramatically with CMOS technology scaling. The transistors will have different die-to-die (inter-die; DTD) and within-die (intra-die; WID) variation behaviors after actual manufacturing process [Bowman02]. DTD variations consisting of parametric variations between different runs, lots, and wafers, affect each transistor equally on the same die. On

Figure 2.3: Energy consumption of an inverter-based ring oscillator as a function of supply voltage.

Figure 2.4: Delay distribution of a 4FO4 inverter chain under process variations (a) at 1V and (b) at 300mV.

the other hand, WID variations result in random fluctuations of transistor characteristics within the same die. These variations severely increase the performance variability of CMOS digital circuits, and their impacts are especially significant at low supply voltages. Fig. 2.4 shows the delay distribution of a 4FO4 inverter chain under process variations in 90nm CMOS technology using Monte Carlo SPICE simulator. A delay spread of 70% at 1V and of 190% at 0.3V is observed. This demonstrates that at low supply voltages, circuit delay becomes highly sensitive to device parameters due to the lower circuit overdrive voltage.

In actual operating environment, unfortunately, other variation sources must also be considered, such as supply voltage and temperature variations. Fig. 2.5 shows the computation delay of a 16FO4 inverter chain in 65nm CMOS technology on the blue curve for supply voltages ranging from 300mV down to 200mV. The red curve illustrates the worst-case delay

Figure 2.5: Delay penalty of the worst-case design methodology under process, voltage and temperature variations.

considering process variations, while the purple curve shows the worst-case delay considering both process and temperature variations. Assuming that the initial design point is to operate at 250mV, in order to guarantee the circuit functionality for the worst-case scenario, the circuit speed must be slowed down by 5X for process variations, by 9X if 10% supply change is further considered, and by up to 147X for process, voltage and temperature variations. As a result, in the presence of severe delay variability, using traditional worst-case design methodology to ensure reliability is very expensive at low supply voltages.

Furthermore, this extra delay margin to guarantee the circuit functionality for the worst-case scenario not only slows down the overall circuit speed during typical operation, but also translates into extra leakage waste because circuits must be idle longer. The total leakage energy including this extra idle leakage can be rewritten as

$$E_{leak} = V_{DD}I_{leak} \left( T_{delay} + T_{margin} \right) \tag{2.9}$$

Fig. 2.6 shows that both leakage energy and total energy increase after extra timing margin is included for delay uncertainty. The amount of total energy increase is especially significant at low supply voltages where leakage dominates.

Figure 2.6: Leakage and total energy increase as more timing margin is reserved.

### 2.3 Low-Voltage Design Techniques

Various circuit techniques have been proposed to reduce leakage consumption at design time. Header and footer switches with multiple threshold voltage have already been widely employed in today's mobile devices to minimize standby leakage [Sakurai03]. Other popular leakage control techniques including the use of non-minimum channel length devices, stacked transistors and body-biasing, are discussed and well summarized in [Chatterjee03]. Novel circuit topologies exhibiting better effective on-to-off operating current ratio than traditional static CMOS structure have also been proposed for low-voltage operation, such as sense amplifier-based pass transistor logic [Alarcón07] and Schmitt-Trigger logic [Lotze12]. Most low-voltage designs today employ several aforementioned leakage reduction techniques simultaneously to minimize leakage.

In order to reduce the impact of process variations, designers can use regular layout structures [Pang09] and variation-aware design methodologies [Ickes12] at design time to minimize performance variability due to process variations. After chips are fabricated, post-silicon tuning is widely used to recover performance and thus increase yield. Post-silicon tuning is usually accomplished by first measuring performance characteristics of replica process monitor, and then re-adjusting supply voltage and body bias to meet performance and yield specifications [Hanson08]. Since this approach estimates circuit variability indirectly using replica process-control circuits, it is only effective to recover performance and yield loss from DTD variations, but incapable of capturing characteristics of WID variations and dynamic variations such as supply ripples and real-time changes in circuit activity.

To deal with dynamic variations, most approaches requires additional tracking and feedback loops [Kurd09], which are usually very costly or difficult to deploy at fine-grained levels at low supply voltages. System architecture employing inherent error detection and correction circuitry has been proposed to deal with performance variability [Bul111, Bowman11]. This approach uses additional latch and error detector along the circuit critical path to identify system failure due to insufficient timing margin. The error events are then either corrected with correction circuitry, or fixed at the system level. Since the error detection and correction are implemented in the main datapath, this approach is effective to reduce the impact of DTD, WID and dynamic variations. However, since only the error event happening before the end of next clock cycle can be detected, the error-recovery range of this technique is very limited, up to 2X delay variations reported in literature. Therefore, it is not sufficient for ultra-low voltage operation where delay variations can easily exceed 10X.

### 2.4 Summary

Voltage scaling is the most effective way of reducing digital power and energy consumption. However, dramatic increase in leakage and variability resulted from both technology and voltage scaling makes further energy reduction externely difficult. Leakage energy dominates the total energy consumption at low supply voltages. Variability slows down the circuit operating speed, which futher increases idle leakage and total energy consumption.

Various design techniques have been proposed to minimize circuit leakage and variability at the circuit and system levels. However, most techniques either require significant implementation cost, or have restricted application or exhibit performance limit at low supply voltages. In the next chapter, an asychornous self-timed design apporach is introduced to realize robust and energy-efficient computation at low supply voltages.

## Chapter 3

# Design and Analysis of Asynchronous Circuits

Traditionally, asynchronous timing strategies have been advocated to enhance the speed and ease the global clocking problem in high-performance digital systems [Sparsø01]. However, the built-in timing mechanisms that automatically adapt to different operating conditions make asynchronous design an attractive alternative for the realization of robust and energy-efficient computation at low supply voltages. In this chapter, energy and delay performances of CMOS circuits with different timing methodologies in the presence of variability are evaluated with a statistical analysis framework. The sweet spots of different timing schemes are then demonstrated. Section 3.1 presents the opportunities and implementation challenges of asynchronous self-timed circuits. Section 3.2 introduces a delay variability model of CMOS digital circuit across a wide range of supply voltage and logic depth. Section 3.3 presents a statistical performance model to analyze the minimum delay overheads required to implement different timing schemes under process variations. Section 3.4 evaluates energy and delay performances of synchronous and asynchronous CMOS digital circuits, based on the variability and statistical performance models developed in section 3.2 and section 3.3. Section 3.5 concludes this chapter.

### 3.1 Opportunity and Challenge

Process variations continue to increase dramatically with CMOS technology scaling. These variations severely increase the performance variability of CMOS digital circuits [Bowman02]. Fig. 3.1 shows the typical delay distribution of digital circuit in the presence of process variations on the black curve. Traditional synchronous approach uses a very conservative timing margin to meet a certain reliability requirement. As a result, a synchronous design must slow down for the "worst-case" scenario, which causes a design to fail to exercise the whole capacity after actual fabrication. The red curve shown in Fig. 3.1 illustrates the performance loss using synchronous timing scheme after including extra timing margin

Figure 3.1: Performance characteristics of original (black), synchronous (red) and asynchronous (blue) digital circuits.

for delay variability. Furthermore, as the variation keeps increasing, this performance loss becomes larger and might offset all the performance enhancements from technology scaling.

Asynchronous self-timed approach, on the other hand, can get the best performance in the presence of variability while still guaranteeing circuit reliability. Fig. 3.1 also shows the performance characteristic of asynchronous circuit on the blue curve. Ideally, the statistical performance of asynchronous circuit can closely follow the statistical profile of actual circuit behavior and achieve "average-case" performance.

In addition to speed enhancement, asynchronous computing can also achieve better power performance. Since the accurate timing information can be immediately obtained for an asynchronous system, circuit computation can still be realized efficiently even in the presence of variations. Fig. 3.2 shows the operating power profiles of synchronous and asynchronous systems. An asynchronous design can response and minimize the standby leakage immediately after an operation completes, instead of being limited by the worst-case delay. On the other hand, a traditional synchronous design must slow down for the worst-case variation because it has no information of real-time circuit behavior. This causes extra timing slack most of time, which translates into extra leakage waste.

Despite a better statistical performance of asynchronous operation, the overhead cost to implement a handshaking protocol might be nontrivial and may offset all the statistical performance advantages. A statistical analysis framework is therefore necessary to compare different timing schemes and determine the optimal approach in the presence of variability.

In summary, the major implementation challenge of self-timed circuit is the additional energy, delay and hardware cost from the protocol circuitry. The self-timed approach only

Figure 3.2: Power profiles of synchronous and asynchronous systems.

makes sense when this protocol circuit overhead is smaller than the circuit delay variability. On the other hand, self-timing is very attractive to realize ultra-low power digital circuits, since variations is relatively large at low supply voltages. A self-timed design can achieve average-case performance in the presence of variability. Moreover, it can dynamically control leakage paths, realizing real-time power management at fine-grain level and minimizing leakage as much as possible. This leakage minimization technique is demonstrated in two design examples introdued in chapter 4 and chapter 5. Finally, since a self-timed design operates based on request-acknowledgement handshaking control protocols, it is the most robust solution for ultra-low voltage operation.

In the following sections, a statistical analysis framework is presented to efficiently evaluate energy and delay performances of CMOS circuits with different timing schemes under process variations. The communication costs of implementing different self-timed pipeline protocols have been modeled and compared in [Stevens11], and are not discussed here. Instead, a statistical model is presented to estimate the computation costs and performance upper bounds of generic synchronous, asynchronous bundled-data and dual-rail self-timed approaches for various operating points. This is accomplished by evaluating the minimum delay overhead required to guarantee circuit functionality in the presence of variability across a wide range of supply voltage and logic depth. Note that the specific variation-tolerant circuit techniques in synchronous design such as post-silicon adaptive tuning [Hanson08], or other hybrid-timing methodologies like globally-asynchronous locally-synchronous (GALS) approach [Muttersbach00], are not discussed. The proposed analysis framework, however, can be easily extended or modified to evaluate the statistical performances of the aforementioned approaches.

#### 3.2 Modeling of CMOS Digital Circuit

A MOSFET transistor exhibits dramatically different performance characteristics in the strong-inversion and sub-threshold regions. In order to efficiently estimate the delay variability across a wide range of supply voltage, it is essential to have a generic analytical model that describes transistor behaviors across different operating regions. A unified current model that captures the most essential physical characteristics of MOSFET transistor and exhibits excellent model scalability as derived in is used in this work [Cao07]. The device current I is described as:

$$I \propto \frac{\left\{\ln\left[1 + \exp\left(\frac{V_{DD} - V_{th}}{2S}\right)\right]\right\}^2}{\left\{1 + \ln\left[1 + \exp\left(\frac{V_{DD} - V_{th}}{m}\right)\right]\right\}}$$

(3.1)

where S is the sub-threshold swing parameter and m is the parameter modeling the effect of velocity saturation.

In the strong-inversion region where the exponential term dominates, Eq. 3.1 becomes the well-known square-law formula with velocity saturation effect

$$I \propto \frac{\left(V_{DD} - V_{th}\right)^2}{1 + \left(\frac{V_{DD} - V_{th}}{m}\right)} \tag{3.2}$$

Similarly, in the sub-threshold region, the exponential term is much smaller than the constant 1 term. Eq. 3.1 can be simplified as

$$I \propto \exp\left(\frac{V_{DD} - V_{th}}{S}\right) \tag{3.3}$$

#### 3.2.1 Delay Model

The delay model of CMOS gate across a wide range of supply voltage can now be derived based on Eq. 3.1. After substituting Eq. 3.1 into the Alpha-power law model for device current, the gate delay  $T_d$  can be expressed as [Sakurai90, Cao07]:

$$T_d \propto \frac{CV_{DD}}{I} = \frac{K \cdot V_{DD} \cdot \left\{1 + \ln\left[1 + \exp\left(\frac{V_{DD} - V_{th}}{m}\right)\right]\right\}}{\left\{\ln\left[1 + \exp\left(\frac{V_{DD} - V_{th}}{2S}\right)\right]\right\}^2}$$

(3.4)

where k is the delay-fitting parameter.

To extract delay model parameters in Eq. 3.2, supply voltages from 300mV to 1V are swept for an industrial 65nm CMOS technology. Fig. 3.3 shows the nominal delay predicted by Eq. 3.4 and simulated results as a function of  $V_{DD}$  for a four-stage fanout-of-four (4FO4)

Figure 3.3: Simulated and modeled delay of a 4FO4 inverter chain in 65nm CMOS technology.

inverter chain. The model error is smaller than 5% across the entire range of supply voltage, which demonstrates the accurate prediction of CMOS gate delay in both the strong-inversion and sub-threshold regions. The unified delay model Eq. 3.4 is used in the next section as a baseline to derive a delay variability model.

#### 3.2.2 Variability Model

To estimate the delay variability of a CMOS gate, two major parametric variation components are considered: threshold voltage variations due to random dopant fluctuations, and geometric variations due to fluctuations of device length, width and oxide thickness [Ghosh10]. If the variations in devices parameters follow the Gaussian statistical distribution, the delay variability of CMOS gate can be estimated directly from Eq. 3.4. The normalized variation of gate delay  $\frac{\sigma_{T_d}}{\mu_{T_d}}$  due to parametric variations can be thus given by

$$\frac{\sigma_{T_d}}{\mu_{T_d}} = \sqrt{\left(S_{T_d}^{v_{th}}\right)^2 \cdot \left(\frac{\sigma_{V_{th}}}{\mu_{V_{th}}}\right)^2 + \left(S_{T_d}^K\right)^2 \cdot \left(\frac{\sigma_K}{\mu_K}\right)^2} \tag{3.5}$$

where

$$S_{T_d}^{V_{th}} = \frac{\partial V_{th}/V_{th}}{\partial T_d/T_d}$$

and  $S_{T_d}^K = \frac{\partial K/K}{\partial T_d/T_d}$  (3.6)

Figure 3.4: Simulated and modeled delay variability results.

After actual manufacturing process, the transistors will have different die-to-die (inter-die; DTD) and within-die (intra-die; WID) variation behaviors [Bowman02]. Both DTD and WID variation behaviors can be estimated using Eqs. 3.5 and 3.6. However, since DTD and WID variations affect circuit performances in completely different ways, they must be estimated separately to derive the total delay variability model accounting for both variations. If DTD and WID variations are completely independent, the combined effects on delay variability of CMOS gate can be expressed as

$$\frac{\sigma_{T_{d,total}}}{\mu_{T_{d,total}}} = \sqrt{\left(\frac{\sigma_{T_{d,DTD}}}{\mu_{T_{d,DTD}}}\right)^2 + \left(\frac{\sigma_{T_{d,WID}}}{\mu_{T_{d,WID}}}\right)^2}$$

(3.7)

Fig. 3.4 shows the estimated delay variation results using Eqs. 3.5 to 3.7 as a function of  $V_{DD}$  for a 4FO4 inverter chain, as well as the simulation results using Monte Carlo SPICE simulator. The simulation results show that the model accurately predicts delay variability due to DTD and WID variations. DTD variation is the dominant delay variation source at high supply voltages, while the impact of WID variation grows rapidly as the supply voltage is lowered. The model error is smaller than 8% across the entire range of supply voltage. In this work, Eqs. 3.5 to 3.7 are used as delay variability models to estimate the delay variability of CMOS circuit under process variations. More parametric variation components can be easily incorporated in Eqs. 3.5 and 3.6 to increase model accuracy.

#### 3.2.3 Circuit Delay Variability with Different Logic Depths

If WID variations are completely random, it has been shown that a longer logic path with more gate stages is expected to have less variability from WID variations since timing variations are averaged out [Eisele96]. However, circuits with longer logic path cannot reduce the impact of DTD variations. If each state delay in a logic path is completely independent and random, Eq. 3.7 can be modified to include the effect of logic depth on delay variability as

$$\frac{\sigma_{T_{d,total}_{n}}}{\mu_{T_{d,total}_{n}}} = \sqrt{\left(\frac{\sigma_{T_{d,DTD}_{-4}}}{\mu_{T_{d,DTD}_{-4}}}\right)^{2} + \left(\frac{4}{n}\right) \cdot \left(\frac{\sigma_{T_{d,WID}_{-4}}}{\mu_{T_{d,WID}_{-4}}}\right)^{2}}$$

(3.8)

where n is the logic depth,  $\frac{\sigma_{T_{d,DTD}\_4}}{\mu_{T_{d,DTD}\_4}}$  and  $\frac{\sigma_{T_{d,WID}\_4}}{\mu_{T_{d,WID}\_4}}$  are the normalized DTD and WID delay variability of a 4FO4 inverter chain, respectively. The delay variability model of a 4FO4 inverter chain is employed as a baseline model to estimate the delay variability of an nFO4 inverter chain. To verify the scalability of Eq. 3.8, the delay variability results predicted by Eq. 3.8 are compared with the Monte Carlo SPICE simulation results for n=8 and 24, as shown in Fig. 3.5. The model error is smaller than 13% for n=8, and smaller than 15% for n=24 across the entire range of supply voltage. Since delay variability models Eqs. 3.5 to 3.8 are derived directly from a closed-form formula, the impact of process variations on circuit performance across a wide range of supply voltage and logic depth can be efficiently estimated, instead of performing extensive Monte Carlo SPICE simulations. This enables designers to perform design exploration and system optimization much more efficiently at early design stage.

In the next section, a statistical model is introduced to evaluate performance characteristics of synchronous and asynchronous digital circuits in the presence of delay variability.

### 3.3 Statistical Analysis of Synchronous and Asynchronous Timing Schemes

In order to deal with the delay variability due to process variations, traditional synchronous digital circuits must slow down to meet a certain reliability requirement. Asynchronous circuits, on the other hand, can exploit local timing information to achieve both reliability and "average-case" performance in the presence of variability. Although the advantages of asynchronous timing are well known, the actual statistical performance gain and implementation overhead of asynchronous circuit under process variations have not been investigated quantitatively. In this section, a statistical model is introduced to analyze the performances of synchronous and asynchronous circuits in the presence of delay variability.

Figure 3.5: Simulated and modeled delay variability results for different logic depths.

#### 3.3.1 Synchronous Approach

If process variations in a digital circuit follow the Gaussian statistical distribution, the delay variability of a critical path can be modeled as a normal distribution with a probability density function

$$f_{logic}(t) = N\left(\mu_{logic}, \sigma_{logic}^2\right) \tag{3.9}$$

where  $\mu_{logic}$ , and  $\sigma_{logic}$  are the mean and standard deviation of the critical path delay, respectively. The probability of a critical path satisfying a specified period of synchronous clock  $t_{sync}$  can be given by

$$P\left(t_{logic} \le t_{sync}\right) = \int_{0}^{t_{sync}} f_{logic}\left(t\right) dt \tag{3.10}$$

In order to achieve a yield of 99.7%,  $t_{sync}$  is set to  $(\mu_{logic} + 3\sigma_{logic})$  in conventional synchronous designs. As a result, a " $3\sigma$  worst-case" synchronous design will fail to exercise the whole circuit capacity after actual fabrication most of time, which indicates a statistical performance loss. In this work, this statistical performance loss of synchronous design under process variations is defined as a delay overhead required to implement a synchronous

timing scheme. Both DTD and WID variations contribute to delay overhead in conventional synchronous designs. The normalized delay overhead  $D_{sync}$  of synchronous design is given by

$$D_{sync} = \frac{3\sigma_{logic,total}}{\mu_{logic,total}} \tag{3.11}$$

#### 3.3.2 Bundled-Data Self-Timed Approach

Bundled-data self-timed approach employs an additional delay line to generate local control signals instead of using a global clock [Sparsø01]. The delay line is designed to exhibit similar delay characteristics to the circuit critical path. Therefore, a bundled-data approach is effective to eliminate the impact of DTD variations. WID variations, however, would still cause delay mismatches between a critical path and a delay line, which poses a major performance limitation in a bundled-data self-timed design. The statistical performance of bundled-data self-timed scheme is evaluated by assuming that the delay variability of delay line can also be modeled as a normal distribution

$$f_{delay-line}(t) = N\left(\mu_{delay-line}, \sigma_{delay-line}^2\right)$$

(3.12)

In order to ensure a reliable timing generation, the delay of delay line must be always larger than the critical path delay in the presence of process variations. This timing constraint is specified by

$$P\left(t_{logic} \le t_{delay-line}\right) \approx 1$$

(3.13)

In actual circuit implementation, a delay line is usually just a replica of main circuit critical path with more gate stages. Therefore, it is reasonable to further assume that a replica delay line and a circuit critical path exhibit similar statistical characteristics that can be expressed as

$$\mu_{delay-line} - \mu_{logic} = D_{bundled-data} \cdot \mu_{logic} \tag{3.14}$$

$$\sigma_{delay-line}^2 = (D_{bundled-data} + 1) \cdot \sigma_{logic}^2 \tag{3.15}$$

where  $D_{bundled-data}$  is the normalized delay overhead of bundled-data self-timed scheme, which indicates the number of additional gate stage required for a replica delay line to satisfy Eq. 3.13. If the final yield requirement is still 99.7%,  $D_{bundled-data}$  can be calculated by solving Eqs 3.12 to 3.15:

Figure 3.6: Delay overhead characteristics of bundled-data self-timed scheme.

$$D_{bundled-data} = D_{variation}^2 \cdot \left(\frac{1}{2} + \sqrt{\frac{1}{4} + \frac{2}{D_{variation}^2}}\right)$$

(3.16)

where

$$D_{variation} = \frac{3\sigma_{logic,WID}}{\mu_{logic,WID}} \tag{3.17}$$

$$D_{bundled-data} \propto \begin{cases} \sqrt{2} \cdot D_{variation} & when D_{variation} \to 0\\ D_{variation}^2 & when D_{variation} \to \infty \end{cases}$$

(3.18)

Note that only WID variation contributes to  $D_{variation}$  in a bundled-data design. Fig. 3.6 shows the normalized delay overhead  $D_{bundled-data}$  as a function of process variability  $D_{variation}$ . It is clear that the delay overhead of bundled-data self-timed scheme has different characteristics as the amount of process variation changes. While  $D_{bundled-data}$  increases linearly with small  $D_{variation}$ , its dependency on  $D_{variation}$  becomes quadratic as  $D_{variation}$  becomes large.

#### 3.3.3 Dual-Rail Self-Timed Approach

Another popular asynchronous self-timed scheme, dual-rail self-timed approach, uses dual-rail encoding to represent the data, and four-phase handshaking protocol to ensure a reliable operation [Sparsø01]. Since a dual-rail self-timed design responses immediately after a computation, its performance can closely follow the actual circuit delay statistics, as shown in Fig. 3.1. As a result, a dual-rail self-timed design would not have delay overhead to compensate the timing variability of critical path. Despite its better statistical performance, a dual-rail self-timed design must employ additional circuitry to implement dual-rail handshaking protocol and completion detection. This extra delay overhead from protocol circuit may not be trivial, and must be considered in final performance evaluation and optimization. To account for this protocol overhead, the delay of the protocol circuitry is estimated and added to the final critical path delay. Note that a bundled-data self-timed design would also require additional protocol circuitry, but the corresponding protocol overhead is much smaller than a dual-rail design since it can be utilized as part of matched delay line without slowing down system speed.

In the next section, the statistical performance models developed in this section, combined with the variability model of CMOS circuit developed in section 3.2, is employed to evaluate energy and delay performances of CMOS digital circuits with different timing methodologies.

# 3.4 Performance Comparison

In the previous section, a statistical model to analyze the performances of synchronous and asynchronous circuits under process variations is presented. Together with the delay variability model of CMOS circuit developed in section 3.2, the impacts of process variations on synchronous and asynchronous CMOS digital circuits across a wide range of supply voltage and logic depth can be evaluated. In this section, the delay and energy performances of different timing schemes are first evaluated. The proposed statistical analysis framework is then used to determine the optimal timing strategy, pipeline depth and supply voltage under process variations for a low-energy application example.

# 3.4.1 Speed Performance

Table 3.1 summaries the delay overheads required to implement different timing schemes.  $P_{bundled-data}$  and  $P_{dual-rail}$  represent the normalized delay overheads of protocol circuits associated with bundled-data and dual-rail self-timed designs, respectively. The total delay here represents the time required to correctly evaluate a logic function in the presence of process variations. The latency and cycle time performances, which must be evaluated with respect to the actual implementation of handshaking control protocol, are not discussed here.

Eqs. 3.5 to 3.8, Eq. 3.11 and Eq. 3.16 are first used to estimate  $D_{sync}$  and  $D_{bundled-data}$  associated with CMOS digital circuits under process variations. As discussed in section

|               | -                    | · ·                     | ~                                                     |

|---------------|----------------------|-------------------------|-------------------------------------------------------|

| Timing Scheme | Delay Overhead $(D)$ | Protocol Overhead $(P)$ | Total Delay                                           |

| Synchronous   | $D_{sync}$           | -                       | $t_{logic} \left(1 + D_{sync}\right)$                 |

| Bundled-Data  | $D_{bundled-data}$   | $P_{bundled-data}$      | $t_{logic} (1 + D_{bundled-data} + P_{bundled-data})$ |

| Dual-Rail     | -                    | $P_{dual-rail}$         | $t_{logic} \left(1 + P_{dual-rail}\right)$            |

Table 3.1: Speed Performance Analysis Model

Figure 3.7: Delay overhead characteristics of synchronous and bundled-data schemes for a critical path delay of 4FO4.

Figure 3.8: Delay overhead characteristics of synchronous and bundled-data schemes for a critical path delay of 24FO4.

3.2, DTD variations is assumed to affect only synchronous approach, while WID variations influence both synchronous and bundled-data designs. Fig. 3.7 shows the delay overhead results of synchronous and bundled-data schemes for a critical path delay of 4FO4 as the supply voltage varies from 300mV to 1V. As the supply voltage is lowered,  $D_{bundled-data}$  becomes larger and eventually greater than  $D_{sync}$ . This is because WID variations become larger and dominate at low supply voltages as shown in Fig. 3.4. This causes  $D_{bundled-data}$  to increase rapidly as predicted by Eq. 3.16. Therefore, a bundled-data design operating below 600mV would suffer more delay overheads than a synchronous approach. Fig. 3.8 shows the delay overheads required for a larger critical path delay of 24FO4. Since a longer critical path with more gate stages can greatly reduce the impact of WID variations, a bundled-data design now has less delay overheads than a synchronous approach across the entire supply range.

To compare the total delay required to perform synchronous and asynchronous computations, both delay overhead D and protocol overhead P are considered as summarized in table 3.1. In actual circuit implementations, a bundled-data design can utilize its protocol overhead as part of matched delay line to improve the speed. As a result,  $P_{bundled-data}$  is set to 1FO4 first assuming that the overall protocol delay can be less than one-stage delay after optimization. A dual-rail design, on the other hand, requires additional completion detection circuitry and cannot utilize it as part of matched delay line.  $P_{dual-rail}$  is set to 2FO4 to account for this extra delay of completion detection since the completion detector is usually

Figure 3.9: Speed performances of bundled-data and dual-rail schemes for a critical path delay of 4FO4. The delay is normalized to the synchronous design.

a single-stage NOR/NAND gate. Note that the protocol overhead here is independent of the number of logic stages, and is simply estimated to the first order to demonstrate the design tradeoff and its impact on the overall speed performance. The actual protocol overhead of an asynchronous scheme can be determined after actual circuit implementation.

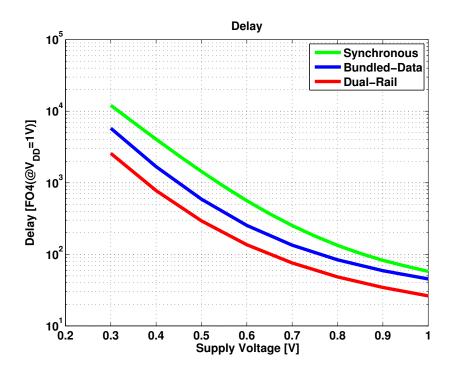

Fig. 3.9 shows the estimated speed performances of bundled-data and dual-rail asynchronous circuits for a critical path delay of 4FO4 as the supply voltage varies from 300mV to 1V. The performances of both asynchronous approaches are normalized to the synchronous design. For this specific design example, a synchronous design achieves better speed performance at high supply voltages, while a dual-rail approach performs better below 450mV where circuit delay variability becomes larger. Fig. 3.10 shows another example of larger critical path delay of 24FO4. Both asynchronous designs now have better speed performances than synchronous approach. This is because for circuits with larger critical path delay, protocol overhead becomes relatively smaller than delay overhead required to guarantee reliability under process variations. In summary, for a circuit topology with fixed critical path delay, a synchronous timing scheme is a better choice for high-speed applications with smaller critical path delay operating at higher supply voltages, while a dual-rail self-timed scheme performs better when the protocol overhead is relatively small compared to the circuit critical path delay.

Figure 3.10: Speed performances of bundled-data and dual-rail schemes for a critical path delay of 24FO4. The delay is normalized to the synchronous design.

# 3.4.2 Energy Performance

The energy per operation of a CMOS gate  $E_{total}$  contains both active and leakage components, as shown in Eq. 2.8. An asynchronous design has a larger  $C_{switch}$  and  $I_{leak}$  than a synchronous design due to additional protocol circuit overheads, but may have small  $T_d$  under process variations as discussed in the previous section. Assuming that the extra leakage and switched capacitance from implementing an asynchronous self-timed scheme is also proportional to the protocol overhead P in table 3.1, the computation energy of a datapath under process variations can be estimated as

$$E_{total} = \alpha C_{switch} (1+P) V_{DD}^2 + V_{DD} I_{leak} (1+P) T_d (1+P+D)$$

(3.19)

Note that Eq. 3.19 evaluates only the average computation energy of a datapath in the presence of variability. The corresponding communication energy with different timing schemes, such as clocking network in synchronous design and delay line in bundled-data design, is not included in Eq. 3.19. Fig. 3.11 and Fig. 3.12 show the estimated energy consumption of a 24FO4 inverter chain using different timing schemes as a function of supply voltage for  $\alpha = 0.1$  and  $\alpha = 0.01$ , respectively. The simulation results show that if the circuit activity is high and active energy dominates, a synchronous approach generally consumes less computation energy. However, if a circuit has a low activity factor operating at low supply

Figure 3.11: Energy performances of a 24FO4 inverter chain with different timing schemes for  $\alpha = 0.1$ .

voltages, leakage energy becomes the dominant component of total energy consumption. An asynchronous design now demonstrates better energy performances especially at low supply voltages, as shown in Fig. 3.12. This is because both bundled-data and dual-rail designs have smaller idle time than a synchronous design in the presence of variability, and therefore consume less leakage energy and achieve better overall energy performance.

# 3.5 Summary

Asynchronous self-timed schemes allow for an adaptive adjustment to delay variations and support for an inherent leakage minimization for both static and dynamic variations, indicating a robust and energy-efficient alternative for ultra-low voltage operation. A statistical analysis framework is presented to evaluate energy and delay performances of CMOS digital circuits with different timing methodologies in the presence of variability. The proposed analysis framework consists of two parts: a delay variability model of CMOS circuit and a statistical performance model of synchronous and asynchronous timing schemes. The variability model accurately estimates the impact of process variations on speed performance of CMOS circuits operating in both the strong-inversion and subthreshold regions with different logic depths. The statistical performance model efficiently predicts the delay overheads required to implement synchronous, bundled-data and dual-rail self-timed schemes under

Figure 3.12: Energy performances of a 24FO4 inverter chain with different timing schemes for  $\alpha = 0.01$ .

process variations. By using the proposed statistical analysis framework, designers can efficiently evaluate energy and delay performances of CMOS digital circuit under process variations, and perform system optimization considering a variety of timing methodologies and design parameters such as logic depth and supply voltage, instead of performing extensive Monte Carlo SPICE simulations.

Based on the proposed statistical models and inverter chain simulation results in 65nm CMOS technology, the analysis shows that in the presence of variability, a synchronous design generally demonstrates better delay performance for high-speed applications and consumes lower computation energy for circuits with high activity. On the other hand, an asynchronous design exhibits better energy and delay characteristics for circuits with low activity and larger critical path delay. Note that since the delay variability of CMOS transistor actually follows the log-normal distribution in sub-threshold region, an asynchronous design is expected to perform even better at low supply voltages. For future technology nodes with smaller transistor dimensions, both process variations and their impact on circuit performance would become even significant. As a result, a timing methodology that is capable of achieving better statistical performance in the presence of variability, such as asynchronous dual-rail self-timed scheme, would be a promising approach for future CMOS digital circuit design.

In the next two sections, two implementation examples using asynchronous self-timed circuits for ultra-low energy applications are presented. Self-timed circuit designs using sense

amplifier-based pass transistor logic are first introduced. After that, a self-timed neural signal processor for brain-machine interfaces is presented.

# Chapter 4

# Case Study I: Asynchronous SAPTL Design

Lowering the supply voltage effectively reduces dynamic energy consumption but is accompanied by a dramatic increase in leakage energy due to the lower device threshold voltage needed to maintain performance. As a result, for low-energy applications, the leakage energy that the system can tolerate ultimately sets the minimum total energy point and limits the minimum device threshold voltage. Speed, therefore, benefits little from technology scaling. The sense amplifier-based pass transistor logic (SAPTL) [Alarcón07] is a novel circuit topology that breaks this tradeoff to realize very low energy logic without sacrificing speed. SAPTL modules were initially designed to operate synchronously. In this chapter, asynchronous operation is introduced in SAPTL to further improve energy-delay performance.

This chapter presents two different approaches to realize self-timed SAPTL: the bundled-data and the dual-rail handshaking protocol. Section 4.1 introduces the basic operation and circuit architecture of SAPTL. Section 4.2 defines the handshaking protocol between two SAPTL modules to realize self-timed operation. A self-timed SAPTL architecture with bundled-data protocol is presented including the circuit architecture and a detailed performance analysis. Section 4.3 introduces a glitch-free adaptation to the handshaking protocol between self-timed SAPTL modules that can further improve robustness and performance. Section 4.4 presents the design and implementation of self-timed SAPTL with a dual-rail protocol. Section 4.5 shows the test chip implementation of self-timed SAPTL in 90nm CMOS technology. Section 4.6 shows the simulated and measured energy, delay, and leakage of various self-timed SAPTL circuits with different handshake protocols. Section 4.7 concludes this chapter.

#### 4.1 SAPTL Architecture

Fig. 4.1 shows the basic architecture of a SAPTL circuit, which is composed of a stack, a driver, and a sense amplifier [Alarcón07].

Figure 4.1: Architecture of SAPTL module with synchronous timing control.

#### 4.1.1 Stack and Driver

The stack consists of an NMOS-only pass transistor tree with full-swing inputs and low-swing pseudo-differential outputs to perform the required logic function, as shown in Fig. 4.2. The stack can implement a given Boolean expression by connecting the minterm branches of the tree to one output, and the maxterm branches to the other as illustrated by the programming switches in the diagram. In this implementation, the logic function of a SAPTL stack is determined and permanently fixed at fabrication by replacing the programming switches with hardwired connections. Because the stack has no supply rail connections, it does not contribute sub-threshold leakage current, and it also has no gain.

Because the stack has no supply rail connections, a driver, which is a simple inverter in this example, is placed at the root input of the stack to inject the evaluation current. In operation, either Sout or  $\overline{Sout}$ , but not both, is charged toward the supply rail when the driver energizes the selected path through the stack. After each computation and before every evaluation, both differential outputs are reset to ground (logical "0") to initialize the stack to a known state. This initialization is done by turning on all the transistors in the stack and draining the charges out through the root of the stack when the driver output is zero. The alternate charging and resetting of Sout or  $\overline{Sout}$  realizes a standard dual-rail encoding [Sparsø01].

The speed of the SAPTL module depends strongly on the depth of the stack,  $N_{stack}$ , which is defined as the number of transistors in series from the root node to the differential outputs. Because the stack contributes no sub-threshold leakage current, the stack transistors can have a very low threshold voltage and still operate in the super-threshold region even with a very low supply voltage. Therefore, SAPTL is a promising candidate to realize ultra-low energy computation without soliciting sub-threshold operation [Alarcón07].

Figure 4.2: Schematic of a two-input stack with  $N_{stack} = 5$ .

## 4.1.2 Sense Amplifier