# A Framework for Composing High-Performance OpenCL from Python Descriptions

Michael Anderson

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2014-210 http://www.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-210.html

December 5, 2014

Copyright © 2014, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## A Framework for Composing High-Performance OpenCL from Python Descriptions

by

Michael Jeffrey Anderson

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Kurt Keutzer, Chair Professor James Demmel Associate Professor Sara McMains

Fall 2014

## A Framework for Composing High-Performance OpenCL from Python Descriptions

$\begin{array}{c} {\rm Copyright~2014} \\ {\rm by} \\ {\rm Michael~Jeffrey~Anderson} \end{array}$

#### Abstract

A Framework for Composing High-Performance OpenCL from Python Descriptions

by

Michael Jeffrey Anderson

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley

Professor Kurt Keutzer, Chair

Parallel processors have become ubiquitous; most programmers today have access to parallel hardware such as multi-core processors and graphics processors. This has created an implementation gap, where efficiency programmers with knowledge of hardware details can attain high performance by exploiting parallel hardware, while productivity programmers with application-level knowledge may not understand low-level performance trade-offs. Ideally, we would like to be able to write programs in productivity languages such as Python or MATLAB, and achieve performance comparable to the best hand-tuned code.

One approach toward achieving this ideal is to write libraries that get high efficiency on certain operations, and call these libraries from the productivity environment. We propose a framework that addresses two problems with this approach: that it fails to fuse operations for efficiency, and that it may not consider runtime information such as shapes and sizes of data structures. With our framework, efficiency programmers write and/or generate customized OpenCL snippets at runtime and the framework automatically fuses, compiles, and executes these operations based on a Python description.

We evaluate the framework with case studies of two very different applications: space-time adaptive radar processing and optical flow. For a space-time adaptive radar processing application, our framework's implementation is competitive with a hand-coded implementation that uses a vendor-optimized library. For optical flow, a computer vision application, the framework achieves frame rates that are between  $0.5\times$  and  $0.97\times$  hand-coded OpenCL performance.

## Contents

| $\mathbf{C}$ | onter                                         | nts                                        |                                                              |

|--------------|-----------------------------------------------|--------------------------------------------|--------------------------------------------------------------|

| Li           | st of                                         | Figures                                    | iv                                                           |

| Li           | $\mathbf{st}$ of                              | Tables                                     | v                                                            |

| 1            | Intr<br>1.1<br>1.2                            | Thesis Contributions                       |                                                              |

| 2            | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | Reground and Motivation  Parallel Hardware | . 8<br>. 9<br>. 15<br>. 15                                   |

| 3            | Opt 3.1 3.2 3.3 3.4 3.5 3.6 3.7 3.8           | Introduction                               | . 22<br>. 26<br>. 28<br>. 3 <sup>2</sup><br>. 3 <sup>3</sup> |

| 4            | Opt 4.1 4.2 4.3                               | Introduction                               | . 42                                                         |

CONTENTS ii

|   | 4.4<br>4.5<br>4.6<br>4.7                                                    | One Problem Per Thread                               | 45<br>47<br>56<br>57                                                       |

|---|-----------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------|

|   | 4.8                                                                         | Conclusion                                           | 57                                                                         |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11 |                                                      | 59<br>59<br>61<br>62<br>63<br>64<br>65<br>70<br>73<br>75<br>79<br>80<br>83 |

| 6 | Case<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                       | e Study: Space-Time Adaptive Processing Introduction | 84<br>86<br>90<br>90<br>91<br>96                                           |

| 7 | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9<br>7.10         |                                                      | 98<br>98<br>99<br>102<br>106<br>109<br>112<br>114<br>115<br>116<br>117     |

| 8 | <b>Sum</b>                                                                  | nmary and Conclusion                                 | 118                                                                        |

| CONTENTS        | iii |

|-----------------|-----|

| 8.1 Future Work | 120 |

| Bibliography    | 121 |

## List of Figures

| 2.1  | NVIDIA Fermi GPU system diagram                                                 | 7  |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Intel Haswell quad-core CPU system diagram                                      | 8  |

| 2.3  | The parallel programming problem                                                | 10 |

| 2.4  | Our Pattern Language                                                            | 16 |

| 2.5  | Jacobi solver software architecture                                             | 17 |

| 3.1  | lacktriangle                                                                    | 23 |

| 3.2  | Stages of Tall-Skinny QR                                                        | 24 |

| 3.3  | Communication-Avoiding QR                                                       | 26 |

| 3.4  | CAQR host pseudocode with binomial reduction tree                               | 29 |

| 3.5  | Matrix-vector multiply and rank-1 update                                        | 31 |

| 3.6  | Distributed data layout in register file                                        | 32 |

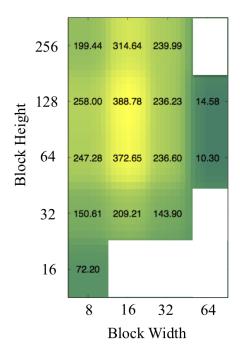

| 3.7  | Performance in GFLOPS for different block sizes                                 | 33 |

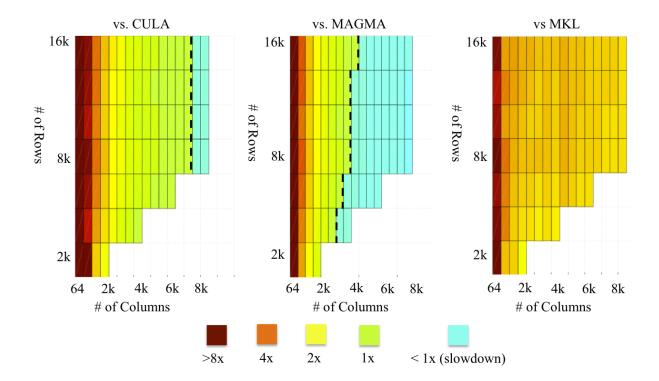

| 3.8  | Speedup vs. SGEQRF from popular libraries                                       | 34 |

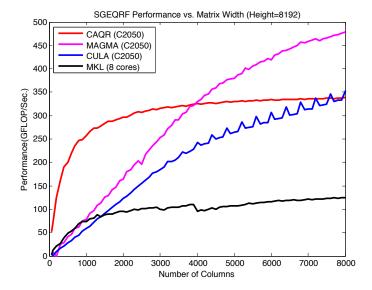

| 3.9  | Performance in GFLOPS vs. matrix width                                          | 36 |

| 3.10 | Video background subtraction sample output                                      | 37 |

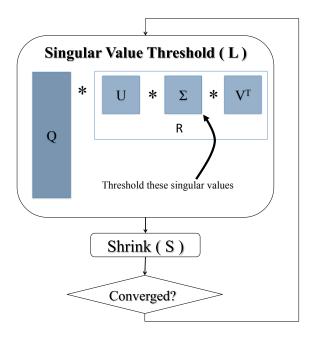

| 3.11 | Alternating-directions algorithm                                                | 39 |

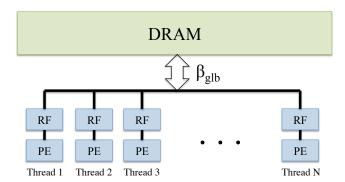

| 4.1  | Simplified GPU model for the one-problem-per-thread approach                    | 45 |

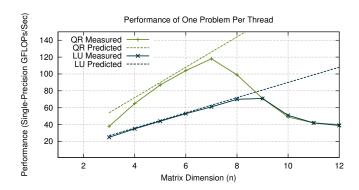

| 4.2  | Performance for 64,000 independent small QR and LU (no pivoting) factorizations | 46 |

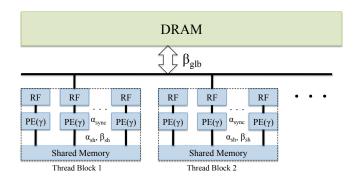

| 4.3  | Complete GPU model for one-problem-per-block approach                           | 47 |

| 4.4  | 2D cyclic layout and 1D row cyclic layout                                       | 48 |

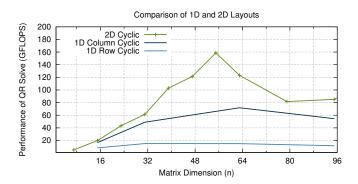

| 4.5  | Performance of varous data layouts for one-problem-per-block approach           | 49 |

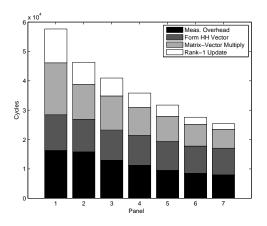

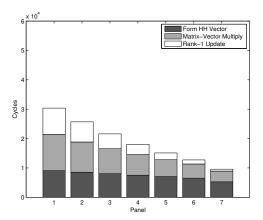

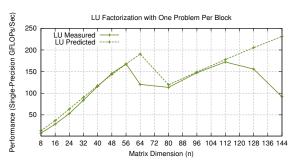

| 4.6  | Number of cycles on QR measured vs. modeled                                     | 51 |

| 4.7  | Performance of 8,000 LU and QR factorizations with one-problem-per-block ap-    |    |

|      | proach                                                                          | 53 |

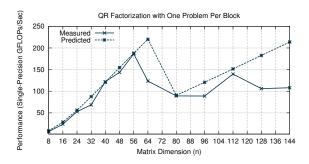

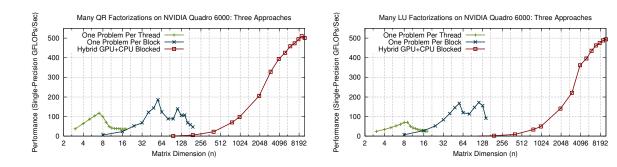

| 4.8  | Performance of different approaches vs. matrix size                             | 55 |

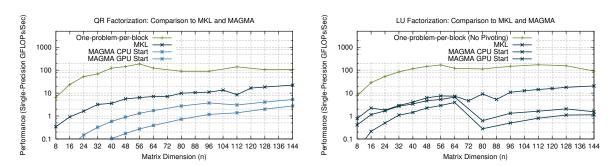

| 4.9  | Performance of one-problem-per-block approach compared to other libraries on    |    |

|      | LU and QR                                                                       | 55 |

| 5.1  | Structural patterns for Jacobi solver example                                   | 63 |

| 5.2  | Iteration space for our OpenCL kernels                                          | 66 |

LIST OF FIGURES v

| 5.3  | Kernel fusion of a vector addition operation and a vector squaring operation 71     |

|------|-------------------------------------------------------------------------------------|

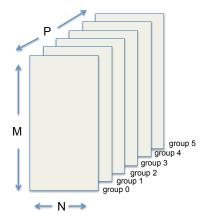

| 5.4  | Example partitioning of a 3D array across work groups                               |

| 5.5  | Basic blocks for the Jacobi solver example                                          |

| 5.6  | Demonstrating kernel fusion for the Jacobi solver example                           |

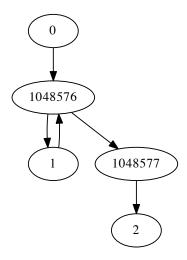

| 6.1  | Key computational kernels for the STAP application                                  |

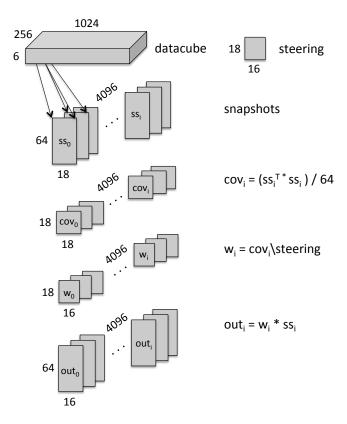

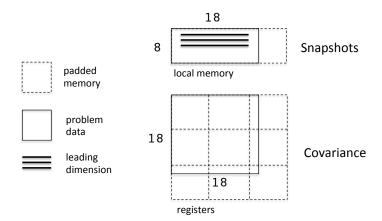

| 6.2  | Data layout of outer products kernel                                                |

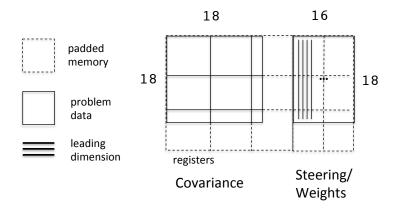

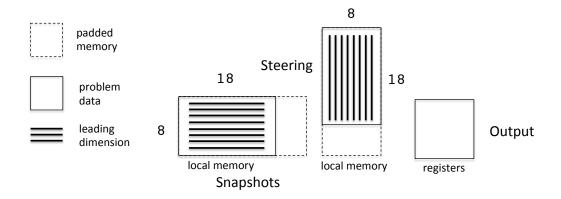

| 6.3  | Data layout of system solve kernel                                                  |

| 6.4  | Data layout of inner products kernel                                                |

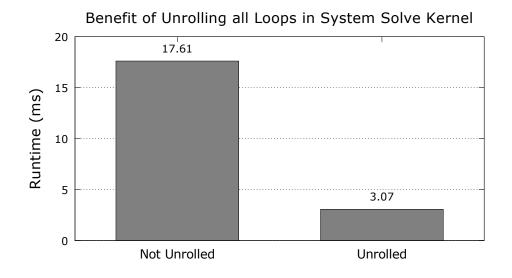

| 6.5  | Runtime for unrolled system solve kernel                                            |

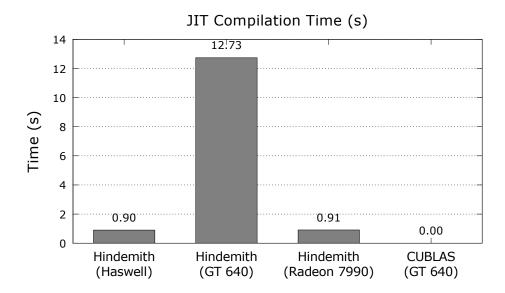

| 6.6  | Time spent in JIT compilation phase for STAP on various machines 92                 |

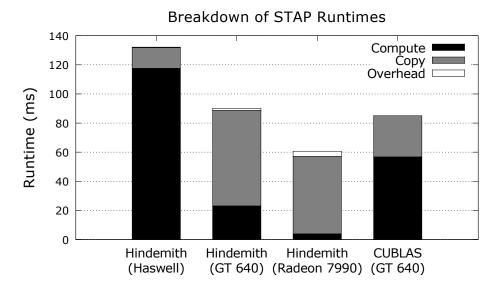

| 6.7  | Runtime for STAP for Hindemith implementation on various machines 92                |

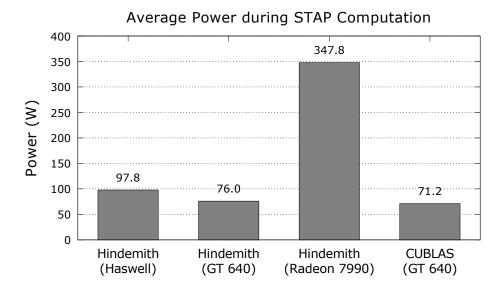

| 6.8  | Average power consumption measured during compute portion of STAP 94                |

| 6.9  | Energy expended during compute portion of STAP                                      |

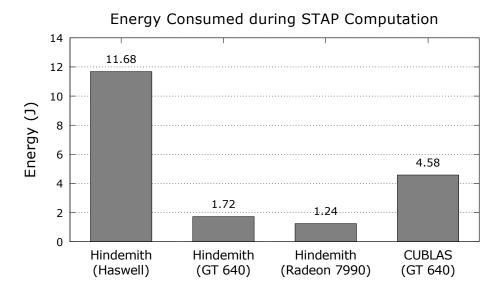

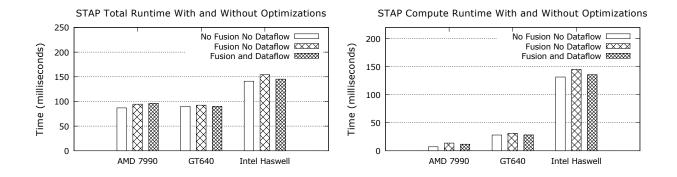

| 6.10 | Runtime of STAP application with and without fusion and dataflow optimizations 95   |

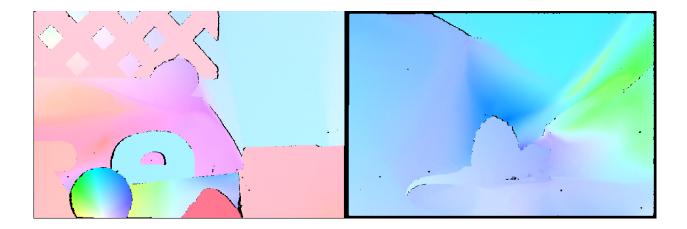

| 7.1  | Visualization of ground truth optical flow from the Middlebury benchmark dataset 99 |

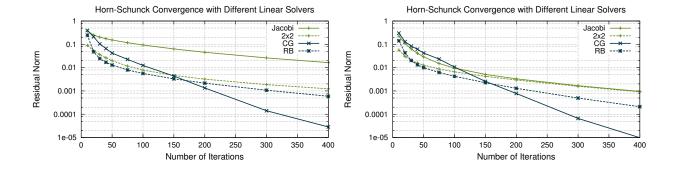

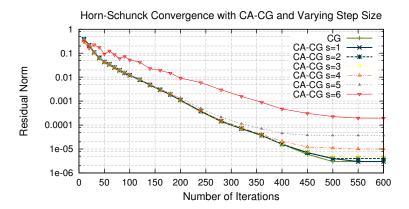

| 7.3  | Convergence of different linear solvers                                             |

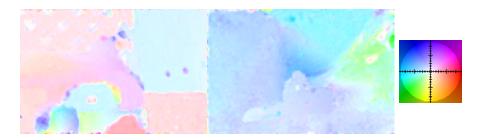

| 7.4  | Visualization of Horn-Schunck flow field                                            |

| 7.5  | Visualization of Lucas-Kanade flow field                                            |

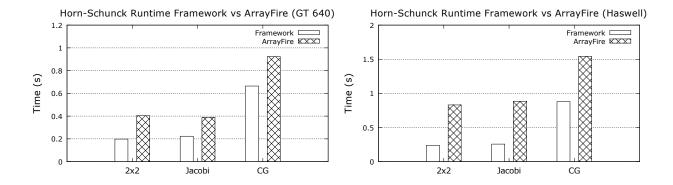

| 7.6  | Runtime for Horn-Schunck vs. ArrayFire                                              |

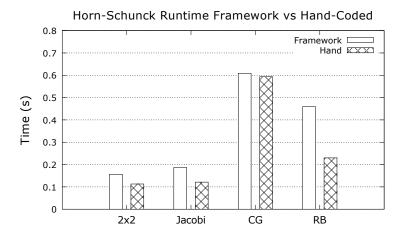

| 7.7  | Runtime for Horn-Schunck vs. hand-coded                                             |

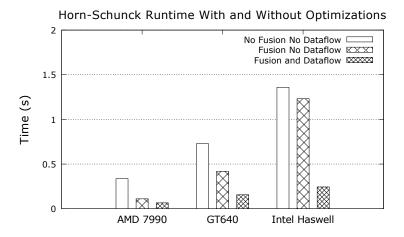

| 7.8  | Runtime for Horn-Schunck with and without optimizations                             |

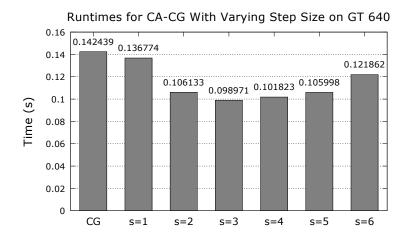

| 7.9  | Runtime for Horn-Schunck optical flow using communication-avoiding CG with          |

|      | varying step sizes                                                                  |

| 7.10 | Convergence of communication-avoiding linear solvers for Horn-Schunck 116           |

## List of Tables

| 3.1<br>3.2               | Performance for very tall-skinny matrices                                                                                                              | 36<br>39             |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 4.1<br>4.2<br>4.3<br>4.4 | NVIDIA GF100 summary                                                                                                                                   | 43<br>43<br>51<br>54 |

| 5.1<br>5.2<br>5.3        | Launch parameters for Array2DOp operation                                                                                                              | 69<br>75<br>76       |

| 6.1                      | Runtime for various implementations of STAP on different platforms                                                                                     | 93                   |

| 7.1<br>7.2               | Performance measurements for Horn-Schunck and Lucas-Kanade optical flow Performance and accuracy results for Horn-Schunck using a multi-level approach |                      |

LIST OF TABLES vii

#### Acknowledgments

I would like to express thanks to Kurt Keutzer for advising me and providing encouragement and direction. I would also like to thank the rest of my committee: Jim Demmel, Kathy Yelick, David Wessel, and Sara McMains.

I received a great deal of help and support from current and former members of the PALLAS group, including Jike Chong, Bryan Catanzaro, Mark Murphy, Bor-Yiing Su, Narayanan Sundaram, David Sheffield, Katya Gonina, Patrick Li, Peter Jin, Forrest Iandola, Zach Rowinski, and Matt Moskewicz. Specific thanks to David Sheffield for his close collaboration on several projects and daily interactions in the lab. Also to Bryan Catanzaro for helpful discussions and for sharing his enthusiasm for GPU computing. Bryan's work on the Copperhead framework laid the foundation for the framework described in this dissertation. Katya Gonina's work on PyCASP connected the ideas of SEJITS, structural patterns, and composition, which helped to motivate and organize my framework. Thanks to Narayanan Sundaram for frequent discussions. Narayanan's work on dense optical flow led to my focusing on this application as a case study in this dissertation. Finally, to Patrick Li for helping me with my dissertation talk.

I also want to acknowledge members of the BeBOP group. Thanks to Vasily Volkov for helping me understand the GPU register file and encouraging me to work on small batch factorizations. Also to Grey Ballard for helping me understand communication-avoiding algorithms and how to map them to cache hierarchies. Finally, to Erin Carson and Nick Knight for their help with communication-avoiding linear solvers.

## Chapter 1

### Introduction

The transistor density of integrated circuits doubles every 18 to 24 months in a trend that is commonly referred to as Moore's law. Since its initial observation in 1965 [1], this exponential growth has continued steadily, enabling new applications with cheaper and more powerful processors. In the 28 years from 1982 to 2010 the number of transistors on Intel's processors grew from 134,000 transistors for the 80286 to 1.17 billion transistors for the Core i7. [2]. This is an  $8731 \times$  increase that corresponds roughly to 13 transistor-count doublings.

Single-thread performance, as measured by the SPEC benchmarks [3], has also historically increased at an exponential rate similar to the Moore's law trend, growing 25% per year from 1978 to 1986, 52% per year from 1986 to 2003, and 22% per year from 2003 to 2010 [2]. This exponential speedup has been attributed to faster transistors, larger on-chip caches, and clever micro-architectural techniques enabled by increased transistor budgets [4]. In the mid-2000s however, the growth of clock frequencies of commercial processors flattened, and the increases in single-thread performance slowed [5, 6]. The scaling technique that allowed transistors to shrink while maintaining the same overall power, called Dennard scaling [7], came to an end and power consumption became the limiting constraint in microprocessor design [4, 8]. Since then, the extra transistors provided by the continuation of Moore's law have been largely devoted to multi-core parallelism, wider SIMD units, larger caches, and further integration.

As hardware becomes more parallel, it becomes harder to get high performance on today's architectures. Achieving high performance can require significant effort and understanding of low-level hardware details. Most programmers are focused on their application and are not interested in or perhaps not capable of tuning low-level code to target architectures. They would rather program in productivity languages such as MATLAB, Python, or Perl, and call optimized libraries in a sequential manner. These are called *productivity programmers* [9]. Those who implement the optimized libraries are called *efficiency programmers*. Efficiency programmers write using low-level languages, and use tools such as OpenMP, vector intrinsics, and OpenCL. They are experts in achieving high hardware utilization, throughput, and maximizing reuse in caches.

The implementation gap [9, 10] is a term for the gulf between the productivity program-

mers and the efficiency programmers. This gap presents a serious problem for developers of emerging applications, and also for chip makers who see both performance and programmability as key selling points of their products. In a typical scenario today, a productivity programmer will write an application in MATLAB or Python, then send the specification to the efficiency programmer to implement as an efficient library. The productivity programmer may make high level decisions without knowledge of the low-level parallel performance implications. Similarly, the efficiency programmer may expend effort optimizing computations that can easily be eliminated with a slight change in the high-level approach. Bridging the implementation gap is necessary to avoid these undesirable outcomes.

On one end of the implementation gap is the efficiency programmer. Chapters 3 and 4 describe the efficiency-level implementation of dense linear algebra applications on GPUs. In Chapter 3 we optimize the QR factorization and apply it to a video background subtraction application. The matrix is very tall and skinny, meaning there are many more rows than columns. We show that a communication-avoiding QR factorization can outperform the traditional blocked QR factorization. High performance was achieved through extensive manual and auto-tuning the computation to fit the GPU hardware. In Chapter 4, we focus on solving many small (e.g.  $56 \times 56$ ) matrix factorizations in parallel on GPUs. We build a model of the GPU memory hierarchy to inform our tuning. In the case of small matrix factorizations, we find that runtime code generation, which allows us to use the GPU register file, is essential for good performance.

We set out to build a framework to attempt to bridge the implementation gap. We use the experiences tuning dense linear algebra in Chapters 3 and 4 to determine our framework's design and requirements:

- First, our experience convinces us that transparency is necessary for high performance. That is, a framework must allow for low-level code tuning. This empowers the efficiency programmer to make problem-specific or machine-specific optimizations that our framework never may have envisioned. This is in contrast to frameworks that would choose to hide these details behind programming abstractions.

- Second, optimizing with knowledge of specific shapes and sizes of data structures was very effective in our experience. In Chapter 3, the algorithm and block sizes we chose worked particularly well for tall and skinny matrices, but less well for square matrices. For the small linear algebra operations in Chapter 4, we generate different code for different sized matrices.

- Third, we observed that the time it takes to perform computations is much less than the time it takes to load operands from memory. Even for relatively compute-intensive small dense linear algebra factorizations, described in Chapter 4, we show that roughly 25% of the time is spent loading and storing data from global memory, and only 75% of the time is spent on computation. The gap between processor performance and memory performance is a well known problem with today's machines that seems to get worse over time [11]. This leads to a situation where composing two operations

can provide substantial speedups if the operations access the same data and memory traffic can be avoided. Whether composition is profitable or not can depend on the details of the operations being composed, and on machine details, as we demonstrate in the case studies in Chapters 6 and 7.

• Finally, we recognize that in order to reach productivity programmers, we must provide a front end in a popular productivity language such as Python or Ruby.

In light of these observations, we propose a framework called *Hindemith*, described in Chapter 5, that uses the selective embedded just-in-time specialization (SEJITS) methodology [9], along with high-performance hand-coded operations, organized around the principles of pattern-based software engineering. Inspired by recent SEJITS frameworks, Copperhead [12], PyCASP [13], and Three Fingered Jack [14], our framework is embedded in Python, meaning that productivity programmers can invoke it by writing specialized Python functions. The productivity programmer designs a program using a hierarchical composition of structural patterns and specialized operations. Any operation that is invoked by the productivity programmer must have a corresponding specialized implementation, which is written by the efficiency programmer. The entire program, including each individual operation, is processed at runtime, fused together, and just-in-time compiled using OpenCL. Furthermore, the shapes and sizes of all the data structures are propagated through the program description. This means that each operation has access to this vital runtime information during the code generation phase.

Hindemith is designed to be transparent, meaning that the efficiency programmer can provide operations with as much control over the hardware as OpenCL provides. The space-time adaptive processing case study in Chapter 6 shows the benefit of this transparency as it allows operations to be specifically tuned to run in the GPU's register file. The framework also provides automatic fusion of related operations. The optical flow case study in Chapter 7 is an example where extremely light-weight operations, such as vector addition, are combined into one to reduce unnecessary traffic between processors and memory.

We perform two case studies in Chapters 6 and 7, implementing a space-time adaptive processing (STAP) application and optical flow application in our framework. The STAP application boils down to doing many small linear algebra operations in parallel, so we leverage the hand-coded solutions developed in Chapter 4 and wrap these as framework operations. On an Intel Core i7 CPU, our STAP implementation exceeds the performance of a serial C reference implementation by over  $10\times$ . On an NVIDIA GT 640 GPU, our implementation is 8% slower than a CUDA + CUBLAS version, but  $2.4\times$  faster than the CUDA + CUBLAS version if only considering the time spent on computation. We also find that excessive kernel fusion can hurt performance for the STAP application. In Chapter 7, we implemented two different optical flow methods and four different linear solvers used for optical flow in our framework. Compared to ArrayFire, a commercial JIT-compiled linear algebra library for GPUs, our solutions performed between  $1.4\times$  to  $2\times$  faster on the NVIDIA GT 640 platform, and between  $1.8\times$  and  $3.5\times$  faster on the Intel Core i7 platform.

On the same benchmarks, the framework achieved between  $0.5 \times$  and  $0.97 \times$  the performance of our hand-coded implementation. These performance comparisons do not include JIT-compilation time. The applications we chose are meant to be run repeatedly in a real-time setting, and JIT-compilation time only appears in the first run of the program.

#### 1.1 Thesis Contributions

This thesis makes the following contributions:

- In an effort to bridge the implementation gap, we propose a framework called Hindemith (Chapter 5) that is transparent and allows for custom hand-tuned code, can take advantage of runtime knowledge such as shapes and sizes, composes operations to reduce communication between processors and memory, and is embedded in a productivity language. To this end, we deliver as a software artifact an implementation of Hindemith. The Hindemith framework uses the selective embedded just-in-time specialization (SEJITS) methodology, along with high-performance hand-coded operations, organized around the principles of pattern-based software engineering.

- We evaluate the Hindemith framework using two application case studies: space-time adaptive processing (STAP) and optical flow. Ignoring JIT compilation time, our framework delivers optical flow performance that is between  $0.5 \times$  and  $0.97 \times$  our own hand-coded implementations. For STAP, the our implementation is competitive with a hand-coded CUDA + CUBLAS implementation.

#### 1.2 Thesis Outline

- Chapter 2 covers background on the parallel programming problem, parallel platforms, and software.

- Chapter 3 demonstrates efficiency-level programming and tuning for the communication-avoiding QR factorization targeting GPUs.

- Chapter 4 demonstrates efficiency-level programming and tuning for solving small linear algebra factorization on GPUs. We also introduce a predictive model of the GPU memory hierarchy.

- Chapter 5 explains how the Hindemith framework works, including how to create operations, the analysis performed by the framework, and how it is embedded in Python.

- Chapter 6 provides a case study using Hindemith to implement a space-time adaptive processing (STAP) benchmark.

- Chapter 7 provides a case study using Hindemith to implement the optical flow application.

- Chapter 8 concludes.

### Chapter 2

### Background and Motivation

In this chapter, we provide relevant background material. We begin in Section 2.1 by introduce the parallel hardware targets used in the rest of this thesis. In Section 2.3 we describe the parallel programming problem that arises as a result of parallel hardware, and how we must balance productivity, efficiency, and portability. Current solutions to the parallel programming problem are described in Section 2.4, including efficiency languages, productivity languages and domain-specific languages (DSLs). In Section 2.6, we give an overview of parallel programming patterns and SEJITS. These are concepts that serve as the basis for our framework, which is introduced in Chapter 5.

#### 2.1 Parallel Hardware

Parallel processors have become ubiquitous. A personal computer today is likely to include a single chip containing a quad-core CPU with 256-bit AVX 2.0 SIMD extensions, and an integrated GPU [15]. One or more discrete GPUs can be added to the system as well to create a commodity high-performance heterogeneous parallel machine. We focus our attention on two design points for parallel systems: graphics processors (GPUs) and general-purpose multicore processors (CPUs). We chose these particular design points simply due to their popularity; most desktops and laptops sold today include programmable multicore and GPU hardware.

#### Graphics Processors (GPUs)

Graphics processors (GPUs) were first designed as mostly fixed-function accelerators for graphics applications, but have since been further developed into more general-purpose programmable data-parallel processors capable of a wide variety of highly parallel workloads [16, 17]. In order to get high performance on a GPU, an application must provide a large amount of parallelism to fill the GPU with work and to keep the memory system busy. Applications that are dense or structured are better suited to GPUs than sparse irregular

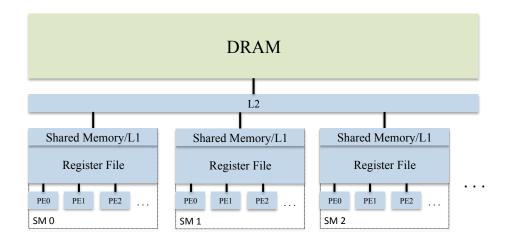

Figure 2.1: Block diagram of the memory hierarchy for an NVIDIA Fermi GPU

applications, because the GPU hardware performs better when it can coalesce parallel work into SIMD instructions and wide memory accesses.

A block diagram of the memory hierarchy for an NVIDIA Fermi GPU is shown in Figure 2.1. The global dynamic random access memory (DRAM) is located on the PCI card in the case of a discrete GPU. The Fermi architecture uses multiple GDDR5 DRAM interfaces optimized for fast parallel access [18]. The 768 KByte L2 cache is shared among all streaming multiprocessors (SMs). Each SM has a 64 KByte scratchpad memory that can alternatively be configured as an L1 cache. The register file, as suggested by the figure, is the largest on-chip memory with 128 KByte per SM. An important feature of the GPU compared to multicore CPUs is the structure of the memory hierarchy. On the Fermi GPU, the largest cache memories are physically closest to the processing elements. On CPUs the cache memories are much larger per core then on GPUs, and the larger CPU caches are physically further away from the processing elements than the smaller CPU caches.

GPUs are also being integrated onto the same die as CPUs. Recent offerings from Intel (e.g. Haswell with HD integrated graphics) and AMD (e.g. Fusion Llano) have included increasingly powerful and programmable GPUs [19, 20, 21]. The integrated GPUs along with the host CPUs are also programmable with OpenCL using the Intel OpenCL SDK and the AMD APP SDKs respectively. The advantage of providing integrated GPUs is that one less ASIC is required for a complete system, as compared to discrete GPUs.

#### **Multicore Processors**

Unlike GPUs, multicore processors are designed to perform well on a wide variety of general purpose workloads including desktop processing, games, web servers, and scientific computing. Among other techniques, multicore processors rely on deep cache hierarchies to increase performance by making main memory appear closer and faster than it is. Cache memories

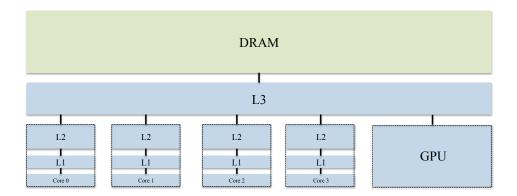

Figure 2.2: System block diagram for an Intel Haswell quad-core CPU with integrated graphics

were already common in "virtually all modern large computer systems" by 1982 [22], and recent Intel processors include up to four levels of cache [19]. Multicore processors also typically have dedicated hardware for single-instruction, multiple-data (SIMD) instructions that take advantage of parallelism and amortization of instruction fetch overhead to increase performance on data-parallel workloads [23, 24]. In recent years, SIMD units have increased in width and added support for new operations such as double-precision floating-point, fused multiply-add, and scatter/gather instructions [25].

Figure 2.2 shows a system block diagram for the CPU portion of an Intel Haswell quadcore processor [19, 20]. The system includes four cores, which all share an 8MB L3 cache memory. Each core has a 256 Kbyte L2 and a 64 KByte L1 cache, split evenly between instructions and data, per core. The system maintains coherence between cache memories. Some processor configurations include an integrated GPU, which also has access to the L3 cache memory.

The growth in SIMD width and throughput, as well as core count, has increased the performance of scientific and throughput-oriented workloads on multicore processors. A recent study has shown that, by making use of SIMD and other architectural features, the performance gap for high-throughput workloads between multicore processors and GPUs is  $2.5\times$  on average [26]. The memory bandwidth gap between multicore processors and GPUs may be diminishing as well, with new L4 cache memories achieving peak bandwidth speeds of 102 GB/s [19, 20].

#### 2.2 The Memory Wall

Another major trend impacting performance is the growing disparity between processor speed and memory speed, often called the *memory wall* [27]. The observation in 1994 that DRAM speeds were increasing by only 7% per year and processor performance was increasing at a rate of 80% per year indicated that average memory access time would, at some point,

dominate the runtimes of many important applications. The STREAM benchmark, released in 1995, measures performance on a set of bandwidth-bound vector operations such as vector addition [28]. The STREAM benchmark is useful not only for characterizing a single machine, but also observing trends in memory bandwidth performance over time. Wulf and McKee's presentation of STREAM benchmark data shows that from 1980 to 2000, memory bandwidth increased at roughly a 35% annual rate, while peak processor floating-point performance increased at roughly a 50% annual rate [11]. Memory latency improves at even a slower rate than bandwidth. An analysis of memory performance from 1982 to 2001 showed that memory bandwidth had grown from 13 MByte/s to 1,600 MByte/s while memory latency had only improved from 225 nanoseconds to 52 nanoseconds [29]. They observe that for every doubling in memory bandwidth, latency has only improved by roughly a factor of 1.2 to 1.4. These trends are expected to continue in the near term. A recent report on trends in supercomputing estimated the annual improvement in single-chip floating-point performance to be 59% through year 2020, compared to an annual 25% improvement in DRAM bandwidth and an annual 5.5% improvement in DRAM latency [30]. The high energy cost of moving data compared to performing computation is also a concern. According to another recent report, it costs roughly half the energy to fetch three double-precision operands as it does to perform a multiply-add operation on those operands from on-chip memories that are 1 millimeter away, and it costs an order of magnitude more energy to fetch from 20 millimeters away than to perform the multiply-add [31].

These memory trends affect some computations more than others. Certain applications that can make effective use of cache hierarchies are less affected by poor memory performance than applications that must stream large amounts of data to and from global memory. This has motivated research into communication-avoiding algorithms that aim to turn communication-bound applications into compute-bound applications by asymptotically reducing the amount of data transferred between levels of the memory hierarchy, and also asymptotically reducing the number of synchronizations across parallel elements [32, 33]. Communication-avoiding algorithms have the potential to provide speedups on existing applications, and may also improve energy efficiency in future microprocessor systems [4].

#### 2.3 The Parallel Programming Problem

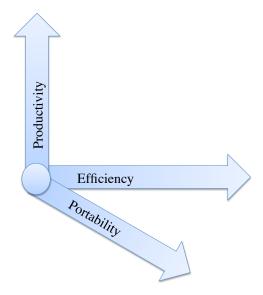

The ubiquity of parallel hardware brings a problem: how can we enable programmers to take advantage of it? Parallel hardware can enable higher efficiency through the use of multiple cores or multiple SIMD lanes. However, to make use of parallel resources, the programmer must identify parallelism in his or her application and modify the implementation for parallel execution. This can reduce programmer productivity by adding complexity to the specification. Additionally, the programmer may want to tune his or her implementation for particular hardware details for maximum efficiency, which reduces productivity and potentially costs portability as well. The programmer thus faces a trade-off between competing forces of efficiency, portability, and productivity illustrated by the three axes in

Figure 2.3: The parallel programming problem entails a trade-off between efficiency, portability, and productivity.

Figure 2.3. The next subsections will describe the competing forces of efficiency, portability, and productivity in more detail.

#### **Efficiency**

We measure efficiency in different ways depending on the application and its constraints. Floating point applications and benchmarks, such as LINPACK [34], have historically been measured in terms of floating-point operations completed per second (FLOPS). This work focuses on machines capable of computation on the order of billions of floating-point operations per second, or GigaFLOPS (GFLOPS). Bandwidth performance is reported in terms of billions of bytes per second transferred from memory to processors (GBytes/s). Power is measured in Watts (W), with a typical machine drawing between 10W and 300W in total wall power. Energy consumption, measured in Joules (J), is an important application performance measure. We also report energy efficiency of floating-point applications in terms of GigaFLOPS per Watt of wall power (GFLOPS/W), which can be alternatively interpreted as the total number of floating-point operations per Joule of energy spent. A typical GFLOPS/W number in today's technology would be 1.0, possibly for a machine that draws 100 Watts and can perform a matrix-multiplication operation at a rate of 100 GFLOPS.

A given application's performance is often contextualized by reporting GFLOPS or GBytes/s achieved as a percentage of the peak attainable GFLOPS or GBytes/s. The roofline model is a methodology for identifying whether an application is bounded by floating-point throughput or memory bandwidth, which can suggest the most profitable optimization techniques to apply in each case [35]. Getting a high percentage of peak performance often

requires significant hand-tuning and knowledge of underlying hardware. A study of sparse matrix-vector multiplication for parallel processors identified optimizations such as loop unrolling, software pipelining, and register blocking, that helped to increase the application's bandwidth utilization [36]. In Chapters 3, 4, and 6 of this work, we describe in detail the hand tuning required to increase performance of certain dense linear algebra operations on GPUs.

#### **Portability**

We would like to have the same code run on multiple processor designs. Often, a specific architecture will require a specific programming environment in order to program it. Multicore SIMD units, for example, often require special instructions, which can be accessed using assembly intrinsics. On GPUs, the instruction set is kept hidden from the programmer to allow for greater hardware flexibility. The programmer must use special languages such as CUDA or OpenCL to program GPUs. These languages are designed to encourage the use of fine-grained parallelism, which is necessary to achieve high performance on GPUs.

Industry recently coalesced around a new open standard for heterogeneous parallel computing called OpenCL (Open Computing Language) [37, 38]. Programs can be written once in the OpenCL language and run on a wide range of parallel devices, providing they support the standard. Programs are typically compiled at runtime to enable such portability. OpenCL is now supported on a wide range of devices including GPUs, multicore CPUs and their integrated graphics, accelerators, DSPs, and FPGAs. However, in many cases OpenCL programs are not performance portable, meaning specific tuning needs to take place for each potential OpenCL target in order to achieve good performance.

#### Productivity

Productivity is a measure of how challenging and/or time consuming it is to implement an application. This can roughly translate into number of lines of code or number of hours spent on implementation and maintenance. Languages such as Python or Perl are thought to be more productive than languages such as C++ because they are interpreted and untyped. Third party libraries can also increase the productivity of a programming environment. Python, in particular, has an extensive catalog of third-party libraries ranging from numerical processing [39, 40] to data visualization [41], to posting messages on Twitter [42].

Programming environments can be more productive especially when they are designed for a specific domain. For example, MATLAB [43] is a domain-specific programming environment for scientists and engineers that allows the programmer to very succinctly describe matrix and vector codes, image and signal processing applications, statistics applications, etc. Tools such as AMPL [44] or CPLEX [45] are very productive for modeling and solving a particular class of problems including linear programming, mixed integer programming and convex optimization.

#### 2.4 Current Solutions

Programmers have many choices when it comes to programming parallel hardware. We outline them here in three broad classes: productivity languages, efficiency languages, and domain-specific languages (DSLs).

#### Productivity Languages

Productivity languages were designed with programmer productivity in mind. Languages such as MATLAB, Python, and Perl are among the most popular productivity languages. They are often not compiled and use interpreters in order to execute. This leads to poor performance which, in the case of Python, can be improved through the use of JIT compilers (PyPy [46]) or C language extensions (Cython [47]). Productivity languages are often untyped, which contributes to their slow performance. They often come with extensive debugging support, and also a wide array of supporting libraries. MATLAB has over 40 toolboxes available for purchase in domains ranging from symbolic math to bioinformatics [48], and untold numbers of 3rd party functions written in efficiency languages and wrapped using the MATLAB mex interface. Any of these 3rd party functions are free to take advantage of available parallel hardware. Python also has an extensive catalog of third-party libraries including popular tools for numerical processing [39, 40] and data visualization [41].

#### Efficiency Languages

As opposed to productivity languages, which are designed with programmer productivity in mind, efficiency languages are often designed with details of the target hardware in mind. The C language, which grew out of Bell Labs in the 1970s, gives the programmer a high degree of control over the machine and was useful especially for implementing the UNIX operating system [49]. The Fortran language works especially well with optimizing compilers targeting vector and parallel hardware, particularly for scientific applications with dense loop nests [50]. With the advent of highly programmable GPUs, new efficiency languages like CUDA [51] and OpenCL [38] have emerged to provide programmers with a way to write implicitly parallel code that can execute effectively on GPU hardware.

Most high-performance software is written in an efficiency language and packaged as a library, to be called either from another efficiency language or encapsulated in a wrapper and called from a productivity language. Among the most popular efficiency language libraries are OpenCV [52], a collection of computer vision routines, and Basic Linear Algebra Subprograms (BLAS) and LAPACK [53, 54], efficient and numerically correct implementations of common linear algebra operations. Hardware vendors also release versions of these libraries optimized for their hardware, for example AMD's Core Math Library (ACML), Intel's Math Kernel Library (MKL), and NVIDIA's CUBLAS.

#### Domain Specific Languages (DSLs)

Domain specific languages can potentially provide both high productivity and high efficiency simultaneously. This is achieved by limiting the scope of what can be implemented to a specific domain such as matrix algebra or image processing, or to a specific style of computation such as data parallel computations.

ArrayFire [55] is a commercial parallel programming framework that does just-in-time compilation of array codes to compose operations in such a way as to eliminate unnecessary reads and writes, generating OpenCL at runtime. Halide [56, 57], designed for image processing pipelines, allows the programmer to write transformations on images, along with a specification of the schedule in which the operations execute. Theano [58] takes mathematical operations specified at a high level in Python, performs both numerical and compiler optimizations, and executes on GPUs and multicore. Liszt [59] is a performance-oriented domain specific language for partial differential equation (PDE) solvers.

Instead of targeting a certain domain, some frameworks target applications that have a specific computational structure. Sequoia [60] is a framework that optimizes recursive applications and automatically tunes them to fit various memory hierarchies. Copperhead [12, 61] is a framework that takes a subset of Python, namely data parallel operations, does runtime compilation and executes these operations efficiently on GPUs and multicore. Three Fingered Jack [14, 62] is a runtime optimizing compiler targeting dense loop nests that targets CPUs, GPUs, and custom hardware. PyCASP [13, 63] is a SEJITS framework designed for content-analysis applications that leverages structural pattern insights to perform composition of specialized functions from a productivity-language specification.

There is also an effort to share and reuse DSL-building infrastructure. Delite [64] is a DSL building framework based in Scala, and OptiML [65] is an example DSL for machine learning that uses Delite. The ASP [66] framework is a tool for embedding specializers in Python using the selective embedded just-in-time specialization (SEJITS) methodology.

#### 2.5 Limitations of Current Solutions

Each class of parallel programming solution has advantages and disadvantages. Efficiency languages provide the programmer with control over machine resources to allow for baremetal tuning, however this style of programming is less productive than productivity languages. Productivity languages are exceedingly slow because they must interpret every operation, but one can embed libraries written in efficiency languages. This provides access to high-performance libraries from productivity languages. However, most productivity languages do not take advantage of composition opportunities. Domain specific languages can do an excellent job of composing related operations for efficiency, but these languages are often restricted to a specific sub-domain.

We begin to motivate our solution in Chapters 3 and 4 with our experiences hand-tuning dense linear algebra operations for GPUs. From these experiences, we derived the following set of requirements for our framework:

- It is transparent and allows for custom hand-tuned code,

- It can take advantage of runtime knowledge such as shapes and sizes,

- It composes operations for efficiency, taking advantage of data reuse to reduce communication between processors and memory and

- It is embeddable in a popular productivity language.

Here we describe these requirements in more detail and the motivation behind each.

#### Requirement 1: Transparency

The programmer must be able to write arbitrary low-level code that takes advantage of machine details in order to attain high performance. Machine details should be transparent and not always hidden behind programming abstractions. Instead, the programmer should be able to write directly in efficiency languages if he or she chooses.

In Chapters 3 and 4, we note that programming for the memory hierarchy and register file are essential to achieving high performance. This includes blocking computations, choosing particular block sizes that fit the memory hierarchy, and application-specific optimizations such as transposing data to improve performance. This strongly influences our opinion that any solution to the parallel programming problem should be transparent and provide the efficiency programmer with the option to write custom, hand-tuned code.

#### Requirement 2: Knowledge of Runtime Shapes and Sizes

Code should be generated at runtime and the programmer should be able to use runtime information in the code generation process, such as datatypes, problem shapes, and problem sizes.

It is difficult to compile directly to machine code without datatype information, which is often not available until runtime when working with interpreted languages such as Python. Runtime code generation can solve this problem elegantly. Shape information can also be useful for performance optimization, and different parallelism strategies may be advantageous for differently shaped problems. In Chapter 3, we show that a different parallel algorithm, communication-avoiding QR, can outperform a more traditional algorithm, blocked Householder QR, but only when the matrix has a certain shape. In Chapter 4 and the case study in Chapter 6, we show the benefits of compiling different code for different sized problems. Runtime code generation allows us to use the GPU register file, but in order to use it we have to know the exact size of the problem. In Section 6.3, we show that this code generation and use of the register file leads to a  $5.7\times$  speedup for the system-solve kernel in the space-time adaptive processing application.

#### Requirement 3: Composition

A framework should have the ability to join multiple operations at runtime into a single operation, if this provides higher performance than executing the operations individually. Composition of operations is often essential for high performance. Once data has been fetched into on-chip cache memories or registers, it should stay there as long as it is being used. This is especially true for light-weight operations such as BLAS1 vector operations or 2D stencils. However, even in the case of heavy-weight operations, the time to load and store data is non-negligible. In Section 4.5, we show that when doing a set of  $56 \times 56$  LU factorizations on a Quadro 6000 GPU, 25% of the time is spent loading and storing data to and from global memory, and only 75% of the time is spent on the  $O(n^3)$  computation.

Given the long-term trend towards increasing processor speeds over memory speeds, described in Section 2.2, composition is becoming more and more important. In order to achieve high performance, a framework should use its runtime code generation abilities to fuse related operations into a single loop nest or OpenCL kernel. In the case of discrete GPUs with disjoint memory systems, it is also important to leave data in device memory for as long as its being used and to minimize the amount of transfers to and from the device. A framework should also manage on which device the data structures reside and try to minimize data transfers between devices, although recent CUDA releases have taken steps to unify the host and device memory spaces and manage data transfer automatically at a lower software layer [67].

#### Requirement 4: Embedded in a Popular Productivity Language

Python is a popular language among domain experts and productivity programmers. Making a framework programmable from Python gives productivity programmers a reasonable interface to use the framework. It also means that the inputs and outputs of the framework can easily be passed to other libraries, visualization tools, and frameworks that provide Python bindings.

#### 2.6 Our Solution

Our solution to the parallel programming problem follows the example of prior work in pattern-oriented frameworks [10, 13, 12, 68]. We begin in this section by describing design patterns for parallel programming. These are common solutions to recurring problems that arise while engineering parallel software. They describe the software architecture, how components are arranged and how data flows between components, the computation itself, and various tools and techniques for efficient parallel implementation. The aim of the patterns is to document and convey techniques that are necessary and familiar to an expert software architect and parallel programmer.

Patterns are not, however, specific software artifacts. They are recorded in documents and books that programmers reference. Frameworks are software artifacts that can restrict

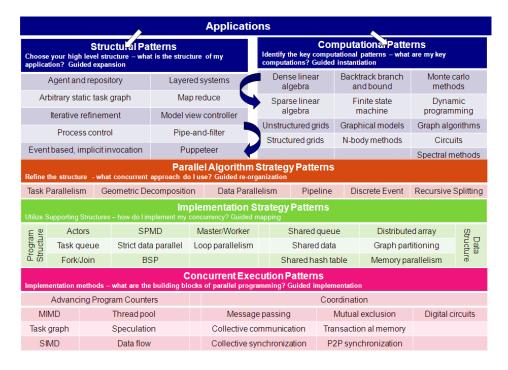

Figure 2.4: Keutzer and Mattson's Our Pattern Language [71]

the programmer to a specific set of patterns or a specific method of implementation. Selective embedded just-in-time specialization (SEJITS) is a methodology for designing frameworks that allows for runtime code generation of selected patterns and computations. We introduce the SEJITS methodology here and we describe our SEJITS framework, called Hindemith, in Chapter 5. Details of how our proposed framework differs from other related frameworks are in Section 5.2.

#### Patterns

Design patterns are solutions to recurring problems. These problem-solution pairs are documented and named as *patterns* in a *pattern language* [69]. Though design patterns were originally conceived to describe civil architecture, the concept has since been successfully applied to computer software, the most famous example being the object-oriented programming textbook *Design Patterns: Elements of Reusable Object-Oriented Software* by the so-called Gang of Four [70].

The domain of high-performance parallel software is different in many ways than traditional object-oriented software design. A pattern language specifically for parallel programming was designed to address the specific concerns of parallel programmers. A revision of this pattern language is shown in the lower half of Figure 2.4. The idea is that parallel programmers would read up on each of these patterns, in the text *Patterns for Parallel Programming* [72], which provides a step-by-step guide toward efficient parallel implementa-

```

def jacobi(D, R, b, x):

for i in range(num_iter):

r = b - R*x

x = D * r

return x

```

(a) Jacobi linear solver example written in Python

(b) Architected using structural patterns

Figure 2.5: Architecting the Jacobi linear solver with structural patterns

tions. Later, ideas from software architecture were incorporated into the pattern language. These *structural* and *computational* patterns, included in the top half of Figure 2.4, provide a common language for software architecture and computation. The final product, called *Our Pattern Language* [71] serves as the basis for our design philosophy. The following sections will describe each level of Our Pattern Language in more detail.

#### Structural Patterns

The process of architecting software using the pattern language begins with an iterative process of choosing a combination of structural and computational patterns are used to map out a software architecture. Structural patterns describe common ways in which software components are composed. These are like the boxes and arrows one would write on a white board to describe a software architecture. Structural patterns are useful not only to communicate a design, but because they encode modularity and certain invariants that can be exploited by frameworks. The PyCASP framework leverages three structural patterns (Pipe and Filter, Iterator, and MapReduce) for optimizations such as operation composition, allowing efficient execution of audio processing applications [13, 63].

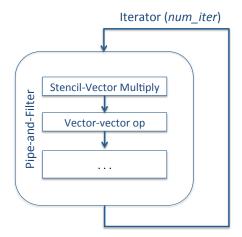

Figure 2.5 shows Python code for a Jacobi solver on the left and its software architecture on the right. The architecture uses two structural patterns. The highest level pattern is an iterator that loops num\_iter times. Inside the loop there is a pipe-and-filter pattern, containing a number of computations including stencil-vector multiplication and vector-vector operations.

#### Computational Patterns

Computational patterns describe core classes of computations found in applications [5]. Where as structural patterns describe the layout of computation, computational patterns describe what is computed and how. Computational patterns fit into a software architecture as the nodes of a graph, where the graph is a hierarchial composition of structural patterns. Computational patterns are usually supported by application-specific or pattern-specific libraries. Examples include the CombBLAS library for a certain class of graph algorithms [73], BLAS and LAPACK for the dense linear algebra pattern [53, 54], and the Liszt framework for structured grid computations [59].

#### Lower Levels of Pattern Language

Notice that both structural and computational patterns do not directly deal with concurrency or parallelism. After a software architecture is designed using computational and structural patterns, the lower levels of the pattern language help guide the programmer towards an efficient parallel implementation. He or she starts by applying parallel algorithm strategy patterns, which are high level approaches to exploiting concurrency such as *Task Parallelism*, *Data Parallelism*, and *Pipeline*. Below this are the implementation strategy patterns, which are software mechanisms that help the programmer implement efficient parallel code. At the bottom are concurrent execution patterns, which are separated into patterns for advancing program counters, and patterns for communicating between concurrent tasks.

#### Selective Embedded Just-In-Time Specialization (SEJITS)

As mentioned earlier, patterns are not software artifacts in themselves. Frameworks are a vehicle for encoding pattern knowledge into a usable software artifact. Selective embedded just-in-time specialization (SEJITS) is a methodology for designing frameworks that allow for runtime code generation of selected patterns and computations.

SEJITS was designed explicitly to tackle the implementation gap [9]. Starting with code written in a scripting language, a SEJITS specializer will inspect the abstract syntax tree that it is to execute, perform transformations and code generation, JIT compile the code, execute it, and cache it for future use. This process is selective, meaning it only takes place on certain portions of the code that are computationally intensive, and it is embedded in the productivity language, making it directly accessible to productivity programmers. This provides a natural division of labor between the efficiency programmer, who designs the specializers, and the productivity programmer, who invokes them in his or her applications. It also provides a natural setting for hardware-specific tuning or autotuning. The specializer has access to both the program and the hardware information, at runtime. The SEJITS methodology has been successfully applied in bridging the implementation gap for stencil computations, communication-avoiding algorithms, and audio analytics [74, 75, 13]. The

2.7. SUMMARY

success of this work also led to the create of the ASP framework, which makes SEJITS infrastructure available for more general use [66].

#### 2.7 Summary

In this chapter, we provided relevant background material. We introduced two important classes of parallel hardware, CPUs and GPUs, and discussed the parallel programming problem. To motivate our framework in Chapter 5, we introduced four framework requirements. We summarized related work and the SEJITS methodology.

## Chapter 3

## Optimizing for Problem Shape

In Chapters 3 and 4 we focus on optimizing dense linear algebra computations on GPUs using extensive hand tuning. We show that both the shape and the size of the matrices involved in these computations affects which implementation approaches perform best. This motivates our assertion that knowledge of shape and size information is beneficial for achieving high performance implementations.

In this chapter we focus on the QR factorization, a frequently used linear algebra routine that can, among other things, solve least squares problems. For a particular shape of tall-skinny matrices, where the number of rows is much larger than number of columns, we show that a communication-avoiding (CAQR) algorithm is faster than traditional approaches.

We also discuss stationary video background subtraction, a motivating application of the QR factorization. We use a recent statistical approach to stationary video background subtraction, which requires many iterations of computing the singular value decomposition of a tall-skinny matrix. Using CAQR as a first step to getting the singular value decomposition, we are able to get the answer 3x faster than if we use a traditional bandwidth-bound GPU QR factorization tuned specifically for that matrix size, and 30x faster than if we use Intel's Math Kernel Library (MKL) singular value decomposition routine on a multicore CPU.

#### 3.1 Introduction

One of the fundamental problems in linear algebra is the QR decomposition, in which a matrix A is factored into a product of two matrices Q and R, where Q is orthogonal and R is upper triangular. The QR decomposition is most well known as a method for solving linear least squares problems, and is used commonly across all of dense linear algebra.

In terms of getting good performance, a particularly challenging case of the QR decomposition is tall-skinny matrices. Examples of tall-skinny matrices are when the ratio of rows to columns are 3 to 1, 1,000 to 1, or even 100,000 to 1 in some cases. QR decompositions of this shape matrix, more than any other, require a large amount of communication between processors in a parallel setting. This means that most libraries, when faced with this

problem, employ approaches that are bandwidth-bound and cannot fully make use of the floating-point capabilities of processors.

Matrices with these extreme aspect ratios would seem like a rare case; however they actually occur frequently in applications of the QR decomposition. The most common example is linear least squares, which is ubiquitous in nearly all branches of science and engineering and can be solved using QR. Least squares matrices may have thousands of rows representing observations, and only a few tens or hundreds of columns representing the number of parameters. Another example is stationary video background subtraction. This problem can be solved using many QR decompositions of matrices on the order of 100,000 rows by 100 columns [76]. An even more extreme case of tall-skinny matrices are found in s-step Krylov methods [77]. These are methods for solving a linear equation Ax = b by generating an orthogonal basis for the Krylov sequence  $\{v, Av, A^2v, ...A^nv\}$  for a starting vector v. In s-step methods, multiple basis vectors are generated at once and can be orthogonalized using a QR factorization. The dimensions of this QR factorization can be millions of rows by less than ten columns.

These applications demand a high-performance QR routine. Extracting the foreground from a 10-second surveillance video, for example, can require over a teraflop of computation [76]. Unfortunately, existing GPU libraries do not provide good performance for these applications. While several parallel implementations of QR factorization for GPUs are currently available [78, 79, 80], they all use generally the same approach, tuned for large square matrices, and thus have up to an order of magnitude performance degradation for tall-skinny problems. The loss in performance is largely due to the communication demands of the tall-skinny case. We aim to supplement the existing libraries with a QR solution that performs well over all matrix sizes.

Communication-Avoiding QR (CAQR) is a recent algorithm for solving QR decomposition that is optimal with regard to the amount of communication performed [81]. This means that the algorithm minimizes the amount of data that must be sent between processors in the parallel setting, or alternatively the amount of data transmitted to and from global memory. As a result, the CAQR algorithm is a natural fit for the tall-skinny case where communication is usually the bottleneck.

In this chapter we discuss the implementation and performance of CAQR for a single NVIDIA Fermi graphics processor (GPU). It is a distinguishing characteristic of our work that the entire decomposition is performed on the GPU using compute-bound kernels. Despite their increasing general-purpose capabilities, it is still a very challenging task to map the entirety of this particular algorithm to the GPU. In doing so, however, we are able to leverage the enormous compute capability of GPUs while avoiding potentially costly CPU-GPU transfers in the inner loop of the algorithm. The benefits can most clearly be seen for very skinny matrices where communication demands are large relative to the amount of floating-point work. As a result, we can outperform existing libraries for a large class of tall-skinny matrices. In the more extreme ratios of rows to columns, such as 1 million by 192, we achieved speedups of up to 17x over standard GPU linear algebra libraries. It is important to note that everything we compare to is parallel. The speedups we show are a

result of using the parallel hardware more efficiently.

We do not directly use available Basic Linear Algebra Subroutine (BLAS) libraries as a building block. CAQR requires many hundreds or thousands of small QR decompositions and other small BLAS and LAPACK [54] operations to be performed in parallel. Consequently, we had to do significant low-level tuning of these very small operations to achieve sufficient performance. We will discuss and quantify the effect of specific low-level optimizations that were critical to improving performance. We also highlight new trade-offs the GPU introduces, which differ from previous CAQR work on clusters and multicore architectures [81] [82].

Finally, we discuss the application of CAQR to stationary video background subtraction, which was a motivating application for this work. Stationary video background subtraction can be solved using Robust Principal Component Analysis (PCA), by formulating the problem as a regularized nuclear norm minimization [76]. In the Robust PCA algorithm, the video is transformed into a tall-skinny matrix where each column contains all pixels in a frame, and the number of columns is equal to the number of frames. In an iterative process, the matrix is updated by taking its singular value decomposition (SVD) and thresholding its singular values. The SVD can be solved using the QR decomposition as a first step. We will show that our CAQR implementation gives us a significant runtime improvement for this problem.

Several implementations of CAQR exist, as well as Tall-Skinny QR (TSQR), a building block of CAQR that deals only with extremely tall-skinny matrices. TSQR has been applied in distributed memory machines [81] [83] and grid environments [84] where communication is exceptionally expensive. However, previous work in large-scale distributed environments focuses on different scales and types of problems than ours. More recently, CAQR was also applied to multicore machines [82], and resulted in speedups of up to 12x over Intel's Math Kernel Library (MKL) at the time. Note, however, that implementing CAQR on GPUs is a much different problem than on multi-core and it is likely that both will be needed in future libraries and applications.

The chapter is organized as follows. In Section 3.1 we survey previous algorithms and implementations of the QR decomposition. Next we discuss the high-level problem of mapping CAQR to heterogeneous systems in Section 3.3. Section 3.4 describes the specifics of our GPU implementation and tuning process. Section 3.5 contains our performance compared to currently available software. In Section 3.6 we outline our motivating video processing application and the performance benefits of using CAQR. Section 8 draws conclusions.

#### 3.2 Background on QR Approaches

There are several algorithms to find the QR decomposition of a matrix. For example, one can use Cholesky QR, the Gram-Schmidt process, Givens rotations, or Householder reflectors [85]. Even though it is less numerically stable than Householder reflectors or Givens rotations, if the matrix is well conditioned, then Cholesky QR may be accurate enough, and it may also may be the fastest approach because it uses matrix multiplication. CAQR is a form of

Figure 3.1: Blocked Householder QR

the Householder approach, where the Householder vectors are broken up in such a way that communication is minimized.

#### Householder QR

Most existing implementations of QR for GPUs have used the Householder approach, as does LAPACK. One favorable property of the Householder algorithm is that it can be organized in such a way that it makes use of BLAS3 (matrix-matrix) operations. Specifically, the trailing matrix updates for several Householder vectors can be delayed and done all at once using matrix-multiply. This allows for higher arithmetic intensity on machines with a memory hierarchy because matrix-multiplication can be blocked for good cache performance. Higher arithmetic intensity then leads to better performance. This is called blocked Householder QR, because it allows the updates to the trailing matrix to be blocked in cache. Several implementations of the blocked Householder approach for GPUs are currently available [80] [79] [86]. These are generally all very fast due to the heavy use of well-optimized matrix-multiply routines [87] [78].

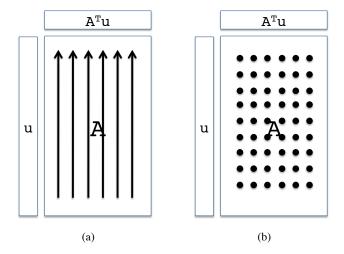

Figure 3.1 shows a sketch of one step in the blocked Householder algorithm. Here, a panel of some width less than the total number of columns is factored using the Householder algorithm with BLAS2 (matrix-vector) operations. Next, a triangular matrix T is formed from the inner products of the columns in the panel. Finally, the trailing submatrix is updated using a matrix-matrix multiply of the panel's Householder vectors, T, and the trailing matrix itself. After the update, the next panel is factored, and so on.

From Figure 3.1 we can intuitively understand a shortcoming of the blocked Householder algorithm. For very wide matrices, a significant portion of the runtime is spent doing matrix-matrix multiply, which is a very efficient use of hardware given the available high-performance dense matrix-multiply routines for GPUs [88]. However, if the matrix is skinny, a greater portion of the runtime is being spent in the BLAS2 panel factorization, which is not an efficient use of the hardware because matrix-vector routines are generally bandwidth-bound.

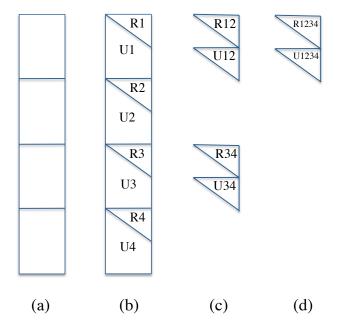

Figure 3.2: Stages of Tall-Skinny QR. First, each block is factored using Householder reflectors. Then, the upper triangular results are stacked and factored until only one upper triangular result remains.

Clever implementations of blocked Householder for heterogeneus CPU+GPU envoronments can hide this cost for wide matrices by sending the panel factorization to the CPU and overlapping it with the previous trailing matrix update, which is performed on the GPU [78]. While this greatly improves the performance for wide matrices, it does not eliminate the latency problem for the skinny case.

#### Tall-Skinny QR (TSQR)

The TSQR algorithm reorganizes the factorization of a tall-skinny matrix (such as a column panel) to minimize memory accesses [81]. Instead of computing one Householder vector for each column directly, we divide the tall-skinny matrix vertically into small blocks, as shown in Figure 3.2(a). Next, we factor each block independently using Householder reflectors. This creates a small Householder representation of Q, which we call U, and an upper-triangular R for each block. This is shown in Figure 3.2(b). We would like to eliminate all the Rs below the top-most diagonal, so we can group sets together in a stack and apply the Householder algorithm to each (possibly exploiting the sparsity pattern), which is done in Figure 3.2(c). We can continue to reduce the Rs with another level as in Figure 3.2(d). This leaves us with our final upper triangular matrix R, and a series of small Us which, if needed, can be used to generate the explicit orthogonal matrix Q of the factorization.

The TSQR algorithm exposes parallelism. Each block in the panel can be processed independently by a different processor. TSQR also allows us to divide the problem into chunks with a more managable size. If we choose block sizes that fit in cache, we can achieve significant bandwidth savings.

In the figure, the Rs were eliminated in a binary tree. However, this can be done using any tree shape. The optimal shape can differ depending on the characteristics of the architecture. For example, on multi-core machines a binomial tree reduction was used [82], whereas our GPU approach employs a oct-tree reduction. The type of reduction changes how the Q matrix is implicitly represented in memory. That is, the implicit representation of a Q matrix that was generated using a binary tree reduction is incompatable with a routine that uses a oct-tree reduction. The motivation behind our choice to use an oct-tree reduction will be explained in Section 3.4.

#### Communication-Avoiding QR (CAQR)

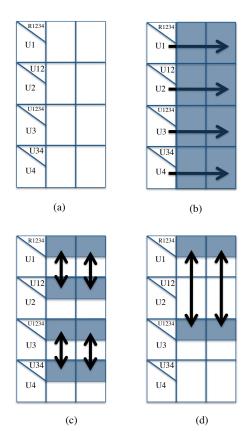

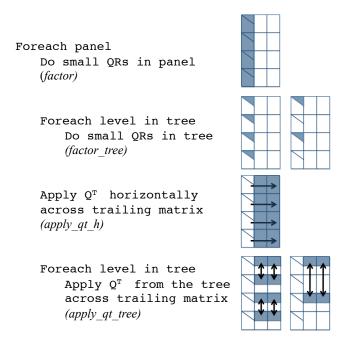

CAQR is an extension of TSQR for arbitrarily sized matrices [81]. This time we divide the matrix into a grid of small blocks. Like blocked Householder, CAQR involves a panel factorization and a trailing matrix update. The panel factorization is done using TSQR, shown in Figure 3.3(a). We must then do the trailing matrix update, which means applying the  $Q^T$  of the panel to the trailing matrix. Note that because TSQR works on blocks in the column panel, the trailing matrix update can begin before the entire panel is factored. This removes the synchronization in the standard blocked Householder approach and exposes more parallelism. We do not just use a large matrix-matrix multiply as we did in blocked Householder. This is due to the distributed format in which TSQR produces its Q. Instead, we carry out small updates in each small block of the trailing submatrix. Recent work by Ballard et al uncovered a method to recover the Householder vectors that would have been generated with the traditional blocked Householder approach (ie  $I - Y * T * Y^T$ ) [89]. This could be more efficient than the trailing matrix updates described here because it would use matrix-multiplication for the bulk of the computation. We do not attempt this technique in this chapter.

There are two types of trailing matrix updates: horizontal updates and tree updates. Horizontal updates are the easier case. Here we take the Householder vectors generated from the first stage of TSQR and apply them horizontally across the matrix, shown in Figure 3.3(b). This operation is very uniform, and the update of each block in the trailing matrix is independent. The more challenging update is the tree update. Here we take the Householder vectors generated during each level of TSQR's tree reduction and apply them across the matrix. This involves mixing small pieces of the trailing matrix, as shown in Figure 3.3(c) and (d). The rows of the trailing matrix that get updated vary with each level of the reduction tree. This can be challenging on the GPU because the accesses to the matrix are more irregular and somewhat sparse.

After the trailing matrix is updated we can move to the next panel. We must take care to shift the bounds of the working submatrix lower by a number of rows equal to the panel

Figure 3.3: Communication-Avoiding QR

width, reflecting the fact that the trailing matrix becomes both shorter and narrower after each step.

# 3.3 Mapping CAQR to Heterogeneous (CPU+GPU) Systems

Here we briefly discuss two different options for mapping CAQR to current heterogeneous systems. We consider a heterogeneous system containing one or more multi-core host CPUs with DRAM, a GPU with DRAM, and a physical link between the two memories. The GPU has more compute and bandwidth capability generally than the CPUs, whereas CPUs generally have a larger cache, more ability to exploit instruction-level parallelism, and are better equipped to handle irregular computation and data accesses.

The two questions we want to answer with regard to CAQR are: where we should do each step of the computation? Where should we store the data?

# First option: CPU panel factorization and GPU trailing matrix update

With this approach, the algorithm proceeds as follows. A panel (a handful of columns) is sent to the CPU, if necessary, and the CPU factors the panel using TSQR. The result of the factorization is sent back to the GPU and used for the trailing matrix update. Potentially, the CPU could begin factoring the next panel while the GPU is still busy applying the previous panel to the trailing matrix.

The main advantage of this approach is that offloading work to the CPU makes it possible to overlap GPU and CPU work. This allows one to use the entire system. The TSQR panel factorization can be a good fit for the CPU because of the irregular nature of the reduction tree. The trailing matrix update is regular and can be done efficiently on the GPU.

One disadvantage of this approach is that in order to offload work to the CPU we must transfer the data between CPU and GPU memories. On current systems, this involves latency that can hurt performance for skinny problems. Unless we successfully overlap CPU and GPU computation, sending the panel factorization to the CPU means we cannot use the superior compute and bandwidth capabilities of the GPU for these parts of the computation.

#### Second Option: Entire factorization the GPU

With this approach, the entire factorization is done on the GPU. This includes the TSQR panel factorization and the trailing matrix updates.

Assuming the matrix is entirely in GPU memory, this approach eliminates transfer latency. This means that we can get good performance even on skinny problems. We also can benefit from the higher compute and bandwidth capability of the GPU for the panel factorizations.

Unfortunately, this approach is much more difficult to program. This is first because we cannot reuse existing tuned CPU libraries. Also, certain parts of the QR algorithm involve more irregular computations and are therefore more challenging and less efficient to carry out in the GPU's programming and execution models. The pseudocode in Figure 3.4, described in the next section, illustrates some of the irregular operations necessary for a GPU-only approach.