# Interference Management Techniques for Multi-Standard Wireless Receivers

Ashkan Borna

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2014-187 http://www.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-187.html

December 1, 2014

Copyright  $\bigcirc$  2014, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Interference Management Techniques for Multi-Standard Wireless Receivers

by

Ashkan Borna

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Jan M. Rabaey Professor Paul K. Wright

Fall 2012

### Interference Management Techniques for Multi-Standard Wireless Receivers

Copyright 2012 by Ashkan Borna

#### Abstract

Interference Management Techniques for Multi-Standard Wireless Receivers

by

Ashkan Borna

#### Doctor of Philosophy in Electrical Engineering and Computer Science

University of California, Berkeley

Professor Ali M. Niknejad, Chair

The performance of wireless standards is improving steadily for a foreseeable future. Wireless communications are used for a variety of applications from data steaming to Internet access. There is an increasing need for wireless connectivity with emerging applications. More frequency spectrum is going to be opened-up and the number of standards seems to increase even further to cover this gap and the question arises of how to design the next generation of wireless receivers.

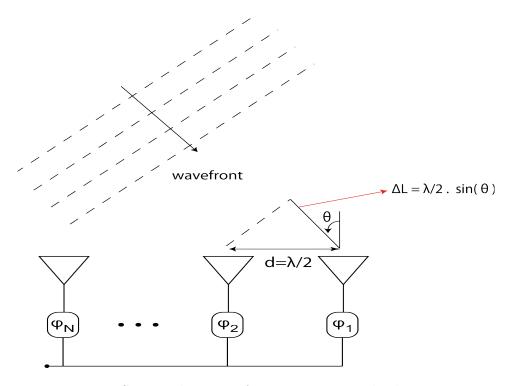

From a general perspective it is very appealing to have a single handheld device that can support a large number of wireless standards. Consequently, mobile handsets have started supporting multiple modes over the past few years. Since there are too many standards, integrating multiple dedicated radios on one platform is leading to bulky, complex designs and hence hardware sharing is becoming the only solution. One of the last hurdles in the realization of a multi-standard receiver is the elimination of off-chip SAW filters. Direct conversion receivers are widely implemented due to low cost and high-levels of integration at the cost of sensitivity to interferes and second order distortion, which are key contributors to degrading system sensitivity. This thesis describes two linearity enhancement techniques for an RF receiver.

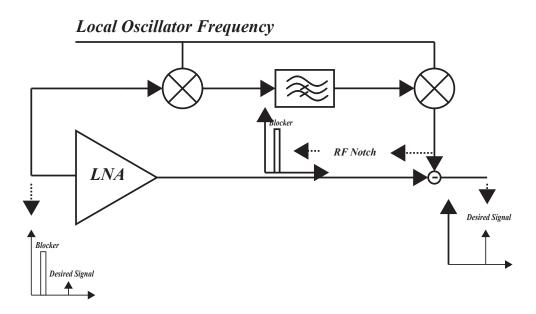

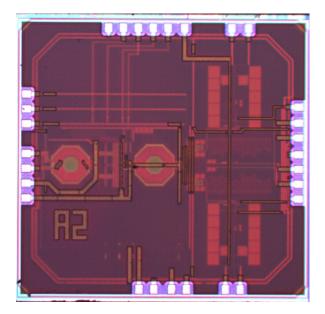

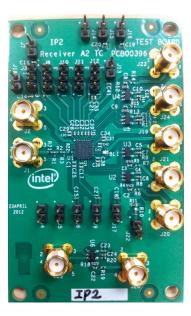

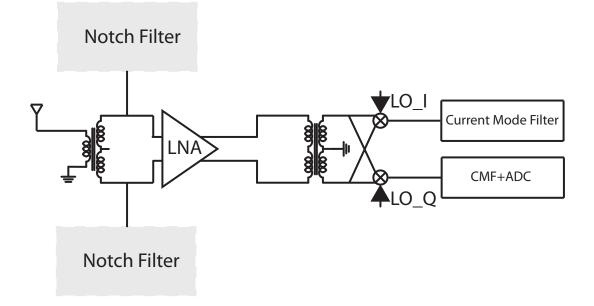

A self-calibrating even-order distortions technique is presented whereby different mechanisms responsible for even-order distortions, characterized by IIP2 metric (Second Harmonic Input referred Intercept Point), were independently calibrated, resulting in robust performance independent of the amplitude and frequency of the blocker. Second, an active dynamic blocker-notching scheme is proposed and tested. The filter uses the blocker frequency to upconvert a DC null to the pass-band, attenuating the blocker before entering the receiver. The prototype circuits are fabricated in a 90nm CMOS technology. Measurements were performed on a PCB with a packaged chip.

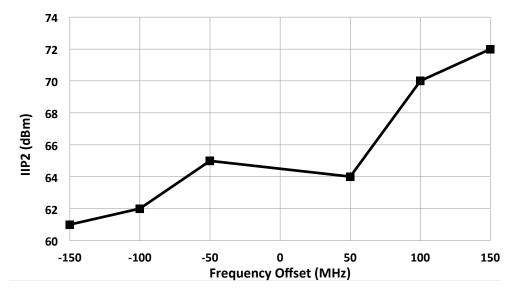

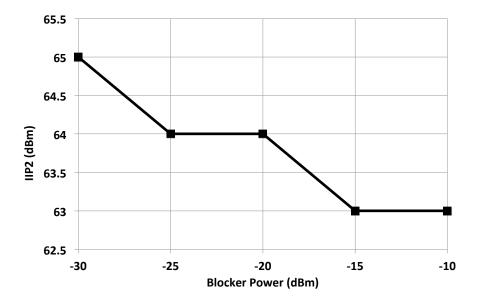

IIP2 measurements were performed with the blocker frequency and power swept. The IIP2 of more than 60dBm for wide range of blockers as high as -10dBm has been achieved which satisfy the most stringent IIP2 requirements. To test the functionality of the dynamic notch, a blocker signal and a desired signal are summed and injected into the front-end

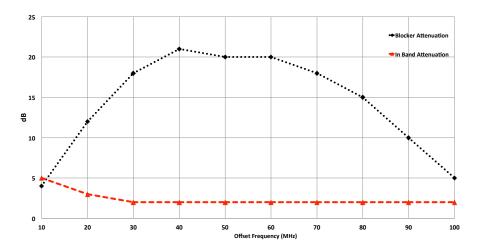

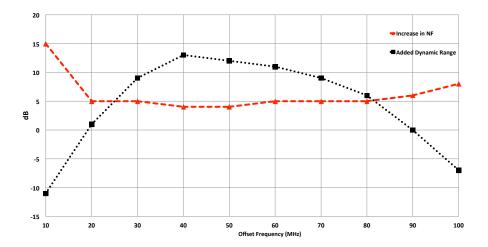

receiver. The amount of desired blocker attenuation and the amount of undesired in-band signal attenuation are both measured versus the offset frequency of the blocker. Blocker attenuation as large as 20dB is observed at only 40 MHz offset while the in-band attenuation increases by only 2dB. The resulting increase in noise figure due to the blocker is 4dB. When all of this data is taken into account, the overall SNR improvement due to the notch filter is as high as 14dB. This proves that the technique may be effective for attenuating blockers.

To My Mother, Professor Shahnaz Atabak

# Contents

| С  | ontents                                                                                                                                                                                   | ii                                                                                                         |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Li | st of Figures                                                                                                                                                                             | iv                                                                                                         |

| Li | st of Tables                                                                                                                                                                              | vii                                                                                                        |

| 1  | Introduction                                                                                                                                                                              | 1                                                                                                          |

| 2  | Fundamentals of Wireless Receivers         2.1       Receiver Architecture         2.2       Wireless Receiver Performance Metrics                                                        | <b>4</b><br>4<br>5                                                                                         |

| 3  | Trends and Challenges in Wireless Receivers3.1Multi-Mode Operation: An inevitable Trend3.2Tackling the Problem; ON Chip or OFF Chip?                                                      | 1 <b>7</b><br>17<br>22                                                                                     |

| 4  | Review of State-of-the-Art Wireless Receivers4.1Spatial Filtering                                                                                                                         | <ul> <li>28</li> <li>28</li> <li>29</li> <li>33</li> <li>34</li> <li>37</li> <li>38</li> <li>41</li> </ul> |

| 5  | Stable IIP2 Receiver5.1 Coping with Jammers: Two schools of thought5.2 IP2 Metrics Characterization5.3 IM2 Generation Mechanisms5.4 Automatic IP2 Calibration Chip5.5 Measurement Results | <b>46</b><br>46<br>47<br>48<br>62<br>68                                                                    |

| 6  | Adaptive Notch                                                                                                                                                                            | <b>75</b>                                                                                                  |

### 6 Adaptive Notch

|    |              | High-Q Notch Filter DesignFRONT END ARCHITECTURE |    |  |  |

|----|--------------|--------------------------------------------------|----|--|--|

|    |              | Measurement Results                              |    |  |  |

| 7  | Con          | clusion                                          | 96 |  |  |

| Bi | Bibliography |                                                  |    |  |  |

# List of Figures

| 1.1 | Marconi's station                                                                                                                                                                             | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

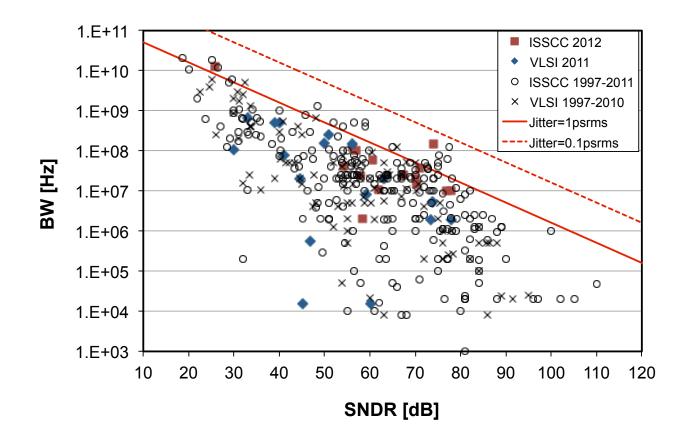

| 2.1 | ADC performance [55]                                                                                                                                                                          | 5  |

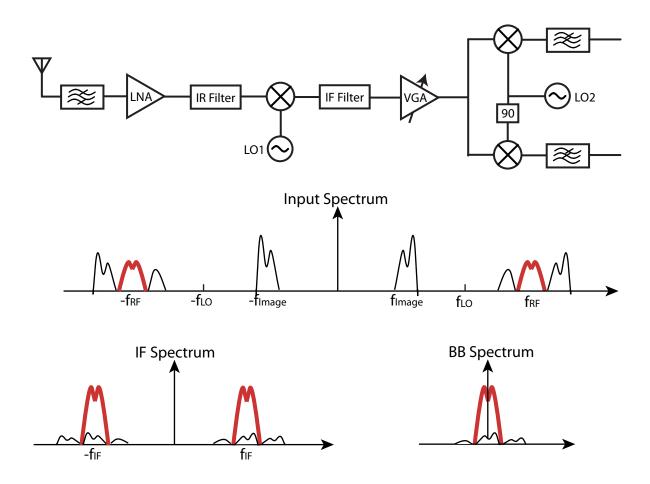

| 2.2 | Superheterodyne receiver                                                                                                                                                                      | 6  |

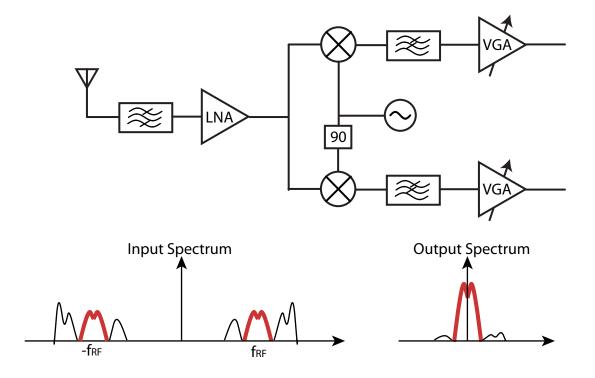

| 2.3 | Homodyne receiver                                                                                                                                                                             | 7  |

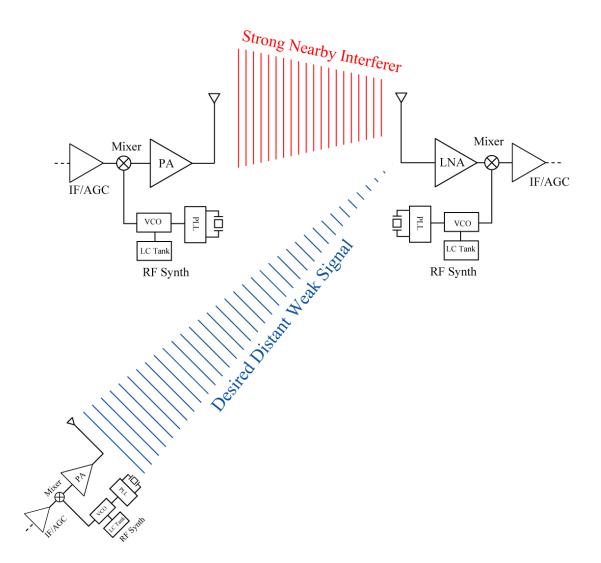

| 2.4 | Near far issue in wireless receivers [56]                                                                                                                                                     | 8  |

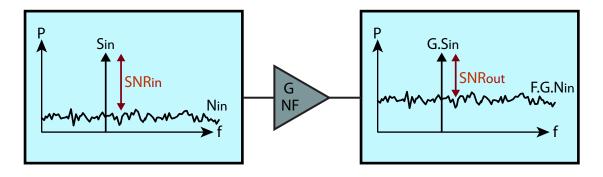

| 2.5 | Signal to noise ratio at input and output [26]                                                                                                                                                | 9  |

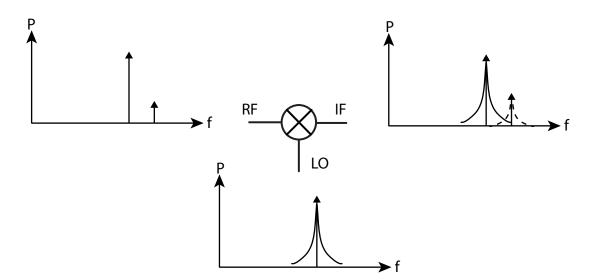

| 2.6 | Reciprocal mixing                                                                                                                                                                             | 10 |

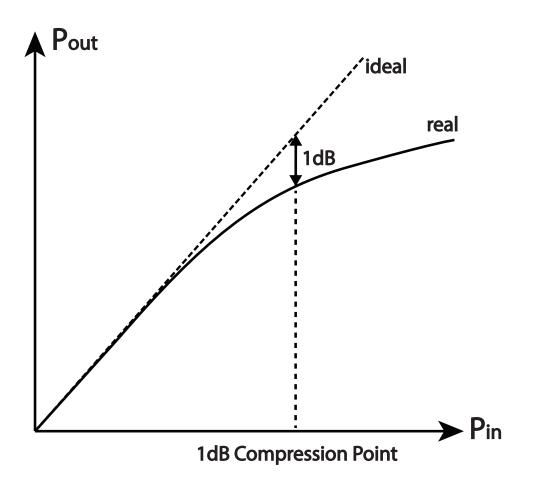

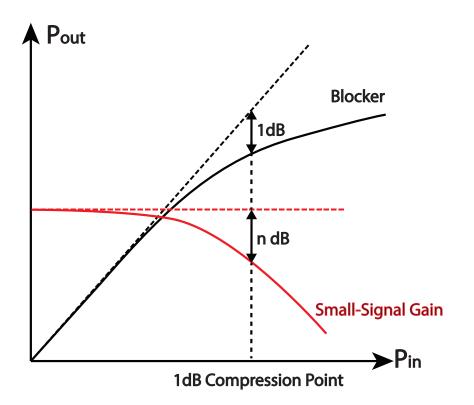

| 2.7 | Gain compression                                                                                                                                                                              | 12 |

| 2.8 | Desensitization                                                                                                                                                                               | 14 |

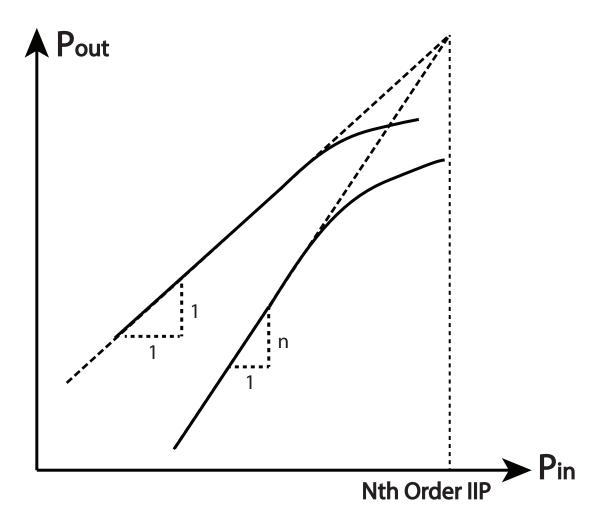

| 2.9 | Intercept point                                                                                                                                                                               | 15 |

| 3.1 | State of the art mobile handset. Source: isuppli                                                                                                                                              | 18 |

| 3.2 |                                                                                                                                                                                               | 18 |

| 3.3 |                                                                                                                                                                                               | 19 |

| 3.4 | Mask cost versus process                                                                                                                                                                      | 20 |

| 3.5 | CC spectrum allocation and the measured usage at the Berkeley Wireless Re-<br>search Center. The measurements were performed in the 0-2.5GHz frequencies<br>over a period of 10 minutes, [52] | 21 |

| 3.6 |                                                                                                                                                                                               | 22 |

| 3.7 |                                                                                                                                                                                               | 23 |

| 3.8 |                                                                                                                                                                                               | 25 |

| 4.1 | Current (a) and future (b) architectures of 3G receivers [23]                                                                                                                                 | 29 |

| 4.2 |                                                                                                                                                                                               | 30 |

| 4.3 |                                                                                                                                                                                               | 31 |

| 4.4 |                                                                                                                                                                                               | 32 |

| 4.5 | Positive feedback translational loop [36]                                                                                                                                                     | 33 |

| 4.6 | Q-Enhancement architecture                                                                                                                                                                    | 34 |

| 4.7 | Baseband noise amplification                                                                                                                                                                  | 36 |

| 4.8 | Impedance seen by the base-band looking at the RF side                                                                                                                                        | 36 |

| 4.9 |                                                                                                                                                                                               | 37 |

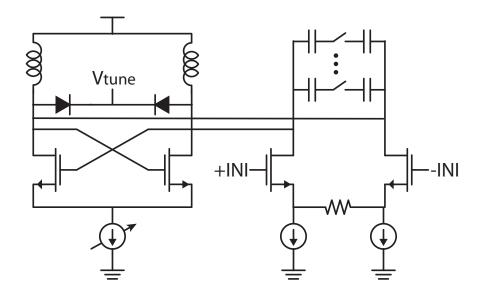

| 4.10 | Circuit diagram of the injection locked oscillator                                 | 38       |

|------|------------------------------------------------------------------------------------|----------|

|      | Circuit schematic of the core of the injection locked oscillator                   | 39       |

|      | Switched capacitor bandpass filter concept [49]                                    | 40       |

|      | Switched capacitor bandpass filter circuit schematics                              | 41       |

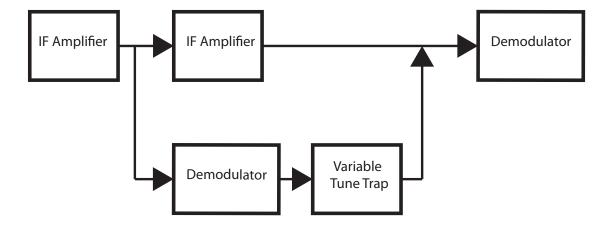

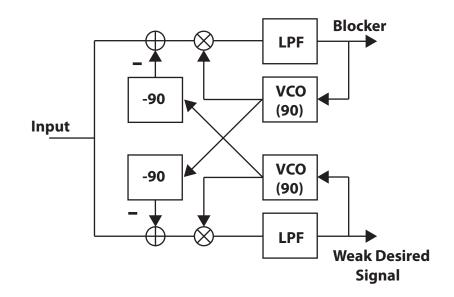

|      | System diagram of variable notch filter for FM radios                              | 42       |

|      | System diagram of a fixed notch filter for FM radios                               | 42       |

|      | Cross-coupled FM system with the interference canceler                             | 43       |

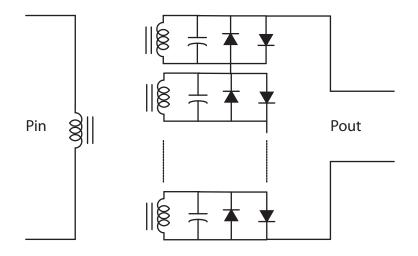

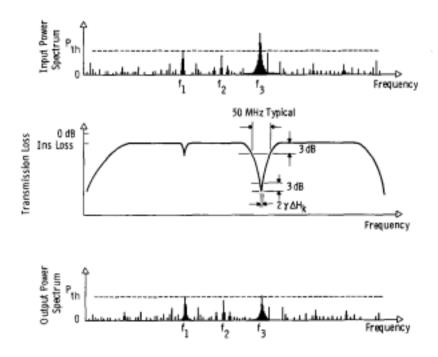

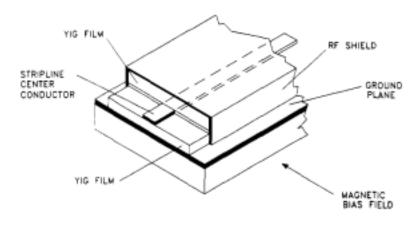

|      | Conceptual representation of frequency selective limiters (FS)                     | 43       |

|      | Typical frequency response of an FSL for different power input levels and the      |          |

| 1.10 | resulting output power [3]                                                         | 44       |

| 4.19 |                                                                                    | 45       |

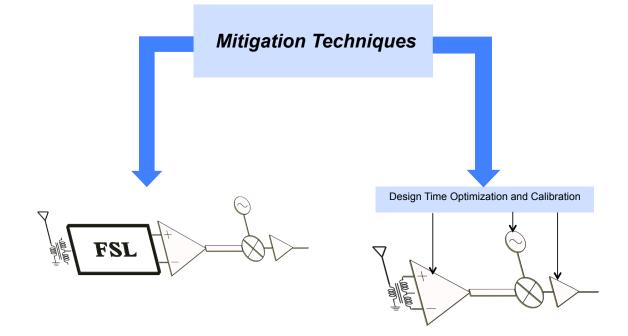

| 5.1  | Where to deal with blockers                                                        | 47       |

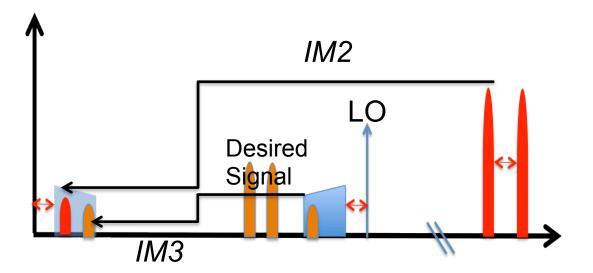

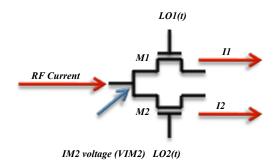

| 5.2  | Wideband susceptibility of systems to IM2 contents                                 | 48       |

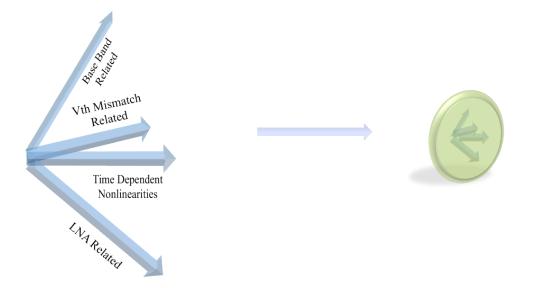

| 5.3  | Vectors responsible for IM2 generation                                             | 49       |

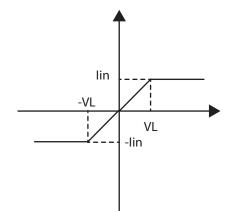

| 5.4  | I-V characteristics of mixers                                                      | 50       |

| 5.5  | Mixer as a black box with time-varying impedance characteristics                   | 52       |

| 5.6  | Differential mixer input and output currents                                       | 53       |

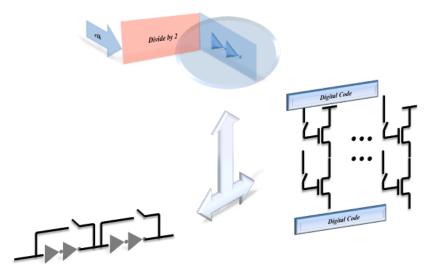

| 5.7  | Course and fine tuning of the applied clock                                        | 56       |

| 5.8  | Waveforms crossing at $50\%$                                                       | 57       |

| 5.9  | Non-overlapping waveforms                                                          | 57       |

| 5.10 | Overlapping waveforms                                                              | 58       |

| 5.11 | Impedance path during the overlap time                                             | 59       |

| 5.12 |                                                                                    | 60       |

| 0.1  | Mixer with baseband load's mismatch                                                | 60       |

|      | Passive mixer with baseband load                                                   | 61       |

|      | Crosstalk between I and Q channels                                                 | 61       |

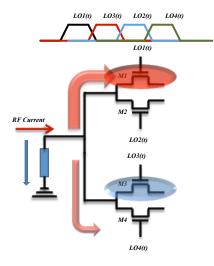

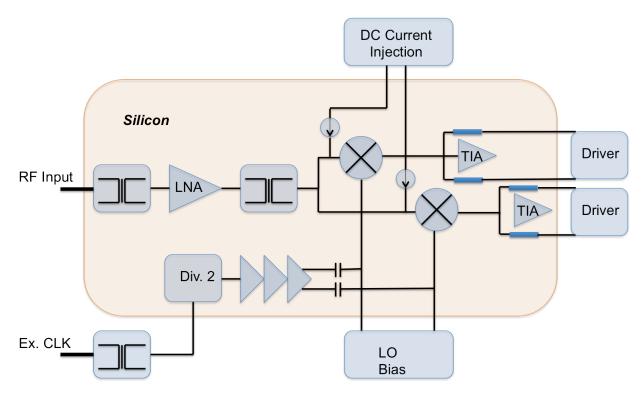

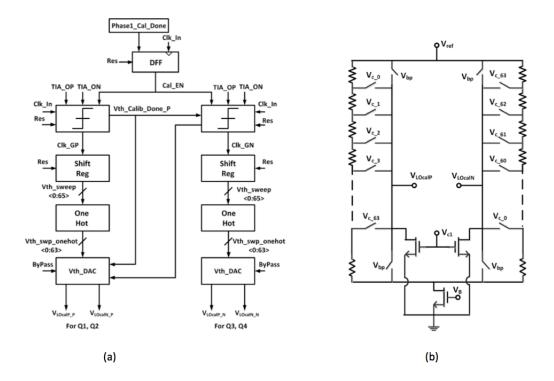

|      | System level diagram of the chip                                                   | 62       |

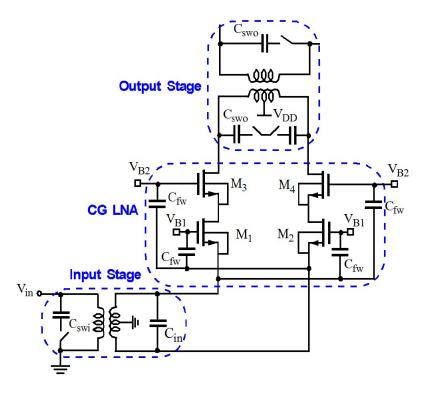

|      | Common gate LNA                                                                    | 64       |

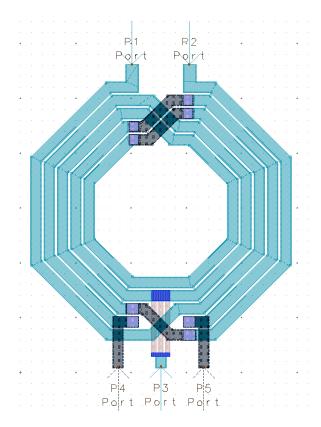

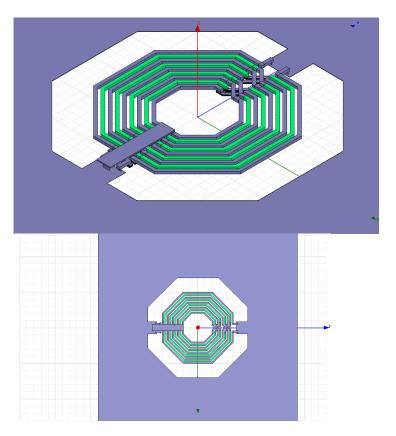

|      | Input balun                                                                        | 65       |

|      | LNA output network design consideration                                            | 65       |

|      |                                                                                    | 66       |

|      | Output balun                                                                       | 66       |

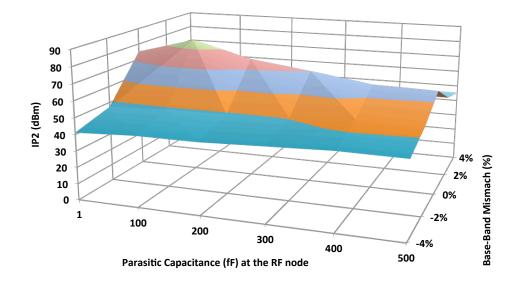

|      | Parasitic capacitance effect on the IP2 performance                                | 67       |

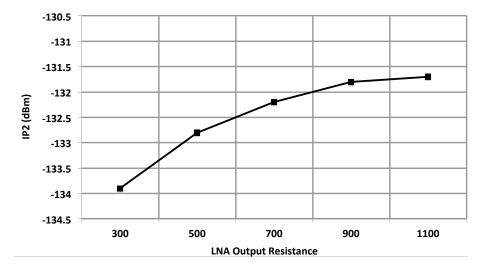

|      | LNA output impedance effect on the IP2 performance                                 | 07       |

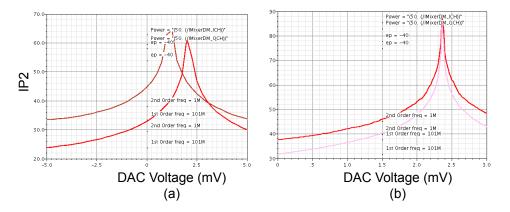

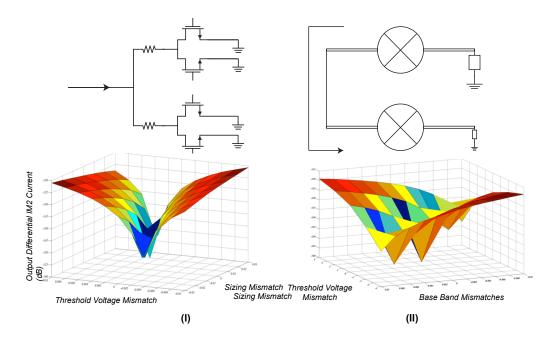

| 0.23 | Threshold vs. sizing (I) and threshold vs. baseband (II) comparison for IM2        | 69       |

| F 04 | generation                                                                         | 68<br>68 |

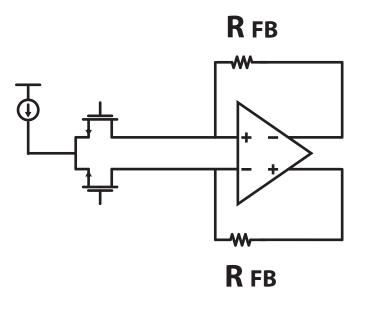

|      | Baseband calibration scheme                                                        | 69<br>60 |

|      | Injecting a DC current to the mixer                                                | 69       |

| 5.26 |                                                                                    |          |

|      | TIA section and (b) schematic of the mixer fed with digitally controlled gate bias |          |

| - 0- | voltages                                                                           | 70       |

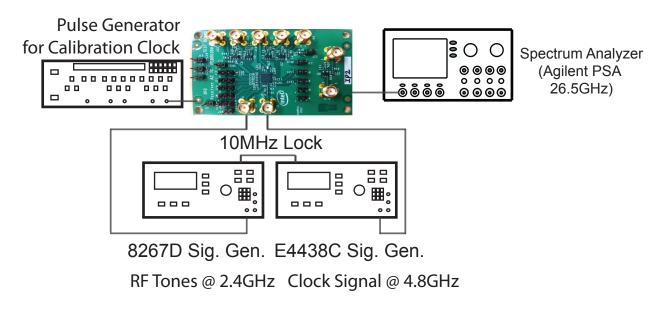

| 5.27 | Measurement setup                                                                  | 71       |

| 5.29<br>5.30<br>5.31 | IIP2 vs. blocker frequency (LO=2.4GHz and tone separation=1MHz)7IIP2 vs. blocker input power (dBm) (LO=2.4GHz and blockers @ 2.3GHz)7Die photo of the self-calibrating IP2 chip7PCB of the self-calibrating IP2 chip7PCB of the manual-calibrating IP2 chip7 |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

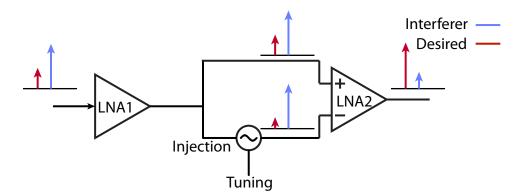

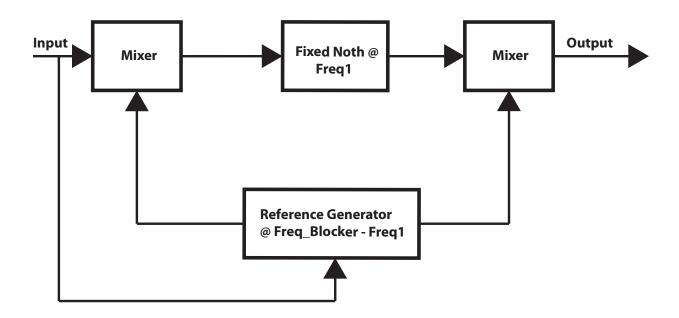

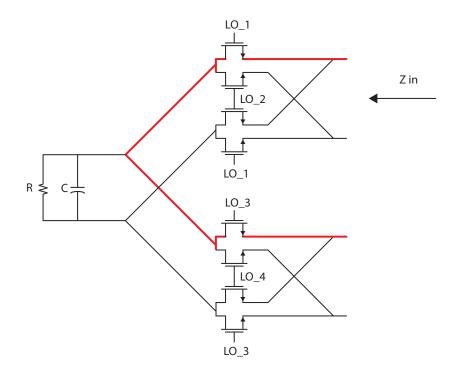

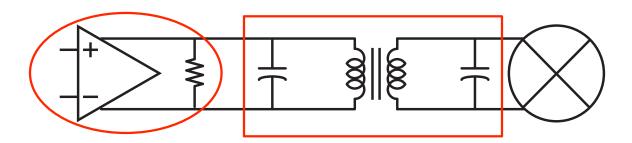

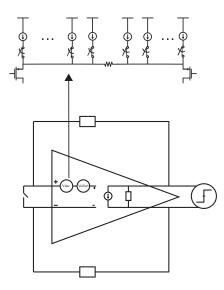

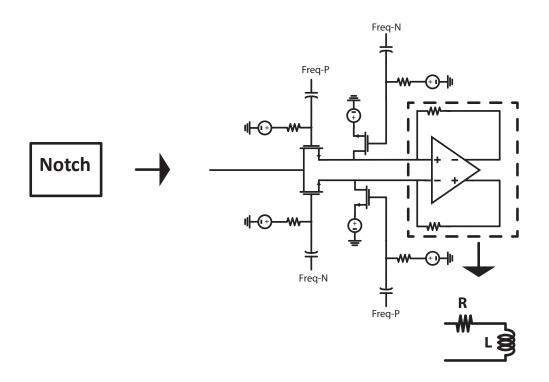

| 6.1                  | Conceptual schematic of the notch filter                                                                                                                                                                                                                     |

| 6.2                  | Schools of thought for dealing with blockers                                                                                                                                                                                                                 |

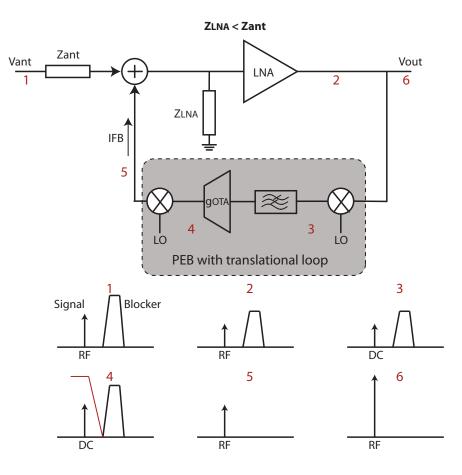

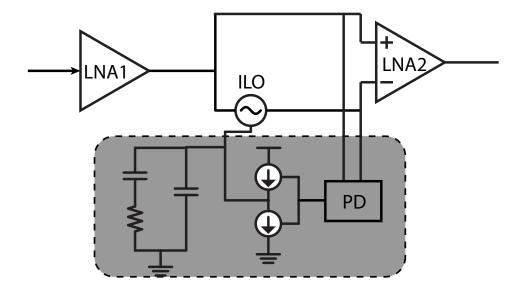

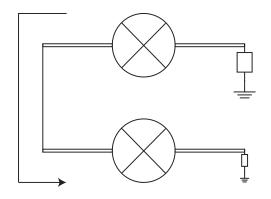

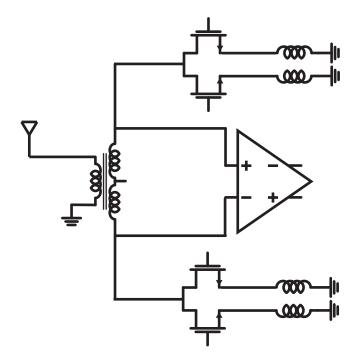

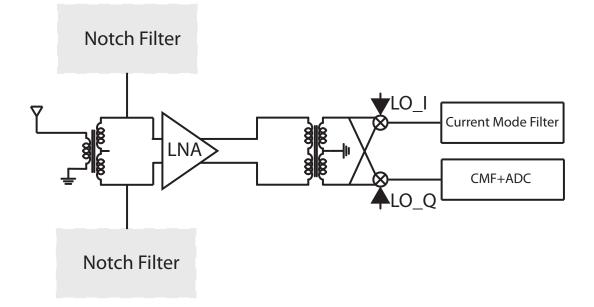

| 6.3                  | System level diagram of the receiver with adaptive notch                                                                                                                                                                                                     |

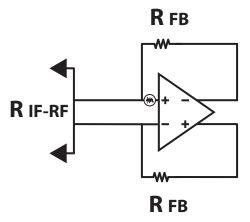

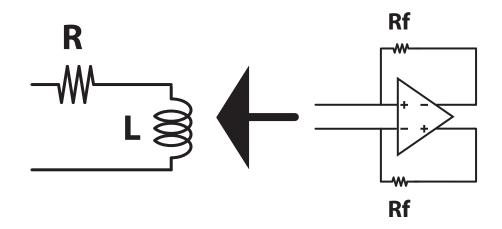

| 6.4                  | Feedback amplifier for synthesizing an inductor                                                                                                                                                                                                              |

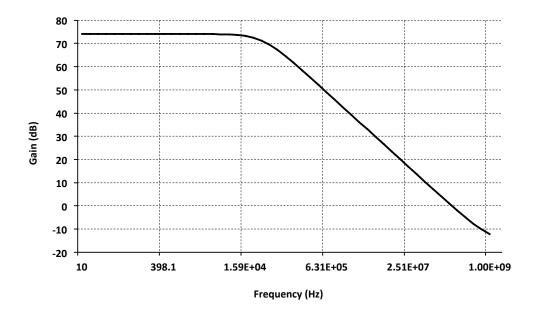

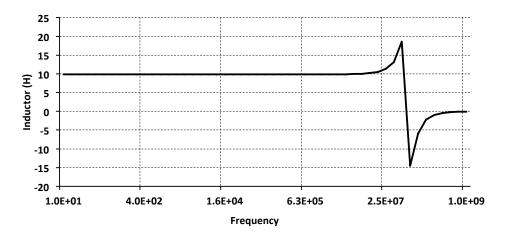

| 6.5                  | Gain of the operational amplifier for the synthesized inductor                                                                                                                                                                                               |

| 6.6                  | Synthesized inductor's magnitude vs. Frequency                                                                                                                                                                                                               |

| 6.7                  | Conceptual Schematics of the notch                                                                                                                                                                                                                           |

| 6.8                  | Active inductor with switches                                                                                                                                                                                                                                |

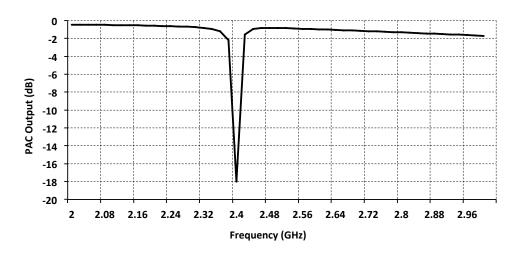

| 6.9                  | Frequency response of the notch filter                                                                                                                                                                                                                       |

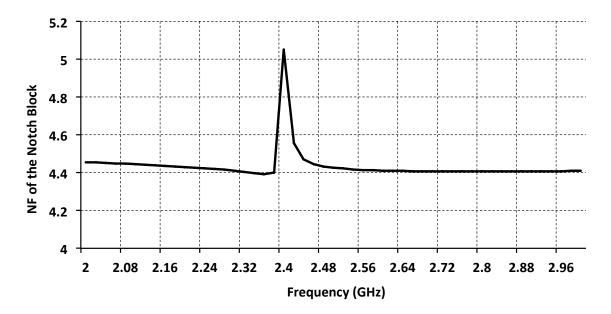

| 6.10                 | NF vs. frequency of the notch                                                                                                                                                                                                                                |

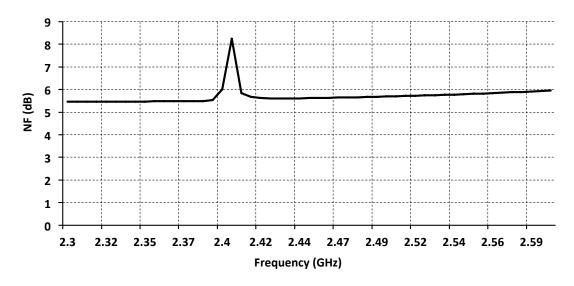

| 6.11                 | NF vs. frequency of the whole system when the notch filter is ON                                                                                                                                                                                             |

|                      | Block diagram of the receiver with an adaptive notch filter                                                                                                                                                                                                  |

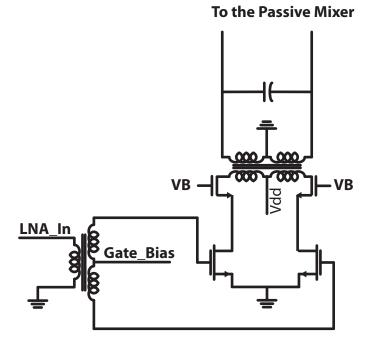

|                      | Schematic of the LNA with input balun                                                                                                                                                                                                                        |

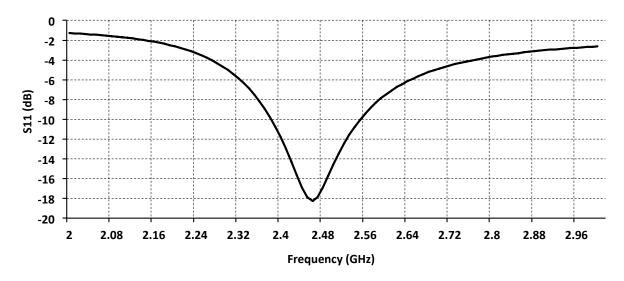

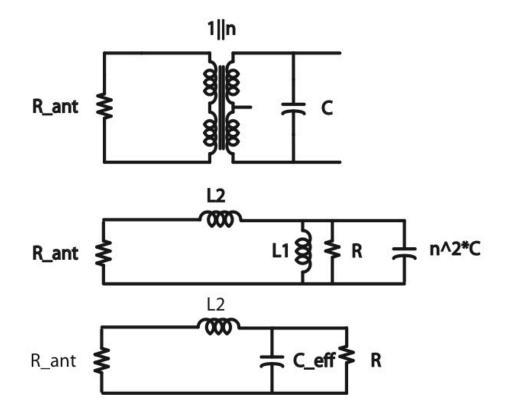

|                      | Matching of the common source architecture by a low-K balun                                                                                                                                                                                                  |

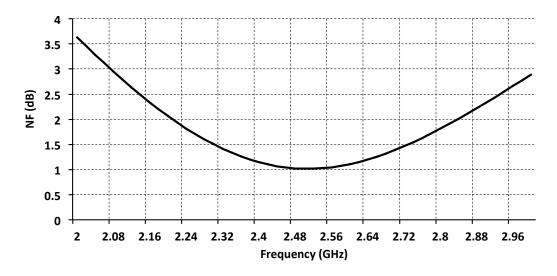

|                      | Noise figure of the LNA 8                                                                                                                                                                                                                                    |

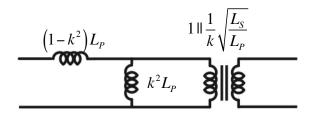

|                      | Balun equivalent circuit                                                                                                                                                                                                                                     |

|                      | Impedance step-up matching                                                                                                                                                                                                                                   |

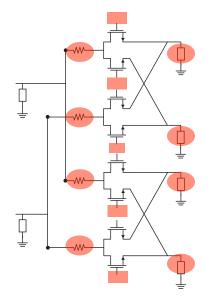

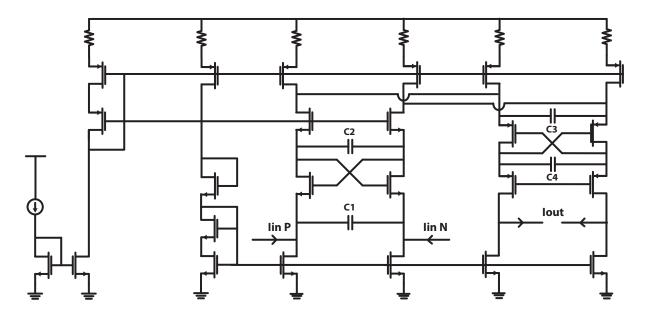

|                      | Schematic of the current-in current-out baseband filer                                                                                                                                                                                                       |

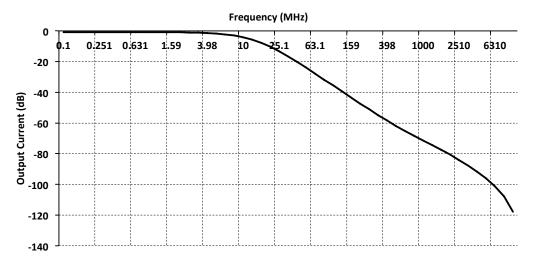

|                      | Frequency response of the baseband current mode filter                                                                                                                                                                                                       |

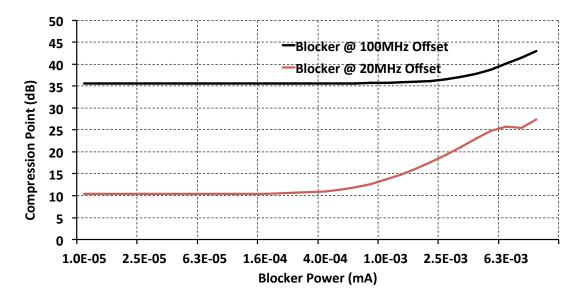

|                      | Baseband filter compression point vs. blocker power                                                                                                                                                                                                          |

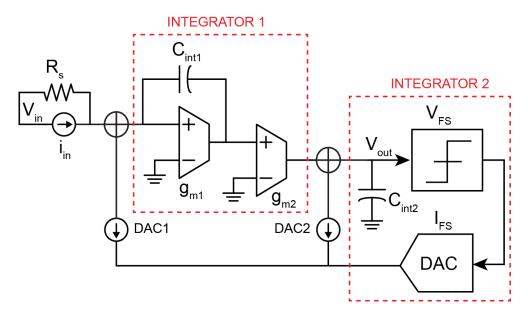

|                      | Schematic of the sigma-delta ADC with current domain input                                                                                                                                                                                                   |

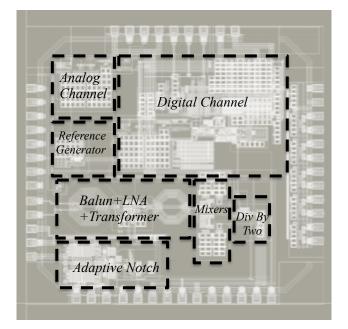

|                      | Die photo of the current mode receiver with an integrated adaptive notch filter . 9                                                                                                                                                                          |

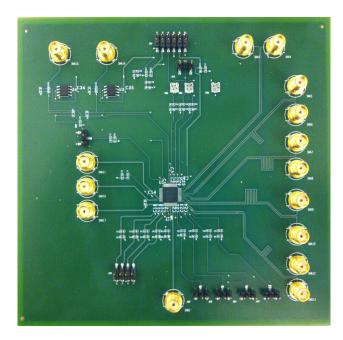

|                      | PCB of the current mode receiver with an integrated adaptive notch filter 9                                                                                                                                                                                  |

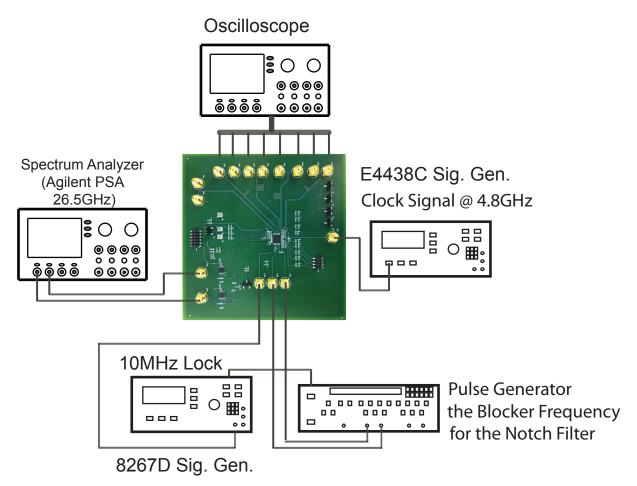

|                      | Measurement setup                                                                                                                                                                                                                                            |

| 6.25                 | Notch performance vs. frequency offset of blocker: Blocker attenuation and un-                                                                                                                                                                               |

|                      | desired signal attenuation                                                                                                                                                                                                                                   |

| 6.26                 | Notch performance v. frequency offset of blocker: Increase in NF and the overall                                                                                                                                                                             |

|                      | increase in receiver dynamic range                                                                                                                                                                                                                           |

# List of Tables

| 5.1 | LNA Specifications           |     | • |   |     |   |     | •   |   | • |   | • |       | 63 |

|-----|------------------------------|-----|---|---|-----|---|-----|-----|---|---|---|---|-------|----|

| 5.2 | IP2 Chip Performance Summary |     | • | • |     |   |     | • • | • | • | • | • |       | 74 |

|     |                              |     |   |   |     |   |     |     |   |   |   |   |       |    |

| 61  | ADC Targeted Specification   |     |   |   |     |   |     |     |   |   |   |   |       | 01 |

| 0.1 | ADC Targeted Specification   | • • | • | • | • • | • | • • | • • | · | · | • | • | <br>• | 91 |

#### Acknowledgments

I am grateful for working with brilliant minds at Berkeley during the past few years. First, I want to thank my advisor, professor Ali M. Niknejad who patiently sat with me, monitored my thoughts and instead of overriding them, showed me the correct way as "another way to look at it". This way I could gradually learn critical thinking skills.

I am also thankful of my qualification and thesis committee members professor Jan M. Rabaey, professor Elad Alon and professor Paul K. Wright. It was an honor to have them on my committees. I learnt a lot from their visionary thoughts and valuable feedbacks.

I want to thank my best friends Amin Arbabian and Maryam Tabesh. We started our friendships from early days of undergraduate studies and we have been classmates and group mates ever since. We grew up together and I cannot think of any part of my life without them.

I also thank my friends and colleagues Ehsan Adabi, Wei-Hung Chen, Jun-Chau Chien, Lu Ye, Jiashu Chen, Siva Thyagarajan, Steven Callender, Shinwon Kang, Chintan Thakkar, Lingkai Kong, Yue Lu, Jesse Richmond, Simone Gambini, Arash Parsa, Pedram Zadeh and other Berkeley Wireless Research Center (BWRC) colleagues along with directors and staffs for making BWRC a world-class research center and an enjoyable place to work.

I would like to thank my co-workers Christopher D. Hull, Yanjie J. Wang and Hua Wang at Intel Corp. where I did an internship and learnt how to look at problems from the industry's perspective.

I will be always proud of being part of the Berkeley community.

# Chapter 1 Introduction

In 1864 James Clerk Maxwell derived the fundamental equations for electromagnetic fields. Shortly afterward, Heinrich Hertz validated the equations based on a experiment which propagated the electromagnetic waves into the free space. The radio was invented later on with the patent of Guglielmo Marconi, the first patent in wireless communications. The idea was to put information on these free-space propagating EM waves to get rid of the wires.

Since then, quite a large number of brilliant minds (and also billions of dollars!) from different fields contributed to evolving the wireless communication. Looking at the pace of progress, one would observe the kink, [58], at the mid-twentieth century where two groundbreaking scientific discoveries happened. Invention of the transistor by William Shockley at Bell laboratories and on the information theory side, the definition of the channel capacity by Claude Shannon. Microelectronics and information theory ever since have progressed quite dramatically that connectivity and mobility is a commodity. Variety of wireless standards are providing different services, e.g. voice and data transfer, Internet access, etc. among different geographical regions. The ever-increasing need for bandwidth has been fulfilled with developing semiconductor technology, and as a result, the wireless services have kept improving steadily.

Wireless communication is routinely used in everyday life and it is more like a commodity these days than a fancy technology. It's used for all kind of information transferring without a need for troublesome, expensive infrastructure to connect the devices. Consequently more and more platforms are being built upon it and hence the quest for bandwidth has been steadily intensified.

The wireless service industries need to keep pace with markets needs. Therefore, they have started to include more and more radios on one platform that would result in bulky complex designs which not only takes massive amount of resources to design but also this approach can't be sustained with the continually increasing number of standards and fastchanging technology which requires porting designs frequently.

Hence hardware sharing or multi-standard modules have become a must to meet the ever-increasing market's need. One of the most important issues in the realization of multistandard receivers is the elimination of off-chip SAW filters so that signals from different

Marconi's Mobile Telegraph Station 1906

Figure 1.1: Marconi's station

bands can enter the shared hardware.

One can imagine this wide-band system would process a number of non-desired, interferers, along with the desired signals. Now the blocks that were designed to only deal with desired signals should be able to withstand blockers, sometimes many orders of magnitudes higher than desired signals. This issue would be exacerbated by the fact that in more advanced nodes, transistors have poor linearity performance and supply voltage reduction deprives designer from a pool of circuit tricks that would allow them to tackle this issue.

Hence, during past few years a number of promising solutions have been offered from different themes in the wireless systems to enable multi-mode multi-standard operation so that society would witness faster and smarter device which are enabler to communicate with almost everything in the environment, from satellite GPS all the way down to inside our bodies.

This thesis will first present the fundamentals of wireless receivers and what are the important parameters one should be looking at optimizing. Then it will discuss the trends in the wireless industry and will present the state-of-the-art systems with their pros and cons.

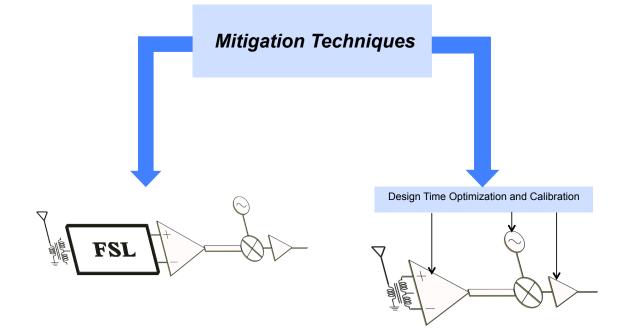

Overall there are two schools of thought for attacking the blocker problem. One is to optimize each block to linearity so it could process the blockers without loosing their sensitivity. The other approach is to get rid of the jammers as soon as possible.

Both approaches have been pursued in this work and the pros and will be presented in chapters 5 and 6.

## Chapter 2

# **Fundamentals of Wireless Receivers**

In this chapter, fundamentals of wireless receivers will be reviewed. It begins with the introduction of direct conversion receiver and its inherent trade-offs. Furthermore, performance metrics characterizing receivers will be covered.

### 2.1 Receiver Architecture

The application of wireless receiver is to identify the desired signal, transform it from the electromagnetic domain to electric signals, and process them (frequency shift and amplification) such that the analog to digital converters can be able to convert them to the digital domain. Where to put the border for this transition depends on the accuracy and speed of these converters and hence the definition of wireless receiver and its architectures should be revisited every once in while due to rapid change in the technology. The so call holy grail is to put an ADC right after the antenna [53]. Looking at today's ADC performances, it reveals the speed of operation and the dynamic range required haven't been met concurrently. As a result, traditional architectures still play a vital role.

Among different receiver architectures that have been invented, heterodyne and direct conversion receiver are the most used ones. However, due to extremely simple architecture, the direct conversion receiver [2] and [60] has become the receiver topology of choice for monolithically integrated receivers. In the cellular market, direct conversion architectures have superseded the well established heterodyne architecture.

In heterodyne receivers, the RF signal is first down-converted to an intermediate frequency (IF). Then, the signal would be filtered with high Q IF filter which could not be implemented in the RF domain. Afterward the final down-conversion would occur. This approach requires a few number of off-chip filters for band-selection and image rejection, two reference clocks and is quite power hungry and overall, not friendly to integration.

On the other hand, the direct conversion architecture requires minimum number of filters since it doesn't need image rejection as the frequency shifting is happening once. However, this approach suffers from a number of disadvantages. Most important ones arise from the

Figure 2.1: ADC performance [55]

fact that signal is directly retrieved from a low-frequency regime. That makes the system very sensitive to any phenomena leading to generation noise/non-desirable content at low-frequency.

In terms of noise, when it comes to low-frequency regime, the flicker noise will be dominant mechanism. Unfortunately it exacerbates as transistors scale down. From non-desirable content generation, the main mechanisms responsible for them are even order distortions as they have an inherent down-conversion mechanism mathematically. These two effects, specially the second one, will make the design of DCR challenging. One chapter of this thesis is dedicated to the issue of the even-order distortions and will be covered in details.

### 2.2 Wireless Receiver Performance Metrics

In order to characterize wireless receivers, performance metrics have to be defined. In this section, fundamental parameters which characterize a wireless receiver are discussed. The quality of wireless signal is deteriorated by receiving undesired signals throughout the chan-

Figure 2.2: Superheterodyne receiver

nel. Also other than the noise added by the channel, the wireless transceivers add their own noise and unwanted signal degrading the quality even further.

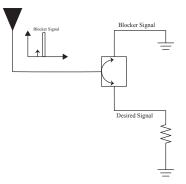

Above shows a typical challenging scenario of a receiver receiving a weak desired signal from a far away transmitter and at the same time, a close-by transmitter is jamming the receive with a strong unwanted signal.

Since jammers in channels can be several orders of magnitude greater than the desired signal, implementing a system that is able to detect the weak wanted signal while receiving a strong interferer presents the major RF design challenge of incorporating a low noise system with good linearity.

To characterize an extent to which wireless receivers deteriorate signal quality, various parameters are used.

Figure 2.3: Homodyne receiver

#### Noise

Random fluctuations of physical quantities would cause picking up signals at the frequencies of interest that are not related to our desired signal and would place a threshold on the minimum signal one can detect. This is a serious problem in wireless receiver as the signals they are trying to pick-up sometimes are extremely small (on the order of microvolt). The metric for that in wireless receivers is noise figure. Generally noise in CMOS receiver is coming from three sources [31]:

- **Thermal noise** is due to thermal movement of charge carriers. Any circuit elements that include resistor in its modeling, has thermal noise. The spectral density of thermal noise is constant and can be modeled as white noise.

- Shot noise exists in structures that charge carriers are passing a potential barrier such as P-N junctions or the gate barriers. The power spectral density of this type is constant as well and can be modeled as a white noise.

- **Flicker noise** is due to trap and release of the carriers at the silicon channel and the oxide. The time constant of this phenomenon causes the power spectral density to have 1/f characteristics.

Figure 2.4: Near far issue in wireless receivers [56]

Figure 2.5: Signal to noise ratio at input and output [26]

No matter what the source of the noise, one needs to characterize the overall noise performance of the receiver. This can be done with the following equation. Since the input noise which is coming from black body radiation to the system and the desired signal will see the same gain down the chain, the signal to noise ratio would get exacerbated due to the noise added by the system. This ratio is called noise factor and the logarithm of F is defined as the noise figure:

NoiseFactor =

$$\frac{\text{SNR}_{\text{in}}}{\text{SNR}_{\text{out}}}$$

(2.1)

$$NF = 10\log(NoiseFactor)[dB]$$

(2.2)

The receiver noise factor is an important parameter in determining the weakest signal that the system can process. This translates directly into a maximum distance from the transmitter where communication is possible. The output noise power of a receiver, being a function of the noise factor, bandwidth and receiver gain, can be calculated as follow:

$$N_{OUT}[dBm] = -174dBm + 10logBW + NF[dB] + G[dB]$$

$$(2.3)$$

Now if one divides the output noise by the receiver gain to get the equivalent input referred noise, that would set the minimum signal that the system is able to detect.

$$MDS[dBm] = -174dBm + 10logBW + NF[dB]$$

(2.4)

The noise floor is directly proportional to bandwidth. Consequently, higher data rate systems which require more bandwidth for a specific modulation scheme, the minimum detectable signal rises.

Figure 2.6: Reciprocal mixing

#### Sensitivity

Sensitivity is defined as the minimum signal power required for a specific quality of received information. In digital information, this would be measured by the bit error rate. Basically, sensitivity is the required power level to achieve a specific signal to noise ratio:

$$Sens[dBm] = MDS[dBm] + SNR[dB]$$

(2.5)

#### Phase Noise

The local oscillator of the system is the unit in charge of frequency shifting of the received RF signal. The ideal condition from a mathematical point of view is to have a tone in the frequency spectrum to shift the frequency content. However, due to non-idealities and the existence of noise, the phase of the waveform has a jitter component which would spread the energy of the tone in the spectrum.

$$LO(t) = A\cos(\omega_{LO}t + \phi_{n(t)}) \tag{2.6}$$

$\phi_{n(t)}$  represents phase noise. Basically it would modulate the signal that results in sidebands forming around the carrier. Phase noise is characterized in the frequency domain in terms of dBc/Hz at a given offset frequency from the carrier frequency.

Phase noise in wireless receiver is responsible for a phenomenon called reciprocal mixing. Since the function of mixer is multiplying the RF signal with the LO signal in the time domain, that would translate to convolution in the frequency domain. Now if there are blockers near the RF signal, lets say X Hz away, coming through the RF port, they would be down-converted and fall ON top of the desired signal with the noise energy X Hz away from the carrier.

The noise level in the wanted signal band caused by reciprocal mixing can be expressed as follow:

$$P_{n,recmix}[dBm] = P_{blocker}[dBm] + L(\Delta f) + 10logBW$$

(2.7)

where  $P_{blocker}$  is the blocker level,  $\Delta f$  is the offset between the blocker and the wanted signal frequencies while BW denotes the wanted signal bandwidth. The assumption is that the phase noise is constant across the BW of the desired signal. If the bandwidth of the signal is large and it changes across it, that should be taken under consideration.

#### Nonlinearity

Nonlinear systems can be categorized as systems which are capable of generating new frequencies. In other words, their output frequency spectrum is not necessarily the same as the input.

To begin the study the effects of nonlinearities, one should start with the time-invariant, memoryless nonlinear systems. For such systems, the output signal can be expressed using a Taylor series expansion as:

$$y(t) = a_1 x(t) + a_2 x^2(t) + a_3 x^3(t) + \dots$$

(2.8)

#### Harmonics

If a sinusoid is applied to a nonlinear system, the output contains frequency components that are integer multiplies of the input frequency. Putting  $A\cos(\omega t)$  in the above equation one obtains:

$$y(t) = a_0 + a_1 A \cos(\omega t) + a_2 A^2 \cos^2(\omega t) + a_3 A^3 \cos^3(\omega t)$$

(2.9)

$$= a_0 + a_1 A \cos(\omega t) + \frac{a_2 A^2}{2} (1 + \cos(2\omega t)) + \frac{a_3 A^3}{4} (3\cos(\omega t) + \cos(3\omega t))$$

$$= a_0 + \frac{a_2 A^2}{2} + (a_1 A + \frac{3a_3 A^3}{4}) \cos(\omega t) + \frac{a_2 A^2}{2} \cos(2\omega t) + \frac{a_3 A^3}{4} \cos(3\omega t)$$

From the above equation, one can calculate the expected harmonics power in the output spectrum. There are a few important metrics obtained from the above equation:

#### Gain Compression

All designed systems have specific dynamic range. The minimum signal that the system can be detected which is set by the the gain and noise budget. The maximum signal which is

Figure 2.7: Gain compression

function of the gain and available headroom and the linearity characteristics of the building blocks.

The small-signal gain  $a_1$  parameter valid only for sufficiently low-power regimes. As the amplitude of the power of the input signal increases, the power of output signal increases linearly until certain amount. Then, the gain of the system at that particular frequency starts changing. This phenomenon is natural as there is always limitations to the amount of signal power a system can generate.

To quantify the effect, a parameter called 1dB compression point (1dB CP) is defined. It is defined as the input signal level at which the output signal level drops by 1dB compared to a perfectly linear device. Consider a system in which it can be defined by nonlinearities up to third order. As expanded above, the gain which the fundamental tone would see is:

$$G = a_1 + \frac{3}{4}a_3A^2 \tag{2.10}$$

where A is the amplitude of the input signal. Evidently, the second term is responsible

for the gain compression. First, one might notice about the importance of the sign of  $a_3$ . Considering the conservation of energy in the electronic system,  $a_3$  should be negative for a signal large enough. Then the 1dB compression point would be:

$$\sqrt{0.11\frac{4|a_1|}{3|a_3|}}\tag{2.11}$$

Generally, the 1dB CP gives system designer a sense of how linear the system is and when it will enter the nonlinear regime so one should start to worry about other mechanisms.

#### Desensitization

This phenomenon is much more troublesome for RF designer than the compression. Since in this one, the desired signal remains weak and the interference is the one jamming the radio.

So why desensitization is harming the system? Imagine a scenario in which a high power undesired signal is accompanying a desired low power signal. The gain of the system is compressed due to processing of this large undesired signal. Hence, the noise figure would rise according to the:

$$F_{\text{Total}} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_k - 1}{G_1 G_2 \dots G_{k-1}}$$

(2.12)

If the gain drops,  $G_1$ , the noise contribution from the following stages becomes important. Now the minimum detectable signal should have a higher power to be seen through the noise.

To quantify the effect, the equations is the same as the compression scenario with the difference in the input signal. This time there are two signals, desired and the jammer,  $x(t) = (A_S \cos(\omega_S t) + A_L \cos(\omega_L t))$ , then the output is:

$$y(t) = (a_1 A_S + \frac{3a_3 A_S^3}{4} + \frac{3a_3 A_S A_L^2}{2})\cos(\omega_S t)$$

(2.13)

Having in mind  $A_S \ll A_L$ , one can obtain the gain which the desired signal sees:

$$y(t) = (a_1 + \frac{3a_3 A_L^2}{2}) A_S \cos(\omega_S t)$$

(2.14)

As discussed before, the  $a_3$  term is negative and as a result, the gain would be decreased with increasing the blocker power. Based on the above equation, one can calculate the amount of gain drop as the blocker power increases.

#### Intermodulation Distortion

Intermodulation distortion (IMD) happens when the input signals are not pure tones anymore. In such scenarios, the components in the output spectrum are not necessarily harmonics of one another. These distortion products originate from the difference and sum of input tones and their harmonics. To quantify these effects, one can consider the following

Figure 2.8: Desensitization

input signal in which the  $x(t) = A_1 \cos(\omega_1 t) + A_2 \cos(\omega_2 t)$ . Calculating up to third order one would get:

$$y(t) = a_0 + a_1(x(t)) + a_2(x(t))^2 + a_3(x(t))^3$$

(2.15)

Expanding this equation would result in component at fundamentals and also at  $\omega_1 \pm \omega_2$ ,  $2\omega_1 \pm \omega_2$  and  $2\omega_2 \pm \omega_1$ . Products at  $\omega_1 \pm \omega_2$  result from second-order nonlinearity (described by the coefficient a2) and are referred to as second-order intermodulation distortion (IMD2). Products at  $2\omega_1 \pm \omega_2$  and  $2\omega_2 \pm \omega_1$  result from third-order nonlinearity (described by the coefficient  $a_3$ ) and are called third-order intermodulation distortion (IMD3). Second-order distortion products at  $\omega_1 \pm \omega_2$  are problematic mainly in Homodyne receivers. On the other hand, third-order intermodulation products are problematic in all the receivers regardless of their architecture since they can be quite close to the incoming desired RF signal in the frequency spectrum.

For fundamentals:

$$\left(a_1 A_1 + \frac{3a_3 A_1^3}{4} + \frac{3a_3 A_1 A_2^2}{2}\right)\cos(\omega_1 t) \tag{2.16}$$

Figure 2.9: Intercept point

$$\left(a_1 A_2 + \frac{3a_3 A_2^3}{4} + \frac{3a_3 A_2 A_1^2}{2}\right)\cos(\omega_2 t) \tag{2.17}$$

$$a_2 A_1 A_2 \cos[(\omega_1 + \omega_2)t] + a_2 A_1 A_2 \cos[(\omega_1 - \omega_2)t]$$

(2.18)

$$\frac{3a_3A_1^2A_2}{4}\cos[(2\omega_1+\omega_2)t] + \frac{3a_3A_1^2A_2}{4}\cos[(2\omega_1-\omega_2)t]$$

(2.19)

$$\frac{3a_3A_2^2A_1}{4}\cos[(2\omega_2+\omega_1)t] + \frac{3a_3A_2^2A_1}{4}\cos[(2\omega_2-\omega_2)t]$$

(2.20)

N-th order intermodulation distortion is a useful metric in evaluating a system for its nonlinear behavior. The way to measure it is to inject a two equal tones close to each other

and set the amplitude such that the N-th order terms become visible in the spectrum. Then one can calculate the input referred intercept point at that given input signal with:

$$IIP_{n}[dBm] = P_{IN}[dBm] + \frac{P_{IN}[dBm] - P_{IMD_{n}}[dBm]}{n-1}$$

(2.21)

Second and third order intercept point are the most importanct for wireless receivers.

#### **Cross Modulation Distortion**

Cross modulation is a nonlinear phenomenon in which amplitude modulation of one signal would transfer onto another signal due to odd-order nonlinearities.

$$x(t) = A_S \cos(\omega_S t) + A_B [1 + m(t)] \cos(\omega_B t)$$

(2.22)

$$y(t) = (a_1 + \frac{3}{4}a_3A_L^2[1 + 2m(t) + m^2(t)])A_S\cos(\omega_S t)$$

(2.23)

The above equation shows that a distorted version of the AM modulation of the blocker signal has been transferred to the desired signal. Cross modulation is a very important metric in transceivers where both the transmitter and the receiver operate concurrently (full duplex system).

#### **Dynamic Range**

Dynamic range is the input signal level range the receiver can process with a specific quality. It's defined as the difference in power level between the 1dB compression point and the system noise floor.

$$DR[dB] = CP_{1dB,IN}[dBm] - MDS[dBm]$$

(2.24)

= CP<sub>1dB,IN</sub>[dBm] + 174dBm - 10log(BW) - NF[dB]

## Chapter 3

# Trends and Challenges in Wireless Receivers

### 3.1 Multi-Mode Operation: An inevitable Trend

#### System Point of View

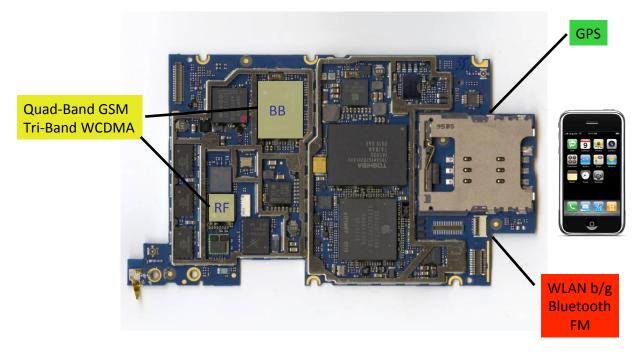

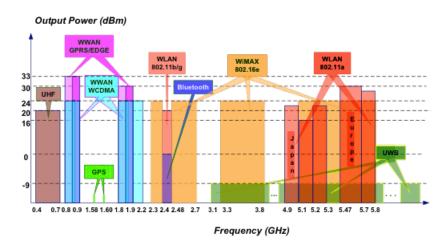

In order to keep up with the market's need, the wireless service industries have started integrating more and more radios on one platform [58]. A state-of-the-art is shown in Figure 3.1. Evidently with increasing the number of standards and consequently front-end modules, this approach becomes bulky, costly and gradually impossible. [41, 34, 84] are a few examples of current designs in multi-standard radios. Figure 3.3 clearly shows the current trend which can be called evolutionary progress of wireless front-end design. It needs to be revisited and a so-called quantum leap is needed to realize a radio that can work from couple of hundred megahertz to a few gigahertz. For example, consider a radio that is supposed to work with the standards in Figure 3.2. Thus from system point of view, having a front-end which can support multiple modes of operation is in tremendous demand, a system which can be reconfigured to transmit and receive different waveform at different frequencies.

#### **CMOS** Point of View

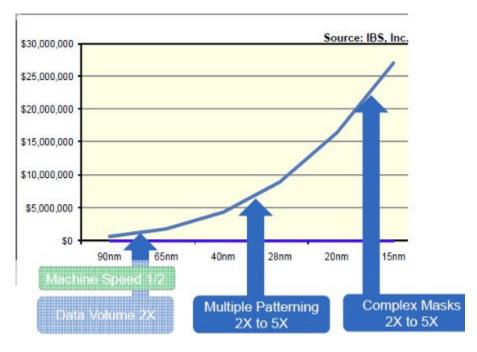

In parallel, progress in the CMOS technology has gone a far way in the last decades. Transistors are getting smaller and faster and hence the computation power and the frequency of operation have gone-up considerably, allowing engineers to communicate and process data at an astonishing pace. However, how does that benefit (if at all) radio designers? One thing which should be considered is the drastic increase in the mask cost, Figure 3.4.

Figure 3.4 shows having low-power, small-footprint computing modules comes at the enormous increase in the cost of mask and fabrication facilities which can be considered non-recurring engineering (NRE) cost, [58]. At the same time, the issues which were not

Figure 3.1: State of the art mobile handset. Source: isuppli

Figure 3.2: Frequency and power allocation for different standards

critical in the previous nodes get exacerbated with scaling, e.g. reliability and variability. This consumes more time of designers to get a robust design.

At the same time, cost per transistor is going down for logic, but for analog and RF cost per area is going up since passives don't scale with technology. Having in mind the cost of chip area and designer's time, the inevitable direction is to take advantage of the computation power available on the silicon. This concept has been around for a while under

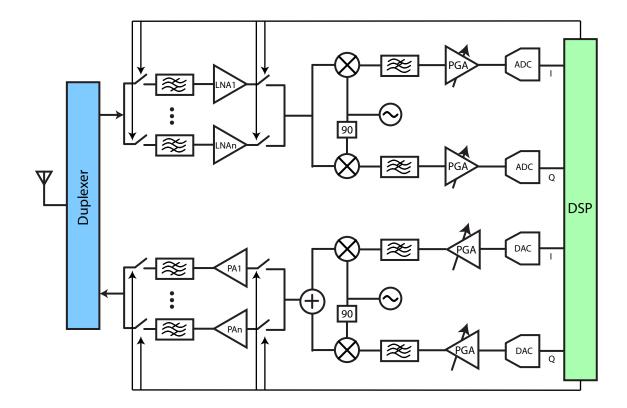

Figure 3.3: Typical multi-Standard transceiver architecture

the general category of software defined radios (SDRs) [53, 63, 12]. The general idea is to have an ADC in front of the antenna to convert the data into digital format and perform all the filtering and processing in the digital domain, or in the other way, change the mode of the module with software. Yet, there are extremely challenging issues to solve in the RF circuits before getting there [67, 58, 64, 66, 65].

#### Software Defined Radios

As it was discussed in the previous section, the natural way of thinking about the future of the wireless architectures is to have a flexible hardware with the capability of being reconfigured based on the required scenario. How does reconfigurability benefit the wireless industry?

Other than the form factor discussed above, cumbersome design iterations for achieving required performance would be diminished. To emphasize the importance of this phase, one should consider the vast amount of time designers should spend to tweak their modules to meet the required performance over the process corners. This task keeps getting harder and harder as the technology shrinks due to more complicated devices and more variabilities.

Hence the motivation for having the same infrastructure which can be re-tuned is rather

Figure 3.4: Mask cost versus process

high for service providers that are facing monthly updates on the standards. This is not the first time the electronics industry is going through this phase. As the quest for computation was rising, dedicated logic gates seemed an implausible approach and the trend tilted toward arrays of programmable gates (FPGA) so each customer can program the logics for the specific applications. Of course the performance would be lower than the dedicated designed logic, but after a certain threshold, expandability is by far the mot important issue to be addressed.

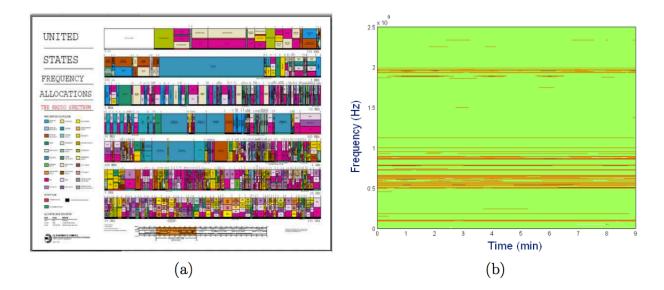

The benefits of incorporating such front-ends does not stop there. The other crisis the limitation of spectrum. The figure below shows the current allocation of the spectrum, showing that there is barely any room for new bands. There are two solutions for opening the new bands. One is to release spectrum, e.g. President Obama signed an order in 2010 to release 500MHz more spectrum. However, the allocated spectrum is not under constant use. Figure 3.5 shows the spectrum usage as a function of time.

Clearly if one could have the option of detecting the unused portion of the frequency spectrum and hopping to that slot, that would free a vast domain of spectrum for the users. The very idea of SDR can embed this functionality.

The question to be answered is considering all the benefits, why SDRs have not paved their way to the market yet [21]?

There are a few reasons ranging from management to technical levels. Among the technical levels, perhaps the most challenging part is the filtering requirements. This issue is even worse for modules implemented in the newer technologies.

Figure 3.5: CC spectrum allocation and the measured usage at the Berkeley Wireless Research Center. The measurements were performed in the 0-2.5GHz frequencies over a period of 10 minutes, [52]

Removing the filter will let the signals from the entire spectrum enter the system. Having in mind these systems are designed for typically retrieving the very weak desired signal, there are a few fundamental issues that potentially can hinder the above-mentioned functionality.

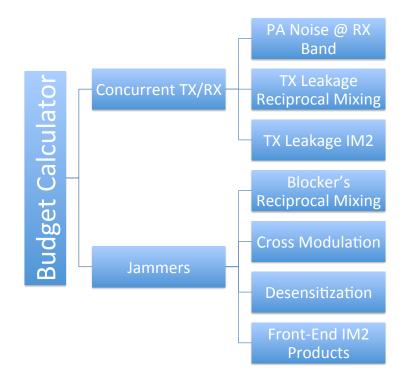

Looking at Figure 3.6, one can summarize the issues due to receiving strong jammers at the input of this time-varying system:

- A very strong jammer can saturate the receiver and prevent it from processing further signal in the spectrum. In the extreme case one can imagine a jammer that rails-out the receiver blocks. Also this issue exacerbates as the interferer signal gets closer to the channel since the gain of the chain is maximized for that particular band. The more typical scenario is the increase in the minimum detectable signal due to lower gain if the system.

- Reciprocal mixing is the other problem which is quite fundamental. When a jammer enters the receiver, even if the modules are designed to tolerate that power level, the frequency shifting action can still impose serious limitations on the blocker handling. Since with today's technology still the received signal should be down-converted to be be digitized with reasonable power consumption, there should be a oscillator to perform the task. The desired characteristics of that module is to generate a single tone in the frequency spectrum. However, the non-ideality of the block which is characterized by phase noise will cause other parts of the spectrum to be down-converted on top of the

Figure 3.6: Budget calculator for wireless receivers

desired signal. There are two regions which is quite sensitive. close to the desired signal and the regions around harmonics of the oscillation frequency. The latter is not a big concern once the carrier frequency is in the GHz range. Since the third harmonics falls couple of GHz away from the desired band and it will get attenuated by the passive filtering.

• Other than the saturation that can happen for any system, the receiver is a time-variant system which means the output signal frequency can be a linear function of the input frequencies. Now if the arrangement of blockers are such that the linear function of the jammer frequencies fall on top of the desired signal, the signal to noise ratio (SNR) would be degraded. The difference between these scenarios and the above mentioned one is that for the latter to be effective, the power level of the blockers should not necessarily be high to impact the performance whereas for the former, since there is no information at that specific frequency, the power level becomes important in the picture.

### 3.2 Tackling the Problem; ON Chip or OFF Chip?

As mentioned in the previous section, for realizing software-defined-radio, perhaps the most cumbersome barrier is the existence of blockers. For example, covering the frequency band

Figure 3.7: SAW Filters

of operation up to 6GHz is not a challenging task with today's technology. The fundamental question to be answered is what are the options for dealing with this challenge?

The answer varies based on the required form factor, cost, etc. Generally the solutions can be categorized into the on-chip vs off-chip components. One school of thought, which is quite dominant over the past decade, is that everything should eventually be on CMOS.

On the parallel path, there has been a huge progress in the field of integration of heterogeneous systems. The advantage of using such devices is the unprecedented quality factor which can never be achieved in the pure CMOS technology.

### OFF CHIP SOLUTION

- Surface Acoustic Wave (SAW): SAW devices are used as filters, resonators and oscillators and appear both in the RF and IF (intermediate frequency) stages of present cellular handset designs. Their size is about few  $mm^2$  though which is a fundamental bottleneck for having too many of them on one platform for having multiple band of operation.

- Bulk Acoustic Wave (BAW): BAW filters are electromechanical devices which operate at frequencies from around 1 to around 15 GHz. BAW filters are smaller than microwave ceramic filters and have a lower height profile. They have better power handling capability than SAW filters and achieve steeper roll off characteristics. A typical BAW duplexer takes up a footprint of about 5mm by 5mm which again poses the same issue as SAW counterparts introduce.

- MEMS (capacitive transducer) are also being suggested as potential replacements for off-chip filters. The idea of using micro electro-mechanical resonators has been the sub-

ject of academic discussion and academic/industrial research for almost 40 years. The problem with realizing a practical resonator in a MEMS device is the large frequency coefficient of silicon, aging, material fatigue and contamination. A single atomic layer of contaminant will shift the resonant frequency of the device. Also the other main issue with these resonators which seem to be fundamental, is the power handle-ability of these resonators. If one wants to increase the frequency of operation, the geometry of these devices should be scaled down. That would reduce the power handling as it will be explained below. The fundamental mechanism of operation of these devices is having a time-varying capacitor and extracting the current out of that.

$$i_{out} = \frac{d}{dt}(CV) = C\frac{dV}{dt} + V_{DC}\frac{dC}{dt}$$

(3.1)

Where the second term in Eq. 3.1 is the current picked-up by electrodes. The capacitor in the MEMS structures is time-varying based on the input voltage.  $C \propto \epsilon \frac{A}{d}$ . If the dimensions of these devices scale down, the gap between the electrodes would get smaller (d) and as a result, the high power signals can cause the mechanical system to enter the non-linear regime and in the extreme case, the resonator plates can collide. This issue is quite serious since one is using these filters to knock-out the high power jammers that the electronic systems can not tolerate. But at the same time these devices seem to work great for low-power interferences which are not a bottleneck and yet they are having a hard-time processing the strong jammers.

#### ON CHIP SOLUTION

The fundamental question to be addressed is if the holy grail of the wireless systems is being flexible multi-standard, what is the extent that one can benefit from scaled CMOS? How does that change with scaling?

What mechanical filters do is remove the blockers right after the antennas. Then the remaining blocks are responsible for processing the desired signals and in-band blockers which have profiles carefully engineered according to the standards. Consequently from the system point of view, it's manageable to allocate the design metrics for different building blocks for meeting the required dynamic range. That is the minimum detectable signal which sets the gain and noise figure, and also being able to tolerate the maximum power level entering the system, which is one of the dominant factors in the power consumption.

The most desired solution is to put the electronic block designed to perform the filtering function in front of the antenna. Depending on the type of the filter, in series or shunt with the front-end. The approach has been pursued [47], however, there are two critical issues which should be taken under careful considerations:

• Noise: As explained by the cascaded noise figure equation, the reason designers traditionally put the low-noise-amplifier (LNA) blocks in the beginning is to suppress the

Figure 3.8: Filter function for blocker removal

noises added by the consequent blocks which are in charge of frequency translation, further filtering and amplification and finally digitizing. The LNA plays a vital role in retrieving the minimum detectable signals. Now by adding an electronic block BE-FORE the LNA, one might get the desired filtering characteristics, but the amount of noise that would be pumped into the receiver is usually unacceptable. Why this is not an issue for mechanical filters? Well, to some extent it is. One can model these filters with equivalent electrical model of resistor, capacitive and inductor. The important point is they can demonstrate high quality factors not achievable with electronic components. However, since L and C do not have noise, the only noise source is the resistive part and actually they do hit the performance by a few dB. However, one needs not worry about a lot of different noise mechanism in CMOS like channel noise, reciprocal mixing due to phase noise and the harmonics of the oscillators etc.

• Linearity: Probably the harder problem to tackle, is designing electronic blocks that are functional for high power signals. In the designing phase, one would carefully bias the transistors in the right regime and carefully connect devices together to get the required performance. If the block is supposed to process a high power blocker, the different nodes in the block start to fluctuate and consequently transistors would come out of their desired operating points and as a result, the performance would deviate from the designed phase. On the other hand, scaling the CMOS technology is reducing the dynamic range available to designers as the power supply is shrinking at the same time. This makes designing such blocks much harder in the advanced nodes.

Maybe the other way to look at this issue is to ask when can we deal with blockers? Or

the other way to put it, when it's not too late?

#### Filtering before the LNA

The two problems to tackle is how to design a block which can do the filtering without increasing the noise-floor significantly. At the same time the block should be able to manage to keep the performance while processing large signals.

#### Filtering after the LNA

As explained above, the fundamental issue is when the blockers are entering the carefully designed LNA, the noise floor and the gain would drop and rise respectively and hence the noise floor of the system would increase significantly causing the loss of dynamic range. There are extensive techniques [86, 8, 15, 6, 17, 14, 85, 69, 44, 29, 25, 39, 42, 7, 45, 18] which can be utilized to squeeze as much of linearity as possible from the LNAs, however, the techniques are process-temperature sensitive and at the same time they are not suitable for high power blockers.

#### Filtering after the mixer and before digitization

At this stage, other than the issues mentioned above, another fundamentally limiting mechanism would happen. Suppose the mixer which is the block in charge of the frequency translation is linear enough so it would not introduce additional non-idealities when the input signal is high power. It's a reasonable assumption if one adopts a passive configuration. However, there are three terminals for the mixer and the bottleneck is the third port which is fed by the oscillator. The two dominant issues regarding this port while the block is processing jammers:

- 1. The blockers that fall on top of the odd harmonics of the reference clock. Since the mixing action basically is forcing the signal to toggle between path A and B, mathematically it's a pulse train. Hence by looking at the Fourier transform of the pulse train, one can see that there would be components at the odd harmonics of the reference clock and if there are jammers at those frequencies, they would be down-converted and fall on top of the desired signal. There are different techniques, [70, 13, 79, 16, 61], to reject the harmonic down-conversion and they're quite effective. Also this is less of an issue if the operation is at GHz regime since the harmonics are couple of GHz away and passive attenuations alleviate the issue.

- 2. The close-in blockers prove to be much more difficult to handle when it comes to the non-ideality of the local oscillator. Phase noise would cause the spreading of the tone of the reference clock and hence the energy in the near frequencies is considerable. If there is a signal in the near-by frequencies, they can be downconverted on top of the desired signal. This phenomenon is called reciprocal mixing [67] and it's a critical factor in system level planing for handling the blockers.

Since even if one designs a perfect LNA that can handle ANY signal level, this phenomenon would bury the desired signal under the high power jammers. The issue gets exacerbated by acknowledging the fact that based on Leeson's equation [43], the phase noise is fundamentally limited to the quality of passives. That means if one wants to avoid using heterogeneous integration, the reciprocal mixing is a fundamental limitations on the maximum power in close-in signals that wireless receivers can handle.

# Chapter 4

# Review of State-of-the-Art Wireless Receivers

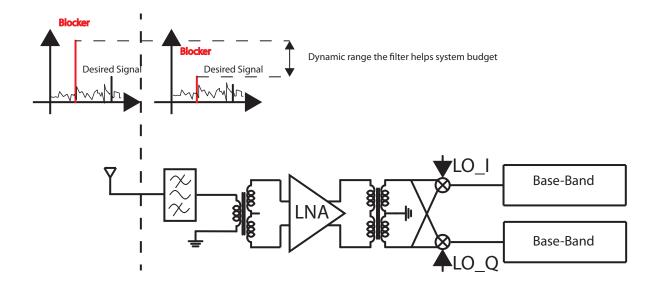

For the reasons mentioned in the previous chapter, current state-of-the-art solutions incorporate several external filters and duplexers to alleviate the noise and linearity issues imposed by signals and noise outside the band of interest. Figure 4.1 shows an example of quadband GSM/EDGE and tri-band WCDMA which is using 10 SAW filters, 3 duplexers and several matching network components [23]. Other than the obvious cost and size implications, the front-end partitioning by these components opposes the idea of flexibility which is the ultimate goal. Hence in this chapter we will review and analyze the current proposed solutions for removing the filters and dealing with blockers with on-chip approaches. It's worth mentioning the emphasis is on the techniques that achieve filtering in the RF domain since doing so in base-band means RF blocks should still tolerate the jammers and doesn't pave the way for SDR realm. Another thing to note is that these approaches should all have the assumption of not having the copy of the jammers. For example in case of concurrent operation of TX/RX, [9, 38], the copy of the blocker is available and can be deployed in the cancellation schemes.

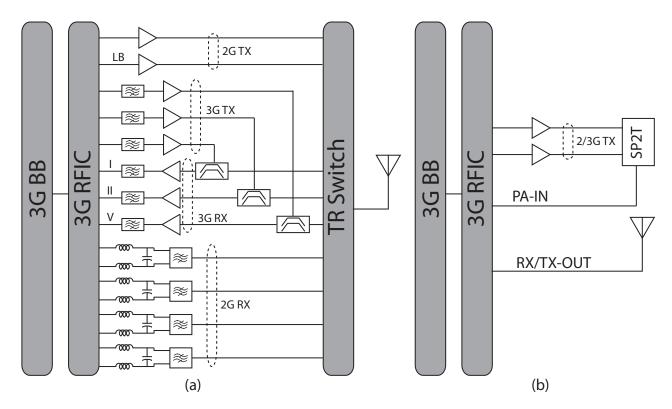

# 4.1 Spatial Filtering

The original use of multiple antenna in wireless systems was to enable sending independent data on each channel and increasing the throughput of the physical media. In receivers multiple antennas are also being used to counteract the multi-path issues. However, the same architectures can be used to do the spatial filtering, exploiting the fact that the desired signal and the interfering signal come from different angles. Then from the Figure 4.2 one can derive the phase difference between antennas 1 and 2 as:

$$2\pi \frac{d}{\lambda} \sin(\theta) \tag{4.1}$$

Figure 4.1: Current (a) and future (b) architectures of 3G receivers [23]

Since the desired signal comes with the angle of  $\theta_1$  and the interference comes with the angle of  $\theta_2$ , [57] shows that by using channel estimation techniques one can get the direction of the desired signal and cancel N-1 jammers with N antenna elements.

There are two issues that make this approach quite unattractive for cellular domain. First and by far the more important one is the use of multiple antenna is prohibited for SDRs since the increase in form factor contradicts the purpose of removing the SAW filters. Secondly, it is not a wide-band solution since the cancellation is a function of  $\frac{d}{\lambda}$  and  $\lambda$  is quite large in low-frequency regimes. The other subtle problem arises from the phase-shifting requirements in the system which can be done either in the RF or base-band. If it's done in the baseband, that would mean the RF blocks should process the jammers and there is no blocker power alleviation for them, and wide-band phase shifting in RF is not an easy solution [75].

### 4.2 Translational Loop Filters

The idea of translational loop filters is to replicate the blocker at one path and then subtract it from the main branch so from then on; the system front-end and dependencies on the cancellation mechanism can be categorized in two subcategories.

Figure 4.2: System diagram of incorporating multiple antennas

#### **Feedforward Cancellation**

One solution is to divide the incoming signal from the antenna into two branches and subtract the blocker at the output of the LNA. This approach has been pursued in [30, 10, 22, 72]. Basic idea is to copy the incoming signals, remove the desired signal and subtract the remaining at the LNA output. The first question one should ask is why go through all the trouble? The answer comes back to the limitation of passive quality factors. The Q is not good enough to be able to remove the blockers at front-end. So how does this technique bypass this limitations? First the incoming signals will be down-converted, pass through a high Q base-band filter to remove the desired signal and then it will be subtracted at the LNA output. Since the filtering is done at the base-band, the effective quality factor is much better. But that doesn't come for free.

The availability of quadrature LO signal in the receiver makes it easy to implement a notch in the single side manner.

However, this approach suffers from number of issues:

Matching Requirement There are two paths, the main and the auxiliary, and since the cancellation mechanism is feedforward, there is no procedure for fixing the residual errors and hence the cancellation is a huge function of matching between the path. Both a) gain and b) phase prove to be very important factor in the amount of attenuation

Figure 4.3: Feedforward scheme for blocker removal in receivers

one would get.

Noise Performance The other fundamental issue that is always of concern is the noise added to the system. Every new function added to the system degrades the noise performance, specially if the block is placed in the first stage. However, two factors helps designer for such blocks. First is the fact that these blocks can be turned-off if there is no blocker which can be monitored, and the second is the higher NF constraint once there is a blocker entering the system. For example in 3GPP, the noise figure limit when there is blocker is 15 dB [49].

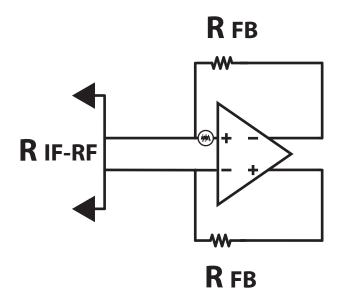

#### Feedback Notch Filtering

This approach has been pursued in [72, 80, 81] and the very feature that makes it very interesting is that there is no need to control the gain and phase of the loop as long as the feedback is stable. However, this approach shares the other issues the feedforward solution has and on top of those, it suffers from stability, a problem that all the feedback systems have, but one which is harder to solve in the RF regime.

### **Positive Feedback Translational Loop**

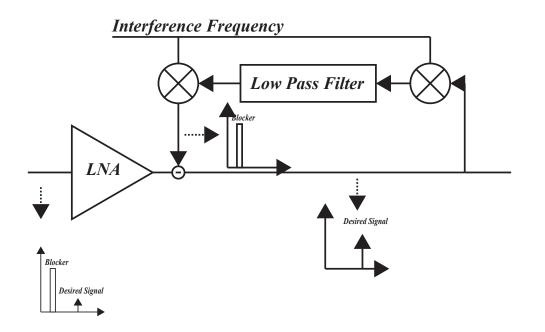

This solution has been pursued in [37, 36] and has some interesting characteristics. The idea is to down-convert the blocker and the desired signal, filter out the desired signal and subtract the blocker at the input of the LNA. The loop is positive feedback to enhance the

Figure 4.4: Feedback scheme for blocker removal in receivers

sharpness of the filter. Cancellations at the input of the LNA which saves the LNA from high dynamic.

However, there is a time-delay in which the LNA should process the signal in order to get the loop up and running. Doing so the impedance seen from the antenna would be:

$$Z_{IN} = \frac{Z_{LNA}}{1 - \frac{Z_{LNA} * G_{BPfilter}}{K}}$$

(4.2)

in which the K is set such that  $\frac{Z_{LNA}}{1-\frac{Z_{LNA}}{K}} = Z_{Antenna}$  so the in-band signal is matched and the out-of-band is going to be attenuated by:

$$AT(dB) = -20\log\left(\frac{Z_{IN}}{Z_{ANT} + Z_{IN}} * \frac{Z_{LNA} + Z_{ANT}}{Z_{LNA}}\right)$$

(4.3)

However, the stability of the system is based upon the value of K and there should be a good control over the value of the K. Other factor one should consider is that the amount of attenuation is proportional to the input impedance of the LNA and the lower it gets, the more attenuation is achieved. However, extremely low input impedance would translate to noisy power-hungry block which is not a good candidate for cellular applications.

Figure 4.5: Positive feedback translational loop [36]

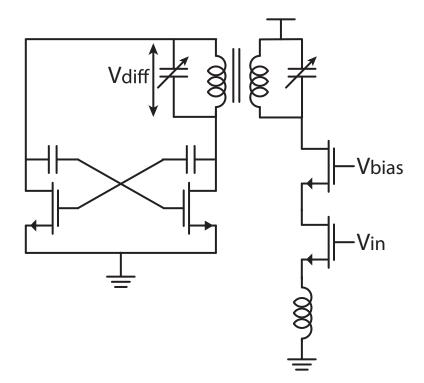

## 4.3 Q-Enhancement Techniques

Q-enhancement filters are basically using the fact that one can see negative resistance looking at the cross-coupled pair with positive feedback loop. Since Q is inversely proportional to the resistive losses, the negative impedance increases the Q and hence the selectivity [73].

Looking at Figure 4.6, there are a few factors that should be pointed out. First is the fact that the positive feedback scenario makes it sensitive to oscillation and there should be a calibration circuitry to monitor that section. Perhaps the more important fact is the nonlinear behavior of this approach. The performance is a function of exact magnitude of the impedance of the cross-coupled pair and due to large-signal behavior of the transistor, that's a function of the input power. On top of this, one should consider the noisy behavior of this approach which made the designers put the block after the first stage of the LNA. Overall, this might be a good architecture when dealing with low power signals in the GPS and assuming there is a SAW filter in the front-end, but doesn't prove to be attractive for

Figure 4.6: Q-Enhancement architecture

cellular domain.

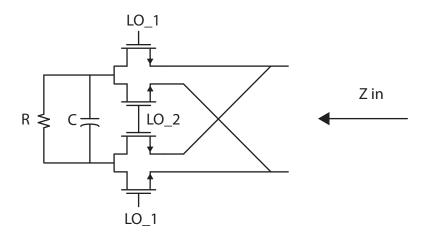

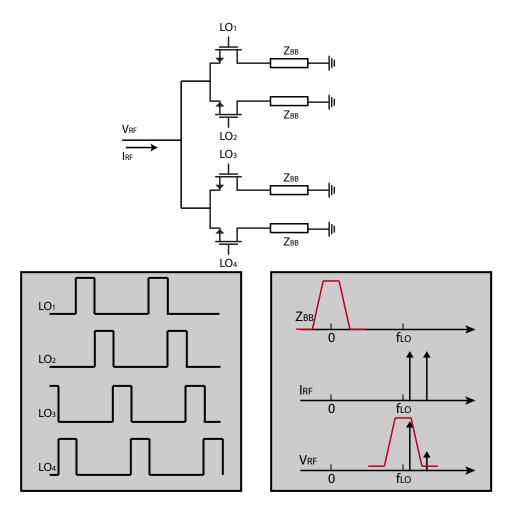

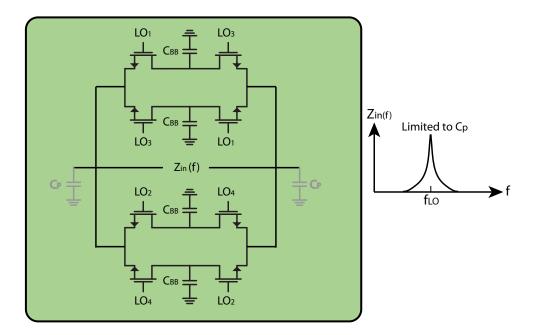

## 4.4 Mixer-First Approach

This solution uses an intuitive and contradictory approach. If the LNA starts entering nonlinear regime with strong jammers, and amplification of the jammers would cause the following blocks to saturate as well, then why not get rid of the LNA and start with the mixer?