# An Open Architecture for Improving VLSI Circuit Performance

By

#### Fred W. Obermeier

B.S. (University of Cincinnati) 1983M.S. (University of California) 1985

#### **DISSERTATION**

Submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in

#### **COMPUTER SCIENCE**

in the

#### **GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA at BERKELEY

| Approved: Randy H | Kat    | 4/19/89 |

|-------------------|--------|---------|

| Reliense          | who    | 4/20/89 |

| Andrew W.         | Shogan | 4/25/89 |

\*\*\*\*\*\*\*\*\*\*

# An Open Architecture for Improving VLSI Circuit Performance

Copyright © 1989

by

Fred W. Obermeier

All rights reserved.

(Reduced version of the Ph.D. thesis.)

| • |   |  |  |

|---|---|--|--|

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   | · |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

| ] |   |  |  |

|   |   |  |  |

# An Open Architecture for Improving VLSI Circuit Performance

Fred W. Obermeier

#### **ABSTRACT**

Electrical performance and area improvement are important parts of the overall integrated circuit design task. However, few design tools allow easy exploration of the design space (area, delay, and power) or offer designers different performance alternatives. Given designer specified constraints on area, delay, and power, EPOXY will size a circuit's transistors and will attempt small circuit changes to help meet the constraints. The system provides an open flexible framework for developing and evaluating the effects of different area and electrical models, optimization algorithms, and circuit modifications.

EPOXY takes a physical and electrical description of the circuit and produces a series of symbolic equations that model its performance. This results in circuit performance evaluation 5 times faster than Crystal and 56 times faster when these equations are subsequently compiled. EPOXY employs a virtual-grid area model since the sum of transistor area is a better measure of dynamic power than cell area. Optimization of a CMOS eight-stage inverter chain illustrates this difference; a typical minimum power implementation is 32% larger than the one for minimum area.

Next EPOXY attempts to find a parameter assignment for the input variables of these equations, transistor widths, to meet the constraints while minimizing the user defined objective function. Previous transistor sizing systems are limited to fixed electrical models and only consider time and power tradeoffs. After evaluating two non-linear optimization techniques, the TILOS-style heuristic and augmented Lagrangian algorithm, a combination of the two was found to produce quality results rapidly.

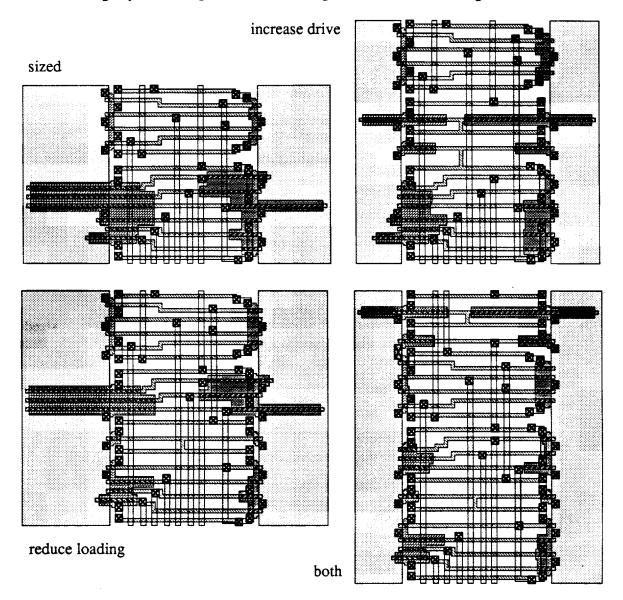

If the performance constraints cannot be met by transistor sizing, EPOXY considers inserting buffers stages, rearranging transistors within a pull-down or pull-up tree, and splitting large transistors so that cell height and width can be traded off. This level handles the discrete decisions of proposing circuit alternatives while the two lower levels determine the best possible implementation for this alternative. From an implementation viewpoint, EPOXY's underlying equation abstraction of circuit performance automatically provides critical path information and allows rapid modification of the circuit structure. A typical speed improvement of 23% for several CMOS circuits was achieved over transistor sizing alone while satisfying difficult height (pitch) constraints.

## Acknowledgements

First, I like to express my deep appreciation for Randy Katz for his patience, support, and encouragement. He often provided need inspiration during those difficult times. I'd also like to thank my research committee; Randy Katz, Richard Newton, and Andrew Shogan, for suggesting improvements to this dissertation.

My early association with the members of the Magic team; John Ousterhout, Michael Arnold, Gordon Hamachi, Robert Mayo, Walter Scott, and George Taylor, provided valuable exposure to research in computer aided design (CAD) for integrated circuits. Their work showed that a powerful and useful design system could be constructed cleanly from good basic ideas.

I particularly value the stimulating conversations with my fellow officemates; Gaetano Borriello, David Wood, David Gedye, and Ellis Chang. Despite our cramped quarters, the close interaction has enriched my graduate experience by exposure to a broader scope of research. I like to thank Bill Lin and Gino Cheng for their comments and suggestions. In addition, I would also like to express my deep appreciation to Thuan Nguyen for his personal support and encouragement.

David Marple provided a copy of his transistor sizing program, COP. His work served as a model for implementing the augmented Lagrangian optimization algorithm.

Throughout my college experience I have had the pleasure of working with many talented people. My assignment at the IBM T.J. Watson Research Center introduced me to a wonderful research setting. In particular, Ed Adams and Rolf-Dieter Fiebrich encouraged my work towards a Ph.D. degree. As an undergraduate, Thomas Ridgway provided an enjoyable and rewarding setting to develop hardware and software PC systems. His projects have stimulated my creative efforts and have provided invaluable knowledge of microprocessor-based systems and assembly language development.

This research was supported in part by an American Electronics Association Faculty Development Fellowship and a NSF grant MIP-83-52227. My first year at Berkeley was funded by a California, Microelectronics Fellowship (MICRO).

# **Table of Contents**

| 1.   | Introduction                                                  |

|------|---------------------------------------------------------------|

| 1.1. |                                                               |

| 1.2. | Unique Aspects of EPOXY                                       |

| 1.3. | Goals of this Research                                        |

| 1.4. | Organization of this Dissertation                             |

| 2.   | Modeling Circuit Performance                                  |

| 2.1. | Time                                                          |

| 2.2. | Power                                                         |

| 2.3. | Area                                                          |

| 2.4. | Noise Margins                                                 |

| 2.5. | Conclusions                                                   |

| 3.   | Optimization and Heuristic Techniques                         |

| 3.1. | Performance Envelope                                          |

| 3.2. | Step Size Algorithms                                          |

| 3.3. | Augmented Lagrangian Method                                   |

| 3.4. | Heuristic Improvement Techniques                              |

| 3.5. | TILOS Heuristic                                               |

| 3.6. | Comparison of Solution Quality and Running Times              |

| 3.7. | Conclusions                                                   |

| 4.   | Performance-Based Circuit Modifications                       |

| 4.1. | Split Large Transistors                                       |

| 4.2. | Insert Buffers                                                |

| 4.3. | Reorder Transistors                                           |

| 4.4. | Strategy for Applying Several Circuit Modification Techniques |

| 4.5. |                                                               |

| 4.6. | Conclusions                                                   |

| 5.   | System Architecture and Implementation                        |

| 5.1. | Implementation Strategy                                       |

| 5.2. | 1                                                             |

|      | Deriving the Performance Equations                            |

|              | Non-Linear Problem Formulation and the Jacobian Matrix  Handling Sequential Circuits          | 65<br>73 |

|--------------|-----------------------------------------------------------------------------------------------|----------|

| 5.6.<br>5.7. | Evaluating the Performance Equations  Space/Time Tradeoff  Implementing Circuit Modifications |          |

|              | Conclusions                                                                                   | 80       |

|              | Conclusions and Contributions  Future Research                                                |          |

| 7.           | References                                                                                    | 84       |

| 8.           | Appendix: Generating C Simulation Programs                                                    | 87       |

# List of Figures

| Figure | 1.1: Layouts and performance of two inverters.               | 2  |

|--------|--------------------------------------------------------------|----|

| Figure | 2.1: Critical path derivation of a CMOS static gate          | 1  |

|        | 2.2: Total cell area ≠ total transistor area. 1              | 4  |

| Figure | 2.3: Layout effects of free transistor width                 | 6  |

| Figure | 2.4: Free transistor widths for a CMOS adder                 | 7  |

| Figure | 2.5: Virtual grid model for a generic PLA.                   | 8  |

| Figure | 3.1: Typical performance envelope. 2                         | 3  |

| Figure | 3.2: Layouts for an eight stage inverter chain. 2            | 4  |

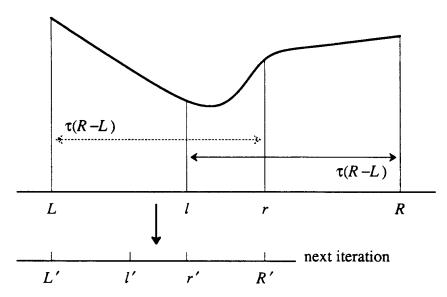

|        | 3.3: Example of the Golden section method                    | :6 |

| Figure | 3.4: Pseudo code for Golden section method                   | :6 |

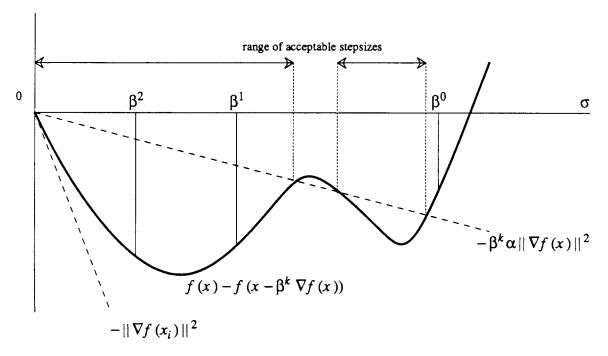

| Figure | 3.5: Example of the Armijo method                            | :7 |

| Figure | 3.6: Pseudo code for the Armijo method.                      | 8  |

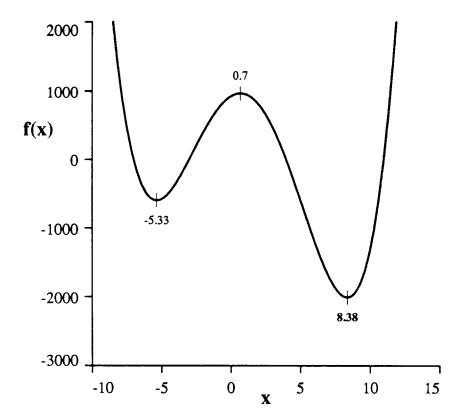

| Figure | 3.7: Example function for testing step size techniques       | 9  |

| Figure | 3.8: Pseudo code for a steepest descent algorithm            | C  |

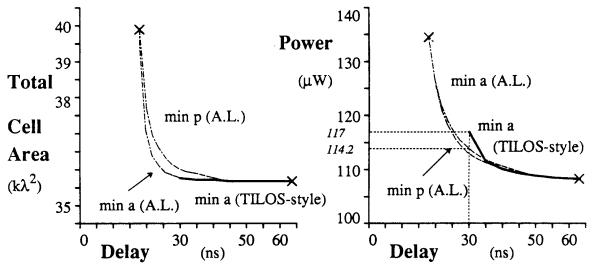

| Figure | 3.9: Comparison of TILOS and augmented Lagrangian methods    | 7  |

| Figure | 4.1: Example of splitting larger transistors. 4.1.           | 1  |

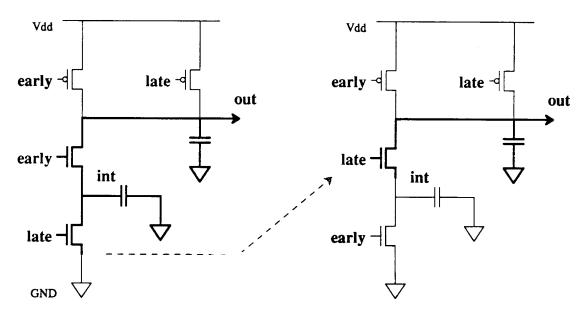

| Figure | 4.2: Example of buffer insertion strategies. 4               | 12 |

| Figure | 4.3: Layouts before and after transistor sizing. 4           | 13 |

| Figure | 4.4: Layouts for buffer insertion strategies.                | 4  |

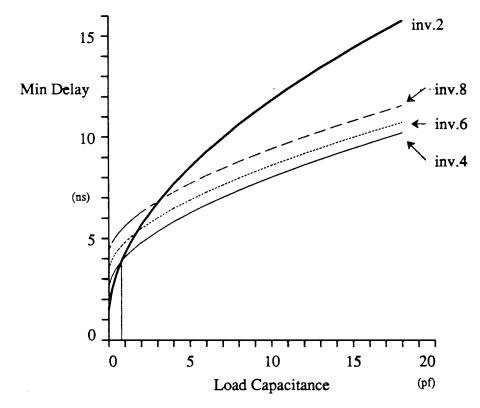

| Figure | 4.5: Graphs of the fastest inverter chains. 4                | 5  |

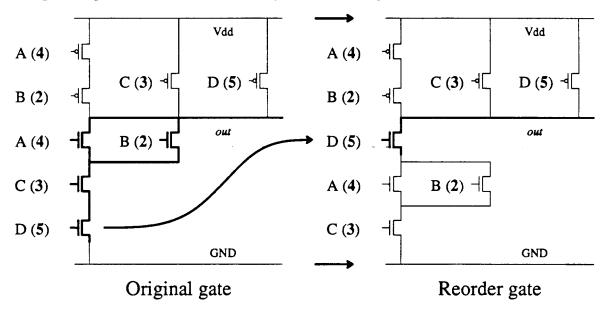

| Figure | 4.6: Reordering transistors for a NOR logic gate 4           | 16 |

| Figure | 4.7: Example of reordering transistors. 4                    | 17 |

| Figure | 4.8: Pseudo code to apply several heuristics                 | 8  |

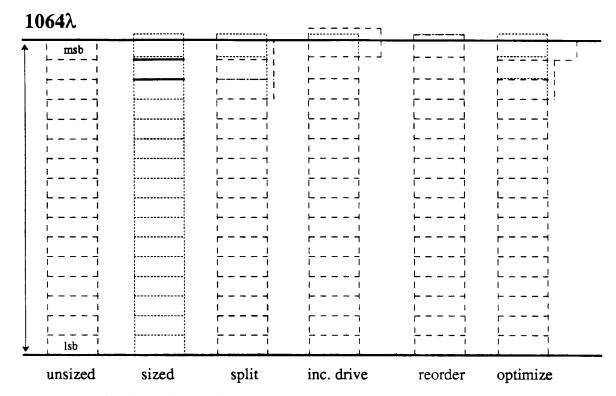

| Figure | 4.9: Outlines of the 16 stage adder cells                    | 1  |

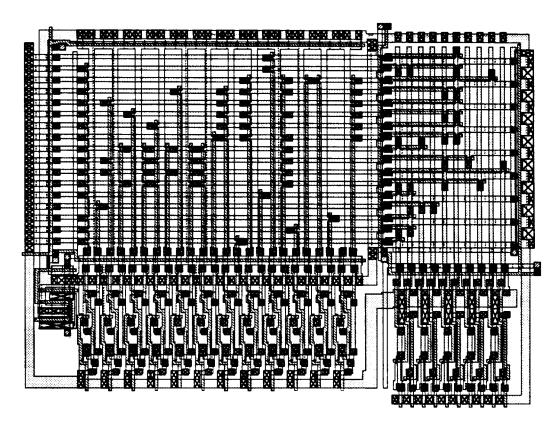

| Figure | 4.10: Layout for the CMOS PLA: pla.cpu1 5                    | 12 |

| Figure | 4.11: Layout for one JK flip-flop. 5                         | 13 |

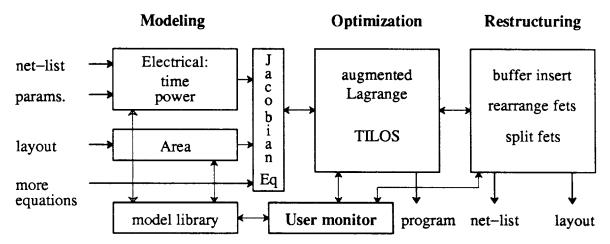

| Figure | 5.1: EPOXY system architecture. 5                            | 6  |

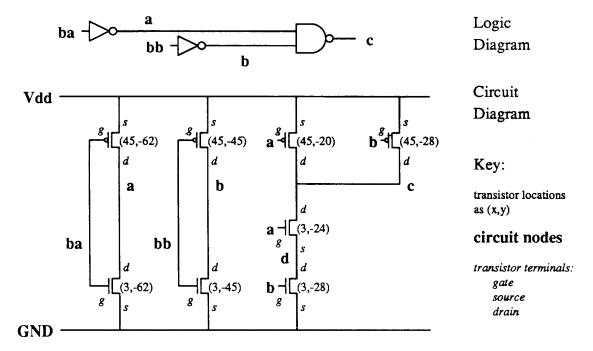

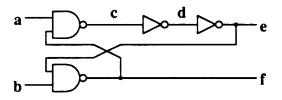

| _      | 5.2: Logic and circuit diagrams for the buffered NAND gate 5 | 8  |

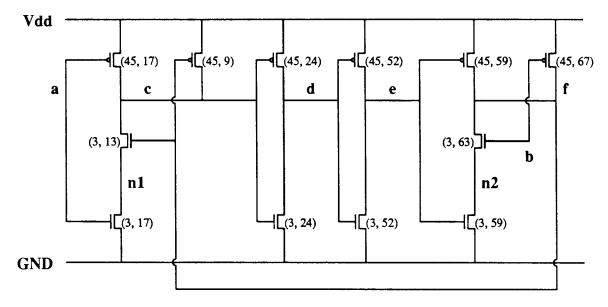

| Figure | 5.3: Layout for a standard-cell CMOS buffered NAND gate 5    | 9  |

| Figure | 5.4: Net-list file for the buffered CMOS NAND gate           | C  |

| Figure 5.5: Parameter  | file for the buffered CMOS NAND gate.           | 60 |

|------------------------|-------------------------------------------------|----|

| Figure 5.6: Additiona  | d equations for the buffered CMOS NAND gate     | 62 |

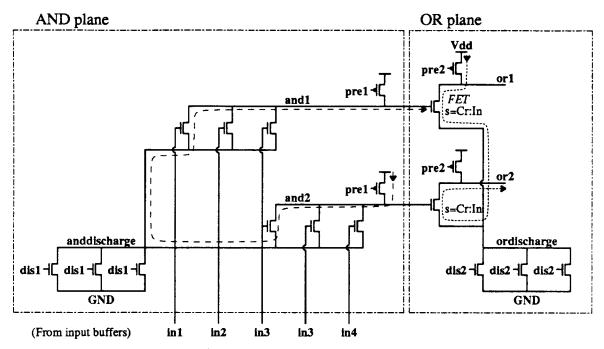

| Figure 5.7: False pre- | charge paths in a dynamic CMOS PLA              | 65 |

| Figure 5.8: NLP form   | nulation for the buffered CMOS NAND gate        | 71 |

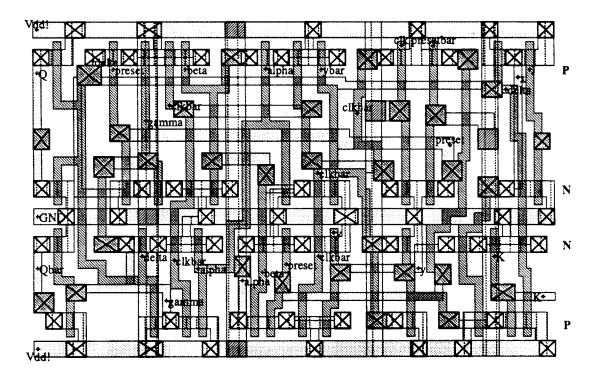

| Figure 5.9: Logic and  | d circuit diagrams for an RS-latch and a buffer | 74 |

| Figure 5.10: Critical  | delay paths through the RS-latch and buffer     | 75 |

| Figure 5.11: Equation  | as for the critical path diagrams.              | 76 |

# List of Tables

| Table | 1.1: | A comparison of VLSI performance improvement systems | 3  |

|-------|------|------------------------------------------------------|----|

| Table | 2.1: | Summary of Crystal time models.                      | 10 |

| Table | 3.1: | Comparison of an area and power optimization.        | 23 |

| Table | 3.2: | Golden section and Armijo step size routines.        | 31 |

| Table | 3.3: | Summary of heuristics used by several systems.       | 34 |

| Table | 3.4: | Results of several performance optimization problems | 36 |

| Table | 4.1: | Summary of circuit modification techniques.          | 39 |

| Table | 4.2: | Performance improvement for 16 stage ripple adder.   | 50 |

| Table | 4.3: | Performance improvement for a CMOS PLA               | 52 |

| Table | 4.4: | Performance improvement for a JK array.              | 53 |

| Table | 5.1: | Equation templates for the electrical models.        | 64 |

| Table | 5.2: | Input vector for the Jacobian matrix.                | 72 |

| Table | 5.3: | EPOXY Circuit Statistics.                            | 72 |

| Table | 5.4: | Equation evaluation techniques and modes in EPOXY    | 78 |

| Table | 5.5: | Storage requirements and execution time savings.     | 79 |

| Table | 8.1: | Intermediate variable formats.                       | 87 |

| Table | 8.2: | Format of the generated timing analyzer program      | 88 |

|       |      | Format of the C program for NLP routines.            | 91 |

The computer industry is undergoing a rapid evolution. Each successive generation of computers is faster and more powerful than the previous one. Many of these improvements can be directly traced to developments in the underlying integrated circuit (IC) technology. Therefore, a company's success directly depends on how effectively these innovations can be rapidly incorporated into new products.

VLSI designers play a crucial role in the development of new products. These designers are faced with the difficult task of producing layout that meets aggressive electrical performance and area requirements. The current trend in the design of VLSI integrated circuits is to start with a functional specification using a high-level description. Next, a designer selects an architecture of major functional blocks that satisfies the overall functional requirements and general design strategy. The implementation of each block is constrained by the performance requirements dictated by the functional partitioning. Once these requirements are refined to a sufficiently detailed level, the designer can select a suitable layout generator or library element.

Typical layout generators and standard-cell library elements contain fixed over-sized or minimum-sized transistors. Often these systems produce only a single design. This gives a designer little control over the electrical and area performance of the resulting implementation. Even when transistor sizes can be specified, it is difficult for a designer, without some assistance, to determine the appropriate sizes for the large number of transistors to achieve the best implementation. Therefore automated transistor sizing plays an important role in the overall design process.

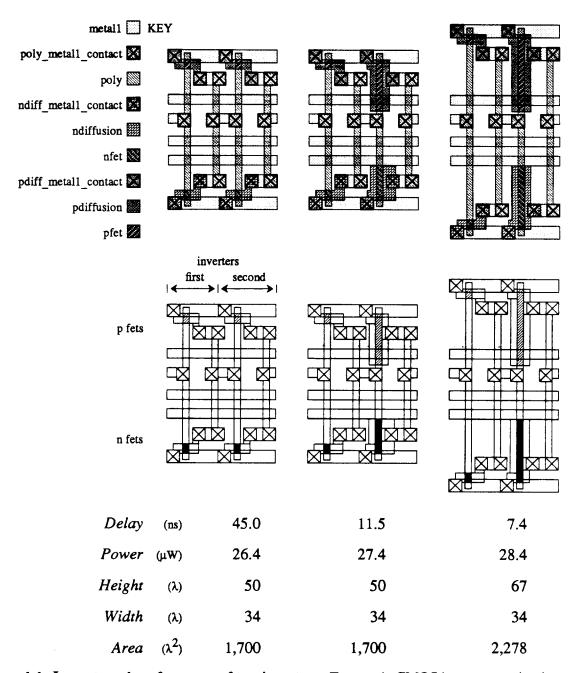

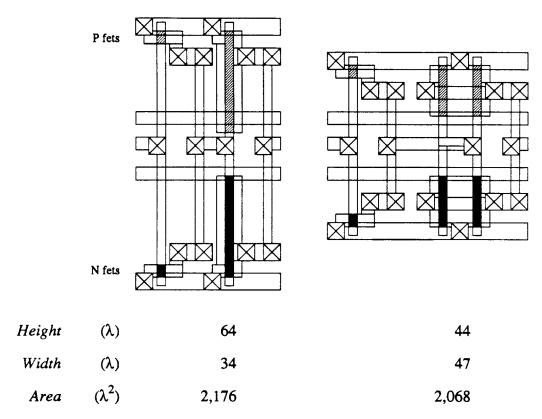

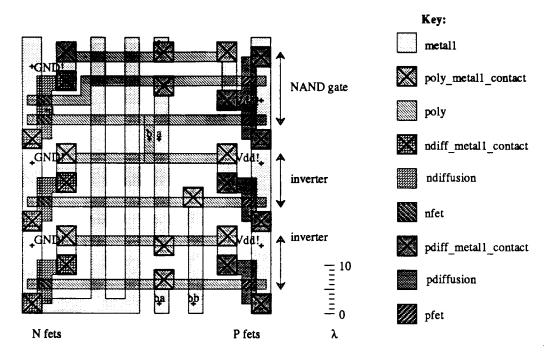

Figure 1.1 illustrates how the performance of a small example changes as a function of transistor widths. The layout implements two static CMOS inverters in a standard-cell organization. The upper layouts show all interconnect layers, while only the transistors are shaded in the lower layouts. Layouts on the left represent the design with all minimum sized transistors. The second inverter for the middle and right layouts employs wider transistors. As the transistors in the second inverter are widened, the delay is reduced at the expense of additional power. The trend continues until the fastest design is achieve. Thereafter, increases in the transistor widths will cause an undersirable increase in power and delay. The height and area changes only if the larger transistors cannot fit into the layout. This example does not adequately illustrate the increased complexity involved in determining the sizes for a large number of transistors when subject to constraints on performance.

Transistor sizing alone may not be sufficient for meeting the required performance goals for a defined functional block. Even though circuit changes at the logic level can have a significant impact on the quality of the circuit, most logic reorganization programs cannot consider the important detailed parasitics which can have a dramatic effect on the overall performance.

EPOXY, the design tool described in this dissertation, not only sizes transistors but also considers detailed circuit modifications for meeting the performance goals and size limitations. The system improves VLSI circuit performance by generating the equations that model circuit performance, formulating the transistor sizing

Figure 1.1. Layouts and performance of two inverters. Two static CMOS inverters are implemented by layout in a standard-cell organization. In standard cells, the p- and n-type transistors (fets.) are grouped into rows. The complete layouts are shown in the top portion of this figure. Each transistor type is shaded in the lower layouts. The layouts on the left employ transistors of minimum size. Increasing the transistor widths of the second inverter decreases the delay (increases the speed) at the expense of additional power and height.

problem as a non-linear program, and then modifying the circuit to improve the solution further. Therefore, EPOXY can complete the design process by modifying the layout resulting from logical reorganization.

### **VLSI Performance Improvement Systems**

| System  | Author    | Obj.            | Constr.                        | Method         | Model | Tech.       | Mode     | Comments                                               |

|---------|-----------|-----------------|--------------------------------|----------------|-------|-------------|----------|--------------------------------------------------------|

| _       | [Glas84]  | min AA          | m≤AA<br>T≤k & m≤A<br>T≤k & m≤A |                | LS RC | nMOS        | batch    | Single path.                                           |

| -       | [Lee84]   | min T<br>min AA | T≤k                            | opt.           | L RC  | CMOS        | batch    | (step 1)<br>k=minT+ΔT                                  |

| _       | [Mats86]  |                 | T≤k<br>m≤AA≤k                  | opt.           | Macro | nMOS        | batch    |                                                        |

| _       | [Shyu88a] | min AA          | T≤k                            | opt.           | D RC  | <b>CMOS</b> | b/i      |                                                        |

| AESOP   | [Hedl87]  |                 | m≤AA≤k<br>m≤AA≤k               | opt.           | L RC  | n/CMOS      | inter.   | Fixed paths (gate model)                               |

| ANDY    | [Trim83]  |                 | m≤AA≤k<br>T=k                  | heur.          | L RC  | nMOS        | b/i      |                                                        |

| APLSTAP | [Bray81]  | $\min f(n)$     | f(n)≤k                         | opt.           | ASTA  | P           | inter.   | Very general                                           |

| DELIGHT | [Nye88]   | min f(n)        | f(n)≤k                         | opt.           | SPICE |             | inter.   | Very general                                           |

| EO      | [Hed184]  |                 |                                |                |       |             |          | 1 path (PLAOPT)                                        |

| EPOXY   | [Ober88b] | min f(n)        | f(n)≤k                         | all†           | all†  | all†        | b/i      | Also [Ober88a]                                         |

| LTIME   | [Ciri87]  |                 | T≤k                            | opt.           | D RC  | MOS         | inter.   | Single path                                            |

| MOST    | [Pinc86]  | min AA          | T≤k                            | heur.          | L RC  | CMOS        | b/i      | A framework.                                           |

| OPT     | [Wolf78]  | min P           | T≤k                            | opt.           | L RC  | nMOS        | batch    | Place using T & P                                      |

| PLAOPT  | [Hedl85]  |                 | m≤AA≤k<br>T≤k                  | opt.           | L RC  | nMOS        | inter.   | PLA critical path oriented                             |

| PLATO   | [Marp86]  | min A           | T≤k                            | opt.           | LS RC | CMOS        | batch    | Dynamic PLA                                            |

| COP     | [Marp87]  | min T           | T≤k<br>P≤k                     | opt.           | LS RC | CMOS        | batch    | Static comb.                                           |

|         |           |                 | T≤k                            |                |       |             |          |                                                        |

| TILOS   | [Fish85]  | min AA          | m≤AA≤k<br>T≤k & m≤A<br>m≤AA≤k  | heur.<br>A.A≤k | D RC  | CMOS        | batch    | Extracts sequential and combinational transistor nets. |

| TV/IA   | [Joup83]  |                 | T≤k                            | heur.          | D RC  | nMOS        | inter.   |                                                        |

| XTRAS   | [Kao85]   | min AA          | T≤k                            | heur.          | LS RC | n/CMOS      | inter.   | T = max. all paths.                                    |

| Key     | A total   | design area     | T o                            | ielay          |       | L RC L      | umped    | RC model                                               |

| •       |           | transistor area | 1                              | any function   | · ·   |             | -        | Slope RC model                                         |

|         |           | design height   | 1 ' '                          | constants      |       |             | -        | ed RC model                                            |

|         |           | design width    | 1 ' '                          | optimization   | based | batch b     | atch mo  | ode opt.                                               |

|         | P pow     | er              |                                | neuristic      |       | inter. ir   | teractiv | e opt.                                                 |

Table 1.1. A comparison of VLSI performance improvement systems. The objective function and constraints for each program are given under (Obj.) and (Constr.) respectively. The type of technique used for design improvement is given under (Method). The model which determines response times (Model) and the technology supported (Tech.) are then listed. The last two columns give the supported operating modes and addition comments. († EPOXY supports a variety of methods, models and technologies.)

EPOXY's major innovation is its efficient flexible open system architecture for developing and evaluating performance models, non-linear optimization techniques and circuit changes. The system delivers these advantages by representing circuit performance by a set equations. Each of these issues (performance modeling, optimization and circuit changes) corresponds to a component in EPOXY.

#### 1.1. Comparison of Performance Improvement Systems

Since the relationship between transistor size (and layout dimensions) and delay is non-linear even for simple models, the transistor sizing problem can be formulated as a non-linear program (NLP). Even though a transistor sizing tool many not employ non-linear programming techniques, a transistor sizing program can be succinctly described by the non-linear program (an objective function and constraints) it solves.

The value of any performance improvement tool depends on how well the system helps a VLSI IC designer achieve the desired performance goals. However, these requirements vary radically depending on the intended application. Designers of high volume parts place chip area at a premium while requiring a sufficient speed and maximum power dissipation necessary for an application. Alternatively, advanced specialized parts often require high speed at the expense of additional area and operating power. Therefore, one metric of comparison of performance improvement systems is how flexible they are in specifying user constraints and an objective function, and assisting a user to attain these design requirements.

Table 1.1 summarizes several VLSI MOS performance improvement systems. The program name and reference for each system is given under the first two columns. The next two columns define the objective function and corresponding design constraints each system considers; a separate line is given for each type of optimization a system performs. The standard constraint, that transistor widths must be larger than some minimum width as defined by the technology, has been omitted from this table. The abbreviations for each of the design metrics is given in the lower portion of the table. The technique that a system uses to improve a circuit's performance can be classified as either optimization-based or heuristic. Optimization techniques rely on formal mathematical methods to assure converge to a minima while heuristic techniques encode designer experience in improving designs. Although heuristic techniques usually do not yield optimal results, they do improve designs rapidly. The electrical model for circuit response time and the technology supported by each system is listed in the two subsequent columns. column describes a user's interaction with each system as either batch or interactive. The final column provides terse comments which detail some unique aspects or limitations of each system.

Performance improvement systems can also be classified by the level of detail considered in determining the transistor sizes. The electrical model (Model in Table 1.1) can be applied at the transistor (e.g.: TILOS) or gate level (e.g.: AESOP). Gate level models typically reduce the input design space by associating a single factor with a logic gate. The transistor sizes are assigned based on the resultant logic gate factor. While gate level models reduce the input design space and the amount of computation, they often yield inferior results. The single gate factor cannot encompass significant differences in input arrival times and intermediate parasitic capacitance that dramatically effect the overall circuit performance. EPOXY is flexible enough to implement both transistor and gate level models.

#### 1.2. Unique Aspects of EPOXY

EPOXY offers a unique approach to performance optimization. Most transistor sizing programs integrate fixed electrical models with a fixed optimization technique (e.g.: ANDY, COP, OPT, PLATO, TILOS, TV/AI). Performance improvement systems (e.g.: APLSTAP, DELIGHT) that permit a selection of models and optimization algorithms are computationally expensive because these two tasks are handled by separate programs. Separation of modeling and optimization routines results in extra storage and communication expense to maintain essentially equivalent information. However, EPOXY provides a unique flexibility in selecting, substituting, and evaluating performance models and optimization algorithms while retaining the computational efficiency of integrated systems.

The flexibility of performance improvement systems can be classified by the design metrics they consider. Typical design metrics include worst-case response times (circuit delay), maximum power consumption, total cell height, width, and area. However, most systems are restricted to minimizing a single predefined design metric and fixed constraints. TV/IA can provide a user with sensitivity information so that other design metrics can be taken into account manually. However, these systems inhibit a user from automatically achieving the desired tradeoff among other design metrics since they incorporate fixed objective functions and constraints. EPOXY allows a user to specify the objective function and constraints.

Even at the modeling level, many of the transistor sizing programs quote total transistor (active) area as an area metric. However, total transistor area does not accurately represent the overall area required for the design since it does not consider transistor placement and routing effects imposed by larger transistors. Total transistor area is actually a better measure of worst-case maximum dynamic power rather than total cell area. Therefore *Table 1.1* differentiates between these two metrics. The only two systems that model the area of the cell are COP and PLATO. Although COP's area model considers the relative placement of transistors, it does not take advantage of the significant area underneath the routing channel. However, PLATO does model details such as snaking transistors for PLA's. EPOXY's virtual grid area model accurately relates changes in transistor sizes to changes in the overall cell area for all layout styles.

Matson and Glasser [Mats86] discuss how the parameters for their nMOS gate model are automatically derived. EPOXY extends this concept by deriving the performance equations symbolically for the entire circuit of interest. Then the partial differential equations required by most non-linear optimization methods are derived. Therefore, the sensitivity information can be quickly and accurately provided by evaluating these differential equations without having to resort to approximations such as finite differences. In addition, EPOXY can easily incorporate new models since the underlying derivation and manipulation routines for the equations need not change. A new performance model need only generate the appropriate equations. The remaining routines can create the partial derivative equations and evaluate all of the generated equations.

Traditional circuit optimization programs have concentrated on transistor sizing to improve the speed of a circuit at the expense of increased power and area. However, if the design goals cannot be met by transistor sizing alone, structural techniques can be applied. EPOXY considers several circuit changes such as splitting large transistors into several smaller ones, inserting buffers, and rearranging transistors in pull-down or pull-up trees. While circuit changes can be considered during synthesis as in MIS [Bray86], MTA [Hofm87], and [Mich87], these tools consider the whole circuit and thus are forced to employ simplified models for performance and area estimation. EPOXY, on the other hand, makes local modifications at the layout level by examining the circuit in greater detail with more accurate models.

Global changes in circuit structure such as logic resynthesis are best made earlier in the design process. EPOXY deals with the remaining complexity of detailed circuit performance improvement given design constraints and performance goals. Therefore, the limited circuit structural changes that may be necessary can be made at a level where the performance impact of these changes can be accurately assessed.

#### 1.3. Goals of this Research

Many of the previous transistor sizing tools tightly couple the electrical models with an optimization routine that solves a fixed predefined optimization problem. However, it is difficult for users to determine how much of the performance improvements come from using less accurate electrical models or from a particular optimization routine. EPOXY can answer these questions by providing a framework in which the user specifies an objective function and a set of constraints, and which can substitute the performance models and optimization routines. EPOXY's use of performance equations combines the execution speed comparable to integrated systems with the flexibility of applying different performance models, optimization routines and circuit modification techniques.

EPOXY is a system for sizing transistors and modifying circuits to help meet performance constraints. EPOXY's unique features addresses the concerns of VLSI circuit designers and design tool developers:

flexible

A VLSI designer can specify (1) an objective function to minimize, and (2) additional performance constraints. Therefore, a designer can more readily determine the tradeoffs among several of the design metrics of interest such as area, time, power, etc.

A user can select the appropriate performance models, optimization routine and circuit modification techniques.

open

The effects of model accuracy and speed of evaluation in producing an optimized design are easily determined. For example, a fair comparison of several electrical models can be made using the same optimization algorithm. The results of these tests can also suggest which models and optimization routines are appropriate for various technologies and design styles.

#### architecture

Representing the performance by deriving a set of equations is the key to providing the **flexible** and **open** features. This strategy leads to equations that can be evaluated rapidly, but at the expense of additional memory. EPOXY provides several basic operations that support the equation representation of circuit performance:

- 1. Macros and function calls construct the equations directly in memory.

- 2. Circuits with feedback lead to equations that reference each other in a cycle. These cycles are removed by expanding each unique path through the cycle.

- 3. Equations are then ordered so they can be evaluated rapidly. Some of the possible evaluation modes are:

- a. Evaluate all equations.

- b. Evaluate only those equations affected by a change in one variable (incremental evaluation).

- c. Evaluate those equations affected by a change in a small number of variables (a larger-grain incremental evaluation).

A variable whose value has changed is marked so that the corresponding equations can be re-evaluated.

- d. Output the equations symbolically so they can be compiled for additional speed and storage advantages.

- 2. New equations can be incrementally inserted in the linear ordering.

- 3. Partial derivative equations are generated from the performance equations automatically. These equations form the sparse Jacobian matrix required by several non-linear optimization-based routines.

- 4. Macros and function calls can alter the equations and corresponding node and transistor data structures. These routines directly manipulate the underlying circuit structure without re-extracting and rebuilding the entire circuit.

#### 1.4. Organization of this Dissertation

In this dissertation, transistor sizing and local circuit modifications are investigated as a means of improving VLSI circuit performance. Each of these issues corresponds to a component of EPOXY. EPOXY's approach to improving VLSI circuit performance is to derive the equations from the layout which model the circuit performance, formulate the transistor sizing problem as a non-linear program (NLP), and then modify the circuit to improve the solution further. A key benefit to this representation is that clear comparisons can be made between different performance models, optimization routines, and circuit modification techniques.

The first two chapters will examine performance models and optimization algorithms necessary for sizing transistors to meet performance goals. Chapter 2 details

the performance models currently available in EPOXY and describes how these models affect the final optimized results. The choice of models requires a careful balance between simulation accuracy and evaluation speed. The following chapter (Chapter 3) describes the optimization algorithms implemented within the tool. Each optimization algorithm is evaluated by the quality of solutions obtained for some representative circuits and by the running times to find these solutions. Solution quality is evaluated by the user specified performance goals.

Chapter 4 describes how several techniques are used to improve the solutions that fail to meet the design constraints after transistor sizing. Although specific circuit modifications are evaluated, the technique of how these modifications are implemented is described so that they may serve as a template for implementing other kinds of beneficial circuit modifications.

The conflicting requirements of rapid circuit modification and rapid evaluation speed were satisfied by generating equations that determine the circuit performance. The equations provide increased flexibility and improve the overall execution speed at the expense of additional memory. The larger memory requirement, which limits the maximum circuit size, is evaluated for several representative circuits. A discussion of the implementation strategy for the equations and evaluation of their effectiveness within EPOXY follows in *Chapter 5*. An example circuit illustrates the information that a user specifies and the equations that EPOXY generates.

The final chapter (*Chapter 6*) summarizes the major contributions of this thesis and outlines several research topics for future investigation.

## 2. Modeling Circuit Performance

The task of any performance improvement system is to determine an assignment of the input parameters that best satisfies the performance constraints. This problem has two main components: modeling the circuit performance and selecting the best implementation (optimization). This chapter will concentrate on the issues associated with circuit performance modeling.

A designer of integrated circuits is interested in several metrics that characterize the quality of layout. For MOS VLSI circuits, these include the response time (circuit delay), maximum power dissipation, total layout area, cell height and width. The designer has control over many input parameters such as the placement of transistors, their width and lengths, and parasitic capacitance. Electrical models relate these physical parameters to the electrical performance metrics, i.e., delay (time) and power. The area model provides total height and width and an estimation of layout parasitics. This chapter presents a virtual grid area model that considers detailed layout effects caused by changes in transistor sizes. As illustrated later in this chapter, this area model is well suited for many layout styles such as PLA's and standard cells.

The choice of the appropriate model for each design metric must carefully balance the conflicting requirements of accuracy in estimating the actual circuit performance and computational expense. Since the goal is to produce a quality layout that meets the desired performance constraints, the crucial issue is how these models affect the optimization results. The next subsections present models for each of the typical design metrics of interest to VLSI designers.

#### 2.1. Time

A VLSI designer is faced with many node delays of potential interest. In his work on ATV [Wall88], an abstract timing verifier, Wallace outlines several timing models: single numbers, ranges (min-max), and statistical descriptions (mean and standard deviation), and asymmetric rise/fall versions of these. MOS designers are usually concerned with the worst-case response times (a single number model) for their layout as dictated by worst-case input arrival times and required output response times.

The input arrival times and required output response times are quantities given to a designer. Therefore, the input node times will be represented as constants in the problem formulation of the non-linear optimization, while the output node times will be specified as constraints.

Worst-case response times can be determined using gate-level or transistor-level models. Gate level models identify logic gates by grouping the transistors that drive an output node. All transistor sizes that compose the logic gate are then related by a single factor. For example, AESOP [Hedl87] scales all of the transistors in a gate using the same factor. The gate factors also determine the response times. Alternatively, transistor-level models determine node response times by calculating the effects of each transistor on the attached nodes. Optimization programs based on gate-level models such as AESOP are usually faster since the ensuing

optimization routine considers a much smaller input vector space (the gate factors). Because several transistors are used to create a single gate, there are many more transistor sizes than gate factors. Unfortunately, transistor sizing systems based on gate models produce many over-sized transistors since the single gate factor will unnecessarily increase the size of transistors that do not participate in any critical path. These larger transistors will consume more power by loading the output of the previous logic gate. Therefore, transistor-level models are better suited for producing quality optimization results.

| RC Model                    | Transistor      | Evaluation | Average   |

|-----------------------------|-----------------|------------|-----------|

|                             | Model           | Time       | Error     |

|                             |                 | fets/sec   | to SPICE† |

| Lumped                      | Linear          | 82.3       | 24%       |

| Lumped                      | Slope           | 66.0       | 8%        |

| Distributed                 | Slope           | 55.8       | 6%        |

| $t_{out} = f(t_{in}, R, C)$ | R = f(w,l,type) |            |           |

| Out m                       | C = f(w,l,type) |            |           |

Table 2.1. Summary of Crystal time models. The evaluation time and accuracy for Crystal's time models in the first two columns are given by the third and fourth columns. The evaluation time is the average over 1000 timing analyses for a full 32 bit adder on a standard Sun-3/140‡. († Data in this column from [Oust85].) The transistor model determines the transistor's equivalent on-resistance and capacitance. The RC model combines these resistances and capacitances to determine the worst-case response times.

Ousterhout has outlined several value-independent (transistor-based) switch-level models for calculating worst-case delays given layout parasitics and transistor widths and lengths [Oust85] as described in Table 2.1. These include the lumped RC, lumped slope RC, and the distributed slope RC models. The lumped and distributed models differ in how the transistor resistance and capacitance values are combined to produce a worst-case node time. These models determine the delay effect of each transistor switching independently from all others. The linear transistor model assigns a single resistance depending on the transistor width, length, and type (p- or n-type). For most circuits, the linear transistor model is sufficient. However, slow rising and falling edges cause transistors to switch more slowly than fast rising edges. The slope transistor model also considers the signal rising and falling times in determining its resistance. For most logic gates, only one transistor switches at a time. Therefore the more accurate slope transistor model is used for the single switching transistor while all others use the simple linearly-interpolated default transistor model.

Equations for the response time of a node are derived using the template:  $t_{output\ node} = \max(t_{input\ node} + delay())$  where  $t_{input\ node}$  is the time the input changes. EPOXY currently provides a worst-case distributed linear RC electrical

<sup>‡</sup> Sun-3 is a trademark of Sun Microsystems, Inc.

model for *delay* (), although other models could be substituted. EPOXY is not restricted to RC trees, as *Figure 2.1* demonstrates.

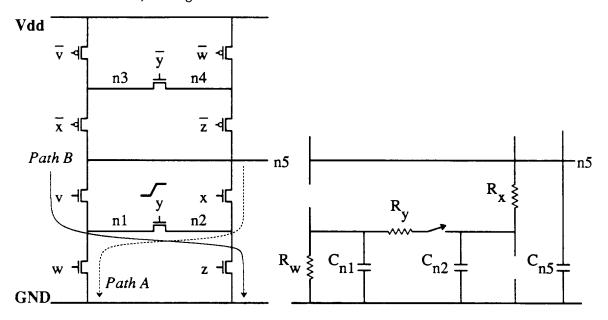

Figure 2.1. Critical path derivation of a CMOS static gate. A static CMOS combinational logic gate and the corresponding RC equivalent circuit for deriving one possible discharge path (path A) for node n5 caused by a rising signal on node y, the gate of the transistor (y).  $R_{fet}$  is the on-resistance of the transistor (fet) and  $C_{node}$  is the total capacitance on the node.

The equations that determine the worst-case response time of node n5 in Figure 2.1 due to a rising transition on node y are listed below.

(Path A)

$$t_{fall, n5} \ge t_{rise, y} + (R_y + R_w)C_{n2} + (R_x + R_y + R_w)C_{n5};$$

(Path B)  $t_{fall, n5} \ge t_{rise, y} + (R_y + R_z)C_{n1} + (R_v + R_y + R_z)C_{n5};$

Since the derivation of these equations involves finding all paths from each output node through attached transistors to the power supply rails, EPOXY actually represents these equations using intermediate variables and equations. The equations that EPOXY generates to determine the response time for node n5 are given below. Note that even a simple circuit fragment can generate a large number of equations. Several intermediate variables are used in the following equations to represent the resistance through a path of transistors from a particular node to the power supply in response to an input transition (rising or falling) on a transistor ( $R_{transition, node, transistor, path)$ ) and the inherent delay of the switching transistor and all transistors between it to the power supply subject to an input transition ( $t_{transition, transistor}$ ). This example illustrates that a simple circuit can generate several equations. These equations were generated automatically by EPOXY.

$$R_{fall,n1,fet\ w,path0} = R_{fet\ w};$$

$R_{fall,n1,fet\ y,path0} = R_{fet\ y} + R_{fall,n2,fet\ z,path0};$   $R_{fall,n2,fet\ z,path0} = R_{fet\ z};$   $R_{fall,n2,fet\ y,path0} = R_{fet\ y} + R_{fall,n1,fet\ w,path0};$

```

R_{fall, n3, fet \ \overline{v}, path 0} = R_{fet \ \overline{v}}; \quad R_{fall, n3, fet \ \overline{y}, path 0} = R_{fet \ \overline{y}} + R_{fall, n4, fet \ \overline{w}, path 0};

R_{fall,n4,fet \ \overline{w},path0} = R_{fet \ \overline{w}}; R_{fall,n4,fet \ \overline{y},path0} = R_{fet \ \overline{y}} + R_{fall,n3,fet \ \overline{v},path0};

R_{fall, n5, fet v, path0} = R_{fet v} + R_{fall, n1, fet v, path0};

R_{fall, n5, fet \ v, path 1} = R_{fet \ v} + R_{fall, n1, fet \ w, path 0};

R_{fall, n5, fet x, path 0} = R_{fet x} + R_{fall, n2, fet z, path 0};

R_{fall, n5, fet x, path 1} = R_{fet x} + R_{fall, n2, fet y, path 0};

R_{fall, n5, fet \ \overline{x}, path0} = R_{fet \ \overline{x}} + R_{fall, n3, fet \ \overline{y}, path0};

R_{fall, n5, fet \ \overline{x}, path 1} = R_{fet \ \overline{x}} + R_{fall, n3, fet \ \overline{v}, path 0}

R_{fall, n.5, fet \bar{z}, path0} = R_{fet \bar{z}} + R_{fall, n.4, fet \bar{y}, path0};

R_{fall, n5, fet \ \overline{z}, path 1} = R_{fet \ \overline{z}} + R_{fall, n4, fet \ \overline{w}, path 0};

t_{fall, fet \ \overline{v}} \ge C_{n5} R_{fall, n5, fet \ \overline{x}, path 1} + C_{n3} R_{fall, n3, fet \ \overline{v}, path 0};

t_{fall, fet \ \overline{v}} \ge C_{n5}R_{fall, n5, fet \ \overline{z}, path 0} + C_{n4}R_{fall, n4, fet \ \overline{v}, path 0}

+ C_{n3}R_{fall,n3,fet \bar{v},path0};

t_{fall, fet \ \overline{w}} \ge C_{n5} R_{fall, n5, fet \ \overline{x}, path 0} + C_{n3} R_{fall, n3, fet \ \overline{y}, path 0}

+ C_{n4}R_{fall,n4,fet \overline{w},path0};

t_{fall.fet \ \overline{w}} \ge C_{n5} R_{fall.n5, fet \ \overline{z}, path 1} + C_{n4} R_{fall,n4, fet \ \overline{w}, path 0}

t_{fall, fet \ \overline{x}} \ge C_{n5} R_{fall, n5, fet \ \overline{x}, path 0}; t_{fall, fet \ \overline{x}} \ge C_{n5} R_{fall, n5, fet \ \overline{x}, path 1};

t_{fall, fet \ \overline{y}} \ge C_{n5} R_{fall, n5, fet \ \overline{x}, path0} + C_{n3} R_{fall, n3, fet \ \overline{y}, path0};

t_{fall, fet \ \overline{y}} \ge C_{n5} R_{fall, n5, fet \ \overline{z}, path 0} + C_{n4} R_{fall, n4, fet \ \overline{y}, path 0};

t_{fall, fet \ \overline{z}} \ge C_{n5} R_{fall, n5, fet \ \overline{z}, path 0};

t_{fall, fet \bar{z}} \geq C_{n5} R_{fall, n5, fet \bar{z}, path 1};

t_{fall,n5} \ge t_{rise,v} + t_{rise,fet,v};

t_{fall.n5} \ge t_{rise.w} + t_{rise,fet.w};

t_{fall,n5} \ge t_{rise,x} + t_{rise,fet x};

t_{fall, n5} \ge t_{rise, y} + t_{rise, fet, y};

t_{fall,n5} \ge t_{rise,z} + t_{rise,fet} z;

t_{rise, fet \ v} \geq C_{n5} R_{fall, n5, fet \ v, path 0};

t_{rise, fet \ v} \geq C_{n,5} R_{fall, n,5, fet \ v, path 1};

t_{rise, fet \ w} \ge C_{n5} R_{fall, n5, fet \ v, path 1} + C_{n1} R_{fall, n1, fet \ w, path 0};

t_{rise, fet \ w} \ge C_{n5} R_{fall, n5, fet \ x, path 1} + C_{n2} R_{fall, n2, fet \ y, path 0}

+ C_{n,1}R_{fall,n,1,fet,w,path,0};

t_{rise, fet x} \geq C_{n5} R_{fall, n5, fet x, path 0};

t_{rise, fet x} \ge C_{n5} R_{fall, n5, fet x, nath 1};

t_{rise, fet \ y} \ge C_{n5} R_{fall, n5, fet \ v, path0} + C_{n1} R_{fall, n1, fet \ y, path0};

t_{rise, fet y} \ge C_{n5} R_{fall, n5, fet x, path1} + C_{n2} R_{fall, n2, fet y, path0};

t_{rise, fet z} \ge C_{n5} R_{fall, n5, fet v, path 0} + C_{n1} R_{fall, n1, fet v, path 0}

+ C_{n2}R_{fall,n2,fet\ z,path\ 0};

t_{rise, fet z} \ge C_{n5} R_{fall, n5, fet x, path0} + C_{n2} R_{fall, n2, fet z, path0};

t_{rise, n5} \ge t_{fall, \overline{v}} + t_{fall, fet, \overline{v}};

t_{rise, n5} \ge t_{fall, \overline{w}} + t_{fall, fet \overline{w}};

t_{rise,n5} \ge t_{fall,\bar{x}} + t_{fall,fet,\bar{x}};

t_{rise, n5} \ge t_{fall, \overline{y}} + t_{fall, fet, \overline{y}};

t_{rise, n5} \ge t_{fall, \bar{z}} + t_{fall, fet, \bar{z}};

```

The transistor model provides the on-resistances and parasitic capacitances for a given width, length and type (n- or p-channel). EPOXY currently supports a

first-order approximation of a transistor's resistance and capacitance, the linear model. The constants,  $Kr_{type}$ ,  $Kg_{type}$ , and  $Ksd_{type}$  are automatically determined by a least squares fit of these modeling equations to SPICE simulations of small representative circuits.  $Kr_{type}$  relates the transistor strength (length over width) to its average resistance subject to a fast switching input signal. The gate oxide capacitance per unit area,  $Kg_{type}$ , and the diffusion capacitance per transistor width,  $Ksd_{type}$ , can be determined instead from the process parameters for transistors. Since the source and drains of MOS devices are symmetric, equal values for the source and drain capacitances ( $C_{sd,fet}$ ) are used.

$$R_{type,fet} = Kr_{type} \left[ \frac{l_{fet}}{w_{fet}} \right];$$

$C_{gate,fet} = Kg_{type} w_{fet} l_{fet};$   $C_{sd,fet} = Ksd_{type} w_{fet};$

Finally, node capacitance is determined by adding the parasitic capacitance and the capacitance of attached transistor gates, sources, and drains. The variables appearing in the node capacitance equation are determined by the interconnection of transistors within the circuit. For the example CMOS circuit, the capacitance of node n1 is given below.

$$C_{n1} = C_{parasitic \ n1} + C_{sd,v} + C_{sd,w} + C_{sd,y};$$

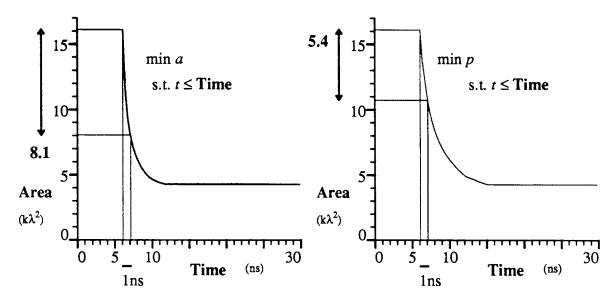

Although simple models may be sufficient for ordering critical paths, they are not likely to be accurate enough for optimization that requires absolute comparisons to delay constraints (e.g., "critical paths must be less than 20ns"). Aggressive designs are typically forced into the region where a designer must balance minimum delay (maximum speed) with an overall area limitation. A small error in estimating delay to meet a fixed time constraint can have a large impact on overall area. That is, if the timing model overestimates the delay, a faster than necessary design will be produced. The design is larger because it employs larger transistors. Similarly, a timing model that underestimates the delay will produce designs that do not meet the timing constraints. To correct the design, substantial additional area may be required. Figure 2.2 clearly shows that overestimating the delay will produce larger designs for the minimization of area and power for an eight-stage CMOS inverter chain (using the MOSIS SCMOS  $\lambda$ =0.7 $\mu$ m design process). A 1ns time error results in a 3,956  $\mu$ m<sup>2</sup> (8,074  $\lambda$ <sup>2</sup>) error for area minimization and 2,636  $\mu m^2$  (5,380  $\lambda^2$ ) error for power minimization. Therefore, if the model underestimates the delay by 16% (1ns), a circuit 100% larger than necessary will be reported for a minimum area implementation and 50% for a minimum power implementation. Since the lumped RC model has an average error of 25%, transistor sizing tools based on this model would exhibit even larger area and power errors.

Some designers are interested producing circuitry that is hazard and race free. Kohavi [Koha78] describes several conditions that can cause hazards or races. A hazard is a situation where a change in a single input may cause a momentary incorrect output. Whether or not an incorrect signal is actually generated depends on the exact delay associated with the various circuit elements. A race condition arises when two or more state variables are required to change their value simultaneously in a finite state machine. If the final state of the circuit does not depend on the order in which the input variables change, then the race is noncritical.

Figure 2.2. Total cell area  $\neq$  total transistor area. The graphs indicate the total cell area (Area) required by an eight-stage inverter chain (MOSIS SCMOS  $\lambda$ =0.7 $\mu$ m) to achieve a specific delay (Time). The graph on the left shows the minimum area implementation while the one on the right gives the minimum power configuration. The smallest circuit that meets a 7.1ns time constraint requires an area of  $8,044\lambda^2$  (3,942  $\mu$ m<sup>2</sup>). The smallest circuit that meets a 6.1ns time constraint requires an area of  $16,118\lambda^2$  ( $16,118\lambda^2$

Designers of asynchronous circuits should avoid both of these difficulties.

Designers can eliminate some of the hazard or race conditions by constraining the performance problem. Lower bound constraints on some of the delay paths assure that a signal is stable long enough to avoid generating an incorrect signal. For asynchronous designs that employ level-sensitive latches, the fastest path though the combinational logic should not be less than half of the slowest path through the logic; otherwise, an input signal may feed through the circuit more than once per cycle. Unfortunately, single number timing models are incapable of generating the required information. However, a min-max (worst-case/best-case) timing model can generate the required fastest and slowest response times. A min-max timing model is easily implemented within EPOXY since the best-case equations are similar to the worst-case equations already described. The following equations implement a min-max timing model.

$$R_{min, type, fet} = Kr_{min, type} \left( \frac{l_{fet}}{w_{fet}} \right); \qquad R_{max, type, fet} = Kr_{max, type} \left( \frac{l_{fet}}{w_{fet}} \right);$$

$$C_{gate, min, fet} = Kg_{min, type} w_{fet} l_{fet}; \qquad C_{gate, max, fet} = Kg_{max, type} w_{fet} l_{fet};$$

$$C_{sd, min, fet} = Ksd_{min, type} w_{fet}; \qquad C_{sd, max, fet} = Ksd_{max, type} w_{fet};$$

$$C_{min, node} = C_{parasitic} + \sum_{attachedfets} C_{gate, min, fet} + \sum_{attachedfets} C_{sd, min, fet};$$

$$C_{max, node} = C_{parasitic} + \sum_{attachedfets} C_{gate, max, fet} + \sum_{attachedfets} C_{sd, max, fet};$$

$$t_{min, output node} = \min(t_{min, input node} + \sum_{paths} R_{min, fet} C_{min, node});$$

$$t_{max, output node} = \max(t_{max, input node} + \sum_{paths} R_{max, fet} C_{max, node});$$

#### 2.2. Power

The IC package imposes an maximum power dissipation limit (constraint) on the entire design. Total power has dynamic and static components. Static power usually dominates for nMOS and pseudo-nMOS design styles, while dynamic power dominates for most other CMOS design styles [West85]. Since dynamic power is a function of the operating frequency, a maximum operating frequency must be defined along with the maximum allowable power.

The static component is determined by the minimum resistance between the power supply signal lines. For nMOS, the smallest resistance occurs when all the transistors are on. Since the static current is mainly determined by the depletion-mode pull-up of each gate, the static maximum power can be approximated by:

$$power_{static, nMOS} = \sum_{gates} \left[ \frac{V_{dd}^2}{R_{depletion, gate}} \right];$$

For CMOS, the small static power consumption is due to reverse bias leakage between the diffusion regions and substrate. The power due to leakage current can be described by the diode equation. The maximum dynamic power required by a circuit is directly related to the capacitance it drives. Since the power to drive the input nodes comes from external circuitry, the maximum dynamic power a circuit consumes is related to the internal and output load capacitance (excluding the supply nodes), whose total will be represented the variable,  $C_{driven}$ . For the CMOS example, the total power will be approximated by the maximum dynamic power component. The following equations result:

$$power_{CMOS} \approx power_{dynamic} = C_{driven} V_{dd}^2$$

frequency max;

$C_{driven} = C_{n1} + C_{n2} + C_{n3} + C_{n4} + C_{n5}$ ;

#### 2.3. Area

There are many possible choices for representing the area design metric. A VLSI designer usually needs to generate a layout to fit within a given space in an existing design. Alternatively the aspect ratio (ratio of height to width) of a circuit must be maintained so that it can be placed in a realistic package. Therefore, an appropriate area metric for an optimization program should include cell height and width.

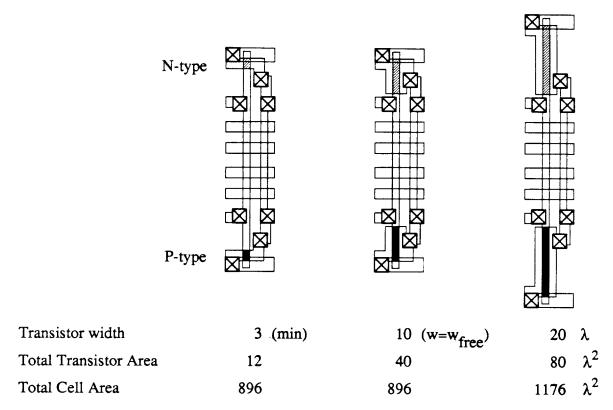

Figure 2.3. Layout effects of free transistor width. The effect of transistor widths on total cell height and width are illustrated by layout fragments of a static CMOS standard-cell inverter. The layout on the left contains transistors of minimum width  $(3 \lambda, 2.1 \mu m)$ . As long as the transistor width falls below the *free* limit, the layout area will not change (center layout fragment). The layout on the right illustrates the additional cell area required if the transistors increase well above their *free* limit.

Most transistor sizing tools (e.g.: [Shyu88b], MOST, TILOS, TV/AI, XTRAS) do not model the total cell height and width. Instead, they use total active transistor area, which is actually a component of dynamic power rather than a measure of total cell area. The chapter on optimization techniques will show the difference in area, delay, and power resulting from a change in the objective function. Typically this can be as much as 32% for even the simple eight inverter chain.

Another consequence of choosing a realistic area metric is that there is no longer any need to artificially constrain the maximum size on every transistor as in AESOP. Instead, transistors take on the appropriate size necessary to meet the design constraints.

Cell height and width are not determined simply by transistor and routing dimensions alone. The overlap between routing area and total transistor area, significantly impacts the overall area and performance. Therefore, an important element in characterizing layout is how well the area under the routing channel is utilized before the overall dimensions must change. This factor is identified by the free transistor width, the width that a transistor can grow without affecting the area of the cell. If a transistor width falls within the minimum and free width, then the

2.3. Area 17

overall cell width will not change. The free transistor width is determined by local routing and connections.

In a structured design environment such as standard cells, if one transistor has exceeded its *free* width, then all transistors in the same row (a track) also benefit from the additional width. This simple factor can rapidly relate transistor size changes to cell height and width changes. EPOXY considers splitting of large transistors into smaller ones [Hill87] in the restructuring section, since width/height tradeoffs are best made once these large transistors are identified by transistor sizing. *Figure 2.3* illustrates the effects of *free* transistor width on overall cell area.

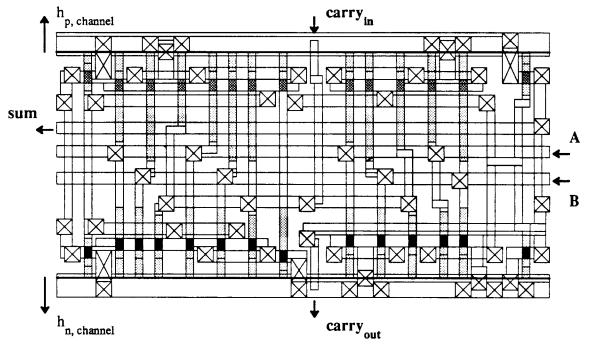

Figure 2.4. Free transistor widths for a CMOS adder. The rows of p- and n- type transistors are highlighted in the standard-cell CMOS layout for a static full adder. The inputs to this full adder are A, B, and carry<sub>in</sub>; the outputs are sum and carry<sub>out</sub>. The free width for each transistor is described by the lighter shading around the transistor. If any transistor exceeds its free width, the track must be enlarged to accommodate it.

Given a circuit architectural style, total height and width can be used as the area metric rather than the simple sum of transistor area. The virtual grid area model takes into account routing effects on each transistor by determining its *free* transistor width. Since typical standard-cell layout styles employ columns of n- and p-channel transistors, the formulation of the area equations is straightforward. Figure 2.4 illustrates a standard-cell implementation of a static CMOS full adder. The format of the area equations for a standard-cell layout are listed below. The last constraint shows that the sizing of power busses to provide sufficient current can be incorporated into this model.

$area = height \ width;$

```

width = \max w_{channels}; w_{channel} = w_{interconnect} + \sum l_{fet};

height = \sum h_{channels}; h_{channel} = h_{routing, channel} + h_{n, channel} + h_{p, channel};

h_{type, channel} \ge w_{fet} - w_{free, fet}; h_{type, channel} \ge 0;

h_{type, channel} \ge h_{power buss, channel} - h_{power buss, min};

```

COP [Marp87] estimates total area for standard cells by adding the widths of the maximum p- and n- channel transistors to the height of the routing channel. While this is a measure of total cell area, it fails to consider the space available to larger transistors under the particular routing channel.

The area model based on free transistor width is general enough to accurately model other layout styles. In essence, this approach results in a virtual grid expansion technique for detailed layout. First, free widths are identified for each transistor. Next, transistors are grouped into tracks (virtual grid lines). When a transistor exceeds its free width, the layout is expanded along the track line (the virtual grid line is moved). Transistors that share a track must have the same orientation and contain layout (routing) which can be expanded perpendicular to the track.

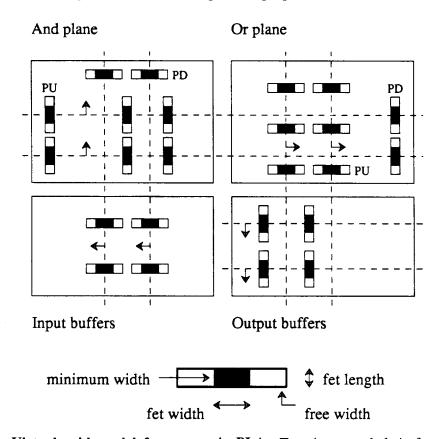

Figure 2.5. Virtual grid model for a generic PLA. Transistors and their free widths are identified in a PLA. If a transistor exceeds its free width, the design is widened along the corresponding dashed track line in the direction of the arrow. All transistors that share the track (virtual grid line) have additional space in which to expand. The pull-up (PU) transistors and the pull-down (PD) transistors of dynamic designs may be omitted in static PLA's.

2.3. Area 19

PLATO [Marp86] accurately models the height and width of PLAs. Similarly, EPOXY's general virtual grid based area model also accurately models the height and width of PLAs, as Figure 2.5 illustrates. Changes in width of a transistor are reflected in the overall PLA area if the transistor dominates its virtual grid track. Unlike standard cells, the virtual grid lines for PLA's will intersect, since transistors assume different orientations. Once the virtual grid lines are place, the computation of overall PLA area is similar to that for standard cells. The only difference is that transistor widths may effect the PLA cell height and width. PLATO also considers snaking of transistors in the AND and OR planes. The free widths for transistors and track information can be provided by the PLA template as in MPLA [Scot85].

#### 2.4. Noise Margins

Digital circuits require immunity from noise in order to produce logic results. Noise margins specify the allowable noise voltage on the input so that acceptable logic voltage values appear on all outputs. The noise margin for a gate is directly related the ratio of the pull up resistance to the pull down resistance [West85]. Since changes in transistor size effect this ratio, a designer may wish to restrict the ratio to assure an acceptable noise margin. CMOS circuits are less sensitive to variations in this ratio than are nMOS circuits.

$$NM_{min} \le \frac{R_{pull\ up}}{R_{pull\ down}} \le NM_{max};$$

#### 2.5. Conclusions

This chapter outlines models for determining total cell area, height, width, maximum power dissipation and worst-case delay. These models are represented by a set of equations so that they can be easily substituted in order to evaluate their effect on the optimized results. EPOXY currently represents these models by creating equations using the following templates:

Distributed linear RC delay model:

$$R_{type,fet} = Kr_{type} \left[ \frac{l_{fet}}{w_{fet}} \right]; \qquad C_{gate,fet} = Kg_{type} w_{fet} l_{fet};$$

$$C_{sd,fet} = Ksd_{type} w_{fet};$$

$$C_{node} = C_{parasitic} + \sum_{attachedfets} C_{gate,fet} + \sum_{attachedfets} C_{sd,fet};$$

$$delay() = \sum_{paths} R_{fet} C_{node};$$

$$t_{output node} = \max(t_{input node} + delay())$$

Maximum dynamic power:

$$C_{driven} = \sum_{internal nodes} C_{node};$$

$$power_{dynamic} = C_{driven} V_{dd}^{2} frequency_{max};$$

2.5. Conclusions 20

Total area, cell height and width depend on the transistor orientations:

```

area = height width;

width = \max w_{channels}; w_{channel} = w_{interconnect} + \sum l_{fet};

height = \sum h_{channels}; h_{channel} = h_{routing, channel} + h_{n, channel} + h_{p, channel};

h_{type, channel} \ge w_{fet} - w_{free, fet}; h_{type, channel} \ge 0;

```

This chapter considers and analyzes several alternative models for representing the design metrics. The key concepts from this chapter are:

- 1. Accurate timing models are crucial in performance optimization, since a small error in meeting a time constraint (16%) can typically result in much larger area (100% more area) and power dissipation (50%) than necessary.

- 2. The sum of transistor areas is not an appropriate measure of total cell area. Rather it is a component of dynamic power. The optimization of an eight-stage inverter chain shows that the minimum power implementation is 32% larger than the one for minimum area for a 10ns time constraint.

- 3. A virtual grid area model accurately represents the cell height, width and area by considering the detailed routing using free transistor width. Two examples demonstrate how the equations are easily derived from standard cell and PLA layouts.

- 4. The optimization problem is uniformly formulated using equations. The flexibility of EPOXY is demonstrated by allowing the user to specify an objective function and performance constraints so that the user can pursue a layout with the desired performance tradeoffs. From this information, a performance envelope that describes the full range of performance implementations of interest can be derived.

## 3. Optimization and Heuristic Techniques

Systems that improve a design's performance primarily rely on either optimization-based or heuristic techniques. Optimization-based algorithms make use of gradient information (partial derivatives) to indicate specific changes in the input parameters that lead to better values for the objective function. However, the constraint equations limit the changes in the input parameters so that the constraints are satisfied. On the other hand, heuristic techniques are based on designer experience that certain changes usually improve the design.

Ideally, a user could select the most appropriate heuristic or optimization technique for a design problem based on extensive analysis. However, most transistor sizing programs tightly couple an electrical model with a fixed optimization algorithm to improve the overall execution speed. By representing the performance by a set of equations, EPOXY allows electrical models and optimization techniques to be substituted, yet retains the rapid execution comparable to integrated systems. Chapter 5 explains the advantages of the equation representation within EPOXY. This chapter describes and compares the results of a few optimization and heuristic techniques.

The performance design problem can be formulated as a classical optimization program:

min f(x) subject to  $g(x) \le 0$

The objective function, f(x), defines the quality of a configuration represented by the independent vector of variables, x. For transistor sizing problems, a design is specified by the assigned transistors widths, x. The VLSI design quality is usually described by the area, delay, or power consumed by the circuit. The constraint functions, g(x), define requirements on the input variables such as minimum transistor width, overall maximum cell height and width, maximum dynamic power and delay constraints.

When the design problem is cast as a non-linear program, the performance models provide the equations and constraints that determine the overall design metrics. EPOXY automatically generates these core set of equations from the circuit layout. The non-linear program is complete when the user defines an objective function and performance constraints.

The task of an optimization routine is to determine the best feasible implementation, as described by an objective function, that meets all of the performance constraints. The performance optimization problem involves non-linear equations, since delay is a non-linear function of transistor width (a total cell area metric) even for a simple lumped RC electrical model. This non-linear relationship will appear in at least one of the constraint equations. In general, non-linear programs (NLP) are difficult to solve because of many potential local minima.

To simplify the design rules, lambda-based designs [Mead80] restrict transistor sizes to integer multiples of lambda. However, this arbitrary limitation results in an integer non-linear program that is much more difficult to solve than the original NLP. Therefore, as in most transistor sizing programs, the transistors widths are not restricted to integer multiples of lambda. A user can appropriately round the

transistor widths to achieve the desired integer values. Although an integer-valued optimization cannot be solved by rounding the corresponding real-valued solution, a design with performance similar to the real-valued solution can be produced by rounding the transistor sizes.

The following subsection will describe the design space for a CMOS example to illustrate the performance tradeoffs. Next, the augmented Lagrangian optimization technique and several heuristics will be discussed. The augmented Lagrangian algorithm has been implemented within EPOXY since it represents one of the classic optimization techniques whose convergence rate to a local optimum can be derived. The TILOS-style heuristic will be examined in greater detail since it rapidly sizes transistors subject to timing constraints. Then the results of several optimization problems are compared using the augmented Lagrangian optimization technique and TILOS-style heuristic.

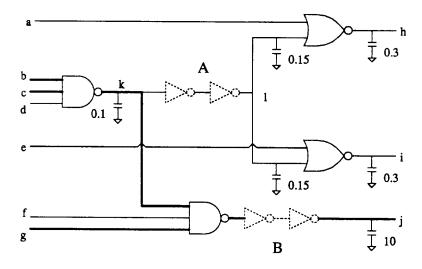

#### 3.1. Performance Envelope

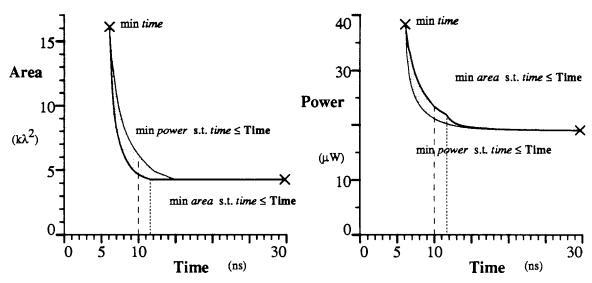

Since a VLSI designer is interested in balancing several performance metrics, the non-linear program results in a multi-dimensional problem. Unfortunately, it is difficult to visualize multi-dimensional graphs or to extract numerical information from them. Therefore, projections of the multi-dimensional boundary onto areadelay and power-delay graphs bound the region within which lay all designs of interest. This region, which we call the *performance envelope*, is illustrated in *Figure 3.1* for a standard-cell layout of an eight-stage CMOS inverter chain. These curves were generated by substituting a variety of objective functions and constraints within EPOXY.

The graph on the left of Figure 3.1 shows the area required to implement a standard-cell static CMOS eight inverter chain to meet a given time constraint. The X on the upper left part of the graph marks the performance of the fastest (minimum time) implementation regardless of power consumption and area. The lower right X indicates the performance of the implementation with minimum device sizes. This configuration needs the smallest area and power. Since the transistor widths can assume any non-integer value, these two points are connected by continuous curves that give the minimum area and minimum dynamic power implementations for a given time constraint. For the area versus time graph, there exists no circuit smaller than the minimum area implementation that meets the time constraint (the region below the minimum area curve). Circuits that draw more than the minimum power implementation would not be of interest (the region above the minimum power curve). Therefore, the only circuits of interest lie between the two curves as illustrated by the shaded region. The maximum dynamic power versus time graph describes a similar situation. Circuits between the two curves represent a tradeoff between the requirements of area, power, and time.

These graphs clearly show the effects of the more accurate area model. As the circuit delay decreases, the required area does not change above the minimum size implementation (the flat portion of the area versus time graph for the minimum area configurations) until at least one transistor exceeds its free width. At this

Figure 3.1. Typical performance envelope. These graphs illustrate the area required (left graph) and dynamic power required (right graph) to implement the minimum dynamic power (min power) and minimum area (min area) configurations of an eight-stage static CMOS inverter chain to achieve a specific delay (Time). Only the region between these curves represents the designs of interest to a VLSI designer. The dashed line highlights the range of performance for designs that operate at 10ns. The dotted line indicates the fastest design that still requires the smallest cell area. The output has an additional 1 pf capacitance load.

point (as highlighted by the dotted line at 11.8ns), the other transistors in the circuit can assume sizes that still meet the required response time, but which draw less power. Therefore, the curve for the power required by the minimum area implementations changes slope on the power versus time graph at 11.8ns. Thereafter, additional area is required for circuits with less delay.

| Minimum | Constraint  | Area $\lambda^2$ | (µm <sup>2</sup> ) | Power<br>μW |

|---------|-------------|------------------|--------------------|-------------|

| power   | time ≤ 10ns | 6188.            | 3032.              | 21.22       |

| area    | time ≤ 10ns | 4677.            | 2292.              | 23.48       |

Table 3.1. Comparison of an area and power optimization. This table gives the area and maximum dynamic power required (column headers) to implement the minimum area and minimum power configurations (row headers) of an eight inverter chain. Both optimizations are subject to a 10ns response time constraint. Figure 3.2 illustrates the layout for these two designs.

Table 3.1 contains data extracted from the graphs of Figure 3.1. For a 10ns implementation (as marked by the dashed line in Figure 3.1), the minimum power implementation is 32% larger than the minimum area implementation. Total transistor area is closely related to the maximum dynamic power. Therefore if one uses total transistor area (a power metric) to approximate total cell area, the resulting solution may be as much as 32% larger than necessary since the minimum

power implementation is 32.3% larger than the minimum area design.

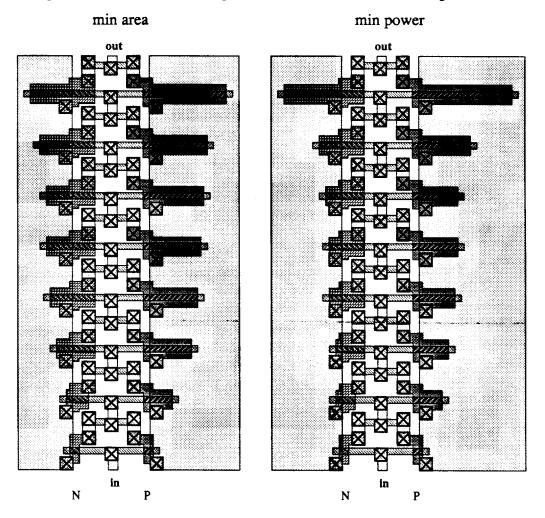

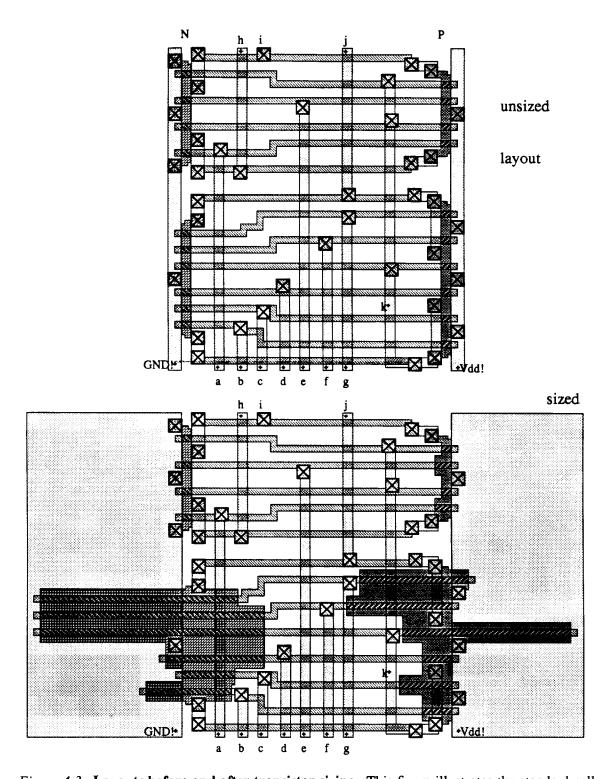

Figure 3.2. Layouts for an eight stage inverter chain. This figure illustrates the standard-cell layouts for an eight-stage static CMOS inverter chain. The left design requires the minimum cell area to meet a 10ns delay constraint while the right design requires the least dynamic power to meet this delay constraint. The input is applied at the bottom of each design at the node marked in. A 10pf load is added to the output node at the top of each design marked out.

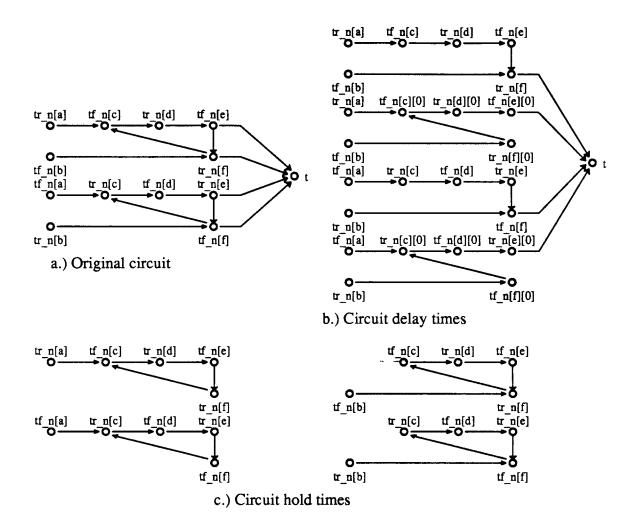

Figure 3.2 contains the layouts for the minimum area and minimum power implementations subject to the 10ns delay constraint. The eight stage inverter takes its input at the bottom at the node marked in and produces the output at the top as marked by the node out. The first stage is fixed to minimum sized devices so that the loading on the previous stage is constant. The remaining transistors are sized appropriately. Note that the overall cell width for the minimum power implementation is larger than the minimum area design since the minimum power configuration uses larger transistors in the last stages located at the top of the layout. However, the minimum area design uses larger transistors in the middle of the design than the minimum power implementation.