## Analysis of Branch Prediction Strategies and Branch Target Buffer Design\*

Johnny K. F. Lee\*\*

and

Alan Jay Smith\*\*\*

University of California, Berkeley

Keywords: pipeline, branches, branch prediction, instruction statistics.

C.R. Categories: B.12, C.11, C.4

#### ABSTRACT

CPU pipelines need a steady flow of instructions in order to function with maximum effectiveness. Branches which change the expected order of instruction execution require that the pipeline be reloaded, resulting in several lost machine cycles per such branch. By examining the type of branch and the past execution behavior of that branch (taken/not taken) it is possible to predict with high accuracy whether the branch will be taken or not taken, and by remembering the previous branch target (destination), to predict the current branch target. In this paper we use a systematic approach to selecting good prediction strategies. Our studies are based on 26 program address traces grouped into four IBM 370 workloads (scientific, commercial, compiler, supervisor) and CDC 6400 and DEC PDP-11 Our results show the effectiveness of various prediction workloads. strategies, the number of past branches that should be remembered, the amount of state required for each and the effect of workload and branch type. Improvements of from 5% to 20% can be expected in CPU performance when a branch target buffer is installed. We also consider issues relating to the implementation of real branch target buffers.

<sup>\*</sup>Partial support for this research was provided by the National Science Foundation under grants MCS77-28429 and MCS-8202591 and by the Department of Energy under contract DE-AC03-76SF00515 to the Stanford Linear Accelerator Center.

\*\*Present Address - Hewlett-Packard Company, GSD, 978 E. Arques Ave., Sunnyvale, Ca. 94086.

\*\*\*Computer Science Division, EECS Department, University of California, Berkeley, Ca. 94720.

#### I. Introduction

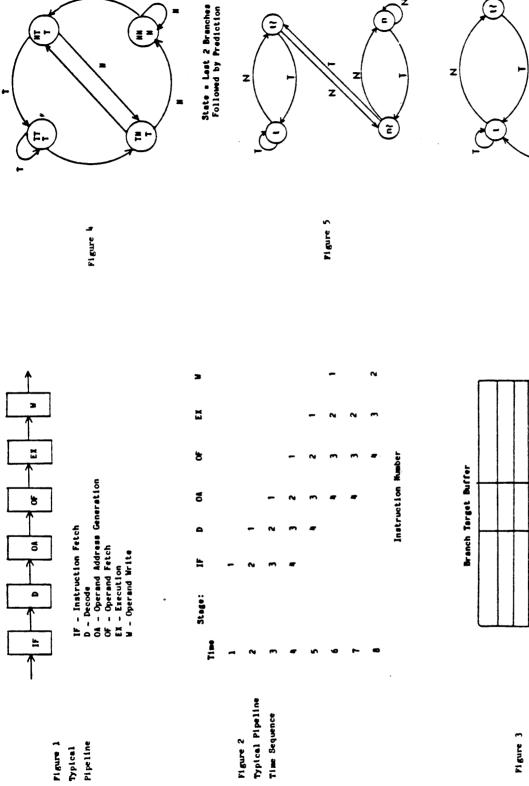

Modern high speed computer systems achieve their high performance by two means: fast logic and parallelism. One of the most important aspects of that parallelism is the pipelining of instruction execution. That is, to execute each instruction, a number of operations must be performed sequentially. A typical sequence might consist of instruction fetch (IF), instruction decode, operand address generation, operand fetch, execution and operand write. This sequence is illustrated in figure 1. Pipelining consists of executing several instructions concurrently, with each instruction in a different stage of the processing sequence (see figure 2.) The pipeline (pipe) shown in figure 1 could contain up to 7 instructions, each in a different stage. We refer the reader to [Ram77] or [Kogg81] for a comprehensive survey of pipelining.

Pipelines are very cost effective as a means to achieve parallelism because although several instructions may be processed in parallel, each is in a different phase of execution, and thus there need exist only one set of hardware for each stage. Of course, the logic required to implement a totally non-pipelined machine would be less, since there would be less control logic, but a significant savings is still obtained.

For a number of reasons, the N-fold parallelism promised by an N stage pipeline is seldom realized. First, we note that the pipeline is constrained to run no faster than its slowest stage. Even if all of the stages have the same average processing time, random variations in one or more of them will disrupt the smooth flow of instructions [Pine79]. For example, the execution stage of the pipeline will generally run more slowly for "decimal divide" than for "integer add". We will refer to the minimum time for an instruction to advance one stage in the pipe as the pipeline stage time (PST). Other delays encountered in pipelines occur because of attempts to use busy resources (e.g. conflicts in accessing a single port register file), or failure to have an input available. (E.g. one instruction uses the output of the immediately previous one as part of

Figure 6

Branch Target Address

Branch Prediction Statistics

Branch Instruction Address

3

an address calculation, but that previous instruction has not passed the execute stage of the pipeline.) Cache memory misses are another major source of pipeline delay [Smit79].

One of the major problems in designing a CPU pipeline is to ensure a steady flow of instructions to the initial stage of the pipeline. Such a flow can be either impeded or interrupted for two reasons: (1) The memory access time is long enough that a request by the instruction fetch (IF) stage of the pipe for another instruction will not be satisfied in one PST; or (2) a change in the expected sequence of instructions, due, for example, to a branch, will cause the contents of part of the pipeline to be discarded, and the pipeline to be reloaded. We call this latter reason the "branch problem". The branch problem is intimately related to the timely fetch of instructions since the penalty for a branch will depend on the time required to fetch the branch target.

The branch problem can be explained more fully as follows: The "execution" of a branch instruction consists of causing the instruction fetch unit to select a different instruction as the next instruction to execute. Thus, considering the pipeline shown in figure 1, all of the partially executed instructions in the stages of the pipeline preceding the execution unit must be discarded; an additional delay is also encountered in fetching the new, out of sequence instruction. Each of these two delays can seriously impact the CPU performance.

There are a number of ways in which the performance degradation due to branches in the instruction stream can be reduced. We list those methods here; each is discussed in more detail in the next section: loop buffer(s), prepare to branch, delayed branch, multiple instruction streams, prefetch branch target, data fetch target, taken/not taken switch, and the branch target buffer. The branch target buffer (BTB), the principal topic of this paper, is a small associative memory which retains the addresses of recently executed branches and their targets (destinations). This buffer is used to predict whether the branch will be

taken this time, and if so, what the target of the branch will be. The instruction fetch stage then continues by fetching instructions from the predicted target address.

In this paper we present a thorough and systematic study of the design and effectiveness of branch target buffers. In the next section we review the various existing solutions to the branch problem and also discuss previous studies of the BTB. Our research is based on extensive analysis of program instruction traces, which is explained in section III. Section IV considers instruction behavior and tabulates a large variety of measurements on those traces. After that, we consider branch prediction mechanisms of various complexity. There are a number of implementation considerations which are discussed in section VI. Finally, we estimate the overall effectiveness of the BTB.

### II. Existing Approaches to the Branch Problem

Modern computers implement a variety of mechanisms to minimize the branch problem. In this section, we briefly discuss each.

#### A. Loop Buffer(s)

A loop buffer is a small, very high speed buffer maintained by the instruction fetch stage of the pipeline. A single loop buffer contains one set of sequential instructions. Multiple loop buffers contain n sequences, one per buffer, but the contents of the various buffers need not be contiguous with each other. The loop buffer functions in two ways: first, it contains instructions sequentially ahead of the current instruction fetch address; thus instructions fetched in sequence will be available without the usual memory access time. Second, it will recognize when the target of a branch falls within its contents (this may include backward branches) and will deliver those instructions without accessing memory. It is possible to fetch all of the instructions for a loop entirely from this buffer; thus the name "loop buffer". Among the machines using a loop buffer include the CDC Star-100 [CDC73] with a

buffer of 256 bytes, the CDC-6600 with 60 bytes, [Thor64,CDC74] and the CDC 7600 with twelve 60 bit words [CDC75].

The Cray-I maintains four loop buffers [Cray76,Russ78], and replaces their contents in a FIFO manner. The idea here is that a loop may consist of several non-contiguous instruction sequences and thus may be better captured this way than by a mechanism that permits only one sequence.

## B. Multiple Instruction Streams

A normal pipeline suffers a branch penalty because for a conditional branch it must make a choice - the instruction fetch unit must either fetch the next sequential instruction or it must fetch the branch target. A brute force approach to this problem is to replicate the initial stages of the pipeline, so that both the sequential instruction and the potential branch target can be fetched, decoded, and processed. There are three problems with this approach: (1) The branch target cannot be fetched until its address is determined. That may require a computation, as when a displacement is added to both a base and index register. This computation requires time even when all operands are available. Further delays may occur when operands are not available, which occurs if an operand is the result of a not yet completed instruction or when a memory fetch is required. There may also be contention delays, as, for example, in accessing the register file. Also, additional memory traffic is generated, further creating resource contention [Garc80]. instruction I is a branch instruction, then there may be additional branch instructions to enter the pipeline (either part) before I is resolved as to taken/not taken and target. Riseman and Foster [Rise72] found that for a typical length pipeline, more than two branches would have to be so processed for there to be a significant improvement. The net amount of (3) Finally, the cost of hardware is likely to be impractical. replicating significant parts of the pipeline (including instruction fetch, instruction decode, operand address generate) is substantial; thus this mechanism is of questionable cost effectiveness.

Despite the problems with following multiple instruction streams, a number of machines do so: The IBM 370/168 [IBM73] can fetch one alternate instruction path; the IBM 3033 [IBM78] can pursue two alternate instruction streams. The 3033 only fetches an alternate instruction stream when it is predicted to be taken; this prediction depends on the branch condition mask in the instruction, the operation code and the target address operand register. (See also [Hugh81b].)

#### C. Prefetch Branch Target

Rather than replicate several initial stages of the pipeline, it is helpful to duplicate only enough logic to prefetch the branch target. That is, when a branch is recognized, a special mechanism calculates and prefetches the target of the branch; thus if the branch is found to be taken, the target is loaded immediately into the instruction decode stage of the pipe, with no additional delay for instruction fetch [Yamo80]. Several such prefetches can be accumulated along the main instruction sequence, but since the secondary (prefetched) sequences are not decoded, no additional prefetches can be generated there.

IBM 360/91 uses the simple prefetch mechanism described, whereby it prefetches a double word target [Ande67, IBM70].

#### D. Data Fetch Target

In the IBM 370 architecture, the Branch Conditional instruction has the same form as the Load or Add (from memory) instruction; that is, the target of the branch is computed in just the same way as the memory based operand of the Load or Add. The Amdahl 470 computers [Amda76] use this feature to produce an effect very much like the target prefetch mechanism of the 360/91: the branch target is accessed as if it were an ordinary operand; if the branch is taken, the target is loaded into the instruction decode stage of the pipeline. (Rather than being placed in a register, as for Load, or being sent to the adder, as for Add.)

#### E. Prepare to Branch

The Texas Instruments ASC computer [TI76] uses two buffers into which it alternately prefetches instructions from memory. The Prepare To Branch

and Load Look Ahead instructions can cause the machine to prefetch from the branch target rather than to prefetch sequentially. The effectiveness of this scheme depends on the programmer or the compiler correctly inserting these instructions.

### F. Delayed Branch

The problem with a branch is that if instruction I is a taken (successful) branch, then instruction I+1 will be out of sequence, with the consequences described above. The instruction set architecture can be specified so that a branch is defined to affect the address not of instruction I+1 but of instruction I+k, for some k. If k is equal to or larger than the number of pipeline stages preceding the stage at which the branch is resolved (executed) then the instruction fetch can (almost) always be given the correct address from which to fetch. (The "almost" refers to the occurence of asynchronous events such as interrupts, which cannot be predicted from the instruction stream.)

There are several problems with designing a machine to use a delayed branch. The most significant is that it is likely that human programmers will find it very difficult to write code in which some instructions (branches) have delayed effects. Thus code for such a machine must be almost entirely compiler generated, with the consequent need for a bug free and very efficient compiler. We also note that the delayed branch requires a new architecture; it cannot be used as a technique to speed up an existing one. In addition, not all of the potential speed up of the delayed branch may be realized; there may not be k-1 instructions that can be usefully performed once the branch is resolved.

Despite the problems noted above, there are two existing experimental computers which use the delayed branch: the IBM 801, an experimental minicomputer constructed at IBM Research, Yorktown Heights [Radi82], and a dedicated microprogrammed machine constructed by E. R. Berlekamp [Berl79] to insert and remove error correcting codes from signal transmissions. It has been proposed for the RISC computer [Patt81].

## G. Taken/Not Taken Switch

As we will show in the remainder of this paper, whether or not a branch will be taken can be predicted with good accuracy. A prediction mechanism which specifies whether a branch will or won't likely be taken is called the taken/ not taken switch. The idea is that with every instruction in the cache memory, one or more bits are associated. The setting of these bits determines whether the branch is predicted to be taken or not. After the branch is resolved, the values of the bits may be reset in the cache to reflect the prediction for the next time.

The taken - not taken switch has been proposed for the S-1 computer [Widd77; see also Hail79,Wood79]. Two bits are stored with each instruction. One bit specifies whether a jump should be predicted (the Jump bit) and the other tells whether the last prediction wrong (the Wrong bit). Two wrong predictions in a row cause the Jump bit to be changed. The effectiveness of this prediction algorithm is discussed in [Widd77] and below in section V.B. We note that this mechanism still encounters delays due to target address computation and the out of sequence fetch. A version of this scheme is proposed in [Lile79].

### H. Look Ahead Resolution

Another proposed solution to the branch problem [Hugh81a] is to place extra logic in the pipeline so that an early stage of the pipeline can resolve a branch whenever possible. It is possible if the condition code affecting a conditional branch has already been determined. See also [Losq82b] and [Rao82].

### I. Branch Target Buffer

The Branch Target Buffer is a small cache memory associated with the instruction fetch (IF) stage of the pipeline. The BTB retains three-tuples, each of which contains: the address of a previously executed instruction, information which permits a prediction as to whether the instruction branch will be taken, and the most recent target address for that branch (see figure 3). It functions as follows: The instruction

fetch stage compares the instruction address against the instruction addresses in the BTB. If there is a match, then a prediction is made as to whether the branch is likely to be taken. If the prediction is that the branch will occur, then the target address field is used to select the next instruction fetch address. When the branch is actually resolved, at the execute stage of the pipe, the BTB is updated, if necessary, with the corrected prediction information and target address. We note that the BTB can be used for every instruction fetch, and thus it can have as many predictions in force as there are instructions uncompleted in the pipeline.

The major optimization problem in the design of a BTB is the selection of the algorithm that predicts whether or not the branch will be taken. There are also the implementation issues of how large the BTB will/should be, and how it should be organized (e.g. set associative, hashed, etc.). There have been two previous papers which study these optimizations. Holgate and Ibbett [Holg80] study its effectiveness in the context of the MU-5, which actually implements a branch target buffer, roughly of the type described. (See also [Losq82c] which proposes this idea.) J. Smith [Smit81] examines a number of BTB designs using traces for the CDC Cyber 170 computer. In both cases, the results are similar to our own, but in this paper we study three different machine architectures (IBM 370, DEC PDP-11, CDC 6400) and we consider prediction strategies much more systemmatically. We compare their results to our own as appropriate in the remainder of this paper.

### III. Methodology and Data

There currently exists no statistically acceptable model to characterize any aspect of program behavior (although with respect to paging and memory management, there has been much research [Smit78c], [Spir77]). With respect to the design and evaluation of branch target buffers, there is the need for a model of when branches occur, whether

they will be taken or not, and whether the branch target will change. Because there is no model which can accurately predict these things, our research will be based on the thorough analysis and use for trace driven simulation of program address traces.

#### A. The Data

We have available 26 program address traces (see Appendix I) which we have grouped into six workloads. Four of these workloads are for the IBM 370 architecture and consist of compiler executions (PL/I, Cobol, Fortran-H), business programs (Cobol, PL/I), a scientific mix (Fortran) and a supervisor state set of traces (MVS operating system). Six traces form the Digital Equipment Corporation PDP-11 workload, and six more traces comprise the Control Data Corporation 6400 workload. In Appendix I we list each of the programs in each workload and also give their combined total length in instructions.

From each program trace, the branch instructions were extracted, along with their targets, addresses, number in sequence and operation codes. All of the analysis was based on this extraction.

The large number of traces used in this research and the grouping of them into workloads serves several purposes: First, the large number of individual traces, and the use of several of them in each workload, should give representative behavior; no individual trace, no matter how peculiar, can significantly throw off the overall results. Conversely, the use of workloads, rather than a grand average, serves to show the variation to be expected from the different job mixes experienced on different computer centers, different machines and at different times of day. It is well known that certain workloads have different instruction mixes; e.g. business programs use many more SS type operations on the IBM 370 than scientific programs. Conversely, the scientific programs have far more floating point operations. If such differences affect the effectiveness of a branch target buffer, it will be apparent in our studies. Similarly, the use of traces from three very (!) different machine architectures will

we some indication of whether the results are sensitive to the instruction set architecture.

Some of our studies will show results for various specific machine instructions. For reference purposes, we show the branch instructions for each machine in Appendix II. Some of our studies will be limited to conditional branches only; the instructions considered to be conditional branches are also listed in Appendix II.

#### B. Methodology

Trace driven simulation is a technique by which a trace is recorded of the operation of some system. That trace is then used to drive a model of the system, in which various parameters or features of interest can be varied. If the variation in parameters does not affect the validity of the trace, then the trace driven simulation can accurately predict the effect of changes in the system. An early example of trace driven simulation for the evaluation of paging algorithms is given in [Bela66], and for the evaluation of CPU scheduling, in [Sher72].

We use our program address traces in two different ways. First, we examine them and measure various features of interest; for example, the frequency of taken and not taken branches. We then use these measurements as one basis from which we can formulate branch buffering strategies. The traces are then used to evaluate branch target buffer designs.

### IV. Branch Behavior

## A. Taken/Not Taken and Branch Frequency by Opcode

For each trace, in table 1 we show the overall probability of a branch being taken or not, and the ratio (r) of branch instructions to all instructions in the trace. We note two important features here: first, branches are taken twice as often as not; thus by just guessing that branches are always taken, we are right 60 to 70% of the time. (In [Smit81] the range over six traces is 57% to 99%, with an average of 76.7%.) Variation between workloads is moderate, and for all workloads, branches are taken a majority of the time.

|     | IBM<br>CPL | IBM<br>BUS | IBM<br>SCI | IBM<br>SUP     | DEC<br>PDP11   | CDC<br>6400    | Ave.           |

|-----|------------|------------|------------|----------------|----------------|----------------|----------------|

| • - | 0.360      | 0.343      | 0.296      | 0.460<br>0.540 | 0.262<br>0.738 | 0.222<br>0.778 | 0.324<br>0.676 |

| _   | 0.317      | 0.057      | 0.105      | 0.376          | 0.388          | 0.079          | 0.242          |

Fraction of Branches, taken, not taken, and fraction of branches overall(r).

Table 1

| Op                                                                                        | IBM                                                                                             | IBM                                                                                             | IBM                                                                                                      | IBM                                                                                             | Op                                                                     | DEC                                                                                    | Op                                            | CDC                                                         |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------|

| Code                                                                                      | CPL                                                                                             | BUS                                                                                             | SCI                                                                                                      | SUP                                                                                             | Code                                                                   | PDP11                                                                                  | Code                                          | 6400                                                        |

| BR,B<br>BAL<br>BALR<br>BCT<br>BCTR<br>BXH<br>BXLE<br>BC<br>BCR<br>EX<br>SVC<br>LPSW<br>MC | 0.222<br>0.056<br>0.036<br>0.024<br>0.022<br>0.004<br>0.032<br>0.544<br>0.051<br>0.009<br>0.000 | 0.243<br>0.036<br>0.050<br>0.013<br>0.050<br>0.000<br>0.000<br>0.521<br>0.005<br>0.001<br>0.000 | 0.254<br>0.013<br>0.079<br>0.027<br>0.006<br>0.000<br>0.188<br>0.318<br>0.112<br>0.003<br>0.000<br>0.000 | 0.138<br>0.036<br>0.065<br>0.016<br>0.019<br>0.000<br>0.003<br>0.674<br>0.034<br>0.005<br>0.001 | JSR<br>SOB<br>BGET<br>BVCS<br>BHSL<br>BNEQ<br>RTS<br>JMP<br>BR<br>TRAP | 0.111<br>0.008<br>0.113<br>0.030<br>0.031<br>0.278<br>0.074<br>0.190<br>0.162<br>0.002 | RJ<br>JP<br>XJ<br>EQ<br>NE<br>GE<br>LT<br>SYS | 0.049<br>0.017<br>0.560<br>0.157<br>0.199<br>0.000<br>0.015 |

Frequency of Branch Types

Table 2

| Op         IBM         SUP           BR,B         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000         1.000 <th>Code PDP11</th> | Code PDP11 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

Probabilities of Branch Taken by Branch Type (- indicates instruction not in that trace)

Table 3

The probability that a branch is of a specific operation code is shown in table 2 for each workload. In the case of the 370 workloads, we note significant variation in the frequency of the various operation types.

Table 3 shows the probability that a branch is taken for each operation code. It is worth noting, of course, that unconditional branches are always either taken or not taken. (But BALR is sometimes used to set up the base registers, and so is not taken). Those used for indexing are usually taken (but BCTR is usually not taken because it is often used as a decrement instruction).

## B. Dynamic Branch Behavior

It is important to note that not all branches are executed equally frequently. A good deal of our ability to predict branches will depend on the fact that some branches are executed large numbers of times and therefore from past behavior we can make a good guess as to what will happen next. To provide a clear vocabulary for discussing this, we first define two terms:

Static Branch Instructions - This refers to the individual branch instructions found in a program. For a given program, the number of these branches is fixed and can be counted by looking at the program.

Dynamic Branch Instructions - This refers to the branch instructions found in the trace of a program. A static branch instruction can occur more than once as a dynamic branch instruction; every instance of the execution of a static branch instruction results in a new dynamic branch.

In table 4 we show the probability distribution for each workload for the number of times a static branch occurs as a dynamic branch. Table 5 shows the probability that a dynamic branch is due to a static branch which is executed n times. As may be evident, the large bulk of dynamic branches occur for frequently executed static branches; for example, the 23.4% of the static branches of the IBM/CPL mix get executed only once, but they account for only .5% of the dynamic branches. On the other hand,

| n1234567891 | BM CPL 23.1 4.0 22.8 3.2 2.7 1 | IBM<br>BUS<br>25.7<br>8.3<br>7.9<br>4.6<br>0.5<br>2 | IBM<br>SCI<br>19.0<br>8.1<br>3.1<br>2.4<br>2.1<br>2.6<br>4.2 | IBM<br>SUP<br>64.7<br>10.6<br>5.0<br>3.3<br>4.6<br>1.7<br>0.9<br>1.6<br>.5 | DEC<br>PDP11<br>13.8<br>5.6<br>5.0<br>1.5<br>3.7 | CDC<br>6400<br>16.2<br>3.8<br>2.7<br>1.1<br>1.0<br>2.9 |

|-------------|--------------------------------|-----------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------|

| 10<br>>200  | 1.1                            | 4.2<br>9.3                                          |                                                              | .5                                                                         | .7<br>40.1                                       | .7<br>32.0                                             |

Percentage of branch instructions executed n times

Table 4

| 1 | .0 |

|---|----|

|---|----|

Percentage of branch instructions executed n times weighted by n i.e. Probability that Dynamic Branch Results from Static Branch Executed n times.

Table 5

```

1

1111111111111111111111111111111111

234567890

110100110100111

110110110111110

11

12

13

14

15

16

17

18

19

20

Some Sample Sequences of Takens and Not Takens

1 = taken)

(0 = not taken;

Table 6

```

the 10.4% of the static branches that were executed over 200 times comprise 48.2% of the dynamic branches.

Many of our predictions of whether a branch will be taken will be contingent on the past behavior (taken/not taken) of that branch. To illustrate such branch behavior, we show in table 6 some sequences of taken/not taken for a number of branches. We observe that for many branches, there are long sequences of either taken or not taken; it is less common to see an alternation. Such a sequence of taken or not taken, we call a "run"; a run is defined as a sequence of identical behavior (taken, not taken, taken with a changed target) of a static branch as it gets executed many times. For example, the sequence of takens (T) and not takens (N) TTTTTNNTTTTNNNN consists of run lengths of 5, 2, 4, 1, 1, etc. Tables 7 and 8 show the distributions of run lengths for the conditional branches and all branches respectively. The same data is shown weighted by the run length in tables 9 and 10. (That is, tables 9 and 10 show the probability that a given dynamic branch is an element of a run of length n.) As can be seen, most branches occur as parts of long runs.

### C. Branch Clustering

Earlier, in section II.B, we described one method of coping with the branch problem called "multiple instruction streams." That involved recognizing branches at the instruction decode step of the pipeline, and then fetching and decoding both the taken and not taken outcomes of the branch. As noted, one difficulty with that solution was the potential occurence of a large number of closely clustered branches, so that it would be impossible to follow all 2\*\*k paths possible from k branches. A measure of the size of k appears in tables 11 and 12. Those tables show the probability that in H sequential instructions (H=10 and H=6 respectively), there are k branches. If the pipeline is long enough (and 6 and 10 are typical numbers for high speed machines), then there is a significant probability that there is more than one branch unresolved at any one time.

Table 7

Distribution of Run Lengths (Conditional Branches)

| n123456789011234566 | IBM<br>CPL<br>0.517<br>0.132<br>0.066<br>0.049<br>0.033<br>0.022<br>0.024<br>0.014<br>0.012<br>0.009<br>0.011<br>0.007<br>0.007<br>0.007<br>0.007 | IBM<br>BUS<br>0.417<br>0.099<br>0.060<br>0.047<br>0.022<br>0.025<br>0.015<br>0.017<br>0.007<br>0.009<br>0.002<br>0.002<br>0.002<br>0.002<br>0.229<br>ribution | IBM<br>SCI<br>0.500<br>0.148<br>0.040<br>0.019<br>0.070<br>0.016<br>0.014<br>0.012<br>0.014<br>0.018<br>0.025<br>0.018<br>0.009<br>0.013<br>0.008<br>0.064<br>of Run<br>Table 8 | IBM<br>SUP<br>0.674<br>0.112<br>0.050<br>0.034<br>0.036<br>0.014<br>0.009<br>0.012<br>0.006<br>0.004<br>0.026<br>0.003<br>0.003<br>0.001<br>0.002<br>0.001<br>0.013<br>Lengths | DEC<br>PDP11<br>0.487<br>0.142<br>0.067<br>0.041<br>0.028<br>0.028<br>0.014<br>0.016<br>0.010<br>0.010<br>0.009<br>0.009<br>0.009<br>0.009<br>0.004<br>0.005<br>0.121<br>(All Types) | CDC<br>6400<br>0.601<br>0.189<br>0.033<br>0.032<br>0.014<br>0.017<br>0.005<br>0.006<br>0.003<br>0.009<br>0.004<br>0.001<br>0.003<br>0.003 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| n<br>123456789011<br>121314<br>1516                                       | IBM<br>CPL<br>0.069<br>0.032<br>0.024<br>0.021<br>0.016<br>0.018<br>0.015<br>0.014<br>0.013<br>0.016<br>0.010<br>0.010<br>0.010<br>0.010 | IBM<br>BUS<br>0.030<br>0.014<br>0.015<br>0.015<br>0.007<br>0.009<br>0.005<br>0.004<br>0.002<br>0.004<br>0.002<br>0.003<br>0.003<br>0.871 | IBM<br>SCI<br>0.110<br>0.083<br>0.025<br>0.014<br>0.086<br>0.014<br>0.014<br>0.013<br>0.011<br>0.011<br>0.012<br>0.012<br>0.008<br>0.047<br>0.501 | IBM<br>SUP<br>0.218<br>0.074<br>0.046<br>0.045<br>0.064<br>0.030<br>0.022<br>0.031<br>0.018<br>0.014<br>0.083<br>0.011<br>0.004<br>0.006<br>0.007<br>0.317 | DEC<br>PDP11<br>0.058<br>0.019<br>0.039<br>0.032<br>0.014<br>0.011<br>0.018<br>0.015<br>0.008<br>0.009<br>0.007<br>0.008<br>0.009 | CDC<br>6400<br>0.215<br>0.123<br>0.021<br>0.025<br>0.011<br>0.024<br>0.010<br>0.005<br>0.008<br>0.005<br>0.008<br>0.005<br>0.005<br>0.005 |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                           |                                                                                                                                          |                                                                                                                                          |                                                                                                                                                   |                                                                                                                                                            |                                                                                                                                   |                                                                                                                                           |  |  |

| 210<br>Dietaibuti                                                         | on of Ru                                                                                                                                 | n Lengti                                                                                                                                 |                                                                                                                                                   |                                                                                                                                                            | (Conditional                                                                                                                      | Branches)                                                                                                                                 |  |  |

| Distribution of Run Lengths Weighted by n (Conditional Branches)  Table 9 |                                                                                                                                          |                                                                                                                                          |                                                                                                                                                   |                                                                                                                                                            |                                                                                                                                   |                                                                                                                                           |  |  |

| n 1 2 3 4 5 6 7 8 9 0 1 1 2 3 4 5 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | IBM<br>CPL<br>0.052<br>0.027<br>0.021<br>0.020<br>0.016<br>0.014<br>0.017<br>0.012<br>0.011<br>0.009<br>0.013 | IBM<br>BUS<br>0.025<br>0.013<br>0.014<br>0.008<br>0.009<br>0.007<br>0.006<br>0.004<br>0.0011<br>0.004<br>0.003<br>0.002 | IBM<br>SCI<br>0.074<br>0.046<br>0.015<br>0.011<br>0.013<br>0.014<br>0.016<br>0.017<br>0.018<br>0.016<br>0.014<br>0.032 | IBM<br>SUP<br>0.228<br>0.075<br>0.050<br>0.046<br>0.061<br>0.039<br>0.019<br>0.014<br>0.096<br>0.012<br>0.011<br>0.005<br>0.008 | DEC<br>PDP11<br>0.032<br>0.016<br>0.017<br>0.014<br>0.011<br>0.007<br>0.011<br>0.006<br>0.008<br>0.006<br>0.011<br>0.003<br>0.006<br>0.004 | CDC<br>6400<br>0.130<br>0.091<br>0.008<br>0.014<br>0.008<br>0.006<br>0.002<br>0.008<br>0.077<br>0.002<br>0.004<br>0.005<br>0.001 |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                                                                       | 0.008<br>0.013<br>0.009<br>0.739                                                                              | 0.003<br>0.002<br>0.003<br>0.872                                                                                        | 0.014<br>0.032<br>0.015<br>0.598                                                                                       |                                                                                                                                 |                                                                                                                                            |                                                                                                                                  |

Distribution of Run Lengths Weighted by n (All Types)

Table 10

| n 0 1 2 3 4 5 6 | IBM<br>CPL<br>0.025<br>0.119<br>0.345<br>0.613<br>0.840<br>0.976<br>0.999 | IBM<br>BUS<br>0.182<br>0.495<br>0.722<br>0.855<br>0.911<br>0.983<br>0.999 | IBM<br>SCI<br>0.405<br>0.734<br>0.878<br>0.959<br>0.985<br>0.996 | IBM<br>SUP<br>0.028<br>0.140<br>0.402<br>0.739<br>0.940<br>0.995<br>1.000 | DEC<br>PDP11<br>0.005<br>0.088<br>0.347<br>0.792<br>1.000<br>1.000 | CDC<br>6400<br>0.509<br>0.726<br>0.985<br>0.998<br>1.000 |

|-----------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|

| 6<br>7          | 1.000                                                                     | 1.000                                                                     | 1.000                                                            | 1.000                                                                     | 1.000                                                              | 1.000                                                    |

Table 11

Probability of n or fewer Branches in Window of Size 10

| IBM IBM DUS CPL BUS 0.087 0.341 1 0.370 0.689 2 0.724 0.875 3 0.969 0.984 0.999 1.000 5 1.000 1.000 Probability of n |  | IBM<br>SUP<br>0.104<br>0.430<br>0.827<br>0.985<br>1.000<br>1.000<br>Branches | DEC<br>PDP11<br>0.065<br>0.337<br>0.937<br>1.000<br>1.000<br>1.000<br>in Window | CDC<br>6400<br>0.603<br>0.931<br>0.994<br>1.000<br>1.000<br>1.000<br>of Size 6 |

|----------------------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| IBM   | IBM   | IBM   | IBM   | DEC   | CDC   |

|-------|-------|-------|-------|-------|-------|

| CPL   | BUS   | SCI   | SUP   | PDP11 | 6400  |

| 0.662 | 0.692 | 0.710 | 0.552 | 0.798 | 0.778 |

Probability of Correct Branch Prediction, Given Only Op-Code, and Assuming Branch Is Always Either Taken or Not Taken, Based on Op-Code.

Table 13.

| 1 | NNNNT ON NNNTT ON NNNTT ON NNTTH ON NNTTH ON NTTH ON NTHIN ON NTHI | IBM<br>CPL7<br>.0132<br>.0013<br>.0024<br>.0003<br>.0004<br>.0003<br>.0004<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.0003<br>.00 | IBM BUS 0.414 0.006 0.004 0.003 0.005 0.001 0.002 0.005 0.001 0.005 0.001 0.001 0.001 0.002 0.001 0.002 0.001 0.002 0.001 0.002 0.001 0.002 0.001 0.009 0.009 0.009 0.009 0.009 0.009 0.009 0.005 0.009 0.005 0.009 0.005 0.009 0.005 0.009 0.005 0.009 0.005 0.005 0.009 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.005 0.00 | IBM SC37 4 4 0 1 4 5 0 0 0 1 4 5 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | <br>0.011<br>0.012<br>0.003<br>0.012<br>0.001<br>0.001<br>0.003<br>0.014 | CDC<br>6400<br>0.170<br>0.008<br>0.002<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.005<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.003<br>0.0 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |                                                                          | Branche                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

TTTTT

Distribution of 5 Consecutive Executions (Conditional Branches)

Table 14

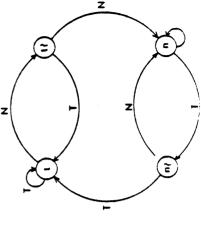

#### V. Branch Prediction

A number of the solutions to the branch problem, as discussed in section II, attempt to predict whether a branch will be taken or not. The general problem can be stated as: what is the value of F(x1,x2,...) where F is the probability that a branch is taken, and x1, x2, ... are parameters on which F may be reasonably conditioned. If F(x1,x2,...) > .5, then we predict that a branch will occur, and conversely. (We note that if the costs of errors of commission are not equal to errors of omission, then the best figure for deciding to predict a branch may not be equal to .5. We discuss this issue below in section VI.A). Of particular interest is x1= operation code, and x2= past execution history of this branch. It is possible to continue with other factors (for x3, x4, etc.) such as other dynamic branches that precede the current dynamic branch (and their execution behavior) [Angi82], other dynamic instructions that precede the current dynamic instruction, the source language of the program, the direction of the branch (e.g. forward/back [Smit81]), etc. For example, certain instruction sequences will generally indicate a taken branch; others will almost always fall through.