# **Systems for Machine Learning on Edge Devices**

Shishir Patil

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2024-1 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2024/EECS-2024-1.html

January 3, 2024

Copyright © 2024, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

Acknowledgement

To my Parents.

#### Systems for Machine Learning on Edge Devices

Ву

Shishir Girishkumar Patil

A thesis submitted in partial satisfaction of the requirements for the degree of

Master of Science

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Joseph Edgar Gonzalez, Chair Professor Prabal Dutta

Fall 2023

| The thesis of Shishir Girishkumar Patil, titled Systems for M is approved: | fachine Learning | g on Edge Devices, |

|----------------------------------------------------------------------------|------------------|--------------------|

|                                                                            |                  |                    |

|                                                                            |                  |                    |

|                                                                            |                  |                    |

|                                                                            |                  |                    |

| Chair Joseph E. Wongdung                                                   | Date             | 12/8/2023          |

| Prabal K Duttz                                                             | Date             | 12/7/2023          |

University of California, Berkeley

## Systems for Machine Learning on Edge Devices

Copyright 2023 by Shishir Girishkumar Patil

#### Abstract

Systems for Machine Learning on Edge Devices

by

Shishir Girishkumar Patil

Master of Science in Computer Science

University of California, Berkeley

Professor Joseph Edgar Gonzalez, Chair

Modern edge applications increasingly rely on Machine Learning (ML) based predictions. ML models deployed in the real world rapidly degrade in quality due to the evolution of data and our interpretation of data with time. Cloud applications combat model staleness by retraining models frequently. However, this is challenging on Edge devices such as smartphones and wearables, since they are characterized by memory and energy constraints, while the ML models continue to grow bigger. To overcome this, we propose two complementary systems POET and Minerva.

POET is an algorithm designed to facilitate the training of large neural networks on memory-scarce, battery-operated edge devices. It optimizes the integrated search spaces of rematerialization and paging, two techniques that significantly reduce the memory requirements of backpropagation. By formulating a mixed-integer linear program (MILP), POET achieves energy-optimal training within given memory and runtime constraints. This approach not only allows for training substantially larger models on embedded devices but also enhances energy efficiency without compromising the mathematical correctness of backpropagation.

Complementing POET, Minerva offers an end-to-end ML model update system specifically tailored for microcontroller-based devices. At its core is a novel system abstraction known as capsules, which facilitates efficient and flexible ML model updates without necessitating disruptive full device firmware updates (DFUs). These capsules exploit the pure function nature of ML model inference, overcoming the challenges typically associated with updating parts of a running program. Recognizing the absence of ground-truth labels, Minerva presents a novel technique to evaluate deployed models. Minerva's efficient updates and the ability to shadow-test enable a wide array of embedded devices to receive regular model updates.

Together, POET enables training models locally, and in those scenarios where training requires the cloud, Minerva enables efficient deployment and testing thereby opening up newer domains of computing to exploit ML models on the edge.

To my Parents.

# Contents

| $\mathbf{C}$     | ontents                                                                                                       | ii                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Li               | ist of Figures                                                                                                | iii                                                                                    |

| Li               | ist of Tables                                                                                                 | v                                                                                      |

| 1                | Introduction                                                                                                  | 1                                                                                      |

| 3                | POET: Training Neural Networks on Tiny Devices with Integrated Rematerialization and Paging  2.1 Introduction | 3<br>3<br>5<br>6<br>7<br>8<br>12<br>15<br>20<br>23<br>26<br>30<br>34<br>40<br>41<br>42 |

| 4                | Conclusion                                                                                                    | 43                                                                                     |

| $\mathbf{B}^{i}$ | ibliography                                                                                                   | 44                                                                                     |

# List of Figures

| 2.1 | POET optimizes state-of-the-art ML models for training on Edge devices. Operators of the ML model are profiled on target edge device to obtain fine-grained                                                                                     |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | profiles. POET adopts an integrated rematerialization and paging to produce an energy-optimal training schedule                                                                                                                                 | ,  |

| 2.2 | Rematerialization and paging are complementary. This plot visualizes the execu-                                                                                                                                                                 | 4  |

|     | tion schedule for an eight layer neural network. We represent logical timesteps<br>in increasing order on the y-axis while different layers are represented by the                                                                              |    |

|     | x-axis. Layers 2 and 3 are cheap-to-compute operators and therefore can be rematerialized at low cost. However, layers 5 and 6 are compute intensive so it is                                                                                   |    |

|     | more energy-efficient to page them to secondary flash storage                                                                                                                                                                                   | 17 |

| 2.3 | POET consumes less energy across diverse models and devices: We                                                                                                                                                                                 |    |

|     | profile the energy usage of each method relative to a full-memory configuration as                                                                                                                                                              |    |

|     | the device's available memory capacity shrinks. For ResNet-18 (top row), VGG                                                                                                                                                                    |    |

|     | (middle row) and BERT (bottom), POET outperforms competitive methods in                                                                                                                                                                         |    |

|     | most configurations. When training ResNet-18 on the TX2, POET consumes up to 35% less energy than DTR while discovering solutions at tighter memory                                                                                             |    |

|     | budgets                                                                                                                                                                                                                                         | 18 |

| 2.4 | Both rematerialization and paging are necessary for low-energy sched-                                                                                                                                                                           | 10 |

|     | ules with limited memory: We compare ablations of POET on VGG for CIFAR-10 and find that both rematerialization and paging are required to achieve                                                                                              |    |

|     | low-energy solutions at limited memory budgets across all runtime constraint                                                                                                                                                                    |    |

|     | values                                                                                                                                                                                                                                          | 19 |

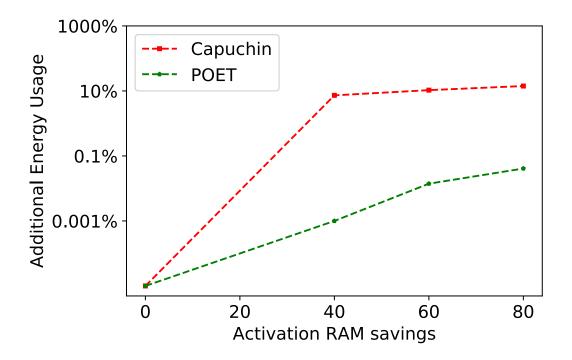

| 2.5 | Optimal integrated rematerialization and paging outperforms Capuchin                                                                                                                                                                            |    |

|     | (log scale): POET incurs 73% to 140% less energy overhead relative to a full-                                                                                                                                                                   |    |

|     | memory baseline by rematerializing earlier alongside paging. Capuchin strongly                                                                                                                                                                  |    |

|     | prefers paging before falling-back on rematerializing activations which makes it sub-optimal                                                                                                                                                    | 19 |

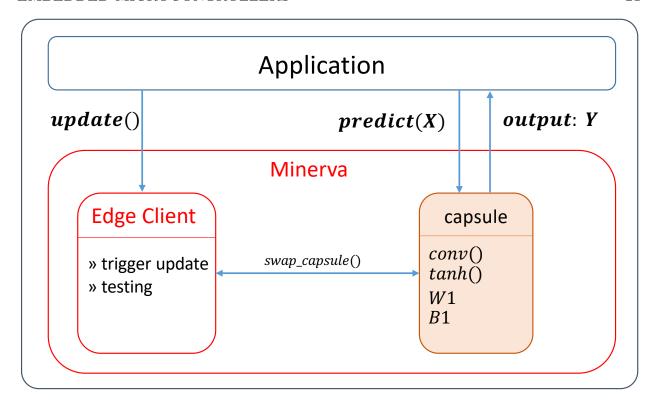

| 3.1 | Minerva explores an user-space library design that interposes between ML models and rest of the application. The operators (code) and weights are stored in self-contained and isolated capsules enabling rapid update of ML models transparent |    |

|     | to the application logic.                                                                                                                                                                                                                       | 21 |

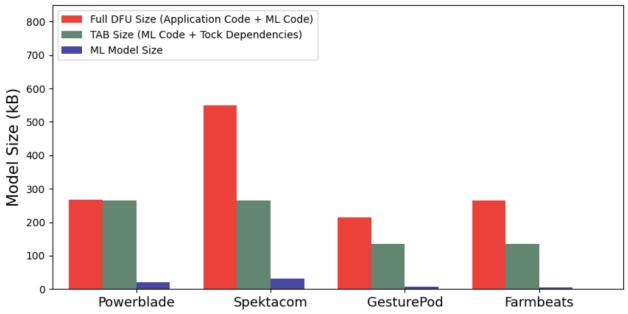

| 3.2 | Comparison of machine learning model size to full DFU size and TAB size (Tock     |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | Application Binary, a compiled application to be loaded onto a board with Tock    |    |

|     | OS) for several edge applications. ML model size (blue) includes ML operators     |    |

|     | and weights. TAB Size includes the ML model size and Tock support modules.        |    |

|     | The full DFU size (red) includes ML model size along with application logic, and  |    |

|     | networking modules. Unlike the cloud setting, machine learning model sizes are    |    |

|     | only a fraction of the total edge application size                                | 25 |

| 3.3 | Changes to source-code required on the Edge device. Only two lines are necessary  |    |

|     | to support - one to include the library, and one to trigger the swap              | 30 |

| 3.4 | Changes to ML training source-code required to interface with Minerva. Only the   |    |

|     | four additional lines are necessary to interface Minerva with Tensorflow/PyTorch, |    |

|     | while the rest of the source-code remains unchanged                               | 33 |

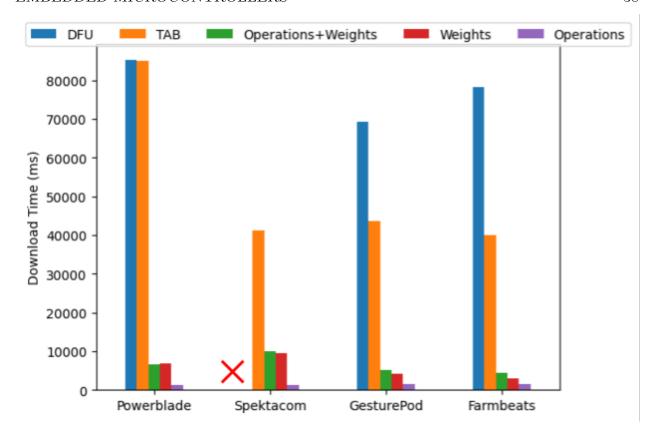

| 3.5 | Time taken to Download Update. Downloading the full DFU and TAB [48] far out-     |    |

|     | weigh the time taken to download Minerva updates, shown in green {ops+weights},   |    |

|     | red {weights}, and purple {ops}. Due to the application size, a DFU is not even   |    |

|     | possible for Spektacom!                                                           | 38 |

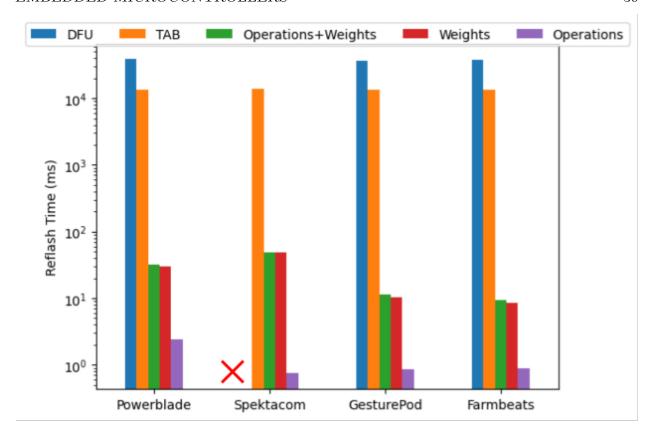

| 3.6 | Time taken to re-flash update. Notice that this is a log-linear graph. Blue       |    |

|     | represents reflashing the entire application binary as part of a DFU, orange      |    |

|     | represents Tockloader re-installing the TAB, and green, red, and purple represent |    |

|     | Minerva updates of just the ML model {operators (ops) + weights}, {weights},      |    |

|     | and {operators} respectively                                                      | 39 |

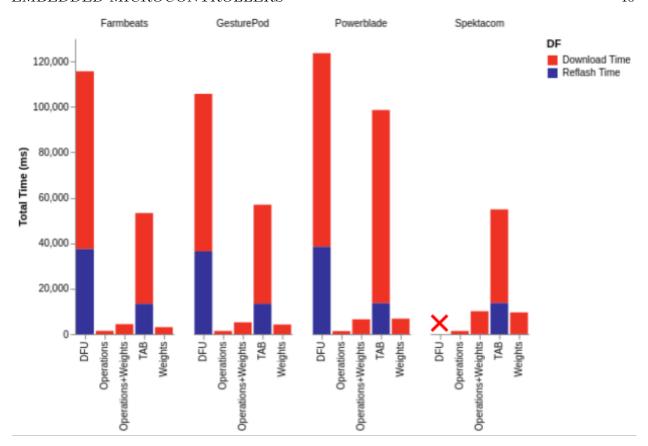

| 3.7 | Time taken for complete update. This graph combines download time with reflash    |    |

|     | time. Full DFUs (leftmost bar of each cluster) and TAB re-installs (rightmost bar |    |

|     | of each cluster) split time between downloading the update and re-flashing the    |    |

|     | binary. Minerva update times, on the other hand, are dominated by time taken      |    |

|     | to download the update. Note that the re-flash time for Minerva updates, shown    |    |

|     | in blue, are on the order of tens of milliseconds and thus not visible            | 40 |

# List of Tables

| 4.1 | Comparison of baseline methods under power, compute, memory and generality         |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | metrics. POET satisfies all criteria, enabling end-to-end training on the edge     | (   |

| 2.2 | We evaluate a wide variety of battery-powered edge devices. All devices have at    |     |

|     | least 32GB of flash memory via an SD card or flash to enable paging of activations |     |

|     | or tensors. FPU is floating-point unit.                                            | 13  |

| 2.3 | POET's MILP formulation lowers peak memory consumption by 8.3% and im-             |     |

|     | proves throughput by 13% compared to POFO [3] on Nvidia's Jetson TX2 edge          |     |

|     | device                                                                             | 14  |

|     | device                                                                             | 17  |

| 3.1 | Microbenchmarks for a capsule update (milliseconds). Hashing the capsule far       |     |

|     | outweights the time taken to overwrite the capsule by two orders of magnitude.     |     |

|     | This suggests that manipulation of the data to provide security and integrity      |     |

|     | guarantees dominate the time taken to perform the capsule update                   | 36  |

| 3.2 | Microbenchmarks for full DFU (milliseconds). Downloading the update and            |     |

| 0.2 | reflashing the application occupy on average 94% of the time taken to perform      |     |

|     | the DFU. This suggests that reducing the size of data needing to be downloaded     |     |

|     | and reflashed will speed up model updates                                          | 36  |

| 9 9 |                                                                                    | 30  |

| 3.3 | Microbenchmarks for Tockloader application install (milliseconds). The time        |     |

|     | taken to erase the post-user space flash page is comparable to the application     | 0.5 |

|     | re-flash time itself.                                                              | 37  |

| 3.4 | Memory footprint (KB). Full Device Firmware Updates are approximately 30×          |     |

|     | machine learning model sizes                                                       | 37  |

# Chapter 1

## Introduction

Deep learning has revolutionized edge computing, with models now widely deployed for inference on edge devices such as smartphones and embedded platforms. However, training these models is still predominantly centralized, typically occurring on large cloud servers equipped with high-throughput accelerators like GPUs, TPUs, etc. This centralized training model necessitates the transfer of sensitive data from edge devices to the cloud, compromising user privacy and incurring additional data movement costs in network bandwidth and energy. To counter these issues, on-device training methods like federated learning have emerged, allowing for local training updates without consolidating data to the cloud, as seen in applications like Google Gboard and iPhone's Automatic Speech Recognition (ASR).

Despite these advancements, current on-device training methods struggle to support state-of-the-art models such as large language models (LLMs) due to the limited device memory insufficient for storing activations for backpropagation. To address this, prior work has suggested strategies like paging to auxiliary memory and rematerialization to reduce memory footprint, but these often lead to increased total energy consumption. Our work introduces POET (Power Optimal Edge Training) [57], a novel algorithm that optimally combines paging and rematerialization, scaling effective memory capacity with minimal energy overhead. POET reframes edge training as an optimization problem, enabling the training of sophisticated models like BERT on mobile-class edge devices. This is achieved by formulating an integer linear program (ILP) that discovers optimal schedules on weather to retain in main-memory, page to secondary storage, or rematerialize each layer of a neural network resulting in minimal energy consumption. POET also strictly adheres to application specified memory and runtime constraints to accommodate training during device idle times. Unlike sparsification, quantization, Neural Architecture Search (NAS) and other approximation techniques, POET is designed to work with existing architectures without approximations.

While training locally enables devices to keep up with personalized experiences, often ML models need to be updated centrally. This could be for many reasons such as access to a new dataset previously not available, the functionality of the model changed, etc. In such scenarios, it is critical to have a efficient mechanism to allow these ML models trained on the cloud to be deployed on edge devices, where they are invoked for inference.

Updating ML models on edge devices, especially microcontroller-based (MCU) applications is challenging due to their limited capabilities. Traditional model updates through device firmware updates (DFUs) are bandwidth-intensive and inflexible, often requiring a system-reboot and thereby losing application state. To overcome these limitations, we propose Minerva, an efficient model update system for MCU-based edge devices. Minerva leverages a novel system abstraction called capsules, enabling efficient, state-preserving, and low-bandwidth transparent updates for ML models. Capsules exploit the pure function nature of ML models, allowing updates without the need for reboots. This system dramatically reduces update times compared to standard DFUs and integrates seamlessly with existing ML platforms.

Together, POET and Minerva present an exhaustive paradigm for dealing with the challenges of deploying and maintaining ML models on edge devices. POET addresses the need for efficient on-device training, enabling large models to be trained on devices with stringent memory and energy constraints. Minerva, on the other hand, focuses on the deployment stage of the ML lifecycle, offering a flexible and efficient solution for updating models on MCU-based devices. These systems mark a significant stride in making edge computing more adaptable, robust, and efficient.

# Chapter 2

# POET: Training Neural Networks on Tiny Devices with Integrated Rematerialization and Paging

#### 2.1 Introduction

Deep learning models are widely deployed for inference on edge devices like smartphones and embedded platforms. In contrast, training is still predominantly done on large cloud servers with high-throughput accelerators such as GPUs. The centralized cloud training model requires transmitting sensitive data from edge devices to the cloud such as photos and keystrokes, thereby sacrificing user privacy and incurring additional data movement costs.

To enable users to personalize their models without relinquishing privacy, on-device training methods such as federated learning [49] perform local training updates without the need to consolidate data to the cloud. These methods have been widely deployed to personalize keyboard suggestions in Google Gboard [25] and to improve Automatic Speech Recognition (ASR) on iPhones [61].

At the same time, current on-device training methods cannot support training modern architectures and large models. For example, Google Gboard fine-tunes a simple logistic regression model. Training larger models on edge devices is infeasible primarily due to the limited device memory which cannot store activations for backpropagation. A single training iteration for ResNet-50 [26] requires  $200 \times$  more memory than inference.

Prior work has proposed strategies including paging to auxiliary memory [62] and rematerialization [11, 33, 40] to reduce the memory footprint of training in the cloud. However, these methods result in a significant increase in total energy consumption. The data transfers associated with paging methods often require more energy than recomputing the data. Alternatively, rematerialization increases energy consumption at a rate of  $O(n^2)$  as the memory budget shrinks.

In this work, we show that paging and rematerialization are highly complementary. By

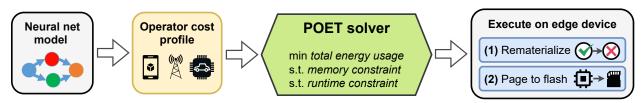

Figure 2.1: POET optimizes state-of-the-art ML models for training on Edge devices. Operators of the ML model are profiled on target edge device to obtain fine-grained profiles. POET adopts an integrated rematerialization and paging to produce an energy-optimal training schedule.

carefully rematerializing cheap operations while paging results of expensive operations to auxiliary memory such as a flash or an SD card, we can scale effective memory capacity with minimal energy overhead. By combining these two methods, we demonstrate it is possible to train models like BERT on mobile-class edge devices. By framing edge training as an optimization problem, we discover optimal schedules with provably minimal energy consumption at a given memory budget. While the focus of this thesis is edge deployemnts, the energy objective is increasingly becoming relevant even for cloud deployments [60].

We present POET (Private Optimal Energy Training), an algorithm for energy-optimal training of modern neural networks on memory-constrained edge devices (Fig 2.1). Given that it is prohibitively expensive to cache all activation tensors for backpropagation, POET optimally pages and rematerializes activations, thereby reducing memory consumption by up to 2x. We reformulate the edge training problem as an integer linear program (ILP) and find it is solved to optimality in under ten minutes by commodity solvers.

For models deployed on real-world edge devices, training happens when the edge device is relatively idle and spare compute cycles are available. For example, Google Gboard schedules model updates when the phone is put to charge. Hence POET also incorporates a hard training constraint. Given a memory constraint and the number of training epochs, POET generates solutions that also satisfy the given training deadline. POET transparently develops a comprehensive cost model by profiling the target hardware with the target network's operators. Finally, POET is mathematically value preserving (i.e, it makes no approximations), and it works for existing architectures out-of-the-box.

The novel contributions of this work include:

- 1. A formulation of an integer linear program to find the **energy-optimal** schedule to train modern deep neural networks **with a)** memory and **b)** runtime as hard constraints.

- 2. A unified algorithm for hybrid activation recomputation and paging.

- 3. The first demonstration of how to train ResNet-18 and BERT on tiny Cortex M class devices with memory and timing constraints.

#### 2.2 Related Work

Scarcity of compute and memory is one of the largest constraint for machine learning on edge devices. Large models with state-of-the-art performance have largely been exorbitantly expensive for edge devices. The research community has predominantly focused on addressing *inference* on edge devices via methods like efficient DNN architecture [31, 70], quantization [17] or pruning [5].

Instead, we aim to make training large neural networks feasible on tiny edge devices. While compute is the limiting resource for inference on the edge, limited memory capacity constraints prevent training large models on the edge. Training via vanilla backpropagation requires caching the output of all intermediate layers (activations). We categorize methods to reduce memory usage of training as activation (1) compression, (2) rematerialization, and (3) paging. We then discuss prior work in energy-efficient training.

Activation quantization: ActNN [9], Weighted-Entropy-Based Quantization [56], and others have proposed techniques to quantize activations while performing full-precision multiply-accumulates (MACs). However, these techniques compromise accuracy and correctness. Moreover, poor hardware support for quantized operations under 8 bits limits the practical savings of these techniques. We do not consider methods for pruning during training like The Lottery Ticket Hypothesis [19] as they do not reduce the size of activations.

Rematerialization: Rematerialization discards activations in the forward pass and recomputes those values during gradient calculation. Chen et. al (2016) [11] proposed a simple and widely used algorithm for rematerialization where every  $O(\sqrt{n})$  layer is retained for the backward pass. Griewank & Walther (2000) [22] propose an optimal algorithm for rematerialization on unit-cost linear auto-diff graphs. However, they force the strong assumption that models have uniform compute requirements across layers. Checkmate [33] identifies the optimal rematerialization schedule for arbitrary static graphs. Monet [67] extends Checkmate with operator implementation selection, but this is orthogonal to our work's scheduling problem. Dynamic Tensor Rematerialization (DTR) [40] finds an approximation that is near-optimal for common computer-vision models. Our work addresses the following limitations of Checkmate: (1) Checkmate does not consider energy nor latency as a constraint and (2) Checkmate does not page activations to secondary memory. POET is the first work that demonstrates provably optimal integrated paging and rematerialization.

Paging: SwapAdvisor [28] and DeepSpeed [65] page activations off a memory-scarce GPU to the CPU when out of memory. However, we find paging is very energy-intensive and is often less efficient than rematerialization. Capuchin [62] uses the Memory Saving Per Second (MSPS) heuristic to decide what to page. Only if paging is insufficient will Capuchin rematerialize activations thereby making it sub-optimal as demonstrated in Sec 2.6. POFO [3] formulates finding finding the optimal sequence combining rematerialization and paging as a dynamic programming problem. POFO makes many assumptions that limit generality: POFO only supports chain (linear) model graphs while we support arbitrary graphs such as BERT (Fig 2.3). POFO limits layers to a single rematerialization or page operation while POET can remat/page layers repeatedly. POFO forces all page-out operations to occur prior

| Method                             | General<br>Graphs | Compute<br>Aware | v         | Power<br>Aware |

|------------------------------------|-------------------|------------------|-----------|----------------|

| Checkpoint all (PyTorch)           |                   | ×                | ×         | ×              |

| Griewank & Walther (2000) [22]     | ×                 | ×                | ×         | ×              |

| Chen et. al (2016) $\sqrt{n}$ [11] | X                 | ×                | ×         | ×              |

| Chen et. al (2016) greedy [11]     | ×                 | ×                | $\sim$    | ×              |

| Checkmate [33]                     |                   |                  |           | ×              |

| POFO [3]                           | ×                 | $\sqrt{}$        | $\sqrt{}$ | ×              |

| DTR [40]                           | $\sqrt{}$         | $\sqrt{}$        | $\sqrt{}$ | ×              |

| POET (ours)                        |                   |                  |           |                |

Table 2.1: Comparison of baseline methods under power, compute, memory and generality metrics. POET satisfies all criteria, enabling end-to-end training on the edge.

to calculating the loss while we have no such restriction. And finally, while POFO assumes paging is asynchronous (e.g., CUDA) but this is not universally true for the edge devices we evaluate. Notice that POET is not only optimizing a different metric (energy vis-a-vis time) but a) adhere's to strict timing guarantees and b) is *provably optimal*.

Energy-efficient training: We are not the first to consider energy-optimal training. Prior work on energy-optimal training for the edge either a) required the design of new architectures [7, 70], or proposed b) new techniques of training by dropping activations, updating only select layers of the network, or c) used a different optimizer [76]. Compared to these techniques, POET is a) mathematically value preserving (makes no approximations, or modifications), and b) works for existing and new architectures out-of-the-box.

### 2.3 Background

In response to the growing edge machine learning applications, the community has developed systems to enable machine learning on edge devices. EdgeML [15], CoreML [36] and TensorFlow Lite [44] from Google are all efforts to meet this demand.

However, each of these efforts is application-specific and proposes new algorithms or optimizations to address the computational and memory requirements for machine learning inference on the edge [43]. While inference is already commonly deployed on edge devices, training remains ad-hoc and infeasible for large models.

Training on the edge is critical for privacy, cost, and connectivity. First, due to privacy concerns, many edge applications cannot transmit data to the cloud. Second, the energy consumed by bulk data transmission can significantly reduce battery life [47].

Third, applications such as ocean sensing and communication [34], and those deployed in farms [73] are designed for offline operations – with no access to the internet.

Our objective of optimizing for energy is a non-trivial contribution. On edge devices, the energy objective can oftentimes conflict with the objective of running to completion. For example, on a given platform, rematerializing might consume lower energy, but paging might be quicker. This is because, on edge devices, it is common practise to turn-off/duty-cycle components that are not utilized (e.g., SD card, DMA, etc.) The energy profile may vary depending on the size of the tensor, and if the PCIe/DMA/SPI/I2C memory bus needs to be activated, etc. Exploiting this enables POET to find the most energy-efficient schedule which would not have been possible had we not optimized for energy.

While definitions differ on which devices are included in "the edge" (e.g., mobile phones, routers, gateways, or even self-driving cars). In the context of this chapter, the edge refers to mobile phones and microcontrollers (Table 2.2). These devices are characterized by limited memory (ranging from KBs to a few GBs) and are commonly battery-powered ( $\sim$  few hundred mAh) for real-world deployment. Further, in our research we found that it is quite common for these edge devices to be augmented with an off-chip secondary storage such as a flash or an SD card as seen in [73, 34, 58]. This presents us with an opportunity to exploit the off-chip memory for paging.

## 2.4 Integrated paging and rematerialization

Rematerialization and paging are two techniques to lower the memory consumption of large, state-of-the-art ML models. In rematerialization, an activation tensor is deleted as soon as they are no longer needed, most often, during a forward pass. This frees up precious memory that can be used to store the activations of the following layers. When the deleted tensor is needed again, for example, to compute gradients during backpropagation, it is recomputed from the other dependent activations as dictated by the lineage. Paging, also known as offloading, is a complementary technique to reduce memory. In paging, an activation tensor that is not immediately needed is paged-out from the primary memory to a secondary memory such as a flash or an SD card. When the tensor is needed again, it is paged back in.

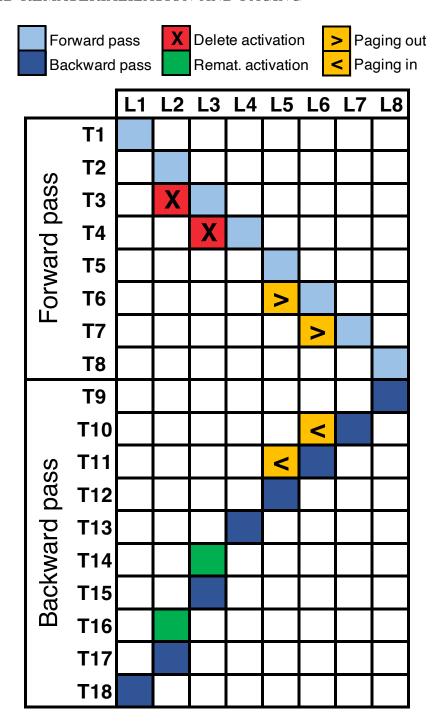

This is best understood with the representative neural-network training timeline from Figure 2.2. Along the X-axis, each cell corresponds to a single layer of an eight-layered, linear, neural-network. The Y-axis represents the logical timesteps over one epoch. An occupied cell indicates that an operation (forward/backward pass computation, rematerialization, or paging) is executed at the corresponding timestep. For example, we can see that the activation for Layer 1 (L1) is computed at the first timestep (T1). At timestep T2 and T3, the activations of L2 and L3 are computed respectively. Suppose layers L2 and L3 happen to be memory-intensive but cheap-to-compute operators, such as non-linearities (tanH, ReLU, etc.) then rematerialization becomes the optimal choice. We can delete the activations ({T3, L2}, {T4, L3}) to free up memory, and when these activations are needed during backward propagation we can rematerialize them ({T14, L3}, {T16, L2}).

Suppose layers L5 and L6 are compute-intensive operators such as convolutions, dense matrix-multiplication, etc. For such operations, rematerializing the activations would lead to an increase in run-time and energy and is sub-optimal. For these layers, it is optimal to page-out the activation tensor to secondary storage ({T6,L5}, {T7, L6}), and page-in when they are needed ({T10,L6}, {T11, L5}).

One major advantage of paging is that depending the memory bus utilization, it can be pipelined to hide latency. This is because modern systems have DMA (Direct Memory Access) which can move the activation tensor from the secondary storage to the primary memory while the compute engine is running in parallel. For example, at timestep T7, we are both paging L6 out and computing L7. However, rematerialization is compute-intensive, cannot be parallelized. This leads to an increase in run-time. For example, we have to dedicate timestep T14 to recompute L3 thereby delaying the rest of the backward pass execution.

## 2.5 POET: Private Optimal Energy Training

We introduce Private Optimal Energy Training (POET), a graph-level compiler for deep neural networks that rewrites training DAGs for large models to fit within the memory constraints of edge devices while remaining energy-efficient. POET is hardware-aware and first traces the execution of the forward and backward pass with associate memory allocation requests, runtime, and per-operation memory and energy consumption. This fine-grained profiling for each workload happens only once for a given hardware, is automated, cheap, and provides the most accurate cost model for POET. POET then generates a Mixed Integer Linear Programming (MILP) which can be efficiently solved. The POET optimizer searches for an efficient rematerialization and paging schedule that minimizes end-to-end energy consumption subject to memory constraints. The resulting schedule is then used to generate a new DAG to execute on the edge device. While the MILP is solved on commodity hardware, the generated schedule shipped to the edge device is only a few hundred bytes, making it highly memory efficient.

Rematerialization is most efficient for operations that are cheap-to-compute yet memory-intensive. These operations can be recalculated with low energy overhead. Paging, however, is best suited to compute-intensive operations where rematerialization would otherwise incur significant energy overhead. POET jointly considers both rematerialization and paging in an integrated search space.

Without a minimum training throughput limit, it is possible that the energy optimal strategy is also far too slow to train in practical applications. In reality, training needs to run while the device is idle where spare compute cycles are available. For example, Google Android schedules ML model updates when the phone is charging. To maintain high training throughputs, the POET optimizer can maintain a minimum training throughput to ensure that training completes during downtime.

Given a memory budget  $\mu_{RAM}$  and a training time budget  $\mu_{deadline}$ , POET finds an energy optimal schedule by choosing to either a) rematerialize or b) page the tensors to/from

secondary storage such as an SD card. Our method scales to complex, realistic architectures and is *hardware-aware* through the use of microcontroller-specific, profile-based cost models. We jointly consider integrated rematerialization and paging, to optimize for an energy objective rather than the runtime, and implement a minimum throughput constraint.

$$\begin{aligned} & \text{arg min} & \sum_{T} \left[ R\Phi_{compute} + M_{in}\Phi_{pagein} + M_{out}\Phi_{pageout} \right]_{T} \\ & \text{subject to} & R_{t,i} + S_{t,i}^{RAM} \geq R_{t,j} & \forall t \in V \ \forall (v_{i},v_{j}) \in E \\ & R_{t-1,i} + S_{t-1,i}^{RAM} + M_{t-1,i}^{in} \geq S_{t,i}^{RAM} & \forall k \in K \ \forall t \geq 2 \ \forall i \\ & S_{t-1,i}^{AUX} + M_{t-1,i}^{out} \geq S_{t,i}^{AUX} & \forall t \geq 2 \ \forall i \\ & S_{t,i}^{AUX} \geq M_{t,i}^{in} & \forall k \in K \ \forall t \geq 2 \ \forall i \\ & S_{t,i}^{RAM} \geq M_{t,i}^{out} & \forall k \in K \ \forall t \geq 2 \ \forall i \\ & S_{t,i}^{RAM} \leq \mu_{RAM} & \forall t \in V \ \forall i \in V \\ & \sum_{T} [R\Psi_{compute}]_{T} \leq \mu_{deadline} \\ & S_{1,i} = 0 & \forall i \in V \\ & R_{v,v} = 1 & \forall v \in V \end{aligned}$$

$$R, S_{SD}, S_{RAM}, M_{in}, M_{out} \in \{0, 1\}^{T \times T}$$

**Algorithm 1: POET optimizer**: The complete memory constrained MILP with O(|V||E|) variables and constraints.

Assumptions: We assume operations execute sequentially on edge devices without inter-operator parallelism. Moreover, we assume parameters and gradients are stored in a contiguous memory region without paging. Unlike prior work in rematerialization [11, 40], we do not limit rematerialization to occur once. We assume auxiliary storage (e.g., flash/SD card) is available. However, if auxiliary storage is not available, the POET optimizer will fall back to only performing rematerialization.

### **Optimal Rematerialization**

We introduce the formulation of the rematerialization problem below. Given a directed acyclic dataflow graph G = (V, E) with n nodes, a topological ordering  $\{v_1, \ldots, v_n\}$  is computed which constrains execution to that order of instructions. Two key decision variables are introduced: (1)  $R \in \{0, 1\}^{n \times n}$  where  $r_{t,i}$  represents the decision to (re)materialize an operation  $v_i$  at timestep t and (2)  $S \in \{0, 1\}^{n \times n}$  where  $s_{t,i}$  represents whether the result of an operation  $v_i$  is resident in memory at timestep t.

From the rematerialization matrix R, and the storage matrix S, we define a series of constraints to maintain graph dependencies. All arguments for an operation j must be resident

in memory prior to running that operation, yielding constraint  $R_{t,i} + S_{t,i} \ge R_{t,j} \ \forall (i,j) \in E \ \forall t \in \{1,\ldots,n\}$ . Similarly, the result of an operation is only resident in memory in one of the two cases: a) if it was already resident in memory before, or b) if it was (re)materialized  $(S_{t,i} \le S_{t-1,i} + R_{t-1,i} \ \forall i \in V \ \forall t \in \{1,\ldots,n\})$ .

To adhere to the strict constraints on the peak memory used during training, an intermediate variable  $U \in \mathbb{R}^{n \times n}$  is defined.  $U_{t,i}$  is the total memory used by the system during training at timestep t when evaluating operation i. By bounding the maximum value of  $U_{t,i} \ \forall i \in V \ \forall t \in \{1, \ldots, n\}$  to the user-specified memory limit  $\mu_{RAM}$ , we limit the total memory consumption during training.

#### Optimal integrated paging and rematerialization

While rematerialization can provide significant memory savings, it introduces significant energy consumption overheads from duplicate recomputations. Similarly, paging if done wrong will result in a wasteful shuffling of data between memories. Here, we formalize a joint search space for rematerialization and paging to enable the discovery of the energy-optimal hybrid schedule.

Like rematerialization, the discovery of the optimal paging schedule is a challenging combinatorial search problem. However, we find that independently solving for paging first, and then solving for rematerialization will not produce globally optimal solutions. As an example, consider a graph where the output depends on the result of two operations  $v_1$  and  $v_2$  where both nodes have equivalent memory costs but  $v_2$  is cheaper to evaluate. A paging strategy may evict  $v_2$  which would force rematerialization to recompute the more expensive  $v_1$  rather than  $v_2$ .

We represent a schedule as a series of nodes that are either being saved  $S^{RAM}$ , (re)computed R or paged from secondary storage  $S^{AUX}$ . To model when a node is copied from secondary storage to RAM, we introduce a variable  $M^{in} \in \{0,1\}^{n \times n}$  where  $M^{in}_{t,i}$  represents paging a tensor from secondary storage to RAM between timesteps t-1 and t. Similarly, we model page-out with  $M^{out}$ .

We now present the intuition behind adding the following constraints to the optimization problem in order to search over optimal schedules for paging and rematerialization:

- 1c For  $S_{t,i}^{RAM}$  to be in memory at time-step t, either compute  $R_{t,i}$  at timestep t, or retain  $S_{t,i}^{RAM}$  in memory from the previous timestep t-1, or page-in if  $S_{t-1,i}^{RAM}$  is resident on flash (at t-1).

- 1d Each node i can reside on flash  $S_{t,i}^{AUX}$ , either if it resided on flash at timestep t-1  $(S_{t-1,i}^{AUX})$ , or it was paged out at time-step t-1  $(M_{t-1,i}^{out})$ .

- 1e To page-in  $M_{t,i}^{in}$  at time-step t, it has to be resident on flash  $S_{t,i}^{AUX}$  at time-step t.

- 1f Each node i can reside in memory  $S_{t,i}^{RAM}$  at timestep t, only if it was paged out of flash  $(M_{t,i}^{out})$ .

1g Corresponds to ensuring latency constraints are met. The total time for all computations, including the rematerializations, should be less than the specified budget  $U_{deadline}$ .

Algorithm 1 defines the complete optimization problem.

#### Expressing an energy consumption objective

If we only consider rematerialization, then minimizing runtime will generally correlate with decreased energy usage. However, this is no longer true when considering paging; paging can be more energy-efficient than rematerializing a compute-intensive operation. To address this, we introduce a new objective function to the optimization problem that minimizes the combined energy consumption due to computation, page-in, and page-out.

When paging occurs on an edge device, the vast majority of energy consumed is due to powering-on the flash/SD block device. As this power is in addition to any power the CPU is consuming, the total power consumption is a linear combination of paging and CPU energy. We precompute each of these values, generally as the integral of the power of active components of the edge device integrated over the runtime of the operation.  $\Phi_{compute}$ ,  $\Phi_{pagein}$  and  $\Phi_{pageout}$  represent the energy consumed for each node for computing, paging in, and paging out respectively.

Therefore, the new objective function combining paging and rematerialization energy usage is:

$$\sum_{T} \left[ R\Phi_{compute} + M_{in}\Phi_{pagein} + M_{out}\Phi_{pageout} \right]_{T}$$

(2.2)

### Ensuring minimum training throughput

If we attempt to find the minimum energy schedule subject to only a memory constraint, the POET solver may select solutions with poor end-to-end training throughput. Ideally, training should occur in the downtime between interactive workloads on an edge device. To ensure this, we introduce a new constraint to the optimization problem that ensures schedules meet a minimum training throughput threshold. This constraint effectively trades off between energy consumption and training throughput.

To enforce a particular throughput, we compute a latency target. Via profiling, we capture  $\Psi_{compute}$  denoting the runtime of each operation. We then constrain total runtime with :

$$\sum_{T} [R\Psi_{compute}]_T \le \mu_{deadline} \tag{2.3}$$

### Paging latency hiding via transfer planner

POET outputs the DAG schedule in terms of which nodes of the graph (k) to rematerialize, and which to page-in  $(M_{t,k}^{in})$  or page-out  $(M_{t,k}^{out})$  at each time-step (t). Our Algorithm 2

```

Input: Graph G = (V, E), schedule R, M_{in}, M_{out} for t=1,...,|V| do

| for k=1,...,|V| do

| if M_t^{in} then

| | add %r = pagein v_k to P

| end

| if R_{t,k} then

| | add %r = compute v_k to P

| end

| if M_{t,k}^{out} then

| | add %r = pageout v_k to P

| end

| for i \in DEPS[k] \cup \{k\} do

| if M_{t,k}^{out} \vee FREE_{t,i,k} then

| | add deallocate %r to P

| end

| end

| end

| end

| end

| end

| Cutput: execution plan P = (v_1, ..., v_n)

| Algorithm 2: Training Graph Execution Plan

```

takes the ILP solves to generate and dictate the strategy that determines which tensors are resident-in-memory  $(S_{t,k}^{aux})$  at a fine-grained (operator) level.

We factor in the latency introduced by paging. As described in Section 2.6, POET is hardware-aware by profiling the latency per platform for paging activations to secondary storage. Fine-grained profiling helps in fine-tuning when to start paging, such that the activation tensors arrive just-in-time. We then modify the page-in  $(M_{t,k}^{in})$  and the page-out  $(M_{t,k}^{out})$  schedule to ensure there is no contention for the memory bus as the tensors are paged-in just-in-time. For example, if  $(M_{t,i}^{in})$  can contend with  $(M_{t,j}^{in})$ , then we schedule one of them to page-in at an earlier time  $(M_{t-1,i}^{in})$  and update the in-memory schedule  $(S_{t-1,i}^{aux})$  to account for the earlier paging-in. While this ensures the activations are paged in just-in-time, in parallel,  $(R_{t',j})$  informs the PyTorch DAG scheduler to deallocate the tensors that we have chosen to rematerialize  $(S_{t,k}^{aux})$  at a future timestep (t').

## 2.6 Evaluation

In our evaluation of POET we seek to answer three key questions. First, how much energy consumption does POET reduce across different models and platforms? Second, how does POET benefit from the hybrid paging and rematerialization strategy? Lastly, how does POET adapt to different runtime budgets?

| Device           | Clock              | RAM               | FPU?      |

|------------------|--------------------|-------------------|-----------|

| M0 (MKR1000)     | $48~\mathrm{MHz}$  | 32 KB             | ×         |

| M4 (nrf52840)    | $64~\mathrm{MHz}$  | $256~\mathrm{KB}$ | $\sqrt{}$ |

| A72 (RPi-4B+).   | $1.5~\mathrm{GHz}$ | 2  GB             | $\sqrt{}$ |

| A57 (Jetson TX2) | $2~\mathrm{GHz}$   | 8 GB              | $\sqrt{}$ |

Table 2.2: We evaluate a wide variety of battery-powered edge devices. All devices have at least 32GB of flash memory via an SD card or flash to enable paging of activations or tensors. FPU is floating-point unit.

#### Experimental setup

We evaluate POET on four distinct hardware devices listed in Table 2.2: the ARM Cortex M0 class MKR1000, ARM Cortex M4F class nrf52840, A72 class Raspberry Pi 4B+, and Nvidia Jetson TX2.

POET is fully hardware-aware and relies on fine-grained profiling. For example, on the Jetson-TX2 hardware we profile each operator along with its variations in dimensionality (e.g., conv2d with varying kernel-sizes, strides, padding, etc.) These fine-grained time, energy, and memory profiles then inform POET about the exact specifications. These devices test a diverse set of memory, compute, and power configurations. As POET is hardware and energy-aware, it takes device-specific characteristics into account.

We evaluate POET on VGG16 [68] and ResNet-18 [26] trained on the CIFAR-10 dataset as well as BERT [16]. In all of our baselines, we limit all MILP solves to no more than 10 min on commodity CPUs. Our experiments are with a batch-size of 1. We compare POET to work PyTorch's default scheduler, Chen et. al[11], Griewank & Walther[22], DTR [40], and Checkmate [33].

**Hyperparameters:** POET only decides on the optimal scheduling of nodes in the training graph and does *not* change the training routine (learning rate, optimizer, etc.). Hence, our system is robust to hyper-parameters.

Sensitivity to Batch-size: POET is mathematically preserving and can be easily scaled to arbitrary batch sizes without loss of generality. Of course, this is conditioned on the underlying device's memory capacity. It is possible that as batch size varies, the underlying operator implementation might change. POET, with its fine-grained profiling is robust to these changes and transparently adapts to artifacts.

# How much energy consumption does POET reduce across models and platforms?

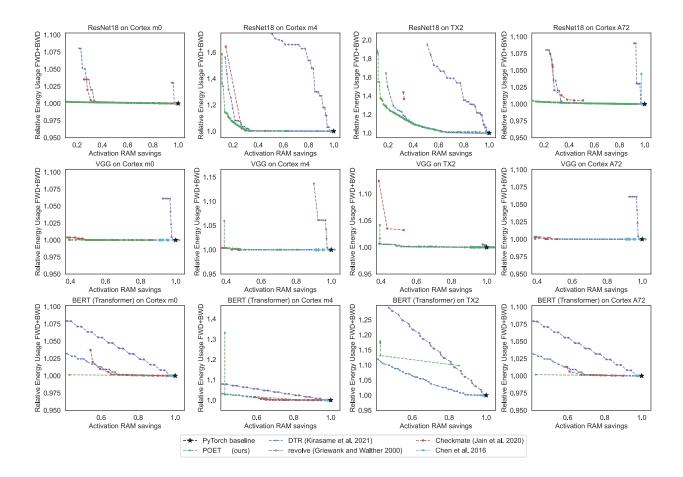

Figure 2.3 shows the energy consumed for a single epoch of training. Each column represents a unique hardware platform as defined in Table 2. We notice that across all platforms, POET

|         | ResNet-18 Training  |                             |  |

|---------|---------------------|-----------------------------|--|

|         | POET                | POFO (Beaumont et al. 2021) |  |

| Memory  | 285,873 kB          | 311,808 kB                  |  |

| Runtime | $82.36~\mathrm{ms}$ | 94.79  ms                   |  |

Table 2.3: POET's MILP formulation lowers peak memory consumption by 8.3% and improves throughput by 13% compared to POFO [3] on Nvidia's Jetson TX2 edge device

generates the most energy-optimal (Y-axis) schedule all the while reducing the peak memory consumed (X-axis) and adhering to the timing budget.

For the BERT model on the Cortex M4 and the TX2 platform, we noticed an interesting behavior: our ILP solves time-out. This is because we limit all solves to no more than 10 min. With a longer ILP solve budget (<30 min), POET can predictably find more optimal solutions. Further, notice that a) POET has an additional timing budget which none of the other baselines do, and b) all of our baselines are already mature. Checkmate [33] is provably optimal for rematerialization, while DTR [40] closely approximated Checkmate. Furthermore, POET tried to solve a much "harder" problem as its search space with rematerialization and paging together is larger.

# How does POET benefit from integrated rematerialization and paging?

We compare our joint optimal paging and rematerialization schedule with Capuchin which optimizes each with a heuristic. Capuchin will effectively page until no longer feasible and only then will it begin to rematerialize. Instead, POET begins rematerializing cheap operations like ReLU much earlier which yields considerable energy savings (up to 141% lower overhead).

In Figure 2.5, we benchmark POET and Capuchin when training ResNet-18 on the A72. As the RAM budget decreases (to the right), Capuchin consumes 73% to 141% more energy than a baseline with full memory. In comparison, POET incurs less than a 1% energy overhead. This trend holds for all architectures and platforms we tested.

In Table 2.3 we benchmark POET and POFO when training ResNet-18 on Nvidia's Jetson TX2. We find that POET finds an integrated rematerialization and paging schedule that lowers *peak memory consumption by 8.3%* and *improves throughput by 13%*. This showcases the benefit of POET's Mixed-integer linear programming (MILP) solver, which is able to optimize over a much larger search-space. While POFO only supports linear models, POET generalizes to non-linear models as demonstrated in Fig 2.3.

#### How does POET adapt to varying runtimes?

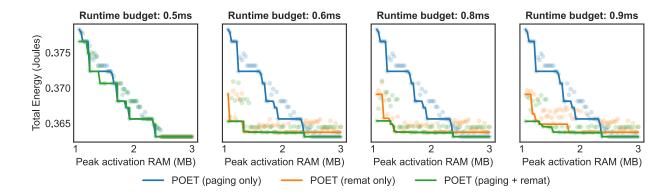

Figure 2.4 highlights the benefit of the integrated strategies that POET adopts across different timing constraints. The run-time budget refers to the total time available for one epoch of training naïvely (without paging or rematerialization). For each of the runtimes, we plot the total energy consumed if we were to restrict to either of a) paging or b) rematerialization only, and the c) integrated solution.

We find that rematerialization is energy-optimal compared to paging at higher (looser) timing budgets. This is reflected in the POET (paging+remat) green curve, closely tracking the POET (remat only) yellow curve at runtime budgets of 0.6 - 0.9 ms. However, at lower runtime budget (0.5 ms), paging is preferable as rematerialization strategies become infeasible. This is because, rematerialization is a compute intensive serial operation, however, our Algorithm 2 benefits from the ability to hide paging latencies by pipelining (see Section 2.6) to realize the tighter deadline bounds. POET's optimal, integrated solution consumes up to 40% lower energy compared to paging or rematerialization only solutions.

#### 2.7 Conclusion

Enabling large models to be trained on edge devices is important due to privacy constraints as well as offline operation. Edge devices deployed in the real-world are powered by tiny microcontrollers that are low-powered, and have limited memory (e.g. 32 KB). The low-power and limited memory, coupled with tight timing constraints imposed by real-time systems makes training on the edge challenging.

Our novel mixed-integer linear programming based Power Optimal Edge Training (POET) algorithm enables training on tiny chips with memory as low as 32 KB. Given a memory budget and a timing constraint, POET finds the most energy optimal schedule to train the model by choosing to either rematerialize or page the tensors to secondary storage.

Across a diverse set of models and devices, we discover low-power training schedules at less memory than baselines. POET enables new applications for privacy-preserving personalization of large models like BERT on tiny devices at the edge for the first time. Future directions include integrating activation compression as well as expanding POET's search space to paging parameters.

## Acknowledgement

We thank Prateek Jain, Charles Packer, Daniel Rothchild, Alex Smola, Pete Warden, and the anonymous reviewers whose insightful comments, and feedback helped improve the project. This research is supported by a NSF CISE Expeditions Award CCF-1730628, and gifts from Amazon Web Services, Ant Group, Ericsson, Facebook, Futurewei, Google, Intel, Microsoft, Scotiabank, and VMware. This work was supported in part by the CONIX Research Center, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA.

Figure 2.2: Rematerialization and paging are complementary. This plot visualizes the execution schedule for an eight layer neural network. We represent logical timesteps in increasing order on the y-axis while different layers are represented by the x-axis. Layers 2 and 3 are cheap-to-compute operators and therefore can be rematerialized at low cost. However, layers 5 and 6 are compute intensive so it is more energy-efficient to page them to secondary flash storage.

Figure 2.3: **POET** consumes less energy across diverse models and devices: We profile the energy usage of each method relative to a full-memory configuration as the device's available memory capacity shrinks. For ResNet-18 (top row), VGG (middle row) and BERT (bottom), POET outperforms competitive methods in most configurations. When training ResNet-18 on the TX2, POET consumes up to 35% less energy than DTR while discovering solutions at tighter memory budgets.

Figure 2.4: Both rematerialization and paging are necessary for low-energy schedules with limited memory: We compare ablations of POET on VGG for CIFAR-10 and find that both rematerialization and paging are required to achieve low-energy solutions at limited memory budgets across all runtime constraint values.

Figure 2.5: Optimal integrated rematerialization and paging outperforms Capuchin (log scale): POET incurs 73% to 140% less energy overhead relative to a full-memory baseline by rematerializing earlier alongside paging. Capuchin strongly prefers paging before falling-back on rematerializing activations which makes it sub-optimal.

# Chapter 3

# Minerva: Efficient ML Model Updates for Deeply Embedded Microcontrollers

### 3.1 Introduction

Frequent updates of machine learning (ML) models are necessary to respond to changes in the environment and data, the arrival of new datasets, user feedback, and rapid innovation in model design [20, 71]. ML model updates include not only data (e.g., the weights of a neural network) but also model architecture and the associated code of its operators, which may change in an update. This cycle of feedback, re-training, and re-deployment continues for the lifetime of a deployment.

At the same time, ML applications that have historically resided in the cloud are moving closer to the edge. In this chapter, we focus on the extreme edge, consisting of embedded microcontrollers (MCUs) built around Cortex-M family of ARM CPUs. For example, Farmbeats [73] has used microcontrollers in sensor boxes for precision agriculture. Recent efforts have looked at designing models for the constraints of the edge [73, 58, 74]. However, updated models that are trained centrally, e.g. in the cloud, must then be deployed on edge devices to provide better predictions for the embedded applications they support. In this chapter, we focus on this critical deployment stage of the ML lifecycle for edge devices.

On server-class systems, the model is served from a separate process or microservice using Remote Procedure Calls (RPCs) [30, 21]. This allows the model executable to be updated independently of the rest of the application. Such decoupling of the application from the model also provides *flexibility*—it is easy to test the new model on samples of traffic and roll back changes to earlier models if necessary, permitting *AB testing* and *acceptance testing*.

Unfortunately, this multi-process approach does not work on MCU-based edge devices. The reason is that MCUs lack MMUs and have only *kilobytes* of RAM, making them ill-suited to running full-fledged operating systems like Linux [64, 37, 50, 54]. On MCUs, the application and system share an address space and are typically linked into a single logical program called the *image*. While possible, it is difficult to update only part of the image, because the layout

Figure 3.1: Minerva explores an user-space library design that interposes between ML models and rest of the application. The operators (code) and weights are stored in self-contained and isolated capsules enabling rapid update of ML models transparent to the application logic.

of code and data (e.g., the lengths of functions, etc.) may change with each update. This would break any jumps, branches, and function calls into the updated part of the image. And, unless the device is rebooted, any data structures and pointers in RAM must be transformed for use with the updated code and data.

Instead, ML model updates on MCU-based devices are typically carried out through device firmware updates (DFUs), in which an entire new image is installed on the device. DFUs are a natural solution for classical use cases, such as infrequent reprogramming of a sensor network to a new application or patching a vulnerability [dfu-vulnerability]. But DFUs have several downsides, exacerbated in the context of model updates. First, although only the model is updated, DFUs download a full program image, which is bandwidth-intensive, especially over low-rate links like NB-IoT, LoRA, or even satellites. Second, each DFU requires a reboot, losing application and system state, which is costly because model updates may be frequent and it may take time to recreate precious state. Third, DFUs are less flexible than the process-based approach, increasing friction and overhead for local model testing and rollback. Fourth, it restricts software to only half of the available memory, to have space to download an update before switching to it. In practice, edge devices update models less

frequently or not at all due to these downsides [73, 8].

In this context, we study how to enable efficient model updates for edge devices. We propose a system, Minerva, that does so with minimal application changes, with no added overhead in obtaining a model prediction, and while retaining much of the flexibility of the multi-process approach.

A seemingly natural starting point for Minerva is to make DFUs more efficient. For example, one can reduce the bandwidth for DFUs using delta updates [41, 35, 75], which are represented as a *diff* from the previous image instead of as a fresh new image. Unfortunately, this still requires device reboots and lacks the flexibility of the multi-process model.

Instead, our approach is to bring a service decomposition similar to the multi-process model to MCUs, within a single address space. The key observation is that models are *pure functions*. In particular, an model can be naturally abstracted as a single **predict** function that (1) returns its output by value, and (2) maintains no state across invocations. Our key insight is that this property allows us to build a carefully-structured, updatable memory segment that we call a *capsule*, which contains the ML model.

To understand how capsules work, consider the challenges we described earlier in updating only part of the image. Because ML models are pure functions, they *never* expose pointers to their internal code or data or maintain state across invocations. Thus, there is no need to update data structures and pointers throughout RAM when updating the capsule. By leveraging this property of ML models, we sidestep a significant source of complexity in performing live updates [10, 52].

Another challenge is that updates may break branches, jumps, and function calls into the capsule. To address this, we structure the capsule such that the predict function is always at the same memory address after each update. Because the application and model only interact via the predict function, the application can use the updated model without having to patch any code outside of the capsule. As predict is called just like a normal function, capsules add no overhead in the critical path of ML inference. Importantly, capsules are simple to integrate into an application. The programmer merely annotates functions and data belonging to the capsule and uses a special linker script that structures the capsule correctly at build time. To update the capsule, the device first downloads the update, and then invokes a lightweight library to apply it to the capsule.

Certain systems for MCUs, like Maté [46] and Tock [48], provide general dynamic loading facilities that we could use instead of capsules. However, they are far more intrusive than capsules, requiring applications to run in a software interpreter or be ported to a particular runtime environment. Unlike these approaches, capsules do not require tight integration with the underlying system and are largely platform-agnostic. This is critical for wide applicability because MCU-based edge devices exhibit heterogeneity in hardware and software.

To demonstrate the utility of capsules, we also design Minerva, an end-to-end capsule-based ML model update system. Minerva coordinates updates using a pull-based model and uses a simplified form of delta updates to efficiently transmit updated capsules to edge devices. Additionally, Minerva leverages the flexibility afforded by capsules to perform local acceptance testing for model updates. Although devices may lack access to ground-truth

labels, we show that we can locally test the utility of model updates using an established statistical technique called discounted cumulative gain (DCG).

We have implemented our system on four real-world applications and found that Minerva enables model updates up to 89× faster than a standard DFU and up to 73× faster than an application update in Tock (a widely-used embedded OS). Further, eliminating the need to re-flash non-ML code or perform a reboot enables applications to maintain state without checkpoints and restores. We designed Minerva to be easy to deploy and to integrate well with existing ML platforms. Concretely, it requires four additional lines of code to interface with TensorFlow/PyTorch, and two additional lines of code in the edge application—one to include the library, and the other to apply a capsule update (swap\_capsule()).

With Minerva, (1) We introduce capsules, which enable state-preserving low-bandwidth transparent updates for ML models. (2) We introduce a mathematical formulation for locally testing the utility of the received model using discounted cumulative gain (DCG) and the ability to perform acceptance testing for model updates. (3) We implement Minerva on MCUs and evaluate it on four real-world embedded machine learning applications. We demonstrate up to 89× reduction in DFU time.

## 3.2 Background

Although the term *edge* can refer to a variety of devices and services, including mobile phones, routers, gateways, and CDNs, this chapter focuses on the *extreme edge* consisting of deeply embedded devices. These include sensors for environmental monitoring [73, 51], structural health monitoring [77, 39], and IoT [58].

It is increasingly common to deploy ML models on such devices. For example, **Farmbeats** [73] is an end-to-end IoT platform for precision agriculture that processes data collected from various sensors deployed in farms. To identify faulty sensors, Farmbeats recently incorporated Fall-curves [8] to detect sensor faults using an ML-based predictor [23]. As the underlying soil condition changes, weather patterns change, and newer data is ingested, Farmbeats benefits from frequent model updates. Other examples of MCU-based edge ML devices are GesturePod [58], Picovoice [63], Powerblade [14], Zanzibar [74] and Permamote [32].

A model is composed of *operators* and *weights*. Operators are the building blocks of an ML architecture, such as tanh, ReLU, convolutions, and max-pooling. Weights are the parameters associated with these operators, such as convolution filter weights and biases. Model updates could include updates to both the code and data associated with an model—that is, to both the operators and weights. Additionally, as we shall explain in §3.2, models are often only a small fraction of the overall image size.

#### MCU-Based Device Hardware

Deeply embedded devices must be cheap to produce, easy to embed in the physical world, and operate for long periods of time (e.g., for years on a small, cheap,  $\leq 100$  mAh battery).

As such, they are typically built around microcontrollers (MCUs) that are cheap, small, and energy-efficient, such as the Nordic nRF52 series [66] or Atmel SAM R21 series [2].

Such MCUs typically use ARM Cortex-M CPUs that lack MMUs and have only *kilobytes* of RAM. Importantly, they have less RAM per unit of compute power than conventional systems. The reason is that MCUs use only SRAM (instead of DRAM) to minimize energy consumption, and even so, are limited in RAM size by SRAM leakage current. Whereas non-MCU systems have  $\approx 1$  MiB of RAM per MIPS of CPU (3M rule), the nRF52832 MCU, used by Farmbeats, has  $\approx 100$  DMIPS of CPU (ARM Cortex-M4F @ 64 MHz) but only 64 KiB of RAM. Thus, while embedded CPUs have grown more powerful over the years, making algorithms like ML attractive, embedded RAM has not grown commensurately.

To deal with limited RAM size, these MCUs also include nonvolatile, flash-backed "read-only memory," or ROM. On these devices, ROM is more plentiful than RAM; the nRF52832, for example, has 64 KiB of RAM but 512 KiB of ROM. As a result, RAM is only used for data that may change at runtime, like stack, heap, and mutable globals. Any data that will not change at runtime, like program text (code) and static data, are stored in ROM. This is possible because ROM and RAM are in a unified physical address space, enabling the program to execute code and access data directly out of ROM without first loading that data into RAM.

Network bandwidth is also a constrained resource for devices at the extreme edge. Low-power wireless network technologies, like LoRa and IEEE 802.15.4, provide only *kilobits* per second of bandwidth. Even if network bandwidth is available, battery-powered devices must use it sparingly, as network usage can dominate energy consumption [47, 29, 37].

#### MCU-Based Device Software

MCU-based devices do not run fully-fledged operating systems like Linux or Windows. Instead, they typically run specialized *embedded OSes*, like TinyOS [27], Contiki OS [18], or RIOT OS [37], that are carefully designed to be lightweight. Embedded OSes generally provide a scheduler, timers, device drivers, and an IP-based network stack. However, as MCUs lack hardware support for address translation (i.e., MMUs), embedded OSes generally lack memory virtualization, protection/isolation, and dynamic linking/loading. The application and system are linked into a monolithic program, called an *image*, and execute together in the same address space. Applications request system services via direct function calls and can freely obtain and follow pointers to OS data structures. This design stems from the classical view that, for maximum efficiency, the system and application should be tightly integrated and co-specialized [27].

A notable exception is Tock OS [48]. Tock uses hardware support for memory protection in modern MCUs to provide multiprogramming with isolation. Still, it does not support virtual memory or address translation, requiring apps to be compiled with position-independent code (PIC) to support dynamic loading. Furthermore, Tock's dynamic loading only applies to data in RAM, not in ROM—all loadable apps must be part of the device's ROM when the device is initially programmed, and new apps cannot be downloaded over the network at runtime.

#### DFU Size vs. TAB Size vs. ML Model Size

Figure 3.2: Comparison of machine learning model size to full DFU size and TAB size (Tock Application Binary, a compiled application to be loaded onto a board with Tock OS) for several edge applications. ML model size (blue) includes ML operators and weights. TAB Size includes the ML model size and Tock support modules. The full DFU size (red) includes ML model size along with application logic, and networking modules. **Unlike** the cloud setting, machine learning model sizes are only a fraction of the total edge application size.

We use Tock as a starting point in designing capsules and compare Minvera's performance to Tock's.

#### DFUs for MCU-Based Devices

Currently, the most accessible way to update an ML model on an MCU-based device is to perform a device firmware update (DFU). In a DFU, an entirely new image, containing not only the model but also the application and system, is built and deployed to a device. In this section, we describe how DFUs work and explain why they are inefficient for model updates. **Step 1: Obtaining the New Image.** Embedded OS solutions often rely on a physical connection (e.g., J-Tag) or close proximity (e.g., Bluetooth) to install or update an application. Unfortunately, it is difficult to physically access edge devices deployed in the field, particularly for devices in remote locations like farmlands [73] or the deep sea [34]. As a result, it is desirable to use over-the-air (OTA) updates, in which updates are transferred over the network. Herein lies the first challenge of DFUs—while edge devices are constrained in network bandwidth, OTA DFUs are bandwidth-intensive. As an extreme example, Farmbeats

uses LoRa with a bit rate of only  $\approx 100~bits$  per second, making it slow to download a  $\approx 100~KiB~DFU$ . DFUs are particularly inefficient in the context of model updates because, as shown in Figure 3.2, the model is only a small fraction of the update size. Also notice the green bars highlighting the "bloatware" introduced by embedded OSes. Even a compiled binary containing only ML code and no other application logic is still considerably larger than the standalone size of the ML model.

Step 2: Reflashing ROM with the New Image. The new image must be stored in ROM. The process of updating data in ROM is called *reflashing*. ROM, as its name ("read-only memory") suggests, is optimized for reading; writing to ROM is far slower and more energy-intensive than writing to RAM. As a result, reflashing ROM with the new update is a significant source of overhead in the update process, as we will see in §3.5. The large size of DFUs exacerbates this overhead.

Step 3: Verifying the New Image. Reliability for DFUs is accomplished via a two-bank memory model. ROM is partitioned into two separate regions called *banks*, one of which stores the active image. In a DFU, the new image is downloaded into the other bank and checked for integrity. If the integrity check passes, then either the new image is copied into the active bank, or the bank containing the new image is marked as active. If the update fails, then the device can still boot the old image. While the two-bank model helps ensure reliability, it effectively halves the available ROM space.

Step 4: Booting the New Image. Every DFU requires a reboot, which causes the application to lose the contents of RAM (application state). While this can be addressed by checkpointing state in persistent memory and restoring it after the reboot, this is challenging because state is often spread throughout the application (e.g., networking state, application logic, etc.). Additionally, rebooting a device involves re-initializing and synchronizing sensors, serial communication modules, and other peripherals, which takes time.

Rebooting also reduces flexibility. Concretely, ML deployments on server-class devices benefit from acceptance testing. Acceptance testing is important for edge deployments because not all edge devices observe the same data distribution. In the precision agriculture example, a sensor in a farm in Alaska observes a different data distribution than a sensor in a farm in Texas. Hence, even though the new model is better than the old one in most cases (in expectation), it may not be universally better across all nodes of a deployed fleet. One way to solve this is to build profiles of each deployed device and test the model in the cloud. However, this is not always feasible as bandwidth constraints prevent streaming data to the cloud. This calls for local acceptance testing. Having to reboot to switch models adds friction to this process.

## 3.3 Capsules

In this section, we describe *capsules*, which allow ML model updates to be efficiently and flexibly deployed on MCU-based devices. We focus here only on the mechanisms of capsules—how capsules are structured, how to generate them, and how to apply updates on a device.

Other details of an end-to-end model update system, like how to trigger updates and how to transfer them over the air, are described in §3.4.

### Motivation and Opportunities