# High Performance Hybrid Switched-Capacitor Converters for Aerospace Applications

Sam Coday Robert Pilawa-Podgurski

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2023-79 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2023/EECS-2023-79.html

May 9, 2023

Copyright © 2023, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### High Performance Hybrid Switched-Capacitor Converters for Aerospace Applications

By

#### Samantha Coday

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Associate Professor Robert Pilawa-Podgurski, Chair Associate Professor Duncan Callaway Professor Kristopher Pister Dr. Ansel Barchowsky

Spring 2023

#### High Performance Hybrid Switched-Capacitor Converters for Aerospace Applications

Copyright 2023 by Samantha Coday

#### Abstract

High Performance Hybrid Switched-Capacitor Converters for Aerospace Applications

by

#### Samantha Coday

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Associate Professor Robert Pilawa-Podgurski, Chair

Innovations within power electronics are necessary to enable future electric aircraft and space exploration. In these aerospace applications, power converters must be light-weight, efficient and reliable. Conventional, inductor-based, power electronics tend to be heavy, and have high switch stress making them difficult to implement in these applications. In this thesis, hybrid switched-capacitor converters are explored as they utilize energy-dense capacitors as the primary energy storage element, and also decrease the voltage stress of the switches. The basics of hybrid switched-capacitor converters are covered, with a focus on why these topologies are suitable for aerospace applications. Next, the losses of the capacitors, the main building block of these converters, are characterized and a model is proposed which allows for simple loss estimation. Then, the design and flight qualification of a hybrid switchedcapacitor converter is discussed, showcasing a converter with high efficiency, power density and reliable control. Moreover, the safe control of hybrid switched-capacitor converters during shutdown is described, with a model proposed which allows designers to understand the shutdown of the converter and trade-offs in different shutdown techniques. Hybrid switchedcapacitor converters are motivated for their use in harsh space environments, where radiation effects make designing high performance converters challenging. Two different converters designed for space applications are then described, utilizing techniques such as partial power processing to minimize passive component mass. Overall, this thesis showcases the design of several high performance hybrid switched-capacitor converters, but also introduces models and comparison frameworks to allow future designers to better understand the design and operation of hybrid switched-capacitor converters in aerospace applications.

To Chance.

### Contents

| Co | onter                                         | nts                                                                                                    | ii                               |

|----|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------|

| Li | st of                                         | Figures                                                                                                | iv                               |

| Li | st of                                         | Tables                                                                                                 | xi                               |

| 1  | Intr<br>1.1<br>1.2                            | Introduction                                                                                           | 1<br>1<br>2                      |

| 2  | Fun<br>2.1<br>2.2<br>2.3                      | damentals of Hybrid Switched-Capacitor Converters  Motivation for Hybrid Switched-Capacitor Converters | <b>5</b> 5 8                     |

| 3  | Cha<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | Introduction                                                                                           | 11<br>17<br>21<br>24<br>25<br>28 |

| 4  | Flyi<br>4.1<br>4.2<br>4.3<br>4.4              | Ing Capacitor Multilevel Converter for Hybrid Electric Aircraft  Motivation                            | 30<br>30<br>31<br>38<br>39       |

| 5  | 5.1<br>5.2                                    | System Control                                                                                         | 41<br>41<br>41<br>43             |

|    | 5.4   | Fault Detection                                                    | 45         |

|----|-------|--------------------------------------------------------------------|------------|

|    | 5.5   | Flight Qualification                                               | 47         |

|    | 5.6   | Preliminary Electromagnetic Interference testing                   | 51         |

|    | 5.7   | Conclusion                                                         | 51         |

| 6  | Safe  | Shutdown of Flying Capacitor Multilevel Converters                 | 52         |

|    | 6.1   | Motivation                                                         | 52         |

|    | 6.2   | FCML Circuit Model                                                 | 53         |

|    | 6.3   | General Shutdown Dynamics                                          | 57         |

|    | 6.4   | Model Description                                                  | 61         |

|    | 6.5   | Model Validation and Hardware Prototype                            | 62         |

|    | 6.6   | Safe Shutdown Techniques                                           | 65         |

|    | 6.7   | Conclusion                                                         | 70         |

| 7  | Ove   | rview of Converter Requirements in Space Applications              | 72         |

|    | 7.1   | Radiation Effects in Space                                         | 72         |

|    | 7.2   | Motivation for Hybrid Switched-Capacitor Converters                | 73         |

| 8  | Flyi  | ng Capacitor Multilevel Converter Designed for Electric Propulsion | <b>7</b> 5 |

|    | 8.1   | Motivation                                                         | 75         |

|    | 8.2   | Converter Design                                                   | 76         |

|    | 8.3   | Converter Performance                                              | 80         |

|    | 8.4   | Conclusion                                                         | 83         |

| 9  | Con   | aposite Hybrid Switched-Capacitor Converter                        | 84         |

|    | 9.1   | Motivation                                                         | 84         |

|    | 9.2   | Capacitively-Isolated Dickson Converter Design                     | 86         |

|    | 9.3   | Regulating FCML Converter Design                                   | 95         |

|    | 9.4   | Composite Converter Operation                                      | 101        |

|    | 9.5   | Conclusion                                                         | 105        |

| 10 | Con   | clusion                                                            | 107        |

|    | 10.1  | Topology Comparisons                                               | 107        |

| Bi | bliog | raphy                                                              | 110        |

# List of Figures

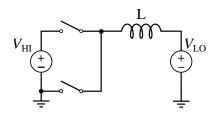

| 2.1 | Conventional switched-inductor style buck converter                                                                                                        | 5      |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

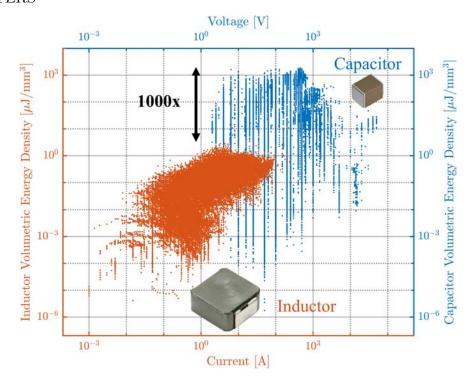

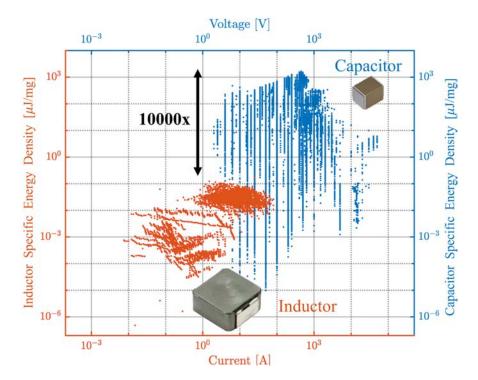

| 2.2 | Calculated energy density for a survey of commercially available inductors and capacitors [6]. Note, the most energy-dense capacitor has over 1000x higher |        |

|     | energy density than the most energy-dense inductor. This difference in component                                                                           |        |

|     | energy density motivates the use of capacitors as the primary energy storage                                                                               |        |

|     |                                                                                                                                                            | c      |

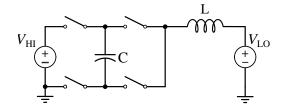

| 2.3 | element to design compact converter topologies                                                                                                             | 6<br>7 |

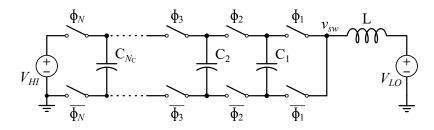

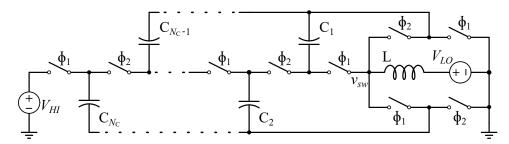

| 2.3 | An N-level FCML buck converter                                                                                                                             | 7      |

| 2.4 | An N-level Dickson converter                                                                                                                               | 7      |

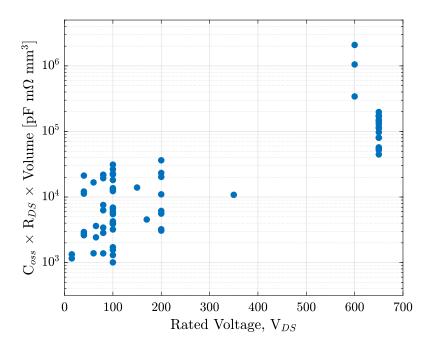

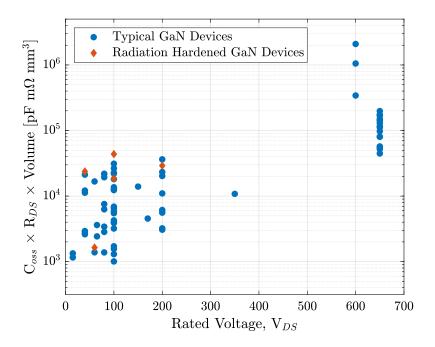

| 2.6 | A survey of commercially available GaN devices and the corresponding figure-of-                                                                            | '      |

| 2.0 | merit, where a lower figure-of-merit corresponds to higher performance                                                                                     | 8      |

| 2.7 | Calculated <i>specific</i> energy density for a survey of commercially available inductors                                                                 | O      |

|     | and capacitors [6]. Note, the most energy-dense capacitor has over 10,000x higher                                                                          |        |

|     | energy density than the most energy dense inductor                                                                                                         | 9      |

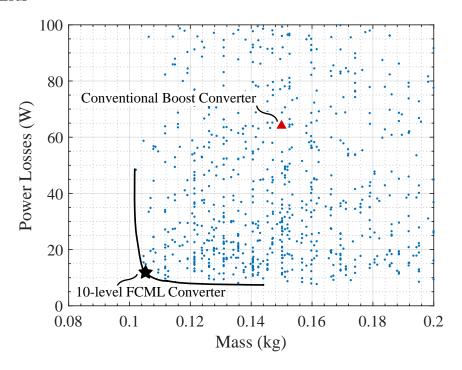

| 2.8 | Pareto front optimization, where the blue dots represent possible FCML con-                                                                                |        |

|     | verter designs. The star represents an optimized 10-level FCML converter which                                                                             |        |

|     | minimizes both loss and weight. A conventional boost converter is shown, op-                                                                               |        |

|     | timized around the same operating conditions, modeled with 1.2 kV SiC FETs.                                                                                |        |

|     | The design of this FCML converter is described in Chapter 4                                                                                                | 10     |

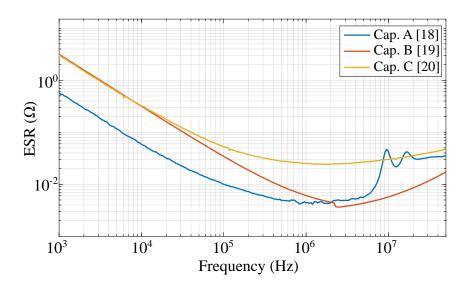

| 3.1 | Standard capacitor model simplified [31]                                                                                                                   | 12     |

| 3.2 | Plot of manufacturer-provided ESR of three Class II MLCCs, listed in Table 3.3                                                                             |        |

|     | over a range of frequencies, at 0 V bias small signal excitation (0.1 $V_{rms}$ ) [32] [33]                                                                |        |

|     | [34]                                                                                                                                                       | 12     |

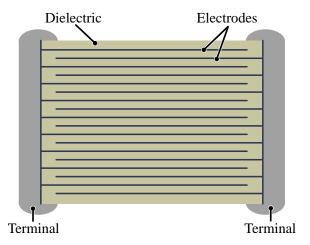

| 3.3 | Model of MLCC, highlighting the internal structure of interwoven metallic plates                                                                           |        |

|     | and dielectric material resulting in energy-dense capacitors                                                                                               | 13     |

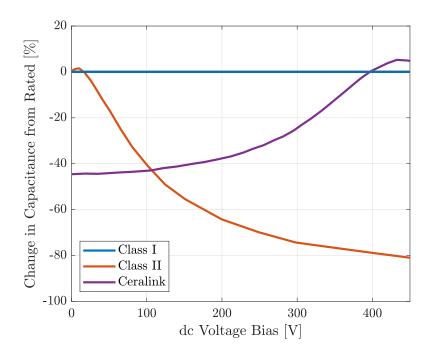

| 3.4 | Percent change in capacitance over rated dc voltage. From Table 3.3 Cap. E                                                                                 |        |

|     | (Class I) has invariant capacitance with dc voltage bias, Cap. A (Class II) de-                                                                            |        |

|     | rates with bias, and Cap. D (Ceralink) has increased capacitance with increased                                                                            |        |

|     | bias                                                                                                                                                       | 14     |

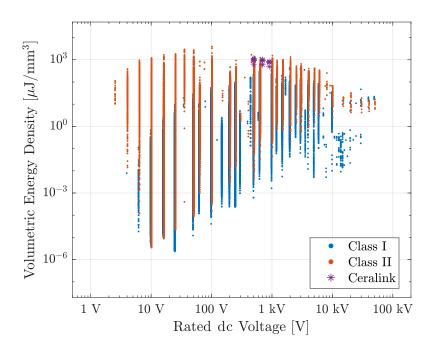

| 3.5 | Comparison of volumetric energy density of commercially available multilayer                                                                               |        |

|     | ceramic capacitors. Energy density metric includes derating for Class II and                                                                               |        |

|     | Ceralink capacitors                                                                                                                                        | 15     |

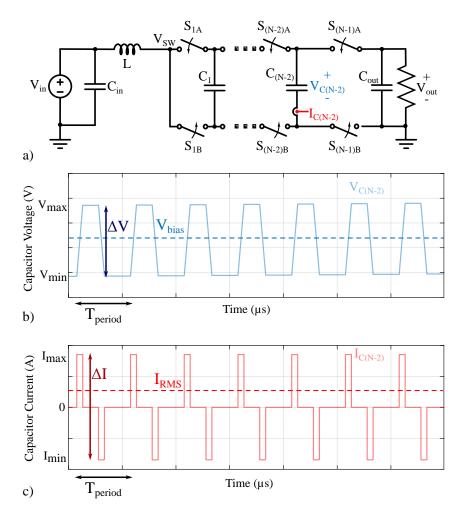

| 3.6  | Generic N-level FCML boost converter a) schematic, with (b) voltage and (c) current waveforms for a flying capacitor. These waveforms highlight the non-                                                                                                                                                                                                                                                         |                                 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|      | sinusoidal large signal excitations of the MLCC within the circuit                                                                                                                                                                                                                                                                                                                                               | 16                              |

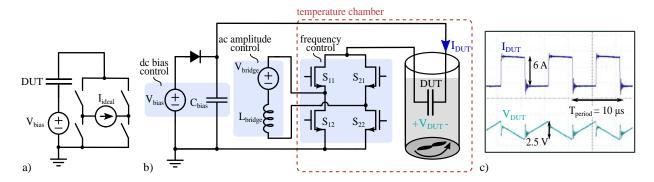

| 3.7  | a) Ideal circuit which allows for varying dc bias voltage, and varying ac current amplitude with an ideal current source and h-bridge. b) Electrical excitation circuit used to replicate hybrid switched-capacitor operation with adjustable frequency, dc bias and ac amplitude. Portions of the electrical excitation are placed within the temperature chamber to decrease the inductance in the path to the |                                 |

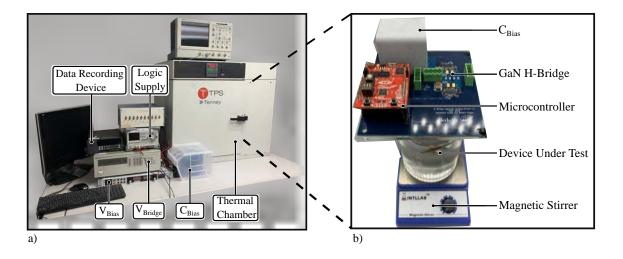

| 3.8  | DUT. c) Example capacitor excitations created by the electrical excitation circuit.<br>a) Equipment setup developed to generate electrical excitation, as well as log temperature data. b) The electrical excitation circuit board and other calorimetric                                                                                                                                                        | 18                              |

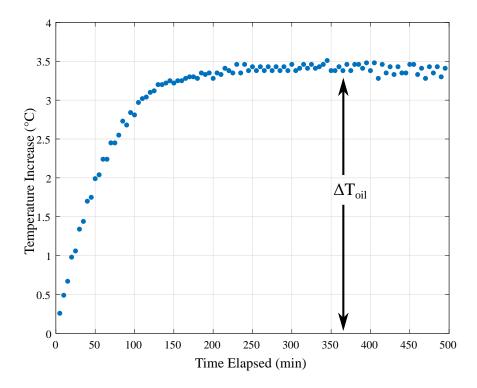

| 3.9  | components located within the temperature-controlled chamber                                                                                                                                                                                                                                                                                                                                                     | 19                              |

| 3.10 | to ensure thermal equilibrium                                                                                                                                                                                                                                                                                                                                                                                    | 20                              |

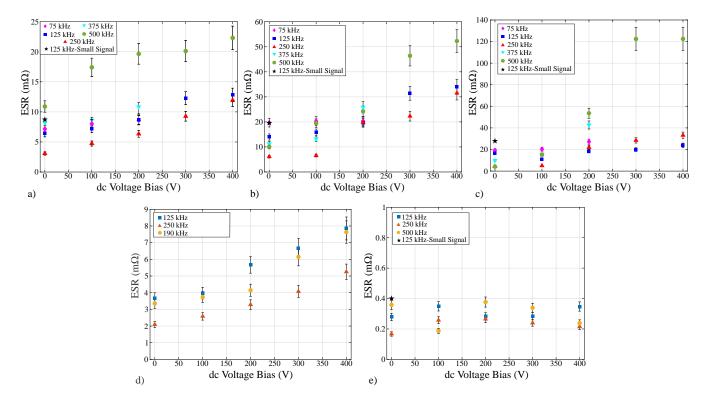

| 3.11 | invariant to voltage bias                                                                                                                                                                                                                                                                                                                                                                                        | 22                              |

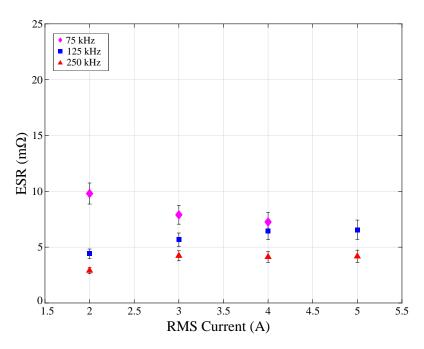

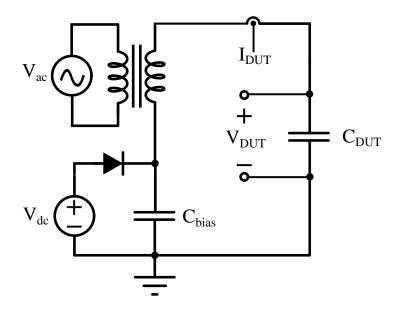

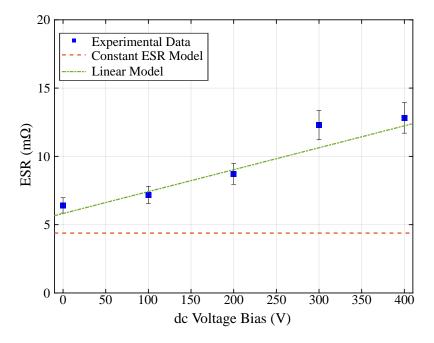

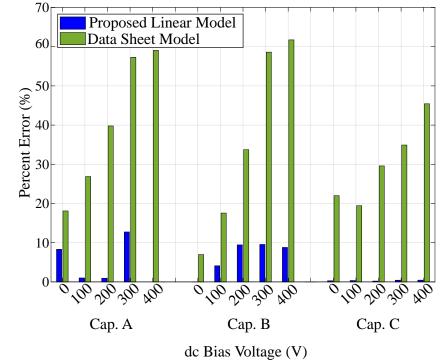

|      | has a much larger affect on losses compared to the effect of ac current amplitude.  Low frequency electrical measurement capacitor testing circuit                                                                                                                                                                                                                                                               | <ul><li>24</li><li>25</li></ul> |

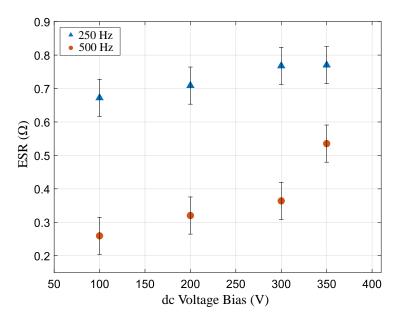

|      | Low frequency bias dependent ESR results, for Cap A in Table 3.3, attained through electrical experimental setup                                                                                                                                                                                                                                                                                                 | 26                              |

| 3.15 | constant ESR approximation is found from [37]                                                                                                                                                                                                                                                                                                                                                                    | 27<br>28                        |

|      | 125 KHZ                                                                                                                                                                                                                                                                                                                                                                                                          | 20                              |

| 4.1  | Proposed electric aircraft system architecture. This work focuses on the design and implementation of the dc-dc boost converter                                                                                                                                                                                                                                                                                  | 31                              |

| 4.2  | Pareto front optimization, utilizing loss model presented in [40]. The star represents the selected design, which minimizes both loss and weight. A conventional boost converter is shown, optimized around the same operating conditions, mod-                                                                                                                                                                  |                                 |

| 4.3  | eled with 1.2 kV SiC FETs                                                                                                                                                                                                                                                                                                                                                                                        | 32                              |

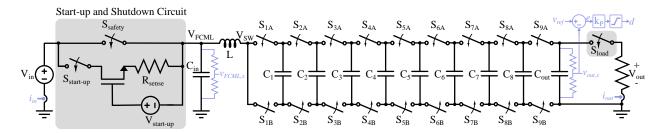

|      | iliary circuits. The relevant control sensing circuitry and diagram are also shown.                                                                                                                                                                                                                                                                                                                              | 33                              |

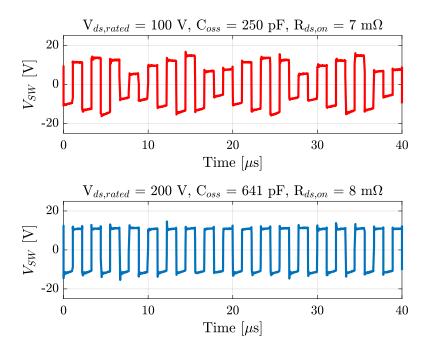

| 4.4 | Switch-node measurement of 10-level FCML converter, measured with the same board and operating point, but two different GaN switches. Verified by work |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | · • • · · · · · · · · · · · · · · · · ·                                                                                                                |     |

|     | in [64], the switches with higher $C_{oss}$ results in better flying capacitor voltage                                                                 | 36  |

| 4 5 | natural balancing                                                                                                                                      | 30  |

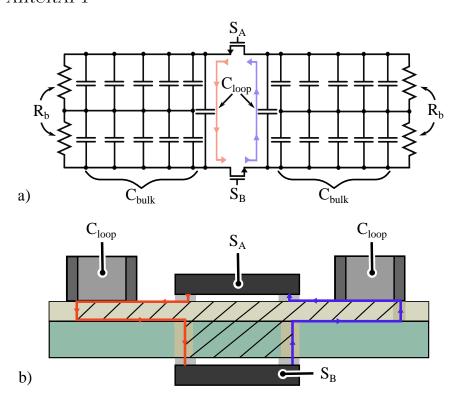

| 4.5 | a) High voltage switching cell depicting large bulk capacitance and associated                                                                         |     |

|     | biasing resistors in addition to small high-frequency capacitors, $C_{loop}$ , placed close                                                            |     |

|     | to the switching devices. b) Commutation loop dual sided design using a modified                                                                       |     |

|     | electrically-thin layout with local capacitors to minimize loop inductance and                                                                         | 25  |

| 1.0 | blind vias to shape the current path                                                                                                                   | 37  |

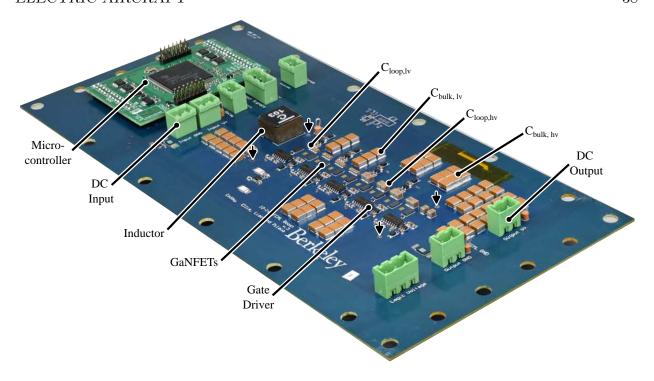

| 4.6 | Top view of the hardware prototype. The four arrows show the mounting holes                                                                            | 20  |

| 4 7 | placed close to the main power stage to provide further structural support                                                                             | 38  |

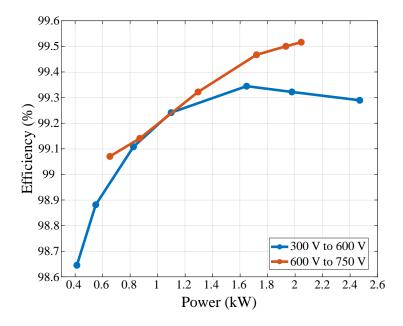

| 4.7 | Measured efficiency of the FCML converter stage over a range of power levels.                                                                          | 0.0 |

| 4.0 | Note that these efficiency measurements include gate drive losses                                                                                      | 39  |

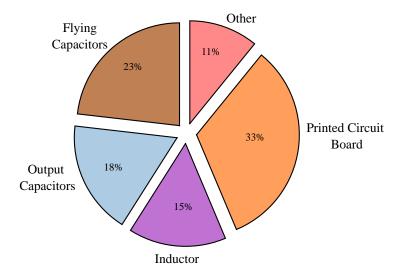

| 4.8 | Weight breakdown of FCML converter. The majority of the weight is from the                                                                             |     |

|     | PCB and capacitors; both flying capacitance and output capacitance. Note,                                                                              |     |

|     | this weight breakdown is of the FCML converter only, and does not include the                                                                          | 40  |

| 4.0 | enclosure or the auxiliary boards which are independent of core converter design.                                                                      | 40  |

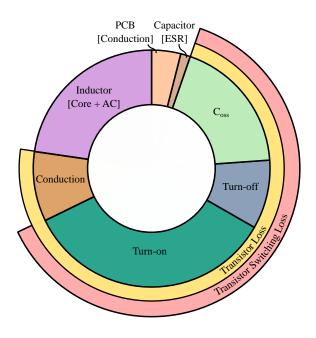

| 4.9 | Approximate loss breakdown of FCML converter, while operating at 1.6 kW, 500                                                                           | 40  |

|     | V input and 750 V output                                                                                                                               | 40  |

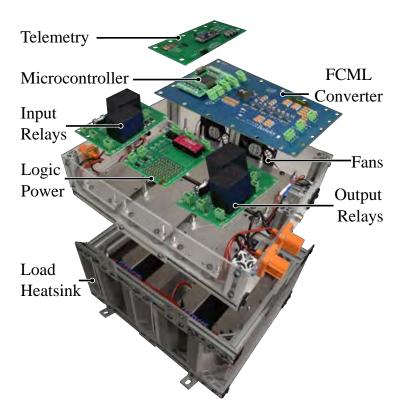

| 5.1 | Exploded view of system, highlighting key components and printed circuit boards.                                                                       | 42  |

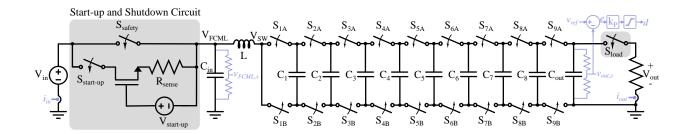

| 5.2 | Ten-level FCML converter, highlighting the necessary start-up and shutdown aux-                                                                        |     |

|     | iliary circuits. The relevant control sensing circuitry and diagram are also shown.                                                                    |     |

|     | This figure first appeared as Fig. 4.3, but is repeated here for readability                                                                           | 42  |

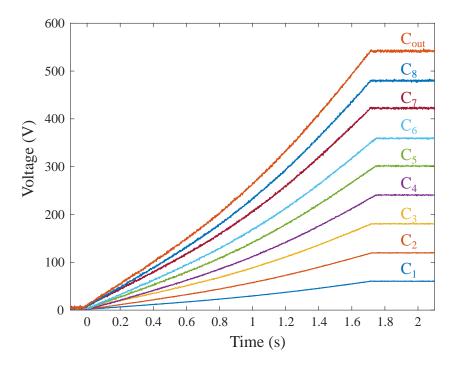

| 5.3 | Flying capacitor voltages during start-up ramp, $t_{ramp,input}$ . Measured at 500 V                                                                   |     |

|     | input                                                                                                                                                  | 44  |

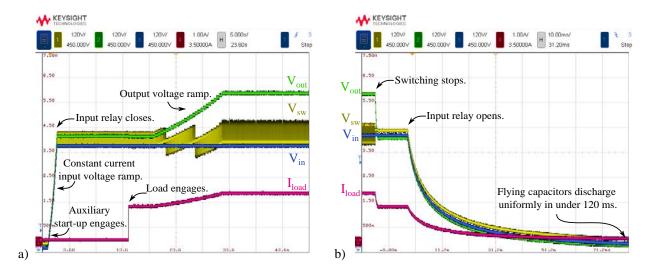

| 5.4 | a) Experimental waveforms showing FCML converter start-up procedure using                                                                              |     |

|     | auxiliary start-up circuit. Start-up is measured at 500 V input, while regulating                                                                      |     |

|     | to 750 V output and 1.6 kW. b) FCML converter safe shutdown procedure, in-                                                                             |     |

|     | dicating uniform discharge of flying capacitors. Shutdown is measured at $550~\mathrm{V}$                                                              |     |

|     | input, while regulating to 750 V output and 1.6 kW                                                                                                     | 45  |

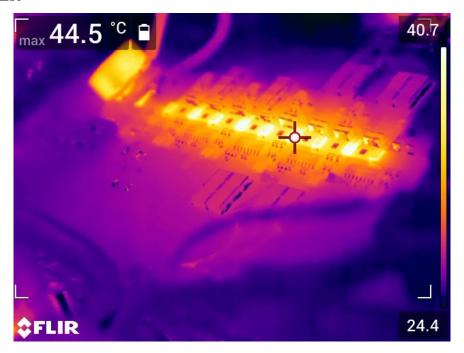

| 5.5 | Thermal image of FCML converter at 1.6 kW, 500 V input and 750 V output,                                                                               |     |

|     | measured at room temperature, captured with a FLIR T540 thermal camera. The                                                                            |     |

|     | GaNFETs and inductor experience the greatest heat measured at approximately                                                                            |     |

|     | 45 degrees Celsius. Note, in this thermal image the inductor is lifted such that                                                                       |     |

|     | the current can be measured with a current probe                                                                                                       | 48  |

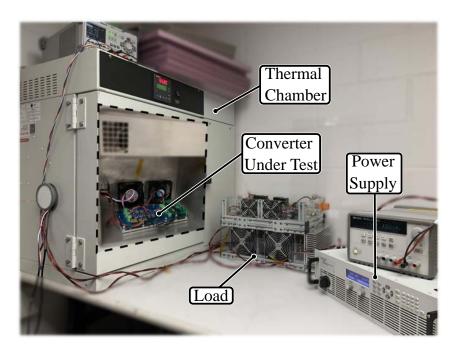

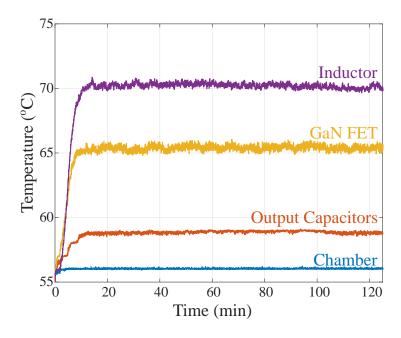

| 5.6 | Annotated photograph showing thermal testing set-up                                                                                                    | 49  |

| 5.7 | Measured temperatures on board the FCML during thermal testing                                                                                         | 49  |

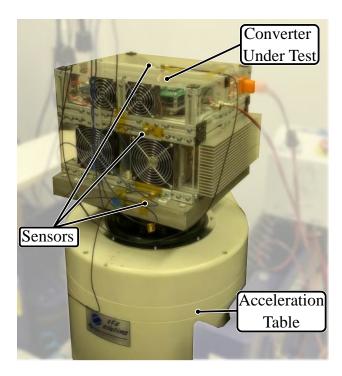

| 5.8 | Annotated photograph of vibration and shock testing, showing acceleration ap-                                                                          |     |

|     | plied in Z-axis.                                                                                                                                       | 50  |

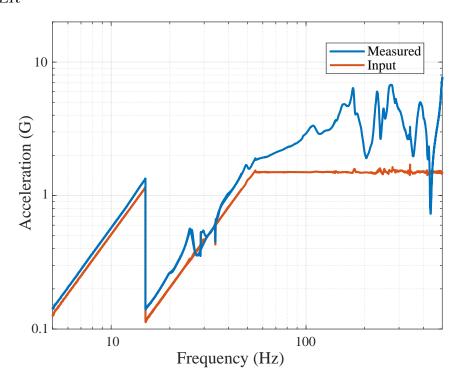

| 5.9        | Input drive acceleration, used for characterization in X,Y and Z-axis. Measured acceleration from sensor placed on top of system, collected during acceleration in the Z-axis                                                                                                                                                                                                                                                                                                                                      | 51 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

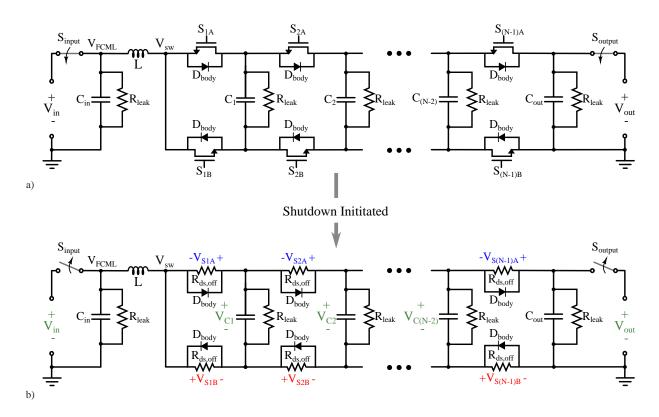

| 6.1        | a) Circuit model of a generic N-level FCML converter [10], with input and output breakers. b) Circuit model once shutdown is initiated, with relevant parasitic components shown. Capacitor and switch voltages are also labeled                                                                                                                                                                                                                                                                                   | 54 |

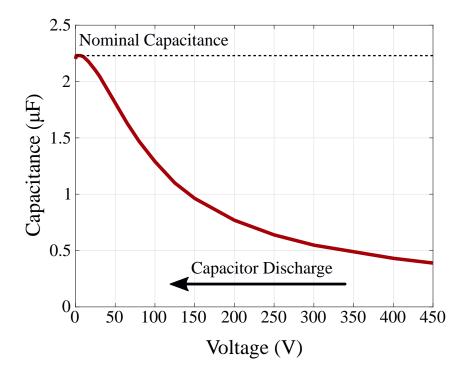

| 6.2        | Class II MLCC capacitance de-rating curve, as the capacitor discharges the capacitance will increase non-linearly [37].                                                                                                                                                                                                                                                                                                                                                                                            | 56 |

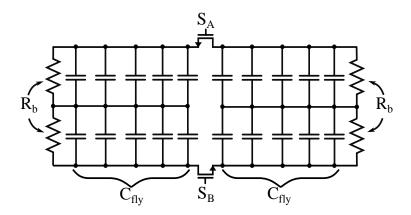

| 6.3        | Example flying capacitor implementation showing series stacked capacitors and balancing resistors, $R_b$ , which serve to ensure uniform voltage distribution among capacitors                                                                                                                                                                                                                                                                                                                                     | 57 |

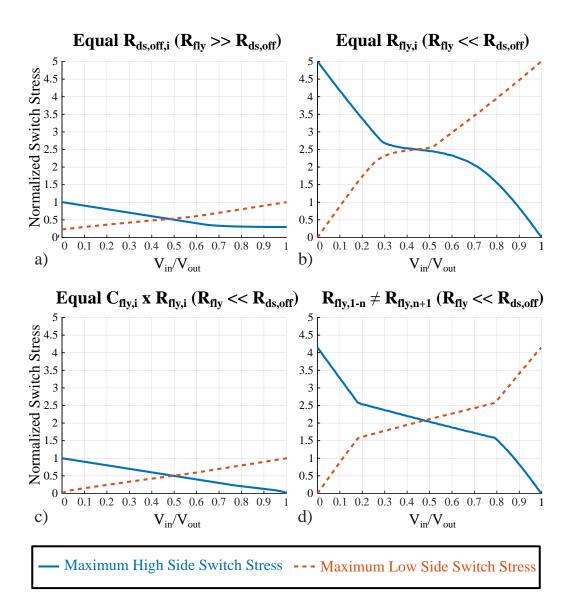

| 6.4        | Simulated switch stress during shutdown as a function of conversion ratio, normalized about the nominal steady-state blocking voltage. (a) Safe shutdown with $R_{ds,off}$ of each switch equal and with dominant impact on rate of discharge. (b) Increased switch stress observed for $R_{fly}$ induced discharge where $C_{fly} \neq C_{in/out}$ results in mismatched $RC$ time constants. (c) No increased switch stress is observed when $RC$ time constants are well matched. (d) Unequal $R_{fly}$ between |    |

|            | cells, where $R_b$ is implemented only for high-voltage cells                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59 |

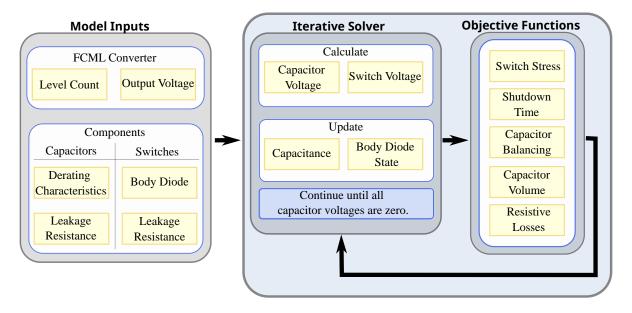

| 6.5        | Flowchart for iteratively solved MATLAB shutdown model                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61 |

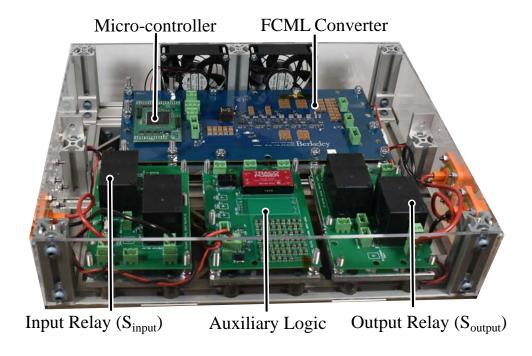

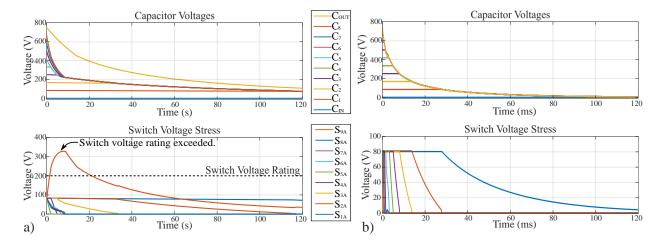

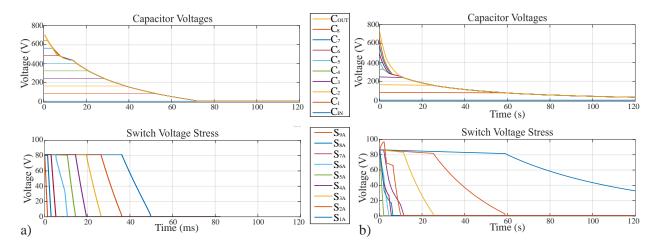

| 6.6<br>6.7 | Hardware prototype, showing FCML converter, input and output relays a) Modeled shutdown, where no safe shutdown techniques are implemented. The complete shutdown process takes over two minutes and the voltage rating of the switches is exceeded, resulting in an unsafe shutdown condition. b) Modeled shutdown with resistive load. With this method complete shutdown occurs after 120 milliseconds. All switch voltages remain under their rated voltages, therefore                                        | 62 |

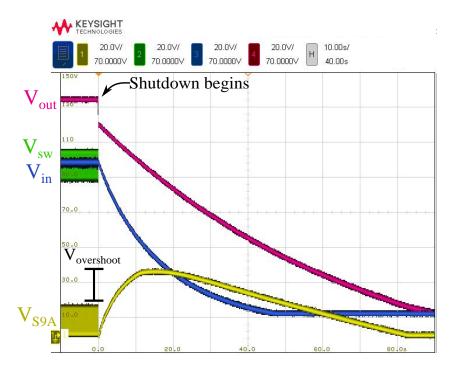

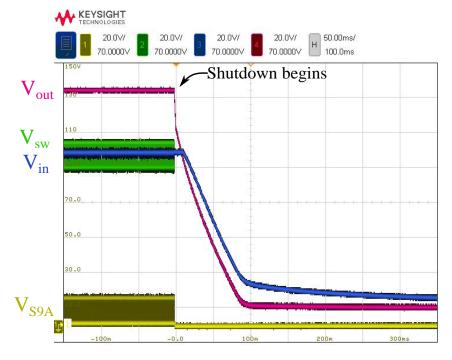

| 6.8        | resulting in a safe shutdown condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64 |

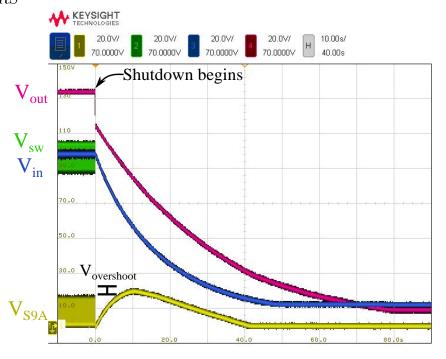

| <i>c</i> 0 | begins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65 |

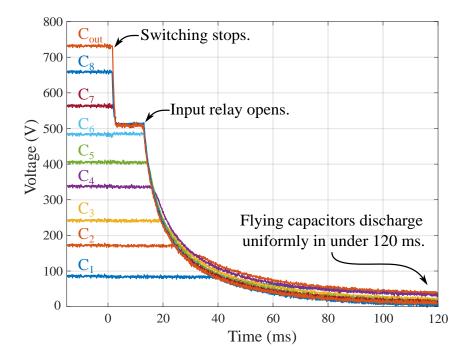

| 6.9        | Experimentally measured flying capacitor voltages during shutdown, with resistive load connected. Shutdown initiated from 750 V output steady-state operation.                                                                                                                                                                                                                                                                                                                                                     | 66 |

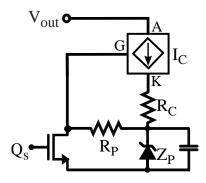

| 6.10       | Auxiliary shutdown circuit, utilizing a switchable current regulator $(I_C)$                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67 |

| 6.11       | Experimentally measured voltages during shutdown, while implementing the auxiliary shutdown circuit shown in Fig. 6.10. With this method no overshoot is observed.                                                                                                                                                                                                                                                                                                                                                 | 67 |

| 6.12       | a) Modeled shutdown with auxiliary shutdown circuit. b) Modeled shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 6.13       | with adjusted balancing resistor value to decrease voltage stress                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68 |

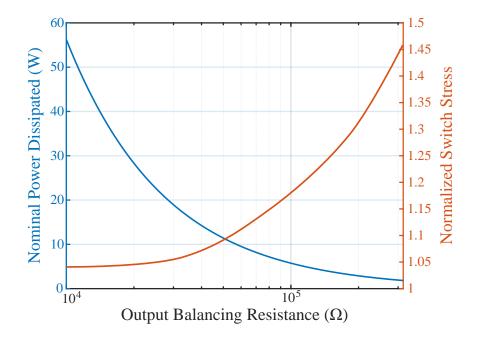

|            | resistor. There is a small amount of overshoot measured with this method  Power dissipated in balancing resistors during nominal operation and normalized                                                                                                                                                                                                                                                                                                                                                          | 69 |

|            | switch stress as a function of modified output resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69 |

| 7.1<br>7.2 | 1                                                                                                                                                             |          |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| 8.1        | System level architecture showing the role of the dc-dc converter presented in this work                                                                      | 73<br>75 |  |

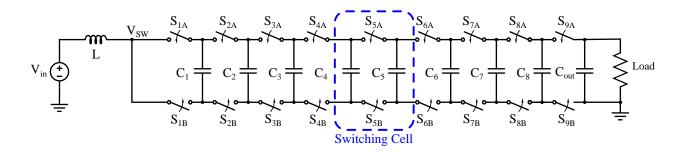

| 8.2        | Schematic of 10-level flying capacitor multilevel boost converter                                                                                             | 76       |  |

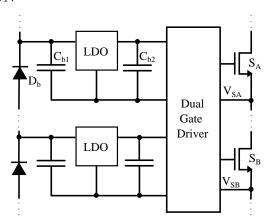

| 8.3        | Schematic of the cascaded bootstrap circuit, showing one pair of complementary switches                                                                       | 78       |  |

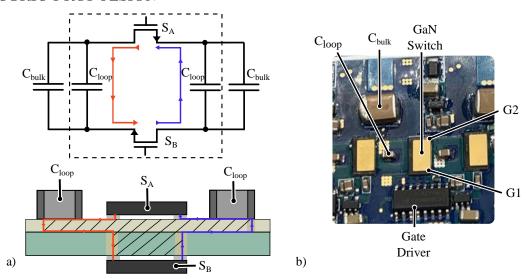

| 8.4        | a) Commutation loop design using a modified electrically-thin layout with local small capacitors to minimize loop inductance. b) Focused view of commutation  |          |  |

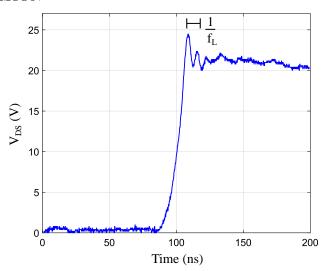

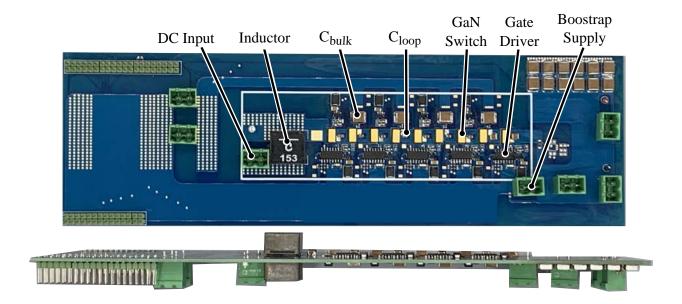

| 8.5        | loop on top-side of hardware prototype                                                                                                                        | 79<br>80 |  |

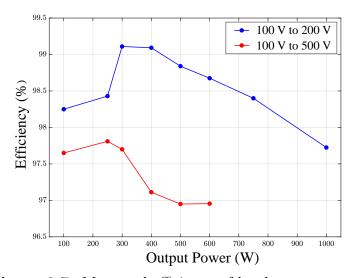

| 8.6        | Top and side views of the hardware prototype                                                                                                                  | 82       |  |

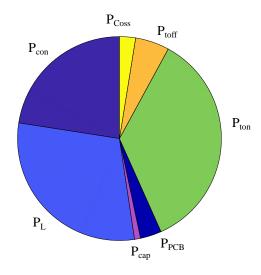

| 8.7        | Measured efficiency of hardware prototype                                                                                                                     | 82       |  |

| 8.8        | Loss breakdown at 1 kW, 100 V to 200 V conversion                                                                                                             | 83       |  |

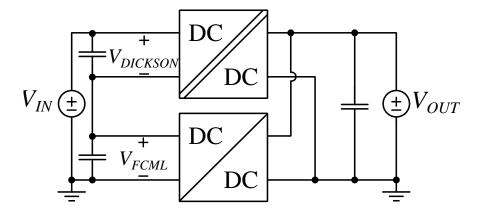

| 9.1        | Configuration of a high step-down converter which utilizes partial power process-                                                                             |          |  |

| 9.2        | ing to achieve large conversion ratios and regulation                                                                                                         | 85       |  |

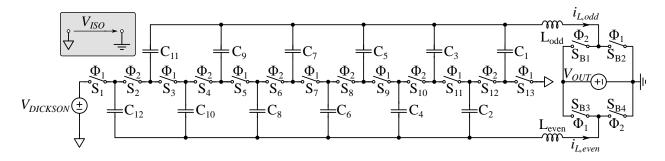

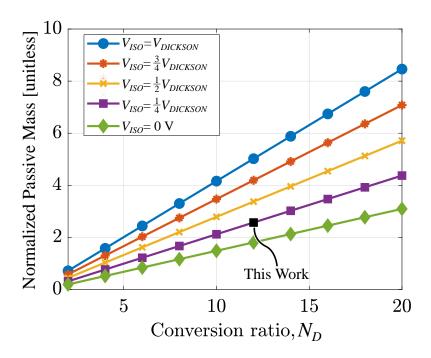

| 9.3        | the input and output negative potentials                                                                                                                      | 85       |  |

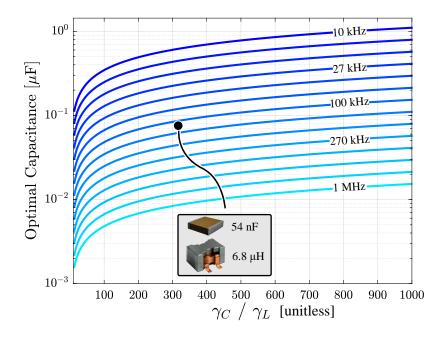

| 9.4        | ratio                                                                                                                                                         | 89       |  |

|            | kHz.                                                                                                                                                          | 90       |  |

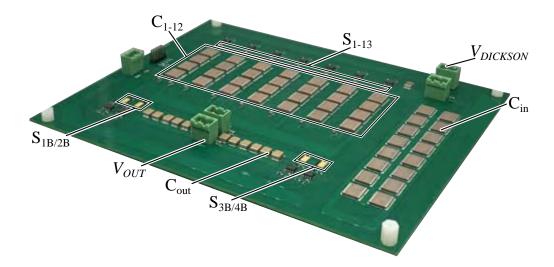

| 9.5        | Fixed-ratio 12:1 capacitively-isolated Dickson hardware prototype. The inductors are placed on the back of the board below $S_{B[1-4]}$                       | 92       |  |

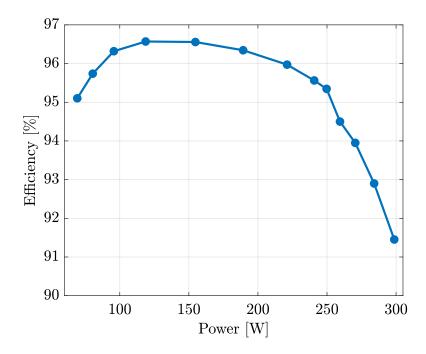

| 9.6        | Measured efficiency of capacitively-isolated Dickson converter hardware proto-<br>type, over a range of output power with a fixed 600 V input $(V_{DICKSON})$ | 92       |  |

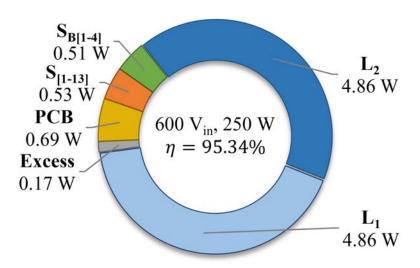

| 9.7        | Estimated capacitively-isolated Dickson converter loss breakdown for 600 V input, 250 W delivered at 95.34% efficient.                                        | 93       |  |

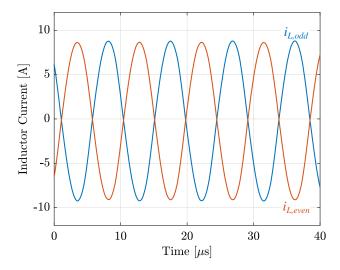

| 9.8        | Measured inductor currents in the capacitively-isolated Dickson converter, operating at 600 V input and 250 W output power.                                   | 94       |  |

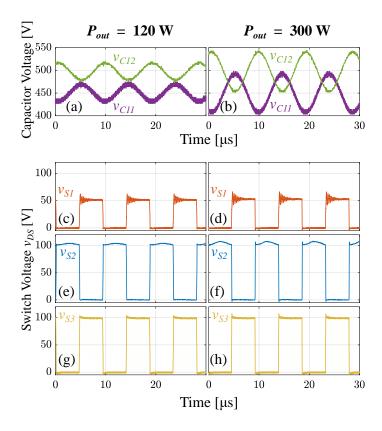

| 9.9   | Measured operating waveforms of capacitively-isolated Dickson converter (Fig. 9.2) at peak efficiency, 120 W, and heavy load, 300 W. As shown in (a) and (b) as the                                                                              |     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | load increases the capacitor peak-to-peak voltage increases. However, as shown in                                                                                                                                                                |     |

|       | subfigures (c)-(h) the drain-to-source voltage of the switches does not experience                                                                                                                                                               |     |

|       | substantial increased ripple, allowing the use of lower voltage devices, indepen-                                                                                                                                                                |     |

|       | dent of load condition                                                                                                                                                                                                                           | 95  |

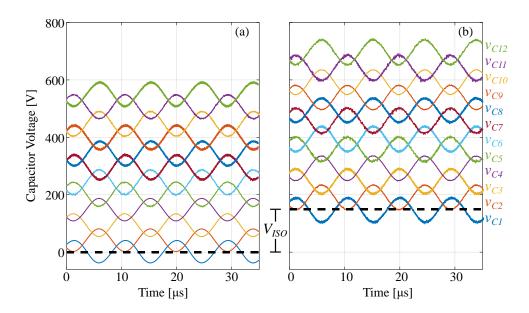

| 9.10  | Flying capacitor voltages in the capacitively-isolated Dickson converter measured with 600 V input and 250 W output power. a) Measured capacitor voltages with no isolation voltage applied. b) Measured capacitor voltages with 150 V isolation |     |

|       | voltage applied                                                                                                                                                                                                                                  | 96  |

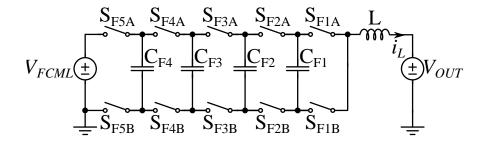

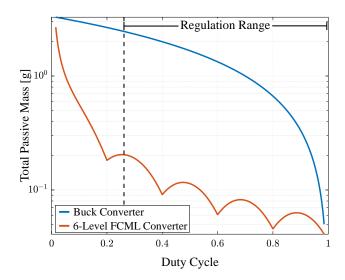

| 9.11  | Schematic of regulating six-level FCML converter, chosen as the optimal level count to minimize the total passive mass                                                                                                                           | 97  |

| 9.12  | Comparison of optimized total passive mass for a six-level FCML converter and a buck converter (operating in boundary conduction mode). Optimization is performed for the operating conditions described in Table 9.4. The range of              |     |

|       | regulation is annotated, and the worst-case duty cycle of 0.25 is used for the passive component design                                                                                                                                          | 98  |

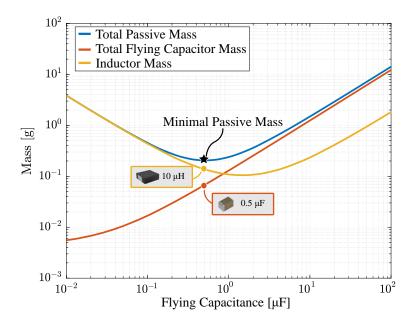

| 0 13  | Mass of the flying capacitors, inductor and combined total passive mass for a                                                                                                                                                                    | 90  |

| 3.10  | six-level FCML converter swept over flying capacitance values. This analysis is                                                                                                                                                                  |     |

|       | performed under the operating conditions described in Table 9.4 and the worst-                                                                                                                                                                   |     |

|       | case duty cycle shown in Fig. 9.12. The minimal mass is used to select the flying                                                                                                                                                                |     |

| 0 1 4 | capacitance and inductance used in design                                                                                                                                                                                                        | 96  |

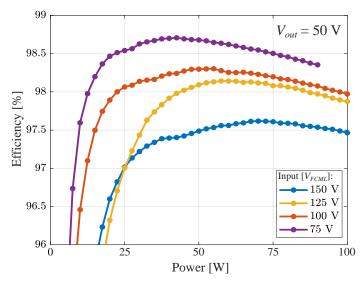

| 9.14  | Annotated photograph of the FCML converter used to validate the passive volume calculations. Constructed on a white soldermask, the hardware presented in [116]                                                                                  |     |

|       | is modified to include the passive component cases depicted in Fig. 9.13. $ \dots $                                                                                                                                                              | 100 |

| 9.15  | 7                                                                                                                                                                                                                                                |     |

|       | input voltages, showcasing the full range of regulation. Note: When the input                                                                                                                                                                    |     |

|       | voltage is 75 V, the output power is limited by the allowable capacitor voltage                                                                                                                                                                  |     |

|       | ripple.                                                                                                                                                                                                                                          | 100 |

| 9.16  | Photograph of passive components utilized in the hardware prototype. Compo-                                                                                                                                                                      |     |

|       | nents are chosen to minimize total passive mass in the Dickson converter and                                                                                                                                                                     |     |

|       | FCML converter. The passive components are shown in the same scale, and                                                                                                                                                                          |     |

|       | highlights the small volume and weight of the FCML converter which is designed                                                                                                                                                                   | 101 |

| 0.17  | to process minimal power                                                                                                                                                                                                                         | 101 |

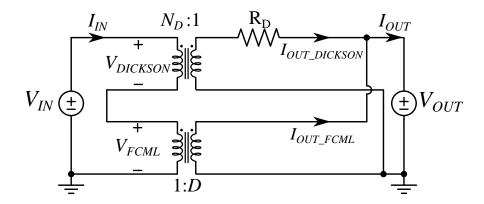

| 9.17  | v i                                                                                                                                                                                                                                              | 100 |

| 0.10  | converter is modeled as $R_D$                                                                                                                                                                                                                    | 102 |

| 9.18  | The measured output impedance for the Dickson converter over a range of output                                                                                                                                                                   | 109 |

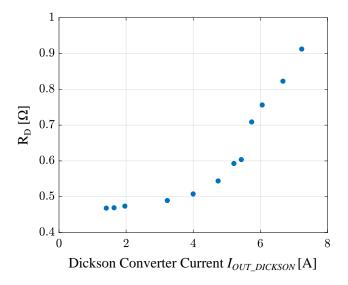

| 0.10  | currents with a fixed 600 V input $(V_{DICKSON})$                                                                                                                                                                                                | 103 |

| 9.19  | The required duty cycle (D) of the FCML converter to maintain a fixed 50 V                                                                                                                                                                       |     |

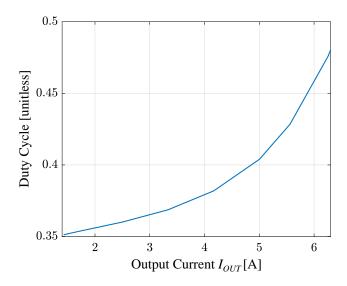

|       | output voltage $(V_{OUT})$ , given a 750 V input voltage $(V_{IN})$ over a range of load                                                                                                                                                         | 109 |

|       | conditions                                                                                                                                                                                                                                       | 103 |

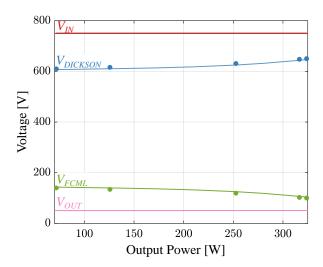

| 9.20 | The modeled Dickson converter $(V_{DICKSON})$ and FCML converter $(V_{FCML})$ in-       |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | put voltages for a regulated 50 V output voltage $(V_{OUT})$ , given a 750 V input      |     |

|      | voltage $(V_{IN})$ over a range of load conditions. The discrete data points show       |     |

|      | experimentally collected data, which match closely with the model                       | 104 |

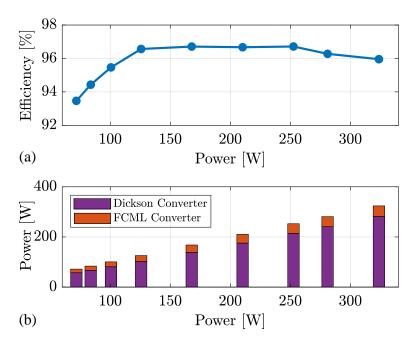

| 9.21 | (a) Measured efficiency of full composite converter operating at 750 V input $(V_{IN})$ |     |

|      | and regulating to a 50 V output $(V_{OUT})$ . (b) A breakdown of the portion of output  |     |

|      | power delivered by the Dickson converter and FCML converter                             | 105 |

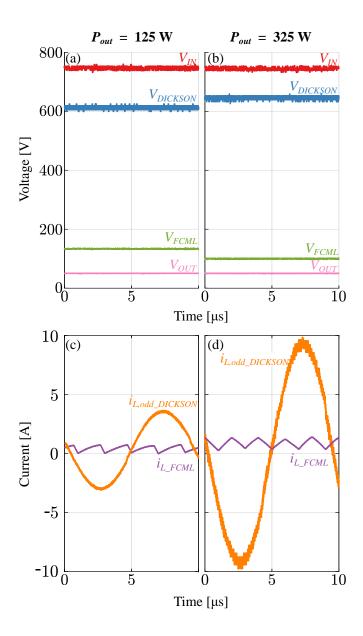

| 9.22 | Measured operating waveforms of the full composite converter, shown at the peak         |     |

|      | efficiency, 125 W, and heavy load, 325 W. As shown in (a) and (b) the input             |     |

|      | $(V_{IN})$ and output $(V_{OUT})$ voltages remain constant across load conditions due   |     |

|      | to the regulation of the FCML converter. However, as the load increases the             |     |

|      | impedance of the Dickson converter $(R_D)$ increases, as described in Fig. 9.18.        |     |

|      | Therefore the voltage split between the Dickson converter and FCML converter            |     |

|      | stages changes with load condition. Subfigures (c) and (d) show the measured            |     |

|      | inductor currents in the Dickson converter and FCML converter, showing the              |     |

|      | increased amplitude with increased load                                                 | 106 |

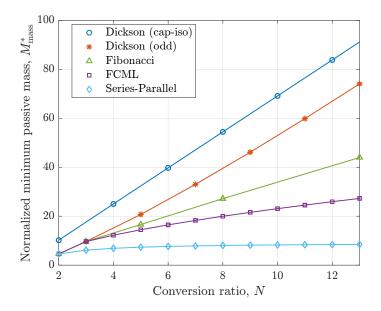

| 10.1 | Normalized minimum total passive mass versus conversion ratio for a selection of        |     |

| 10.1 | hybrid switched-capacitor converters operating at resonance                             | 108 |

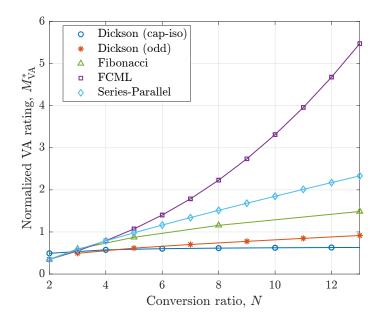

| 10.2 | Normalized switch stress versus conversion ratio for a selection of hybrid switched-    | 100 |

|      | capacitor converters operating at resonance, with optimally sized passive compo-        |     |

|      | nents.                                                                                  | 109 |

|      |                                                                                         |     |

## List of Tables

| 3.1 | Survey of state-of-art FCML converters                                        | 10 |

|-----|-------------------------------------------------------------------------------|----|

| 3.2 | Components used in electrical excitation circuit and calorimetric setup       | 18 |

| 3.3 | Experimentally evaluated capacitors                                           | 21 |

| 3.4 | Devices used in low frequency electrical setup                                | 25 |

| 4.1 | Flying capacitor design specifications                                        | 34 |

| 4.2 | Component list for 10-level FCML boost design                                 | 37 |

| 4.3 | FCML converter performance summary                                            | 39 |

| 6.1 | Experimental prototype specifications                                         | 63 |

| 6.2 | Flying capacitor design specifications                                        | 63 |

| 6.3 | Comparison of proposed shutdown techniques                                    | 70 |

| 8.1 | Component list for 10-level FCML boost design                                 | 81 |

| 8.2 | Performance summary                                                           | 81 |

| 9.1 | Composite converter operating specifications                                  | 86 |

| 9.2 | Capacitively-isolated Dickson converter operating specifications              | 87 |

| 9.3 | Components selected for Capacitively-Isolated Dickson converter hardware pro- |    |

|     | totype                                                                        | 91 |

| 9.4 | Regulating FCML converter operating specifications                            | 96 |

| 9.5 | Components selected for regulating FCML converter hardware prototype          | 99 |

#### Acknowledgments

I want to start by thanking Prof. Robert Pilawa-Podgurski. He has opened up doors and opportunities for me that I had never dreamed possible. Robert has shown me what it means to be a researcher, a communicator, a mentor and a teacher. He has supported, motivated and pushed me to become a better engineer and more importantly a better person. As I start my own research group, he is the standard to which I will hold myself. Thank you Robert, for your support and encouragement.

I want to thank my Dissertation Committee; Prof. Duncan Callaway, Prof. Kris Pister and Dr. Ansel Barchowsky. In particular, I would like to thank Ansel for his mentorship and support over the past five years. I have learned an incredible amount from working with Ansel and am continuously impressed with his passion and knowledge in the field. I would also like to thank Prof. Andrew Stillwell for serving on my Qualifying Exam Committee and for being a wonderful mentor and friend over the past six years.

I am immensely grateful for the time I spent at ETH Zurich and all I learned there. I want to thank Prof. Johann Kolar for allowing me to join his research group and to Dr. David Menzi and Dr. Jonas Huber for their mentorship during my stay. Additionally I would like to thank Dr. Spasoje Mirić, Dr. Pascal Niklaus, Morris Heller, Neha Nain, Gwendolin Rohner, Yunni Li and many more who made my time in Switzerland such a wonderful learning experience.

I am fortunate that Prof. Jessica Boles joined Berkeley this year. Jessica has been an extremely supportive mentor as I have gone through the academic job search and answered all of my small and large questions/fears/concerns. Thank you Jessica for being a voice of reason and encouragement during one of the most stressful parts of my career.

I am so fortunate that Maggie and I joined the research group at the same time. When we joined we both thought we were committing to a degree at UIUC; one move and six years later so much has changed. While we have both grown over the past six years, Maggie has remained one of my favorite people. Her opinion, both in technical matters and life, has helped calm me, encourage me and always steer me in the right direction. I am sad to not be working next to Maggie in the future but I am so grateful for getting to tackle graduate school with her by my side.

The best part of the Preliminary Exam was studying with Rose and the resulting friend-ship. Anytime I need to work through a decision, I know I can count on Rose to grab a cup of coffee or head out on a hike to talk through it. Anytime I have a crazy idea, I know that I can tell Rose about it and get both an honest opinion and support. She has (literally and figuratively) helped me learn to stop and smell the flowers, and appreciate my surroundings. Thank you Rose, for being a great conference roommate, brilliant engineer and an even better friend.

I am grateful for Nathan Brooks and all of the chats we have had over the past six years. Nathan is one of the few people I can talk to for hours about pretty much anything (or nothing) and lose track of time. I love that Nathan is always willing and happy to talk through a technical or personal challenge. I will miss having him nearby, but I know that his care and support will make him a wonderful professor.

I think I joined the Pilawa Research Group at the perfect time. The students who came before me did amazing research and I am fortunate for the opportunity to build and grow from that knowledge. In particular, I would like to thank Enver, Chris, Andrew, Zichao, Pourya, Joseph, Zitao and Sophia for all they taught me and for supporting me during the beginning of my degree. A huge thank you to Nathan Pallo who has been a wonderful mentor and taught me to love hardware design.

I want to thank the math mania/energy method/tutorial group: Nathan Ellis, Maggie, Rose and Nathan Brooks. Those whiteboard sessions were some of the most fun I had in graduate school (while attempting to solve integrals). Thank you again to Robert for supporting our endeavors. The most notable, giving a tutorial in Fiji, was a wonderful experience that I will never forget.

I want to thank Nicole for being a fantastic undergraduate researcher. I am grateful for Nicole's patience as I learned how to define projects and communicate my ideas. I know I am a better mentor because of my experience working with Nicole. While I am sad to no longer work directly with her, I am excited to see all amazing work she does in the future.

I am appreciative of the opportunity to work with Elisa this past year. Elisa is brilliant, and I am only disappointed that our time collaborating was too short. I cannot wait to see all the wonderful things Elisa accomplishes during the rest of her degree and beyond.

I want to thank Finn and Sahana for the dozens of coffee breaks, strange lunch conversations and laughter during our slow runs. You both make the group a more fun and happier environment. Thank you to the rest of the fun run crew: Yicheng, Rod, Elisa, Kelly and Nathan Biesterfeld. I enjoyed the post-run treats and the opportunity to explore more of Berkeley. Thank you to the rest of the Pilawa group who has made my time such a wonderful experience: Logan, Rahul, Jiarui, Haifah, Nagesh, Amanda, and Will.

Thank you to my friends who have supported me, well beyond the past six years. I want to thank Candice for being a wonderful sister/friend and for always having my back. Thank you to Haley and Joe for becoming our California family. I am ecstatic that we will be living even closer next year. I want to thank Holly and Allison for being so kind and supportive, especially during the wedding planning process. Thank you to Hannah, Troy and Clay who started as Chance's friends but I am now so happy to call mine too.

I am grateful to have married into such a supportive and wonderful family. Thank you Paul and Joyce for welcoming me into your family and for all of your help over the past six years. Additionally, thank you to Tammy and Dave for your support and fun adventures. Thank you to my extended family who have offered incredible support and encouragement. To Mindi and Joe, I am so happy you moved to Dallas and for all of the time we have spent together. Thank you both for all you have done in support of my career, and for always offering a hand or an ear. Thank you to Liz for always cheering me on and for providing me a second home during the beginning of my graduate degree.

While technically I started this degree six years ago, I think the process actually started over twenty years ago. I think about all the science fairs my parents helped me with, all the

games and performances they showed up to, and the hundreds of hours they spent driving me across the country to visit colleges. My parents believed in me and showed me I was capable of handwork and determination every day growing up. They gave me a safe environment to learn how to fail and chase my curiosity, two skills that have greatly helped me during my studies. Thank you to my dad for convincing me that changing tires was a fun game and showing me that tools belong in the hands of girls too. Thank you to my mom for believing I am capable of anything, and for reminding me of that pretty much every day. Thank you both for all of the sacrifices, time, sweat and love, it means everything.

Lastly, I want to thank my husband, Chance, to whom this thesis is dedicated. I am incredibly proud of the life we have built together and the people we have grown into. Thank you for listening to all my presentations, reading my papers, and for being the only music educator who can list the benefits of capacitive-based power converters. You have supported me every day through this process, showing me that you believe in me and helping me believe in myself. I am incredibly grateful for all the times you took a gamble on me and my crazy ideas, moving to California, coming with me to Switzerland, and getting married in the middle of interviewing for jobs. I am grateful for the risks you took during the job search process and for betting on my success. I am looking forward to returning the support as you start your graduate degree. With you by my side I know we can handle whatever comes next and I am so excited for our next adventure.

### Chapter 1

### Introduction

#### 1.1 Introduction

The need for high performance power converters is growing as there is an increase both in the number of renewable energy sources, such as solar and wind energy and electric loads, such as electric vehicles. It is estimated that by 2030, over 80% of electricity in the United States will flow through at least one power converter [1]. The need for further electrification expands beyond terrestrial applications and into sky and space.

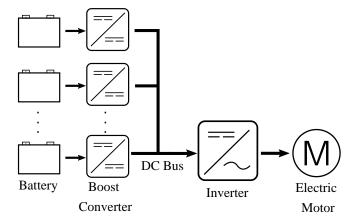

By 2030, the number of aircraft passengers is expected to triple [2]. Hybrid electric, and eventually fully electric aircraft, offer solutions in reduction of maintenance, noise and emissions [3]. However, to enable hybrid electric aircraft, we need innovation within the electric drivetrain, requiring extremely light-weight and efficient power converters [4].

Space exploration has seen a recent surge in interest, both in public and private organizations. With the goal of future human exploration of Mars, we need further technology advancements in robotic exploration, lunar micro-grids and satellites [5]. All of these technologies require high performance power converters which are light-weight and can handle the radiation effects of the harsh space environment.

This thesis focuses on these challenges associated with future electric aircraft and space exploration, where light-weight, efficient and reliable power conversion is crucial. The design of several power converters is described, and for each system the requirements and optimal performance are considered. Moreover, this thesis also tackles fundamental challenges within the design of power converters, such as the losses of key components, the control of converters to ensure safe shutdown procedures and the combination of multiple converters to utilize partial power processing.

#### 1.2 Organization of Thesis

# Chapter 2: Fundamentals of Hybrid Switched-Capacitor and Multilevel Converters

Hybrid switched-capacitor converters offer the potential for extremely dense designs, due to their use of energy-dense capacitors as the primary energy storage element. Moreover, hybrid switched-capacitor topologies result in lower voltage stress across the switches, allowing for designs which utilize high performing low voltage devices to achieve higher voltages at the input/output terminals. This chapter presents the motivation for utilizing hybrid switched-capacitor converters in aerospace applications, where light-weight designs are critical for future technology development.

#### Chapter 3: Characterization and Modeling of Ceramic Capacitor Losses

Recent work on hybrid switched-capacitor converters has demonstrated exceptionally high efficiencies and power densities through the use of multilayer ceramic capacitors (MLCCs). However, when used in such converters as the main energy transfer components, the capacitors experience high voltage and current ripple often under large dc voltage bias. Yet, capacitor characterization is typically done only with small signal excitation and under low or no dc bias, yielding highly inaccurate loss models. This chapter presents a technique for obtaining detailed loss characterizations of MLCCs under more realistic operating conditions through a carefully designed calorimetric setup. Experimental results from several types of MLCCs are presented over a wide range of operating conditions. Finally, a linear model is presented to accurately estimate MLCC losses.

# Chapter 4: Flying Capacitor Multilevel Converter for Hybrid Electric Aircraft

Multilevel switched-capacitor converters, such as the flying capacitor multilevel (FCML) converter, offer high energy density and efficiency, over a wide voltage range, making them suitable for applications in electrified aircraft. However, concerns of reliability due to the increased number of active and passive components have limited the use of high-level count converters in aircraft applications. We present detailed component selection and design techniques to achieve this goal, along with a high-performance 28.2 kW/kg, 99.52% efficient high-voltage dc-dc step-up power converter for experimental validation.

# Chapter 5: Flight Qualification of Flying Capacitor Multilevel Converter

This chapter addresses the challenges of designing a high-level count converter with the goal of extremely high efficiency and power density, with maintained reliability and flight readiness. Building on the design presented in Chapter 4, the full system design, control and fault tolerance is described, with a focus on robustness. Finally, we demonstrate successful completion of critical flight qualification testing of the hardware prototype, including thermal, shock and vibration.

#### Chapter 6: Safe Shutdown of Flying Capacitors Multilevel Converters

This chapter explores the dynamic behavior of the flying capacitor multilevel (FCML) converter during unplanned shutdown. A model for a general N-level FCML converter is developed, which captures capacitor non-linearities, component leakage paths, and body diode behavior. This chapter highlights how switch voltage ratings may be exceeded during unplanned shutdown, and proposes several mitigation strategies. Using a ten-level FCML converter hardware prototype, the time-domain behavior of the model is verified, and a successful hardware mitigation strategy is demonstrated which ensures safe and rapid converter shutdown.

# Chapter 7: Overview of Converter Requirement in Space Applications

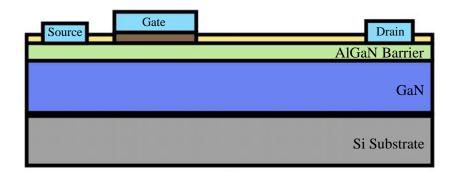

In the harsh environment of space, the design of power converters is particularly challenging. This chapter explains some of the types of radiation experienced in space and how wide-bandgap GaN devices can be utilized to achieve radiation hardened designs. Moreover, hybrid switched-capacitor converters are further motivated for their low switch stress and passive component mass.

#### Chapter 8: Flying Capacitor Multilevel Converter Designed for Electric Propulsion

Recent work has shown the high efficiency and high power density of multilevel converters in terrestrial applications. This chapter applies the advantages of multilevel converters to space applications by investigating a ten-level flying capacitor multilevel boost converter for compact and efficient high-voltage generation. The converter exploits the low on-state resistance and reduced parasitic capacitance, as well as radiation hardened qualities of GaN power semiconductor switches to achieve high efficiency and power density. Practical challenges such as driving a large number of high-side switches while maintaining high-voltage

creepage and clearance requirements are addressed through innovative cascaded bootstrap techniques for gate driver power, and a new commutation loop design with reduced parasitic inductance. The performance benefits of these techniques are demonstrated in a 1 kW, 100 V to 500 V step-up dc-dc hardware prototype, achieving 99.1% efficiency and a power density of  $24~\mathrm{kW/kg}$ .

#### Chapter 9: Composite Converter Designed for Space Applications

To enable next generation robotic space exploration, innovations in the area of high step-down voltage converters is necessary. This chapter explores the use of multilevel hybrid switched-capacitor power converters which have unique advantages in mass-critical and harsh radiation space environments. A composite converter topology is presented which utilizes two different hybrid switched-capacitor converters in a partial power processing system. First, a fixed-ratio capacitively-isolated resonant Dickson converter is designed for a high step-down conversion ratio and to process the majority of the system power. In addition, a flying capacitor multilevel (FCML) converter is designed to provide regulation over a wide range of input voltages. The optimization of each converter is discussed with careful attention dedicated to the minimization of passive component mass. The hardware results for each converter and the full composite system are presented, showcasing a system efficiency of over 96% for a nominal 15:1 conversion ratio with regulation capability.

#### Chapter 10: Conclusion

To conclude this thesis, a comparison of hybrid SC topologies is presented. The minimized passive component mass and normalized switch stress are computed which allows for a comparison of different topologies. The trade-offs for these metrics are discussed, highlighting necessary future work in characterization of losses and converter performance.

### Chapter 2

### Fundamentals of Hybrid Switched-Capacitor Converters

#### 2.1 Motivation for Hybrid Switched-Capacitor Converters

#### Passive Component Utilization

Conventional power converters use inductors as the primary energy storage element. For example, the conventional buck converter, shown in Fig. 2.1 is a type of switched-inductor converter which is typically used for step-down conversion. These converters have been historically used due to their uncomplicated control (requiring only one active device in the simplest case) and reliable performance. However, recent advancements in digital control, high-bandgap devices and energy-dense capacitors have opened the possibility for alternative topologies.

Within power converters, the two primary components used for storing and processing energy are capacitors and inductors. While inductors are typically used, commercially available capacitors have the potential for over 1000x higher energy density than inductors [6], as shown in Fig. 2.2. Therefore, motivating the use of capacitors as the primary energy storage element instead of inductors to design compact converters.

Figure 2.1: Conventional switched-inductor style buck converter.

**Figure 2.2:** Calculated energy density for a survey of commercially available inductors and capacitors [6]. Note, the most energy-dense capacitor has over 1000x higher energy density than the most energy-dense inductor. This difference in component energy density motivates the use of capacitors as the primary energy storage element to design compact converter topologies.

Hybrid switched-capacitor (SC) converters are one family of topologies which use capacitors as the primary energy storage element. The simplest 2-to-1 hybrid SC converter, known commonly as a doubler topology, is shown in Fig. 2.3. The capacitor, C, is known as a flying capacitor as it is not referenced to ground. This flying capacitor is used as the primary energy storage element and the inductor, L, is utilized for filtering and to enable soft-charging of the flying capacitor [7]–[9], thus greatly reducing the required volt-second on the inductor compared to a switched-inductor converter. Note, there are topologies which do not include any inductance. These topologies, pure SC converters, can suffer from large losses due to capacitor charge sharing. Moreover, by adding in the small inductor to a SC converter, the topologies can be operated at-resonance, achieving zero current switching (ZCS), above resonance to reduce converter impedance and component sensitivity and in some cases achieve zero voltage switching (ZVS) and regulation.

In this thesis, two specific converter topologies will be discussed in detail: The flying capacitor multilevel (FCML) converter [10], shown in Fig. 2.4 and the hybrid SC Dickson converter [11], a variant of which is shown in Fig. 2.5.

Figure 2.3: A simple 2-to-1 hybrid SC buck converter.

Figure 2.4: An N-level FCML buck converter.

Figure 2.5: An N-level Dickson converter.

#### **Active Component Utilization**

As shown in Fig. 2.3, the hybrid SC converter does require additional switches compared to the conventional buck converter. These switches require additional control and advanced gate drive solutions, challenges which will be discussed throughout this thesis. However, in many hybrid SC topologies, the switches only block a fraction of the high-side voltage, instead of the entire high-side voltage, as is the case in the conventional buck converter. This decreased switch stress is due to the flying capacitors which block a portion of the high-side voltage from the switches. As a result, lower voltage switches can be utilized, while still achieving higher voltages at the input/output terminals.

Fig. 2.6 shows a survey of commercially available GaN devices and their blocking voltage versus figure-of-merit. Here the figure-of-merit is defined as the multiplication of the parasitic capacitance  $(C_{oss})$ , on-resistance  $(R_{ds})$  and package volume [12]. Therefore, lower figure-of-merit corresponds to lower losses and smaller devices. As shown in Fig. 2.6, the lower

**Figure 2.6:** A survey of commercially available GaN devices and the corresponding figure-of-merit, where a lower figure-of-merit corresponds to higher performance.

rated voltage devices have significantly lower figure-of-merit compared to higher voltage devices, motivating the use of lower voltage switches to achieve lower losses and smaller converter volume. Across other switch technologies, such as silicon and SiC, the trend of higher performance at lower blocking voltages is also verified [13], [14]. Due to GaN devices demonstrating highest performance at the voltage levels investigated for this thesis (100 V-650 V), GaN is utilized throughout this work. Moreover, as discussed in Chapter 7, GaN devices have higher tolerance to radiation effects [15], making them preferable in space applications.

#### 2.2 Suitability for Aerospace Applications

This thesis focuses on high-performance power converters for aerospace applications. Specifically, Chapters 4-5 demonstrate a design for hybrid electric aircraft and Chapters 7-9 focus on designs with application in space. In both of these applications, light-weight designs are crucial for enabling future technologies.

Designing for minimal mass, opposed to minimal volume, is difficult, since often manufacturers do not include component mass on datasheets. Recent work [6] has provided a model for commercially available capacitors and inductors, to approximate component mass

based on the component's volume (which is typically provided on datasheets). Using this model, Fig. 2.7 shows the comparative specific energy density of commercially available capacitors and inductors. The specific energy density of capacitors is over 10,000x higher than inductors, therefore motivating the use of capacitors in mass critical applications even more than in volume critical applications.

**Figure 2.7:** Calculated *specific* energy density for a survey of commercially available inductors and capacitors [6]. Note, the most energy-dense capacitor has over 10,000x higher energy density than the most energy dense inductor.

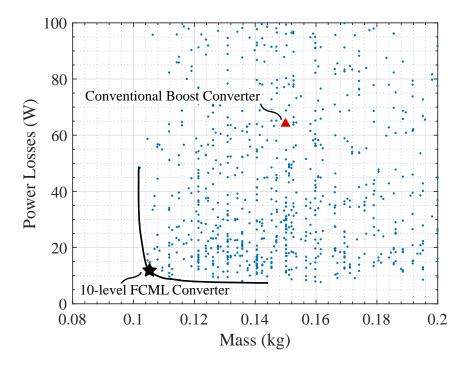

For example, in Chapter 4 the optimization of a converter designed for hybrid electric aircraft is presented. Shown in Fig. 2.8, a 10-level FCML converter, a type of hybrid SC converter shown in Fig. 2.4, results in significantly lower losses and lower mass compared to a conventional switched-inductor boost converter.

There are a number of other specific challenges that exist when designing for aerospace applications. Concerns of reliability, efficiency and resiliency to radiation effects will be discussed throughout the following section and the remainder of this thesis.

#### 2.3 Hybrid Switched-Capacitor Converter Challenges

Hybrid SC converters have gained recent interest due in large part to advancements in devices, both wide-bandgap switches and capacitors. However, there still exist many challenges

**Figure 2.8:** Pareto front optimization, where the blue dots represent possible FCML converter designs. The star represents an optimized 10-level FCML converter which minimizes both loss and weight. A conventional boost converter is shown, optimized around the same operating conditions, modeled with 1.2 kV SiC FETs. The design of this FCML converter is described in Chapter 4.