# Millimeter-Wave Receiver and Package Design Close to the Device Activity Limits

Nima Baniasadi

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2023-40 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2023/EECS-2023-40.html

May 1, 2023

# Copyright © 2023, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Acknowledgement

I want to express my profound gratitude to my research advisor, Prof. Ali M. Nikne- jad. He provided me with excellent academic guidance and supported me personally, and taught me to be patient when facing various problems. I also thank Prof. Mehrdad Sharif Bakhtiar and Prof. Ali Fotowat Ahmady, my undergraduate professors at Sharif University of Technology, from whom I learned a lot.

This journey would not have been possible without the support of my family and friends. I am grateful to my parents and brother; they have always helped me wherever and whenever I needed them the most. I would also like to thank my friends who provided me with a warm and supportive environment during the years of the pandemic and political crisis.

#### Millimeter-Wave Receiver and Package Design Close to the Device Activity Limits

by

#### Nima Baniasadi

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Elad Alon Professor William L. Holzapfel

Fall 2021

### Millimeter-Wave Receiver and Package Design Close to the Device Activity Limits

Copyright 2021

by

Nima Baniasadi

#### Abstract

Millimeter-Wave Receiver and Package Design Close to the Device Activity Limits

by

#### Nima Baniasadi

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali M. Niknejad, Chair

For several decades, rapid improvements in the semiconductor industry, particularly the scaling of CMOS processes, have enabled high-speed wireless communications. However, the scaling of CMOS processes seems to be paying off less and less. Moreover, as the carrier frequency increases, the limited power of the CMOS chip can be quickly dissipated by passive elements or at the edges of the chip. The next generations of high-speed radios will require co-design and co-optimization of the chip and package to ensure that the highest data rates are achieved.

This work addresses the design of a packaged wideband millimeter-wave radio. The fundamental limitations of the CMOS process for millimeter-wave applications are examined. Noise measure theory is used to design low-noise amplifiers near the device activity limits. New techniques for minimizing the insertion loss of passive matching networks are proposed. The challenges of a package design are investigated, and an optimized transition structure is proposed. Finally, a 140GHz wideband receiver operating at half the transit frequency of the technology is implemented.

To my parents for their endless love and support

and to my brother who made me laugh countless times.

# Contents

| $\mathbf{C}_{\mathbf{C}}$ | onter                  | nts                                                               | ii   |

|---------------------------|------------------------|-------------------------------------------------------------------|------|

| $\mathbf{Li}$             | $\operatorname{st}$ of | Figures                                                           | iv   |

| Li                        | $\operatorname{st}$ of | Tables                                                            | viii |

| $\mathbf{A}$              | ckno                   | wledgements                                                       | ix   |

| 1                         | Intr                   | roduction                                                         | 1    |

|                           | 1.1                    | Connectivity                                                      | 1    |

|                           | 1.2                    | Capacity                                                          | 3    |

|                           | 1.3                    | Silicon limits                                                    | 14   |

|                           |                        | Transit Frequency $f_t$                                           | 15   |

|                           |                        | Analog Efficiency $f_t \frac{g_m}{I_d}$                           | 15   |

|                           |                        | Speed-Power Trade-off                                             | 17   |

|                           |                        | Termination Levels vs. Frequency                                  | 19   |

|                           |                        | Large Signal Power Gain vs. Frequency                             | 19   |

|                           |                        | Detailed Model with Extrinsic Parasitics                          | 20   |

|                           | 1.4                    | Challenges                                                        | 24   |

| 2                         | Mil                    | limeter-wave LNA Design                                           | 27   |

|                           | 2.1                    | Introduction                                                      | 27   |

|                           | 2.2                    | Derivation of the Noise Measure                                   | 30   |

|                           | 2.3                    | Examples                                                          | 38   |

|                           |                        | CMOS Noise Measure                                                | 38   |

|                           |                        | Multiple Active Devices                                           | 40   |

|                           | 2.4                    | Design of Low-Noise CS Amplifiers with Single Feedback Component  | 41   |

|                           | 2.5                    | Design of Low-Noise CS Amplifiers with General Peripheral Network | 43   |

|                           | 2.6                    | Optimal Bias Condition                                            | 45   |

|                           | 2.A                    | Simulation Flow of Minimum Noise Measure                          | 47   |

| 3                         | 140                    | GHz Receiver Design                                               | 49   |

|                           |                        | Low-Loss LC Matching Networks                                     | 49   |

|   | 3.2                                    | Transformers                                                                                                                                                                                                                              | 55                                                              |

|---|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|   | 3.3                                    | High Quality-Factor Inductors                                                                                                                                                                                                             | 63                                                              |

|   | 3.4                                    | Low Noise Active Balun                                                                                                                                                                                                                    | 65                                                              |

|   | 3.5                                    | Interstage Amplifiers                                                                                                                                                                                                                     | 71                                                              |

|   | 3.6                                    | I/Q Splitter                                                                                                                                                                                                                              | 78                                                              |

|   | 3.7                                    | Mixer Design                                                                                                                                                                                                                              | 79                                                              |

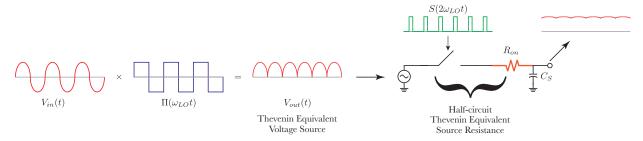

|   |                                        | Current Mode Mixer                                                                                                                                                                                                                        | 82                                                              |

|   |                                        | Voltage Mode Mixer                                                                                                                                                                                                                        | 82                                                              |

|   | 3.8                                    | Baseband Amplifier                                                                                                                                                                                                                        | 90                                                              |

|   | 3.9                                    | Full Receiver Performance                                                                                                                                                                                                                 | 04                                                              |

| 4 | Chi                                    | p-to-Package Transition 1                                                                                                                                                                                                                 | 07                                                              |

| - | 4.1                                    |                                                                                                                                                                                                                                           | 07                                                              |

|   | 4.2                                    |                                                                                                                                                                                                                                           | 08                                                              |

|   | 4.3                                    |                                                                                                                                                                                                                                           | 14                                                              |

|   | 4.4                                    | *                                                                                                                                                                                                                                         | 19                                                              |

|   |                                        |                                                                                                                                                                                                                                           |                                                                 |

| _ | ъ                                      |                                                                                                                                                                                                                                           |                                                                 |

| 5 |                                        |                                                                                                                                                                                                                                           | 23                                                              |

| 5 | 5.1                                    | Introduction                                                                                                                                                                                                                              | 23                                                              |

| 5 | 5.1<br>5.2                             | Introduction                                                                                                                                                                                                                              | 23<br>24                                                        |

| 5 | 5.1<br>5.2<br>5.3                      | Introduction15Design Principles15Design Considerations15                                                                                                                                                                                  | 23<br>24<br>25                                                  |

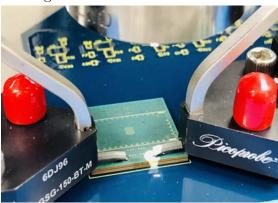

| 5 | 5.1<br>5.2                             | Introduction15Design Principles15Design Considerations15Prototype Design and Measurement Results15                                                                                                                                        | 23<br>24<br>25<br>28                                            |

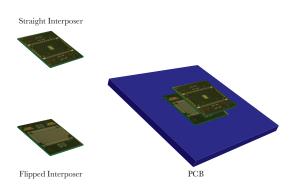

| 5 | 5.1<br>5.2<br>5.3                      | Introduction15Design Principles15Design Considerations15Prototype Design and Measurement Results15Interposer Technology15                                                                                                                 | 23<br>24<br>25<br>28<br>28                                      |

| 5 | 5.1<br>5.2<br>5.3                      | Introduction15Design Principles15Design Considerations15Prototype Design and Measurement Results15Interposer Technology15Channel Design Trade-offs15                                                                                      | 23<br>24<br>25<br>28<br>28<br>28                                |

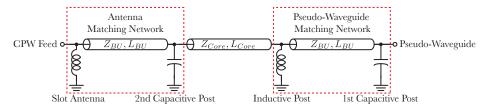

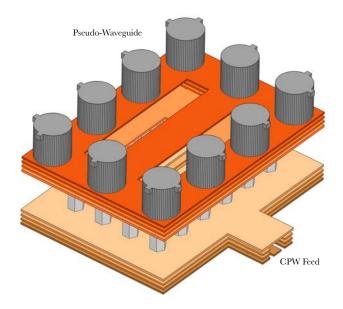

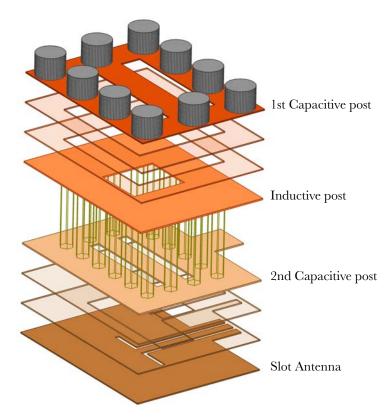

| 5 | 5.1<br>5.2<br>5.3                      | Introduction15Design Principles15Design Considerations15Prototype Design and Measurement Results15Interposer Technology15Channel Design Trade-offs15Antenna Design with Distributed Matching Network15                                    | 23<br>24<br>25<br>28<br>28<br>28<br>30                          |

| 5 | 5.1<br>5.2<br>5.3<br>5.4               | Introduction15Design Principles15Design Considerations15Prototype Design and Measurement Results15Interposer Technology15Channel Design Trade-offs15Antenna Design with Distributed Matching Network15Prototype Performance15             | 23<br>24<br>25<br>28<br>28<br>28<br>30<br>30                    |

| 5 | 5.1<br>5.2<br>5.3                      | Introduction15Design Principles15Design Considerations15Prototype Design and Measurement Results15Interposer Technology15Channel Design Trade-offs15Antenna Design with Distributed Matching Network15Prototype Performance15             | 23<br>24<br>25<br>28<br>28<br>28<br>30                          |

| 5 | 5.1<br>5.2<br>5.3<br>5.4               | Introduction15Design Principles15Design Considerations15Prototype Design and Measurement Results15Interposer Technology15Channel Design Trade-offs15Antenna Design with Distributed Matching Network15Prototype Performance15Conclusion15 | 23<br>24<br>25<br>28<br>28<br>28<br>30<br>30                    |

|   | 5.1<br>5.2<br>5.3<br>5.4               | Introduction                                                                                                                                                                                                                              | 23<br>24<br>25<br>28<br>28<br>28<br>30<br>30<br>33              |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>Cor | Introduction                                                                                                                                                                                                                              | 23<br>24<br>25<br>28<br>28<br>28<br>30<br>30<br>33<br><b>34</b> |

# List of Figures

| 1.1  | Maslow's hierarchy of human needs with an additional new layer $[1]$                 | 2        |

|------|--------------------------------------------------------------------------------------|----------|

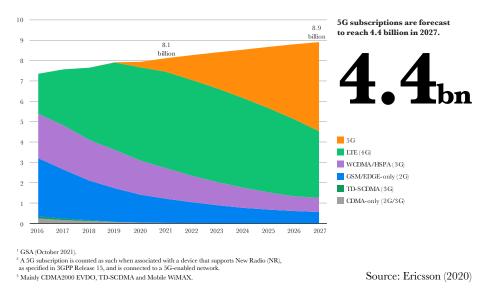

| 1.2  | Mobile subscriptions by technology (billions)                                        | 2        |

| 1.3  | Backhaul capacity per distributed site                                               | 3        |

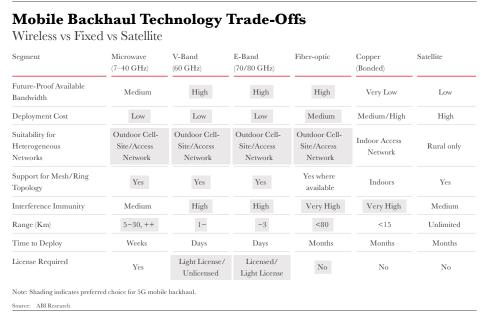

| 1.4  | Mobile backhaul technology trade-Offs                                                | 4        |

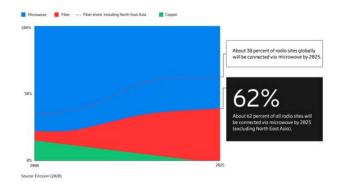

| 1.5  | Global backhaul media distribution                                                   | 4        |

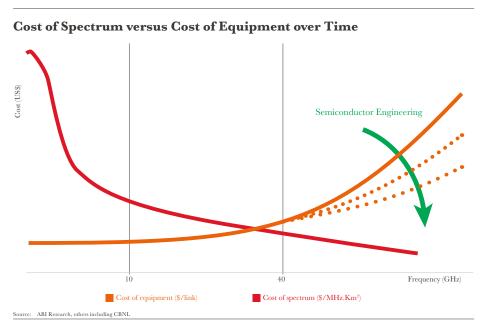

| 1.6  | Cost of spectrum vs. cost of equipment over time                                     | 5        |

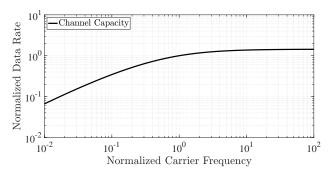

| 1.7  | Capacity vs. carrier frequency                                                       | 6        |

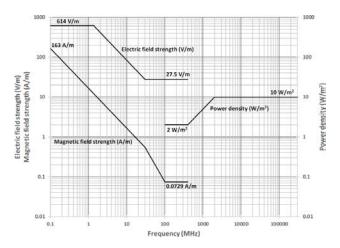

| 1.8  | Safe radiation levels for persons in unrestricted environments [2]                   | 6        |

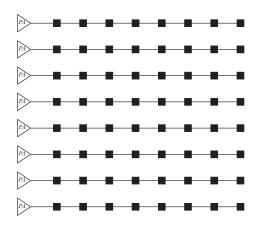

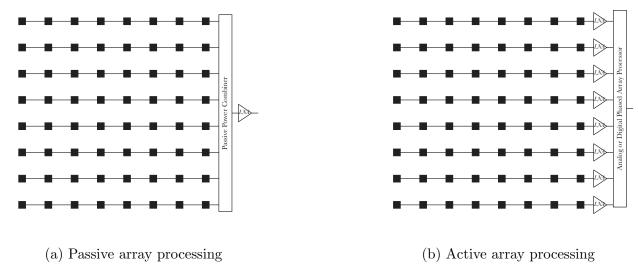

| 1.9  | An $8 \times 8$ 2-D transmitter phased array with 1-D steering capability            | 8        |

| 1.10 | An $8 \times 8$ 2-D receiver phased array                                            | 9        |

| 1.11 | 1-D Phased Array                                                                     | 10       |

| 1.12 | Channel capacity vs. carrier frequency for a link based on Table. 1.2                | 11       |

| 1.13 | Spectral efficiency vs. carrier frequency for a link based on Table. 1.2             | 12       |

| 1.14 | The output power of published power amplifiers as a function of carrier frequency[3] | 13       |

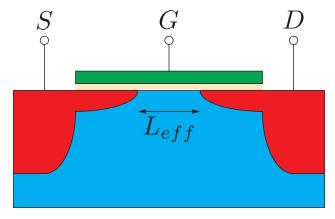

| 1.15 | A simple model of planar CMOS transistor                                             | 14       |

| 1.16 | Estimating the mobility of the device from simulations for different current den-    |          |

|      | sities $(A/\mu m)$                                                                   | 16       |

| 1.17 | Parasitic elements of a single-finger transistor                                     | 21       |

|      | A simple planar transistor in layout view and its 3D representation                  | 23       |

| 1.19 | Parasitic elements of a transistor                                                   | 23       |

| 1.20 | Simplified transistor model                                                          | 25       |

| 1.21 | Packaged millimeter-wave radios                                                      | 26       |

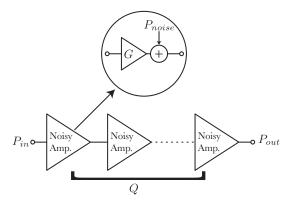

| 2.1  | Chain of identical noisy amplifiers                                                  | 28       |

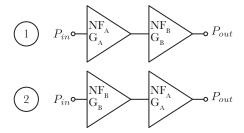

| 2.2  | Two scenarios for cascading non-identical amplifiers                                 | 29       |

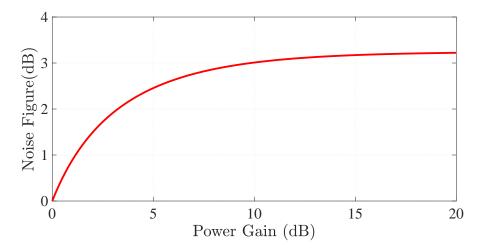

| 2.3  | Noise figure vs. power gain                                                          | 31       |

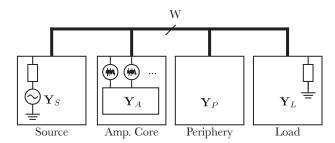

| 2.4  | Y-parameter model of the circuit                                                     | 31       |

| 2.5  | Thevenin equivalent circuit                                                          | 32       |

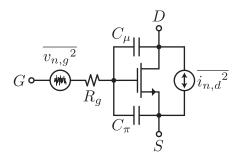

| 2.6  | CMOS transistor parasitic model                                                      | 38       |

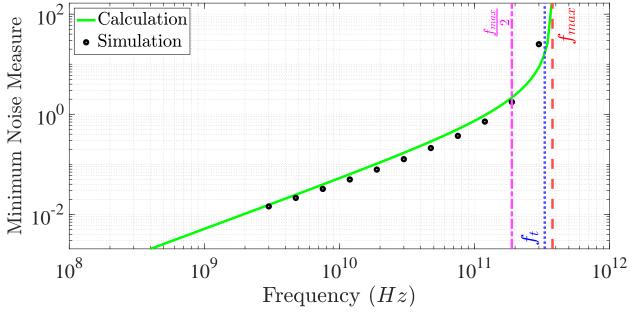

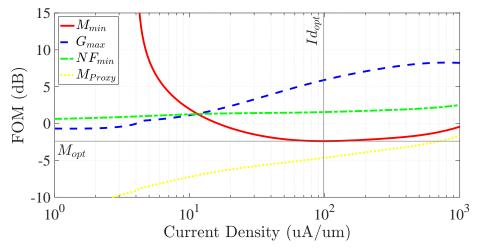

| 2.7  | Noise measure vs. frequency                                                          | 40       |

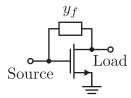

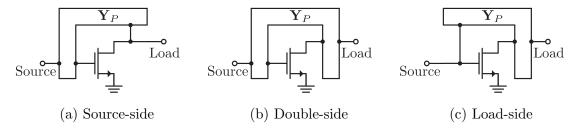

| 2.8  | Using a feedback component to improve the input reflection with minimum noise        | 40       |

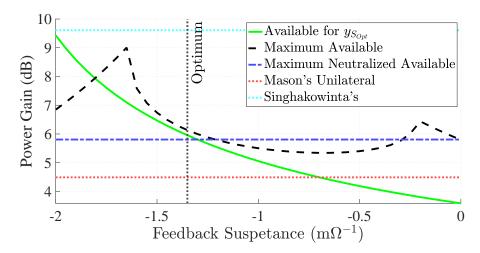

| 2.9  | measure                                                                              | 42<br>43 |

|      |                                                                                      |          |

|       | 1 1                                                                                                                          | 43     |

|-------|------------------------------------------------------------------------------------------------------------------------------|--------|

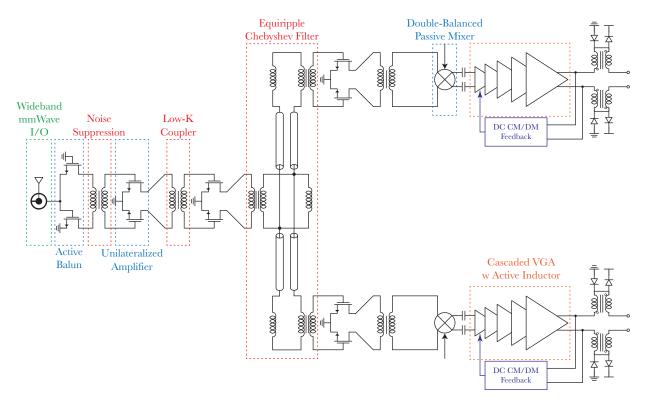

| 3.1   | Block diagram of the receiver chain                                                                                          | 50     |

| 3.2   | Single-component matching network                                                                                            | 50     |

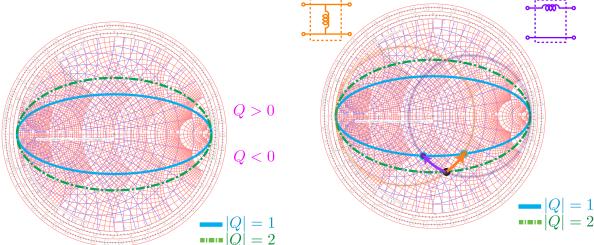

| 3.3   | Definition of Q and moving between different Q-contours                                                                      | 52     |

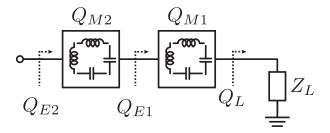

| 3.4   | Cascade of several elements                                                                                                  | 52     |

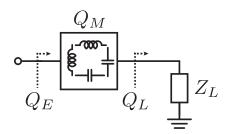

| 3.5   | Circuit model used to obtain the maximum transmission                                                                        | 52     |

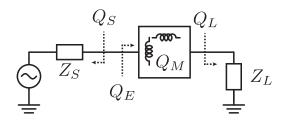

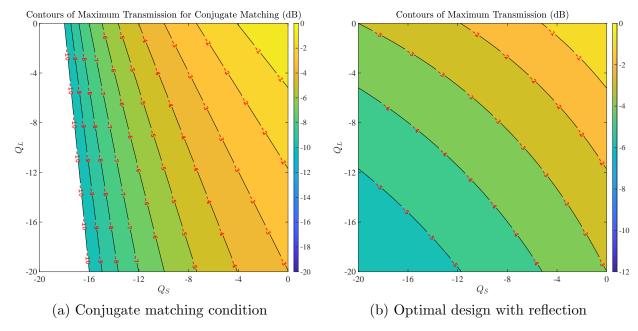

| 3.6   | The optimal input quality factor for the network with $Q_M = 20$                                                             | 54     |

| 3.7   | Contours of total transmission loss for different source and load quality factors                                            |        |

|       | with $Q_M = 20 \dots $ | 55     |

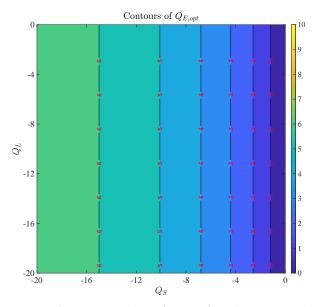

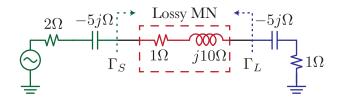

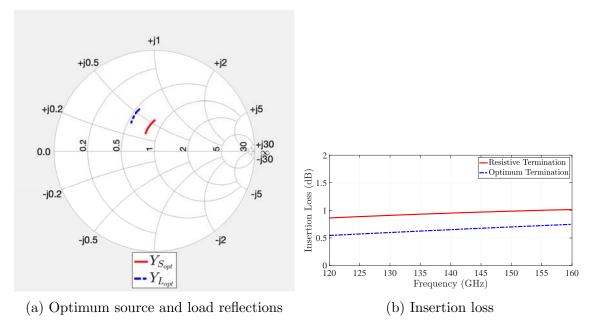

| 3.8   | Asymmetry of source and load reflections of a lossy matching network                                                         | 55     |

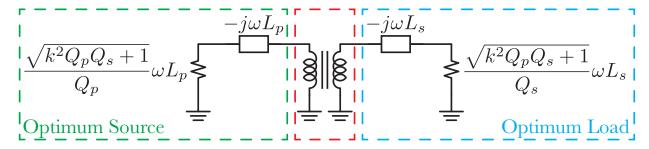

| 3.9   | Optimal loading condition to achieve the minimum insertion loss of the transformer                                           | 58     |

| 3.10  | Step-up and step-down matching networks with the same insertion loss                                                         | 59     |

| 3.11  | Gate and drain quality factor vs. frequency                                                                                  | 60     |

| 3.12  | Symbolic structure of a stacked single-turn transformer                                                                      | 60     |

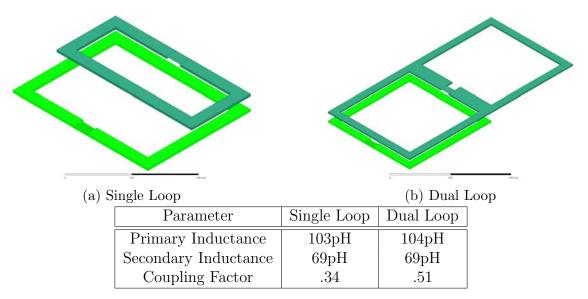

|       | 1 0                                                                                                                          | 61     |

| 3.14  | Transformer equivalents                                                                                                      | 61     |

| 3.15  | Example of equivalent transformer topologies                                                                                 | 62     |

| 3.16  | Coupling factor of a transformer as a function of the center-to-center distance,                                             |        |

|       | normalized to the width of each loop                                                                                         | 62     |

|       |                                                                                                                              | 63     |

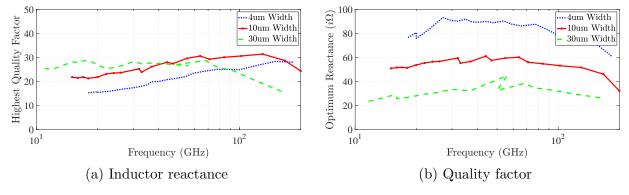

|       | Optimal inductors at different frequencies                                                                                   | 65     |

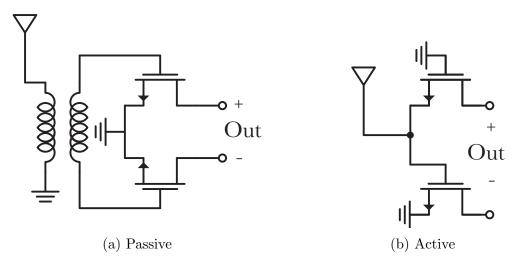

|       | Active and passive balun topologies                                                                                          | 66     |

|       |                                                                                                                              | 66     |

|       | 1                                                                                                                            | 68     |

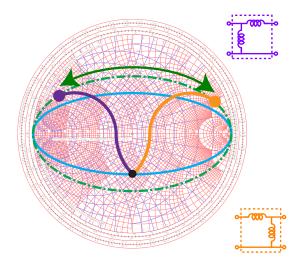

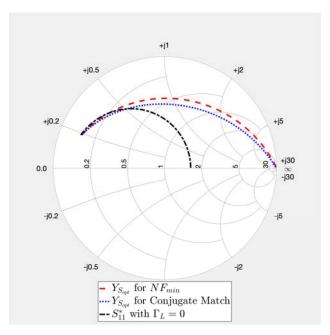

|       | Optimum source reflection in different cases                                                                                 | 70     |

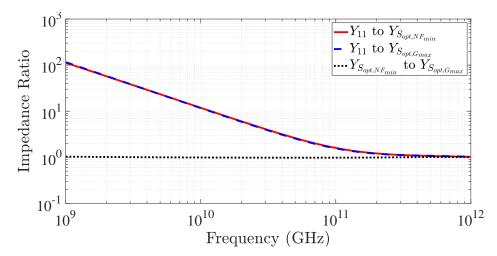

|       | Optimum impedance ratios vs. Frequency                                                                                       | 71     |

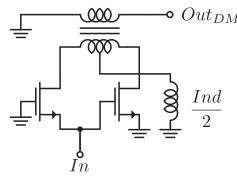

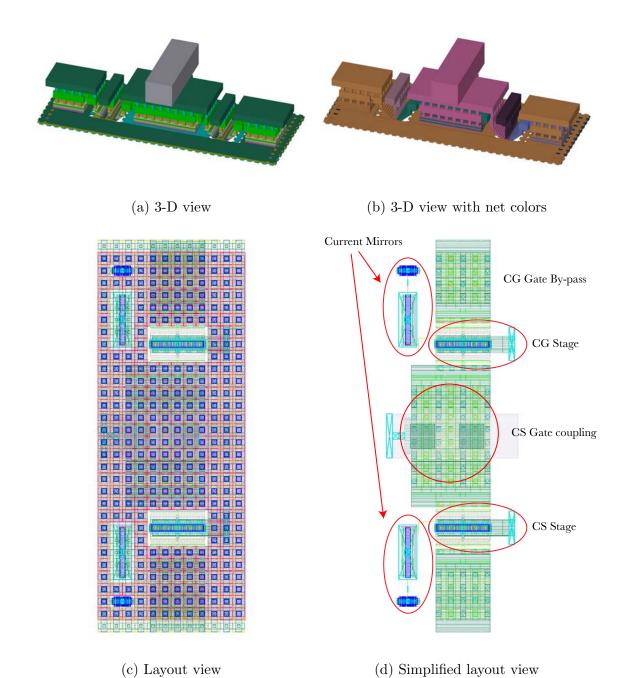

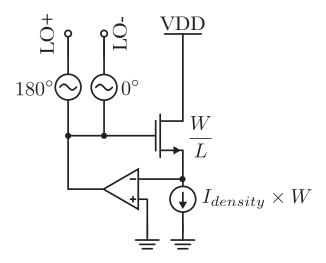

|       | Active balun transistor core                                                                                                 | 72     |

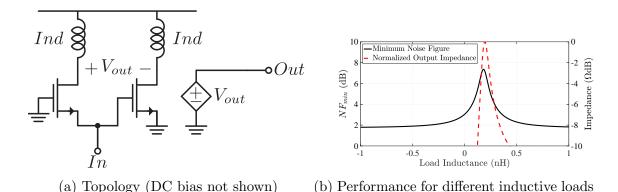

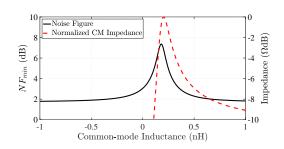

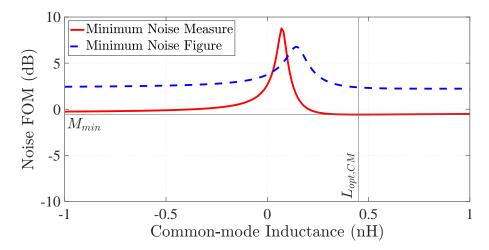

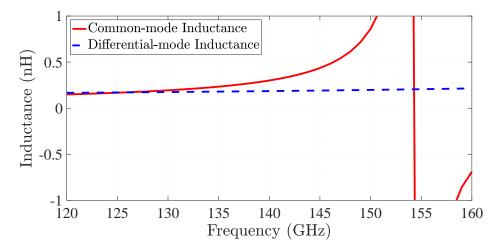

|       | Noise performance vs. different output common-mode inductance                                                                | 73     |

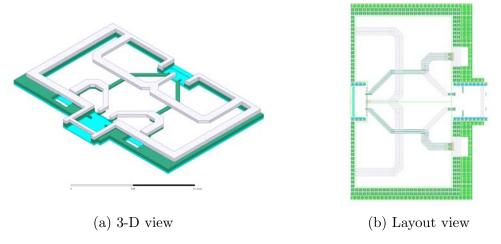

|       | Matching network of the active balun.                                                                                        | 73     |

|       | <u> </u>                                                                                                                     | 74     |

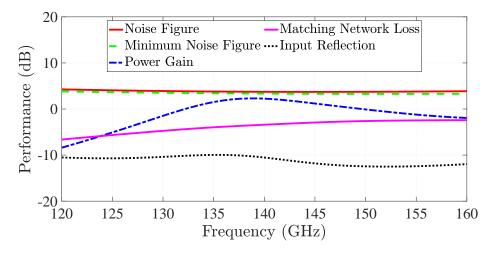

|       | Performance of the active balun with matching network                                                                        | 74     |

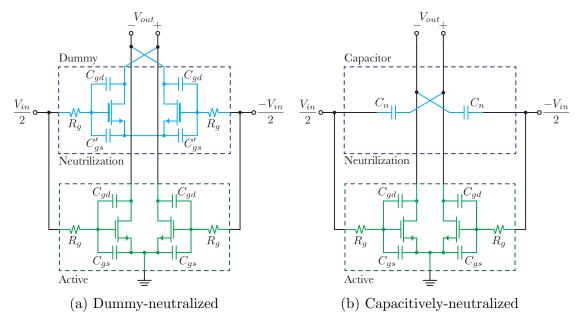

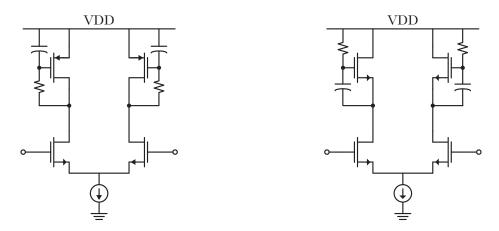

|       | Neutralized pseudo-differential CS amplifiers                                                                                | 75     |

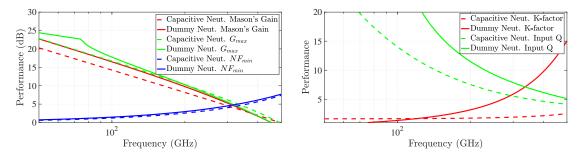

| 3.30  | Comparison of dummy-neutralized and capacitively-neutralized amplifiers (Post                                                |        |

| 0.01  | layout-extraction up to M1)                                                                                                  | 75     |

|       | Amplifier core transistors                                                                                                   | 76     |

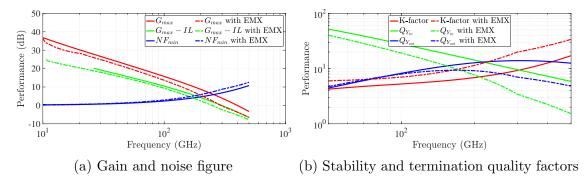

|       | Performance of the amplifier core with RC-extraction and EMX                                                                 | 77     |

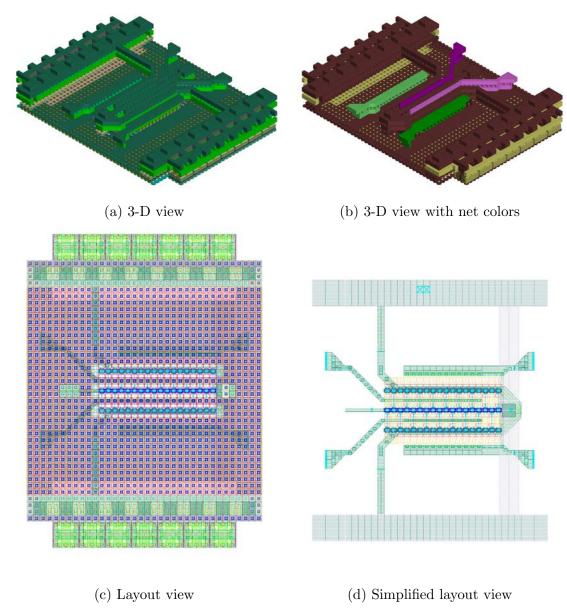

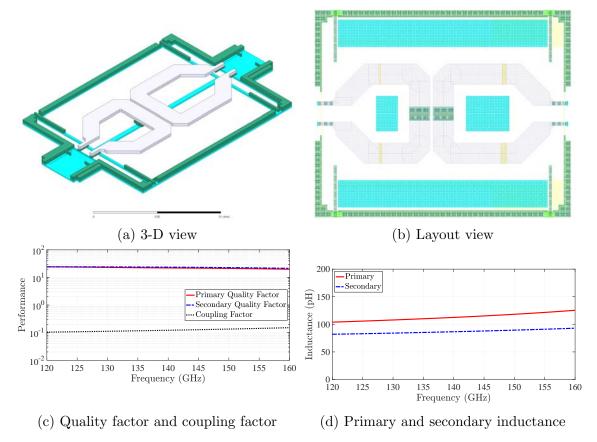

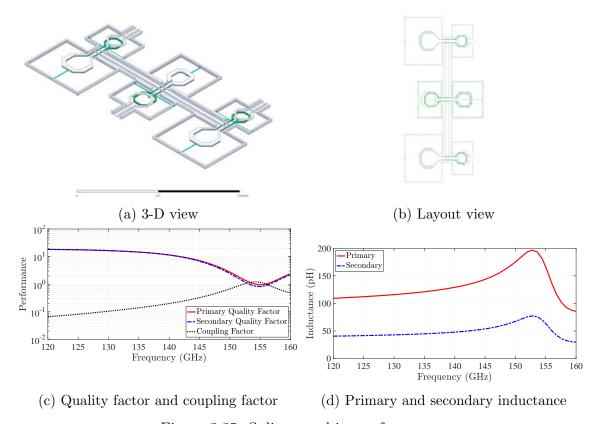

|       | Interstage transformer                                                                                                       | 77     |

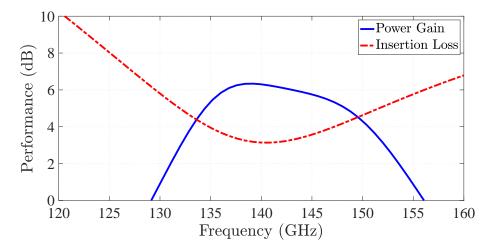

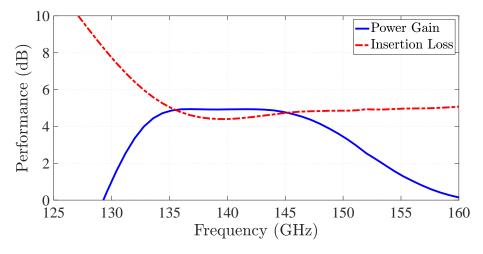

|       | Performance of interstage amplifiers                                                                                         | 78     |

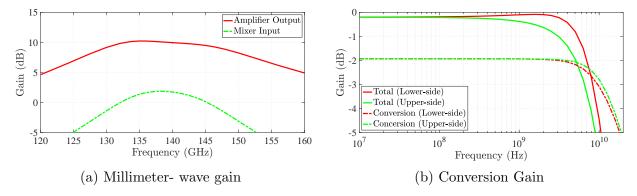

|       | Splitter and its performance                                                                                                 | 79     |

| 3 3 D | T BEIGNERS OF A LEADERHEEDER HIND WILL DILLDFOIL LOTTHINGTIONS                                                               | $\sim$ |

| 3.37         | Performance of the amplifier driving the splitter with the insertion loss of the splitter | 30         |

|--------------|-------------------------------------------------------------------------------------------|------------|

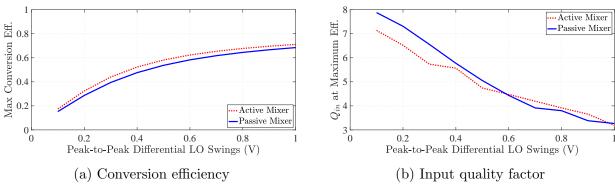

| 3 38         | •                                                                                         | 31         |

|              |                                                                                           | 31<br>82   |

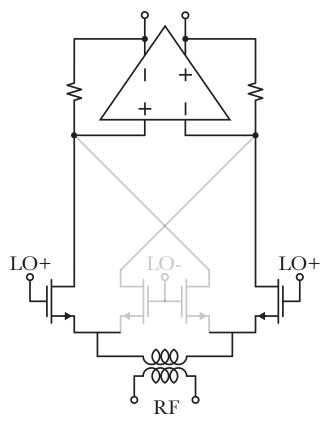

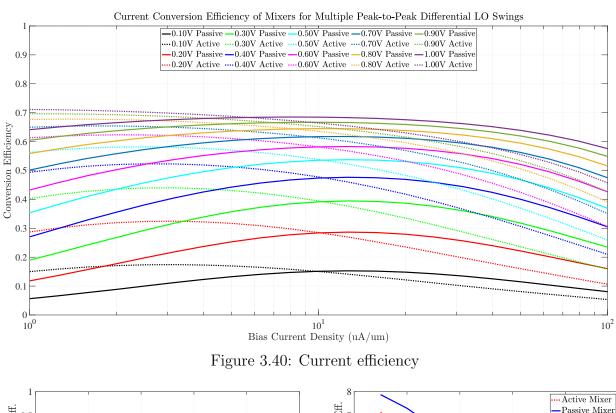

|              |                                                                                           | 32<br>33   |

|              | Comparison of peak current conversion efficiency and corresponding input quality          | <i>)</i> • |

| 0.41         |                                                                                           | 33         |

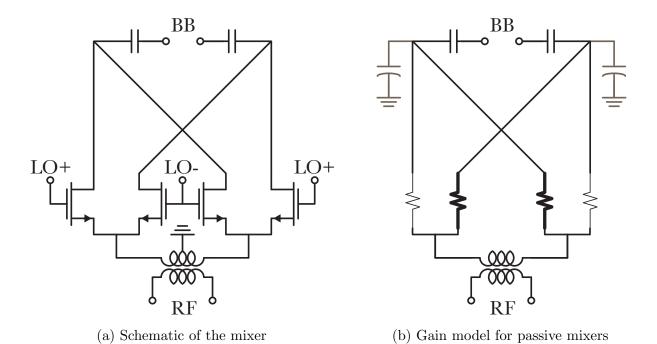

| 3 49         |                                                                                           | 34<br>34   |

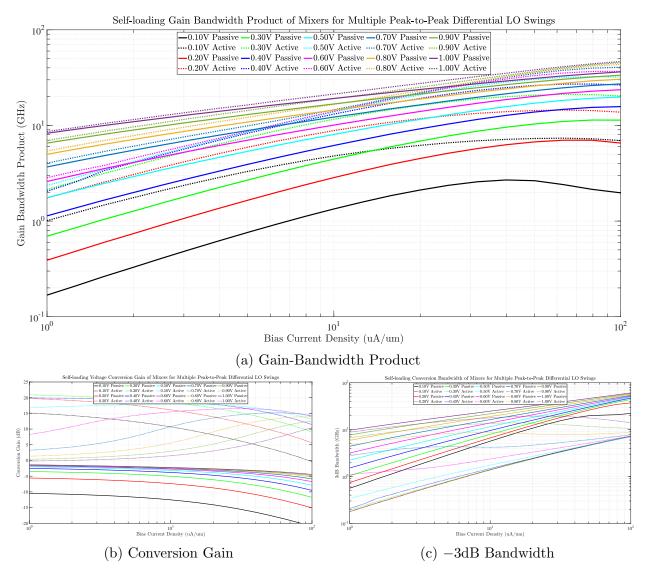

|              | Comparison of active and passive mixers in voltage mode with different peak-to-           | <u>-</u> ر |

| J.4J         |                                                                                           | 36         |

| 2 11         | •                                                                                         | 30<br>87   |

|              | •                                                                                         | ) (        |

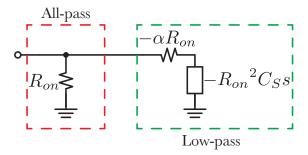

| 3.43         | Decomposition of the impedance seen by the equivalent source into an all-pass             | o =        |

| 2 46         | ±                                                                                         | 37         |

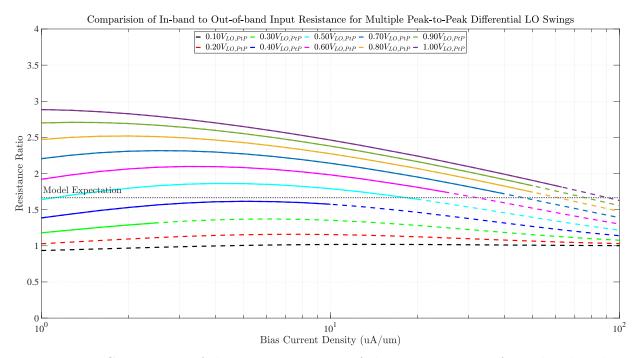

| 3.40         | Comparison of the input resistance of the passive mixers for in-band and out-of-          |            |

|              | band tones. The dashed portion of each line shows the region where the gain falls         | ٦ <b>،</b> |

| 9 47         | $\pi$                                                                                     | 39<br>20   |

|              |                                                                                           | 36         |

|              | 1                                                                                         | 9(<br>21   |

|              | , I I [ ]                                                                                 | 91         |

|              | 1 1 30                                                                                    | 94<br>25   |

|              |                                                                                           | 97<br>27   |

|              |                                                                                           | 97         |

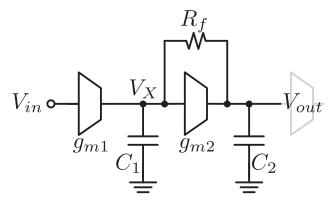

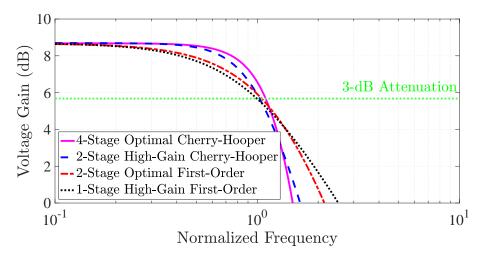

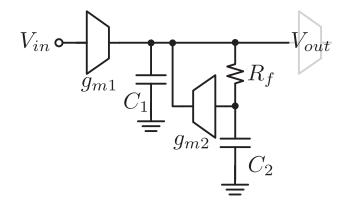

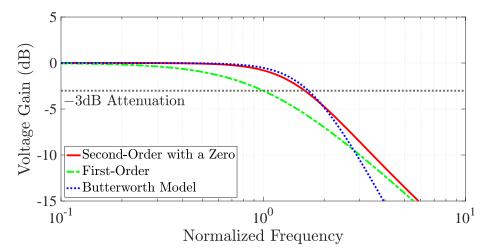

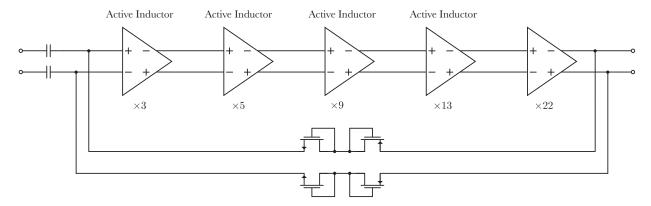

| <u>ა.</u> ეა | Comparison of the voltage gain in an amplifier with active inductor with its first-       | ٦,         |

| 0 5 4        | ±                                                                                         | 96<br>36   |

|              | ±                                                                                         | 96         |

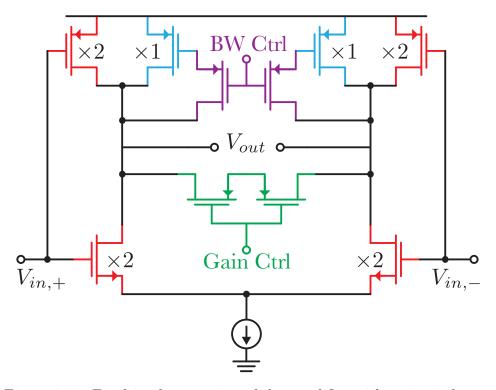

|              | Final implementation of the amplifier with active inductor                                |            |

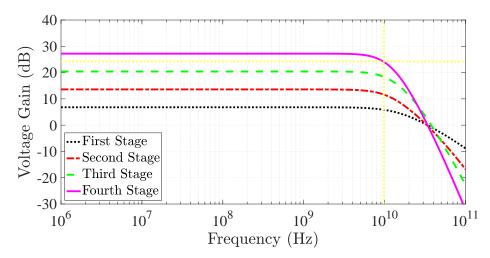

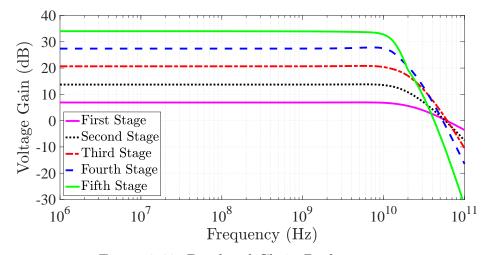

|              | Performance of cascaded active inductor stages                                            |            |

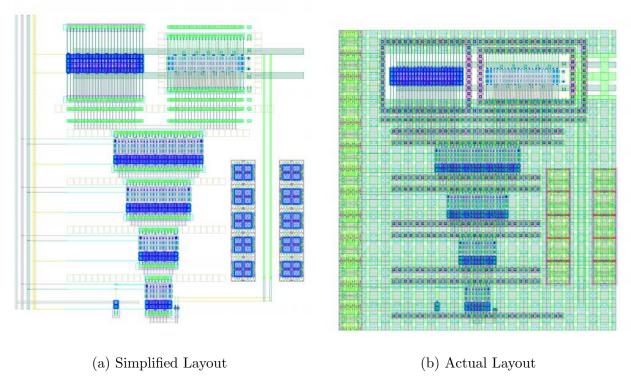

|              | Baseband chain                                                                            |            |

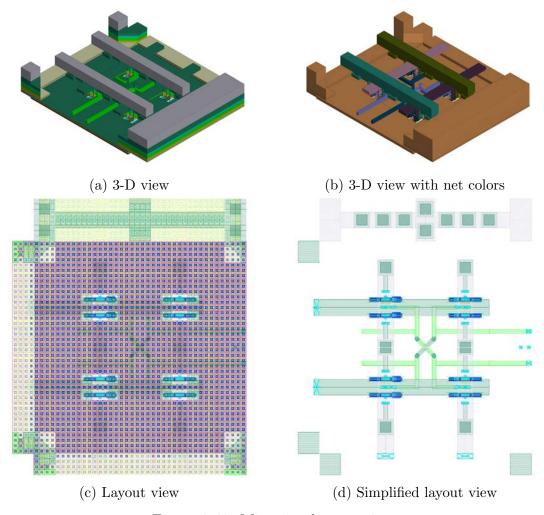

|              | The layout of the baseband amplifier                                                      |            |

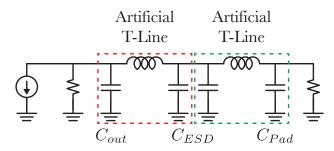

|              | Using an artificial T-line to increase the bandwidth                                      |            |

|              | Baseband Chain Performance                                                                |            |

|              | The layout of the baseband amplifier                                                      |            |

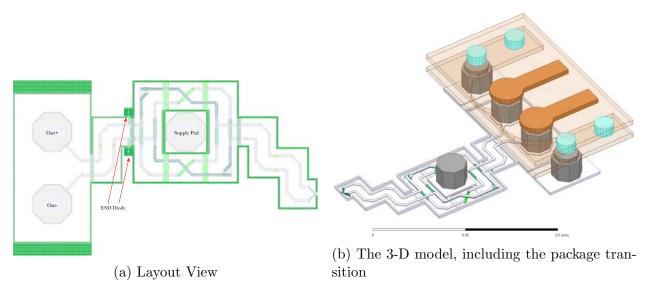

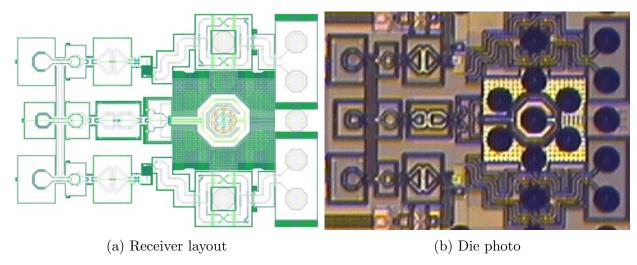

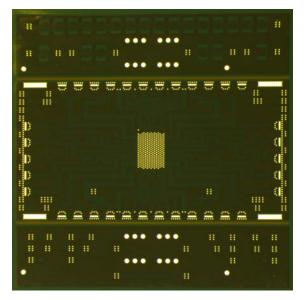

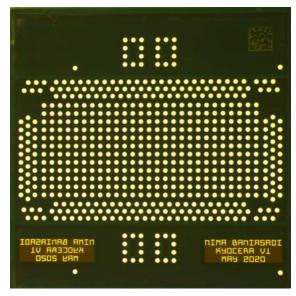

|              | 140GHz receiver taped out in 28nm CMOS technology                                         |            |

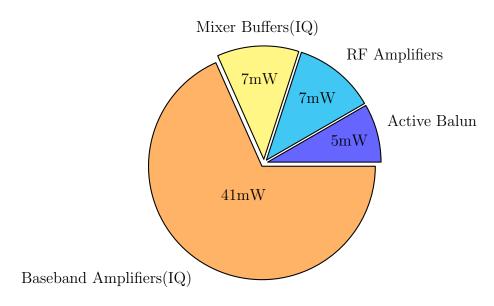

|              | Power consumption of the receiver                                                         |            |

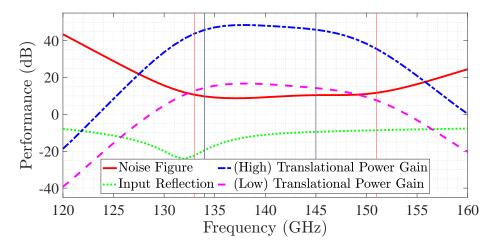

|              | Performance of the receiver chain                                                         |            |

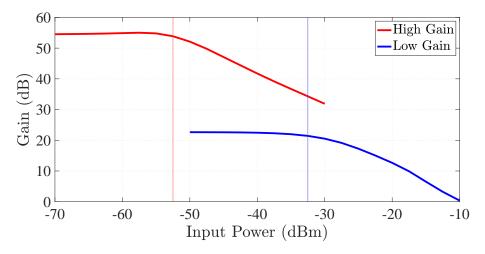

| 3.65         | Translation gain vs. input power                                                          | )(         |

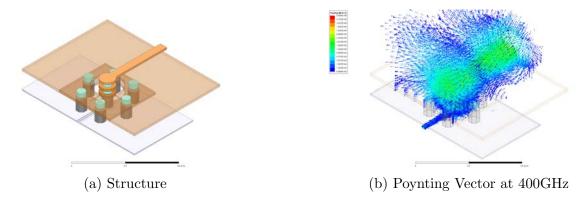

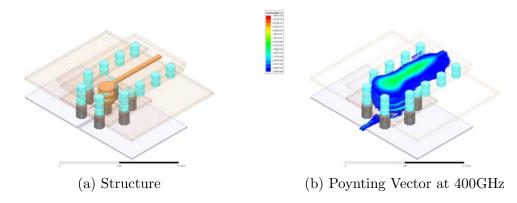

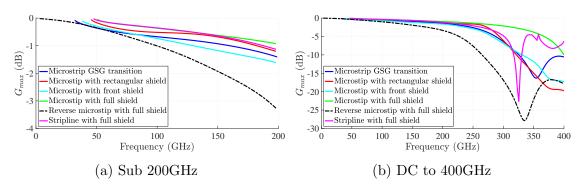

| 4.1          | Conventional microstrip GSG pads                                                          | )(         |

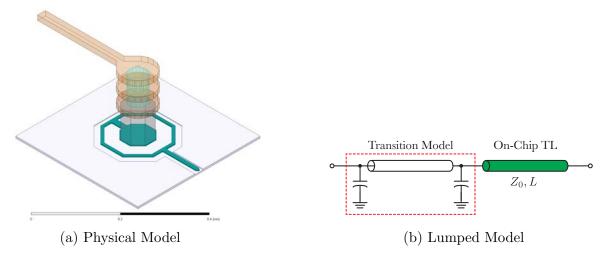

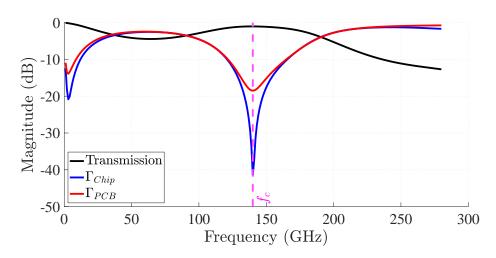

| 4.2          | Modeling the microstrip transition with transmission lines                                | )6         |

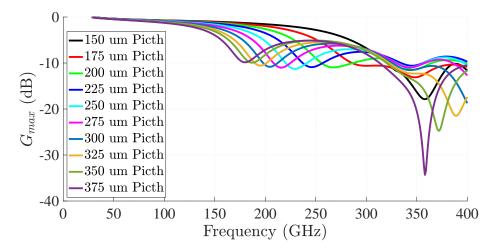

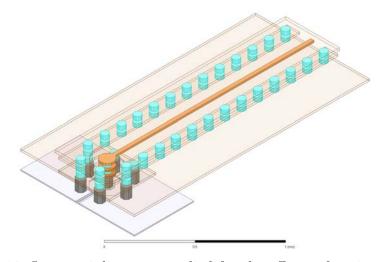

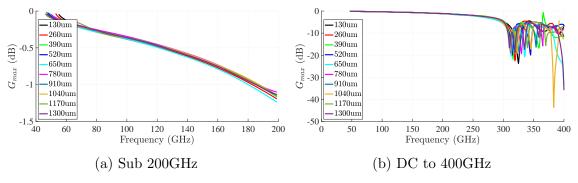

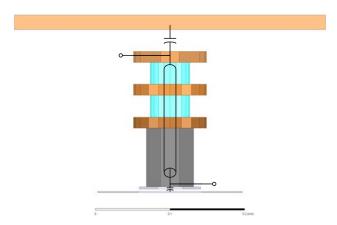

| 4.3          | $G_{max}$ versus frequency for different distances                                        | 11         |

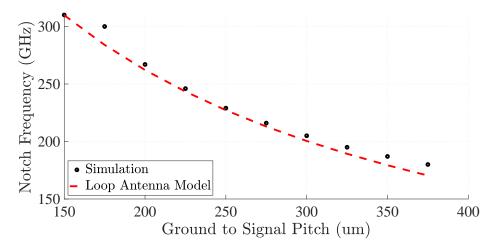

| 4.4          | Notch frequency of $G_{max}$ in the simulation versus the loop antenna model 1            | 11         |

| 15           | Microstrip with front shield                                                              | ۱،         |

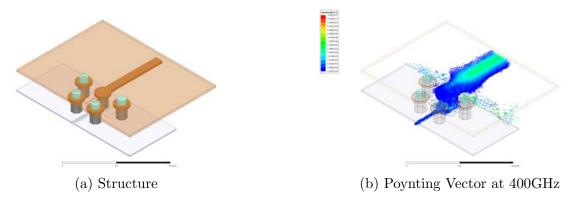

| 4.6  | Microstrip with rectangular shield                                                             | 112 |

|------|------------------------------------------------------------------------------------------------|-----|

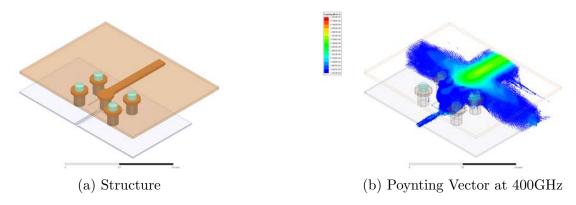

| 4.7  | Microstrip with full shield                                                                    | 113 |

| 4.8  |                                                                                                | 113 |

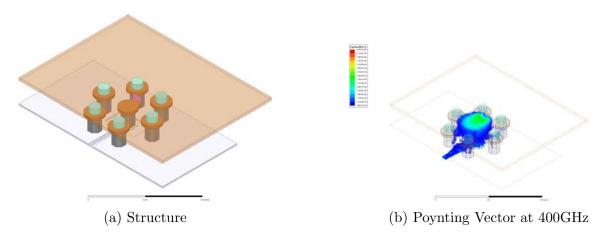

| 4.9  | Stripline with full shield                                                                     | 114 |

| 4.10 |                                                                                                | 114 |

| 4.11 |                                                                                                | 115 |

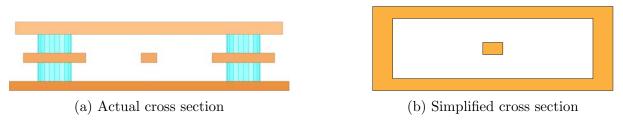

| 4.12 | Two propagation modes of the stripline cross section                                           | 115 |

| 4.13 | Characteristics of TEM and TE waves in striplines                                              | 116 |

| 4.14 | Difference between $G_{max}$ and $S_{21}$ in different lumped structures with $R = 10\Omega$ , |     |

|      |                                                                                                | 117 |

| 4.15 | Eigenmode simulation of resonant modes with different stripline length                         | 118 |

| 4.16 | Long striplines are studied for the effects of cavity resonance                                | 119 |

| 4.17 | $G_{max}$ of the stripline transition when the length of the stripline extension is varied     | 119 |

|      |                                                                                                | 120 |

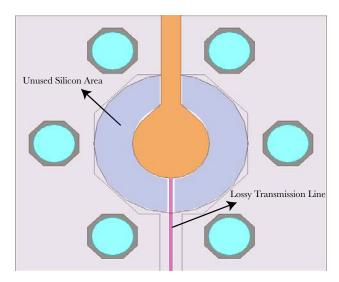

| 4.19 | Wasted silicon area and additional losses due to the access line                               | 120 |

| 4.20 | The final design of the transition with a suitable matching network                            | 121 |

|      |                                                                                                | 121 |

| F 1  |                                                                                                |     |

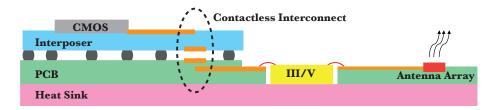

| 5.1  | Proposed millimeter-wave phased array packaging solution with integrated III/V                 | 101 |

| - 0  |                                                                                                | 124 |

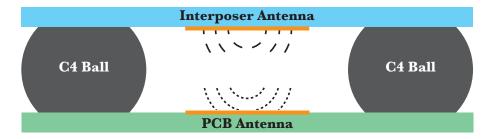

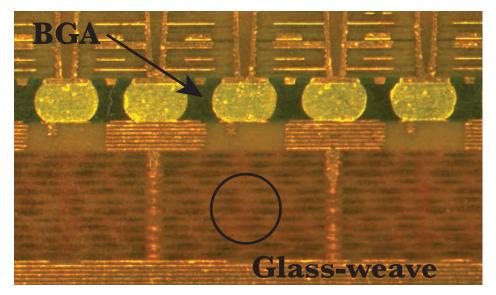

| 5.2  | 1 0                                                                                            | 125 |

| 5.3  | 1 0                                                                                            | 126 |

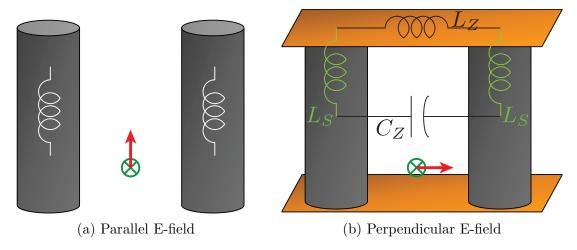

| 5.4  |                                                                                                | 127 |

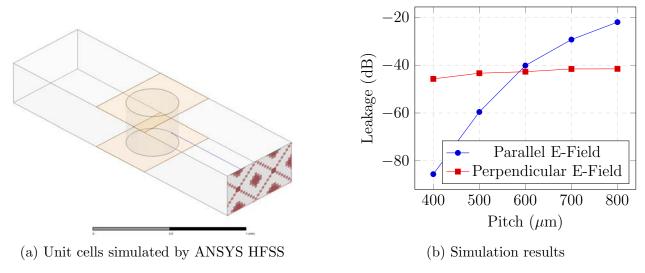

| 5.5  | Simulation results for the leakage of an incident wave with the frequency of                   |     |

|      | 140GHz with different E-field polarization upon arrival to a shorted BGA with                  | 100 |

| r c  |                                                                                                | 128 |

| 5.6  |                                                                                                | 129 |

| 5.7  | O 1                                                                                            | 129 |

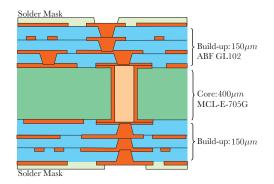

| 5.8  | •                                                                                              | 130 |

| 5.9  | 1                                                                                              | 131 |

| 5.10 | 1                                                                                              | 131 |

|      |                                                                                                | 132 |

|      |                                                                                                | 132 |

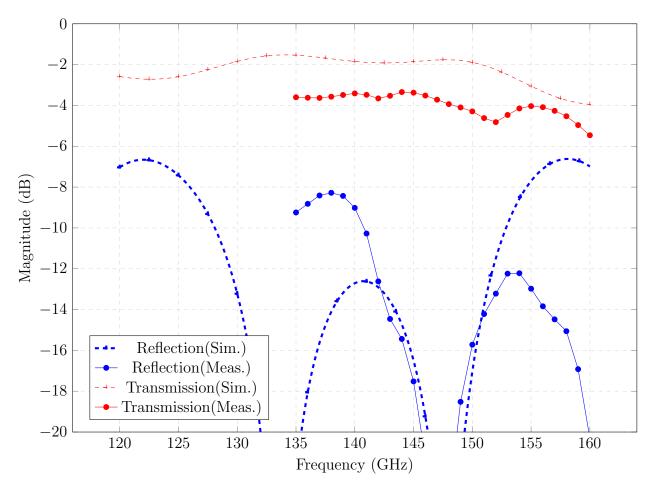

| ა.13 | Simulation and measurement results for a back-to-back millimeter-wave contact-                 | 199 |

|      | less interconnect                                                                              | 133 |

| 6.1  | Estimating the noise measure of an amplifier including the inserion loss of the                |     |

|      | 1                                                                                              | 135 |

|      |                                                                                                |     |

# List of Tables

| 1.1 | Microwave and fiber consideration $[4]$                           | 3   |

|-----|-------------------------------------------------------------------|-----|

| 1.2 | A numerical example of an optimal over-the-air communication link | 12  |

| 1.3 | Model values                                                      | 24  |

| 2.1 | Parameter values used for calculations                            | 41  |

| 3.1 | Summery of different matching network design methodologies        | 56  |

| 3.2 | Comparison of the baseband amplifier with earlier work            | 101 |

| 3.3 | Comparison of the receiver with the state-of-the-art              | 105 |

| 4.1 | Performance of the final design                                   | 121 |

| 4.2 | Summary of performance and comparison with the state-of-the-art   | 122 |

### Acknowledgments

I want to express my profound gratitude to my research advisor, Prof. Ali M. Nikne-jad. He provided me with excellent academic guidance and supported me personally, and taught me to be patient when facing various problems. I also thank Prof. Mehrdad Sharif Bakhtiar and Prof. Ali Fotowat Ahmady, my undergraduate professors at Sharif University of Technology, from whom I learned a lot.

This journey would not have been possible without the support of my family and friends. I am grateful to my parents and brother; they have always helped me wherever and whenever I needed them the most. I would also like to thank my friends who provided me with a warm and supportive environment during the years of the pandemic and political crisis.

## Chapter 1

### Introduction

### 1.1 Connectivity

The internet has become an essential part of daily life over the last three decades. The need for a stable Internet connection is so high that it can be considered an additional layer to Maslow's hierarchy of human needs (Fig. 1.1). For example, during the COVID-19 crisis, the internet played a crucial role in keeping people connected despite physical isolation.

Although the speed of the internet has increased dramatically, user demand has also increased exponentially, and it continues to grow. For example, 5G subscriptions will reach 4.4 billion by 2027 (Fig. 1.2). While Internet Service Providers (ISPs) are upgrading their infrastructure to meet users' needs, they need to keep costs low in such a competitive environment where operators demand 99.999% availability (about 5 minutes of downtime per year) [5].

Subsequent generations of mobile communications have smaller cells for higher spectral efficiency and lower path loss in free space. Fig. 1.3 shows the required backhaul capacity, which is in the tens of Gbps.

Operators have the choice to deploy different technologies. For a detailed comparison of fiber and wireless technologies and their tradeoffs, see Table. 1.1 and Fig. 1.4.

Fiber optic cables are often prohibitively expensive to deploy, and they are still prone to breaks and lengthy disruptions. However, they will be essential for core and inner-city aggregation sites with extremely high capacity requirements. Microwave and millimeter bands are suitable for heterogeneous network backhaul because they allow outdoor cell sites and network aggregation of traffic from multiple base stations, which can then be handed off to mobile switching centers and the core network at the end [6]. Note that tower placement

Figure 1.1: Maslow's hierarchy of human needs with an additional new layer [1]

Figure 1.2: Mobile subscriptions by technology (billions)

is not always required in urban areas (antennas can be mounted on rooftops, for example). Therefore, wireless will be used mainly in urban and densely populated areas as the last mile access. It is predicted that between 2021 and 2027, more than 60% of cellular base stations will be connected via microwaves and millimeter waves[7].

Wireless communication in licensed frequency bands increases ISP costs. However, as

|                            |          | 2020            | 2022            | 2025          |

|----------------------------|----------|-----------------|-----------------|---------------|

|                            | Urban    | 250Mbps-500Mbps | 450Mbps-5Gbps   | 3Gbps-10Gbps  |

| selective 5G               | Suburban | 100Mbps-250Mbps | 200Mbps—1Gbps   | 500Mbps-3Gbps |

|                            | Rurol    | 50Mbps-100Mbps  | 75Mbps-250Mbps  | 200Mbps-1Gbps |

|                            | Urban    | 500Mbps-1Gbps   | 1Gbps-10Gbps    | 5Gbps-20Gbps  |

| sb/46 and<br>ubiquitous 5G | Suburban | 200Mbps-500Mbps | 500Mbps-2Gbps   | 1Gbps-5Gbps   |

|                            | Rural    | 100Mbps-150Mbps | 150Mbps-350Mbps | 300Mbps-2Gbps |

Figure 1.3: Backhaul capacity per distributed site

|                 | Wireless                          | Fiber                             |

|-----------------|-----------------------------------|-----------------------------------|

| Capacity        | Up to several Gbps                | Unlimited                         |

| Regulation      | Requires spectrum                 | Requires right of ways            |

| Deployment Time | Fast deployment time              | Increases linearly with distance  |

| Deployment Cost | Increases partially with distance | Increase linearly with distance   |

| Terrain         | Requires line-of-sight between    | Costly when trenching in          |

|                 | two end-points                    | difficult terrain (if accessible) |

| Climate         | Prone to weather conditions       | Normally, not affected            |

Table 1.1: Microwave and fiber consideration [4]

the carrier frequency increases, spectrum costs decrease (Fig. 1.6). On the other hand, the cost of equipment increases as the carrier frequency increases. However, new semiconductor technologies and novel circuit designs reduce these costs. Therefore, using higher carrier frequencies is cost-beneficial to the ISP and subsequently to the end-user.

### 1.2 Capacity

In this section, the relationship between the link's capacity and the carrier frequency is investigated. Based on Shannon's theorem, the channel capacity C is given by

$$C = \frac{1}{\ln 2} B \ln (1 + SNR) \tag{1.1}$$

Figure 1.4: Mobile backhaul technology trade-Offs

Figure 1.5: Global backhaul media distribution

Assuming a white profile for thermal noise,  $SNR = \frac{P_r}{\kappa B}$  and the capacity is

$$C = \frac{1}{\ln 2} B \ln \left( 1 + \frac{P_r}{\kappa B} \right) \tag{1.2}$$

where  $\kappa$  is the background noise level. It is not immediately clear whether increasing the total bandwidth contributes to the increase in channel capacity or not, since a higher bandwidth allows for a higher thermal noise. Further investigation of this relationship,

$$\frac{\partial C}{\partial B} = \ln\left(1 + \frac{P_r}{\kappa B}\right) - \frac{1}{1 + \frac{\kappa B}{P_r}} \tag{1.3}$$

Figure 1.6: Cost of spectrum vs. cost of equipment over time

shows that increasing the absolute bandwidth always increases the capacity, since  $\frac{\partial C}{\partial B} > 0$ . Since B represents the absolute bandwidth, the same capacity can be obtained for different carrier frequencies  $(f_c)$ . Defining the fractional bandwidth as

$$B_F = \frac{B}{f_c} \tag{1.4}$$

most radio systems support a limited fractional bandwidth. There are several reasons for this, to name a few:

- Despite the existence of ultra-wideband antennas, most high-efficiency antennas have a relatively limited fractional bandwidth.

- High-frequency circuits tend to use resonators to compensate for the parasitic capacitance of the various elements. The Bode-Fano criterion [8] places an upper limit on the achievable bandwidth when parasitic reactive elements are present.

Therefore, it seems reasonable to use higher carrier frequencies to achieve higher capacity at a given fractional bandwidth (Fig. 1.7). However, as explained in the next section, it should be kept in mind that power generation at higher frequencies is less efficient, and the generated power is attenuated when propagating through the air. Therefore, THz radio systems use phased arrays to generate higher power. Note that phased arrays can increase

Figure 1.7: Capacity vs. carrier frequency

the directivity of the radiation compared to other power combining techniques, resulting in a higher EIRP<sup>1</sup>.

In the non-ionizing frequency range of the electromagnetic spectrum, safety protocols [2] limit the output power of each radiator to avoid electrostimulation of nerve and muscle cells (mainly below 1MHz) or excessive tissue heating. Based on Fig. 1.8, the power density  $(P_D)$  is defined as

$$P_D = \frac{P_t G_t}{4\pi d^2} \tag{1.5}$$

should be less than  $10 \mathrm{W \, m^{-2}}$ , where  $P_t$  is the transmit power and  $G_t$  is the antenna gain, and d is the minimum distance in any direction from any part of the radiating structure to the user's body. The FCC<sup>2</sup> currently regulates the maximum EIRP level, which must be below  $55 \mathrm{dBm/MHz}[9, 10]$  for a wide range of frequencies to ensure user safety. While service providers should adhere to this limit, power generation in the millimeter-wave band becomes extremely difficult, and most of these systems have limited total output power. Based on

Figure 1.8: Safe radiation levels for persons in unrestricted environments [2].

<sup>&</sup>lt;sup>1</sup>Equivalent Isotropically Radiated Power

<sup>&</sup>lt;sup>2</sup>Federal Communications Commission

Friis's formula, the received power is

$$P_r = P_D \frac{\lambda^2 G_r}{4\pi} \tag{1.6}$$

where  $\lambda$  is the wavelength and  $G_r$  is the antenna gain of the receiver. The effective area  $A_e$  of the receiver is defined as

$A_e = \frac{\lambda^2 G_r}{4\pi} \tag{1.7}$

With a continuous wave approximation of  $\lambda \approx \frac{v}{f_c}$  and a maximum output EIRP of  $P_{max} = P_t G_t|_{max}$ , the channel capacity can be written as

$$C = \frac{1}{\ln 2} B_F f_c \ln \left( 1 + \frac{\frac{P_{max}}{4\pi d^2} \frac{\lambda^2 G_r}{4\pi}}{\kappa B_F f_c} \right)$$

$$\tag{1.8}$$

$$= \frac{1}{\ln 2} B_F f_c \ln \left( 1 + \frac{v^2}{(4\pi)^2} \frac{1}{d^2} \frac{P_{max} G_r}{\kappa B_F} \frac{1}{f_c^3} \right)$$

(1.9)

Assuming a user device with a single antenna and a fixed fractional bandwidth, the optimal carrier frequency for the maximum channel capacity can be found by solving the following equation.

$$\frac{\partial C}{\partial f_c} = 0 \tag{1.10}$$

With a change in the variables  $\mathfrak{X} = 1 + \frac{\mathfrak{S}}{f_c^3}$  and  $\mathfrak{S} = \frac{v^2}{(4\pi)^2} \frac{1}{d^2} \frac{P_{max} G_r}{\kappa B_F}$

$$C = \frac{1}{\ln 2} B_F \sqrt[3]{\frac{\mathfrak{S}}{\mathfrak{X} - 1}} \ln(\mathfrak{X}) \tag{1.11}$$

and

$$\frac{\partial C}{\partial \mathfrak{X}} = \frac{-1}{\ln 2} B_F \left( \frac{\mathfrak{S}}{3\sqrt[3]{\left(\frac{\mathfrak{S}}{\mathfrak{X}-1}\right)^2} \left(\mathfrak{X}-1\right)^2} \right) \left( \ln(\mathfrak{X}) - 3 + \frac{3}{\mathfrak{X}} \right)$$

(1.12)

The maximum capacity can be reached when

$$\mathfrak{X} = e^{W_0\left(\frac{-3}{e^3}\right) + 3} \approx 16.8\tag{1.13}$$

where e is the Euler's number and W(.) is the Lambert function. The important observation here is that for a maximum allowable transmitter EIRP and a fixed fractional bandwidth, the carrier frequency should be increased so that the total SNR at the end of the receive chain is approximately  $\approx 12 \text{dB}$ , suggesting that for a high-speed over-the-air communication (with a target bit error rate of  $10^{-3}$ ), low-order digital modulations such as QPSk or 16-QAM should be used <sup>3</sup>. Higher-order modulations increase the spectral efficiency, but the absolute

<sup>&</sup>lt;sup>3</sup>QPSK also has the advantage of allowing power amplifiers to operate at their saturated power.

bandwidth must be reduced to achieve the same bit error rate, which ultimately lowers the data rate. The maximum channel capacity of

$$C_{max} \approx \sqrt[3]{\frac{4.2v^2}{(4\pi)^2} \frac{1}{d^2} \frac{P_{max}G_r}{\kappa} B_F^2}$$

(1.14)

is obtained when the carrier frequency is chosen as

$$f_{c,opt} \approx \sqrt[3]{\frac{1}{15.8} \frac{v^2}{(4\pi)^2} \frac{1}{d^2} \frac{P_{max} G_r}{\kappa B_F}}$$

(1.15)

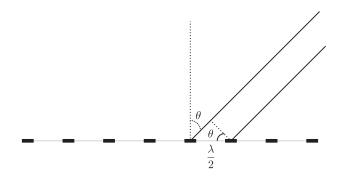

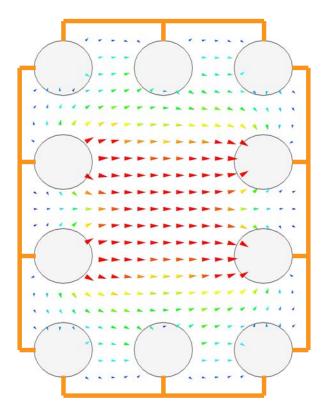

Figure 1.9: An 8 × 8 2-D transmitter phased array with 1-D steering capability.

Now, let us consider the impact of phased arrays. Fig. 1.9 represents an example of  $N \times N$  2-D phased array that is steerable in one dimension only. In this figure, the black squares represent patch antennas that are series-fed. Assuming that each PA has a maximum output power of  $P_e$  per element, the total radiated power is

$$P_{max} = N \times P_e \tag{1.16}$$

In practice, the routing loss and the antenna's efficiency should also be considered. As for the directivity of the array, an  $N \times N$  array of antennas with  $\frac{\lambda}{2}$  spacing provides a directivity of  $N^2$ . Moreover, patch antennas provide an additional advantage since these antennas radiate from the front side and ideally have no backside radiation. Hence,

$$G_t = 2N^2 (1.17)$$

which sets the maximum EIPR as

$$P_{max} = 2N^3 P_e (1.18)$$

Figure 1.10: An  $8 \times 8$  2-D receiver phased array

For example, if each PA has 0dBm of output power, EIRP of 30dBm can be achieved.

The receiver side is a bit more challenging. First, let us consider a fully passive power combining for the phased array as depicted in Fig. 1.10a. Assuming the same patch antenna,

$$G_r = 2N^2 \tag{1.19}$$

Recall that the available noise power of a passive device <sup>4</sup> in thermal equilibrium is equal to kT [8], where k is the Boltzmann constant and T is the absolute temperature. In other words, the use of multiple antennas does not affect the thermal noise power picked up from the ambient blackbody radiation. However, it does increase the directivity of the antennas. It may be difficult to understand why the power level of the radiation noise remains constant despite the combined noise of multiple antennas. The reason is that a passive loss-less power combiner with more than two matched ports does not exist [8]. Therefore, the passive combiner will either partially dissipate or reflect the power to the antennas. Another view is that the thermal noise of the individual elements is generally considered uncorrelated. In contrast, the radiation noise picked up by the different antennas is correlated because it has the same origin, namely the environment. Therefore, different sources can add constructively or destructively after the combiner. The important observation is that the SNR increases by a factor  $G_r$  when the antenna array is used. After the LNA, the input-referred noise of the LNA  $(\mathfrak{N}_{LNA})$  is added directly to the output. Let us now consider the active array from Fig. 1.10b. In this case, the N uncorrelated noise powers of the LNAs are visible at the output. However, since the signal adds correlatedly in the voltage domain, it is amplified by  $N^2$ . The ambient thermal noise at the input of each LNA is preserved as kT because the

<sup>&</sup>lt;sup>4</sup>Including passive antennas and passive power combiners.

passive structures are in thermal equilibrium. However, since they are partially correlated, the correct method to determine the noise level at the output due to the ambient thermal noise (Fig. 1.11) is to use

Figure 1.11: 1-D Phased Array

$$V_{\mathfrak{N},out} = \sum_{m=1}^{N} \left[ \iint v_{\mathfrak{N}}(\theta', \phi') e^{jm\pi \sin(\theta')} g_m(\theta', \phi') \sin(\theta') d\theta' d\phi' e^{-jm\pi \sin(\theta)} \right]$$

(1.20)

where  $v_{\mathfrak{N}}(\theta', \phi')$  is the thermal noise source at different spherical locations,  $g_m(\theta', \phi')$  is the effective gain of each group of passive antennas for each noise source in spherical coordinates,  $\frac{\lambda}{2}\sin(\theta')\frac{2\pi}{\lambda}=\pi\sin(\theta')$  is the phase delay of each noise source to each set of antennas, and  $-\pi\sin(\theta)$  is the correction phase that the phased array processor must apply to steer its beam toward the angle of incidence  $\theta$ . If we assume that each group of antennas is isolated from others (which is not necessarily true [11]), the gain of all groups is approximately equal to  $g(\theta', \phi')$  and

$$\overline{V_{\mathfrak{N},out}}^2 = \iint \overline{(v_{\mathfrak{N}}(\theta', \phi')g(\theta', \phi'))^2} \left[ \sum_{m=1}^N e^{jm\pi(\sin(\theta') - \sin(\theta))} \right]^2 \sin(\theta')d\theta'd\phi'$$

(1.21)

Note that if each group of antennas has a radiation resistance of R,

$$\iint \overline{(v_{\mathfrak{N}}(\theta', \phi')g(\theta', \phi'))^2} \sin(\theta')d\theta'd\phi' = 4kTR$$

(1.22)

since each group of antennas is in thermal equilibrium. If we assume that ambient thermal noise power coming from different directions is equal  $(v_{\mathfrak{N}}(\theta',\phi')^2 = \overline{v_{\mathfrak{N}}^2})$  and each group of series-fed antennas has a uniform radiation distribution in the  $\theta'$  axis  $(g(\theta',\phi')=g(\phi'))$ , Eq. 1.21 can be simplified to

$$\overline{V_{\mathfrak{N},out}}^2 = \int \overline{(v_{\mathfrak{N}}g(\phi'))^2} \int \left[ \sum_{m=1}^N e^{jm\pi(\sin(\theta') - \sin(\theta))} \right]^2 \sin(\theta') d\theta' d\phi'$$

(1.23)

Note that the term in the second integral is nothing but the total radiated power (in all directions) of N number of radiators normalized to the total radiated power of a single antenna, equal to N. It follows,

$$\overline{V_{\mathfrak{N},out}^2} = 4kTR \times N \tag{1.24}$$

In other words, there is no difference between passive and active combiners when it comes to the SNR of the received signal due to ambient thermal noise. The only difference is that when multiple LNAs are used in an active combiner, the noise of the LNAs is averaged. For the rest of this section, for simplicity, we consider active combiners with LNA amplification that provides the same signal power as the passive combiner  $(G_{P,LNA} = \frac{1}{N})$ . Therefore, the noise level of the Shannon's capacity equation is

$$\kappa = kT \frac{1}{N} \left( N + N \left( \mathcal{F}_{LNA} - 1 \right) \right)$$

(1.25)

$$=kT\mathcal{F}_{LNA} \tag{1.26}$$

where  $\mathcal{F}_{LNA}$  is the linear noise figure of the LNA. Now, maximum channel capacity and optimum carrier frequency can be calculated as

$$C_{max} \approx \sqrt[3]{\frac{4.2v^2}{(4\pi)^2} \frac{1}{d^2} \frac{4N^5 L^2 P_e}{kT \mathcal{F}_{LNA}} B_F^2}$$

(1.27)

$$f_{c,opt} \approx \sqrt[3]{\frac{1}{15.8} \frac{v^2}{(4\pi)^2} \frac{1}{d^2} \frac{4N^5 L^2 P_e}{\text{kT} \mathcal{F}_{LNA} B_F}}$$

(1.28)

where L models the routing loss and radiation efficiency of the antennas. As a numerical

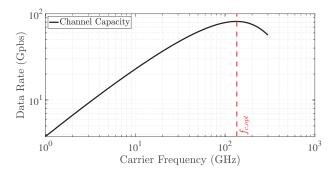

Figure 1.12: Channel capacity vs. carrier frequency for a link based on Table. 1.2

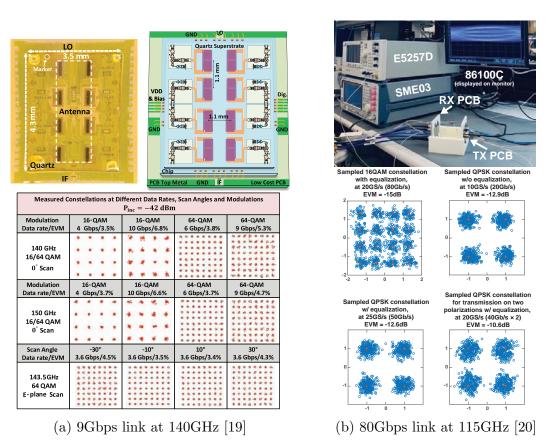

example (Table. 1.2), in an  $8 \times 8$  1-D steerable phased array where each PA generates 3dBm output power followed by -3dB routing loss, 30dBm EIRP is generated at the transmitter side. Assuming a noise figure of 12dB for the LNAs, a carrier frequency of 135GHz is suitable for 15% fractional bandwidth (20GHz absolute bandwidth) at a distance of 10m. Such a

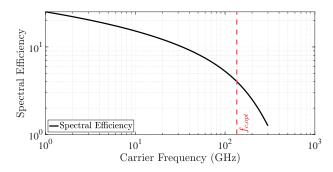

Figure 1.13: Spectral efficiency vs. carrier frequency for a link based on Table. 1.2

| Parameter           | Value           | Description                                             |  |

|---------------------|-----------------|---------------------------------------------------------|--|

| N                   | 8               | Number of antennas in each axis of the TRX phase arrays |  |

| $P_e$               | 3 dBm           | Output power of each PA element                         |  |

| $B_F$               | 15%             | Fractional bandwidth of radio                           |  |

| d                   | $10 \mathrm{m}$ | Distance between receiver and transmitter               |  |

| L                   | -3dB            | Routing loss on PCB                                     |  |

| $\mathcal{F}_{LNA}$ | 12dB            | Noise figure of millimeter-wave LNAs                    |  |

| EIRP                | 30dBm           | Equivalent Isotropic Radiated Power                     |  |

| $f_{c,opt}$         | 135GHz          | Optimum carrier frequency for the maximum capacity      |  |

| $C_{max}$           | 81Gbps          | Maximum channel capacity                                |  |

Table 1.2: A numerical example of an optimal over-the-air communication link

system can deliver a data rate of 81Gbps at maximum capacity (Fig. 1.12). It is clear that a simple QPSK modulation is sufficient to achieve the maximum data rate in this system, since SNR has been traded off for a higher data rate (Fig. 1.13). This is easy to understand since

$$C_{max} \approx 4B_F f_{c,opt} \tag{1.29}$$

The strength of phased arrays is easy to see here because  $C_{max} \propto \sqrt[3]{N^5}$ . However, the physical dimension of the array ultimately limits the number of antenna elements. Let  $W = N\frac{\lambda}{2}$  be the width of the antenna array,

$$f_{c,opt} \approx \pi dv \sqrt[2]{2.0 \frac{\text{kT} \mathcal{F}_{LNA} B_F}{W^5 L^2 P_e} v}$$

(1.30)

which shows that an optimal carrier frequency should be used for a fixed-size antenna array. The reader should note that the optimal carrier frequency increases as the number of antennas increases as  $f_{c,opt} \propto \sqrt[3]{N^5}$ , so that the total width of the antenna array is proportional to  $W_{opt} \propto \frac{1}{\sqrt[3]{N^2}}$ . Although increasing the number of elements without changing the carrier frequency increases the data rate, the channel capacity is suboptimal because a higher carrier frequency increases the data rate. For example, if the antenna array cannot occupy more

than  $1 \text{cm} \times 1 \text{cm}$ , a carrier frequency of 100GHz with a number of 6 antennas is optimal if the other parameters are taken from Table. 1.2. For a fixed array dimension, the optimal number of elements is

$$N_{opt} \approx \pi d \sqrt{7.9 \frac{1}{W^3} \frac{kT \mathcal{F}_{LNA} B_F}{L^2 P_e} v}$$

(1.31)

So far, increasing the number of elements has increased the channel capacity in the optimal case and made the array dimension smaller. It is easy to see that with this trend, the power density, defined as  $\frac{N \times P_e}{W_{opt}} \propto \sqrt[3]{N^5}$ , increases with the number of elements used in the array. The high power density makes the packaging of such arrays quite difficult, as they have to cope with higher heat dissipation.

Before concluding this section, let us consider device constraints and their impact on the link capacity. For a CMOS device, the minimum noise figure increases linearly with frequency.

$$\mathcal{F}_{min} = \gamma f_c \tag{1.32}$$

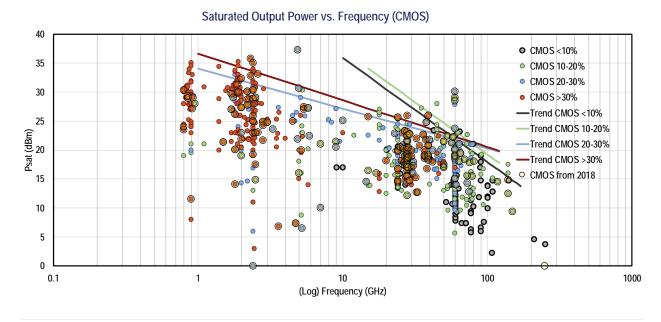

where  $\gamma$  is a technology-dependent proportionality factor. Moreover, the PA survey of

Figure 1.14: The output power of published power amplifiers as a function of carrier frequency[3]

Fig. 1.14 shows that the output power decreases with increasing carrier frequency as

$$P_{e,max} \propto \frac{\mathcal{P}}{f_c}$$

(1.33)

where  $\mathcal{P}$  is a technology-dependent factor. Now, considering Eq. 1.34

$$W_{opt} \approx \sqrt[5]{2.0\pi^2 \frac{k T \gamma B_F}{L^2 \mathcal{P}} v^3} \sqrt[5]{d^2}$$

(1.34)

This means that for a given technology and a fixed distance between two transceivers, an optimal array dimension can achieve the maximum data rate of communication.

### 1.3 Silicon limits

High carrier frequencies require fast transistors. While other compound semiconductors can achieve higher  $f_t$  and  $f_{max}$ , silicon remains the dominant semiconductor since it has unique capabilities in digital-intense designs. In this section, we will explore some of the limitations of the Bulk CMOS process as shown in Fig. 1.15.

Figure 1.15: A simple model of planar CMOS transistor.

Note that only the semiconductor device is considered here, and the parasitic impact of the back end of the line metallization is not considered. In practice, the performance of deep sub-micron devices is deteriorated by extrinsic parasitic elements.

### Transit Frequency $f_t$

For a CMOS device, the transit frequency  $f_t$  is defined as

$$f_{t} = \frac{1}{2\pi} \frac{g_{m}}{C_{gs}}$$

$$= \frac{1}{2\pi} \frac{\frac{\partial I_{ds}}{\partial V_{gs}}}{\frac{\partial Q_{gs}}{\partial V_{gs}}}$$

$$= \frac{1}{2\pi} \frac{\partial I_{ds}}{\partial Q_{gs}}$$

$$(1.35)$$

Assuming that the device operates under velocity saturation <sup>5</sup>, the maximum drain-source current is reached when all new charges on the source side  $(\partial Q_{gs})$  traverse the effective channel length  $(L_{eff})$  at the maximum saturation velocity  $(v_{sat})$ . This means

$$\partial I_{ds,max} = \partial Q_{gs} \frac{v_{sat}}{L_{eff}} \tag{1.36}$$

This means that for a CMOS process, there is a maximum limit to the  $f_t$  of the device

$$f_{t,max} = \frac{1}{2\pi} \frac{v_{sat}}{L_{eff}}$$

$$\tag{1.37}$$

To achieve higher current gain and higher transit frequency, either the channel length must be reduced, or the saturation velocity of carriers must be increased. While the latter can be achieved by channel engineering, scaling the channel length remains the main strategy to increase the operating speed of transistors. For example, for a 28nm CMOS node with a saturation velocity of  $10^7 \text{cm s}^{-1}$ , one can expect a maximum  $f_t$  of 570GHz. In practice, the effective channel length is about one-third of the drawn channel for the smallest channel length of each node, which can potentially increase the transition speed. On the other hand, the transition frequency is reduced by fringe capacitors and the gate-source and gate-drain overlap capacitors  $^6$ , negating any potential improvement from the smaller effective channel length. Once the parasitic capacitance of the back-end metallization is added, the transition frequency drops again.

### Analog Efficiency $f_t \frac{g_m}{I_d}$

Another commonly used metric for CMOS transistors is  $f_t \frac{g_m}{I_d}$ . It gives the analog efficiency of a transistor at a fixed current consumption. Although this metric is not useful for millimeter-wave circuit design, it is still instructive to examine the limits of this metric for a square-law

<sup>&</sup>lt;sup>5</sup>Diffusion currents are neglected.

<sup>&</sup>lt;sup>6</sup>For 28nm devices, the fringe capacitors of gate-drain and gate-source are about the same size as the channel capacitance, reducing the transition frequency by a factor of about 3.

device. Analog efficiency can be described as

$$f_{t} \frac{g_{m}}{I_{d}} = \frac{1}{2\pi} \frac{g_{m}}{C_{gs}} \frac{\frac{2I_{ds}}{V_{od}}}{I_{ds}}$$

$$= \frac{1}{\pi} \frac{g_{m}}{C_{gs}} \frac{1}{V_{od}}$$

(1.38)

where  $V_{od}$  is the overdrive voltage. Substitute  $g_m = \mu C_{ox} \frac{W}{L} V_{od}$  and  $C_{gs} = \frac{2}{3} C_{ox} WL$  into the previous equation, the analog efficiency can be calculated as

$$f_{t} \frac{g_{m}}{I_{d}} = \frac{1}{\pi} \frac{\mu C_{ox} \frac{W}{L} V_{od}}{\frac{2}{3} C_{ox} W L} \frac{1}{V_{od}}$$

$$= \frac{1}{\frac{2}{3} \pi} \frac{\mu}{L^{2}}$$

(1.39)

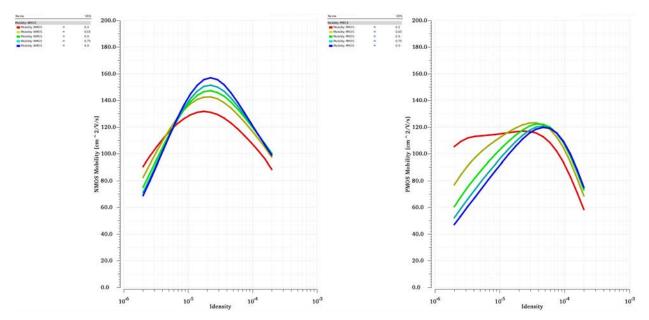

It should now be clear that for a square-law device with a fixed channel length, the maximum analog efficiency is achieved at a gate-source voltage that provides the highest mobility for the charges in the channel. Fig. 1.16 shows simulation results for NMOS and PMOS devices,

Figure 1.16: Estimating the mobility of the device from simulations for different current densities  $(A/\mu m)$

where the mobility of the device is given by

$$\mu = \frac{2}{3}\pi f_t \frac{g_m}{I_d} L^2$$

$$= \frac{2}{3}\pi \frac{g_m}{C_{GS} - C_{GD}} \frac{g_m}{I_d} L^2$$

(1.40)

Note that  $C_{gs}$ , the channel capacitance, is replaced by  $C_{GS} - C_{GD}$  to remove fringe capacitors. Note that, as expected [12], the NMOS device still performs better than its PMOS counterpart. However, as silicon doping increases, NMOS and PMOS devices become more similar.

### Speed-Power Trade-off

Johnson has shown [13] that for bipolar transistors, there is a relationship between the maximum current, the input impedance of the device, and the cutoff frequency of the device. The cutoff frequency is defined by  $f_T = \frac{1}{2\pi} \frac{1}{\tau}$ , where  $\tau$  is the average time required for a carrier to traverse the base at the saturated drift velocity. This definition agrees well with the maximum transit frequency defined earlier

$$f_T = f_{t.max} \tag{1.41}$$

Considering a CMOS process with a dielectric breakdown field of  $E_{Si}$ , the maximum drain-source voltage can be described as

$$V_{ds,max} = E_{Si}L_{eff} (1.42)$$

Thus, there is a relationship between the maximum drain-source voltage and the device cutoff frequency where

$$V_{ds,max}f_{t,max} = \frac{1}{2\pi}E_{Si}v_{sat} \tag{1.43}$$

A transistor with a transit frequency of 400GHz cannot generate more than 2 volts peak-to-peak drain-source voltage, assuming  $E_{Si} \approx 5 \times 10^5 \mathrm{V \, cm^{-1}}$  and  $v_{sat} \approx 10^7 \mathrm{cm \, s^{-1}}$ .

While the dielectric breakdown field sets a maximum drain-source voltage, any drainsource current can be achieved at the cost of increased input capacitance by connecting multiple devices in parallel. The load current through a charge control device is defined by

$$I_{ds} = \frac{Q_{ch}}{\tau} \tag{1.44}$$

where  $Q_{ch}$  is the total mobile charge in the channel, and  $\tau$  is the average charge transit time. To calculate the maximum current, we should assume the highest drift velocity, which sets  $\tau_{min} = \frac{v_{sat}}{L_{eff}}$ . Also, we assume a dielectric breakdown field of  $E_{ox}$  for the dielectric barrier between the gate and the channel,

$$Q_{max} = C_{gs} E_{ox} t_{ox} (1.45)$$

where  $t_{ox}$  is the oxide thickness. It follows that,

$$I_{ds,max} = C_{gs} E_{ox} t_{ox} \frac{v_{sat}}{L_{eff}} \tag{1.46}$$

If we define  $X_{f_T} = \frac{1}{2\pi f_T C_{gs}}$  as the reactive input impedance between gate and source, it is clear that

$$I_{ds,max}X_{f_T} = E_{ox}t_{ox} (1.47)$$

In other words, for a fixed impedance at the device cutoff frequency, the maximum drainsource current is fixed by the properties of the gate oxide. For most CMOS process nodes, the drain-source and gate-source breakdown fields are close to each other because the drain of the preceding transistors directly controls the gate nodes of digital circuits. For example, with  $E_{ox} = 14 \text{MV cm}^{-1}$  for silicon dioxide [14] and an oxide thickness of 1nm,

$$E_{ox}t_{ox} \approx E_{Si}L_{eff} \approx 1.5 \text{V}$$

(1.48)

For a CMOS process optimized for digital circuits,

$$I_{ds,max} = C_{gs} E_{ox} t_{ox} \frac{v_{sat}}{L_{eff}}$$

$$\approx C_{gs} E_{Si} L_{eff} \frac{v_{sat}}{L_{eff}}$$

$$\approx C_{gs} E_{Si} v_{sat}$$

$$(1.49)$$

Therefore, the relationship between the volt-ampere product (as an approximation for the maximum output power), the input impedance level  $(X_f = \frac{1}{2\pi f C_{gs}})$ , and the cutoff frequency of the transistor can be found as

$$f \times I_{ds,max} \times V_{ds,max} = f \frac{1}{2\pi} \frac{E_{Si} v_{sat}}{f_T} C_{gs} E_{Si} v_{sat}$$

$$= 2\pi f C_{gs} \left(\frac{E_{Si} v_{sat}}{2\pi}\right)^2 \frac{1}{f_T}$$

(1.50)

and thus,

$$f \times I_{ds,max} \times V_{ds,max} \times X_f = \left(\frac{E_{Si}v_{sat}}{2\pi}\right)^2 \frac{1}{f_T}$$

(1.51)

Note that

- increasing the cutoff frequency decreases the output power for a fixed technology and a fixed input impedance, and

- for a fixed input impedance, faster process nodes provide lower output power at a fixed operating frequency.

### Termination Levels vs. Frequency

The optimal large-signal termination load for maximum power transfer can be studied by finding the proper ratio of  $\frac{V_{ds,max}}{I_{ds,max}}$

$$R_{opt} = \frac{V_{ds,max}}{I_{ds,max}} = \frac{\frac{1}{2\pi} \frac{E_{Si}v_{sat}}{f_T}}{C_{gs}E_{Si}v_{sat}} = \frac{1}{2\pi f_T C_{qs}}$$

(1.52)

which shows that for a fixed input impedance level, output terminations should be smaller for faster process nodes

$$R_{opt} = X_f \frac{f}{f_T} \tag{1.53}$$

### Large Signal Power Gain vs. Frequency

In the simple model presented above, gate impedance is considered purely imaginary. It is generally not the case as the operating frequency of the transistor increases since one must consider the non-quasistatic model for the device. First, consider a resistor  $R_g$  in series with the gate capacitance. We will discuss the origins of this resistance later. Let us assume a small resistor,

$$I_{gs} = 2\pi f Q_{ch} \tag{1.54}$$

where  $Q_{ch}$  is the total mobile charge in the channel. Thus, the peak power dissipation at the series resistor is

$$P_{in} = \frac{1}{2} \left( 2\pi f Q_{ch} \right)^2 R_g \tag{1.55}$$

The maximum output current is

$$I_{ds} = \frac{Q_{ch}}{\tau_{min}} \tag{1.56}$$

and therefore the peak output power is

$$P_{out} = \frac{1}{2} \left(\frac{Q_{ch}}{\tau_{min}}\right)^2 R_L \tag{1.57}$$

where  $R_L$  is the terminating resistor. Assume that the terminating resistor  $R_L = R_{opt}$  is chosen,

$$P_{out} = \left(\frac{Q_{ch}}{\tau_{min}}\right)^2 \frac{1}{4\pi f_T C_{qs}} \tag{1.58}$$

and the power gain can be calculated as

$$G = \frac{P_{out}}{P_{in}}$$

$$= \frac{1}{(2\pi f Q)^{2} R_{g}} \left(\frac{Q_{ch}}{\tau_{min}}\right)^{2} \frac{1}{2\pi f_{T} C_{gs}}$$

$$= \frac{2\pi f_{T}}{(2\pi f)^{2}} \frac{1}{R_{g} C_{gs}}$$

(1.59)

Considering only the intrinsic device,  $R_g C_{gs}$  is the time constant for the redistribution of the channel charge in response to the gate excitation and can be calculated to be about  $\frac{1}{5} \sim \frac{1}{8} \times \frac{1}{2\pi f_t}$  for a square-law device [15]. The exact coefficient depends on the exact charge distribution in the channel. Therefore, we assume that  $\alpha$  represents this coefficient, which ranges between  $5 \sim 8$  for square-law devices and drops to smaller values ( $\approx 2$ ) for a uniform charge distribution. It follows,

$$G = \alpha \left(\frac{f_T}{f}\right)^2 \tag{1.60}$$

Interestingly, although the output power of faster process nodes tends to decrease for a fixed input impedance, the large-signal power gain improves when faster transistors are used. Defining  $f_{max}$  as the frequency at which the power gain drops to 0dB, we find that.

$$f_{max} \propto f_T$$

(1.61)

#### Detailed Model with Extrinsic Parasitics

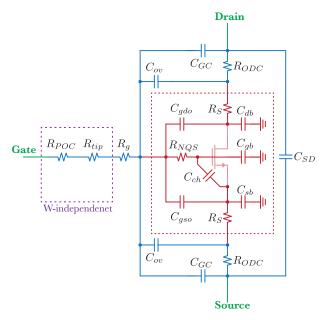

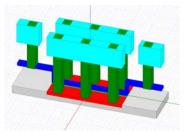

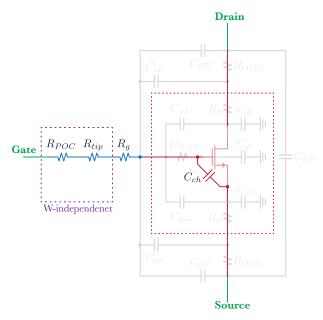

Fig. 1.17 shows a complex model of a transistor with the first layer of back-end metallization, and the different values are listed in Table. 1.3. The red components are calculated within the BSIM model, while the blue components extract the parasitic elements in the layout. These parasitic elements include:

•  $R_{tip}$  is the resistance from the edge of the via to the edge of the OD definition. In HKMG<sup>7</sup> processes, the work function of the metal is used to set the threshold voltage of the device. Therefore, devices with the same layout but different thresholds may have different series resistance and high-frequency response. While other parasitic components scale with the width of the device, the minimum  $R_{tip}$ , which corresponds to the shortest distance between the transistor and the poly contact, is fixed by the process capabilities.

<sup>&</sup>lt;sup>7</sup>HKMG: High-K Metal Gate

Figure 1.17: Parasitic elements of a single-finger transistor.

•  $R_{POC}$  is the poly contact resistance from the first metal layer (M1) to the gate metal (PO). It should be mentioned that some process nodes allow negative enclosure for the contact. It allows devices with a shorter channel length (and consequently faster  $f_t$ ), but the current crowding at the contact tip increases the contact resistance. Instead of using a single contact, the designer can use multiple contacts in parallel. It seems compelling, but since additional poly contacts are connected in series with the added resistance of the gate extension, the advantage is quickly exhausted. For example, for a single poly contact

$$R_{POC} + R_{tip} = 100 + 117\Omega$$

$$= 217\Omega \tag{1.62}$$

while two poly contacts

$$R_{POC} + R_{tip} = (100 + 117)||100 + 117\Omega$$

= 185\Omega (1.63)

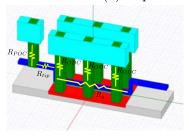

will only provide 15% of improvement. In contrast, using a double-sided contact, as shown in Fig. 1.18, halves the effective resistance  $R_{POC} + R_{tip}$  in series with  $R_g$  and improves the overall gate resistance by more than %50  $^8$ . Although the double-sided contact strategy is promising, it requires a complex layout and additional parasitic capacitance. Therefore, the double-sided contact should be used only when necessary.

<sup>&</sup>lt;sup>8</sup>Since the gate metal is driven from both sides, its effective resistance also decreases

•  $R_g$  is the series resistance of the metal gate on the active area (OD). For a planar transistor,

$$R_g = \alpha \rho_{MG} \frac{W}{t_{MG}L} \tag{1.64}$$

where  $t_{MG}$  is the thickness of the metal gate,  $\rho_{MG}$  is the resistivity of the metal used for the gate, and  $\frac{1}{2}$  assumes a simple T-model <sup>9</sup>. It should be mentioned that when a double-sided contact is used, the effective resistance of the metal gate decreases by a factor of 4.

- $C_{ch}$  is the channel capacitance. It is a nonlinear capacitance that depends strongly on the bias of the gate voltage and the response to large signals.

- $C_{gdo}$  and  $C_{gso}$  are the gate-drain and gate-source overlap capacitance modeled in the BSIM model. These are relatively linear, bias-independent capacitors generally symmetric on both the drain and source sides. While these capacitors are negligible for devices with long channels, they become comparable with the highest channel capacitance of the short channel device.

- Similarly,  $C_{ov}$  is the stray capacitance between gate to source and drain extracted from the layout extractor.  $C_{GC}$  also represents the coupling capacitor between gate and M1.

- $C_{sb}$  and  $C_{db}$  represent the source-bulk and drain-bulk junction capacitance, respectively, and  $C_{gb}$  represents the gate-bulk capacitance. This capacitor comes from the gate metal extensions running away from the active area. All these capacitors are weakly dependent on the gate bias voltage.

- $R_S$  models the resistance of the shallow drain-source junction extensions. It is one of the most critical limiting factors for the minimum switch resistance in digital circuits [16, 17]. Therefore, it is essential to model this resistance in a passive mixer properly. In analog and high-frequency applications, this physical resistor also generates thermal noise. It acts like a degeneration resistor in series with the device source and ultimately limits the device's transconductance.

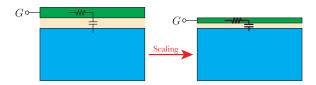

As mentioned earlier, the use of more advanced nodes improves the intrinsic cutoff frequency of the device. However, scaling is detrimental to the effect of back-end metallization. As shown in Fig. 1.19, as the technology scales, not only do the lateral dimensions (e.g., channel length and channel width of the transistors) scale but so do the vertical dimensions (e.g., the thickness of the metals and the thickness of the interlayer dielectrics). If the designer keeps the device's width constant from one technology node to another, driving the same transistor will result in higher power dissipation because the series resistance of the gate has increased. Therefore, despite improving the device's cutoff frequency, the device's power gain may not follow the same improvement. To illustrate this point, let us calculate

<sup>&</sup>lt;sup>9</sup>Most parasitic extraction programs use a T-model for the gate resistance.

(a) Top view of a single-sided contact

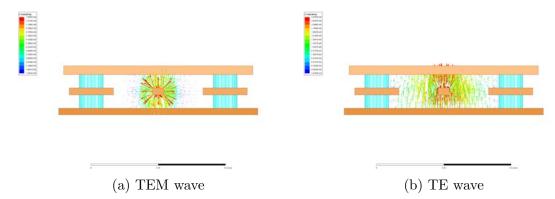

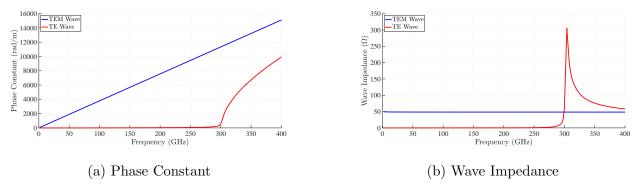

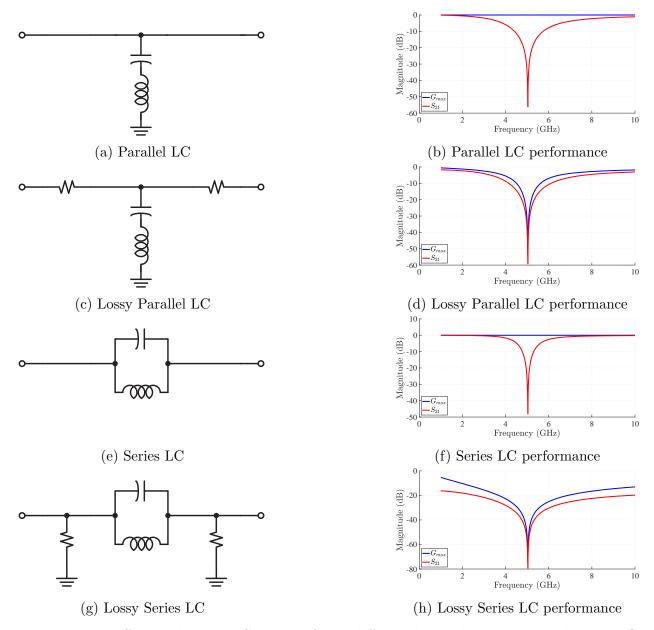

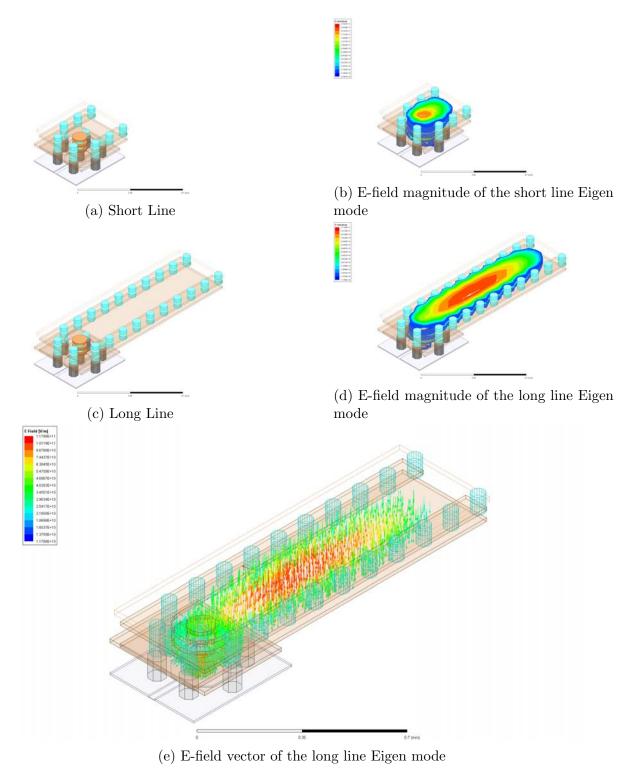

(b) Side view of a single-sided contact (c) Side view of a double-sided contact